# **Application Note** SLG46880/1 F(1) Block

**AN-CM-237**

# **Abstract**

This application note how to use the F(1) computation macrocell in the SLG46880/1.

This application note comes complete with design files which can be found in the References section.

# **Contents**

| Ab  | stract                                                                                               | 1   |

|-----|------------------------------------------------------------------------------------------------------|-----|

| Со  | ntents                                                                                               | 2   |

| Fig | jures                                                                                                | 2   |

| Tal | bles                                                                                                 | 2   |

| 1   | Terms and Definitions                                                                                | 3   |

| 2   | References                                                                                           | 3   |

| 3   | Introduction                                                                                         | 4   |

| 4   | Creating a New F(1) Configuration                                                                    | 5   |

| 5   | F(1) Commands                                                                                        | 5   |

| 6   | F(1) Example Commands                                                                                | 6   |

| 7   | Sensor Application                                                                                   | 7   |

| 8   | Other F(1) Applications                                                                              |     |

| 9   | Conclusion                                                                                           | 13  |

| Re  | vision History                                                                                       |     |

| Fi  | gures                                                                                                |     |

|     | ure 1: F(1) Block and Connections                                                                    |     |

|     | ure 2: LOAD Configuration                                                                            |     |

|     | ure 3: DELAY Configuration                                                                           |     |

|     | ure 4: LOOP with DELAY Configuration<br>ure 5: Example #1 from Datasheet                             |     |

|     | ure 6: Example #1 Schematic, State 0                                                                 |     |

|     | ure 7: Example #1 Schematic, State 1                                                                 |     |

|     | ure 8: ASM Diagram                                                                                   |     |

|     | ure 9: ASM Output Matrix                                                                             |     |

|     | lure 10: Example #1 Application Circuit<br>lure 11: Room Temperature (25 °C); Potentiometer at 50 kΩ |     |

| Fia | iure 12: Over Temperature (20 °C); Potentiometer at 1.5 kΩ                                           | 11  |

| Fia | ure 13: Example #2 from Datasheet                                                                    | .11 |

| Fig | ure 14: Example #2 Schematic                                                                         | 12  |

|     | ure 15: Example #3 from Datasheet                                                                    |     |

|     | ure 16: Example #3 Schematic, State 0<br>ure 17: Example #3 Schematic, State 1                       |     |

|     |                                                                                                      | 1   |

| 18  | ables                                                                                                |     |

| Tal | ble 1: E(1) Commands                                                                                 | 5   |

#### 1 Terms and Definitions

ASM Asynchronous state machine

# 2 References

For related documents and software, please visit:

GreenPAK™ Programmable Mixed-signal Products | Renesas

Download our free GreenPAK™ Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools to freeze the design into your own customized IC in a matter of minutes. Renesas Electronics provides a complete library of application notes [3] featuring design examples as well as explanations of features and blocks within the IC.

- [1] GreenPAK Designer Software, Software Download and User Guide, Renesas Electronics

- [2] AN-CM-237 SLG46880/1 F(1) Block.gp, GreenPAK Design File, Renesas Electronics

- [3] GreenPAK Application Notes, GreenPAK Application Notes Webpage, Renesas Electronics

- [4] 50K6A1 SERIES 1 Thermistor Datasheet [Online]. Available: 50K6A1 SERIES 1 Thermistor (mouser.com) [Accessed 11 01 2018]

# 3 Introduction

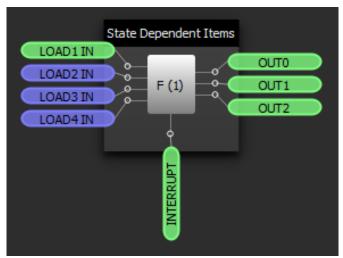

The F(1) Computation Macrocell, also referred to as the F(1) block, is a specialized block within the SLG46880/1's Asynchronous State Machine (ASM) which allows the designer to trigger sequences of commands upon entering a new state of the ASM.

Whenever the ASM enters a new state, the F(1) block can execute a sequence of up to 12 commands for loading and storing single-bit data in a stack up to 16 bits deep, as well as perform logical operations on bits at the top of the stack, such as AND, OR, XOR, and INV.

Once the F(1) completes its sequence, control is relinquished back to the ASM. While the F(1) block is active, there is no ASM activity (i.e. the ASM cannot change states).

The F(1) block has two digital inputs: ASM\_nRESET and f1\_Interrupt. An active HIGH signal on either of those inputs will immediately halt any command execution for the F(1) block, and will immediately relinquish control back to the ASM.

The user can define up to 4 different F(1) configurations, which can each hold a set of up to 12 commands. Only one configuration may be executed per ASM state. The user can also decide to not use the F(1) block for a particular state.

The F(1) block also has 4 analog inputs coming from various pins that can be muxed into the positive input for the F(1) block's dedicated Analog Comparator.

The F(1) stack can serve as a persistent data source or data destination for commands running in the F(1) block. LOADx commands will push data down into the stack. OUTx commands will pop data off the stack, and send to the contents to one of three outputs to the Connection Matrix. The contents of this memory are not changed during state transitions, and are only changed by the commands running inside the F(1) Computation Macrocell itself.

Figure 1: F(1) Block and Connections

# 4 Creating a New F(1) Configuration

To create a new F(1) configuration, display the F(1) block on your workspace by clicking on its checkbox in the Components List. Then double-click the F(1) block to bring up its Properties panel.

Create a new F(1) configuration by clicking on the green "+" button at the top right of the Properties panel. You can rename configurations to whatever you want, but for this app note I'll leave the default configuration names in place.

For each of your F(1) configurations, you can choose whether or not you want an interrupt to reset the stack's memory. You can also select the initial state for each of the F(1) block's 3 outputs. The options for the OUTx initial states are: keep, 0, 1, and none.

# 5 F(1) Commands

Table 1 includes all of the commands available in the F(1) block.

Table 1: E(1) Commands

| Command     | Description                                                                                 |

|-------------|---------------------------------------------------------------------------------------------|

| LOAD1       | Push one bit. Source defined by LOAD1 configuration.                                        |

| LOAD2       | Push one bit. Source defined by LOAD2 configuration.                                        |

| LOAD3       | Push one bit. Source defined by LOAD3 configuration.                                        |

| LOAD4       | Push one bit. Source defined by LOAD3 configuration.                                        |

| AND         | Pop two bits. Perform Logical AND, then Push the output.                                    |

| OR          | Pop two bits. Perform Logical OR, then Push the output.                                     |

| XOR         | Pop two bits. Perform Logical XOR, then Push the output.                                    |

| INV         | Pop one bit. Perform Logical INV, then Push the output.                                     |

| PUSH0       | Push a 0 to the top of the stack.                                                           |

| POP         | Pop one bit from the top of the stack.                                                      |

| DELAY       | Delay according to F(1) delay configuration. Then continue.                                 |

| LOOP w/ DLY | If the top bit is 0, execute delay and then jump to specified command. Otherwise, continue. |

| OUT0        | Output the top value to OUT0                                                                |

| OUT1        | Output the top value to OUT1                                                                |

| OUT2        | Output the top value to OUT2                                                                |

| END         | End F(1). Return control to ASM.                                                            |

# **6** F(1) Example Commands

To create a LOAD command, select LOADx from the dropdown menu in the Command Sequence section. You can choose whether you want to load a bit from the LOADx IN matrix connector or from an ACMP comparison. If you choose to load from the ACMP, you can choose both the IN+ source and the IN- reference.

When the LOAD command executes, it will PUSH the value from either the connection matrix or the ACMP into the stack.

Figure 2: LOAD Configuration

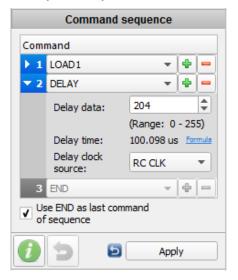

To add a DELAY command, click on the "+" button next to LOAD1 and select DELAY from the next dropdown menu. Now, you can select your delay clock source and data to configure the delay length.

**Figure 3: DELAY Configuration**

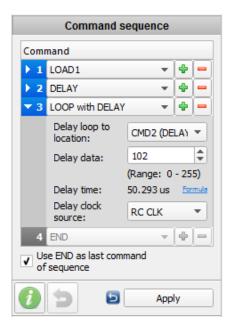

The LOOP with DELAY command essentially works as a GOTO command. It allows the designer to jump to an out-of-sequence command after a delay. First, select the command you wish to jump to in the "Delay loop to location" dropdown. Then configure the delay just as was shown in the DELAY command above.

Figure 4: LOOP with DELAY Configuration

Use the OUTx commands to output the value at the top of the stack to the matrix connections. Finally, use the END command to return control back to the ASM.

# 7 Sensor Application

Example #1: Sensor Application showing the command sequence for a potential use case of the f(1) Macrocell.

| f(1) Command<br>Sequence | Command | Description                                                                                                    |

|--------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| 1                        | INV     | Change Top Memory location from $0 \rightarrow 1$                                                              |

| 2                        | OUT1    | Output a 1 to a pin defined by OUT1 register. This can be used to turn on or bias an external sensor           |

| 3                        | DELAY   | Wait for a time defined by DELAY register. This can be used to allow sensor to settle.                         |

| 4                        | LOAD1   | Capture the output of $f(1)$ ACMP from an analog pin connected to the sensor as defined by the LOAD1 register. |

| 5                        | LOAD2   | Capture the output of a pin as defined by the LOAD2 register. This can be used to check a power good signal    |

| 6                        | AND     | Logically AND the top two values of the 1x16 memory that were just loaded with LOAD1 and LOAD2                 |

| 7                        | OUT2    | Output the result of sensor output AND power good signal for a control decision for the ASM                    |

| 8                        | END     | ASM can now act on OUT2 signal                                                                                 |

Figure 5: Example #1 from Datasheet

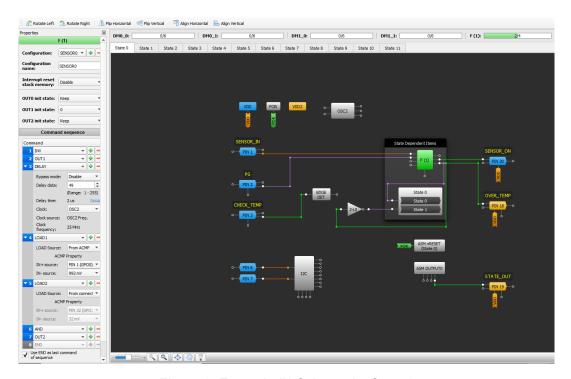

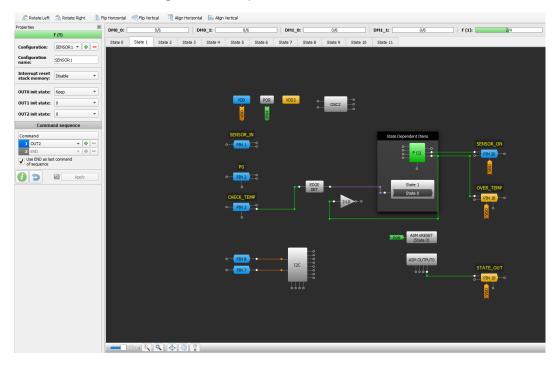

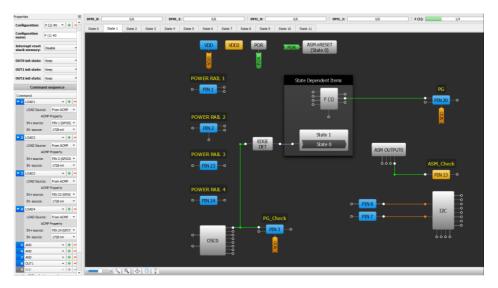

Example #1 of the datasheet provides an example using the F(1) block to detect the voltage of a sensor when the state changes in the ASM (Figure 5). OUT1 is connected to PIN #20 (SENSOR\_ON) and OUT2 is connected to PIN #18 (OVER\_TEMP). The delay on command 3 is defined as 2 µs. LOAD 1's ACMP IN+ is connected to PIN#1 (SENSOR\_IN) and has a threshold of 992 mV. LOAD 2 is connected to PIN #2 (PG). See Figure 6 and Figure 7 for a view of the schematic in GreenPAK Designer. See Figure 8 and Figure 9 for a view of the ASM settings.

Figure 6: Example #1 Schematic, State 0

Figure 7: Example #1 Schematic, State 1

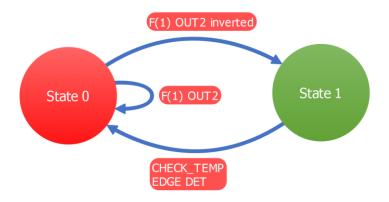

Figure 8: ASM Diagram

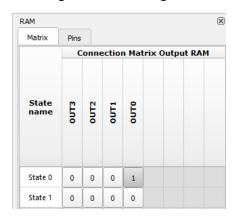

Figure 9: ASM Output Matrix

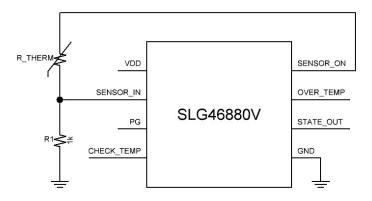

For a more specific use of this F(1) sequence, it can be used to flag an overtemperature condition while the state machine is transitioning to a new state and the device that the GreenPAK is sensing already has a power good condition. For this application, the SENSOR\_ON output is connected to one node of an NTC thermistor. Another resistor is connected to the other node of the thermistor and to ground to make a voltage divider for the SENSOR\_IN input (Figure 10).

Figure 10: Example #1 Application Circuit

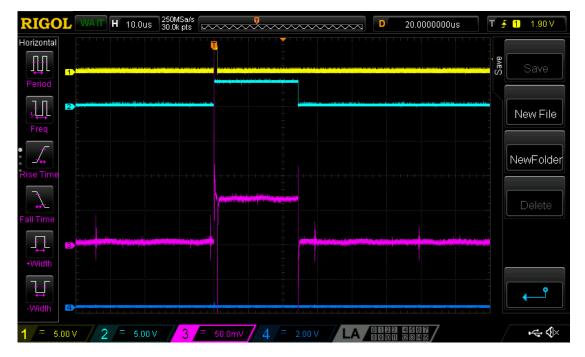

When the thermistor senses room temperature, the voltage at SENSOR\_IN is about 65 mV. This is well below the 992 mV threshold of the ACMP and the OVER\_TEMP output remains low (Figure 11). As the thermistor senses a higher temperature, it will decrease in resistance and increase the voltage seen on SENSOR\_IN. Once the thermistor senses a temperature above 110 °C, the voltage at SENSOR\_IN will be about 1 V. This crosses the 992 mV threshold set in the ACMP and the OVER\_TEMP output will go high while in State 0 if the PG input is also high (Figure 12).

At room temperature (25 °C) the thermistor was measured about 50 k $\Omega$  and according to a datasheet of a similarly rated NTC thermistor [5] it would be 1.5 k $\Omega$  at 120 °C. To test the design, a potentiometer was used to match what the thermistor's resistance would be at these given temperatures.

Channel 1 - PIN #3 (CHECK TEMP)

Channel 2 - PIN #19 (STATE\_OUT)

Channel 3 - PIN #1 (SENSOR ON)

Channel 4 - PIN #18 (OVER\_TEMP)

Figure 11: Room Temperature (25 °C); Potentiometer at 50 kΩ

Figure 12: Over Temperature (120 °C); Potentiometer at 1.5 k $\Omega$

# 8 Other F(1) Applications

Example #2: Power Good Application showing the command sequence for a potential use case of the f(1) Macrocell.

| f(1) Command<br>Sequence | Command | Description                                                                                                                                                    |

|--------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | LOAD1   | Capture the output of f(1) ACMP from an analog pin connected to power rail 1 as defined by the LOAD1 register. A "1" means that power is good on power rail 1. |

| 2                        | LOAD2   | Capture the output of f(1) ACMP from an analog pin connected to power rail 2 as defined by the LOAD2 register. A "1" means that power is good on power rail 2. |

| 3                        | LOAD3   | Capture the output of f(1) ACMP from an analog pin connected to power rail 3 as defined by the LOAD3 register. A "1" means that power is good on power rail 3. |

| 4                        | LOAD4   | Capture the output of f(1) ACMP from an analog pin connected to power rail 4 as defined by the LOAD4 register. A "1" means that power is good on power rail 4. |

| 5                        | AND     | LOAD4 result ANDs with LOAD3 result (LOAD4 & LOAD3). This combines two of the Power Good signals.                                                              |

| 6                        | AND     | (LOAD4 & LOAD3) & LOAD2. This combines three of the Power Good signals.                                                                                        |

| 7                        | AND     | ((LOAD4 & LOAD3) & LOAD2) & LOAD1. This combines four of the Power Good signals                                                                                |

| 8                        | OUT1    | Output the Master Power Good signal to a location defined by the OUT1 register                                                                                 |

Figure 13: Example #2 from Datasheet

Figure 14: Example #2 Schematic

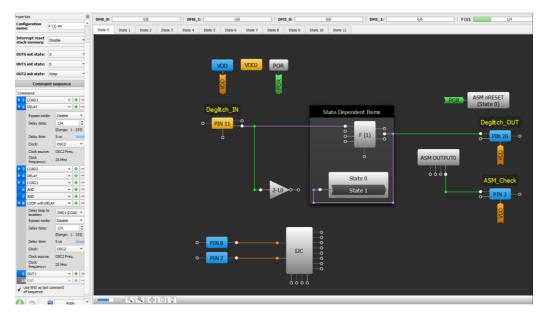

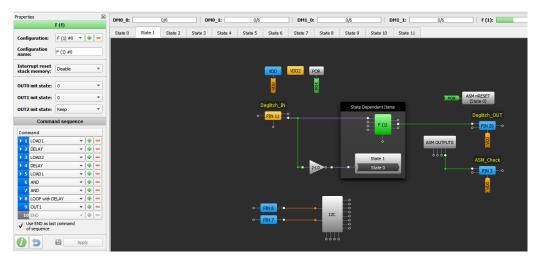

Example #3: Rising Edge Deglitch Application showing the command sequence for a potential use case of the f(1) Macrocell.

| f(1) Command<br>Sequence | Command              | Description                                                                                                                                                                             |

|--------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | LOAD1                | Capture the output of a pin or any macrocell output defined by the LOAD1 register.                                                                                                      |

| 2                        | DELAY                | Delay for the time defined by configuration register.                                                                                                                                   |

| 3                        | LOAD1                | Capture the output of a pin or any macrocell output defined by the LOAD1 register.                                                                                                      |

| 4                        | DELAY                | Delay for time defined by configuration register.                                                                                                                                       |

| 5                        | LOAD1                | Capture the output of a pin or any macrocell output defined by the LOAD1 register.                                                                                                      |

| 6                        | AND                  | Logically AND the top two values of the 1x16 memory stack, that was loaded before. (LOAD1 & LOAD1 after Delay).                                                                         |

| 7                        | AND                  | (LOAD1 & LOAD1 after Delay) & LOAD1 after double Delay.                                                                                                                                 |

| 8                        | LOOP WITH DE-<br>LAY | If the calculated value is 0, then start to execute first command once again, which is defined by the configuration bits. Otherwise f(1) continues to execute next command (command 9). |

| 9                        | OUT1                 | Output the result value, which is a high level.                                                                                                                                         |

| 10                       | END                  | ASM can act on any other signals.                                                                                                                                                       |

Figure 15: Example #3 from Datasheet

The rising edge deglitch will load the value from PIN #11. After 5  $\mu$ s it will load the value from PIN #11 again and repeat this a second time after another 5  $\mu$ s. If PIN #11 was held high for these three successive LOAD1 commands it will output to OUT1 of the F(1) block. If PIN #11 was not held high for these three successive LOAD1 commands, it will loop back to the first command (LOAD1) and restart the process.

Figure 16: Example #3 Schematic, State 0

Figure 17: Example #3 Schematic, State 1

# 9 Conclusion

In this app note we discussed how to use the F(1) computation macrocell in the SLG46880/1. The F(1) block allows the designer to assign up to 12 commands to manipulate a 16-bit deep stack of bits. Since the F(1) block's has up to 4 configurations, it can be reused in different ASM states for different purposes. Thanks to its multi-purpose functionality, the F(1) block enhances the flexibility of the GreenPAK platform.

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 19-Mar-2018 | Initial Version |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.