# SH7262/SH7264 グループ

RJJ06B1155-0100

Rev.1.00

マルチファンクションタイマパルスユニット 2、A/D 変換器、

2010.04.15

およびダイレクトメモリアクセスコントローラの組み合わせ使用例

## 要旨

本アプリケーションノートでは、マルチファンクションタイマパルスユニット 2、A/D 変換器、およびダイレクトメモリアクセスコントローラの組み合わせ使用例について説明しています。

## 動作確認デバイス

SH7262/SH7264

以下、総称して「SH7264」として説明します。

## 目次

|    |                  |    |

|----|------------------|----|

| 1. | はじめに .....       | 2  |

| 2. | 応用例の説明.....      | 3  |

| 3. | 参考プログラムリスト ..... | 17 |

| 4. | 参考ドキュメント.....    | 27 |

## 1. はじめに

### 1.1 仕様

- マルチファンクションタイマパルスユニット 2 で A/D 変換器を起動し、ダイレクトメモリアクセスコントローラを使用して、A/D 変換結果を高速内蔵 RAM に転送します。

### 1.2 使用機能

- マルチファンクションタイマパルスユニット 2 (MTU2)

- A/D 変換器 (ADC)

- ダイレクトメモリアクセスコントローラ (DMAC)

### 1.3 適用条件

|            |                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| マイコン       | SH7262/SH7264                                                                                                                                                                                                                                                  |

| 動作周波数      | 内部クロック : 144 MHz<br>バスクロック : 72 MHz<br>周辺クロック : 36 MHz                                                                                                                                                                                                         |

| 統合開発環境     | ルネサスエレクトロニクス製<br>High-performance Embedded Workshop Ver.4.07.00                                                                                                                                                                                                |

| C コンパイラ    | ルネサスエレクトロニクス製 SuperH RISC engine ファミリ<br>C/C++コンパイラパッケージ Ver.9.03 Release00                                                                                                                                                                                    |

| コンパイルオプション | High-performance Embedded Workshop でのデフォルト設定<br>(-cpu=sh2afpu -fpu=single -object="\$(CONFIGDIR)\$(FILELEAF).obj"<br>-debug -gbr=auto -chgincpath -errorpath -global_volatile=0 -opt_range=all<br>-infinite_loop=0 -del_vacant_loop=0 -struct_alloc=1 -nologo) |

### 1.4 関連アプリケーションノート

本アプリケーションノートに関連するアプリケーションノートを以下に示します。合わせて参照してください。

- SH7262/SH7264 グループ 初期設定例

### 1.5 "L"アクティブ端子（信号）の表記について

端子名（信号名）末尾の#は“L”アクティブ端子（信号）であることを示します。

## 2. 応用例の説明

本応用例では、マルチファンクションタイマパルスユニット 2 (MTU2) で A/D 変換器 (ADC) を起動し、ダイレクトメモリアクセスコントローラ (DMAC) を使用して、A/D 変換結果を高速内蔵 RAM に転送します。

### 2.1 使用機能の動作概要

#### 2.1.1 マルチファンクションタイマパルスユニット 2 (MTU2)

MTU2 は、5 チャネルの 16 ビットタイマにより構成されている多機能なタイマユニットで、チャネルごとに、コンペアマッチ機能やインプットキャプチャ機能などの設定が可能です。チャネル 3 とチャネル 4 では、リセット同期 PWM モードや相補 PWM モードに設定することで、6 本の PWM 出力制御が可能です。また、コンペアマッチやインプットキャプチャをトリガにして、CPU を介さずに DMAC や ADC を起動することができます。

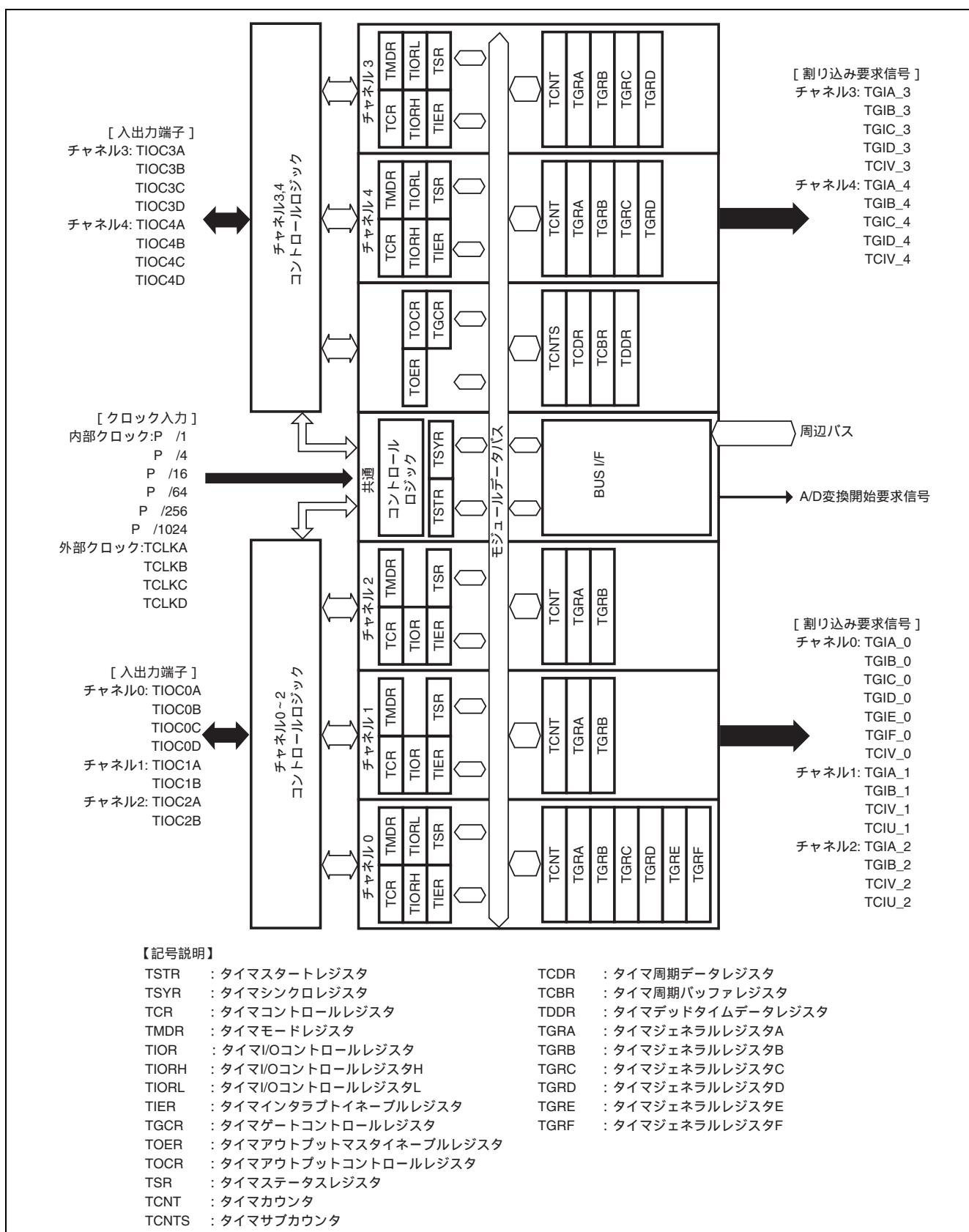

表 1 に MTU2 の特長を、また図 1 にブロック図を示します。MTU2 の詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル マルチファンクションタイマパルスユニット 2」の章を参照してください。

表1 MTU2 の特長

| 項目          | 概要                                                                                                                                                                                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| チャネル数       | 16 ビットタイマ×5 チャネル (チャネル 0~4)                                                                                                                                                                                                                                         |

| パルス入出力端子数   | 最大 16 本 (チャネル 0、3、4 : 各 4 本、チャネル 1、2 : 各 2 本)                                                                                                                                                                                                                       |

| カウンタクロック    | チャネルごとに 8 種類のカウンタ入力クロックを選択可能                                                                                                                                                                                                                                        |

| 設定可能な動作     | <ul style="list-style-type: none"> <li>カウンタクリア動作、コンペアマッチによる波形出力、インプットキャプチャ機能、同期動作、PWM モード 1 (チャネル 0~4)</li> <li>PWM モード 2 (チャネル 0~2)</li> <li>相補 PWM モード、リセット PWM モード (チャネル 3、4 の連動)</li> <li>AC 同期モータ駆動モード (チャネル 0、3、4 の連動)</li> <li>位相計数モード (チャネル 1、2)</li> </ul> |

| バッファ動作      | チャネル 0、3、4 はレジスタのバッファ動作を設定可能                                                                                                                                                                                                                                        |

| カスケード接続動作   | チャネル 1 とチャネル 2 の 16 ビットカウンタを接続して 32 ビットカウンタとして動作可能                                                                                                                                                                                                                  |

| DMAC 起動     | チャネル 0~4 のコンペアマッチまたはインプットキャプチャで DMAC を起動可能                                                                                                                                                                                                                          |

| A/D 変換開始トリガ | <ul style="list-style-type: none"> <li>TGRA のインプットキャプチャ／コンペアマッチと、相補 PWM モード時の TCNT_4 の谷での A/D 起動</li> <li>TCNT_0 と TGRE_0 のコンペアマッチによる A/D 起動</li> <li>A/D 変換開始要求ディレイド機能による A/D 起動</li> </ul>                                                                        |

| 割り込み要因      | 25 種類 (コンペアマッチ／インプットキャプチャ割り込み、オーバフロー割り込み、アンダフロー割り込みなど)                                                                                                                                                                                                              |

| 割り込み間引き機能   | チャネル 3 のコンペアマッチ割り込み、チャネル 4 のオーバフロー／アンダフロー割り込みを間引くことが可能                                                                                                                                                                                                              |

| その他         | <ul style="list-style-type: none"> <li>内部 16 ビットバスによる高速アクセス</li> <li>モジュールスタンバイモードを設定可能</li> </ul>                                                                                                                                                                  |

図1 MTU2 のブロック図

### 2.1.2 A/D 変換器 (ADC)

SH7264 は、10 ビット精度の逐次比較方式 A/D 変換器を内蔵しています。最大 8 チャネルのアナログ入力を選択することができます。（SH7262 は 4 チャネル）

A/D 変換器の動作モードにはシングルモードおよびマルチモード、スキャンモードがあります。シングルモードとマルチモードは、指定した 1 チャネル以上の A/D 変換を 1 回行った後、A/D 変換待機状態になるモードです。スキャンモードは、指定した 1 チャネル以上の A/D 変換を繰り返し行うモードです。また、A/D 変換終了時には CPU に対し A/D 変換終了割り込みを発生することができます。また、A/D 変換終了割り込み発生時には DMAC を起動することができます。DMAC 起動時は CPU に対する割り込みは発生しません。

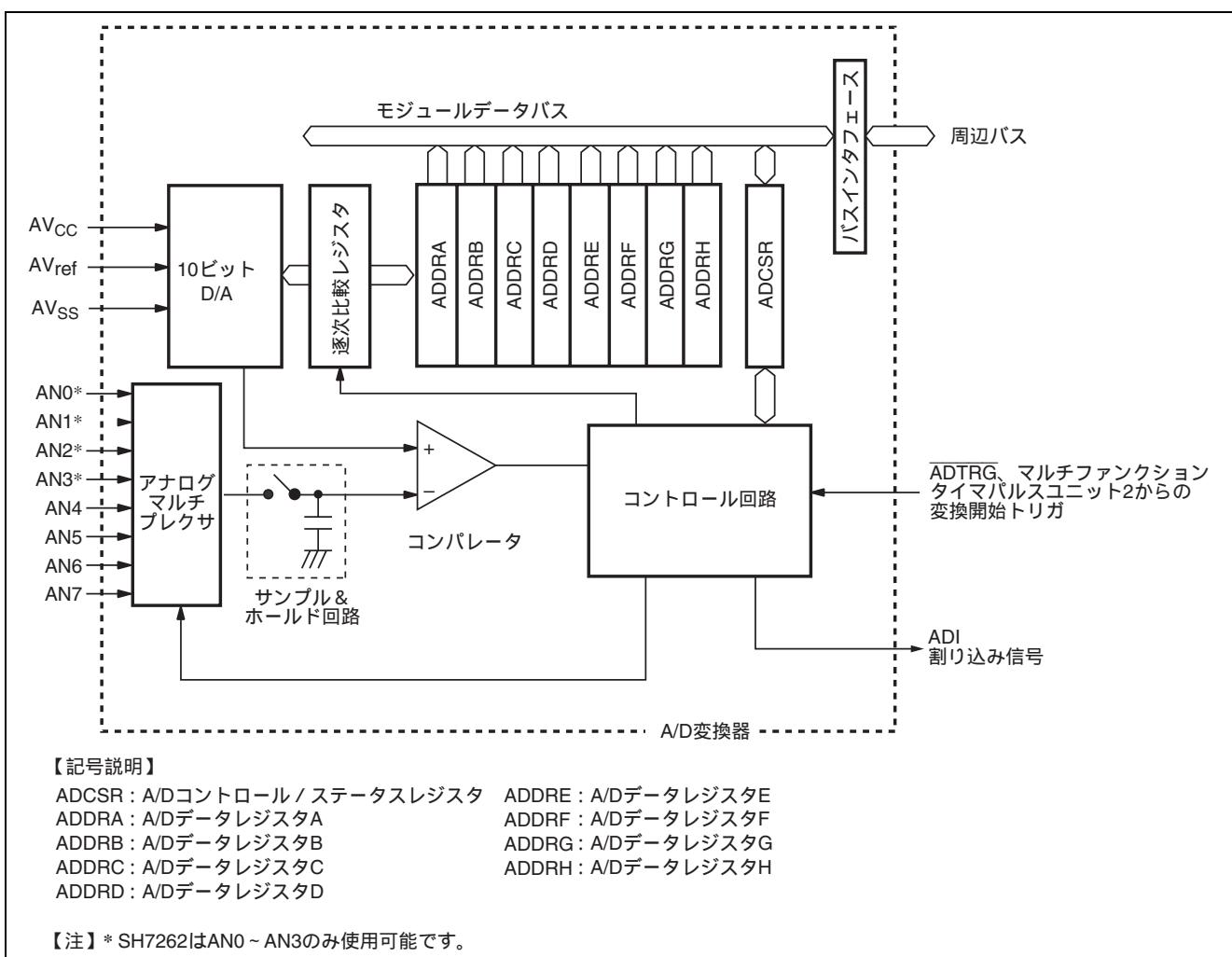

表 2 に A/D 変換器の仕様を、また図 2 にブロック図を示します。A/D 変換器についての詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル A/D 変換器」の章を参照してください。

表2 ADC の特長

| 項目          | 内容                                                                                                                                                                                                                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 分解能         | 10 ビット                                                                                                                                                                                                                        |

| 入力チャネル数     | SH7262 は 4 チャネル、SH7264 は 8 チャネル                                                                                                                                                                                               |

| 最小変換時間      | 1 チャネル当たり 4.0 $\mu$ s                                                                                                                                                                                                         |

| 絶対精度        | $\pm 4$ LSB                                                                                                                                                                                                                   |

| 動作モード       | <ul style="list-style-type: none"> <li>シングルモード：1 チャネルの A/D 変換</li> <li>マルチモード：1~4 チャネルの A/D 変換または 1~8 チャネルの A/D 変換（SH7262 は 1~4 チャネル）</li> <li>スキャンモード：1~4 チャネルの連続 A/D 変換または 1~8 チャネルの連続 A/D 変換（SH7262 は 1~4 チャネル）</li> </ul> |

| データレジスタ     | 8 本（変換結果を各チャネルに対応した 16 ビットデータレジスタに保持）                                                                                                                                                                                         |

| サンプル&ホールド機能 | あり                                                                                                                                                                                                                            |

| A/D 変換開始方法  | <ul style="list-style-type: none"> <li>ソフトウェア：ADST ビットの設定</li> <li>MTU2 による変換開始トリガ：MTU2 の TRGAN、TRG0N、TRG4AN、TRG4BN</li> <li>外部トリガ：ADTRG#端子</li> </ul>                                                                        |

| 割り込み要因      | A/D 変換終了時に、A/D 変換終了割り込み（ADI）要求を発生可能                                                                                                                                                                                           |

| その他         | <ul style="list-style-type: none"> <li>モジュールスタンバイモードの設定可能</li> <li>A/D 変換終了割り込み（ADI）要求により DMAC を起動可能</li> </ul>                                                                                                               |

図2 ADC のブロック図

### 2.1.3 ダイレクトメモリアクセスコントローラ (DMAC)

DMAC は、DACK (転送要求受け付け信号) 付き外部デバイス、外部メモリ、内蔵メモリ、メモリマップト外部デバイス、および内蔵周辺モジュール間のデータ転送を CPU に代わって高速に行うことができます。

DMAC のバスモードにはサイクルスチールモードとバーストモードがあります

サイクルスチールモードでは、DMAC は 1 回の転送単位（バイト、ワード、ロングワード、または 16 バイト単位）の転送を終了するたびにバス権を他のバスマスターに渡します。その後転送要求があれば、他のバスマスターからバス権を取り戻し、再び 1 転送単位の転送を行い、その転送を終了するとまたバス権を他のバスマスターに渡します。これを転送終了条件が満たされるまで繰り返します。

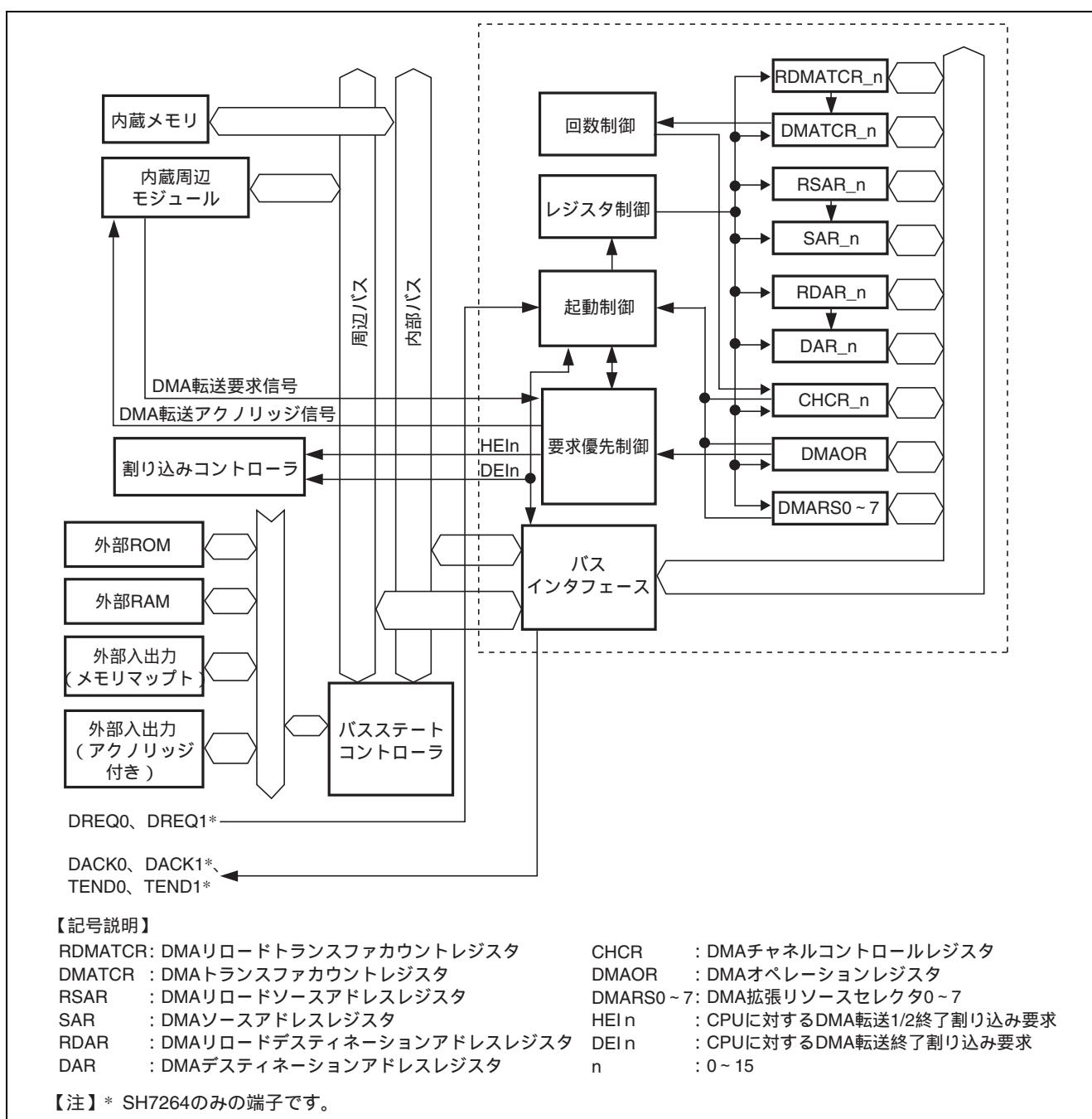

表 3 に DMAC の特長を、図 3 にブロック図を示します。DMAC についての詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル ダイレクトメモリアクセスコントローラ」の章を参照してください。

表3 DMAC の特長

| 項目      | 内容                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| チャネル数   | 16 チャネル                                                                                                                                                          |

| アドレス空間  | アーキテクチャ上は 4G バイト                                                                                                                                                 |

| 転送データ単位 | バイト、ワード、ロングワード、16 バイト                                                                                                                                            |

| 最大転送回数  | 16,777,216 (24 ビット) 回                                                                                                                                            |

| アドレスモード | シングルアドレスモード、デュアルアドレスモード                                                                                                                                          |

| 転送要求    | 外部リクエスト、内蔵周辺モジュールリクエスト、オートリクエスト                                                                                                                                  |

| バスモード   | サイクルスチールモード（通常モードとインターミッティントモード）、バーストモード                                                                                                                         |

| 優先順位    | チャネル優先順位固定モードの 2 種類から選択可能                                                                                                                                        |

| 割り込み要求  | データ転送 1/2 終了、データ転送終了                                                                                                                                             |

| リロード機能  | 実行中の DMA 転送と同じ設定での DMA 転送を再設定することなく繰り返し実行することができます。また、DMA 転送中にリロードレジスタをあらかじめ設定しておくことで、次回の DMA 転送を異なる設定で実行することができます。このリロード機能は、チャネルごと、リロードレジスタごとに ON/OFF の設定が可能です。 |

## 【記号説明】

RDMATCR: DMAリロードトランസ്ഫァカウントレジスタ

DMATCR : DMAトранസ്ഫァカウントレジスタ

RSAR : DMAリロードソースアドレスレジスタ

SAR : DMAソースアドレスレジスタ

RDAR : DMAリロードデスティネーションアドレスレジスタ

DAR : DMAデスティネーションアドレスレジスタ

CHCR : DMAチャネルコントロールレジスタ

DMAOR : DMAオペレーションレジスタ

DMARS0~7: DMA拡張リソースセレクタ0~7

HEIn : CPUに対するDMA転送1/2終了割り込み要求

DEIn : CPUに対するDMA転送終了割り込み要求

n : 0~15

【注】\* SH7264のみの端子です。

図3 DMAC のブロック図

## 2.2 使用機能の設定手順

### 2.2.1 マルチファンクションタイマパルスユニット2 (MTU2) の設定手順

ここでは、MTU2 のチャネル 0 を使用して ADC を起動するための初期設定フロー例を示します。動作モードには PWM モード 1 を設定します。

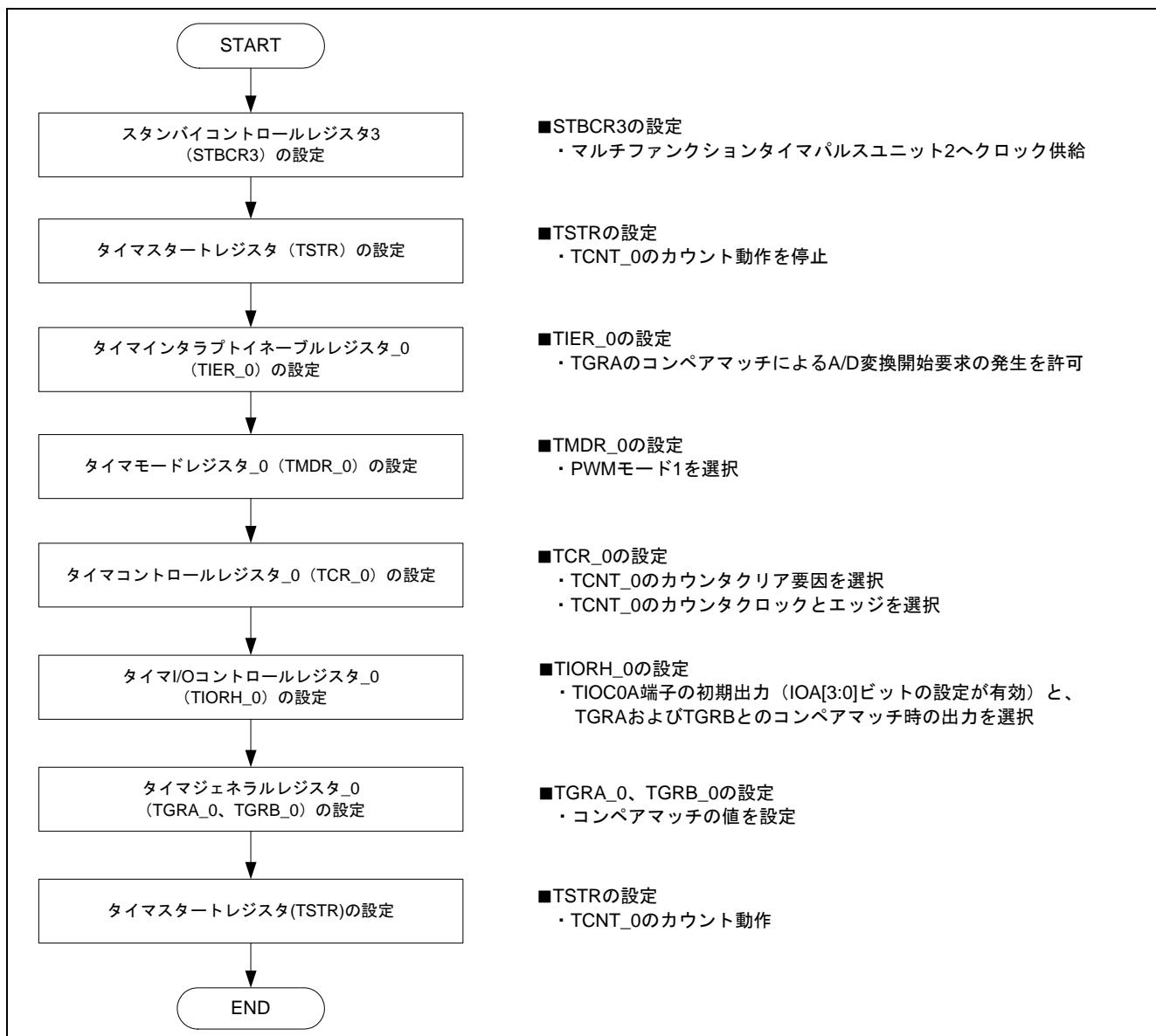

図 4 に MTU2 の初期設定フロー例を示します。なお、各レジスタ設定の詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル」を参照してください。

図4 MTU2 の初期設定フロー例

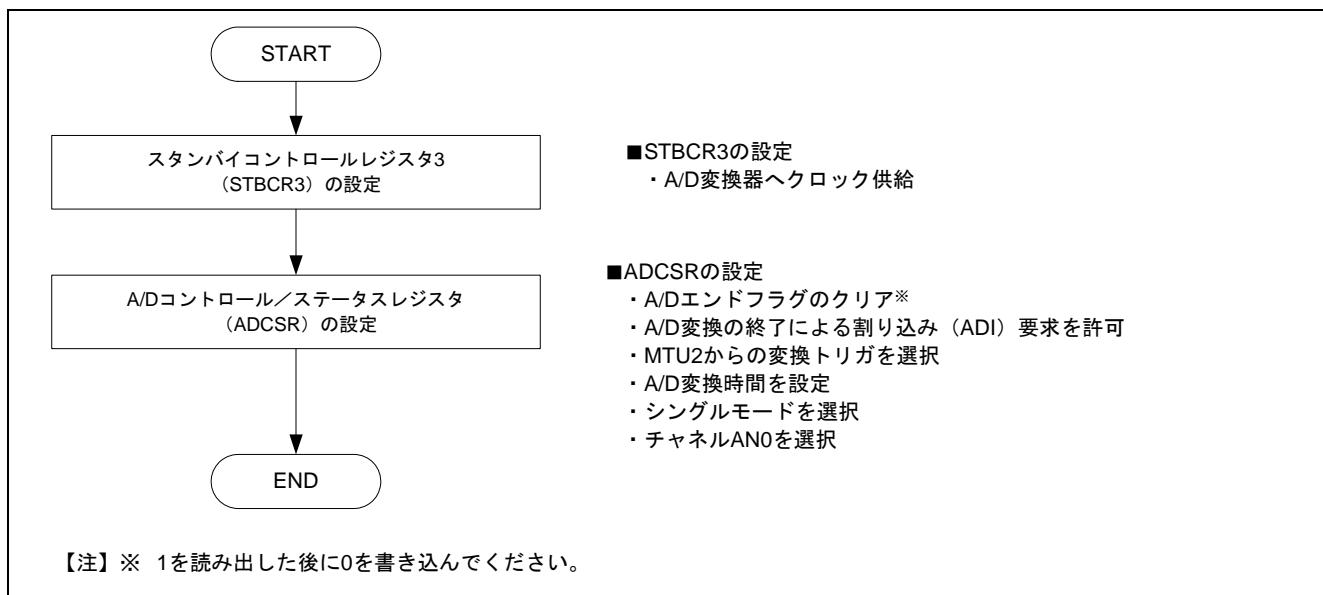

## 2.2.2 A/D 変換器 (ADC) の設定手順

ここでは、MTU2 からの A/D 変換開始要求により A/D 変換を行うための初期設定フロー例を示します。動作モードにはシングルモードを設定して、アナログ入力 AN0 を A/D 変換します。

図 5に ADC の初期設定フロー例を示します。なお、各レジスタ設定の詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル」を参照してください。

図5 ADC の初期設定フロー例

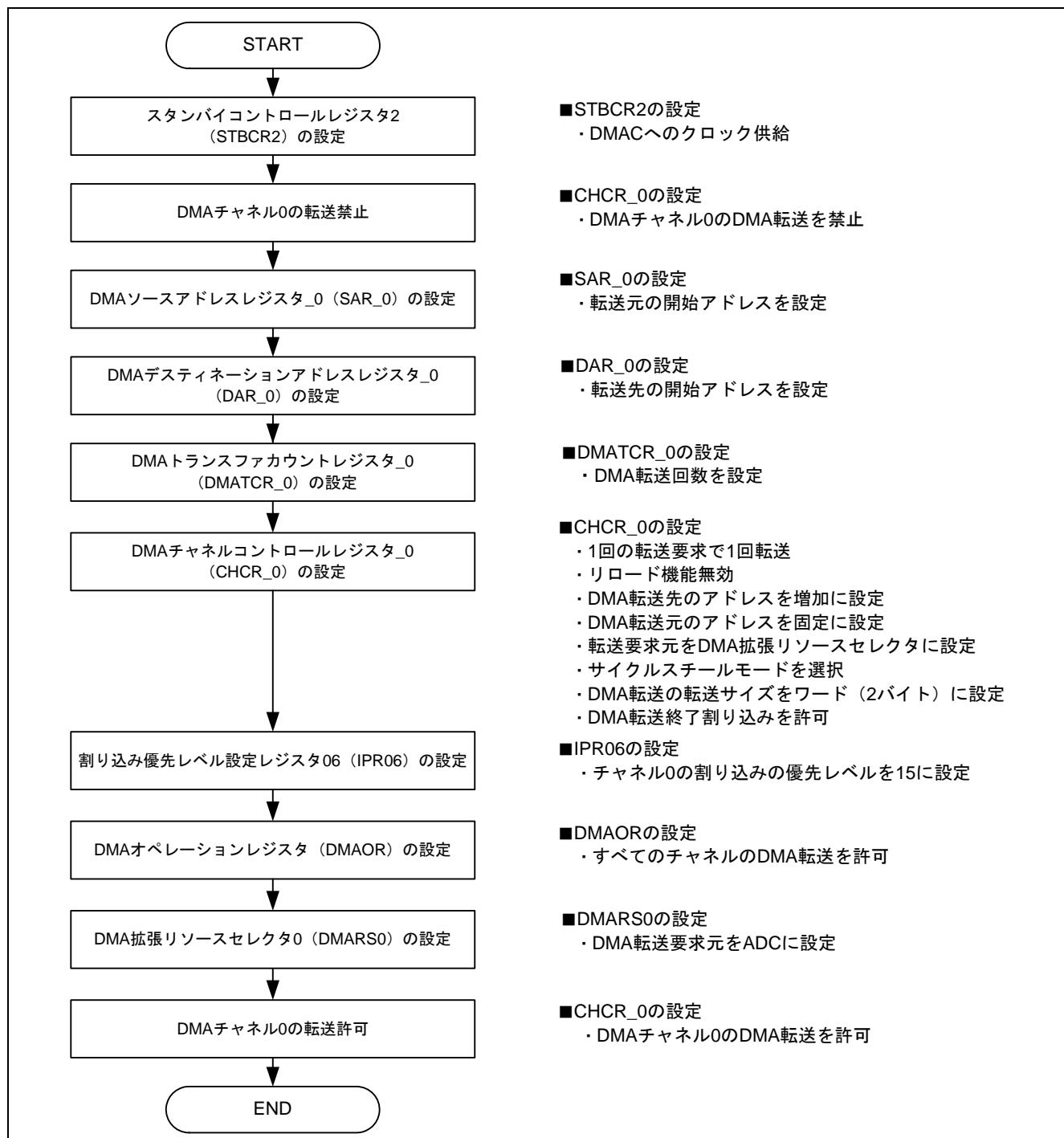

### 2.2.3 ダイレクトメモリアクセスコントローラ (DMAC) の設定手順

ここでは、ADC の A/D 変換終了割り込み (ADI) により DMA 転送を行うための初期設定フロー例を示します。ADI を起動要因とした場合、使用できるバスモードはサイクルスチールモードです。

図 6 に DMAC の初期設定フロー例を示します。なお、各レジスタ設定の詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル」を参照してください。

図6 DMAC の初期設定フロー例

## 2.3 参考プログラムの処理手順

### 2.3.1 参考プログラムの動作概要

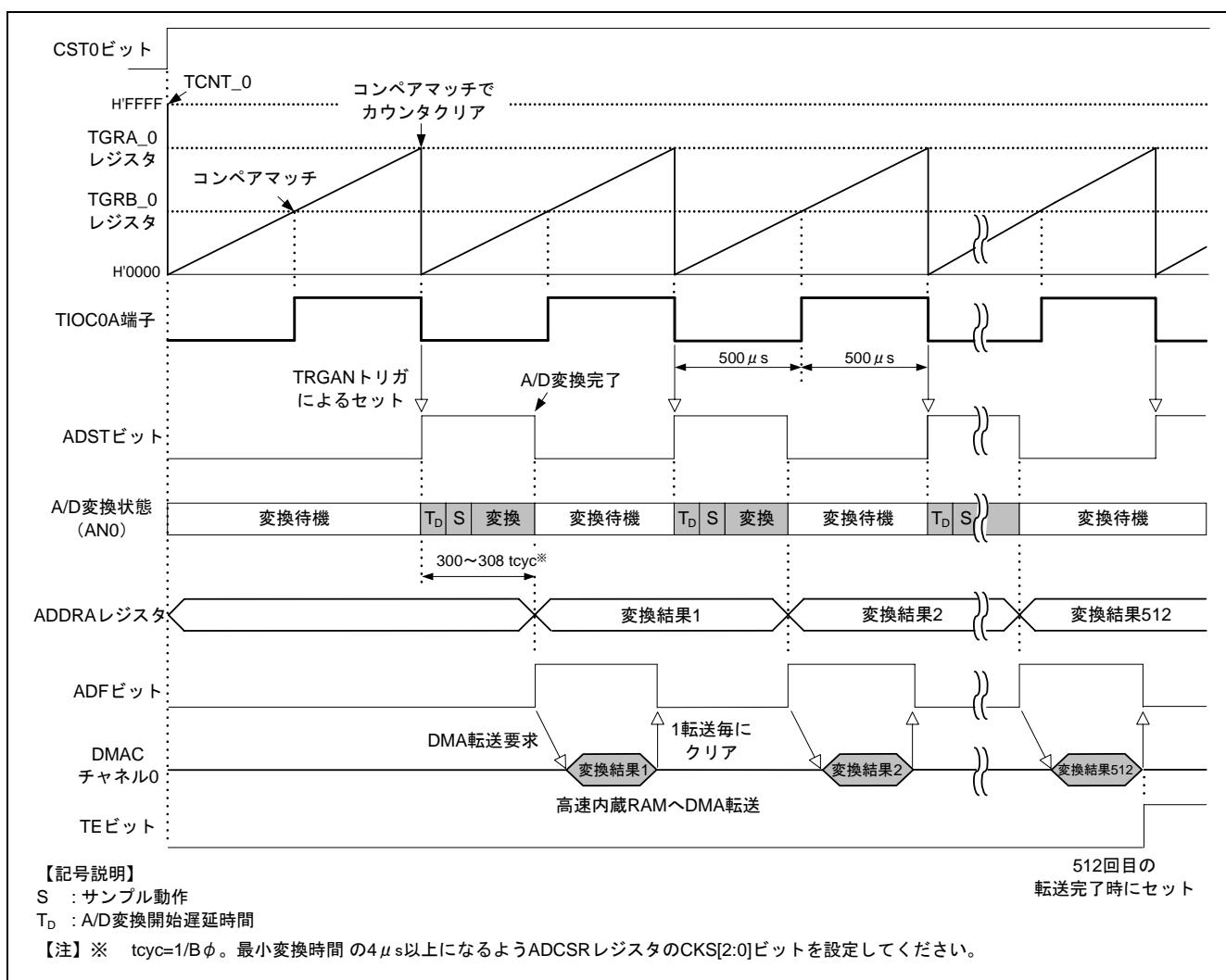

参考プログラムでは、MTU2 を用いて PWM 波形を出力し、周期ごとに ADC を起動します。そして、A/D 変換が終了するごとに DMA を用いて変換結果を高速内蔵 RAM に転送します。1K バイト分の転送を完了すると、動作を停止します。

MTU2 は、PWM モード 1 で動作し、周期 1ms、デューティ比 50% の PWM 波形を TIOC0A 端子より出力します。周期はタイマジェネラルレジスタ A\_0 (TGRA\_0) に、デューティ比はタイマジェネラルレジスタ B\_0 (TGRB\_0) に設定します。また、タイマカウンタ\_0 (TCNT\_0) と TGRA\_0 のコンペアマッチ時に A/D 変換の開始要求 (TRGAN) を発生します。\*

ADC は、シングルモードで動作し、TRGAN によりアナログ入力チャネル AN0 の A/D 変換を開始します。A/D 変換終了時は、A/D 変換終了割り込み (ADI) 要求を発生します。

DMA は、サイクルスチールモードで動作し、ADI により A/D データレジスタ A (ADDRA) から高速内蔵 RAM に A/D 変換結果を転送します。1K バイト分の転送が終了すると、DMA 転送終了割り込み (DEI) 要求を発生します。

**【注】**\* PWM 出力の有無に関係なく、A/D 変換開始要求を発生させることができます。

図 7 に、参考プログラムの動作概要を示します。

図7 参考プログラムの動作概要

## 2.3.2 マルチファンクションタイマパルスユニット 2 (MTU2) のレジスタ設定

表 4 に MTU2 のレジスタ設定例を示します。

表4 MTU2 のレジスタ設定例

| レジスタ名                                | アドレス        | 設定値    | 機能                                                                                                                                                                                                                                                                          |

|--------------------------------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 3 (STBCR3)       | H'FFFE 0408 | H'5A   | <ul style="list-style-type: none"> <li>MSTP35 = "0" :<br/>マルチファンクションタイマパルス<br/>ユニット 2 へクロック供給</li> </ul>                                                                                                                                                                    |

| ポート G コントロール<br>レジスタ 3 (PGCR3)       | H'FFFE 38C8 | H'0002 | <ul style="list-style-type: none"> <li>PG12MD = "2" :<br/>PG12 端子を TIOC0A に設定</li> </ul>                                                                                                                                                                                    |

| ポート G·IO レジスタ 0<br>(PGIOR0)          | H'FFFE 38D2 | H'1000 | <ul style="list-style-type: none"> <li>PG12IOR = "1" :<br/>TIOC0A を出力に設定</li> </ul>                                                                                                                                                                                         |

| タイマスタートレジスタ<br>(TSTR)                | H'FFFE 4280 | H'00   | <ul style="list-style-type: none"> <li>CST0 = "0" :<br/>TCNT_0 はカウント停止</li> </ul>                                                                                                                                                                                           |

|                                      |             | H'01   | <ul style="list-style-type: none"> <li>CST0 = "1" :<br/>TCNT_0 はカウント動作</li> </ul>                                                                                                                                                                                           |

| タイマモードレジスタ_0<br>(TMDR_0)             | H'FFFE 4301 | H'02   | <ul style="list-style-type: none"> <li>MD[3:0] = "B'0010" :<br/>PWM モード 1 を選択</li> </ul>                                                                                                                                                                                    |

| タイマインタラプト<br>イネーブルレジスタ_0<br>(TIER_0) | H'FFFE 4304 | H'80   | <ul style="list-style-type: none"> <li>TTGE = "1" :<br/>TGRA のコンペアマッチによる A/D 変換<br/>開始要求の発生を許可</li> </ul>                                                                                                                                                                   |

| タイマコントロール<br>レジスタ_0 (TCR_0)          | H'FFFE 4300 | H'23   | <ul style="list-style-type: none"> <li>CCLR[2:0] = "B'001" :<br/>TGRA_0 のコンペアマッチ／インプット<br/>キャプチャで TCNT_0 クリア</li> <li>CKEG[1:0] = "B'00" :<br/>入力クロックの立ち上がりエッジで<br/>カウント</li> <li>TPSC[2:0] = "B'011" :<br/>内部クロック : P<math>\phi</math> / 64 で TCNT_0 を<br/>カウント</li> </ul> |

| タイマ I/O コントロール<br>レジスタ H_0 (TIORH_0) | H'FFFE 4302 | H'21   | <ul style="list-style-type: none"> <li>IOB[3:0] = "B'0010" :<br/>TGRI はアウトプットコンペアレジスタ<br/>として動作、初期出力は 0 出力 (PWM<br/>モード 1 選択時は無効) 、コンペアマッ<br/>チで 1 出力</li> <li>IOA[3:0] = "B'0001" :<br/>TGRI はアウトプットコンペアレジスタ<br/>として動作、初期出力は 0 出力、コンペ<br/>アマッチで 0 出力</li> </ul>            |

| タイマジェネラルレジスタ A_0<br>(TGRA_0)         | H'FFFE 4308 | H'0232 | TCNT_0 とのコンペアマッチの値を設定                                                                                                                                                                                                                                                       |

| タイマジェネラルレジスタ B_0<br>(TGRI_0)         | H'FFFE 430A | H'0118 | TCNT_0 とのコンペアマッチの値を設定                                                                                                                                                                                                                                                       |

## 2.3.3 A/D 変換器 (ADC) のレジスタ設定

表 5に ADC のレジスタ設定例を示します。

なお、本設定は A/D 変換終了割り込み要求を許可していますが、DMAC の起動設定を行うため、CPU への割り込み要求は発生しません。

表5 ADC のレジスタ設定例

| レジスタ名                          | アドレス        | 設定値    | 機能                                                                                                                                                                                                                                                                                                             |

|--------------------------------|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 3 (STBCR3) | H'FFFE 0408 | H'5A   | <ul style="list-style-type: none"> <li>MSTP32 = "0" : ADC にクロック供給</li> </ul>                                                                                                                                                                                                                                   |

| ポート H コントロール<br>レジスタ 0 (PHCR0) | H'FFFE 38EE | H'0001 | <ul style="list-style-type: none"> <li>PH0MD = "1" : PH0 端子を AN0 に設定</li> </ul>                                                                                                                                                                                                                                |

| A/D コントロール／ステータスレジスタ (ADCSR)   | H'FFFF 9820 | H'4280 | <ul style="list-style-type: none"> <li>ADF="0" : A/D エンドフラグのクリア</li> <li>ADIE = "1" : A/D 変換終了割り込み要求を許可</li> <li>TRGS[3:0] = "B'0001" : MTU2 からの変換トリガ TRGAN による A/D 変換開始</li> <li>CKS[2:0] = "B'010" : 変換時間 = 308tcyc※ (最大値)</li> <li>MDS[2:0] = "B'000" : シングルモード</li> <li>CH[2:0] = "B'000" : AN0</li> </ul> |

【注】※ tcyc=1/B $\phi$

## 2.3.4 ダイレクトメモリアクセスコントローラ (DMAC) のレジスタ設定

表 6 に DMAC のレジスタ設定例を示します。

表6 DMAC のレジスタ設定例

| レジスタ名                               | アドレス        | 設定値         | 機能                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 2 (STBCR2)      | H'FFFE 0018 | H'00        | <ul style="list-style-type: none"> <li>MSTP8 = "0" :<br/>DMAC にクロック供給</li> </ul>                                                                                                                                                                                                                                                                                                            |

| DMA ソースアドレス<br>レジスタ_0 (SAR_0)       | H'FFFE 1000 | H'FFFF 9800 | 転送元のアドレス :<br>ADDRA レジスタアドレス                                                                                                                                                                                                                                                                                                                                                                |

| DMA デスティネーション<br>アドレスレジスタ_0 (DAR_0) | H'FFFE 1004 | H'FFF8 4000 | 転送先のアドレス :<br>高速内蔵 RAM (転送先の領域) の<br>先頭アドレス                                                                                                                                                                                                                                                                                                                                                 |

| DMA トランスマカウント<br>レジスタ_0 (DMATCR_0)  | H'FFFE 1008 | H'0000 0200 | 転送回数 : 512 回                                                                                                                                                                                                                                                                                                                                                                                |

| DMA チャネルコントロール<br>レジスタ_0 (CHCR_0)   | H'FFFE 100C | H'0000 0000 | <ul style="list-style-type: none"> <li>DE = "0" :<br/>DMA の転送禁止</li> </ul>                                                                                                                                                                                                                                                                                                                  |

|                                     |             | H'0000 480C | <ul style="list-style-type: none"> <li>TC = "0" :<br/>1 回の DMA 要求で 1 回転送</li> <li>RLDSAR = "0"、RLDDAR = "0" :<br/>リロード機能無効</li> <li>DM[1:0] = "B'01" :<br/>デスティネーションアドレス増加</li> <li>SM[1:0] = "B'00" :<br/>ソースアドレス固定</li> <li>RS[3:0] = "B'1000" :<br/>DMA 拡張リソースセレクタ</li> <li>TB = "0" :<br/>サイクルスチールモード</li> <li>TS[1:0] = "B'01" :<br/>ワード転送</li> <li>IE = "1" :<br/>割り込み要求許可</li> </ul> |

|                                     |             | H'0000 480D | <ul style="list-style-type: none"> <li>DE = "1" :<br/>チャネル 0 の DMA 転送を許可</li> </ul>                                                                                                                                                                                                                                                                                                         |

| DMA オペレーションレジスタ<br>(DMAOR)          | H'FFFE 1200 | H'0001      | <ul style="list-style-type: none"> <li>DME = "1" :<br/>全チャネルの DMA 転送を許可</li> </ul>                                                                                                                                                                                                                                                                                                          |

| DMA 拡張リソースセレクタ 0<br>(DMARS0)        | H'FFFE 1300 | H'00B3      | <ul style="list-style-type: none"> <li>CHO MID[5:0] = "B'1011 00" :<br/>CHO RID[1:0] = "B'11" :<br/>DMA 転送要求元を A/D 変換器に設定</li> </ul>                                                                                                                                                                                                                                                        |

| 割り込み優先レベル設定<br>レジスタ 06 (IPR06)      | H'FFFE 0C00 | H'F000      | 転送終了割り込みレベル : 15                                                                                                                                                                                                                                                                                                                                                                            |

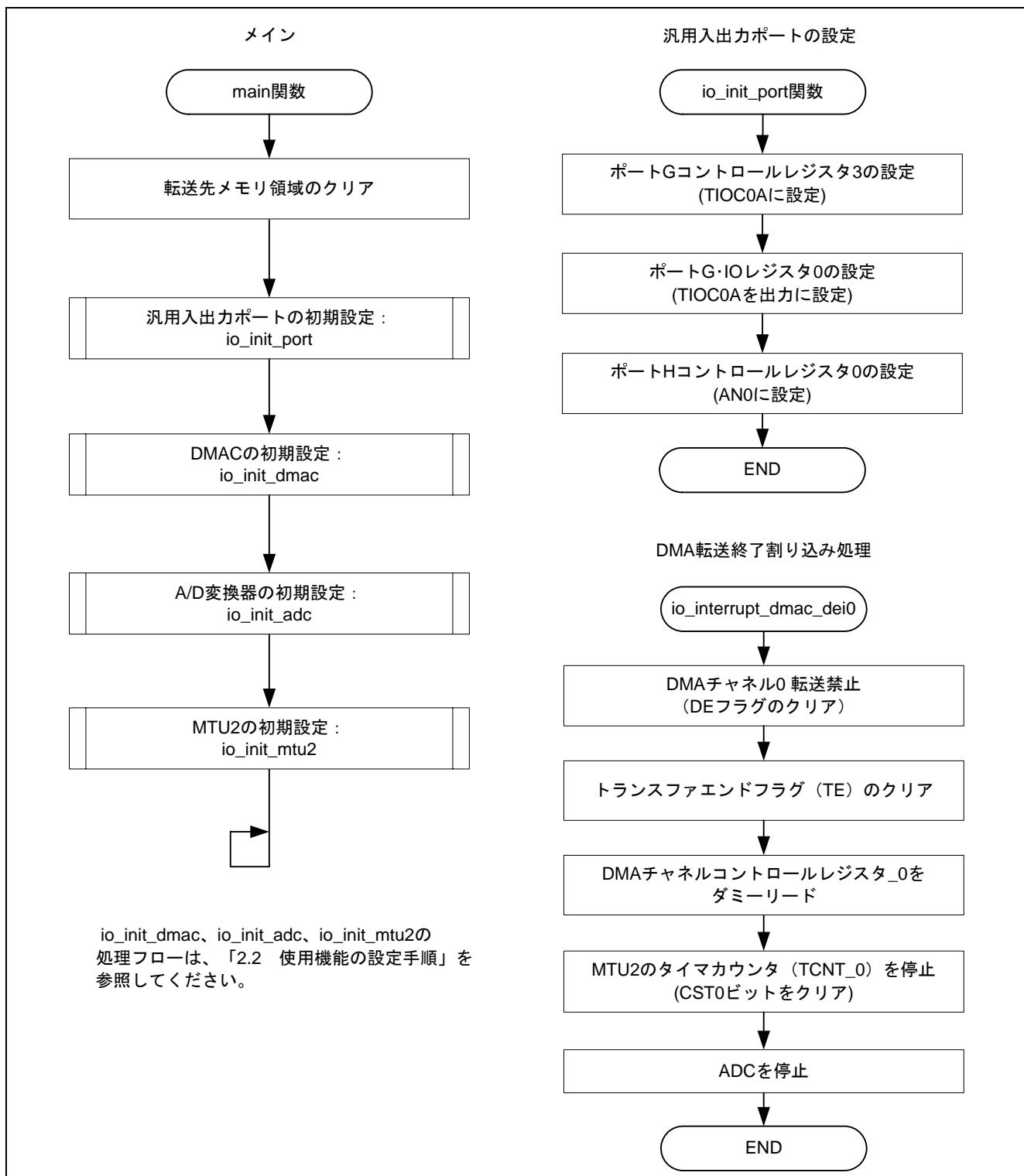

## 2.3.5 参考プログラムの動作フロー

図 8に、参考プログラムのフローチャートを示します。

図8 参考プログラムのフローチャート

### 3. 参考プログラムリスト

#### 3.1 参考プログラムについての補足

SH7264 は、製品によって大容量内蔵 RAM の容量が 1MB または 640KB と異なるため、参考プログラムのセクション配置やレジスタの設定を一部変更する必要があります。そのため本アプリケーションノートでは 1MB 用と 640KB 用の 2 つのワークスペースを用意しています。

640KB 版はライトプロテクトを解除しなければ保持用内蔵 RAM へ書き込むことができないため、640KB 版のワークスペースは、システムコントロールレジスタ 5 (SYSCR5) にライトプロテクトの解除を設定しています。

使用する製品を確認した上で、対応するワークスペースを使用してください。

## 3.2 サンプルプログラムリスト "main.c" (1)

```

1  ****

2  * DISCLAIMER

3  *

4  * This software is supplied by Renesas Electronics Corp. and is only

5  * intended for use with Renesas products. No other uses are authorized.

6  *

7  * This software is owned by Renesas Electronics Corp. and is protected under

8  * all applicable laws, including copyright laws.

9  *

10 * THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11 * REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

12 * INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13 * PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14 * DISCLAIMED.

15 *

16 * TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17 * ELECTRONICS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18 * FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19 * FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

20 * AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21 *

22 * Renesas reserves the right, without notice, to make changes to this

23 * software and to discontinue the availability of this software.

24 * By using this software, you agree to the additional terms and

25 * conditions found by accessing the following link:

26 * http://www.renesas.com/disclaimer

27 ****

28 * (C) 2010 Renesas Electronics Corporation. All rights reserved.

29 * """FILE COMMENT""***** Technical reference data *****

30 * System Name : SH7264 Sample Program

31 * File Name  : main.c

32 * Abstract   : MTU2+ADC+DMAC Module Application

33 * Version    : 1.00.01

34 * Device     : SH7262/SH7264

35 * Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36 *             : C/C++ compiler package for the SuperH RISC engine family

37 *             : (Ver.9.03 Release00).

38 * OS         : None

39 * H/W Platform: M3A-HS64G50(CPU board)+M3A-HS64G02(IO board)

40 * Description :

41 ****

42 * History    : Feb.16,2010 ver.1.00.00

43 *             : Apr.15,2010 Ver.1.00.01 Changed the company name

44 * """FILE COMMENT END""*****/

45 #include <string.h>

46 #include "iodefine.h"      /* SH7264 iodefine */

47

```

## 3.3 サンプルプログラムリスト "main.c" (2)

```

48     /* ---- プロトタイプ宣言 ---- */

49     void main(void);

50     void io_init_port(void);

51     void io_init_dmac(void *src, void *dst, int count);

52     void io_init_adc(void);

53     void io_init_mtu2(void);

54     void io_interrupt_dmac_dei0( void );

55

56     /* ---- マクロ定義 ---- */

57     #define NUM_OF_BUFF    10          /* 受信バッファの面数 */

58     #define DST_ADR        0xffff84000 /* DMA 転送先(高速内蔵 RAM)の先頭アドレス */

59     #define SRC_ADR        0xfffff9800 /* DMA 転送元(A/D データレジスタ A)のアドレス */

60     #define COUNT          0x200       /* 転送回数 512 回(1 ワード/1 回) */

61

62

63

```

## 3.4 サンプルプログラムリスト "main.c" (3)

```

64  /* "FUNC COMMENT" *****/

65  * ID          :

66  * Outline     : Sample program main

67  *-----

68  * Include      : <string.h>

69  *-----

70  * Declaration  : void main(void);

71  *-----

72  * Description   : データ格納先の内蔵メモリ領域をクリアした後、PORT、DMAC、ADC、

73  *                  : MTU2 の各モジュールの初期設定を行います。初期設定後、MTU2 の

74  *                  : TCNT がカウント動作し、TCNT のコンペアマッチにより、AD 変換を

75  *                  : 開始し、変換データを内蔵 RAM に DMA 転送します。変換データを

76  *                  : 1K バイト分 DMA 転送した後に、CPU に対し DMAC の転送完了割り込みが

77  *                  : 発生します。なお一連の動作は H/W によって行われます。

78  *-----

79  * Argument      : void

80  *-----

81  * Return Value  : void

82  *-----

83  * Note          :

84  * "FUNC COMMENT END" *****/

85 void main(void)

86 {

87     /* === 転送先メモリ領域のクリア === */

88     memset((void *)DST_ADR, 0, COUNT*2);

89

90     /* === 汎用入出力ポートの設定 === */

91     io_init_port();

92

93     /* === DMAC の初期設定 === */

94     io_init_dmac((void *)SRC_ADR, (void *)DST_ADR, COUNT);

95

96     /* === A/D 変換器の初期設定 === */

97     io_init_adc();

98

99     /* === MTU2 の初期設定 === */

100    io_init_mtu2();

101

102    while(1){

103        /* loop */

104    }

105 }

```

## 3.5 サンプルプログラムリスト "main.c" (4)

```

106  /* "FUNC COMMENT" *****/

107  * ID      :

108  * Outline    : 汎用入出力ポートの設定

109  *

110  * Include    : "iodefine.h"

111  *

112  * Declaration : void io_init_port(void);

113  *

114  * Description  : 端子の機能、入出力方向の設定を行います。

115  *

116  * Argument    : void

117  *

118  * Return Value : void

119  *

120  * Note       :

121  * """FUNC COMMENT END"" *****/

122 void io_init_port(void)

123 {

124     /* === MTU2 (TIOC0A 端子出力) の設定 === */

125     PORT.PGCR3.BIT.PG12MD = 2;          /* PG12 端子を TIOC0A に設定 */

126     PORT.PGIOR0.BIT.PG12IOR = 1;        /* PG12 端子を出力方向に設定 */

127                                         /* MTU2 機能選択時は入出力方向も設定します。 */

128                                         /* また本設定後、端子からは'L'が出力されます。 */

129

130     /* === ADC (AN0 入力) の設定 === */

131     PORT.PHCR0.BIT.PH0MD = 1;          /* PH0 端子を AN0 に設定 */

132 }

133

```

## 3.6 サンプルプログラムリスト "main.c" (5)

```

134  /* " FUNC COMMENT " ****

135  * ID          :

136  * Outline     : DMAC の初期設定

137  *-----

138  * Include     : "iodefine.h"

139  *-----

140  * Declaration : void io_init_dmac(void *src, void *dst, int count);

141  *-----

142  * Description  : ダイレクトメモリアクセスコントローラ(DMAC)の初期設定を行います。

143  *                 : 動作モード：サイクルスチールモード

144  *                 : 内蔵周辺モジュールリクエスト：A/D 変換器、

145  *                 : 転送元：A/D データレジスタ A、転送先：高速内蔵 RAM、

146  *                 : 転送データ長：ワード。リロード機能は使用しません。

147  *-----

148  * Argument    : void *src ; I : 転送元アドレス

149  *                 : void *dst ; O : 転送先アドレス

150  *                 : int count ; I : 転送回数

151  *-----

152  * Return Value: void

153  *-----

154  * Note        :

155  * " FUNC COMMENT END " ****

156 void io_init_dmac(void *src, void *dst, int count)

157 {

158     volatile unsigned long dummy;

159

160     /* ===スタンバイコントロールレジスタ 2 (STBCR2) の設定 === */

161     CPG.STBCR2.BIT.MSTP8 = 0;           /* DMAC へのクロック供給 */

162

163     /* ===DMA_チャネル 0 転送禁止 === */

164     DMAC.CHCR0.BIT.DE = 0x0;           /* DMA 禁止 */

165

166     /* ===DMA ソースアドレスレジスタ_0 (SAR_0) の設定 === */

167     DMAC.SAR0.LONG = (unsigned long)src;

168

169     /* ===DMA デスティネーションアドレスレジスタ_0 (DAR_0) の設定 === */

170     DMAC.DAR0.LONG = (unsigned long)dst;

171

172     /* ===DMA トランスマカウントレジスタ_0 (DMATCR_0) の設定 === */

173     DMAC.DMATCR0.LONG = count;

174

```

## 3.7 サンプルプログラムリスト "main.c" (6)

```

175     /* =====DMA チャネルコントロールレジスタ_0 (CHCR_0) の設定 ===== */

176     dummy = DMAC.CHCR0.LONG;      /* TE フラグクリアのためのダミーリード */

177     DMAC.CHCR0.LONG = 0x0000480c;

178

179             /*

180             bit31   : TC DMATCR 転送 : 0----- 1 回の転送要求で 1 回転送

181             bit30   : reserve 0

182             bit29   : RLDSAR ON : 0----- リロード機能無効 (RSAR)

183             bit28   : RLDDAR ON : 0----- リロード機能無効 (RDAR)

184             bit27   : reserve 0

185             bit26   : DAF :0----- 未使用

186             bit25   : SAF :0----- 未使用

187             bit24   : reserve 0

188             bit23   : DO over run0 : 0----- 未使用

189             bit22   : TL TEND low active : 0--- 未使用

190             bit21   : reserve 0

191             bit20   : TEMASK :0----- 未使用

192             bit19   : HE :0----- 未使用

193             bit18   : HIE :0----- 未使用

194             bit17   : AM :0----- 未使用

195             bit16   : AL :0----- 未使用

196             bit15-14 : DM1:0 DM0:1----- デスティネーションアドレス増加

197             bit13-12 : SM1:0 SM0:0----- ソースアドレス固定

198             bit11-8  : RS : B'1000----- DMA 拡張リソースセレクタ

199             bit7    : DL : DREQ level : 0 ----- 未使用

200             bit6    : DS : DREQ select :0 Low level 未使用

201             bit5    : TB :cycle :0----- サイクルスチール

202             bit4-3  : TS : transfer size:B'01-- ワード単位転送

203             bit2    : IE : interrupt enable:1-- 割り込み許可

204             bit1    : TE : transfer end:0----- TE フラグのクリア

205             bit0    : DE : DMA enable bit:0---- DMA 転送禁止

206

207     /* =====割り込み優先レベル設定レジスタ 06 (IPR06) の設定===== */

208     INTC.IPR06.BIT._DMAC0 = 0xf; /* 割り込みレベルを 15 に設定 */

209

210     /* ----DMA オペレーションレジスタ (DMAOR) の設定---- */

211     DMAC.DMAOR.WORD |= 0x0007; /* DME ビットをセット。アドレスエラーフラグ、*/

212                               /* NMI フラグのクリア防止のため、AE ビット、*/

213                               /* NMIF フラグには 1 をライト */

214     /* ----DMA 拡張リソースセレクタ (DMARSO) の設定---- */

215     DMAC.DMARS0.BYTE.CH0 = 0xB3; /* 転送要求元を ADC に設定 */

216

217     /* =====DMA_チャネル 0 転送許可===== */

218     DMAC.CHCR0.BIT.DE = 0x1;

219 }

```

## 3.8 サンプルプログラムリスト "main.c" (7)

```

220  /* "FUNC COMMENT" ****

221  * ID      :

222  * Outline   : A/D 変換器の初期設定

223  *-----

224  * Include    : "iodefine.h"

225  *-----

226  * Declaration : void init_adc(void);

227  *-----

228  * Description  : A/D 変換器(ADC)の初期設定を行います。

229  *                 : 動作モード：シングルモード、A/D 起動要因：TRGAN(MTU2)

230  *-----

231  * Argument     : void

232  *-----

233  * Return Value : void

234  *-----

235  * Note         :

236  * "FUNC COMMENT END" ****

237 void io_init_adc(void)

238 {

239     volatile unsigned short dummy;

240

241     /* === スタンバイコントロールレジスタ 3 (STBCR3) の設定 === */

242     CPG.STBCR3.BIT.MSTP32 = 0;          /* ADC へのクロック供給 */

243

244     /* === A/D コントロール／ステータスレジスタ (ADCSR) の設定 === */

245     dummy = ADC.ADCSR.WORD;           /* ADF フラグクリアのためのダミーリード */

246     ADC.ADCSR.WORD = 0x4280;

247

248     /*

249      bit15  : ADF:0----- A/D エンドフラグのクリア

250      bit14  : ADIE:1----- A/D 変換終了割り込み(ADI)要求を許可

251      bit13  : ADST:0----- A/D 変換を停止

252      bit12-9 : TRGS[3:0]:B'0001 - MTU2 からの変換トリガ TRGAN

253      bit8-6  : CKS[2:0]:B'010 --- 変換時間=308*tcyc > 4us (B φ: 72MHz 時)

254      bit5-3  : MDS[2:0]:B'000 --- シングルモード

255      bit2-0  : CH[2:0]:B'000 ---- チャネル : AN0

256

257     */

258 }

```

## 3.9 サンプルプログラムリスト "main.c" (8)

```

257  /* "FUNC COMMENT" ****

258  * ID          :

259  * Outline     : MTU2 の初期設定

260  *-----

261  * Include     : "iodefine.h"

262  *-----

263  * Declaration : void init_mtu2(void);

264  *-----

265  * Description  : マルチファンクションタイマパルスユニット 2 (MTU2) の初期設定を行います。

266  *                 : 動作モード : PWM モード 1、

267  *                 : TCNT のカウント : 内部クロック  $P\phi/64$  でカウント、

268  *                 : A/D 変換開始要求を行います。

269  *-----

270  * Argument    : void

271  *-----

272  * Return Value : void

273  *-----

274  * Note        :

275  * "FUNC COMMENT END" ****

276 void io_init_mtu2(void)

277 {

278     /* ===スタンバイコントロールレジスタ (STBCR3) の設定 === */

279     CPG.STBCR3.BIT.MSTP35 = 0;           /* MTU2 へのクロック供給*/

280

281     /* ===タイマスタートレジスタ (TSTR) の設定 === */

282     MTU2.TSTR.BIT.CST0 = 0;             /* タイマカウンタ(TCNT_0)カウント停止 */

283

284     /* ===タイマモードレジスタ_0 (TMDR_0) の設定== */

285     MTU2.TMDR_0.BYTE = 0x02;            /* PWM モード 1 に設定 */

286

287     /* ===タイマインタラブトイネーブルレジスタ (TIER_0) の設定 == */

288     MTU2.TIER_0.BYTE = 0x80;            /* TGRA のインプットキャプチャ／コンペアマッチによる */

289                                         /* A/D 変換開始要求の発生を許可 */

290

291     /* ===タイマコントロールレジスタ (TCR_0) の設定 == */

292     MTU2.TCR_0.BYTE = 0x23;

293     /*

294         bit7-5 : CCLR:B'001---TRGA のコンペアマッチで TCNT クリア

295         bit4-3 : CKEG:B'00----入力クロックの立ち上がりエッジで TCNT カウント

296         bit2-0 : TPSC:B'011---内部クロック: $P\phi/64$  でカウント

297     */

298

299     /* ===タイマ I/O コントロールレジスタ H_0 (TIORH_0) の設定 == */

300     MTU2.TIORH_0.BYTE = 0x21;

301     /*

302         bit7-4 : IOB:B'0010---TGRB はアウトプットコンペアレジスタとして動作

303                                         初期出力は 0 出力 (PWM モード 1 時は無効)

304                                         コンペアマッチで 1 出力

305         bit3-0 : IOA:B'0001---TGRA はアウトプットコンペアレジスタとして動作

306                                         初期出力は 0 出力

307                                         コンペアマッチで 0 出力

308     */

```

## 3.10 サンプルプログラムリスト "main.c" (9)

```

309     /* === タイマジエネラルレジスタ (TGRA_0) の設定 === */

310     MTU2.TGRA_0.WORD = 562;           /* f(1kHz) = TCNT カウンタクロック (36MHz/64) / (N+1) */

311           /* N = 562(0x232) */

312     /* === タイマジエネラルレジスタ (TGRB_0) の設定 === */

313     MTU2.TGRB_0.WORD = 280;           /* f(2kHz) = TCNT カウンタクロック (36MHz/64) / (N+1) */

314           /* N = 280(0x118) */

315     /* === タイマスタートレジスタ (TSTR) の設定 === */

316     MTU2.TSTR.BIT.CST0 = 1;          /* タイマカウンタ(TCNT_0)カウントスタート */

317 }

318

319 /* ** FUNC COMMENT **** */

320 * ID           :

321 * Outline      : DMA 転送完了割り込み (チャネル 0)

322 *

323 * Include      : "iodefine.h"

324 *

325 * Declaration  : void io_interrupt_dmac_dei0(void);

326 *

327 * Description   : DMAC チャネル 0 の転送完了割り込みを処理します。

328 *                   : DMA を停止して TEND フラグをクリアします。

329 *                   : また、MTU2 のタイマカウントを停止します。

330 *

331 * Argument      : void

332 *

333 * Return Value  : void

334 *

335 * Note          :

336 /* ** FUNC COMMENT END **** */

337 void io_interrupt_dmac_dei0( void )

338 {

339     volatile unsigned long dummy;

340

341     /* === DMA 転送の停止 === */

342     DMAC.CHCR0.BIT.DE = 0;

343

344     /* === TEND フラグのクリア === */

345     DMAC.CHCR0.BIT.TE = 0;

346     dummy = DMAC.CHCR0.LONG; /* 確実にフラグクリアを行うためのダミーリード */

347

348     /* === MTU2 のタイマカウンタ(TCNT_0)を停止 === */

349     MTU2.TSTR.BIT.CST0 = 0;

350

351     /* === ADC の停止 === */

352     dummy = ADC.ADCSR.WORD;           /* ADF フラグクリアのためのダミーリード */

353     ADC.ADCSR.WORD = 0x0000;

354 }

355 /* End of File */

```

#### 4. 参考ドキュメント

- ソフトウェアマニュアル

SH-2A、SH2A-FPU ソフトウェアマニュアル Rev.3.00

(最新版をルネサスエレクトロニクスのホームページから入手してください。)

- ハードウェアマニュアル

SH7262 グループ、SH7264 グループ ハードウェアマニュアル Rev.2.00

(最新版をルネサスエレクトロニクスのホームページから入手してください。)

## ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

<http://japan.renesas.com/>

お問合せ先

<http://japan.renesas.com/inquiry>

すべての商標および登録商標は、それぞれの所有者に帰属します。

## 改訂記録

| Rev. | 発行日        | 改訂内容 |      |

|------|------------|------|------|

|      |            | ページ  | ポイント |

| 1.00 | 2010.04.15 | —    | 初版発行 |

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の記載が優先するものとします。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

### 3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子（または外部発振回路）を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子（または外部発振回路）を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

## ご注意書き

1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に關し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

3. 当社製品を改造、改変、複製等しないでください。

4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に關し、当社は、一切その責任を負いません。

5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができます。

6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができます。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に關し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準： コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準： 輸送機器（自動車、電車、船舶等）、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器（厚生労働省定義の管理医療機器に相当）

特定水準： 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器（生命維持装置、人体に埋め込み使用するもの、治療行為（患部切り出し等）を行うもの、その他直接人命に影響を与えるもの）（厚生労働省定義の高度管理医療機器に相当）またはシステム等

8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエーペンジング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に關して、当社は、一切その責任を負いません。

11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサス エレクトロニクス株式会社

■営業お問合せ窓口

<http://www.renesas.com>

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2（日本ビル）

(03)5201-5307

■技術的なお問合せおよび資料のご請求は下記へどうぞ。

総合お問合せ窓口：<http://japan.renesas.com/inquiry>