お客様各位

---

## カタログ等資料中の旧社名の扱いについて

---

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願ひ申し上げます。

ルネサスエレクトロニクス ホームページ (<http://www.renesas.com>)

2010年4月1日

ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (<http://www.renesas.com>)

【問い合わせ先】<http://japan.renesas.com/inquiry>

## ご注意書き

1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

3. 当社製品を改造、改変、複製等しないでください。

4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準： コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パソコン機器、産業用ロボット

高品質水準： 輸送機器（自動車、電車、船舶等）、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器（厚生労働省定義の管理医療機器に相当）

特定水準： 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器（生命維持装置、人体に埋め込み使用するもの、治療行為（患部切り出し等）を行うもの、その他直接人命に影響を与えるもの）（厚生労働省定義の高度管理医療機器に相当）またはシステム等

8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエーペンギング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

## SH7262/SH7264 グループ

### FIFO 内蔵シリアルコミュニケーションインターフェース クロック同期式シリアル通信設定例（全二重）

#### 要旨

本アプリケーションノートでは、FIFO 内蔵シリアルコミュニケーションインターフェース（SCIF）機能のクロック同期式シリアル通信について説明しています。

#### 動作確認デバイス

SH7262/SH7264

以下、総称して「SH7264」として説明します。

#### 目次

|                     |    |

|---------------------|----|

| 1. はじめに .....       | 2  |

| 2. 応用例の説明 .....     | 3  |

| 3. 参考プログラムリスト ..... | 15 |

| 4. 参考ドキュメント .....   | 24 |

## 1. はじめに

### 1.1 仕様

- FIFO 内蔵シリアルコミュニケーションインターフェース (SCIF) のチャネル 1 をクロック同期式モードの送受信モジュールとして初期化します。

- 送信および受信割り込みによって、SCIF チャネル 1 の全二重通信を行います。送信側は送信 FIFO データエンブティ割り込みで、受信側は受信 FIFO データフル割り込みで、それぞれの割り込み処理が起動します。

### 1.2 使用機能

- FIFO 内蔵シリアルコミュニケーションインターフェース (SCIF)

- 割り込みコントローラ

### 1.3 適用条件

|            |                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| マイコン       | SH7262/SH7264                                                                                                                                                                                                                                                 |

| 動作周波数      | 内部クロック : 144 MHz<br>バスクロック : 72 MHz<br>周辺クロック : 36 MHz                                                                                                                                                                                                        |

| 統合開発環境     | ルネサステクノロジ製<br>High-performance Embedded Workshop Ver.4.07.00                                                                                                                                                                                                  |

| C コンパイラ    | ルネサステクノロジ製 SuperH RISC engine ファミリ<br>C/C++コンパイラパッケージ Ver.9.03 Release00                                                                                                                                                                                      |

| コンパイルオプション | High-performance Embedded Workshop でのデフォルト設定<br>(-cpu=sh2afpu -fpu=single -object="\$(CONFIGDIR)\$(FILEEAF).obj" -debug<br>-gbr=auto -chgincpath -errorpath -global_volatile=0 -opt_range=all<br>-infinite_loop=0 -del_vacant_loop=0 -struct_alloc=1 -nologo) |

### 1.4 関連アプリケーションノート

本アプリケーションノートに関連するアプリケーションノートを以下に示します。合わせて参照してください。

- SH7262/SH7264 グループ 初期設定例

- SH7262/SH7264 グループ FIFO 内蔵シリアルコミュニケーションインターフェース 調歩同期式モード 送信設定例

- SH7262/SH7264 グループ FIFO 内蔵シリアルコミュニケーションインターフェース 調歩同期式モード 受信設定例

### 1.5 "L"アクティブ端子（信号）の表記について

端子名（信号名）末尾の#は“L”アクティブ端子（信号）であることを示します。

## 2. 応用例の説明

本応用例では、FIFO内蔵シリアルコミュニケーションインターフェース（SCIF）を使用します。

### 2.1 使用機能の動作概要

SCIF のクロック同期式モードでは、クロックパルスに同期してデータ送受信を行います。クロックソースとして内部クロックまたは、SCK 端子より外部クロック入力の選択ができます。内部クロックを選択した場合は、同期クロックを SCK 端子から出力します。外部クロックを選択した場合は、同期クロックを SCK 端子に入力します。通信フォーマットは、8 ビットデータ固定です。

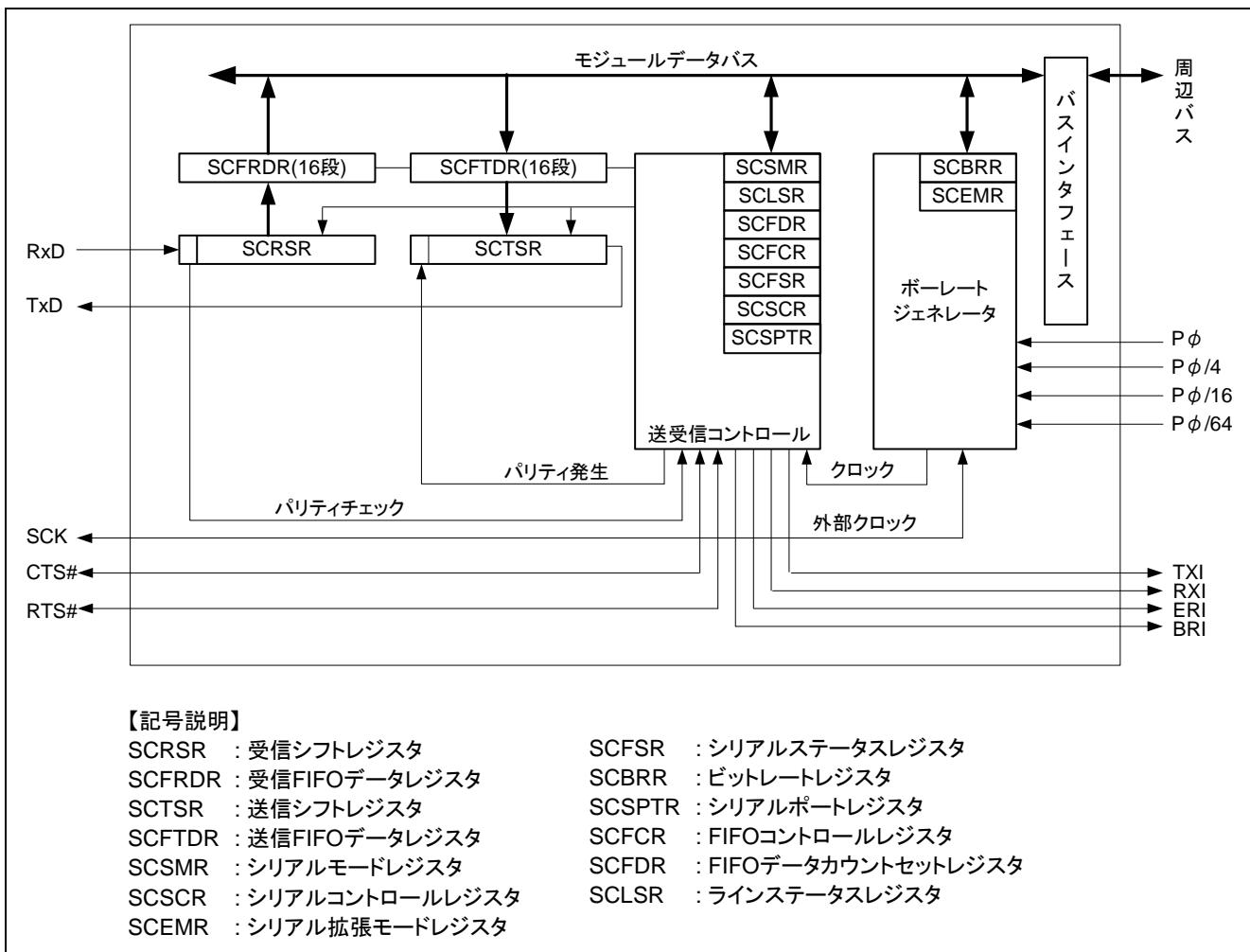

表 1 にクロック同期式モードの概要を示します。図 1 に SCIF のブロック図を示します。

表1 SCIF（クロック同期式モード）の概要

| 項目        | 概要                                                                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| チャネル数     | 8 チャネル (SCIF0～SCIF7)                                                                                                                                                                                             |

| クロックソース   | 内部クロック : $P\phi$ , $P\phi/4$ , $P\phi/16$ , $P\phi/64$ $P\phi$ : 内蔵周辺クロック<br>外部クロック : SCK0～SCK3 端子入力クロック                                                                                                         |

| データフォーマット | 転送データ長 : 8 ビット固定<br>転送順序 : LSB ファースト固定                                                                                                                                                                           |

| ボーレート     | 内部クロックを選択時 : 549bps～9Mbps ( $P\phi=36MHz$ 動作時)<br>外部クロックを選択時 : 最大 3Mbps<br>( $P\phi=36MHz$ 、外部入力クロック 3MHz 動作時)<br>【注】SH7264 と通信相手先の電気的特性を満足することを確認してください。                                                        |

| エラー検出     | オーバランエラー                                                                                                                                                                                                         |

| 割り込み要求    | 送信 FIFO データエンプティ (TDFE) による割り込み (TXI)<br>ブレーク (BRK) またはオーバランエラー (ORER) による割り込み (BRI)<br>受信 FIFO データフル (RDF) またはデータレディ (DR) による割り込み (RXI)<br>受信エラー (ER) による割り込み (ERI)                                             |

| その他       | <ul style="list-style-type: none"><li>内部クロックを選択した場合に、SCK 端子から同期クロックを出力</li><li>消費電力低減のために、未使用チャネルのクロック供給を停止させることが可能</li><li>送信および受信 FIFO データレジスタ内に格納されている有効データ数、および受信 FIFO データレジスタ内に格納されている受信エラー数を検出可能</li></ul> |

【注】 SCIF についての詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル FIFO 内蔵シリアルコミュニケーションインターフェース」の章を参照してください。

図 1 SCIF のブロック図

## 2.2 使用機能の設定手順

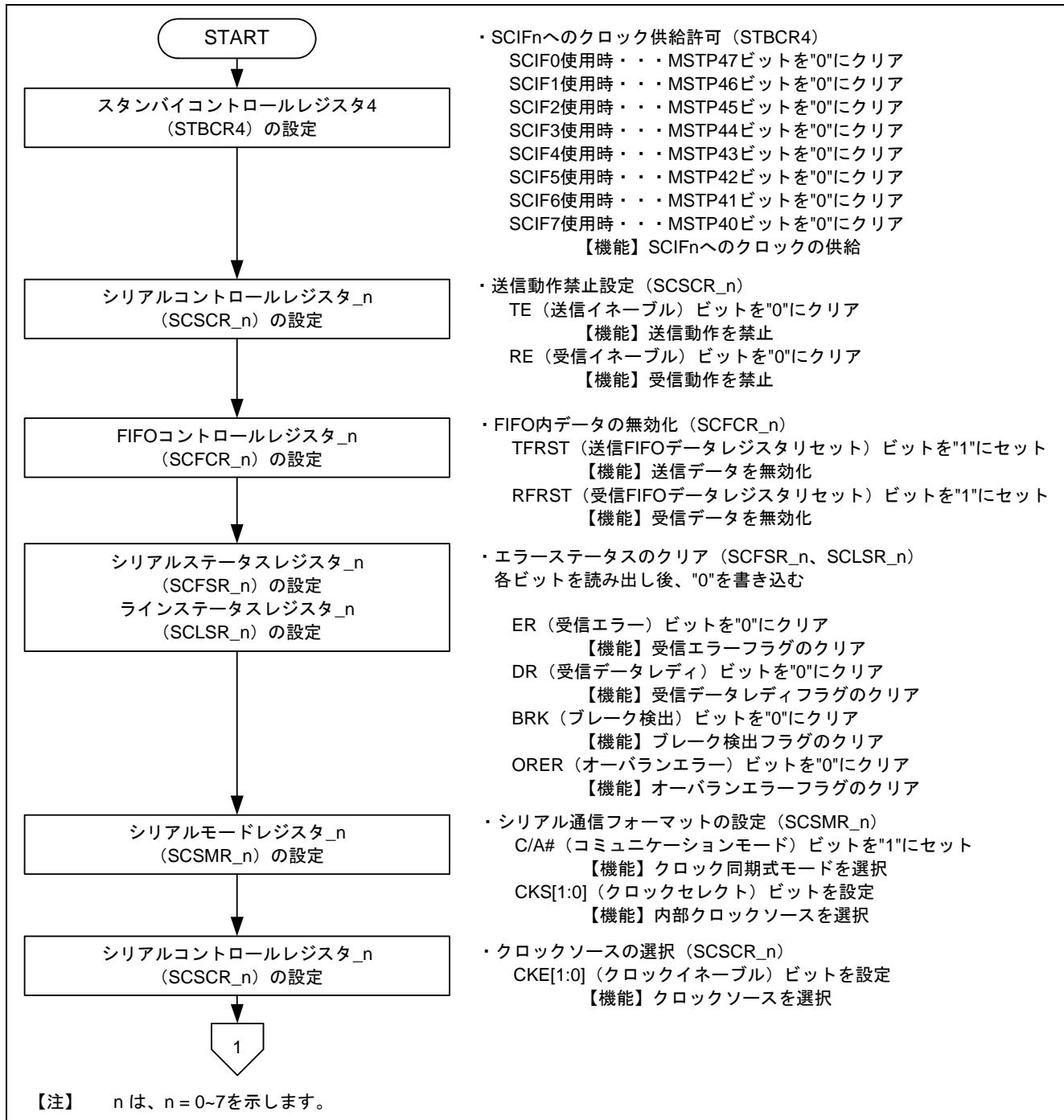

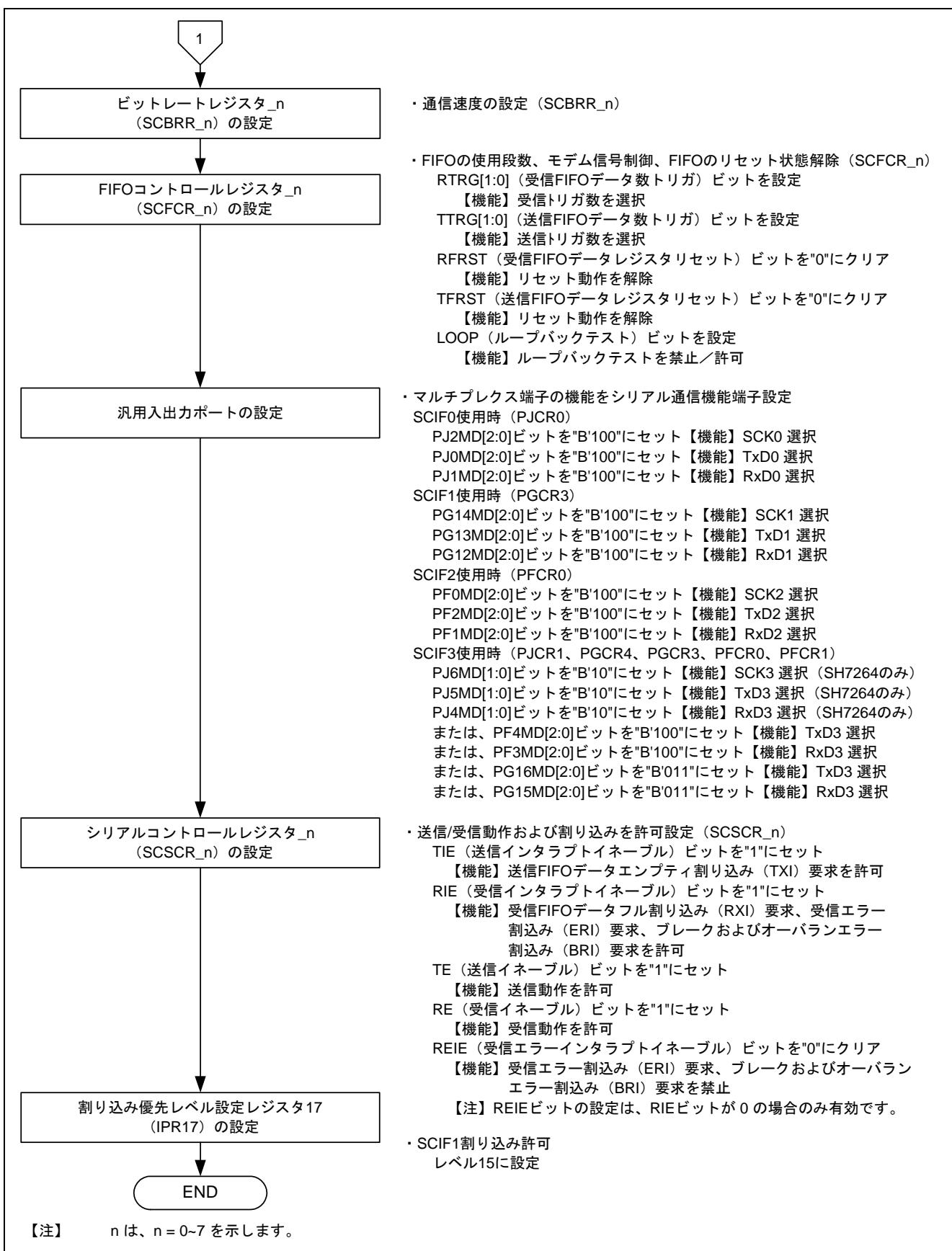

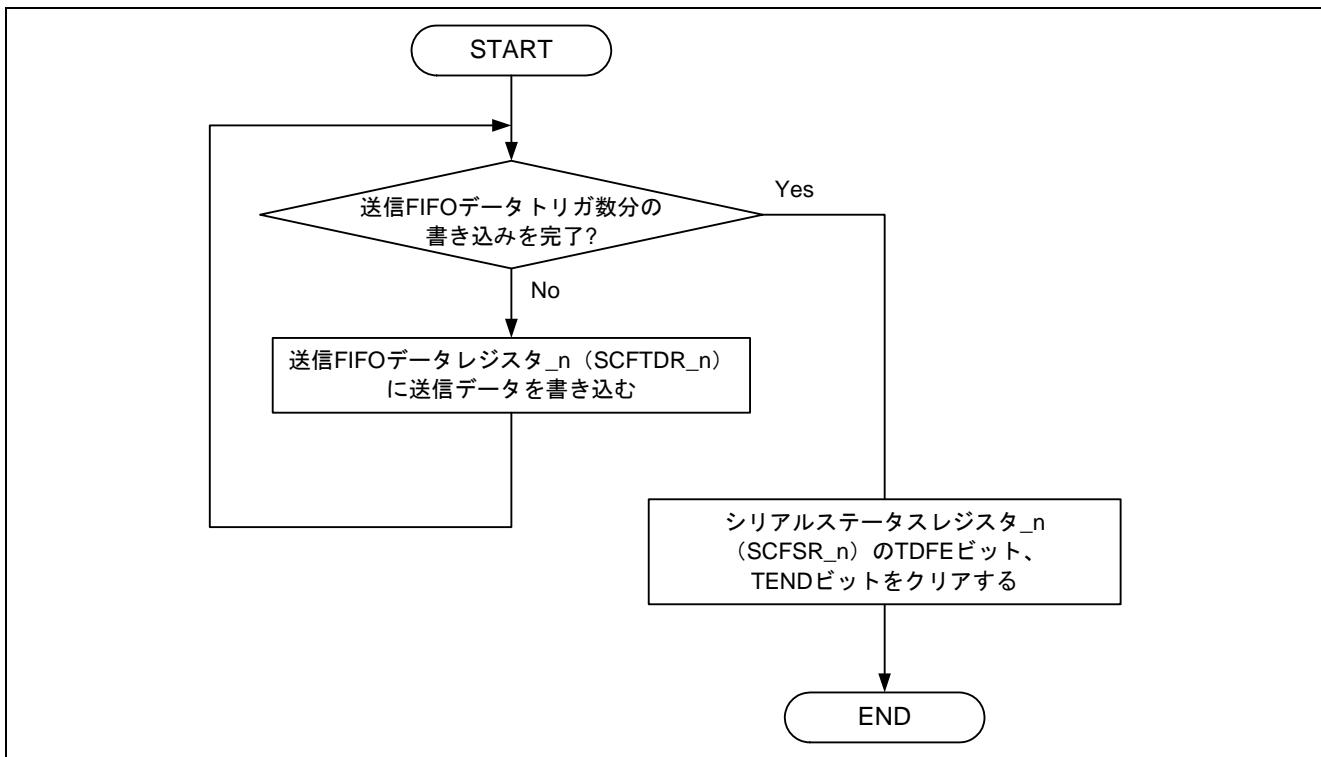

ここでは、SCIFのクロック同期式モードの基本的な設定例について説明します。図2、図3にクロック同期式モード送受信初期設定フロー例を、図4にクロック同期式モード送信割り込み設定処理フロー例を、図5にクロック同期式モード受信割り込み処理フロー例を示します。また、図6にオーバランエラー割り込み処理フロー例を示します。各レジスタ設定の詳細は、「SH7262 グループ、SH7264 グループ ハードウェアマニュアル FIFO内蔵シリアルコミュニケーションインターフェース」を参照してください。

図2 クロック同期式モード送受信初期設定フロー例 (1)

図3 クロック同期式モード送受信初期設定フロー例 (2)

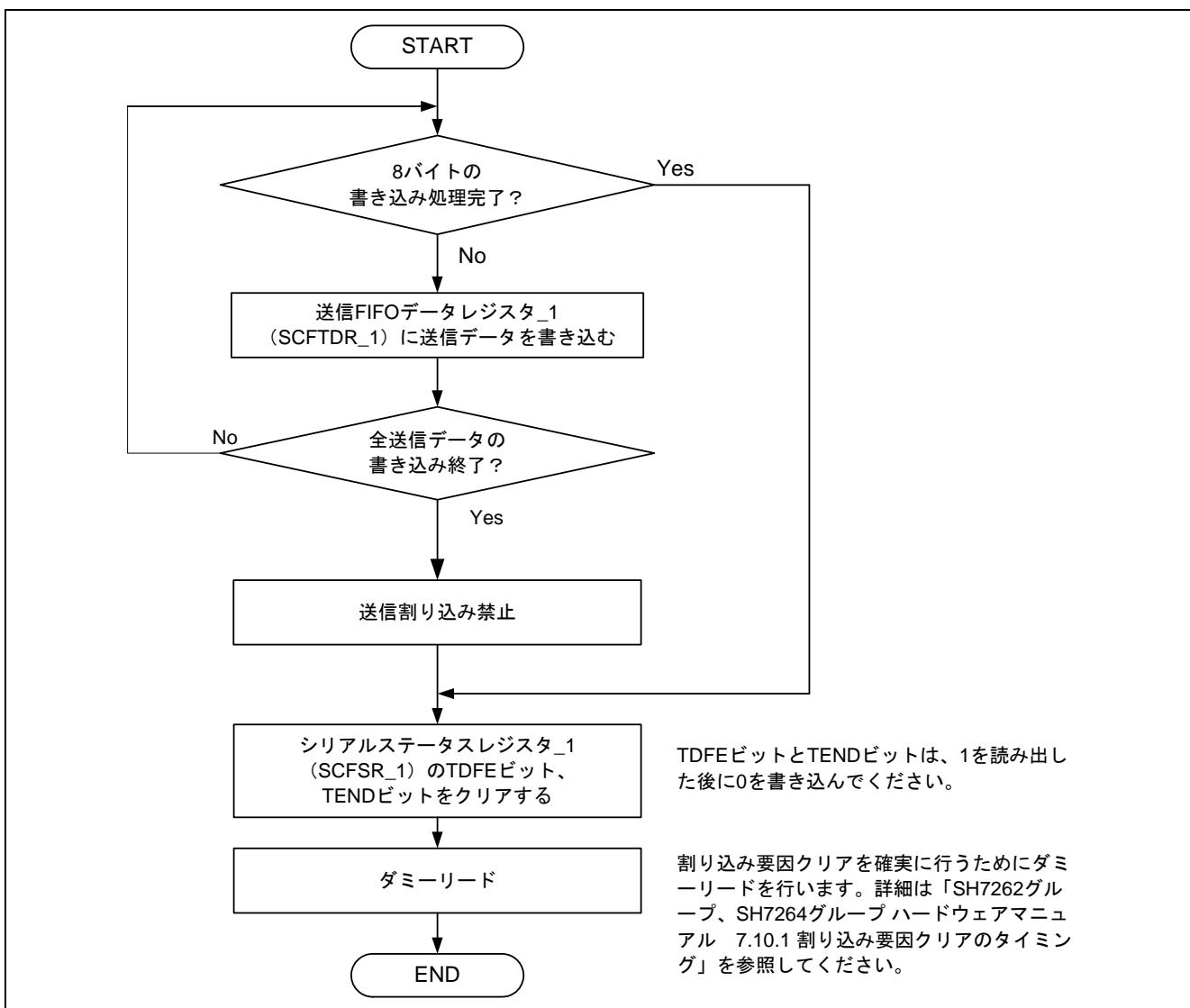

図4 クロック同期式モード送信割り込み処理（TXI）フロー例

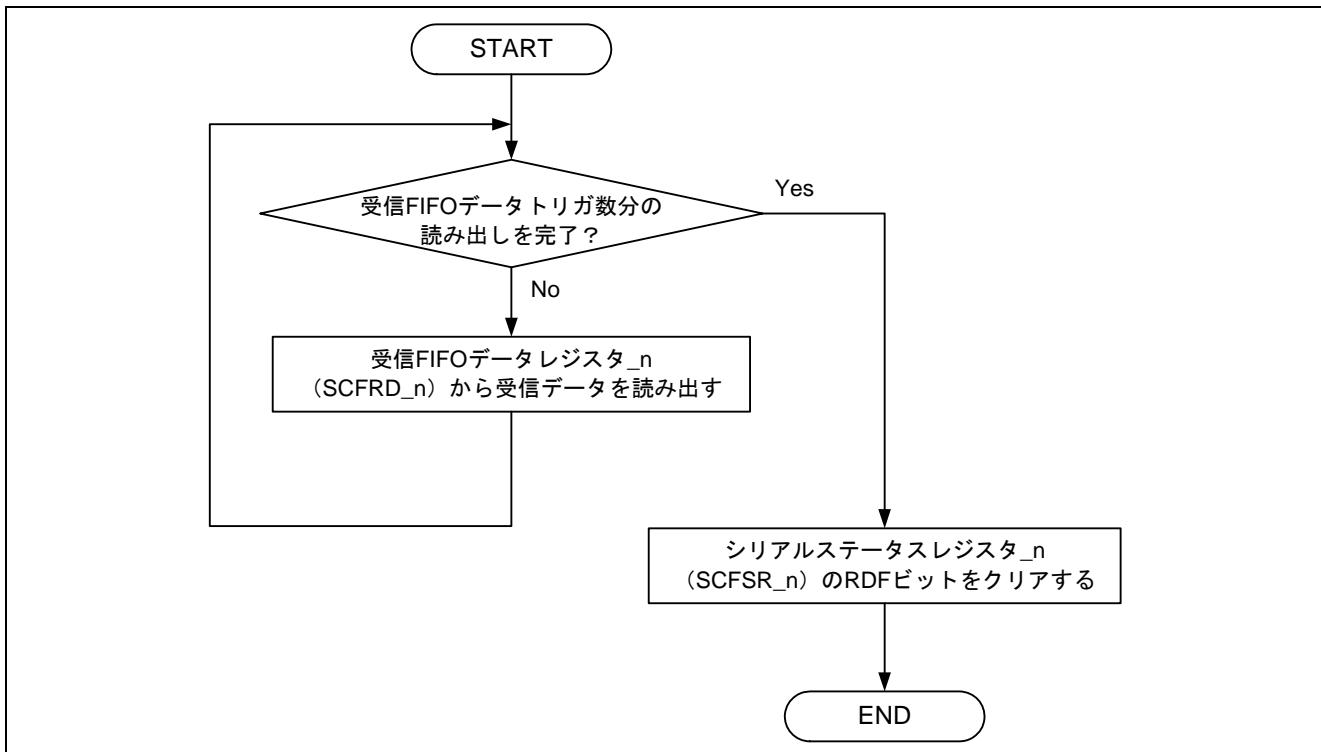

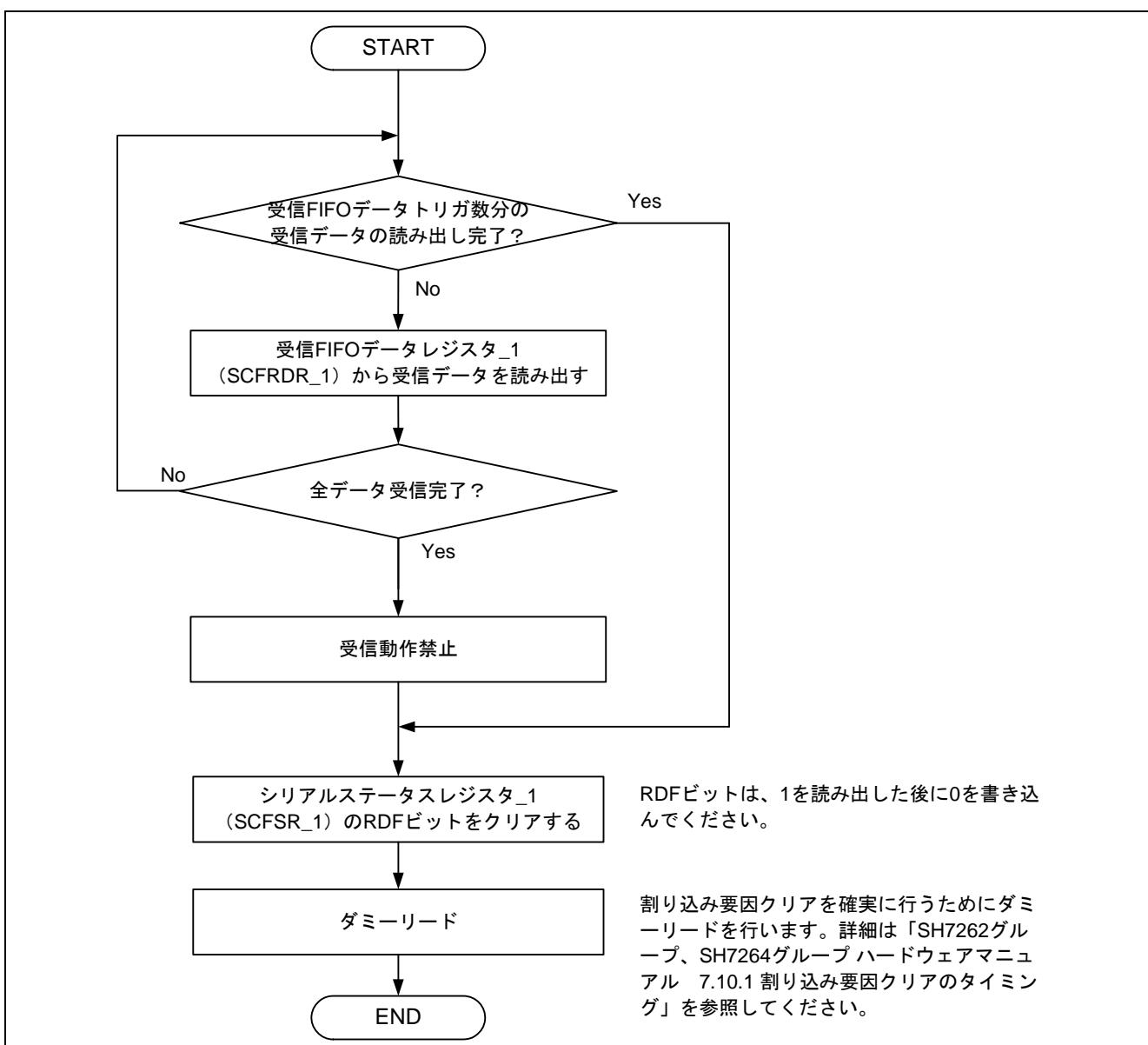

図5 クロック同期式モード受信割り込み処理（RXI）フロー例

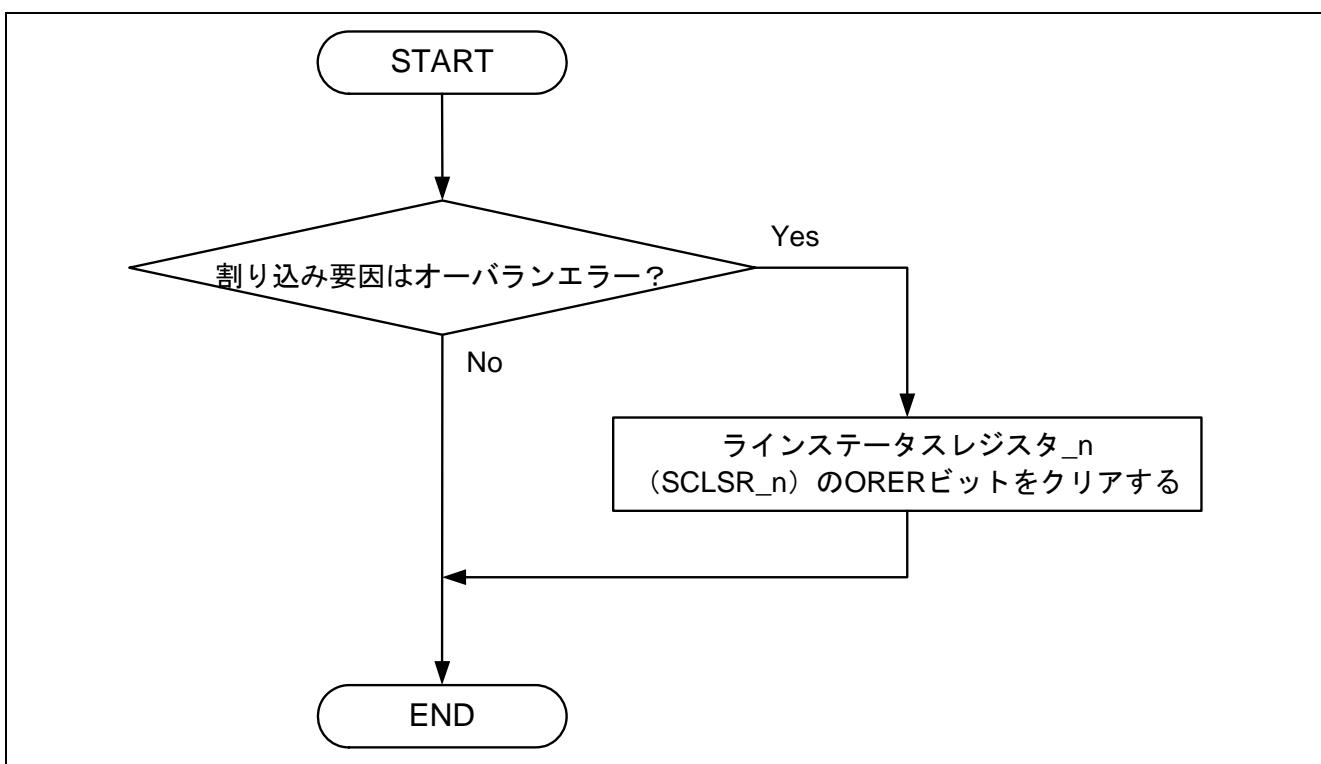

図6 オーバランエラー割り込み処理 (BRI) フロー例

### 2.3 参考プログラムの動作

本参考プログラムでは、SCIF チャネル 1 をクロック同期式モード送受信モジュールとして使用します。SCIF チャネル 1 のループバックテスト機能を使用して、シリアル送信端子 TxD1 と受信端子 RxD1 端子を内部で接続し、全二重通信を行います。ループバックテスト機能は、FIFO コントロールレジスタ (SCFCR) のループバックテスト (LOOP) ビットを 1 にセットすることにより有効になります。

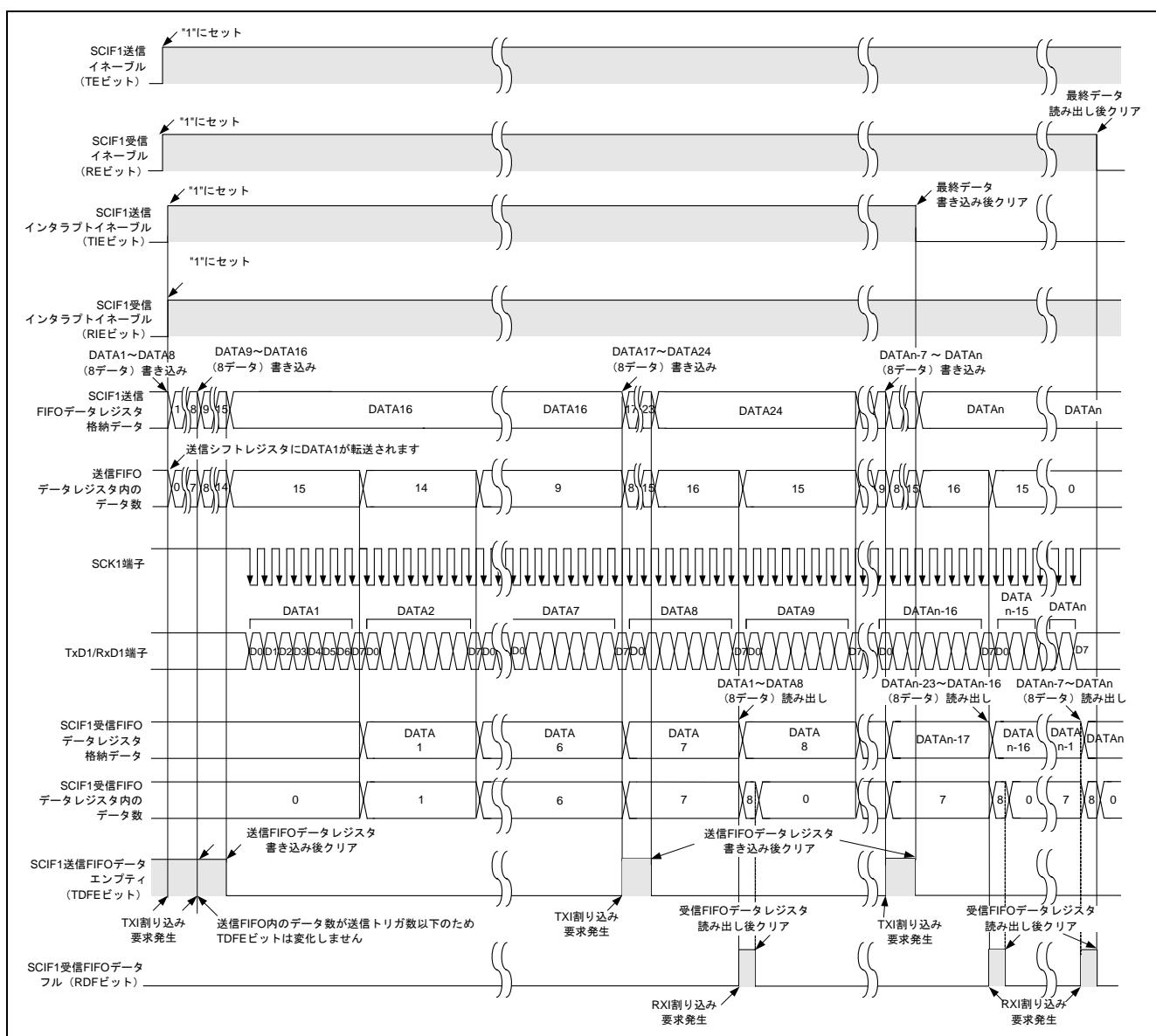

表 2 に参考プログラムの通信機能設定を示します。また、図 7 に参考プログラムの動作タイミングを示します。

表2 参考プログラムの通信機能設定

| 通信フォーマット     | 設定機能                              |

|--------------|-----------------------------------|

| 通信モード        | クロック同期式                           |

| 使用チャネル       | チャネル 1                            |

| 割り込み         | 送信 FIFO データエンプティ<br>受信 FIFO データフル |

| 通信速度         | 100kbps                           |

| データ長         | 8 ビット                             |

| ビット順序        | LSB ファースト                         |

| 同期クロック       | SCIF チャネル 1 の外部クロック出力             |

| FIFO データ数トリガ | 受信 : 8、送信 : 8                     |

| ループバックテスト機能  | 許可 (TxD1 端子と RxD1 端子を内部で接続)       |

図7 参考プログラムの動作タイミング

## 2.4 参考プログラムの処理手順

参考プログラムでは、SCIF チャネル 1 をクロック同期式モード送受信モジュールとして使用し、送信および受信割り込みによる全二重通信を行います。送信割り込み処理では、送信 FIFO データ数トリガを 8 に設定しており、1 回の割り込み処理で 8 バイトの送信データを送信 FIFO データレジスタ (SCFTDR\_1) に書き込みます。受信割り込み処理では、受信 FIFO データ数トリガを 8 に設定しており、1 回の割り込み処理で受信 FIFO データレジスタ (SCFRDR\_1) から 8 バイトの受信データを読み出します。

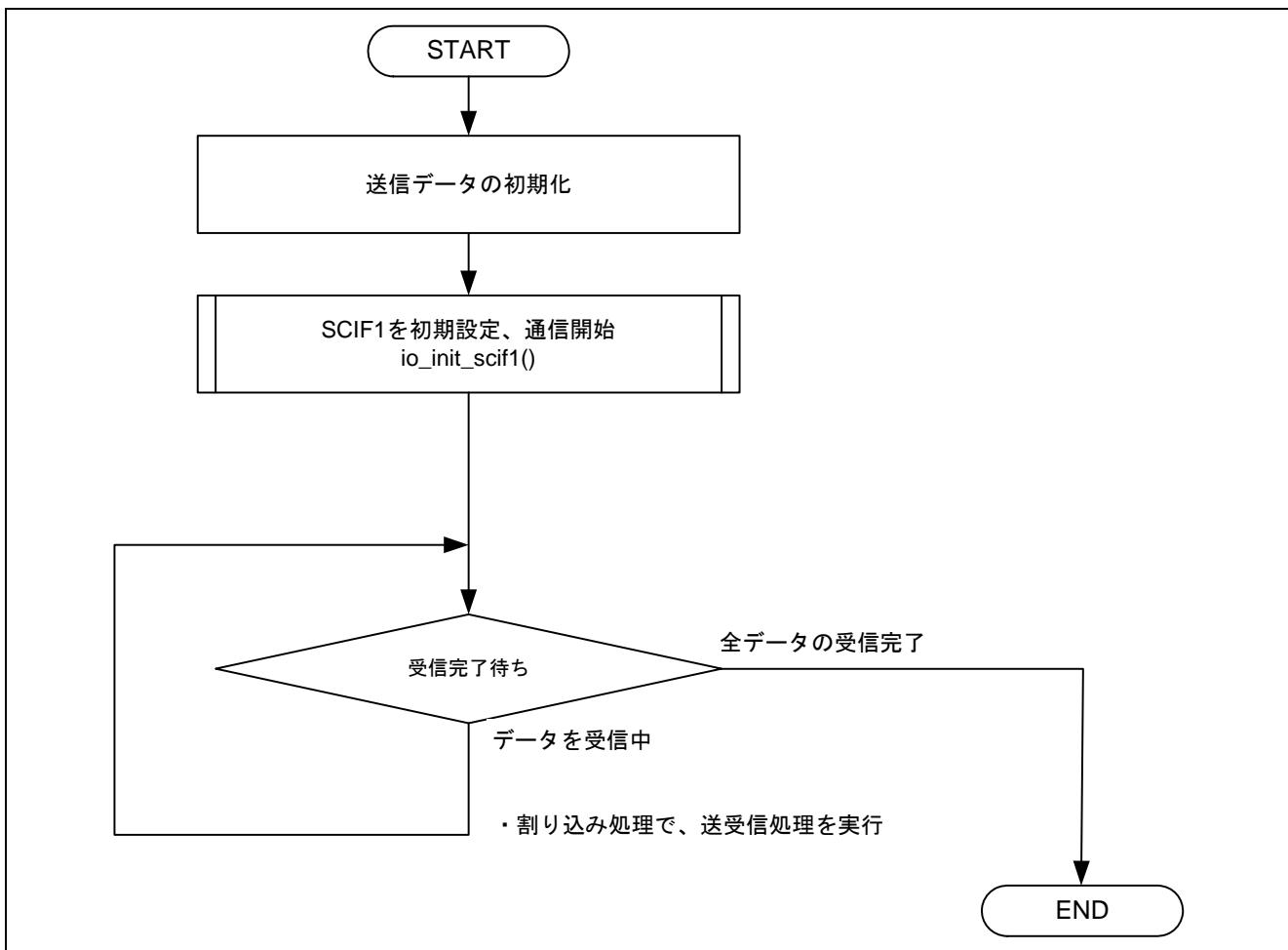

表 3 に参考プログラムにおけるレジスタ設定値を示します。また図 8～図 10 に参考プログラムの処理フローを示します。

表3 参考プログラムのレジスタ設定

| レジスタ名                           | アドレス        | 設定値    | 機能と設定値                                                                                                                                                                                                                                                  |

|---------------------------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 4 (STBCR4)  | H'FFFE 040C | H'BF   | <ul style="list-style-type: none"> <li>MSTP46="0" : SCIF1 は動作 (クロック供給)</li> </ul>                                                                                                                                                                       |

| ポート G コントロール<br>レジスタ 3 (PGCR3)  | H'FFFE 38C8 | H'0444 | <ul style="list-style-type: none"> <li>PG14MD[2:0]= "B'100" : SCK1 出力 (SCIF1)</li> <li>PG13MD[2:0]= "B'100" : TxD1 出力 (SCIF1)</li> <li>PG12MD[2:0]= "B'100" : RxD1 出力 (SCIF1)</li> </ul>                                                                |

| シリアルコントロール<br>レジスタ_1 (SCSCR_1)  | H'FFFE 8808 | H'0000 | <ul style="list-style-type: none"> <li>TE="0" : 送信動作を禁止</li> <li>RE="0" : 受信動作を禁止</li> <li>CKE[1:0]= "B'00" : 内部クロック/SCK 端子は同期クロック出力</li> </ul>                                                                                                         |

|                                 |             | H'00F0 | <ul style="list-style-type: none"> <li>TIE="1" : 送信割り込み動作を許可</li> <li>RIE="1" : 受信割り込み動作および受信エラー割り込み動作、ブレークおよびオーバランエラー割り込み動作を許可</li> <li>TE="1" : 送信動作を許可</li> <li>RE="1" : 受信動作を許可</li> <li>REIE="0" : 受信エラー割り込み動作、ブレークおよびオーバランエラー割り込み動作を禁止</li> </ul> |

| FIFO コントロール<br>レジスタ_1 (SCFCR_1) |             | H'0006 | <ul style="list-style-type: none"> <li>TFRST="1" : 送信 FIFO のリセット動作を許可</li> <li>RFRST="1" : 受信 FIFO のリセット動作を許可</li> </ul>                                                                                                                                |

|                                 |             | H'0081 | <ul style="list-style-type: none"> <li>RTRG[1:0]= B'10 : 受信 FIFO データ数= 8</li> <li>TTRG[1:0]= B'00 : 送信 FIFO データ数= 8</li> <li>TFRST="0" : 送信 FIFO のリセット動作を禁止</li> <li>RFRST="0" : 受信 FIFO のリセット動作を禁止</li> <li>LOOP="1" : ループバックテストを許可</li> </ul>         |

| シリアルステータスレジスタ<br>_1 (SCFSR_1)   | H'FFFE 8810 | H'FF6E | <ul style="list-style-type: none"> <li>ER="0" : 受信エラー</li> <li>BRK="0" : ブレーク検出</li> <li>DR="0" : 受信データレディ<br/>ビットクリアは読み出し後に 0 を書き込む</li> </ul>                                                                                                         |

| ラインステータスレジスタ<br>_1 (SCLSR_1)    | H'FFFE8824  | H'0000 | <ul style="list-style-type: none"> <li>ORER="0" : オーバランエラー<br/>ビットクリアは読み出し後に 0 を書き込む</li> </ul>                                                                                                                                                         |

| シリアルモードレジスタ_1<br>(SCSMR_1)      | H'FFFE 8800 | H'0080 | <ul style="list-style-type: none"> <li>C/A#="1" : クロック同期式モード</li> <li>CKS[1:0]= "0" : Pφクロック</li> </ul>                                                                                                                                                 |

| ビットレートレジスタ_1<br>(SCBRR_1)       | H'FFFE 8804 | H'59   | <ul style="list-style-type: none"> <li>100kbps 設定</li> </ul>                                                                                                                                                                                            |

図8 参考プログラムのメイン処理フロー

図10 参考プログラムの受信割り込み処理フロー

### 3. 参考プログラムリスト

#### 3.1 参考プログラムについての補足

SH7264 は、製品によって大容量内蔵 RAM の容量が 1MB または 640KB と異なるため、参考プログラムのセクション配置やレジスタの設定を一部変更する必要があります。そのため本アプリケーションノートでは 1MB 用と 640KB 用の 2 つのワークスペースを用意しています。

640KB 版はライトプロテクトを解除しなければ保持用内蔵 RAM へ書き込むことができないため、640KB 版のワークスペースは、システムコントロールレジスタ 5 (SYSCR5) にライトプロテクトの解除を設定しています。

使用する製品を確認した上で、対応するワークスペースを使用してください。

### 3.2 サンプルプログラムリスト "main.c" (1)

```

1  /*****

2  *  DISCLAIMER

3  *

4  *  This software is supplied by Renesas Technology Corp. and is only

5  *  intended for use with Renesas products. No other uses are authorized.

6  *

7  *  This software is owned by Renesas Technology Corp. and is protected under

8  *  all applicable laws, including copyright laws.

9  *

10 *  THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11 *  REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

12 *  INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13 *  PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14 *  DISCLAIMED.

15 *

16 *  TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17 *  TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18 *  FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19 *  FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

20 *  AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21 *

22 *  Renesas reserves the right, without notice, to make changes to this

23 *  software and to discontinue the availability of this software.

24 *  By using this software, you agree to the additional terms and

25 *  conditions found by accessing the following link:

26 *  http://www.renesas.com/disclaimer

27 ****

28 *  Copyright (C) 2010. Renesas Technology Corp., All Rights Reserved.

29 *  **FILE COMMENT***** Technical reference data ****

30 *  System Name : SH7264 Sample Program

31 *  File Name  : main.c

32 *  Abstract   : FIFO 内蔵シリアルコミュニケーションインターフェース(SCIF)

33 *                : クロック同期式シリアル送受信・割り込みサンプルプログラム

34 *  Version    : 1.00.00

35 *  Device     : SH7262/SH7264

36 *  Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

37 *                : C/C++ compiler package for the SuperH RISC engine family

38 *                : (Ver.9.03 Release00).

39 *  OS         : None

40 *  H/W Platform: M3A-HS64G50(CPU board)

41 *  Description :

42 ****

43 *  History    : Jan.29,2010 ver.1.00.00

44 *  **FILE COMMENT END***** */

45 #include <machine.h>

46 #include "iodefine.h"      /* SH7264 iodefine */

```

## 3.3 サンプルプログラムリスト "main.c" (2)

```

48  /* === プロトタイプ宣言 === */

49  void main(void);

50  void io_init_scif1(int);

51  void io_interrupt_scif1_bri(void);

52  void io_interrupt_scif1_rxi(void);

53  void io_interrupt_scif1_txi(void);

54

55  /* === 型宣言 === */

56  /* SCIF ポーレート設定 */

57  typedef struct {

58      unsigned char scbrr;

59      unsigned short scsmr;

60  } SH7264_BAUD_SET;

61

62  /* ---- ポーレート指定値 ---- */

63  enum{

64      CBR_500,

65      CBR_1K,

66      CBR_2_5K,

67      CBR_5K,

68      CBR_10K,

69      CBR_25K,

70      CBR_50K,

71      CBR_100K,

72      CBR_250K,

73      CBR_500K,

74      CBR_1M

75  };

76  /* ---- 転送データ数 ---- */

77  #define DATA_NUM          0x100u      /* 受信トリガ数の倍数を設定してください */

78

79  /* === 変数定義 === */

80  /* ---- レジスタ設定値テーブル(Pφ=36MHz) ---- */

81  static SH7264_BAUD_SET scif_baud[] = {

82      {255, 3}, /* 500Hz */

83      {140, 3}, /* 1,000Hz */

84      {224, 2}, /* 2,500Hz */

85      {112, 2}, /* 5,000Hz */

86      {224, 1}, /* 10,000Hz */

87      {89, 1}, /* 25,000Hz */

88      {179, 0}, /* 50,000Hz */

89      {89, 0}, /* 100,000Hz */

90      {35, 0}, /* 250,000Hz */

91      {17, 0}, /* 500,000Hz */

92      {8, 0} /* 1,000,000Hz */

93  };

94  unsigned int DataNum = DATA_NUM; /* 送信データ数 */

95  unsigned int SndCnt;           /* 送信カウンタ */

96  unsigned int RcvCnt;           /* 受信カウンタ */

97  unsigned char SndData[DATA_NUM]; /* 送信データ格納バッファ */

98  unsigned char RcvData[DATA_NUM]; /* 受信データ格納バッファ */

```

### 3.4 サンプルプログラムリスト "main.c" (3)

```

99  /* ** FUNC COMMENT *****/

100 * ID          :

101 * Outline     : サンプルプログラムメイン(クロック同期式シリアル I/O 送受信処理)

102 *-----

103 * Include     : "iodefine.h"

104 *-----

105 * Declaration : void main(void);

106 *-----

107 * Description  : SCIF1 の送信 FIFO データエンブティ割り込みと、受信データフル割り込みと

108 *                  : FIFO を使って、テストデータを送受信する。

109 *-----

110 * Argument    : void

111 *-----

112 * Return Value: void

113 *-----

114 * Note         :

115 * ** FUNC COMMENT END *****/

116 void main(void)

117 {

118     int i;

119

120     /* === 送信データの初期化 === */

121     for( i = 0; i < DATA_NUM; i++ ){

122         SndData[i] = (unsigned char)i;

123     }

124

125     /* === SCIF1 を初期設定、通信開始 === */

126     io_init_scif1(CBR_100K);      /* ビットレートは 100kbps を指定 */

127

128     /* === 受信完了待ち === */

129     while(RcvCnt < DATA_NUM){

130         /* 割り込み処理で送受信を実行 */

131     }

132

133     while (1) {

134         /* プログラムエンド */

135     }

136 }

137

```

### 3.5 サンプルプログラムリスト "main.c" (4)

```

138  /* ** "FUNC COMMENT" **** */

139  * ID          :

140  * Outline     : SCIF1 初期設定

141  *-----

142  * Include     : "iodefine.h"

143  *-----

144  * Declaration : void io_init_scif1(int bps);

145  *-----

146  * Description  : SCIF1 のクロック同期式で初期設定を行います

147  *                 : 設定は クロック同期式モード、外部クロック出力です。

148  *                 : また、送受信割り込みを許可します。

149  *-----

150  * Argument     : int bps ; I : ビットレート選択値

151  *-----

152  * Return Value : void

153  *-----

154  * Note         : ポーレート設定値は内部クロックを使った周辺モジュール用動作周波数

155  *                 :  $P_f = 36MHz$  の場合です。他のクロックを使用する場合はポーレート

156  *                 : 設定値を変更してください

157  * ** "FUNC COMMENT END" ****

158 void io_init_scif1(int bps)

159 {

160     /* === 低消費電力モードの解除 === */

161     /* ---- スタンバイコントロールレジスタ 4 (STBCR4) の設定 ---- */

162     CPG.STBCR4.BIT.MSTP46 = 0;          /* SCIF1 への、クロック供給開始 */

163

164     /* === SCIF1 の初期設定 === */

165     /* ---- シリアルコントロールレジスタ (SCSCRi) の設定 ---- */

166     SCIF1.SCSCR.WORD = 0x0000;          /* SCIF1 送受信動作停止 */

167

168     /* ---- FIFO コントロールレジスタ (SCFCRi) の設定 ---- */

169     SCIF1.SCFCR.WORD = 0x0006;          /* 受信／送信 FIFO リセット */

170

171     /* ---- シリアルステータスレジスタ (SCFSRi) の設定 ---- */

172     SCIF1.SCFSR.WORD &= 0xff6eu;        /* ER、BRK、DR ビットのクリア */

173

174     /* ---- ラインステータスレジスタ (SCLSRi) の設定 ---- */

175     SCIF1.SCLSR.BIT.ORER = 0;          /* ORER ビットクリア */

176

177     /* ---- シリアルモードレジスタ (SCSMRi) の設定 ---- */

178     SCIF1.SCSMR.WORD = scif_baud[bps].scsmr | 0x0080u;

179                 /* コミュニケーションモード 1: クロック同期式 */

180                 /* クロックセレクト          : テーブル値 */

181

182     /* ---- シリアルコントロールレジスタ (SCSCRi) の設定 ---- */

183     SCIF1.SCSCR.BIT.CKE = 0x0;          /* B'00 : 内部クロック / 同期クロック出力 */

184

185     /* ---- ビットレートレジスタ (SCBRRi) の設定 ---- */

186     SCIF1.SCBRR.BYTE = scif_baud[bps].scbrr;

187

```

## 3.6 サンプルプログラムリスト "main.c" (5)

```

188     /* ---- FIFO コントロールレジスタ(SCFCRi)の設定 ---- */

189     SCIF1.SCFCR.WORD = 0x0081;           /* RTS 出力アクティベートリガ      : 初期値 */

190                           /* 受信 FIFO データ数トリガ      B'10 : 8 データ */

191                           /* 送信 FIFO データ数トリガ      B'00 : 8 データ */

192                           /* モデムコントロールイネーブル  : 禁止 */

193                           /* 受信 FIFO データレジスタリセット : 禁止 */

194                           /* 送信 FIFO データレジスタリセット : 禁止 */

195                           /* ループバックテスト           1 : 許可 */

196

197     /* ===== 汎用入出力ポートの設定 ===== */

198     PORT.PGCR3.BIT.PG14MD = 4;           /* SCK1 端子に切り替え */

199     PORT.PGCR3.BIT.PG13MD = 4;           /* TxD1 端子に切り替え */

200     PORT.PGCR3.BIT.PG12MD = 4;           /* RxD1 端子に切り替え */

201

202     /* ---- 送信/受信動作および割り込みを許可 ---- */

203     SCIF1.SCSCR.WORD |= 0x00f0u;

204

205     /* ---- TXI1,RXI1 割り込み許可 ---- */

206     INTC.IPR17.BIT._SCIF1 = 15;          /* レベル 15 に設定 */

207 }

208

```

### 3.7 サンプルプログラムリスト "main.c" (6)

```

209  /* "FUNC COMMENT" ****

210  * ID          :

211  * Outline     : ブレークまたはオーバランによる割り込み処理 (BRI)

212  *-----

213  * Include     : "iodefine.h"

214  *-----

215  * Declaration : void io_interrupt_scif1_bri(void);

216  *-----

217  * Description  : クロック同期式モードで発生するオーバランエラー処理を行います。

218  *                 : 本サンプルでは ORER ビットのクリアのみ行います。

219  *-----

220  * Argument    : void

221  *-----

222  * Return Value: void

223  *-----

224  * Note        :

225  * "FUNC COMMENT END" ****

226 void io_interrupt_scif1_bri(void)

227 {

228     volatile unsigned short dummy;

229

230     /* === オーバランエラーの確認 === */

231     if(SCIF1.SCLSR.BIT.OLER == 1) {

232

233         /* ---- 割り込み要因クリア (OLER ビットのクリア) ---- */

234         SCIF1.SCLSR.BIT.OLER = 0;

235         dummy = SCIF1.SCLSR.WORD;      /* 割り込み要因を確実にクリアするためのダミーリード */

236     }

237 }

238 }

```

## 3.8 サンプルプログラムリスト "main.c" (7)

```

239  /*" "FUNC COMMENT" ****

240  * ID          :

241  * Outline     : 受信 FIFO データフルまたはデータレディによる割り込み処理 (RXI)

242  *

243  * Include     : "iodefine.h"

244  *

245  * Declaration : void io_interrupt_scif1_rxi(void);

246  *

247  * Description  : SCIF1 の RXI 割り込み処理を行います。クロック同期式モードでは

248  *                 : 受信 FIFO データフル割り込みによって起動されます。

249  *                 : 本サンプルでは初期設定にて受信 FIFO データ数トリガを 8 データに

250  *                 : 設定し、8 データ単位の読み出しを行います。

251  *                 : クロック同期式モードでは受信 FIFO データ数トリガに満たないデータ

252  *                 : を受信した場合のデータレディ割り込みは発生しないため、注意が

253  *                 : 必要です。

254  *

255  * Argument     : void

256  *

257  * Return Value : void

258  *

259  * Note         :

260  *""FUNC COMMENT END" ****

261 void io_interrupt_scif1_rxi(void)

262 {

263     int fifo_cnt;

264     volatile unsigned short dummy;

265

266     /* === 受信 FIFO の読み出し可能サイズを算出 === */

267     fifo_cnt = 8;

268

269     /* === 受信 FIFO からのデータ読み出し === */

270     while(fifo_cnt-- != 0 ){

271

272         /* ---- 受信データの読み出し ---- */

273         RcvData[RcvCnt++] = SCIF1.SCFRDR.BYTE;

274

275         /* ---- 全データ受信完了したか? ---- */

276         if(RcvCnt == DataNum){

277             /* ---- 受信動作を禁止 ---- */

278             SCIF1.SCSCR.BIT.RE = 0;

279             break;

280         }

281     }

282     /* === 割り込み要因クリア (RDF ビットのクリア) === */

283     SCIF1.SCFSR.BIT.RDF = 0;

284     dummy = SCIF1.SCFSR.WORD;      /* 割り込み要因を確実にクリアするためのダミーリード */

285 }

```

## 3.9 サンプルプログラムリスト "main.c" (8)

```

286  /* "FUNC COMMENT" ****

287  * ID          :

288  * Outline     : SCIF1 送信割り込み処理 (TXI)

289  *-----

290  * Include     : "iodefine.h"

291  *-----

292  * Declaration : void io_interrupt_scif1_txi(void);

293  *-----

294  * Description  : SCIF1 の TXI 割り込み処理を行います。送信 FIFO データエンブティ割り

295  *                 : 込みによって起動されます。

296  *                 : 本サンプルでは受信側の受信データ数にあわせ 8 バイトずつ送信データ

297  *                 : を書き込みます。送信データがなくなった場合は、送信 FIFO データ

298  *                 : エンブティ割り込みを禁止します。

299  *-----

300  * Argument     : void

301  *-----

302  * Return Value : void

303  *-----

304  * Note         : 全送信データ書き込み後、送信エンド (SCFSR.TEND) ビット

305  *                 : で FIFO 内の送信データがすべて送出されたことを確認することができます。

306  * "FUNC COMMENT END" ****

307 void io_interrupt_scif1_txi(void)

308 {

309     int i, fifo_cnt;

310     volatile unsigned short dummy;

311

312     /* ---- 送信 FIFO の書き込み可能サイズを算出 ---- */

313     fifo_cnt = 8;

314

315     /* ---- 送信 FIFO へのデータ書き込み ---- */

316     while(fifo_cnt-- != 0 ){

317

318         /* ---- 送信データの書き込み ---- */

319         SCIF1.SCFTDR.BYTE = SndData[SndCnt++];

320

321         /* ---- 全データ書き込み終了か? ---- */

322         if(SndCnt == DataNum){

323             /* ---- 送信割り込みを禁止 ---- */

324             SCIF1.SCSCR.BIT.TIE = 0;

325             break;

326         }

327     }

328     /* ---- 割り込み要因クリア、および送信開始 (TDFE, TEND ビットのクリア) ---- */

329     SCIF1.SCFSR.WORD &= ~0x0060u;

330     dummy = SCIF1.SCFSR.WORD;      /* 割り込み要因を確実にクリアするためのダミーリード */

331 }

332

333 /* End of File */

334

```

#### 4. 参考ドキュメント

- ソフトウェアマニュアル

SH-2A、SH2A-FPU ソフトウェアマニュアル Rev.3.00

(最新版をルネサステクノロジのホームページから入手してください。)

- ハードウェアマニュアル

SH7262 グループ、SH7264 グループ ハードウェアマニュアル Rev.2.00

(最新版をルネサステクノロジのホームページから入手してください。)

## ホームページとサポート窓口

ルネサス テクノロジホームページ

<http://japan.renesas.com/>

お問合せ先

<http://japan.renesas.com/inquiry>

[csc@renesas.com](mailto:csc@renesas.com)

## 改訂記録

| Rev. | 発行日        | 改訂内容 |      |

|------|------------|------|------|

|      |            | ページ  | ポイント |

| 1.00 | 2010.03.10 | —    | 初版発行 |

すべての商標および登録商標は、それぞれの所有者に帰属します。

本資料ご利用に際しての留意事項

1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負いません。

3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(<http://www.renesas.com>)などを通じて公開される情報に常にご注意ください。

5. 本資料に記載した情報は、正確を期すため慎重に制作したのですが、万一本資料の記述の誤りに起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に対する責任は負いません。

7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしかるべきは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません（弊社が自動車用と指定する製品を自動車に使用する場合を除きます）。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1) 生命維持装置。

- 2) 人体に埋め込み使用するもの。

- 3) 治療行為（患部切り出し、薬剤投与等）を行うもの。

- 4) その他、直接人命に影響を与えるもの。

9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

10. 弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤動作防止設計などの安全設計（含むハードウェアおよびソフトウェア）およびエーディング処理等、機器またはシステムとしての出荷保証をお願いいたします。特にマイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

11. 本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることができないよう、お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故につきましては、弊社はその責任を負いません。

12. 本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

13. 本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会ください。

D039444