# SH7262/SH7264 グループ

# NOR フラッシュメモリ接続例

RJJ06B1000-0200 Rev.2.00 2010.05.21

# 要旨

本アプリケーションノートは、SH7264のバスステートコントローラ (BSC) の通常空間インタフェース機能を紹介し、NOR型フラッシュメモリとの接続例について説明しています。

#### 動作確認デバイス

#### SH7262/SH7264

以下、総称して「SH7264」として説明します。

# 目次

| 1. | はじめに       | 2  |

|----|------------|----|

|    |            |    |

| 2. | 応用例の説明     | 3  |

|    |            |    |

| 3. | 参考プログラムリスト | 22 |

|    |            |    |

| 4  | 参老ドキュメント   | 26 |

# 1. はじめに

#### 1.1 仕様

- 4M バイト (2M ワード×16 ビット) の NOR 型フラッシュメモリを 1 個使用し、SH7264 と 16 ビットバス幅で接続します。

- SH7264 のバスステートコントローラ (BSC) を使用し、外部の NOR 型フラッシュメモリに対するリード / ライトを行います。リードにはランダムアクセスまたはページリードを使用します。

### 1.2 使用機能

• バスステートコントローラ (BSC)

### 1.3 適用条件

マイコン SH7262/SH7264

動作周波数 内部クロック:144 MHz

バスクロック:72 MHz 周辺クロック:36 MHz

統合開発環境 ルネサスエレクトロニクス製

High-performance Embedded Workshop Ver.4.07.00

Cコンパイラ ルネサスエレクトロニクス製SuperH RISC engineファミリ

C/C++コンパイラパッケージ Ver.9.03 Release00

コンパイルオプション High-performance Embedded Workshopでのデフォルト設定

(-cpu=sh2afpu -fpu=single -object="\$(CONFIGDIR)\pmu\\$(FILELEAF).obj" -debug -gbr=auto -chgincpath -errorpath -global\_volatile=0 -opt\_range=all

-infinite\_loop=0 -del\_vacant\_loop=0 -struct\_alloc=1 -nologo)

# 1.4 関連アプリケーションノート

本アプリケーションノートに関連するアプリケーションノートを以下に示します。合わせて参照してください。

• SH7262/SH7264 グループ 初期設定例

#### 1.5 "L"アクティブ端子(信号)の表記について

端子名(信号名)末尾の#は"L"アクティブ端子(信号)であることを示します。

# 2. 応用例の説明

SH7264 のバスステートコントローラ (BSC) を使用して、外部に接続された NOR 型フラッシュメモリを制御するための初期設定を行います。

# 2.1 使用機能の動作概要

SH7264のBSCは、外部アドレス空間に接続された各種メモリ、外部デバイスに対し制御信号を出力します。これにより、SRAM、SDRAMなどの各種メモリおよび外部デバイスを直接接続することができます。

表 1にBSCの特長を、表 2に通常空間インタフェースとバーストROMインタフェース (クロック非同期) の特長を示します。

# 表1 BSC の特長

| 項目     | 内容                                             |

|--------|------------------------------------------------|

| 制御対象空間 | CS0~CS6 の各空間をそれぞれ最大 64M バイトまでサポート              |

| メモリ種類  | 空間ごとに、以下から選択可能                                 |

|        | ● 通常空間インタフェース                                  |

|        | ● バイト選択付き SRAM インタフェース                         |

|        | ● バースト ROM(クロック同期または非同期)                       |

|        | MPX-I/O                                        |

|        | • SDRAM                                        |

|        | ● PCMCIA インタフェース                               |

| データバス幅 | CSO 空間のデータバス幅は 16 ビット、CS1~CS6 空間はそれぞれ 8 ビットまたは |

|        | 16 ビットから選択可能                                   |

| ウェイト制御 | 空間ごとに、ウェイトステートの挿入を制御可能                         |

| アイドル制御 | 連続するアクセスがリードーライト(同一空間または別空間)、リードーリード           |

|        | (同一空間または別空間)、および先頭サイクルがライトの場合の5種類独立にアイ         |

|        | ドルサイクルを設定可能                                    |

#### 表2 各インタフェースの特長

| 項目        | 仕様                           |

|-----------|------------------------------|

| 通常空間      | SRAM との直結が可能なインタフェースをサポート    |

| インタフェース   | SICAIMI との世紀が可能なインテンエースをサポート |

| バースト ROM  |                              |

| (クロック非同期) | ページモード機能を有する ROM を高速にアクセス可能  |

| インタフェース   |                              |

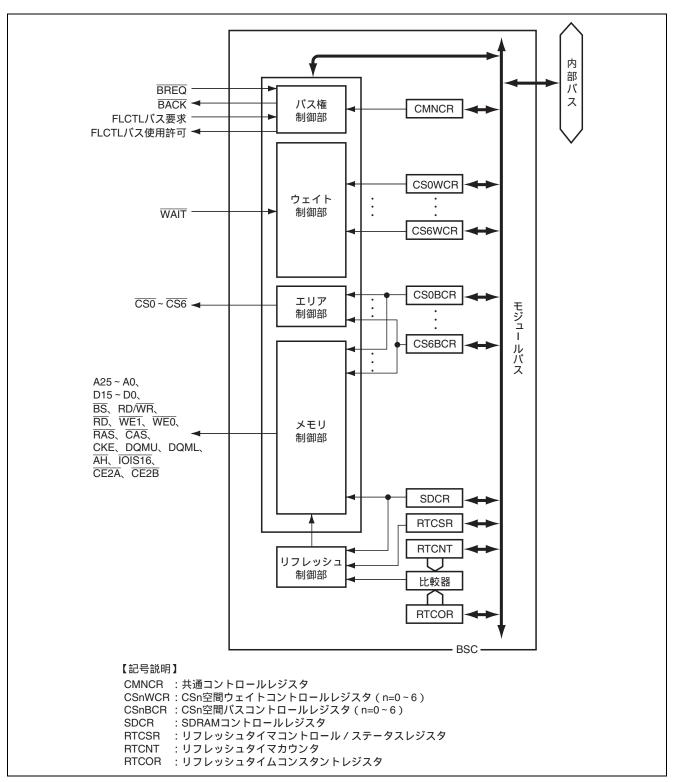

図1にBSCのブロック図を示します。

図1 BSC のブロック図

#### 2.2 接続例

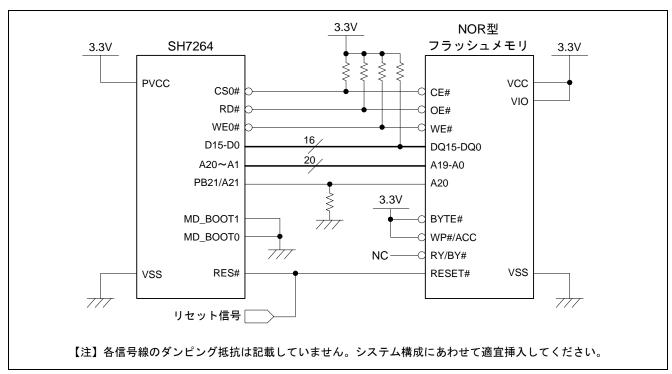

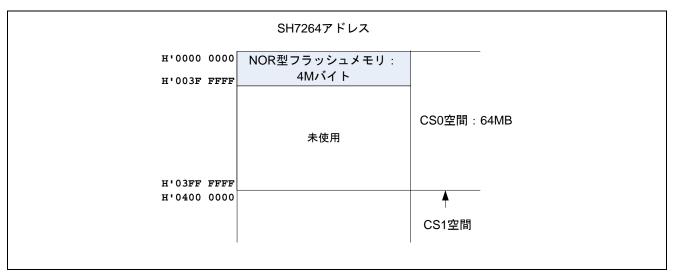

表 3に本応用例で使用するNOR型フラッシュメモリの仕様を示します。また図 2にNOR型フラッシュメモリ接続回路例を、図 3にNOR型フラッシュメモリ関連のメモリマップを示します。

| 項目      | 仕様                         |

|---------|----------------------------|

| 型名      | S29GL032N90                |

| 容量、構成   | 32M ビット(2M ワード×16 ビット×1 個) |

| データバス幅  | 16 ビット                     |

| アクセス時間  | ランダムアクセス時:90ns (最大)        |

|         | ページリード時: 25ns (最大)         |

| ブートブロック | トップブート、ボトムブートはモデル番号で識別     |

表3 本応用例で使用する NOR 型フラッシュメモリの仕様

図2 NOR 型フラッシュメモリ接続回路例

図3 NOR 型フラッシュメモリ関連メモリマップ

#### 【補足1】データバス幅とブートモードについて

SH7264 の CS0 空間(エリア 0)は 16 ビットバス幅固定です。そのため SH7264 の CS0 空間に接続する NOR 型フラッシュメモリは 16 ビットバス幅で接続します。NOR 型フラッシュメモリのデータバス幅を 16 ビット固定とするため NOR 型フラッシュメモリの BYTE #端子は"H"に固定します。また NOR 型フラッシュメモリでブートするためには SH7264 の MD\_BOOT0  $\angle$  MD\_BOOT1 端子は"L"に固定します(ブートモード 0)。 ブートモード 0 の場合、A20~A1 端子はアドレスバスに設定されます。ただし、A21~A25 端子は汎用入出力ポートに設定されますので注意してください。

#### 【補足 2】制御信号端子の外付け抵抗によるプルアップ/プルダウン処理について

A21~A25 端子、WE0#端子の各制御端子は初期状態が汎用入力ポートのため、端子の初期状態が決まらず不定となります。そこで不定状態の回避とメモリ動作を安定させるために、上記制御信号については外付け抵抗によるプルアップ/プルダウン処理を推奨します。

A21~A25 端子は、パワーオンリセット時に NOR 型フラッシュメモリの 0 番地にアクセスできるようにプルダウンします。なお、本応用例では A22~A25 端子は使用しません。

制御信号に対するプルアップ/プルダウン処理の選択については、一般的には動作をより安定させる状態を選択しますので、CSO#、RD#、WEO#端子については外付け抵抗でプルアップ処理を行い、"H"レベルにすることを推奨します。

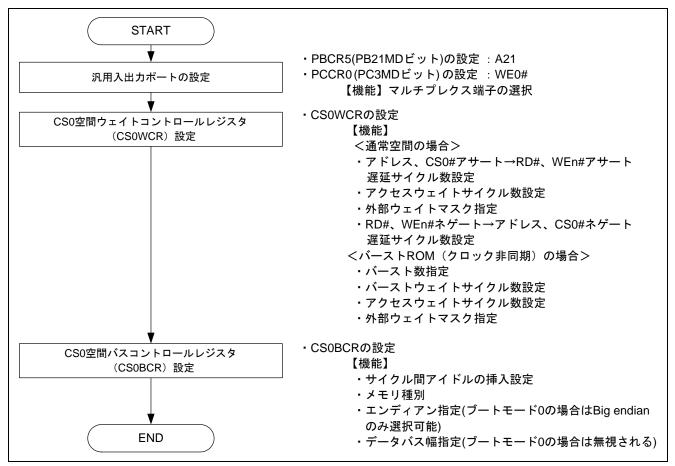

#### 2.3 使用機能の設定手順

図 4にCSO 空間使用時のBSCの設定手順例を示します。各レジスタの詳細についてはSH7262 グループ、SH7264 グループ ハードウェアマニュアル「第9章 バスステートコントローラ」を参照してください。

図4 BSC と汎用入出カポートの設定手順例(CS0 空間)

#### 2.3.1 ランダムアクセス使用時の設定例

ランダムアクセスは  $CS0\sim CS6$  の全ての空間で使用可能です。使用する空間の CSn 空間バスコントロールレジスタ (CSnBCR) ( $n=0\sim6$ ) の TYPE[2:0]ビットを「通常空間 (B'000) 」に設定します。

表 4と表 5にCSO 空間使用時のBSCの設定例を示します。各レジスタの詳細についてはSH7262 グループ、SH7264 グループ ハードウェアマニュアルの「第9章 バスステートコントローラ」または「第32章 汎用入出力ポート」を参照してください。

表4 汎用入出力ポートの設定例

| レジスタ名       | アドレス        | 設定値         | 機能                                      |

|-------------|-------------|-------------|-----------------------------------------|

| CS0 空間バスコン  | H'FFFC 0004 | H'1240 0400 | ● IWW[2:0]="B'001": ライト-リード/ライト-ライト間    |

| トロールレジスタ    |             |             | アイドル:1アイドルサイクル挿入                        |

| (CS0BCR)    |             |             | • IWRWD[2:0]、IWRWS[2:0]="B'001": リード-ライ |

|             |             |             | ト間アイドル:1アイドルサイクル挿入                      |

|             |             |             | • IWRRD[2:0]、IWRRS[2:0]、="B'000":       |

|             |             |             | リード-リード間アイドル:アイドルなし                     |

|             |             |             | ● TYPE[2:0]="B'000":通常空間                |

|             |             |             | ● ENDIAN="0":ビッグエンディアン <sup>※</sup>     |

|             |             |             | ● BSZ[1:0]="B'10": 16 ビット幅 <sup>※</sup> |

| CS0 空間ウェイト  | H'FFFC 0028 | H'0000 0B41 | • SW[1:0]="B'01": アドレス、CS0#アサート→RD#、    |

| コントロールレジ    |             |             | WE#アサート遅延サイクル数:1.5 サイクル                 |

| スタ (CS0WCR) |             |             | ● WR[3:0]="B'0110":アクセスウェイトサイクル数:       |

|             |             |             | 6 サイクル                                  |

|             |             |             | ● WM ="B'1":外部ウェイト入力無視                  |

|             |             |             | ● HW[1:0]="B'01": RD#、WE#ネゲート→アドレス、     |

|             |             |             | CS#ネゲート遅延サイクル:1.5 サイクル                  |

【注】※ ブートモード 0 の場合、データバスは 16 ビット幅固定となり、エリア 0 のリトルエンディアン設定はできません。

表5 汎用入出力ポートの設定例

| レジスタ名     | アドレス        | 設定値    | 機能                                       |

|-----------|-------------|--------|------------------------------------------|

| ポートBコントロー | H'FFFE 3824 | H'0011 | ● PB21MD[1:0]="B'01": PB21 端子を A21 機能に設定 |

| ルレジスタ 5   |             |        |                                          |

| (PBCR5)   |             |        |                                          |

| ポートCコント   | H'FFFE 384E | H'1011 | ● PC3MD[1:0]="B'01": PC3 端子を WE0#機能に設定   |

| ロールレジスタ 0 |             |        |                                          |

| (PCCR0)   |             |        |                                          |

#### 2.3.2 ページリード使用時の設定例

ページリードは CSO 空間および CS4 空間で使用可能です。使用する空間の CSn 空間バスコントロールレジスタ (CSnBCR) (n=0、4) の TYPE[2:0]ビットを「バースト ROM (クロック非同期) (B'001)」に設定します。

表 6と表 7にCSO 空間使用時のBSCの設定例を示します。各レジスタの詳細についてはSH7262 グループ、SH7264 グループ ハードウェアマニュアルの「第9章 バスステートコントローラ」または「第32章 汎用入出力ポート」を参照してください。

| レジスタ名      | アドレス        | 設定値         | 機能                                                 |

|------------|-------------|-------------|----------------------------------------------------|

| CS0 空間バスコン | H'FFFC 0004 | H'2480 1400 | ● IWW[2:0]="B'010": ライト-リード/ライト-ライト間               |

| トロールレジスタ   |             |             | アイドル:2アイドルサイクル挿入                                   |

| (CS0BCR)   |             |             | • IWRWD[2:0]、IWRWS[2:0]="B'010": リード-ライ            |

|            |             |             | ト間アイドル:2 アイドルサイクル挿入                                |

|            |             |             | • IWRRD[2:0]、IWRRS[2:0]、="B'000": リード-リー           |

|            |             |             | ド間アイドル:アイドルなし                                      |

|            |             |             | ● TYPE[2:0]="B'001":バーストROM(クロック非同期) <sup>※1</sup> |

|            |             |             | • ENDIAN="0": ビッグエンディアン <sup>※2</sup>              |

|            |             |             | • BSZ[1:0]="B'10":16 ビット幅 <sup>※2</sup>            |

| CS0 空間ウェイト | H'FFFC 0028 | H'0022 03C0 | • BST[1:0]="B'10": 4-4 または 2-4-2 バースト              |

| コントロールレジ   |             |             | ● BW[1:0]="B'10":バーストウェイトサイクル数:2                   |

| スタ(CS0WCR) |             |             | サイクル                                               |

|            |             |             | ● W[3:0]="B'0111": アクセスウェイトサイクル数:8<br>サイクル         |

|            |             |             | ● WM ="B'1":外部ウェイト入力無視                             |

表6 BSC の設定例

【注】 ※1 CSOWCR レジスタの設定を行った後で TYPE[2:0]をバースト ROM の設定にしてください。

※2 ブートモード 0 の場合、データバスは 16 ビット幅固定となり、エリア 0 のリトルエンディアン設定はできません。

| レジスタ名      | アドレス        | 設定値    | 機能                                       |

|------------|-------------|--------|------------------------------------------|

| ポートBコントロール | H'FFFE 3824 | H'0011 | ● PB21MD[1:0]="B'01": PB21 端子を A21 機能に設定 |

| レジスタ 5     |             |        |                                          |

| (PBCR5)    |             |        |                                          |

| ポートCコントロール | H'FFFE 384E | H'1011 | ● PC3MD[1:0]="B'01": PC3 端子を WE0#機能に設定   |

| レジスタ 0     |             |        |                                          |

| (PCCR0)    |             |        |                                          |

表7 汎用入出力ポートの設定例

#### 2.4 NOR 型フラッシュメモリのタイミング設定参考例

NOR型フラッシュメモリを接続する場合には、使用するフラッシュメモリのアクセススピードやその他AC特性に応じたウェイトサイクルを設定する必要があります。ここではランダムアクセス使用時とページリード使用時の参考例を示します。

SH7264 および NOR 型フラッシュメモリの AC 特性に関しては、各デバイスのデータシートを参照してください。なお、参考例の SH7264 の動作条件は、バスクロック 72MHz(teyc = 13.9ns)です。

以下の計算式における Th と Tf の値には、CSO 空間ウェイトコントロールレジスタ(CSOWCR)の SW[1:0] ビットまたは HW[1:0]ビットで設定した遅延サイクルから 0.5 サイクルを引いたサイクル数を使用します。また、T1、T2 は T1 = T2 = teye とします。

#### 2.4.1 ランダムアクセス使用時のタイミング例

ランダムアクセス使用時のタイミング設定参考例を示します。

以下のタイミングを満足するようにレジスタを設定してください。表 8に参考例の設定内容を示します。

| 項目                 | 略称     | サイクル数 | 関連レジスタ                     |

|--------------------|--------|-------|----------------------------|

| アドレス、CS0#アサート→RD#、 | Th     | 1     | CS0WCR レジスタの SW[1:0]ビット    |

| WEn#アサート遅延サイクル数    |        |       |                            |

| アクセスウェイトサイクル数      | Tw     | 6     | CS0WCR レジスタの WR[3:0]ビット    |

|                    |        |       |                            |

| RD#、WEn#ネゲート→アドレス、 | Tf     | 1     | CS0WCR レジスタの HW[1:0]ビット    |

| CS0#ネゲート遅延サイクル数    |        |       |                            |

| ライト―リード/ライト―ライト    | Taw(w) | 1     | CS0BCR レジスタの IWW[2:0]ビット   |

| サイクル間アイドル          |        |       |                            |

| 同一空間リード―ライト        | Taw(r) | 1     | CS0BCR レジスタの IWRWS[2:0]ビット |

| サイクル間アイドル          |        |       |                            |

表8 参考例のウェイト設定

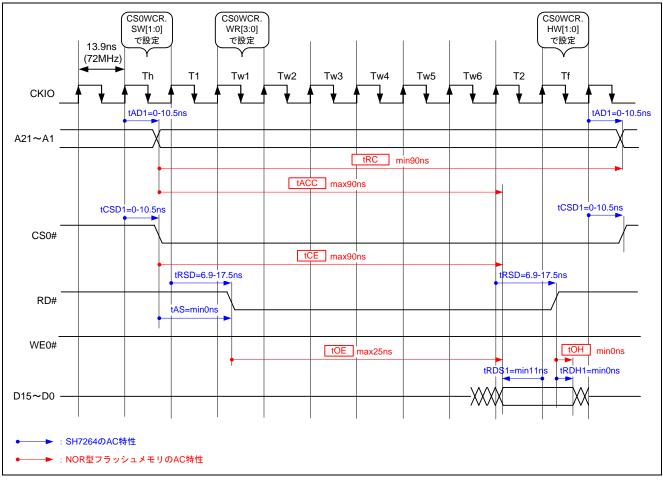

#### <リードタイミング>

- NOR 型フラッシュメモリの tRC (リードサイクル時間) tRC(min) ≦ (tcyc×Th-tAD1\_max)+(T1)+(tcyc×Tw)+(T2)+(tcyc×Tf)+(tAD1\_min) ...... (図 5)

- NOR 型フラッシュメモリの tACC (アドレスアクセス時間) tACC(max) ≦ (tcyc×Th-tAD1\_max)+(T1)+(tcyc×Tw)+(T2-tRDS1\_min) ......(図 5)

- NOR 型フラッシュメモリの tCE (CE#アクセス時間) tCE(max) ≦ (tcyc×Th-tCSD1 max)+(T1)+(tcyc×Tw)+(T2-tRDS1 min).....(図 5)

- NOR 型フラッシュメモリの tOE (OE#アクセス時間) tOE(max) ≦ (T1-tRSD\_max)+(tcyc×Tw)+(T2-tRDS1\_min) ......(図 5)

- NOR 型フラッシュメモリの tOH (前サイクルデータ出力保持時間)

tOH(min) ≦ tRDH1(min) .....(図 5)

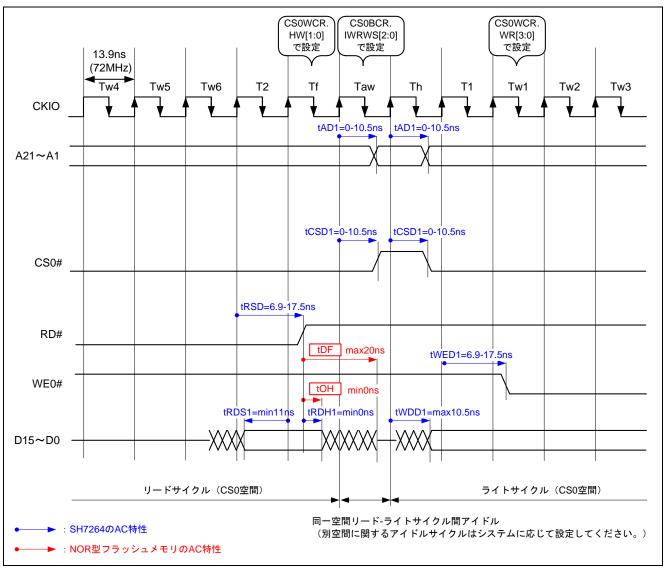

- NOR 型フラッシュメモリの tDF (データフローティング時間) tDF(max) ≦ T2+(tcyc×Tf)+(tcyc×Taw(r))-tRSD\_max....(図 6)

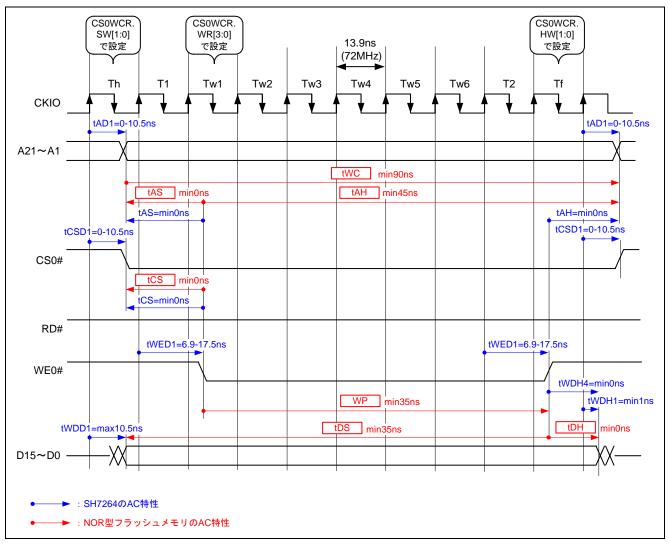

#### <ライトタイミング>

- NOR型フラッシュメモリの tCS (チップイネーブルセットアップ時間)

tCS(min) ≦ tCS\_min....(図7)

- NOR 型フラッシュメモリの tAH(アドレスホールド時間) tAH(min) ≦ (T1-tWED1\_max)+(tcyc×Tw)+(T2)+(tcyc×Tf)+(tAD1\_min) ......(図 7)

- NOR 型フラッシュメモリの tWC (ライトサイクル時間) ) tWC(min) ≦ (tcyc×Th−tAD1\_max)+(T1)+(tcyc×Tw)+(T2)+(tcyc×Tf)+(tAD1\_min) .... (図 7)

- NOR 型フラッシュメモリの tAS (アドレスセットアップ時間)

tAS(min) ≦ tAS\_min....(図 7)

- NOR 型フラッシュメモリの tWP (ライトパルス幅)

tWP(min) ≦ (T1-tWED1\_max)+(tcyc×Tw)+(tWED1\_min) .....(図7)

- NOR 型フラッシュメモリの tDS (データセットアップ時間) tDS(min) ≦ (tcyc×Th-tWDD1\_max)+(T1)+(tcyc×Tw)+(tWED1\_min) ......(図 7)

- NOR 型フラッシュメモリの tDH (データホールド時間)

tDH(min) ≦ tWDH4 min......(図 7)

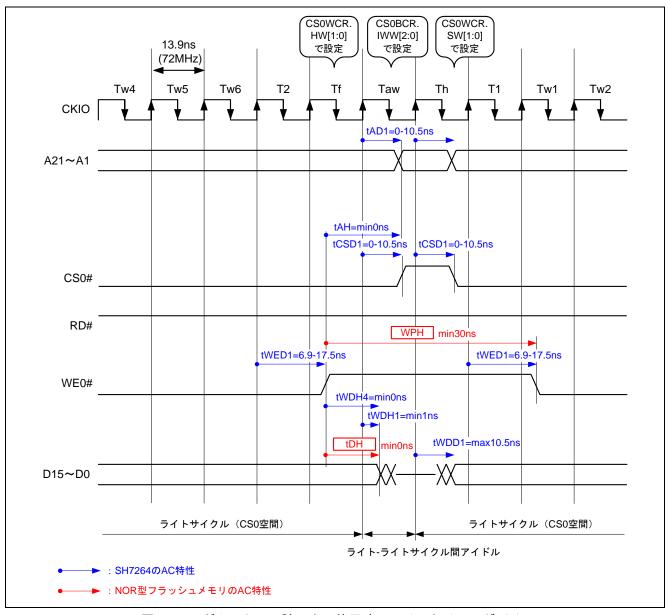

- NOR 型フラッシュメモリの tWPH("H"ライトパルス幅) tWPH(min) ≦ (T2-tWED1\_max)+(tcyc×Tf)+(tcyc×Taw(w))+(tcyc×Th)+(tWED1\_min). (図 8)

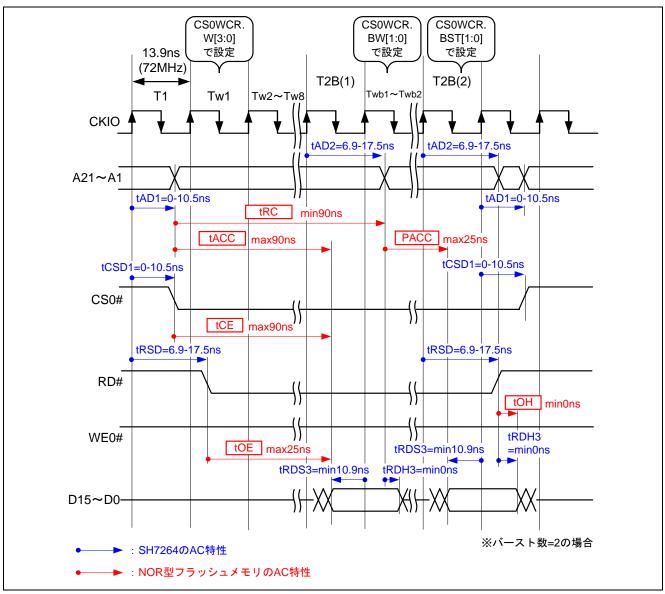

図5 ランダムアクセス読み出し使用時のリードタイミング(1)

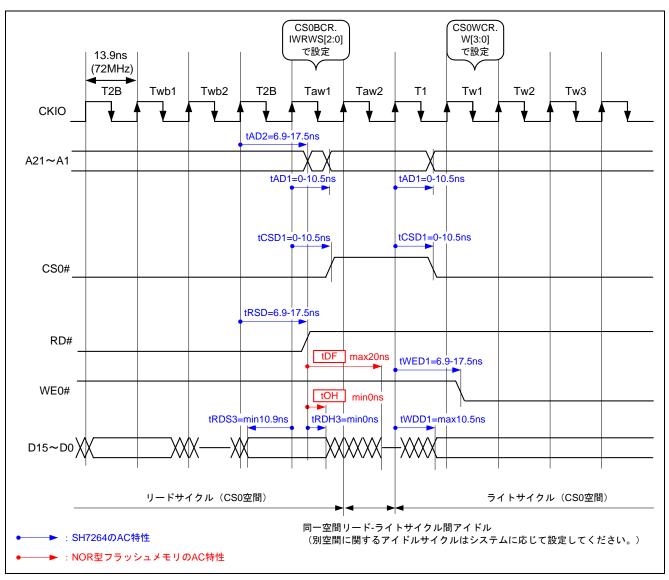

図6 ランダムアクセス読み出し使用時のリードタイミング(2)

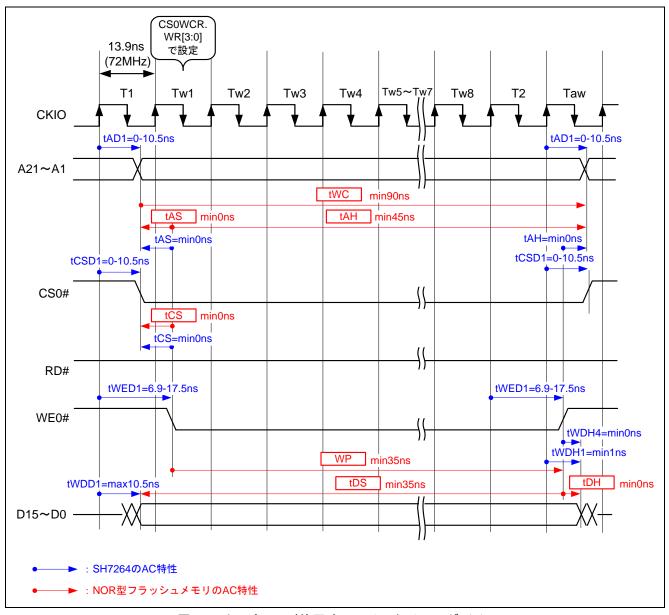

図7 ランダムアクセス読み出し使用時のライトタイミング(1)

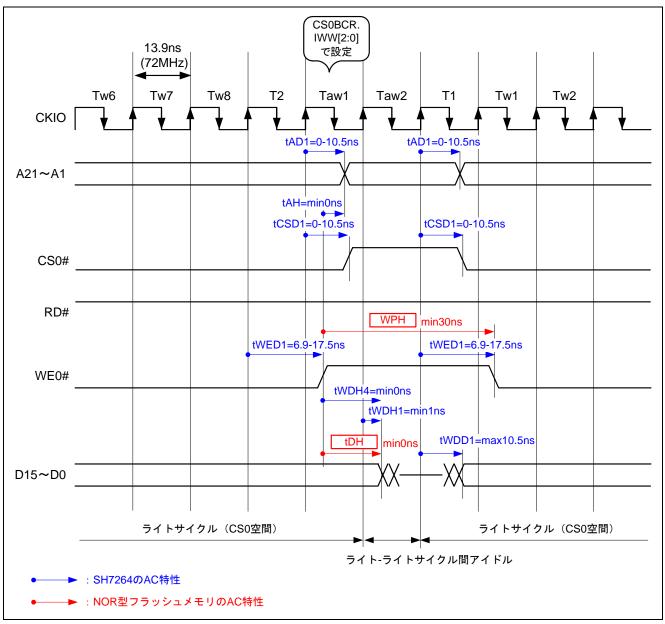

図8 ランダムアクセス読み出し使用時のライトタイミング(2)

#### 2.4.2 ページリード使用時のタイミング例

ページリード使用時のタイミング設定参考例を示します。

以下のタイミングを満足するようにレジスタを設定してください。表 9に参考例の設定内容を示します。

表9 参考例のウェイト設定

略称 サイクル数 関連レジスタ Twb 2

項目 バーストウェイトサイクル数 CS0WCR レジスタの BW[1:0]ビット アクセスウェイトサイクル数 Tw 8 CS0WCR レジスタの W[3:0]ビット CS0BCR レジスタの IWW[2:0]ビット ライト―リード/ライト―ライト Taw(w) 2 サイクル間アイドル CS0BCR レジスタの IWRWS[2:0]ビット 同一空間リード―ライト Taw(r) 2

【注】 CS0 空間でページリード使用時には CS アサート期間拡張は設定できません。そのため、Th と Tf は 0 サイクルになります。

#### <リードタイミング>

サイクル間アイドル

- NOR 型フラッシュメモリの tRC (リードサイクル時間)  $tRC(min) \le (T1-tAD1_max)+(tcyc \times Tw)+(tAD2_min)$  (29)

- NOR 型フラッシュメモリの tACC (アクセスアクセス時間) tACC(max) ≤  $(T1-tAD1_max)+(tcyc \times Tw)+(T2B-tRDS3_min)$ .....(図 9)

- NOR 型フラッシュメモリの tCE (CE#アクセス時間)  $tCE(max) \le (T1-tCSD1_max)+(tcyc \times Tw)+(T2B-tRDS3_min)$  (29)

- NOR 型フラッシュメモリの tOE (OE#アクセス時間) tOE(max) ≤  $(T1-tRSD_max)+(tcyc \times Tw)+(T2B-tRDS3_min)$  .....(図 9)

- NOR 型フラッシュメモリの tPACC (ページアクセス時間/第2アクセスサイクル以降) tPACC(max) ≤  $(T2B-tAD2_max)+(tcyc \times Twb)+(T2B-tRDS3_min)$  ......(図 9)

- NOR 型フラッシュメモリの tOH (前サイクルデータ出力保持時間) tOH(min) ≤ tRDH3(min) ......(図 9)

- NOR 型フラッシュメモリの tDF (データフローティング時間) tDF(max) ≤  $T2+(tcyc \times Taw(r))-tRSD$  max.....(図 10)

# <ライトタイミング>

| • | NOR 型フラッシュメモリの tCS(チップイネーブルセットアップ時間) tCS(min) $\leq$ tCS_min(図 1                                          | 11) |

|---|-----------------------------------------------------------------------------------------------------------|-----|

| • | NOR 型フラッシュメモリの tAH(アドレスホールド時間)を満足していることを確認します。<br>tAH(min) ≦ (T1−tWED1_max)+(tcyc×Tw)+(T2)+(tAD1_min)(図 1 | 11) |

| • | NOR 型フラッシュメモリの tWC(ライトサイクル時間)<br>tWC(min) ≦ (T1−tAD1_max)+(tcyc×Tw)+(T2)+(tAD1_min)(図 1                   | 11) |

| • | NOR 型フラッシュメモリの tAS(アドレスセットアップ時間)<br>tAS(min) ≦ tAS_min(図 1                                                | 11) |

| • | NOR 型フラッシュメモリの tWP(ライトパルス幅)<br>tWP(min) ≦ (T1−tWED1_max)+(tcyc×Tw)+(tWED1_min)(図 1                        | 11) |

| • | NOR 型フラッシュメモリの tDS(データセットアップ時間))<br>tDS(min) ≦ (T1−tWDD1_max)+(tcyc×Tw)+(tWED1_min)(図 1                   | 11) |

| • | NOR 型フラッシュメモリの tDH(データホールド時間))<br>tDH(min) ≦ tWDH4_min(図 1                                                | 11) |

| • | NOR 型フラッシュメモリの tWPH("H"ライトパルス幅)<br>tWPH(min) ≦ (T2−tWED1_max)+(tcyc×Taw(w))+(tWED1_min)(図 1               | 12) |

図9 ページリード使用時のリードタイミング(1)

図10 ページリード使用時のリードタイミング(2)

図11 ページリード使用時のライトタイミング(1)

図12 ページリード使用時のライトタイミング(2)

# 3. 参考プログラムリスト

# 3.1 参考プログラムについての補足

SH7264 は、製品によって大容量内蔵 RAM の容量が 1MB または 640KB と異なるため、参考プログラムのセクション配置やレジスタの設定を一部変更する必要があります。そのため本アプリケーションノートでは 1MB 用と 640KB 用の 2 つのワークスペースを用意しています。

640KB 版はライトプロテクトを解除しなければ保持用内蔵 RAM へ書き込むことができないため、640KB 版のワークスペースは、システムコントロールレジスタ 5 (SYSCR5) にライトプロテクトの解除を設定しています。

使用する製品を確認した上で、対応するワークスペースを使用してください。

# 3.2 サンプルプログラムリスト "bsc\_cs0.c"(1)

```

1

* DISCLAIMER

3

^{\star} \, This software is supplied by Renesas Electronics Corp. and is only

intended for use with Renesas products. No other uses are authorized.

6

7

This software is owned by Renesas Electronics Corp. and is protected under

* all applicable laws, including copyright laws.

8

9

10

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

12

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* ELECTRONICS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

19

20

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

* software and to discontinue the availability of this software.

* By using this software, you agree to the additional terms and

24

25

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

*******************

28

* (C) 2008(2010) Renesas Electronics Corporation. All rights reserved.

*""FILE COMMENT""******* Technical reference data *******************************

29

* System Name : SH7264 Sample Program

* File Name : bsc_cs0.c

31

* Abstract : SH7264 Initial Settings

32

33

Version

: 1.03.00

: SH7262/SH7264

Device

35

Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36

: C/C++ compiler package for the SuperH RISC engine family

37

(Ver.9.03 Release00).

38

* OS

: None

* H/W Platform: M3A-HS64G50(CPU board)

39

40

Description :

************************

41

42

History

: Dec.11,2008 Ver.1.00.00

43

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

: Mar.30,2010 Ver.1.02.00 Changed PAGEMODE setting

45

: Apr.15,2010 Ver.1.03.00 Changed the company name

*""FILE COMMENT END""********************

46

47

#include "iodefine.h"

48

49

```

# 3.3 サンプルプログラムリスト "bsc\_cs0.c"(2)

```

50

/* CS0 PAGEMODE setting */

51

//#define PAGEMODE

52

/* ==== Prototype Declaration ==== */

53

void io_init_bsc_cs0(void);

55

56

#pragma section ResetPRG

57

* ID

59

* Outline

: CSO setting

*-----

60

61

* Include

: iodefine.h

63

* Declaration : void io_init_bsc_cs0(void);

64

*-----

* Description : Pin function controller (PFC) and bus state controller (BSC)

: are set, and the access timing to the Flash Memory of CSO space

66

67

: The PFC setting is set by bit manipulation not to change the PFC

: set value which is set by other process.

69

70

71

: void

*-----

72

73

* Return Value : void

74

*_____

75

76

77

void io_init_bsc_cs0(void)

78

79

/* ==== PFC settings ==== */

PORT.PBCR5.BIT.PB21MD = 1u; /* Set A21 */

80

PORT.PCCR0.BIT.PC3MD = 1u; /* Set WE0# */

81

82

83

#ifdef PAGEMODE

84

85

/* ==== CS0WCR settings ==== */

86

87

BSC.CSOWCR.BROM_ASY.LONG = 0x002203C0ul;

/* Number of Burst: 4-4 or 2-4-2

88

89

/* Number of Burst Wait Cycles: 2 cycles */

/* Number of Access Wait Cycles: 8 cycles

90

91

92

93

/* ==== CS0BCR settings ==== */

BSC.CS0BCR.LONG = 0x24801400ul;

95

96

/* Idle Cycles between Write-read Cycles */

97

/* and Write-write Cycles: 2 idle cycles */

98

/* Idle Cycles between Read-write Cycls

99

/*

: 2 idle cycles */

100

/* Type:Burst ROM (ASY)

*/

/* Data Bus Size: 16-bit

```

# 3.4 サンプルプログラムリスト "bsc\_cs0.c" (3)

```

102

103

#else /* PAGEMODE */

104

105

106

/* ==== CS0WCR settings ==== */

107

BSC.CSOWCR.NORMAL.LONG = 0x00000b41ul;

108

109

/* Number of Delay Cycles from Address, */

110

/* CSO# Assertion to RD#, WEn Assertion */

/* : 1.5 cycles

111

/* Number of Access Wait Cycles: 6 cycles

112

/* Delay Cycles from RD, WEn# negation to */

113

114

/* Address, CSn# negation: 1.5 cycles

115

116

117

/* ==== CS0BCR settings ==== */

118

BSC.CS0BCR.LONG = 0x12400400ul;

/* Idle Cycles between Write-read Cycles */

119

120

/* and Write-write Cycles : 1 idle cycle */

121

/\,^\star and read-write Cycles : 1 idle cycle \,^\star/\,

122

/* Type: Normal space

123

/* Data Bus Size: 16-bit

* /

124

#endif /* PAGEMODE */

125

126

127

/* End of File */

128

129

```

# 4. 参考ドキュメント

- ソフトウェアマニュアル

SH-2A、SH2A-FPU ソフトウェアマニュアル Rev.3.00

(最新版をルネサスエレクトロニクスのホームページから入手してください。)

- ハードウェアマニュアル SH7262 グループ、SH7264 グループ ハードウェアマニュアル Rev.2.00 (最新版をルネサスエレクトロニクスのホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |                       |  |

|------|------------|------|-----------------------|--|

| Rev. | 発行日        | ページ  | ポイント                  |  |

| 1.00 | 2009.01.22 | _    | 初版発行                  |  |

| 2.00 | 2010.05.21 | 全頁   | ページリード設定を追加し、全体の構成を変更 |  |

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営 業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、 ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害 に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されて いる当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の 法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器

(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療

行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム等

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を 直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2(日本ビル)

(03)5201-5307

| ■技 | <b>技術的なお問合せ</b> お | よび資料       | のご請求は      | 下記へど      | うぞ。  |

|----|-------------------|------------|------------|-----------|------|

| 糸  | 総合お問合せ窓口:         | http://jap | an.renesas | .com/inqu | uiry |