## APPLICATION NOTE

## Introduction

This application note presents the method of achieving a defined phase relationship between the input reference clock and output clock for IDT UFT3G Zero-Delay Buffers. Outputs can be selectively divided, multiplied or inverted while still maintaining very low input to output skew.

The UFT3G family consists of the six devices with the properties pertinent to zero delay buffers, as summarized in Table 1 below.

Table 1: Summary of UFT 3G Family

| Part Number | Number of<br>Inputs | Number of<br>Outputs | Number of APLLs | Max Number of ZDB | Jitter<br>Performance |

|-------------|---------------------|----------------------|-----------------|-------------------|-----------------------|

| 8T49N281    | 2                   | 8                    | 1               | 1                 | Standard UFT3G        |

| 8T49N282    | 4                   | 8                    | 2               | 2                 | Standard UFT3G        |

| 8T49N283    | 2                   | 8                    | 2               | 1                 | Standard UFT3G        |

| 8T49N285    | 2                   | 8                    | 1               | 1                 | Improved UFT3G        |

| 8T49N286    | 4                   | 8                    | 2               | 2                 | Improved UFT3G        |

| 8T49N287    | 2                   | 8                    | 2               | 1                 | Improved UFT3G        |

Note: Fully hitless switching is not supported when external loopback is being used, so only the phase-slope limiting is selected for the switches between input references or enters/leaves the holdover state in this ZDB application.

# **Zero Delay Buffer Architecture**

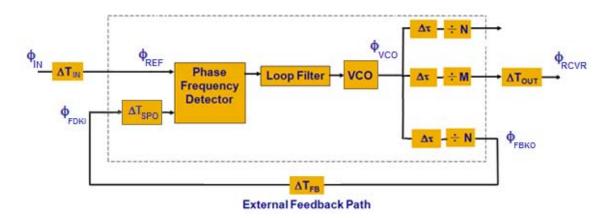

A zero-delay buffer is a device that can fan out one clock signal into multiple clock signals with zero delay between the input reference to the buffer and the inputs of the downstream clock receivers driven by the zero delay buffer. The device is well suited for a variety of clock distribution application requiring tight input-output and output-output skew relationship. A simplified block diagram of a ZDB is shown in Figure 1 below where  $\Delta$ TSPO is called the Static Phase Offset and is due to internal input and feedback clock Pre-divider and Phase/Frequency Detector delays. Since this is usually frequency independent, it is has units of time delay and is shown as such in the block diagram.

A feature of the UFT3G PLLs is that a clock input can be specified as the feedback input to the PLL phase detector rather than an internal connection. Board-level trace-length mismatches can be compensated for in order to achieve a defined skew relationship between the input and output clock as shown in Figure 1 below. "Δτ" in the part can fine tune delay line to manage the clock skew and the delay variations in the other six output clocks.

Figure 1. UFT3G Architecture Applied to a Single Zero-Delay Buffer

The relationship between the reference phase φιν and the phase at the inputs to the downstream clock receivers, φRCVR is developed below. In principle, the delay of the feedback path is shown to allow any skew between φιν and φRCVR.

Working back from the phase detector inputs, the input phase can be related to the output phase of the feedback path as below where f is the frequency of the input phase reference.

$$\begin{split} \phi_{REF} &= \phi_{FBKI} + 2\pi \, f \, \Delta T_{SPO} \\ \phi_{IN} &+ 2\pi \, f \, \Delta T_{REF} = \phi_{FBKI} + 2\pi \, f \, \Delta T_{SPO} \end{split}$$

From the external feedback path;

$$\phi_{FBKI} = \phi_{FBKO} + 2\pi f \Delta T_{FB}$$

The input phase can be related to the feedback output phase as follows:

$$\phi_{IN} + 2\pi f \Delta T_{REF} = \phi_{FBKO} + 2\pi f (\Delta T_{FB} + \Delta T_{SPO})$$

At the clock receiver, the phase at the receiver can be related back to the phase of the VCO:

$$\begin{split} \frac{\phi_{VCO}}{M} + 2\pi f \; \Delta T_{OUT} \; &= \phi_{RCVR} \\ \phi_{VCO} \; &= M \left( \phi_{RCVR} - 2\pi f \; \Delta T_{OUT} \right) \end{split}$$

These relationships are put together for the dependence of the clock receiver input phase to the UFT3G input phase.

$$\begin{split} \phi_{\mathit{IN}} + 2\pi \, f \, \Delta T_{\mathit{REF}} &= \phi_{\mathit{FBKO}} + 2\pi \, f \left( \Delta T_{\mathit{FB}} + \Delta T_{\mathit{SPO}} \right) \\ \phi_{\mathit{IN}} &= \frac{\phi_{\mathit{VCO}}}{N} + 2\pi \, f \left[ \Delta T_{\mathit{FB}} + \Delta T_{\mathit{SPO}} - \Delta T_{\mathit{REF}} \right] \\ &= \frac{M}{N} \left( \phi_{\mathit{RCVR}} - 2\pi \, f \, \Delta T_{\mathit{OUT}} \right) + 2\pi \, f \left[ \Delta T_{\mathit{FB}} + \Delta T_{\mathit{SPO}} - \Delta T_{\mathit{REF}} \right] \\ &= \frac{M}{N} \phi_{\mathit{RCVR}} - 2\pi \, f \left[ \Delta T_{\mathit{REF}} - \Delta T_{\mathit{SPO}} + \frac{M}{N} \, \Delta T_{\mathit{OUT}} - \Delta T_{\mathit{FB}} \right] \\ \phi_{\mathit{RCVR}} &= \frac{N}{M} \phi_{\mathit{IN}} + 2\pi \, f \left[ \left( \Delta T_{\mathit{REF}} - \Delta T_{\mathit{SPO}} + \frac{M}{N} \, \Delta T_{\mathit{OUT}} \right) - \Delta T_{\mathit{FB}} \right] \end{split}$$

By adjusting the external path length,  $\Delta$ TFB, on the printed wiring board to cancel the cumulative effect of  $\Delta$ TOUT,  $\Delta$ TREF and  $\Delta$ TSPO, the output clock can be timed to arrive at the receiver phase-aligned with the input clock. That is when  $\phi$ IN equals zero,  $\phi$ RCVR equals zero. In general,  $\Delta$ TSPO depends on the particular settings of the internal dividers and the phase/frequency detector comparison frequency.

In general, phase advance or a smaller phase delay is also possible, but there is a practical limit to the maximum delay achievable with a length of a circuit board trace due to the propagation velocity of the feedback transmission line (165ps/in typically). The effective  $\Delta$ TFB can also be increased by inverting the feedback output. In cases where inversion of the feedback clock does not generate enough additional delay, an RC network can be used to increase the effective  $\Delta$ TFB.

## **Procedure**

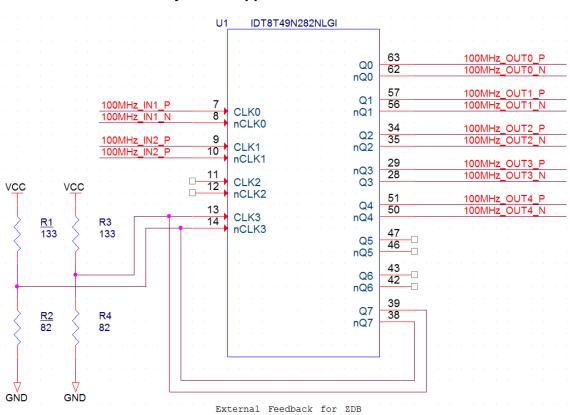

The user must first connect the 8T49N282 as a Zero Delay Buffer as shown schematically in Figure 2.

Figure 2. Schematic for Zero Delay Buffer Application

After the 8T49N282 is connected as a ZDB, the device must be configured as a ZBD in Timing Commander as shown in the following steps.

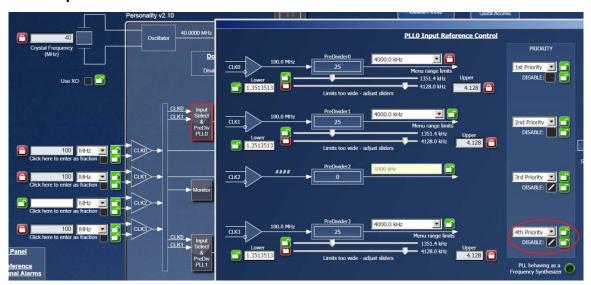

1. Click "Input Select & PreDiv PLL0", select the PFD frequency and disable the selection for the feedback input as shown in Figure 3.

Figure 3. PLL0 Input Reference Control

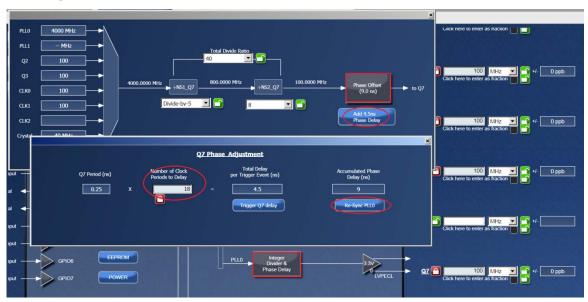

2. Click on "Integer Divider & Phase Delay", then select "Phase Offset" box and click "Re-Sync PLL0" to trigger all outputs synchronization from PLL0, and entering desired phase offset in the feedback path for the external trace compensated as in Figure 4. Generally the trace lengths for all outputs to their respective clock receivers should be the same length as the external feedback path, otherwise, the phase offset of each output need to be individually adjusted for the different trace length to the corresponding clock receiver.

Figure 4. Setting the Phase Offset

The description in the datasheet, shown in Table 1, lists the steps in detail.

Table 2: Output Clock Control Register

| Output Clock Source Control Register Block Field Locations |      |               |    |          |               |               |          |          |  |

|------------------------------------------------------------|------|---------------|----|----------|---------------|---------------|----------|----------|--|

| Address (Hex)                                              | D7   | D6            | D5 | D4       | D3            | D2            | D1       | D0       |  |

| 00A8                                                       | Rs   | Rsvd          |    | PLL0_SYN | CLK_SEL3      | CLK_SEL2      | CLK_SEL1 | CLK_SEL0 |  |

| 00A9                                                       | Rsvd | CLK_SEL5[2:0] |    |          | Rsvd          | CLK_SEL4[2:0] |          |          |  |

| 00AA                                                       | Rsvd | CLK_SEL7[2:0] |    | Rsvd     | CLK_SEL6[2:0] |               |          |          |  |

| 00AB                                                       | 1    | 11            |    | 11       |               | Rsvd          |          | Rsvd     |  |

| Output Clock Source Control Register Block Field Descriptions |            |               |                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------------------------------------------------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit Field Name                                                | Field Type | Default Value | Description                                                                                                                                                                                                                                                                                                                                               |  |  |

| PLL1_SYN                                                      | R/W        | Ob            | Output Synchronization Control for Outputs Derived from PLL1.  Setting this bit from 0→1 will cause the output divider(s) for the affected outputs to be held in reset.  Setting this bit from 1→0 will release all the output divider(s) for the affected outputs to run from the same point in time with the coarse output phase adjustment reset to 0. |  |  |

| PLL0_SYN                                                      | R/W        | Ob            | Output Synchronization Control for Outputs Derived from PLL0.  Setting this bit from 0→1 will cause the output divider(s) for the affected outputs to be held in reset.  Setting this bit from 1→0 will release all the output divider(s) for the affected outputs to run from the same point in time with the coarse output phase adjustment reset to 0. |  |  |

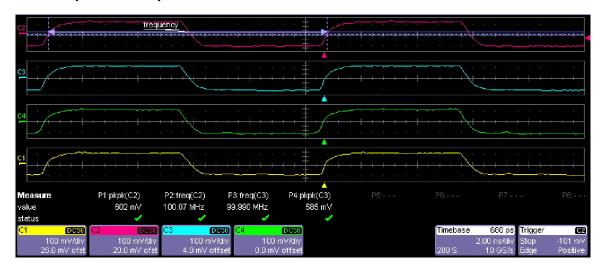

3. If the external feedback path can't fully compensate the delay of the clock between the reference and the Buffer output, the user can adjust the Number of Clock Period Delay through COARSE7[4:0] of register 0xA5, then set CRSE\_TRG7 of register 0x9D to trigger Coarse phase adjustment for OUT7, a 4GHz VCO gives a step size of 250ps (For Q2/Q3, the step size is 16ps). By the method adjusting, the user can observe the waveform by the scope as shown in Figure 5.

Figure 5. UFT3GT Input and Output Waveform Plots

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.