# RENESAS Application Considerations Using 82V2048 to Replace LXT384

# Introduction

Both IDT's 82V2048 and Cortina's LXT384 are 8-channel short haul LIUs. According to the Cortina website, LXT384BE (160-pin BGA) is noted as End of Life (EOL) and LXT384LE (144-pin TQPF) is "Not Recommended for New Designs". As a result, many existing applications may use 82V2048 to replace LXT384 in both new and existing customer designs. This application note first compares the two devices and then reveals some differences in applications. Overall, 82V2048 is a superset of LXT384 in features, register map and application flexibility. The IDT part is available in production in both BGA and TQFP packages.

# Comparisons Between IDT82V2048 and LXT384

## **Overall Comparison**

Table 1 provides an overall comparison between 82V2048 and LXT384 package, pin definitions, register map and some other features.

| Items                                          | IDT82V2048                                                                                                | LXT384                                                                                        |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| General functions                              | 8-channel short-haul T1/E1 LIU                                                                            | 8-channel short-haul T1/E1 LIU                                                                |

| Pin/Package                                    | TQFP-144 and PBGA-160<br>Pin-to-pin compatible with LXT384                                                | TQFP-144 and PBGA-160                                                                         |

| Voltage Supply                                 | 3.3V, line driver can be 3.3V or 5.0V                                                                     | 3.3V, line driver can be 3.3V or 5.0V                                                         |

| Register Map                                   | Primary Registers: 22 (00h~15h)<br>Expanded registers: 16 (00h~0Fh)                                       | 22 (00h~15h)<br>None                                                                          |

| Transmit Resistors                             | $9.5\Omega \pm 1\%$ in E1 applications                                                                    | 11 $\Omega$ ±1% in E1 applications                                                            |

| JA Corner Frequencies                          | Hardware mode (T1/E1): 1.7Hz/2.5Hz<br>Host mode T1: 2.5Hz/5.0Hz,<br>Host mode E1: 1.7Hz/6.5Hz             | Hardware mode (T1/E1): 3.5Hz/6.0Hz<br>Host mode T1: 3.0Hz/6.0Hz,<br>Host mode E1: 2.5Hz/3.5Hz |

| Transmit All Ones when<br>TCLK is logic "high" | MCLK is clocked and TCLK is logic<br>"high". TCLK1 is internally used as MCLK<br>when MCLK is not clocked | MCLK is clocked and TCLK is logic "high"                                                      |

## Table 1: Overall Comparison Between IDT82V2048 and LXT384

#### Hardware Interface Comparison

Both 82V2048 and LXT384 support hardware mode where pin-strapping is used to select different operations of each channel. Table 2 lists pins that are used for selecting functions. Please note some differences are only in the name of the pins, such as pin CODE (82V2048) and pin CODEN (LXT384). They are functionally the same pins.

| Items                                     | IDT82V2048                                                                                                                                   | LXT384                                                                                                                                            |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Rail Mode Setting                  | Unipolar/Bipolar Selection:<br>TDN pin = "0" - Dual rail<br>TNN pin = "1" - Single rail                                                      | Unipolar/Bipolar Selection:<br>TNEG pin = "0" - Dual rail<br>TNEG pin = "1" - Single rail                                                         |

| Encode/Decoder Setting                    | Line coding selection:<br>CODE pin = "0" - AMI<br>CODE pin = "1" - B8ZS/HDB3                                                                 | Line Coding Selection:<br>CODEN pin = "0" - AMI<br>CODEN pin = "1" - B8ZS/HDB3                                                                    |

| Clock Recovery Enable/Disable             | Pulling MCLK "high" to disable clock recovery<br>function                                                                                    | Same as 82V2048                                                                                                                                   |

| Power-down Setting for Receiver           | Pulling MCLK "low" to set Receiver to power-down                                                                                             | Same as 82V2048                                                                                                                                   |

| Power-down Setting for<br>Transmitter     | Pulling TCLK "low" to set Transmitter to<br>power-down                                                                                       | Same as 82V2048                                                                                                                                   |

| LP/LOOP Pins Setting in<br>Hardware Mode  | Loop-back Selection:<br>LP pin = "0" - Remote Loop-back<br>LP pin = "1" - Analog Loop-back<br>LP pin = VDDIO/2 - No Loop-back                | Loop-back Selection:<br>LOOP pin = "0" - Remote Loop-back<br>LOOP pin = "1" - Analog Loop-back<br>LOOP pin = NC - NC Loop-back                    |

| JAS/JASEL Pin Setting in<br>Hardware Mode | Jitter Attenuator Selection:<br>JAS pin = "0" - JA in Transmit Path<br>JAS pin = "1" - JA in Receive Path<br>JAS pin = VDDIO/2 - JA disabled | Jitter Attenuator Selection:<br>JASEL pin = "0" - JA in Transmit Path<br>JASEL pin = "1" - JA in Receive Path<br>JASEL pin = High-Z - JA disabled |

# Table 2: Comparison in Hardware Mode Configuration

**Note:** In 82V2048, when LP pins are not connected, they are internally pulled to VDDIO/2. Therefore they can be used in exactly the same way as LOOP pins in LXT384 for "No Loop-back" operation. Likewise, when JAS pins are not connected, they are internally pulled to VDDIO/2. They can be handled exactly the same way as JASEL pins in LXT384 for "JA disabled" selection.

#### Host Mode Comparison

Both 82V2048 and LXT384 include internal registers for host-interface mode. 82V2048 includes both a primary register map and an expanded register map while LXT384 includes only a primary register map. Please see Table 3 and Table 4 for primary and expanded register map, respectively.

# Table 3: Comparison of Primary Register Map of 82V2048 and LXT384

| Registers                         | IDT82          | V2048         | LXT384         |               |

|-----------------------------------|----------------|---------------|----------------|---------------|

|                                   | Offset address | Default Value | Offset address | Default Value |

| Device ID                         | 00h            | 10h*          | 00h            | 00h or 15h*   |

| Analog Loop-back Configuration    | 01h            | 00h           | 01h            | 00h           |

| Remote Loop-back configuration    | 02h            | 00h           | 02h            | 00h           |

| Transmit All Ones configuration   | 03h            | 00h           | 03h            | 00h           |

| Loss of Signal Status             | 04h            | 00h           | 04h            | 00h           |

| Driver Fault Status               | 05h            | 00h           | 05h            | 00h           |

| Loss of Signal Interrupt Mask     | 06h            | 00h           | 06h            | 00h           |

| Driver Fault Interrupt Mask       | 07h            | 00h           | 07h            | 00h           |

| Loss of Signal Interrupt Status   | 08h            | 00h           | 08h            | 00h           |

| Driver Fault Interrupt Status     | 09h            | 00h           | 09h            | 00h           |

| Software Reset (per channel)      | 0Ah            | FFh           | 0Ah            | FFh           |

| Performance Monitor Control       | 0Bh            | 00h           | 0Bh            | 00h           |

| Digital Loop-back Configuration   | 0Ch            | 00h           | 0Ch            | 00h           |

| LOS/AIS Criteria Selection        | 0Dh            | 00h           | 0Dh            | 00h           |

| Automatic TAOS Configuration      | 0Eh            | 00h           | 0Eh            | 00h           |

| Global Configuration              | 0Fh            | 00h           | 0Fh            | 00h           |

| Pulse Shaping Indirect Address    | 10h            | 00h           | 10h            | 00h           |

| Transmit Template Selection       | 11h            | 00h           | 11h            | 00h           |

| Output Enable Configuration       | 12h            | 00h           | 12h            | 00h           |

| Alarm Indication Signal Status    | 13h            | 00h           | 13h            | 00h           |

| Alarm Indication Interrupt Mask   | 14h            | 00h           | 14h            | 00h           |

| Alarm Indication Interrupt Status | 15h            | 00h           | 15h            | 00h           |

| Address Pointer Control Register  | 1Fh*           | 00h*          | N/A            | N/A           |

\* Note: Bold text displays the differences between register maps of 82V2048 and LXT384.

When the Address Pointer Control Register = 0x00, the primary register map is employed in 82V2048. When the Address Pointer Control Register is written with 0xAA, the expanded register map is enabled as shown in Table 4. The LXT384 does not include these registers and uses pin-strapping as discussed in hardware mode to achieve such selections. In this respect, 82V2048 may be more flexible to configure and easier to use in host mode. In addition, the 82V2048 supports Inband loop-back in host mode. LXT384 does not support inband loop-back in either hardware mode or host mode.

## Table 4: 82V2048 Expanded Registers

| Register Names                                        | <b>IDT82V2048</b><br>(n = 07 represents each channel)                                                                                      | LXT384                         |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Single Rail Mode<br>Setting Register <b>SING[7:0]</b> | SING[n] = "0" - Use TDN pins to select single/dual rail mode<br>SING[n] = "1" - Single rail mode                                           | Not supported in host mode     |

| Encoder/Decoder<br>Selection CODE[7:0]                | CODE[n] = "0" - B8ZS encoder/Decoder<br>CODE[n] = "1" - AMI encoder/Decoder                                                                | Not supported in host mode     |

| Clock Recovery Enable/Disable Selection CRS[7:0]      | CRS[n] = "0" - Clock recovery enabled<br>CRS[n] = "1" - Clock recovery disabled                                                            | Not supported in host mode     |

| Receive Power-Down<br>Control <b>RPDN[7:0]</b>        | RPDN[n] = "0" - Receiver normal operation<br>RPDN[n] = "1" - Receiver powered down                                                         | Not supported in host mode     |

| Transmitter Power-down<br>Control <b>TPDN[7:0]</b>    | TPDN[n] = "0" - Transmitter normal operation<br>TPDN[n] = "1" - Transmitter powered down                                                   | Not supported in host mode     |

| EXZ Error Detection<br>Control CZER[7:0]              | CZER[n] = "0" - Excessive zero detection disabled<br>CZER[n] = "1" - Excessive zero detection enabled for<br>B8ZS/HDB3 in single rail mode | Not supported in host mode     |

| Equalizer Enable/Disable<br>Control <b>EQUA[7:0]</b>  | EQUA[n] = "0" - Normal operation<br>EQUA[n] = "1" - Receive equalizer is enabled                                                           | Not supported in host mode     |

| In-band Loop-back<br>Configuration <b>LBCF[7:0]</b>   | Setting LBCF, LBAC, LBDC, LBS, LBM, LBI, LBGS and LBGE registers to enable inband loop-back functions.                                     | Inband Loop-back not supported |

# Application Considerations When Using 82V2048 to Replace LXT384

In Table 1, it is seen that 82V2048 has the same pin-out in both package types (TQPF and BGA) as LXT384. Replacing LXT384 with 82V2048 requires no board changes. However, depending on different mode of device configuration (hardware mode or host mode), the following application considerations may be considered.

#### Host Mode

When host mode is selected, the two devices share a common primary register map. LXT384 defines 22 eight-bit registers with offset addresses from 00h to 15h.

82V2048, not counting Expanded Registers, contains the same number of registers with the same offset addresses and bit definitions of each register.

A thorough register access test was conducted in ATE (Automatic Test Equipment) with the test vector designed as follows:

- 1. After power-up, software reset was issued by writing to 0x0A register;

- 2. Read all registers and check for register default values;

- 3. Write all registers with 0xFF data;

- 4. Read back from all registers again and compare with what was written in (0xFF).

- 5. The access was made with Intel-multiplexed and non-multiplexed bus mode, Motorola multiplexed and non-multiplexed bus mode.

The test results show that, all registers have the same default values after reset between the two devices. All write-and-read operations were correct with both devices. Please note that reading Device ID register (offset 0x00) will have different values between two devices per each vendor's definition.

# MCLK and TCLK

MCLK is the reference clock for the device. TCLK is the system transmit clock for each channel's transmit path. When MCLK is not clocked (in logic "high" or "low"), the receive path of the two devices will respond the same. However, in the transmit path, the two devices respond differently.

In 82V2048, if MCLK is not available, TCLK1 (transmit clock for the first channel) will be internally used as a virtual MCLK in the transmit path. As a result, same operations can be expected as long as TCLK1 is supplied. If neither MCLK nor TCLK1 is supplied, the device will put all TTIP and TRING pairs in high impedance. These operations are tabulated below.

Table 5: Impact of TCLK on IDT82V2048 Transmit Path

| MCLK | TCLK1   | TCLK0, TCLK2~7 | 82V2048 Transmit Path Operations      |

|------|---------|----------------|---------------------------------------|

| H/L  | Clocked | Clocked        | Transmit with pulse-shaping           |

|      |         | H/L            | Transmit All Ones                     |

| H/L  | H/L     | Don't care     | All TIP/RRING pairs in high-impedance |

In LXT384, when MCLK is not available, the status of TCLK has different impacts on the transmit path. The combinations of MCLK and TCLK availability result in the different operations in the transmit path tabulated below.

Table 6:

Impact of TCLK on LXT384 Transmit Path

| MCLK     | TCLK0~7 | LXT384 Transmit Path Operations                                                                                                   |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| H/L      | Clocked | Transmit with pulse-shaping                                                                                                       |

| h<br>H/L | Н       | Transmit without pulse shaping, TPOS and TNEG control the width and polarity of pulses on TTIP and TRING (clock-less transmission |

|          | L       | Transmit path in high-impedance                                                                                                   |

# **External Components**

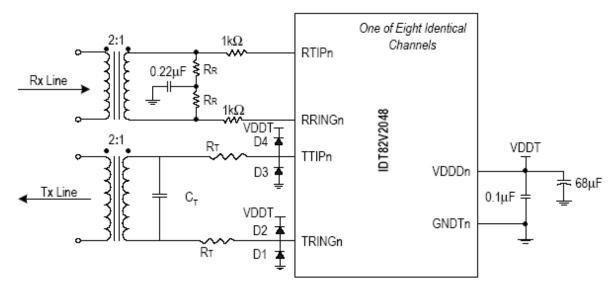

The following diagram shows a typical application diagram for 82V2048. Note that, based on the datasheet of both devices, RT value is recommended to be  $9.5\Omega$  +/-1% for 82V2048,  $9.1\Omega$  +/-1% for LXT384 for VDDT = 5.0V. CT is 1000pF for 82V2048 while 560pF for LXT384.

# RENESAS

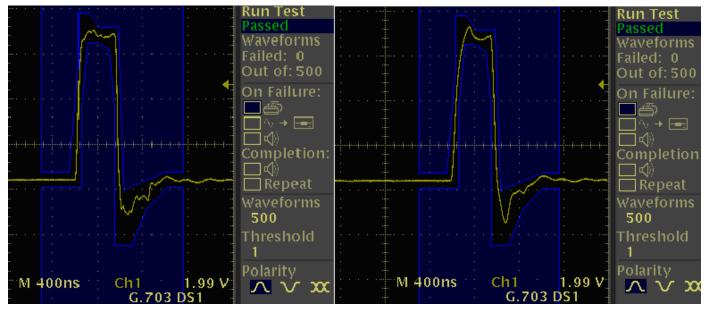

Transmit pulse shape has been verified with the recommended external components. For simple data pattern (i.e., 1-in-8) it can be observed that transmit pulse shape meets G.703 pulse template as shown below in Figure 2. The following picture shows transmit pulse shape in T1 mode 0ft and 655ft cable configurations, respectively.

# Figure 2. Transmit Pulse Shape Of 82V2048 in T1 mode with external components recommended for LXT384. Data pattern:1-in-8 Cable length configurations: 0~133ft (left figure), 533~655ft (right figure)

Note that transmit pulse shape is dependent on the line's overall impedance conditions. In actual applications, the specific values of these external components may need some adjustments to achieve optimal pulse shape.

# **Appendix: Power Consumption Measurement**

| Table 7: | <b>Device Power</b> | Consumption | Comparison |

|----------|---------------------|-------------|------------|

|----------|---------------------|-------------|------------|

| Device         | Data Pattern | 50% Ones |     | 100% | Ones |

|----------------|--------------|----------|-----|------|------|

|                | Mode         | E1       | T1  | E1   | T1   |

| IDT82V2048     | VDDA (mA)    | 25       | 24  | 24   | 24   |

|                | VDDD (mA)    | 33       | 26  | 38   | 29   |

|                | VDDT (mA)    | 55       | 197 | 107  | 344  |

|                | Total (mA)   | 113      | 247 | 169  | 397  |

| Cortina LXT384 | VDDA (mA)    | 53       | 45  | 52   | 44   |

|                | VDDD (mA)    | 60       | 46  | 61   | 46   |

|                | VDDT (mA)    | 67       | 173 | 136  | 321  |

|                | Total (mA)   | 180      | 377 | 249  | 411  |

# References

- [1] IDT82V2048 device datasheet, March 18, 2009

- [2] LXT384 Datasheet 248994, Revision 6.0, January 30, 2008

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.