# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Application Note**

# 78K/0 Series

# 8-bit Single-chip Microcontroller

# Basic (III)

$\mu$ PD78054 subseries  $\mu$ PD78064 subseries  $\mu$ PD78078 subseries  $\mu$ PD78083 subseries  $\mu$ PD780018 subseries  $\mu$ PD780058 subseries  $\mu$ PD780308 subseries  $\mu$ PD78058F subseries  $\mu$ PD78064B subseries  $\mu$ PD78075B subseries  $\mu$ PD78098B subseries

$\mu$ PD78054Y subseries  $\mu$ PD78064Y subseries  $\mu$ PD78078Y subseries  $\mu$ PD78098 subseries  $\mu$ PD780018Y subseries  $\mu$ PD780058Y subseries  $\mu$ PD780308Y subseries  $\mu$ PD78058FY subseries  $\mu$ PD78070A, 78070AY  $\mu$ PD78075BY subseries

Document No. U10182EJ2V0AN00 (2nd edition)

Date Published October 1997 N

[MEMO]

#### NOTES FOR CMOS DEVICES -

#### 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

FIP, EEPROM, and IEBus are trademarks of NEC Corporation.

Purchase of NEC  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130

Tel: 253-8311 Fax: 250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC do Brasil S.A.**

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

# Major Revisions in This Edition

| Page         | Description                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout   | Addition of following products as target products:                                                                                               |

|              | μPD780018, 780018Y, 780058, 780058Y, 780308, 780308Y, 78058F, 78058FY, 78064B, 78075B, 78075BY,                                                  |

|              | 78098B subseries, μPD78070A, 78070AY                                                                                                             |

|              | μPD78052(A), 78053(A), 78054(A)                                                                                                                  |

|              | μPD78062(A), 78063(A), 78064(A)                                                                                                                  |

|              | μPD78081(A), 78082(A), 78P083(A), 78081(A2)                                                                                                      |

|              | μPD78058F(A), 78058FY(A)                                                                                                                         |

|              | μPD78064B(A)                                                                                                                                     |

|              | Deletion of following products as target products:                                                                                               |

|              | μPD78P054Y, 78P064Y, 78074, 78075, 78075, 78074Y, 78075Y                                                                                         |

| p.100        | Addition of Note 2 and Caution 2 to Figure 4-5 Format of Watchdog Timer Mode Register                                                            |

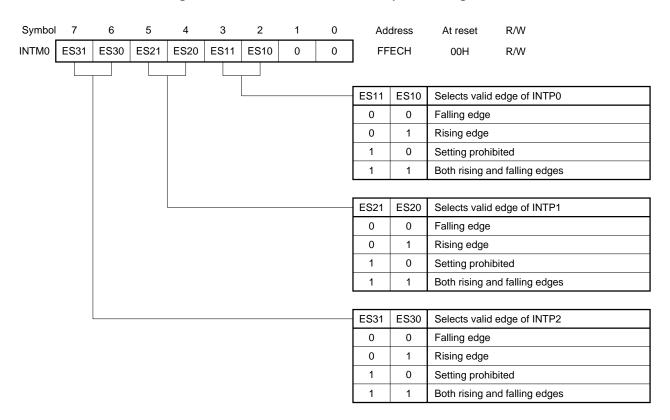

| p.113        | Addition of Caution to Figure 5-8 Format of External Interrupt Mode Register 0                                                                   |

| p.196        | Addition of Table 8-2 Items Supported by Each Subseries                                                                                          |

| p.197        | Addition of Table 8-3 Registers of Serial Interface                                                                                              |

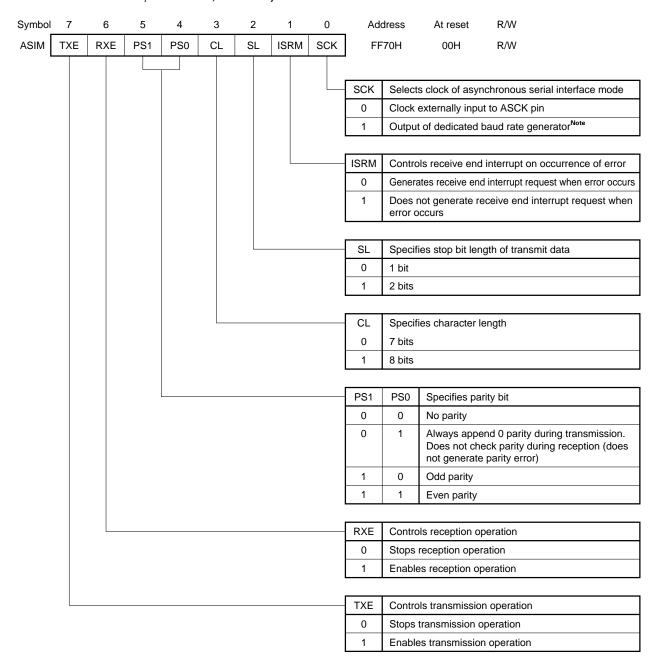

| p.204, p206  | Addition of note on using wake-up function and note on changing operation mode to Figures 8-7 and 8-8 Format of Serial Operating Mode Register 0 |

| p.218, p.224 | Addition of Caution to Figures 8-16 and 8-17 Format of Automatic Data Transfer/Reception Interval Specification Register                         |

| p.239        | Addition of Figures 8-23 and 8-24 Format of Serial Interface Pin Select Register                                                                 |

| p.240        | μPD6252 as maintenance product in <b>8.1 Interface with EEPROM<sup>TM</sup> (μPD6252)</b>                                                        |

| p.250        | Addition of (5) Limitations when using I <sup>2</sup> C bus mode to 8.1.2 Communication in I <sup>2</sup> C bus mode                             |

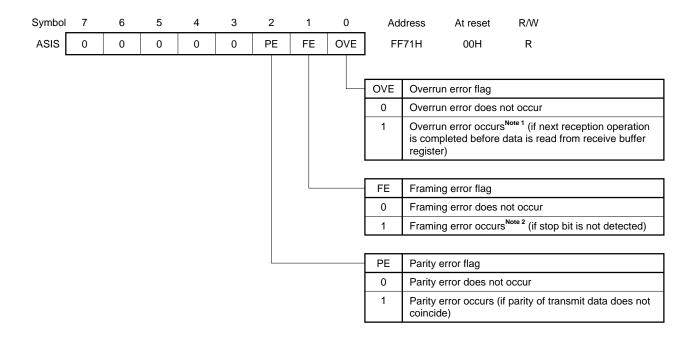

| p.286        | Addition of (f) Limitations when using UART mode to 8.5 Interface in Asynchronous Serial Interface (UART) Mode                                   |

| p.347        | Addition of Figure 11-3 Format of Port Mode Register 12                                                                                          |

| p.216, p.217 | Description of following register formats and tables for each subseries:                                                                         |

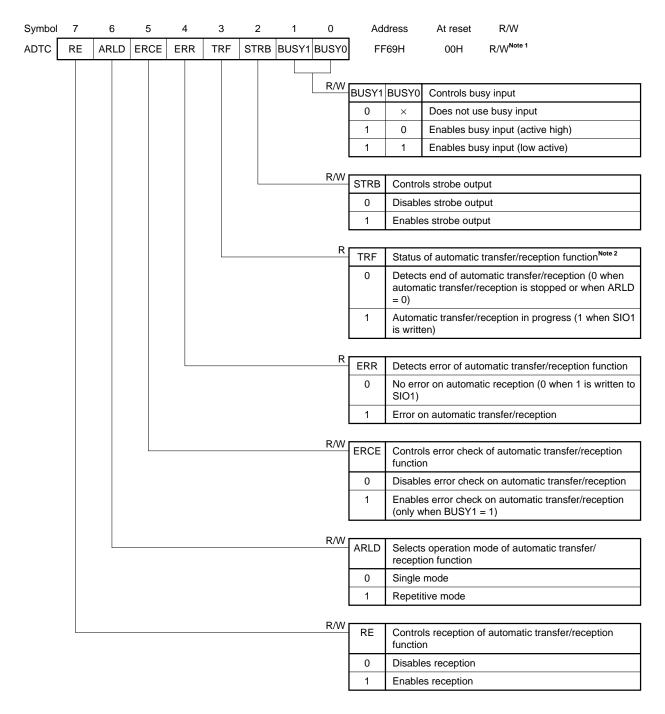

| p.229-p.232  | Figures 8-14 and 8-15 Format of Automatic Data Transmission/Reception Control Register                                                           |

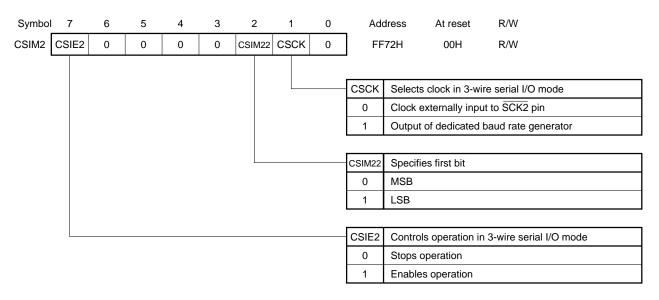

| p.352, p.353 | Tables 8-4, 8-5, and 8-6 Setting of Operation Modes of Serial Interface Channel 2                                                                |

|              | Figures 12-1 and 12-2 Format of LCD Display Mode Register                                                                                        |

| p.387        | Addition of APPENDIX B REVISION HISTORY                                                                                                          |

The mark ★ shows major revised points.

#### INTRODUCTION

#### Readers

This Application Note is intended for use by engineers who understand the functions of the 78K/0 series and wish to design application programs with the following subseries products:

#### Subseries

μPD78054 subseries : μPD78052, 78053, 78054, 78P054, 78055, 78056,

78058, 78P058, 78052(A), 78053(A), 78054(A)

$\mu$ PD78054Y subseries :  $\mu$ PD78052Y, 78053Y, 78054Y, 78055Y, 78056Y,

78058Y, 78P058Y

μPD78064 subseries : μPD78062,78063,78064,78P064,78062(A),78063(A),

78064(A)

$\mu$ PD78064Y subseries :  $\mu$ PD78062Y, 78063Y, 78064Y  $\mu$ PD78078 subseries :  $\mu$ PD78076, 78078, 78P078  $\mu$ PD78078Y subseries :  $\mu$ PD78076Y, 78078Y, 78P078Y

μPD78083 subseries : μPD78081, 78082, 78P083, 78081(A), 78082(A),

78P83(A), 78081(A2)

$\mu$ PD78098 subseries :  $\mu$ PD78094, 78095, 78096, 78098A $^{Note\ 1}$ , 78P098A $^{Note\ 1}$  $\mu$ PD780018 subseries :  $\mu$ PD780016 Note 2, 780018 Note 2, 78P0018 Note 2  $\mu$ PD780018Y subseries:  $\mu$ PD780016Y<sup>Note 2</sup>, 780018Y<sup>Note 2</sup>, 78P0018Y<sup>Note 2</sup>  $\mu$ PD780058 subseries :  $\mu$ PD780053<sup>Note 1</sup>, 780054<sup>Note 1</sup>, 780055<sup>Note 1</sup>.

$780056^{\text{Note 1}}$ ,  $780058^{\text{Note 1}}$ ,  $78F0058^{\text{Note 1}}$

$\mu$ PD780058Y subseries:  $\mu$ PD780053YNote 2, 780054YNote 2.

780055YNote 2, 780056YNote 2, 780058YNote 2,

78F0058YNote 2

$\mu$ PD780308 subseries :  $\mu$ PD780306<sup>Note 1</sup>, 780308<sup>Note 1</sup>, 78P0308<sup>Note 1</sup>  $\mu$ PD780308Y subseries:  $\mu$ PD780306Y<sup>Note 1</sup>, 780308Y<sup>Note 1</sup>, 78P0308Y<sup>Note 1</sup>

$\mu$ PD78058F subseries :  $\mu$ PD78056F, 78058F, 78P058F, 78058F(A)

μPD78058FY, 78P058FY, 78P058FY, 78P058FY, 78P058FY(A)

$\mu$ PD78064B subseries :  $\mu$ PD78064B, 78P064B, 78064B(A)

μPD78070A, 78070AY

$\mu$ PD78075B subseries :  $\mu$ PD78074B, 78075B

$\mu$ PD78075BY subseries:  $\mu$ PD78074BYNote 1, 78075BYNote 1

$\mu$ PD78098B subseries :  $\mu$ PD78095BNote 2, 78096BNote 2, 78098BNote 2,

78P098BNote 2

#### Notes 1. Under development

### 2. Planned

- **Remarks 1.** The  $\mu$ PD78052(A), 78053(A), and 78054(A) have higher reliability than the  $\mu$ PD78052, 78053, and 78054.

- **2.** The  $\mu$ PD78062(A), 78063(A), and 78064(A) have higher reliability than the  $\mu$ PD78062, 78063, and 78064.

- 3. The  $\mu$ PD78081(A), 78082(A), 78P083(A), and 78081(A2) have higher reliability than the  $\mu$ PD78081, 78082, and 78P083.

- **4.** The  $\mu$ PD78058F(A) and 78058FY(A) have higher reliability than the  $\mu$ PD78058F and 78058FY.

- **5.** The  $\mu$ PD78064B(A) has higher reliability than the  $\mu$ PD78064B.

#### **Purpose**

This Application Note is to deepen your understanding of the basic functions of the

78K/0 series by using program examples.

Note that the programs and hardware configuration shown in this document are only examples and not subject to mass production.

### Organization

This Application Note consists of the following contents:

- General

- Software

- Hardware

In addition to this Application Note, the following Application Notes are also available:

| Document Name                                                  | Document Number |               | Targeted Subseries                                                                                                                                                                                                                             | Contents                                                                       |  |

|----------------------------------------------------------------|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Document Name                                                  | Japanese        | English       | rargeted Subseries                                                                                                                                                                                                                             | Contents                                                                       |  |

| 78K/0 Series<br>Application Note<br>Basic (I)                  | IEA-715         | IEA-1288      | μPD78002, 78002Y<br>μPD78014, 78014Y<br>μPD78018F, 78018FY                                                                                                                                                                                     | Explains basic functions of products in 78K/0 series by using program examples |  |

| 78K/0 Series<br>Application Note<br>Basic (II)                 | U10121J         | U10121E       | μPD78044<br>μPD78044H<br>μPD780208<br>μPD780228                                                                                                                                                                                                |                                                                                |  |

| 78K/0 Series<br>Application Note<br>Basic (III)                | U10182J         | This document | μPD78054, 78054Y<br>μPD78064, 78064Y<br>μPD78078, 78078Y<br>μPD78083<br>μPD78098<br>μPD780018, 780018Y<br>μPD780058, 780058Y<br>μPD780308, 780308Y<br>μPD78058F, 78058FY<br>μPD78064B<br>μPD78070A, 78070AY<br>μPD78075B, 78075BY<br>μPD78098B |                                                                                |  |

| 78K/0 Series Application Note Floating-Point Operation Program | IEA-718         | IEA-1289      | All subseries in 78K/0 series $ \left( \begin{array}{c} \text{except } \mu \text{PD78002 and} \\ \text{78002Y subseries} \end{array} \right) $                                                                                                 | Explains floating-point operation programs of products in 78K/0 series         |  |

| μPD78014 Series Application Note Electronic Pocketbook         | IEA-744         | IEA-1301      | $\mu$ PD78014 only $\mu$ PD78014 and 78P014                                                                                                                                                                                                    | Explains how to organize electronic pocketbook by using μPD78014 subseries     |  |

Caution The application examples and program lists shown in this Application Note assume that the main system clock operates at 4.19 MHz, not at 5.0 MHz.

#### **How to Read This Manual**

Although this Application Note explains the functions of the 78K/0 series products, the functions of some products in each subseries differ from those of the others.

(1/2)

| Subseries<br>Chapter                                 | μPD78054<br>μPD78054Y | μPD78064<br>μPD78064Y | μPD78078<br>μPD78078Y | μPD78083 | μPD78098 | μPD780018<br>μPD780018Y | μPD780058<br>μPD780058Y |

|------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------|----------|-------------------------|-------------------------|

| CHAPTER 1 GENERAL                                    | 0                     | 0                     | 0                     | 0        | 0        | 0                       | 0                       |

| CHAPTER 2 FUNDAMENTALS OF SOFTWARE                   | 0                     | 0                     | 0                     | 0        | 0        | 0                       | 0                       |

| CHAPTER 3 APPLICATIONS OF SYSTEM CLOCK SELECTION     | 0                     | 0                     | 0                     | $\circ$  | 0        | 0                       | 0                       |

| CHAPTER 4 APPLICATIONS OF WATCHDOG TIMER             | 0                     | 0                     | 0                     | 0        | 0        | 0                       | 0                       |

| CHAPTER 5 APPLICATIONS OF 16-BIT TIMER/EVENT COUNTER | 0                     | 0                     | 0                     | _        | 0        | 0                       | 0                       |

| CHAPTER 6 APPLICATIONS OF 8-BIT TIMER/EVENT COUNTER  | 0                     | 0                     | 0                     | _        | 0        | 0                       | 0                       |

| CHAPTER 7 APPLICATIONS OF WATCH TIMER                | 0                     | 0                     | 0                     | _        | 0        | 0                       | 0                       |

| CHAPTER 8 APPLICATIONS OF SERIAL INTERFACE           | 0                     | 0                     | 0                     | $\circ$  | 0        | 0                       | 0                       |

| CHAPTER 9 APPLICATIONS OF A/D CONVERTER              | 0                     | 0                     | 0                     | $\circ$  | 0        | 0                       | 0                       |

| CHAPTER 10 APPLICATIONS<br>OF D/A CONVERTER          | 0                     | _                     | 0                     | _        | 0        | _                       | 0                       |

| CHAPTER 11 APPLICATION OF REAL-TIME OUTPUT PORT      | 0                     | _                     | 0                     | _        | 0        | _                       | 0                       |

| CHAPTER 12 APPLICATIONS OF LCD CONTROLLER/DRIVER     | _                     | 0                     | _                     | _        | _        | _                       | _                       |

| CHAPTER 13 APPLICATIONS<br>OF KEY INPUT              | 0                     | 0                     | 0                     | -        | 0        | 0                       | 0                       |

(2/2)

| Subseries<br>Chapter                                 | μPD780308<br>μPD780308Y | μPD78058F<br>μPD78058FY | μPD78064B | μPD78070A<br>μPD78070AY | μPD78075B<br>μPD78075BY | μPD78098B |

|------------------------------------------------------|-------------------------|-------------------------|-----------|-------------------------|-------------------------|-----------|

| CHAPTER 1 GENERAL                                    | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 2 FUNDAMENTALS OF SOFTWARE                   | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 3 APPLICATIONS OF SYSTEM CLOCK SELECTION     | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 4 APPLICATIONS OF WATCHDOG TIMER             | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 5 APPLICATIONS OF 16-BIT TIMER/EVENT COUNTER | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 6 APPLICATIONS OF 8-BIT TIMER/EVENT COUNTER  | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 7 APPLICATIONS OF WATCH TIMER                | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 8 APPLICATIONS OF SERIAL INTERFACE           | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 9 APPLICATIONS OF A/D CONVERTER              | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

| CHAPTER 10 APPLICATIONS<br>OF D/A CONVERTER          | _                       | 0                       | _         | 0                       | 0                       | 0         |

| CHAPTER 11 APPLICATION OF REAL-TIME OUTPUT PORT      | _                       | 0                       | _         | 0                       | 0                       | 0         |

| CHAPTER 12 APPLICATIONS<br>OF LCD CONTROLLER/DRIVER  | 0                       | _                       | 0         | _                       | _                       | _         |

| CHAPTER 13 APPLICATIONS<br>OF KEY INPUT              | 0                       | 0                       | 0         | 0                       | 0                       | 0         |

The (A)-model and standard models differ only in quality grade.

The  $\mu$ PD78081(A2) differs from standard models and (A)-models in terms of supply voltage and operating temperature range. For details, refer to the individual Data Sheet.

In this document, read (A)-models and (A2)-model as follows:

Legend

Data significance : Left: higher digit, right: lower digit

Low active : xxx (top bar over pin or signal name)

Note : Description of Note in the text

**Caution** : Important information

Remark : Supplement

Numeric representation: Binary ... xxxx or xxxxB

Decimal ... ××××

Hexadecimal ... ××××H

#### **Quality Grade**

#### Standard

```

\muPD78052, 78053, 78054, 78055, 78056, 78058, 78P058

\muPD78052Y, 78053Y, 78054Y, 78055Y, 78056Y, 78058Y, 78P058Y

μPD78062, 78063, 78064, 78P064

\muPD78062Y, 78063Y, 78064Y

μPD78076, 78078, 78P078

\muPD78076Y, 78078Y, 78P078Y

μPD78081, 78082, 78P083

\muPD78094, 78095, 78096, 78098A, 78P098A

\muPD780016, 780018, 78P0018

μPD780016Y, 780018Y, 78P0018Y

\muPD780053, 780054, 780055, 780056, 780058, 78F0058

μPD780053Y, 780054Y, 780055Y, 780056Y, 780058Y, 78F0058Y

μPD780306, 780308, 78P0308

\muPD780306Y, 780308Y, 78P0308Y

μPD78056F, 78058F, 78P058F

μPD78056FY, 78058FY, 78P058FY

μPD78064B, 78P064B

\muPD78070A, 78070AY

\muPD78074B, 78075B

μPD78074BY, 78075BY

μPD78095B, 78096B, 78098B, 78P098B

```

#### Special

```

μPD78052(A), 78053(A), 78054(A)

μPD78062(A), 78063(A), 78064(A)

μPD78082(A), 78083(A), 78P083(A), 78081(A2)

μPD78058F(A), 78058FY(A)

μPD78064B(A)

```

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

### **Application Field**

• Consumer appliances

#### **Related documents**

Some of the related documents listed below are preliminary versions but not so specified here.

#### Common related documents

| Document Name                                                    | Document Number |               |  |

|------------------------------------------------------------------|-----------------|---------------|--|

| Document Name                                                    | Japanese        | English       |  |

| 78K/0 Series Application Note - Basic (III)                      | U10182J         | This document |  |

| 78K/0 Series Application Note - Floating-Point Operation Program | IEA-718         | IEA-1289      |  |

| 78K/0 Series User's Manual - Instruction                         | U12326J         | U12326E       |  |

| 78K/0 Series Instruction Set                                     | U10904J         | _             |  |

| 78K/0 Series Instruction Table                                   | U10903J         | _             |  |

# • Documents dedicated to product

# (1) $\mu$ PD78054 subseries

| Document Name                                          | Document Number |         |  |

|--------------------------------------------------------|-----------------|---------|--|

| Document Name                                          | Japanese        | English |  |

| μPD78052, 78053, 78054, 78055, 78056, 78058 Data Sheet | U12327J         | IC-3403 |  |

| μPD78P054 Data Sheet                                   | U12346J         | U12346E |  |

| μPD78P058 Data Sheet                                   | IC-8884         | U10417E |  |

| μPD78054, μPD78054Y Subseries User's Manual            | U11747J         | U11747E |  |

| μPD78054 Subseries Special Function Register Table     | U10102J         | _       |  |

| μPD78052(A), 78053(A), 78054(A) Data Sheet             | U12171J         | U12171E |  |

# (2) $\mu$ PD78054Y subseries

| Document Name                                        | Document Number |         |  |

|------------------------------------------------------|-----------------|---------|--|

| Document Name                                        | Japanese        | English |  |

| μPD78052Y, 78053Y, 78054Y, 78056Y, 78058Y Data Sheet | U10906J         | U10906E |  |

| μPD78P058Y Data Sheet                                | U10907J         | U10907E |  |

| μPD78054, 78054Y Subseries User's Manual             | U11747J         | U11747E |  |

| μPD78054Y Subseries Special Function Register Table  | U10087J         | _       |  |

# (3) $\mu$ PD78064 subseries

| Document Name                                      | Document Number |         |  |

|----------------------------------------------------|-----------------|---------|--|

| Document Name                                      | Japanese        | English |  |

| μPD78062, 78063, 78064 Data Sheet                  | U12238J         | U12338E |  |

| μPD78P064 Data Sheet                               | U12589J         | U12589E |  |

| μPD78062(A), 78063(A), 78064(A) Data Sheet         | U10335J         | U10335E |  |

| μPD78064, 78064Y Subseries User's Manual           | U10105J         | U10105E |  |

| μPD78064 Subseries Special Function Register Table | IEM-5568        | _       |  |

# (4) $\mu$ PD78064Y subseries

| Document Name                                       | Document Number |         |  |

|-----------------------------------------------------|-----------------|---------|--|

| Document Name                                       | Japanese        | English |  |

| μPD78062Y, 78063Y, 78064Y Data Sheet                | U10330J         | U10330E |  |

| μPD78064, 78064Y Subseries User's Manual            | U10105J         | U10105E |  |

| μPD78064Y Subseries Special Function Register Table | IEM-5583        | -       |  |

# (5) $\mu$ PD78078 subseries

| Document Name                                      | Document Number |         |  |

|----------------------------------------------------|-----------------|---------|--|

| Document Name                                      | Japanese        | English |  |

| μPD78076, 78078 Data Sheet                         | U10167J         | U10167E |  |

| μPD78P078 Data Sheet                               | U10168J         | U10168E |  |

| μPD78078 Subseries User's Manual                   | U10641J         | U10641E |  |

| μΡD78078 Subseries Special Function Register Table | IEM-5607        | _       |  |

# (6) $\mu$ PD78078Y subseries

| Document Name                                       | Document Number |         |  |

|-----------------------------------------------------|-----------------|---------|--|

| Document Name                                       | Japanese        | English |  |

| μPD78076Y, 78078Y Data Sheet                        | U10605J         | U10605E |  |

| μPD78P078Y Data Sheet                               | U10606J         | U10606E |  |

| μPD78078, 78078Y Subseries User's Manual            | U10641J         | U10641E |  |

| μΡD78078Y Subseries Special Function Register Table | U10257J         | _       |  |

# (7) $\mu$ PD78083 subseries

| Document Name                                      | Document Number |                     |  |

|----------------------------------------------------|-----------------|---------------------|--|

| Document Name                                      | Japanese        | English             |  |

| μPD78081, 78082 Data Sheet                         | U11415J         | U11415E             |  |

| μPD78P083 Data Sheet                               | U11006J         | U11006E             |  |

| uPD78081(A), 78082(A) Data Sheet                   | U12436J         | To be released soon |  |

| uPD78P083(A) Data Sheet                            | U12175J         | U12175E             |  |

| μPD78083 Subseries User's Manual                   | U12176J         | U12176E             |  |

| μPD78083 Subseries Special Function Register Table | IEM-5599        | _                   |  |

# (8) $\mu$ PD78098 subseries

| Document Name                                     | Document Number  |          |

|---------------------------------------------------|------------------|----------|

|                                                   | Japanese English | English  |

| μPD78094, 78095, 78096, 78098A Data Sheet         | U10146J          | U10146E  |

| μPD78P098A Data Sheet                             | U10203J          | U10203E  |

| μPD78098 Subseries User's Manual                  | IEU-854          | IEU-1381 |

| μPD78098 Subseries Special Function Register List | IEM-5591         | _        |

# (9) $\mu$ PD780018 subseries

| Document Name                                     | Document Number  |                 |

|---------------------------------------------------|------------------|-----------------|

| Document Name                                     | Japanese English |                 |

| μPD780016, 780018 Preliminary Product Information | Plan to prepare  | Plan to prepare |

| μPD78P0018 Preliminary Product Information        | Plan to prepare  | Plan to prepare |

| μPD780018, 780018Y Subseries User's Manual        | Plan to prepare  | Plan to prepare |

# (10) $\mu$ PD780018Y subseries

| Document Name                                       | Document Number  |                 |

|-----------------------------------------------------|------------------|-----------------|

| Document Name                                       | Japanese English |                 |

| μPD780016Y, 780018Y Preliminary Product Information | U11810J          | U11810E         |

| μPD78P0018Y Preliminary Product Information         | Plan to prepare  | Plan to prepare |

| μΡD780018, 780018Y Subseries User's Manual          | Plan to prepare  | Plan to prepare |

# (11) $\mu$ PD780058 subseries

| Document Name                              | Document Number  |         |

|--------------------------------------------|------------------|---------|

|                                            | Japanese English | English |

| μPD780053, 780054, 780055, 780056, 780058  | U12182J          | U12182E |

| Preliminary Product Information            |                  |         |

| μPD78F0058 Preliminary Product Information | U12092J          | U12092E |

| μPD780058, 780058Y Subseries User's Manual | U12013J          | U12013E |

# (12) $\mu$ PD780058, 780058Y subseries

| Degument Name                                  | Document Number  |                 |

|------------------------------------------------|------------------|-----------------|

| Document Name                                  | Japanese English | English         |

| μPD780053Y, 780054Y, 780055Y, 780056Y, 780058Y | Plan to prepare  | Plan to prepare |

| Preliminary Product Information                |                  |                 |

| μPD78F0058Y Preliminary Product Information    | U12324J          | U12324E         |

| μΡD780058, 780058Y Subseries User's Manual     | U12013J          | U12013E         |

# (13) $\mu$ PD780308 subseries

| Document Name                              | Documer          | Document Number |  |

|--------------------------------------------|------------------|-----------------|--|

|                                            | Japanese English | English         |  |

| μPD780306, 780308 Data Sheet               | U11105J          | U11105E         |  |

| μPD78P0308 Preliminary Product Information | U11776J          | U11776E         |  |

| μΡD780308, 780308Y Subseries User's Manual | U11377J          | U11377E         |  |

# (14) $\mu$ PD780308Y subseries

| Document Name                               | Document Number  |         |

|---------------------------------------------|------------------|---------|

|                                             | Japanese English | English |

| μPD780306Y, 780308Y Data Sheet              | U12251J          | U12251E |

| μPD78P0308Y Preliminary Product Information | U11832J          | U11832E |

| μPD780308, 780308Y Subseries User's Manual  | U11377J          | U11377E |

# (15) $\mu$ PD78058F subseries

| Document Name                              | Document Number     |                 |

|--------------------------------------------|---------------------|-----------------|

| Document Name                              | Japanese            | English         |

| μPD78056F, 78058F Data Sheet               | U11795J             | U11795E         |

| μPD78P058F Data Sheet                      | U11796J             | U11796E         |

| μPD78058F(A) Data Sheet                    | To be released soon | Plan to prepare |

| μPD78058F, 78058FY Subseries User's Manual | U12068J             | U12068E         |

# (16) $\mu$ PD78058FY subseries

| Document Name                              | Document Number |                     |

|--------------------------------------------|-----------------|---------------------|

| Document Name                              | Japanese        | English             |

| μPD78056FY, 78058FY Data Sheet             | U12142J         | U12142E             |

| μPD78P058FY Data Sheet                     | U12076J         | U12076E             |

| μPD78058F, 78058FY Subseries User's Manual | U12068J         | To be released soon |

# (17) $\mu$ PD78064B subseries

| Document Name                    | Document Number  |         |

|----------------------------------|------------------|---------|

|                                  | Japanese English | English |

| μPD78064B Data Sheet             | U11590J          | U11590E |

| μPD78064B(A) Data Sheet          | U11597J          | U11597E |

| μPD78P064B Data Sheet            | U11598J          | U11598E |

| μPD780308, 780308Y User's Manual | U10785J          | U10785E |

# (18) $\mu$ PD78070A, 78070AY subseries

| Decument Name                    | Document Number |         |

|----------------------------------|-----------------|---------|

| Document Name                    | Japanese        | English |

| μPD78070A Data Sheet             | U10326J         | U10326E |

| μPD78070AY Data Sheet            | U10542J         | U10542E |

| μΡD78070A, 78070AY User's Manual | IEU-907         | U10200E |

| μΡD78070A                        | U10133J         | _       |

| μΡD78070ΑΥ                       | U10134J         | _       |

### (19) $\mu$ PD78075B subseries

| Document Name                              | Document Number |                     |

|--------------------------------------------|-----------------|---------------------|

| Document Name                              | Japanese        | English             |

| μPD78074B, 78075B Data Sheet               | U12017J         | U12017E             |

| μΡD78075B, 78075BY Subseries User's Manual | U12560J         | To be released soon |

# (20) $\mu$ PD78075BY subseries

| Document Name                              | Document Number |                     |  |

|--------------------------------------------|-----------------|---------------------|--|

| Document Name                              | Japanese        | English             |  |

| μPD78074BY, 78075BY Data Sheet             | Plan to prepare | Plan to prepare     |  |

| μPD78075B, 78075BY Subseries User's Manual | U12560J         | To be released soon |  |

# (21) $\mu$ PD78098B subseries

| Document Name                        | Document Number     |                 |

|--------------------------------------|---------------------|-----------------|

| Document Name                        | Japanese English    |                 |

| μPD78095B, 78096B, 78098B Data Sheet | Plan to prepare     | Plan to prepare |

| μPD78P098B Data Sheet                | Plan to prepare     | Plan to prepare |

| μPD78098B Subseries User's Manual    | To be released soon | Plan to prepare |

The contents of the above related documents are subject to change without notice. Be sure to use the latest edition when you design your system.

# CONTENTS

| CHAPTER | ? 1 GENERAL                                                                  | 1   |

|---------|------------------------------------------------------------------------------|-----|

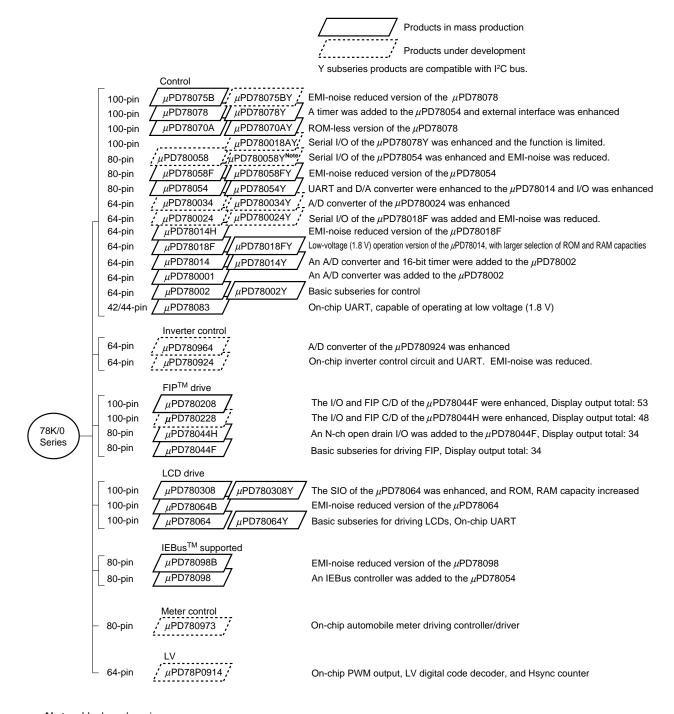

| 1.1     | Product Development of 78K/0 Series                                          | 1   |

| 1.2     | Features of 78K/0 Series                                                     | 3   |

| CHAPTER | 2 FUNDAMENTALS OF SOFTWARE                                                   | 57  |

| 2.1     | Data Transfer                                                                | 57  |

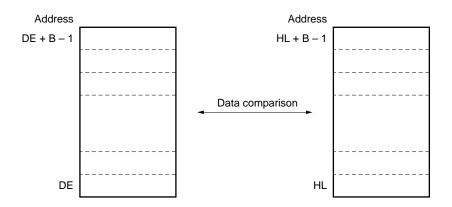

| 2.2     | Data Comparison                                                              | 58  |

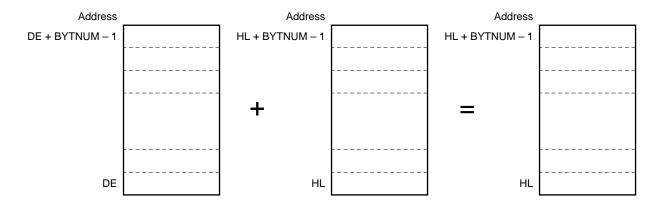

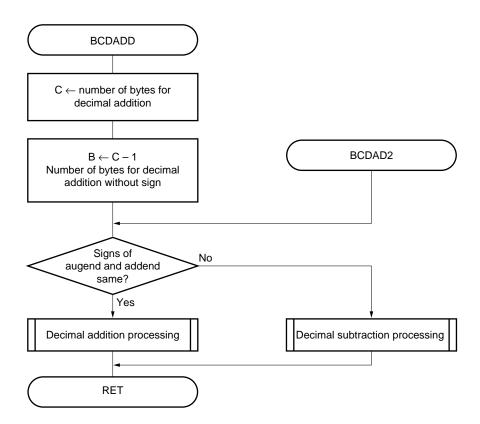

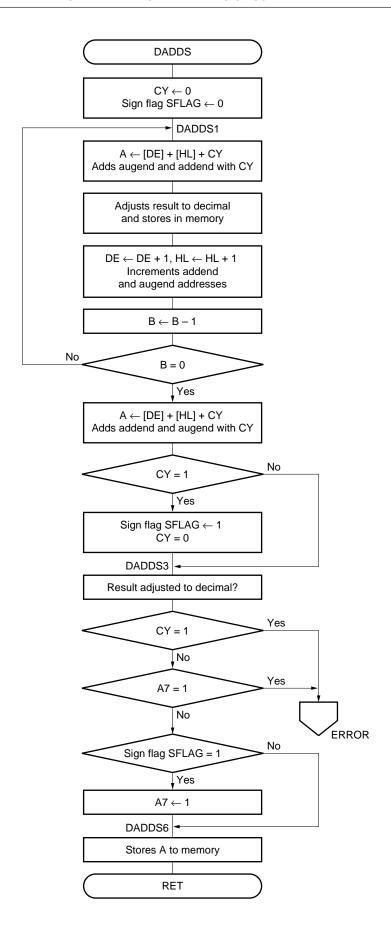

| 2.3     | Decimal Addition                                                             | 59  |

| 2.4     | Decimal Subtraction                                                          | 66  |

| 2.5     | Binary-to-Decimal Conversion                                                 | 68  |

| 2.6     | Bit Manipulation Instruction                                                 | 70  |

| 2.7     | Binary Multiplication (16 bits × 16 bits)                                    | 71  |

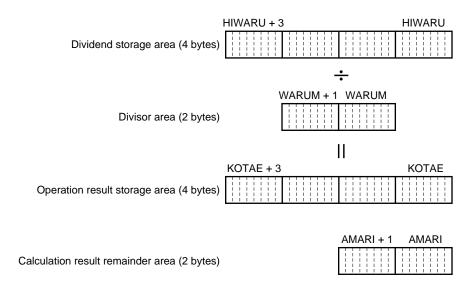

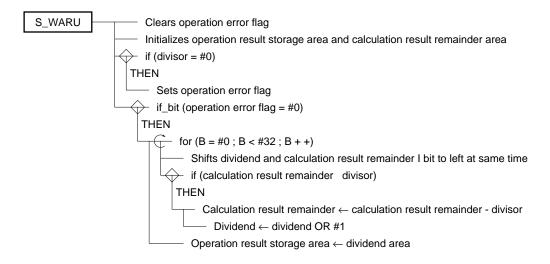

| 2.8     | Binary Division (32 bits ÷ 16 bits)                                          | 75  |

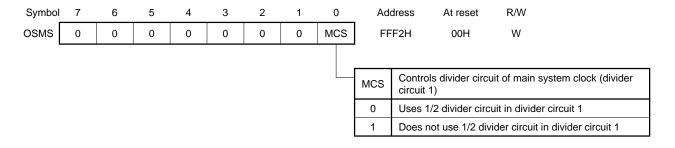

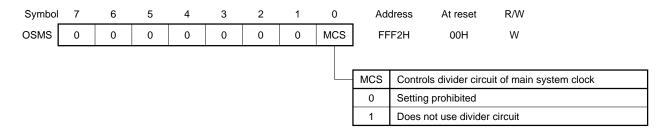

| CHAPTER | 3 APPLICATION OF SYSTEM CLOCK SELECTION                                      | 79  |

| 3.1     | Changing PCC Immediately after RESET                                         | 89  |

| 3.2     | Selecting Power ON/OFF                                                       | 91  |

| CHAPTER | 4 APPLICATIONS OF WATCHDOG TIMER                                             | 95  |

| 4.1     | Setting Watchdog Timer Mode                                                  | 101 |

| 4.2     | Setting Interval Timer Mode                                                  | 103 |

| CHAPTER | 5 APPLICATIONS OF 16-BIT TIMER/EVENT COUNTER                                 | 105 |

| 5.1     | Setting of Interval Timer                                                    | 116 |

| 5.2     | PWM Output                                                                   | 118 |

| 5.3     | Remote Controller Signal Reception                                           | 121 |

|         | 5.3.1 Remote controller signal reception by counter clearing                 | 123 |

|         | 5.3.2 Remote controller signal reception by PWM output and free running mode | 137 |

| 5.4     | One-Shot Pulse Output                                                        | 152 |

| 5.5     | PPG Output                                                                   | 156 |

| CHAPTER | 8 6 APPLICATIONS OF 8-BIT TIMER/EVENT COUNTER                                | 163 |

| 6.1     | Setting of Interval Timer                                                    | 171 |

|         | 6.1.1 Setting of 8-bit timers                                                | 172 |

|         | 6.1.2 Setting of 16-bit timer                                                | 173 |

| 6.2     | Musical Scale Generation                                                     | 174 |

| CHAPTER | 7 APPLICATIONS OF WATCH TIMER                                                | 181 |

| 7.1     | Watch and LED Display Program                                                | 187 |

| CHAPTER | 8 8 APPLICATIONS OF SERIAL INTERFACE                                         | 195 |

| 8.1     | Interface with EEPROM <sup>TM</sup> (µPD6252)                                | 240 |

|         | 8.1.1 Communication in 2-wire serial I/O mode                                | 242 |

|         | 8.1.2 Communication in I <sup>2</sup> C bus mode                             | 250 |

| 8.2     | Interta | ace with OSD LSI ( $\mu$ PD6451A)                | 260 |

|---------|---------|--------------------------------------------------|-----|

| 8.3     | Interfa | ace in SBI Mode                                  | 265 |

|         | 8.3.1   | Application as master CPU                        | 267 |

|         | 8.3.2   | Application as slave CPU                         | 276 |

| 8.4     | Interfa | ace in 3-Wire Serial I/O Mode                    | 279 |

|         | 8.4.1   | Application as master CPU                        | 280 |

|         | 8.4.2   | Application as slave CPU                         | 283 |

| 8.5     | Interfa | ace in Asynchronous Serial Interface (UART) Mode | 286 |

| CHAPTE  | R 9 AP  | PLICATIONS OF A/D CONVERTER                      | 299 |

| 9.1     | Level   | Meter                                            | 307 |

| 9.2     | Therm   | nometer                                          | 316 |

| 9.3     | Analo   | g Key Input                                      | 326 |

| 9.4     | 4-Cha   | nnel Input A/D Conversion                        | 332 |

| CHAPTEI | R 10 A  | PPLICATIONS OF D/A CONVERTER                     | 337 |

| 10.1    | SIN W   | ave Output                                       | 338 |

| CHAPTEI | R 11 A  | PPLICATION OF REAL-TIME OUTPUT PORT              | 345 |

| 11.1    | Stepp   | ing Motor                                        | 348 |

| CHAPTEI | R 12 A  | PPLICATIONS OF LCD CONTROLLER/DRIVER             | 351 |

| 12.1    | Static  | Display                                          | 360 |

| 12.2    | 4-Time  | e Division Display                               | 366 |

| CHAPTE  | R 13 A  | PPLICATIONS OF KEY INPUT                         | 373 |

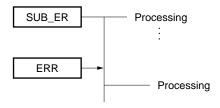

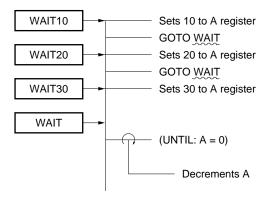

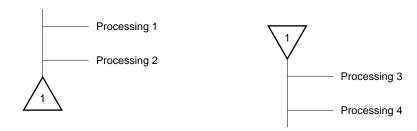

| APPEND  | IX A DI | ESCRIPTION OF SPD CHART                          | 379 |

| APPEND  | X B R   | EVISION HISTORY                                  | 387 |

# LIST OF FIGURES (1/6)

| Fig. No. | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

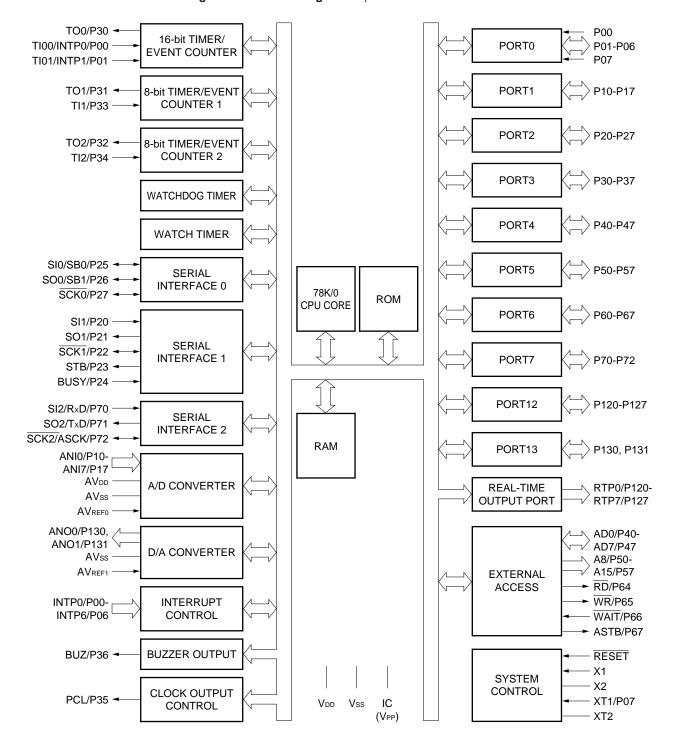

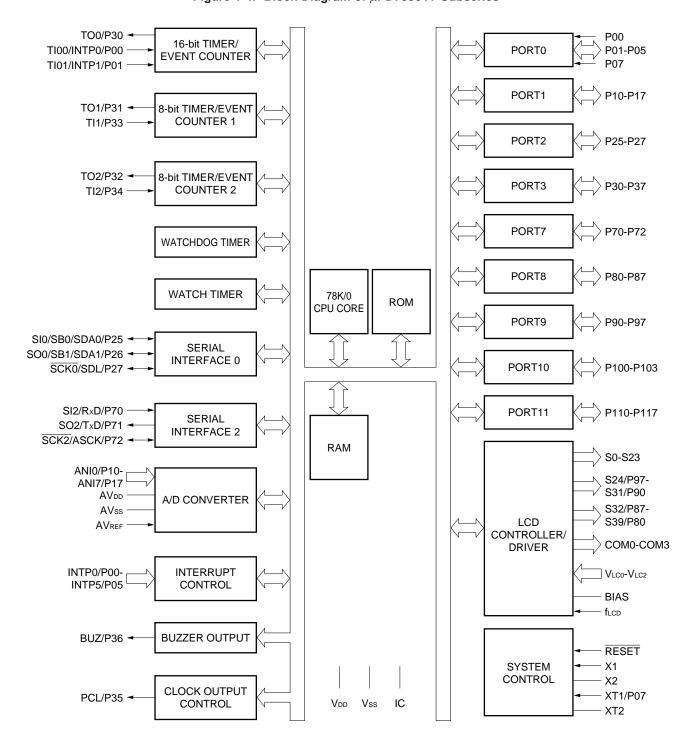

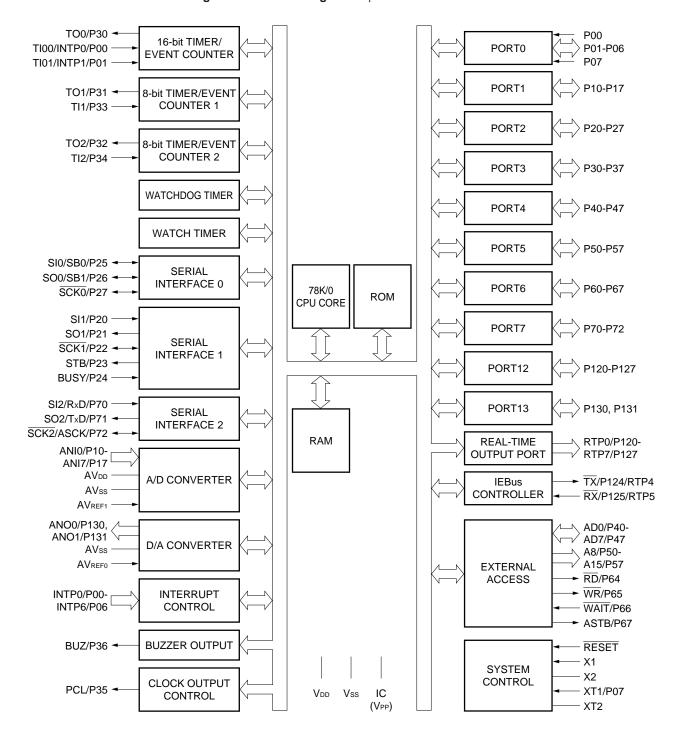

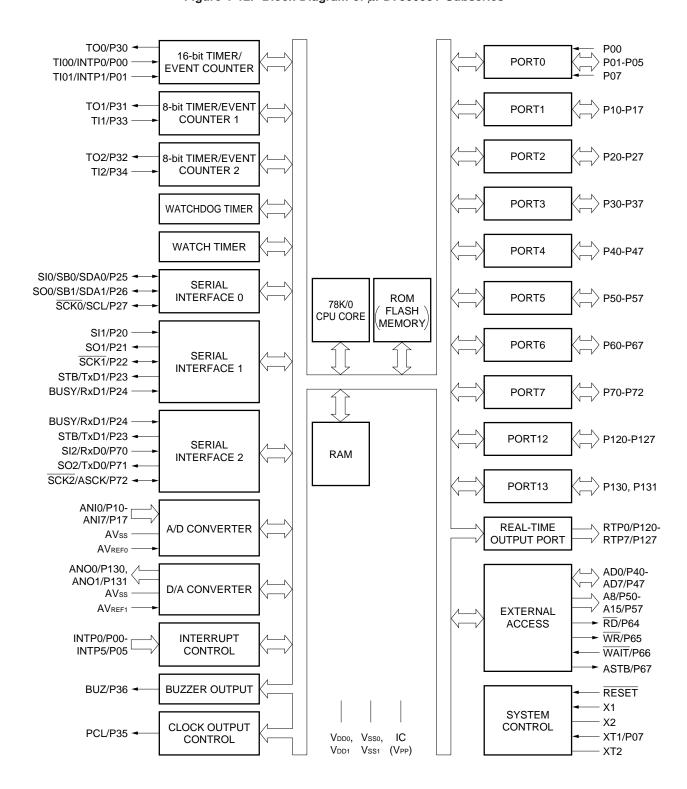

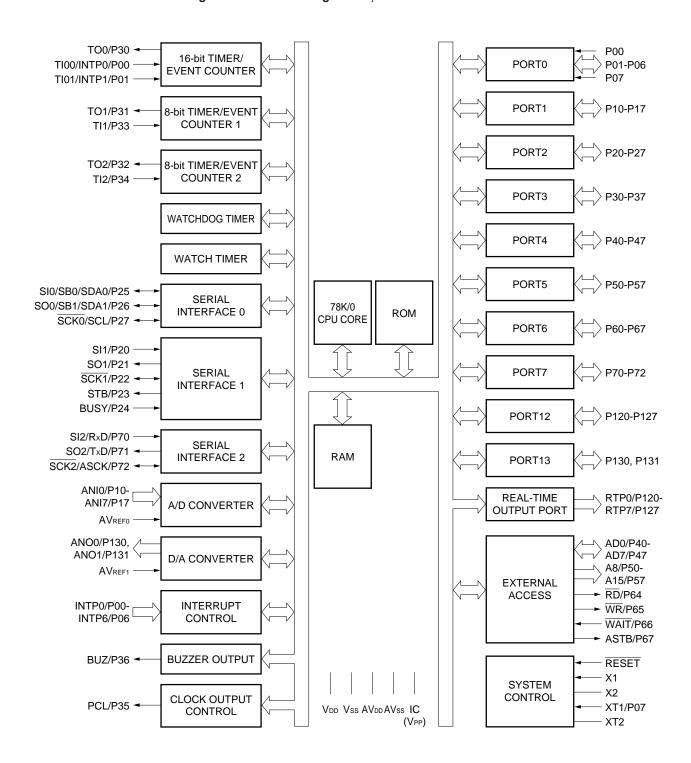

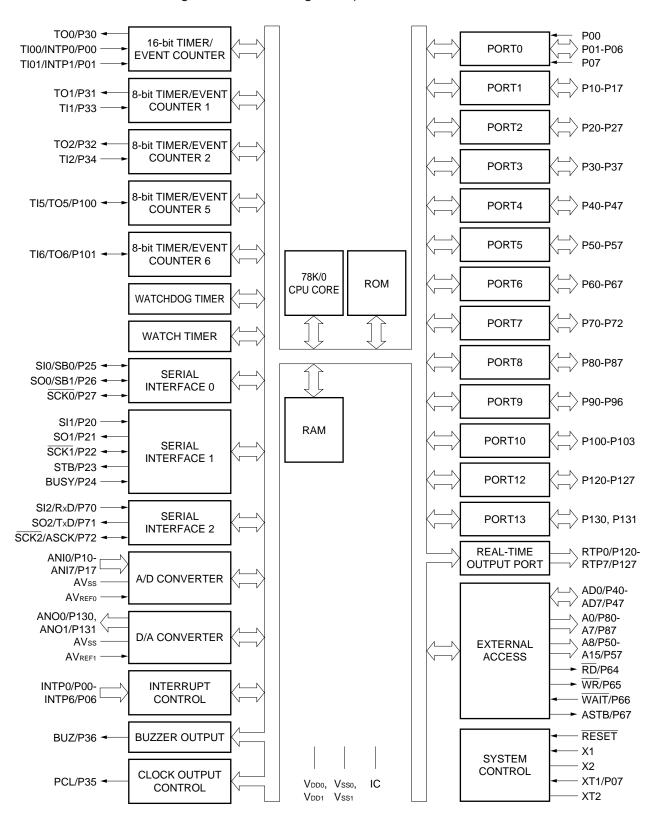

| 1-1.     | Block Diagram of μPD78054 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4    |

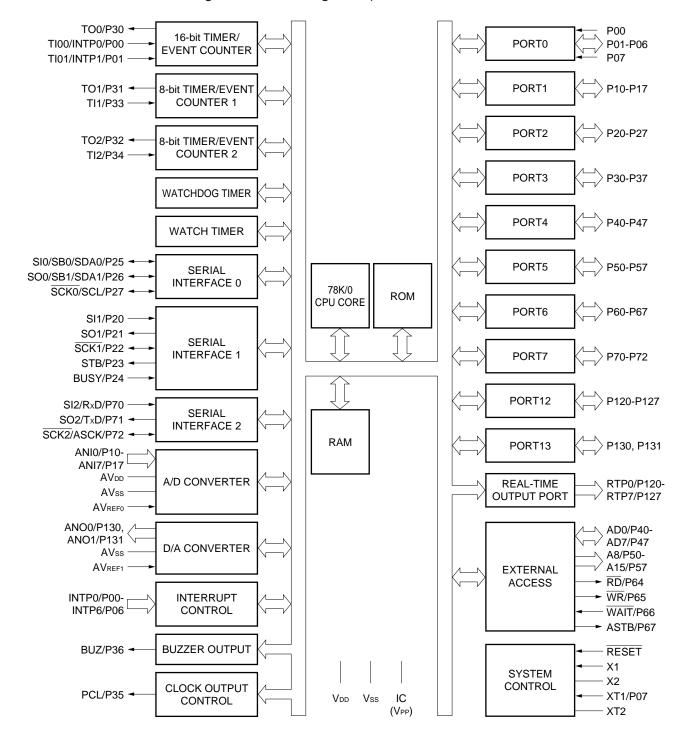

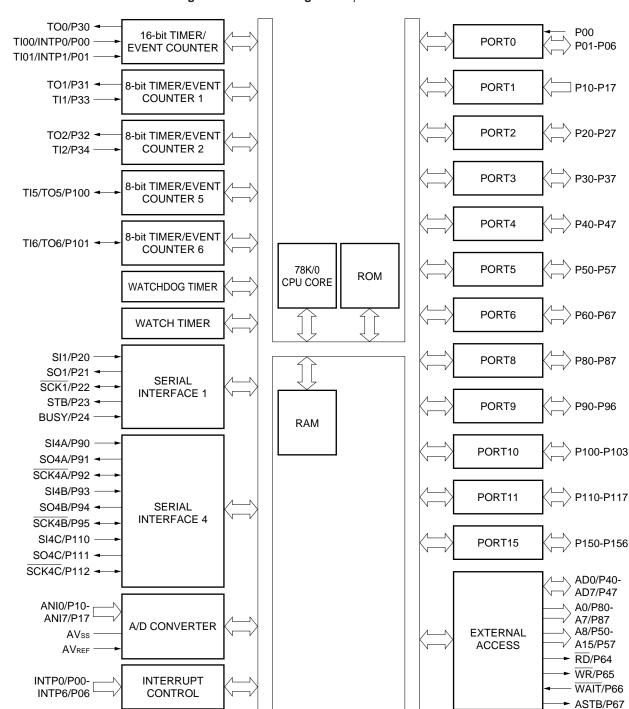

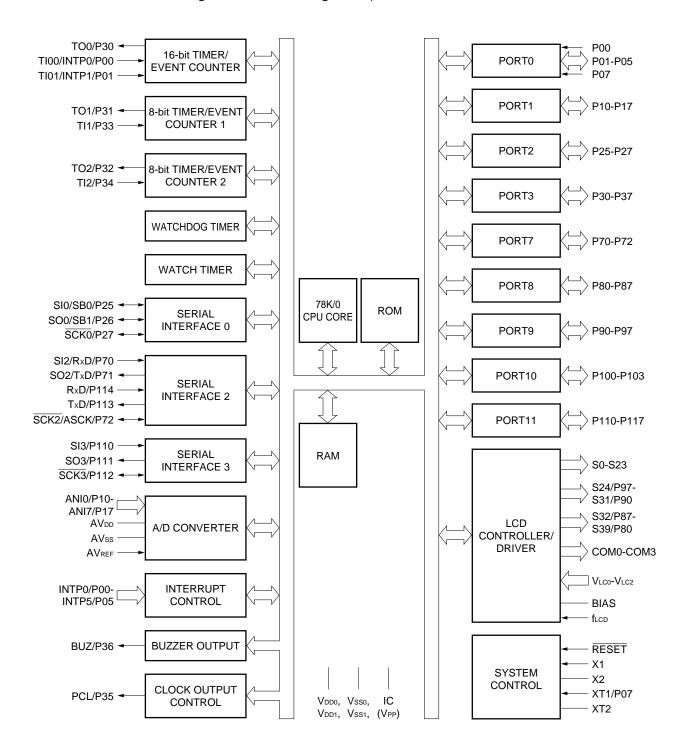

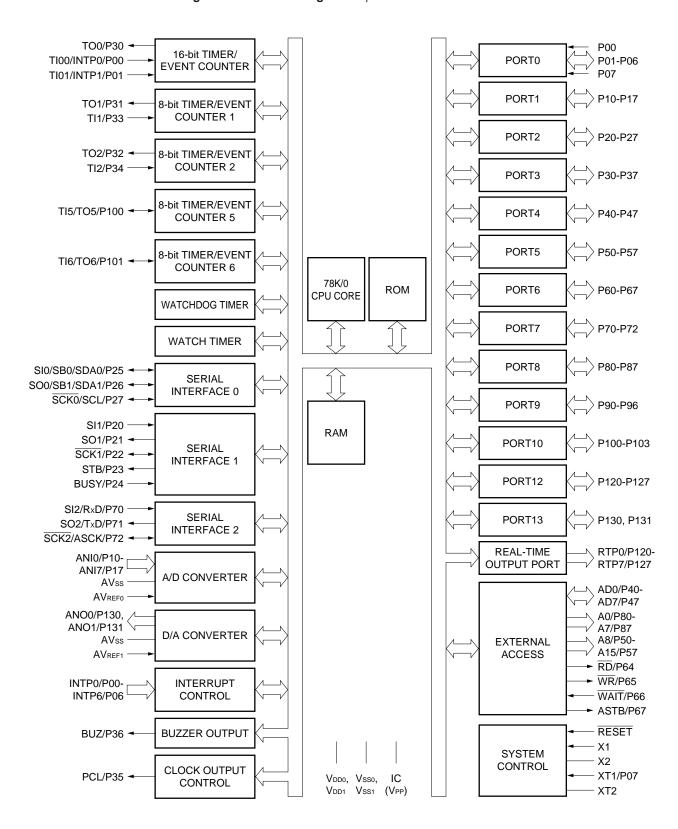

| 1-2.     | Block Diagram of μPD78054Y Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7    |

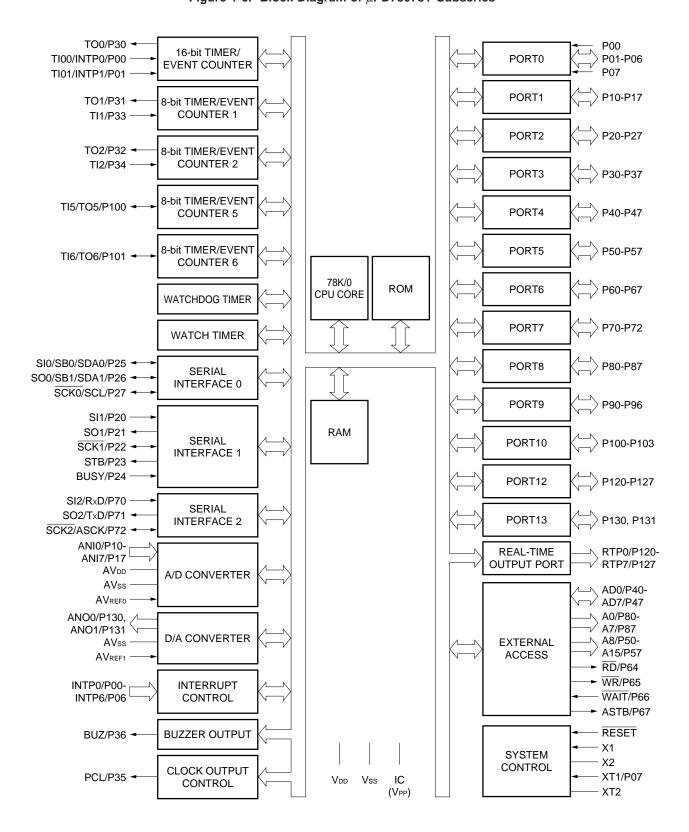

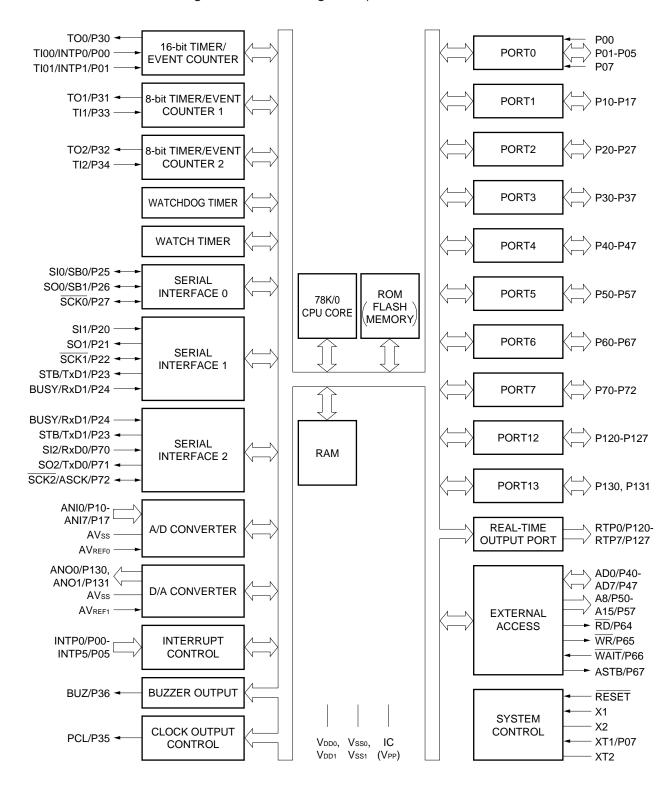

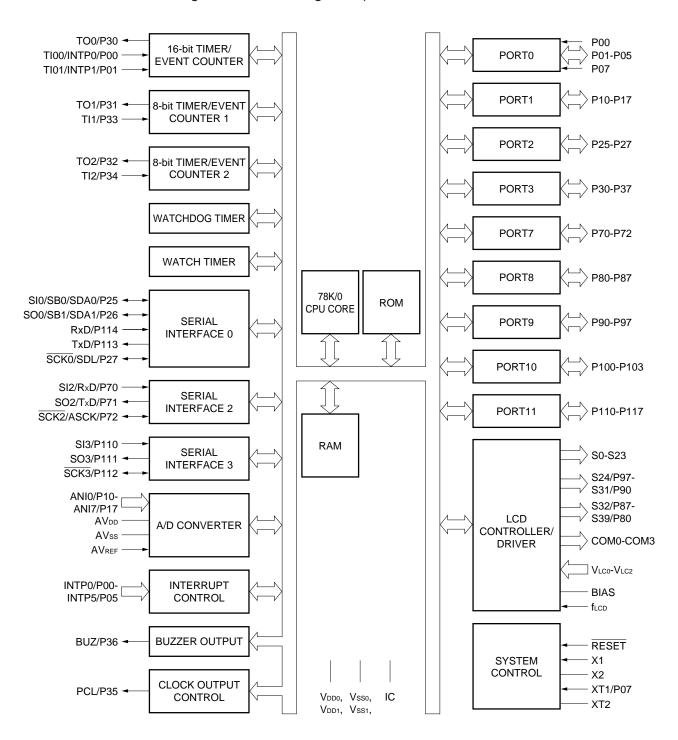

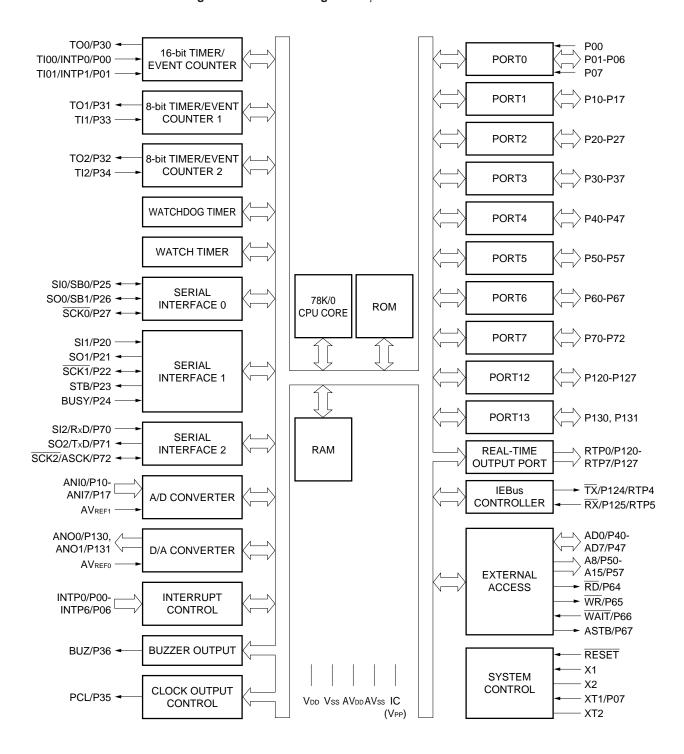

| 1-3.     | Block Diagram of μPD78064 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10   |

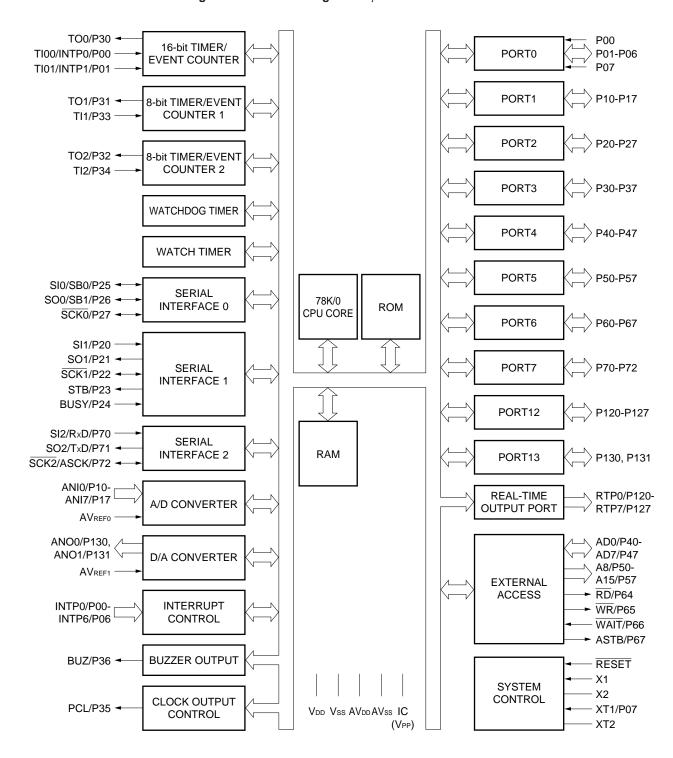

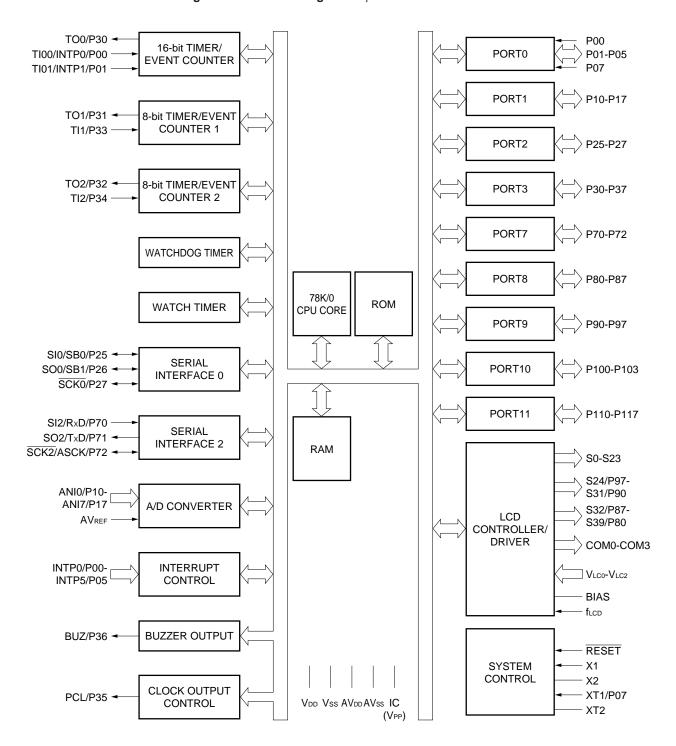

| 1-4.     | Block Diagram of μPD78064Y Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12   |

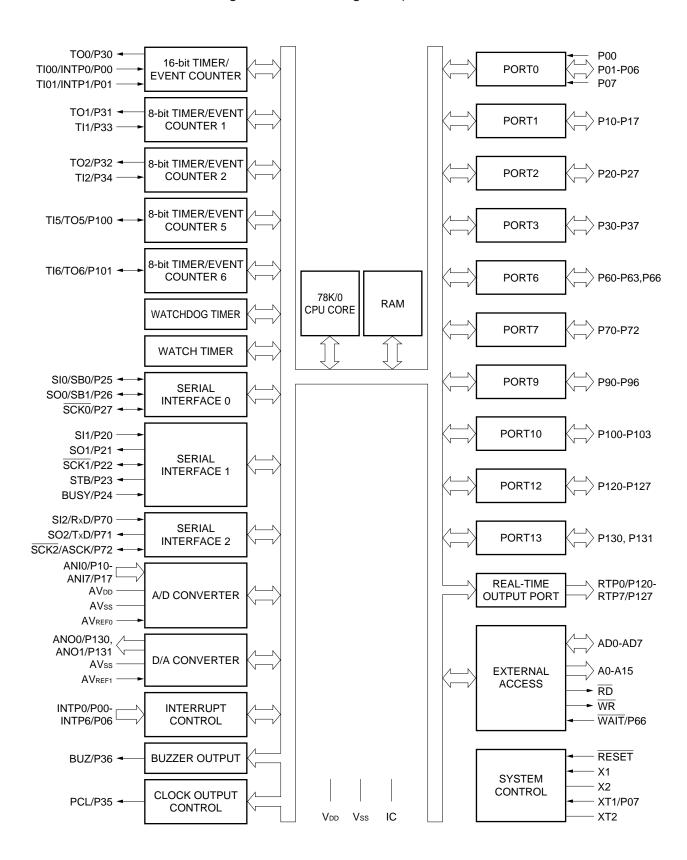

| 1-5.     | Block Diagram of μPD78078 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14   |

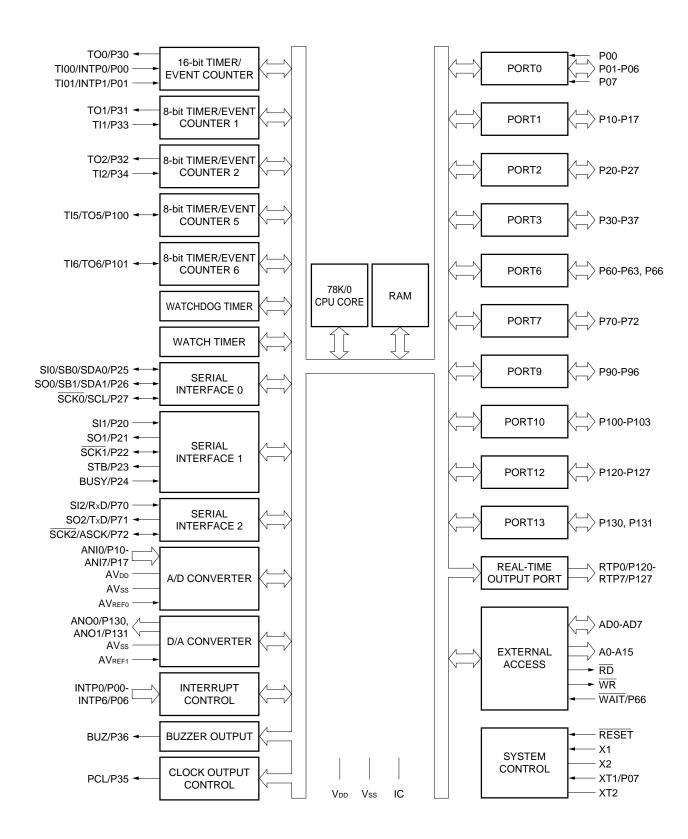

| 1-6.     | Block Diagram of μPD78078Y Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16   |

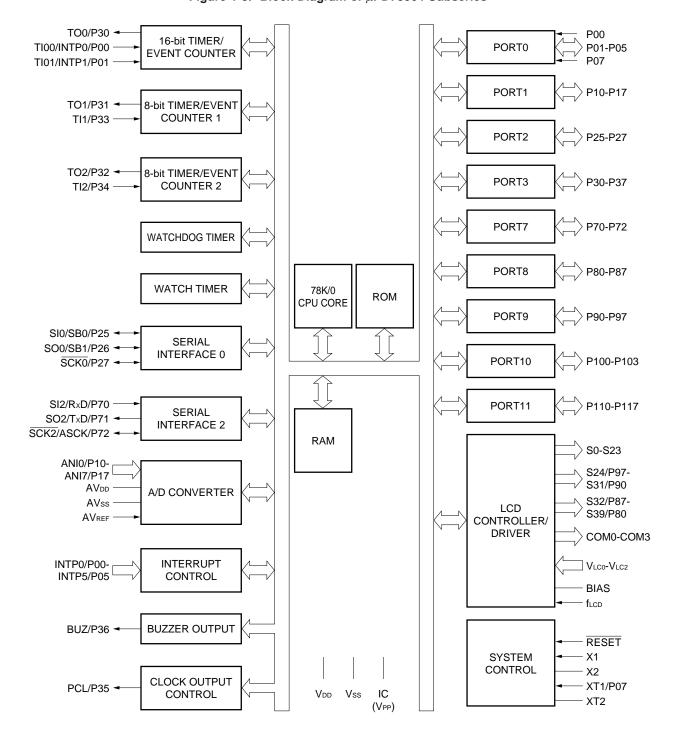

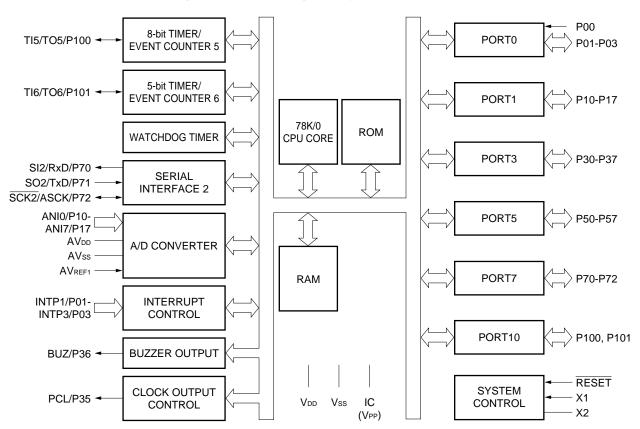

| 1-7.     | Block Diagram of μPD78083 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18   |

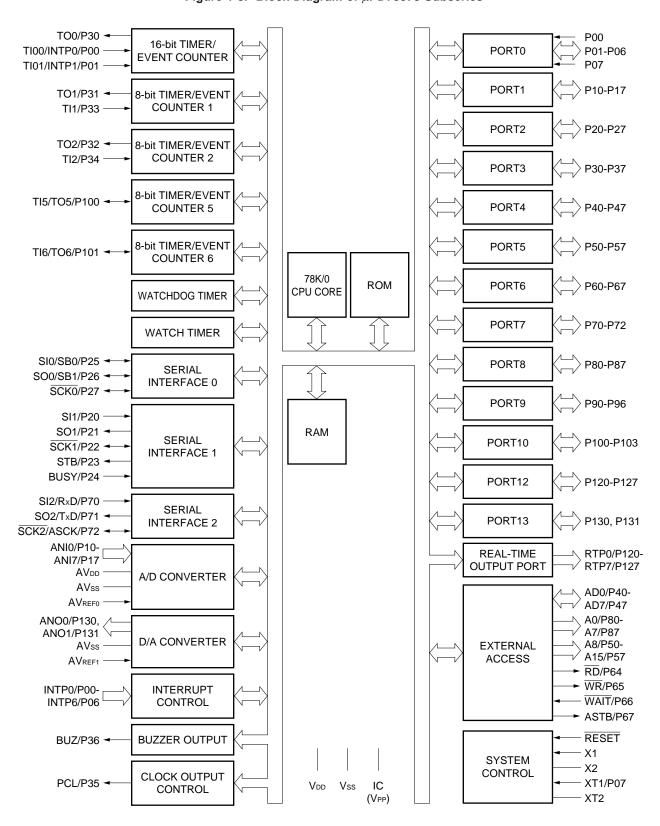

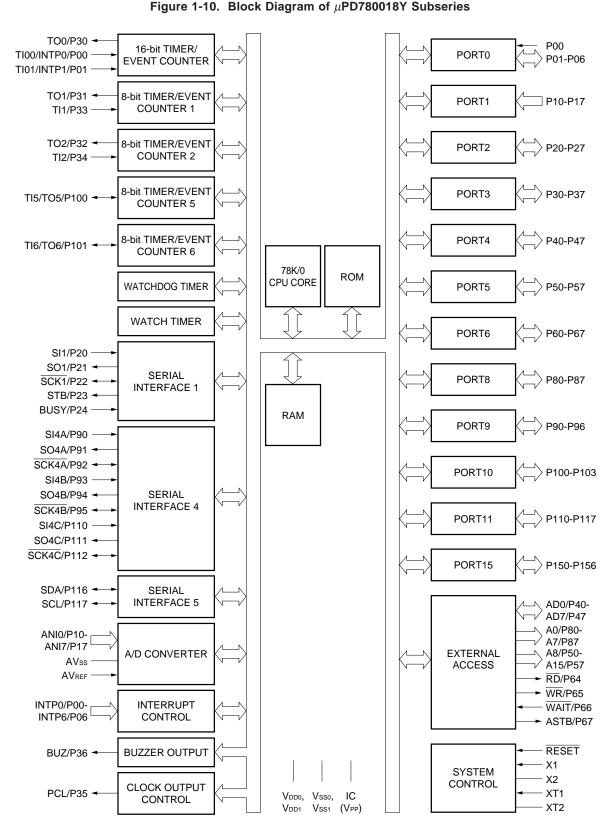

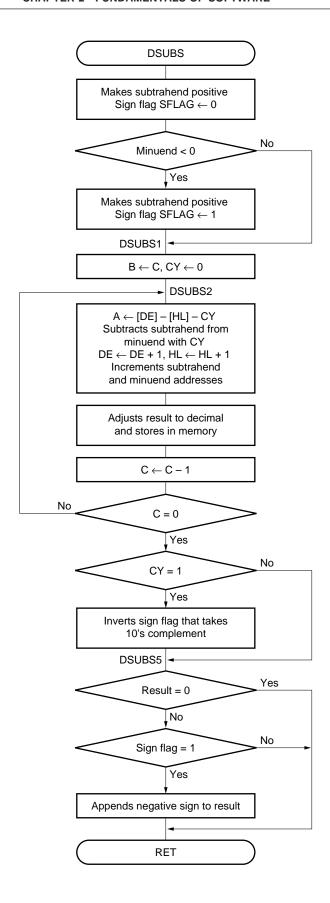

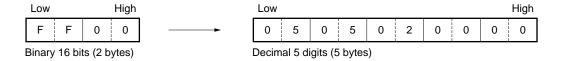

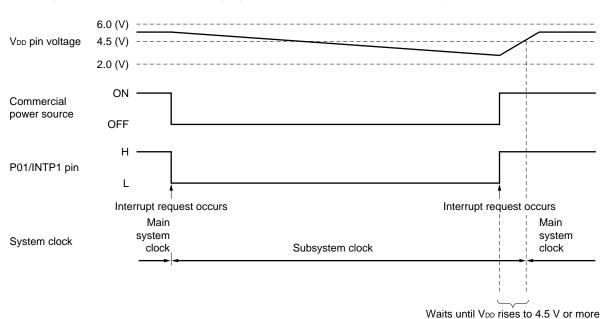

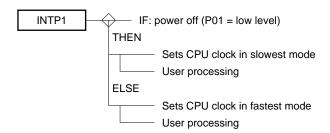

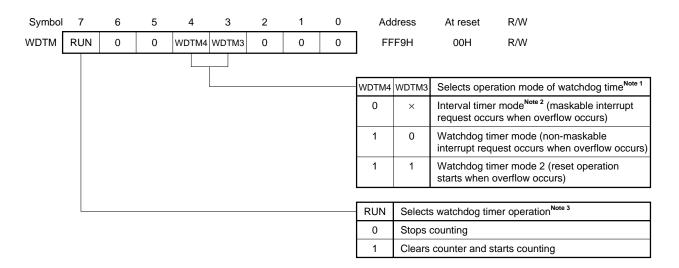

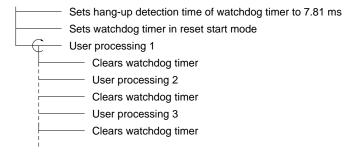

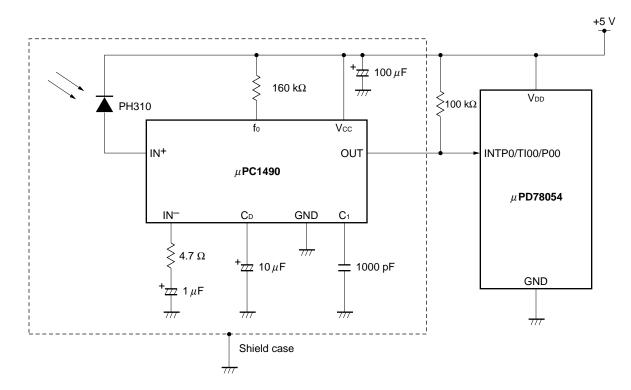

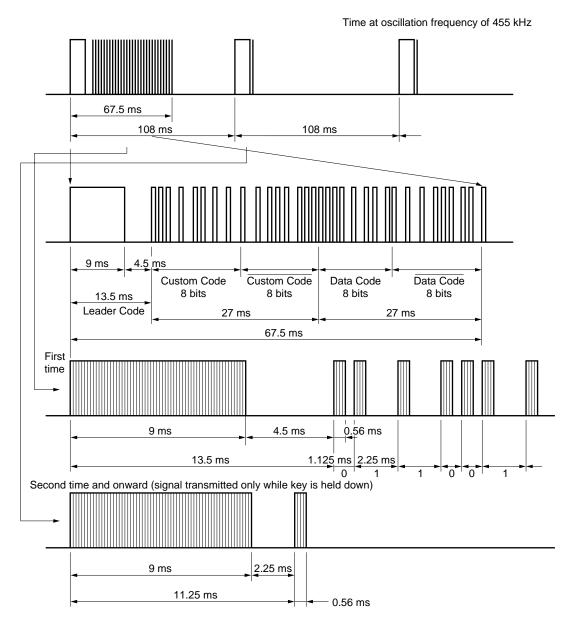

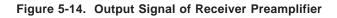

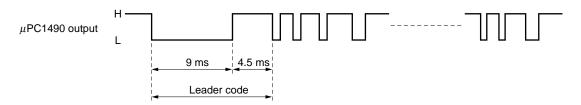

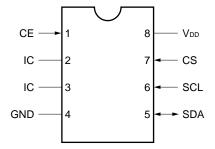

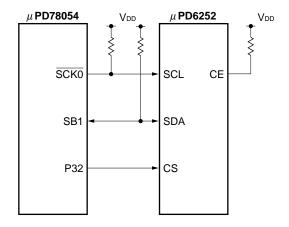

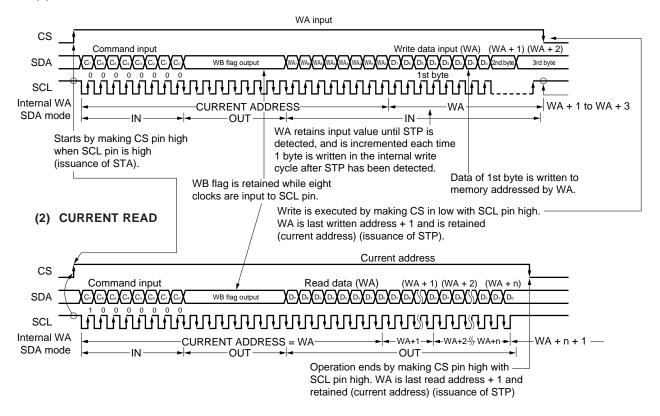

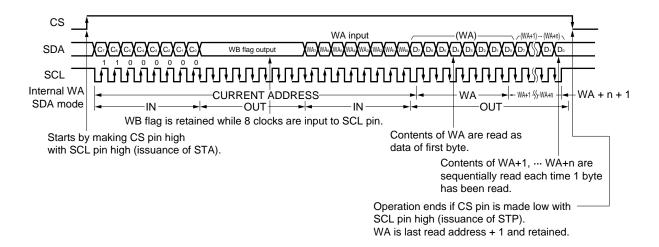

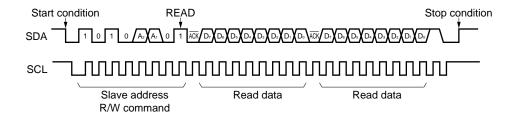

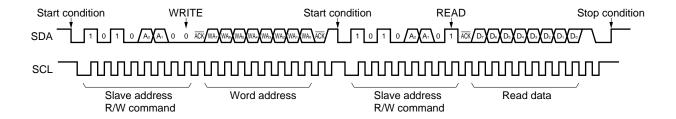

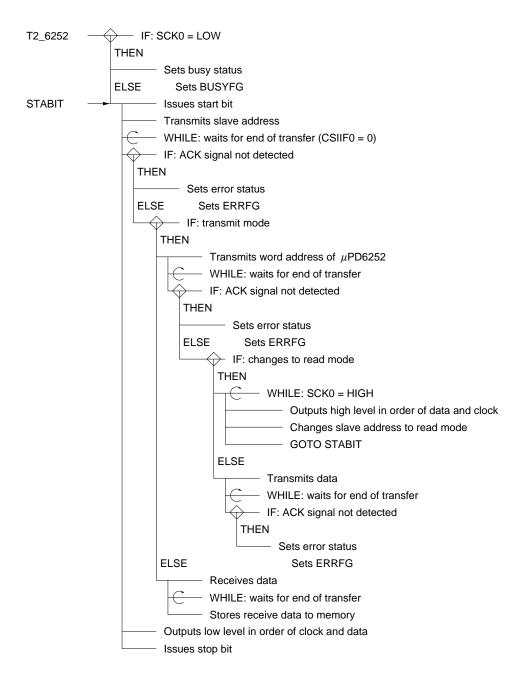

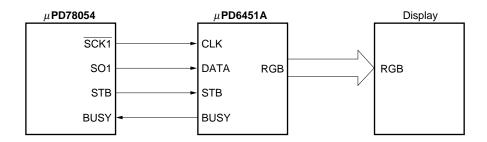

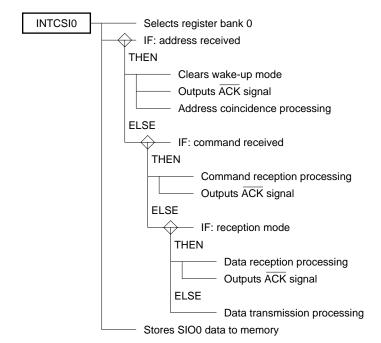

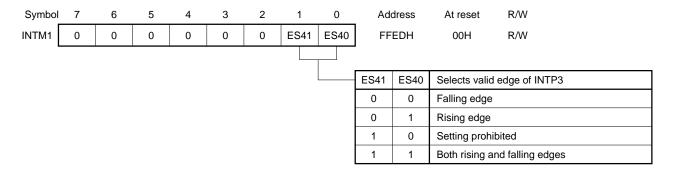

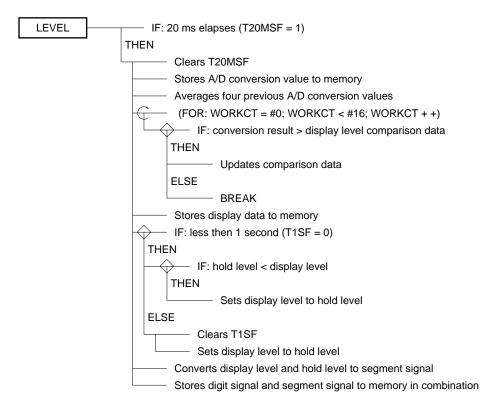

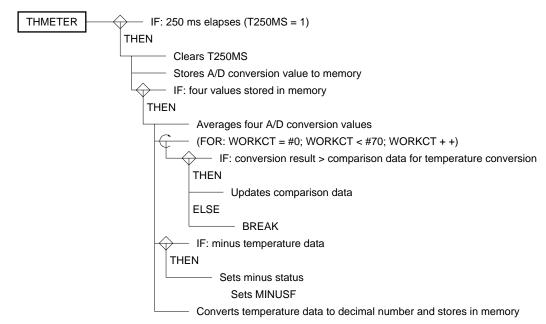

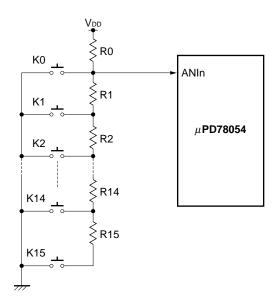

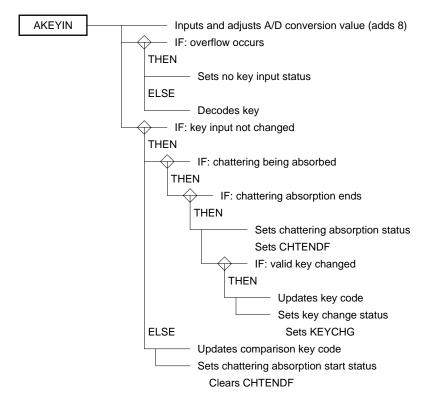

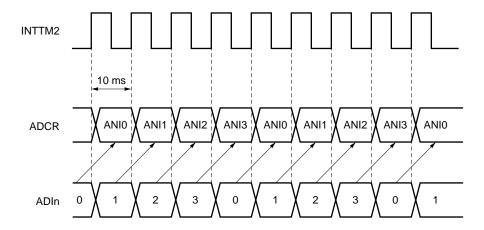

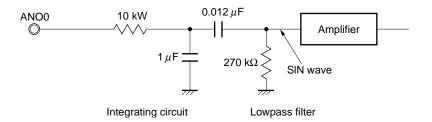

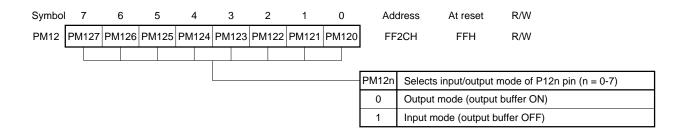

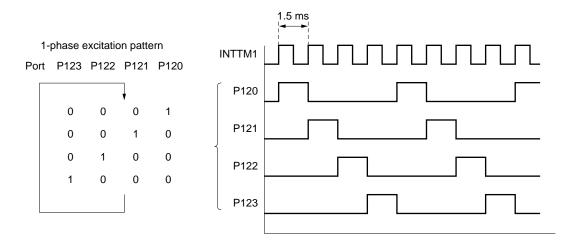

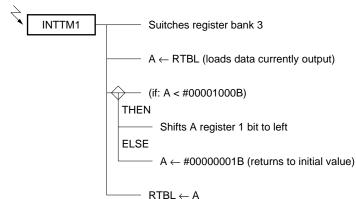

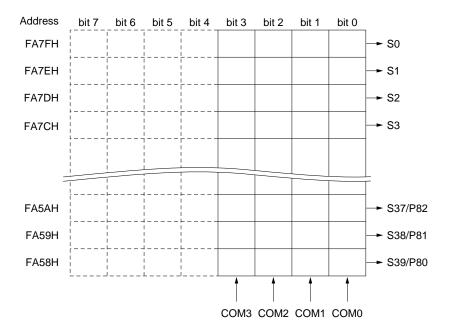

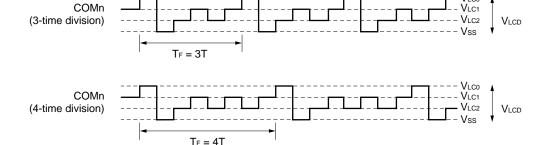

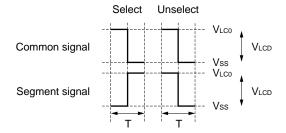

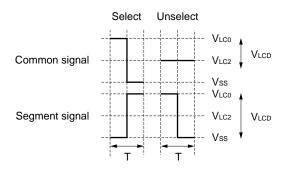

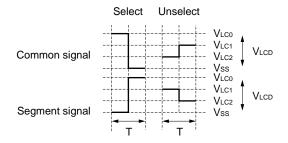

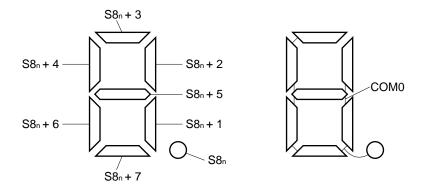

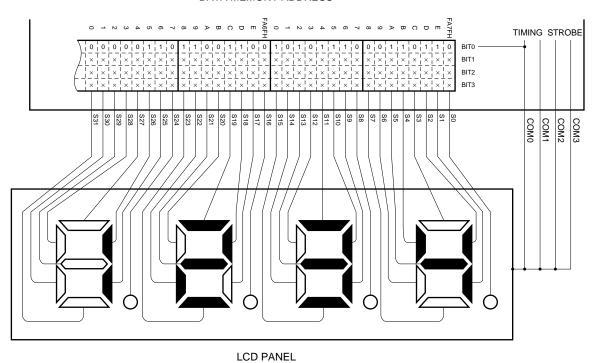

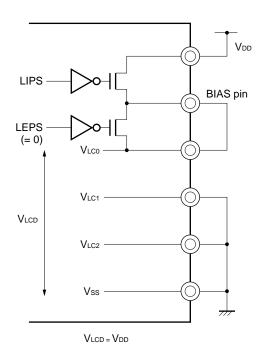

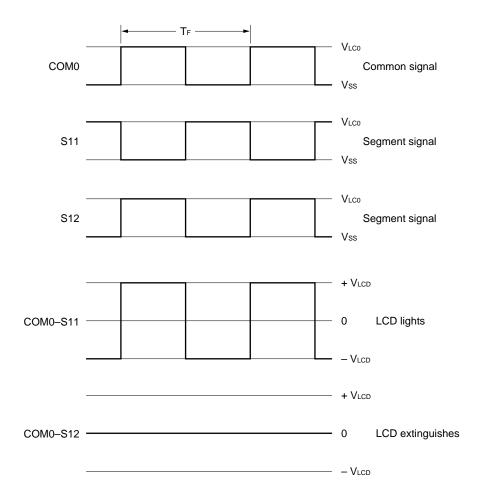

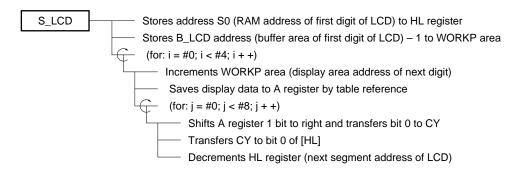

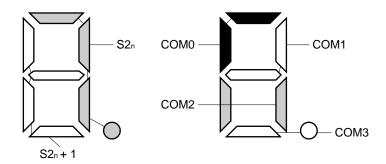

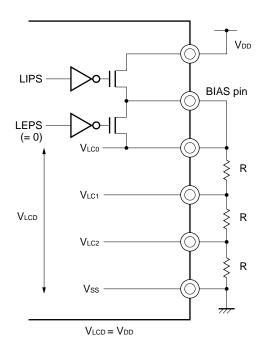

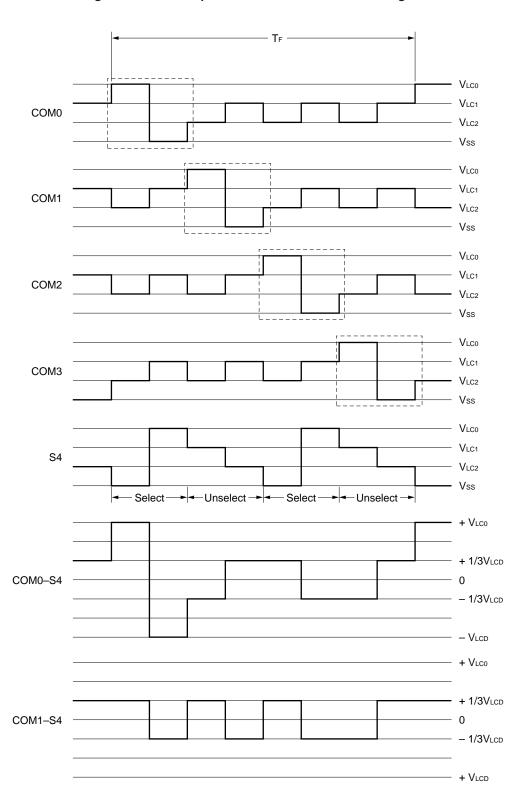

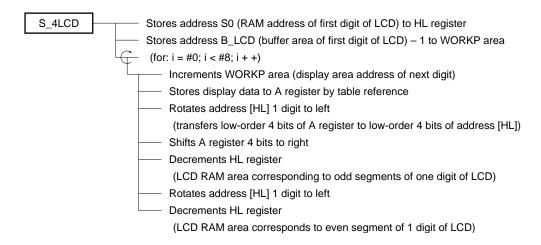

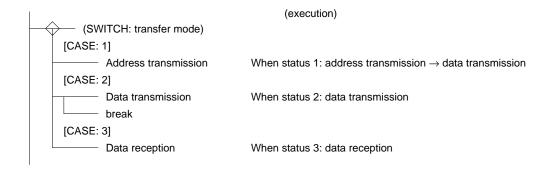

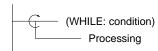

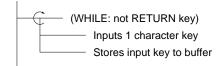

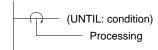

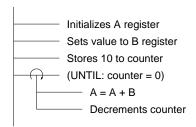

| 1-8.     | Block Diagram of μPD78098 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20   |