### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

32

# SH-3、SH3-DSP、 SDRAMインタフェース編

SH7709S/SH7729R/SH7706/SH7727編 ルネサス32ビットRISCマイクロコンピュータ SuperH<sup>™</sup> RISC engineファミリ/ SH7000シリーズ

#### ご注意

#### 安全設計に関するお願い

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただく ための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが 所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の 使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサス テクノロジ は責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の 記述誤りに起因する損害がお客様に生じた場合には、ルネサス テクノロジはその責 任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサス テクノロジ、ルネサス販売または特約店までご照会ください。

### はじめに

SuperHTM RISC engine マイクロコンピュータは、RISC 方式の CPU により高性能な演算処理を実現します。さらに、システム構成に必要な周辺機能を集積すると同時に、マイコン応用機器に不可欠な低消費電力を実現する、新世代 RISC マイコンです。

SH-3、SH3-DSP SDRAM インタフェース編 アプリケーションノートは、ユーザにてハードウェア 設計にご参考としていただける構成となっています。

本アプリケーションノートでは、SH-3、SH3-DSPマイコンと外部メモリ (SDRAM) とのインタフェース例をまとめています。

なお、本アプリケーションノートに掲載されているタスク例は動作確認をしておりますが、実際に ご使用になる場合には、必ず動作確認の上ご使用ください。

【注】SuperH™は(株)ルネサス テクノロジの商標です。

# 目次

| 第 1 5 | 章 アプ   | リケーションノート使用手引き                       |    |

|-------|--------|--------------------------------------|----|

| 1.1   | SDRAN  | M インタフェース編構成                         | 1  |

| 第25   | 章 SDR  | AM インタフェース例                          |    |

| 2.1   | SH7709 | 9S / SH7729R / SH7706 SDRAM インタフェース例 | 3  |

|       | 2.1.1  | SDRAM 直結方式                           | 3  |

|       | 2.1.2  | パワーオンシーケンス (SH7709S/SH7729R/SH7706)  | 4  |

|       | 2.1.3  | HM5264165F-B60 (1Mword×16bit×4bank)  | 5  |

|       | 2.1.4  | HM5264165F-B60 (1Mword×16bit×4bank)  | 7  |

|       | 2.1.5  | uPD45128163 (2Mword×16bit×4bank)     | 9  |

|       | 2.1.6  | uPD45128163 (2Mword×16bit×4bank)     | 11 |

|       | 2.1.7  | HM5225165B-B6 (4Mword×16bit×4bank)   | 13 |

|       | 2.1.8  | HM5225165B-B6 (4Mword×16bit×4bank)   |    |

|       | 2.1.9  | HM5257165B-A6 (8Mword×16bit×4bank)   | 17 |

| 2.2   | SH7727 | 7 SDRAM インタフェース例                     | 19 |

|       | 2.2.1  | SDRAM 直結方式                           | 19 |

|       | 2.2.2  | パワーオンシーケンス (SH7727)                  | 20 |

|       | 2.2.3  | HM5264165F-B60 (1Mword×16bit×4bank)  | 21 |

|       | 2.2.4  | HM5264165F-B60 (1Mword×16bit×4bank)  | 23 |

|       | 2.2.5  | uPD45128163 (2Mword×16bit×4bank)     | 25 |

|       | 2.2.6  | uPD45128163 (2Mword×16bit×4bank)     | 27 |

|       | 2.2.7  | HM5225165B-B6 (4Mword×16bit×4bank)   |    |

|       | 2.2.8  | HM5225165B-B6 (4Mword×16bit×4bank)   | 31 |

|       | 2.2.9  | HM5257165B-A6 (8Mword×16bit×4bank)   | 33 |

### 1. アプリケーションノート使用手引き

### 1.1 SDRAM インタフェース編構成

SDRAM インタフェース編は下記に示す構成で、SDRAM とのインタフェース方法について説明しています。

#### SDRAM インタフェース編

- バスステートコントローラ (BSC) の設定 SDRAMを接続する場合のBSCの設定内容を示します。

- 接続図 SDRAMとインタフェースする接続図を示します。

本アプリケーションノートでは下記製品と SDRAM とのインタフェースを製品別に示しています。

| 製品名                        | SDRAM*                                   |

|----------------------------|------------------------------------------|

| SH7709S / SH7729R / SH7706 | HM5264165F-B60 (1Mword x 16bit x 4bank)  |

|                            | uPD45128163-A10 (2Mword x 16bit x 4bank) |

|                            | HM5225165B-B6 (4Mword x 16bit x 4bank)   |

|                            | HM5257165B-A6 (8Mword x 16bit x 4bank)   |

| SH7727                     | HM5264165F-B60 (1Mword x 16bit x 4bank)  |

|                            | uPD45128163-A10 (2Mword x 16bit x 4bank) |

|                            | HM5225165B-B6 (4Mword x 16bit x 4bank)   |

|                            | HM5257165B-A6 (8Mword x 16bit x 4bank)   |

【注】 \* エルピーダメモリ株式会社の製品です。

### 2. SDRAM インタフェース例

### 2.1 SH7709S / SH7729R / SH7706 SDRAM インタフェース例

#### 2.1.1 SDRAM 直結方式

シンクロナス DRAM は  $\overline{\text{CS}}$  信号によって選択できるため、 $\overline{\text{RAS}}$  等の制御信号を共通に使用して物理空間のエリア 2 とエリア 3 に接続が可能です。BCR1 メモリタイプビット(DRAMTP2~0)を 010 に設定すると、エリア 2 が通常メモリ空間、エリア 3 がシンクロナス DRAM 空間になり、011 に設定するとエリア 2、エリア 3 がともにシンクロナス DRAM 空間となります。

本 LSI ではシンクロナス DRAM の動作モードとして、バースト長 1 のバーストリード/シングルライトのモードをサポートしています。データのバス幅は 16、32 ビットから選択できます。キャッシュのフィル/コピーバックサイクルでは 16 バイトのバースト転送が行われ、ライトスルー領域の書き込みや、キャッシュ非対象領域の読み出し・書き込みでは 1 回のみアクセスが行われます。

シンクロナス DRAM を直結するための制御信号は  $\overline{RAS3L}(\overline{RASL})$ 、 $\overline{RAS3U}(\overline{RASU})$ 、 $\overline{CASL}$ 、 $\overline{CASU}$ 、 $\overline{RD/WR}$ 、 $\overline{CS2}$  または  $\overline{CS3}$ 、 $\overline{DQMUU}$ 、 $\overline{DQMUL}$ 、 $\overline{DQMLU}$  、 $\overline{DQMLL}$  および CKE 信号です。  $\overline{CS2}$  または  $\overline{CS3}$  を除く信号は各エリア共通であり、CKE を除く信号は  $\overline{CS2}$  または  $\overline{CS3}$  がアサートされたときのみ有効となり取り込まれます。したがって、複数のエリアにシンクロナス  $\overline{DRAM}$  を並列に接続することができます。CKE はセルフリフレッシュを行うときのみネゲート(L レベルに)され、それ以外は常にアサート(H レベルに)されています。

ただし、 $\overline{RAS3U}(\overline{RASU})$ 、 $\overline{RAS3U}(\overline{RASU})$ 、 $\overline{CASU}$  は、アドレスが各エリアの上位 32M バイトか下位 32M バイトかによって、どちらを出力するか決まります。上位 32M バイト(エリア 2: H'0A000000~H'0BFFFFFF、エリア 3:H'0E000000~H'0FFFFFF)の場合、 $\overline{RAS3U}(\overline{RASU})$ 、 $\overline{CASU}$  が出力されます。下位 32M バイト(エリア 2:H'08000000~H'09FFFFF、エリア 3:H'0C000000~H'0DFFFFF)の場合、 $\overline{RAS3L}$ 、 $\overline{CASL}$  が出力されます。リフレッシュサイクルおよびモードレジスタ書き込みサイクルでは、 $\overline{RAS3L}(\overline{RASL})$ 、 $\overline{RAS3U}(\overline{RASU})$ または $\overline{CASU}$  がともに出力されます。

RAS3L(RASL)、RAS3U(RASU)、CASL、CASU、RD/WR および特定のアドレス信号によって、シンクロナス DRAM に対するコマンドが指定されます。コマンドには、NOP、オートリフレッシュ(REF)、セルフリフレッシュ(SELF)、全バンクプリチャージ(PALL)、ロウアドレスストローブ・バンクアクティブ(ACTV)、リード(READ)、プリチャージ付きリード(READA)、ライト(WRIT)、プリチャージ付きライト(WRITA)、モードレジスタ書き込み(MRS)があります。

バイトの指定は DQMUU、DQMUL、DQMLU、DQMLL によって行われます。該当する DQM が L のバイトに対して読み出し書き込みが行われます。ビックエンディアンモードの場合、DQMUU は 4n 番地のアクセスを、DQMLL は 4n+3 番地のアクセスを指定します。またリトルエンディアンモードの場合、DQMUU は 4n+3 番地のアクセスを、DQMLL は 4n 番地のアクセスを指定します。

#### 2.1.2 パワーオンシーケンス (SH7709S / SH7729R / SH7706)

シンクロナス DRAM を使用するためには、パワーオン後、まずモードの設定を行う必要があります。シンクロナス DRAM の初期化を正しく行うためには、まず最初にバスステートコントローラのレジスタを設定した後、シンクロナス DRAM のモードレジスタに対する書き込みを行わなければなりません。シンクロナス DRAM のモードレジスタの設定は  $\overline{\text{RAS}}$ 、 $\overline{\text{CAS}}$ 、 $\overline{\text{RD/WR}}$  信号の組み合わせで、その時点のアドレス信号の値が取り込まれます。バスステートコントローラは、設定したい値を Xとすると、エリア 2 のシンクロナス DRAM に対しては HTFFFFD000+X 番地に、またエリア 3 のシンクロナス DRAM に対しては HTFFFE000+X に書き込みを行うことによって、値 X がシンクロナス DRAM のモードレジスタに書き込まれるように動作します。この際データは無視されますが、モードの書き込みはバイトサイズで行います。本 LSI でサポートしているバーストリード/シングルライト、CAS レイテンシ 1 から 3、ラップタイプ=シーケンシャル、バースト長 1 を設定するには以下のアドレスにバイトサイズで任意のデータを書き込みます。

|                |                            | エリア 2               | エリア 3               |

|----------------|----------------------------|---------------------|---------------------|

| 32 ビット幅        | CAS レイテンシ 1                | H'FFFFD840          | H'FFFFE840          |

| 接続時            | CAS レイテンシ 2                | H'FFFFD880          | H'FFFFE880          |

|                | CAS レイテンシ 3                | H'FFFFD8C0          | H'FFFFE8C0          |

|                |                            |                     |                     |

|                |                            | エリア 2               | エリア 3               |

| 16 ビット幅        | CAS レイテンシ 1                | エリア 2<br>H'FFFFD420 | エリア 3<br>H'FFFFE420 |

| 16 ビット幅<br>接続時 | CAS レイテンシ 1<br>CAS レイテンシ 2 | • • -               | * * -               |

HTFFFFD000+X もしくは HTFFFE000+X 番地への書き込みによって、まず、全バンクプリチャージコマンド(PALL)が TRp1 サイクルに発行され、それに続く TMw1 サイクルにモードレジスタ書き込みコマンドが発行されます。

モードレジスタ書き込みコマンド発行時のアドレス信号は、以下のようになります。

| 32 ビット幅 | A15~A9 | 0000100(バーストリード&シングルライト) |

|---------|--------|--------------------------|

| 接続時     | A8~A6  | CAS レイテンシ                |

|         | A5     | 0(バーストタイプ=シーケンシャル)       |

|         | A4~A2  | 000 (バースト長 1)            |

| 16 ビット幅 | A14~A8 | 0000100(バーストリード&シングルライト) |

| 接続時     | A7~A5  | CAS レイテンシ                |

|         | A4     | 0(バーストタイプ=シーケンシャル)       |

|         | A3~A1  | 000 (バースト長 1)            |

|         |        |                          |

モードレジスタの設定に先立って、シンクロナス DRAM の要求する電源投入後  $100 \mu s$  のアイドル時間(メモリメーカによって異なる)を保証しなければなりません。リセット信号のパルス幅がこのアイドル時間より長い場合には、直ちにモードレジスタの設定を行っても問題はありません。ダミーのオートリフレッシュサイクルをメーカの規定する回数(通常 8 回)以上実行する必要があります。これはオートリフレッシュの設定を行った後、種々の初期化を行っているうちに自然に実現されるのが普通ですが、より確実に行うためには、このダミーサイクルを実行する間だけリフレッシュ要求の発生する間隔を短く設定しておく方法があります。単なるリードまたはライトアクセスではオートリフレッシュに使用するシンクロナス DRAM 内部のアドレスカウンタが初期化されないため、必ずオートリフレッシュサイクルでなければなりません。

#### 2.1.3 HM5264165F-B60 (1Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 16 ビットバス幅で SDRAM (HM5264165F-B60)  $\times$  2 個 を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.1 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                            |                             | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                |

|-------------------------------|-----------------------------|--------|--------|---------------|-------------|--------------------|

| バスコントロールレジ                    | ジスタ 1                       | BCR1   | H'0000 | H'FFFFFF60    | 16          | H'0008             |

| バスコントロールレジスタ 2                |                             | BCR2   | H'3FF0 | H'FFFFFF62    | 16          | H'3FB0             |

| ウェイトステートコントロール                |                             | WCR1   | H'3FF3 | H'FFFFFF64    | 16          | H'3FF3             |

| レジスタ 1                        |                             |        |        |               |             |                    |

| ウェイトステートコン                    | ノトロール                       | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF             |

| レジスタ 2                        |                             |        |        |               |             |                    |

| 個別メモリコントロ-                    | -ルレジスタ                      | MCR    | H'0000 | H'FFFFFF68    | 16          | H'5224             |

| PCMCIA コントロールレジスタ             |                             | PCR    | H'0000 | H'FFFFF6C     | 16          | 設定不要               |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |                             | RTCSR  | H'0000 | H'FFFFF6E     | 16          | H'A508             |

| リフレッシュタイマカ                    | カウンタ                        | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500             |

| リフレッシュタイム:<br>カウンタ            | コンスタント                      | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A5F8             |

| リフレッシュカウン                     | トレジスタ                       | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要               |

| シンクロナス                        | エリア2用                       | SDMR   | _      | H'FFFFD000    | 8           | 設定不要               |

| DRAM モード                      |                             |        |        | to H'FFFFDFFF |             |                    |

| レジスタ                          | エリア3用                       |        |        | H'FFFFE000    |             | H'FFFFE440 に任      |

|                               |                             |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>込みます。* |

| MCS0 コントロールし                  | <b>ノジスタ</b>                 | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要               |

| MCS1 コントロールし                  | <b>ノジスタ</b>                 | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要               |

| MCS2 コントロールし                  | <b>レジスタ</b>                 | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要               |

| MCS3 コントロールし                  | <b>レジスタ</b>                 | MCSCR3 | H'0000 | H'FFFFF56     | 16          | 設定不要               |

| MCS4 コントロールし                  | <b>ノジスタ</b>                 | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要               |

| MCS5 コントロールし                  | <b>ノジスタ</b>                 | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要               |

| MCS6 コントロールし                  | <b>ノジスタ</b>                 | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要               |

| MCS7 コントロールし                  | <u></u><br><sub>ノ</sub> ジスタ | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要               |

表 2.1 BSC の設定(HM5264165F-B60)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.1** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0100 に設定してください。

図 2.1 ブロックダイアグラム

#### 2.1.4 HM5264165F-B60 (1Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 32 ビットバス幅で SDRAM(HM5264165F-B60)×2 個を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.2 に示します。

なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                            |                             | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                |

|-------------------------------|-----------------------------|--------|--------|---------------|-------------|--------------------|

| バスコントロールレジ                    | ジスタ 1                       | BCR1   | H'0000 | H'FFFFF60     | 16          | H'0008             |

| バスコントロールレジ                    | ジスタ 2                       | BCR2   | H'3FF0 | H'FFFFFF62    | 16          | H'3FF0             |

| ウェイトステートコン                    | ノトロール                       | WCR1   | H'3FF3 | H'FFFFFF64    | 16          | H'3FF3             |

| レジスタ 1                        |                             |        |        |               |             |                    |

| ウェイトステートコン                    | ノトロール                       | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF             |

| レジスタ 2                        |                             |        |        |               |             |                    |

| 個別メモリコントロ-                    | -ルレジスタ                      | MCR    | H'0000 | H'FFFFFF68    | 16          | H'5224             |

| DRAM コントロール                   | レジスタ                        | DCR    | H'0000 | H'FFFFFF6A    | 16          | 設定不要               |

| PCMCIA コントロールレジスタ             |                             | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要               |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |                             | RTCSR  | H'0000 | H'FFFFFF6E    | 16          | H'A508             |

| リフレッシュタイマカ                    | カウンタ                        | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500             |

| リフレッシュタイム:<br>カウンタ            | コンスタント                      | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A5F8             |

| リフレッシュカウン                     | トレジスタ                       | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要               |

| バスコントロールレジ                    | ジスタ 3                       | BCR3   | H'0000 | H'FFFFFF7E    | 16          | 設定不要               |

| シンクロナス                        | エリア 2 用                     | SDMR   | _      | H'FFFFD000    | 8           | 設定不要               |

| DRAM モード                      |                             |        |        | to H'FFFFDFFF |             |                    |

| レジスタ                          | エリア 3 用                     |        |        | H'FFFFE000    |             | H'FFFFE880 に任      |

|                               |                             |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>込みます。* |

| MCS0 コントロールし                  | <b>ノジスタ</b>                 | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要               |

| MCS1 コントロールし                  | <b>ノジスタ</b>                 | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要               |

| MCS2 コントロールし                  | <b>レジスタ</b>                 | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要               |

| MCS3 コントロールし                  | <b>レジスタ</b>                 | MCSCR3 | H'0000 | H'FFFFF56     | 16          | 設定不要               |

| MCS4 コントロールし                  | <b>ノジスタ</b>                 | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要               |

| MCS5 コントロールし                  | <b>ノジスタ</b>                 | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要               |

| MCS6 コントロールし                  | <b>ノジスタ</b>                 | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要               |

| MCS7 コントロールし                  | <u></u><br><sub>ノ</sub> ジスタ | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要               |

表 2.2 BSC の設定 (HM5264165TT-B60)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

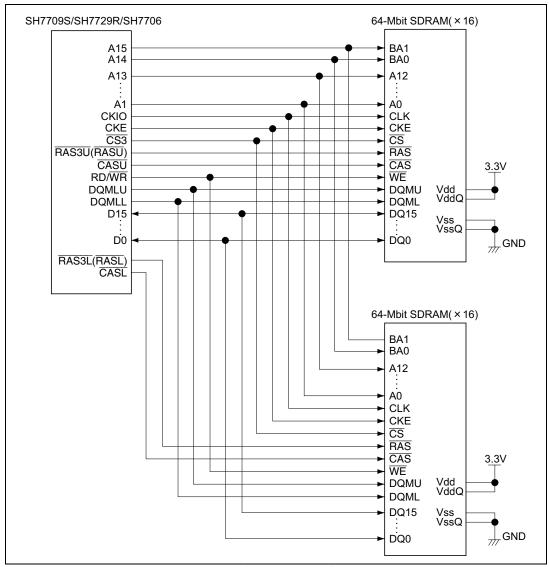

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.2** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0100 に設定してください。

図 2.2 ブロックダイアグラム

#### 2.1.5 uPD45128163 (2Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 16 ビットバス幅で SDRAM(uPD45128163)×2 個を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.3 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=3 の条件で接続します。

| 名称                            |                  | 略称     | 初期値        | アドレス          | アクセス<br>サイズ | 設定値                |

|-------------------------------|------------------|--------|------------|---------------|-------------|--------------------|

| バスコントロールレジ                    | ジスタ 1            | BCR1   | H'0000     | H'FFFFFF60    | 16          | H'0008             |

| バスコントロールレシ                    | ブスタ 2            | BCR2   | H'3FF0     | H'FFFFFF62    | 16          | H'3FB0             |

| ウェイトステートコン                    | ノトロール            | WCR1   | H'3FF3     | H'FFFFFF64    | 16          | H'3FF3             |

| レジスタ 1                        |                  |        |            |               |             |                    |

| ウェイトステートコン                    | ノトロール            | WCR2   | H'FFFF     | H'FFFFFF66    | 16          | H'FFDF             |

| レジスタ 2                        |                  |        |            |               |             |                    |

| 個別メモリコントロー                    | MCR              | H'0000 | H'FFFFFF68 | 16            | H'522C      |                    |

| PCMCIA コントロールレジスタ             |                  | PCR    | H'0000     | H'FFFFFF6C    | 16          | 設定不要               |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |                  | RTCSR  | H'0000     | H'FFFFFF6E    | 16          | H'A508             |

| リフレッシュタイマカ                    | ウンタ              | RTCNT  | H'0000     | H'FFFFFF70    | 16          | H'A500             |

| リフレッシュタイム=<br>カウンタ            | コンスタント           | RTCOR  | H'0000     | H'FFFFFF72    | 16          | H'A5F8             |

| リフレッシュカウント                    | <b>・</b> レジスタ    | RFCR   | H'0000     | H'FFFFFF74    | 16          | 設定不要               |

| シンクロナス                        | エリア2用            | SDMR   | _          | H'FFFFD000    | 8           | 設定不要               |

| DRAM モード                      |                  |        |            | to H'FFFFDFFF |             |                    |

| レジスタ                          | エリア3用            |        |            | H'FFFFE000    |             | H'FFFFE440 に任      |

|                               |                  |        |            | to H'FFFFEFFF |             | 意のデータを書き<br>込みます。* |

| MCS0 コントロールし                  | <b>ノジスタ</b>      | MCSCR0 | H'0000     | H'FFFFFF50    | 16          | 設定不要               |

| MCS1 コントロールし                  | <b>レジスタ</b>      | MCSCR1 | H'0000     | H'FFFFFF52    | 16          | 設定不要               |

| MCS2 コントロールし                  | <b>ノジスタ</b>      | MCSCR2 | H'0000     | H'FFFFFF54    | 16          | 設定不要               |

| MCS3 コントロールし                  | <b>ノジスタ</b>      | MCSCR3 | H'0000     | H'FFFFFF56    | 16          | 設定不要               |

| MCS4 コントロールし                  | <b>ノジスタ</b>      | MCSCR4 | H'0000     | H'FFFFFF58    | 16          | 設定不要               |

| MCS5 コントロールし                  | <sub>ノジ</sub> スタ | MCSCR5 | H'0000     | H'FFFFFF5A    | 16          | 設定不要               |

| MCS6 コントロールし                  | <b>ノジスタ</b>      | MCSCR6 | H'0000     | H'FFFFF5C     | 16          | 設定不要               |

| MCS7 コントロールし                  | <b>ノジスタ</b>      | MCSCR7 | H'0000     | H'FFFFFF5E    | 16          | 設定不要               |

表 2.3 BSC の設定 (uPD45128163)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

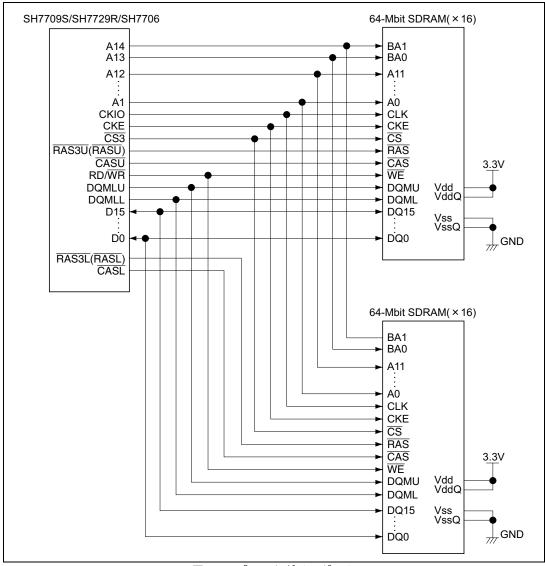

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.3** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0101 に設定してください。

図 2.3 ブロックダイアグラム

#### 2.1.6 uPD45128163 (2Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S/SH7729R/SH7706 のエリア 3 に 32 ビットバス幅で SDRAM(uPD45128163)×2 個を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.4 に示します。

なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=3 の条件で接続します。

|                               | 表       | 2.4 BSC | の設定(い  | iPD45128163)  |             |                |

|-------------------------------|---------|---------|--------|---------------|-------------|----------------|

| 名称                            |         | 略称      | 初期値    | アドレス          | アクセス<br>サイズ | 設定値            |

| バスコントロールレジ                    | ジスタ 1   | BCR1    | H'0000 | H'FFFFF60     | 16          | H'0008         |

| バスコントロールレジ                    | ジスタ 2   | BCR2    | H'3FF0 | H'FFFFFF62    | 16          | H'3FF0         |

| ウェイトステートコン                    | ノトロール   | WCR1    | H'3FF3 | H'FFFFF64     | 16          | H'3FF3         |

| レジスタ 1                        |         |         |        |               |             |                |

| ウェイトステートコン                    | ノトロール   | WCR2    | H'FFFF | H'FFFFFF66    | 16          | H'FFDF         |

| レジスタ 2                        |         |         |        |               |             |                |

| 個別メモリコントロ-                    | -ルレジスタ  | MCR     | H'0000 | H'FFFFFF68    | 16          | H'522C         |

| DRAM コントロール                   | レジスタ    | DCR     | H'0000 | H'FFFFFF6A    | 16          | 設定不要           |

| PCMCIA コントロールレジスタ             |         | PCR     | H'0000 | H'FFFFFF6C    | 16          | 設定不要           |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |         | RTCSR   | H'0000 | H'FFFFF6E     | 16          | H'A508         |

| リフレッシュタイマカ                    | カウンタ    | RTCNT   | H'0000 | H'FFFFFF70    | 16          | H'A500         |

| リフレッシュタイム:<br>カウンタ            | コンスタント  | RTCOR   | H'0000 | H'FFFFFF72    | 16          | H'A5F8         |

| リフレッシュカウン                     | トレジスタ   | RFCR    | H'0000 | H'FFFFFF74    | 16          | 設定不要           |

| バスコントロールレジ                    | ジスタ 3   | BSC3    | H'0000 | H'FFFFFF7E    | 16          | 設定不要           |

| シンクロナス                        | エリア2用   | SDMR    | _      | H'FFFFD000    | 8           | 設定不要           |

| DRAM モード                      |         |         |        | to H'FFFFDFFF |             |                |

| レジスタ                          | エリア 3 用 |         |        | H'FFFFE000    |             | H'FFFFE880 に任  |

|                               |         |         |        | to H'FFFFEFFF |             | 意のデータを書き       |

| MCS0 コントロールし                  | ジフタ     | MCSCR0  | H'0000 | H'FFFFFF50    | 16          | 込みます。*<br>設定不要 |

| MCS0 コントロールI                  |         | MCSCR0  | H'0000 | H'FFFFFF52    | 16          |                |

|                               |         |         |        |               |             | 設定不要           |

| MCS2 コントロールL                  |         | MCSCR2  | H'0000 | H'FFFFFF54    | 16<br>16    | 設定不要           |

| MCS3 コントロールI                  |         | MCSCR3  | H'0000 | H'FFFFFF56    |             | 設定不要           |

| MCS4 コントロールし                  |         | MCSCR4  | H'0000 | H'FFFFFF58    | 16          | 設定不要           |

| MCS5 コントロールし                  |         | MCSCR5  | H'0000 | H'FFFFFF5A    | 16          | 設定不要           |

| MCS6 コントロールし                  |         | MCSCR6  | H'0000 | H'FFFFFF5C    | 16          | 設定不要           |

| MCS7 コントロールし                  | ノンスタ    | MCSCR7  | H'0000 | H'FFFFFF5E    | 16          | 設定不要           |

表 2.4 BSC の設定 (uPD45128163)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

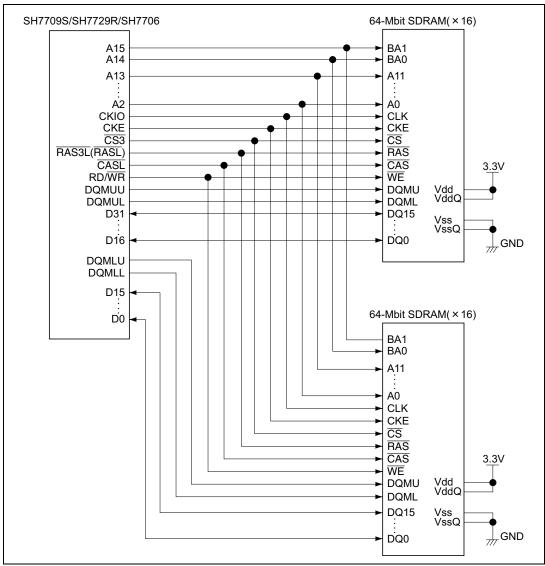

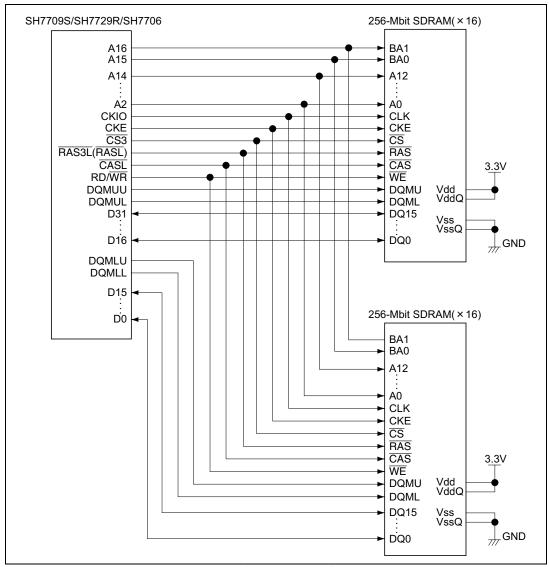

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.4** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0101 に設定してください。

図 2.4 ブロックダイアグラム

#### 2.1.7 HM5225165B-B6 (4Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 16 ビットバス幅で SDRAM(HM5225165B-B6)  $\times$  2 個を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.5 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                            | 13, 2       | 略称     | 初期値    | アドレス          | アクセス | 設定値                |

|-------------------------------|-------------|--------|--------|---------------|------|--------------------|

|                               |             |        |        |               | サイズ  |                    |

| バスコントロールレ                     | ジスタ 1       | BCR1   | H'0000 | H'FFFFFF60    | 16   | H'0008             |

| バスコントロールレ                     | ジスタ 2       | BCR2   | H'3FF0 | H'FFFFFF62    | 16   | H'3FB0             |

| ウェイトステートコン                    | ントロール       | WCR1   | H'3FF3 | H'FFFFFF64    | 16   | H'3FF3             |

| レジスタ 1                        |             |        |        |               |      |                    |

| ウェイトステートコン                    | ントロール       | WCR2   | H'FFFF | H'FFFFFF66    | 16   | H'FFDF             |

| レジスタ 2                        |             |        |        |               |      |                    |

| 個別メモリコントロ-                    | ールレジスタ      | MCR    | H'0000 | H'FFFFFF68    | 16   | H'526C             |

| PCMCIA コントロールレジスタ             |             | PCR    | H'0000 | H'FFFFFF6C    | 16   | 設定不要               |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |             | RTCSR  | H'0000 | H'FFFFFF6E    | 16   | H'A508             |

| リフレッシュタイマ                     |             | RTCNT  | H'0000 | H'FFFFFF70    | 16   | H'A500             |

| リフレッシュタイム                     |             | RTCOR  | H'0000 | H'FFFFFF72    | 16   | H'A57C             |

| カウンタ                          | 12/1/21     | KICOK  | 110000 | 11111111111   | 10   | 117370             |

| リフレッシュカウン                     | トレジスタ       | RFCR   | H'0000 | H'FFFFFF74    | 16   | 設定不要               |

| シンクロナス                        | エリア 2 用     | SDMR   | _      | H'FFFFD000    | 8    | 設定不要               |

| DRAM モード                      |             |        |        | to H'FFFFDFFF |      |                    |

| レジスタ                          | エリア 3 用     |        |        | H'FFFFE000    |      | H'FFFFE440 に任      |

|                               |             |        |        | to H'FFFFEFFF |      | 意のデータを書き<br>込みます。* |

| MCS0 コントロールI                  | <b>ノジスタ</b> | MCSCR0 | H'0000 | H'FFFFFF50    | 16   | 設定不要               |

| MCS1 コントロールI                  | <b>ノジスタ</b> | MCSCR1 | H'0000 | H'FFFFFF52    | 16   | 設定不要               |

| MCS2 コントロールI                  | <b>ノジスタ</b> | MCSCR2 | H'0000 | H'FFFFF54     | 16   | 設定不要               |

| MCS3 コントロールI                  | <b>ンジスタ</b> | MCSCR3 | H'0000 | H'FFFFF56     | 16   | 設定不要               |

| MCS4 コントロールI                  | <b>ノジスタ</b> | MCSCR4 | H'0000 | H'FFFFFF58    | 16   | 設定不要               |

| MCS5 コントロールI                  | <b>ノジスタ</b> | MCSCR5 | H'0000 | H'FFFFFF5A    | 16   | 設定不要               |

| MCS6 コントロールI                  | <b>ノジスタ</b> | MCSCR6 | H'0000 | H'FFFFFF5C    | 16   | 設定不要               |

| MCS7 コントロールI                  | <br>ノジスタ    | MCSCR7 | H'0000 | H'FFFFFF5E    | 16   | 設定不要               |

表 2.5 BSC の設定 (HM5225165B-B6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

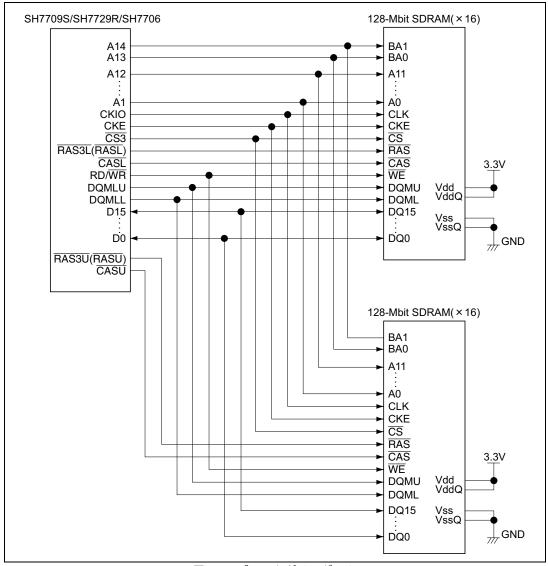

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.5** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1101 に設定してください。

図 2.5 ブロックダイアグラム

#### 2.1.8 HM5225165B-B6 (4Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 32 ビットバス幅で SDRAM(HM5225165B-B6)×2 個を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.6 に示します。

なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

|                               | 表 2         | 2.6 BSC 0 | )設定(HI    | M5225165B-B6) |             |               |

|-------------------------------|-------------|-----------|-----------|---------------|-------------|---------------|

| 名称                            |             | 略称        | 初期値       | アドレス          | アクセス<br>サイズ | 設定値           |

| バスコントロールレジ                    | ジスタ 1       | BCR1      | H'0000    | H'FFFFFF60    | 16          | H'0008        |

| バスコントロールレジ                    | ジスタ 2       | BCR2      | H'3FF0    | H'FFFFFF62    | 16          | H'3FF0        |

| ウェイトステートコン                    | ノトロール       | WCR1      | H'3FF3    | H'FFFFFF64    | 16          | H'3FF3        |

| レジスタ 1                        |             |           |           |               |             |               |

| ウェイトステートコン                    | ノトロール       | WCR2      | H'FFFF    | H'FFFFFF66    | 16          | H'FFDF        |

| レジスタ 2                        |             |           |           |               |             |               |

| 個別メモリコントロ-                    | -ルレジスタ      | MCR       | H'0000    | H'FFFFF68     | 16          | H'526C        |

| DRAM コントロール                   | レジスタ        | DCR       | H'0000    | H'FFFFFF6A    | 16          | 設定不要          |

| PCMCIA コントロール                 | レレジスタ       | PCR       | H'0000    | H'FFFFFF6C    | 16          | 設定不要          |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |             | RTCSR     | H'0000    | H'FFFFF6E     | 16          | H'A508        |

| リフレッシュタイマカ                    | カウンタ        | RTCNT     | H'0000    | H'FFFFFF70    | 16          | H'A500        |

| リフレッシュタイム:<br>カウンタ            | コンスタント      | RTCOR     | H'0000    | H'FFFFFF72    | 16          | H'A57C        |

| リフレッシュカウン                     | トレジスタ       | RFCR      | H'0000    | H'FFFFFF74    | 16          | 設定不要          |

| バスコントロールレジ                    | ジスタ 3       | BSC3      | H'0000    | H'FFFFFF7E    | 16          | 設定不要          |

| シンクロナス                        | エリア2用       | SDMR      | _         | H'FFFFD000    | 8           | 設定不要          |

| DRAM モード                      |             |           |           | to H'FFFFDFFF |             |               |

| レジスタ                          | エリア3用       |           |           | H'FFFFE000    |             | H'FFFFE880 に任 |

|                               |             |           |           | to H'FFFFEFFF |             | 意のデータを書き      |

| M000 - > 1 - 11 - 11 - 11     | ** 7 5      | MOOODO    | 1,110,000 | LUEEEEEE      | 40          | 込みます。*        |

| MCS0 コントロールし                  |             | MCSCR0    | H'0000    | H'FFFFFF50    | 16          | 設定不要          |

| MCS1 コントロールし                  |             | MCSCR1    | H'0000    | H'FFFFFF52    | 16          | 設定不要          |

| MCS2 コントロールし                  |             | MCSCR2    | H'0000    | H'FFFFFF54    | 16          | 設定不要          |

| MCS3 コントロールし                  |             | MCSCR3    | H'0000    | H'FFFFF56     | 16          | 設定不要          |

| MCS4 コントロールし                  |             | MCSCR4    | H'0000    | H'FFFFF58     | 16          | 設定不要          |

| MCS5 コントロールし                  |             | MCSCR5    | H'0000    | H'FFFFFF5A    | 16          | 設定不要          |

| MCS6 コントロールし                  |             | MCSCR6    | H'0000    | H'FFFFFF5C    | 16          | 設定不要          |

| MCS7 コントロールし                  | <b>ノジスタ</b> | MCSCR7    | H'0000    | H'FFFFFF5E    | 16          | 設定不要          |

表 2.6 BSC の設定 (HM5225165B-B6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

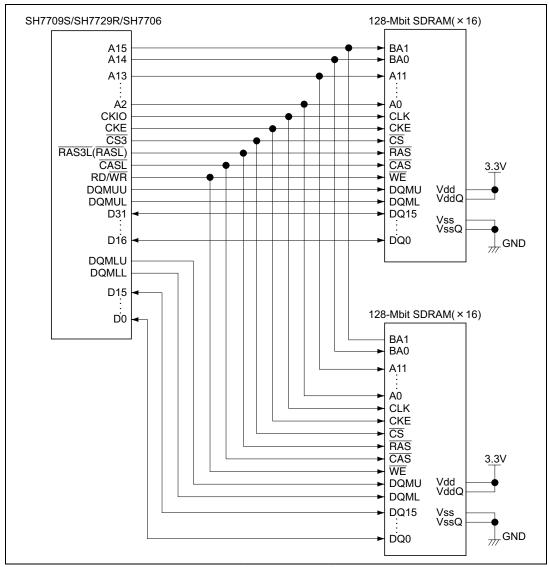

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.6** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1101 に設定してください。

図 2.6 ブロックダイアグラム

#### 2.1.9 HM5257165B-A6 (8Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7709S / SH7729R / SH7706 のエリア 3 に 16 ビットバス幅で SDRAM(HM5257165B-A6)×1 を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.7 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                            | <b>衣</b> 2      | 略称       | 初期値    | アドレス          | アクセス | 設定値                  |

|-------------------------------|-----------------|----------|--------|---------------|------|----------------------|

|                               |                 |          |        |               | サイズ  |                      |

| バスコントロールレ                     | ジスタ 1           | BCR1     | H'0000 | H'FFFFFF60    | 16   | H'0008               |

| バスコントロールレ                     | ジスタ 2           | BCR2     | H'3FF0 | H'FFFFFF62    | 16   | H'3FB0               |

| ウェイトステートコン                    | ントロール           | WCR1     | H'3FF3 | H'FFFFFF64    | 16   | H'3FF3               |

| レジスタ 1                        |                 |          |        |               |      |                      |

| ウェイトステートコン                    | ントロール           | WCR2     | H'FFFF | H'FFFFFF66    | 16   | H'FFDF               |

| レジスタ 2                        |                 |          |        |               |      |                      |

| 個別メモリコントロ-                    | ールレジスタ          | MCR      | H'0000 | H'FFFFFF68    | 16   | H'5274               |

| PCMCIA コントロールレジスタ             |                 | PCR      | H'0000 | H'FFFFFF6C    | 16   | 設定不要                 |

| リフレッシュタイマコントロール<br>/ステータスレジスタ |                 | RTCSR    | H'0000 | H'FFFFF6E     | 16   | H'A508               |

| リフレッシュタイマス                    |                 | RTCNT    | H'0000 | H'FFFFFF70    | 16   | H'A500               |

| リフレッシュタイム                     |                 | RTCOR    | H'0000 | H'FFFFFF72    | 16   | H'A57C               |

| カウンタ                          |                 | iti ooit | 110000 |               | 10   | 117.070              |

| リフレッシュカウン                     | トレジスタ           | RFCR     | H'0000 | H'FFFFFF74    | 16   | 設定不要                 |

| シンクロナス                        | エリア 2 用         | SDMR     | _      | H'FFFFD000    | 8    | 設定不要                 |

| DRAM モード                      |                 |          |        | to H'FFFFDFFF |      |                      |

| レジスタ                          | エリア 3 用         |          |        | H'FFFFE000    |      | H'FFFFE440 に任        |

|                               |                 |          |        | to H'FFFFEFFF |      | 意のデータを書き<br>  込みます。* |

| MCS0 コントロールI                  | L<br>ノジスタ       | MCSCR0   | H'0000 | H'FFFFFF50    | 16   | 設定不要                 |

| MCS1 コントロール I                 | <b>ンジスタ</b>     | MCSCR1   | H'0000 | H'FFFFFF52    | 16   | 設定不要                 |

| MCS2 コントロール I                 | <b></b><br>ノジスタ | MCSCR2   | H'0000 | H'FFFFFF54    | 16   | 設定不要                 |

| MCS3 コントロールI                  | <b>ノジスタ</b>     | MCSCR3   | H'0000 | H'FFFFF56     | 16   | 設定不要                 |

| MCS4 コントロールI                  | <b>ノジスタ</b>     | MCSCR4   | H'0000 | H'FFFFF58     | 16   | 設定不要                 |

| MCS5 コントロールI                  | <b>ンジスタ</b>     | MCSCR5   | H'0000 | H'FFFFF5A     | 16   | 設定不要                 |

| MCS6 コントロールI                  | <b>ンジスタ</b>     | MCSCR6   | H'0000 | H'FFFFFF5C    | 16   | 設定不要                 |

| MCS7 コントロールI                  | <b>ノジスタ</b>     | MCSCR7   | H'0000 | H'FFFFFF5E    | 16   | 設定不要                 |

表 2.7 BSC の設定 (HM5257165B-A6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

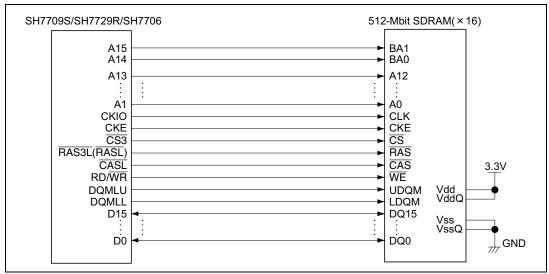

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.7** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1110 に設定してください。

図 2.7 ブロックダイアグラム

#### 2.2 SH7727 SDRAM インタフェース例

#### 2.2.1 SDRAM 直結方式

シンクロナス DRAM は  $\overline{\text{CS}}$  信号によって選択できるため、 $\overline{\text{RAS}}$  等の制御信号を共通に使用して物理空間のエリア 2 とエリア 3 に接続が可能です。BCR1 メモリタイプビット(DRAMTP2~0)を 010 に設定すると、エリア 2 が通常メモリ空間、エリア 3 がシンクロナス DRAM 空間になり、011 に設定するとエリア 2、エリア 3 がともにシンクロナス DRAM 空間となります。

本 LSI ではシンクロナス DRAM の動作モードとして、バースト長 1 のバーストリード/シングルライトのモードをサポートしています。データのバス幅は 16、32 ビットから選択できます。キャッシュのフィル/コピーバックサイクルでは 16 バイトのバースト転送が行われ、ライトスルー領域の書き込みや、キャッシュ非対象領域の読み出し・書き込みでは 1 回のみアクセスが行われます。

シンクロナス DRAM を直結するための制御信号は  $\overline{RAS3}$ 、 $\overline{CAS}$ 、 $RD/\overline{WR}$ 、 $\overline{CS2}$  または  $\overline{CS3}$ 、DQMUU、DQMUL、DQMLL および CKE 信号です。  $\overline{CS2}$  または  $\overline{CS3}$  を除く信号は各エリア共通であり、CKE を除く信号は  $\overline{CS2}$  または  $\overline{CS3}$  がアサートされたときのみ有効となり取り込まれます。したがって、複数のエリアにシンクロナス DRAM を並列に接続することができます。CKE はセルフリフレッシュを行うときのみネゲート(L レベルに)され、それ以外は常にアサート(H レベルに)されています。

$\overline{RAS3}$ 、 $\overline{CAS}$ 、 $RD/\overline{WR}$  および特定のアドレス信号によって、シンクロナス DRAM に対するコマンドが指定されます。コマンドには、NOP、オートリフレッシュ(REF)、セルフリフレッシュ(SELF)、全バンクプリチャージ(PALL)、ロウアドレスストローブ・バンクアクティブ(ACTV)、リード(READ)、プリチャージ付きリード(READA)、ライト(READA)、プリチャージ付きライト(READA)、モードレジスタ書き込み(READA)があります。

バイトの指定は DQMUU、DQMUL、DQMLU、DQMLL によって行われます。該当する DQM が L のバイトに対して読み出し書き込みが行われます。ビックエンディアンモードの場合、DQMUU は 4n 番地のアクセスを、DQMLL は 4n+3 番地のアクセスを指定します。またリトルエンディアンモードの場合、DQMUU は 4n+3 番地のアクセスを、DQMLL は 4n 番地のアクセスを指定します。

#### 2.2.2 パワーオンシーケンス (SH7727)

シンクロナス DRAM を使用するためには、パワーオン後、まずモードの設定を行う必要があります。シンクロナス DRAM の初期化を正しく行うためには、まず最初にバスステートコントローラのレジスタを設定した後、シンクロナス DRAM のモードレジスタに対する書き込みを行わなければなりません。シンクロナス DRAM のモードレジスタの設定は  $\overline{\text{RAS}}$ 、 $\overline{\text{CAS}}$ 、 $\overline{\text{RD/WR}}$  信号の組み合わせで、その時点のアドレス信号の値が取り込まれます。バスステートコントローラは、設定したい値を Xとすると、エリア 2 のシンクロナス DRAM に対しては HTFFFFD000+X 番地に、またエリア 3 のシンクロナス DRAM に対しては HTFFFE000+X に書き込みを行うことによって、値 X がシンクロナス DRAM のモードレジスタに書き込まれるように動作します。この際データは無視されますが、モードの書き込みはバイトサイズで行います。本 LSI でサポートしているバーストリード/シングルライト、CAS レイテンシ 1 から 3、ラップタイプ=シーケンシャル、バースト長 1 を設定するには以下のアドレスにバイトサイズで任意のデータを書き込みます。

|                |             | エリア 2      | エリア 3      |

|----------------|-------------|------------|------------|

| 32 ビット幅        | CAS レイテンシ 1 | H'FFFFD840 | H'FFFFE840 |

| 接続時            | CAS レイテンシ 2 | H'FFFFD880 | H'FFFFE880 |

|                | CAS レイテンシ 3 | H'FFFFD8C0 | H'FFFFE8C0 |

|                |             | エリア 2      | エリア 3      |

| 16 ビット幅        | CAS レイテンシ 1 | H'FFFFD420 | H'FFFFE420 |

| 接続時            |             |            |            |

| וייין טעוי אַנ | CAS レイテンシ 2 | H'FFFFD440 | H'FFFFE440 |

HTFFFFD000+X もしくは HTFFFE000+X 番地への書き込みによって、まず、全バンクプリチャージコマンド(PALL)が TRp1 サイクルに発行され、それに続く TMw1 サイクルにモードレジスタ書き込みコマンドが発行されます。

モードレジスタ書き込みコマンド発行時のアドレス信号は、以下のようになります。

| 32 ビット幅 | A15~A9 | 0000100(バーストリード&シングルライト) |

|---------|--------|--------------------------|

| 接続時     | A8~A6  | CAS レイテンシ                |

|         | A5     | 0(バーストタイプ=シーケンシャル)       |

|         | A4~A2  | 000 (バースト長 1)            |

|         |        |                          |

| 16 ビット幅 | A14~A8 | 0000100(バーストリード&シングルライト) |

| 接続時     | A7~A5  | CAS レイテンシ                |

|         | A4     | 0(バーストタイプ=シーケンシャル)       |

|         | A3~A1  | 000 (バースト長 1)            |

|         |        |                          |

モードレジスタの設定に先立って、シンクロナス DRAM の要求する電源投入後  $100 \mu s$  のアイドル時間(メモリメーカによって異なる)を保証しなければなりません。リセット信号のパルス幅がこのアイドル時間より長い場合には、直ちにモードレジスタの設定を行っても問題はありません。ダミーのオートリフレッシュサイクルをメーカの規定する回数(通常 8 回)以上実行する必要があります。これはオートリフレッシュの設定を行った後、種々の初期化を行っているうちに自然に実現されるのが普通ですが、より確実に行うためには、このダミーサイクルを実行する間だけリフレッシュ要求の発生する間隔を短く設定しておく方法があります。単なるリードまたはライトアクセスではオートリフレッシュに使用するシンクロナス DRAM 内部のアドレスカウンタが初期化されないため、必ずオートリフレッシュサイクルでなければなりません。

#### 2.2.3 HM5264165F-B60 (1Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 16 ビットバス幅で SDRAM(HM5264165F-B60)×1 を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.8 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| ·                                          | 11, 2       | 1      |        | - is          |             | == +++               |

|--------------------------------------------|-------------|--------|--------|---------------|-------------|----------------------|

| 名称<br>———————————————————————————————————— |             | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                  |

| バスコントロールレ                                  | ジスタ 1       | BCR1   | H'0000 | H'FFFFFF60    | 16          | H'0008               |

| バスコントロールレ                                  | ジスタ 2       | BCR2   | H'3FF0 | H'FFFFFF62    | 16          | H'3FB0               |

| ウェイトステートコン                                 | ントロール       | WCR1   | H'3FF3 | H'FFFFFF64    | 16          | H'3FF3               |

| レジスタ 1                                     |             |        |        |               |             |                      |

| ウェイトステートコン                                 | ントロール       | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF               |

| レジスタ 2                                     |             |        |        |               |             |                      |

| 個別メモリコントロ-                                 | -ルレジスタ      | MCR    | H'0000 | H'FFFFFF68    | 16          | H'5224               |

| PCMCIA コントロー                               | ルレジスタ       | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要                 |

| リフレッシュタイマ:<br>/ステータスレジス:                   |             | RTCSR  | H'0000 | H'FFFFF6E     | 16          | H'A508               |

| リフレッシュタイマス                                 | カウンタ        | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500               |

| リフレッシュタイム:<br>カウンタ                         | コンスタント      | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A5F8               |

| リフレッシュカウン                                  | トレジスタ       | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要                 |

| シンクロナス                                     | エリア2用       | SDMR   | _      | H'FFFFD000    | 8           | 設定不要                 |

| DRAM モード                                   |             |        |        | to H'FFFFDFFF |             |                      |

| レジスタ                                       | エリア 3 用     |        |        | H'FFFFE000    |             | H'FFFFE440 に任        |

|                                            |             |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>  込みます。* |

| MCS0 コントロール                                | <b>ノジスタ</b> | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要                 |

| MCS1 コントロール                                | <b>ノジスタ</b> | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要                 |

| MCS2 コントロールI                               | <b>ノジスタ</b> | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要                 |

| MCS3 コントロール                                | <b>ノジスタ</b> | MCSCR3 | H'0000 | H'FFFFFF56    | 16          | 設定不要                 |

| MCS4 コントロール                                | <b>ノジスタ</b> | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要                 |

| MCS5 コントロール                                | <b>ノジスタ</b> | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要                 |

| MCS6 コントロールI                               | <b>ノジスタ</b> | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要                 |

| MCS7 コントロール                                |             | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要                 |

表 2.8 BSC の設定 (HM5264165F-B60)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値と H'FFFFE000 を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

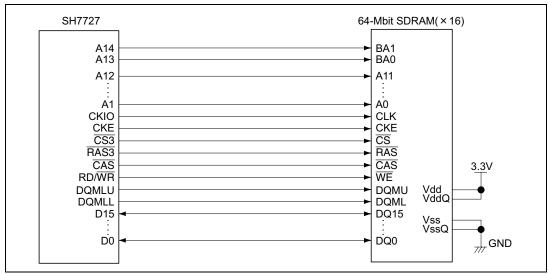

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.8** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0100 に設定してください。

図 2.8 ブロックダイアグラム

#### 2.2.4 HM5264165F-B60 (1Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 32 ビットバス幅で SDRAM(HM5264165F-B60)×2 を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.9 に示します。

なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                       | 衣 2          | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                |

|--------------------------|--------------|--------|--------|---------------|-------------|--------------------|

| バスコントロールレシ               | ジスタ 1        | BCR1   | H'0000 | H'FFFFFF60    | 16          | H'0008             |

| バスコントロールレシ               | ジスタ 2        | BCR2   | H'3FF0 | H'FFFFFF62    | 16          | H'3FF0             |

| ウェイトステートコン               | ノトロール        | WCR1   | H'3FF3 | H'FFFFFF64    | 16          | H'3FF3             |

| レジスタ 1                   |              |        |        |               |             |                    |

| ウェイトステートコン               | ノトロール        | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF             |

| レジスタ 2                   |              |        |        |               |             |                    |

| 個別メモリコントロー               | -ルレジスタ       | MCR    | H'0000 | H'FFFFF68     | 16          | H'5224             |

| DRAM コントロールし             | <b>レジスタ</b>  | DCR    | H'0000 | H'FFFFFF6A    | 16          | 設定不要               |

| PCMCIA コントロール            | レレジスタ        | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要               |

| リフレッシュタイマ=<br>/ステータスレジスタ |              | RTCSR  | H'0000 | H'FFFFFF6E    | 16          | H'A508             |

| リフレッシュタイマカ               | コウンタ         | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500             |

| リフレッシュタイム=<br>カウンタ       | コンスタント       | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A5F8             |

| リフレッシュカウント               | ・レジスタ        | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要               |

| シンクロナス                   | エリア2用        | SDMR   | _      | H'FFFFD000    | 8           | 設定不要               |

| DRAM モード                 |              |        |        | to H'FFFFDFFF |             |                    |

| レジスタ                     | エリア3用        |        |        | H'FFFFE000    |             | H'FFFFE880 に任      |

|                          |              |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>込みます。* |

| MCS0 コントロールし             | <b>,</b> ジスタ | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要               |

| MCS1 コントロールし             | <b>ノジスタ</b>  | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要               |

| MCS2 コントロールし             | <b>ノジスタ</b>  | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要               |

| MCS3 コントロールし             | <b>ノジスタ</b>  | MCSCR3 | H'0000 | H'FFFFFF56    | 16          | 設定不要               |

| MCS4 コントロールし             | <b>ンジスタ</b>  | MCSCR4 | H'0000 | H'FFFFF58     | 16          | 設定不要               |

| MCS5 コントロールし             | <b>ノジスタ</b>  | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要               |

| MCS6 コントロールし             | <b>ノジスタ</b>  | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要               |

| MCS7 コントロールし             | <b>ンジスタ</b>  | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要               |

表 2.9 BSC の設定 (HM5264165F-B60)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

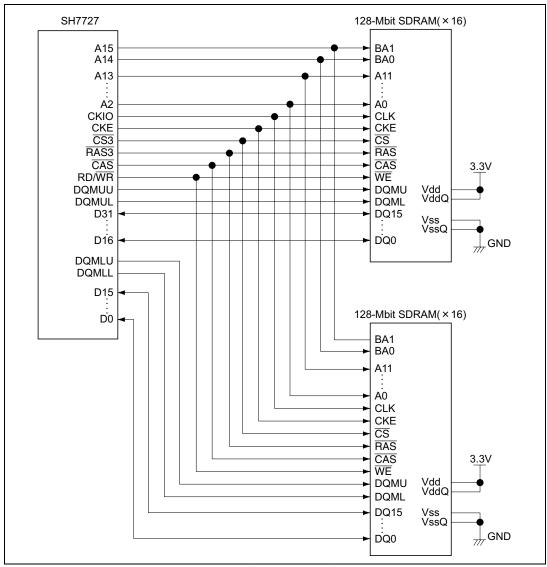

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.9** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0100 に設定してください。

図 2.9 ブロックダイアグラム

#### 2.2.5 uPD45128163 (2Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 16 ビットバス幅で SDRAM(uPD45128163)×1 を接続する場合、バスステートコントローラ(以下、BSC)の設定を行う必要があります。各 BSC レジスタの設定値を表 2.10 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

表 2.10 BSC の設定 (uPD45128163)

| 名称                       |                        | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                |

|--------------------------|------------------------|--------|--------|---------------|-------------|--------------------|

| バスコントロールレジ               | ジスタ 1                  | BCR1   | H'0000 | H'FFFFFF60    | 16          | H'0008             |

| バスコントロールレジ               | ジスタ 2                  | BCR2   | H'3FF0 | H'FFFFF62     | 16          | H'3FB0             |

| ウェイトステートコン               | ノトロール                  | WCR1   | H'3FF3 | H'FFFFFF64    | 16          | H'3FF3             |

| レジスタ 1                   |                        |        |        |               |             |                    |

| ウェイトステートコン               | ノトロール                  | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF             |

| レジスタ 2                   |                        |        |        |               |             |                    |

| 個別メモリコントロー               | -ルレジスタ                 | MCR    | H'0000 | H'FFFFFF68    | 16          | H'522C             |

| PCMCIA コントロール            | レレジスタ                  | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要               |

| リフレッシュタイマコ<br>/ステータスレジスタ |                        | RTCSR  | H'0000 | H'FFFFF6E     | 16          | H'A508             |

| リフレッシュタイマカ               | コウンタ                   | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500             |

| リフレッシュタイム=<br>カウンタ       | コンスタント                 | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A5F8             |

| リフレッシュカウント               | <b>・</b> レジスタ          | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要               |

| シンクロナス                   | エリア 2 用                | SDMR   | _      | H'FFFFD000    | 8           | 設定不要               |

| DRAM モード                 |                        |        |        | to H'FFFFDFFF |             |                    |

| レジスタ                     | エリア 3 用                |        |        | H'FFFFE000    |             | H'FFFFE440 に任      |

|                          |                        |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>込みます。* |

| MCS0 コントロールし             | <b><sub>ノジスタ</sub></b> | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要               |

| MCS1 コントロールし             | <b><sub>ノジスタ</sub></b> | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要               |

| MCS2 コントロールし             | <br>,ジスタ               | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要               |

| MCS3 コントロールし             | <b>ノジスタ</b>            | MCSCR3 | H'0000 | H'FFFFF56     | 16          | 設定不要               |

| MCS4 コントロールし             | <br>,ジスタ               | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要               |

| MCS5 コントロールし             | <b>レジスタ</b>            | MCSCR5 | H'0000 | H'FFFFF5A     | 16          | 設定不要               |

| MCS6 コントロールし             | <b>レジスタ</b>            | MCSCR6 | H'0000 | H'FFFFF5C     | 16          | 設定不要               |

| MCS7 コントロールし             | <b>ンジスタ</b>            | MCSCR7 | H'0000 | H'FFFFF5E     | 16          | 設定不要               |

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.10** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0101 に設定してください。

<u>図 2.10</u> ブロックダイアグラム

#### 2.2.6 uPD45128163 (2Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 32 ビットバス幅で SDRAM (uPD45128163)  $\times$ 2 を接続する場合、バスステートコントローラ (以下、BSC) の設定を行う必要があります。各 BSC レジスタの設定値を表 2.11 に示します。

なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 表 2.11 BSC の設定(uPD45128163) |                  |        |            |                             |             |                                          |  |  |

|-----------------------------|------------------|--------|------------|-----------------------------|-------------|------------------------------------------|--|--|

| 名称                          |                  | 略称     | 初期値        | アドレス                        | アクセス<br>サイズ | 設定値                                      |  |  |

| バスコントロールレシ                  | ジスタ 1            | BCR1   | H'0000     | H'FFFFF60                   | 16          | H'0008                                   |  |  |

| バスコントロールレシ                  | ジスタ 2            | BCR2   | H'3FF0     | H'FFFFFF62                  | 16          | H'3FF0                                   |  |  |

| ウェイトステートコン                  | ノトロール            | WCR1   | H'3FF3     | H'FFFFFF64                  | 16          | H'3FF3                                   |  |  |

| レジスタ 1                      |                  |        |            |                             |             |                                          |  |  |

| ウェイトステートコン                  | ノトロール            | WCR2   | H'FFFF     | H'FFFFFF66                  | 16          | H'FFDF                                   |  |  |

| レジスタ 2                      |                  |        |            |                             |             |                                          |  |  |

| 個別メモリコントロー                  | -ルレジスタ           | MCR    | H'0000     | H'FFFFFF68                  | 16          | H'522C                                   |  |  |

| DRAM コントロールし                | <b>レジスタ</b>      | DCR    | H'0000     | H'FFFFFF6A                  | 16          | 設定不要                                     |  |  |

| PCMCIA コントロール               | レレジスタ            | PCR    | H'0000     | H'FFFFFF6C                  | 16          | 設定不要                                     |  |  |

| リフレッシュタイマニ                  |                  | RTCSR  | H'0000     | H'FFFFFF6E                  | 16          | H'A508                                   |  |  |

| <b>/ステータスレジスタ</b>           |                  |        |            |                             |             |                                          |  |  |

| リフレッシュタイマカ                  |                  | RTCNT  | H'0000     | H'FFFFFF70                  | 16          | H'A500                                   |  |  |

| リフレッシュタイム=<br>  カウンタ        | RTCOR            | H'0000 | H'FFFFFF72 | 16                          | H'A5F8      |                                          |  |  |

| リフレッシュカウント                  | しいジュカ            | RFCR   | H'0000     | H'FFFFFF74                  | 16          | 設定不要                                     |  |  |

| *                           |                  | _      | П 0000     |                             |             |                                          |  |  |

| シンクロナス<br>DRAM モード          | エリア2用            | SDMR   | _          | H'FFFFD000<br>to H'FFFFDFFF | 8           | 設定不要                                     |  |  |

| レジスタ                        | エリア3用            |        |            | H'FFFFE000                  |             | H'FFFFE880 に任                            |  |  |

|                             | エリアる用            |        |            | to H'FFFFEFFF               |             | ೧೯೯೯ E C C C C C C C C C C C C C C C C C |  |  |

|                             |                  |        |            | UHFFFEFFF                   |             | 込みます。*                                   |  |  |

| MCS0 コントロールし                | <b>ンジスタ</b>      | MCSCR0 | H'0000     | H'FFFFFF50                  | 16          | 設定不要                                     |  |  |

| MCS1 コントロールし                | <b>ノジスタ</b>      | MCSCR1 | H'0000     | H'FFFFFF52                  | 16          | 設定不要                                     |  |  |

| MCS2 コントロールし                | <b>,ジスタ</b>      | MCSCR2 | H'0000     | H'FFFFFF54                  | 16          | 設定不要                                     |  |  |

| MCS3 コントロールし                | <b>ノジスタ</b>      | MCSCR3 | H'0000     | H'FFFFFF56                  | 16          | 設定不要                                     |  |  |

| MCS4 コントロールし                | <b>,ジスタ</b>      | MCSCR4 | H'0000     | H'FFFFFF58                  | 16          | 設定不要                                     |  |  |

| MCS5 コントロールし                | <b>ノジスタ</b>      | MCSCR5 | H'0000     | H'FFFFFF5A                  | 16          | 設定不要                                     |  |  |

| MCS6 コントロールし                | <b>ノジスタ</b>      | MCSCR6 | H'0000     | H'FFFFFF5C                  | 16          | 設定不要                                     |  |  |

| MCS7 コントロールし                | <sub>ノ</sub> ジスタ | MCSCR7 | H'0000     | H'FFFFF5E                   | 16          | 設定不要                                     |  |  |

表 2.11 BSC の設定 (uPD45128163)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

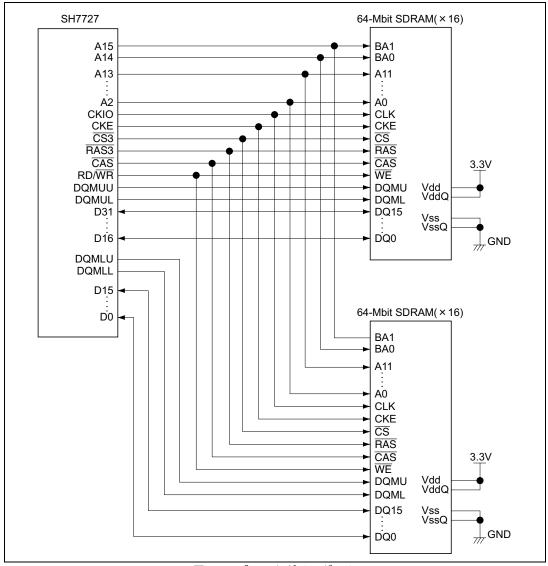

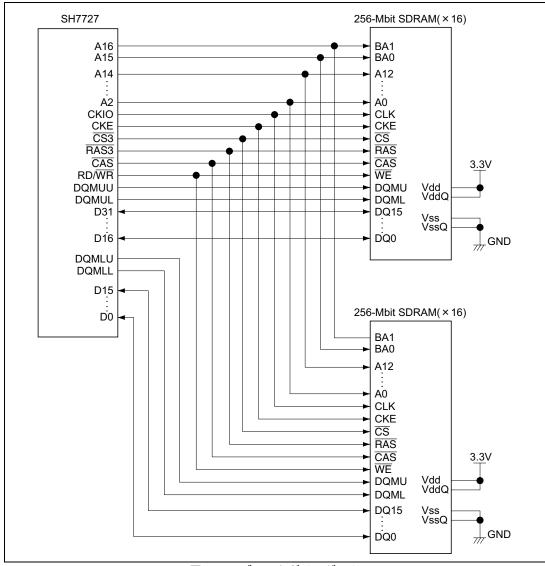

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.11** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=0101 に設定してください。

図 2.11 ブロックダイアグラム

#### 2.2.7 HM5225165B-B6 (4Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 16 ビットバス幅で SDRAM(HM5225165B-B6)×1 を接続する場合、バスステートコントローラ (以下、BSC) の設定を行う必要があります。各 BSC レジスタの設定値を表 2.12 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                       |              | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                  |  |  |

|--------------------------|--------------|--------|--------|---------------|-------------|----------------------|--|--|

| バスコントロールレジ               | ジスタ 1        | BCR1   | H'0000 | H'FFFFF60     | 16          | H'0008               |  |  |

| バスコントロールレジ               | <b>ジスタ 2</b> | BCR2   | H'3FF0 | H'FFFFF62     | 16          | H'3FB0               |  |  |

| ウェイトステートコン               | ントロール        | WCR1   | H'3FF3 | H'FFFFF64     | 16          | H'3FF3               |  |  |

| レジスタ 1                   |              |        |        |               |             |                      |  |  |

| ウェイトステートコン               | ントロール        | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF               |  |  |

| レジスタ 2                   |              |        |        |               |             |                      |  |  |

| 個別メモリコントロ-               | ールレジスタ       | MCR    | H'0000 | H'FFFFFF68    | 16          | H'526C               |  |  |

| PCMCIA コントロー             | ルレジスタ        | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要                 |  |  |

| リフレッシュタイマ:<br>/ステータスレジスタ |              | RTCSR  | H'0000 | H'FFFFF6E     | 16          | H'A508               |  |  |

| リフレッシュタイマス               | カウンタ         | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500               |  |  |

| リフレッシュタイム:<br>カウンタ       | コンスタント       | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A57C               |  |  |

| リフレッシュカウン                | トレジスタ        | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要                 |  |  |

| シンクロナス                   | エリア2用        | SDMR   | _      | H'FFFFD000    | 8           | 設定不要                 |  |  |

| DRAM モード                 |              |        |        | to H'FFFFDFFF |             |                      |  |  |

| レジスタ                     | エリア3用        |        |        | H'FFFFE000    |             | H'FFFFE440 に任        |  |  |

|                          |              |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>  込みます。* |  |  |

| MCS0 コントロールI             | <b>ノジスタ</b>  | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要                 |  |  |

| MCS1 コントロール I            | <b>ノジスタ</b>  | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要                 |  |  |

| MCS2 コントロール I            | <b>ノジスタ</b>  | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要                 |  |  |

| MCS3 コントロール I            | <b>ノジ</b> スタ | MCSCR3 | H'0000 | H'FFFFFF56    | 16          | 設定不要                 |  |  |

| MCS4 コントロール I            | <b>ノジスタ</b>  | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要                 |  |  |

| MCS5 コントロール I            | <b>ノジスタ</b>  | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要                 |  |  |

| MCS6 コントロール I            | <b>ノジスタ</b>  | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要                 |  |  |

| MCS7 コントロールI             | <b>ノジスタ</b>  | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要                 |  |  |

表 2.12 BSC の設定 (HM5225165B-B6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値とH'FFFFE000を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.12** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1101 に設定してください。

<u>図 2.12</u> ブロックダイアグラム

#### 2.2.8 HM5225165B-B6 (4Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 32 ビットバス幅で SDRAM(HM5225165B-B6)×2 を接続する場合、バスステートコントローラ (以下、BSC) の設定を行う必要があります。各 BSC レジスタの設定値を表 2.13 に示します。なお、バスクロック 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                 | 衣∠                   | 略称     | 初期値    | M5225165B-B6)<br>アドレス | アクセス | 設定値                    |

|--------------------|----------------------|--------|--------|-----------------------|------|------------------------|

| 石桥                 |                      | 哈尔     | 初舟恒    | 7 7 7 7               | サイズ  | <b>設</b> 是胆            |

| バスコントロールレジ         | ジスタ 1                | BCR1   | H'0000 | H'FFFFFF60            | 16   | H'0008                 |

| バスコントロールレジ         | ジスタ 2                | BCR2   | H'3FF0 | H'FFFFFF62            | 16   | H'3FF0                 |

| ウェイトステートコン         | ノトロール                | WCR1   | H'3FF3 | H'FFFFFF64            | 16   | H'3FF3                 |

| レジスタ 1             |                      |        |        |                       |      |                        |

| ウェイトステートコン         | ノトロール                | WCR2   | H'FFFF | H'FFFFF66             | 16   | H'FFDF                 |

| レジスタ 2             |                      |        |        |                       |      |                        |

| 個別メモリコントロ-         | -ルレジスタ               | MCR    | H'0000 | H'FFFFFF68            | 16   | H'526C                 |

| DRAM コントロール        | レジスタ                 | DCR    | H'0000 | H'FFFFFF6A            | 16   | 設定不要                   |

| PCMCIA コントロール      | レレジスタ                | PCR    | H'0000 | H'FFFFFF6C            | 16   | 設定不要                   |

| リフレッシュタイマコ         | コントロール               | RTCSR  | H'0000 | H'FFFFFF6E            | 16   | H'A508                 |

| <b>/</b> ステータスレジスタ | 7                    |        |        |                       |      |                        |

| リフレッシュタイマカ         | カウンタ                 | RTCNT  | H'0000 | H'FFFFFF70            | 16   | H'A500                 |

| リフレッシュタイム=         | コンスタント               | RTCOR  | H'0000 | H'FFFFFF72            | 16   | H'A57C                 |

| カウンタ               |                      |        |        |                       |      |                        |

| リフレッシュカウン          | · · · · · · ·        | RFCR   | H'0000 | H'FFFFFF74            | 16   | 設定不要                   |

| シンクロナス<br>DRAM モード | エリア2用                | SDMR   | _      | H'FFFFD000            | 8    | 設定不要<br>               |

| レジスタ               |                      |        |        | to H'FFFFDFFF         |      |                        |

| DDAG               | エリア3用                |        |        | H'FFFFE000            |      | H'FFFFE880 に任          |

|                    |                      |        |        | to H'FFFFEFFF         |      | │ 意のデータを書き<br>│ 込みます。* |

| MCS0 コントロールし       | <br><sub>ノ</sub> ジスタ | MCSCR0 | H'0000 | H'FFFFFF50            | 16   | 設定不要                   |

| MCS1 コントロールし       | - · · · · ·          | MCSCR1 | H'0000 | H'FFFFFF52            | 16   | 設定不要                   |

| MCS2 コントロールし       | · · · · ·            | MCSCR2 | H'0000 | H'FFFFF54             | 16   | 設定不要                   |

| MCS3 コントロールし       | <br>ノジスタ             | MCSCR3 | H'0000 | H'FFFFFF56            | 16   | 設定不要                   |

| MCS4 コントロールし       | · · · · ·            | MCSCR4 | H'0000 | H'FFFFFF58            | 16   | 設定不要                   |

| MCS5 コントロールし       | <br>ノジスタ             | MCSCR5 | H'0000 | H'FFFFF5A             | 16   | 設定不要                   |

| MCS6 コントロールし       | <br>ノジスタ             | MCSCR6 | H'0000 | H'FFFFFF5C            | 16   | 設定不要                   |

| MCS7 コントロールし       | <b></b><br>ノジスタ      | MCSCR7 | H'0000 | H'FFFFFF5E            | 16   | 設定不要                   |

表 2.13 BSC の設定 (HM5225165B-B6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値と H'FFFFE000 を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば、SDMRに設定されます。

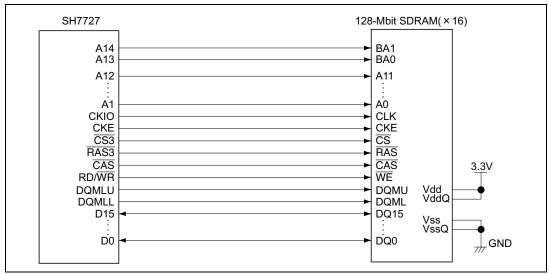

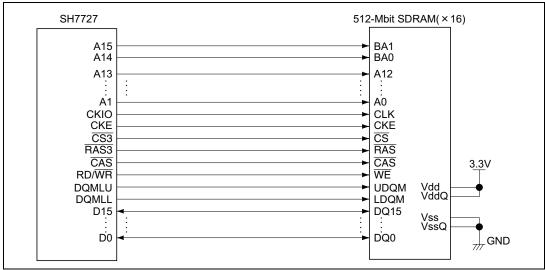

エリア 3 に 32 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.13** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1101 に設定してください。

図 2.13 ブロックダイアグラム

#### 2.2.9 HM5257165B-A6 (8Mword × 16bit × 4bank)

#### (1) バスステートコントローラ (BSC) の設定

SH7727 のエリア 3 に 16 ビットバス幅で SDRAM(HM5257165B-A6)×1 を接続する場合、バスステートコントローラ (以下、BSC) の設定を行う必要があります。各 BSC レジスタの設定値を表 2.14 に示します。

なお、バスクロックを 66MHz、CL=2、TPC=2、RCD=2、TRWL=1、TRAS=4 の条件で接続します。

| 名称                       |             | 略称     | 初期値    | アドレス          | アクセス<br>サイズ | 設定値                  |  |  |

|--------------------------|-------------|--------|--------|---------------|-------------|----------------------|--|--|

| バスコントロールレジ               | ジスタ 1       | BCR1   | H'0000 | H'FFFFF60     | 16          | H'0008               |  |  |

| バスコントロールレジ               | ジスタ 2       | BCR2   | H'3FF0 | H'FFFFF62     | 16          | H'3FB0               |  |  |

| ウェイトステートコン               | ントロール       | WCR1   | H'3FF3 | H'FFFFF64     | 16          | H'3FF3               |  |  |

| レジスタ 1                   |             |        |        |               |             |                      |  |  |

| ウェイトステートコン               | ントロール       | WCR2   | H'FFFF | H'FFFFFF66    | 16          | H'FFDF               |  |  |

| レジスタ 2                   |             |        |        |               |             |                      |  |  |

| 個別メモリコントロ-               | ールレジスタ      | MCR    | H'0000 | H'FFFFFF68    | 16          | H'5274               |  |  |

| PCMCIA コントロー             | ルレジスタ       | PCR    | H'0000 | H'FFFFFF6C    | 16          | 設定不要                 |  |  |

| リフレッシュタイマ:<br>/ステータスレジスタ |             | RTCSR  | H'0000 | H'FFFFF6E     | 16          | H'A508               |  |  |

| リフレッシュタイマス               | カウンタ        | RTCNT  | H'0000 | H'FFFFFF70    | 16          | H'A500               |  |  |

| リフレッシュタイム:<br>カウンタ       | コンスタント      | RTCOR  | H'0000 | H'FFFFFF72    | 16          | H'A57C               |  |  |

| リフレッシュカウン                | トレジスタ       | RFCR   | H'0000 | H'FFFFFF74    | 16          | 設定不要                 |  |  |

| シンクロナス                   | エリア2用       | SDMR   | _      | H'FFFFD000    | 8           | 設定不要                 |  |  |

| DRAM モード                 |             |        |        | to H'FFFFDFFF |             |                      |  |  |

| レジスタ                     | エリア 3 用     |        |        | H'FFFFE000    |             | H'FFFFE440 に任        |  |  |

|                          |             |        |        | to H'FFFFEFFF |             | 意のデータを書き<br>  込みます。* |  |  |

| MCS0 コントロールI             | <b>ノジスタ</b> | MCSCR0 | H'0000 | H'FFFFFF50    | 16          | 設定不要                 |  |  |

| MCS1 コントロール I            | <b>ノジスタ</b> | MCSCR1 | H'0000 | H'FFFFFF52    | 16          | 設定不要                 |  |  |

| MCS2 コントロール I            | <b>ノジスタ</b> | MCSCR2 | H'0000 | H'FFFFFF54    | 16          | 設定不要                 |  |  |

| MCS3 コントロール I            | <b>ノジスタ</b> | MCSCR3 | H'0000 | H'FFFFFF56    | 16          | 設定不要                 |  |  |

| MCS4 コントロール I            | <b>ノジスタ</b> | MCSCR4 | H'0000 | H'FFFFFF58    | 16          | 設定不要                 |  |  |

| MCS5 コントロール I            | <b>ノジスタ</b> | MCSCR5 | H'0000 | H'FFFFFF5A    | 16          | 設定不要                 |  |  |

| MCS6 コントロール I            | <b>ノジスタ</b> | MCSCR6 | H'0000 | H'FFFFFF5C    | 16          | 設定不要                 |  |  |

| MCS7 コントロールI             | <b>ノジスタ</b> | MCSCR7 | H'0000 | H'FFFFFF5E    | 16          | 設定不要                 |  |  |

表 2.14 BSC の設定 (HM5257165B-A6)

<sup>【</sup>注】 本例の接続に関係のないビットは初期値としています。システムに応じて全レジスタを見直してください。

<sup>\*</sup> エリア3の場合、SDMRのアドレスは、設定したい値と H'FFFFE000 を加算した値がアドレスとなります。このアドレスに任意のデータを書き込めば SDMR に設定されます。

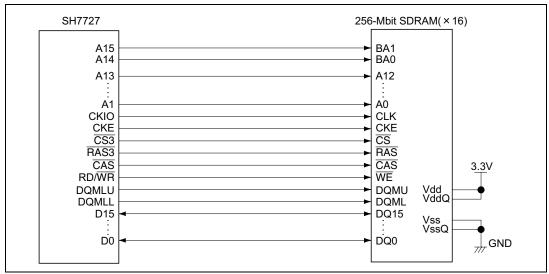

エリア 3 に 16 ビットバス幅で SDRAM を接続する場合の接続図を**図 2.14** に示します。 MCR のアドレスマルチプレクスの設定は、AMX[3:0]=1110 に設定してください。

図 2.14 ブロックダイアグラム

SH-3、SH3-DSP SDRAMインタフェース編 アプリケーションノート

発行年月 2003年7月31日 Rev.1.00

発 行 株式会社ルネサス テクノロジ 営業企画統括部 〒100-0004 東京都千代田区大手町 2-6-2

編 集 株式会社ルネサス小平セミコン 技術ドキュメント部

©2003 Renesas Technology Corp. All rights reserved. Printed in Japan.

|          | • <enes as<="" th=""></enes> |

|----------|------------------------------|

| 営業お問合せ窓口 |                              |

| 1 | h | 44 | tr | ` | - / | // |   |   | ٠. | ,  | rn | n | _ |    | ıs. | ~ | ٠, | ~ |  |

|---|---|----|----|---|-----|----|---|---|----|----|----|---|---|----|-----|---|----|---|--|

|   | П | u  | u  | J | ./  | /1 | N | w | W  | ١. | ıe | п | e | Sc | ıs. | C | N  | ı |  |

|    |                                                |   |           | ·                                     |                |

|----|------------------------------------------------|---|-----------|---------------------------------------|----------------|

| ル  | ネサス販売本                                         | 社 | 〒100-0005 | 千代田区丸の内1-8-2 (第二鉄鋼ビル)                 | (03) 3215-8600 |

| 京  | 浜 支                                            | 社 | 〒212-0058 | 川崎市幸区鹿島田890-12 (新川崎三井ビル)              | (044) 549-1662 |

| 西  | 東京支                                            | 社 | 〒190-0023 | 立川市柴崎町2-2-23 (第二高島ビル2F)               | (042) 524-8701 |

| 札  | 幌 支<br>北 支                                     | 店 | 〒060-0002 | 札幌市中央区北二条西4-1 (札幌三井ビル5F)              | (011) 210-8717 |

| 東  | 北  支                                           | 社 | 〒980-0013 | 仙台市青葉区花京院1-1-20 (花京院スクエア13F)          | (022) 221-1351 |

| しり | わ き 支                                          | 店 | 〒970-8026 | いわき市平小太郎町4-9 (損保ジャパンいわき第二ビル3F)        | (0246) 22-3222 |

| 茨  | 城  支                                           | 社 | 〒312-0034 | ひたちなか市堀口832-2 (日立システムプラザ勝田1F)         | (029) 271-9411 |

| 新  | 城 支<br>潟 支<br>本 支                              | 店 | 〒950-0087 | 新潟市東大通1-4-2 (新潟三井物産ビル3F)              | (025) 241-4361 |

| 松  | 本  支                                           | 社 | 〒390-0815 | 松本市深志1-2-11 (昭和ビル7F)                  | (0263) 33-6622 |

| 中  | 部 営 業 本                                        | 部 | ₹460-0008 | 名古屋市中区栄3-13-20 (栄センタービル4F)            | (052) 261-3000 |

| 浜  | 松  支                                           | 店 | 〒430-7710 | 浜松市板屋町111-2 (浜松アクトタワー10F)             | (053) 451-2131 |

| 西  | 部 営 業 本                                        | 部 | 〒541-0044 | 大阪市中央区伏見町4-1-1 (大阪明治生命館ランドアクシスタワー10F) | (06) 6233-9500 |

| 北  | 陸  支                                           | 社 | 〒920-0031 | 金沢市広岡3-1-1 (金沢パークビル8F)                | (076) 233-5980 |

| 中  | 陸<br>国<br>山<br>取<br>対<br>支<br>支<br>支<br>支<br>支 | 社 | 〒730-0036 | 広島市中区袋町5-25 (広島袋町ビルディング8F)            | (082) 244-2570 |

| 松  | 山  支                                           | 店 | 〒790-0003 | 松山市三番町4-4-6 (GEエジソンビル松山2号館3F)         | (089) 933-9595 |

| 鳥  | 取  支                                           | 店 | 〒680-0822 | 鳥取市今町2-251 (日本生命鳥取駅前ビル)               | (0857) 21-1915 |

| 九  | 州  支                                           | 社 | 〒812-0011 | 福岡市博多区博多駅前2-17-1 (ヒロカネビル本館5F)         | (092) 481-7695 |

| 鹿  | 児 島 支                                          | 店 | 〒890-0053 | 鹿児島市中央町12-2 (明治生命西鹿児島ビル2F)            | (099) 256-9021 |

|    |                                                |   |           |                                       |                |

■技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口:カスタマサポートセンタ E-Mail: csc@renesas.com

## SH-3、SH3-DSP、SDRAM インタフェース編 SH7709S/SH7729R/SH7706/SH7727 編