シーケンサー

Author: Volodymyr Batig Date: August 22, 2013

#### 始めに

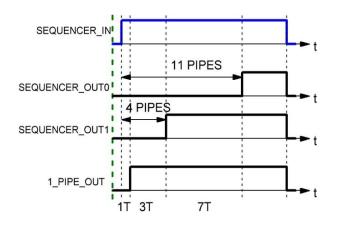

シーケンサーとは、一定の手順のもとに、入力信号に対応して出力状態を変化させる回路です。ここで ご紹介するのは、入力端子1本と出力端子3本からなる簡単な例です。主な回路要素はパイプディレイ のセルで、nRESET 入力により初期状態戻ります (図1参照)。

### シーケンサー回路設計

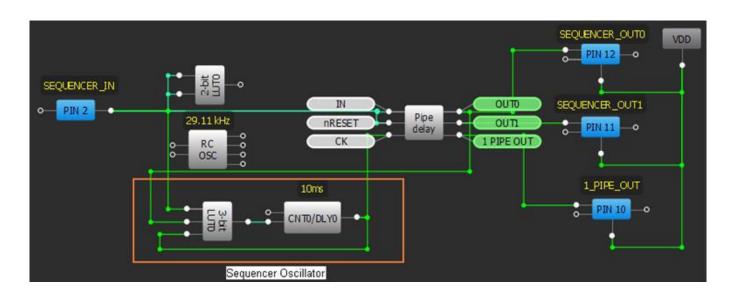

図 4 に示す通り、パイプディレイにデータ入力 SEQUENCER\_IN (PIN2)とリセット、クロック入力 を CNT0/DLY0 と LUT3 により構成される発振回路 に接続することで、シーケンサーを実現できます。 1 PIPE OUT を 1\_PIPE\_OUT (PIN10)に、OUT1 を SEQUENCER\_OUT1 (PIN11) に 、 OUT0 を SEQUENCER\_OUT0 (PIN12) にそれぞれ接続、 Output Enable を全て VDD に接続して push-pull に 設定します。

図 1. シーケンサーの動作タイミング

#### デジタルシーケンサー動作説明

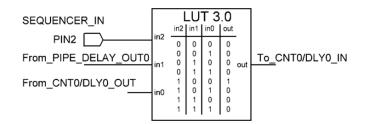

SEQUENCER\_IN (PIN2)に"H"レベルが入力されると、それはシーケンサーの発振回路(1/29.11kHz)のパルス幅と CNTO/DLYO により設定されるT=10ms 周期でパイプディレイに取り込まれ、これが立ち上がりエッジ遅延となります。1 PIPE OUTは、10ms 間隔のクロックの最初の立ち上がりで"H"になり、OUT1は4回目(40ms)、OUT0は11回目(110ms)で出力されます。パイプディレイの OUT0が"H"になると、シーケンサー発振回路は OFF 状態になります(図2参照)。シーケンサーは、SEQUENCER\_IN (PIN2)が"L"になるまで、その出力の状態を維持します。

図 2. シーケンサー発振回路 LUT 真理値表

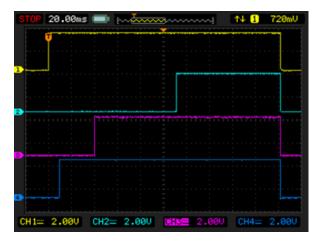

GreenPAK2 Designer により設計されたシーケンサー回路の動作波形を図 3 に示します。Channel1 (黄色) — PIN2 (SEQUENCER\_IN)、Channel2 (ライトブルー) — PIN12 (SEQUENCER\_OUT0)、Channel 3 (マゼンダ ) — PIN11 (SEQUENCER\_OUT1)、Channel4 (青) — PIN10 (1\_PIPE\_OUT)。図 3 から分かるように、実際の波形は図1に示す設計時の波形と一致しています。

図 3. GreenPAK2 Designer によるシーケンサー回路

図 4. シーケンサー動作波形

### 結論

デジタルシーケンサーは、簡単な構成ながら有用であり、パワーマネジメントやLED の駆動などの応用が考えられます。

(注)適切な動作のために、入出力端子の正確な記述を行うよう注意して下さい。図3の場合、入力端子はシュミットトリガー内蔵、出力端子はCMOS push-pullに設定されています。

#### 関連ファイル

GreenPAK Designer によるプログラムコード有

# GreenPAK Macro Circuit Design: シーケンサー

#### **About the Author**

Name: Volodymyr Batig

Background: Volodymyr Batig graduated from Ivan Franko Lviv National University in 2012, studying

at the Department of Medical and Biomedical Electronics. Presently he's working with Configurable Mixed Signal ICs and their application notes. Moreover, for more than 10 years his particular sphere of interest has included design, modernization and repair of

everything related to electronics.

## **Document History**

Document Title: GreenPAK Macro Circuit Design: シーケンサー

Document Number: AN-1037

| Revision | Orig. of Change | Submission Date | Description of Change |

|----------|-----------------|-----------------|-----------------------|

| А        | Volodymyr Batig | 08/22/2013      | New application note  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/