# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan **Renesas Electronics Corporation**

| Product<br>Category    | MPU/MCU                                                                                                                                          | Document<br>No. | TN-R8C-A038A/E Rev. 1.0 |                        |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|------------------------|--|--|--|

| Title                  | R8C/L3xx Group Timer RE Supplement and                                                                                                           | Correction      | Information<br>Category | Technical Notification |  |  |  |

| Applicable<br>Products | R8C/L35A, L35B, L35C, L35M Groups<br>R8C/L36A, L36B, L36C, L36M Groups<br>R8C/L38A, L38B, L38C, L38M Groups<br>R8C/L3AA, L3AB, L3AC, L3AM Groups | Lot No.         | Reference<br>Document   |                        |  |  |  |

This document supplements and corrects descriptions of timer RE in the User's Manual: Hardware of the above applicable MCUs. Some MCUs may not have the functions. Refer to the User's Manual: Hardware of your product.

1. Correction on timer RE reset bit (TRERST bit)

The follow correction to the timer RE reset bit (TRERST bit) is taken from the R8C/L35M, R8C/L36M, R8C/L38M, and R8C/L3AM Group User's Manual: Hardware (R01UH0110EJ0100). Refer to the User's Manual: Hardware of your product.

### 22.2.5 Timer RE Control Register 1 (TRECR1) in Real-Time Clock Mode

|               |                                  |                                                            | H12_H24       | PM         | TRERST                                                                                                                                                              | INT                                                                                                                      | TOENA                                                                                            | TCSTF                                                                         | _                 |             |  |

|---------------|----------------------------------|------------------------------------------------------------|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------|-------------|--|

| After         | Reset                            | Х                                                          | Х             | X          | х                                                                                                                                                                   | Х                                                                                                                        | 0                                                                                                | Х                                                                             | Х                 |             |  |

| Bit           | Symbol                           |                                                            | Bit           | Name       |                                                                                                                                                                     |                                                                                                                          | a na second                                                                                      | Function                                                                      |                   | R/          |  |

| b0            | -                                | <ul> <li>Nothing is assigned. If necessary, set</li> </ul> |               |            |                                                                                                                                                                     |                                                                                                                          | et to 0. When read, the content is 0.                                                            |                                                                               |                   |             |  |

| b1            | TCSTF Timer RE count status flag |                                                            |               |            | 0: Count stopped<br>1: Counting                                                                                                                                     |                                                                                                                          |                                                                                                  |                                                                               |                   |             |  |

| b2            | TOENA                            | TREO pin output enable bit                                 |               |            | 0: Clock output disabled<br>1: Clock output enabled                                                                                                                 |                                                                                                                          |                                                                                                  |                                                                               |                   |             |  |

| b3            | INT                              | Interrupt request timing bit                               |               |            |                                                                                                                                                                     | Set to 1 in real-time clock mode.                                                                                        |                                                                                                  |                                                                               |                   |             |  |

| b4            | TRERST                           |                                                            | r RE reset b  | nt.        |                                                                                                                                                                     | <ul> <li>the follow</li> <li>Registe<br/>and TRI</li> <li>Bits TC:<br/>the TRE</li> <li>The 8-b<br/>is set to</li> </ul> | ving will occ<br>rs TR ESEC<br>ECR2 are s<br>STF, INT, PI<br>ECR1 regist<br>it counter is<br>0h. | ur:_<br>, TREMIN,<br>et to 00h.<br>M, H12_H2<br>er are set to<br>set to 00h ; | and the 4-bit cou | in<br>Inter |  |

| b5            | PM                               | A.m./p.m. bit                                              |               |            | When the H12 H24 bit is set to 0 (12-hour mode) <sup>(1)</sup><br>0: a.m.<br>1: p.m.<br>When the H12 H24 bit is set to 1 (24-hour mode), its<br>value is undefined. |                                                                                                                          |                                                                                                  |                                                                               |                   |             |  |

| b6            | H12_H24                          | Operating mode select bit                                  |               |            |                                                                                                                                                                     | 0: 12-hour mode<br>1: 24-hour mode                                                                                       |                                                                                                  |                                                                               |                   |             |  |

| b7            | TSTART                           | Time                                                       | r RE count s  | start bit  |                                                                                                                                                                     | 0: Count<br>1: Count                                                                                                     |                                                                                                  |                                                                               |                   | R/          |  |

| ote:<br>1. Th | nis bit is aut                   | omatio                                                     | cally modifie | ed while t | timer RE co                                                                                                                                                         | unts.                                                                                                                    |                                                                                                  |                                                                               |                   |             |  |

The above correction also applies in output compare mode.

#### 2. Correction on notes on timer RE

The following correction to notes on timer RE is taken from the R8C/L35M, R8C/L36M, R8C/L38M, and R8C/L3AM Group User's Manual: Hardware (R01UH0110EJ0100). Refer to the manual of your product.

# 22.4 Notes on Timer RE

## 22.4.1 Reset

A reset input does not reset the timer RE data registers that store data of seconds, minutes, hours, and days of the week. This requires the initial setting of all registers after power on.

The registers and bits associated with timer RE below will not be reset by hardware reset, power-on reset, voltage monitor 0 reset, watchdog timer reset, or software reset. As the content of such registers and bits are undefined after power on, initialize these registers and bits after setting the TRERST bit to 0. When the TRERST bit is set to 1, the registers and bits are set to 0, and the timer RE control circuit will be initialized. After setting the TRERST bit to 1, make sure to set it to 0.

Applicable registers and bits:

Registers TRESEC, TREMIN, TREHR, TREWK, and TRECR2 Bits TCSTF, INT, TRERST, PM, H12\_H24, TSTART in the TRECR1 register

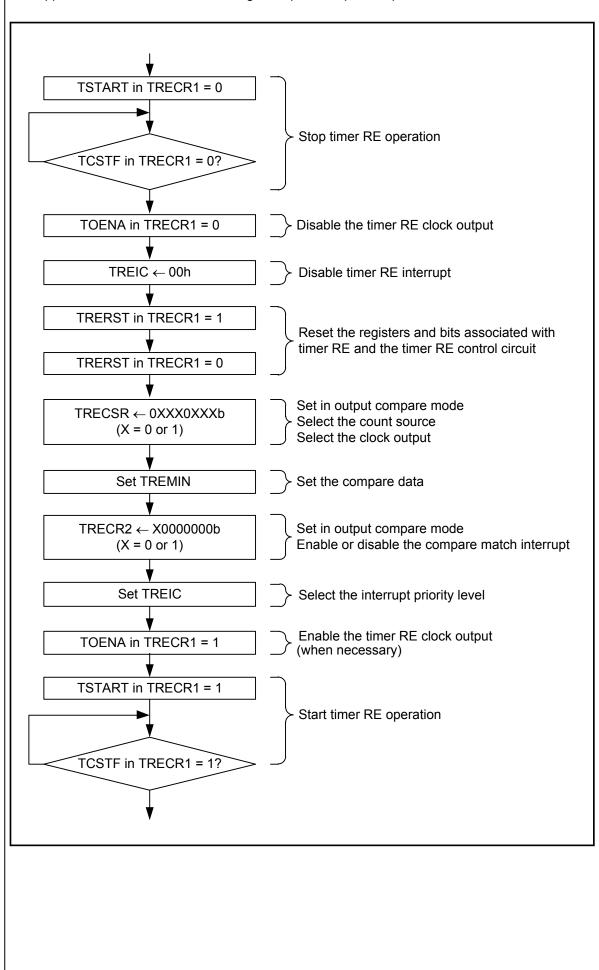

3. Supplement information for the setting example in output compare mode