Date: Nov. 25, 2013

# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category    | MPU/MCU                                                                                         |         | Document<br>No.         | TN-R8C-A039A/E         | Rev. | 1.00 |

|------------------------|-------------------------------------------------------------------------------------------------|---------|-------------------------|------------------------|------|------|

| Title                  | Notes When Using A/D Converter<br>Correction and Supplement Information on the INT<br>Interrupt |         | Information<br>Category | Technical Notification |      |      |

| Applicable<br>Products | R8C/34K, R8C/34U Groups,<br>R8C/3MK, R8C/3MU Groups                                             | Lot No. | Reference<br>Document   |                        |      |      |

## 1. Notes when using the A/D converter

Applicable products:

R8C/34K Group, R8C/34U Group, R8C/3MK Group, R8C/3MU Group

### Phenomenon:

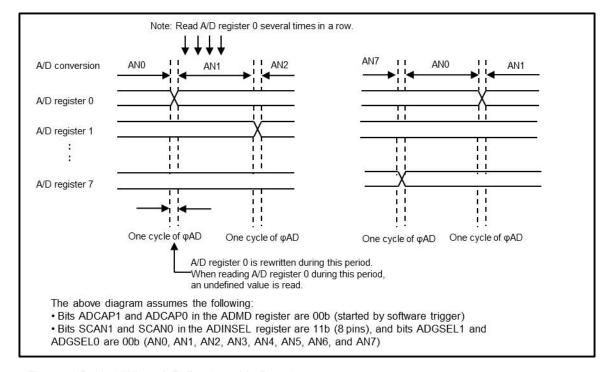

In repeat mode 0, repeat mode 1, or repeat sweep mode, when reading the A/D register i (ADi, i = 0 to 7) while the register value is rewritten, an undefined value may be read. The period for reading an undefined value is one cycle of  $\varphi$ AD.

## Countermeasure:

Read A/D register i several times in a row to determine whether the read value is valid, or use the A/D converter in one-shot mode or single sweep mode.

Figure 1 Period When A/D Register i is Rewritten

Date: Nov. 25, 2013

2. Correction and supplement information on the INT interrupt

Applicable products:

R8C/34K Group, R8C/34U Group

This section corrects and supplements descriptions of registers INTEN and INTF in the R8C/34U Group, R8C/34K Group User's Manual: Hardware Rev.1.00.

## 11.4.3 External Input Enable Register 0 (INTEN)

| Address    | 01FAh  |        |    |    |        |        |    |    |

|------------|--------|--------|----|----|--------|--------|----|----|

| Bit        | b7     | b6     | b5 | b4 | b3     | b2     | b1 | b0 |

| Symbol     | INT3PL | INT3EN | _  | _  | INT1PL | INT1EN | _  | _  |

| fter Reset | 0      | 0      | 0  | 0  | 0      | 0      | 0  | 0  |

| [ | Bit | Symbol | Bit Name                              | Function                     | R/W |

|---|-----|--------|---------------------------------------|------------------------------|-----|

|   | b0  | _      | Reserved bits                         | Set to 0.                    | R/W |

| l | b1  | _      |                                       | 4 (100)                      |     |

|   | b2  | INTIEN | INT1 input enable bit                 | 0. Disabled<br>1: Enabled    | R/W |

|   | b3  | INT1PL | INT1 input polarity select bit (1, 2) | 0: One edge<br>1: Both edges | R/W |

| 1 | b4  | _      | Reserved bits                         | Set to 0.                    | R/W |

| J | b5  | _      |                                       |                              |     |

|   | b6  | INT3EN | INT3 input enable bit                 | 0: Disabled<br>1: Enabled    | R/W |

|   | b7  | INT3PL | INT3 input polarity select bit (1, 2) | 0: One edge<br>1: Both edges | R/W |

#### Notes

- To set the INTiPL bit (i = 1 or 3) to 1 (both edges), set the POL bit in the INTiIC register to 0 (falling edge selected).

- The IR bit in the INTIIC register may be set to 1 (interrupt requested) if the INTEN register is rewritten. Refer to 11.8.4 Changing Interrupt Sources.

| b0 | Secreta Internacional | III TO III put eriable bit            | 0: Disabled<br>1: Enabled    | R/W |

|----|-----------------------|---------------------------------------|------------------------------|-----|

| b1 | INT0PL                | INT0 input polarity select bit (1, 2) | 0: One edge<br>1: Both edges | R/W |

|   |    |        | INT2 input enable bit                 | 0: Disabled<br>1: Enabled    | R/W |

|---|----|--------|---------------------------------------|------------------------------|-----|

| l | b5 | INT2PL | INT2 input polarity select bit (1, 2) | 0: One edge<br>1: Both edges | R/W |

Date: Nov. 25, 2013

#### INT Input Filter Select Register 0 (INTF) Address 01FCh b5 b4 b2 b1 b0 Symbol INT3F1 INT3F0 INT1F1 INT1F0 After Reset Bit Name R/W Bit Symbol Function b0 Reserved bits Set to 0. R/W b1 INT1F0 INT1 input filter select bit b2 R/W 0 0: No filter INT1F1 b3 R/W 0 1: Filter with f1 sampling 1 0: Filter with f8 sampling 1 1: Filter with f32 sampling Reserved bits Set to 0. R/W b4 b5 INT3F0 b6 R/W INT3 input filter select bit 0 0: No filter INT3F1 R/W b7 0 1: Filter with f1 sampling 1 0: Filter with f8 sampling 1 1: Filter with f32 sampling INT0F0 INT0 input filter select bit b0 R/W 0 0: No filter INT0F1 R/W b1 0 1: Filter with f1 sampling 1 0: Filter with f8 sampling 1 1: Filter with f32 sampling INT2F0 R/W INT2 input filter select bit 0 0: No filter INT2F1 R/W 0 1: Filter with f1 sampling 1 0: Filter with f8 sampling 1 1: Filter with f32 sampling