Date: Feb. 22, 2016

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                        | Document<br>No.         | TN-RL*-A033C/E         | Rev.                                                   | 3.00 |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/L1C Descriptions in the User's Manual<br>Rev. 2.00 Changed | Information<br>Category | Technical Notification |                                                        |      |  |

|                       |                                                                                                                |                         | D. 70# 40 H            |                                                        |      |  |

| Applicable<br>Product | RL78/L1C Group                                                                                                 | All lots                |                        | RL78/L1C User's Man<br>Rev. 2.00<br>R01UH0409EJ0200 (F |      |  |

This document describes misstatements found in the RL78/L1C User's Manual: Hardware Rev. 2.00 (R01UH0409EJ0200).

# **Corrections**

| Applicable Item                                                           | Applicable<br>Page | Contents                       |

|---------------------------------------------------------------------------|--------------------|--------------------------------|

| 2.1.1 80/85-pin products (with USB)                                       | p.24               | Incorrect descriptions revised |

| 2.1.2 80/85-pin products (without USB)                                    | p.27               | Incorrect descriptions revised |

| 2.1.3 100-pin products (with USB)                                         | p.30               | Incorrect descriptions revised |

| 2.1.4 100-pin products (without USB)                                      | p.33               | Incorrect descriptions revised |

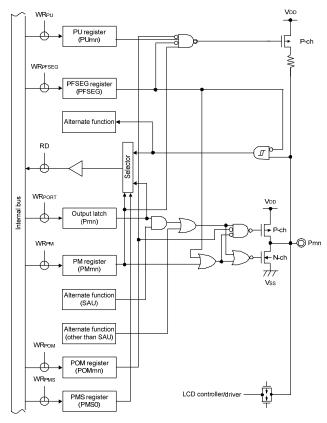

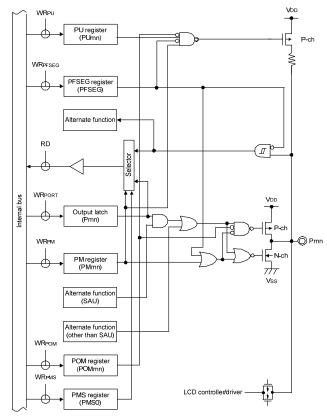

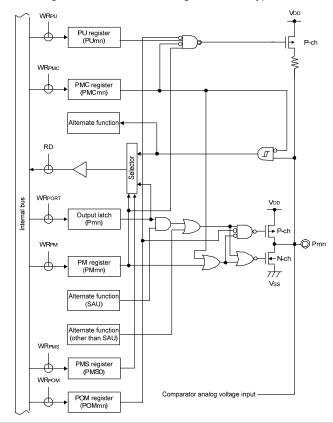

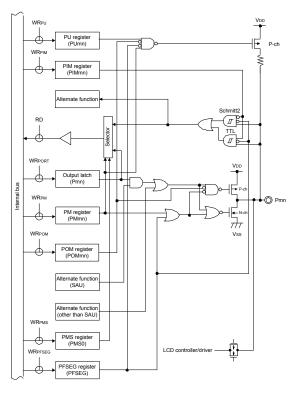

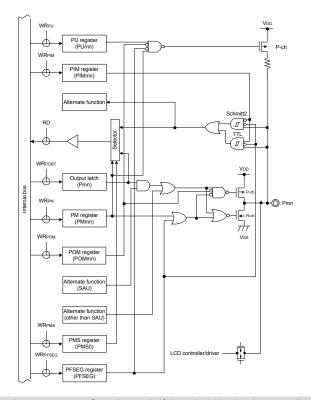

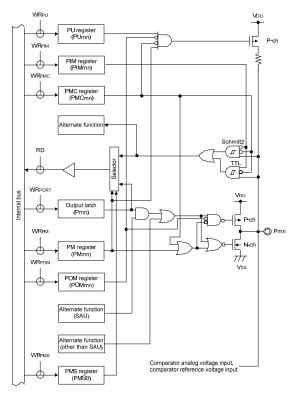

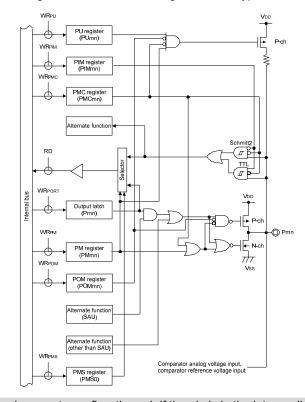

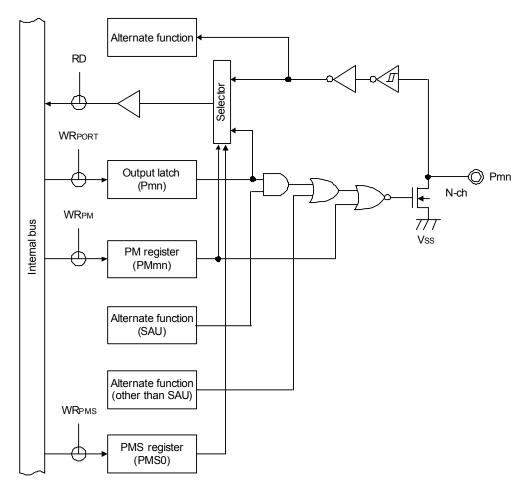

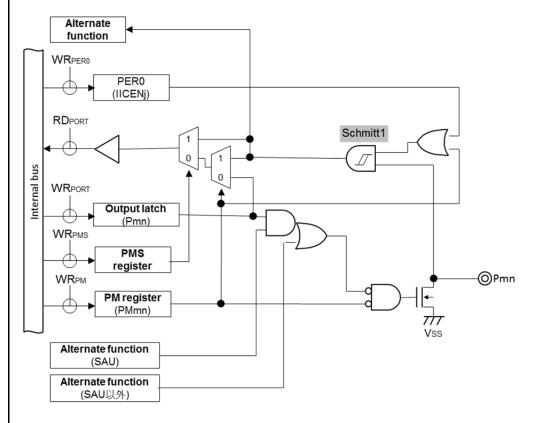

| 2.4 Pin Block Diagrams Figure 2 - 7 Pin Block Diagram of Pin Type 7-5-10  | p.47               | Caution added                  |

| 2.4 Pin Block Diagrams Figure 2 - 11 Pin Block Diagram of Pin Type 7-3-4  | p.51               | Caution added                  |

| 2.4 Pin Block Diagrams Figure 2 - 14 Pin Block Diagram of Pin Type 8-5-10 | p.54               | Caution added                  |

| 2.4 Pin Block Diagrams Figure 2 - 15 Pin Block Diagram of Pin Type 8-3-4  | p.55               | Caution added                  |

| 2.4 Pin Block Diagrams Figure 2 - 16 Pin Block Diagram of Pin Type 12-1-2 | p.56               | Incorrect descriptions revised |

### **Document Improvement**

The above corrections will be made for the next revision of the User's Manual: Hardware.

# **Corrections in the User's Manual: Hardware**

|     |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Corrections and Applicable Items                |                        | Pages in this   |

|-----|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|-----------------|

| No. |                                         | Document No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | English                                         | R01UH0409EJ0200        | document for    |

|     | 2212                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · ·                                             |                        | corrections     |

| 1   |                                         | pecial function registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pages 82 and 83                                 | Page 4 and 5           |                 |

| 2   |                                         | mer mode register r<br>node register mn (TMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page 248                                        | Page 6                 |                 |

| 3   |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | illator trimming register (HIOTRM)              | Page 186               | Page 7          |

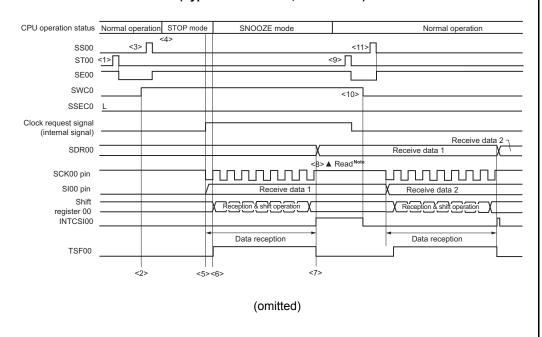

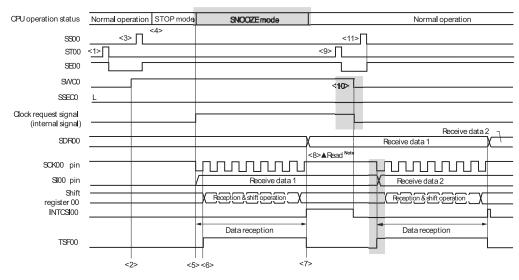

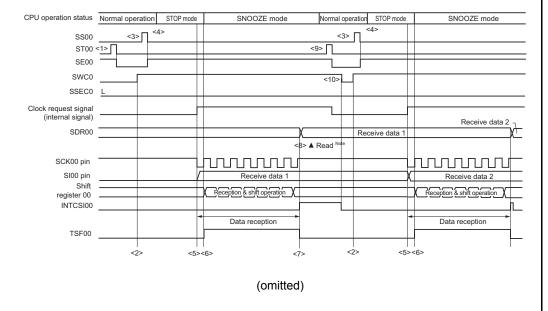

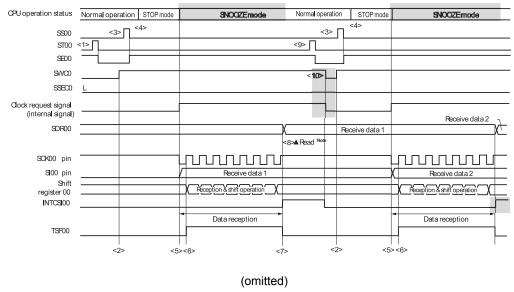

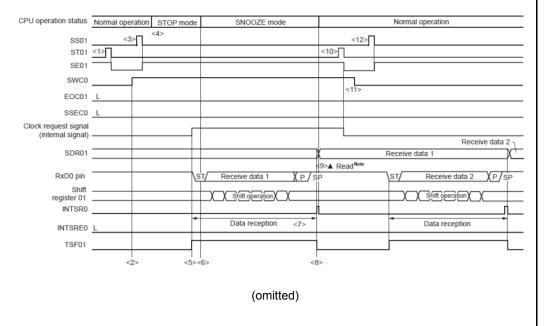

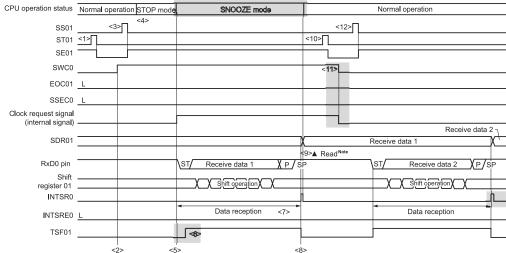

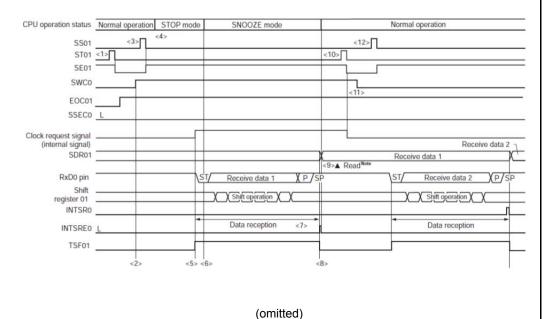

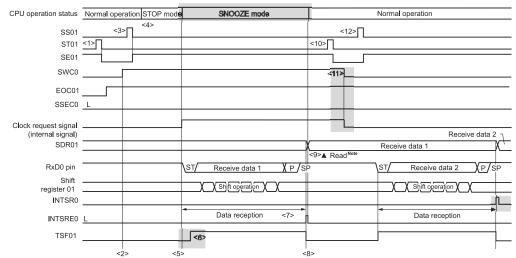

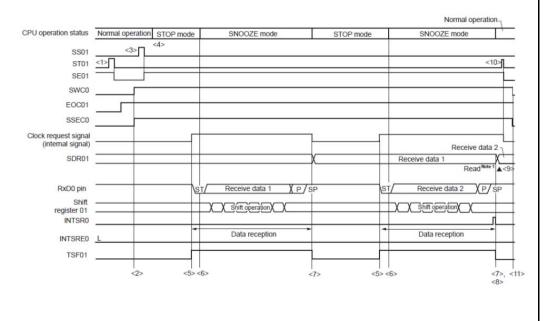

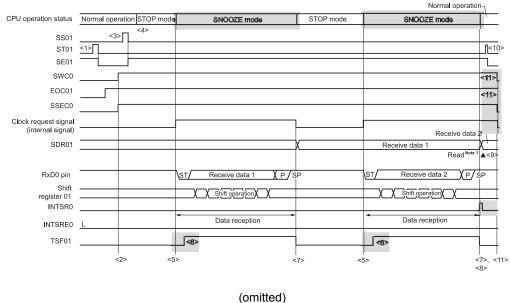

| 4   |                                         | SNOOZE mode function Chart of SNOOZE Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | on<br>de Operation (Figure 14-74. and Figure    | Pages 663 and 665      | Page 8 and 9    |

| 5   | 15.6.3                                  | SNOOZE mode function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | on                                              | Page 688               | Page 10         |

| 6   | Timing                                  | SNOOZE mode function Chart of SNOOZE Industries | on<br>Mode Operation (Figure 15-95., Figure     | Pages 690, 691 and 693 | Page 11 to 13   |

| 7   | 17.4.5.3                                | DTC Transfers (D0F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IFO and D1FIFO Ports)                           | Page 895               | Page 14         |

| 8   | 34.6.1 3                                | 34.6.1 A/D converter of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | haracteristics                                  | Page 1221              | Page 15 and 16  |

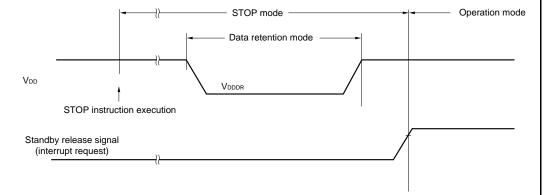

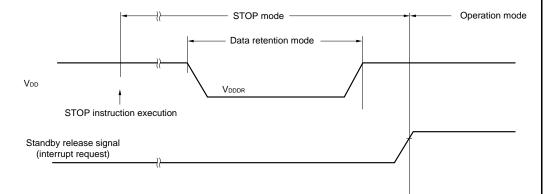

| 9   | 34.9 Da<br>Charact                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | de Low Supply Voltage Data Retention            | Page 1234              | Page 17         |

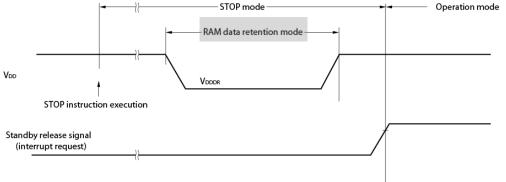

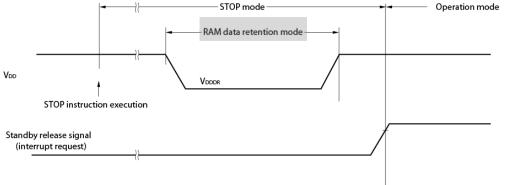

| 10  |                                         | ta Memory STOP Mo<br>cteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | de Low Supply Voltage Data Retention            | Page 1294              | Page 18         |

| 11  | 8.3.4 Re                                | eal-time clock control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | register 1 (RTCC1)                              | Page 457               | Page 19         |

| 12  | 5.2 Con                                 | figuration of Clock Ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | enerator                                        | page 170               | Page 20         |

| 13  | 5.3.2 Sy                                | stem clock control re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | gister (CKC)                                    | page 174               | Page 21         |

| 14  | 5.3.6 Pe                                | eripheral enable regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ters 0, 1, 2 (PER0, PER1, PER2)                 | page 180, 181          | Page 22         |

| 15  | 5.3.10 F                                | PLL control register (D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SCCTL)                                          | page 187               | Page 23         |

| 16  | 5.4.5 PL                                | L (Phase Locked Loc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | op)                                             | page 194               | Page 24         |

| 17  | 5.6.1 Ex                                | cample of setting high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -speed on-chip oscillator                       | page 197               | Pages 25        |

| 18  | 5.6.4 Ex                                | cample of setting PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | circuit                                         | page 199               | Page 26 and 27  |

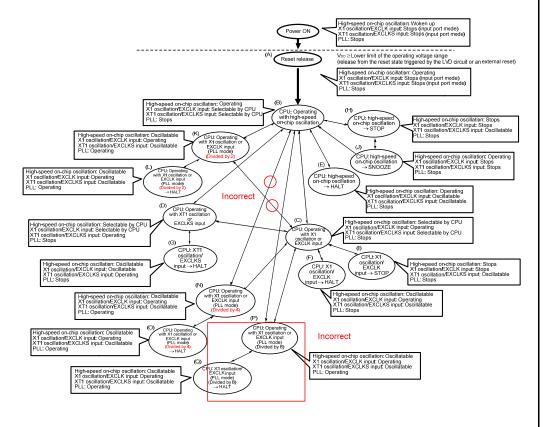

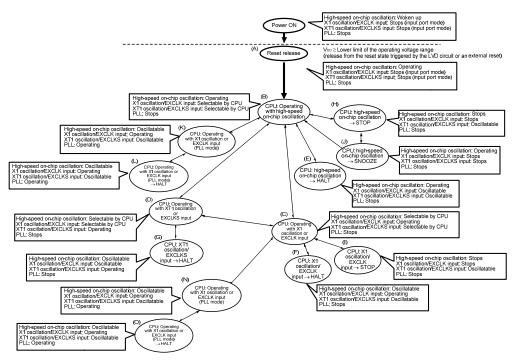

| 19  | 5.6.5 CI                                | PU clock status transi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tion diagram                                    | page 202               | Pages 28        |

| 20  | Table 5                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tion diagram<br>tion and SFR Register Setting   | pages 203 to 209       | Page 29 to 36   |

| 21  |                                         | PU clock status transi<br>- 11 CPU Clock Tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | tion diagram<br>sition and SFR Register Setting | page 213               | Page 37         |

| 22  |                                         | ondition before chang<br>ng CPU clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ing CPU clock and processing after              | pages 216 to 217       | Page 38 and 39  |

| 23  | 6.3.1 Pe                                | eripheral enable regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ter 0 (PER0)                                    | page 240               | Page 40         |

| 24  | 8.3.1 Pe                                | eripheral enable regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ter 0 (PER0)                                    | page 451               | Page 41         |

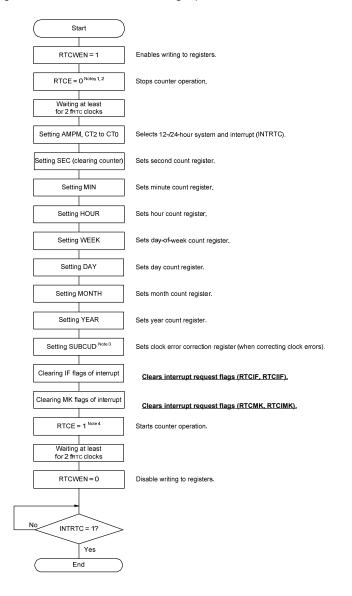

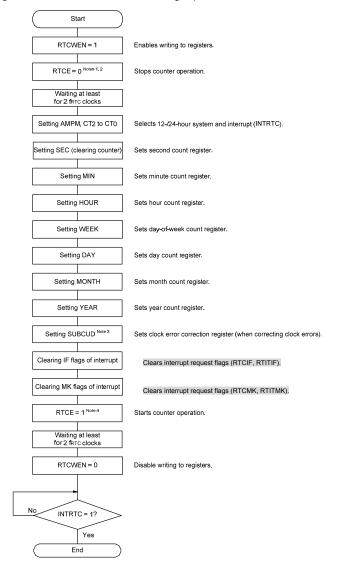

| 25  | 8.4.1 St                                | arting operation of rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | al-time clock 2                                 | page 469               | Page 42         |

| 26  | 12.3.1 F                                | Peripheral enable regi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ster 0 (PER0)                                   | page 502               | Page 43         |

| 27  | 15.3.1 F                                | Peripheral enable regi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ster 0 (PER0)                                   | page 591               | Page 44         |

| 28  | 16.3.1 F                                | Peripheral enable regi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ster 0 (PER0)                                   | page 734               | Pages 45        |

| 29  | 34.1 Ab                                 | solute Maximum Rati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ngs                                             | page 1172              | Page 46         |

| 30  | 34.3.1 F                                | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 | page 1175              | Pages 47 and 48 |

| 31  | 35.1 Absolute Maximum Ratings page 1239 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | page 1239                                       | Page 49                |                 |