#### ISL71444M

19MHz 40V Quad Rail-to-Rail Input-Output, Low-Power Operational Amplifier

The ISL71444M features four radiation tolerant, low-power amplifiers optimized to provide maximum dynamic range. These op amps feature a unique combination of rail-to-rail operation on the input and output as well as a slew enhanced front-end that provides ultra fast slew rates positively proportional to a given step size. They also offer low-power, low-offset voltage, and low temperature drift, making the ISL71444M ideal for applications requiring both high DC accuracy and AC performance.

### **Applications**

- Low Earth Orbit (LEO) applications

- · High altitude avionics

- Precision instruments

- Data acquisition

- Power supply control

#### **Features**

- Qualified to Renesas Rad Tolerant Screening and QCI Flow (R34TB0004EU)

- Passes NASA Low Outgassing specifications

- Unity gain stable with wide gain-bandwidth product: 19MHz

- Wide single and dual supply range: 2.7V to 40V maximum

- Low input offset voltage: 400µV

- Low current consumption (per amplifier): 1.1mA, typical

- High large signal slew rate: 60V/µs

- Operating temperature range: -55°C to +125°C

- 14 Ld TSSOP with NiPdAu lead finish

- TID Radiation Lot Acceptance Testing (LDR: ≤10mrad(Si)/s)

- ISL71444M30: 30krad(Si)

- ISL71444M50: 50krad(Si)

- SEE Characterization

- No DSEE for V<sub>S</sub> = ±20V at 43MeV•cm<sup>2</sup>/mg

- SETs shorter than 1µs at 43MeV•cm<sup>2</sup>/mg

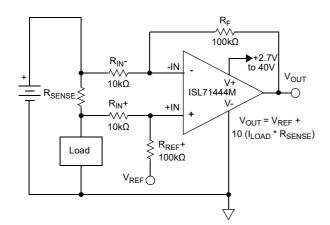

Figure 1. Typical Application: Single-Supply, High-Side Current Sense Amplifier

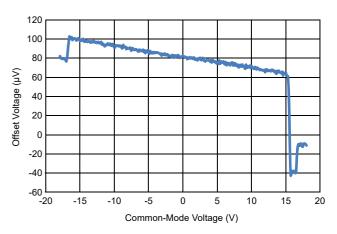

Figure 2. Offset Voltage vs Common-Mode Voltage

# **Contents**

| 1. | Pin I      | Information                           | 3  |

|----|------------|---------------------------------------|----|

|    | 1.1        | Pin Assignments                       | 3  |

|    | 1.2        | Pin Descriptions                      | 3  |

| 2. | Spec       | cifications                           | 4  |

|    | 2.1        | Absolute Maximum Ratings              | 4  |

|    | 2.2        | Outgas Testing                        |    |

|    | 2.3        | Thermal Information                   | 4  |

|    | 2.4        | Recommended Operation Conditions      | 4  |

|    | 2.5        | Electrical Specifications             |    |

|    |            | 2.5.1 VS = ±18V                       |    |

|    |            | 2.5.2 VS = ±2.5V                      |    |

|    |            | 2.5.3 VS = ±1.5V                      |    |

| 3. | Typi       | ical Performance Curves               | 9  |

| 4. | Appl       | olications Information                | 17 |

|    | 4.1        | Functional Description                | 17 |

|    | 4.2        | Operating Voltage Range               |    |

|    | 4.3        | Input Performance                     |    |

|    | 4.4        | Input ESD Diode Protection            |    |

|    | 4.5        | Output Short-Circuit Current Limiting |    |

|    | 4.6<br>4.7 | Output Phase Reversal                 |    |

|    | 4.7        | Slew Rate Enhancement                 |    |

|    | 4.9        | Unused Channel Configuration          |    |

| 5. |            | liation Tolerance                     |    |

|    | 5.1        | Total lonizing Dose (TID) Testing     |    |

|    |            | 5.1.1 Introduction                    |    |

|    |            | 5.1.2 Results                         | 21 |

|    |            | 5.1.3 Conclusion                      | 21 |

|    | 5.2        | Single Event Effects Testing          |    |

|    |            | 5.2.1 Introduction                    |    |

|    |            | 5.2.2 SEE Test Setup                  |    |

|    |            | 5.2.3 SEB/SEL Testing Results         |    |

| _  |            | 5.2.4 Single Event Transient Testing  |    |

| 6. |            | kage Outline Drawing                  |    |

| 7. | Orde       | ering Information                     | 28 |

| 8. | Revi       | rision History                        | 28 |

# 1. Pin Information

# 1.1 Pin Assignments

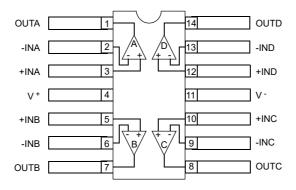

Figure 3. Pin Assignments - Top View

# 1.2 Pin Descriptions

| Pin Number           | Pin Name                | Equivalent ESD<br>Circuit | Description                                    |

|----------------------|-------------------------|---------------------------|------------------------------------------------|

| 1                    | OUTA                    | Circuit 2                 | Amplifier A output                             |

| 2                    | -INA                    | Circuit 1                 | Amplifier A inverting input                    |

| 3                    | +INA                    | Circuit 1                 | Amplifier A non-inverting input                |

| 4                    | V <sup>+</sup>          | Circuit 3                 | Positive power supply                          |

| 5                    | +INB                    | Circuit 1                 | Amplifier B non-inverting input                |

| 6                    | -INB                    | Circuit 1                 | Amplifier B inverting input                    |

| 7                    | OUTB                    | Circuit 2                 | Amplifier B output                             |

| 8                    | OUTC                    | Circuit 2                 | Amplifier C output                             |

| 9                    | -INC                    | Circuit 1                 | Amplifier C inverting input                    |

| 10                   | +INC                    | Circuit 1                 | Amplifier C non-inverting input                |

| 11                   | V-                      | Circuit 3                 | Negative power supply                          |

| 12                   | +IND                    | Circuit 1                 | Amplifier D non-inverting input                |

| 13                   | -IND                    | Circuit 1                 | Amplifier D inverting input                    |

| 14                   | OUTD                    | Circuit 2                 | Amplifier D output                             |

| IN- Ω G00Ω Circuit 1 | V <sup>+</sup> 600Ω IN+ | V+ OUT V- Circuit 2       | V+ Capacitively Triggered ESD Clamp  Circuit 3 |

# 2. Specifications

## 2.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                                                         | Minimum                    | Maximum             | Unit |

|---------------------------------------------------------------------------------------------------|----------------------------|---------------------|------|

| Maximum Supply Voltage                                                                            | -                          | 42                  | V    |

| Maximum Differential Input Current                                                                | -                          | 20                  | mA   |

| Maximum Differential Input Voltage                                                                | 42 or V <sup>-</sup> - 0.5 | V <sup>+</sup> +0.5 | V    |

| Min/Max Input Voltage                                                                             | 42 or V <sup>-</sup> - 0.5 | V+ +0.5             | V    |

| Max/Min Input Current for Input Voltage >V+ or <v-< td=""><td>-</td><td>±20</td><td>mA</td></v-<> | -                          | ±20                 | mA   |

| Maximum Storage Temperature Range                                                                 | -65                        | +150                | °C   |

| Human Body Model (Tested per JS-001-2014)                                                         | -                          | 7                   | kV   |

| Machine Model (Tested per JESD22-A115C)                                                           | -                          | 400                 | V    |

| Charged Device Model (Tested per JS-002-2014)                                                     | -                          | 2                   | kV   |

| Latch-Up (Tested per JESD78E; Class 2, Level A), at +125°C                                        | -                          | 100                 | mA   |

# 2.2 Outgas Testing

| Specification (Tested per ASTM E 595, 1.5)             | Value | Unit |

|--------------------------------------------------------|-------|------|

| Total Mass Lost <sup>[1]</sup>                         | 0.06  | %    |

| Collected Volatile Condensible Material <sup>[1]</sup> | <0.01 | %    |

| Water Vapor Recovered                                  | 0.03  | %    |

<sup>1.</sup> Outgassing results meet NASA requirements of Total Mass Lost <1% and Collected Volatile Condensible Material of <0.1%.

### 2.3 Thermal Information

| Parameter          | Package              | Symbol                         | Conditions          | Typical<br>Value | Unit |

|--------------------|----------------------|--------------------------------|---------------------|------------------|------|

| Thermal Resistance | 14 Ld TSSOP Package  | θ <sub>JA</sub> [1]            | Junction to ambient | 92               | °C/W |

| Thermal Nesistance | 14 Lu 10001 1 ackage | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 30               | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board. See TB379.

## 2.4 Recommended Operation Conditions

| Parameter                              | Minimum   | Maximum  | Unit |

|----------------------------------------|-----------|----------|------|

| Ambient Operating Temperature Range    | -55       | +125     | °C   |

| Maximum Operating Junction Temperature | -         | +150     | °C   |

| Single Supply Voltage                  | 3 ±10%    | 36 ±10%  | V    |

| Split Rail Supply Voltage              | ±1.5 ±10% | ±18 ±10% | V    |

<sup>2.</sup> For  $\theta_{\text{JC}},$  the case temperature location is the top center.

# 2.5 Electrical Specifications

## $V_S = \pm 18V$

$V_{\rm CM} = V_{\rm O} = 0$ V,  $R_{\rm L} = {\rm Open}$ ,  $T_{\rm A} = +25^{\circ}{\rm C}$ , unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ).

| Parameter                                                 | Symbol            | Test Conditions                                                                                             | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit       |

|-----------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------------|

|                                                           |                   | V <sub>CM</sub> = 0V, 30krad(Si)                                                                            | -400               | 100  | 400                | μV         |

| Offset Voltage                                            | $V_{OS}$          | V <sub>CM</sub> = 0V, 50krad(Si) <sup>[2]</sup>                                                             | -500               | 100  | 500                | μV         |

|                                                           |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                                                          | -500               | 130  | 500                | μV         |

| Offset Voltage Temperature Coefficient                    | TCV <sub>OS</sub> | V <sub>CM</sub> = V <sup>+</sup> - 2V to V <sup>-</sup> + 2V                                                | -                  | 0.5  | -                  | μV/°C      |

| Input Offset Channel-to-Channel Match                     | AV                | V <sub>CM</sub> = V <sup>+</sup>                                                                            | -800               | 150  | 800                | μV         |

| input Offset Charmer-to-Charmer Match                     | $\Delta V_{OS}$   | V <sub>CM</sub> = V <sup>-</sup>                                                                            | -800               | 170  | 800                | μV         |

|                                                           |                   | V <sub>CM</sub> = 0V                                                                                        | -                  | 200  | 500                | nA         |

|                                                           |                   | V <sub>CM</sub> = V <sup>+</sup>                                                                            | -                  | 174  | 500                | nA         |

| Input Bias Current                                        | $I_{B}$           | V <sub>CM</sub> = V <sup>-</sup>                                                                            | -                  | 268  | 650                | nA         |

|                                                           |                   | V <sub>CM</sub> = V <sup>+</sup> - 0.5V                                                                     | -                  | 174  | 500                | nA         |

|                                                           |                   | V <sub>CM</sub> = V <sup>-</sup> + 0.5V                                                                     | -                  | 268  | 650                | nA         |

|                                                           |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup> , 30krad(Si)                                             | -30                | 3    | 30                 | nA         |

| Input Offset Current                                      | los               | $V_{CM} = V^{+} \text{ to } V^{-}, 50 \text{krad}(Si)^{[2]}$                                                | -50                | 3    | 50                 | nA         |

|                                                           |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                                                          | -50                | -    | 50                 | nA         |

| Common-Mode Input Voltage Range                           | V <sub>CMIR</sub> | -                                                                                                           | V-                 | -    | V+                 | V          |

| Common-Mode Rejection Ratio                               | CMRR              | V <sub>CM</sub> = V <sup>-</sup> to V <sup>+</sup>                                                          | 70                 | 113  | -                  | dB         |

| Common-wode Rejection Ratio                               |                   | $V_{CM} = V^+ - 0.5V$ to $V^- + 0.5V$                                                                       | 80                 | 113  | -                  | dB         |

| Power Supply Rejection Ratio                              | PSRR              | V <sup>-</sup> = -18V; V <sup>+</sup> = 0.5V to 18V<br>V <sup>+</sup> = 18V; V <sup>-</sup> = -0.5V to -18V | 83                 | 143  | -                  | dB         |

| Open-Loop Gain                                            | A <sub>VOL</sub>  | $R_L = 10k\Omega$ to ground                                                                                 | 90                 | 130  | -                  | dB         |

| Output Voltage High (V to V/t)                            | \/                | R <sub>L</sub> = No load                                                                                    | -                  | 25   | 160                | mV         |

| Output Voltage High (V <sub>OUT</sub> to V <sup>+</sup> ) | V <sub>OH</sub>   | $R_L = 10k\Omega$                                                                                           | -                  | 75   | 175                | mV         |

| Output Voltage Low (V <sub>OUT</sub> to V <sup>-</sup> )  | V                 | R <sub>L</sub> = No load                                                                                    | -                  | 22   | 160                | mV         |

| Output voltage Low (vout to v)                            | $V_{OL}$          | $R_L = 10k\Omega$                                                                                           | -                  | 65   | 175                | mV         |

| Output Short-Circuit Current                              | I <sub>SRC</sub>  | Sourcing; V <sub>IN</sub> = 0V, V <sub>OUT</sub> = -18V                                                     | 10                 | 56   | -                  | mA         |

| Output Short-Circuit Current                              | I <sub>SNK</sub>  | Sinking; V <sub>IN</sub> = 0V, V <sub>OUT</sub> = +18V                                                      | 10                 | 56   | -                  | mA         |

| Supply Current/Amplifier                                  | I <sub>S</sub>    | Unity gain                                                                                                  | -                  | 1.5  | 2.8                | mA         |

| AC Specifications                                         |                   |                                                                                                             |                    |      |                    |            |

| Gain-Bandwidth Product                                    | GBW               | A <sub>CL</sub> = 101, R <sub>L</sub> = 10k                                                                 | -                  | 19   | -                  | MHz        |

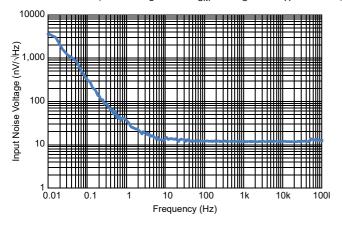

| Voltage Noise Density                                     | e <sub>n</sub>    | f = 10kHz                                                                                                   | -                  | 11.3 | -                  | nV/√H<br>z |

$V_{\rm CM} = V_{\rm O} = 0$ V,  $R_{\rm L} = {\rm Open}$ ,  $T_{\rm A} = +25^{\circ}{\rm C}$ , unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ). (Cont.)

| Parameter              | Symbol         | Test Conditions                                   | Min <sup>[1]</sup> | Тур       | Max <sup>[1]</sup> | Unit       |

|------------------------|----------------|---------------------------------------------------|--------------------|-----------|--------------------|------------|

| Current Noise Density  | i <sub>n</sub> | f = 10kHz                                         | -                  | 0.31<br>2 | -                  | pA/√H<br>z |

| Large Signal Slew Rate | SR             | $A_V = 1$ , $R_L = 10k\Omega$ , $V_O = 10V_{P-P}$ | 60                 | 180       | -                  | V/µs       |

- 1. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

- 2. Radiation Acceptance Test Limit for the ISL71444M50VZ.

### $V_S = \pm 2.5V$

$V_{CM} = V_{O} = 0V$ ,  $R_{L} = Open$ ,  $T_{A} = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ).

| Description                               | Parameter         | Test Conditions                                                                                                                                 | Min <sup>[1]</sup> | Тур | Max <sup>[1]</sup> | Unit  |

|-------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-------|

|                                           |                   | V <sub>CM</sub> = 0V, 30krad(Si)                                                                                                                | -400               | 100 | 400                | μV    |

| Offset Voltage                            | $V_{OS}$          | V <sub>CM</sub> = 0V, 50krad(Si) [2]                                                                                                            | -500               | 100 | 500                | μV    |

|                                           |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                                                                                              | -500               | 130 | 500                | μV    |

| Offset Voltage Temperature<br>Coefficient | TCV <sub>OS</sub> | V <sub>CM</sub> = V <sup>+</sup> - 2V to V <sup>-</sup> + 2V                                                                                    | -                  | 0.5 | -                  | μV/°C |

| Input Offset Channel-to-Channel           | 41/               | V <sub>CM</sub> = V <sup>+</sup>                                                                                                                | -800               | 150 | 800                | μV    |

| Match                                     | $\Delta V_{OS}$   | V <sub>CM</sub> = V-                                                                                                                            | -800               | 180 | 800                | μV    |

|                                           |                   | V <sub>CM</sub> = 0V                                                                                                                            | -                  | 211 | 400                | nA    |

|                                           |                   | V <sub>CM</sub> = V <sup>+</sup>                                                                                                                | -                  | 157 | 400                | nA    |

| Input Bias Current                        | l <sub>B</sub>    | V <sub>CM</sub> = V <sup>-</sup>                                                                                                                | -                  | 235 | 580                | nA    |

|                                           |                   | V <sub>CM</sub> = V <sup>+</sup> - 0.5V                                                                                                         | -                  | 157 | 400                | nA    |

|                                           |                   | V <sub>CM</sub> = V <sup>-</sup> + 0.5V                                                                                                         | -                  | 235 | 580                | nA    |

|                                           | I <sub>OS</sub>   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup> , 30krad(Si)                                                                                 | -30                | 3   | 30                 | nA    |

| Input Offset Current                      |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup> , 50krad(Si) <sup>[2]</sup>                                                                  | -50                | 3   | 50                 | nA    |

|                                           |                   | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                                                                                              | -50                | -   | 50                 | nA    |

| Common-Mode Input Voltage Range           | V <sub>CMIR</sub> | -                                                                                                                                               | V-                 | -   | V+                 | ٧     |

| Common Mode Rejection Retic               | CMDD              | V <sub>CM</sub> = V <sup>-</sup> to V <sup>+</sup>                                                                                              | 70                 | 95  | -                  | dB    |

| Common-Mode Rejection Ratio               | CMRR              | V <sub>CM</sub> = V <sup>+</sup> - 0.5V to V <sup>-</sup> + 0.5V                                                                                | 74                 | 93  | -                  | dB    |

| Downey Comply Deigntion Detic             | Depp              | V <sup>-</sup> = -2.5V; V <sup>+</sup> = 0.5V to 2.5V<br>V <sup>+</sup> = 2.5V; V <sup>-</sup> = -0.5V to -2.5V<br>T <sub>A</sub> = 25°C, 125°C | 80                 | 135 | -                  | dB    |

| Power Supply Rejection Ratio              | PSRR              | $V^- = -2.5V$ ; $V^+ = 0.5V$ to 2.5V<br>$V^+ = 2.5V$ ; $V^- = -0.5V$ to -2.5V<br>$T_A = -55^{\circ}C$                                           | 70                 | 97  | -                  | dB    |

| Open-Loop Gain                            | A <sub>VOL</sub>  | $R_L = 10k\Omega$ to ground                                                                                                                     | 90                 | 120 | -                  | dB    |

$V_{\rm CM} = V_{\rm O} = 0$ V,  $R_{\rm L} = {\rm Open}$ ,  $T_{\rm A} = +25^{\circ}{\rm C}$ , unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ). (Cont.)

| Description                                               | Parameter       | Test Conditions                                  | Min <sup>[1]</sup> | Тур   | Max <sup>[1]</sup> | Unit   |

|-----------------------------------------------------------|-----------------|--------------------------------------------------|--------------------|-------|--------------------|--------|

|                                                           |                 | R <sub>L</sub> = No load                         | -                  | 14    | 85                 | mV     |

| Output Voltage High (V <sub>OUT</sub> to V <sup>+</sup> ) | V <sub>OH</sub> | $R_L = 10k\Omega$                                | -                  | 23    | 105                | mV     |

|                                                           |                 | $R_L = 600\Omega$                                | -                  | 230   | 400                | mV     |

| Output Voltage Low (V <sub>OUT</sub> to V <sup>-</sup> )  |                 | R <sub>L</sub> = No load                         | -                  | 10    | 85                 | mV     |

|                                                           | V <sub>OL</sub> | $R_L = 10k\Omega$                                | -                  | 18    | 105                | mV     |

|                                                           |                 | $R_L = 600\Omega$                                | -                  | 200   | 400                | mV     |

| Supply Current/Amplifier                                  | Is              | Unity gain                                       | -                  | 1.1   | 2.0                | mA     |

| AC Specifications                                         |                 |                                                  |                    |       |                    |        |

| Gain-Bandwidth Product                                    | GBW             | A <sub>CL</sub> = 101, R <sub>L</sub> = 10k      | -                  | 17    | -                  | MHz    |

| Voltage Noise Density                                     | e <sub>n</sub>  | f = 10kHz                                        | -                  | 12.3  | -                  | nV/√Hz |

| Current Noise Density                                     | i <sub>n</sub>  | f = 10kHz                                        | -                  | 0.313 | -                  | pA/√Hz |

| Large Signal Slew Rate                                    | SR              | $A_V = 1$ , $R_L = 10k\Omega$ , $V_O = 3V_{P-P}$ | -                  | 60    | -                  | V/µs   |

- 1. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

- 2. Radiation Acceptance Test Limit for the ISL71444M50VZ.

### $V_S = \pm 1.5V$

$V_{\rm CM} = V_{\rm O} = 0$ V,  $R_{\rm L} = {\rm Open}$ ,  $T_{\rm A} = +25$ °C, unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ).

| Description                                               | Parameter       | Test Conditions                                                                | Min <sup>[1]</sup> | Тур | Max <sup>[1]</sup> | Unit |

|-----------------------------------------------------------|-----------------|--------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                                                           |                 | V <sub>CM</sub> = 0V, 30krad(Si)                                               | -400               | 100 | 400                | μV   |

| Offset Voltage                                            | $V_{OS}$        | V <sub>CM</sub> = 0V, 50krad(Si) [2]                                           | -500               | 100 | 500                | μV   |

|                                                           |                 | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                             | -500               | 130 | 500                | μV   |

| Input Offset Channel-to-Channel                           | A\/             | V <sub>CM</sub> = V <sup>+</sup>                                               | -800               | 150 | 800                | μV   |

| Match                                                     | $\Delta V_{OS}$ | V <sub>CM</sub> = V <sup>-</sup>                                               | -800               | 180 | 800                | μV   |

|                                                           | I <sub>B</sub>  | V <sub>CM</sub> = 0V                                                           | -                  | 176 | 375                | nA   |

|                                                           |                 | V <sub>CM</sub> = V <sup>+</sup>                                               | -                  | 155 | 375                | nA   |

| Input Bias Current                                        |                 | V <sub>CM</sub> = V <sup>-</sup>                                               | -                  | 232 | 565                | nA   |

|                                                           |                 | V <sub>CM</sub> = V <sup>+</sup> - 0.5V                                        | -                  | 155 | 375                | nA   |

|                                                           |                 | V <sub>CM</sub> = V <sup>-</sup> + 0.5V                                        | -                  | 232 | 565                | nA   |

|                                                           |                 | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup> , 30krad(Si)                | -30                | 3   | 30                 | nA   |

| Input Offset Current                                      | Ios             | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup> , 50krad(Si) <sup>[2]</sup> | -50                | 3   | 50                 | nA   |

|                                                           |                 | V <sub>CM</sub> = V <sup>+</sup> to V <sup>-</sup>                             | -50                | -   | 50                 | nA   |

| Common-Mode Input Voltage Range                           | $V_{CMIR}$      |                                                                                | V-                 | -   | V+                 | V    |

| Output Voltage High (V to V/t)                            | V               | R <sub>L</sub> = No load                                                       | -                  | 19  | 50                 | mV   |

| Output Voltage High (V <sub>OUT</sub> to V <sup>+</sup> ) | V <sub>OH</sub> | $R_L = 10k\Omega$                                                              | -                  | 19  | 70                 | mV   |

$V_{\rm CM} = V_{\rm O} = 0$ V, R<sub>L</sub> = Open, T<sub>A</sub> = +25°C, unless otherwise noted. **Boldface limits apply across the operating temperature range**, -55°C to +125°C by characterization with production testing at +25°C; over a total ionizing dose of 30krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M30VZ); or over a total ionizing dose of 50krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s (ISL71444M50VZ). (Cont.)

| Description                                 | Parameter       | Test Conditions                             | Min <sup>[1]</sup> | Тур   | Max <sup>[1]</sup> | Unit   |

|---------------------------------------------|-----------------|---------------------------------------------|--------------------|-------|--------------------|--------|

| Output Voltage Low (V <sub>OUT</sub> to V-) | V               | R <sub>L</sub> = No load                    | -                  | 14    | 50                 | mV     |

| Output voltage Low (V <sub>OUT</sub> to V)  | V <sub>OL</sub> | $R_L = 10k\Omega$                           | -                  | 14    | 70                 | mV     |

| Supply Current/Amplifier                    | I <sub>S</sub>  | Unity Gain                                  | -                  | 1.1   | 2.0                | mA     |

| AC Specifications                           |                 |                                             |                    |       |                    |        |

| Gain-Bandwidth Product                      | GBW             | A <sub>CL</sub> = 101, R <sub>L</sub> = 10k | -                  | 16    | -                  | MHz    |

| Voltage Noise Density                       | e <sub>n</sub>  | f = 10kHz                                   | -                  | 12    | -                  | nV/√Hz |

| Current Noise Density                       | i <sub>n</sub>  | f = 10kHz                                   | -                  | 0.312 | -                  | pA/√Hz |

- 1. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

- 2. Radiation Acceptance Test Limit for the ISL71444M50VZ.

# 3. Typical Performance Curves

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM}$  = 0,  $V_O$  = 0V,  $T_A$  = +25°C.

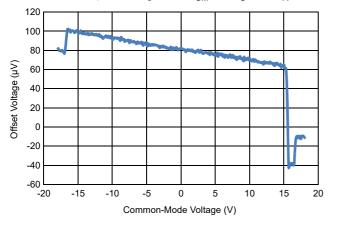

Figure 4. Offset Voltage vs Common-Mode Voltage

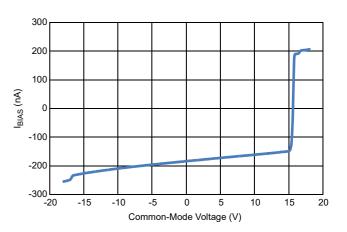

Figure 5. I<sub>BIAS</sub> vs Common-Mode Voltage

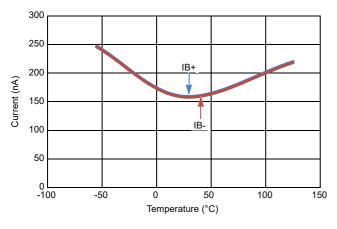

Figure 6.  $I_{BIAS}$  vs Temperature ( $V_S = \pm 18V$ )

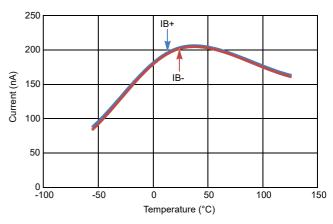

Figure 7.  $I_{BIAS}$  vs Temperature ( $V_S = \pm 2.5V$ )

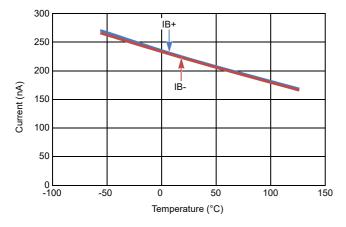

Figure 8.  $I_{BIAS}$  vs Temperature ( $V_{S} = \pm 1.5V$ )

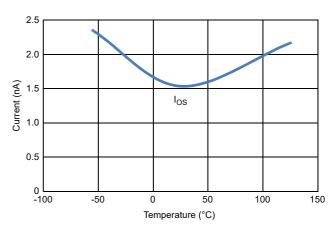

Figure 9.  $I_{OS}$  vs Temperature ( $V_S = \pm 18V$ )

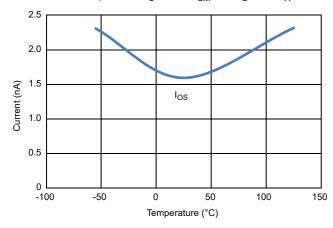

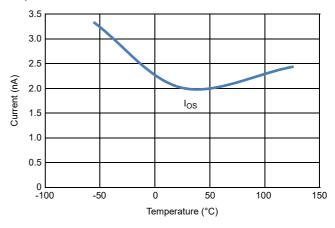

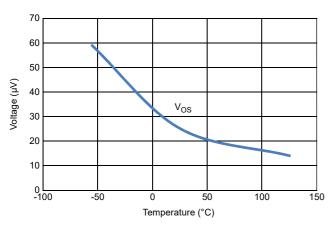

Unless otherwise specified,  $V_S$  ± 18V,  $V_{CM}$  = 0,  $V_O$  = 0V,  $T_A$  = +25°C. (Cont.)

Figure 10.  $I_{OS}$  vs Temperature ( $V_S = \pm 2.5V$ )

Figure 11.  $I_{OS}$  vs Temperature ( $V_S = \pm 1.5V$ )

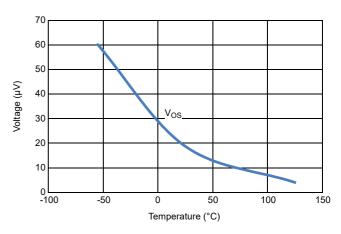

Figure 12.  $V_{OS}$  vs Temperature ( $V_S = \pm 18V$ )

Figure 13.  $V_{OS}$  vs Temperature ( $V_S = \pm 2.5V$ )

Figure 14.  $V_{OS}$  vs Temperature ( $V_{S} = \pm 1.5V$ )

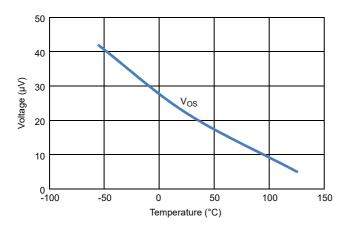

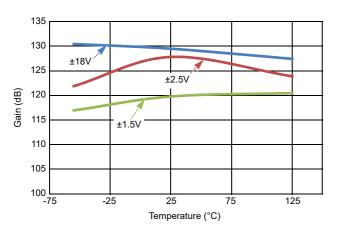

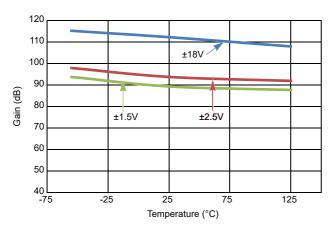

Figure 15.  $A_{VOL}$  vs Temperature vs Supply Voltage

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25^{\circ}C$ . (Cont.)

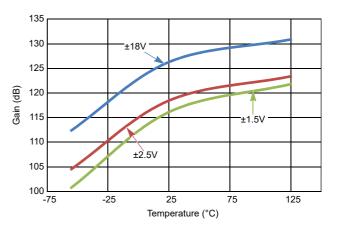

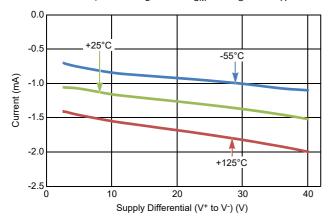

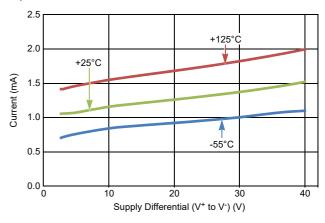

Figure 16. Negative Supply Current vs Supply Voltage

Figure 17. Positive Supply Current vs Supply Voltage

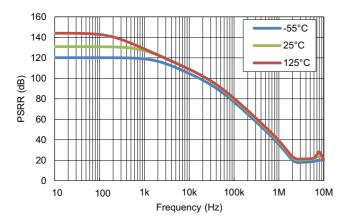

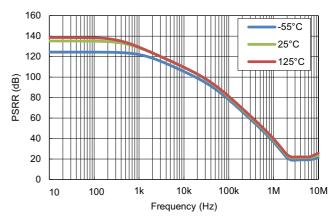

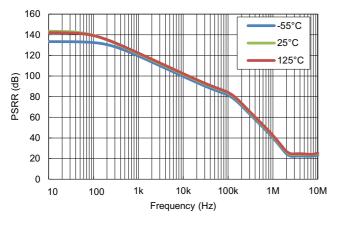

Figure 18. PSRR+ vs Temperature vs Supply Voltage

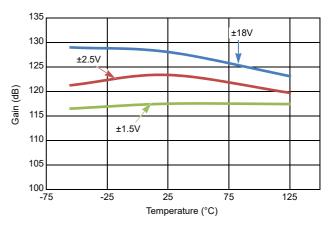

Figure 19. PSRR- vs Temperature vs Supply Voltage

Figure 20. CMRR vs Temperature vs Supply Voltage

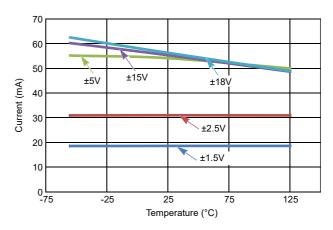

Figure 21. Short-Circuit Current vs Temperature

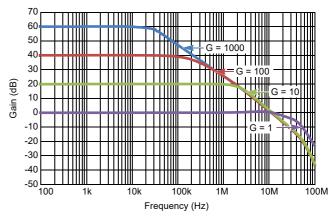

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM}$  = 0,  $V_O$  = 0V,  $T_A$  = +25°C. (Cont.)

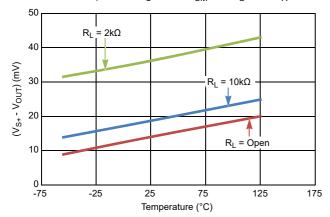

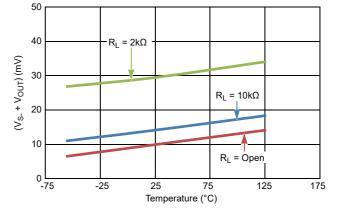

Figure 22. ( $V_S = \pm 1.5V$ )  $V_{OH}$  vs Temperature

Figure 23. ( $V_S = \pm 2.5V$ )  $V_{OH}$  vs Temperature

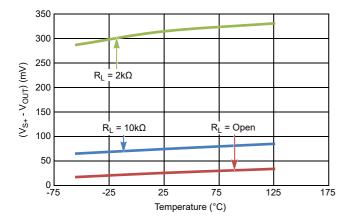

Figure 24. ( $V_S = \pm 18V$ )  $V_{OH}$  vs Temperature

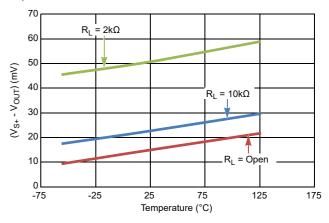

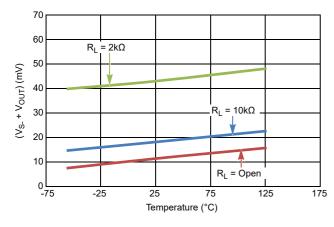

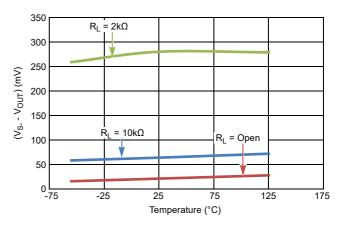

Figure 25. ( $V_S = \pm 1.5V$ )  $V_{OL}$  vs Temperature

Figure 26. ( $V_S = \pm 2.5V$ )  $V_{OL}$  vs Temperature

Figure 27. ( $V_S = \pm 18V$ )  $V_{OL}$  vs Temperature

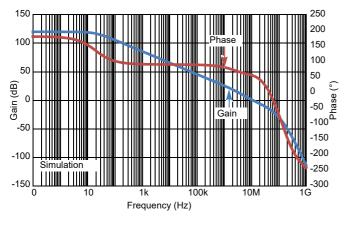

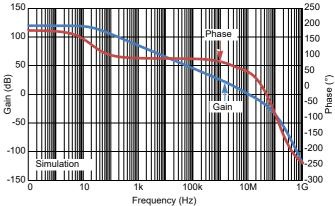

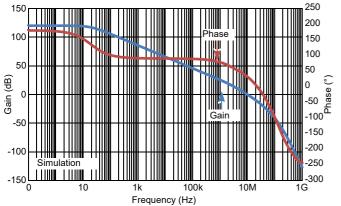

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25$ °C. (Cont.)

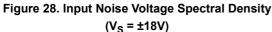

Figure 29. Input Noise Current Spectral Density  $(V_S = \pm 18V)$

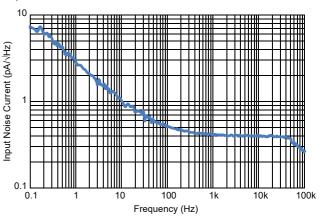

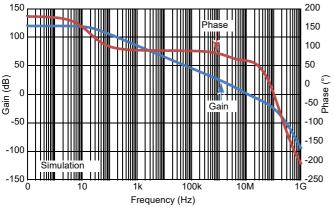

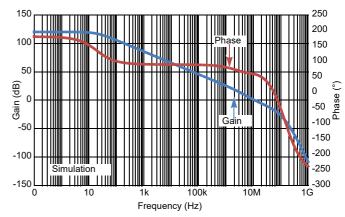

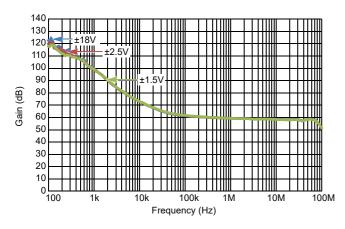

Figure 30. Open-Loop Frequency Response  $(C_L = 0.01pF)$

Figure 31. Open-Loop Frequency Response  $(C_L = 10pF)$

Figure 32. Open-Loop Frequency Response  $(C_L = 22pF)$

Figure 33. Open-Loop Frequency Response  $(C_L = 47pF)$

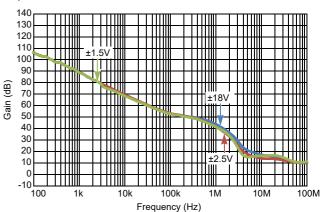

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25^{\circ}C$ . (Cont.)

Figure 34. Open-Loop Frequency Response

(C<sub>1</sub> = 100pF)

Figure 35. CMRR vs Frequency

Figure 36. PSRR vs Frequency ( $V \pm = \pm 1.35V$ )

Figure 37. PSRR vs Frequency ( $V \pm = \pm 2.5V$ )

Figure 38. PSRR vs Frequency (V± = ±18V)

Figure 39. Frequency Response vs Closed-Loop Gain

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25^{\circ}C$ . (Cont.)

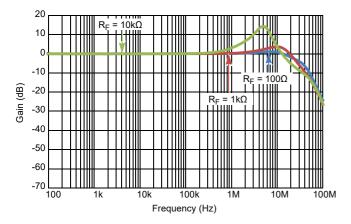

Figure 40. Frequency Response vs Feedback Resistance  $(R_F)$

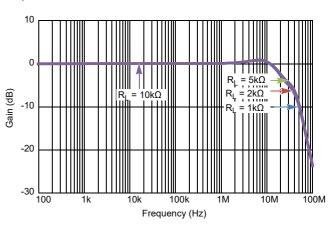

Figure 41. Frequency Response vs Load Resistance

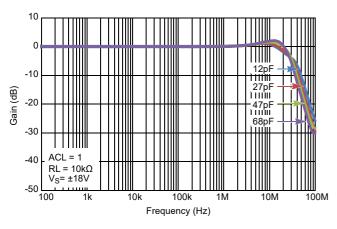

Figure 42. Unity Gain Response vs Load Capacitance

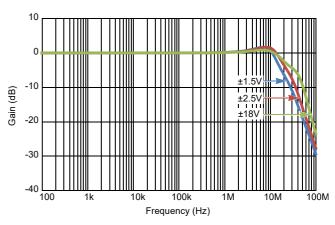

Figure 43. Frequency Response vs Supply Voltage

Figure 44. Crosstalk Rejection

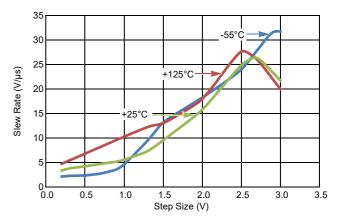

Figure 45. Slew Rate vs Step Size vs Temperature  $(V_S = \pm 1.5V)$

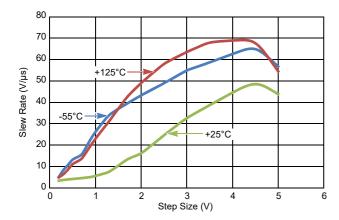

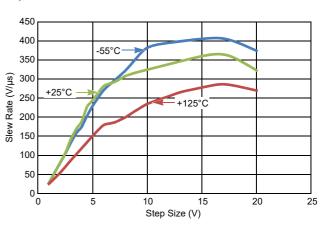

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25$ °C. (Cont.)

Figure 46. Slew Rate vs Step Size vs Temperature  $(V_S = \pm 2.5V)$

Figure 47. Slew Rate vs Step Size vs Temperature  $(V_S = \pm 18V)$

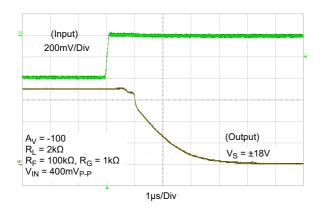

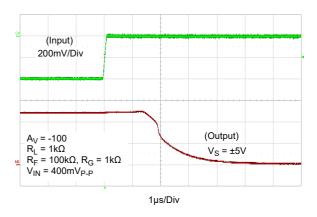

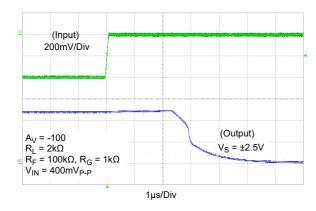

Figure 48. Saturation Recovery ( $V_S = \pm 18V$ )

Figure 49. Saturation Recovery  $(V_S = \pm 5V)$

Figure 50. Saturation Recovery  $(V_S = \pm 2.5V)$

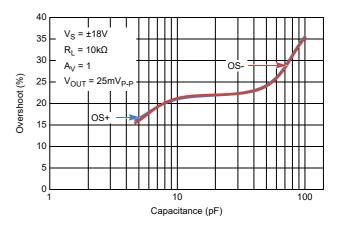

Figure 51. Overshoot (%) vs Load Capacitance

Unless otherwise specified,  $V_S \pm 18V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25$ °C. (Cont.)

Figure 52. Input Overdrive Response

# 4. Applications Information

### 4.1 Functional Description

The ISL71444M contains four high-speed and low-power op amps designed to take advantage of its full dynamic input and output voltage range with rail-to-rail operation. By offering low power, low offset voltage, and low temperature drift coupled with its high bandwidth and enhanced slew rates upwards of 50V/µs, these op amps are ideal for applications requiring both high DC accuracy and AC performance. The ISL71444M is manufactured with the Renesas PR40 silicon-on-insulator process, which makes this device immune to single event latch-up and provides excellent radiation tolerance. This makes it the ideal choice for high reliability applications in harsh radiation-prone environments.

# 4.2 Operating Voltage Range

This device is designed to operate with a split supply rail from  $\pm 1.35$ V to  $\pm 20$ V or a single supply rail from 2.7V to 40V. The ISL71444M is fully characterized in production for supply rails of 5V ( $\pm 2.5$ V) and 36V ( $\pm 18$ V). The power supply rejection ratio is typically 120dB across the full operating voltage range. The worst case common-mode rejection ratio across temperature is within 1.5V to 2V of each rail. When VCM is inside that range, the CMRR performance is typically >110dB with a  $\pm 18$ V supply. The minimum CMRR performance across the -55°C to +125°C temperature range and radiation is >70dB across the full common-mode input range for power supply voltages from  $\pm 2.5$ V (5V) to  $\pm 18$ V (36V).

## 4.3 Input Performance

The slew enhanced front-end is a block that is placed in parallel with the main input stage and functions based on the input differential.

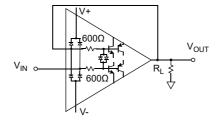

### 4.4 Input ESD Diode Protection

The input terminals (IN+ and IN-) have internal ESD protection diodes to the positive and negative supply rails, series-connected  $600\Omega$  current limiting resistors, and an anti-parallel diode pair across the inputs.

Figure 53. Input ESD Diode Current Limiting, Unity Gain

### 4.5 Output Short-Circuit Current Limiting

The output current limit has a worst case minimum limit of  $\pm 8$ mA but may reach as high as  $\pm 100$ mA. The op amp can withstand a short-circuit to either rail for a short duration (<1s) as long as the maximum operating junction temperature is not violated. This applies to only one amplifier at a given time. Continued use of the device in these conditions may degrade the long-term reliability of the part and is not recommended. Figure 21 shows the typical short-circuit currents that can be expected. The ISL71444M's current limiting circuitry automatically lowers the current limit of the device if short-circuit conditions carry on for extended periods of time. This protects the device from malfunction; however, extended operation in this mode degrades the output rail-to-rail performance by increasing the  $V_{OH}/V_{OL}$  levels.

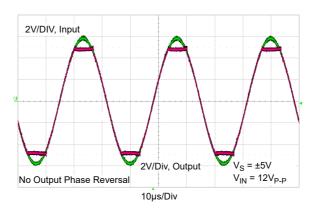

# 4.6 Output Phase Reversal

Output phase reversal is a change of polarity in the amplifier transfer function when the input voltage exceeds the supply voltage. The ISL71444M is immune to output phase reversal, even when the input voltage is 1V beyond the supplies. This is illustrated in Figure 52.

## 4.7 Power Dissipation

It is possible to exceed the +150°C maximum junction temperatures under certain load and power supply conditions. It is therefore important to calculate the maximum junction temperature (T<sub>JMAX</sub>) for all applications to determine if power supply voltages or load conditions need to be modified to remain in the safe operating area. These parameters are related using Equation 1:

(EQ. 1)

$$T_{JMAX} = T_{AMAX} + \theta_{JA} \times PD_{MAXTOTAL}$$

where:

- P<sub>DMAXTOTAL</sub> is the sum of the maximum power dissipation of each amplifier in the package (PD<sub>MAX</sub>)

- PD<sub>MAX</sub> for each amplifier can be calculated using Equation 2:

(EQ. 2)

$$PD_{MAX} = V_S \times I_{qMAX} + (V_S - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_I}$$

where:

- T<sub>AMAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of one amplifier

- V<sub>S</sub> = Total supply voltage

- I<sub>gMAX</sub> = Maximum quiescent supply current of one amplifier

- V<sub>OUTMAX</sub> = Maximum output voltage swing of the application

#### 4.8 Slew Rate Enhancement

The ISL71444M has slew enhanced front-end that increases the drive on the output transistors proportional to the differential voltage across the inputs. This increase in output drive shows up as an increased transient current on top of the op amp's steady-state supply current. If the voltage differential between the inputs remains constant, as in comparator applications, the added drive current to the output transistors becomes steady-state and increases the DC power supply current of the IC. For this reason, Renesas recommends not using the ISL71444M in a comparator configuration.

## 4.9 Unused Channel Configuration

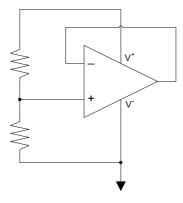

If the application does not require the use of all four op amps, you must configure the unused channels to prevent it from oscillating. Any unused channels oscillate if the input and output pins are floating. This results in higher than expected supply currents and possible noise injection into any of the active channels being used. The proper way to prevent oscillation is to short the output to the inverting input and tie the positive input to a known voltage, such as mid-supply.

When the V- supply is less than or equal to -1.0V, configure your op amp as in Figure 54, otherwise follow the configuration shown in Figure 55. The resistors in Figure 55 are of equal value and high resistance (≥10kΩ) to minimize current draw, while keeping the positive input at mid-supply. All unused op amps can have their inputs tied to the same resistor divider to minimize the number of components.

Tying the positive input to ground in Figure 55 (where V- = GND) produces a voltage differential across the inputs as the inverting input is at the VOL of the op amp and the positive input is at GND, thereby increasing the steady-state supply current. While this does not damage the op amp, the increased supply current can result in additional unnecessary power dissipation.

Figure 54. Preventing Oscillations in Unused Channels

Figure 55. Preventing Oscillations in Unused Channels, Single Supply

### 5. Radiation Tolerance

The ISL71444M is a radiation tolerant device for commercial space applications, Low Earth Orbit (LEO) applications, high altitude avionics, launch vehicles, and other harsh environments. This device's response to Total Ionizing Dose (TID) radiation effects and Single Event Effects (SEE) has been measured, characterized, and reported in the proceeding sections. However, only the ISL71444M50VZ is radiation acceptance tested to 50krad(Si) at LDR (10mrad(Si)/s). TID performance of other versions is not guaranteed through radiation acceptance testing, nor is the characterized SEE performance guaranteed.

### 5.1 Total Ionizing Dose (TID) Testing

#### 5.1.1 Introduction

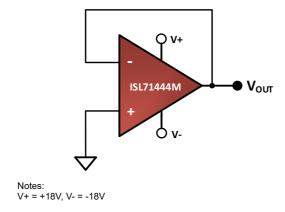

Total dose testing of the ISL71444M proceeded in accordance with the guidelines of MIL-STD-883 Test Method 1019. The experimental matrix consisted of 16 samples irradiated under bias, as shown in Table 1, and 18 samples irradiated with all pins grounded (unbiased). Three control units were used. The bias configuration is shown in Figure 56.

Figure 56. Irradiation Bias Configuration for the ISL71444M

Samples of the ISL71444M were drawn from fabrication lot X7J8AB and were packaged in the production 14 Ld plastic TSSOP, Package Outline Drawing (POD) M14.173. The samples were screened to datasheet limits at room temperature only, before irradiation.

Total dose irradiations were performed using a Hopewell Designs N40 panoramic vault-type low dose rate 60Co irradiator located in the Renesas Palm Bay, Florida facility. The dose rate was 0.01rad(Si)/s (10mrad(Si)/s). PbAl spectrum hardening filters were used to shield the test board and devices under test against low energy secondary gamma radiation.

Downpoints for the testing were 0krad(Si), 10krad(Si), 30krad(Si), and 50krad(Si).

All electrical testing was performed outside the irradiator using production Automated Test Equipment (ATE) with data logging of all parameters at each downpoint. All downpoint electrical testing was performed at room temperature.

#### 5.1.2 Results

Table 1 summarizes the attributes data. Bin 1 indicates a device that passes all datasheet specification limits.

Table 1. ISL71444M Total Dose Test Attributes Data

| Dose Rate<br>(mrad(Si)/s) | Bias      | Sample Size | Down Point | Bin 1 | Rejects |

|---------------------------|-----------|-------------|------------|-------|---------|

|                           |           |             | Pre-rad    | 16    |         |

| 10                        | Eiguro 56 | 16          | 10krad(Si) | 16    | 0       |

| 10                        | Figure 56 |             | 30krad(Si) | 16    | 0       |

|                           |           |             | 50krad(Si) | 16    | 0       |

|                           |           | 18          | Pre-rad    | 18    |         |

| 40                        | Grounded  |             | 10krad(Si) | 18    | 0       |

| 10                        |           |             | 30krad(Si) | 18    | 0       |

|                           |           |             | 50krad(Si) | 18    | 0       |

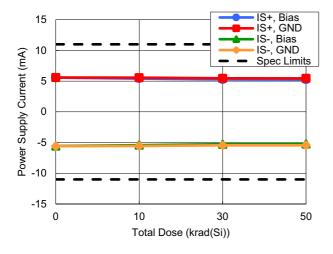

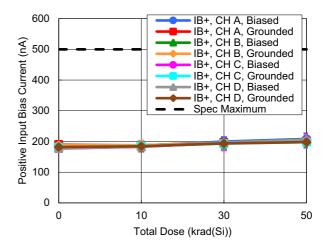

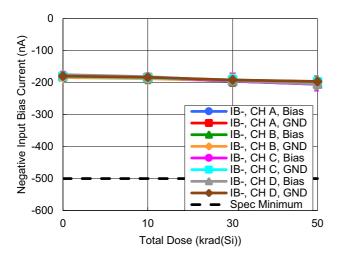

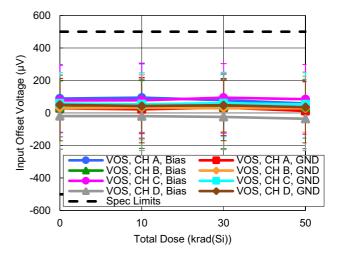

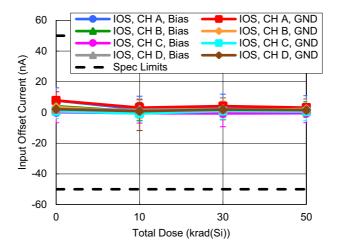

The plots in Figure 57 through Figure 61 show data for key parameters at all downpoints. The plots show the average as a function of total dose for each of the irradiation conditions. All parts showed excellent stability over irradiation.

Table 2 shows the average of other key parameters with respect to total dose in tabular form.

#### 5.1.3 Conclusion

As shown in Table 2 and the selected graphs (Figure 57 through Figure 61), all parameters showed excellent stability over irradiation, with no observed bias sensitivity. For brevity, only the ±18V results are shown; the ±2.5V and ±1.5V results were just as stable.

Figure 57. Operating Supply Current vs TID  $V_S = \pm 18V$

Figure 58. Positive Input Bias Current vs TID ( $V_S = \pm 18V$ )

Figure 59. Negative Input Bias Current vs TID ( $V_S = \pm 18V$ )

Figure 60. Input Offset Voltage vs TID ( $V_S = \pm 18V$ )

Figure 61. Input Offset Current vs TID ( $V_S = \pm 18V$ )

Table 2. ISL71444M Response of Key Parameters vs. TID ( $V_S = \pm 18V$ )

| Parameter                                                          | Condition       | Bias           | 0krad(Si) | 10krad(Si) | 30krad(Si) | 50krad(Si) | Unit |  |

|--------------------------------------------------------------------|-----------------|----------------|-----------|------------|------------|------------|------|--|

|                                                                    | I <sub>S+</sub> | Avg (Biased)   | 5.56      | 5.42       | 5.28       | 5.24       |      |  |

| Quad Power Supply<br>Current (Positive)                            |                 | Avg (Unbiased) | 5.59      | 5.56       | 5.46       | 5.45       | mA   |  |

| $V_S = \pm 18.0V$                                                  |                 | Limit -        | -         | -          | -          | -          |      |  |

|                                                                    |                 | Limit +        | 11        | 11         | 11         | 11         |      |  |

| Quad Power Supply<br>Current (Negative)<br>V <sub>S</sub> = ±18.0V | I <sub>S-</sub> | Avg (Biased)   | -5.56     | -5.42      | -5.28      | -5.24      | - mA |  |

|                                                                    |                 | Avg (Unbiased) | -5.59     | -5.56      | -5.46      | -5.45      |      |  |

|                                                                    |                 | Limit -        | -11       | -11        | -11        | -11        |      |  |

|                                                                    |                 | Limit +        | -         | -          | -          | -          |      |  |

Table 2. ISL71444M Response of Key Parameters vs. TID ( $V_S = \pm 18V$ ) (Cont.)

| Parameter                                                 | Condition             | Bias           | 0krad(Si) | 10krad(Si) | 30krad(Si) | 50krad(Si) | Unit |  |  |

|-----------------------------------------------------------|-----------------------|----------------|-----------|------------|------------|------------|------|--|--|

| Power Supply                                              |                       | Avg (Biased)   | 1.39      | 1.35       | 1.32       | 1.31       |      |  |  |

| Current/Amplifier                                         |                       | Avg (Unbiased) | 1.40      | 1.39       | 1.37       | 1.36       | m A  |  |  |

| (Positive)                                                | I <sub>S+</sub>       | Limit -        | -         | -          | -          | -          | mA   |  |  |

| $V_{S} = \pm 18.0V$                                       |                       | Limit +        | 2.75      | 2.75       | 2.75       | 2.75       |      |  |  |

| D 0 1                                                     |                       | Avg (Biased)   | -1.39     | -1.35      | -1.32      | -1.31      |      |  |  |

| Power Supply<br>Current/Amplifier                         |                       | Avg (Unbiased) | -1.40     | -1.39      | -1.36      | -1.36      | mΛ   |  |  |

| (Negative)                                                | I <sub>S-</sub>       | Limit -        | -2.75     | -2.75      | -2.75      | -2.75      | mA   |  |  |

| $V_{S} = \pm 18.0V$                                       |                       | Limit +        | -         | -          | -          | -          |      |  |  |

|                                                           |                       | Avg (Biased)   | 44.78     | 48.90      | 46.66      | 34.94      |      |  |  |

| Input Offset Voltage                                      | .,                    | Avg (Unbiased) | 41.85     | 37.94      | 42.64      | 32.63      | /    |  |  |

| $V_S = \pm 18.0V$<br>$V_{CM} = 0V$                        | V <sub>OS</sub>       | Limit -        | -500.00   | -500.00    | -500.00    | -500.00    | μV   |  |  |

| CIM O                                                     |                       | Limit +        | 500.00    | 500.00     | 500.00     | 500.00     |      |  |  |

|                                                           |                       | Avg (Biased)   | 181.19    | 184.42     | 197.09     | 206.40     |      |  |  |

| Positive Input Bias<br>Current                            | as<br>I <sub>B+</sub> | Avg (Unbiased) | 185.23    | 186.24     | 194.88     | 199.82     |      |  |  |

| $V_{S} = \pm 18.0V$                                       |                       | Limit -        | -         | -          | -          | -          | nA   |  |  |

| $V_{CM} = 0V$                                             |                       | Limit +        | 500.00    | 500.00     | 500.00     | 500.00     |      |  |  |

| Negative Input Bias<br>Current<br>V <sub>S</sub> = ±18.0V | I <sub>B-</sub>       | Avg (Biased)   | -177.52   | -183.39    | -195.32    | -204.68    |      |  |  |

|                                                           |                       | Avg (Unbiased) | -181.53   | -185.11    | -192.65    | -197.74    |      |  |  |

|                                                           |                       | Limit -        | -500.00   | -500.00    | -500.00    | -500.00    | nA   |  |  |

| $V_{CM} = 0V$                                             |                       | Limit +        | -         | -          | -          | -          |      |  |  |

|                                                           |                       | Avg (Biased)   | 3.53      | 1.02       | 1.57       | 1.54       | nA   |  |  |

| Input Offset Current                                      |                       | Avg (Unbiased) | 3.55      | 0.95       | 2.02       | 1.88       |      |  |  |

| $V_S = \pm 18.0V$<br>$V_{CM} = 0V$                        | I <sub>OS</sub>       | Limit -        | -50.00    | -50.00     | -50.00     | -50.00     |      |  |  |

| vCM - ov                                                  |                       | Limit +        | 50.00     | 50.00      | 50.00      | 50.00      |      |  |  |

|                                                           |                       | Avg (Biased)   | 23.72     | 26.80      | 24.30      | 23.87      |      |  |  |

| Output Voltage High                                       |                       | Avg (Unbiased) | 23.53     | 26.85      | 24.41      | 24.12      |      |  |  |

| $V_S = \pm 18.0V$<br>$R_L = No Load$                      | V <sub>OH</sub>       | Limit -        | -         | -          | -          | -          | mV   |  |  |

| NL - No Load                                              |                       | Limit +        | 160.00    | 160.00     | 160.00     | 160.00     |      |  |  |

|                                                           |                       | Avg (Biased)   | 22.46     | 24.86      | 22.96      | 23.39      |      |  |  |

| Output Voltage Low                                        |                       | Avg (Unbiased) | 22.46     | 24.38      | 22.71      | 22.99      |      |  |  |

| $V_S = \pm 18.0V$<br>$R_L = No Load$                      | V <sub>OL</sub>       | Limit -        | -         | -          | -          | -          | mV   |  |  |

|                                                           |                       | Limit +        | 160.00    | 160.00     | 160.00     | 160.00     |      |  |  |

|                                                           |                       | Avg (Biased)   | 126.44    | 126.34     | 125.55     | 123.28     |      |  |  |

| Open Loop Gain<br>(Positive)                              |                       | Avg (Unbiased) | 126.25    | 126.42     | 126.01     | 124.77     |      |  |  |

| $V_{S} = \pm 18.0V$                                       | A <sub>VOL+</sub>     | Limit -        | 96.00     | 96.00      | 96.00      | 96.00      | dB   |  |  |

| $R_L = 10k\Omega$                                         |                       | Limit +        | _         | -          | -          | -          |      |  |  |

Table 2. ISL71444M Response of Key Parameters vs. TID ( $V_S = \pm 18V$ ) (Cont.)

| Parameter                                        | Condition        | Bias           | 0krad(Si) | 10krad(Si) | 30krad(Si) | 50krad(Si) | Unit |  |  |

|--------------------------------------------------|------------------|----------------|-----------|------------|------------|------------|------|--|--|

| Open Loop Gain                                   |                  | Avg (Biased)   | 126.90    | 126.71     | 126.34     | 124.46     |      |  |  |

| (Negative)                                       |                  | Avg (Unbiased) | 127.03    | 126.73     | 126.74     | 125.40     | dВ   |  |  |

| $V_S = \pm 18.0V$                                | A <sub>VOL</sub> | Limit -        | 96.00     | 96.00      | 96.00      | 96.00      | dB   |  |  |

| $R_L = 10k\Omega$                                |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Power Supply Rejection                           |                  | Avg (Biased)   | 128.51    | 128.07     | 127.93     | 128.11     |      |  |  |

| Ratio (Positive)                                 | PSRR+            | Avg (Unbiased) | 127.60    | 127.74     | 127.64     | 128.03     | dB   |  |  |

| $V_{S+} = +18.0V$                                | PORRT            | Limit -        | 83.00     | 83.00      | 83.00      | 83.00      | иь   |  |  |

| V <sub>S-</sub> = -0.5V to -18.0V                |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Power Supply Rejection                           |                  | Avg (Biased)   | 123.27    | 123.32     | 123.29     | 123.39     |      |  |  |

| Ratio (Negative)                                 | Denn             | Avg (Unbiased) | 123.45    | 123.70     | 123.34     | 123.42     | dB   |  |  |

| $V_{S-} = -18.0V$                                | PSRR-            | Limit -        | 83.00     | 83.00      | 83.00      | 83.00      |      |  |  |

| $V_{S+} = 0.5V \text{ to } 18.0V$                |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Common Mode                                      | CMRR             | Avg (Biased)   | 111.59    | 111.45     | 111.59     | 111.03     | dB   |  |  |

| Rejection Ratio                                  |                  | Avg (Unbiased) | 111.13    | 110.54     | 111.04     | 111.41     |      |  |  |

| $V_S = \pm 18.0V$                                |                  | Limit -        | 70.00     | 70.00      | 70.00      | 70.00      |      |  |  |

| $V_{CM} = -18.0V \text{ to } 18.0V$              |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Common Mode                                      |                  | Avg (Biased)   | 111.49    | 111.39     | 111.63     | 111.04     |      |  |  |

| Rejection Ratio                                  | CMDD             | Avg (Unbiased) | 111.07    | 110.59     | 111.10     | 111.40     | ٩D   |  |  |

| $V_S = \pm 18.0V$                                | CMRR             | Limit -        | 80.00     | 80.00      | 80.00      | 80.00      | dB   |  |  |

| V <sub>CM</sub> = -17.5V to 17.5V                |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Large Signal Slew Rate                           |                  | Avg (Biased)   | 128.81    | 250.66     | 134.77     | 127.67     |      |  |  |

| (Rising)<br>V <sub>S</sub> = ±18.0V, Gain = 1,   | CD.              | Avg (Unbiased) | 128.04    | 246.64     | 132.49     | 126.06     | Muo  |  |  |

| $R_L = 2k\Omega$ ,                               | SR <sub>R</sub>  | Limit -        | 60.00     | 60.00      | 60.00      | 60.00      | V/µs |  |  |

| $V_{OUT} = 10V_{P-P}$                            |                  | Limit +        | -         | -          | -          | -          |      |  |  |

| Large Signal Slew Rate                           |                  | Avg (Biased)   | 172.55    | 197.26     | 173.13     | 160.97     |      |  |  |

| (Falling)<br>V <sub>S</sub> = ±18.0V, Gain = 1,  | QD.              | Avg (Unbiased) | 171.83    | 200.02     | 170.58     | 158.51     | \//  |  |  |

| $V_S = 116.0V$ , Gain = 1,<br>$R_L = 2k\Omega$ , | SR <sub>F</sub>  | Limit -        | 60.00     | 60.00      | 60.00      | 60.00      | V/µs |  |  |

| V <sub>OUT</sub> = 10V <sub>P-P</sub>            |                  | Limit +        | -         | -          | -          | -          |      |  |  |

# 5.2 Single Event Effects Testing

### 5.2.1 Introduction

The intense heavy ion environment encountered in space applications can cause a variety of Single Event Effects (SEE). SEE can lead to system-level performance issues including disruption, degradation, and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response. The following is a summary of the ISL71444M SEE testing.

### 5.2.2 SEE Test Setup

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility. This facility is coupled to a K500 super-conducting cyclotron, which is capable of generating a wide range of test particles with the various energy, flux, and fluence levels needed for advanced radiation testing.

The test circuit is a non-inverting configuration with a gain of 10. Digital multimeters were used to monitor the supply voltage (V+/V-), output voltage (V<sub>OUT</sub>), and supply current (I+/I-). The outputs were monitored using four LeCroy 4-channel digital oscilloscopes to capture and store the signal waveforms. Table 3 shows the scope configuration used during the testing.

| Scope | CH 1 | CH 2 | CH 3 | CH 4 | Trigger         |

|-------|------|------|------|------|-----------------|

| 1     | OUTA | OUTB | OUTC | OUTD | CH1, 1% of OUTA |

| 2     | OUTA | OUTB | OUTC | OUTD | CH2, 1% of OUTB |

| 3     | OUTA | OUTB | OUTC | OUTD | CH3, 1% of OUTC |

| 4     | OUTA | OUTB | OUTC | OUTD | CH4, 1% of OUTD |

Table 3. Oscilloscope Setup for SET Testing

### 5.2.3 SEB/SEL Testing Results

A failure due to burnout was indicated by a permanent change to the part's supply current or output voltage after the beam was turned off. If the part's supply current or output voltage reverted back to its pre-exposure value after a power cycle, the event was deemed as latch-up. A failure for burnout was indicated by a  $\pm 4\%$  delta (which would allow for measurement repeatability) in supply current or output voltage. The ISL71444M units did not exceed the aforementioned limits with  $V_S = \pm 20V$  at an LET of  $43 \text{MeV} \cdot \text{cm}^2/\text{mg}$  and therefore are deemed as passing. The output voltage of the amplifiers had a 0% delta pre and post exposure for all channels and all parts and therefore are not shown for brevity.

| Unit | Unit Temp (°C) |         | Current<br>posure | Supply<br>Post-Ex | SEB/L   |      |

|------|----------------|---------|-------------------|-------------------|---------|------|

|      |                | I+ (mA) | I- (mA)           | I+ (mA)           | I- (mA) |      |

| 1    | +125           | 8.54    | 7.52              | 8.26              | 7.53    | Pass |

| 2    | +125           | 9.18    | 8.44              | 9.15              | 8.41    | Pass |

| 3    | +125           | 8.10    | 7.37              | 8.08              | 7.36    | Pass |

| 4    | +125           | 8.07    | 7.34              | 8.06              | 7.33    | Pass |

Table 4. SEB/SEL Results (V<sub>S</sub> = ±20V, LET = 43MeV•cm<sup>2</sup>/mg)

### 5.2.4 Single Event Transient Testing

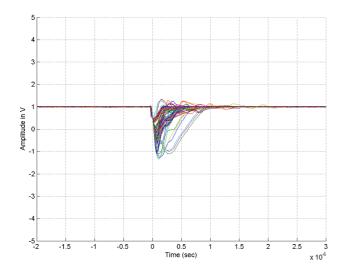

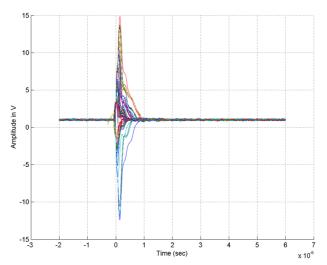

Single Event Transient (SET) testing was conducted in a gain of 10 non-inverting with a 0.1V input with a supply voltage of ±1.35V and an input of 0.2V with supplies at ±15.0V.

The plots in Figure 62 and Figure 63 show the typical SET performance of the ISL71444M at LET =  $43\text{MeV} \cdot \text{cm}^2/\text{mg}$ . Fluence was run at  $2 \times 10^6/\text{cm}^2$ .

Figure 62. SET Response with  $V_S = \pm 1.35V$

Figure 63. SET Response with  $V_S = \pm 15.0V$

With an LET = 43MeV•cm²/mg, all transients lasted no longer than 1µs regardless of supply voltage. Voltage deviations were predominantly negative-going down to -1.35V with supplies at ±1.35V. With ±15V supplies, the voltage deviations were both positive up to +15V and negative down to approximately -12V.

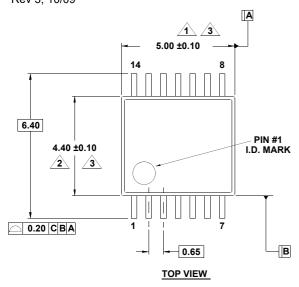

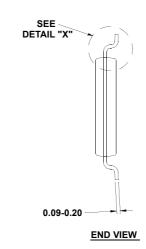

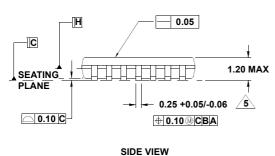

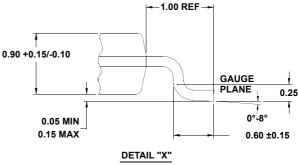

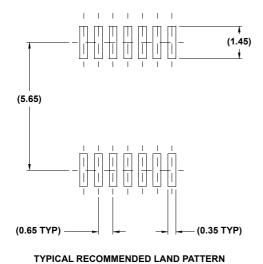

# 6. Package Outline Drawing

For the most recent package outline drawing, see M14.173.

M14 173

14 LD Thin Shrink Small Outline Package (TSSOP) Rev 3, 10/09

#### NOTES:

- Dimension does not include mold flash, protrusions or gate burrs.

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- Dimension does not include dambar protrusion. Allowable protrusion shall be 0.80mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153, variation AB-1.

# 7. Ordering Information

| Part Number <sup>[1]</sup> | Part<br>Marking | Radiation<br>Lot<br>Acceptance<br>Testing | TID Data<br>Pack<br>Included | Package<br>Description <sup>[2]</sup><br>(RoHS Compliant) | Pkg.<br>Dwg. # | MSL<br>Rating <sup>[3]</sup> | Carrier<br>Type <sup>[4]</sup> | Temp<br>Range    |  |  |  |  |  |  |

|----------------------------|-----------------|-------------------------------------------|------------------------------|-----------------------------------------------------------|----------------|------------------------------|--------------------------------|------------------|--|--|--|--|--|--|

| ISL71444MVZ                |                 |                                           |                              |                                                           |                |                              | Tube                           |                  |  |  |  |  |  |  |

| ISL71444MVZ-T              | 71444<br>MVZ    | N/A                                       | No                           | 14 Ld TSSOP                                               | M14.173        | 1                            | Reel,<br>2.5k                  | -55 to<br>+125°C |  |  |  |  |  |  |

| ISL71444MVZ-T7A            |                 |                                           |                              |                                                           |                |                              | Reel,<br>250                   |                  |  |  |  |  |  |  |

| ISL71444M30VZ              |                 |                                           |                              |                                                           |                |                              | Tube                           |                  |  |  |  |  |  |  |

| ISL71444M30VZ-T            | 71444<br>MVZ    | 30krad(Si)                                | Yes                          | 14 Ld TSSOP                                               | M14.173        | 1                            | Reel,<br>2.5k                  | -55 to<br>+125°C |  |  |  |  |  |  |

| ISL71444M30VZ-<br>T7A      |                 |                                           |                              |                                                           |                |                              | Reel,<br>250                   |                  |  |  |  |  |  |  |

| ISL71444M50VZ              |                 |                                           |                              |                                                           |                |                              | Tube                           |                  |  |  |  |  |  |  |

| ISL71444M50VZ-T            | 71444<br>MVZ    | 50krad(Si)                                | Yes                          | 14 Ld TSSOP                                               | M14.173        | 1                            | Reel,<br>2.5k                  | -55 to<br>+125°C |  |  |  |  |  |  |

| ISL71444M50VZ-<br>T7A      |                 |                                           |                              |                                                           |                |                              | Reel,<br>250                   |                  |  |  |  |  |  |  |

| ISL71444MEVAL1Z            | Evaluation      | Board                                     |                              |                                                           |                |                              |                                | Evaluation Board |  |  |  |  |  |  |

<sup>1.</sup> These Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu-Ag plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 2. For the Pb-Free Reflow Profile, see TB493.

- 3. Moisture Sensitivity Level (MSL) tested per JEDEC J-STD-020. For more information about MSL, see TB363.

- 4. See TB347 for details about reel specifications.

# 8. Revision History

| Rev. | Date         | Description                                                                                                                                                                                         |  |  |  |  |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3.03 | Jun 25, 2025 | Updated Feature bullets. Added MVZ parts back.                                                                                                                                                      |  |  |  |  |

| 3.02 | Dec 12, 2024 | On page 1 in Figure 1 updated the V <sub>OUT</sub> equation.                                                                                                                                        |  |  |  |  |

| 3.01 | Nov 16, 2023 | Applied the latest template and formatting. Removed Related Literature section. Added ISL71444M30 and ISL71444M50 information throughout the document. Removed MVZ parts.                           |  |  |  |  |

| 3.00 | Nov 6, 2020  | Electrical Spec table, Power Supply Rejection Ratio: $V_S = \pm 18V$ , changed Typ from 130dB to 143dB $V_S = \pm 2.5V$ , changed Typ from 125dB to 135dB Replaced Figure 35 with three PSRR charts |  |  |  |  |

| 2.00 | Aug 16, 2019 | Updated links throughout document. Added Slew Rate Enhancement section. Updated Unused Channel Configuration section. Updated disclaimer.                                                           |  |  |  |  |

### ISL71444M Datasheet

| Rev. | Date        | Description                                                                                                                                 |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00 | Apr 6, 2018 | Added Features bullet on page 1.  Added Section 2.2 Outgas Testing on page 5.  Removed About Intersil section and added Renesas disclaimer. |

| 0.00 | Jun 6, 2017 | Initial release                                                                                                                             |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.