# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

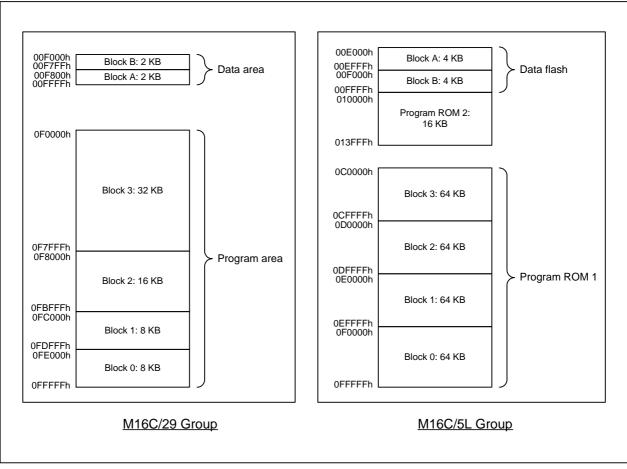

# M16C/29 Group, M16C/5L Group Differences between M16C/29 and M16C/5L

# 1. Abstract

This document describes differences between M16C/29 80-pin version and M16C/5L 80-pin version. Refer to each device's hardware manual for details.

# 2. Introduction

The explanation of this application note is applied to the following MCUs: Applicable MCUs: M16C/29 80-pin version, M16C/5L 80-pin version

# 3. Differences

# 3.1 Differences in Functions

Table 3.1.1 and Table 3.1.2 list Differences in Functions.

| Table 3.1.1         Differences in Functions (1/2) (1) | (1) |

|--------------------------------------------------------|-----|

|--------------------------------------------------------|-----|

| Item                                  |                                                                  | M16C/29                                                                                                                                                                                                                                                                                      | M16C/5L                                                                                                                     |  |

|---------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Minimum Instruction<br>Execution Time |                                                                  | 50 ns (f(BCLK) = 20 MHz, VCC = 3.0 to 5.5 V)<br>(Normal-ver./T-ver.)<br>100 ns (f(BCLK) = 10 MHz, VCC = 2.7 to 5.5 V)<br>(Normal-ver.)<br>50 ns (f(BCLK) = 20 MHz,<br>VCC = 4.2 to 5.5 V, -40 to 105°C) (V-ver.)<br>62.5 ns (f(BCLK) = 16 MHz,<br>VCC = 4.2 to 5.5 V, -40 to 125°C) (V-ver.) | 31.25 ns (f(BCLK) = 32 MHz, VCC = 3.0 to<br>5.5 V)                                                                          |  |

| Voltage<br>Detector                   | Voltage<br>detect<br>circuits                                    | Available (Normal-ver.), Not available (T-ver./V-<br>ver.)                                                                                                                                                                                                                                   | 2 voltage detect points                                                                                                     |  |

|                                       | Power-on<br>reset                                                | No                                                                                                                                                                                                                                                                                           | Yes                                                                                                                         |  |

| Clock Gen                             | erator                                                           | 4 circuits<br>Main clock <sup>(2)</sup> , sub clock <sup>(2)</sup> , on-chip oscillator,<br>PLL frequency synthesizer                                                                                                                                                                        | 5 circuits<br>Main clock, sub clock, PLL frequency<br>synthesizer, 125 kHz on-chip oscillator, 40<br>MHz on-chip oscillator |  |

| CPU Clock after Reset                 |                                                                  | On-chip oscillator clock f2(ROC) divided by 16                                                                                                                                                                                                                                               | 125 kHz on-chip oscillator clock (fOCO-S) divided by 8                                                                      |  |

| Power<br>Control                      | Slow read mode                                                   | No                                                                                                                                                                                                                                                                                           | Yes                                                                                                                         |  |

|                                       | Low current consumption read mode                                | No                                                                                                                                                                                                                                                                                           | Yes                                                                                                                         |  |

| Power sup                             | ply voltage                                                      | (Normal-ver.)<br>VCC = 3.0 to 5.5 V (f(BCLK) = 20 MHz)<br>VCC = 2.7 to 5.5 V (f(BCLK) = 10 MHz)<br>(T-ver.) VCC = 3.0 to 5.5 V                                                                                                                                                               | 32 MHz/3.0 to 5.5 V                                                                                                         |  |

|                                       |                                                                  | (V-ver.) VCC = 4.2 to 5.5 V                                                                                                                                                                                                                                                                  |                                                                                                                             |  |

| Current consumption                   |                                                                  | 18 mA (VCC = 5 V, f(BCLK) = 20 MHz)<br>25 $\mu$ A (f(XCIN) = 32 kHz on RAM)<br>3.0 $\mu$ A (VCC = 5 V, f(XCIN) = 32 kHz, in wait<br>mode)<br>0.8 $\mu$ A (VCC = 5 V, in stop mode)                                                                                                           | TBD                                                                                                                         |  |

| Watchdog<br>timer                     | Count source                                                     | CPU clock, on-chip oscillator                                                                                                                                                                                                                                                                | CPU clock, dedicated 125 kHz on-chip oscillator for watchdog timer                                                          |  |

|                                       | Reset start function                                             | No                                                                                                                                                                                                                                                                                           | Selectable from start and stop                                                                                              |  |

|                                       | Refresh 100% (can be refreshed constantly)<br>possible<br>period |                                                                                                                                                                                                                                                                                              | 25%, 50%, 75%, 100% (selectable)                                                                                            |  |

| DMAC                                  |                                                                  | 2 channels<br>Trigger sources: 23                                                                                                                                                                                                                                                            | 4 channels<br>Trigger sources: 41                                                                                           |  |

Notes:

1. Refer to hardware manual for electrical characteristics and more details.

2. These circuits contain a built-in feedback resistor.

| lte                                                                     | em                                              | M16C/29                                                                                  | M16C/5L                                                                                                                     |

|-------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Timers                                                                  | Timer A,<br>timer B<br>count<br>source          | f1, f2, f8, f32, fC32                                                                    | f1TIMAB, f2TIMAB, f8TIMAB, f32TIMAB,<br>f64TIMAB, fOCO-F, fOCO-S, fC32                                                      |

| Clock select<br>prior to<br>timer AB<br>division<br>Timer A<br>modes    |                                                 | f1 only                                                                                  | Selectable from f1 and fOCO-F                                                                                               |

|                                                                         |                                                 | Timer mode, event counter mode, one-shot timer mode, pulse width modulation mode         | Timer mode, event counter mode, one-shot<br>timer mode, pulse width modulation mode<br>(PWM mode), programmable output mode |

|                                                                         | Task monitor<br>timer                           | No                                                                                       | 16-bit timer x 1 channel                                                                                                    |

|                                                                         | Real-time<br>clock                              | No                                                                                       | Count: seconds, minutes, hours, days of the week                                                                            |

| Serial<br>interface                                                     | UART                                            | Clock synchronous/asynchronous x 3<br>Dedicated clock-synchronous x 2                    | Clock synchronous/asynchronous x 5                                                                                          |

| Multi-master Slave<br>I <sup>2</sup> C-bus address<br>Interface setting |                                                 | 1                                                                                        | 3 (maximum)                                                                                                                 |

| CAN Module                                                              |                                                 | 16 slots                                                                                 | 32 slots                                                                                                                    |

| A/D                                                                     | Resolution                                      | 8-bit/10-bit (selectable)                                                                | 10-bit only                                                                                                                 |

| Converter                                                               | Sample and hold                                 | Yes/No (selectable)                                                                      | Yes                                                                                                                         |

|                                                                         | Open-circuit<br>detection<br>assist<br>function | No                                                                                       | Yes                                                                                                                         |

| Flash<br>Memory                                                         | Program/<br>erase power<br>supply<br>voltage    | 2.7 to 5.5 V (Normal-ver.)<br>3.0 to 5.5 V (T-ver.)<br>4.2 to 5.5 V (V-ver.)             | 3.0 to 5.5 V                                                                                                                |

|                                                                         | Program/<br>erase cycles                        | 100 times (all space) or 1,000 times (blocks<br>0 to 5)<br>10,000 times (blocks A and B) | 1,000 times (program ROM 1, program ROM<br>2),<br>10,000 times (data flash)                                                 |

# Table 3.1.2 Differences in Functions (2/2) <sup>(1)</sup>

Note:

1. Refer to the hardware manual for electrical characteristics and more details.

# 3.2 **Pin Characteristics**

Table 3.2.1 lists Differences in Pin Characteristics.

### Table 3.2.1 Differences in Pin Characteristics

| M16C/29                          | M16C/5L                         | Changes from M16C/29          |

|----------------------------------|---------------------------------|-------------------------------|

| P9_3/CTX/AN2_4                   | P9_3/CTX0/AN2_4                 | Added: CTX0<br>Deleted: CTX   |

| P9_2/TB2IN/CRX/AN3_2             | P9_2/TB2IN/CRX0/AN3_2           | Added: CRX0<br>Deleted: CRX   |

| P7_0/TA0OUT/TXD2/SDA2/RTS1/CTS1/ | P7_0/TA0OUT/TXD2/SDA2/RTS1/CTS1 | Deleted: CTS0/CLKS1           |

| CTS0/CLKS1                       |                                 |                               |

| P6_4/RTS1/CTS1/CTS0/CLKS1        | P6_4/RTS1/CTS1                  | Deleted: CTS0/CLKS1           |

| P3_3                             | P3_3/CTS3/RTS3                  | Added: CTS3/RTS3              |

| P3_2/SOUT3                       | P3_2/TXD3                       | Added: TDX3<br>Deleted: SOUT3 |

| P3_1/SIN3                        | P3_1/RXD3                       | Added: RXD3<br>Deleted: SIN3  |

| P6_0/RTS0/CTS0                   | P6_0/RTCOUT/RTS0/CTS0           | Added: RTCOUT                 |

| P9_7/SIN4/AN2_7                  | P9_7/RXD4/AN2_7                 | Added: RXD4<br>Deleted: SIN4  |

| P9_6/SOUT4/AN2_6                 | P9_6/TXD4/AN2_6                 | Added: TXD4<br>Deleted: SOUT4 |

# 4. Detailed Comparison

# 4.1 Differences in Protection

Table 4.1.1 lists Differences in Registers Associated with Protection.

#### Table 4.1.1 Differences in Registers Associated with Protection

| Symbol     | Address<br>M16C/29 M16C/5L Bi |   | Dit                                                                                                                | Differences                                                                                                       |                                                                                                                          |  |

|------------|-------------------------------|---|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Symbol     |                               |   | DIL                                                                                                                | M16C/29                                                                                                           | M16C/5L                                                                                                                  |  |

| PRCR 000Ah |                               | 0 | Protect bit 0<br>Enable write access to registers<br>CM0, CM1, CM2, <u>ROCR</u> , PLC0,<br>PCLKR, and <u>CCLKR</u> | Protect bit 0<br>Enable write access to registers<br>CM0, CM1, CM2, PLC0, PCLKR,<br><u>FRA0</u> , and <u>FRA2</u> |                                                                                                                          |  |

|            |                               |   | 2                                                                                                                  | Protect bit 2<br>Enable write access to registers<br>PD9, PACR, <u>S4C</u> , and NDDR                             | Protect bit 2<br>Enable write access to registers<br>PD9, <u>U4MR</u> , NDDR, and PACR                                   |  |

|            |                               |   | 3                                                                                                                  | Protect bit 3<br>Enable write access to registers<br>VCR2 and <u>D4INT</u>                                        | Protect bit 3<br>Enable write access to registers<br>VCR2, <u>VWCE</u> , <u>VD2LS</u> , <u>VW0C</u> ,<br>and <u>VW2C</u> |  |

|            |                               |   | 6                                                                                                                  | No register bit                                                                                                   | Protect bit 6<br>Enable write access to <u>PRG2C</u><br>register                                                         |  |

Note:

1. Different registers are underlined.

### 4.2 Differences in Resets

Table 4.2.1 lists Differences in Resets and Table 4.2.2 lists Differences in Register Associated with Resets.

| Table 4.2.1 | Differences in Resets |

|-------------|-----------------------|

|-------------|-----------------------|

| Item            | M16C/29                                                                                                                                                       | M16C/5L                                                                                                                                                              |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Types of resets | Hardware reset 1<br>Software reset<br>Watchdog timer reset<br>Oscillation stop detection reset<br>Brown-out detection reset (hardware reset 2) <sup>(1)</sup> | Hardware reset<br>Software reset<br>Watchdog timer reset<br>Oscillation stop detection reset<br>Voltage monitor 0 reset<br>Voltage monitor 2 reset<br>Power-on reset |

Note:

1. This reset cannot be used in T-ver. and V-ver.

| Sympol | Address Differences |         | Differences |         |                                                                               |

|--------|---------------------|---------|-------------|---------|-------------------------------------------------------------------------------|

| Symbol | M16C/29             | M16C/5L | DIL         | M16C/29 | M16C/5L                                                                       |

| RSTFR  | —                   | 0018h   | 1           | —       | Hardware reset detection flag<br>0: Not detected<br>1: Detected               |

|        |                     |         | 2           |         | Software reset detection flag<br>0: Not detected<br>1: Detected               |

|        |                     |         | 3           |         | Watchdog timer reset detection flag<br>0: Not detected<br>1: Detected         |

|        |                     |         | 5           |         | Voltage monitor 2 reset detection flag<br>0: Not detected<br>1: Detected      |

|        |                     |         | 6           |         | Oscillator stop detect reset detection flag<br>0: Not detected<br>1: Detected |

#### 4.3 Differences in Voltage Detector

Table 4.3.1 lists Differences in Voltage Detector and Table 4.3.2 lists Differences in Registers Associated with Voltage Detector.

| Table 4.3.1 | Differences | in | Voltage | Detector |

|-------------|-------------|----|---------|----------|

|-------------|-------------|----|---------|----------|

| Item                                         | M16C/29   | M16C/5L                                                                                              |

|----------------------------------------------|-----------|------------------------------------------------------------------------------------------------------|

| Voltage detection<br>interrupt monitor level | Vdet4     | Vdet2 (voltage detection circuit 2)                                                                  |

| Voltage detection reset monitor level        |           | <ul> <li>Vdet2 (voltage detection circuit 2)</li> <li>Vdet0 (voltage detection circuit 0)</li> </ul> |

| Sampling clock                               | CPU clock | fOCO-S                                                                                               |

Refer to the electrical characteristics on hardware manual for detection voltage.

| O wash a l | Address |         | Dit   | Differ                                                                                                                                                                                                                                                                               | ences                                                                                                                                                                                     |

|------------|---------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol     | M16C/29 | M16C/5L | Bit   | M16C/29                                                                                                                                                                                                                                                                              | M16C/5L                                                                                                                                                                                   |

| VCR1       | 0019h   |         | 3     | Low voltage monitor flag<br>0: VCC < Vdet4<br>1: VCC ≥ Vdet4                                                                                                                                                                                                                         | Low voltage monitor flag<br>0: VCC < Vdet2<br>1: VCC ≥ Vdet2<br>or voltage detector 2 circuit<br>disabled                                                                                 |

| VCR2       | 001Ah   |         | 5     | Reserved bit                                                                                                                                                                                                                                                                         | Voltage detector 0 enable bit<br>0: Voltage detector 0 disabled<br>1: Voltage detector 0 enabled                                                                                          |

|            |         |         | 6     | Reset level monitor bit<br>0: Disable reset level detection<br>circuit<br>1: Enable reset level detection<br>circuit                                                                                                                                                                 | Reserved bit                                                                                                                                                                              |

|            |         |         | 7     | Low voltage monitor bit<br>0: Disable low voltage detection<br>circuit<br>1: Enable low voltage detection<br>circuit                                                                                                                                                                 | Voltage detector 2 enable bit<br>0: Voltage detector 2 disabled<br>1: Voltage detector 2 enabled                                                                                          |

| VWCE       | —       | 0026h   | —     | —                                                                                                                                                                                                                                                                                    | M16C/5L only                                                                                                                                                                              |

| VD2LS      | —       | 0028h   | —     | —                                                                                                                                                                                                                                                                                    | M16C/5L only                                                                                                                                                                              |

| VW0C       | —       | 002Ah   | —     | —                                                                                                                                                                                                                                                                                    | M16C/5L only                                                                                                                                                                              |

| VW2C       | —       | 002Ch   | —     | —                                                                                                                                                                                                                                                                                    | M16C/5L only                                                                                                                                                                              |

| D4INT      | 001Fh   |         | 0     | Low voltage detection interrupt<br>enable bit<br>0: Disable<br>1: Enable<br>Stop mode deactivation control bit<br>0: Disable (do not use the low<br>voltage detection interrupt to exit<br>stop mode)<br>1: Enable (use the low voltage<br>detection interrupt to exit stop<br>mode) |                                                                                                                                                                                           |

|            |         |         | 2     | Voltage change detection flag<br>0: Not detected<br>1: Vdet4 passing detection                                                                                                                                                                                                       |                                                                                                                                                                                           |

|            |         |         | 3     | WDT overflow detect flag<br>0: Not detected<br>1: Detected                                                                                                                                                                                                                           |                                                                                                                                                                                           |

|            |         |         | 5 - 4 | Sampling clock select bit<br>00: CPU clock divided by 8<br>01: CPU clock divided by 16<br>10: CPU clock divided by 32<br>11: CPU clock divided by 64                                                                                                                                 |                                                                                                                                                                                           |

| OFS1       | -       | FFFFh   | 6     | —                                                                                                                                                                                                                                                                                    | <ul><li>Voltage detector 0 start bit</li><li>0: Voltage monitor 0 reset enabled<br/>after hardware reset.</li><li>1: Voltage monitor 0 reset disabled<br/>after hardware reset.</li></ul> |

# Table 4.3.2 Differences in Registers Associated with Voltage Detector

### 4.4 Differences in Clock Generator

Table 4.4.1 lists Differences in Clock Generator and Table 4.4.2 lists Differences in Registers Associated with Clock Generator.

| Item                                                 | M16C/29                                                                                                                                                           | M16C/5L                                                                                                                                                                                                     |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU clock<br>after reset                             | On-chip oscillator clock f2(ROC) divided by 16                                                                                                                    | 125 kHz on-chip oscillator clock (fOCO-S) divided by 8                                                                                                                                                      |

| Peripheral<br>clock (fC)                             | Supply constantly                                                                                                                                                 | Provided/Not provided selectable using the PM25 bit in the PM2 register                                                                                                                                     |

| On-chip<br>oscillator<br>types and<br>frequency      | 3 types<br>On-chip oscillator frequency 1 (f1(ROC)): 1 MHz<br>On-chip oscillator frequency 2 (f2(ROC)): 2 MHz<br>On-chip oscillator frequency 3 (f3(ROC)): 16 MHz | 3 types<br>40 MHz on-chip oscillator (fOCO-F): Approx. 40 MHz<br>125 kHz on-chip oscillator (fOCO-S): Approx. 125 kHz<br>Dedicated 125 kHz on-chip oscillator for watchdog<br>timer (fWDT): Approx. 125 kHz |

| PLL clock<br>frequency                               | 10 to 20 MHz                                                                                                                                                      | 10 to 32 MHz                                                                                                                                                                                                |

| Calculation<br>formula for<br>PLL clock<br>frequency | f(XIN) x n                                                                                                                                                        | f(XIN)/(m x n)                                                                                                                                                                                              |

Table 4.4.1

Differences in Clock Generator

n: Multiplication rate set by bits PLC02 to PLC00 in the PLC0 register m: Division ratio set by bits PLC05 to PLC04 in the PLC0 register

| Sumbol | Add      | ress    | Dit    | Bit                                     |                                                                                                                                                 | es                                   |                                                                                                              |

|--------|----------|---------|--------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Symbol | M16C/29  | M16C/5L | Bit    |                                         | M16C/29                                                                                                                                         |                                      | M16C/5L                                                                                                      |

| CM1    | 0007h    |         | 3      | Reserve                                 | ed bits                                                                                                                                         | 0: Inte<br>con<br>1: Inte<br>con     | OUT feedback resistor select bit<br>rnal feedback resistor<br>nected<br>rnal feedback resistor not<br>nected |

|        |          |         | 4      |                                         |                                                                                                                                                 | 0: 125                               | Hz on-chip oscillator stop bit<br>kHz on-chip oscillator oscillates<br>kHz on-chip oscillator stops          |

| PCLKR  | 025Eh    | 0012h   | _      |                                         | Addre                                                                                                                                           | ess cha                              | nged                                                                                                         |

| PLC0   | 001Ch    |         | 2 - 0  | 000: Do<br>001: Mu                      | Itiplying factor select bit<br>not set<br>ultiply by 2<br>ultiply by 4<br>Do not set                                                            | 000: D<br>001: N<br>010: N<br>011: N | Do not set these values                                                                                      |

|        |          |         | 4<br>5 | Reserve<br>Set to 1<br>Reserve          |                                                                                                                                                 | 00: No<br>01: Di                     | ence frequency counter set bit<br>) division<br>vide-by-2<br>vide-by-4                                       |

|        |          |         |        |                                         |                                                                                                                                                 |                                      | not set                                                                                                      |

| PM2    | 001Eh    |         | 0      | Specifyi<br>SFR<br>0: 2 wai<br>1: 1 wai |                                                                                                                                                 | Reser<br>Set to                      | ved bit<br>1.                                                                                                |

|        |          |         | 2      | 0: CPU<br>watch<br>1: On-c<br>used      | bunt source protective bit<br>clock is used for the<br>ndog timer count source<br>hip oscillator clock is<br>for the watchdog timer<br>t source | No reo                               | jister bit                                                                                                   |

|        |          |         | 5      | No regi                                 | ster bit                                                                                                                                        | 0: fC c                              | eral clock fC provide bit<br>lisabled<br>enabled                                                             |

| FRA0   | <b> </b> | 0022h   | —      | —                                       |                                                                                                                                                 | M16C                                 | /5L only                                                                                                     |

| FRA2   | <b>—</b> | 0024h   | —      | —                                       |                                                                                                                                                 | M16C                                 | /5L only                                                                                                     |

| ROCR   | 025Ch    | _       |        | M16C/2                                  | 9 only                                                                                                                                          | —                                    |                                                                                                              |

| CCLKR  | 025Fh    | _       | —      | M16C/2                                  | 9 only                                                                                                                                          | —                                    |                                                                                                              |

# Table 4.4.2 Differences in Registers Associated with Clock Generator

## 4.5 Differences in Power Control

Table 4.5.1 lists Differences in Power Control and Table 4.5.2 lists Differences in Registers Associated with Power Control.

#### Table 4.5.1 Differences in Power Control

| Item                              | M16C/29 | M16C/5L |

|-----------------------------------|---------|---------|

| Slow read mode                    | No      | Yes     |

| Low current consumption read mode | No      | Yes     |

#### Table 4.5.2 Differences in Registers Associated with Power Control

| Symbol | Add     | ress    | Bit | Differences |              |

|--------|---------|---------|-----|-------------|--------------|

| Symbol | M16C/29 | M16C/5L | DIL | M16C/29     | M16C/5L      |

| FMR2   | —       | 0222h   |     | —           | M16C/5L only |

#### 4.6 Differences in Processor Mode

Table 4.6.1 lists Differences in Register Associated with Processor Mode.

#### Table 4.6.1 Differences in Register Associated with Processor Mode

| Symbol | Add     | ress    | Bit | Differences |              |  |

|--------|---------|---------|-----|-------------|--------------|--|

| Symbol | M16C/29 | M16C/5L | Dit | M16C/29     | M16C/5L      |  |

| PRG2C  | — 0010h |         | —   | —           | M16C/5L only |  |

# 4.7 Differences in Programmable I/O Ports

Table 4.7.1 lists Differences in Registers Associated with Programmable I/O Ports.

# Table 4.7.1 Differences in Registers Associated with Programmable I/O Ports

| Symbol | Add     | lress   | Bit | Differences     |              |

|--------|---------|---------|-----|-----------------|--------------|

| Symbol | M16C/29 | M16C/5L | DIL | M16C/29         | M16C/5L      |

| NDDR   | 033Eh   | 02FEh   |     | Address         | changed      |

| P17DDR | 033Fh   | 02FFh   |     | Address         | changed      |

| PUR0   | 03FCh   | 0360h   |     | Address         | changed      |

| PUR1   | 03FDh   | 0361h   |     | Address changed |              |

| PUR2   | 03FEh   | 0362h   |     | Address changed |              |

| PCR    | 03FFh   | 0366h   |     | Address         | changed      |

| VLT0   | _       | 036Ch   |     | —               | M16C/5L only |

| VLT1   | —       | 036Dh   |     | — M16C/5L only  |              |

| VLT2   | _       | 036Eh   |     | — M16C/5L only  |              |

| PACR   | 025Dh   | 0370h   |     | Address         | changed      |

### 4.8 Differences in Interrupts

Table 4.8.1 to Table 4.8.2 list Differences in Interrupt Vectors, Table 4.8.3 lists Differences in SFRs Associated with Interrupts, and Table 4.8.4 Differences in Interrupt Source Select Registers.

| Software<br>Interrupt<br>Number | Vector Address                | M16C/29                                                       | M16C/5L                                                                                 |

|---------------------------------|-------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 0                               | +0 to +3 (0000h to 0003h)     | BRK instruction                                               | BRK instruction                                                                         |

| 1                               | +4 to +7 (0004h to 0007h)     | CAN0 wakeup                                                   | — (Reserved)                                                                            |

| 2                               | +8 to +11 (0008h to 000Bh)    | CAN0 receive completion                                       | — (Reserved)                                                                            |

| 3                               | +12 to +15 (000Ch to 000Fh)   | CAN0 transmit completion                                      | — (Reserved)                                                                            |

| 4                               | +16 to +19 (0010h to 0013h)   | INT3                                                          | INT3                                                                                    |

| 5                               | +20 to +23 (0014h to 0017h)   | IC/OC interrupt 0                                             | — (Reserved)                                                                            |

| 6                               | +24 to +27 (0018h to 001Bh)   | IC/OC interrupt 1, I <sup>2</sup> C-bus interface             | — (Reserved)                                                                            |

| 7                               | +28 to +31 (001Ch to 001Fh)   | IC/OC base timer, SCL/SDA                                     | — (Reserved)                                                                            |

| 8                               | +32 to +35 (0020h to 0023h)   | SI/O4, INT5                                                   | ĪNT5                                                                                    |

| 9                               | +36 to +39 (0024h to 0027h)   | SI/O3, INT4                                                   | ĪNT4                                                                                    |

| 10                              | +40 to +43 (0028h to 002Bh)   | UART2 start/stop condition detection, bus collision detection | UART2 start/stop condition<br>detection, bus collision detection,<br>task monitor timer |

| 11                              | +44 to +47 (002Ch to 002Fh)   | DMA0                                                          | DMA0                                                                                    |

| 12                              | +48 to +51 (0030h to 0033h)   | DMA1                                                          | DMA1                                                                                    |

| 13                              | +52 to +55 (0034h to 0037h)   | CAN0 state, error                                             | Key input interrupt                                                                     |

| 14                              | +56 to +59 (0038h to 003Bh)   | A/D converter, key input interrupt                            | A/D converter                                                                           |

| 15                              | +60 to +63 (003Ch to 003Fh)   | UART2 transmit, NACK2                                         | UART2 transmit, NACK2                                                                   |

| 16                              | +64 to +67 (0040h to 0043h)   | UART2 receive, ACK2                                           | UART2 receive, ACK2                                                                     |

| 17                              | +68 to +71 (0044h to 0047h)   | UART0 transmit                                                | UART0 transmit                                                                          |

| 18                              | +72 to +75 (0048h to 004Bh)   | UART0 receive                                                 | UART0 receive                                                                           |

| 19                              | +76 to +79 (004Ch to 004Fh)   | UART1 transmit                                                | UART1 transmit                                                                          |

| 20                              | +80 to +83 (0050h to 0053h)   | UART1 receive                                                 | UART1 receive                                                                           |

| 21                              | +84 to +87 (0054h to 0057h)   | Timer A0                                                      | Timer A0                                                                                |

| 22                              | +88 to +91 (0058h to 005Bh)   | Timer A1                                                      | Timer A1                                                                                |

| 23                              | +92 to +95 (005Ch to 005Fh)   | Timer A2                                                      | Timer A2                                                                                |

| 24                              | +96 to +99 (0060h to 0063h)   | Timer A3                                                      | Timer A3                                                                                |

| 25                              | +100 to +103 (0064h to 0067h) | Timer A4                                                      | Timer A4                                                                                |

| 26                              | +104 to +107 (0068h to 006Bh) | Timer B0                                                      | Timer B0                                                                                |

| 27                              | +108 to +111 (006Ch to 006Fh) | Timer B1                                                      | Timer B1                                                                                |

| 28                              | +112 to +115 (0070h to 0073h) | Timer B2                                                      | Timer B2                                                                                |

Table 4.8.1

Differences in Interrupt Vectors (1/2)

| Software<br>Interrupt<br>Number | Vector Address                      | M16C/29            | M16C/5L                                                              |

|---------------------------------|-------------------------------------|--------------------|----------------------------------------------------------------------|

| 29                              | +116 to +119 (0074h to 0077h)       | INTO               | INTO                                                                 |

| 30                              | +120 to +123 (0078h to 007Bh)       | INT1               | INT1                                                                 |

| 31                              | +124 to +127 (007Ch to 007Fh)       | INT2               | INT2                                                                 |

| 32 to 40                        | +128 to +131 (0080h to 0083h)<br>to | Software interrupt | INT instruction interrupt                                            |

|                                 | +160 to +163 (00A0h to 00A3h)       |                    |                                                                      |

| 41                              | +164 to +167 (00A4h to 00A7h)       |                    | DMA2                                                                 |

| 42                              | +168 to +171 (00A8h to 00ABh)       |                    | DMA3                                                                 |

| 43                              | +172 to +175 (00ACh to 00AFh)       |                    | — (Reserved)                                                         |

| 44                              | +176 to +179 (00B0h to 00B3h)       |                    | — (Reserved)                                                         |

| 45                              | +180 to +183 (00B4h to 00B7h)       |                    | — (Reserved)                                                         |

| 46                              | +184 to +187 (00B8h to 00BBh)       |                    | — (Reserved)                                                         |

| 47                              | +188 to +191 (00BCh to 00BFh)       |                    | UART4 transmit, real-time clock<br>compare                           |

| 48                              | +192 to +195 (00C0h to 00C3h)       |                    | UART4 receive                                                        |

| 49                              | +196 to +199 (00C4h to 00C7h)       |                    | CAN0 wakeup                                                          |

| 50                              | +200 to +203 (00C8h to 00CBh)       |                    | UART3 transmit, CAN0 error                                           |

| 51                              | +204 to +207 (00CCh to 00CFh)       |                    | UART3 receive                                                        |

| 52                              | +208 to +211 (00D0h to 00D3h)       |                    | Real-time clock periodic                                             |

| 53                              | +212 to +215 (00D4h to 00D7h)       |                    | CAN0 receive completion                                              |

| 54                              | +216 to +219 (00D8h to 00DBh)       |                    | CAN0 transmit completion                                             |

| 55                              | +220 to +223 (00DCh to 00DFh)       |                    | CAN0 receive FIFO                                                    |

| 56                              | +224 to +227 (00E0h to 00E3h)       |                    | CAN0 transmit FIFO                                                   |

| 57                              | +228 to +231 (00E4h to 00E7h)       |                    | IC/OC interrupt 0 (0 to 7)                                           |

| 58                              | +232 to +235 (00E8h to 00EBh)       |                    | IC/OC channel 0                                                      |

| 59                              | +236 to +239 (00ECh to 00EFh)       |                    | IC/OC interrupt 1 (0 to 7), I <sup>2</sup> C-bus interface interrupt |

| 60                              | +240 to +243 (00F0h to 00F3h)       | 1                  | IC/OC channel 1, SCL/SDA interrupt                                   |

| 61                              | +244 to +247 (00F4h to 00F7h)       | 1                  | IC/OC channel 2                                                      |

| 62                              | +248 to +251 (00F8h to 00FBh)       |                    | IC/OC channel 3                                                      |

| 63                              | +252 to +255 (00FCh to 00FFh)       | ]                  | IC/OC base timer                                                     |

# Table 4.8.2 Differences in Interrupt Vectors (2/2)

|                                     | Add            | Iress          | Differences       |                 |  |

|-------------------------------------|----------------|----------------|-------------------|-----------------|--|

| Symbol                              | M16C/29        | M16C/5L        | M16C/29           | M16C/5L         |  |

| AIER                                | 0009h          | 020Eh          | Address           | s changed       |  |

| AIER2                               | —              | 020Fh          | —                 | M16C/5L only    |  |

| RMAD0                               | 0010h to 0012h | 0210h to 0212h | Address changed   |                 |  |

| RMAD1                               | 0014h to 0016h | 0214h to 0216h | h Address changed |                 |  |

| RMAD2                               | —              | 0218h to 021Ah | —                 | M16C/5L only    |  |

| RMAD3                               | —              | 021Ch to 021Eh | —                 | M16C/5L only    |  |

| M16C/29: C01WKIC<br>M16C/5L: C0WIC  | 0041h          | 0071h          | Symbol and a      | ddress changed  |  |

| M16C/29: C0RECIC<br>M16C/5L: C0RIC  | 0042h          | 0075h          | Symbol and a      | ddress changed  |  |

| M16C/29: C0TRMIC<br>M16C/5L: C0TIC  | 0043h          | 0076h          | Symbol and a      | ddress changed  |  |

| C0FRIC                              | <u> </u>       | 0077h          | <b> </b>          | M16C/5L only    |  |

| COFTIC                              | —              | 0078h          | <b> </b>          | M16C/5L only    |  |

| ICOCOIC                             | 0045h          | 0079h          | Address           | changed         |  |

| ICOCH0IC                            | _              | 007Ah          | _                 | M16C/5L only    |  |

| ICOC1IC, IICIC                      | 0046h          | 007Bh          | Address           | changed         |  |

| BTIC                                | 0047h          | 007Fh          | Address           | s changed       |  |

| SCLDAIC                             | 0047h          | 007Ch          | Address           | changed         |  |

| ICOCH1IC                            | _              | 007Ch          | —                 | M16C/5L only    |  |

| ICOCH2IC                            | _              | 007Dh          | —                 | M16C/5L only    |  |

| ICOCH3IC                            | _              | 007Eh          | —                 | M16C/5L only    |  |

| S4IC                                | 0048h          | _              | M16C/29 only      | _               |  |

| S4TIC                               | _              | 006Fh          | _                 | M16C/5L only    |  |

| S4RIC                               | _              | 0070h          | —                 | M16C/5L only    |  |

| S3IC                                | 0049h          | _              | M16C/29 only      | _               |  |

| S3TIC                               | _              | 0072h          | _                 | M16C/5L only    |  |

| S3RIC                               | _              | 0073h          | —                 | M16C/5L only    |  |

| M16C/29: C01ERRIC<br>M16C/5L: C0EIC | 004Dh          | 0072h          | Symbol and a      | ddress changed  |  |

| KUPIC                               | 004Eh          | 004Dh          | Address           | s changed       |  |

| IFSR3A                              | _              | 0205h          | —                 | M16C/5L only    |  |

| IFSR2A                              | 035Eh          | 0206h          | Address and o     | content changed |  |

| IFSR                                | 035Fh          | 0207h          | Address and o     | content changed |  |

| G1IR                                | 0330h          | 02F0h          | Address           | s changed       |  |

| G1IE0                               | 0331h          | 02F1h          | Address           | s changed       |  |

| G1IE1                               | 0332h          | 02F2h          |                   | s changed       |  |

| NDDR                                | 033Eh          | 02FEh          |                   | s changed       |  |

| TMOSIC                              | —              | 004Ah          | —                 | M16C/5L only    |  |

| DM2IC                               | —              | 0069h          | <u> </u>          | M16C/5L only    |  |

| DM3IC                               | —              | 006Ah          | <b> </b>          | M16C/5L only    |  |

| RTCCIC                              |                | 006Fh          |                   | M16C/5L only    |  |

| RTCTIC                              | <u> </u>       | 0074h          | <b> _</b>         | M16C/5L only    |  |

| COICR                               | 0216h to 0217h |                | M16C/29 only      | _               |  |

#### Table 4.8.3 Differences in SFRs Associated with Interrupts

| Symbol | Ad      | dress   | Bit |                                                           | Differences                                               |

|--------|---------|---------|-----|-----------------------------------------------------------|-----------------------------------------------------------|

| Symbol | M16C/29 | M16C/5L | DIL | M16C/29                                                   | M16C/5L                                                   |

| IFSR3A | —       | 0205h   | 6   | —                                                         | 0: UART4 transmission<br>1: Real-time clock compare       |

| IFSR2A | 035Eh   | 0206h   | 0   | Reserved bit                                              | 0: UART2 bus collision detection<br>1: Task monitor timer |

|        |         |         | 1   | 0: A/D conversion<br>1: Key input                         | Reserved bit                                              |

|        |         |         | 2   | 0: CAN0 wakeup/error<br>1: Do not set                     | 0: IC/OC interrupt 1<br>1: I <sup>2</sup> C-bus interface |

|        |         |         | 3   | No register bits                                          | 0: IC/OC channel 1 interrupt<br>1: SCL/SDA                |

|        |         |         | 4   |                                                           | 0: Reserved<br>1: CAN0 wakeup                             |

|        |         |         | 5   |                                                           | 0: UART3 transmission<br>1: CAN0 error                    |

|        |         |         | 6   | 0: IC/OC base timer<br>1: SCL/SDA                         | Reserved bits                                             |

|        |         |         | 7   | 0: IC/OC interrupt 1<br>1: I <sup>2</sup> C-bus interface |                                                           |

| IFSR   | 035Fh   | 0207h   | 6   | 0: <u>SI/O3</u><br>1: INT4                                | 0: Reserved<br>1: INT4                                    |

|        |         |         | 7   | 0: <u>SI/O</u> 4<br>1: INT5                               | 0: <u>Rese</u> rved<br>1: INT5                            |

#### Table 4.8.4 Differences in Interrupt Source Select Registers

# 4.9 Differences in Watchdog Timer

Table 4.9.1 lists Differences in Watchdog Timer and Table 4.9.2 lists Differences in Registers Associated with Watchdog Timer.

| Item                                                            | M16C/29                                                                                                                  | M16C/5L                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count source in count source protect mode                       | On-chip oscillator clock                                                                                                 | On-chip oscillator clock for watchdog timer                                                                                                                                                                                                                                                                                                                                                                     |

| Count source protect mode enable setting                        | Set the PM22 bit in the PM2 register to 1.                                                                               | Set the CSPRO bit in the CSPR register to 1. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                     |

| Watchdog timer cycle<br>in count source<br>protect mode         | Watchdog timer count (32768)<br>On-chip oscillator clock<br>On-chip oscillator clock can be set in the ROCR<br>register. | Watchdog timer count (m)<br>fWDT (Approx. 125 kHz)<br>m: Value set by bits WDTUFS1 to WDTUFS0 in<br>the OFS2 address                                                                                                                                                                                                                                                                                            |

| Values settable to the watchdog timer                           | 7FFFh                                                                                                                    | 03FFh, 0FFFh, 1FFFh, 3FFFh                                                                                                                                                                                                                                                                                                                                                                                      |

| A value of watchdog<br>timer can be read in the<br>WDC register | High-order bits of watchdog timer                                                                                        | <ul> <li>Bits b10 to b5 can be read when the count source protect mode is disabled.</li> <li>When the count source protect mode is enabled, while bits WDTUFS1 and WDTUFS0 in the OFS2 address are:</li> <li>00b (03FFh), bits b5 to b0 can be read</li> <li>01b (0FFFh), bits b8 to b3 can be read</li> <li>10b (1FFFh), bits b9 to b4 can be read</li> <li>11b (3FFFh), bits b10 to b5 can be read</li> </ul> |

| Watchdog timer counter initialization                           | Watchdog timer counter is initialized and starts counting by writing to the WDTS register.                               | Write 00h, and then FFh to the WDTR register                                                                                                                                                                                                                                                                                                                                                                    |

| Count start conditions                                          |                                                                                                                          | <ul> <li>Count automatically starts after reset by<br/>setting the WDTON bit in the OFS1 address to<br/>0.</li> <li>Count starts by writing to the WDTS register.</li> </ul>                                                                                                                                                                                                                                    |

| Refresh possible period                                         | 100% (can be refreshed constantly)                                                                                       | 25%, 50%, 75%, 100% (selectable)                                                                                                                                                                                                                                                                                                                                                                                |

| WDT detect flag                                                 | The D43 bit in the D4INT register<br>WDT overflow detect flag<br>0: Not detected<br>1: Detected                          | The VW2C3 bit in the VW2C register<br>WDT detection flag<br>0: Not detected<br>1: Watchdog timer underflow detected                                                                                                                                                                                                                                                                                             |

Table 4.9.1 Differences in Watchdog Timer

Note:

1. When the CSPROINI bit in the OFS1 address is 0, the value after reset becomes 1.

| Sumbol | Symbol Address |         | Dit   | Differences                                                                                                                                                                                                |                                                                                                                                                                                                                     |  |  |

|--------|----------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|