*Author: Roger Liang Date: September 15, 2015*

## Introduction

The Serial-Parallel Interface (SPI) bus is a synchronous serial communication interface specification made popular by Motorola before it spun off to Freescale and then acquired by NXP. Typical applications include SDIO and LCD. GreenPAK4 includes a SPI slave macro-cell. The purpose of this application note is to demonstrate the SPI macro-cell's parallel to serial (P2S) mode configuration. AN-1065 covers serial to parallel (S2P) mode configuration. Specific to GreenPAK4, P2S applications include converting ADC or FSM counter data into standard SPI serial data for system-level communication. Please note the SPI macrocell cannot send and receive serial data in the same application; it is set up either in S2P or P2S mode.

### **P2S Converter Design**

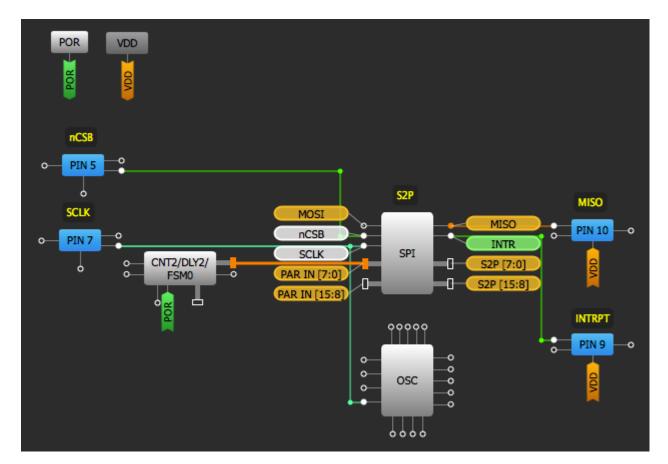

A P2S design is shown in figure 1 and its SPI macro-cell's properties are shown in figure 2. This example is built in SLG46620. The FSM0 counter is used as a parallel input source for demonstration purposes only. In figure 1, the thicker orange line signifies an 8-bit bus going into the SPI macro-cell. Several notes to point out:

1. P2S mode doesn't support sampling on the leading  $(1^{st})$  clock edge (CPHA=0); make sure sampling occurs on the trailing  $(2^{nd})$ clock edge by setting CPHA = 1. S2P mode supports CPHA=0. 2. Master Input Slave Output (MISO) outputs data either at SPI clock (SCLK)'s rising edge or falling edge. This is configured by setting the base value of the clock to either "0" or "1" respectively under "Clock polarity" (CPOL) in properties.

3. Either one or two bytes can be converted at a time; this example converts one byte at a time.

4. The ADC, PWM, and FSM data can sync with the SPI clock even when they are not from the same clock source. The data sync options accomplish this by stopping the respective clocks while the parallel data is loaded into the SPI macro-cell. There will be no runt pulses since clocks are gated.

5. SPI macro-cell can accept parallel data either from the FSM counter or ADC macro-cell.

6. MISO can only route to pin 10 (pin 12 in SLG46140); make sure it is configured as a digital output.

7. The "INTR" pin pulses high for one clock period each time data after transmission completes. When CPOL=0, this pulse starts at the  $8^{th}/16^{th}$  falling clock edge. Likewise when CPOL=1, interrupt starts at the  $8^{th}/16^{th}$  rising clock edge.

# RENESAS

#### **P2S Converter Operation**

The P2S Design in figure 1 uses FSM0 counter as its input. This is for demonstration purpose only since it is easy to set FSM0's value. In this example, FSM0's counter data is set at 169, or 1010,1001 in binary. The SPI macro-cell grabs this value and converts it to serial format, outputting the MSB first.

For proper P2S operation, please observe below steps in sequence:

1. Enable SPI macro-cell by pulling nCSB pin low.

2. SCLK's 1<sup>st</sup> edge should occur at least 250ns after nCSB is pulled low. Unexpected behavior can occur if nCSB and SCLK edges are concurrent.

3. After data transmission is complete on MISO, SPI's INTR pin will pulse high.

Figure 1. P2S Converter Design

# RENESAS

## **SPI Parallel to Serial Converter**

4. Stop SCLK at least 250ns after INTR rising edge; MISO will output repeated data if SCLK is not stopped.

5. Disable SPI macro-cell by pulling nCSB pin high at least 250ns after last SCLK edge.

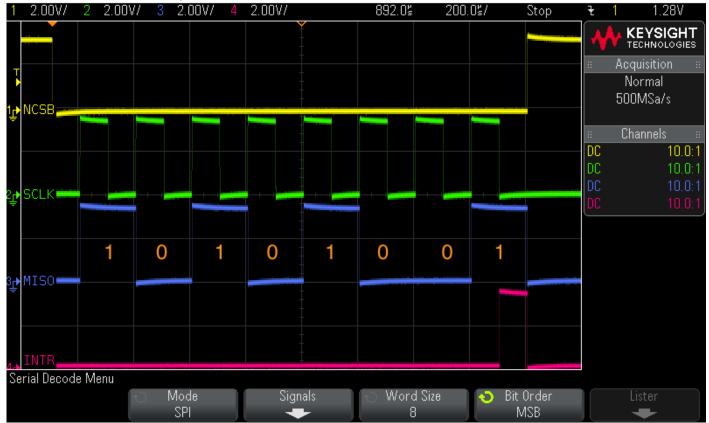

Figure 4 shows proper SPI timing waveform with CPOL=0. Channel 3 is the serial output MISO. Notice that it is outputting 10101001 with respect to the rising edge of SCLK.

| Properties                       |                      |

|----------------------------------|----------------------|

| SPI                              |                      |

| Mode:                            | P2S 🗘                |

| Clock phase<br>(CPHA):           | 1                    |

| Clock polarity<br>(CPOL):        | 0                    |

| Byte selection:                  | [7:0]                |

| ADC data sync<br>with SPI clock: | Disable ᅌ            |

| PWM data sync<br>with SPI clock: | Disable              |

| FSM data sync<br>with SPI clock: | Enable               |

| Connections                      |                      |

| PAR input<br>data source:        | FSM0[7:0] FSM1[ ᅌ    |

| Serial data:                     | SPI -> PIN 10 (in) ᅌ |

| 0 5                              | Apply                |

Figure 2. P2S Configuration

| Properties                       |                                                |  |

|----------------------------------|------------------------------------------------|--|

| 14-bit CNT2/DLY2/FSM0            |                                                |  |

| Mode:                            | Counter/FSM                                    |  |

| Counter data:                    | 169                                            |  |

| Output period:                   | (Range: 1 - 16383)<br>6.8000 ms <u>Formula</u> |  |

| Edge select:                     | Both ᅌ                                         |  |

| Counter value<br>control:        | Set (counter valu ᅌ                            |  |

| DFF bypass<br>enable:            | None 🗘                                         |  |

| FSM data sync<br>with SPI clock: | Enable ᅌ                                       |  |

| Connections                      |                                                |  |

| FSM data:                        | Counter data ᅌ                                 |  |

| Clock:                           | CLK                                            |  |

| Clock source:                    | OSC Freq.                                      |  |

| 0 5                              | Apply                                          |  |

**Figure 3. FSM0 Properties**

## **SPI Parallel to Serial Converter**

#### MS0-X 2024A, MY52160677: Thu Sep 10 07:12:01 2015

Figure 4. SPI Timing Waveform with CPHA=1 and CPOL=0

For completeness' sake, figure 5 shows proper SPI timing waveform with CPOL=1. Notice that MISO is outputting 10101001 with respect to the falling edge of SCLK.

### **Possible Applications**

Let's take sensor timing for example. Window comparators are often used to count time between tripped thresholds. This data can be recorded in the FSM counter, and then outputted as serial data via the SPI macrocell.

## **SPI Parallel to Serial Converter**

often used when ADC or counter data needs

#### Figure 5. SPI Timing Waveform with CPHA=1 and CPOL=1

to be written to another

## Conclusion

GreenPAK4's SPI block provides a convenient communication interface for the GreenPAK to other chips in the system. The P2S mode is

to be written to another chip in the system via SPI.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.