## データセンタにおける電源アーキテクチャの進化

ルネサス エレクトロニクス株式会社

Pietro Scalia, シニアダイレクター、パワーシステムマーケティング&アーキテクチャ

Yong Perry Li, シニアダイレクター、GaNシステム&アプリケーション

Ashish Ekbote, シニアマネージャー、GaNアプリケーションエンジニアリング

### 概要

AIの爆発的な成長とそれに伴うハードウェアの高度化により、データセンター内のITラックの消費電力レベルは飛躍的に増加し、すでに数百kW規模に達しています。こうした変化に対応するため、OCP標準に基づく従来の48V電源分配アーキテクチャは、抜本的な再設計が求められています。ラック内の電力分配損失やバスバー用の銅の使用量を最小限に抑えるには、より高電圧でラック内に給電する必要があり、その実現手段として800V(2線または3線)方式の採用が進んでいます。新たなアーキテクチャの中核となるのが、高電力密度の絶縁型16:1 DC/DCコンバータです。このコンバータはDC800VをDC48Vに変換し、既存のエコシステムの大部分を迅速に再利用できる構成となります。

技術面での鍵となるのは、中電圧GaN(窒化ガリウム)であり、一次側でスイッチング周波数を高めつつ、高効率を実現しています。さらに、LLCダイレクトカレントトランス(DCX)トポロジーは、一定のスイッチング周波数(fs)でオープンループ動作し、98%の効率で安定した48V出力を実現します。

## データセンタにおける電源アーキテクチャの進化

本稿では、このコンバータの詳細な解析とともに、制御・駆動・アクティブスイッチといった主要コンポーネントがどのように高性能を実現しているかを紹介します。この高電圧アーキテクチャは、さらなる高密度化と高効率化を目指して進化を続けています。その一環として、変換段数の削減とコンバータ構成や中間バス電圧の最適化など様々なアプローチが模索されています。これらのアプローチにより、低電圧GaNをはじめとする低電圧テクノロジーでの効率向上の可能性も最大限に検討されています。さらに、GaNがアーキテクチャの発展を支えるもう一つの領域として、新たに定義されたサイドカーラックがあります。ここでは、三相ACを高電圧DCへ変換する機能が実装されています。中電圧双方向GaNにより、フロントエンド整流段のトポロジーが簡素化され、より高効率でコンパクトな設計を実現します。このようなアーキテクチャの進化は、今後のxPU世代におけるさらなる高電力需要に対応しながら、今後も継続的に発展を遂げていくと予測されています。ルネサスは、これまで長年にわたり、IBC(中間バスコンバータ)電源ソリューションおよびコア電源供給で業界をリードしてきました。現在は、高電圧インフラ分野にも事業領域を拡大し、データセンター向けの新しい800VアーキテクチャにおいてNVIDIAと協業しています。

また、グリッドからコアに至るまでの電力変換技術のイノベーションに取り組み、この移行を支えるためのリファレンスソリューションを提供しています。これらのソリューションは、技術面で最適な選択肢を評価できるように設計されており、最高のFOM(性能指數)、コスト効率、信頼性を実現し、データセンターインフラの加速度的な進化に貢献しています。

### はじめに

データセンターは、AIハードウェアの急速な普及により、かつてない大変革期を迎えています。xPUやASICを手がけるOEM各社は、従来およそ30か月であった技術更新サイクルを12~15か月へと大幅に短縮し、次々と新技術を投入しています。これに伴い、ハイパースケーラーは、従来のサーバーアップグレードを大きく上回る規模で設備投資を進めており、半導体サプライヤーもこのハードウェア革命を支える中核的な役割を果たしています。

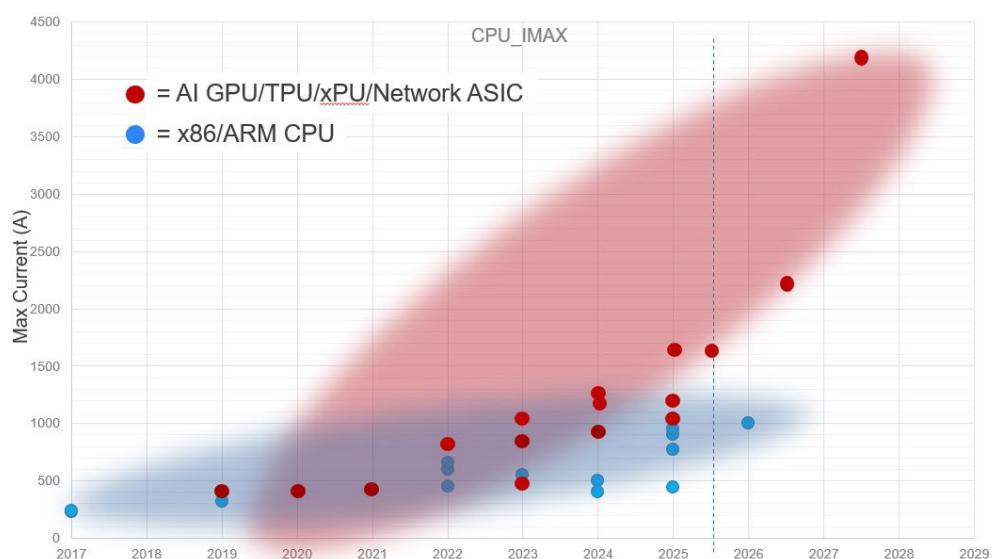

xPUの電力消費は急増しており(図1参照)、VR200 NVL144では、GPUラック全体の消費電力が来年には数百kW規模に達する見込みです。これは、現行のGB300 NVL72の2倍以上に相当します。

AIおよびネットワーキングの進化と需要拡大により、電流のピーク値は今後2年間で大幅に上昇すると見込まれています。CPUの電力要件も増加しますが、AI用途に比べるとその伸びは緩やかです。ムーアの法則では、半導体の集積度は3年ごとに2倍の進化を実現してきました。現在のAIは、並列処理の進化によって、12~18か月ごとに性能が2倍進化するという「ファンの法則」に沿った成長を遂げています。

したがって、AC電源から生成された48Vの中間バスに基づく従来のラック内電力分配アーキテクチャは、[Open Compute Project\(OCP\)で標準化されていますが](#)、今の急激な電力需要増大に対応できるように再設計する必要があります。現在のラック構造およびアーキテクチャのまま電力増大に対応する際には、膨大な分配損失や、バスバー用の銅の大量使用を避けることができません。

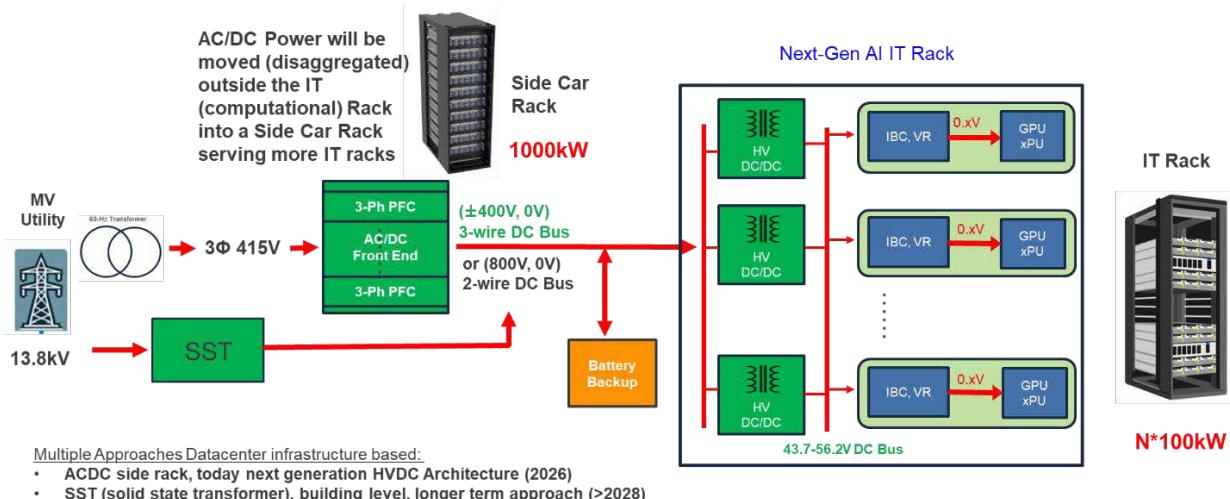

この課題に取り組むため、ハイパースケーラーはより高電圧のDCバスを導入する予定であり、またOEMや電源ユニット(PSU)、エネルギーシステムのサプライヤーはその研究開発面での支援を強化しています(図2参照)。こうした高電圧化により、銅の使用量は最大で約50%削減できます。

## データセンタにおける電源アーキテクチャの進化

2線式の800V構成では銅の利用効率が高く、3線方式は絶縁要件が緩和される利点がある一方で、負荷分散の制御がより複雑になるという課題があります。

DC高電圧バスは、外部のサイドカーラック側でメインの三相交流（ライン間電圧480Vrms）からの変換で生成されます。ITラック側はこのDC電圧によって給電され、AIインフラの計算性能を高めるために必要なGPUおよびTPUが全て搭載されています。

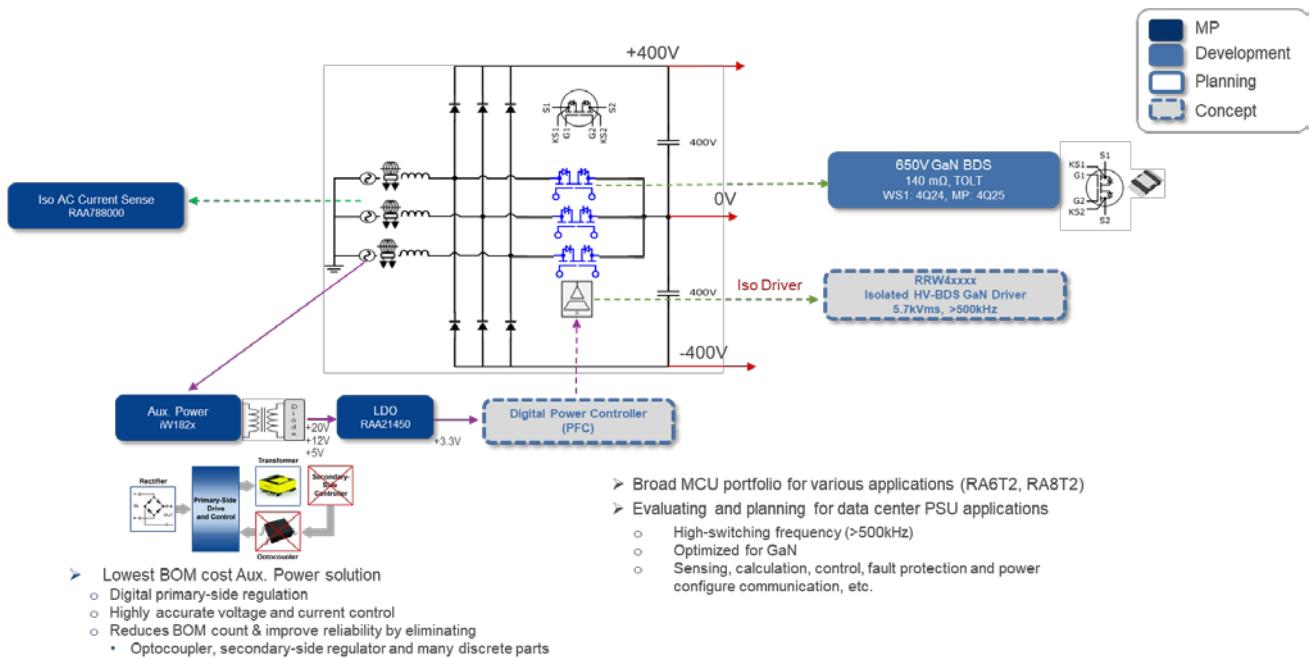

本稿では、新しいアーキテクチャに適合するコンバータおよびトポロジーの具体例を分析するとともに、それらを可能にする技術とコンポーネントについても解説します。サイドカーラック内では、Vienna整流トポロジー（図4参照）を用いた双方向GaNスイッチ（BDS）によって、AC/DCフロントエンドの構成を簡素化し、コストを削減しながら、800V DCバスを生成することができます。サイドカーラック向けAC/DC構成ブロックの電力レベルは、20kW以上が主流となりつつあります。

注: 熱設計電流は、CPUでピーク電流の約50～70%、AIで約70%、ネットワーキングで約90%が目安です。

図1: SoC電力トレンド – 最大電流

## データセンタにおける電源アーキテクチャの進化

図2: 次世代800V HVDC電力供給アーキテクチャ

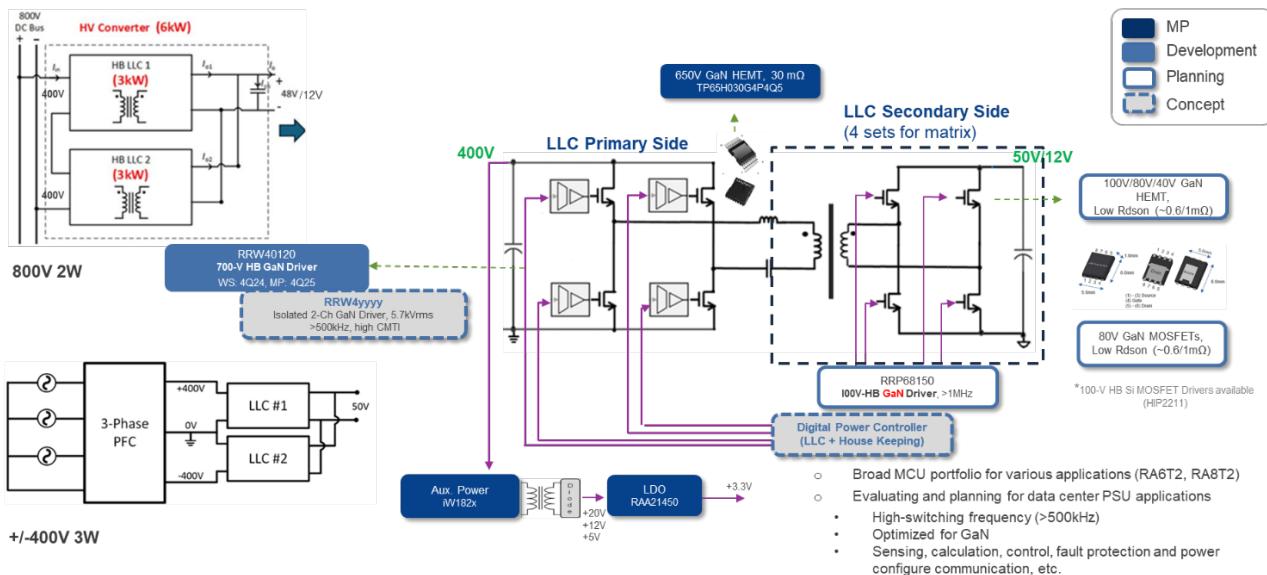

ITラック内では、800Vから48Vへの16:1変換を実現するDC/DCトポロジーとして、LLCダイレクトカレントトランス(DCX)構成が最も有効です。この場合には、2段階の直列構成が用いられ、DC入力電圧全体をサポートします。(図5参照)。ここでも、GaNスイッチが重要な役割を果たします。MHzレベルでスイッチングできる特性により、損失を抑制しつつ高周波動作を実現できるため、小型化と高電力密度の両立が求められる新しいラック構成に最適です。低電圧側では、DCXが中間電圧の48Vを生成し、既存のエコシステム全体を再利用できるようにします。この構成要素として、性能とサイズの要件を満たすために、シリコンMOSFETまたはGaN HEMTのいずれも選択肢となります。このDC/DCコンバータトポロジーは、64:1変換にも応用可能です。48V IBCを省略して12Vへ直接変換することで、2段階構成で達成可能な96%の効率を超えることが出来れば、変換段数の削減が可能になります。より直接的なアプローチとしては、48Vからコア電圧への直接変換も検討されています。この場合には、すべての仕様を満たすために、90%以上の電力変換効率、2A/mm<sup>2</sup>以上の電流密度、3kA/μsec以上の過渡応答特性を満たすDC/DCトポロジーが必要になります。全体的な性能をさらに高めるために、さまざまな構成の組み合わせが検討されています。例えば、現行IBC(中間バスコンバータ)の4:1構成を8:1構成に置き換えることや、GaNを用いた8スイッチのハイブリッドスイッチキャップ方式(1000W/in<sup>3</sup>)によって6Vへ降圧することで、電力ステージをより低い電圧で動作させ、コア電圧への変換効率をさらに向上させることができます。

実際には、GPUへの電力要求が、数kW規模に達するため、低電圧側でも課題が生じます。このような大電力を効率的に供給するためには、従来とは異なる電力供給方式が求められます。その一つとして、SoCの反対側から垂直方向に電力を供給して分配損失を低減する垂直電力供給(VPD)方式が検討されています。この垂直電力供給(VPD)方式は、サイズと寄生要素を抑えるためにインダクタやコンデンサとアクティブ素子を高度に統合したモジュール構成で実装され、最大ブレードサイズの高さに収まるように設計されています。

## データセンタにおける電源アーキテクチャの進化

また、最終段の電圧変換には、高周波の統合型電圧レギュレータ(IVR)が用いられる場合があります。ルネサスのシステムアーキテクチャは現在、これら複数の代替アプローチを検討しながら、利用可能な技術やロードマップに基づいて最適な性能評価を行い、OEMやハイパースケーラーが次世代アーキテクチャを設計する際に最適な支援を行っています。

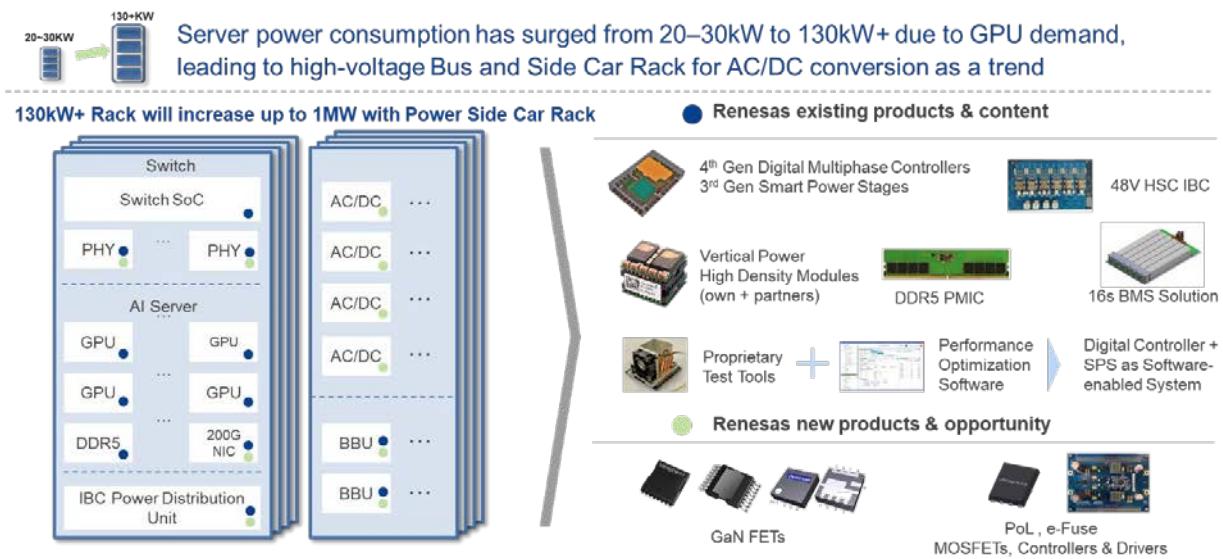

ルネサスは、これまで複数世代にわたり、データセンター向け電源ソリューションを提供してきました。ITラック内のブレードに搭載されるすべてのソケットに対応するだけでなく、次世代アーキテクチャ要素にも対応しています。この次世代要素技術を支えているのが、GaNおよびSiスイッチ、IBCおよびマルチフェーズコアソリューション用のデジタルコントローラ、ドライバ、そしてデジタル/アナログのPoLおよびBMSコントローラなどの豊富な電源ポートフォリオです(図3参照)。

図3: 現代のデータセンタでAI電源ソリューションを支えているルネサスの電源ポートフォリオ

## データセンタにおける電源アーキテクチャの進化

図4: 次世代サイドカーラック向けのBDS(双方向GaNスイッチ)搭載三相PFC Vienna整流回路

図5: 次世代ITラック向けのHVバスデータセンタDC/DCソリューション

## オープンコンピュートプロジェクトの基本原則への準拠

ここで紹介する内容は、オープンコンピュートプロジェクト(OCP)の基本原則に則ったものです。本稿の目的は、新しいアーキテクチャによって生じる課題に対し、標準化されたオープンなトポロジーアプローチを提示して、業界全体での採用を促することにあります。

## データセンタにおける電源アーキテクチャの進化

これにより、ITラック全体での銅使用量削減と、グリッドからコアに至る電力経路全体の効率向上が実現し、持続可能なITラック設計を可能にします。本稿で取り上げるDC/DCアプローチは、フルブリックサイズでおよそ12kW級の電力レベルにおいて実証済みであり、電力スケーリングへの柔軟な対応が可能です。さらに、現在の48Vからより低い中間電圧への移行を視野に入れて、ブレードおよびITラック全体の電力密度と効率の更なる向上が期待されています。また、新アーキテクチャの回路構成に用いられるこれらの技術やコンポーネントは、サイドカーAC/DCラックにも応用可能です。GaN双方向スイッチおよび単方向スイッチデバイスを活用することで、トポロジーを簡素化し、効率性とコスト効率の両面で優れた性能を発揮できます。

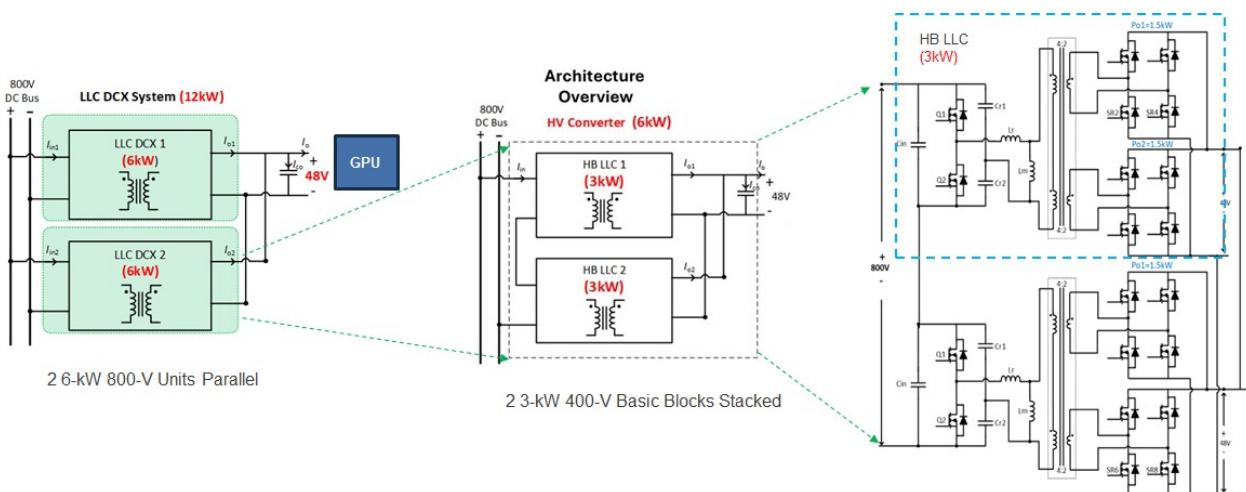

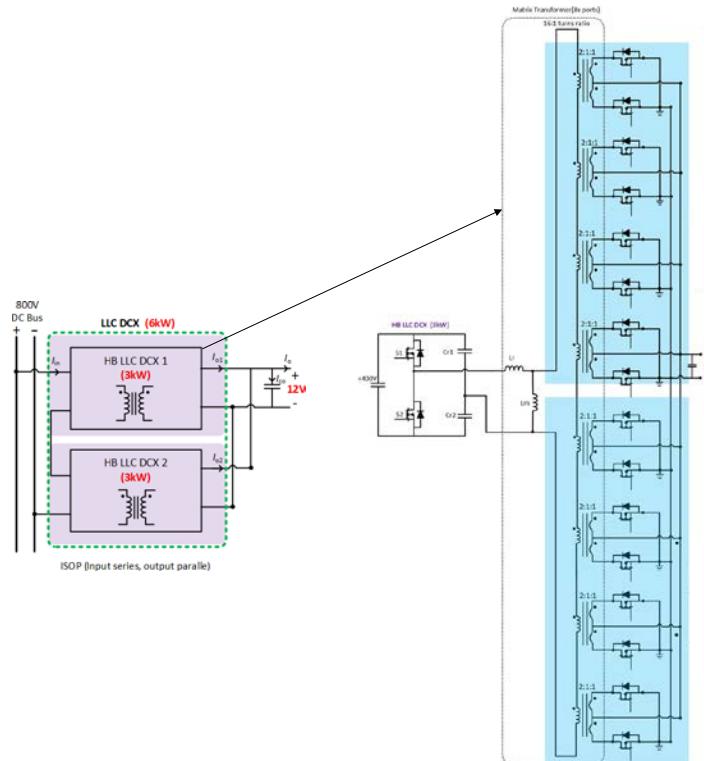

## ITラック向けの16:1 800V DC/DCコンバータ設計

図6では、約12kWクラスとなる800V入力から48V出力への高電圧DC/DCコンバータに採用されたシステムアーキテクチャとトポロジーを示しています。6kWコンバータを2台構成し、それぞれを独立して設計・実装した後、入力および出力を並列に接続することで、12kWの高出力に対応します。各6kWユニットは、3kW対応400V入力から48V出力へのLLC方式DCXコンバータを2台直列に積層した構成で、入力側を直列接続することで800V入力に対応し、出力側は並列接続で6kWの高出力を実現します。このように、3kW対応400V入力から48V出力へのLLC方式DCXコンバータが、高電圧DC/DCシステムにおける基本構成ブロックとなります。このアーキテクチャは高い拡張性を備えており、複数のブロックを並列または直列に組み合わせることで、柔軟なスケーラビリティを確保することができます。

図6:12kW 800V入力48V出力の高電圧DC/DCシステムのアーキテクチャ

## 高効率・高電力密度を実現する主要システム技術

高電圧DC/DCシステムにおいて高効率かつ高電力密度を実現するための主要技術として、LLCダイレクトカレントトランスマトリックストラnsの2つが挙げられます。

### LLCダイレクトカレントトランス

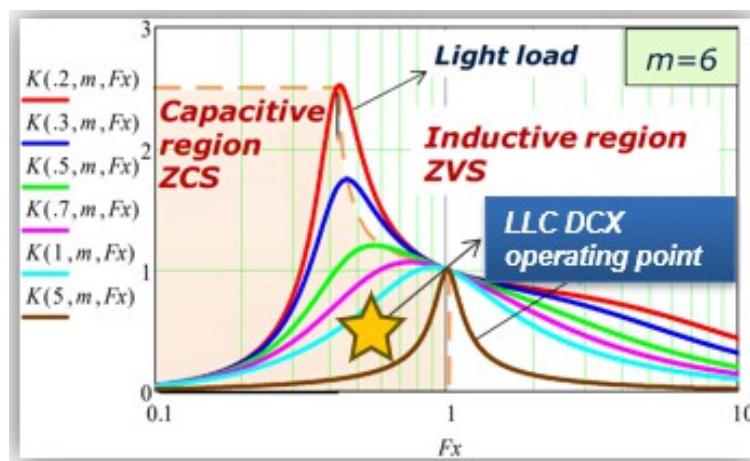

LLC共振コンバータは、ソフトスイッチングを実現できる特性から広く採用されており、損失と電磁干渉(EMI)を低減します。また、LLCは高周波動作によって高い電力密度を実現できる点も大きな特長です。さらに、新しい800V DC/DCアーキテクチャ特有の構成により、LLCダイレクトカレントトランスで動作させることが可能となり、高効率化や制御の簡素化といった追加の利点も得られます。この新しい高電圧DC/DCシステムでは、48Vまたは12Vの出力は必ずしも制御する必要がありません。下流の低電圧DC/DC段が電圧制御を担い、GPUデバイスに安定したDC電圧を供給できるためです。

これにより、LLCをDCXモードで設計・動作させることが可能になります。標準的なLLCコンバータがスイッチング周波数を変化させて出力電圧を制御するのに対し、LLCダイレクトカレントトランスは常に共振周波数付近で動作します。この動作点ではゲインがほぼ1となり、一次側スイッチではZVS(ゼロ電圧スイッチング)、二次側ではZCS(ゼロ電流スイッチング)を実現します。この方式は、トランジスタの巻線比によって決定される明確な入力・出力比に基づいて、電力を高効率に伝送することにより、LLCダイレクトカレントトランスは固定変換比で動作し、トランジスタのように機能します(このため「DCX」と呼ばれます。図7参照)。標準的なLLCコンバータでは、電圧制御のためにクローズドループ制御が必要です。これは通常、高速ADCによる複数の電圧・電流信号のサンプリングと、各スイッチングサイクル内のリアルタイム制御アルゴリズムの実行を伴います。一方、LLCダイレクトカレントトランスはその動作特性上、オープンループ制御で動作します。出力電圧を制御する必要がないため、時間のかかる複雑な制御ループを省略できます。定義済みのスイッチング周波数でオープンループ動作するため、リアルタイム制御を行う必要がありません。高速ADCも不要です。一部の高レベルの保護機能に対応した低速ADCによる監視のみで十分となるためです。その結果、標準的なマイコンを使用してLLCダイレクトカレントトランスの制御を実装することが可能になります。さらに、LLCダイレクトカレントトランスの活用を進めることで、AIデータセンター向けの800V DCアーキテクチャに最適化されたデジタル電源コントローラを新たに開発できる機会が生まれる可能性もあります。

図7:LLCの代表的な動作カーブ

### マトリックストラns

マトリックストラnsは、LLCダイレクトカレントトランスが高電力密度と高効率を実現するうえで不可欠な技術です。従来のトランスが巻線ごとに個別の磁性体を使用するのに対して、マトリックストラnsは複数の巻線を相互に接続し、共通の磁性体を共有するアレイ構造として設計・構築されており、全体で1つのトランスとして機能します。巻線は主電力用PCB上に統合することができ、同期整流(SR)および出力コンデンサと一体化した構造として設計されます。これにより、基板レイアウトや製造プロセスを最適化できます。図8に示すように、マトリックストラnsの主な利点は以下の通りです。

- 複数フェーズの脚が同一コアを共有し、磁束キャンセルを生成する

- フェーズ間の漏れインダクタンスを精密に制御し、電流分配を改善する

- フェーズ間巻線構成によって磁束キャンセル効果を高め、コア損失とサイズを低減する

- 小型の多相トランスを1つのコアに統合することで、サイズ最適化と、磁気損失の最小化を実現する

- 単相トランスと比較して並列デバイスが不要になる

- 単相トランスに比べて終端損失が少ない

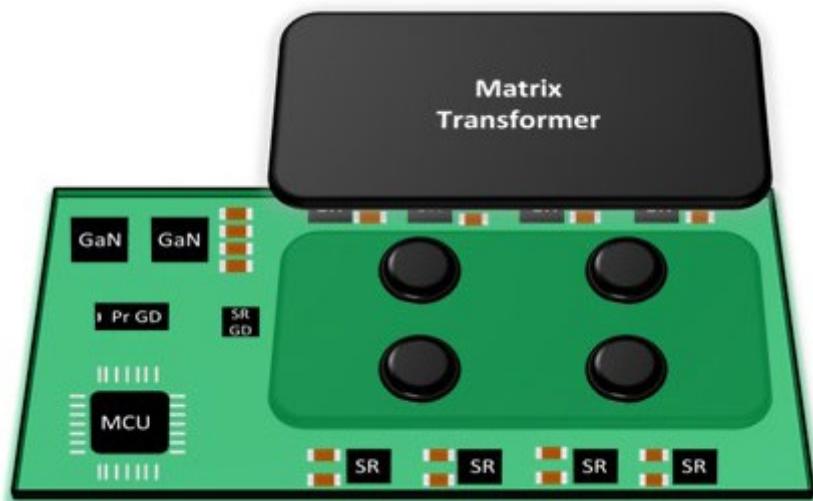

図8:マトリックストラnsを用いたLLCダイレクトカレントトランスの構成

### 基本構成ブロック設計 — 3kW対応400V入力48V出力のLLC方式DCXコンバータ

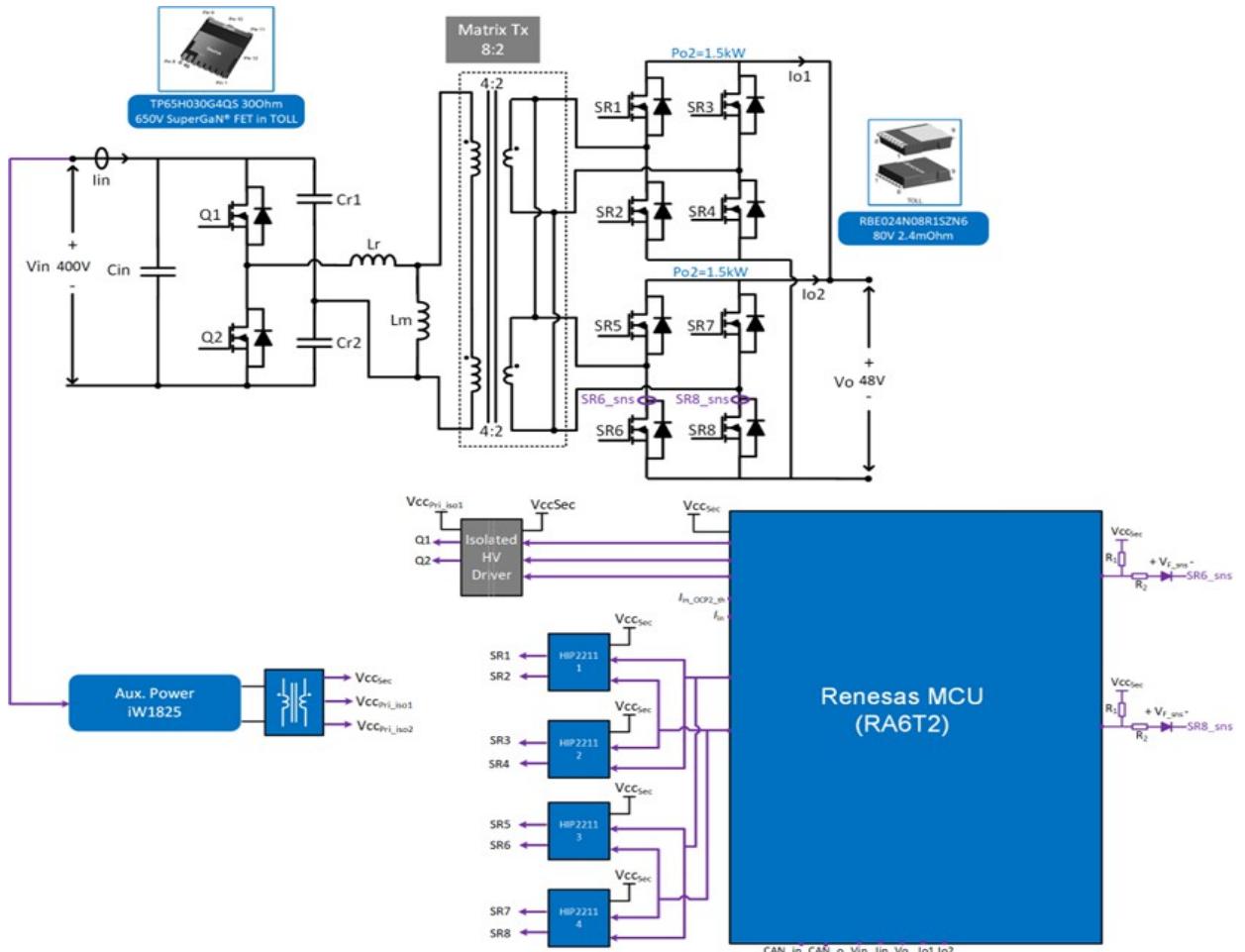

本回路は、図9に示すハーフブリッジ(HB) LLCトポロジーをベースとしています。一次側デバイスには、ルネサス製 [TP65H030G4PRS](#)(650V/30mΩ) GaN FET(TOLTパッケージ)を2個使用しています。このデバイスは、3kW対応400V入力から48V/12V出力するLLC方式DCXコンバータモジュールでの一次側高電圧スイッチとして最適な製品です。LLCダイレクトカレントトランストポロジーにおいて、最小の損失で最高の性能を発揮するパラメータの組み合わせを実現します。さらに、このGaNデバイスは上面冷却に対応しており、実装や放熱設計に優れています。

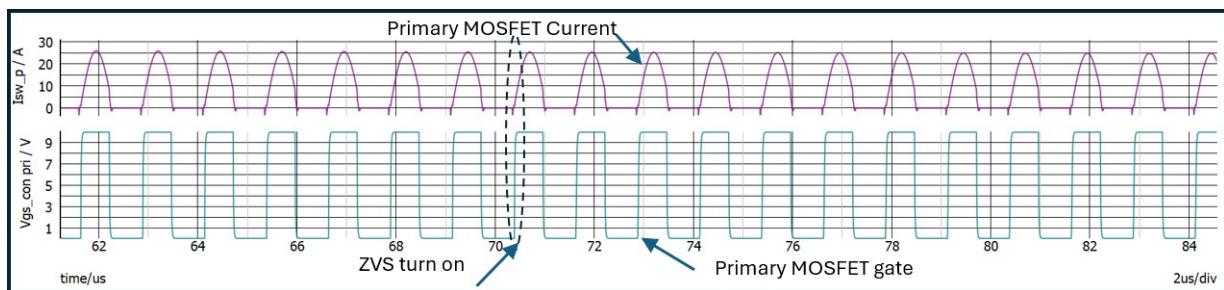

二次側は、2フェーズ構成のフルブリッジ(FB)同期整流(SR)回路で構成されています。各フェーズには、現在開発中のルネサス製 [RBE024N08R1SZN6](#)(80V/2.4mΩ) MOSFET(BSCパッケージ)を4個ずつ使用しています。各SRフェーズは、約1.5kWの電力を処理します。2フェーズSR構成を採用する主な理由は、高電力・大電流動作時の損失、熱、寄生成分、ゲート駆動の制御を容易にするためです。これにより、デバイスの並列接続が不要となり、漏れインダクタンスの制御に伴う複雑さを回避できます。なお、12V出力を実現する場合は、二次側のフェーズ数を増やし、センタータップ構成とローサイドドライバを組み合わせて設計します。48V出力版の設計では、マトリックストラns構造を採用しています。2フェーズSR回路の二次側巻線は、同一トランスクアの2つの脚にそれぞれ巻かれています。これにより、コアサイズの最適化と磁気損失の低減を両立します。動作および制御の観点から見ると、ハーフブリッジLLCトポロジー(HB LLC)はDCXモードで設計・制御されており、常に共振周波数で動作します。動作範囲全体でZVS(ゼロ電圧スイッチング)を達成し、650kHz～1MHzのスイッチング周波数により、高い電力密度を実現します。制御デバイスには、ルネサス製 [RA6T2マイコン](#)を使用しています。前述のとおり、LLCダイレクトカレントトランスでは出力電圧の制御が不要なため、時間のかかる複雑な制御ループやリアルタイム制御を実装する必要がありません。RA6T2マイコンは、オープンループPWMコントロールや二次側の同期整流(SR)制御をはじめ、監視機能やフォルト処理機能を実行するのに十分な処理性能と内部リソースを備えています。HB-LLCはフォワード動作を行うため、SRのスイッチング信号は基本的に一次側スイッチのPWM信号に追従します。これにより、マイコン側の制御要件を軽減できます。基本的なLLCおよびSR制御に加えて、損失を最小化し、効率を最大化するための高度な制御アルゴリズムも存在しますが、本稿ではその詳細については扱いません。一次側および二次側のPWM信号はいずれも同一のマイコンによって生成され、このマイコンは二次側のグランド基準上に配置されています。一次側スイッチング用PWM信号は、ガルバニック絶縁を介して伝送され、絶縁型の高電圧・高速ゲートドライバによって駆動されます。これにより、望ましいスイッチング性能を確保します。一方、二次側では絶縁型ゲートドライバは不要ですが、高電流FETを高スイッチング周波数で駆動するための十分なドライバ強度が求められます。電力損失や熱設計にも配慮が必要です。二次側ドライバには、ルネサス製100V対応ハーフブリッジ(HB)ゲートドライバ [HIP2211](#)を採用しており、1つのLLCダイレクトカレントトランス回路につき4個のデバイスを使用しています。また、二次側にGaNスイッチを採用し、適切なドライバと組み合わせることで、さらなる高効率化を実現する構成も可能です。

図9:HVDC基本構成ブロック設計 — 3kW対応400V入力48V出力のLLC方式DCXコンバータ

補助電源は、HVDCシステムにおいても欠かせない重要な要素です。補助電源は、マイコン、ゲートドライバ、各種周辺回路にそれぞれ異なる電圧レベルで電力を供給し、電圧・電流の制御精度やガルバニック絶縁要件を満たす必要があります。さらに、800V DCバスとの接続および切断時には、特有の起動/シャットダウンシーケンスを適切に制御しなければなりません。3kW対応400V入力48V出力のLLC方式DCXコンバータ設計では、ルネサス製*iW1825*フライバックコンバータを補助電源として使用しています。*iW1825*は、700V耐圧のパワーMOSFETと高性能デジタルAC/DCコントローラを統合したフライバックコンバータです。このデバイスは、ルネサス独自の一次側センシング技術を採用しており、フォトカプラやその他の二次側フィードバック回路を不要とします。これにより、優れたライン/ロードレギュレーション(負荷調整機能)を実現することで、高い信頼性と部品点数の削減によるBOMコスト低減との両立を実現します。

### トランス設計

LLC用途で一般的に使用される従来型トランスは、巻線を備えた独立したフェライトコアを必要とします。しかし、従来型トランスは大型で、漏れインダクタンスの制御が難しく、また平面型トランスのように同期整流(SR)やコンデンサを一体化できないため、超高電力密度を求める用途には適していません。そのため、LLCダイレクトカレントトランス用途には、平面構造を基盤としたマトリックストラスが最適とされています。

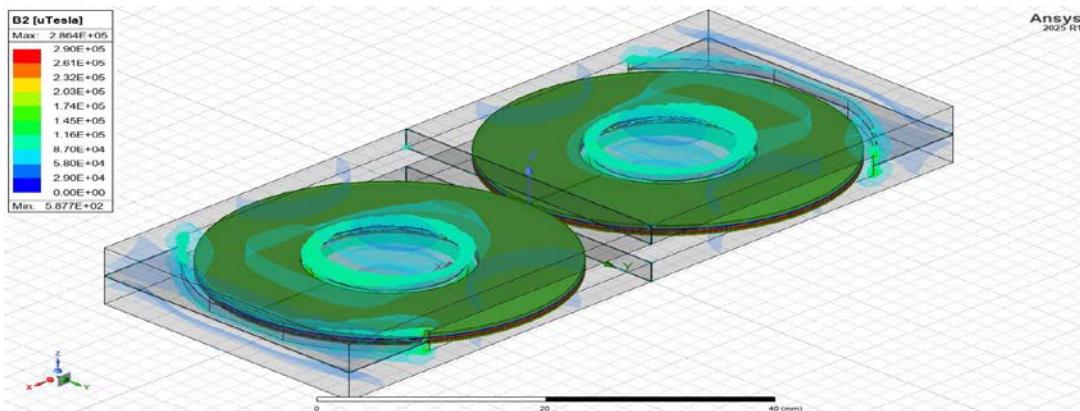

非一体型構造では磁束分布が不均一になり、結果としてコア損失が増加する一方で、一体型構造では磁束が均一に分布するため、コア損失を最小限に抑えることができます。本設計に使用するトランスは、ルネサスのパートナー企業であるPaytonグループと共同で開発されました。Ansysツール上で二脚構造(二本脚構成)の3Dモデルを作成し、複数のバリエーションを解析して導通損失およびコア損失を最小化しました(図10参照)。コア全体に均一なエアギャップを設けることで、磁束および損失を分散させ、コアの利用効率を最大化し、さらにコア損失の低減を実現しています。

### 試験結果 — 3kW対応400V入力48V出力のLLC方式DCXコンバータ

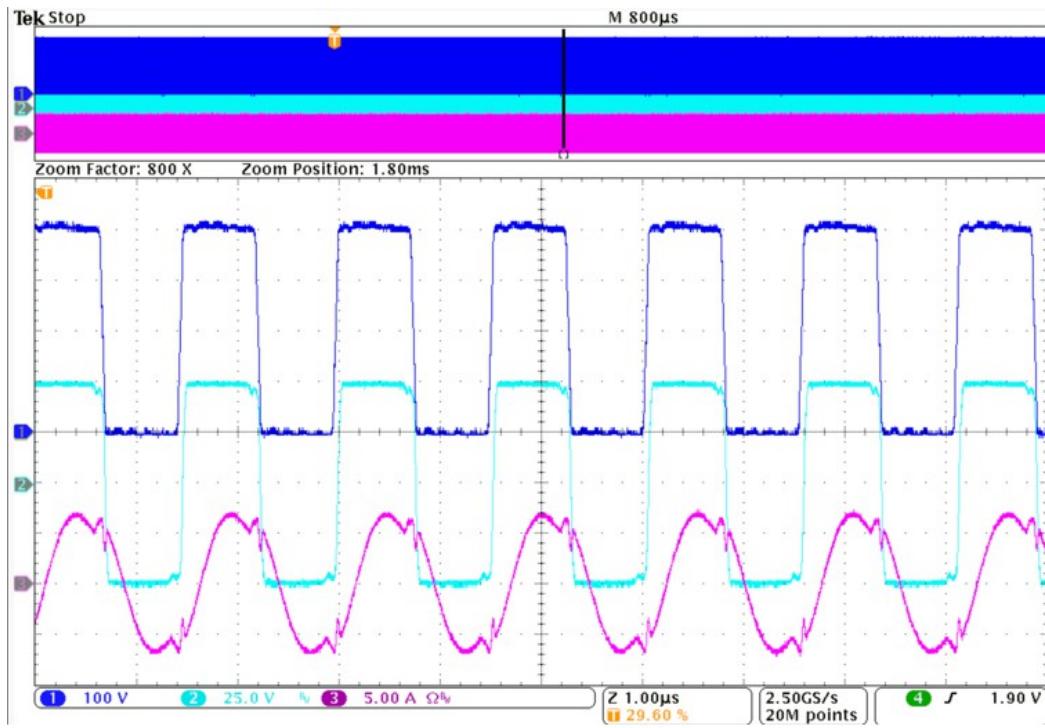

3kW対応400V入力48V出力のLLC方式DCXコンバータを設計し、ハードウェア試作機を製作して評価試験を実施しました。設計の最適化を進めることで、基板サイズをさらに縮小し、最終的には標準のフルブリックモジュールよりもやや大きいサイズ内に、12kWシステム全体を収めることを目指しています。強化絶縁要件に加え、クリアランスと沿面距離要件を満たすことも求められるため、オンボードコンバータのフォームファクタ設計には大きな課題が伴います。図11に示すとおり、このLLC方式DCXコンバータは約650kHzのスイッチング周波数で動作し、一次側スイッチでZVS(ゼロ電圧スイッチング)、二次側スイッチでZCS(ゼロ電流スイッチング)を実現しています。

図10: 均一なエアギャップを設けたコア構造のAnsysツールによる3D解析ビュー。磁束密度がコア全体に均等に分布して低損失化を実現

CH1: Primary-side switching node voltage (100V/div)

CH2: Secondary-side transformer output voltage (25V/div)

CH3: Primary current (5A/div)

図11:LLCダイレクトカレントトランス試作機のテスト波形

## 64:1 800V DC/DCコンバータ拡張

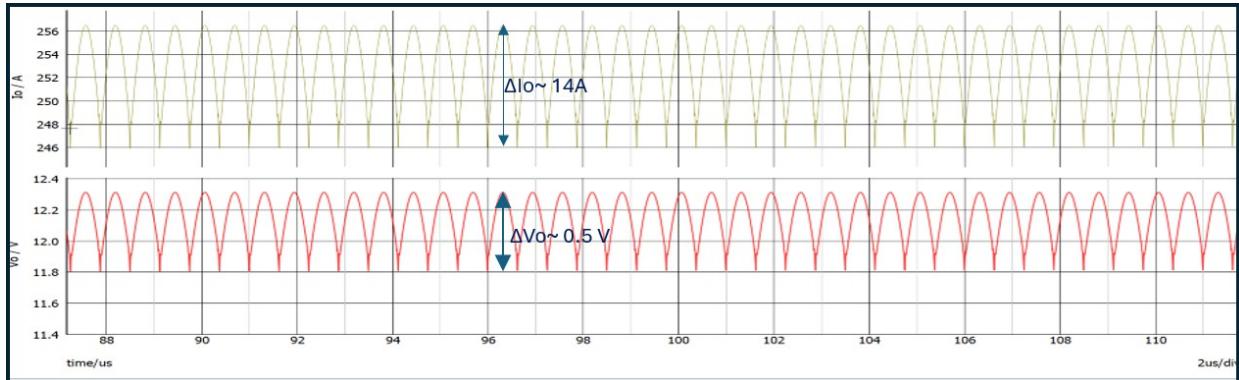

図12に示すように、800V入力から12V出力へのLLC方式DCXコンバータのシステムアーキテクチャは、800V入力から48V出力への構成とほぼ同様です。この構成では、二次側センタータップ構成(8系統)を採用したLLCダイレクトカレントトランスポロジーが推奨されます。これにより、二次側の同期整流(SR)電流と導通損失が低減され、全体の効率がさらに向上します。この設計は現在進行中であり、2個のトランスを用いた構成、1個のトランスを用いた構成、出力数を変更した構成など、さまざまな代替案を評価し、最適な性能と電力密度を追求しています。

図12: 12V出力のLLCダイレクトカレントトランスの構成

Simplisツールを用いたシミュレーション解析(図13および図14)により、さまざまな負荷条件下での効率をベンチマークし、最適なトポロジー構成を選定しました。3kW出力時の効率は約96.7%と見積もられています。これは48V出力時の結果よりも約1%低い値ですが、変換段数を1段削減できるという点で非常に大きなメリットがあります。

図13:一次側共振タンク電流および二次側スイッチ電流

図14:3kW負荷時の出力電圧および電流

## AC/DC(フロントエンド)PFCコンバータ

図4に示すように、サイドカーラック内の主要要素の1つが、AC/DC(フロントエンド)PFCコンバータです。

このAC/DC PFCは商用電力網(ユーティリティグリッド)と接続し、力率1(ユニティ力率)を維持するとともに、800Vの安定したDCバスを供給する役割を担います。Vienna整流器は、単方向電力フロー用途におけるAC/DC PFCコンバータのトポロジーとして、最も広く採用されている構成の一つです。高位ブロック図では、双方向GaNデバイスが統合されており、従来のバック・トゥ・バック接続スイッチを直列接続する方式と比べ、高電力密度用途において、より有利で魅力的な構成となっています。Vienna整流器にBDS(双方向GaNスイッチ)を使用する主な利点として、導通損失の低減、3つのフローティング(浮遊型)高電圧ドライバのみで実装できるシンプルな構成、高いスイッチング周波数によるブースト(昇圧)インダクタの小型化などが挙げられます。これらにより、さらなる高電力密度を実現します。

この双方向スイッチは、理想的な4象限スイッチを実現し、ラテラル構造でありながら、基板(ソースダウン)を通じた放熱を実現するだけでなく、将来的にはトップ側放熱にも対応可能です。逆回復がほぼ発生せず、高速スイッチングが可能なため、スイッチング損失の面でも非常に優れた性能を発揮します。

損失の主な要因は導通損失であるため、デバイスのアクティブ領域を最大化する必要があります。ルネサスの新しい高電圧対応BDS(双方向GaNスイッチ)を1つ使用することで、従来の標準パワートランジスタ2個を置き換えることができます。これにより、電力ステージのサイズを小型化しつつ効率を向上させ、さらに、通常はオン抵抗( $R_{ds\_on}$ )が半分で総ゲート電荷が大きくなるトランジスタ2個直列構成に比べて、トータルコストの削減に寄与できると期待されています。

## 結論

本稿では、AIコアの進化に伴い急速に増大する電力需要に対応するため、メガワット級の電力を必要とする最新のAIデータセンターに向けた新しい高電圧アーキテクチャの全体像を示しました。

## データセンタにおける電源アーキテクチャの進化

---

そして、アーキテクチャの進化に沿って、ITラックおよびサイドカーラックにおける2つの主要構成ブロックを詳しく解説しました。効率と電力密度の両面で求められる性能を実現するため、拡張性の高いオープンなトポロジーとその技術的なアプローチ手法を提案しています。

GaNデバイスは、単方向スイッチおよび双方向スイッチの両方の用途において重要な役割を果たしており、スイッチング損失の低減に加え、マトリックストラnsを用いた16:1 DCXではスイッチング周波数の向上と、AC/DC(フロントエンド)ではトポロジーの簡素化を実現することで、全体として高い信頼性と優れた性能を提供します。3kW対応400V入力48V出力のLLC DCXコンバータについて、設計実装の詳細とともに、拡張モデルに対する電気的および熱機械シミュレーション結果を提示しました。

ここで確立された設計原則と手法は、AIデータセンターの電力供給における次なる課題に取り組むための重要な基盤となります。現在、さらなるアーキテクチャ構成の設計・試作・評価が進められており、将来の技術革新トレンドを見据えた性能検証とベンチマークが実施されています。本稿で示したアプローチは、データセンターOEMおよびハイパースケーラーがルネサスのような半導体サプライヤーと協働し、次世代に向けた高効率・高性能な電源ソリューションを構築することで、より高電力で高度なAIハードウェアの実装を可能にする道筋となることが期待されています。

## 関連情報

ルネサスの[パワーディスクリート](#)および[パワーマネジメントソリューション](#)

[NVIDIA 800 VDC Architecture Will Power the Next Generation of AI Factories](#)

[NVIDIA とパートナーが Vera Rubin に向けた次世代高効率ギガワット AI ファクトリーを推進](#)

[オープンコンピュートプロジェクト\(OCP\)](#)

ルネサスエレクトロニクスまたはその関連会社(Renesas) 無断複写・転載を禁じます。全著作権所有。すべての商標および商品名は、それぞれの所有者のものです。ルネサスは、本書に記載されている情報は提供された時点では正確であると考えていますが、その品質や使用に関してリスクを負いません。すべての情報は、商品性、特定の目的への適合性、または非侵害を含むがこれらに限定されないことを含め、明示、默示、法定、または取引、使用、または取引慣行の過程から生じるかどうかを問わず、いかなる種類の保証もなく現状のまま 提供されます。ルネサスは、直接的、間接的、特別、結果的、偶発的、またはその他のいかなる損害についても、そのような損害の可能性について通知された場合でも、本書の情報の使用または信頼から生じる責任を負いません。ルネサスは、予告なしに製品の製造を中止するか、製品の設計や仕様、または本書の他の情報を変更する権利を留保します。すべてのコンテンツは、米国および国際著作権法によって保護されています。ここで特に許可されている場合を除き、本資料のいかなる部分も、ルネサスからの事前の書面による許可なしに、いかなる形式または手段によっても複製することはできません。訪問者またはユーザは、公共または商業目的で、この資料の派生物を修正、配布、公開、送信、または作成することを許可されていません。(Rev.1.0 Mar 2020)

### 本社所在地

〒 135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

<https://www.renesas.com>

### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄りの営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。:

<https://www.renesas.com/contact-us>

### 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の商標です。すべての商標および登録商標は、それぞれの所有者に帰属します。

© 2025 Renesas Electronics Corporation. All rights reserved.

Doc Number: R30WP0013JJ0100