発行日: 2024年12月27日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 https://www.renesas.com/jp/ja/support/contact/

| 製品  | 品分類   | MPU & MCU                  | 発行番号   | TN-RA*-A0 | )132A/J                                                 | Rev. | 第1版 |  |  |

|-----|-------|----------------------------|--------|-----------|---------------------------------------------------------|------|-----|--|--|

| 題名  | 誤記訂   | 正通知 RA0E1 ユーザーズマニュアル Rev.1 | 情報分類   | 技術情報      |                                                         |      |     |  |  |

| 適   |       |                            | 対象ロット等 |           |                                                         |      |     |  |  |

| 用製品 | RA0E1 | グループ                       | 全て     | 関連資料      | RA0E1 グループユーザーズマニュアル ハードウエア編 Rev.1.00 (R01UH1040JJ0100) |      |     |  |  |

RA0E1 ユーザーズマニュアルハードウェア編 Rev.1.00 (R01UH1040JJ0100) において、下記訂正がございます。

## 今回通知する訂正内容

| 訂正箇所                                                                  | 該当ページ        | 内容   | 本通知での<br>該当ページ |

|-----------------------------------------------------------------------|--------------|------|----------------|

| 表 5.5 リセット発生時のLOCO の状態                                                | p.60         | 誤記訂正 | p.2            |

| 図 9.1 低消費電力モードの遷移                                                     | p.106        | 誤記訂正 | p.3            |

| 表 11.1 ICUの仕様                                                         | p.125        | 誤記訂正 | p.4, p.5       |

| 13.2 使用上の注意事項                                                         | p.154        | 誤記訂正 | p.6            |

| 17.1 概要                                                               | p.209        | 誤記訂正 | p.7, p.8       |

| 21.3.22 SO1: シリアル出力レジスタ1                                              | p.363        | 誤記訂正 | p.9, p.10      |

| 25.2.3 ADM2: A/D コンバータモードレジスタ2                                        | p.575        | 誤記訂正 | p.11           |

| 25.2.6 ADS:アナログ入力チャネル指定レジスタ                                           | p.579        | 誤記訂正 | p.12           |

| 図 25.13 ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)動作タイミングの例                    | p.588        | 誤記訂正 | p.13           |

| 25.7 スヌーズモード機能                                                        | p.604        | 誤記訂正 | p.14           |

| 25.7.1 ソフトウェアトリガの入力によるA/D 変換                                          | p.605, p.606 | 誤記訂正 | p.15, p.16     |

| 図 25.25 ハードウェアトリガ待機モードでスヌーズモードを使用するときのブロック図                           | p.607        | 誤記訂正 | p.17           |

| 表 28.5 スタートアップ領域選択およびセキュリティ設定のエクストラビットのマッピング(アドレス (P/E): 0x0000_0010) | p.634        | 誤記訂正 | p.18           |

| 表 28.6 アクセスウィンドウ情報プログラムのエクストラビット<br>のマッピング (アドレス (P/E): 0x0000_0010)  | p.634        | 誤記訂正 | p.19           |

| 28.3.25 PNRn:型名レジスタn (n = 0~3)                                        | p.642        | 誤記訂正 | p.20, p.21     |

| 表 28.15 基本機能                                                          | p.645        | 誤記訂正 | p.22           |

| 29 真性乱数生成器 (TRNG)                                                     | p.666        | 誤記訂正 | p.23           |

| 表 31.1 絶対最大定格                                                         | p.668        | 誤記訂正 | p.24, p.25     |

| 表 31.11 I/O その他の特性                                                    | p.674, p.675 | 誤記訂正 | p.26, p.27     |

| 表 31.12 動作電流とスタンバイ電流 (1)(2/2)                                         | p.677        | 誤記訂正 | p.28, p.29     |

| 表 31.16 リセットタイミング (2/2)                                               | p.684        | 誤記訂正 | p.30           |

| 図 31.11 リセット入力タイミング (2)                                               | p.684        | 誤記訂正 | p.31           |

| 表 31.46 LVD1 特性 (2/2)                                                 | p.719        | 誤記訂正 | p.32           |

## ドキュメント改善計画

本訂正内容については、次回ユーザーズマニュアル改版時に修正を行います。

発行日: 2024年12月27日

## 修正前:表 5.5 リセット発生時の LOCO の状態 (p.60)

## 表 5.5 リセット発生時の LOCO の状態

|      |       | リセット要因            |  |  |  |  |  |  |

|------|-------|-------------------|--|--|--|--|--|--|

|      |       | POR/LVD0/LVD1 その他 |  |  |  |  |  |  |

| LOCO | 有効/無効 | 初期化(有効)           |  |  |  |  |  |  |

## 修正後:表 5.5 リセット発生時の LOCO の状態

#### 表 5.5 リセット発生時の LOCO の状態

|      |       | リセット要因                               |                   |  |  |  |  |  |  |

|------|-------|--------------------------------------|-------------------|--|--|--|--|--|--|

|      |       | POR/LVD0/LVD1                        | その他               |  |  |  |  |  |  |

| LOCO | 有効/無効 | 初期化(無効)<br>ただし、IWDT動作時、LOCO クロックはLCS | STPの値にかかわらず発振します。 |  |  |  |  |  |  |

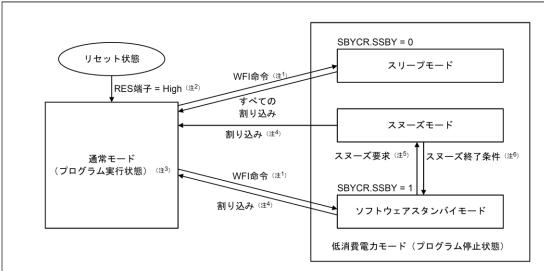

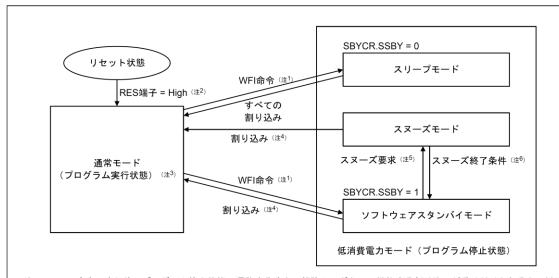

#### 修正前:図 9.1 低消費電力モードの遷移 (p.106)

図 9.1 に通常モードと低消費電力モード間の遷移を示します。

- 注 1. WFI 命令の実行後、プログラム停止状態へ遷移する途中に解除トリガとして機能する割り込みが受け付けられると、低消 費電力モードへは遷移せずに、MCU は割り込み例外処理を実行します。

- リセット状態から通常モードへ遷移した後は、MOCO が動作クロックソースです

- スリープモード、ソフトウェアスタンパイモード、またはスヌーズモード時の割り込みによって、通常モードへ遷移します。クロックソースは低消費電力モードへ遷移する前と同じです。 注 3.

- 表 9.3 を参照してください。

- 注 5.

- 「9.8.1、スヌーズモードへの遷移」を参照してください。 「9.8.3、スヌーズモードからソフトウェアスタンバイモードへの復帰」を参照してください。

図 9.1 低消費電力モードの遷移

#### 修正後: 図 9.1 低消費電力モードの遷移

図 9.1 に通常モードと低消費電力モード間の遷移を示します。

- 注 1. WFI 命令の実行後、プログラム停止状態へ遷移する途中に解除トリガとして機能する割り込みが受け付けられると、低消 費電力モードへは遷移せずに、MCU は割り込み例外処理を実行します。

- リセット状態から通常モードへ遷移した後は、HOCO が動作クロックソースです

- スリープモード、ソフトウェアスタンバイモード、またはスヌーズモード時の割り込みによって、通常モードへ遷移しま 注 3. す。クロックソースは低消費電力モードへ遷移する前と同じです。

- 表 9.3 を参照してください。

- 注 5.

- 「9.8.1. スヌーズモードへの遷移」を参照してください。 「9.8.3. スヌーズモードからソフトウェアスタンバイモードへの復帰」を参照してください。

#### 低消費電力モードの遷移 図 9.1

修正前:表 11.1 ICUの仕様 (p.125)

## 11. 割り込みコントローラユニット (ICU)

## 11.1 概要

割り込みコントローラユニット (ICU) は、ネスト型ベクタ割り込みコントローラ (NVIC) およびデータトランスファコントローラ (DTC) の両モジュールにどのイベント信号がリンクされるかを制御します。ICU はノンマスカブル割り込みも制御します。

表 11.1 に ICU の仕様、図 11.1 に ICU のブロック図、表 11.2 に ICU の入出力端子を示します。

#### 表 11.1 ICU の仕様

| 項目                                                     |                                            | 内容                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| マスカブル<br>割り込み                                          | 周辺機能割り込み                                   | ● 周辺モジュールからの割り込み<br>要因数:33                                                                                                                                                                                                                                                                                         |

|                                                        | 外部端子割り込み                                   | <ul><li>● 割り込み検出:立ち下がりエッジ、立ち上がりエッジ、両エッジ。要因ごとに設定可能。</li><li>● 6要因(IRQi 端子 (i = 0~5) からの割り込み)</li></ul>                                                                                                                                                                                                              |

|                                                        | CPU (NVIC) への割り込<br>み要求                    | ● 39 本の割り込み要求を NVIC に対して出力                                                                                                                                                                                                                                                                                         |

|                                                        | DTC 制御                                     | <ul> <li>割り込み要因によって DTC の起動が可能<sup>(注1)</sup></li> <li>割り込み要因の選択方式は、NVIC への割り込み要求と同一</li> </ul>                                                                                                                                                                                                                    |

| ノンマスカ<br>ブル割り込<br>み <sup>(注2)</sup> IW<br>リ<br>低<br>RI | NMI 端子割り込み                                 | <ul><li>NMI 端子からの割り込み</li><li>割り込み検出:立ち下がりエッジまたは立ち上がりエッジ</li></ul>                                                                                                                                                                                                                                                 |

|                                                        | IWDT アンダーフロー/<br>リフレッシュエラー <sup>(注3)</sup> | ダウンカウンタのアンダーフローまたはリフレッシュエラー発生時の割り込み                                                                                                                                                                                                                                                                                |

|                                                        | 低電圧検出 1 <sup>(注3)</sup>                    | 電圧監視 1 回路の電圧監視 1 割り込み (LVD_LVD1)                                                                                                                                                                                                                                                                                   |

|                                                        | RPEST                                      | SRAM パリティエラー発生時の割り込み                                                                                                                                                                                                                                                                                               |

| 低消費電力モ                                                 | Ξ— ۴                                       | <ul> <li>スリープモード:ノンマスカブル割り込みまたはその他の割り込み要因によって復帰</li> <li>ソフトウェアスタンバイモード:ノンマスカブル割り込みによって復帰。SBYEDCRn レジスタで割り込みの選択が可能</li> <li>スヌーズモード:ノンマスカブル割り込みによって復帰。SBYEDCRn レジスタで割り込みの選択が可能</li> <li>「11.2.14. SBYEDCR0:ソフトウェアスタンバイ/スヌーズ終了コントロールレジスタ 0」と「11.2.15. SBYEDCR1:ソフトウェアスタンバイ/スヌーズ終了コントロールレジスタ 1」を参照してください。</li> </ul> |

- 注 1. DTC 起動要因については、表 11.5 を参照してください。

- 注 2. リセット解除後に1回だけノンマスカブル割り込みを許可することができます。

- 注 3. これらのノンマスカブル割り込みは、マスカブル割り込みとしても使用可能です。マスカブル割り込みとして使用する場合、NMIER レジスタの値をリセット状態から変更しないでください。電圧監視 1割り込みを許可するには、LVD1CR1.IRQSEL ビットを 1にしてください。

#### 修正後:表 11.1 ICU の仕様

## 11. 割り込みコントローラユニット (ICU)

#### 11.1 概要

割り込みコントローラユニット (ICU) は、ネスト型ベクタ割り込みコントローラ (NVIC) およびデータトランスファコントローラ (DTC) の両モジュールにどのイベント信号がリンクされるかを制御します。ICU はノンマスカブル割り込みも制御します。

表 11.1 に ICU の仕様、図 11.1 に ICU のブロック図、表 11.2 に ICU の入出力端子を示します。

#### 表11.1 ICU の仕様

| 項目                                                                         |                                            | 内容                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| マスカブル<br>割り込み<br>ノンマスカ<br>ブル割り込<br>み <sup>(注2)</sup>                       | 周辺機能割り込み                                   | ● 周辺モジュールからの割り込み<br>要因数:33                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                            | 外部端子割り込み                                   | <ul> <li>割り込み検出:立ち下がりエッジ、立ち上がりエッジ、両エッジ。要因ごとに設定可能。</li> <li>6要因(IRQi 端子(i = 0~5) からの割り込み)</li> </ul>                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| マスカブル 割り込み 外 CF み DT ブル割り込 み (注2) IM リ 低                                   | CPU (NVIC) への割り込<br>み要求                    | ● 39 本の割り込み要求を NVIC に対して出力                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                                                            | DTC 制御                                     | <ul><li>割り込み要因によって DTC の起動が可能<sup>(注1)</sup></li><li>割り込み要因の選択方式は、NVIC への割り込み要求と同一</li></ul>                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| ブル割り込                                                                      | NMI 端子割り込み                                 | <ul><li>NMI 端子からの割り込み</li><li>割り込み検出:立ち下がりエッジまたは立ち上がりエッジ</li></ul>                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| マスカブル<br>割り込み<br>タ<br>C<br>み<br>D<br>ノンマスカ<br>フル割り込<br>み <sup>(注2)</sup> N | IWDT アンダーフロー/<br>リフレッシュエラー <sup>(注3)</sup> | ダウンカウンタのアンダーフローまたはリフレッシュエラー発生時の割り込み                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                                            | 低電圧検出 1 <sup>(注3)</sup>                    | 電圧監視 1 回路の電圧監視 1 割り込み (LVD_LVD1)                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                            | RPEST                                      | SRAM パリティエラー発生時の割り込み                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 低消費電力刊                                                                     | Ξ— <b>ド</b>                                | <ul> <li>スリープモード:ノンマスカブル割り込みまたはその他の割り込み要因によって復帰</li> <li>ソフトウェアスタンバイモード:ノンマスカブル割り込みまたはその他の割り込みによって復帰。SBYEDCRn レジスタで割り込みの選択が可能</li> <li>スヌーズモード:ノンマスカブル割り込みまたはその他の割り込みによって復帰。SBYEDCRn レジスタで割り込みの選択が可能</li> <li>「11.2.14. SBYEDCR0:ソフトウェアスタンバイ/スヌーズ終了コントロールレジスタ 0」と「11.2.15. SBYEDCR1:ソフトウェアスタンバイ/スヌーズ終了コントロールレジスタ 1」を参照してください。</li> </ul> |  |  |  |  |  |  |

- 注1. DTC 起動要因については、表11.5 を参照してください。

- 注2. リセット解除後に1回だけノンマスカブル割り込みを許可することができます。

- 注3. これらのノンマスカブル割り込みは、マスカブル割り込みとしても使用可能です。マスカブル割り込みとして使用する場合、NMIER レジスタの値をリセット状態から変更しないでください。電圧監視1割り込みを許可するには、LVD1CR1.IRQSELビットを1にしてください。

#### 修正前:13.2 使用上の注意事項 (p.154)

#### 13.2 使用上の注意事項

#### 13.2.1 デバッガ使用時の注意事項

フラッシュ読み出し保護 (FRP) が有効であると、メモリはデバッグできません。プログラムをデバッグするときは、フラッシュ読み出し保護 (FRP) を無効にしてください。OFS1.FRPDIS ビットが 1 であるときにのみ、OCD デバッグが有効です。

#### 13.2.2 コンパイラの設定

フラッシュ読み出し保護 (FRP) は、一種の execute-only-memory (XOM) です。保護領域のデータは読み出し可能ではないので、保護領域はリテラルプールのような定数データを有することはできません。したがって、適切なコンパイラの設定が必要です。

#### 修正後:13.2 使用上の注意事項

## 13.2 使用上の注意事項

## 13.2.1 デバッガ使用時の注意事項

フラッシュ読み出し保護 (FRP) が有効であると、メモリはデバッグできません。プログラムをデバッグするときは、フラッシュ読み出し保護 (FRP) を無効にしてください。OFS1.FRPDIS ビットが 1 であるときにのみ、OCD デバッグが有効です。

### 13.2.2 コンパイラの設定

フラッシュ読み出し保護 (FRP) は、一種の execute-only-memory (XOM) です。保護領域のデータは読み出し可能ではないので、保護領域はリテラルプールのような定数データを有することはできません。したがって、適切なコンパイラの設定が必要です。

#### 13.2.3 OFS1 レジスタの保護

OFS1.FRPS[5:0]、OFS1.FRPE[5:0]、OFS1.FRPDIS ビットを上書きすると FRP機能の保護が無効になる可能性があるため、OFS1 レジスタ(アドレス =  $0x0000\_0404$ )はアクセスウィンドウで保護する必要があります。ただし、アクセスウィンドウを設定すると(AWS.FSPRビットを0に設定することを含む)、スタートアップ領域選択機能に使用するAWS.BTFLGおよびFISR.SAS[1:0]ビットの変更も無効になります。このため、FRP機能を使用する場合、スタートアップ領域選択機能は使用できません。スタートアップ領域選択機能については「28.5.2 スタートアップ領域選択」を、アクセスウィンドウについては「28.5.3 アクセスウィンドウによるプロテクション」を参照してください。

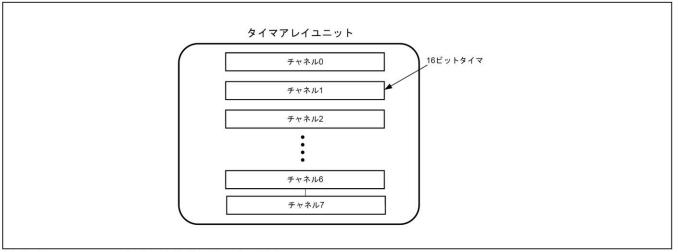

## 修正前:17.1 概要 (p.209)

## 17. タイマアレイユニット (TAU)

#### 17.1 概要

タイマアレイユニットは16ビットタイマを8つ備えています。

各 16 ビットタイマはチャネルと呼ばれ、個別に使用することができます。 さらに、2 つ以上のチャネルで高分解能タイマを構成することができます。

図 17.1 にタイマアレイユニット1 つあたりのチャネル構成を示します。

図 17.1 ユニット 1 つあたりのチャネル構成

ユニット 0 のチャネル 1 と 3 では、16 ビットタイマ 1 つを 8 ビットタイマ 2 つ (上位タイマと下位タイマ) に分割して使用することができます。チャネル 1 と 3 で 8 ビットタイマを使用できる機能は以下の通りです。

- インターバルタイマ(上位または下位8ビットタイマ)および矩形波出力(下位8ビットタイマのみ)

- 外部イベントカウンタ(下位8ビットタイマのみ)

- 遅延カウンタ(下位8ビットタイマのみ)

ユニット 0 のチャネル 7 とシリアルアレイユニットの UART2 とを連携して LIN-bus 通信動作を実現できます。 周辺モジュールクロック (PCLKB) は、RA0E1 のシステムクロック (ICLK) と同じです。

表 17.1 に TAU の機能一覧を示します。図 17.2~図 17.11 に各機能のイメージを示します。

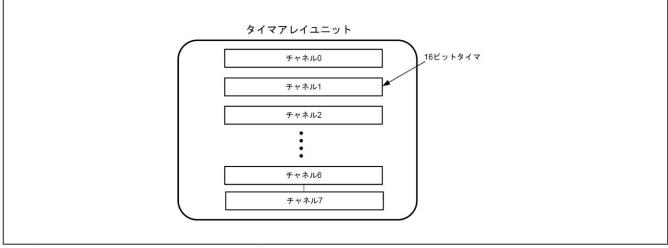

#### 修正後:17.1 概要

## 17. タイマアレイユニット (TAU)

### 17.1 概要

タイマアレイユニットは16ビットタイマを8つ備えています。

各 16 ビットタイマはチャネルと呼ばれ、個別に使用することができます。 さらに、2 つ以上のチャネルで高分解能タイマを構成することができます。

図 17.1 にタイマアレイユニット 1 つあたりのチャネル構成を示します。

図 17.1 ユニット 1 つあたりのチャネル構成

ユニット 0 のチャネル 1 と 3 では、16 ビットタイマ 1 つを 8 ビットタイマ 2 つ (上位タイマと下位タイマ) に分割して使用することができます。チャネル 1 と 3 で 8 ビットタイマを使用できる機能は以下の通りです。

- インターバルタイマ (上位および下位 8 ビットタイマ) および矩形波出力 (下位 8 ビットタイマのみ)

- ◆ 外部イベントカウンタ (下位 8 ビットタイマのみ)

- 遅延カウンタ(下位8ビットタイマのみ)

ユニット 0 のチャネル 7 とシリアルアレイユニットの UART2 とを連携して LIN-bus 通信動作を実現できます。 周辺モジュールクロック (PCLKB) は、RA0E1 のシステムクロック (ICLK) と同じです。

表 17.1 に TAU の機能一覧を示します。図 17.2~図 17.11 に各機能のイメージを示します。

修正前: 21.3.22 SO1: シリアル出力レジスタ 1 (p.363)

21.3.22 SO1: シリアル出力レジスタ 1

Base address: SAU1 = 0x400A\_2200

Offset address: 0x0128

| Bit position:      | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8     | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0     |

|--------------------|----|----|----|----|----|----|-----|-------|---|---|---|---|---|---|----|-------|

| Bit field:         | _  | _  | 1  | I  | _  |    | СКО | [1:0] | 1 | _ |   | _ | - | _ | so | [1:0] |

| Value after reset: | 0  | 0  | 0  | 0  | 1  | 1  | 1   | 1     | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1     |

| ビット   | シンボル     | 機能                                                           | R/W |

|-------|----------|--------------------------------------------------------------|-----|

| 1:0   | SO[1:0]  | チャネル n のシリアルデータ出力<br>0: シリアルデータ出力値が 0<br>1: シリアルデータ出力値が 1    | R/W |

| 7:2   | _        | 読むと0が読めます。書く場合、0としてください。                                     | R/W |

| 9:8   | CKO[1:0] | チャネル n のシリアルクロック出力<br>0: シリアルクロック出力値が 0<br>1: シリアルクロック出力値が 1 | R/W |

| 15:10 | _        | 読むと0が読めます。書く場合、0としてください。                                     | R/W |

SO1 は、シリアルアレイユニット1の各チャネルのシリアル出力バッファレジスタです。

このレジスタの SO[n]ビットの値が、チャネルnのシリアルデータ出力端子から出力されます。

このレジスタの CKO[n]ビットの値が、チャネルnのシリアルクロック出力端子から出力されます。

このレジスタの SO[n]ビットのソフトウェアによる書き換えは、シリアル出力禁止 (SOE1.SOE[n] = 0) 時のみ可能です。シリアル出力許可 (SOE1.SOE[n] = 1) 時は、ソフトウェアによる書き換えは無視され、シリアル通信動作によってのみレジスタの値が変更されます。

このレジスタの CKO[n]ビットのソフトウェアによる書き換えは、チャネル動作停止 (SE1.SE[n] = 0) 時のみ可能です。チャネル動作許可 (SE1.SE[n] = 1) 時は、ソフトウェアによる書き換えは無視され、シリアル通信動作によってのみ CKO[n]の値が変更されます。

また、シリアルインタフェース用端子をポート機能端子として使用する場合は、該当する CKO[n]ビットおよび SO[n]ビットを 1 にしてください。

修正後: 21.3.22 SO1: シリアル出力レジスタ 1

21.3.22 SO1: シリアル出力レジスタ 1

Base address: SAU1 = 0x400A\_2200

Offset address: 0x0128

| Bit position:      | 15 | 14 | 13 | 12 | 11 | 10 | 9          | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0     |

|--------------------|----|----|----|----|----|----|------------|---|---|---|---|---|---|---|-----|-------|

| Bit field:         | 1  | 1  | 1  | 1  | 1  | 1  | - CKO[1:0] |   | 1 | 1 | 1 | _ | _ | 1 | sol | [1:0] |

| Value after reset: | 0  | 0  | 0  | 0  | 0  | 0  | 1          | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1   | 1     |

| ビット   | シンボル     | 機能                                                           | R/W |

|-------|----------|--------------------------------------------------------------|-----|

| 1:0   | SO[1:0]  | チャネル n のシリアルデータ出力<br>0: シリアルデータ出力値が 0<br>1: シリアルデータ出力値が 1    | R/W |

| 7:2   | _        | 読むと0が読めます。 書く場合、0 としてください。                                   | R/W |

| 9:8   | CKO[1:0] | チャネル n のシリアルクロック出力<br>0: シリアルクロック出力値が 0<br>1: シリアルクロック出力値が 1 | R/W |

| 15:10 | _        | 読むと0が読めます。 書く場合、0 としてください。                                   | R/W |

SO1 は、シリアルアレイユニット1の各チャネルのシリアル出力バッファレジスタです。

このレジスタの SO[n]ビットの値が、チャネルnのシリアルデータ出力端子から出力されます。

このレジスタの CKO[n]ビットの値が、チャネルnのシリアルクロック出力端子から出力されます。

このレジスタの SO[n]ビットのソフトウェアによる書き換えは、シリアル出力禁止 (SOE1.SOE[n] = 0) 時のみ可能です。シリアル出力許可 (SOE1.SOE[n] = 1) 時は、ソフトウェアによる書き換えは無視され、シリアル通信動作によってのみレジスタの値が変更されます。

このレジスタの CKO[n]ビットのソフトウェアによる書き換えは、チャネル動作停止 (SE1.SE[n] = 0) 時のみ可能です。チャネル動作許可 (SE1.SE[n] = 1) 時は、ソフトウェアによる書き換えは無視され、シリアル通信動作によってのみ CKO[n]の値が変更されます。

また、シリアルインタフェース用端子をポート機能端子として使用する場合は、該当する CKO[n]ビットおよび SO[n]ビットを 1 にしてください。

修正前: 25.2.3 ADM2: A/D コンパータモードレジスタ 2 (p.575)

#### AWC ビット(スヌーズモードの指定)

スヌーズモードの指定に使用されるビットです。

ソフトウェアスタンバイ中にハードウェアトリガ信号があった場合、ソフトウェアスタンバイモードを終了し、CPU を動作させずに A/D 変換を行います (スヌーズモード)。

- スヌーズモード機能を使用する場合、ソフトウェアトリガ待機モードでは AWC を 0 に設定し、ハードウェアトリガ待機モードでは AWC を 1 に設定します。

- ソフトウェアトリガ待機なしモードまたはハードウェアトリガ待機なしモードでのスヌーズモード機能の使用は禁止されています。

- ソフトウェアトリガ待機なしモード、ソフトウェアトリガ待機モード、またはハードウェアトリガ待機なしモードでのスヌーズモード機能の使用は禁止されています。

- スヌーズモード機能を使用する場合は、ハードウェアトリガ間隔を「スヌーズモード移行時間( $^{(\pm 1)}$ )+変換開始時間+ A/D 電源安定待機時間+ A/D 変換時間+ PCLKB クロック 2 サイクル+ 5  $\mu$ s」以上に指定してください。

- スヌーズモードを使用する場合でも、通常動作時は必ず AWC ビットを 0 にし、ソフトウェアスタンバイモードに移行する直前に 1 に変えてください。 また、ソフトウェアスタンバイモードから通常動作に復帰後は、必ず AWC ビットを 0 に変えてください。 AWC ビットを 1 のままにしておくと、以降のスヌーズモードまたは通常動作にかかわらず A/D 変換が正常に開始されなくなります。

注 1. 「31.4.2. ウェイクアップ時間」の表 31.21 を参照してください。

修正後: 25.2.3 ADM2: A/D コンパータモードレジスタ 2

#### AWC ビット(スヌーズモードの指定)

スヌーズモードの指定に使用されるビットです。

ソフトウェアスタンバイ中にハードウェアトリガ信号があった場合、ソフトウェアスタンバイモードを終了し、CPU を動作させずに A/D 変換を行います (スヌーズモード)。

- スヌーズモード機能を使用する場合、ハードウェアトリガ待機モードでは AWC を 1に設定してください。

- ソフトウェアトリガ待機なしモードまたはソフトウェアトリガ待機モード、ハードウェアトリガ待機なしモードでのスヌーズモード機能の使用は禁止されています。

- スヌーズモード機能を使用する場合、連続変換モードおよびハードウェアトリガ待機モードでの使用は禁止されています。

- スヌーズモード機能を使用する場合は、ハードウェアトリガ間隔を「スヌーズモード移行時間 $(^{(\pm 1)})$ +変換開始時間+ A/D 電源安定待機時間+ A/D 変換時間+ PCLKB クロック 2 サイクル+ 5  $\mu$ s」以上に指定してください。

- スヌーズモードを使用する場合でも、通常動作時は必ず AWC ビットを 0にし、ソフトウェアスタンバイモードに移行する直前に 1に変えてください。 また、ソフトウェアスタンバイモードから通常動作に復帰後は、必ず AWC ビットを 0に変えてください。 AWC ビットを 1 のままにしておくと、以降のスヌーズモードまたは通常動作にかかわらず A/D 変換が正常に開始されなくなります。

注 1. 「31.4.2. ウェイクアップ時間」の表 31.21 を参照してください。

修正前: 25.2.6 ADS: アナログ入力チャネル指定レジスタ (p.579)

(略)

- 注. ADISS ビットの値の書き換えは、変換が停止している (ADCS = 0, ADCE = 0) ときに行ってください。

- 注. VREFH0 を A/D コンバータの「+」側の基準電圧として使用する場合は、AN000 を A/D 変換チャネルに選択しないでください。

- 注. VREFL0 を A/D コンバータの「-」側の基準電圧として使用する場合は、AN001 を A/D 変換チャネルに選択しないでください。

- 注. ADISS ビットの設定値が1の場合、内部基準電圧はA/D コンバータの「+」側の基準電圧には使えません。ADISS ビットを1に設定した後は、内部変換結果を使用できません。設定の流れについては、「25.6.5. 温度センサ出力電圧または内部基準電圧と、ソフトウェアトリガ待機なしモードおよびワンショット変換モード選択時のADC12使用例」を参照してください。

内部基準電圧の詳細は、「31. 電気的特性」を参照してください。 $T_A = -40 \sim +105$ °C。

- 注. ソフトウェアスタンバイモードに移行するとき、または CPU がサブシステムクロックで動作中にスリープモードに 移行するときは、ADISS ビットを 1 に設定しないでください。ADISS ビットを 1 に設定した場合、「31.3.2. 動作電 流とスタンバイ電流」に示す A/D コンバータ基準電圧電流 (IADREF) が加算されます。

- 注. ADISS ビットの設定値が 1 の場合、ハードウェアトリガ待機モードとワンショット変換モードの同時使用はできません。

#### 修正後: 25.2.6 ADS: アナログ入力チャネル指定レジスタ

(略)

- 注. ADISS ビットの値の書き換えは、変換が停止している (ADCS = 0, ADCE = 0) ときに行ってください。

- 注. VREFH0 を A/D コンバータの「+」側の基準電圧として使用する場合は、AN000 を A/D 変換チャネルに選択しないでください。

- 注. VREFL0 を A/D コンバータの「-」側の基準電圧として使用する場合は、AN001 を A/D 変換チャネルに選択しないでください。

- 注. ADISS ビットの設定値が 1 の場合、内部基準電圧は A/D コンバータの「+」側の基準電圧には使えません。ADISS ビットを 1 に設定した後は、内部変換結果を使用できません。設定の流れについては、「25.6.5. 温度センサ出力電圧または内部基準電圧と、ソフトウェアトリガ待機なしモードおよびワンショット変換モード選択時の ADC12 使用例」を参照してください。

内部基準電圧の詳細は、「31. 電気的特性」を参照してください。 $T_A = -40 \sim +105$ °C。

- 注. ソフトウェアスタンバイモードに移行するとき、または CPU がサブシステムクロックで動作中にスリープモードに 移行するときは、ADISS ビットを 1 に設定しないでください。ADISS ビットを 1 に設定した場合、「31.3.2. 動作電 流とスタンバイ電流」に示す A/D コンバータ基準電圧電流 (IADREF) が加算されます。

- 注. ADISS ビットの設定値が 1 の場合、ハードウェアトリガ待機モードとワンショット変換モードの同時使用はできません。

- 注. ADISS ビットの設定値が 1 の場合、ソフトウェアトリガ待機モードとワンショット変換モードの同時使用はできません。

RENESAS

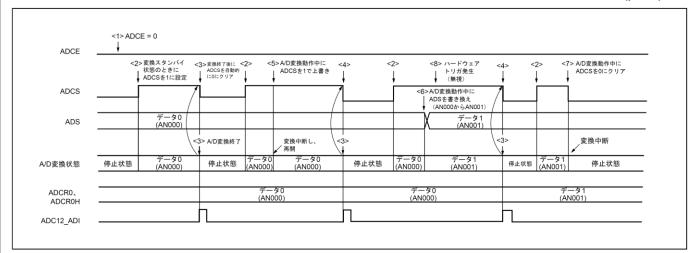

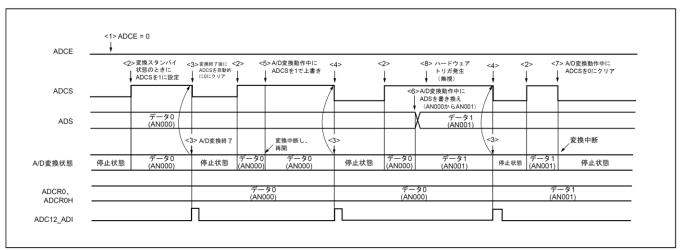

## 修正前:図 25.13 ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)動作タイミングの例 (p.588)

#### 図 25.13 ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)動作タイミングの例

注. 変換動作中に <5> または <6> を検出すると、次の変換クロック (f<sub>AD</sub>) の立ち上がりエッジから安定待機時間が経過した後に変換が自動的に再開されます。最初の変換動作再開時の変換時間は、ソフトウェアトリガ待機モードまたはハードウェアトリガ待機モードで A/D 電源安定待機時間がある場合と同じです。(「25.2.1. ADMO: A/D コンバータモードレジスタ 0」と「25.2.1. ADMO: A/D コンバータモードレジスタ 0」を参照してください。)

#### 修正後:図 25.13 ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)動作タイミングの例

#### 図 25.13 ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)動作タイミングの例

- 注. 変換動作中に <5> または <6> を検出すると、次の変換クロック (f<sub>AD</sub>) の立ち上がりエッジから安定待機時間が経過した後に変換が自動的に再開されます。最初の変換動作再開時の変換時間は、ソフトウェアトリガ待機モードまたはハードウェアトリガ待機モードで A/D 電源安定待機時間がある場合と同じです。(「25.2.1. ADM0: A/D コンバータモードレジスタ 0」と「25.2.1. ADM0: A/D コンバータモードレジスタ 0」を参照してください。)

- 注. ソフトウェアトリガ待機モード(セレクトモード、ワンショット変換モード)では、ADISS = 1 (入力ソース = 温度センサー出力電圧、内部リファレンス電圧)の設定は使用できません。

修正前:25.7 スヌーズモード機能 (p.604)

## 25.7 スヌーズモード機能

スヌーズモードでは、ソフトウェアスタンバイモードでソフトウェアトリガまたはハードウェアトリガを入力することにより、A/D 変換がトリガされます。通常、ソフトウェアスタンバイモードでは A/D 変換が停止しますが、スヌーズモード機能を使用することにより、CPU を作動させずに A/D 変換を行うことができます。これは動作電流の削減に効果があります。

修正後: 25.7 スヌーズモード機能

## 25.7 スヌーズモード機能

スヌーズモードでは、ソフトウェアスタンバイモードでハードウェアトリガを入力することにより、A/D 変換がトリガされます。通常、ソフトウェアスタンバイモードでは A/D 変換が停止しますが、スヌーズモード機能を使用することにより、CPU を作動させずに A/D 変換を行うことができます。これは動作電流の削減に効果があります。

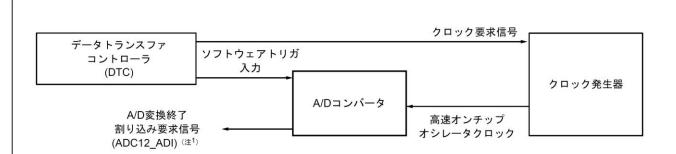

#### 修正前: 25.7.1 ソフトウェアトリガの入力による A/D 変換 (p.605, p.606)

#### 25.7.1 ソフトウェアトリガの入力による A/D 変換

スヌーズモードでは、ソフトウェアトリガの入力により A/D 変換がトリガされます。DTC により作成されたソフトウェアトリガが、A/D 変換の入力トリガとして使われます。スヌーズモードでソフトウェアトリガを入力することで A/D 変換を実行する場合は、以下の 4 つの変換モードのみ使用できます。

- ソフトウェアトリガ待機モード(選択モード、ワンショット変換モード)

- ソフトウェアトリガ待機モード(選択モード、連続変換モード)

- ソフトウェアトリガ待機モード(スキャンモード、ワンショット変換モード)

- ソフトウェアトリガ待機モード(スキャンモード、連続変換モード)

- 注. スヌーズモードは、PCLKBに高速オンチップオシレータクロックまたは中速オンチップオシレータクロックが使用されている場合にのみ指定できます。

- 注 1. A/D 変換の終了ごとに割り込み信号が発生するように、A/D 変換結果比較機能(ADRCK ビットと ADUL/ADLL レジスタ)の設定をクリアして初期値に戻します。

- ワンショット変換モード(選択/スキャン)

A/D 変換が完了して割り込み要求信号 (ADC12\_ADI) が発生した後にソフトウェアスタンバイ命令を実行すると、供給クロックを停止できます。

- 連続変換モード(選択/スキャン) A/D 変換が完了して割り込み要求信号 (ADC12\_ADI) が発生した後に ADCS に 0 を書き込むと、連続変換モードを停止できます。その後、変換クロック (f<sub>AD</sub>) 2 サイクル分の時間が経過した後にソフトウェアスタンバイ命令を実行すると、供給クロック停止できます。

#### 図 25.24 ソフトウェアトリガ待機モードでスヌーズモードを使用するときのブロック図

スヌーズモードを使用する場合は、ソフトウェアスタンバイモードに遷移する前に各レジスタの初期設定を指定します(各設定の詳細については、「25.6.2. ソフトウェアトリガ待機モードの設定」を参照)。ソフトウェア待機モードへの切り替え後にソフトウェアトリガ (ADCS = 1) が入力された場合は、高速オンチップオシレータクロックが A/D コンバータに供給されます。このクロックの供給後、A/D コンバータは、A/D 電源安定待機時間まで自動的にカウントアップを行ってから A/D 変換を開始します。

表 25.20 ソフトウェアトリガ待機なしモードの設定

| 手順                 |      | 処理                                                                                                                                                       | 詳細                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 通常動作               | <1>  | MSTPCRD レジスタの設定                                                                                                                                          | MSTPCRD レジスタの ADC ビットを 0 に設定し、クロック供給を開始します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | <2>  | PmnPFS_A レジスタの設定                                                                                                                                         | ポートをアナログ入力として設定します。<br>(「16.5.4. アナログ機能使用時の注意事項」を参照)                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | <3>  | <ul> <li>ADM0 レジスタの設定</li> <li>ADM1 レジスタの設定</li> <li>ADM2 レジスタの設定</li> <li>ADUL レジスタと ADLL レジスタの設定</li> <li>ADS レジスタの設定</li> <li>(設定の順序は関係なし)</li> </ul> | <ul> <li>ADMO レジスタ<br/>FR[2:0]ビット、LV[1:0]ビット: A/D 変換時間の指定に使用します。<br/>ADMD ビット: 選択モードまたはスキャンモード</li> <li>ADM1 レジスタ<br/>ADTMD1 ビットと ADTMD0 ビット: ソフトウェアトリガ待機モードの指定に使用します。<br/>ADSCM ビット: ワンショット変換モード</li> <li>ADM2 レジスタ<br/>ADREFP[1:0]ビットと ADREFM ビット: 基準電圧の選択に使用します。<br/>ADRCK ビット: 割り込み信号を発生させる A/D 変換結果比較値の範囲を AREA 1、AREA 3、AREA 2 から選択するビットです。<br/>ADTYP[1:0]ビット: 12 ビット、10 ビット、8 ビット分解能ADUL レジスタと ADLL レジスタA/D 変換結果比較値の上限と下限の指定に使用します。</li> <li>ADS レジスタ<br/>ADS [4:0]ビット: アナログ入カチャネルの選択に使用します。</li> </ul> |

|                    | <4>  | 基準電圧安定待機時間カウント A                                                                                                                                         | ADREFP[1:0]ビットの値を変更すると、以下 A に示す基準電圧安定 待機時間カウントが必要になる場合があります。ADREFP[1:0]の値を 10b に変更した場合: $A=5$ $\mu$ s。上記の変更を行う前に、 ADREFP[1:0] = 11b を設定して基準電源ディスチャージ (1 $\mu$ s) を実行してください。 ADREFP[1:0]の値を 00b または 01b に変更した場合は、待機は不要です。                                                                                                                                                                                                                                                                                       |

| ソフトウェアスタン<br>バイモード | <5>  | ソフトウェアスタンバイモードに移<br>行                                                                                                                                    | AWC ビットと ADCE ビットは初期値 0 のままにします。<br>これらのビットはリセットされません。                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| スヌーズモード            | <6>  | ソフトウェアトリガ発生                                                                                                                                              | ソフトウェアトリガ (ADCS = 1) の発生後、A/D コンバータは A/D 電源安定待機時間まで自動的にカウントアップを行ってから、スヌーズモードで A/D 変換を開始します。                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    |      | 1                                                                                                                                                        | (A/D 変換動作が実行されます)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    | <7>  | A/D 変換終了                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    | <8>  | ADC12_ADI の発生 <sup>(注2)</sup>                                                                                                                            | A/D 変換終了割り込み (ADC12_ADI) が発生します。 <sup>(注1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | <9>  | 変換結果を ADCRn レジスタまたは<br>ADCRnH レジスタに格納                                                                                                                    | 変換結果を ADCRn レジスタまたは ADCRnH レジスタに格納します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | <10> | 終了処理(注3)                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ソフトウェアスタン<br>バイモード | <11> | ソフトウェアスタンバイ命令を使用<br>可能 <sup>(注4)</sup>                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

- 注 1. ADRCK ビット、ADUL レジスタ、ADLL レジスタの設定により、割り込み信号が発生しない可能性があります。この場合、結果をADCRn レジスタや ADCRnH レジスタに格納しません。

- 注 2. ADRCK ビット、ADUL レジスタ、および ADLL レジスタをクリアして初期設定時の初期値に戻し、A/D 変換の完了ごとに割り込み要求信号 (ADC12\_ADI) が発生するように設定を行います。

- 注 3. 連続変換モードには終了処理が必要です。ADC12\_ADIの発生後に ADCS に 0 を書き込んでください。その後、変換クロック (f<sub>AD</sub>) 2 サイクル分の時間が経過すれば、ソフトウェアスタンバイ命令を実行できます。

- 注 4. さらに、ソフトウェアスタンバイ命令の実行後にソフトウェアトリガを入力すると、スヌーズモードで再度 A/D 変換動作が実行されます。

修正後: 25.7.1 ソフトウェアトリガの入力による A/D 変換

全て削除

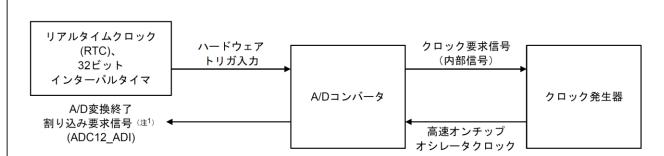

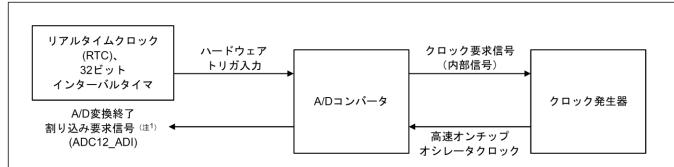

#### 修正前:図 25.25 ハードウェアトリガ待機モードでスヌーズモードを使用するときのブロック図 (p.607)

注 1. A/D 変換結果比較機能の設定(ADRCK ビット、ADUL/ADLL レジスタ)によっては、割り込み信号が発生しない可能性があります。

32 ビット内部タイマ割り込み信号 (ADITLO (= TML32\_ITLO)) をハードウェアトリガとして選択するときは、32 ビットインターバルタイマ割り込み信号 (ADITLO (= TML32\_ITLO)) が発生するごとに ITLSO レジスタの検出フラグをクリアする必要があります。

したがって、A/D 変換終了時に A/D 変換終了割り込み要求信号 (ADC12\_ADI) が発生するように、A/D 変換結果比較機能 (ADRCK ビットと ADUL/ADLL レジスタ) の設定をクリアして初期値に戻します。

図 25.25 ハードウェアトリガ待機モードでスヌーズモードを使用するときのブロック図

#### 修正後:図 25.25 ハードウェアトリガ待機モードでスヌーズモードを使用するときのブロック図

注 1. A/D 変換結果比較機能の設定(ADRCK ビット、ADUL/ADLL レジスタ)によっては、割り込み信号が発生しない可能性があります。

図 25.25 ハードウェアトリガ待機モードでスヌーズモードを使用するときのブロック図

修正前:表 28.5 スタートアップ領域選択およびセキュリティ設定のエクストラビットのマッピング(アドレス (P/E):0x0000\_0010) (p.634)

# 表 28.5 スタートアップ領域選択およびセキュリティ設定のエクストラビットのマッピング(アドレス (P/E): 0x0000 0010)

| b31                       | b30 | b29 | b28 | b27 | b26    | b25  | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|---------------------------|-----|-----|-----|-----|--------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| SASM<br>F <sup>(注1)</sup> | _   | _   | _   | 1   | FAWE[1 | 0:0] |     |     |     |     |     |     |     |     |     |

| b15                       | b14 | b13 | b12 | b11 | b10    | b9   | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

| FSPR<br>(注1)              | _   | _   | _   |     | FAWS[1 | 0:0] |     |     |     |     |     |     |     |     |     |

注 1. これらのビットは、一度 0 にすると 1 に変更することはできません。

# 修正後:表 28.5 スタートアップ領域選択およびセキュリティ設定のエクストラビットのマッピング(アドレス (P/E): $0x0000_0010$ )

# 表 28.5 スタートアップ領域選択およびセキュリティ設定のエクストラビットのマッピング (アドレス (P/E): 0x0000 0010)

| b31          | b30 | b29 | b28 | b27 | b26    | b25  | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|--------------|-----|-----|-----|-----|--------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTFLG        | _   | _   | _   | _   | FAWE[1 | 0:0] |     |     |     |     |     |     |     |     |     |

| b15          | b14 | b13 | b12 | b11 | b10    | b9   | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

| FSPR<br>(注1) | _   | _   | _   | _   | FAWS[1 | 0:0] |     |     |     |     |     |     |     |     |     |

注 1. これらのビットは、一度 0 にすると 1 に変更することはできません。

修正前:表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010) (p.634)

## 表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010) (1/2)

| b31                       | b30 | b29 | b28 | b27 | b26    | b25  | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|---------------------------|-----|-----|-----|-----|--------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| SASM<br>F <sup>(注1)</sup> | _   | _   | _   | _   | FAWE[1 | 0:0] |     |     |     |     |     |     |     |     |     |

| b15                       | b14 | b13 | b12 | b11 | b10    | b9   | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

## 表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010) (2/2)

| FSPR | _ | _ | _ | _ | FAWS[10:0] |

|------|---|---|---|---|------------|

| (注1) |   |   |   |   |            |

注 1. これらのビット内のデータは、一度 0 にすると 1 に変更することはできません。

## 修正後:表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010)

## 表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010) (1/2)

| b31   | b30 | b29 | b28 | b27 | b26    | b25        | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|-------|-----|-----|-----|-----|--------|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTFLG | _   | _   | _   | _   | FAWE[1 | FAWE[10:0] |     |     |     |     |     |     |     |     |     |

| b15   | b14 | b13 | b12 | b11 | b10    | b9         | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

#### 表 28.6 アクセスウィンドウ情報プログラムのエクストラビットのマッピング(アドレス (P/E): 0x0000\_0010) (2/2)

| FSPR<br>(注1) | _ | _ | _ | _ | FAWS[10:0] |

|--------------|---|---|---|---|------------|

| (/エ1)        |   |   |   |   |            |

注 1. これらのビット内のデータは、一度 0 にすると 1 に変更することはできません。

発行日: 2024年12月27日

修正前: 28.3.25 PNRn:型名レジスタ n (n = 0~3) (p.642)

28.3.25 PNRn:型名レジスタ n (n = 0~3)

Address: 0x0101\_1080 + n × 4

Bit position: 31

Bit field:

PNR[31:0]

Value after reset:

チップごとのユニーク値

| ビット  | シンボル      | 機能 | R/W |

|------|-----------|----|-----|

| 31:0 | PNR[31:0] | 型名 | R   |

PNRn レジスタは、16 バイトの型名を格納する読み出し専用レジスタです。PNRn レジスタは 32 ビット単位で読み出してください。各バイトは製品一覧に示すように、製品の型名の ASCII コードに対応しています。

型名が「R7FA0E1073CNK」である場合、16 バイトの型名は以下のように格納されます。

アドレス 0x0101\_1080: 'K', 0x4B (ASCII コード)

アドレス 0x0101\_1081: 'N', 0x4E (ASCII コード)

アドレス 0x0101 1082: 'C', 0x43 (ASCII コード)

アドレス 0x0101\_1083: '3', 0x33 (ASCII コード)

アドレス 0x0101\_1084: '7', 0x37 (ASCII コード)

アドレス 0x0101 1085: '0', 0x30 (ASCII コード)

アドレス 0x0101\_1086: '1', 0x31 (ASCII コード)

アドレス 0x0101\_1087: 'E', 0x45 (ASCII コード)

アドレス 0x0101 1088: '0', 0x30 (ASCII コード)

アドレス 0x0101\_1089: 'A', 0x41 (ASCII コード)

アドレス 0x0101\_1090 : 'F', 0x46 (ASCII コード)

アドレス  $0x0101\_1091$ : '7', 0x37 (ASCII コード)

アドレス 0x0101\_1092: 'R', 0x52 (ASCII コード)

アドレス 0x0101\_1093:"(空白), 0x20 (ASCII コード)

アドレス 0x0101\_1094:"(空白), 0x20 (ASCII コード)

アドレス 0x0101\_1095: "(空白), 0x20 (ASCII コード)

発行日: 2024年12月27日

修正後: 28.3.25 PNRn:型名レジスタ n (n = 0~3)

28.3.25 PNRn:型名レジスタ n (n = 0~3)

Address: 0x0101\_1080 + n × 4

Bit position: 31

\_\_\_\_\_

Bit field:

PNR[31:0]

Value after reset:

チップごとのユニーク値

| ビット  | シンボル      | 機能 | R/W |

|------|-----------|----|-----|

| 31:0 | PNR[31:0] | 型名 | R   |

PNRn レジスタは、16 バイトの型名を格納する読み出し専用レジスタです。PNRn レジスタは 32 ビット単位で読み出してください。各バイトは製品一覧に示すように、製品の型名の ASCII コードに対応しています。

型名が「R7FA0E1073CNK」である場合、16 バイトの型名は以下のように格納されます。

アドレス 0x0101\_1080: 'K', 0x4B (ASCII コード)

アドレス 0x0101\_1081: 'N', 0x4E (ASCII コード)

アドレス 0x0101 1082: 'C', 0x43 (ASCII コード)

アドレス 0x0101\_1083: '3', 0x33 (ASCII コード)

アドレス 0x0101\_1084: '7', 0x37 (ASCII コード)

アドレス 0x0101\_1085: '0', 0x30 (ASCII コード)

アドレス 0x0101\_1086: '1', 0x31 (ASCII コード)

アドレス 0x0101\_1087: 'E', 0x45 (ASCII コード)

アドレス 0x0101 1088: '0', 0x30 (ASCII コード)

アドレス 0x0101\_1089: 'A', 0x41 (ASCII コード)

アドレス  $0x0101\_108A$  : 'F', 0x46 (ASCII コード)

アドレス 0x0101\_108B: '7', 0x37 (ASCII コード)

アドレス 0x0101\_108C: 'R', 0x52 (ASCII コード)

アドレス 0x0101\_108D: "(空白), 0x20 (ASCII コード)

アドレス 0x0101\_108E: "(空白), 0x20 (ASCII コード)

アドレス 0x0101\_108F: "(空白), 0x20 (ASCII コード)

## 修正前:表 28.15 基本機能 (p.645)

## 表 28.15 基本機能

|               |                                                                                                       | サポートの有無                     |

|---------------|-------------------------------------------------------------------------------------------------------|-----------------------------|

| 機能            | 機能概要                                                                                                  | セルフプログラミング/SWD プログラミング      |

| ブランクチェック      | 指定したブロックがプログラムされていないことを確認します。                                                                         | あり                          |

| ブロックイレース      | 指定したブロックのメモリ内容のイレースを行います。                                                                             | あり                          |

| プログラム         | 指定したアドレスのプログラムを行います。                                                                                  | あり                          |

| リード           | フラッシュメモリにプログラムしたデータの読み出しを行います。                                                                        | なし (ユーザープログラムにて読<br>み出しは可能) |

| ID コードプロテクト機能 | ホストが送信した ID コードとコードフラッシュメモリに格納されているコードとを比較します。これら2つが一致する場合、FCB は待機状態に遷移してホストからのプログラミングとイレースコマンドを待ちます。 | なし(ID 認証は行わない)              |

| プロテクション設定     | コードフラッシュメモリにおけるフラッシュ領域プロテクションの<br>アクセスウィンドウを設定します。                                                    | あり                          |

## 修正後:表 28.15 基本機能

#### 表 28.15 基本機能

|               |                                                                                                                         | サポートの                                      | 有無                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| 機能            | 機能概要                                                                                                                    | セルフプログラミング                                 | SWD プログラミング                                |

| ブランクチェック      | 指定したブロックがプログラムされていないことを確認<br>します。                                                                                       | あり                                         | あり                                         |

| ブロックイレース      | 指定したブロックのメモリ内容のイレースを行います。                                                                                               | あり                                         | あり                                         |

| プログラム         | 指定したアドレスのプログラムを行います。                                                                                                    | あり                                         | あり                                         |

| リード           | フラッシュメモリにプログラムしたデータの読み出しを<br>行います。                                                                                      | なし (ユーザープロ<br>グラムにて読み出し<br>は可能)            | なし                                         |

| ID コードプロテクト機能 | ホストが送信した ID コードとコードフラッシュメモリに<br>格納され<br>ているコードとを比較します。これら 2 つが一致する場<br>合、FCB は待機状態に遷移してホストからのプログラミ<br>ングとイレースコマンドを待ちます。 | ない)                                        | あり                                         |

| セキュリティ設定      | セキュリティ機能の保護設定(アクセスウィンドウとス<br>タートアップ領域の選択)                                                                               | あり<br>条件は「28.8 プロ<br>テクション機能」を<br>参照してください | あり<br>条件は「28.8 プロ<br>テクション機能」を<br>参照してください |

| プロテクション設定     | コードフラッシュメモリにおけるフラッシュ領域プロテ<br>クションのアクセスウィンドウを設定します。                                                                      | あり                                         | あり                                         |

修正前: 29 真性乱数生成器 (TRNG) (p.666)

(略)

## 29.3.1 全体処理フロー

表 29.2 に、TRNG 起動の全体処理フローを示します。

#### 表 29.2 真性乱数生成器を使い乱数シード値を生成する手順

| No | 手順          | 説明                                                                                                                                                    |

|----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | モジュールストップ設定 | MSTPCRC.MSTPC28 = 0 を設定し、モジュールストップ状態を解除する。                                                                                                            |

| 2  | ウェイト        | 周辺モジュールクロック (PCLK) の 6 サイクル分待機する。                                                                                                                     |

| 3  | TRNG 許可設定   | TRNGSCR0.SGCEN = 1 を設定し、真性乱数生成器を有効にする。                                                                                                                |

| 4  | TRNG 割り込み設定 | TRNGSCR1.INTEN ビットを設定し、TRNG 割り込み出力を許可/禁止する。                                                                                                           |

| 5  | TRNG 動作開始設定 | TRNGSCR0.SGSTART = 1 を設定し、乱数シード値の生成を開始する。                                                                                                             |

| 6  | シードデータの読み出し | TRNG のシード値生成には、ポーリングと割り込みの 2 つの動作がある。 1. ポーリング動作: TRNGSCR0.RDRDY = 1 が設定された後に、TRNGSDR レジスタを 4 回読み出す。 2. 割り込み動作: TRNG 割り込みの発生後に、TRNGSDR レジスタを 4 回読み出す。 |

| 7  | TRNG 動作停止設定 | TRNGSCR0.SGCEN = 0 を設定し、真性乱数生成器を無効にする。TRNGSCR0.SGSTART = 0 を設定し、乱数シード値の生成を停止する。                                                                       |

| 8  | モジュールストップ設定 | MSTPCRC.MSTPC28 = 1 を設定し、モジュールストップ状態に遷移する。                                                                                                            |

修正後: 29 真性乱数生成器 (TRNG)

(略)

## 29.3.1 全体処理フロー

表 29.2 に、TRNG 起動の全体処理フローを示します。

#### 表 29.2 真性乱数生成器を使い乱数シード値を生成する手順

| No | 手順          | 説明                                                                                                                                                    |

|----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | モジュールストップ設定 | MSTPCRC.MSTPC28 = 0 を設定し、モジュールストップ状態を解除する。                                                                                                            |

| 2  | ウェイト        | 周辺モジュールクロック (PCLK) の 6 サイクル分待機する。                                                                                                                     |

| 3  | TRNG 許可設定   | TRNGSCR0.SGCEN = 1 を設定し、真性乱数生成器を有効にする。                                                                                                                |

| 4  | TRNG 割り込み設定 | TRNGSCR1.INTEN ビットを設定し、TRNG 割り込み出力を許可/禁止する。                                                                                                           |

| 5  | TRNG 動作開始設定 | TRNGSCR0.SGSTART = 1 を設定し、乱数シード値の生成を開始する。                                                                                                             |

| 6  | シードデータの読み出し | TRNG のシード値生成には、ポーリングと割り込みの 2 つの動作がある。 1. ポーリング動作: TRNGSCR0.RDRDY = 1 が設定された後に、TRNGSDR レジスタを 4 回読み出す。 2. 割り込み動作: TRNG 割り込みの発生後に、TRNGSDR レジスタを 4 回読み出す。 |

| 7  | TRNG 動作停止設定 | TRNGSCR0.SGCEN = 0 を設定し、真性乱数生成器を無効にする。TRNGSCR0.SGSTART = 0 を設定し、乱数シード値の生成を停止する。                                                                       |

| 8  | モジュールストップ設定 | MSTPCRC.MSTPC28 = 1 を設定し、モジュールストップ状態に遷移する。                                                                                                            |

## 29.4 使用上の注意事項

MCUの動作モードを遷移させるときの前後20µsは、TRNGが動作禁止になります。

RENESAS

#### 修正前:表 31.1 絶対最大定格 (p.668)

#### 表 31.1 絶対最大定格 (1/2)

| 項目         |                                                               | シンボル              | 値                                              | 単位 |

|------------|---------------------------------------------------------------|-------------------|------------------------------------------------|----|

| 電源電圧       |                                                               | VCC               | -0.5~+6.5                                      | V  |

| VCL 端子入力電圧 |                                                               | V <sub>IVCL</sub> | -0.3~+2.1<br>および-0.3~VCC + 0.3 <sup>(注1)</sup> | ٧  |

| 入力電圧       | P100~P103, P108~P110, P112, P200, P201, P206~P208, P300, P407 | V <sub>I</sub> 1  | -0.3~VCC + 0.3                                 | V  |

|            | P913, P914 (5 V トレラント)                                        | V <sub>I</sub> 2  | -0.3~+6.5                                      | V  |

|            | P008~P015, P212~P215                                          | V <sub>I</sub> 3  | -0.3~VCC + 0.3                                 | V  |

| 出力電圧       | P100~P103, P108~P110, P112, P201, P206~<br>P208, P300, P407   | V <sub>O</sub> 1  | -0.3~VCC + 0.3                                 | V  |

|            | P913, P914(N チャネルオープンドレイン)                                    | V <sub>O</sub> 2  | -0.3~+6.5                                      | V  |

|            | P008~P015, P212, P213                                         | V <sub>O</sub> 3  | -0.3~VCC + 0.3 <sup>(注2)</sup>                 | V  |

#### 表 31.1 絶対最大定格 (2/2)

| 項目           |                                                            |         | シンボル              | 値                                                                      | 単位 |

|--------------|------------------------------------------------------------|---------|-------------------|------------------------------------------------------------------------|----|

| アナログ入力電圧     | AN000~AN007                                                |         | V <sub>Al</sub> 1 | -0.3~VCC + 0.3<br>および-0.3~VREFH0 + 0.3 <sup>(注2) (注3)</sup>            | V  |

|              | AN021, AN022                                               |         | V <sub>Al</sub> 2 | -0.3~VCC + 0.3<br>および-0.3~VREFH0 + 0.3 <sup>(注2)</sup> <sup>(注3)</sup> | V  |

| High レベル出力電流 | P100~P103, P108~                                           | 端子ごと    | I <sub>OH</sub> 1 | -40                                                                    | mA |

|              | P110, P112, P201~<br>P207, P208, P300,<br>P407             | 全端子の合計  |                   | -100                                                                   | mA |

|              | P008~P015, P212,                                           | 端子ごと    | I <sub>OH</sub> 2 | -5                                                                     | mA |

|              | P213                                                       | 全端子の合計  |                   | -20                                                                    | mA |

| Low レベル出力電流  | P100~P103, P108~                                           | 端子ごと    | I <sub>OL</sub> 1 | 40                                                                     | mA |

|              | P110, P112, P201, P206<br>~P208, P300, P407,<br>P913, P914 | 全端子の合計  |                   | 100                                                                    | mA |

|              | P008~P015, P212,                                           | 端子ごと    | I <sub>OL</sub> 2 | 10                                                                     | mA |

|              | P213                                                       | 全端子の合計  |                   | 20                                                                     | mA |

| 動作温度         | 通常動作モード                                                    |         | Та                | -40~+105                                                               | °C |

|              | フラッシュメモリプログ                                                | ラミングモード |                   | -40~+105                                                               | °C |

| 保存温度         |                                                            |         | Tstg              | -65~+150                                                               | °C |

- 注 1. コンデンサ (0.47~1 μF) を介して VCL 端子を VSS 端子に接続してください。表に記載された値は、VCL 端子の絶対最大定格です。 コンデンサ接続のみを使用してください。この端子には特定の電圧を印加しないでください。

- 注 2. この電圧は 6.5 V 以下にしてください。

- 注 3. A/D 変換に使用する端子の電圧は、VREFH0 + 0.3 を超えないでください。

- 注. ある端子の多重化された機能の特性は、他に指定がなければ、ポート端子の特性と同じです。

- 注. VREFH0 は A/D コンバータの正の基準電圧を参照します。

- 注. 基準電圧は VSS です。

【使用上の注意】瞬間的にでも、いずれかの項目が絶対最大定格を超えた場合、製品の品質が損なわれる可能性があります。 つまり、絶対最大定格は、製品に物理的損傷が生じる寸前で評価された値です。したがって、絶対最大定格 を超えない条件下で、製品を使用してください。

#### 修正後:表 31.1 絶対最大定格

#### 表 31.1 絶対最大定格 (1/2)

| 項目         |                                                               | シンボル              | 値                                              | 単位 |

|------------|---------------------------------------------------------------|-------------------|------------------------------------------------|----|

| 電源電圧       |                                                               | VCC               | -0.5~+6.5                                      | V  |

| VCL 端子入力電圧 |                                                               | V <sub>IVCL</sub> | -0.3~+2.1<br>および-0.3~VCC + 0.3 <sup>(注1)</sup> | V  |

| 入力電圧       | P100~P103, P108~P110, P112, P200, P201, P206~P208, P300, P407 | V <sub>I</sub> 1  | -0.3~VCC + 0.3 <sup>(注 2)</sup>                | V  |

|            | P913, P914 (5 V トレラント)                                        | V <sub>I</sub> 2  | -0.3~+6.5                                      | V  |

|            | P008~P015, P212~P215                                          | V <sub>I</sub> 3  | -0.3~VCC + 0.3 <sup>(注 2)</sup>                | V  |

| 出力電圧       | P100~P103, P108~P110, P112, P201, P206~<br>P208, P300, P407   | V <sub>O</sub> 1  | -0.3~VCC + 0.3 <sup>(注 2)</sup>                | V  |

|            | P913, P914(N チャネルオープンドレイン)                                    | V <sub>O</sub> 2  | -0.3~+6.5                                      | V  |

|            | P008~P015, P212, P213                                         | V <sub>O</sub> 3  | -0.3~VCC + 0.3 <sup>(注2)</sup>                 | V  |

#### 表 31.1 絶対最大定格 (2/2)

| 項目           |                                                            |         | シンボル              | 値                                                                      | 単位 |

|--------------|------------------------------------------------------------|---------|-------------------|------------------------------------------------------------------------|----|

| アナログ入力電圧     | AN000~AN007                                                |         | V <sub>Al</sub> 1 | -0.3~VCC + 0.3<br>および-0.3~VREFH0 + 0.3 <sup>(注2) (注3)</sup>            | V  |

|              | AN021, AN022                                               |         | V <sub>Al</sub> 2 | -0.3~VCC + 0.3<br>および-0.3~VREFH0 + 0.3 <sup>(注2)</sup> <sup>(注3)</sup> | V  |

| High レベル出力電流 | P100~P103, P108~                                           | 端子ごと    | I <sub>OH</sub> 1 | -40                                                                    | mA |

|              | P110, P112, P201~<br>P207, P208, P300,<br>P407             | 全端子の合計  |                   | -100                                                                   | mA |

|              | P008~P015, P212,                                           | 端子ごと    | I <sub>OH</sub> 2 | -5                                                                     | mA |

|              | P213                                                       | 全端子の合計  |                   | -20                                                                    | mA |

| Low レベル出力電流  | P100~P103, P108~                                           | 端子ごと    | I <sub>OL</sub> 1 | 40                                                                     | mA |

|              | P110, P112, P201, P206<br>~P208, P300, P407,<br>P913, P914 | 全端子の合計  |                   | 100                                                                    | mA |

|              | P008~P015, P212,                                           | 端子ごと    | I <sub>OL</sub> 2 | 10                                                                     | mA |

|              | P213                                                       | 全端子の合計  |                   | 20                                                                     | mA |

| 動作温度         | 通常動作モード                                                    |         | Та                | -40~+105                                                               | °C |

|              | フラッシュメモリプログ                                                | ラミングモード |                   | -40~+105                                                               | °C |

| 保存温度         |                                                            |         | Tstg              | -65~+150                                                               | °C |

- 注 1. コンデンサ (0.47~1 μF) を介して VCL 端子を VSS 端子に接続してください。表に記載された値は、VCL 端子の絶対最大定格です。 コンデンサ接続のみを使用してください。この端子には特定の電圧を印加しないでください。

- 注 2. この電圧は 6.5 V 以下にしてください。

- 注 3. A/D 変換に使用する端子の電圧は、VREFH0 + 0.3 を超えないでください。

- 注. ある端子の多重化された機能の特性は、他に指定がなければ、ポート端子の特性と同じです。

- 注. VREFH0 は A/D コンバータの正の基準電圧を参照します。

- 注. 基準電圧は VSS です。

【使用上の注意】瞬間的にでも、いずれかの項目が絶対最大定格を超えた場合、製品の品質が損なわれる可能性があります。 つまり、絶対最大定格は、製品に物理的損傷が生じる寸前で評価された値です。したがって、絶対最大定格 を超えない条件下で、製品を使用してください。

## 修正前:表 31.11 I/O その他の特性 (p.674, p.675)

## 表 31.11 I/O その他の特性 (1/2)

条件: VCC = 1.6~5.5 V, VSS = 0 V, Ta = -40~+105°C

| 項目           |                                                                                     | シンボル               | Min | Тур | Max | 単位 | 測定条件                 |

|--------------|-------------------------------------------------------------------------------------|--------------------|-----|-----|-----|----|----------------------|

| 入力リーク電流、High | P100~P103, P108~<br>P110, P112, P200, P201,<br>P206~P208, P300, P407,<br>P913, P914 | I <sub>LIH</sub> 1 | _   | 1   | 1   | μΑ | V <sub>I</sub> = VCC |

|              | P008~P015                                                                           | I <sub>LIH</sub> 2 | _   |     | 1   | μΑ | V <sub>I</sub> = VCC |

|              | P212~P214                                                                           | I <sub>LIH</sub> 3 | _   | 1   | 1   | μΑ | V <sub>I</sub> = VCC |

## 表 31.11 I/O その他の特性 (2/2)

条件: VCC = 1.6~5.5 V, VSS = 0 V, Ta = -40~+105°C

| 項目          | 項目                                                                                  |                    |    | Тур      | Max | 単位 | 測定条件                          |  |

|-------------|-------------------------------------------------------------------------------------|--------------------|----|----------|-----|----|-------------------------------|--|

| 入力リーク電流、Low | P100~P103, P108~<br>P110, P112, P200, P201,<br>P206~P208, P300, P407,<br>P913, P914 | I <sub>LIL</sub> 1 | _  | _        | -1  | μА | V <sub>I</sub> = VSS          |  |

|             | P008~P015                                                                           | I <sub>LIL</sub> 2 | _  | _        | -1  | μΑ | V <sub>I</sub> = VSS          |  |

|             | P212~P214                                                                           | I <sub>LIL</sub> 3 | _  | _        | -1  | μΑ | V <sub>I</sub> = VSS          |  |

| 内蔵プルアップ抵抗   | P100~P103, P108~<br>P110, P112, P201, P206~<br>P208, P212, P213, P300,<br>P407      | R <sub>U</sub>     | 10 | 20       | 100 | kΩ | V <sub>I</sub> = VSS<br>入力ポート |  |

| 入力容量        | P200                                                                                | Cin                | _  | _        | 30  | pF | Vin = 0 V, f = 1 MHz,         |  |

|             | その他の入力端子                                                                            |                    | _  | <u> </u> |     |    | Ta = 25°C                     |  |

注. ある端子の多重化された機能の特性は、他に指定がなければ、ポート端子の特性と同じです。

#### 修正後:表 31.11 I/O その他の特性

## 表 31.11 I/O その他の特性 (1/2)

条件: VCC = 1.6~5.5 V, VSS = 0 V, Ta = -40~+105°C

| 項目           |                                                                                     | シンボル               | Min | Тур | Max | 単位 | 測定条件                 |

|--------------|-------------------------------------------------------------------------------------|--------------------|-----|-----|-----|----|----------------------|

| 入力リーク電流、High | P100~P103, P108~<br>P110, P112, P200, P201,<br>P206~P208, P300, P407,<br>P913, P914 | I <sub>LIH</sub> 1 | _   | _   | 1   | μΑ | V <sub>I</sub> = VCC |

|              | P008~P015                                                                           | I <sub>LIH</sub> 2 | _   | _   | 1   | μΑ | V <sub>I</sub> = VCC |

|              | P212~P215                                                                           | I <sub>LIH</sub> 3 | _   | _   | 1   | μΑ | V <sub>I</sub> = VCC |

## 表 31.11 I/O その他の特性 (2/2)

条件: VCC = 1.6~5.5 V, VSS = 0 V, Ta = -40~+105°C

| 項目          | 項目                                                                                  |                    |    | Тур | Max | 単位 | 測定条件                          |  |

|-------------|-------------------------------------------------------------------------------------|--------------------|----|-----|-----|----|-------------------------------|--|

| 入力リーク電流、Low | P100~P103, P108~<br>P110, P112, P200, P201,<br>P206~P208, P300, P407,<br>P913, P914 | I <sub>LIL</sub> 1 | _  | _   | -1  | μА | V <sub>I</sub> = VSS          |  |

|             | P008~P015                                                                           | I <sub>LIL</sub> 2 | _  | 1   | -1  | μΑ | V <sub>I</sub> = VSS          |  |

|             | P212~P215                                                                           | I <sub>LIL</sub> 3 | _  |     | -1  | μΑ | V <sub>I</sub> = VSS          |  |

| 内蔵プルアップ抵抗   | P100~P103, P108~<br>P110, P112, P201, P206~<br>P208, P212, P213, P300,<br>P407      | R <sub>U</sub>     | 10 | 20  | 100 | kΩ | V <sub>I</sub> = VSS<br>入力ポート |  |

| 入力容量        | P200                                                                                | Cin                | _  | _   | 30  | pF | Vin = 0 V, f = 1 MHz,         |  |

|             | その他の入力端子                                                                            |                    | _  |     | 15  |    | Ta = 25°C                     |  |

注. ある端子の多重化された機能の特性は、他に指定がなければ、ポート端子の特性と同じです。

修正前:表 31.12 動作電流とスタンバイ電流 (1)(2/2)(p.677)

表 31.12 動作電流とスタンバイ電流 (1) (2/2)

条件: VCC = 1.6~5.5 V

| 項目   |                               |        |                   |                   |            | シンボル | Typ<br>(注5) | Max  | 単位 | 測定条件 |

|------|-------------------------------|--------|-------------------|-------------------|------------|------|-------------|------|----|------|

| 消費電流 | Subosc-                       | 通常モー   | 周辺クロックが無          | ICLK = 32.768 kHz | Ta = -40°C | Icc  | 3.3         | _    | μΑ | _    |

| (注1) | speed モ<br>ード <sup>(注4)</sup> | ド      | 効                 |                   | Ta = 25°C  |      | 3.7         | _    |    |      |

|      |                               |        |                   |                   | Ta = 50°C  |      | 3.9         | _    |    |      |

|      |                               |        |                   |                   | Ta = 70°C  | ]    | 4.3         | _    |    |      |

|      |                               |        |                   |                   | Ta = 85°C  | ]    | 4.8         | _    |    |      |

|      |                               | Ta = 1 | Ta = 105°C        |                   | 6.2        | _    | 1           |      |    |      |

|      |                               |        | 周辺クロックが有          | ICLK = 32.768 kHz | Ta = -40°C |      | _           | 7.2  |    |      |

|      |                               |        | 効 <sup>(注6)</sup> |                   | Ta = 25°C  |      | _           | 7.9  |    |      |

|      |                               |        |                   |                   | Ta = 50°C  |      | _           | 9.6  |    |      |

|      |                               |        |                   |                   | Ta = 70°C  |      | _           | 13.0 |    |      |

|      |                               |        |                   |                   | Ta = 85°C  |      | _           | 18.8 |    |      |

|      |                               |        |                   |                   | Ta = 105°C |      | _           | 36.5 |    |      |

|      |                               | スリープ   | 周辺クロックが無          | ICLK = 32.768 kHz | Ta = -40°C |      | 1.0         | _    |    | _    |

|      |                               | モード    | 効                 |                   | Ta = 25°C  |      | 1.3         | _    |    |      |

|      |                               |        |                   |                   | Ta = 50°C  |      | 1.5         | _    |    |      |

|      |                               |        |                   |                   | Ta = 70°C  |      | 1.8         | _    |    |      |

|      |                               |        |                   |                   | Ta = 85°C  |      | 2.2         | -    |    |      |

|      |                               |        |                   |                   | Ta = 105°C |      | 3.2         | _    |    |      |

|      |                               |        | 周辺クロックが有          | ICLK = 32.768 kHz | Ta = -40°C |      | _           | 4.8  |    |      |

|      |                               |        | 効 <sup>(注6)</sup> |                   | Ta = 25°C  | ]    | _           | 5.4  |    |      |

|      |                               |        |                   |                   | Ta = 50°C  |      | _           | 7.0  |    |      |

|      |                               |        |                   |                   | Ta = 70°C  |      | _           | 10.5 |    |      |

|      |                               |        |                   |                   | Ta = 85°C  | ]    |             | 16.1 |    |      |

|      |                               |        |                   |                   | Ta = 105°C |      | _           | 33.3 |    |      |

- 注 1. 消費電流は、VCC に流れ込む電流の合計です。内部プルアップ MOS が OFF 状態のとき、消費電流値が適用されます。また、これらの値にはいずれの端子からの出力充放電電流も含まれません。

- 注 2. クロックソースは高速オンチップオシレータ (HOCO) です。

- 注 3. クロックソースは中速オンチップオシレータ (MOCO) です。

- 注 4. クロックソースはサブクロック発振器 (SOSC) で、CMC.SODRV[1:0] は 10b (低消費電力モード 2) です。

- 注 5. VCC = 3.3 V

- 注 6. PCLBUZ、TAU、SAU、および IICA 機能のみの動作電流を含みます。その他の周辺機能の動作電流については、表 31.14 の周辺機能消費電流を追加してください。

#### 修正後:表 31.12 動作電流とスタンバイ電流 (1)(2/2)

表 31.12 動作電流とスタンバイ電流 (1) (2/2)

条件: VCC = 1.6~5.5 V

| 項目   |                               |      |                    |                   |            | シンボル | Typ<br>(注5) | Max  | 単位 | 測定条件 |

|------|-------------------------------|------|--------------------|-------------------|------------|------|-------------|------|----|------|

| 消費電流 | Subosc-                       | 通常モー | 周辺クロックが無           | ICLK = 32.768 kHz | Ta = -40°C | Icc  | 3.3         | _    | μΑ | _    |

| (注1) | speed モ<br>ード <sup>(注4)</sup> | ド    | 効<br>              |                   | Ta = 25°C  | ]    | 3.7         | _    |    |      |

|      |                               |      |                    |                   | Ta = 50°C  | ]    | 3.9         | _    | ]  |      |

|      |                               |      |                    |                   | Ta = 70°C  | ]    | 4.3 —       | ]    |    |      |

|      |                               |      |                    |                   | Ta = 85°C  | ]    | 4.8         | _    |    |      |

|      |                               |      |                    |                   | Ta = 105°C | ]    | 6.2         | _    |    |      |

|      |                               |      | 周辺クロックが有           | ICLK = 32.768 kHz | Ta = -40°C | ]    | _           | 7.2  | ]  |      |

|      |                               |      | 効 <sup>(注 7)</sup> |                   | Ta = 25°C  | ]    | _           | 7.9  |    |      |

|      |                               |      |                    |                   | Ta = 50°C  |      | _           | 9.6  |    |      |

|      |                               |      |                    |                   | Ta = 70°C  |      | _           | 13.0 | ]  |      |

|      |                               |      |                    |                   | Ta = 85°C  |      | _           | 18.8 |    |      |

|      |                               |      |                    |                   | Ta = 105°C |      | _           | 36.5 |    |      |

|      |                               | スリープ | 周辺クロックが無           | ICLK = 32.768 kHz | Ta = -40°C |      | 1.0         | _    |    | _    |

|      |                               | モード  | 効<br>              |                   | Ta = 25°C  | -    | 1.3         | _    |    |      |

|      |                               |      |                    |                   | Ta = 50°C  |      | 1.5         | _    |    |      |

|      |                               |      |                    |                   | Ta = 70°C  |      | 1.8         | _    |    |      |

|      |                               |      |                    |                   | Ta = 85°C  | ]    | 2.2         | _    |    |      |

|      |                               |      |                    |                   | Ta = 105°C |      | 3.2         | _    | 1  |      |

|      |                               |      | 周辺クロックが有           | ICLK = 32.768 kHz | Ta = -40°C |      | _           | 4.8  |    |      |

|      |                               |      | 対 <sup>(注 7)</sup> |                   | Ta = 25°C  | ]    | _           | 5.4  | ]  |      |

|      |                               |      |                    |                   | Ta = 50°C  |      | _           | 7.0  | ]  |      |

|      |                               |      |                    |                   | Ta = 70°C  |      | _           | 10.5 | ]  |      |

|      |                               |      |                    |                   | Ta = 85°C  | ]    | _           | 16.1 | ]  |      |

|      |                               |      |                    |                   | Ta = 105°C |      | _           | 33.3 | ]  |      |

- 注 1. 消費電流は、VCC に流れ込む電流の合計です。内部プルアップ MOS が OFF 状態のとき、消費電流値が適用されます。また、これらの値にはいずれの端子からの出力充放電電流も含まれません。

- 注 2. クロックソースは高速オンチップオシレータ (HOCO) です。

- 注 3. クロックソースは中速オンチップオシレータ (MOCO) です。

- 注 4. クロックソースはサブクロック発振器 (SOSC) で、CMC.SODRV[1:0] は 10b (低消費電力モード 2) です。

- 注 5. VCC = 3.3 V

- 注 6. PCLBUZ、TAU、SAU、および IICA 機能のみの動作電流を含みます。その他の周辺機能の動作電流については、表 31.14 の周辺機能消費電流を追加してください。

- 注 7. PCLBUZ、TAU、および SAU 機能のみの動作電流を含みます。その他の周辺機能の動作電流については、表 31.14 の周辺機能消費電流を追加してください。

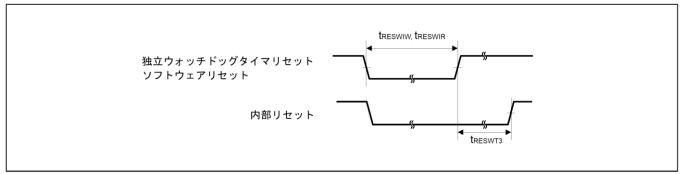

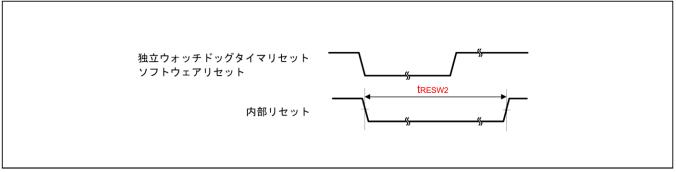

#### 修正前:表 31.16 リセットタイミング (2/2)(p.684)

#### 表 31.16 リセットタイミング (2/2)

| 項目                                                               | シンボル                | Min | Тур  | Max   | 単位 | 測定条件 |

|------------------------------------------------------------------|---------------------|-----|------|-------|----|------|

| 内部リセット解除後の待機時間<br>(独立ウォッチドッグタイマリセット、SRAM パリティエラーリセット、ソフトウェアリセット) | t <sub>RESWT3</sub> |     | 0.04 | 0.041 | ms | _    |

注 1. OFS1.LVDAS = 0 のとき

注 2. OFS1.LVDAS = 1 のとき

注 3. RES 端子が外部リセット入力として使用されない場合、この仕様は無視できます。

## 修正後:表 31.16 リセットタイミング (2/2)

#### 表 31.16 リセットタイミング (2/2)

| 項目                                                           | シンボル   | Min | Тур  | Max   | 単位 | 測定条件 |

|--------------------------------------------------------------|--------|-----|------|-------|----|------|

| 内部リセット<br>(独立ウォッチドッグタイマリセット、SRAM パリティエラー<br>リセット、ソフトウェアリセット) | tresw2 | _   | 0.04 | 0.041 | ms | _    |

注 1. OFS1.LVDAS = 0 のとき

注 2. OFS1.LVDAS = 1 のとき 注 3. RES 端子が外部リセット入力として使用されない場合、この仕様は無視できます。

発行日: 2024年12月27日

## 修正前:図 31.11 リセット入力タイミング (2) (p.684)

図 31.11 リセット入力タイミング (2)

## 修正後:図 31.11 リセット入力タイミング (2)

図 31.11 リセット入力タイミング (2)

## RENESAS TECHNICAL UPDATE TN-RA\*-A0132A/J

修正前:表 31.46 LVD1 特性 (2/2) (p.719)

表 31.46 LVD1 特性 (2/2)

条件: VPDR  $\leq$  VCC  $\leq$  5.5 V, VSS = 0 V, Ta = -40 $\sim$ +105 $^{\circ}$ C

| 項目     |         | シンボル                 | Min  | Тур  | Max  | 単位 | 測定条件    |

|--------|---------|----------------------|------|------|------|----|---------|

| 検出電圧   | 電源電圧レベル | V <sub>det1_B</sub>  | 2.25 | 2.30 | 2.34 | V  | 電源電圧上昇中 |

|        |         |                      | 2.20 | 2.25 | 2.29 | V  | 電源電圧下降中 |

|        |         | V <sub>det1_C</sub>  | 2.15 | 2.20 | 2.24 | V  | 電源電圧上昇中 |

|        |         |                      | 2.10 | 2.15 | 2.19 | V  | 電源電圧下降中 |

|        |         | V <sub>det1_D</sub>  | 2.05 | 2.09 | 2.13 | V  | 電源電圧上昇中 |

|        |         |                      | 2.00 | 2.04 | 2.08 | V  | 電源電圧下降中 |

|        |         | V <sub>det1_E</sub>  | 1.94 | 1.98 | 2.02 | V  | 電源電圧上昇中 |

|        |         |                      | 1.90 | 1.94 | 1.98 | V  | 電源電圧下降中 |

|        |         | V <sub>det1_F</sub>  | 1.84 | 1.88 | 1.91 | V  | 電源電圧上昇中 |