# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製品  | 品分類           | MPU & MCU                      | 発行番号   | TN-RL*-A0 | 140A/J                                     | Rev.     | 第1版 |

|-----|---------------|--------------------------------|--------|-----------|--------------------------------------------|----------|-----|

| 題名  | 誤記訂<br>RL78/0 | 正通知<br>324 ユーザーズマニュアル Rev.1.10 | の記載変更  | 情報分類      | 技術情報                                       |          |     |

| 適   |               |                                | 対象ロット等 |           | DI 70/00/                                  | n _n_    |     |

| 用製品 | RL78/0        | G24 グループ                       | 全ロット   | 関連資料      | RL78/G24 ユーヤ<br>ハードウェア編 I<br>R01UH0961JJ01 | Rev.1.10 |     |

RL78/G24 ユーザーズマニュアル ハードウェア編 Rev.1.10 (R01UH0961JJ0110) において、下記訂正がご ざいます。

# 今回通知する訂正内容

| 訂正箇所                                 | 該当ページ              | 内容   |

|--------------------------------------|--------------------|------|

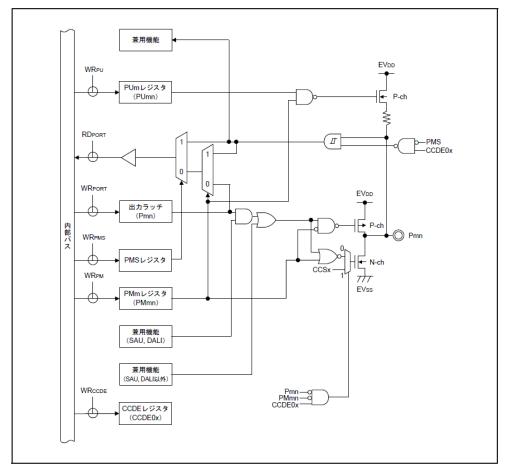

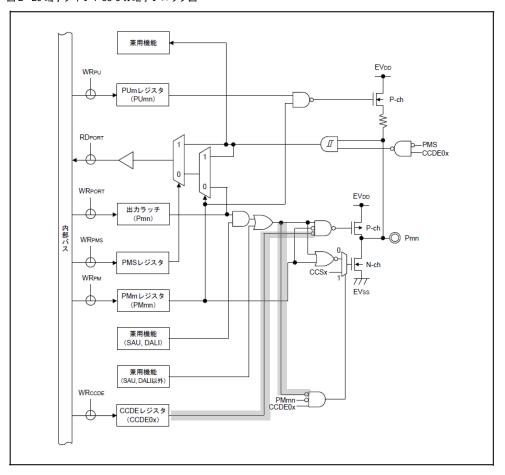

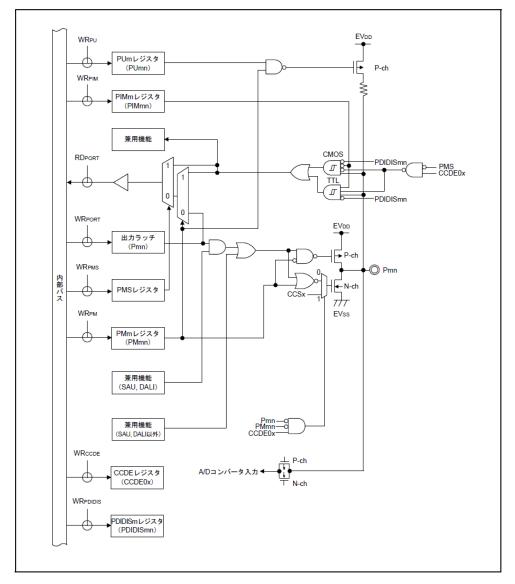

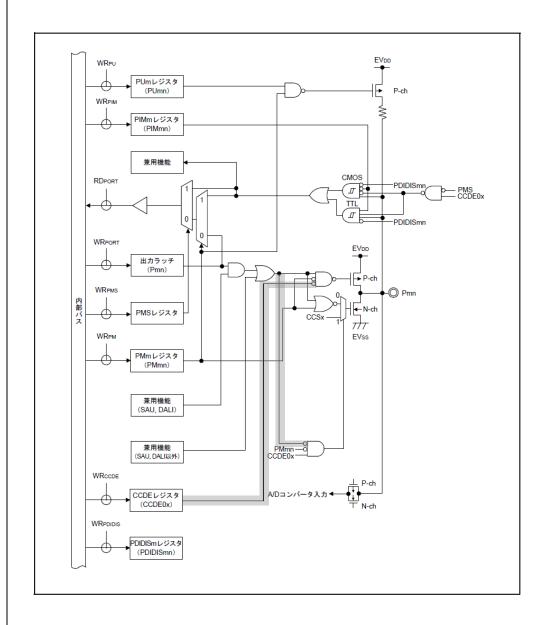

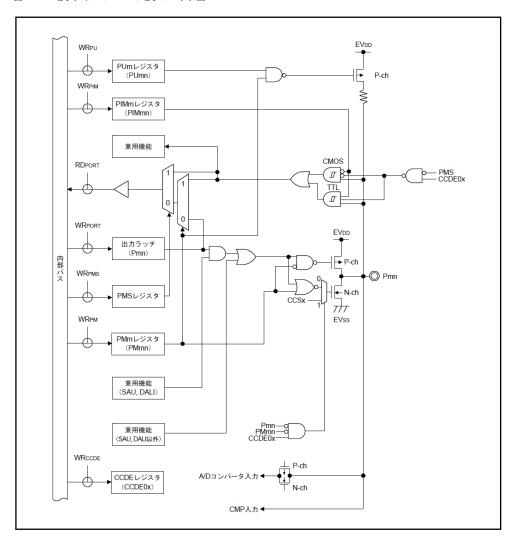

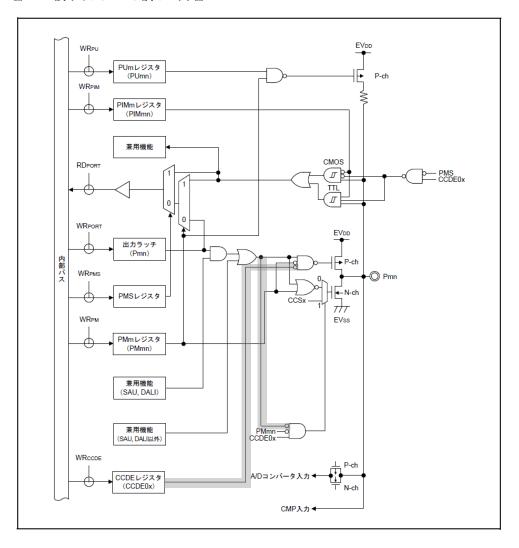

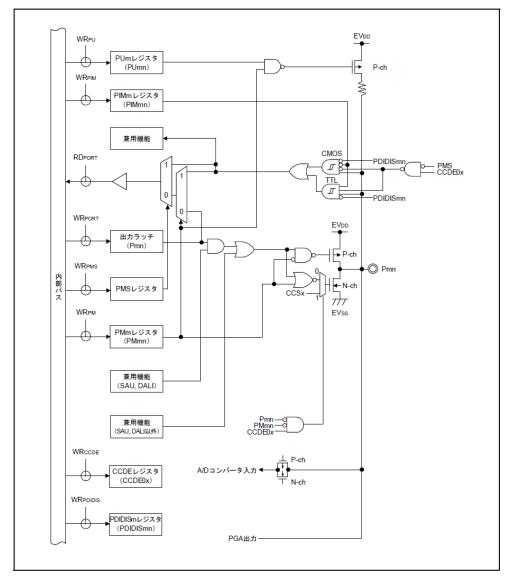

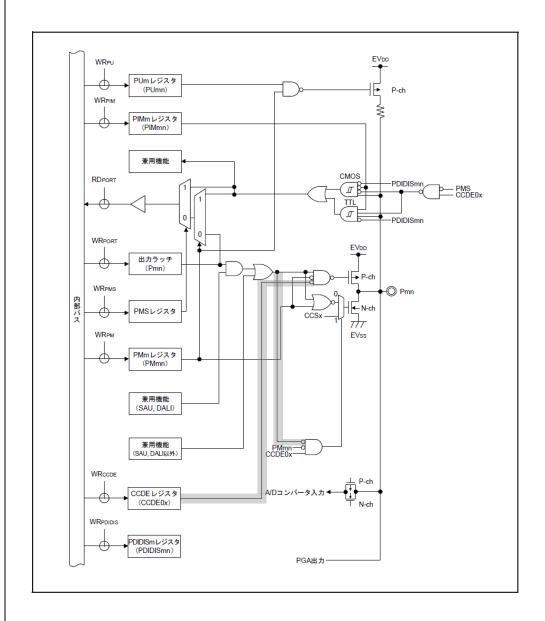

| 2.4 端子ブロック図                          | p.91, p.98, p.104, | 誤記訂正 |

|                                      | p.105, p.106       |      |

| 20.3.9 アナログ入力チャネル指定レジスタ(ADS)         | p.1144             | 誤記訂正 |

| 20.3.10 アナログ入力チャネル指定レジスタn(アドバンスド)    | p.1146             | 誤記訂正 |

| (ADSn) $(n = 0-3)$                   | p.1140             |      |

| 20.6.2 ソフトウェア・トリガ・ノーウエイト・モード(セレク     | p.1159             | 誤記訂正 |

| ト・モード、ワンショット変換モード)                   | p. 1159            |      |

| 24.3.8 シリアル・ステータス・レジスタmn(SSRmn)(mn = | p.1289             | 誤記訂正 |

| 00-03, 10, 11)                       | p. 1209            |      |

| 27.4.3 リピート・モード                      | p.1641             | 誤記訂正 |

| 29.4 割り込み処理動作                        | p.1681, p.1683     | 誤記訂正 |

| 42.2 オペレーション一覧                       | p.1891             | 誤記訂正 |

| 43.2 発振回路特性                          | p.1896             | 誤記訂正 |

| 43.3.2 電源電流特性                        | p.1907, p.1910     | 誤記訂正 |

| 44.2 発振回路特性                          | p.1978             | 誤記訂正 |

| 44.3.2 電源電流特性                        | p.1987, p.1990     | 誤記訂正 |

| 44.4 AC特性                            | p.1995             | 誤記訂正 |

# ドキュメント改善計画

本訂正内容については、次回ユーザーズマニュアル改版時に修正を行います。

# ユーザーズマニュアルの訂正一覧

|    | ≣T⊺                                        | <br>E内容と該当箇所    |                                    |                |

|----|--------------------------------------------|-----------------|------------------------------------|----------------|

| No | ドキュメント<br>No.                              | 和文              | R01UH0961JJ0110                    | 本通知での<br>該当ページ |

| 1  | 3.1 メモリ空間                                  |                 | p.108, p.109, p.114                | p.3 – p.5      |

| 2  | 20.3.3 A/Dコンバータ・モード・レジン                    |                 | p.1116, p.1120,<br>p.1122 – p.1132 | p.6 – p.18     |

| 3  | 20.3.4 A/Dコンバータ・モード・レジス                    | スタ1(ADM1)       | p.1134                             | p.19           |

| 4  | 20.3.5 A/Dコンバータ・モード・レジン                    | スタ2(ADM2)       | p.1136, p.1137                     | p.20, p.21     |

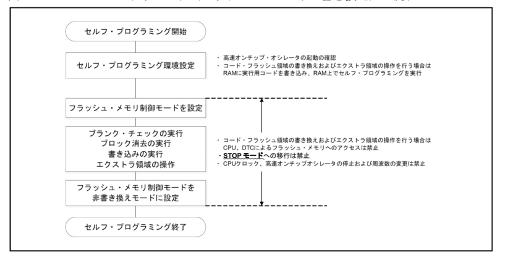

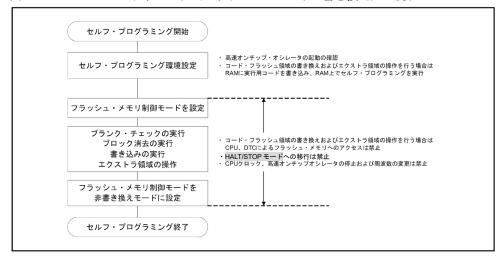

| 5  | 39.6.1 セルフ・プログラミング手順                       |                 | p.1811                             | p.22           |

| 6  | 39.10.1 データ・フラッシュの概要                       |                 | p.1862                             | p.23           |

| 7  | 40.3 オンチップ・デバッグのセキュリ                       | ティ設定            | p.1865                             | p.24           |

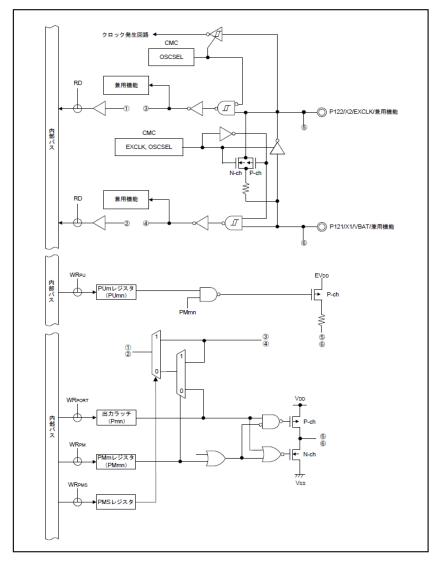

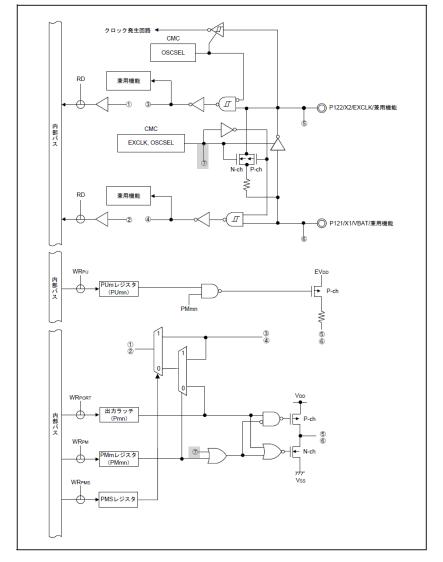

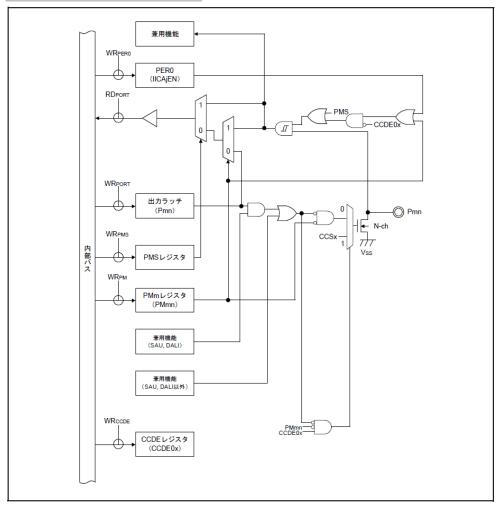

| 8  | 2.4 端子ブロック図                                |                 | p.91, p.98, p.104,<br>p.105, p.106 | p.25 – p.30    |

| 9  | 20.3.9 アナログ入力チャネル指定レジ                      | スタ(ADS)         | p.1144                             | p.31           |

| 10 | 20.3.10 アナログ入力チャネル指定レジ<br>(ADSn)(n = 0-3)  |                 | p.1146                             | p.32           |

| 11 | 20.6.2 ソフトウェア・トリガ・ノーウ<br>ト・モード、ワンショット変換モード |                 | p.1159                             | p.33           |

| 12 | 24.3.8 シリアル・ステータス・レジス<br>00-03, 10, 11)    | タmn(SSRmn)(mn = | p.1289                             | p.34           |

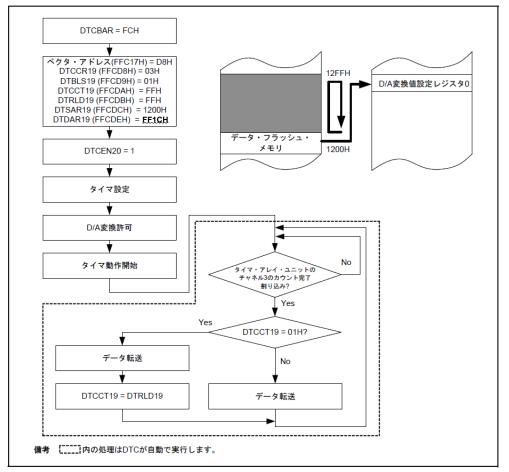

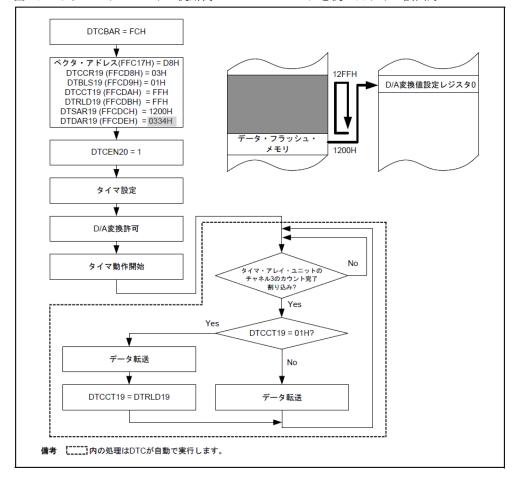

| 13 | 27.4.3 リピート・モード                            |                 | p.1641                             | p.35           |

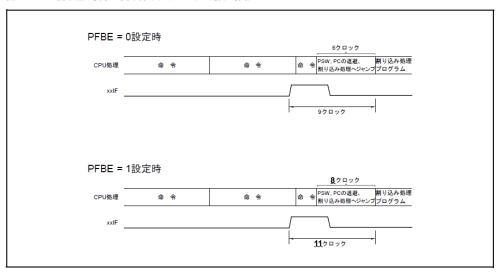

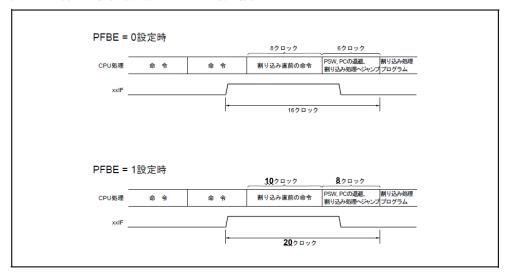

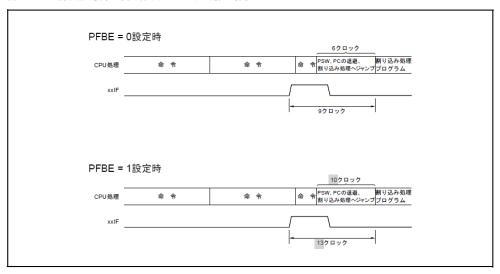

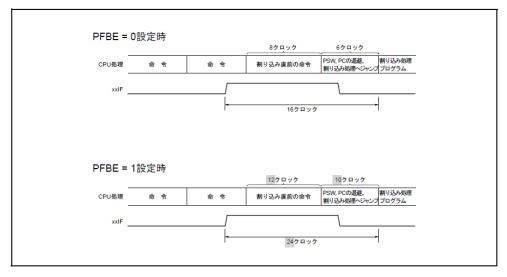

| 14 | 29.4 割り込み処理動作                              |                 | p.1681, p.1683                     | p.36, p.37     |

| 15 | 42.2 オペレーション一覧                             |                 | p.1891                             | p.38           |

| 16 | 43.2 発振回路特性                                |                 | p.1896                             | p.39           |

| 17 | 43.3.2 電源電流特性                              |                 | p.1907, p.1910                     | p.40, p.41     |

| 18 | 44.2 発振回路特性                                |                 | p.1978                             | p.42           |

| 19 | 44.3.2 電源電流特性                              |                 | p.1987, p.1990                     | p.43, p.44     |

| 20 | 44.4 AC特性                                  |                 | p.1995                             | p.45           |

誤記訂正の該当箇所は、誤)太字下線、正)グレー・ハッチングで記載します。

# 発行文書履歴

RL78/G24 ユーザーズマニュアル Rev.1.10 誤記訂正通知 発行文書履歴

| 文書番号            | 発行日        | 記事                               |

|-----------------|------------|----------------------------------|

| TN-RL*-A0135A/J | 2024年4月26日 | 初版発行<br>訂正一覧の No.1 ~ No.7 の誤記訂正  |

| TN-RL*-A0140A/J | 2025年1月8日  | 訂正一覧の No.8 ~ No.20 の誤記訂正(本通知です。) |

発行日:2025年1月8日

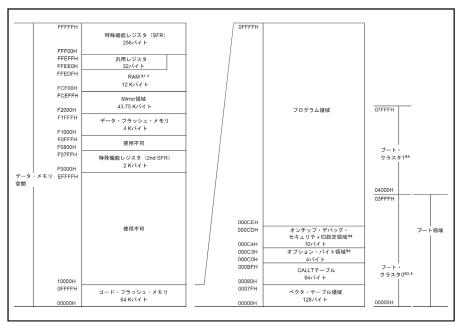

1. <u>3.1 メモリ空間 (p. 108, p.109, p.114)</u>

誤)

(p. 108)

RL78/G24 は、1 M バイトのアドレス空間をアクセスできます。図 3 - 1 ~図 3 - 2 にメモリ・マップを示します。

図 3 - 1 メモリ・マップ(R7F101GxE(x = 6, 7, 8, A, B, E, F, G, J, L))

- 注1. 汎用レジスタを除いたRAM領域から命令実行をすることができます。

- 注2. ブート・スワップ未使用時: 000C0H-000C3H にオプション・バイト、000C4H-000CDH にオンチップ・デバッグ・セキュリティIDを設定 ブート・スワップ使用時: 000C0H-000C3H、040C0H-040C3Hにオプション・バイト、000C4H-000CDH、040C4H-040CDHにオンチップ・デバッグ・セキュリティID設定

(略)

正)

図 3 - 1 メモリ・マップ(R7F101GxE(x = 6, 7, 8, A, B, E, F, G, J, L))

発行日:2025年1月8日

- 注1. 汎用レジスタを除いたRAM領域から命令実行をすることができます。

- 注2. ブート・スワップ未使用時(FLSECレジスタのBTFLGビットが1の状態): 000C0H-000C3H にオプション・バイト、000C4H-000CDH にオンチップ・デバッグ・セキュリティIDを設定

ブート・スワップ使用時およびFLSECレジスタのBTFLGビットが0の状態のとき: 000C0H-000C3H、040C0H-040C3Hにオプション・バイト、000C4H-000CDH、040C4H-040CDHにオンチップ・デバッグ・セキュリティID設定

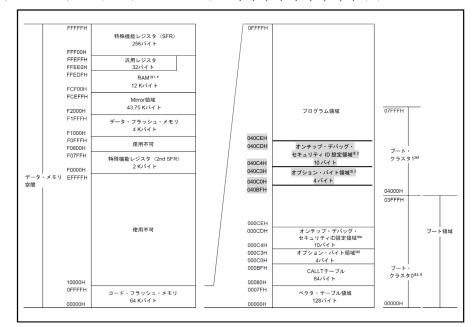

(p. 109)

図 3 - 2 メモリ・マップ(R7F101GxG(x = 6, 7, 8, A, B, E, F, G, J, L))

- 注1. 汎用レジスタを除いたRAM領域から命令実行をすることができます。

- 注2. <u>ブート・スワップ未使用時</u>: 000C0H-000C3H にオプション・バイト、000C4H-000CDH にオンチップ・デバッグ・セキュリティIDを設定 ブート・スワップ使用時: 000C0H-000C3H、040C0H-040C3Hにオプション・バ

**フート・スワップ使用時**: 000C0H-000C3H、040C0H-040C3Hにオフション・ハイト、000C4H-000CDH、040C4H-040CDHにオンチップ・デバッグ・セキュリティID設定

(略)

発行日:2025年1月8日

### 図 3 - 2 メモリ・マップ(R7F101GxG(x = 6, 7, 8, A, B, E, F, G, J, L))

- 注1. 汎用レジスタを除いたRAM領域から命令実行をすることができます。

- 注2. ブート・スワップ未使用時(FLSECレジスタのBTFLGビットが1の状態): 000C0H-000C3H にオプション・バイト、000C4H-000CDH にオンチップ・デバッグ・セキュリティIDを設定

ブート・スワップ使用時およびFLSECレジスタのBTFLGビットが0の状態のとき: 000C0H-000C3H、040C0H-040C3Hにオプション・バイト、000C4H-000CDH、040C4H-040CDHにオンチップ・デバッグ・セキュリティID設定

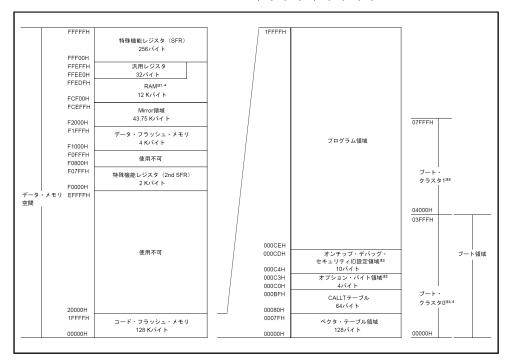

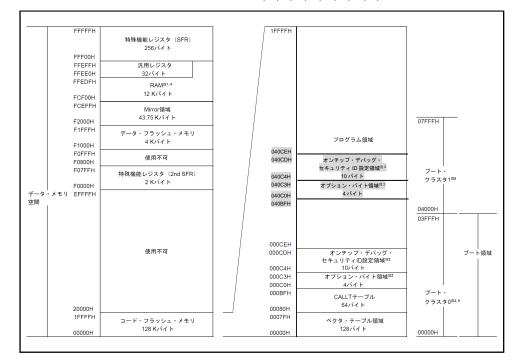

(p.114)

(略)

(3) オプション・バイト領域

000C0H-000C3H の4 バイト領域にオプション・バイト領域を用意しています。**ブート・スワップを使用する際**には040C0H-040C3H にもオプション・バイトを設定してください。詳細は、第**38**章 オプション・バイトを参照してください。

(4) オンチップ・デバッグ・セキュリティID設定領域

000C4H-000CDH、040C4H-040CDH の10 バイト領域にオンチップ・デバッグ・セキュリティID 設定領域を用意しています。**ブート・スワップ未使用時**には000C4H-000CDH に、**ブート・スワップ使用時**には000C4H-000CDHと040C4H-040CDHに10バイトのオンチップ・デバッグ・セキュリティIDを設定してください。詳細は、第**40**章 オンチップ・デバッグ機能を参照してください。

発行日:2025年1月8日

(略)

(3) オプション・バイト領域

000C0H-000C3H の4 バイト領域にオプション・バイト領域を用意しています。 ブート・スワップ使用時およびFLSECレジスタのBTFLGビットが0の状態のときには 040C0H-040C3H にもオプション・バイトを設定してください。詳細は、第38章 オプション・バイトを参照してください。

(4) オンチップ・デバッグ・セキュリティID設定領域

000C4H-000CDH、040C4H-040CDH の10 バイト領域にオンチップ・デバッグ・セキュリティID 設定領域を用意しています。ブート・スワップ未使用時(FLSECレジスタのBTFLGビットが1の状態)には000C4H-000CDHに、ブート・スワップ使用時およびFLSECレジスタのBTFLGビットが0の状態のときには000C4H-000CDHと040C4H-040CDHに10バイトのオンチップ・デバッグ・セキュリティIDを設定してください。詳細は、第40章 オンチップ・デバッグ機能を参照してください。

2. <u>20.3.3 A/D コンパータ・モード・レジスタ 0 (ADM0) (p. 1116, p.</u> 1120, p. 1122 – p. 1132)

誤)

(p. 1116)

図 20 - 4 A/D コンバータ・モード・レジスタ 0 (ADM0) のフォーマット

(略)

| ADCE | A/D電圧コンパレータの動作制御 <sup>注2</sup> |

|------|--------------------------------|

| 0    | A/D 電圧コンパレータの動作停止              |

| 1    | A/D 電圧コンパレータの動作許可              |

- 注1. FR[2:0], LV[1:0]ビットおよびA/D変換に関する詳細は、表20 6 A/D変換時間の選択を参照してください。

- 注2. ソフトウェア・トリガ・ノーウエイト・モード時およびハードウェア・トリガ・ノーウエイト・モード時、A/D電圧コンパレータはADCSビットとADCEビットで動作制御され、動作開始から安定するまでに、1 μs +変換クロック(fAD)の2クロックかかります。このため、ADCEビットに1を設定してから1 μs +変換クロック(fAD)の2クロック以上経過したあとに、ADCSビットに1を設定することで、最初の変換データより有効となります。

ADCE = 0状態でADCS = 1に設定した場合は、安定待ち後A/D変換を開始します。  $1 \mu s$  +変換クロック(fAD)の2クロック以上ウエイトしないでADCSビットに1を設定した場合は、最初の変換データを無視してください。

注意1. ADMD, FR[2:0], LV[1:0]ビットの変更は、変換停止状態(ADCS = 0, ADCE = 0)で行ってください。

注意2. ADCS = 1, ADCE = 1からADCS = 1, ADCE = 0への設定は禁止です。

注意3. ADCS = 0, ADCE = 0の状態から8ビット操作命令でADCS = 1, ADCE = 1に設定することは禁止です。必ず20.7 A/Dコンバータの設定フロー・チャートの手順に従ってください。

注意4. アドバンスド・モードONの場合はADMD = 1に設定することは禁止です。

注意5. アドバンスド・モードONの場合はADCS = 1のとき、ADCS = 1を上書きすることは禁止です。 注意 6. アドバンスド・モード ON の場合は ADCE = 1 のとき、ADCE = 1 を上書きすることは禁止です。

正)

図 20 - 4 A/D コンバータ・モード・レジスタ 0 (ADM0) のフォーマット

(略)

| ADCE | A/D電圧コンパレータの動作制御 <sup>注2</sup> |

|------|--------------------------------|

| 0    | A/D 電圧コンパレータの動作停止              |

| 1    | A/D 電圧コンパレータの動作許可              |

- 注1. FR[2:0], LV[1:0]ビットおよびA/D変換に関する詳細は、表**20 6** A/D変換時間の選択を参照してください。

- 注2. ソフトウェア・トリガ・ノーウエイト・モード時およびハードウェア・トリガ・ノーウエイト・モード時、A/D電圧コンパレータはADCSビットとADCEビットで動作制御され、動作開始から安定するまでに、1 µs +変換クロック(fAD)の2クロックかかります。このため、ADCEビットに1を設定してから1 µs +変換クロック(fAD)の2クロック以上経過したあとに、ADCSビットに1を設定することで、最初の変換データより有効となります。ADCE = 0状態でADCS = 1に設定した場合は、安定待ち後A/D変換を開始します。1 µs +変換クロック(fAD)の2クロック以上ウエイトしないでADCSビットに1を設定した場合は、最初の変換データを無視してください。

- 注意1. ADMD, FR[2:0], LV[1:0]ビットの変更は、変換停止状態(ADCS = 0, ADCE = 0)で行ってください。

- 注意2. ADCS = 1, ADCE = 1からADCS = 1, ADCE = 0への設定は禁止です。

- 注意3. ADCS = 0, ADCE = 0の状態から8ビット操作命令でADCS = 1, ADCE = 1に設定することは禁止です。必ず20.7 A/Dコンバータの設定フロー・チャートの手順に従ってください。

- 注意4. アドバンスド・モードONの場合はADMD = 1に設定することは禁止です。

- 注意5. アドバンスド・モードONの場合はADCS = 1のとき、ADCS = 1を上書きすることは禁止です。

- 注意 6. アドバンスド・モード ON の場合は ADCE = 1 のとき、ADCE = 1 を上書きすることは禁止です。 注意7. 変換待機状態/変換動作状態からADCS=0, ADCE=0の変換停止状態にした場合は、次に

ADCE=1またはADCS=1を設定するまでに5μsウエイトしてください。なお、ADMD, FR2-FR0, LV1, LV0ビットを変更する場合は、ADCS=0, ADCE=0に設定した後、0.2μs経過後にADMD, FR2-FR0, LV1, LV0ビットを変更してください。

(p. 1120)

注意1. ハードウェア・トリガ・ウエイト・モードで使用する場合、ADCSビットに1を設定するのは禁止です(ハードウェア・トリガ信号検出時に、自動的に1に切り替わります)。ただし、A/D変換待機状態にするために、ADCSビットに0を設定することは可能です。

注意2. ハードウェア・トリガ・ノーウエイト・モードおよびアドバンスド・モードでのワンショット 変換モード時、A/D変換終了時にADCSビットは、自動的に0にクリアされません。1のまま保持されます。

注意3. ADCEビットの書き換えは、ADCS = 0 (変換停止/変換待機状態) のときに行ってください。

注意4. アドバンスド・モードではトリガ要因が発生してから、トリガを検知するまでに3 fcLk必要です。表20 - 5にアドバンスド・モードでの、トリガ発生または直前変換終了後~A/D変換開始までのクロック数を示します。

注意5. A/D変換を完了させるためには、ハード・トリガ間隔を次の時間以上としてください。 ハードウェア・トリガ・ノーウエイト・モード時: fCLKの2クロック+変換起動時間+ A/D変換 時間

ハードウェア・トリガ・ウエイト・モード時: fclkの2クロック+変換起動時間+ A/D電源安定 待ち時間+ A/D変換時間

アドバンスド・モード時: fclkの3クロック+変換起動時間+A/D変換時間

備考 fCLK : CPU/周辺ハードウェア・クロック周波数

変換開始遅延 : 変換起動時間経過後、A/D 変換時間が開始するまでに発生する遅延= 1 fAD

割り込み出力遅延: A/D 変換が完了後から INTAD0-3 を発生するまでの遅延= 1 fAD

発行日:2025年1月8日

- 注意1. ハードウェア・トリガ・ウエイト・モードで使用する場合、ADCSビットに1を設定するのは禁止です(ハードウェア・トリガ信号検出時に、自動的に1に切り替わります)。ただし、A/D変換待機状態にするために、ADCSビットに0を設定することは可能です。

- 注意2. ハードウェア・トリガ・ノーウエイト・モードおよびアドバンスド・モードでのワンショット 変換モード時、A/D変換終了時にADCSビットは、自動的に0にクリアされません。1のまま保持されます。

- 注意3. ADCEビットの書き換えは、ADCS = 0(変換停止/変換待機状態)のときに行ってください。

- 注意4. アドバンスド・モードではトリガ要因が発生してから、トリガを検知するまでに3 fcLk必要です。表20 5にアドバンスド・モードでの、トリガ発生または直前変換終了後~A/D変換開始までのクロック数を示します。

- 注意5. A/D変換を完了させるためには、ハード・トリガ間隔を次の時間以上としてください。 ハードウェア・トリガ・ノーウエイト・モード時: fclkの2クロック+変換起動時間+ A/D変換 時間

ハードウェア・トリガ・ウエイト・モード時: fCLK の2 クロック + 変換起動時間 + A/D 電源安定待ち時間 + A/D 変換時間 +  $5\mu s$

アドバンスド・モード時: fclkの3クロック+変換起動時間+ A/D変換時間

備考 fCLK : CPU/周辺ハードウェア・クロック周波数

変換開始遅延 : 変換起動時間経過後、A/D 変換時間が開始するまでに発生する遅延= 1 fAD

割り込み出力遅延: A/D 変換が完了後から INTAD0-3 を発生するまでの遅延= 1 fAD

(p. 1122)

表20 - 6 A/D変換時間の選択 (1/11)

(1) A/D電源安定待ち時間なし 標準モード1, 2

(ソフトウエア・トリガ・ノーウエイト・セレクト・モード/ハードウエア・トリガ・ノーウエイト・セレクト・モード)

| A/Dコンパータ・モード・レジスタ<br>A/Dコンパータ・モード・レジスタ |        |     |     |     |     |     |            |                     |             |                       | (変換       | A/D変換時間<br>変換開始遅延時間+変換時間+割り込み出力遅延時間) |                 |                 |                  |                  |  |  |

|----------------------------------------|--------|-----|-----|-----|-----|-----|------------|---------------------|-------------|-----------------------|-----------|--------------------------------------|-----------------|-----------------|------------------|------------------|--|--|

| (AD<br>M1)                             | (ADM0) |     |     |     |     | モード | クロック 延クロック | 変換開始遅<br>延クロック<br>数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |           | 2.4 V ≦ AVREFP ≦ VDD ≦ 5.5 V         |                 |                 |                  |                  |  |  |

| ADL<br>SP                              | FR2    | FR1 | FR0 | LV1 | LV0 |     | (3.0)      |                     |             | , , , , , ,           |           | fclk =<br>1 MHz                      | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |  |  |

| 0                                      | 0      | 0   | 0   | 0   | 0   | 標準1 | fclk/32    | 1 fAD               | 64 fad      | 1 fad                 | 2112/fcLK | 設定禁止                                 | 設定禁止            | 設定禁止            | 設定禁止             | 66 µs            |  |  |

| 0                                      | 0      | 0   | 1   |     |     |     | fclk/16    | 1 fad               | 64 fad      | 1 fad                 | 1056/fcLK | 設定禁止                                 | 設定禁止            | 設定禁止            | 66 µs            | 33 µs            |  |  |

| 0                                      | 0      | 1   | 0   |     |     |     | fclk/8     | 1 fad               | 64 fad      | 1 fAD                 | 528/fcLK  | 設定禁止                                 | 設定禁止            | 66 µs           | 33 µs            | 16.5 µs          |  |  |

| 1 | 0  | 1  | 1 |  | fclk/4 | 1 fAD | 181 fad         | 1 fAD | 732/fcLK | 設定禁止   | 183 µs   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|-----------------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 0 |  | fcLK/2 | 1 fAD | 181 fad         | 1 fad | 366/fcLK | 設定禁止   | 91.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

| 1 | 1  | 0  | 1 |  | fclk   | 1 fad | 181 <b>f</b> AD | 1 fad | 183/fcLK | 183 µs | 45.75 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        | 設定禁止  |                 |       |          |        |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、標準モード2を使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、標準モード1, 2は使用できません。低電圧モード1, 2を使用してください。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

発行日:2025年1月8日

表20 - 6 A/D変換時間の選択 (1/11)

(1) A/D電源安定待ち時間なし 標準モード1.2

(ソフトウェア・トリガ・ノーウェイト・セレクト・モード/ハードウェア・トリガ・ノーウェイト・セレクト・モード)

|            | A/Dコンパータ・モード・レジスタ<br>A/Dコンパータ・モード・レジスタ |     |     |     |     |     |                             |             |                       |           | A/D変換時間<br>(変換開始遅延時間+変換時間+割り込み出力遅延時間) |                                                                       |                 |                 |                  |                  |  |

|------------|----------------------------------------|-----|-----|-----|-----|-----|-----------------------------|-------------|-----------------------|-----------|---------------------------------------|-----------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|--|

| (AD<br>M1) | ) (ADMU)                               |     |     |     |     | モード | 変換 変換開始遅<br>クロック<br>(fAD) 数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |           |                                       | $2.4 \text{ V} \leq \text{AVREFP} \leq \text{VDD} \leq 5.5 \text{ V}$ |                 |                 |                  |                  |  |

| ADL<br>SP  | FR2                                    | FR1 | FR0 | LV1 | LV0 |     | (IAD)                       | **          |                       | ) L ) ) W |                                       | fclk =<br>1 MHz                                                       | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |  |

| 0          | 0                                      | 0   | 0   | 0   | 0   | 標準1 | fclk/32                     | 1 fad       | 64 fad                | 1 fad     | 2112/fcLK                             | 設定禁止                                                                  | 設定禁止            | 設定禁止            | 設定禁止             | 66 µs            |  |

| 0          | 0                                      | 0   | 1   |     |     |     | fcLK/16                     | 1 fAD       | 64 fad                | 1 fAD     | 1056/fcLK                             | 設定禁止                                                                  | 設定禁止            | 設定禁止            | 66 µs            | 33 µs            |  |

| 0          | 0                                      | 1   | 0   |     |     |     | fclk/8                      | 1 fAD       | 64 fad                | 1 fAD     | 528/fcLK                              | 設定禁止                                                                  | 設定禁止            | 66 µs           | 33 µs            | 16.5 µs          |  |

| 1 | T | 0  | 1  | 1 |  | fclk/4 | 1 fAD | 181 fad | 1 fAD | 732/fcLK | 設定禁止   | 183 µs   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 |   | 1  | 0  | 0 |  | fcLk/2 | 1 fAD | 181 fAD | 1 fAD | 366/fcLK | 設定禁止   | 91.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

| 1 |   | 1  | 0  | 1 |  | fclk   | 1 fAD | 181 fad | 1 fAD | 183/fcLK | 183 µs | 45.75 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   |   | 上記 | 以外 |   |  |        |       |         |       | 設定禁      | LE     |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2μs以上 経過したあとにFR2-FR0. LV1. LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、標準モード2を使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、標準モード1, 2は使用できません。低電圧モード1, 2を使用してください。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

(p. 1123)

表 20 - 6 A/D 変換時間の選択 (2/11)

(2) A/D 電源安定待ち時間なし低電圧モード 1, 2

(ソフトウェア・トリガ・ノーウエイト・セレクト・モード∕ハードウェア・トリガ・ノーウエイト・セレクト・モード)

|            |        |     | モード<br>モード |     |     |      |                     |             |             |                       | A/D変換時間<br>(変換開始遅延時間+変換時間+割り込み出力遅延時間) |                           |                           |                           |                  |                                       |  |  |

|------------|--------|-----|------------|-----|-----|------|---------------------|-------------|-------------|-----------------------|---------------------------------------|---------------------------|---------------------------|---------------------------|------------------|---------------------------------------|--|--|

| (AD<br>M1) | (ADM0) |     |            |     |     | モード  | 変換<br>クロック<br>(fAD) | 変換開始遅延クロック数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |                                       | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V | 1.8 V≦ AVREFP≦ VDD≦ 5.5 V | _                | 2.7 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V |  |  |

| ADL<br>SP  | FR2    | FR1 | FR0        | LV1 | LV0 |      |                     |             |             |                       |                                       | fclk =<br>1 MHz           | fclk =<br>4 MHz           | fclk =<br>8 MHz           | fclk =<br>16 MHz | fclk =<br>32 MHz                      |  |  |

| 0          | 0      | 0   | 0          | 1   | 0   | 低電圧1 | fclk/32             | 1 fAD       | 80 fAD      | 1 fAD                 | 2624/fcLK                             | 設定禁止                      | 設定禁止                      | 設定禁止                      | 設定禁止             | 82 µs                                 |  |  |

| 0          | 0      | 0   | 1          |     |     |      | fcLk/16             | 1 fAD       | 80 fAD      | 1 fAD                 | 1312/fcLK                             | 設定禁止                      | 設定禁止                      | 設定禁止                      | 82 µs            | 41 µs                                 |  |  |

| 0          | 0      | 1   | 0          |     |     |      | fclk/8              | 1 fAD       | 80 fAD      | 1 fAD                 | 656/fclk                              | 設定禁止                      | 設定禁止                      | 82 µs                     | 41 µs            | 20.5 µs                               |  |  |

| 1 | 0  | 1  | 1 |  | fcLk/4 | 1 fAD | 107 fAD | 1 fAD | 436/fclk | 設定禁止   | 109 µs   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 0 |  | fcLk/2 | 1 fAD | 107 fAD | 1 fAD | 218/fclk | 設定禁止   | 54.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

| 1 | 1  | 0  | 1 |  | fclk   | 1 fAD | 107 fAD | 1 fAD | 109/fclk | 109 µs | 27.25 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  | 設定禁止   |       |         |       |          |        |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、低電圧モード2を使用し、かつ変換クロック(fAD)は16 MHz以下で使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、変換クロック(fAD)は1~2 MHzとなります。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

発行日:2025年1月8日

表 20 - 6 A/D 変換時間の選択 (2/11)

(2) A/D 電源安定待ち時間なし低電圧モード 1.2

(ソフトウェア・トリガ・ノーウエイト・セレクト・モード∕ハードウェア・トリガ・ノーウエイト・セレクト・モード)

|            |                            | -   | Eード<br>Eード |     |     |      |                     |             |             |                       | (変換制      | 始遅延時                      | A/D変換<br>間+変換時間           |                 | み出力遅延                                 | 時間)              |

|------------|----------------------------|-----|------------|-----|-----|------|---------------------|-------------|-------------|-----------------------|-----------|---------------------------|---------------------------|-----------------|---------------------------------------|------------------|

| (AD<br>M1) |                            | (   | ADM0       | )   |     | モード  | 変換<br>クロック<br>(fAD) | 変換開始遅延クロック数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |           | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V |                 | 2.4 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V |                  |

| ADL<br>SP  | FR2                        | FR1 | FR0        | LV1 | LV0 |      |                     |             |             |                       |           | fclk =<br>1 MHz           | fclk =<br>4 MHz           | fclk =<br>8 MHz | fclk =<br>16 MHz                      | fclk =<br>32 MHz |

| 0          | 0                          | 0   | 0          | 1   | 0   | 低電圧1 | fclk/32             | 1 fAD       | 80 fad      | 1 fAD                 | 2624/fcLK | 設定禁止                      | 設定禁止                      | 設定禁止            | 設定禁止                                  | 82 µs            |

| 0          | 0                          | 0   | 1          |     |     |      | fcLk/16             | 1 fAD       | 80 fAD      | 1 fAD                 | 1312/fcLK | 設定禁止                      | 設定禁止                      | 設定禁止            | 82 µs                                 | 41 µs            |

| 0          | DL FR2 FR1 FR0 LV1 0 0 0 1 |     |            |     |     |      | fclk/8              | 1 fAD       | 80 fAD      | 1 fAD                 | 656/fclk  | 設定禁止                      | 設定禁止                      | 82 µs           | 41 µs                                 | 20.5 µs          |

| 1 | 0  | 1  | 1 |  | fcLk/4 | 1 fAD | 107 fAD | 1 fAD | 436/fclk | 設定禁止   | 109 µs   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 0 |  | fcLk/2 | 1 fAD | 107 fAD | 1 fAD | 218/fclk | 設定禁止   | 54.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

| 1 | 1  | 0  | 1 |  | fclk   | 1 fAD | 107 fAD | 1 fAD | 109/fclk | 109 µs | 27.25 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        |       |         |       | 設定禁止     |        |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tconv)の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2μs以上 経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、低電圧モード2を使用し、かつ変換クロック(fAD)は16 MHz以下で使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、変換クロック(fAD)は1~2 MHzとなります。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

(p. 1124)

表 20 - 6 A/D 変換時間の選択 (3/11)

(3) A/D 電源安定待ち時間あり標準モード 1, 2

$(ソフトウェア・トリガ・ウエイト・セレクト・モード/ハードウェア・トリガ・ウエイト・セレクト・モード<math>^{21}$ )

| A/D⊐<br>A/D⊐ |     | -   |      |     |     |     | 変換      | A/D電源       |             | 割り込み          | (A/D      | 電源安定待           |                 | 換時間<br>時間+割り辺   | み出力遅延            | 時間)              |

|--------------|-----|-----|------|-----|-----|-----|---------|-------------|-------------|---------------|-----------|-----------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1)   |     | (   | ADM0 | )   |     | モード | クロック    | 安定待ち        | 変換<br>クロック数 | 出力遅延<br>クロック数 |           |                 | 2.4 V ≦ A       | WREFP≦VD        | D ≦ 5.5 V        |                  |

| ADL<br>SP    | FR2 | FR1 | FR0  | LV1 | LV0 |     |         | , , , , , , |             | 注2            |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0            | 0   | 0   | 0    | 0   | 0   | 標準1 | fclk/32 | 4 fAD       | 64 fAD      | 4 fAD         | 2304/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 72 µs            |

| 0            | 0   | 0   | 1    |     |     |     | fCLK/16 | 4 fAD       | 64 fAD      | 4 fAD         | 1152/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 72 µs            | 36 µs            |

| 1 | 1  | 0  | 0 |  | fcLK/2 | 4 fAD | 181 fAD | 4 fAD | 378/fclk | 設定禁止   | 94.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 1 |  | fclk   | 6 fAD | 181 fAD | 4 fAD | 191/fcLK | 191 µs | 47.75 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        |       |         |       | 設力       | E禁止    |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20 6 A/D変換時間の選択 (1/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からの A/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(略)

発行日:2025年1月8日

表 20 - 6 A/D 変換時間の選択 (3/11)

(3) A/D 電源安定待ち時間あり標準モード 1, 2

$(ソフトウェア・トリガ・ウエイト・セレクト・モード/ハードウェア・トリガ・ウエイト・セレクト・モード<math>^{\pm 1}$ )

| A/D ⊐<br>A/D ⊐ |     | -   |      |     |     |     | 変換      | A/D電源       |             | 割り込み  | (A/D      | 電源安定待           | A/D変<br>ち時間+変換  |                 | み出力遅延            | 時間)              |

|----------------|-----|-----|------|-----|-----|-----|---------|-------------|-------------|-------|-----------|-----------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1)     |     | (   | ADM0 | )   |     | モード | クロック    | 安定待ち        | 変換<br>クロック数 |       |           |                 | 2.4 V ≦ A       | VREFP≦VD        | D ≦ 5.5 V        |                  |

| ADL<br>SP      | FR2 | FR1 | FR0  | LV1 | LV0 |     | (11.2)  | , , , , , , |             | 注2    |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0              | 0   | 0   | 0    | 0   | 0   | 標準1 | fcLk/32 | 4 fAD       | 64 fAD      | 4 fAD | 2304/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 72 µs            |

| 0              | 0   | 0   | 1    |     |     |     | fCLK/16 | 4 fAD       | 64 fAD      | 4 fAD | 1152/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 72 µs            | 36 µs            |

| _ |    |    |   |  |        |       |         |       |          |        |          |      |      |      |

|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 0 |  | fcLK/2 | 4 fAD | 181 fAD | 4 fAD | 378/fclk | 設定禁止   | 94.5 µs  | 設定禁止 | 設定禁止 | 設定禁止 |

| 1 | 1  | 0  | 1 |  | fclk   | 6 fAD | 181 fAD | 4 fAD | 191/fcLK | 191 µs | 47.75 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        |       |         |       | 設定       | 2禁止    |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20-6 A/D変換時間の選択 (1/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からのA/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(p. 1125)

表 20 - 6 A/D 変換時間の選択 (4/11)

(4) A/D 電源安定待ち時間あり低電圧モード 1, 2

$(ソフトウェア・トリガ・ウエイト・セレクト・モード/ハードウェア・トリガ・ウエイト・セレクト・モード<math>^{21}$ )

|            | コンバータ・モード・レジスタ0<br>コンバータ・モード・レジスタ1<br>(ADM0)<br>FR2 FR1 FR0 LV1 LV0 |     |      |     |     |      |                     |                        |             |                             | (A/D¶      | 電源安定待ち          | A/D変<br>時間+変換   | 換時間<br>時間+割り辺   | 込み出力遅延           | 時間)                          |

|------------|---------------------------------------------------------------------|-----|------|-----|-----|------|---------------------|------------------------|-------------|-----------------------------|------------|-----------------|-----------------|-----------------|------------------|------------------------------|

| (AD<br>M1) |                                                                     | (   | ADM0 | )   |     | モード  | 変換<br>クロック<br>(fAD) | A/D電源<br>安定待ち<br>クロック数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数<br>注2 | 登   AVREFP |                 |                 |                 |                  | 2.7 V ≦ AVREFP ≦ VDD ≦ 5.5 V |

| ADL<br>SP  | FR2                                                                 | FR1 | FR0  | LV1 | LV0 |      |                     |                        |             |                             |            | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz             |

| 0          | 0                                                                   | 0   | 0    | 1   | 0   | 低雪圧1 | fcl k/32            | 4 fAD                  | 80 fAD      | 4 fAD                       | 2816/fcLK  | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 88 µs                        |

| I | 1 | 1  | 0  | 0 |   |  | fcLK/2 | 4 fAD | 107 fAD | 4 fAD | 230/fcLK | 設定禁止   | 57.5 μs  | 設定禁止 | 設定禁止 | 設定禁止 |

|---|---|----|----|---|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

|   | 1 | 1  | 0  | 1 |   |  | fCLK   | 6 fAD | 107 fAD | 4 fAD | 117/fcLK | 117 µs | 29.25 μs | 設定禁止 | 設定禁止 | 設定禁止 |

| Г |   | 上記 | 以外 |   | ] |  |        |       |         |       | 設定       | 禁止     |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20-6 A/D変換時間の選択 (2/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からの A/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(略)

発行日:2025年1月8日

表 20 - 6 A/D 変換時間の選択 (4/11)

(4) A/D 電源安定待ち時間あり低電圧モード 1, 2

$(ソフトウェア・トリガ・ウエイト・セレクト・モード/ハードウェア・トリガ・ウエイト・セレクト・モード<math>^{\pm 1}$ )

| A/D⊐<br>A/D⊐ |                        |   |      |   |     |      |                     |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | (A/D¶     | 電源安定待ち          | A/D変<br>時間+変換   | 換時間<br>時間+割り辺   | 込み出力遅延           | 時間)                          |

|--------------|------------------------|---|------|---|-----|------|---------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-----------------|-----------------|-----------------|------------------|------------------------------|

| (AD<br>M1)   |                        | ( | ADM0 | ) |     | モード  | 変換<br>クロック<br>(fAD) | A/D電源<br>安定待ち<br>クロック数 | D電源 変換 出力遅延 $AVREFP \le AVREFP S AVREF$ |       |           |                 |                 |                 |                  | 2.7 V ≦ AVREFP ≦ VDD ≦ 5.5 V |

| ADL<br>SP    | FR2   FR1   FR0     V1 |   |      |   | LV0 |      |                     |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz             |

| 0            | 0                      | 0 | 0    | 1 | 0   | 任雪圧1 | fci k/32            | 4 fAD                  | 80 fad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 fAD | 2816/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 88 µs                        |

| 1 | 1  | 0  | 0 | 1 |  | fcLK/2 | 4 fAD | 107 fAD | 4 fAD | 230/fcLK | 設定禁止   | 57.5 μs  | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 1 |   |  | fCLK   | 6 faD | 107 fAD | 4 fAD | 117/fcLK | 117 µs | 29.25 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |   |  |        |       |         |       | 設定       | 禁止     |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20 6 A/D変換時間の選択 (2/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態(ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してください。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からのA/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(p. 1126)

表 20 - 6 A/D 変換時間の選択 (5/11)

(5) A/D 電源安定待ち時間なし標準モード 1, 2

(ソフトウェア・トリガ・ノーウエイト・スキャン・モード∕ハードウェア・トリガ・ノーウエイト・ スキャン・モード)

|            |     |     | モード<br>モード |     |     |     | **                  | ÷45-8844.78 |             | dal i i sa a.         | (変換開       | 始遅延時間             |                 | 換時間<br>引×4+割り   | 込み出力遅            | 延時間)             |

|------------|-----|-----|------------|-----|-----|-----|---------------------|-------------|-------------|-----------------------|------------|-------------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1) |     | (   | (ADM0      | )   |     | モード | 変換<br>クロック<br>(fAD) | 変換開始遅延クロック数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |            |                   | 2.4 V≦          | AVREFP≦\        | /DD≦5.5 V        |                  |

| ADL<br>SP  | FR2 | FR1 | FR0        | LV1 | LV0 |     | (1/10)              | **          |             | 7 - 7 7 55            |            | fclk =<br>1 MHz   | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0          | 0   | 0   | 0          | 0   | 0   | 標準1 | fclk/32             | 1 fAD       | 64 fAD      | 1 fAD                 | 8256/fcLK  | 設定禁止              | 設定禁止            | 設定禁止            | 設定禁止             | 258 µs           |

| 0          | 0   | 0   | 1          |     |     |     | fcLk/16             | 1 fAD       | 64 fAD      | 1 fAD                 | 4128/fclk  | 設定禁止              | 設定禁止            | 設定禁止            | 258 µs           | 129 µs           |

| 0          | 0   | 1   | 0          |     |     |     | fclk/8              | 1 fAD       | 64 fAD      | 1 fAD                 | 2064/fclk  | BATEFALL BATEFALL |                 |                 |                  | 64.5 µs          |

|            |     |     |            |     |     |     |                     |             |             | 4.615                 | 2004/for K | 50 etc 44 1       | 700             | 50 min 44 1     | 50               | an charte        |

| Τ | 1 | 1  | 0  | 0 |  | fclk/2 | 1 fAD | 181 fAD | 1 fAD | 1452/ICEK | 設定業正   | 303 µS   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|---|----|----|---|--|--------|-------|---------|-------|-----------|--------|----------|------|------|------|

| Г | 1 | 1  | 0  | 1 |  | fCLK   | 1 fAD | 181 fAD | 1 fAD | 726/fcLK  | 726 µs | 181.5 µs | 設定禁止 | 設定禁止 | 設定禁止 |

| Γ |   | 上記 | 以外 |   |  |        |       |         |       | 設定禁止      | E      |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、標準モード2を使用してください。

- 注意5.+側の基準電圧に内部基準電圧を選択したときは、標準モード1,2は使用できません。低電圧モード1,2を使用してください。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

発行日:2025年1月8日

表 20 - 6 A/D 変換時間の選択 (5/11)

(5) A/D 電源安定待ち時間なし標準モード 1, 2

(ソフトウェア・トリガ・ノーウエイト・スキャン・モード∕ハードウェア・トリガ・ノーウエイト・ スキャン・モード)

|            |     |     | モード<br>モード |     |     |     | ±#                  | ****************    |             | dal i i i a           | (変換開       | 始遅延時間           |                 | 換時間<br>間×4+割り   | 込み出力遅            | 延時間)             |

|------------|-----|-----|------------|-----|-----|-----|---------------------|---------------------|-------------|-----------------------|------------|-----------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1) |     | (   | (ADM0      | )   |     | モード | 変換<br>クロック<br>(fAD) | 変換開始遅<br>延クロック<br>数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |            |                 | 2.4 V≦          | AVREFP≦∖        | /DD≦5.5 V        |                  |

| ADL<br>SP  | FR2 | FR1 | FR0        | LV1 | LV0 |     | (11.07)             | ~                   |             | , - , , m             |            | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0          | 0   | 0   | 0          | 0   | 0   | 標準1 | fclk/32             | 1 fAD               | 64 fAD      | 1 fAD                 | 8256/fcLK  | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 258 µs           |

| 0          | 0   | 0   | 1          |     |     |     | fcLk/16             | 1 fAD               | 64 fAD      | 1 fAD                 | 4128/fcLK  | 設定禁止            | 設定禁止            | 設定禁止            | 258 µs           | 129 µs           |

| 0          | 0   | 1   | 0          |     |     |     | fclk/8              | 1 fAD               | 64 fAD      | 1 fAD                 | 2064/fclk  | 設定禁止            | 設定禁止            | 258 µs          | 129 µs           | 64.5 µs          |

|            |     |     |            | 1   |     |     |                     |                     | 1016        | 4.610                 | 2004/foliv | <b>6ル☆**・</b> L | 726 uc          | 6几m ** . L      | 60cc ** . L      | en en en         |

| 1 | 1  | 0  | 0 |  | fclk/2 | 1 fAD | 181 fAD | 1 fAD | 1452/ICLK | 設定禁止   | 303 μs   | 設走崇正 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|---------|-------|-----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 1 |  | fCLK   | 1 fAD | 181 fAD | 1 fAD | 726/fcLK  | 726 µs | 181.5 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        |       |         |       | 設定禁止      | Ł      |          |      |      |      |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態(ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、標準モード2を使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、標準モード1, 2は使用できません。低電圧モード1, 2を使用してください。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

(p. 1127)

1 | 1 | 0 |

上記以外

表 20 - 6 A/D 変換時間の選択 (6/11)

(6) A/D電源安定待ち時間なし低電圧モード1, 2

(ソフトウェア・トリガ・ノーウエイト・スキャン・モード/ハードウェア・トリガ・ノーウエイト・スキャン・モード)

|            |     |        | モード<br>モード |     |     |      |                     |                     |             |                       | (変換開始      | 台遅延時間・                                | A/D変換<br>►変換時間>           |                                    | み出力遅延                                 | 正時間)             |

|------------|-----|--------|------------|-----|-----|------|---------------------|---------------------|-------------|-----------------------|------------|---------------------------------------|---------------------------|------------------------------------|---------------------------------------|------------------|

| (AD<br>M1) |     | (ADM0) |            |     |     | モード  | 変換<br>クロック<br>(fAD) | 変換開始遅<br>延クロック<br>数 | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数 |            | 1.6 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V | 1.8 V≦<br>AVREFP≦<br>VDD≦<br>5.5 V | 2.4 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V |                  |

| ADL<br>SP  | FR2 | FR1    | FR0        | LV1 | LV0 |      |                     |                     |             |                       |            | fclk =<br>1 MHz                       | fclk =<br>4 MHz           | fclk =<br>8 MHz                    | fclk =<br>16 MHz                      | fclk =<br>32 MHz |

| 0          | 0   | 0      | 0          | 1   | 0   | 低電圧1 | fcLK/32             | 1 fAD               | 80 fad      | 1 fAD                 | 10304/fcLK | 設定禁止                                  | 設定禁止                      | 設定禁止                               | 設定禁止                                  | 322 µs           |

| 0          | 0   | 0      | 1          |     |     |      | fcLk/16             | 1 fAD               | 80 fAD      | 1 fAD                 | 5152/fcLK  | 設定禁止                                  | 設定禁止                      | 設定禁止                               | 322 µs                                | 161 µs           |

| 0          | 0   | 1      | 0          |     |     |      | fclk/8              | 1 fAD               | 80 fAD      | 1 fAD                 | 2576/fclk  | 設定禁止                                  | 設定禁止                      | 322 µs                             | 161 µs                                | 80.5 µs          |

|            |     |        |            |     |     |      |                     |                     |             |                       |            |                                       | 400                       |                                    |                                       |                  |

| 1          | 1   | 0      | 0          |     |     |      | fclk/2              | 1 fAD               | 107 fAD     | 1 fAD                 | 860/fCLK   | 設定禁止                                  | 215 µS                    | 設定禁止                               | 設定禁止                                  | 設定禁止             |

注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

107 fAD

430/fclk

設定禁止

430 µs 107.5 µs 設定禁止 設定禁止 設定禁止

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、低電圧モード2を使用し、かつ変換クロック(fAD)は16 MHz以下で使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、変換クロック(fAD)は1~2 MHzとなります。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

発行日:2025年1月8日

表 20 - 6 A/D 変換時間の選択 (6/11)

(6) A/D電源安定待ち時間なし低電圧モード1, 2

(ソフトウェア・トリガ・ノーウエイト・スキャン・モード∕ハードウェア・トリガ・ノーウエイト・スキャン・モード)

| A/D⊐<br>A/D⊐ |                                       |     |     |     |     |      |                     |                     |         |                       | (変換開如      | 台遅延時間+                    | A/D変掺<br>・変換時間>                    |                                       | み出力遅延            | <b>E時間</b> )                          |

|--------------|---------------------------------------|-----|-----|-----|-----|------|---------------------|---------------------|---------|-----------------------|------------|---------------------------|------------------------------------|---------------------------------------|------------------|---------------------------------------|

| (AD<br>M1)   | (ADM0)  FR2 FR1 FR0 LV1 LV  0 0 0 1 ( |     |     |     |     | モード  | 変換<br>クロック<br>(fAD) | 変換開始遅<br>延クロック<br>数 | 変換クロック数 | 割り込み<br>出力遅延<br>クロック数 |            | 1.6 V≦ AVREFP≦ VDD≦ 5.5 V | 1.6 V≦<br>AVREFP≦<br>VDD≦<br>5.5 V | 1.8 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V |                  | 2.7 V ≦<br>AVREFP ≦<br>VDD ≦<br>5.5 V |

| ADL<br>SP    | FR2                                   | FR1 | FR0 | LV1 | LV0 |      |                     |                     |         |                       |            | fclk =<br>1 MHz           | fclk =<br>4 MHz                    | fclk =<br>8 MHz                       | fclk =<br>16 MHz | fclk =<br>32 MHz                      |

| 0            | 0                                     | 0   | 0   | 1   | 0   | 低電圧1 | fcLk/32             | 1 fAD               | 80 fAD  | 1 fAD                 | 10304/fcLK | 設定禁止                      | 設定禁止                               | 設定禁止                                  | 設定禁止             | 322 µs                                |

| 0            | 0                                     | 0   | 1   |     |     |      | fcLk/16             | 1 fAD               | 80 fAD  | 1 fAD                 | 5152/fcLK  | 設定禁止                      | 設定禁止                               | 設定禁止                                  | 322 µs           | 161 µs                                |

| 0            | 0                                     | 1   | 0   |     |     |      | fclk/8              | 1 fAD               | 80 fAD  | 1 fAD                 | 2576/fclk  | 設定禁止                      | 設定禁止                               | 322 µs                                | 161 µs           | 80.5 µs                               |

|              |                                       |     |     |     |     |      |                     |                     |         |                       |            |                           | 400                                |                                       |                  |                                       |

| 1            | 1                                     | 0   | 0   |     |     |      | fclk/2              | 1 fAD               | 107 fAD | 1 fAD                 | 860/fclk   | 設定禁止                      | 215 µs                             | 設定禁止                                  | 設定禁止             | 設定禁止                                  |

| 1            | 1                                     | 0   | 1   |     |     |      | fclk                | 1 fAD               | 107 fAD | 1 fAD                 | 430/fclk   | 430 µs                    | 107.5 µs                           | 設定禁止                                  | 設定禁止             | 設定禁止                                  |

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. 変換対象に内部基準電圧、または温度センサ出力電圧を選択したときは、低電圧モード2を使用し、かつ変換クロック(fAD)は16 MHz以下で使用してください。

- 注意5. +側の基準電圧に内部基準電圧を選択したときは、変換クロック (fAD) は1~2 MHzとなります。

備考 fclk: CPU/周辺ハードウェア・クロック周波数

(p. 1128)

表20 - 6 A/D変換時間の選択 (7/11)

(7) A/D電源安定待ち時間あり標準モード1,2

(ソフトウェア・トリガ・ウエイト・スキャン・モード∕ハードウェア・トリガ・ウエイト・スキャン・モード<sup>±1</sup>)

|            | (ADM0) せート グロック 安定符ち (fAD) クロック数 |     |     |     |     |     |                                         |       |             | 割り込み          | (A/D電     | 源安定待ち           |                 | 換時間<br>間×4+割り   | 込み出力遅            | 延時間)             |

|------------|----------------------------------|-----|-----|-----|-----|-----|-----------------------------------------|-------|-------------|---------------|-----------|-----------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1) | (ADM0)                           |     |     |     |     | モード | クロック                                    | 安定待ち  | 変換<br>クロック数 | 出力遅延<br>クロック数 |           |                 | 2.4 V ≦ A       | VREFP≦VDI       | o ≦ 5.5 V        |                  |

| ADL<br>SP  | FR2                              | FR1 | FR0 | LV1 | LV0 |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | , , , |             | 注2            |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0          | 0 0 0 0                          |     |     |     | 0   | 標準1 | fcLK/32                                 | 4 fAD | 64 fad      | 4 fAD         | 8448/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 264 µs           |

| 0          | 0                                | 0   | 1   |     |     |     | fclk/16                                 | 4 fAD | 64 fAD      | 4 fAD         | 4224/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 264 µs           | 132 µs           |

| _ |   |    |    |   |  |      |       |         |       |          |        |          |      |      |      |

|---|---|----|----|---|--|------|-------|---------|-------|----------|--------|----------|------|------|------|

| I | 1 | 1  | 0  | 1 |  | fCLK | 6 fAD | 181 fAD | 4 fAD | 734/fcLK | 734 µs | 183.5 µs | 設定禁止 | 設定禁止 | 設定禁止 |

| Γ |   | 上記 | 以外 |   |  |      |       |         |       | 設定       | 禁止     |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20-6 A/D変換時間の選択 (1/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からの A/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(略)

発行日:2025年1月8日

表20 - 6 A/D変換時間の選択 (7/11)

(7) A/D電源安定待ち時間あり標準モード1,2

(ソフトウェア・トリガ・ウエイト・スキャン・モード/ハードウェア・トリガ・ウエイト・スキャン・モード<sup>±1</sup>)

| A/D⊐<br>A/D⊐ |                          |     |     |     |     |     | 亦協                                      | A/D電源     |             | 割り込み          | (A/D電     | 源安定待ち           |                 | 換時間<br>間×4+割り   | 込み出力遅る           | 正時間)             |

|--------------|--------------------------|-----|-----|-----|-----|-----|-----------------------------------------|-----------|-------------|---------------|-----------|-----------------|-----------------|-----------------|------------------|------------------|

| (AD<br>M1)   | 1) (ADM0) モード クロック (fAD) |     |     |     |     |     | クロック                                    | 安定待ち      | 変換<br>クロック数 | 出力遅延<br>クロック数 |           |                 | 2.4 V ≦ A       | VREFP≦VD        | D ≦ 5.5 V        |                  |

| ADL<br>SP    | FR2                      | FR1 | FR0 | LV1 | LV0 |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | , - , , , |             | 注2            |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0            | 0                        | 0   | 0   | 0   | 0   | 標準1 | fcLK/32                                 | 4 fAD     | 64 fad      | 4 fAD         | 8448/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 264 µs           |

| 0            | 0                        | 0   | 1   |     |     |     | fcLK/16                                 | 4 fAD     | 64 fAD      | 4 fAD         | 4224/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 264 µs           | 132 µs           |

| 1 |   | 1  | 0  | 1 |  | fclk | 6 fAD | 181 fAD | 4 fAD | 734/fcLK | 734 µs | 183.5 µs | 設定禁止 | 設定禁止 | 設定禁止 |

|---|---|----|----|---|--|------|-------|---------|-------|----------|--------|----------|------|------|------|

|   | _ | 上記 | 以外 |   |  |      |       |         |       | 設定       | 禁止     |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20 6 A/D変換時間の選択 (1/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からのA/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(p. 1129)

表20 - 6 A/D変換時間の選択 (8/11)

(8) A/D電源安定待ち時間あり低電圧モード1, 2

(ソフトウェア・トリガ・ウエイト・スキャン・モード/ハードウェア・トリガ・ウエイト・スキャン・モード<sup>注1</sup>)

|            |                                       | (ADMO) モード クロック 安定待ち クロック数 クロック数 クロック |     |     |     |     |             |                             |        |                              | (A/D電                        | [源安定待ち]                      |                              | 換時間<br>:間×4+割り               | 込み出力遅            | 延時間)             |

|------------|---------------------------------------|---------------------------------------|-----|-----|-----|-----|-------------|-----------------------------|--------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------|------------------|

| (AD<br>M1) | (ADMO) モード クロック 安定待ち クロック (fAD) クロック数 |                                       |     |     |     |     | 変換<br>クロック数 | 割り込み<br>出力遅延<br>クロック数<br>注2 |        | 1.6 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 1.6 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 1.8 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 2.4 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 2.7 V ≦ AVREFP ≦ VDD ≦ 5.5 V |                  |                  |

| ADL<br>SP  | FR2                                   | FR1                                   | FR0 | LV1 | LV0 |     |             |                             |        |                              |                              | fclk =<br>1 MHz              | fclk =<br>4 MHz              | fclk =<br>8 MHz              | fclk =<br>16 MHz | fclk =<br>32 MHz |

| 0          | 0                                     | 0                                     | 0   | 1   | 0   | 低電圧 | fclk/32     | 4 fAD                       | 80 fad | 4 fAD                        | 10496/fcLK                   | 設定禁止                         | 設定禁止                         | 設定禁止                         | 設定禁止             | 328 µs           |

| 0          | 0                                     | 0                                     | 1   |     |     | 1   | fcLk/16     | 4 fAD                       | 80 fad | 4 fAD                        | 5248/fclk                    | 設定禁止                         | 設定禁止                         | 設定禁止                         | 328 µs           | 164 µs           |

| 0          | 0                                     | 1                                     | 0   |     |     |     | fcLK/8      | 6 fad                       | 80 fad | 4 fAD                        | 2640/fcLK                    | 設定禁止                         | 設定禁止                         | 330 µs                       | 165 µs           | 82.5 µs          |

| 1 | 1  | 0  | 0 |  | fclk/2 | 4 fAD | 107 fAD | 4 fAD | 872/fCLK | 設定禁止   | 218 µS   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1  | 0  | 1 |  | fclk   | 6 fad | 107 faD | 4 fAD | 438/fclk | 438 µs | 109.5 μs | 設定禁止 | 設定禁止 | 設定禁止 |

|   | 上記 | 以外 |   |  |        |       |         |       | . 設定     | ≧禁止    |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20 6 A/D変換時間の選択 (2/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からのA/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(略)

発行日:2025年1月8日

表20 - 6 A/D変換時間の選択 (8/11)

(8) A/D電源安定待ち時間あり低電圧モード1.2

(ソフトウェア・トリガ・ウエイト・スキャン・モード/ハードウェア・トリガ・ウエイト・スキャン・モード<sup>注1</sup>)

|            |     | -タ・ <del>1</del><br>-タ・ <del>1</del> |     |     |     |     |         |       |                             |       | (A/D電                        | [源安定待ち                       |                              | 換時間<br>:間×4+割り               | 込み出力遅                     | 延時間)             |

|------------|-----|--------------------------------------|-----|-----|-----|-----|---------|-------|-----------------------------|-------|------------------------------|------------------------------|------------------------------|------------------------------|---------------------------|------------------|

| (AD<br>M1) |     | 変数 AD 電源 変換 出対 クロック 変換 クロック数 クロック数   |     |     |     |     |         |       | 割り込み<br>出力遅延<br>クロック数<br>注2 |       | 1.6 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 1.6 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 1.8 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 2.4 V ≦ AVREFP ≦ VDD ≦ 5.5 V | 2.7 V≦ AVREFP≦ VDD≦ 5.5 V |                  |

| SP         | FR2 | FR1                                  | FR0 | LV1 | LV0 |     |         |       |                             |       |                              | fclk =<br>1 MHz              | fclk =<br>4 MHz              | fclk =<br>8 MHz              | fclk =<br>16 MHz          | fclk =<br>32 MHz |

| 0          | 0   | 0                                    | 0   | 1   | 0   | 低電圧 | fclk/32 | 4 fAD | 80 fad                      | 4 fAD | 10496/fcLK                   | 設定禁止                         | 設定禁止                         | 設定禁止                         | 設定禁止                      | 328 µs           |

| 0          | 0   | 0                                    | 1   |     |     | 1   | fcLk/16 | 4 fAD | 80 fad                      | 4 fAD | 5248/fcLK                    | 設定禁止                         | 設定禁止                         | 設定禁止                         | 328 µs                    | 164 µs           |

| 0          | 0   | 1                                    | 0   |     |     |     | fclk/8  | 6 fad | 80 fad                      | 4 fAD | 2640/fcLK                    | 設定禁止                         | 設定禁止                         | 330 µs                       | 165 µs                    | 82.5 µs          |

| T | 1 | 1  | 0  | 0 |  | fcLk/2 | 4 fAD | 107 fAD | 4 fAD | 872/fclk | 設定禁止   | 218 µs   | 設定禁止 | 設定禁止 | 設定禁止 |

|---|---|----|----|---|--|--------|-------|---------|-------|----------|--------|----------|------|------|------|

| 1 | 1 | 1  | 0  | 1 |  | fclk   | 6 fAD | 107 fAD | 4 fAD | 438/fcLK | 438 µs | 109.5 µs | 設定禁止 | 設定禁止 | 設定禁止 |

| Į |   | 上記 | 以外 |   |  |        |       |         |       | 設定       | 禁止     |          |      |      |      |

- 注1. 連続変換モードの2回目以降と、スキャン・モードのスキャン1以降の変換では、ハードウェア・トリガ検出後に、変換起動時間やA/D電源安定待ち時間は発生しません(表20 6 A/D変換時間の選択(2/11)参照)。

- 注2. ワンショット変換モード時の割り込み出力遅延クロック数です。連続変換モードを選択した場合は、変換クロック (fAD) の3クロック分短くなります。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック(fAD)と変換時間(tCONV)の範囲内で選択してください。なお、変換時間(tCONV)は A/D電源安定待ち時間を含みません。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。 なお、変換待機状態/変換動作状態から変換停止状態にした場合は、変換停止状態で0.2µs以上経過したあとにFR2-FR0, LV1, LV0ビットを設定してください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してく ださい。

- 注意4. ハードウェア・トリガ・ウエイト・モード時の変換時間は、ハードウェア・トリガ検出からのA/D電源安定待ち時間を含みます。

ソフトウェア・トリガ・ウエイト・モード時の変換時間は、ADCS = 1からのA/D電源安定待ち時間を含みます。

(p. 1130)

表 20 - 6 A/D 変換時間の選択 (9/11)

(9) A/D 電源安定待ち時間なし標準モード1 (ANIO-7 が対象のケース)

(アドバンスド・モード)

|            |      | -タ・ <del>-</del><br>-タ・ <del>-</del> |      |     |     |     |                     |             |                  |                           |           | (変換開始)          |                 | VD変換時間+書        |                  | 力遅延時間)           | )                       |

|------------|------|--------------------------------------|------|-----|-----|-----|---------------------|-------------|------------------|---------------------------|-----------|-----------------|-----------------|-----------------|------------------|------------------|-------------------------|

| (AD<br>M1) |      | (                                    | ADM0 | )   |     | モード | 変換<br>クロック<br>(fAD) | 変換開始遅延クロック数 | 変換<br>クロック<br>数注 | 割り込み<br>出力遅延<br>クロック<br>数 |           |                 | 2.4 \           | /≦VDD≦          | 5.5 V            |                  | 2.7 V≦<br>VDD≦<br>5.5 V |

| ADL<br>SP  | FR2  | FR1                                  | FR0  | LV1 | LV0 |     |                     | ~           |                  | *                         |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz | fclk =<br>16 MHz | fclk =<br>32 MHz | fclk =<br>48 MHz        |

| 0          | 0    | 0                                    | 0    | 0   | 0   | 標準1 | fclk/32             | 1 fAD       | 41 fAD           | 1 fAD                     | 1376/fcLK | 設定禁止            | 設定禁止            | 設定禁止            | 設定禁止             | 43 µs            | 28.667 μs               |

| 0          | 0    | 0                                    | 1    |     |     |     | fcLk/16             | 1 fAD       | 41 fAD           | 1 fAD                     | 688/fcLK  | 設定禁止            | 設定禁止            | 設定禁止            | 43 µs            | 21.5 µs          | 14.333 µs               |

| 0          | 0    | 1                                    | 0    |     |     |     | fclk/8              | 1 fAD       | 41 fAD           | 1 fAD                     | 344/fclk  | 設定禁止            | 設定禁止            | 43 µs           | 21.5 µs          | 10.75 µs         | 7.1667 µs               |

| 0          | 0    | 1                                    | 1    |     |     |     | fclk/4              | 1 fAD       | 41 fAD           | 1 fAD                     | 172/fcLK  | 設定禁止            | 設定禁止            | 21.5 µs         | 10.75 µs         | 5.375 µs         | 3.5833 µs               |

| 0          | 1    | 0                                    | 0    |     |     |     | fclk/2              | 1 fAD       | 41 fAD           | 1 fAD                     | 86/fclk   | 設定禁止            | 設定禁止            | 10.75 µs        | 5.375 µs         | 2.6875 µs        | 1.7917 µs               |

| 0          | 1    | 0                                    | 1    |     |     |     | fCLK                | 1 fAD       | 41 fAD           | 1 fAD                     | 43/fclk   | 設定禁止            | 設定禁止            | 5.375 µs        | 2.6875 µs        | 1.3438 µs        | 0.8958 µs               |

| 1          | 0    | 1                                    | 1    |     |     |     | fclk/4              | 1 fAD       | 41 fAD           | 1 fAD                     | 172/fcLK  | 設定禁止            | 43 µs           | 設定禁止            | 設定禁止             | 設定禁止             | 設定禁止                    |

| 1          | 1    | 0                                    | 0    |     |     |     | fclk/2              | 1 fAD       | 41 fAD           | 1 fAD                     | 86/fclk   | 設定禁止            | 21.5 µs         | 設定禁止            | 設定禁止             | 設定禁止             | 設定禁止                    |

| 1          | 1    | 0                                    | 1    |     |     |     | fclk                | 1 fAD       | 41 fAD           | 1 fAD                     | 43/fclk   | 43 µs           | 10.75 µs        | 設定禁止            | 設定禁止             | 設定禁止             | 設定禁止                    |

|            | 上記以外 |                                      |      |     |     |     |                     |             |                  |                           |           | 設定禁止            |                 |                 |                  |                  |                         |

- 注 ADSPMODレジスタのADSPMOD[1:0]に01Bを設定した状態での変換クロック数を示します。

- 注意1. A/D変換時間は、43.6.1 A/Dコンバータ特性または44.6.1 A/Dコンバータ特性に示す変換クロック (fAD) と変換時間 (tCONV) の範囲内で選択してください。

- 注意2. FR2-FR0, LV1, LV0ビットを同一データ以外に書き換える場合は、変換停止状態 (ADCS = 0, ADCE = 0) で行ってください。

- 注意3. 変換時間は変換起動時間を含みません。1回目の変換では、変換起動時間を加算してください。 上記起動時間は競合がない状態を示します。競合時の起動時間については、図20 - 5の注2の説明 を参照してください。

また変換時間は、クロック周波数の誤差を含みません。誤差を考慮して、変換時間を選択してください。

注意4. 同時サンプリングを実施する場合は、以下の条件で行ってください。

ADLSP = 0, FR2-FR0 = 100, LV1-LV0 = 00, fclk $\ge$ 32 MHz, VDD  $\ge$  2.7 V ADLSP = 0, FR2-FR0 = 101, LV1-LV0 = 00, fclk $\ge$ 16 MHz, VDD  $\ge$  2.7 V

備考 fclk: CPU/周辺ハードウェア・クロック周波数

発行日: 2025年1月8日

表 20 - 6 A/D 変換時間の選択 (9/11)

(9) A/D 電源安定待ち時間なし標準モード 1 (ANIO-7 が対象のケース)

(アドバンスド・モード)

| A/D⊐<br>A/D⊐ |      | -   |      |     |     |     |                     |             |                  |                           |           | (変換開始)          |                 | VD変換時間<br>を換時間+書 | 間<br>削り込み出り      | 力遅延時間)           | 1                       |

|--------------|------|-----|------|-----|-----|-----|---------------------|-------------|------------------|---------------------------|-----------|-----------------|-----------------|------------------|------------------|------------------|-------------------------|

| (AD<br>M1)   |      | (   | ADM0 | )   |     | モード | 変換<br>クロック<br>(fAD) | 変換開始遅延クロック数 | 変換<br>クロック<br>数注 | 割り込み<br>出力遅延<br>クロック<br>数 |           |                 | 2.4 \           | /≦VDD≦           | 5.5 V            |                  | 2.7 V≦<br>VDD≦<br>5.5 V |

| ADL<br>SP    | FR2  | FR1 | FR0  | LV1 | LV0 |     |                     | **          |                  | **                        |           | fclk =<br>1 MHz | fclk =<br>4 MHz | fclk =<br>8 MHz  | fclk =<br>16 MHz | fclk =<br>32 MHz | fclk =<br>48 MHz        |

| 0            | 0    | 0   | 0    | 0   | 0   | 標準1 | fclk/32             | 1 fAD       | 41 fAD           | 1 fAD                     | 1376/fcLK | 設定禁止            | 設定禁止            | 設定禁止             | 設定禁止             | 43 µs            | 28.667 μs               |