|      |                                                                                             |                               |                      | <u> </u>                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------|-------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                             |                               | 発行番号                 | ZBG-CC-09-0009号 1/2                                                                                                                                |

|      | 技術通知                                                                                        |                               | 発行日                  | 2009 年 4 月 23 日                                                                                                                                    |

| 78   | <br>8K0R/Kx3 マイクロコ                                                                          | ントローラ                         | 発行元                  | NEC エレクトロニクス株式会社<br>マイクロコンピュータ事業本部<br>汎用マイコンシステム事業部<br>製品ソリューショングルーズ<br>(田                                                                         |

| 文書分類 | <b>使用制限事項</b>                                                                               | バージョン・ア                       | ップ                   | ドキュメント誤記訂正 その他                                                                                                                                     |

| 関連資料 | 78KOR/KE3 ユーザース<br>78KOR/KF3 ユーザース<br>78KOR/KG3 ユーザース<br>78KOR/KH3 ユーザース<br>78KOR/KJ3 ユーザース | 、・マニュアル<br>、・マニュアル<br>、・マニュアル | 資料番号<br>資料番号<br>資料番号 | 計: U17854JJ8V0UD00 (第 8 版)<br>計: U17893JJ7V0UD00 (第 7 版)<br>計: U17894JJ8V0UD00 (第 8 版)<br>計: U18432JJ4V0UD00 (第 4 版)<br>計: U18417JJ3V0UD00 (第 3 版) |

#### 1. 対象製品

78KOR/Kx3 マイクロコントローラ全製品:

78KOR/KE3:  $\mu$ PD78F1142,  $\mu$ PD78F1143,  $\mu$ PD78F1144,  $\mu$ PD78F1145,  $\mu$ PD78F1146

$\mu$ PD78F1142A,  $\mu$ PD78F1143A,  $\mu$ PD78F1144A,  $\mu$ PD78F1145A,  $\mu$ PD78F1146A

78K0R/KF3:  $\mu$  PD78F1152,  $\mu$  PD78F1153,  $\mu$  PD78F1154,  $\mu$  PD78F1155,  $\mu$  PD78F1156

$\mu$ PD78F1152A,  $\mu$ PD78F1153A,  $\mu$ PD78F1154A,  $\mu$ PD78F1155A,  $\mu$ PD78F1156A

78KOR/KG3:  $\mu$  PD78F1162,  $\mu$  PD78F1163,  $\mu$  PD78F1164,  $\mu$  PD78F1165,  $\mu$  PD78F1166,  $\mu$  PD78F1167,  $\mu$  PD78F1168

$\mu$ PD78F1162A,  $\mu$ PD78F1163A,  $\mu$ PD78F1164A,  $\mu$ PD78F1165A,  $\mu$ PD78F1166A,  $\mu$ PD78F1167A,  $\mu$ PD78F1168A

78K0R/KH3:  $\mu$ PD78F1174,  $\mu$ PD78F1175,  $\mu$ PD78F1176,  $\mu$ PD78F1177,  $\mu$ PD78F1178

$\mu$  PD78F1174A,  $\mu$  PD78F1175A,  $\mu$  PD78F1176A,  $\mu$  PD78F1177A,  $\mu$  PD78F1178A

$78K0R/KJ3: \mu PD78F1184A, \mu PD78F1185A, \mu PD78F1186A, \mu PD78F1187A, \mu PD78F1188A$

#### 2. 通知内容

78KOR/Kx3 マイクロコントローラについて、ユーザーズ・マニュアルの誤記訂正と制限事項の追加がございます。

# 【誤記訂正及び制限事項の概要】

◆3線シリアルI/O通信 電気的特性の誤記訂正

#### 誤記訂正事項:

ユーザーズ・マニュアルの3線シリアルI/O通信 電気的特性(AC 特性)の以下の項目に誤記訂正がございます。詳細は別紙5をご参照ください。

- ・ シリアル・アレイ・ユニット(CSIモード) マスタ・モード 同電位通信時

- ・ シリアル・アレイ・ユニット(CSIモード) スレーブ・モード 同電位通信時

- シリアル・アレイ・ユニット(CSIモード) マスタ・モード 異雷位通信時

- ・ シリアル・アレイ・ユニット(CSIモード) スレーブ・モード 異電位通信時

#### 改善計画:

ユーザーズ・マニュアルの次回改版時(2009年5月の予定)に修正いたします。

#### ◆DMA コントローラの応答時間の誤記訂正

## 誤記訂正事項:

ユーザーズ・マニュアル DMA コントローラの章 注意事項のDMA応答時間において誤記訂正がございます。詳細は別紙6をご参照ください。

#### 改善計画:

ユーザーズ・マニュアルの次回改版時(2009年5月の予定)に修正いたします。

#### DMA コントローラの終了に関する制限事項

#### 制限事項内容:

DMA のチャネル 0 の転送トリガ、チャネル 1 の転送トリガ、どちらかのチャネルの転送終了(ソフトウエア による強制終了、転送回数完了による自動終了)が競合した場合、終了しなかったチャネルの DMA 転送が 2 回続けて発生する場合があります。詳細は別紙10をご参照ください。

#### 改善計画:

DMA を強制終了する場合は、両チャネルともに DWAITn ビットをセットして DMA 転送を保留にしてから DSTn0 ビットをクリアしてください。その後、DWAITn ビットをクリアし、保留解除後、DENn ビットをクリアする事で回避可能です。また、自動終了の場合は項目 4 (誤記訂正)の内容に従うことにより回避可能です。本件は制限事項とさせて頂きます。

DMA コントローラの DWAITn ビットによる DMA 転送の保留に関する制限事項制限事項内容:

DMA のチャネル 0、チャネル 1 を同時に使用している場合、片方の DMA を保留にした後(DMC n の DWAIT n ビットをセット)、その保留中に保留したチャネルの転送トリガが発生し、それ以降に保留していないチャネルの転送トリガが発生すると、保留したチャネルの DMA 転送が実行される場合があります。詳細は別紙 1 1 をご参照ください。

#### 改善計画:

DMA のチャネル 0、チャネル 1 の両チャネルを共に使用している時に DMA を保留する場合は、両チャネル共に DWAITn ビットをセットして DMA 転送を保留してください。本件は制限事項とさせて頂きます。

備考 n=0,1

本製品について、上記の誤記訂正と制限事項を含め過去にご報告致しました誤記訂正事項一覧(別紙1)と使用制限事項一覧(別紙2)に示します。

#### 3.発行文書履歴

78K0R/Kx3 技術通知 発行文書履歴

| 文書番号           | 発行日        | 記事                                                                                                                                                      |

|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZBG-CC-07-0021 | 2007年10月1日 | 初版発行                                                                                                                                                    |

| ZBG-CC-08-0009 | 2008年6月19日 | $f_{\text{IH}}$ =8MHz , HALT モード時の電源電流 ( $I_{\text{DD}}$ ) の MAX 値の誤記訂正を追加。                                                                             |

| ZBG-CC-09-0009 | 2009年4月23日 | ・3 線シリアルI/O通信 電気的特性の誤記訂正を追加<br>・DMA コントローラの応答時間の誤記訂正を追加<br>・DMA コントローラの終了に関する制限事項を追加<br>・DMA コントローラの DWAITn ビットによる DMA 転送の保留に<br>関する制限事項を追加<br>(本通知です。) |

# 78K0R/Kx3マイクロコントローラユーザーズ・マニュアル誤記訂正事項一覧

# 1)誤記訂正事項履歴

|    | 内容                                                                                                       | 78K0R/KE3 |             |     | 78K0R/KF  | 3           |     | 78K0R/KG3 |             |     |

|----|----------------------------------------------------------------------------------------------------------|-----------|-------------|-----|-----------|-------------|-----|-----------|-------------|-----|

| 項目 | 版数                                                                                                       | 第6版<br>以前 | 第7版と<br>第8版 | 第9版 | 第5版<br>以前 | 第6版と<br>第7版 | 第8版 | 第6版<br>以前 | 第7版と<br>第8版 | 第9版 |

| 1  | リアルタイム・カウンタの<br>RTCC1 レジスタへの書き込み                                                                         | ×         |             |     | ×         |             |     | ×         |             |     |

| 2  | f <sub>IH</sub> =8MHz HALT モード時の電源<br>電流(I <sub>DD2</sub> )の MAX 値<br>誤: 0.6 mA (MAX)<br>正: 1.2 mA (MAX) | ×         |             |     | ×         |             |     | ×         |             |     |

| 3  | 3 線シリアルI / O通信の<br>電気的特性                                                                                 | ×         | ×           |     | ×         | ×           |     | ×         | ×           |     |

| 4  | DMA コントローラの応答時間                                                                                          | ×         | ×           |     | ×         | ×           |     | ×         | ×           |     |

|    | 内容                                                                                                           |           | 78K0R/KH    | 3   |     | 78K0R/KJ    | 3   |

|----|--------------------------------------------------------------------------------------------------------------|-----------|-------------|-----|-----|-------------|-----|

| 項目 | 版数                                                                                                           | 第2版<br>以前 | 第3版と<br>第4版 | 第5版 | 第1版 | 第2版と<br>第3版 | 第4版 |

| 1  | リアルタイム・カウンタの<br>RTCC1 レジスタへの書き込み                                                                             | ×         |             |     | ×   |             |     |

| 2  | f <sub>IH</sub> =8MHz ,HALT モード時の電源<br>電流 ( I <sub>DD2</sub> ) の MAX 値<br>誤: 0.6 mA (MAX)<br>正: 1.2 mA (MAX) | ×         |             |     | ×   |             |     |

| 3  | 3線シリアルI/O通信の<br>電気的特性                                                                                        | ×         | ×           |     | ×   | ×           |     |

| 4  | DMA コントローラの応答時<br>間                                                                                          | ×         | ×           |     | ×   | ×           |     |

# 備考) 各記号はそれぞれ以下の意味を示します。

x:誤記対象:誤記訂正

# 2)誤記訂正事項の詳細

項目 1:詳細は別紙3をご参照ください。 項目 2:詳細は別紙4をご参照ください。 項目 3:詳細は別紙5をご参照ください。 項目 4:詳細は別紙6をご参照ください。

# 78K0R/Kx3マイクロコントローラ使用制限事項一覧

# 1)使用制限事項履歴

| _ | · / 🗠 | ノリルンアスラッテハダル上                               |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                 |

|---|-------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 項目    | 内容                                          | <ul> <li>KE3: μPD78F1142/F1143/F1144/<br/>F1145/F1146</li> <li>KF3: μPD78F1152/F1153/F1154/<br/>F1155/F1156</li> <li>KG3: μPD78F1162/F1163/F1164/<br/>F1165/F1166/F1167/F1168</li> <li>KH3: μPD78F1174/F1175/F1176/<br/>F1177/F1178</li> </ul> | <ul> <li>ΚΕ3: μPD78F1142A/F1143A/F1144A/<br/>F1145A/F1146A</li> <li>ΚF3: μPD78F1152A/F1153A/F1154A/<br/>F1155A/F1156A</li> <li>ΚG3: μPD78F1162A/F1163A/F1164A/<br/>F1165A/F1166A/F1167A/F1168A</li> <li>ΚH3: μPD78F1174A/F1175A/F1176A/<br/>F1177A/F1178A</li> <li>ΚJ3: μPD78F1184A/F1185A/F1186A/<br/>F1187A/F1188A</li> </ul> |

|   | 1     | クロック出力 / ブザー出力制御回路出力<br>停止時の出力レベルに関する制限     | ×                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                 |

|   | 2     | リアルタイム・カウンタ (RTC)                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                 |

|   | 2-1   | 定周期割り込みとアラーム割り込みの<br>同時使用に関する制限             | ×                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                 |

|   | 2-2   | カウンタ動作停止後の年/月/曜日/日/時/<br>分/秒カウント・レジスタに関する制限 | ×                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                 |

|   | 3     | DMA コントローラ                                  |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                 |

|   | 3-1   | DMA コントローラの終了に関する制限事項                       | ×                                                                                                                                                                                                                                              | ×                                                                                                                                                                                                                                                                                                                               |

|   | 3-2   | DMA コントローラの DWAITn ビットによるDMA 転送の保留に関する制限事項  | ×                                                                                                                                                                                                                                              | ×                                                                                                                                                                                                                                                                                                                               |

## 備考) 各記号はそれぞれ以下の意味を示します。

x:制限事項対象 :制限事項対象外

# 2)使用制限事項の詳細

項目1:詳細は別紙7をご参照ください。

項目2-1:詳細は別紙8をご参照ください。 項目2-2:詳細は別紙9をご参照ください。 項目3-1:詳細は別紙10をご参照ください。 項目3-2:詳細は別紙10をご参照ください。

## 項目 1 (誤記訂正): リアルタイム・カウンタの RTCC1 レジスタへの書き込み

ユーザーズ・マニュアルのリアルタイム・カウンタの章にリアルタイム・カウンタ・コントロール・レジスタ 1 (RTCC1) レジスタの注意事項に誤記訂正がございます。

#### 誤記内容

RTCC1 レジスタについての注意事項で、WAFG フラグもしくはRIFG フラグへの書き込みは1ビット操作命令を使用せずに8ビット操作命令で行うよう記載しておりましたが、WAFG フラグおよびRIFG フラグだけでなく、本レジスタの他のビットに対しても、書き込みを行う場合は8ビット操作命令で行ってください。

- 誤)注意 WAFG フラグに 1 ビット操作命令で書き込みを行うと, RIFG フラグがクリアされることがあります。そのため, WAFG フラグに書き込みを行う場合は, 8 ビット操作命令で行ってください。そのとき, RIFG フラグには,必ず書き込みが無効となる"1"を設定してください。また, RIFG フラグに書き込みを行う場合も同様に 8 ビット操作命令で書き込みを行い, WAFG フラグには"1"を設定してください。

- 正)注意 RTCC1 レジスタに 1 ビット操作命令で書き込みを行うと ,RIFG フラグ ,WAFG フラグがクリアされることがあります。そのため ,RTCC1 レジスタへの書き込みは 8 ビット操作命令で設定してください。書き込み時に ,RIFG フラグ ,WAFG フラグをクリアしないようにするためには該当ビットは書き込みが無効となる "1"を設定してください。なお ,RIFG フラグ ,WAFG フラグを使用せず値が書き換わっても問題ない場合は ,RTCC1 レジスタに 1 ビット操作命令で書き込みを行っても問題ございません。

# ドキュメント改善計画

本誤記訂正内容につきましては、ユーザーズ・マニュアルに修正済みです。

項目 2 (誤記訂正): f<sub>H=</sub>8MHz, HALT モード時の電源電流(I<sub>DD</sub>)の MAX 値

## 誤記内容

電気的特性の章に  $f_{H=8MHz}$ , HALT モード時の電源電流 ( $I_{DD2}$ ) の MAX 値に誤記訂正がございます。

(下記の各端子と周辺機能は 78KOR/KG3 の例です。他の製品の場合は各ユーザーズ・マニュアルをご参照ください。)

誤)

(Ta=-40~+85 , 1.8V Vdd=EVdd=EVdd 5.5V, 1.8V AVREFO Vdd, 1.8V AVREF1 Vdd, Vss=EVss0=EVss1=AVss=OV)

| 項目   | 略号                  |      | 条                                   | 件 |                       | TYP. | MAX. | 単 位 |

|------|---------------------|------|-------------------------------------|---|-----------------------|------|------|-----|

| 電源電流 | I <sub>DD2</sub> 注1 | HALT | f <sub>IH</sub> =8MHz <sup>注2</sup> |   | V <sub>DD</sub> =5.0V | 0.45 | 0.6  | mA  |

|      |                     | T-1  |                                     |   | $V_{DD}=3.0V$         | 0.45 | 0.6  | mA  |

正)

(Ta=-40~+85 , 1.8V Vdd=EVdd=EVdd 5.5V, 1.8V AVREFO Vdd, 1.8V AVREF1 Vdd, Vss=EVss0=EVss1=AVss=0V)

| 項 目  | 略号                  |      | 条件                        | =                     | TYP. | MAX. | 単 位 |

|------|---------------------|------|---------------------------|-----------------------|------|------|-----|

| 電源電流 | I <sub>DD2</sub> 注1 | HALT | $f_{IH}$ =8MH $z^{\pm 2}$ | V <sub>DD</sub> =5.0V | 0.45 | 1.2  | mA  |

|      |                     |      |                           | V <sub>DD</sub> =3.0V | 0.45 | 1.2  | mA  |

- 注1  $V_{DD}$ ,  $EV_{DDD}$ ,  $EV_{DDD}$ ,  $AV_{REFD}$ ,  $AV_{REFD}$  に流れるトータル電流です。入力端子を  $V_{DD}$ または  $V_{SD}$  に固定した状態での入力リーク電流を含みます。また MAX.値には周辺動作電流を含みます。ただし, A/D コンバータ, D/A コンバータ, LVI 回路,I/O ポート,内蔵プルアップ / プルダウン抵抗に流れる電流は含みません。フラッシュ・メモリでの HALT 命令実行時。

- 注2 高速システム・クロック, サブシステム・クロックは停止時。

## ドキュメント改善計画

本誤記訂正内容につきましては、ユーザーズ・マニュアルに修正済みです。

# 項目3(誤記訂正):3線シリアルI/O通信の電気的特性

ユーザーズ・マニュアルの3線シリアルI/O通信 電気的特性(AC 特性)の以下の項目に誤記訂正がございます。下記の各端子と周辺機能は78KOR/KG3の例です。他の製品の場合は各ユーザーズ・マニュアルをご参照ください。

#### 誤記内容

# <u>シリアル・アレイ・ユニット(CSIモード) マスタ・モード 同電位通信時</u>

誤)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット(2/17)

$(T_A = -40 \sim +85)$ , 1.8 V  $V_{DD} = EV_{DD} = EV_{DD}$  5.5 V, Vss = EVss0 = EVss1 = AVss = 0 V)

(b) 同電位通信時(CSIモード)(マスタ・モード, SCKp...内部クロック出力)

| 項目                   | 略号     | 条件                             | MIN.        | TYP. | MAX. | 単 位 |

|----------------------|--------|--------------------------------|-------------|------|------|-----|

| SCKpサイクル・タイム         | t KCY1 | 4.0 V V <sub>100</sub> 5.5 V   | 200         |      |      | ns  |

|                      |        | 2.7 V V <sub>00</sub> < 4.0 V  | 400         |      |      | ns  |

|                      |        | 1.8 V V <sub>100</sub> < 2.7 V | 800         |      |      | ns  |

| SCKpハイ , ロウ・レベル幅     | tкнı,  | 4.0 V V <sub>00</sub> 5.5 V    | txcm/2 - 20 |      |      | ns  |

|                      | t KL1  | 2.7 V V <sub>00</sub> < 4.0 V  | txcn/2 - 35 |      |      | ns  |

|                      |        | 1.8 V V <sub>100</sub> < 2.7 V | ticn/2 - 80 |      |      | ns  |

| SIpセットアップ時間          | tsıĸı  | 4.0 V V <sub>00</sub> 5.5 V    | 70          |      |      | ns  |

| (対 <del>SCKp</del> ) |        | 2.7 V V <sub>00</sub> < 4.0 V  | 100         |      |      | ns  |

|                      |        | 1.8 V V <sub>100</sub> < 2.7 V | 190         |      |      | ns  |

| SIpホールド時間            | t KSI1 |                                | 30          |      |      | ns  |

| (対 <del>SCKp</del> ) |        |                                |             |      |      |     |

| SCKp SOp出力遅延時間       | t KS01 | C = 50 pF <sup>注</sup>         |             |      | 40   | ns  |

注 Cは, SCKp, SOp出力ラインの負荷容量です。

正)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット(2/17)

$(T_A = -40 \sim +85)$ , 1.8 V  $V_{DD} = EV_{DDO} = EV_{DD1}$  5.5 V,  $V_{SS} = EV_{SSO} = EV_{SS1} = AV_{SS} = 0$  V)

(b) 同電位通信時(CSIモード)(マスタ・モード, SCKp...内部クロック出力)

| 項目               | 略号     | 条件                                 | MIN.              | TYP. | MAX. | 単 位 |

|------------------|--------|------------------------------------|-------------------|------|------|-----|

| SCKpサイクル・タイム     | t KCY1 | 4.0 V V <sub>00</sub> 5.5 V        | 200 <sup>注1</sup> |      |      | ns  |

|                  |        | 2.7 V V <sub>DD</sub> < 4.0 V      | 300洼1             |      |      | ns  |

|                  |        | 1.8 V V <sub>100</sub> < 2.7 V     | 600洼1             |      |      | ns  |

| SCKpハイ , ロウ・レベル幅 | tкнı,  | 4.0 V V <sub>DD</sub> 5.5 V        | tюл/2 - 20        |      |      | ns  |

|                  | t KL1  | 2.7 V V <sub>00</sub> < 4.0 V      | tюл/2 - 35        |      |      | ns  |

|                  |        | 1.8 V V <sub>20</sub> < 2.7 V      | ticn/2 - 80       |      |      | ns  |

| SIpセットアップ時間      | tsıkı  | 4.0 V V <sub>DD</sub> 5.5 V        | 70                |      |      | ns  |

| ( र्रेगंडिटКр )  |        | 2.7 V V <sub>00</sub> < 4.0 V      | 100               |      |      | ns  |

|                  |        | 1.8 V V <sub>20</sub> < 2.7 V      | 190               |      |      | ns  |

| SIpホールド時間        | t KSI1 |                                    | 30                |      |      | ns  |

| ( प्रेर्गडिटКр ) |        |                                    |                   |      |      |     |

| SCKp SOp出力遅延時間   | t KSO1 | $C = 30 \text{ pF}^{\frac{1}{12}}$ |                   |      | 40   | ns  |

注1 かつ4/fax以上に設定してください。

<sup>2</sup> Cは, SCKp, SOp 出力ラインの負荷容量です。

# シリアル・アレイ・ユニット (CSI モード) スレーブ・モード 同電位通信時

## 誤)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット (3/17) (Ta = -40~+85 , 1.8 V VDD = EVDD0 = EVDD1 5.5 V, Vss = EVss0 = EVss1 = AVss = 0 V)

(c) 同電位通信時 (CSIモード) (スレーブ・モード, SCKp...外部クロック入力)

| 項目                       | 略号           |                         | <u>, , , , , , , , , , , , , , , , , , , </u> | MIN.     | TYP. | MAX.                    | 単 位 |

|--------------------------|--------------|-------------------------|-----------------------------------------------|----------|------|-------------------------|-----|

| SCKpサイクル・タイム             | t KCY2       | 16MHz < f MCK           |                                               | 8/fixx   |      |                         | ns  |

|                          |              | fick 16 MHz             |                                               | 6/fixx   |      |                         | ns  |

| SCKpハイ , ロウ・レベル幅         | t кн₂,       |                         |                                               | t KCY2/2 |      |                         | ns  |

|                          | <b>t</b> KL2 |                         |                                               |          |      |                         |     |

| SIpセットアップ時間              | tsık2        |                         |                                               | 1/fmx+80 |      |                         | ns  |

| (対 <u>SCKp</u> )         |              |                         |                                               |          |      |                         |     |

| SIpホールド時間                | t KSI2       |                         |                                               | 50       |      |                         | ns  |

| ( प्रे <u>पेडिटК</u> р ) |              |                         |                                               |          |      |                         |     |

| SCKp SOp出力遅延時間           | t KS02       | C = 50 pF <sup>i±</sup> | 4.0 V VD 5.5 V                                |          |      | 1/f <sub>NOX</sub> +120 | ns  |

|                          |              |                         | 2.7 V VD < 4.0 V                              |          |      | 1/f <sub>NOX</sub> +120 | ns  |

|                          |              |                         | 1.8 V V <sub>DD</sub> < 2.7 V                 |          |      | 1f <sub>NOX</sub> +180  | ns  |

注 Cは,SOp出力ラインの負荷容量です。

#### 正)

(c) 同電位通信時(CSIモード)(スレーブ・モード, SCKp...外部クロック入力)

| (0) 四电应应旧的 (00)      |        |                               |                  |          |      |            |     |

|----------------------|--------|-------------------------------|------------------|----------|------|------------|-----|

| 項目                   | 略 号    | 务                             | 条 件              | MIN.     | TYP. | MAX.       | 単 位 |

| SCKpサイクル・タイム         | t KCY2 | 4.0 V Voo 5.5 V               |                  | 6/fmck   |      |            | ns  |

|                      |        | 2.7 V V <sub>DD</sub> < 4.0 V | 16 MHz < f мск   | 8/fmck   |      |            | ns  |

|                      |        |                               | fmck 16 MHz      | 6/fmck   |      |            | ns  |

|                      |        | 1.8 V V <sub>DD</sub> < 2.7 V | 16 MHz < f MCK   | 8/fmck   |      |            | ns  |

|                      |        |                               | fmck 16 MHz      | 6/fmck   |      |            | ns  |

| SCKpハイ , ロウ・レベル幅     | t кн₂, |                               |                  | txcv2/2  |      |            | ns  |

|                      | t KL2  |                               |                  |          |      |            |     |

| SIpセットアップ時間          | tsik2  |                               |                  | 80       |      |            | ns  |

| (対 <del>SCKp</del> ) |        |                               |                  |          |      |            |     |

| SIpホールド時間            | t KSI2 |                               |                  | 1/fxx+50 |      |            | ns  |

| (対 <del>SCKp</del> ) |        |                               |                  |          |      |            |     |

| SCKp SOp出力遅延時間       | t KS02 | C = 30 pF <sup>½</sup>        | 4.0 V Vm 5.5 V   |          |      | 2/fnox+45  | ns  |

|                      |        |                               | 2.7 V VD < 4.0 V |          |      | 2/fnox+57  | ns  |

|                      |        |                               | 1.8 V Vm < 2.7 V |          |      | 2/fnox+125 | ns  |

注 Cは,SOp出力ラインの負荷容量です。

# シリアル・アレイ・ユニット (CSI モード) マスタ・モード 異電位通信時

誤)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット(10/17)

$(T_A = -40 \sim +85)$ , 2.7 V  $V_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1}$  5.5 V,  $V_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS} = 0 \text{ V}$ )

(f) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (マスタ・モード, SCKp...内部クロック出力) (1/2)

| 項目                             | 略号               | 条件                                                          | MIN.                   | TYP. | MAX. | 単 位 |

|--------------------------------|------------------|-------------------------------------------------------------|------------------------|------|------|-----|

| SCKpサイクル・タイム                   | t KCY1           | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 500                    |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |                        |      |      |     |

|                                |                  | 2.7 V V <sub>00</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | 1000                   |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |                        |      |      |     |

| SCKpハイ・レベル幅                    | tкнı             | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | t <sub>KCY1</sub> /2 - |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  | 120                    |      |      |     |

|                                |                  | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | t <sub>KCY1</sub> /2 - |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  | 275                    |      |      |     |

| SCKp ロウ・レベル幅                   | t <sub>KL1</sub> | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | tron/2 - 20            |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |                        |      |      |     |

|                                |                  | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | txc/1/2 - 35           |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |                        |      |      |     |

| SIpセットアップ時間                    | tsıkı            | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 195                    |      |      | ns  |

| (対 <u>SCK</u> p ) <sup>注</sup> |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |                        |      |      |     |

|                                |                  | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | 380                    |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |                        |      |      |     |

| SIpホールド時間                      | tksi1            | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 30                     |      |      | ns  |

| (対 <u>SCK</u> p ) <sup>注</sup> |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |                        |      |      |     |

|                                |                  | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | 30                     |      |      | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |                        |      |      |     |

| SCKp Sop力遅延時間 <sup>注</sup>     | t KSO1           | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    |                        |      | 165  | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |                        |      |      |     |

|                                |                  | 2.7 V V <sub>DD</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  |                        |      | 320  | ns  |

|                                |                  | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |                        |      |      |     |

注 DAPmn = 0, CKPmn = 0 またはDAPmn = 1, CKPmn = 1のとき。

備考. Cb [F]:通信ライン(SOp, SCKp)負荷容量値, m:ユニット番号 (m = 0,1), n:チャネル番号 (n = 0-2)

# 誤)

(3) シリアル・インタフェース:シリアル・アレイ・ユニット(11/17)

$(T_A = -40 \sim +85)$ , 2.7 V  $V_{DD} = \text{EV}_{DDD} = \text{EV}_{DDD} = \text{EV}_{SSD} =$

(f) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (マスタ・モード, SCKp...内部クロック出力) (2/2)

| 項目                            | 略号     | 条件                                                          | MIN. | TYP. | MAX. | 単 位 |

|-------------------------------|--------|-------------------------------------------------------------|------|------|------|-----|

| SIpセットアップ時間                   | tsıkı  | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 70   |      |      | ns  |

| (対 <u>SCKp</u> ) <sup>注</sup> |        | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |        | 2.7 V V <sub>DD</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | 100  |      |      | ns  |

|                               |        | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

| SIpホールド時間                     | t KSI1 | 4.0 V Vm 5.5 V, 2.7 V Vb 4.0 V,                             | 30   |      |      | ns  |

| (対 <u>SCKp</u> ) <sup>注</sup> |        | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |        | 2.7 V V <sub>DD</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | 30   |      |      | ns  |

|                               |        | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

| SCKp SOp出力遅延時間 <sup>注</sup>   | t KSO1 | 4.0 V Vm 5.5 V, 2.7 V Vb 4.0 V,                             |      |      | 40   | ns  |

|                               |        | $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |        | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, |      |      | 40   | ns  |

|                               |        | $C_b = 50 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

注 DAPmn = 0, CKPmn = 1 またはDAPmn = 1, CKPmn = 0 のとき。

備考. Cb [F]:通信ライン (SOp, SCKp) 負荷容量値, m:ユニット番号 (m = 0,1), n:チャネル番号 (n = 0-2)

# 正)

(3) シリアル・インタフェース:シリアル・アレイ・ユニット(10/17)

$(T_A = -40 \sim +85)$ , 2.7 V  $V_{DD} = \text{EV}_{DDO} = \text{EV}_{DDO} = \text{EV}_{SDO} = \text{EV}_{SSO} =$

(f) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (マスタ・モード, SCKp...内部クロック出力) (1/2)

| 項目                              | 略号     | 条件                                                          | MIN.              | TYP. | MAX. | 単 位 |

|---------------------------------|--------|-------------------------------------------------------------|-------------------|------|------|-----|

| SCKpサイクル・タイム                    | t KCY1 | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 400 <sup>注1</sup> |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>50</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | 800 <sup>注1</sup> |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

| SCKpハイ・レベル幅                     | t кн1  | 4.0 V V <sub>00</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | txcn/2 - 75       |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>00</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | txx1/2 - 170      |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

| SCKpロウ・レベル幅                     | t ĸ∟1  | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | tron/2 - 20       |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | txc/1/2 - 35      |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

| SIpセットアップ時間                     | tsıkı  | 4.0 V V <sub>100</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,   | 150               |      |      | ns  |

| (対 <u>SCKp</u> ) <sup>注2</sup>  |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | 275               |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

| SIpホールド時間                       | tkSI1  | 4.0 V V <sub>100</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,   | 30                |      |      | ns  |

| (対 <u>SCK</u> p ) <sup>注2</sup> |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>DD</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  | 30                |      |      | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

| SCKp SOp出力遅延時間 <sup>注2</sup>    | t KSO1 | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    |                   |      | 120  | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |                   |      |      |     |

|                                 |        | 2.7 V V <sub>00</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V,  |                   |      | 215  | ns  |

|                                 |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |                   |      |      |     |

注1. かつ4/fax以上に設定してください。

備考. Cb [F]: 通信ライン (SOp, SCKp) 負荷容量値, m: ユニット番号 (m = 0,1), n: チャネル番号 (n = 0-2)

<sup>2.</sup> DAPmn = 0, CKPmn = 0またはDAPmn = 1, CKPmn = 1のとき。

# 正)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット (11/17)

$(T_A = -40 \sim +85)$ , 2.7 V  $V_{DD} = \text{EV}_{DDO} = \text{EV}_{DDO} = \text{EV}_{SDO} = \text{EV}_{SSO} =$

(f) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (マスタ・モード, SCKp...内部クロック出力) (2/2)

| 項目                            | 略号                | 条件                                                          | MIN. | TYP. | MAX. | 単 位 |

|-------------------------------|-------------------|-------------------------------------------------------------|------|------|------|-----|

| SIpセットアップ時間                   | tsıkı             | 4.0 V V <sub>100</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,   | 70   |      |      | ns  |

| (対 <u>SCKp</u> ) <sup>注</sup> |                   | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |                   | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | 100  |      |      | ns  |

|                               |                   | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

| SIpホールド時間                     | t <sub>KSI1</sub> | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    | 30   |      |      | ns  |

| (対 <u>SCKp</u> ) <sup>注</sup> |                   | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |                   | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, | 30   |      |      | ns  |

|                               |                   | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

| SCKp SOp出力遅延時間注               | t KSO1            | 4.0 V V <sub>DD</sub> 5.5 V, 2.7 V V <sub>b</sub> 4.0 V,    |      |      | 40   | ns  |

|                               |                   | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                  |      |      |      |     |

|                               |                   | 2.7 V V <sub>100</sub> < 4.0 V, 2.3 V V <sub>b</sub> 2.7 V, |      |      | 40   | ns  |

|                               |                   | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                  |      |      |      |     |

注 DAPmn = 0, CKPmn = 1 またはDAPmn = 1, CKPmn = 0 のとき。

備考. Cb [F]:通信ライン(SOp, SCKp)負荷容量値, m:ユニット番号 (m = 0,1), n:チャネル番号 (n = 0-2)

# シリアル・アレイ・ユニット (CSI モード) スレーブ・モード 異電位通信時

誤)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット (13/17)

$(TA = -40 \sim +85)$ , 2.7 V VD = EVDD = EVDD = 5.5 V, VSS = EVSS = EVSS = AVSS = 0 V

(g) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (スレーブ・モード, SCKp...外部クロック入力)

| 項目               | 略号                |                                  | 条件                          | MIN.       | TYP. | MAX.                    | 単 位 |

|------------------|-------------------|----------------------------------|-----------------------------|------------|------|-------------------------|-----|

| SCKpサイクル・タイム     | t KCY2            | 4.0 V V <sub>DD</sub> 5.5 V,     | 16.6 MHz < f <sub>MCX</sub> | 12/fmcx    |      |                         | ns  |

|                  |                   | 2.7 V Vb 4.0 V                   | 12.5 MHz < fmcx 16.6 MHz    | 10/fmcx    |      |                         | ns  |

|                  |                   |                                  | 8.3 MHz < fmcx 12.5 MHz     | 8/fmck     |      |                         | ns  |

|                  |                   |                                  | fix 8.3 MHz                 | 6/fmck     |      |                         | ns  |

|                  |                   | 2.7 V Vm < 4.0 V,                | 17.5 MHz < f <sub>MCX</sub> | 18/fmck    |      |                         | ns  |

|                  |                   | 2.3 V Vb 2.7 V                   | 15 MHz < fxxx 17.5 MHz      | 16/fmck    |      |                         | ns  |

|                  |                   |                                  | 12.5 MHz < fmcx 15 MHz      | 14/fmck    |      |                         | ns  |

|                  |                   |                                  | 10 MHz < fxxx 12.5 MHz      | 12/fmck    |      |                         | ns  |

|                  |                   |                                  | 7.5 MHz < fmcx 10 MHz       | 10/fmcx    |      |                         | ns  |

|                  |                   |                                  | 5 MHz < fMcx 7.5 MHz        | 8/fmck     |      |                         | ns  |

|                  |                   |                                  | fix 5 MHz                   | 6/fmck     |      |                         | ns  |

| SCKpハイ , ロウ・レベル幅 | tкн₂,             | 4.0 V Voo 5.5 V, 2               | 2.7 V Vb 4.0 V              | txx2/2 -   |      |                         | ns  |

|                  | t №2              |                                  |                             | 20         |      |                         |     |

|                  |                   | 2.7 V Vm < 4.0 V, 2              | 2.3 V Vb 2.7 V              | txx2/2 -   |      |                         | ns  |

|                  |                   |                                  |                             | 35         |      |                         |     |

| SIpセットアップ時間      | tsik2             |                                  |                             | 1/fmcx +90 |      |                         | ns  |

| (対SCKp )         |                   |                                  |                             |            |      |                         |     |

| SIpホールド時間        | t <sub>KSI2</sub> |                                  |                             | 50         |      |                         | ns  |

| (対SCKp )         |                   |                                  |                             |            |      |                         |     |

| SCKp SOp出力遅延時間   | t KSO2            | 4.0 V Vm 5.5 V, 2                | 2.7 V Vb 4.0 V,             |            |      | 1/fnox+245              | ns  |

|                  |                   | $C_b = 50 \text{ pF}, R_b = 1.4$ | ł k                         |            |      |                         |     |

|                  |                   | 2.7 V Vm < 4.0 V, 2              | 2.3 V Vb 2.7 V,             |            |      | 1/f <sub>MOX</sub> +400 | ns  |

|                  |                   | $C_b = 50 \text{ pF}, R_b = 2.7$ | 7 k                         |            |      |                         |     |

備考. Cb [F]: 通信ライン(SOp)負荷容量値

# 正)

(3) シリアル・インタフェース: シリアル・アレイ・ユニット(13/17)

$(T_A = -40 \sim +85)$ , 2.7 V  $V_{DD} = \text{EV}_{DDO} = \text{EV}_{DDO} = \text{EV}_{SDO} = \text{EV}_{SSO} =$

(g) 異電位 (2.5 V系, 3 V系) 通信時 (CSIモード) (スレーブ・モード, SCKp...外部クロック入力)

| 項目                   | 略号               |                                  | 条件                          | MIN.                   | TYP. | MAX.       | 単 位 |

|----------------------|------------------|----------------------------------|-----------------------------|------------------------|------|------------|-----|

| SCKpサイクル・タイム         | t KCY2           | 4.0 V Vm 5.5 V,                  | f <sub>MCK</sub> > 13.6 MHz | 10/fmcx                |      |            | ns  |

|                      |                  | 2.7 V Vb 4.0 V                   | 6.8 MHz < fmox 13.6 MHz     | 8/fmck                 |      |            | ns  |

|                      |                  |                                  | fick 6.8 MHz                | 6/fmck                 |      |            | ns  |

|                      |                  | 2.7 V Vm < 4.0 V,                | 18.5 MHz < f <sub>MCK</sub> | 16/fmcx                |      |            | ns  |

|                      |                  | 2.3 V Vb 2.7 V                   | 14.8 MHz < fMCK 18.5 MHz    | 14/fmcx                |      |            | ns  |

|                      |                  |                                  | 11.1 MHz < fMCK 14.8 MHz    | 12/fmcx                |      |            | ns  |

|                      |                  |                                  | 7.4 MHz < fmox 11.1 MHz     | 10/fmck                |      |            | ns  |

|                      |                  |                                  | 3.7 MHz < fmox 7.4 MHz      | 8/fmck                 |      |            | ns  |

|                      |                  |                                  | fick 3.7 MHz                | 6/fmck                 |      |            | ns  |

| SCKpハイ , ロウ・レベル幅     | tнz,             | 4.0 V Vm 5.5 V, 2                | 2.7 V Vb 4.0 V              | t KCY2/2 -             |      |            | ns  |

|                      | t <sub>KL2</sub> |                                  |                             | 20                     |      |            |     |

|                      |                  | 2.7 V Vm < 4.0 V, 2              | 2.3 V Vb 2.7 V              | t KC/2/2 -             |      |            | ns  |

|                      |                  |                                  |                             | 35                     |      |            |     |

| SIpセットアップ時間          | tsık2            |                                  |                             | 90                     |      |            | ns  |

| (対 <del>SCKp</del> ) |                  |                                  |                             |                        |      |            |     |

| SIpホールド時間            | tkSI2            |                                  |                             | 1/f <sub>MOX</sub> +50 |      |            | ns  |

| (対SCKp )             |                  |                                  |                             |                        |      |            |     |

| SCKp SOp出力遅延時間       | t KSO2           | 4.0 V V <sub>DD</sub> 5.5 V, 2   | 2.7 V Vb 4.0 V,             |                        |      | 2/fnox+120 | ns  |

|                      |                  | $C_b = 30 \text{ pF}, R_b = 1.4$ | k                           |                        |      |            |     |

|                      |                  | 2.7 V Vm < 4.0 V, 2              | 2.3 V Vb 2.7 V,             |                        |      | 2/fiox+230 | ns  |

|                      |                  | $C_b = 30 \text{ pF}, R_b = 2.7$ | k                           |                        |      |            |     |

備考. Cb [F]: 通信ライン(SOp)負荷容量値

# ドキュメント改善計画

誤記訂正内容は、ユーザーズ・マニュアルの次回改版時(2009年5月の予定)に反映いたします。

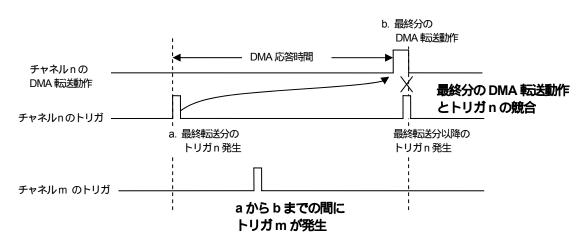

## 項目4(誤記訂正): DMA コントローラの応答時間

ユーザーズ・マニュアルの DMA コントローラの注意事項、DMA 応答時間に誤記訂正がございます。下記の周辺機能は 78KOR/KG3 の例です。他の製品の場合は各ユーザーズ・マニュアルをご参照ください。

## 誤記内容

#### 誤)(2)DMA 応答時間

DMA 転送における応答時間は,次のようになります。

表 DMA 転送における応答時間

|      | 最小時間                | 最大時間                 |

|------|---------------------|----------------------|

| 応答時間 | 2 クロック <sup>注</sup> | 10 クロック <sup>注</sup> |

注 DMA 転送の2クロック分は含まれていません。

備考 1 クロック:1/fCLK(fCLK:CPU クロック)

ただし、次の場合はさらに DMA 転送が遅れる場合があります。遅れるクロック数は条件により異なります。

- ・RAM による命令実行の場合

- ・外部メモリによる命令実行の場合

- ・外部メモリへのアクセスにてウエイトを挿入した場合

- ・DMA 保留命令実行の場合

#### 正)(2)DMA 応答時間

DMA 転送における応答時間は,次のようになります。

表 DMA 転送における応答時間

|                   |        | -       |

|-------------------|--------|---------|

|                   | 最小時間   | 最大時間    |

| 応答時間 <sup>注</sup> | 3 クロック | 10 クロック |

注 内部 ROM からの命令実行時(外部メモリへのデータ・アクセスなし)の時間です。ただし,次の場合はさらに DMA 転送が遅れる場合があります。遅れるクロック数は条件により異なります。

| 条件                    |             | 最大応答時間                           |

|-----------------------|-------------|----------------------------------|

| 内部 ROM からの            | 外部メモリへのデータ・ | 8+ (3× (外部 WAIT + ウエイト ) ) クロック  |

| 命令実行の場合               | アクセスがある場合   |                                  |

|                       | 外部メモリへのデータ・ | <br>  16 クロック                    |

| 内部 RAM からの            | アクセスがない場合   |                                  |

| 命令実行の場合               | 外部メモリへのデータ・ | <br>  16+(3×(外部WAIT+ウエイト))クロック   |

| アクセスがある場合             |             |                                  |

| <br>  外部メモリからの命令実行の場合 |             | <br>  16+(12×(外部 WAIT+ウエイト))クロック |

| 外部グモリからの中マ夫1]の場合      |             |                                  |

- 注意 1. 応答時間には , DMA 転送の 2 クロック分は含まれていません。

- 2. DMA 保留命令実行時は,各条件の最大応答時間にその条件での保留する命令の実行時間を足した時間となります。

- 3. 最大応答時間 + 1 クロック以内での同一チャネルへの連続する転送トリガは , 無視される可能性があるため設定しないでください。

(備考は次のページにあります。)

# 備考1. ウエイト:外部バス・インタフェースのCLKOUT 端子の選択クロックによるウエイト数

| CLKOUT 端子の<br>選択クロック | ウエイト数     |

|----------------------|-----------|

| f <sub>CLK</sub>     | 3 クロック    |

| f <sub>CLK</sub> /2  | 5~6クロック   |

| f <sub>CLK</sub> /3  | 7~9 クロック  |

| f <sub>CLK</sub> /4  | 9~12 クロック |

- 2. 外部 WAIT: 外部バス・インタフェースの WAIT 端子による外部 WAIT 数 (1/fax 単位)

# ドキュメント改善計画

誤記訂正内容は、ユーザーズ・マニュアルの次回改版時(2009年5月の予定)に反映させます。

# **項目1(使用制限事項):**クロック出力 / ブザー出力制御回路出力停止時の出力レベルに関する制限 制限事項詳細

#### 制限事項の対象となる使用方法

CKS レジスタによる出力クロックの選択 ( CSELn, CCSn2, CCSn1, CCSn0 ) で源発振 (  $f_{MAIN}$  ,  $f_{SLB}$  ) 以外の分周クロックを選択し,クロック出力 / ブザー出力を出力禁止 ( PCLOEn ビットをクリア ) とする場合です。

#### 現象

クロック出力 / ブザー出力の出力レベルは , 出力禁止としたとき , 本来であればロウ・レベルで停止するところ , 上記の使用方法においては , 出力禁止としたタイミングでのレベル ( ハイ / ロウ ) で停止します。

# 暫定対策(使用制限)

クロック出力 / ブザー出力を出力禁止 (PCLOEn ビットをクリア) とした後, CKS レジスタによる出力クロックの選択を源発振 (f<sub>MAIN</sub>, f<sub>Sub</sub>) に設定することにより, ロウ・レベル出力になります。但し, 本来出力していた幅と異なるハイ・パルスの出力後にロウ・レベルとなる点はご了承下さい。

## 恒久対策

上記の対象となる使用方法においてもロウ・レベルで出力が停止するようにデバイスを修正します。 修正対象品は、別紙2の使用制限事項一覧をご参照ください。

備考 n = 0, 1

# **項目2 - 1 (使用制限事項):** RTC 定周期割り込みとアラーム割り込みの同時使用に関する制限制限事項詳細

#### 制限事項の対象となる使用方法

定周期割り込みを使用 (RTCCO レジスタの(CT2, CT1, CT0) (0, 0, 0)) し, アラーム割り込みも使用 (RTCC1 レジスタの WALE=1, WALIE=1) した上, 定周期割り込みとアラーム割り込みを同時に発生させる場合です。定周期割り込みのみを使用時や, アラーム割り込みのみを使用時は対象外となります。両方の割り込みを使用する場合でも同時に割り込みを発生させない場合は対象外となります。

#### 現象

上記の対象となる使用方法にて,INTRTC割り込みが発生すると同時にRTCC1レジスタのRIFGフラグはセットされます。しかし,WAFGフラグがセットされるのは,INTRTC割り込みからサブシステム・クロックの1クロック分(約30.52us)経過後となります。そのため,INTRTC割り込み処理内でWAFGフラグを読み出してもWAFGフラグがまだセットされていない場合があります。

## 暫定対策(使用制限)

上記の対象となる使用方法にて INTRTC 割り込みが発生したとき ,割り込みのステータス RIFG フラグを 先に確認してください。RIFG=1 (定周期割り込み発生あり)の場合 , INTRTC 割り込み発生からサブシステム・クロックの 1 クロック分(約30.52us)以上経過後に WAFG フラグを確認してください。RIFG=0 (定周期割り込み発生なし)の場合 ,WAFG フラグの確認にサブシステム・クロックの 1 クロック分(約30.52us)を待つ必要はありません。

# 恒久対策

上記の対象となる使用方法において INTRTC 割り込みが発生するタイミングと同時に WAFG フラグと RIFG フラグをセットするようにデバイスを修正します。修正対象品は , 別紙 2 の使用制限事項一覧をご参照ください。

**項目2-2(使用制限事項):**カウンタ動作停止後の年/月/曜日/日/時/分/秒カウント・レジスタに関する制限 制限事項詳細

#### 制限事項の対象となる使用方法

リアルタイム・カウンタを使用時, サブカウント・レジスタ (RSUBC) のカウント値が  $7FFDH^{\pm 1}$  または  $7FFEH^{\pm 1}$  のタイミングで, RTC を停止 (RTCCO レジスタの RTCE ビットをクリア) する場合です。

#### 現象

上記の対象となる使用方法において,RTCE ビットは"0"となりますが,秒カウント・レジスタ(SEC)が f<sub>SuB</sub>周期でカウントアップしてしまい,停止しないことがあります。その場合,分,時,日,曜日, 月,年のカウント・レジスタもカウントアップを続けます。

# 暫定対策 (使用制限)

RTC を停止(RTCE ビットをクリア)する場合,RTCC1 レジスタのRWAIT ビットをセットし,その後RWST フラグが"1"になったのを確認してからRTCE ビットをクリアしてください。RTC を再開する場合,RTCE ビットをセットしてからRWAIT ビットをクリアしてください。これにより,RTC を停止(RTCE ビットをクリア)時にSEC レジスタが停止せずにカウントアップすることはなく,停止します。

## 恒久対策

上記の対象となる使用方法においても, 秒カウント・レジスタ (SEC) を停止するようにデバイスを修正します。修正対象品は, 別紙2の使用制限事項一覧をご参照ください。

注1 時計誤差補正を行う場合, 7FFDH, 7FFEH ではなく 7FFDH±補正値, 7FFEH±補正値になります。

## 項目3 - 1(使用制限事項): DMA コントローラの終了に関する制限

DMA のチャネル 0 の転送トリガ、チャネル 1 の転送トリガ、どちらかのチャネルの転送終了(ソフトウエアによる強制終了、転送回数完了による自動終了)が競合した場合、終了しなかったチャネルの DMA 転送が 2 回続けて発生する場合があります。

#### 制限事項詳細

#### 制限事項の対象となる使用方法 (ソフトウエアによる強制終了の場合)

DMA のチャネル0,チャネル1の両チャネルを共に使用している時に,"チャネル0の転送トリガ発生"と"チャネル1の転送トリガ発生"と"ソフトウエアによる強制終了(DRCn レジスタのDSTn ビットのクリア)"の3要因のタイミングが競合する場合です。この3要因のタイミングが競合した場合のみ対象となり,どれか一つでも競合しない場合は対象外となります。よって,両チャネルを同時に使用しない場合や,両チャネルを同時に使用していてもソフトウエアによる強制終了をしない場合は対象外となります。

また,競合時の強制終了しないチャネルの転送トリガが最終転送分(DBCn レジスタ値が 0001H 時のトリガ)の場合は,対象外となります。

#### 現象

上記3要因が競合後,DSTn ビットのクリアにて強制終了しなかった方のチャネルのDMA 転送が2回続けて(1回多く)実行されることがあります。その場合,強制終了しなかったチャネルのDBCn レジスタ値はDMA 転送が実行される毎にデクリメントされて,計2減ります。

# 制限事項の対象となる使用方法(転送回数完了による自動終了の場合)

DMA のチャネル 0 , チャネル 1 の両チャネルを共に使用している時に , 片方のチャネル n に設定した 転送回数完了による自動終了時に , 下記 2 つの条件に共に該当する場合制限事項の対象となります。

最終の DMA 転送分の "チャネル n の転送トリガ発生 "から "そのチャネル n の最終の DMA 転送動作終了"タイミングまでの間にチャネル m の転送トリガが発生した場合。

"チャネルnの最終のDMA 転送のタイミング"と"チャネルn の転送トリガ発生"が競合する場合。

両チャネルを同時に使用していても、最終転送分のチャネルnのトリガ発生以降はチャネルnのトリガが発生しない場合や、DMAの転送トリガ間隔が DMA 応答時間+2 クロック以上の場合は、の競合が発生しないため対象外となります。また、チャネルmの転送トリガが最終転送分(DBCm レジスタ値が0001H時のトリガ)の場合は、対象外となります。

# 現象

上記 , の要因が発生後 , チャネル m の DMA 転送が 2 回続けて (1 回多く) 実行されることがあります。その場合 , チャネル m の DBC m レジスタ値は DMA 転送が実行される毎にデクリメントされて , 計 2 減ります。

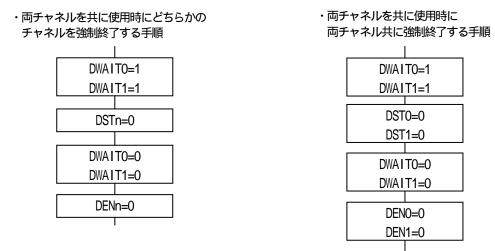

# 対策 (使用制限)

# ソフトウエアによる強制終了の場合

DMA を両チャネル共に使用している時にソフトウエアで強制終了する場合は 両チャネル共に DWAITn ビットをセットして DMA 転送を保留してから , DSTnO ビットをクリアしてください。その後、両チャネル共に DWAITn ビットをクリアし保留を解除してから , DENn ビットをクリアしてください。

備考 n = 0, 1

# 転送回数完了による自動終了の場合

同一チャネルへの連続する転送トリガ間隔は,最大応答時間 + 2 クロック以上に設定してください。 よって,項目 4 の誤記訂正で追加された下記注意事項に従うことにより,本制限事項にも該当いたしません。

#### 備考 項目4(誤記訂正)で追加された注意事項

注意 3 最大応答時間 + 1 クロック以内での同一チャネルへの連続する転送トリガは , 無視される可能性があるため設定しないでください。

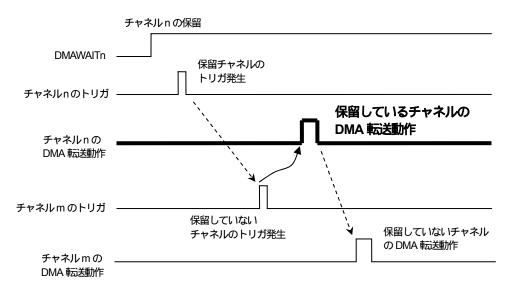

**項目3-2(使用制限事項): DMA コントローラの DWAITn ビットによる DMA 転送の保留に関する制限**

DMA のチャネル 0、チャネル 1 を同時に使用している場合、片方の DMA を保留にした後(DMC n の DWAIT n ビットをセット)、その保留中に保留したチャネルの転送トリガが発生し、それ以降に保留していないチャネルの転送トリガが発生すると、保留したチャネルの DMA 転送が実行される場合があります。

## 制限事項詳細

#### 制限事項の対象となる使用方法

DMA のチャネル0,チャネル1の両チャネルを共に使用している時に,チャネルnを DMCn レジスタの DWAITn ビットをセットして保留にした後,その保留中に保留したチャネルnの転送トリガが発生し,それ以降に保留していないチャネルmの転送トリガが発生した場合です。チャネルnの転送トリガとチャネルmの転送トリガに同一 DMA 起動要因を設定した場合や,同時に発生した場合も対象となります。両チャネルを共に保留している場合は対象外となります。

#### 現象

上記の対象となる使用方法での保留していないチャネルmの転送トリガが発生後に、保留しているチャネルnのDMA 転送が実行されることがあります。その後にチャネルmのDMA 転送も実行されます。本来であれば、チャネルmのDMA 転送だけが実行され、チャネルnのDMA 転送は保留される動作となります。

備考 (n,m)=(0,1)or(1,0)

#### 対策(使用制限)

DMA のチャネル 0 , チャネル 1 の両チャネルを共に使用している時に , DMCn レジスタの DWAITn ビットをセットし保留する場合は , 両チャネル共に DWAITn ビットをセットして DMA 転送を保留してください。

備考 n = 0, 1