# マイクロコンピュータ技術情報

発行番号 SBG-DT-04-0045号 1/3 発行日 2004年 2月 9日 32ビットマイクロコンピュータ NECエレクトロニクス 株式 会社 V850E/SV2 ソリューション事業本部 使用制限事項の件 発行元 第二ソリューション事業部 マイクロコンピュータグループ 使用制限 ドキュメント誤記訂正 文書分類  $\circ$ バージョン・アップ その他 事項 (正誤表) V850E/SV2 ユーザーズ・マニュアル(ハードウェア編) 資料番号:U16384JJ 関連資料 V850E1 ユーザーズ・マニュアル(アーキテクチャ編) 資料番号: U14559JJ

CP(K),O

## 1. 対象製品

V850E/SV2 フラッシュ版

μPD70F3166/70F3166Y (内蔵

(内蔵フラッシュ/RAM:512KB/24KB)

V850E/SV2 マスク版

$\mu$  PD703166 $\angle$ 703166 $\Upsilon$

(内蔵マスク ROM/RAM:512KB/24KB)

※以下 No.1~NO.3 の制限事項についてはマスク版は該当致しません。

## 2. 新たな制限事項

上記対象製品において以下の制限事項があります。

詳細については、別紙1を参照してください。

NO.1 疑似セパレートバス(A0-A15)出力モードの制限事項

外部バスを使用する際に、疑似セパレートバス(A0-A15)出力モードを選択出来ません。

#### NO.2 CLKOUT 端子出力の制限事項

バス・クロック分周機能レジスタ(DVC)の設定値が、00H(fDV=fCPU)、01H(fDV=fCPU/2)のどちらの場合でも、CLKOUT 端子からはfCPU(1/1 倍)のバスクロックが出力されます。ただし、外部バス用基本クロック(fDV)は、DVC レジスタの設定値通りの分周比になります。

- NO.3 自動送受信機能付シリアル・インタフェース(CSIAn)のバッファRAM書き込み時の制限事項 バッファRAM(CBUFnm)に書き込み命令で送信データを書き込む時、

- \*Byte書き込みでも、Half\_word書き込みを行ってしまう

- ・Half\_word 書き込みでも、Byte 書き込みを行ってしまう

などの場合があり、バッファRAM に正しいデータを書き込めません。(n=0,1 m=0-15)なお、バッファRAMのデータの読み出しは、正常に行われます。

## NO.4 mul/mulu命令に関する制限事項

mul、mulu命令において、1stオペランドと3rdオペランドに同じレジスタを使用する命令実行中に割り込みが発生した場合、演算結果(3rdオペランドのレジスタ値)が不正になる場合があります。なお、命令そのものは実行終了し、続く命令を実行します。

#### NO.5 DMA転送強制終了に関する制限事項

DCHCnレジスタのINITnビットの操作により、DMA転送を強制終了する場合、INITnビットをセット (1)したにもかかわらず、強制終了されずに中断状態になる場合があります。または、強制終了後にIN ITnビットをセットした対象のチャネルのDMA転送が初期化された値で1回行われる可能性があります。

#### NO.6 NMIによるDMA転送中断に関する制限事項

DMA転送中のNMI入力により、DMA転送を強制的に中断しますが、NMI割り込みを受け付ける際、既にフェッチが完了している命令まで実行されます。この実行された命令が Ennビットを操作する命令 であった場合、NMIで中断されたDMA転送を期待通りに状態復帰させることができない場合があります。

## NO.7 内蔵RAMでのプログラム実行とDMA転送に関する制限事項

内蔵RAMを対象としたDMA転送を実行しており、かつ内蔵RAM上に配置されたビット操作命令(SET1,CLR1,NOT1)、もしくは、ミス・アライン・アドレスに対するデータ・アクセス命令を実行した場合、内部バスの競合動作により、CPUがデッド・ロックする可能性があります。デッド・ロック中はリセットのみ受付可能です(NMIも割り込みも受け付けられません)。

内蔵RAM上での命令実行を行っていない、もしくは、内蔵RAMを対象としたDMA転送を行っていなければ、非該当です。

## NO.8 DMAのTCnビット自動クリアに関する制限事項

2ch以上のDMA転送を同時に使用する場合、内蔵RAMを対象(転送元または転送先)とするDMA 転送において、DMA転送終了後にDCHCnレジスタのTCnビットを読み出しても、クリア(O)されない 場合があります。

#### NO.9 sld命令と割り込み競合に関する制限事項

以下の特定命令の実行が完了する以前に、後続のsld命令の直前の命令のデコード動作と割り込み要求が競合した場合、先の特定命令の実行結果がレジスタに格納されないことがあります。

本現象は、特定命令のディスティネーション・レジスタとsld命令のディスティネーション・レジスタが同じ、かつ、sld命令の直前に実行される命令でそのレジスタ値を参照した場合にのみ発生することがあります。

#### (特定命令)

·Id命令:Id.b、Id.h、Id.w、Id.bu、Id.hu ·sId命令:SId.b、SId.h、SId.w、SId.bu、SId.hu

•乗算命令 :mul、mulh、mulhi、mulu

## 問題となる命令シーケンス例

例1 ①ld.w [r11],<u>**r10**</u>

2mov <u>r10</u> ,r28

③sld.w 0x28 ,r10

①のId命令の実行が完了する前に、③のsId命令の直前のmov命令(②)のデコード動作と割り込み要求が競合した場合に問題が発生。

例2 ①ld.w [r11],<u>**r10**</u>

2cmp imm5, r10

③sld.w 0x28 ,**r10**

4bz label

①のld命令の実行が完了する前に、③のsld命令の直前のcmp命令(②)のデコード動作と割り込み要求が競合した場合に問題が発生。この結果、cmp命令の比較結果が不正になり、④の分岐命令が不正動作することがある。

例3 ①ld.w [r11],<u>**r10**</u>

:

②add imm5, <u>r10</u>

3sld.w 0x28 ,**r10**

(4)setf r16

①のId命令の実行が完了する前に、③のsId命令の直前のadd命令(②)のデコード動作と割り込み要求が競合した場合に問題が発生。この結果、add命令の演算結果、及びフラグが不正になり、④のsetf命令の実行結果が不正になることがある。

#### 3. 回避策

今回追加した制限事項の回避策です。詳細は別紙 1 をご参照してください。

No.1 疑似セパレートバス(A0-A15)出力モードの制限事項 外部バスを使用する場合は、疑似セパレートバス出力モードを使用せず、マルチプレクスト・バスモード にてご使用下さい。

## No.2 CLKOUT 端子出力の制限事項

外部バスをCLKOUT 同期かつfDV=fcpu/2 で使用するシステムでは、CLKOUT出力を外部回路にて2分周してから、ターゲットデバイスと接続する回路構成にしてください。

- NO.3 自動送受信機能付リアル・インタフェース(CSIAn)のバッファRAM書き込み時の制限事項 ソフトウエアによる回避をお願いします。回避手順は別紙1を参照してください。バッファRAMを使用せずに通常の3線式シリアルインターフェースとして使用すれば非該当です。

- NO.4 mul/mulu命令に関する制限事項 ソフトウエアによる回避をお願いします。回避手順は別紙1を参照してください。

- NO.5 DMA転送強制終了に関する制限事項 ソフトウエアによる回避をお願いします。回避手順は別紙1を参照してください。

- NO.6 NMIによるDMA転送中断に関する制限事項

NMIにより強制中断されたDMA転送は、再度初期化して実行してください。

- NO.7 内蔵RAMでのプログラム実行とDMA転送に関する制限事項

- 以下のいずれかの方法で回避してください。

- ・内蔵RAM上に配置された命令を実行する場合は、内蔵RAMを対象としたDMA転送を行わないでく さい。

- ・内蔵RAMを対象とするDMAを実行する場合は、内蔵RAM上に配置された命令実行を行わないでください。

## NO.8 DMAのTCnビット自動クリアに関する制限事項

内蔵RAMを転送対象とするDMAチャネルに対応するDCHCnレジスタのTCnビットを読み出す場合、TCビットがセット(1)されている状態を読み出したあと、続けて2回DCHCnレジスタを空読みしてください。3回続けて読み出すことにより、確実にTCnビットをクリア(0)することができます。

#### NO.9 sld命令と割り込み競合に関する制限事項

CPU機能に関する使用制限事項として、コンパイラにより該当命令シーケンスの生成を自動的に抑止するように致します。具体的な提供方法はご使用のコンパイラ毎に以下の通りとなります。その他のコンパイラをご使用の場合は弊社販売員または特約店を通じてご相談下さい。詳細は別紙1をご参照願います。

・弊社製コンパイラ: CA850の場合

最新版(V2.60)に対策機能を追加したもの(V2.61)を下記サイトの開発ツール・ダウンロード・サービス(ODS;コンパイラ購入後の郵送によるユーザ登録が必要)にて提供させて頂きます。

http://www.necel.com/micro/ods/jpn/index.html

#### ・GHS製コンパイラ: CC850の場合

以下のバージョンについては、国内販売代理店(アドバンスド・データ・コントロールズ社)にて、対策機能を追加するバージョン・アップ対応をして頂く予定ですので、個別にお問い合わせをお願い致します。その他のバージョンに関しましては、お手数をお掛けしまして申し訳ございませんが、下記の販売代理店窓口にお問い合わせください。

•Multi4. 0 Rel 7. 0. 0

•Multi3. 5. 1 Rel 6. 5. 3

#### 販売代理店窓口

TEL: 03-3576-6805 E-mail: upgv850e@adac.co.jp

#### 4. 改善計画

No1~No.3 につきましては、回路修正を致します。また No.4~No.9 の制限事項に関しましては、大変申し訳ございませんが、デバイス修正は行わず、使用上の注意事項に追加させて頂く形で対応させて頂きます。なお、デバイス修正の日程については、下記を予定しております。

04年2月フラッシュES(ES1. 1)04年10月以降フラッシュMP(E規格)

注1:規格区分は、捺印のロット番号左から5桁目のアルファベットです。

## 5. sld命令と割り込み競合に関する制限事項の補足

現在開発中や既に量産中のシステムへの本制限事項の該当可否の確認につきましては、以下のご対応をよろしくお願い致します。

#### 【開発済みシステムへの対応について】

申し訳ございませんが、添付の該非判定チェック・シート(別紙2)の手順に沿って、問題発生条件の該非判定を行ってください。

なお、問題発生を抑止する要因が多数あり、問題となる命令シーケンスを実行したとしても、実際に問題が発生するケースは極めて稀であるものと考えております。しかしながら、万全を期すために、ご一読の上、対処頂きたく、お願い申し上げます。

#### 【組み込み用ソフトウエア製品の該非確認について】

弊社製リアルタイムOS、ならびにミドルウエアの該非確認状況を以下に示します。

(リアルタイムOS)

RX850 : 非該当 RX850pro : 非該当

## (ミドルウエア)

ファイル・システム(RX-FS): 非該当ネットワーク・ライブラリ(RX-NET): 非該当高速浮動小数点ライブラリ(GOFAST): 非該当音声合成ライブラリ(Text to Speech): 非該当

上記以外の製品については、弊社販売員または特約店を通じて、個別にお問い合わせ下さい。 また、サード・パーティ製品につきましても、各製品の供給元に個別にご相談願います。

## 6. 制限事項一覧

制限事項の履歴とその詳細情報が含まれました制限事項一覧を別紙1に記載いたします。

## 7. 発行文書履歴

## V850E/SV2使用制限事項一覧 発行文書履歴

| 文書番号               | 発行日        | 記事               |  |  |

|--------------------|------------|------------------|--|--|

| SBG-DT-04-0045(初版) | 2004. 2. 9 | 統合版初版(NO.1~NO.9) |  |  |

|                    |            |                  |  |  |

## V850E/SV2の使用制限事項一覧

## 1)製品バージョン

μPD70F3166/F3166Y:ES1. 0、K規格

:ES1. 1、E規格

μPD703166/3166Y :K規格

規格区分は、捺印のロット番号左から5桁目のアルファベットです。

## 2)製品履歴

· µ P D 7 0 F 3 1 6 6 / F 3 1 6 6 Y

| No. 制限事項 | 生川限東西                                          |       | バージョン |  |

|----------|------------------------------------------------|-------|-------|--|

|          |                                                |       | 規格区分  |  |

|          | 只を乗り付け<br>・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | ES1.0 | ES1.1 |  |

|          |                                                |       | E規格   |  |

| 1        | 疑似セパレートバス出力機能の制限事項                             | ×     |       |  |

| 2        | CLKOUT 端子出力の制限事項                               | ×     |       |  |

| 3        | 自動転送機能付きシリアル(CSIA)のパッファ RAM 書き込み時の制限事項         | ×     |       |  |

| 4        | mul/mulu命令に関する制限事項                             |       |       |  |

| 5        | DMA転送強制終了に関する制限事項                              |       |       |  |

| 6        | NMIによるDMA強制中断に関する制限事項                          |       |       |  |

| 7        | 内蔵RAMでのプログラム実行とDMA転送に関する制限事項                   |       |       |  |

| 8        | DMAのTCnビット自動クリアに関する制限事項                        |       |       |  |

| 9        | s l d 命令と割り込み競合に関する制限事項                        |       |       |  |

:該当しません : 今後とも制限事項 x:該当する(修正予定あり)

## · μ P D 7 0 3 1 6 6 / 3 1 6 6 Y

| No. | 制限事項                                   | 規格区分 |

|-----|----------------------------------------|------|

|     |                                        | K規格  |

| 1   | 疑似セパレートバス出力機能の制限事項                     |      |

| 2   | CLKOUT 端子出力の制限事項                       |      |

| 3   | 自動転送機能付きシリアル(CSIA)のパッファ RAM 書き込み時の制限事項 |      |

| 4   | mul/mulu命令に関する制限事項                     |      |

| 5   | DMA転送強制終了に関する制限事項                      |      |

| 6   | NMIによるDMA強制中断に関する制限事項                  |      |

| 7   | 内蔵RAMでのプログラム実行とDMA転送に関する制限事項           |      |

| 8   | DMAのTCnビット自動クリアに関する制限事項                |      |

| 9   | s 1 d命令と割り込み競合に関する制限事項                 |      |

:該当しません : 今後とも制限事項 x:該当する(修正予定あり)

#### 3)使用制限の詳細

## NO.1 疑似セパレートバス出力機能の制限事項

#### 【内容】

外部バスを使用する際に、疑似セパレートバス(A0-A15)出力モードを選択出来ません。

#### 【回避策】

外部バスを使用する場合は、疑似セパレートバス出力モードを使用せず、マルチプレクスト・バスモード にてご使用下さい。

## NO.2 CLKOUT 端子出力の制限事項

#### 【内容】

バス・クロック分周制御レジスタ(DVC)の設定値が00H(fDV=fCPU)、01H(fDV=fCPU/2)のどちらの場合でも CLKOUT 端子からはfCPU(1/1 倍)が出力されます。

ただし、外部バス用基本クロック(fDV)は、DVC レジスタの設定通りの分周比になりますので、外部バスを CLKOUT 非同期で使用するシステムでは問題ありません。

#### 【回避策】

外部バスをCLKOUT 同期かつfDV=fCPU/2 で使用するシステムでは、CLKOUT出力を外部回路にて2分周してから、ターゲットデバイスと接続する回路構成にしてください。

#### NO.3 自動転送機能付シリアル(CSIA)のバッファ RAM 書き込み時の制限事項

#### 【内容】

バッファRAM(CBUFnm)に書き込み命令で送信データを書き込む時、

- Byte書き込みでも、Half word書き込みを行ってしまう

- •Half\_word 書き込みでも、Byte 書き込みを行ってしまう

などの場合があり、バッファRAM に正しいデータを書き込めません。(n=0,1 m=0-15) なお、バッファRAMのデータの読み出しは、正常に行われます。

## 【非該当条件】

バッファRAMを使用せずに通常の3線式シリアル・インターフェースとして使用する際には、非該当です。

#### 【回避策】

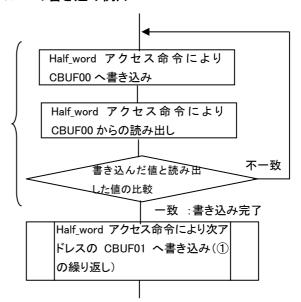

バッファRAMに書き込む際には、ソフトウェアにより以下の回避策の内どれかを行ってください。

#### 【回避策①】

Half\_Word アクセス命令(ST.H)による書き込み後、その内容を読み出し、ベリファイを行い、異なったデータの場合は再度書き込みを行い、正しいデータとなるまで繰り返し実行してください。

この場合、割り込みを禁止する必要はありません。

奇数バイト数のデータを書き込む場合は、上位アドレス番地のバッファ RAM(CBUFnmH)にはダミーデータを書き込んでください。(n=0,1 m=0-15)

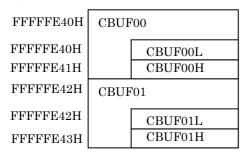

## <バッファ RAM への書き込み例(CBUF00-CBUF01 への書き込み例)>

#### アドレス

バッファ RAM 構成

## <1 バイトデータのみを書き込む場合(CBUF00L への書き込み例)>

CBUF00L(下位アドレス番地のバッファ RAM)のみへの書き込みを行う場合も①の動作を行い、CBUF00H (上位アドレス番地のバッファ RAM)にはダミーデータをライトしてください。

## 【回避策②】

DI 命令により割り込みを禁止し、Half\_Word アクセス命令(ST.H)のみを使用しバッファ RAM への書き込みを行ってください。さらに、書き込みを行った最終の 2 バイトについては、もう一度書き込みを行ってください。(最終 2 バイトのデータの 2 度書きを行ってください。)バッファ RAM にデータを書いてから、最終のデータを 2 度書きするまでの間、NOP/演算命令(算術、飽和、論理)以外の命令を行わないでください。奇数バイト数のデータを書き込む場合は、上位アドレス番地のバッファ RAM(CBUFnmH)にはずミーデータを書き込んでください。(n=0.1 m=0-15)

#### 【回避策③】

DI 命令により割り込みを禁止し、byte アクセス命令(ST.B)のみを使用しバッファ RAM への書き込みを行ってください。さらに、最終のデータをバッファ RAM に書き込んだ後、CSISAn のビット 6,7(CKSAn1, CKSAn0)で選択した入力クロック(fSCKA)の 5 クロック分以上に相当する時間を、NOP 命令もしくは演算命令(算術、飽和、論理)の実行にて確保してください。(n=0,1)

## No.4 mul/mulu命令に関する制限事項

#### 【内容】

mul、mulu命令において、1stオペランドと3rdオペランドに同じレジスタを使用する命令実行中に割り込みが発生した場合、演算結果(3rdオペランドのレジスタ値)が不正になる場合があります。なお、命令そのものは実行終了し、続く命令を実行します。

NEC製のCコンパイラをご使用の場合は、アセンブリ言語による記述箇所で本制限に非該当であれば問題ありません。記述有無の確認としては、プロジェクトマネージャー内のグローバル検索機能等をご使用ください。

GHS社、レッドハット社、ウインドリバー社製品については、下記[関連製品]を参照ください。

#### 記述例)

mul <u>reg1</u>, reg2, <u>reg1</u>

および

mulu <u>reg1</u>, reg2, <u>reg1</u>

[レジスタreg1、reg2は異なるレジスタ。reg1は、rO(ゼロ・レジスタ)以外]

#### 【非該当条件】

1stオペランドと3rdオペランドに使用するレジスタが異なる場合は、非該当です。

また、NEC製Cコンパイラは、本使用制限に該当する命令形式を生成しておりません。さらに、リアルタイムOS(RX850、RX850pro)、ミドルウエアの各製品についても該当する命令形式を使用しておりません。

#### 【回避策】

以下の記述でプログラミングしてください。

mul reg1, reg2, reg3

および

mulu reg1, reg2, reg3

[<u>レジスタreg1、reg2、reg3は異なるレジスタ</u>。reg3は、r0以外]

#### または、

mov reg1, <u>rtmp</u>

mul <u>rtmp</u>, reg2, reg1

および

mov reg1, rtmp

mulu <u>rtmp</u>, reg2, reg1

[レジスタreg1、reg2、rtmpは異なるレジスタ。reg1、rtmpはr0以外]

## 【関連製品】

・GHS製品について

過去にリリースされたCコンパイラ(Ver1.8.9まで)は、組み込み関数\_\_\_\_MULSH()、\_\_\_MULUH()を使った場合で、かつ最適化モードの設定により本使用制限の命令形式が選択生成される可能性があります。

本使用制限命令の有無は、GHS製コンパイラ付属の逆アセンブラである"gdump"を使用し「% gdump a. out | grep mul」により全てのmul命令を抽出して、該非確認をお願いします。

MULTI2000 Rel3. 5からは、本命令形式をC記述でもアセンブラ記述でも生成せず、アセンブリ時にエラーとして検出します。MULTI2000 Rel3. 5は、詳細は株式会社アドバンスド・データ・コントロールズ社にご確認ください。

また、ランタイム・ライブラリについては、mul/mulu命令自体は使用していますが、本使用制限に該当する命令形式は過去、今後とも生成しません。

・レッドハット社、ウインドリバー社製品について

両社のGNUコンパイラは、本使用制限に該当する命令形式を過去、今後とも生成しません。

#### No.5 DMA転送強制終了に関する制限事項

## 【内容】

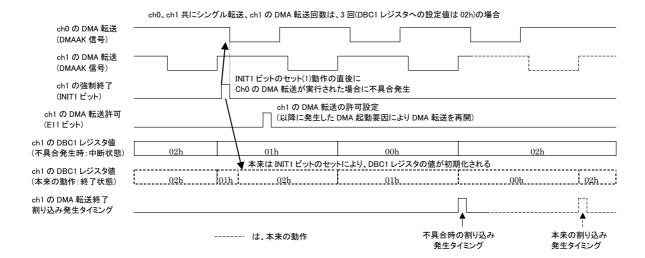

DCHCnレジスタのINITnビットの操作により、DMA転送を強制終了する場合、INITnビットをセット(1) したにも拘わらず、強制終了されずに中断状態になる場合があります。このため、強制終了させたはずのチャネルのDMA転送を再開させた場合に、想定外の転送回数完了後にDMA転送が終了し、DMA転送終了割り込みが発生することがあります(n=0-3)。本不具合は、強制終了(INITnビットのセット(1))の直後にDMA転送が実行された場合に発生します(F図参照)。

本制限事項は転送チャネル数、転送タイプ(2サイクル)、転送対象(メモリーメモリ、メモリーI/O;内蔵資源を含む)、転送モード(シングル/シングル・ステップ/ブロック)、起動要因(内蔵周辺I/Oからの割り込み、ソフトウエア)には依存せず、仕様的に設定可能ないずれの組み合わせでも発生する可能性があります。また、他のチャネルの影響も受けます。

なお、以下のレジスタは、マスタ/スレーブの2段FIFO構成のバッファ・レジスタになっています。このため、DMA転送中、及びDMA中断状態にこれらのレジスタを書き換えた場合、マスタ・レジスタに書き込まれます。DMA転送中、中断状態に書き換えた値は、書き換えたチャネルのDMA転送終了時にスレーブ・レジスタに反映されます。

また、上図における初期化とは、マスタ・レジスタの内容をスレーブ・レジスタに反映させることを指しています。

## 2段FIFO構成のレジスタ

- ・DMAソース・アドレス・レジスタ(DSAnH、DSAnL)

- ・DMAディスティネーション・アドレス・レジスタ(DDAnH、DDAnL)

- ・DMA転送カウント・レジスタ(DBCn)

## 【回避策】

以下のいずれかの手順によりソフトウエアにて回避可能です。

①一時的に全てのDMAチャネルの転送を停止させる方法

次の点を満たして頂ければ、以下の手順で回避可能です。

・以下の回避処理以外で、DCHCnレジスタのTCnビット=1となっていることを期待したプログラム構成になっていない(DCHCnレジスタのTCnビットは読み出しによりクリア(0)されるため、以下(5)②の回避処理ルーチン実行によりクリアされてしまいます。)。

#### <回避手順>

- (1)割り込み禁止(DI)状態にする。

- (2) DMAリスタート・レジスタ(DRST)を読み出し、各チャネルのENnビットを汎用レジスタに転送する。 (値: A)

- (3) DMAリスタート・レジスタ(DRST)に00Hを書き込む(2回実行 $^{\pm}$ )。2回実行 $^{\pm}$ することにより(4) の処理以前に必ずDMA転送が停止します。

- (4)強制終了するチャネルのDCHCnレジスタのINITnビットをセット(1)する。

- (5)(2)で読み出した値(A)に対して次の操作を行う。(値:B)

- ①強制終了するチャネルのビットをクリア(O)する。

- ②強制終了しない各チャネルのTCnビットとENnビットが、共に1(ANDが1)の場合はそのチャネルのビットをクリア(0)する。

- (6)(5)で操作した値(B)をDRSTレジスタに書き込む。

- (7)割り込み許可(EI)状態にする。

- ※:上記(5)は、(2)~(3)の間に正常終了したチャネルに対して、再度ENnビットを不正にセットすることを防ぐため、必ず行ってください。

- X:n=0-3

- 注:転送対象(転送元または転送先)が内蔵RAMの場合は、3回実行してください。

#### ②正常に強制終了するまでINITnビットのセットを繰り返し実行する方法(n=0-3)

#### <回避手順>

- (1)強制終了したいチャネルの初期転送回数を汎用レジスタにコピーする。

- (2)強制終了するチャネルのDCHCnレジスタのINITnビットをセット(1)する。

- (3)強制終了するチャネルのDMA転送カウント・レジスタ(DBCn)の値を読み込み、(1)でコピーした値と比較する。一致しない場合は(2)~(3)を繰り返す。

- ※: (3)でDBCnレジスタを読み込んだ場合、不具合で停止したときは残りの転送回数がリードされます。正常に強制終了した場合には初期転送回数がリードされます。

- ※:この回避方法は、強制終了の対象となっているDMAチャネル以外のDMA転送が、頻繁に行われるようなアプリケーションにおいては、強制終了されるまでに、時間を要する可能性がありますので、ご注意願います。

## No.6 NMIによるDMA強制中断に関する制限事項

## 【内 容】

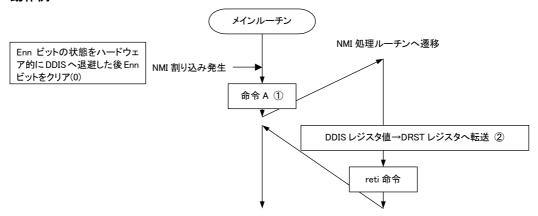

上記製品はDMA転送中のNMI入力により、DMA転送を強制的に中断します。このときDMAコントローラは、すべてのチャネルのEnnビット(DCHCnレジスタのビットO)の状態をDDISレジスタに退避した後、Ennビットをクリア(O)して、DMA転送禁止状態にします。また、CPUのパイプライン動作として、NMI割り込みを受け付ける際、既にフェッチが完了している命令(最大1命令)まで実行されます。

この実行された命令が、Ennビットを操作するような命令であった場合、NMI処理ルーチン内では、中断されているDMA転送を再開させるために、DDISレジスタの内容をDRSTレジスタに転送するため、NMI入力直後に実行されたEnnビットの操作が反映されません。

このため、DMA転送を禁止状態、もしくは許可状態にしたにも拘わらず、NMIで中断されたDMA 転送を期待通りに状態復帰させることができません。

#### 動作例

上記命令Aで、DCHCnレジスタのEnnビットを操作し、DMAを禁止/許可にした場合、上記①と②で、各DMAチャネルの禁止/許可状態に不整合が生じるため、正常に中断されたDMA転送を正常に状態復帰できません。

また、DCHCnレジスタのソフトウエアトリガ(STGn)ビットをセット(1)している状態において、命令AでEnnビットがセット(1)された場合、NMI処理ルーチン内でもDMA転送が行われます。

#### 【非該当条件】

NMIを使用していなければ、問題ありません。

また、NMIにより強制中断されたDMA転送を継続再開しないシステムであれば、問題となることはありません。

#### 【回避策】

NMIにより強制中断されたDMA転送は、再度初期化して実行してください。

## No.7 内蔵RAMでのプログラム実行とDMA転送に関する制限事項

## 【内 容】

内蔵RAMを対象としたDMA転送を実行しており、かつ内蔵RAM上に配置されたビット操作命令 (SET1,CLR1,NOT1)、もしくは、ミス・アライン・アドレスに対するデータ・アクセス命令を実行した場合、内部バスの競合動作により、CPUがデッド・ロックする可能性があります。デッド・ロック中はリセットのみ受付可能です(NMIも割り込みも受け付けられません)。

#### 【非該当条件】

内蔵RAM上での命令実行を行っていない、もしくは、内蔵RAMを対象としたDMA転送を行っていなければ、非該当です。

## 【回避策】

以下のいずれかの方法により、回避をお願い致します。

- 一内蔵RAM上に配置された命令を実行する場合は、内蔵RAMを対象としたDMA転送を 行わない。

- 内蔵RAMを対象とするDMAを実行する場合は、内蔵RAM上に配置された命令実行を 行わない。

## No.8 DMAのTCnビット自動クリアに関する制限事項

#### 【内 容】

本来、DCHCnレジスタのTCnビットは、読み出すことにより自動的にクリア(0)されますが、2ch以上のDMA転送を同時に使用する場合、内蔵RAMを対象(転送元または転送先)とするDMA転送において、DMA転送終了後にDCHCnレジスタのTCnビットを読み出しても、クリア(0)されない場合があります(n=0-3)。

#### 【非該当条件】

以下のいずれかの条件を1つでも満たしていれば、本問題は非該当です。

- ・DMA転送を1chのみしか使用していない。

- ・内蔵RAMを対象(転送元または転送先)とするDMA転送を行っていない。

## 【補足説明】

本不具合現象に該当するのは、CPUプログラムにてDCHCnレジスタをポーリングしながら、T Cビットがセット(1)されるのを待ち合わせているような場合です。

ただし、DMA転送終了割り込み(INTDMAn)による割り込みルーチン内でDCHCnレジスタのTCビットを読み出す処理をした場合にも、下記の4つの条件をすべて満たす場合には、本不具合に該当することがあります。

- (1)DMA転送を複数チャネル使用している。

- (2)内蔵RAMがDMA転送元であるDMA転送を行っている。

- (3) VSWCレジスタの設定値が11H(動作周波数: 25MHz~33MHz未満)である。

- (4)DMA転送終了割り込みルーチン内でDCHCnレジスタを読み出す以前に、内蔵RAM、内蔵I/O領域、外部メモリのいずれかに対するロード命令/ストア命令などを行っていない (最初にアクセスするデータがDCHCnレジスタである)。

#### 【ソフトウエア回避策】

内蔵RAMを転送対象とするDMAチャネルに対応するDCHCnレジスタのTCnビットを読み出す場合、TCビットがセット(1)されている状態を読み出したあと、続けて2回DCHCnレジスタを空読みしてください。3回続けて読み出すことにより、確実にTCnビットをクリア(0)することができます。

#### No.9 sld命令と割り込み競合に関する制限事項

#### 【内容】

以下の特定命令(下記例①に対応)の実行が完了する以前に、後続のsld命令(下記例③に対応)の 直前の命令(下記例②に対応)のデコード動作と割り込み要求が競合した場合、先の特定命令の実行 結果がレジスタに格納されないことがあります。

なお、本現象は、特定命令のディスティネーション・レジスタとsld命令のディスティネーション・レジス タが同じ、かつsld命令の直前に実行される命令でそのレジスタ値を参照した場合にのみ発生すること があります。

## 特定命令

•Id命令:Id.b、Id.h、Id.w、Id.bu、Id.hu •sld命令:sld.b、sld.h、sld.w、sld.bu、sld.hu · 乗算命令 : mul、mulh、mulhi、mulu

## 問題となる命令シーケンス例

例1 ①ld.w [r11],**r10**

2mov **r10** ,r28

3sld.w 0x28 ,r10

①のId命令の実行が完了する前に、③のsId命令の直前の mov命令(②)のデコード動作と割り込み要求が競合した 場合に問題が発生。

例2 ①ld.w [r11],**r10**

2cmp imm5, r10

(3)sld.w 0x28 ,r10

(4)bz label

①のId命令の実行が完了する前に、③のsId命令の直前の cmp命令(②)のデコード動作と割り込み要求が競合した 場合に問題が発生。この結果、cmp命令の比較結果が不正 になり、4の分岐命令が不正動作することがある。

例3 ①ld.w [r11],**r10**

2 add imm5, **r10**

3sld.w 0x28 ,**r10**

4)setf r16

①のId命令の実行が完了する前に、③のsId命令の直前の add命令(②)のデコード動作と割り込み要求が競合した 場合に問題が発生。この結果、add命令の演算結果、及び フラグが不正になり、④のsetf命令の実行結果が不正に なることがある。

## 【発生条件の詳細】

以下の(1)~(3)の条件を全て満たした場合に問題が発生することがあります。

(1)以下の条件 I または II の条件に該当。

#### (条件 I )

特定命令(下記参照)のディスティネーション・レジスタ、ならびに、後続して実行されるsld命令 のディスティネーション・レジスタ、及び、その直前に実行される以下の命令のソース・レジスタ (reg1)が同じである(本文例1参照)。

mov reg1,reg2, not reg1,reg2, satsubr reg1,reg2, satsub reg1,reg2 satadd reg1,reg2, or reg1,reg2, xor reg1,reg2, and reg1,reg2 tst reg1,reg2, subr reg1,reg2, sub reg1,reg2, add reg1,reg2 cmp reg1,reg2. mulh reg1,reg2

#### (条件Ⅱ)

特定命令(下記参照)のディスティネーション・レジスタ、ならびに、後続して実行されるsld命令のディスティネーション・レジスタ、及び、その直前に実行される以下の命令のディスティネーション・レジスタ(reg2)が同じである(本文例2、3参照)。

not reg1,reg2, satsubr reg1,reg2, satsub reg1,reg2, satadd reg1,reg2 satadd imm5,reg2, or reg1,reg2, xor reg1,reg2, and reg1,reg2 tst reg1,reg2, subr reg1,reg2, subr reg1,reg2, add reg1,reg2 add imm5,reg2, cmp reg1,reg2, cmp imm5,reg2, shr imm5,reg2 sar imm5,reg2, shl imm5, reg2

## 特定命令

- ・Id命令 : Id.b、Id.h、Id.w、Id.bu、Id.hu ・sId命令: sId.b、sId.h、sId.w、sId.bu、sId.hu ・乗算命令 : mul、mulh、mulhi、mulu

- (2) CPUパイプライン中で、sld命令の直前の命令(上記条件 I または II の命令)のデコードが開始されるまでに、先に実行された特定命令の実行結果がディスティネーション・レジスタに格納されていない。

- (3)sld命令の直前の命令(上記条件 I または II の命令)のデコード動作と割り込み要求が競合。

#### 【対応策】

CPU機能に関する使用制限事項として、コンパイラにより該当命令シーケンスの生成を自動的に抑止するように致します。具体的な提供方法はご使用のコンパイラ毎に以下の通りとなります。その他のコンパイラをご使用の場合は弊社販売員または特約店を通じてご相談下さい。

## ·弊社製コンパイラ: CA850の場合

最新版(V2.60)に対策機能を追加したもの(V2.61)を下記サイトの開発ツール・ダウンロード・サービス(ODS;コンパイラ購入後の郵送によるユーザ登録が必要)にて提供させて頂きます。

http://www.necel.com/micro/ods/jpn/index.html

## •GHS製コンパイラ: CC850の場合

以下のバージョンについては、国内販売代理店(アドバンスド・データ・コントロールズ社)にて、対策機能を追加するバージョン・アップ対応をして頂く予定ですので、個別にお問い合わせをお願い致します。その他のバージョンに関しましては、お手数をお掛けしまして申し訳ございませんが、販売代理店にお問い合わせください。

•Multi4. 0 Rel 7. 0. 0 •Multi3. 5. 1 Rel 6. 5. 3

#### お問い合わせ先

TEL: 03-3576-6805 E-mail: upgv850e@adac.co.jp

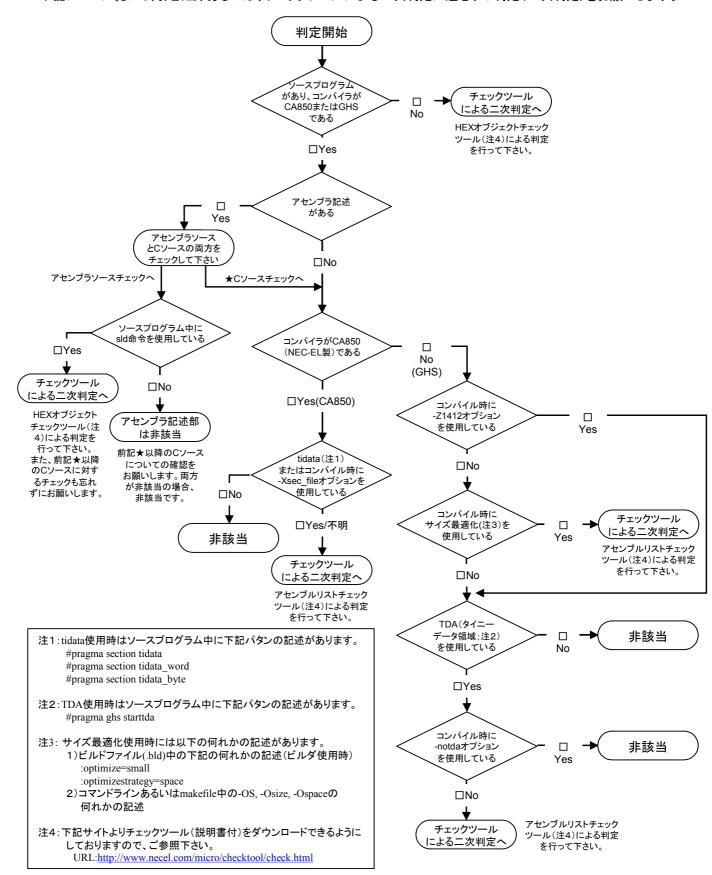

## 該非判定チェック・シート(一次判定用)

下記フローに従って、非該当、あるいは、チェックツールによる二次判定に進む、の判定(一次判定)をお願いします。