## RZ/T2H グループ

### Encoder I/F HIPERFACE DSL Safety sample program

#### 要旨

本書は、RZ/T2H Encoder I/F HIPERFACE DSL® Safety 仕様のサンプルプログラム・パッケージについて記載します。

#### 動作確認デバイス

RZ/T2H Evaluation Board (RTK9RZT2Hxxxxxxxx)

#### 目次

|                                               |    |

|-----------------------------------------------|----|

| 1. パッケージ内容 .....                              | 2  |

| 1.1 ソフトウェア .....                              | 2  |

| 1.2 ドキュメント .....                              | 2  |

| 2. ファイル構成 .....                               | 3  |

| 3. HIPERFACE DSL Safety サンプルプログラムについて .....   | 4  |

| 3.1 ソフトウェア情報 .....                            | 4  |

| 3.1.1 ベース OS .....                            | 4  |

| 3.1.2 メモリサイズ .....                            | 4  |

| 3.2 ハードウェア情報 .....                            | 5  |

| 3.2.1 デバイス .....                              | 5  |

| 3.2.2 ターゲットボード .....                          | 5  |

| 3.3 各開発環境における動作手順: CR52 版 .....               | 7  |

| 3.3.1 サンプルプログラム実行前の準備 .....                   | 7  |

| 3.3.2 EWARM: IAR システムズ社製 .....                | 7  |

| 3.3.3 e <sup>2</sup> studio: RENESAS 社製 ..... | 9  |

| 3.4 各開発環境における動作手順: CA55 版 .....               | 11 |

| 3.4.1 サンプルプログラム実行前の準備 .....                   | 11 |

| 3.4.2 EWARM: IAR システムズ社製 .....                | 11 |

| 3.4.3 e <sup>2</sup> studio: RENESAS 社製 ..... | 13 |

| 改訂記録 .....                                    | 15 |

## 1. パッケージ内容

本パッケージには次のものが含まれています。

RZ/T2H のエンコーダ I/F は 16 軸までに対応していますが、サンプルプログラムは、そのうちの 1 軸のみを使用しています。2 軸以上を同時に使用する場合は、サンプルプログラムを必要な軸の数に合わせて変更してください。

### 1.1 ソフトウェア

- ソースコード

| No. | 名称                                                           | 版数  |

|-----|--------------------------------------------------------------|-----|

| 1   | RZ/T2H HIPERFACE DSL Safety サンプルプログラム (CR52 版 <sup>注</sup> ) | 3.0 |

| 2   | RZ/T2H HIPERFACE DSL Safety サンプルプログラム (CA55 版 <sup>注</sup> ) | 3.0 |

**【注】** サンプルプログラムには、CPU コア Cortex-R52 で動作する CR52 版と、CPU コア Cortex-A55 で動作する CA55 版があります。CR52 版、CA55 版はそれぞれの版に関する説明です。

### 1.2 ドキュメント

| No. | 文書名                                                                 | 版数   | ファイル名                                                                                    |

|-----|---------------------------------------------------------------------|------|------------------------------------------------------------------------------------------|

| 1   | RZ/T2H グループ Encoder I/F HIPERFACE DSL Safety sample program リリースノート | 3.00 | (日) r11an0810jj0300-rzt2h.pdf (本書)<br>(英) r11an0810ej0300-rzt2h.pdf                      |

| 2   | RZ/T2H グループ HIPERFACE DSL Safety サンプルプログラム アプリケーションノート              | 3.00 | (日) r11an0809jj0300-rzt2h-hfdsl-safety.pdf<br>(英) r11an0809ej0300-rzt2h-hfdsl-safety.pdf |

## 2. ファイル構成

本パッケージのファイル構成と内容物の詳細を以下に示します。

Top

```

├── r11an0810jj0300-rzt2h.pdf

├── r11an0810ej0300-rzt2h.pdf

└── workspace

├── Software

│   ├── iccarm

│   │   ├── RZ_T2H_CR52_hfdsl.zip      : RZ/T2H HIPERFACE DSL Safety

│   │   └── RZ_T2H_CA55_hfdsl.zip      : RZ/T2H HIPERFACE DSL Safety

│   └── gcc

│       ├── RZ_T2H_CR52_hfdsl.zip      : RZ/T2H HIPERFACE DSL Safety

│       └── RZ_T2H_CA55_hfdsl.zip      : RZ/T2H HIPERFACE DSL Safety

└── Documents

├── r11an0809jj0300-rzt2h-hfdsl-safety.pdf

└── r11an0809ej0300-rzt2h-hfdsl-safety.pdf

```

RZ\_T2H\_CR52\_hfdsl.zip および RZ\_T2H\_CA55\_hfdsl.zip のファイル構成を以下に示します。

Top folder

```

├── configuration.xml           : FSP Configuration data

├── ( ビルドツール依存 環境ファイル )

└── src

├── hal_entry.c            : HIPERFACE DSL Safety サンプルプログラム

├── hfdsl_main.c            : HIPERFACE DSL Safety サンプルプログラム

├── siochar.c               : SCI_UART サンプルプログラム

├── siorw.c                : SCI_UART サンプルプログラム

├── sio_char.h              : SCI_UART サンプルプログラム

└── drv

└── hfdsl

├── iodefine_hfdsl.h    : HFDSL レジスタ定義ファイル

├── r_hfdsl_rzt2.c       : HFDSL ドライバファイル

├── r_hfdsl_rzt2_config.h : HFDSL ドライバファイル

├── r_hfdsl_rzt2_dat.h   : HFDSL ドライバファイル

└── r_hfdsl_rzt2_if.h    : HFDSL ドライバファイル

```

### 3. HIPERFACE DSL Safety サンプルプログラムについて

HIPERFACE DSL Safety サンプルプログラム一式を使用するためには必要な情報を記載します。

#### 3.1 ソフトウェア情報

##### 3.1.1 ベース OS

本サンプルプログラムは OS に依存しません。

##### 3.1.2 メモリサイズ

本サンプルプログラムおよび、HFDSL ドライバが使用するメモリサイズは次表に示した通りです。表には、Flexible Software Package や、コンパイラの C 言語ライブラリで使われるメモリサイズは含まれません。

##### (1) CR52 版

| 領域名        |               | 開発環境別メモリサイズ       |                                   |

|------------|---------------|-------------------|-----------------------------------|

|            |               | EWARM<br>[kBytes] | e <sup>2</sup> studio<br>[kBytes] |

| HFDSL ドライバ | コード領域         | 5.0               | 3.8                               |

|            | データ領域 (初期値あり) | 0.0               | 0.0                               |

|            | データ領域 (初期値なし) | 0.8               | 0.8                               |

|            | 定数領域          | 0.4               | 0.4                               |

| サンプルプログラム  | コード領域         | 2.7               | 3.1                               |

|            | データ領域 (初期値あり) | 0.0               | 0.0                               |

|            | データ領域 (初期値なし) | 0.4               | 0.4                               |

|            | 定数領域          | 1.2               | 1.6                               |

##### (2) CA55 版

| 領域名        |               | 開発環境別メモリサイズ       |                                   |

|------------|---------------|-------------------|-----------------------------------|

|            |               | EWARM<br>[kBytes] | e <sup>2</sup> studio<br>[kBytes] |

| HFDSL ドライバ | コード領域         | 7.3               | 6.6                               |

|            | データ領域 (初期値あり) | 0.0               | 0.0                               |

|            | データ領域 (初期値なし) | 1.1               | 1.2                               |

|            | 定数領域          | 0.7               | 0.8                               |

| サンプルプログラム  | コード領域         | 4.4               | 5.3                               |

|            | データ領域 (初期値あり) | 0.0               | 0.0                               |

|            | データ領域 (初期値なし) | 0.4               | 0.4                               |

|            | 定数領域          | 1.3               | 1.3                               |

### 3.2 ハードウェア情報

#### 3.2.1 デバイス

RZ/T2H

#### 3.2.2 ターゲットボード

##### (1) ボード名

RZ/T2H Evaluation Board (RTK9RZT2Hxxxxxxxxx)

##### (2) ターゲットボードの設定

ターゲットボードの設定は以下の通りです。

SW1-6: OFF

SW2-1: ON, SW2-2: OFF

SW2-7: OFF

SW2-8: OFF

SW14-1: ON, SW14-2: OFF, SW14-3: ON, SW14-6: OFF (xSPI1 boot mode に設定)

CN39: 2-3pin 間をショート (VDD1833\_2 を 3.3V に設定)

CN40: 2-3pin 間をショート (VDD1833\_3 を 3.3V に設定)

CN78: 1-2pin 間をショート, 3-4pin 間と 5-6pin 間はオープン (VDD1833\_6 を 3.3V に設定)

##### (3) ターゲットボードの使用端子

エンコーダ I/F として使用する端子と、ターゲットボードのピンヘッダ端子との対応は以下の通りです。

| チャネル   | 端子名                 | ピンヘッダ端子 | 入出力 | I/O 電源ドメイン | 内容            |

|--------|---------------------|---------|-----|------------|---------------|

| HFDSL0 | ENCIFDI00 (dsl_in)  | CN2 #9  | 入力  | VDD33      | データ入力端子       |

|        | ENCIFDO00 (dsl_out) | CN2 #7  | 出力  | VDD33      | データ出力端子       |

|        | ENCIFOE00 (dsl_en)  | CN2 #5  | 出力  | VDD33      | ドライブ/レシーブ制御端子 |

| HFDSL1 | ENCIFDI01 (dsl_in)  | CN2 #8  | 入力  | VDD1833_3  | データ入力端子       |

|        | ENCIFDO01 (dsl_out) | CN2 #6  | 出力  | VDD1833_3  | データ出力端子       |

|        | ENCIFOE01 (dsl_en)  | CN2 #4  | 出力  | VDD1833_3  | ドライブ/レシーブ制御端子 |

| HFDSL2 | ENCIFDI02 (dsl_in)  | CN2 #17 | 入力  | VDD33      | データ入力端子       |

|        | ENCIFDO02 (dsl_out) | CN2 #15 | 出力  | VDD33      | データ出力端子       |

|        | ENCIFOE02 (dsl_en)  | CN2 #13 | 出力  | VDD33      | ドライブ/レシーブ制御端子 |

| HFDSL3 | ENCIFDI03 (dsl_in)  | CN2 #18 | 入力  | VDD33      | データ入力端子       |

|        | ENCIFDO03 (dsl_out) | CN2 #16 | 出力  | VDD33      | データ出力端子       |

|        | ENCIFOE03 (dsl_en)  | CN2 #14 | 出力  | VDD33      | ドライブ/レシーブ制御端子 |

| HFDSL4 | ENCIFDI04 (dsl_in)  | CN2 #27 | 入力  | VDD1833_5  | データ入力端子       |

|        | ENCIFDO04 (dsl_out) | CN2 #25 | 出力  | VDD1833_5  | データ出力端子       |

|        | ENCIFOE04 (dsl_en)  | CN2 #23 | 出力  | VDD33      | ドライブ/レシーブ制御端子 |

| HFDSL5 | ENCIFDI05 (dsl_in)  | CN2 #26 | 入力  | VDD1833_6  | データ入力端子       |

|        | ENCIFDO05 (dsl_out) | CN2 #24 | 出力  | VDD1833_6  | データ出力端子       |

|        | ENCIFOE05 (dsl_en)  | CN2 #22 | 出力  | VDD1833_6  | ドライブ/レシーブ制御端子 |

| チャネル    | 端子名                 | ピンヘッダ<br>端子 | 入出力 | I/O<br>電源 ドメイン | 内容            |

|---------|---------------------|-------------|-----|----------------|---------------|

| HFDSL6  | ENCIFDI06 (dsl_in)  | CN3 #9      | 入力  | VDD1833_3      | データ入力端子       |

|         | ENCIFDO06 (dsl_out) | CN3 #7      | 出力  | VDD1833_3      | データ出力端子       |

|         | ENCIFOE06 (dsl_en)  | CN3 #5      | 出力  | VDD1833_3      | ドライブ/レシーブ制御端子 |

| HFDSL7  | ENCIFDI07 (dsl_in)  | CN3 #8      | 入力  | VDD1833_3      | データ入力端子       |

|         | ENCIFDO07 (dsl_out) | CN3 #6      | 出力  | VDD1833_3      | データ出力端子       |

|         | ENCIFOE07 (dsl_en)  | CN3 #4      | 出力  | VDD1833_3      | ドライブ/レシーブ制御端子 |

| HFDSL8  | ENCIFDI08 (dsl_in)  | CN3 #17     | 入力  | VDD33          | データ入力端子       |

|         | ENCIFDO08 (dsl_out) | CN3 #15     | 出力  | VDD33          | データ出力端子       |

|         | ENCIFOE08 (dsl_en)  | CN3 #13     | 出力  | VDD33          | ドライブ/レシーブ制御端子 |

| HFDSL9  | ENCIFDI09 (dsl_in)  | CN3 #18     | 入力  | VDD1833_2      | データ入力端子       |

|         | ENCIFDO09 (dsl_out) | CN3 #16     | 出力  | VDD1833_2      | データ出力端子       |

|         | ENCIFOE09 (dsl_en)  | CN3 #14     | 出力  | VDD1833_2      | ドライブ/レシーブ制御端子 |

| HFDSL10 | ENCIFDI10 (dsl_in)  | CN3 #27     | 入力  | VDD1833_2      | データ入力端子       |

|         | ENCIFDO10 (dsl_out) | CN3 #25     | 出力  | VDD1833_2      | データ出力端子       |

|         | ENCIFOE10 (dsl_en)  | CN3 #23     | 出力  | VDD1833_2      | ドライブ/レシーブ制御端子 |

| HFDSL11 | ENCIFDI11 (dsl_in)  | CN3 #26     | 入力  | VDD1833_2      | データ入力端子       |

|         | ENCIFDO11 (dsl_out) | CN3 #24     | 出力  | VDD1833_2      | データ出力端子       |

|         | ENCIFOE11 (dsl_en)  | CN3 #22     | 出力  | VDD1833_2      | ドライブ/レシーブ制御端子 |

| HFDSL12 | ENCIFDI12 (dsl_in)  | CN10 #9     | 入力  | VDD1833_6      | データ入力端子       |

|         | ENCIFDO12 (dsl_out) | CN10 #7     | 出力  | VDD1833_6      | データ出力端子       |

|         | ENCIFOE12 (dsl_en)  | CN10 #5     | 出力  | VDD1833_6      | ドライブ/レシーブ制御端子 |

| HFDSL13 | ENCIFDI13 (dsl_in)  | CN10 #8     | 入力  | VDD1833_6      | データ入力端子       |

|         | ENCIFDO13 (dsl_out) | CN10 #6     | 出力  | VDD1833_6      | データ出力端子       |

|         | ENCIFOE13 (dsl_en)  | CN10 #4     | 出力  | VDD1833_6      | ドライブ/レシーブ制御端子 |

| HFDSL14 | ENCIFDI14 (dsl_in)  | CN10 #17    | 入力  | VDD33          | データ入力端子       |

|         | ENCIFDO14 (dsl_out) | CN10 #15    | 出力  | VDD33          | データ出力端子       |

|         | ENCIFOE14 (dsl_en)  | CN10 #13    | 出力  | VDD33          | ドライブ/レシーブ制御端子 |

| HFDSL15 | ENCIFDI15 (dsl_in)  | CN10 #18    | 入力  | VDD33          | データ入力端子       |

|         | ENCIFDO15 (dsl_out) | CN10 #16    | 出力  | VDD33          | データ出力端子       |

|         | ENCIFOE15 (dsl_en)  | CN10 #14    | 出力  | VDD33          | ドライブ/レシーブ制御端子 |

### 3.3 各開発環境における動作手順: CR52 版

#### 3.3.1 サンプルプログラム実行前の準備

本サンプルプログラムでは、PC との通信を行います。ターゲットボードの USB 接続端子は、CN34 です。ホスト PC と接続したときに現れる COM ポートのうち、大きい番号のついたポートを選択します。ホスト PC のターミナルソフトは、次表のようになります。

| 機能          | 設定                |

|-------------|-------------------|

| 通信方式        | 調歩同期式 シリアル送信 / 受信 |

| 送信 / 受信順    | LSB ファースト         |

| 転送速度        | 19200 bps         |

| キャラクタ長      | 8 ビット             |

| ストップビット長    | 1 ビット             |

| parity 機能   | なし                |

| ハードウェアフロー制御 | なし                |

#### 3.3.2 EWARM: IAR システムズ社製

##### (1) ビルド環境

IAR Embedded Workbench for ARM (EWARM)

Version 9.60.3 + patch (EWARM\_Patch\_for\_RZT2H\_N2H\_rev1.0)

RENESAS FSP Smart Configurator (FSP SC) 2025-04.1

RENESAS Flexible Software Package (FSP) for RZ/T2 v3.0.0

##### (2) 実行環境 ICE

IAR I-jet

##### (3) サンプルプログラムのビルド手順

サンプルプログラムのビルド手順は以下の通り。

- 1 展開したソースファイルを任意の場所にコピーする。

- 2 EWARM を起動する。

- 3 [ファイル]メニュー→[ワークスペースを開く]を選択する。

- 4 展開したソースファイルの RZ\_T2H\_hfdsl.eww を開く。

- 5 EWARM IDE の[ツール]メニューから FSP Smart Configurator を起動する。 注

**【注】** 次の手順で、EWARM IDE の[ツール]メニューに FSP Smart Configurator の起動が加えられます。

EWARM IDE の[ツール]メニュー→[ツールの設定]を選択する。

[新規作成]ボタンを選択し、各フィールドに表の文字列を指定して、[OK]を押す。

| フィールド     | 文字列                              |

|-----------|----------------------------------|

| メニュー・テキスト | FSP Smart Configurator           |

| コマンド      | \$RASC_EXE_PATH\$                |

| 引数        | --compiler IAR configuration.xml |

| 初期ディレクトリ  | \$PROJ_DIR\$                     |

コマンド欄の文字列は、Smart Configurator 実行ファイル rasc.exe のパスを保持する変数です。なお、コマンドプロンプトから FSP Smart Configurator のインストール先フォルダを直接指定して起動することもできます。

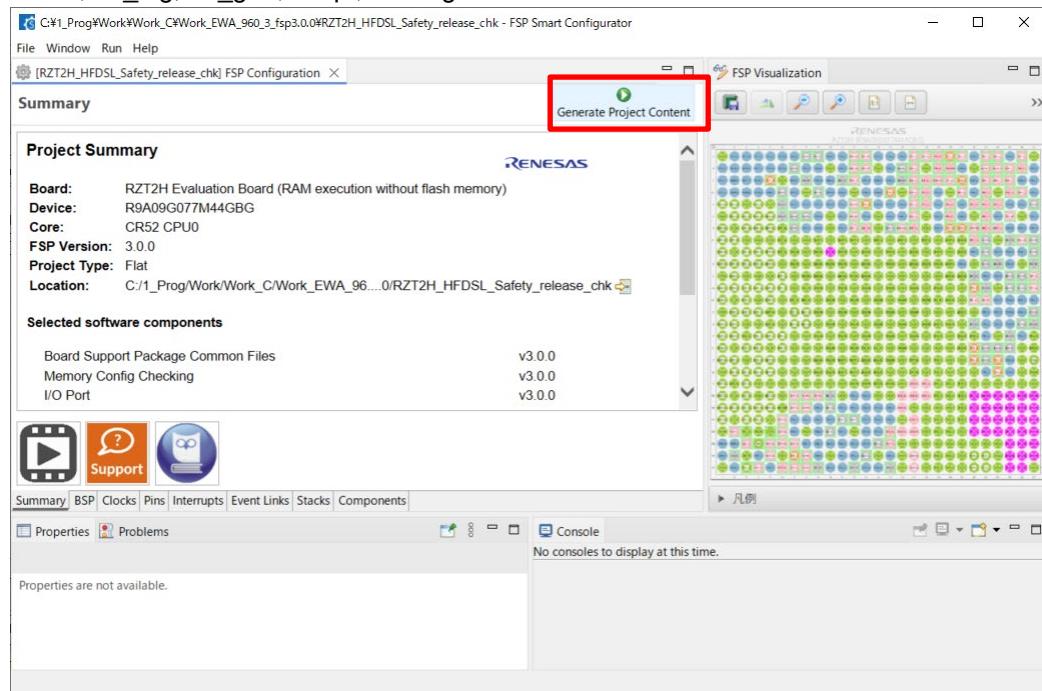

- 6 Smart Configurator の FSP Configuration ペインで、Generate Project Content をクリックする。

rzt, rzt\_cfg, rzt\_gen, script, .settings フォルダが生成される。

- 7 プロジェクト生成が完了したら、Smart Configurator を閉じる。

8 EWARM の[プロジェクト]メニュー→[すべてを再ビルト]を選択する。

ファイル Debug¥Exe¥RZ\_T2H\_hfdsl.out が生成される。

#### (4) サンプルプログラムの実行手順

「ビルト手順」を実行後、ターゲットボード、デバッガを正しく接続し、以下の操作を行う。

- [プロジェクト]メニュー→[ダウンロードしてデバッグ]を選択する。

- [デバッグ]メニュー→[実行]を選択する。

#### (5) サンプルプログラムの実行結果

サンプルプログラムを実行し、ターミナルソフトのウィンドウにコマンドを入力してください。コマンドについては、RZ/T2H グループ HIPERFACE DSL Safety サンプルプログラム アプリケーションノートの 4.11.6 コンソールコマンドを参照してください。

```

COM10 - Tera Term VT

ファイル(F) 編集(E) 設定(S) コントロール(O) ウィンドウ(W) ヘルプ(H)

HFDL Safety sample program start

R_HFDL_GetVersion = 3.0

hfDSL >pos

Fast position

Rotations : 0x00000FC2

Angle : 0x000BD0C1

Safe position

Rotations : 0x00000FC2

Angle : 0x000BD0C0

Error information

EVENT_ERR : 0x00000000

hfDSL >vel

Motor rotation speed

Speed : 0x00FFFFFF

Error information

EVENT_ERR : 0x00000000

hfDSL >

```

3.3.3 e<sup>2</sup> studio: RENESAS 社製

## (1) ビルド環境

RENESAS e<sup>2</sup> studio 2025-04.1

Toolchain version: GNU ARM Embedded 13.3.1.arm-13-24

RENESAS Flexible Software Package (FSP) for RZ/T2 v3.0.0

## (2) 実行環境 ICE

SEGGER J-Link<sup>TM</sup> v8.30

## (3) サンプルプログラムのビルド手順

サンプルプログラムのビルド手順は以下の通り。

- 1 展開したソースファイルを任意の場所にコピーする。

- 2 e<sup>2</sup> studio を起動し、ワークスペースへ移動後 [ファイル]メニュー→[インポート]をクリックし、一般 > 既存プロジェクトをワークスペースへ を選択して[次へ]をクリックする。

- 3 プロジェクトのインポート画面でルートディレクトリとしてサンプルプログラムを展開したフォルダを選択する。

- 4 プロジェクトを選択し、プロジェクトをワークスペースにコピー をチェックして [終了]をクリックする。

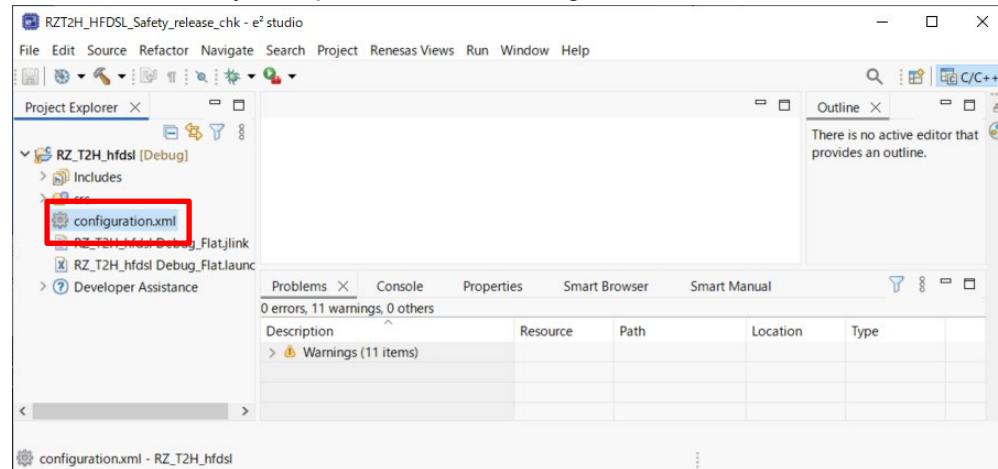

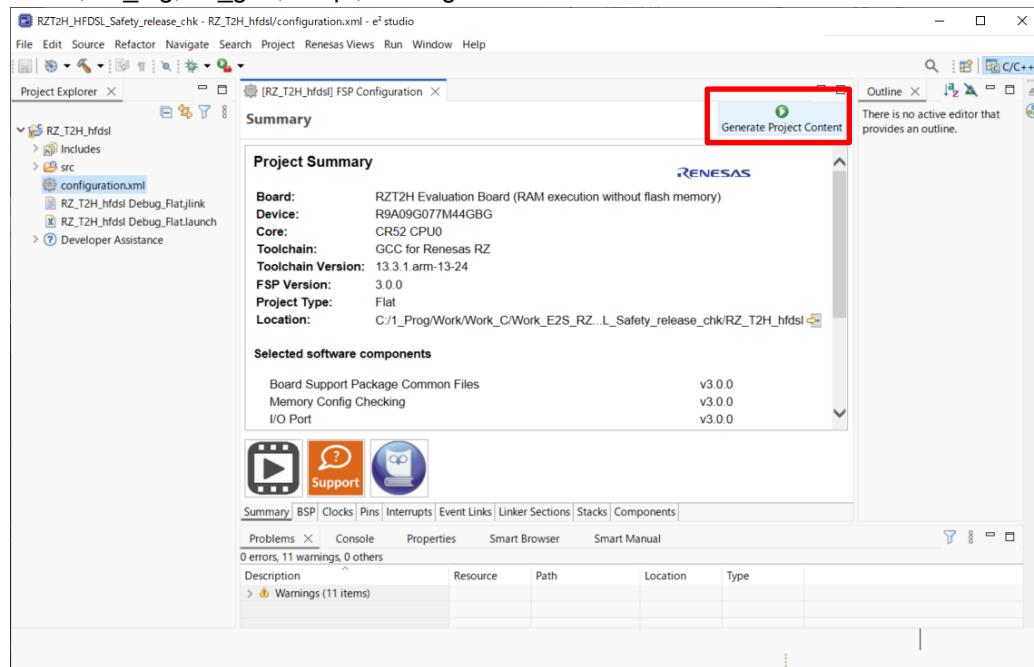

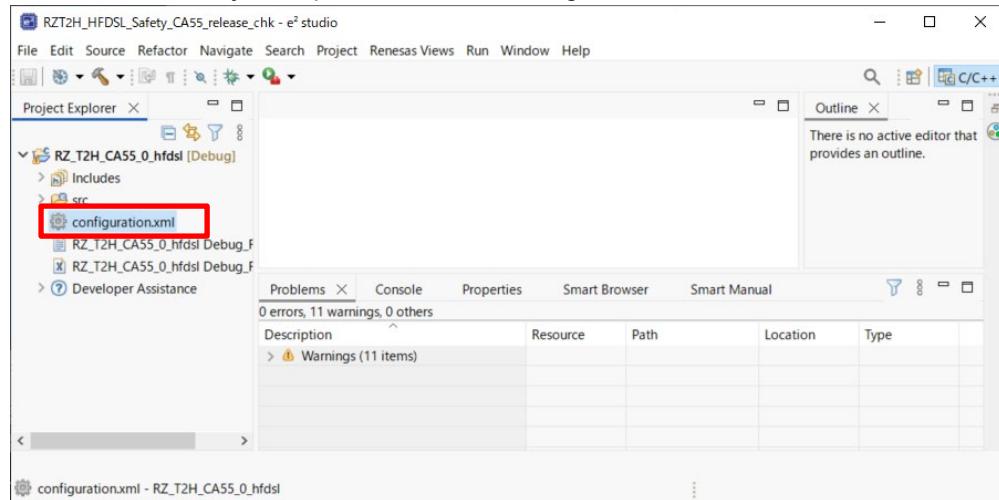

- 5 e<sup>2</sup> studio の Project Explorer ペインで configuration.xml をダブルクリックして開く。

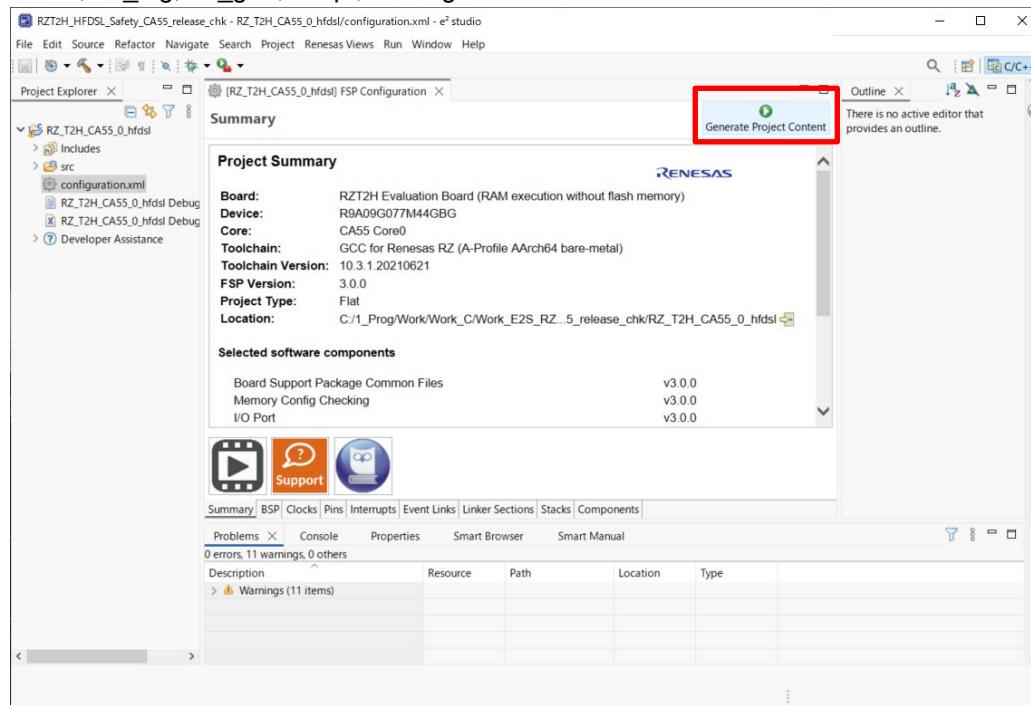

- 6 e<sup>2</sup> studio の FSP Configuration ペインで Generate Project Content をクリックする。

rzt, rzt\_cfg, rzt\_gen, script, .settings フォルダが生成される。

- 7 [プロジェクト]メニュー→[すべてビルド]を選択する。

ファイル Debug\RZ\_T2H\_hfdsl.elf が生成される。

#### (4) サンプルプログラムの実行手順

「ビルド手順」を実行後、ターゲットボード、デバッガを正しく接続し、以下の操作を行う。

- [実行]メニュー→[デバッグ]→[Renesas GDB Hardware Debugging]を選択する。

- [デバッグ]をクリックすると内蔵 RAM へのダウンロードを開始する。

- [実行]メニュー→[再開]をクリックすると、サンプルプログラムが実行される。

#### (5) サンプルプログラムの実行結果

サンプルプログラムを実行し、ターミナルソフトのウィンドウにコマンドを入力してください。コマンドについては、RZ/T2H グループ HIPERFACE DSL Safety サンプルプログラム アプリケーションノートの 4.11.6 コンソールコマンドを参照してください。

```

COM10 - Tera Term VT

ファイル(F) 編集(E) 設定(S) コントロール(O) ウィンドウ(W) ヘルプ(H)

HDSL Safety sample program start

R_HDSL_GetVersion = 3.0

hfDSL >pos

Fast position

Rotations : 0x00000FC2

Angle     : 0x000B09C1

Safe position

Rotations : 0x00000FC2

Angle     : 0x000B09C0

Error information

EVENT_ERR : 0x00000000

hfDSL >vel

Motor rotation speed

Speed : 0x00FFFFFF

Error information

EVENT_ERR : 0x00000000

hfDSL >

```

### 3.4 各開発環境における動作手順: CA55 版

#### 3.4.1 サンプルプログラム実行前の準備

本サンプルプログラムでは、PC との通信を行います。ターゲットボードの USB 接続端子は、CN34 です。ホスト PC と接続したときに現れる COM ポートのうち、小さい番号のついたポートを選択します。ホスト PC のターミナルソフトは、次表のようになります。

| 機能          | 設定                |

|-------------|-------------------|

| 通信方式        | 調歩同期式 シリアル送信 / 受信 |

| 送信 / 受信順    | LSB ファースト         |

| 転送速度        | 19200 bps         |

| キャラクタ長      | 8 ビット             |

| ストップビット長    | 1 ビット             |

| parity 機能   | なし                |

| ハードウェアフロー制御 | なし                |

#### 3.4.2 EWARM: IAR システムズ社製

##### (1) ビルド環境

IAR Embedded Workbench for ARM (EWARM)

Version 9.60.3 + patch (EWARM\_Patch\_for\_RZT2H\_N2H\_rev1.0)

RENESAS FSP Smart Configurator (FSP SC) 2025-04.1

RENESAS Flexible Software Package (FSP) for RZ/T2 v3.0.0

##### (2) 実行環境 ICE

IAR I-jet

##### (3) サンプルプログラムのビルド手順

サンプルプログラムのビルド手順は以下の通り。

- 1 RZ\_T2H\_CA55\_hfdsl.zip を展開し、展開したソースファイルを任意の場所にコピーする。

- 2 EWARM を起動する。

- 3 [ファイル]メニュー→[ワークスペースを開く]を選択する。

- 4 展開したソースファイルの RZ\_T2H\_CA55\_0\_hfdsl.eww を開く。

- 5 EWARM IDE の[ツール]メニューから FSP Smart Configurator を起動する。 注

**【注】** 次の手順で、EWARM IDE の[ツール]メニューに FSP Smart Configurator の起動が加えられます。

EWARM IDE の[ツール]メニュー→[ツールの設定]を選択する。

[新規作成]ボタンを選択し、各フィールドに表の文字列を指定して、[OK]を押す。

| フィールド     | 文字列                              |

|-----------|----------------------------------|

| メニュー テキスト | FSP Smart Configurator           |

| コマンド      | \$RASC_EXE_PATH\$                |

| 引数        | --compiler IAR configuration.xml |

| 初期ディレクトリ  | \$PROJ_DIR\$                     |

コマンド欄の文字列は、Smart Configurator 実行ファイル rasc.exe のパスを保持する変数です。

なお、コマンドプロンプトから FSP Smart Configurator のインストール先フォルダを直接指定して起動することもできます。

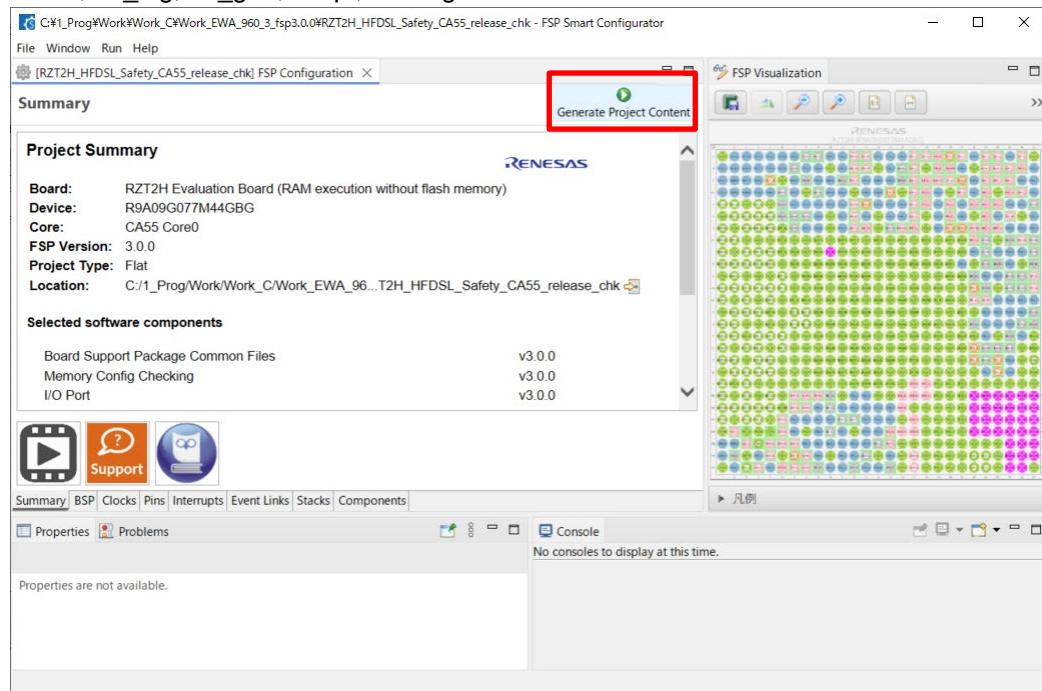

- 6 Smart Configurator の FSP Configuration ペインで、Generate Project Content をクリックする。

rzt, rzt\_cfg, rzt\_gen, script, .settings フォルダが生成される。

- 7 プロジェクト生成が完了したら、Smart Configurator を閉じる。

8 EWARM の[プロジェクト]メニュー→[すべてを再ビルト]を選択する。

ファイル Debug¥Exe¥ RZ\_T2H\_CA55\_0\_hfdsl.out が生成される。

#### (4) サンプルプログラムの実行手順

「ビルト手順」を実行後、ターゲットボード、デバッガを正しく接続し、以下の操作を行う。

- 1 [プロジェクト]メニュー→[ダウンロードしてデバッグ]を選択する。

- 2 [デバッグ]メニュー→[実行]を選択する。

#### (5) サンプルプログラムの実行結果

サンプルプログラムを実行し、ターミナルソフトのウィンドウにコマンドを入力してください。コマンドについては、RZ/T2H グループ HIPERFACE DSL Safety サンプルプログラム アプリケーションノートの 4.11.6 コンソールコマンドを参照してください。

```

COM9 - Tera Term VT

ファイル(F) 編集(E) 設定(S) コントロール(O) ウィンドウ(W) ヘルプ(H)

HFDL Safety sample program start

R_HFDSL_GetVersion = 3.0

hfDSL >pos

Fast position

Rotations : 0x00000FC2

Angle     : 0x000B09C3

Safe position

Rotations : 0x00000FC2

Angle     : 0x000B09C3

Error information

EVENT_ERR : 0x00000000

hfDSL >vel

Motor rotation speed

Speed     : 0x00FFFFFF

Error information

EVENT_ERR : 0x00000000

hfDSL >

```

3.4.3 e<sup>2</sup> studio: RENESAS 社製

## (1) ビルド環境

RENESAS e<sup>2</sup> studio 2025-04.1

Toolchain version: GCC ARM A-Profile (AArch64 bare-metal) 10.3.1.20210621

RENESAS Flexible Software Package (FSP) for R/T2 v3.0.0

## (2) 実行環境 ICE

SEGGER J-Link<sup>TM</sup> v8.30

## (3) サンプルプログラムのビルド手順

サンプルプログラムのビルド手順は以下の通り。

- 1 RZ\_T2H\_CA55\_hfDSL.zip を展開し、展開したソースファイルを任意の場所にコピーする。

- 2 e<sup>2</sup> studio を起動し、ワークスペースへ移動後 [ファイル]メニュー→[インポート]をクリックし、一般 > 既存プロジェクトをワークスペースへ を選択して[次へ]をクリックする。

- 3 プロジェクトのインポート画面でルートディレクトリとしてサンプルプログラムを展開したフォルダを選択する。

- 4 プロジェクトを選択し、プロジェクトをワークスペースにコピー をチェックして [終了]をクリックする。

- 5 e<sup>2</sup> studio の Project Explorer ペインで configuration.xml をダブルクリックして開く。

- 6 e<sup>2</sup> studio の FSP Configuration ペインで Generate Project Content をクリックする。

rzt, rzt\_cfg, rzt\_gen, script, .settings フォルダが生成される。

- 7 [プロジェクト]メニュー→[すべてビルド]を選択する。

ファイル Debug\RZ\_T2H\_CA55\_0\_hfDSL.elf が生成される。

#### (4) サンプルプログラムの実行手順

「ビルド手順」を実行後、ターゲットボード、デバッガを正しく接続し、以下の操作を行う。

- [実行]メニュー→[デバッグ]→[Renesas GDB Hardware Debugging]を選択する。

- [デバッグ]をクリックすると内蔵 RAM へのダウンロードを開始する。

- [実行]メニュー→[再開]をクリックすると、サンプルプログラムが実行される。

#### (5) サンプルプログラムの実行結果

サンプルプログラムを実行し、ターミナルソフトのウィンドウにコマンドを入力してください。コマンドについては、RZ/T2H グループ HIPERFACE DSL Safety サンプルプログラム アプリケーションノートの 4.11.6 コンソールコマンドを参照してください。

```

COM9 - Tera Term VT

ファイル(F) 編集(E) 設定(S) コントロール(O) ウィンドウ(W) ヘルプ(H)

HFDSL Safety sample program start

R_HFDSL_GetVersion = 3.0

hfDSL >pos

Fast position

Rotations : 0x00000FC2

Angle : 0x000B09C3

Safe position

Rotations : 0x00000FC2

Angle : 0x000B09C3

Error information

EVENT_ERR : 0x00000000

hfDSL >vel

Motor rotation speed

Speed : 0x00FFFFFF

Error information

EVENT_ERR : 0x00000000

hfDSL >el

```

## 改訂記録

| Rev. | 発行日       | 改訂内容                                    |                                                                                                                                                                                       |

|------|-----------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |           | ページ                                     | ポイント                                                                                                                                                                                  |

| 0.50 | Oct 31.23 | -                                       | 初版発行                                                                                                                                                                                  |

| 0.60 | Apr 26.24 | 2 - 4<br>5<br>1, 6<br>8 - 11<br>12 - 16 | アプリケーションノート、リリースノートの版数を更新。<br>サンプルプログラムを 0.6 版に更新。(FSP v1.3.0 に対応)<br>ファイル構成を更新。CA55 版の構成を追記。<br>メモリサイズ情報を更新。CA55 版の情報を追記。<br>ボード名の表記を更新。<br>CR52 版のビルド環境、説明図を更新。<br>CA55 版に関する説明を追記。 |

| 2.00 | Nov 21.24 | 2 - 4<br>5<br>6<br>8 - 17               | アプリケーションノート、リリースノートの版数を更新。<br>ソースコードを 2.0 版に更新。(ショートメッセージに対応。<br>FSP v2.2.0 に対応)<br>ファイル構成を更新。<br>メモリサイズ情報を更新。<br>ターゲットボードの設定に SW14 を追加。<br>ビルド環境を FSP v2.2.0 に合わせて更新し、図を差し替え。        |

| 2.01 | Dec 13.24 | 2, 3                                    | リリースノートの版数を更新<br>EWARM 用サンプルプログラム環境ファイル中の FSP SC の<br>パス名を、デフォルトインストールパスに修正。                                                                                                          |

| 3.00 | Aug 20.25 | 2, 3<br>4<br>7 - 14                     | アプリケーションノート、リリースノートの版数を更新。<br>ソースコードを 3.0 版に更新。(FSP v3.0.0 に対応)<br>ファイル構成を更新。<br>メモリサイズ情報を更新。<br>ビルド環境を FSP v3.0.0 に合わせて更新し、図を差し替え。                                                   |

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレー やマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSI の内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識され誤動作を起こす恐れがあります。

### 5. クロックについて

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子（または外部発振回路）を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子（または外部発振回路）を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

### 6. 入力端子の印加波形

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、 $V_{IL}$  (Max.) から  $V_{IH}$  (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、 $V_{IL}$  (Max.) から  $V_{IH}$  (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

### 7. リザーブアドレス（予約領域）のアクセス禁止

リザーブアドレス（予約領域）のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス（予約領域）があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

- HIPERFACE DSL is a registered trademark of SICK AG.

- IAR Embedded Workbench is a registered trademark of IAR Systems.

- J-Link is a trademark of SEGGER Microcontroller GmbH.

- Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

- Additionally all product names and service names in this document are a trademark or a registered trademark which belongs to the respective owners.

## ご注意書き

1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害（お客様または第三者いずれに生じた損害も含みます。以下同じです。）に関し、当社は、一切その責任を負いません。

2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行ふものではなく、また責任を負うものではありません。

3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準： コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準： 輸送機器（自動車、電車、船舶等）、交通制御（信号）、大規模通信機器、金融端末基幹システム、各種安全制御装置等

当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム（生命維持装置、人体に埋め込み使用するもの等）、もしくは多大な物的損害を発生させるおそれのある機器・システム（宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等）に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

7. あらゆる半導体製品は、外部攻撃からの安全性を 100% 保証されているわけではありません。当社ハードウェア／ソフトウェア製品にはセキュリティ対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害（当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。）から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為（「脆弱性問題」といいます。）によって影響を受けないことを保証しません。当社は、脆弱性問題に起因またはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア／ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

8. 当社製品をご使用の際は、最新の製品情報（データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等）をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的に支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

## 本社所在地

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

[www.renesas.com](http://www.renesas.com)

## お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

[www.renesas.com/contact/](http://www.renesas.com/contact/)

## 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の商標です。すべての商標および登録商標は、それぞれの所有者に帰属します。