#### ISL73847SLH

Neutron Test Results of the ISL73847SLH Radiation Hardened Single/Dual Phase Current Mode PWM Controller

#### Introduction

This report documents the results of 1MeV equivalent neutron testing of the ISL73847SLH, a synchronous buck controller that can operate as a single or dual phase controller. The testing was conducted to provide an assessment of the displacement damage (DD) hardness of the parts caused by neutron or proton environments. Neutron fluences ranged from 5×10<sup>11</sup>n/cm<sup>2</sup> to 1×10<sup>13</sup>n/cm<sup>2</sup>.

### **Product Description**

The ISL73847SLH is a synchronous buck controller that can operate as a single or dual phase controller. It is intended to work with the ISL73847SLH (half bridge GaN FET driver) to generate Point-Of-Load voltage rails for commercial space applications.

It accepts an input voltage range of 4.5V to 19V with a programmable output switching frequency between 250kHz and 1.5MHz with a single resistor. The output can regulate a voltage upwards of 600mV and is limited on the top end by the minimum off time and selected switching frequency.

The wide input voltage range makes it a suitable power supply option for a high current FPGA core and other general purpose power solutions. The ISL73847SLH uses current mode modulation which simplifies loop compensation and provides excellent power supply rejection. Additionally, the output is remotely sensed to compensate for any voltage drop in the load conditions. All of this put together results in a robust power supply solution that requires minimal components while achieving high current density.

The ISL73847SLH also features a tri-level output which provides excellent protection against faults by driving a mid-scale voltage to signal the power stage to enter a Hi-Z condition.

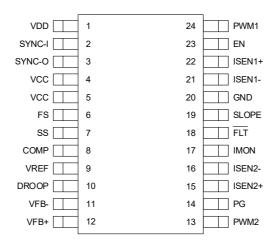

The ISL73847SLH is available in a 24 Ld WSOIC (300 mils). The package and pin assignments for the ISL73847SLH is shown in Figure 1.

Figure 1. Pin Assignments

The pin descriptions are shown in Table 1.

**Table 1. Pin Descriptions**

| The power supply input to the IC. The voltage range on this pin is 4.5V to 19V. Connect a 2.2μF or larger capacitor and a 100μG capacitor from the VDD pin to Colock 180.  This pin is an input that accepts 2x the required PWM output switching frequency (regardless of single or dual phase). Internally the IC divides the cock down to get two clocks 180° from each other for each phase. Note: This pin is an infraind pull down, leave if floating if SYNC function is not needed.  This pin can output either 1x or 2x the PVM output switching frequency depending on the loading present on the pin during power up (before soft-start). When output in its YNC-I on 180° out of phase with phase 1 clock. The 2x SYNC-O output is in phase with the SYNC-I on 180° out of phase with phase 1 clock. The 2x SYNC-O output is 17WM output switching frequency.  100kG to GND: SYNC-O output is 17WM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switching frequency.  100kG to GND: SYNC-O output 3x PVM output switchi                       | Pin<br>Number                                              | Pin Name                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 SYNC-I dual phase). Internally the IC divides the clock down to get two clocks 100° from each other for each phase. Note: This pin has an internal pull down, leave it floating if SYNC furction is not needed.  This pin can output either 1x or 2x the PWM output switching frequency depending on the loading present on the pin during power up (before soft-start). When outputing 1x, the SYNC-I is 180° out of phase with phase 1 clock. The 2x SYNC-O outputs 1x PWM output switching frequency.  100K0 to GND: SYNC-O outputs 2x PWM output switching frequency.  4, 5 VCC  Output of internal LDO for analog circuity. Short pins 4 and 5 together. Connect a 1μF ceramic capacitor from VCC to GND.  This pin sets the frequency for the internal oscillator between 0.5MHz and 3MHz. This sets the output between 0.25 MHz and 1.5MHz for each phase.  When FS is list of to VCC the internal oscillator frequency (flosc) is 1MHz. To adjust the internal oscillator frequency between 0.5MHz and 5MHz (0.25MHz to 1.5MHz PWM switching frequency), use a resistor between FS and GND. If SYNC-I is being used to sync to an external clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.  Yes Equation 3 in the datashete to find which resistor is needed for a given frequency.  This is the soft-start pin. Connect a caramic capacitor from SS to GND to set the soft-start ramp. The soft-start time is adjustable between 2ms and 200ms. Equation 24 in the datashete shows the relationship between the soft-start capacitor and soft-start time.  The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation, soft and the subject of the current sense amp output (sum for parallel with the type-2 series RC components.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This pin is the positive input for differential voltage feedback.  This pin is the power-good indicator. It is an open-drain output. Limit the                       | 1                                                          | VDD                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| the pin during power up (before soft-starf). When outputting it x, the SYNC-O is 180° out of phase with phase 1 clock. The 2x SYNC-O output is in phase with the SYNC-I.  100kΩ to GND: SYNC-O outputs 2x PWM output switching frequency.  Output of internal LDO for analog circuity. Short pins 4 and 5 together. Connect a 1μF ceramic capacitor from VCC to GND.  This pin sets the frequency for the internal oscillator between 0.5MHz and 3MHz. This sets the output between 0.25 MHz and 1.5MHz for each phase.  When FS is tee to VCC the internal oscillator frequency (f <sub>OSC</sub> ) is 1MHz. To adjust the internal oscillator between 0.5MHz and 3MHz (0.25MHz) to 1.5MHz 2 PVM switching frequency), use a resistor between FS and GND. If SYNC-I is being used to sync to an axternal clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.  Use Equation 3 in the datasheet to find which resistor is needed for a given frequency. Use Equation 3 in the datasheet to find which resistor is needed for a given frequency.  This is the soft-start pin. Connect a ceramic capacitor from SS to GND to set the soft-start ramp. The soft-start time is adjustable between 2ms and 200ms. Equation 24 in the datasheet shows the relationship between the soft-start capacitor and soft-start time.  The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.  The output of the Internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Short VREF and DROOP pin together to disable droop regulation. The voltage created by the internal voltage reference insert a resistor between VREF and DROOP to enable droop regulation. The voltage created by the internal voltage feedback.  This pin is the positive input for differential voltage feedback.  This pin is the positive input for the secondary phase current sense amplif            | 2                                                          | SYNC-I                                                                                              | dual phase). Internally the IC divides the clock down to get two clocks 180° from each other for each phase.                                                                                                                                                                                                                                                                                                                                                                                               |

| This pin sets the frequency for the internal oscillator between 0.5MHz and 3MHz. This sets the output between 0.25 MHz and 1.5MHz for each phase.  When FS is tied to VCC the internal oscillator frequency (f <sub>OSC</sub> ) is 1MHz. To adjust the internal oscillator frequency where 0.5MHz and 3MHz (0.5MHz to 1.5MHz PVM switching frequency), use a resistor between FS and GND. If SYNG-I is being used to sync to an external clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.  Use Equation 3 in the datasheet to find which resistor is needed for a given frequency.  This is the soft-start pin. Connect a ceramic capacitor from SS to GND to set the soft-start ramp. The soft-start time is adjustable between 2ms and 200ms. Equation 24 in the datasheet shows the relationship between the soft-start capacitor and soft-start time.  COMP  The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation adjustable. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.  The output of the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Thor VREF and DROOP pin together to disable droop regulation.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation.  This pin is the negative input for differential voltage feedback.  YEB+ This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is pin perates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin is n            | 3                                                          | SYNC-O                                                                                              | the pin during power up (before soft-start). When outputting 1x, the SYNC-O is 180° out of phase with phase 1 clock. The 2x SYNC-O output is in phase with the SYNC-I. $100k\Omega$ to VCC: SYNC-O outputs 1x PWM output switching frequency.                                                                                                                                                                                                                                                              |

| between 0.25 MHz and 1.5MHz for each phase.  When FS is teld to VCC the internal oscillator frequency (f <sub>Occ</sub> ) is 1MHz. To adjust the internal oscillator frequency between 0.5MHz and 3MHz (0.25MHz to 1.5MHz PWM switching frequency), use a resistor between FS and GND. If SYNC-1 is being used to sync to an external clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.  Jise Equation 3 in the datasheet to find which resistor is needed for a given frequency.  This is the soft-start pin. Connect a ceramic capacitor from SS to GND to set the soft-start tarm. The soft-start time is adjustable between 2ms and 200ms. Equation 24 in the datasheet shows the relationship between the soft-start dapacitor and soft-start time.  ROMP  The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.  The output of the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Short VREF and DROOP pin together to disable droop regulation.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop level.  This pin is the positive input for differential voltage feedback.  VFB- This pin is the positive input for differential voltage feedback.  PG This pin is the positive input for differential voltage feedback.  This pin is the positive input for the secondary phase. This pin needs a 100kΩ to GND.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is purp threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SLH, this pin outputs the summed average of the current sense amplifier.  This pin is input thre | 4, 5                                                       | VCC                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SS start time is adjustable between 2ms and 200ms. Equation 24 in the datasheet shows the relationship between the soft-start capacitor and soft-start time.  The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.  The output of the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Short VREF and DROOP pin together to disable droop regulation.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.  11 VFB- This pin is the negative input for differential voltage feedback.  12 VFB+ This pin is the positive input for differential voltage feedback.  13 PWM2 This pin is the positive input for the secondary phase. This pin needs a 100kΩ to GND.  14 PG This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  15 ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  17 Important pin is the negative input for the secondary phase current sense amplifier.  18 This pin is the negative input for the secondary phase current sense amplifier.  This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>ETMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault             | 6 FS                                                       |                                                                                                     | between 0.25 MHz and 1.5MHz for each phase. When FS is tied to VCC the internal oscillator frequency (f <sub>OSC</sub> ) is 1MHz. To adjust the internal oscillator frequency between 0.5MHz and 3MHz (0.25MHz to 1.5MHz PWM switching frequency), use a resistor between FS and GND. If SYNC-I is being used to sync to an external clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.                                                        |

| COMP compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.  The output of the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Short VREF and DROOP pin together to disable droop regulation.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.  This pin is the negative input for differential voltage feedback.  This pin is the positive input for differential voltage feedback.  This pin is the PWM output for the secondary phase. This pin needs a 100kΩ to GND.  This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is the negative input for the secondary phase current sense amplifier.  This pin outputs the summed average of the current sense amplifier.  This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is VFITMID- A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This pin is t                       | 7                                                          | start time is adjustable between 2ms and 200ms. Equation 24 in the datasheet shows the relationship |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| regulation. Short VREF and DROOP pin together to disable droop regulation.  This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.  11 VFB This pin is the negative input for differential voltage feedback.  12 VFB+ This pin is the positive input for differential voltage feedback.  13 PWM2 This pin is the PWM output for the secondary phase. This pin needs a 100kΩ to GND.  14 PG This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  15 ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  16 ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  17 IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SLH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  19 SLOPE This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                          | 8                                                          | COMP                                                                                                | compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2                                                                                                                                                                                                                                                                                                                                                                                                  |

| This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.  This pin is the negative input for differential voltage feedback.  This pin is the positive input for differential voltage feedback.  This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is the positive input for the secondary phase current sense amplifier.  This pin is the negative input for the secondary phase current sense amplifier.  This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                          | VREF                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12 VFB+ This pin is the positive input for differential voltage feedback.  13 PWM2 This pin is the PWM output for the secondary phase. This pin needs a 100kΩ to GND.  14 PG This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  15 ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  16 ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  17 IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  19 SLOPE This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  20 GND This is the ground reference for the ISL73847SLH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10 DROOP This output can be tied to the VREF pin through a |                                                                                                     | This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by                                                                                                                                                                                                                                                                                                                                                                                              |

| This pin is the PWM output for the secondary phase. This pin needs a 100kΩ to GND.  PG This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  RND This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                         | VFB-                                                                                                | This pin is the negative input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14 PG This pin is the power-good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.  15 ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  16 ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  17 IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  18 FLT This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  18 This pin's input threshold voltage is VFLTMID. A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  19 SLOPE This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  20 GND This is the ground reference for the ISL73847SLH.  21 ISEN1- This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12                                                         | VFB+                                                                                                | This pin is the positive input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| below 7.2mA.  15 ISEN2+ This pin is the positive input for the secondary phase current sense amplifier.  16 ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  17 IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  19 SLOPE This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  20 GND This is the ground reference for the ISL73847SLH.  11 ISEN1- This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                         | PWM2                                                                                                | This pin is the PWM output for the secondary phase. This pin needs a $100k\Omega$ to GND.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16 ISEN2- This pin is the negative input for the secondary phase current sense amplifier.  17 IMON This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  19 SLOPE This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  20 GND This is the ground reference for the ISL73847SLH.  11 ISEN1- This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                                                         | PG                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.  This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This is the ground reference for the ISL73847SLH.  This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                         | ISEN2+                                                                                              | This pin is the positive input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| This pin sequences the startup between the ISL73847SLH and compatible drivers. On the ISL73847SLH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This is the ground reference for the ISL73847SLH.  This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                         | ISEN2-                                                                                              | This pin is the negative input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to VCC for a proper high level.  This pin adjusts the slope compensation of the ISL73847SLH. Place a resistor in the range of 25kΩ to 100kΩ to adjust slope compensation.  This is the ground reference for the ISL73847SLH.  This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                         | IMON                                                                                                | This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.                                                                                                                                                                                                                                                                                                                                                                                                        |

| to adjust slope compensation.  20 GND This is the ground reference for the ISL73847SLH.  21 ISEN1- This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                         | FLT                                                                                                 | this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start).  This pin's input threshold voltage is V <sub>FLTMID</sub> . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because FLT is an open-drain output, use a 4.99kΩ typical pull-up resistor to |

| 21 ISEN1- This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                         | SLOPE                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                         | GND                                                                                                 | This is the ground reference for the ISL73847SLH.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22 ISEN1+ This pin is the positive input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                         | ISEN1-                                                                                              | This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                         | ISEN1+                                                                                              | This pin is the positive input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 1. Pin Descriptions (Cont.)

| Pin<br>Number | Pin Name | Description                                                                      |

|---------------|----------|----------------------------------------------------------------------------------|

| 23            | EN       | This pin is the chip enable for the ISL73847SLH.                                 |

| 24            | PWM1     | This pin is the PWM output for the primary phase. This pin needs a 100kΩ to GND. |

#### **Related Literature**

For a full list of related documents, visit our website:

- ISL73847SLH device page

- MIL-STD-883 Test Method 1017

## **Contents**

| 1. | Test I | Description                               | 4    |

|----|--------|-------------------------------------------|------|

|    | 1.1    | Irradiation Facilities                    | 4    |

|    | 1.2    | Test Fixturing                            | 4    |

|    | 1.3    | Radiation Dosimetry                       |      |

|    | 1.4    | Characterization Equipment and Procedures |      |

|    | 1.5    | Experimental Matrix                       | 4    |

| 2. | Test I | Results                                   | 4    |

|    | 2.1    | Attributes Data                           | 5    |

|    | 2.2    | Key Parameter Variables Data              | 5    |

| 3. | Discu  | ssion and Conclusion                      | . 39 |

| 4. | Revis  | ion History                               | . 39 |

| Α. | Repo   | rted Parameters                           | . 39 |

## 1. Test Description

#### 1.1 Irradiation Facilities

Neutron fluence irradiations were performed on the test samples on May 27, 2025, at the University of Massachusetts, Lowell (UMASS Lowell) fast neutron irradiator per Mil-STD-883G, Method 1017.2, with each part unpowered during irradiation. The target irradiation levels were 5×10<sup>11</sup>n/cm<sup>2</sup>, 2×10<sup>12</sup>n/cm<sup>2</sup>, and 1×10<sup>13</sup>n/cm<sup>2</sup>. The parts were shipped back to Renesas (Palm Bay, FL) for post-irradiation electrical testing.

### 1.2 Test Fixturing

No formal irradiation test fixturing is involved, as these DD tests are bag tests in the sense that the parts are irradiated with all leads unbiased.

### 1.3 Radiation Dosimetry

Table 2 shows dosimetry from UMASS Lowell indicating the total accumulated gamma dose and actual neutron fluence exposure levels for each set of samples.

| Irradiation | Requested Fluence (n/cm²) | Reactor<br>Power (kW) | Time (s) | Flux<br>(n/cm <sup>2</sup> -s) <sup>[1]</sup> , <sup>[2]</sup> | Gamma Dose<br>(rad(Si)) <sup>[3]</sup> | Measured Fluence<br>(n/cm <sup>2</sup> ) <sup>[4]</sup> |

|-------------|---------------------------|-----------------------|----------|----------------------------------------------------------------|----------------------------------------|---------------------------------------------------------|

| CRF#98191-C | 5.00E+11                  | 40                    | 262      | 3.06E+09                                                       | 119                                    | 6.12E+11                                                |

| CRF#98191-D | 2.00E+12                  | 80                    | 531      | 6.12E+09                                                       | 484                                    | 2.38E+12                                                |

| CRF#98191-E | 1.00E+13                  | 800                   | 266      | 6.12E+10                                                       | 2424                                   | 1.19E+13                                                |

**Table 2. Neutron Fluence Dosimetry Data**

## 1.4 Characterization Equipment and Procedures

Electrical testing was performed before and after irradiation using the Renesas production automated test equipment (ATE). All electrical testing was performed at room temperature.

## 1.5 Experimental Matrix

Testing proceeded in general accordance with the guidelines of MIL-STD-883 TM 1017. The experimental matrix consisted of 5 samples to be irradiated at 5×10<sup>11</sup>n/cm<sup>2</sup>, 5 to be irradiated at 2×10<sup>12</sup>n/cm<sup>2</sup>, and 5 to be irradiated at 1×10<sup>13</sup>n/cm<sup>2</sup>. The actual levels achieved, which are shown in Table 2, were 6.12×10<sup>11</sup>n/cm<sup>2</sup>, 2.38×10<sup>12</sup>n/cm<sup>2</sup>, and 1.19×10<sup>13</sup>n/cm<sup>2</sup>. Three control units were used.

The ISL73847SLH samples were drawn from Lot V6C685. Samples were packaged in the 24 Ld WSOIC.

### 2. Test Results

Neutron testing of the ISL73847SLH is complete and the results are reported in the balance of this report. It should be understood when interpreting the data that each neutron irradiation was performed on a different set of samples; this is not total dose testing, where the damage is cumulative. Each marker represents a different set of five samples. The line connecting them is for trend visualization only.

Dosimetry method: ASTM E-265

The neutron fluence rate is determined from Initial Testing of the New Ex-Core Fast Neutron Irradiator at UMass Lowell (6/18/02). Validated on 6/07/2011 under the Trident II D5LE neutron facility study by Navy Crane. Reaffirmed 8/1/17 using SACRR transistor transfer calibration based on ASTM F1855 – 15

<sup>3.</sup> Based on reactor power at 1000kW, the gamma dose is 41 ±5.3% krad(Si)/hr as mapped by TLD-based dosimetry.

<sup>4.</sup> Validated by S-32 flux monitors

#### 2.1 Attributes Data

Table 3 shows the ISL73847SLH attributes data.

**Table 3. Attributes Data**

| 1MeV Fluence, (n/cm²) |                | Sample Size | Pass <sup>[1]</sup> | Fail | Notes      |  |

|-----------------------|----------------|-------------|---------------------|------|------------|--|

| Planned               | Planned Actual |             | Sample Size Fass:   |      | Motes      |  |

| 5×10 <sup>11</sup>    | 6.12E+11       | 5           | 5                   | 0    | All passed |  |

| 2×10 <sup>12</sup>    | 2.38E+12       | 5           | 5                   | 0    | All passed |  |

| 1×10 <sup>13</sup>    | 1.19E+13       | 5           | 5                   | 0    | All passed |  |

<sup>1.</sup> A Pass indicates a sample that passes all post-irradiation datasheet limits.

### 2.2 Key Parameter Variables Data

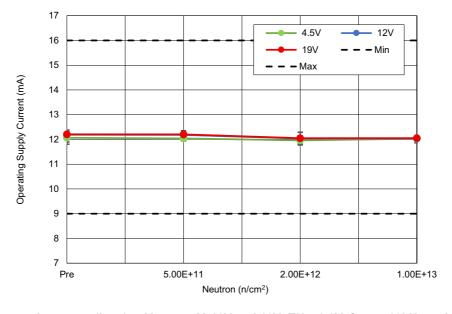

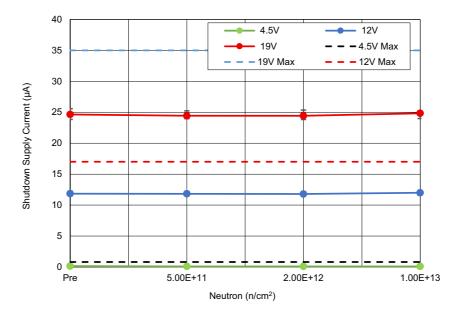

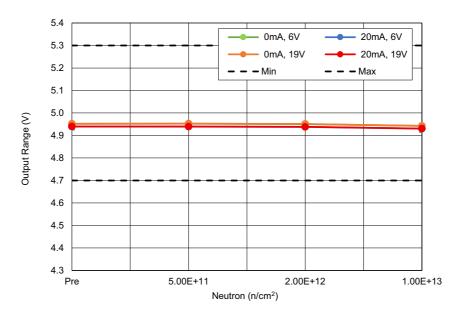

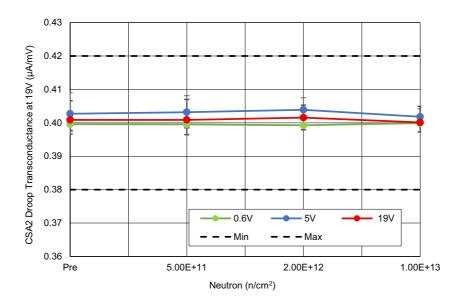

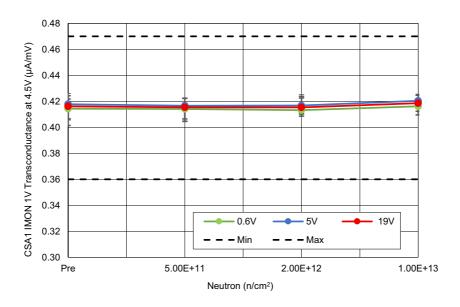

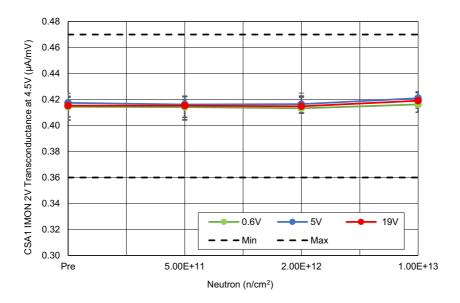

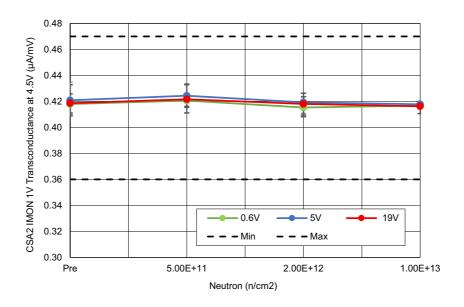

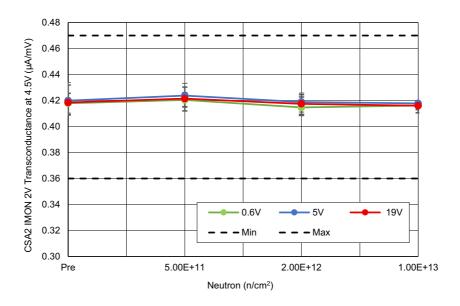

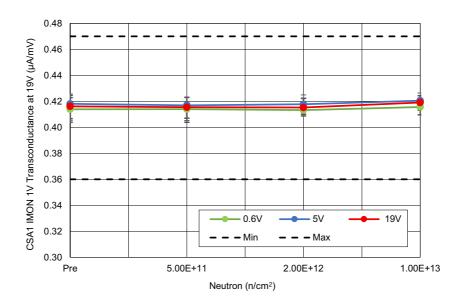

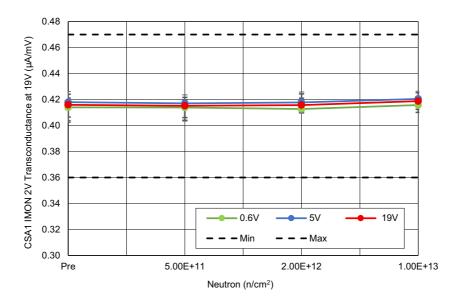

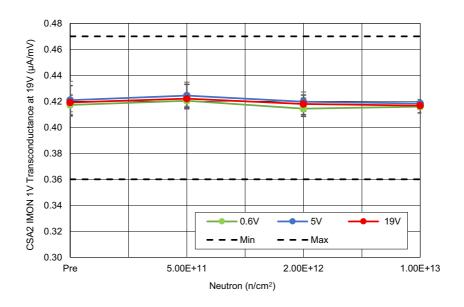

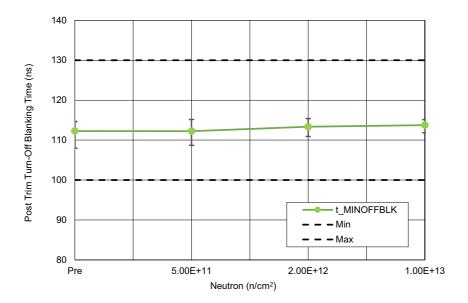

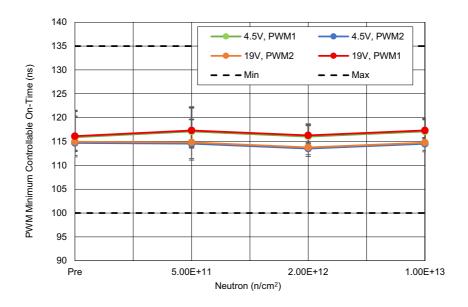

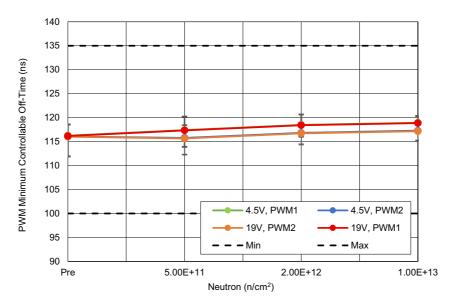

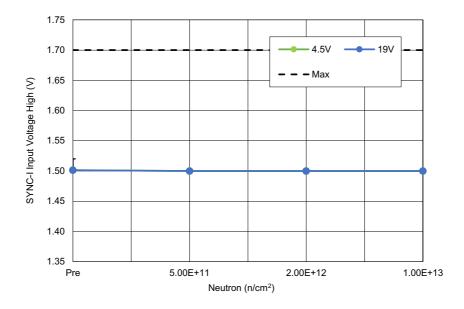

The plots in Figure 2 through Figure 68 illustrate the neutron irradiation response of the selected parameters shown in Table 4 in the Appendix. The plots show the average tested values of the parameters as a function of neutron fluence. The plots also include error bars at each down-point, representing the minimum and maximum measured values of the samples, although in some plots the error bars might not be visible due to their values compared to the scale of the graph.

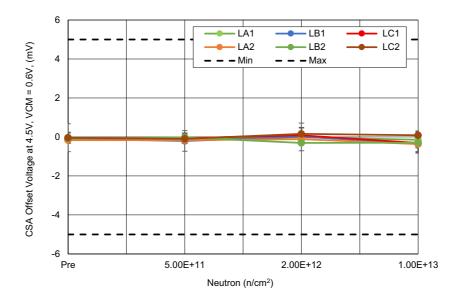

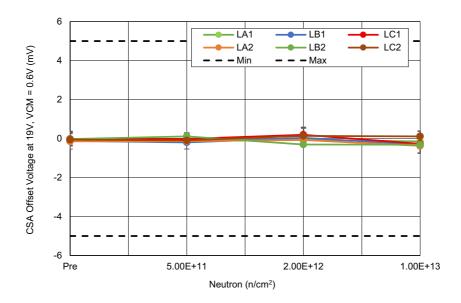

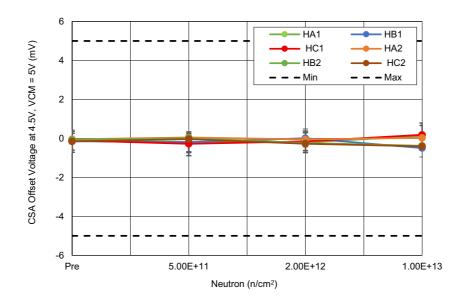

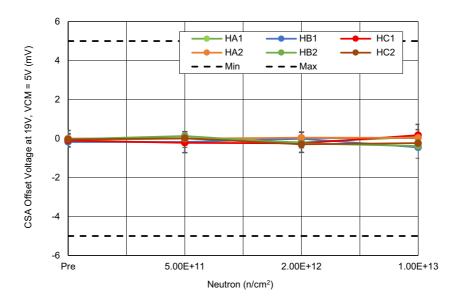

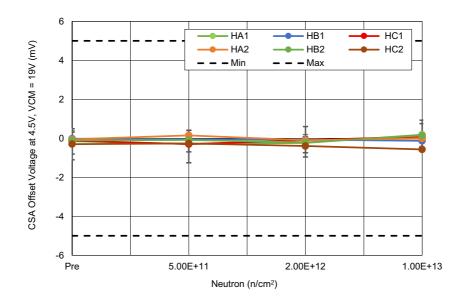

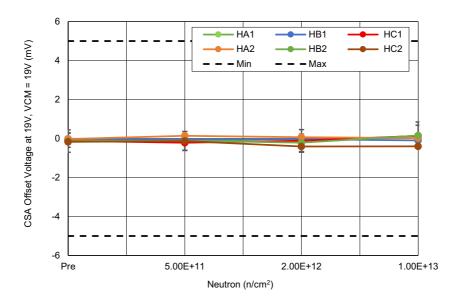

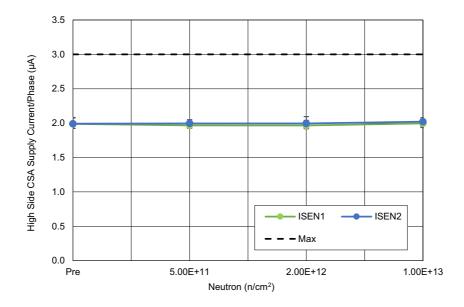

Each Current Sense Amp on the ISL73847SLH has triple redundancy for improved SEE tolerance and therefore has three current sense measurements. These are shown as LA, LB, LC (Low Side) in Figure 38 and Figure 39 and HA, HB, HC (High Side) in Figure 40 through Figure 43.

The irradiated parts passed all parameters up to the highest actual fluence of 1.19×10<sup>13</sup>n/cm<sup>2</sup>.

Figure 2. Operating supply current ( $I_{DDO}$ ) at  $V_{DD}$  = 4.5V, 12V and 19V; EN = 3.3V;  $f_{SW}$  = 500kHz and  $C_L$  = 100pF, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 9mA minimum and 16mA maximum.

Figure 3. Shutdown supply current ( $I_{DDSD}$ ) at  $V_{DD}$  = 4.5V, 12V and 19V; EN = GND, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limit is 35µA maximum at 19V, 17µA maximum at 12V and 0.8µA maximum at 4.5V.

Figure 4. LDO output voltage range ( $V_{CC}$ ) at  $V_{DD}$  = 6V and 19V;  $I_{OUT}$  = 0mA and 20mA, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 4.7V minimum and 5.3V maximum.

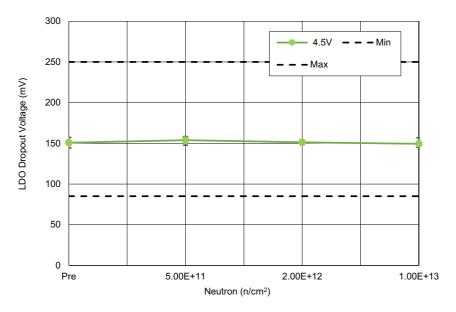

Figure 5. LDO dropout voltage (VCC $_{DO}$ ) at V $_{DD}$  = 4.5V; I $_{OUT}$  = 50mA, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 85mV minimum and 250mV maximum.

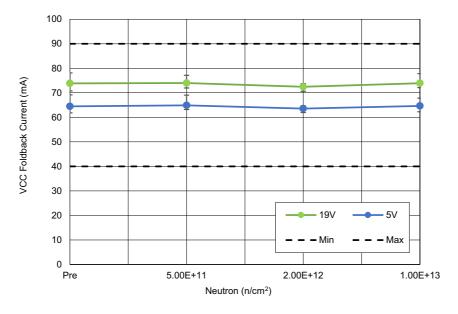

Figure 6.  $V_{CC}$  foldback current ( $I_{CC-SC}$ ) at  $V_{DD}$  = 5.5V and 19V;  $V_{CC}$  = 0V; EN = 1.6V, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 40mA minimum and 90mA maximum.

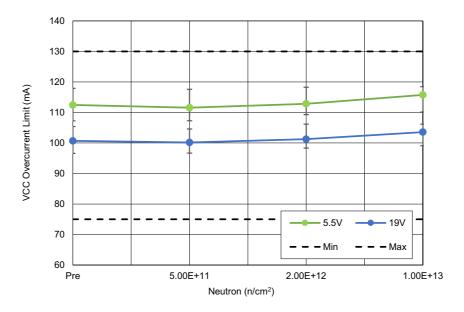

Figure 7.  $V_{CC}$  overcurrent limit ( $I_{CC-CL}$ ) at  $V_{DD}$  = 5.5V and 19V;  $V_{CC}$  = 4.3V; EN = 1.6V, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 75mA minimum and 130mA maximum.

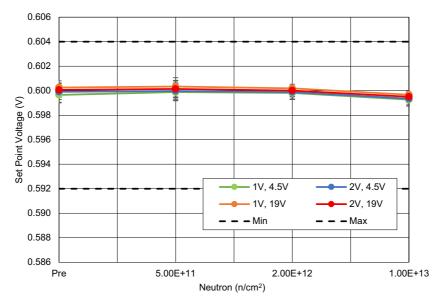

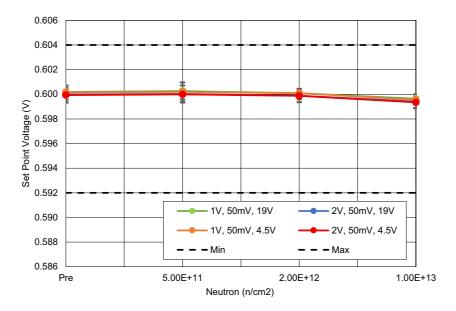

Figure 8. Set point voltage ( $V_{FB+}$ ), at  $V_{DD}$  = 4.5V and 19V;  $V_{REF}$  =  $V_{DROOP}$  = 1V and 2V;  $V_{SEN1}$  =  $V_{SEN2}$  = 0mV, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.592V minimum and 0.605V maximum.

Figure 9. Set point voltage ( $V_{FB+}$ ) at  $V_{DD}$  = 4.5V and 19V;  $V_{REF}$  =  $V_{DROOP}$  = 1V and 2V;  $V_{SEN1}$  =  $V_{SEN2}$  = 50mV, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 0.592V minimum and 0.605V maximum.

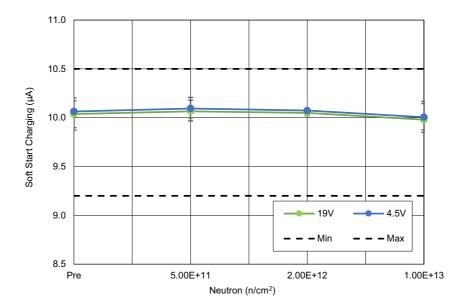

Figure 10. Soft-start sourcing current ( $I_{SOFTSTART}$ ) at  $V_{DD}$  = 4.5V and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 9.2 $\mu$ A minimum and 10.5 $\mu$ A maximum.

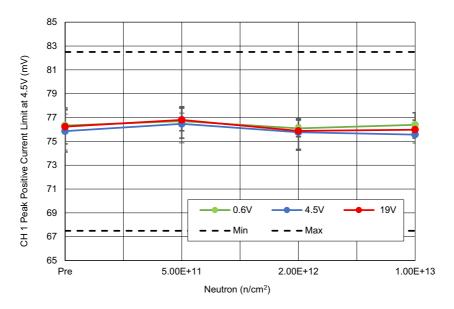

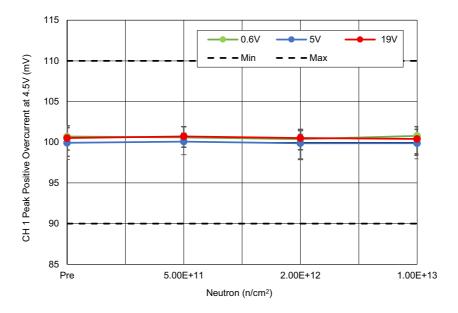

Figure 11. Channel 1 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

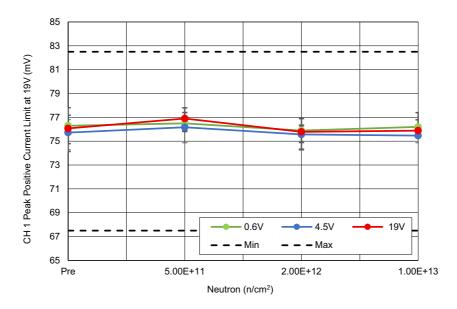

Figure 12. Channel 1 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

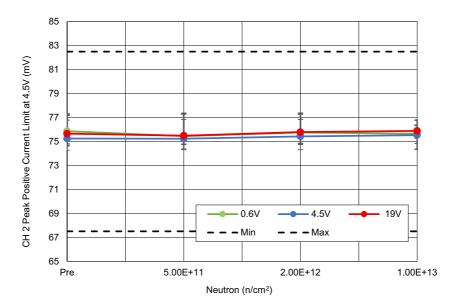

Figure 13. Channel 2 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

Figure 14. Channel 2 peak positive current limit ( $V_{PCL}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 67.5mV minimum and 82.5mV maximum.

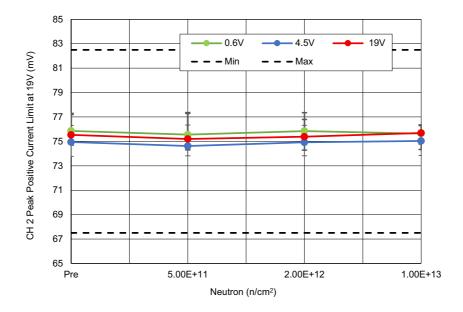

Figure 15. Channel 1 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

Figure 16. Channel 1 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

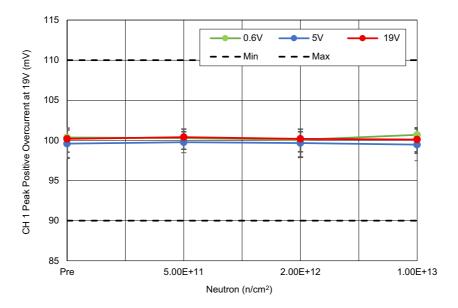

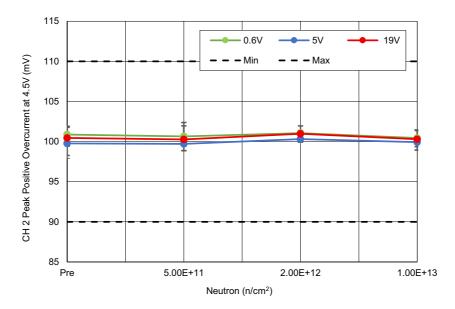

Figure 17. Channel 2 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

Figure 18. Channel 2 peak positive overcurrent ( $V_{POC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 90mV minimum and 110mV maximum.

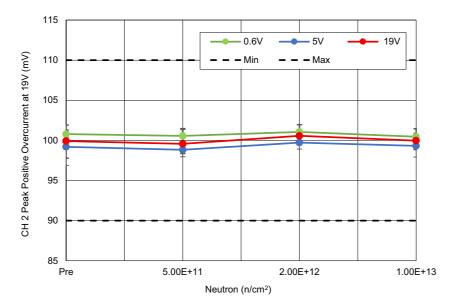

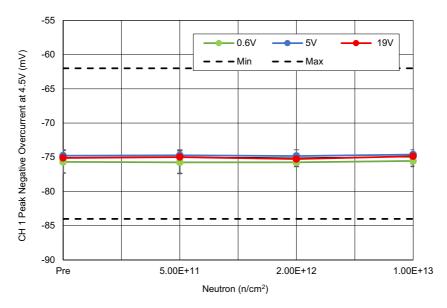

Figure 19. Channel 1 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -62mV maximum.

Figure 20. Channel 1 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -62mV maximum.

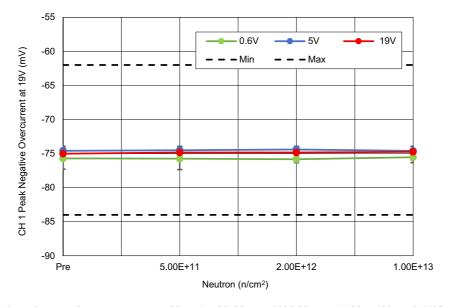

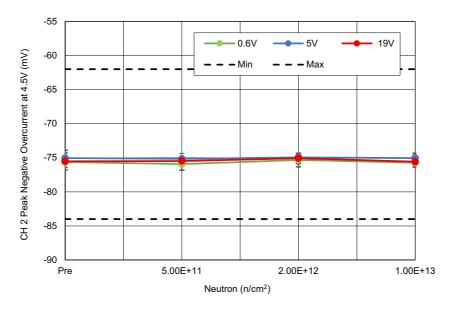

Figure 21. Channel 2 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 4.5V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -62mV maximum.

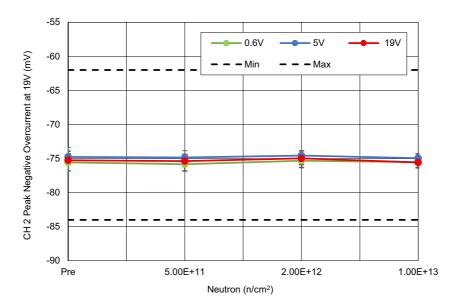

Figure 22. Channel 2 peak negative overcurrent ( $V_{NOC}$ ) with  $V_{DD}$  = 19V;  $V_{CM}$  = 0.6V, 5.0V, and 19V as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are -84mV minimum and -62mV maximum.

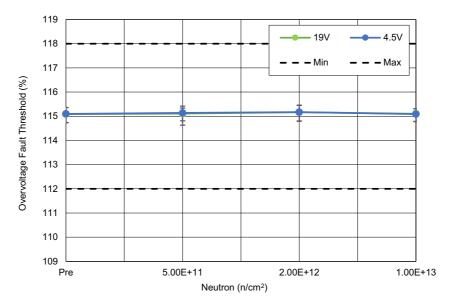

Figure 23. Overvoltage fault threshold ( $V_{FB, OV}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 112% minimum and 118% maximum.

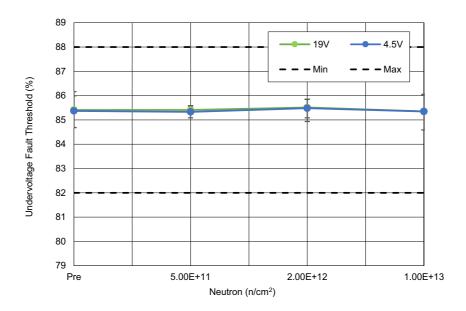

Figure 24. Undervoltage fault threshold ( $V_{FB, UV}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 82% minimum and 88% maximum.

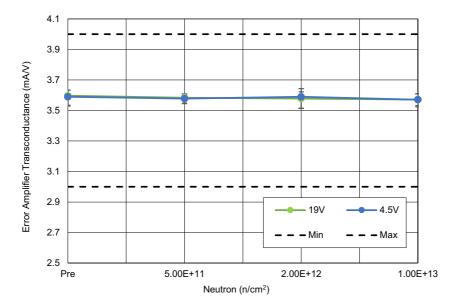

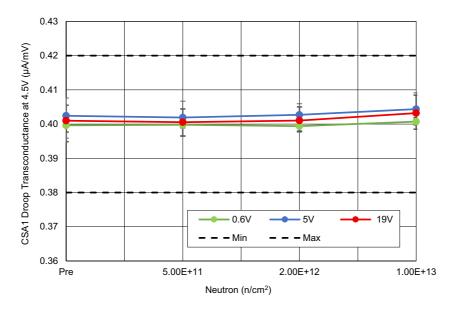

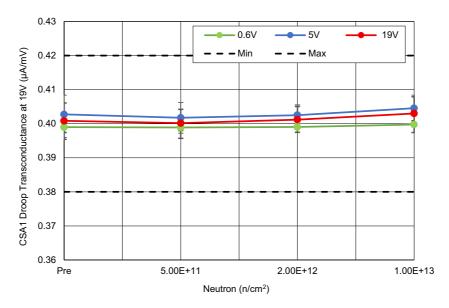

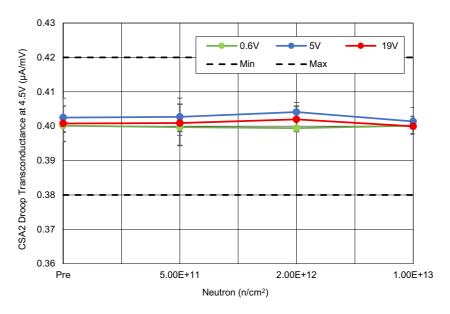

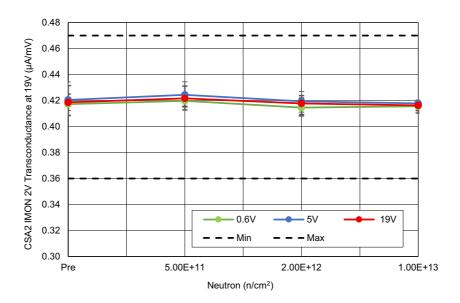

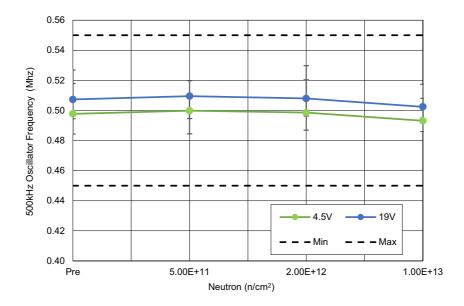

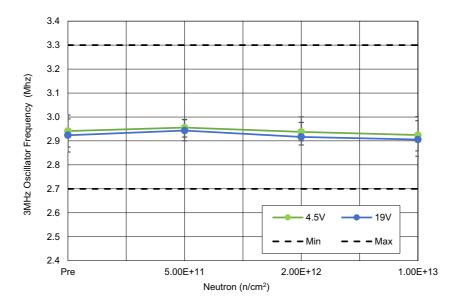

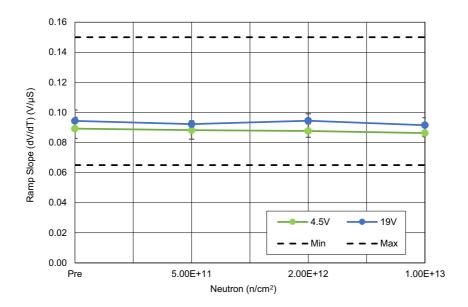

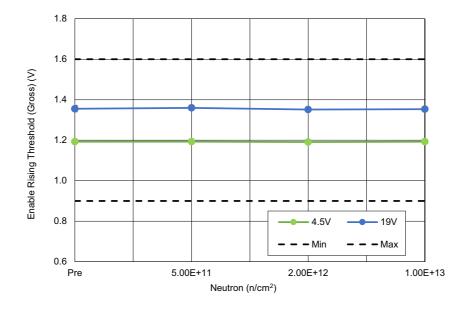

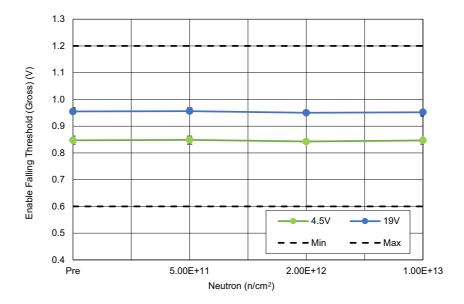

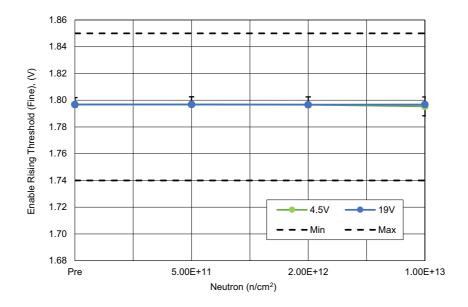

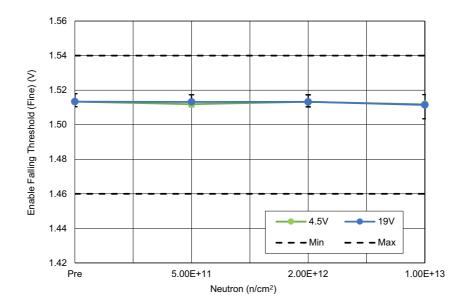

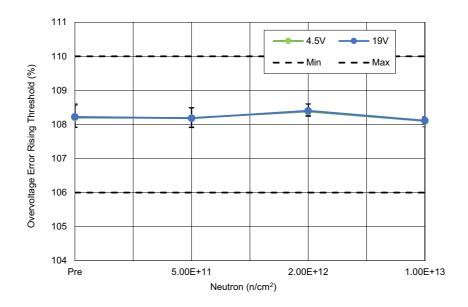

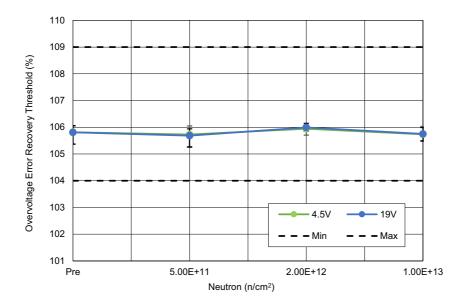

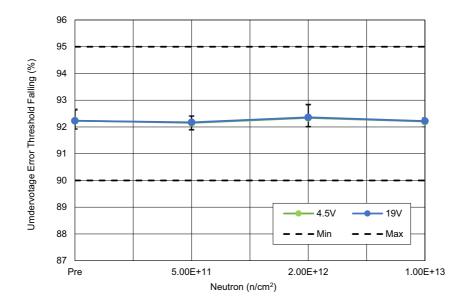

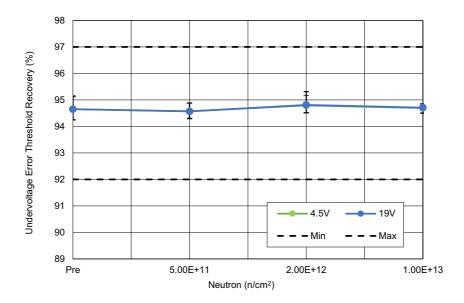

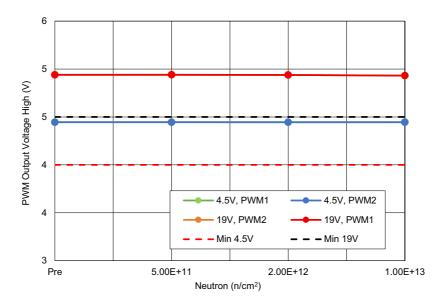

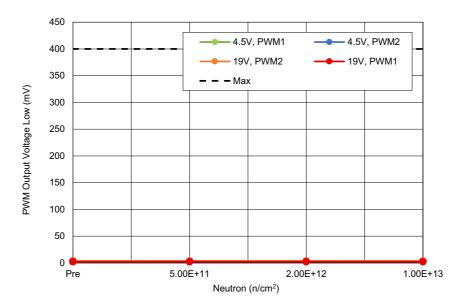

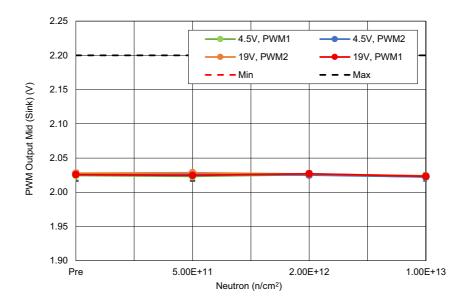

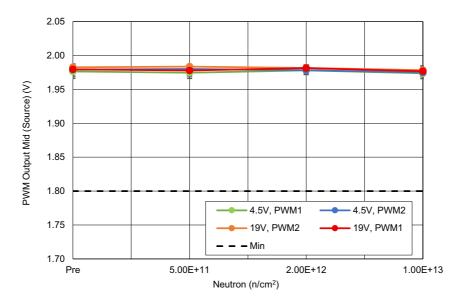

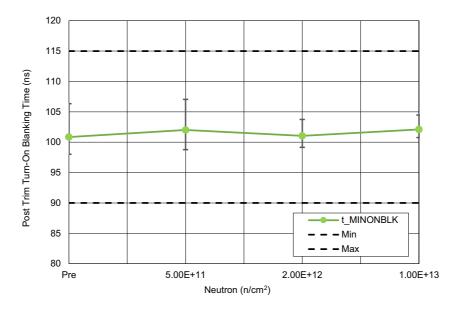

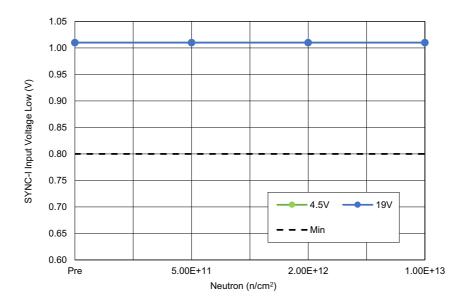

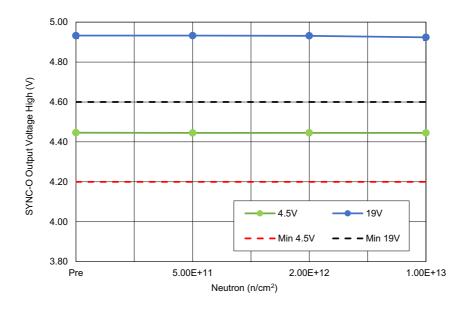

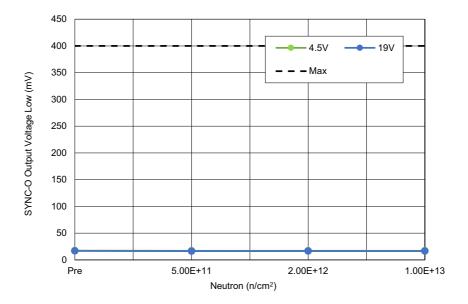

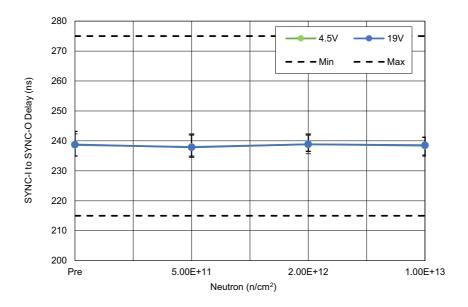

Figure 25. Error amplifier transconductance ( $g_{m-EA}$ ) with  $V_{DD}$  = 4.5V and 19V, as a function of neutron fluence. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation datasheet limits are 3mA/V minimum and 4mA/V maximum.