Going Beyond the HD-6409 Data Sheet

TB463 Rev.0.00 Jul 10, 2006

#### Oscillator

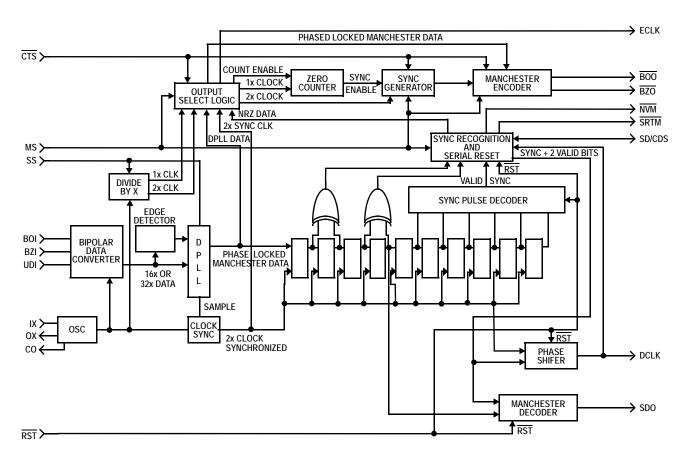

The oscillator circuit provides the clock signal for the entire HD-6409 Encoder/Decoder. The oscillator may be used by connecting a crystal between the IX and OX inputs, or IX may be driven by an external clock. The clock output (CO) is provided as a buffered output of the IX clock.

All gates of the oscillator circuit will be exercised when using a crystal to drive the HD-6409. The CO output should be tested to ensure it follows the IX clock input.

### **Decoder Section**

#### Bipolar Data Converter

The Bipolar Data Converter provides input for Manchester data at the BOI (Bipolar One Input) BZI (Bipolar Zero Input) and UDI (Unipolar Data Input). The UDI Input will accept only non-inverted BOI while the BOI and BZI inputs will accept data from differential input such as a comparator sense transformer and convert it to unipolar data through the

use of a latch and feedback gating. The incoming Manchester data is latched by the 16x or 32x oscillator clock thereby obtaining 16 or 32 data samples per bit period. These data samples are then passed on to the Edge Detect and Digital Phase Lock Loop Circuit.

The Bipolar Data Converter will be fully exercised by using either the decoder or repeater modes and functionally testing the HD-6409, both with the unipolar input and the bipolar input pair.

#### **Edge Detector**

The Edge Detector Circuit continuously monitors incoming Manchester data by latching it with the 16x or 32x oscillator clock. It then compares consecutive data samples by EXCLUSIVE—OR and identifies when a data edge (i.e. transition from '0' to '1' or '1' to '0') has occurred. The Edge Detector signal is passed to the DPLL circuit for sample timing purposes.

All Portions of the Edge Detector circuit are exercised during a standard decoder or repeater operation.

FIGURE 1. HD-6409 BLOCK DIAGRAM

## Digital Phase Lock Loop

The DPLL (Digital Phase Lock Loop) circuit provides the synchronizer for the HD-6409. The purpose of the synchronizer is to ensure that the receiver samples the incoming data at a point furthest from the data transition. This is necessary since signal waveforms have non-zero rise and fall times, and the data will be most stable at a point furthest from any data transitions. The DPLL circuit makes use of the 16x or 32x Clock, the Edge Detector and the Sample Counter. Depending upon whether the 16x or 32x speed is selected, two data points, Mid Count and End Count are initialized. Mid Count is nominally the time when the decoder expects a data transition, and End Count is the time when the decoder expects to sample. A sample is actually taken at one of two places, End Count or a Computed Final Count, based upon where data transition actually occurs with respect to Mid Count. If a transition occurs earlier than expected, the sample is taken one clock cycle early. If the transition occurs late, the sample is taken one clock cycle late. If no transition occurs, the sample is taken at the End Count. The advantage of the above algorithm and the DPLL synchronizer is that it can make adjustments for phase in either direction.

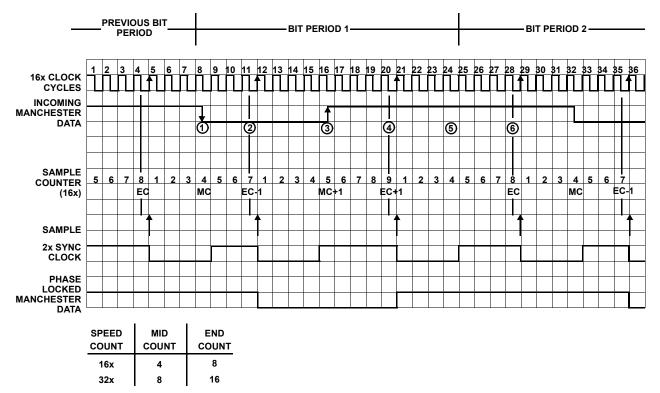

### **Decoder Sampling Timing Diagram**

Figure 2 shows examples of the Manchester data transitions occurring earlier than expected, later than expected and not at all. In the first case, the transition occurs at Mid Count 1, which the algorithm considers early, so the sample occurs at EC-1 2. In the second case, the transition occurs late at MC+1 3, and the sample is taken at EC+1 4. The last case

contains no transition at the time expected  $\mathfrak{G}$ , so the sample is taken at the End Count  $\mathfrak{G}$ .

Since the DPLL will make phase adjustments in either direction, the circuit may be tested by adjusting the Manchester data so that the transition randomly occurs at up to  $\pm 3$  oscillator clock periods from the mid-bit position. The DPLL circuit should adjust it's sampling accordingly and give the correct decode results.

#### Clock Synchronizer

The Clock Synchronizer circuit provides the decoder with a clock signal of 2 times the data rate synchronized with the phase locked Manchester data. This circuit consists of a low-time counter which counts to a value of 4 or 8 depending upon the speed selected, and toggles the clock to a high level. When DPLL circuit samples the incoming data, the counter is reset to '0' and the clock is brought low. The counter then begins its counting sequence again. Note that the 2x clock high time may vary depending upon where the DPLL sampling actually occurs (i.e. EC-1, EC or EC+1). Nominally, the 2x clock should have a high time and low time of 4 oscillator clock cycles (assuming 16x Clock speed). Figure 2 shows examples of the 2x clock being adjusted for synchronization with the incoming Manchester data. The high time is reduced to 3 oscillator clock periods when sampling occurs at EC-1 ②. It is increased to 5 oscillator clock periods, when sampling occurs at EC+1 (4), and remains at 4 oscillator clock periods when sampling actually occurs at EC 6. This counting and reset sequence is continuously repeated, thereby ensuring that the clock is synchronized with the Manchester data at all times.

The clock synchronizer circuit may also be tested in the same manner as the DPLL circuit.

FIGURE 2. DECODER SAMPLING TIMING DIAGRAM

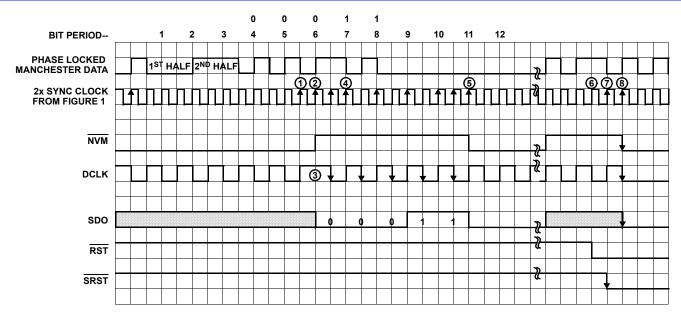

FIGURE 3. DECODER TIMING DIAGRAM

### Sync Pulse Decoder and Sync Recognition Circuits

The Sync Pulse Decoder and Sync Recognition circuits consist of a 10-stage shift register which is clocked by the 2x synchronous clock from the clock synchronizer circuit. It is continuously monitoring the phase locked Manchester data for a valid 5 bit wide pattern (i.e. a 3 bit sync pulse followed by a 2 valid Manchester bits). Since the sync pulse consists of 1½ bit periods in '1' or '0' state followed by 1½ bit periods in the opposite state, and valid Manchester data contains mid-bit transitions, there are 10 specific states which must be recognized in order to initiate synchronization. When these 10 states are recognized, a synchronization signal is sent to the phase shifter and Manchester decoder circuits.

This portion of the circuit may be tested by using the HD-6409 for a standard decoding operation while ensuring there is invalid data present both before and after the valid synchronization sequence and Manchester data. The NVM line should toggle to indicate the presence of the invalid data (refer to Figure 3).

### Phase Shifter

The Phase Shifter Circuit adjusts the phase of the DCLK output upon the receipt of a synchronization signal from the sync recognition circuit. The phase adjustment is necessary in order to ensure that the serial data output from the decoder will be phase matched with the DCLK so that the falling edges of DCLK may be used to latch the data from SDO.

The phase shifter may be tested by phase adjusting the input Manchester data with respect to the DCLK output signal. The DCLK signal should always go high coincident with the NVM recognition of a valid data sequence, or should remain high at this point and become 180° phase shifted. The following DCLK falling edge may then be used for latching the first serial data bit at SDO (refer to Figure 3).

## Manchester Decoder

The Manchester Decoder circuit provides the decoded Manchester data as serial NRZ data on the SDO output. This

data is provided coincident with the rising edge of DCLK so that the next DCLK falling edge may be used to latch the serial data to the external device.

The Manchester decoder will be fully exercised during a standard decoder operation.

#### **Decoder Timing Diagram**

Figure 3 further illustrates the relationships between the various decoder input and output signals. The phase locked Manchester data is shifted into the 10-stage shift register of the sync recognition circuit on every rising edge of the 2x synchronous clock (Note that the 2x clock signal is provided by the DPLL circuit and is continuously being adjusted to match the incoming data). Bit periods 1-5 provide the sync pulse and 2 valid Manchester bits. This data is shifted into sync recognition position at clock edge ①.

The NVM output will go high at the following clock edge ②, indicating valid data is being received. At this point, DCLK is also latched high regardless of its previous state (note that DCLK may change phase by 180° ③).

The first valid data bit will also be provided at the SDO (serial data out) at this clock edge ②.

Serial data will continue to be supplied to the SDO output at every other rising edge of the 2x synchronous clock 4. When invalid Manchester data is detected, the  $\overrightarrow{\text{NVM}}$  line will go low three synchronous clock periods after the invalid data is received.

At any time during a decoding operation, a low on  $\overline{RST}$  input 6 will force SRST (Serial Reset) low one clock cycle later 7. It will also force DCLK,  $\overline{NVM}$  and SDO low two synchronous clock cycles later 8.

### **Encoder Section**

#### Divide-By-X

The Divide-By-X circuit simply takes the incoming oscillator clock and reduces it to free running clock signals of 1 and 2 times the data rate. These clock signals are used by the encoder only.

#### **Output Select Logic:**

The Output Select Logic controls the data that is supplied to the remainder of the Encoder circuit. Depending upon the mode select, either the NRZ data is provided to the encoder, or the Phase-Lock Manchester data is provided to the Encoder circuit for output on the  $\overline{BOO}$ ,  $\overline{BZO}$  lines. The output select logic also controls which internal clock signal will drive the ECLK output. The 2x synchronous clock from the clock synchronizer circuit is used for the repeater mode, and the 1x free running clock is used for the encoder mode.

#### **Zeros Counter**

The Zeros Counter circuit, upon initiation of a count enable signal, begins counting the series of Manchester zeros being supplied by the encoder on the  $\overline{BOO}$ ,  $\overline{BZO}$  lines. The counting sequence is initiated by the assertion of the  $\overline{CTS}$  (Clear To Send) line. When the Zeros Counter reaches a count of eight (8), a sync enable signal will be issued to the Sync Generator circuit. The Zeros Counter is driven by the 1x free running clock.

### Sync Generator

The Sync Generator provides the sync pulse on the BOO and BZO outputs immediately following the eight Manchester zeros sequence. The Sync Generator will initiate the sync pulse when it receives a sync enable signal from the Zeros Counter.

#### Manchester Encoder

The Manchester Encoder circuit makes use of the 2x free running clock and the NRZ serial data. It provides the Manchester equivalent data sequence of the NRZ data stream

being latched into the SD/CDS pins. This circuit will also provide the phase-lock Manchester data from the DPLL circuit synchronous with the ECLK signal if operating in the repeater mode.

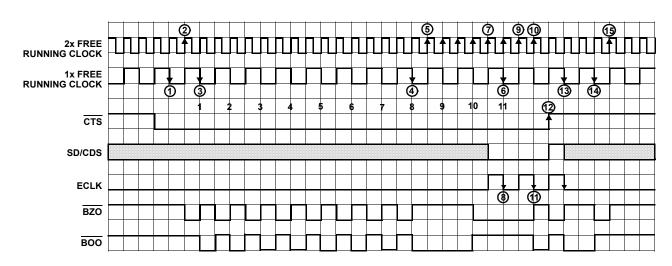

#### Encoder Input to Output Timing Diagram

Figure 4 illustrates the operation of the HD-6409 encoder section. The encoder operates with 1x and 2x free running clock signals taken from the 16x or 32x oscillator clock from the Divide-by-X circuit. The encoder outputs  $\overline{\text{BOO}}$  and  $\overline{\text{BZO}}$  will both remain high and ECLK will remain low while  $\overline{\text{CTS}}$  is not asserted. The encoder cycle begins when the  $\overline{\text{CTS}}$  control line is toggled to a '0' state. The next falling edge of the 1x clock ① latches the  $\overline{\text{CTS}}$  signal. The next rising edge of the 2x clock ② outputs the following:

$\overline{BZO} = \overline{1xCLK}$

$\overline{BOO} = 1xCLK$

The  $\overline{BOO}$  and  $\overline{BZO}$  output will continue to supply the 1x clock until the zeros counter reaches a count of eight (8). The Zeros Counter begins counting on falling edge  $\ 3$  of the 1x clock and continues counting on all following falling edges of the 1x clock until the sync enable count is reached at  $\ 4$ . The following rising edge of the 2x clock  $\ 5$  begins counting in the  $\ 5$  Sync Generator circuit and provides the sync pulse on the  $\ 6$  O and  $\ 7$  O outputs. When the Zeros Counter reaches a count of eleven  $\ 6$ , the sync enable signal becomes inactive, the Sync Generator is disabled, and NRZ data is allowed to be gated through to the encoder circuit.

FIGURE 4. ENCODER INPUT TO OUTPUT TIMING DIAGRAM

The rising edge of the 2x clock n latches ECLK to the inverted state of the 1x clock signal. ECLK will continue being latched on every rising edge of the 2x clock for the remainder of the encoder period. The first falling edge of the ECLK n latches the incoming NRZ data. The next rising edge of the 2x clock n latched the following:

$\overline{BOO} = \overline{NRZ}$  Data

BZO = NRZ Data

The next rising 2x clock edge 10 forces the outputs to change state, thereby completing the Manchester data bit and the falling edge of the ECLK 11 latches the next NRZ data bit.

Data will continue to be encoded in this fashion until the  $\overline{\text{CTS}}$  line is brought high. When  $\overline{\text{CTS}}$  goes high  $^{\textcircled{1}}$ , the next falling edge of the 1x clock forces ECLK low  $^{\textcircled{1}}$  and latches the last NRZ data bit. The following bit period  $^{\textcircled{1}}$  completes the final Manchester data bit. The next rising 2x clock edge  $^{\textcircled{1}}$  forces the  $\overline{\text{BOO}}$  and  $\overline{\text{BZO}}$  outputs to a logic '1' state.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system, Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

# Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited Dukes Meadow, Milliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0898, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd.

13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangiae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338