# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

μPD754144,754244

4ピット・シングルチップ・マイクロコンピュータ

μPD754144 μPD754244 [メ モ]

## 目次要約

第1章 概 説 ... 19

**第2章 端子機能** ... 26

第3章 アーキテクチャの特徴とメモリ・マップ ... 34

第4章 内部CPU機能 ... 63

第5章 EEPROM ... 83

第6章 周辺ハードウエア機能 ... 91

第7章 割り込み機能とテスト機能 ... 192

第8章 スタンバイ機能 ... 221

第9章 リセット機能 ... 234

第10章 マスク・オプション ... 240

第11章 命令セット ... 241

付録A 開発ツール ... 309

**付録B マスク**ROM**発注の手順** ... 313

**付録 C** 命令索引 ... 314

付録 D ハードウエア索引 ... 320

**付録 E 改版履歴** ... 325

#### CMOSデバイスの一般的注意事項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVDDまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

本製品をICカード (SMART CARD) に使用することはできません。

EEPROMは,日本電気株式会社の商標です。

MS-DOSは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。 IBM DOS, PC/AT, PC DOSは,米国IBM社の商標です。 本製品が外国為替および外国貿易管理法の規定による規制貨物等(または役務)に該当するか否かは,ユーザ (仕様を決定した者)が判定してください。

- 本資料の内容は予告なく変更することがありますので、最新のものであることをご確認の上ご使用ください。

- 文書による当社の承諾なしに本資料の転載複製を禁じます。

- 本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に 起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんの でご了承ください。

- 本資料に記載された回路,ソフトウエア,及びこれらに付随する情報は,半導体製品の動作例,応用例を説明するためのものです。従って,これら回路・ソフトウエア・情報をお客様の機器に使用される場合には,お客様の責任において機器設計をしてください。これらの使用に起因するお客様もしくは第三者の損害に対して,当社は一切その責を負いません。

- 当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

M7 98.8

### 本版で改訂された主な箇所

| 箇 所      | 内容                                                      |

|----------|---------------------------------------------------------|

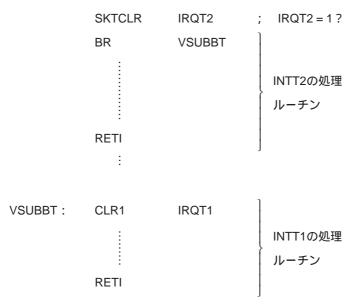

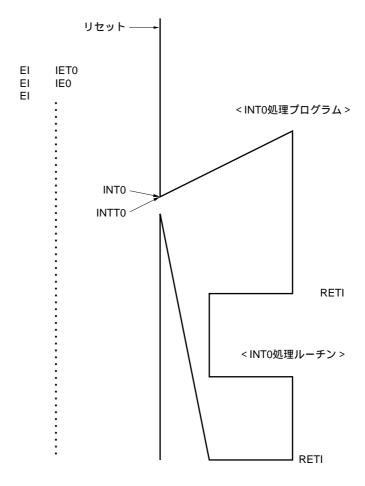

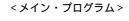

| p.216    | 7.9 割り込みの応用(6)保留割り込みの実行 割り込み処理中の割り込み発生(INTBT            |

|          | <b>を高位,</b> INTT0, INTT2 <b>を低位の割り込み)</b> の図中の記述を訂正     |

| p.260    | 11. <b>3 各命令の命令コード</b> の「BR BCDE」の命令コードを訂正              |

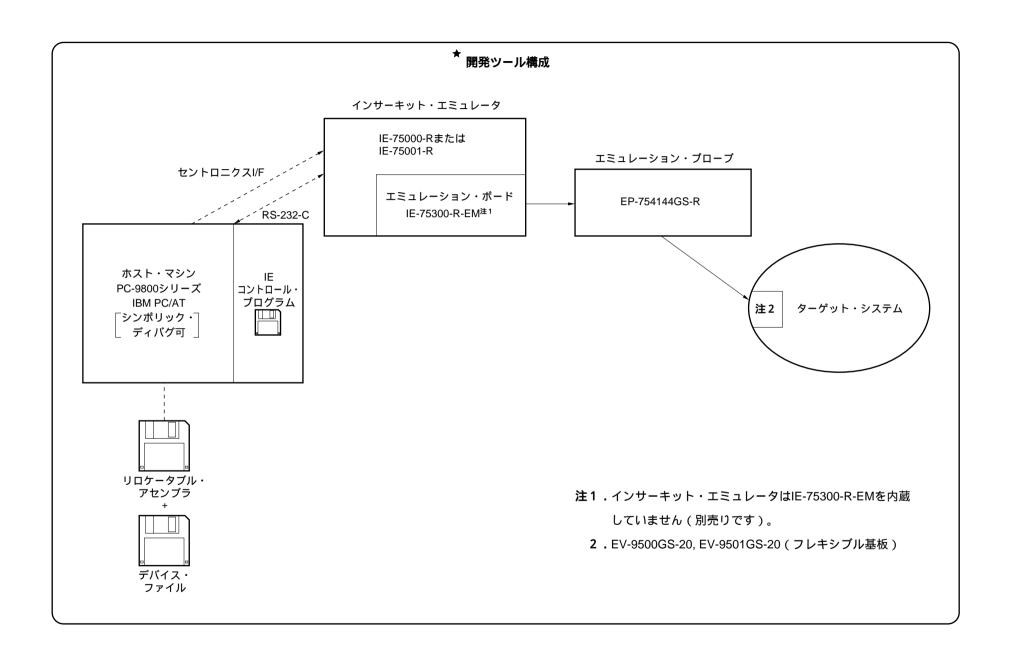

| p.312    | <b>付録A 開発ツール</b> の構成図のフラッシュ関連製品を削除                      |

| 旧版 p.297 | <b>付録A</b> μPD754144, 754244, 75F4264 <b>の機能一覧表</b> を削除 |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

### はじめに

- **ご 利 用** このマニュアルは, μPD754144, 754244の機能を理解し, それを用いたアプリケーション・シス

- 対象者 テムを設計するユーザのエンジニアを対象としています。

- **旬** の このマニュアルは,次の構成に示すμPD754144,754244の持つハードウエア機能をユーザに理解していただくことを目的としています。

- 構 成 このマニュアルは,大きく分けて次の内容で構成しております。

- 概 説

- ・端子機能

- ・アーキテクチャの特徴とメモリ・マップ

- ・内部CPU機能

- EEPROM™

- ・周辺ハードウエア機能

- ・割り込み機能とテスト機能

- ・スタンバイ機能

- ・リセット機能

- ・マスク・オプション

- ・命令セット

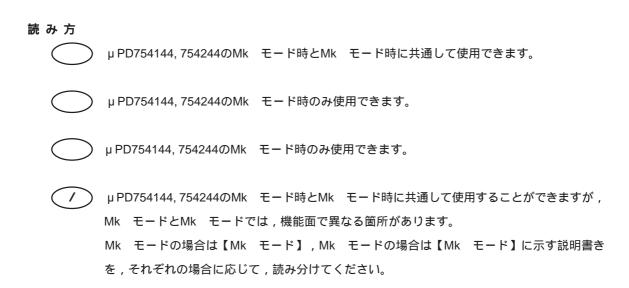

- 読み方 このマニュアルの読者は、電気、論理回路、マイクロコンピュータの一般的な知識を必要とします。

- μPD754144 (RC発振, fcc)のマニュアルとしてお使いになるユーザ

このマニュアルは、特に機能面で違いがないかぎり、μPD754244(クリスタル/セラミック発振, fx)を代表品種として説明してあります。1.3 μPD754144,754244の違いで機能の違いを確認したうえで、μPD754244を μPD754144に、fxをfccに読み替えて使用してください。

- ・ニモニックが分かっているときの命令機能を調べるとき 付録 C 命令索引を利用してください。

- 特定の内蔵回路などの機能を調べたいとき付録D ハードウエア索引を利用してください。

- ・一**通リ** μ PD754144 **,** 754244**の機能を理解しようとするとき** 目次に従って読んでください。

凡 例 データ表記の重み : 左が上位桁,右が下位桁

アクティブ・ロウの表記 : x x x ( 端子, 信号名称に上線 )

メモリ・マップのアドレス : 上部 - 下位, 下部 - 上位

注: 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数...××××または××××B

10進数...××××

16進数...××××H

★ 関連資料 関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

#### デバイス関連資料

| 資 料 名                         | 資料番号    |         |

|-------------------------------|---------|---------|

|                               | 和文      | 英文      |

| μPD754144, 754244 データ・シート     | U10040J | U10040E |

| μPD754144, 754244 ユーザーズ・マニュアル | このマニュアル | U10676E |

| 75XLシリーズ セレクション・ガイド           | U10453J | U10453E |

#### 開発ツール (ソフトウエア) の資料 (ユーザーズ・マニュアル)

| 資 料 名             |           | 資料      | 番号      |

|-------------------|-----------|---------|---------|

|                   |           | 和文      | 英 文     |

| RA75X アセンブラ・パッケージ | 操作編       | U12622J | U12622E |

|                   | 言語編       | U12385J | U12385E |

|                   | 構造化アセンブラ・ | U12598J | U12598E |

|                   | プリプロセッサ   |         |         |

#### 開発ツール (ハードウエア) の資料 (ユーザーズ・マニュアル)

| 資 料 名                                | 資料番号    |          |

|--------------------------------------|---------|----------|

|                                      | 和文      | 英 文      |

| IE-75000-R/IE-75001-R インサーキット・エミュレータ | U15337J | EEU-1455 |

| IE-75300-R-EM エミュレーション・ボード           | U11354J | U11354E  |

| EP-754144GS-R エミュレーション・プローブ          | U10695J | U10695E  |

#### その他の資料

| 資 料 名                          | 資料番号    |         |

|--------------------------------|---------|---------|

|                                | 和文      | 英 文     |

| 半導体総合セレクション・ガイド - 製品・パッケージ情報 - | X13769J | X13769E |

| 半導体デバイス 実装マニュアル                | 注       | C10535E |

| NEC半導体デバイスの品質水準                | C11531J | C11531E |

| NEC半導体デバイスの信頼性品質管理             | C10983J | C10983E |

| 静電気放電(ESD)破壊対策ガイド              | C11892J | C11892E |

| 半導体 品質 / 信頼性ハンドブック             | C12769J | -       |

| マイクロコンピュータ関連製品ガイド 社外メーカ編       | U11416J | -       |

注 「半導体デバイス実装マニュアル」のホーム・ページ参照

( http://www.ic.nec.co.jp/pkg/ja/jissou/index.html )

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 目 次

| 第1章               | 概 説 19                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2<br>1.3<br>1.4 | 機能概要 20<br>オーダ情報 21<br>µPD754144, 754244の違い 21<br>ブロック図 22<br>端子接続図(Top View) 23                                                                                                                                                                                                                                                                                                                                                   |

| 第2章               | <b>端子機能</b> 26                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2               | #PD754244の端子機能一覧 26<br>端子機能の説明 28<br>2.2.1 P30-P33 (PORT3), P60-P63 (PORT6), P80 (PORT8) 28<br>2.2.2 P70-P73 (PORT7) 28<br>2.2.3 PT00-PT02 28<br>2.2.4 INT0 29<br>2.2.5 KR4-KR7 29<br>2.2.6 KRREN 29<br>2.2.7 PTH00, PTH01 29<br>2.2.8 AVREF 30<br>2.2.9 CL1, CL2 ( μ PD754144のみ) 30<br>2.2.9 CL1, CL2 ( μ PD754244のみ) 30<br>2.2.11 RESET 30<br>2.2.12 IC 31<br>2.2.13 Vpp 31<br>3.2.2.14 Vss 31<br>端子の入出力回路 32<br>未使用端子の処理について 33 |

| 第3章               | アーキテクチャの特徴とメモリ・マップ 34                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2               | データ・メモリのバンク構成とアドレシング・モード 34<br>3.1.1 データ・メモリのバンク構成 34<br>3.1.2 データ・メモリのアドレシング・モード 36<br>汎用レジスタのバンク構成 48<br>メモリ・マップトI/O 53                                                                                                                                                                                                                                                                                                          |

| 第4章               | <b>内部</b> CPU <b>機能</b> 63                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2               | Mk モードとMk モードの切り替え機能 63<br>4.1.1 Mk モードとMk モードの違い 63<br>4.1.2 スタック・バンク選択レジスタ(SBS)の設定方法 64<br>プログラム・カウンタ(PC) 65<br>プログラム・メモリ(ROM) 66                                                                                                                                                                                                                                                                                                |

| 4.4 | データ・メモリ (RAM) 68                                    |

|-----|-----------------------------------------------------|

|     | 4.4.1 データ・メモリの構成 68                                 |

| 4 5 | 4.4.2 データ・メモリのバンクの指定 69                             |

|     | <b>汎用レジスタ</b> 72<br>アキュームレータ 73                     |

|     | ァキュームレータ /3<br>スタック・ポインタ(SP),スタック・バンク選択レジスタ(SBS) 73 |

|     | プログラム・ステータス・ワード (PSW) 77                            |

|     | バンク選択レジスタ (BS) 81                                   |

| 第5章 | EEPROM 83                                           |

| 5.1 | EEPROM <b>の構成</b> 83                                |

|     | EEPROM <b>の特徴</b> 83                                |

| 5.3 | EEPROM <b>ライト・コントロール・レジスタ (</b> EWC) 84             |

| 5.4 | EEPROM <b>の制御に関する割り込み</b> 85                        |

| 5.5 | EEPROM <b>の操作方法</b> 86                              |

|     | 5.5.1 EEPROMの操作命令 86                                |

|     | 5.5.2 読み出し操作 87                                     |

|     | 5.5.3 書き込み操作 88                                     |

| 5.6 | EEPROM <b>の書き込みに関する注意</b> 90                        |

| 第6章 | <b>周辺ハードウエア機能</b> 91                                |

| 6.1 | ディジタル入出力ポート 91                                      |

|     | 6.1.1 ディジタル入出力ポートの種類 , 特徴 , 構成 92                   |

|     | 6.1.2 入出力モードの設定 97                                  |

|     | 6.1.3 ディジタル入出力ポート操作命令 99                            |

|     | 6.1.4 ディジタル入出力ポートの動作 101                            |

|     | 6.1.5 プルアップ抵抗の内蔵 103                                |

| 6.3 | 6.1.6 ディジタル入出力ポートの入出力タイミング 104                      |

| 6.2 | <b>クロック発生回路</b> 106<br>6.2.1 クロック発生回路の構成 106        |

|     | 6.2.1 クロック先生回路の構成 106<br>6.2.2 クロック発生回路の機能と動作 108   |

|     | 6.2.3 CPUクロックの設定 115                                |

| 6.3 | ベーシック・インターパル・タイマ/ウォッチドッグ・タイマ 117                    |

|     | 6.3.1 ベーシック・インターバル・タイマ / ウォッチドッグ・タイマの構成             |

|     | 117                                                 |

|     | 6.3.2 ベーシック・インターバル・タイマ・モード・レジスタ(BTM)                |

|     | 118                                                 |

|     | 6.3.3 ウォッチドッグ・タイマ許可フラグ(WDTM) 120                    |

|     | 6.3.4 ベーシック・インターバル・タイマの動作 121                       |

|     | 6.3.5 ウォッチドッグ・タイマの動作 122                            |

|     | 6.3.6 その他の機能 124                                    |

| 6.4 | タイマ・カウンタ 126                                        |

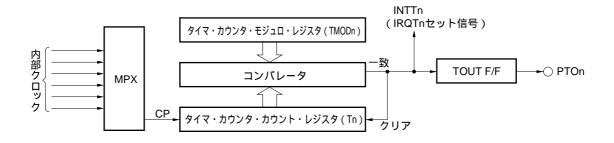

|     | 6.4.1 タイマ・カウンタの構成 126                               |

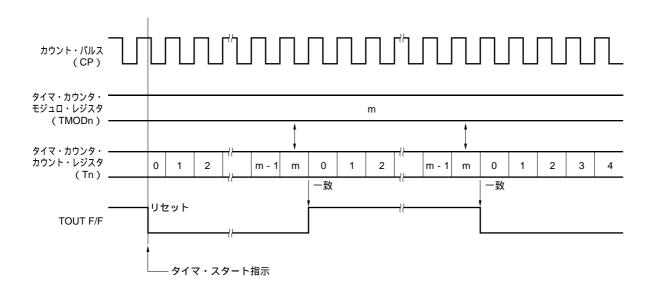

|     | 6.4.2 8ビット・タイマ・カウンタ・モードの動作 139                      |

|     | 6.4.3 PWMパルス・ジェネレータ・モード(PWMモード)の動作                  |

|     | 150                                                 |

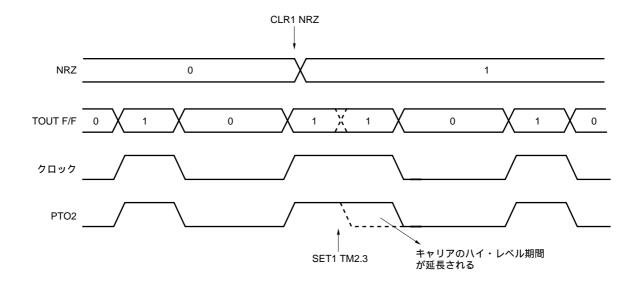

|                      | 6.4.4 16ビット・タイマ・カウンタ・モードの動作 156<br>6.4.5 キャリア・ジェネレータ・モード(CGモード)の動作 165 |

|----------------------|------------------------------------------------------------------------|

|                      | 6.4.6 タイマ・カウンタ応用上の注意 179                                               |

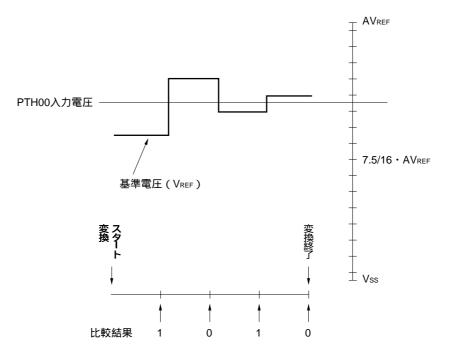

| 6.5                  | プログラマブル・スレッシュホールド・ポート(アナログ入力ポート)                                       |

|                      | 186                                                                    |

|                      | 6.5.1 プログラマブル・スレッシュホールド・ポートの構成と動作                                      |

|                      | 186                                                                    |

|                      | 6.5.2 プログラマブル・スレッシュホールド・ポート・モード・レジスタ                                   |

|                      | (PTHM) 188                                                             |

|                      | 6.5.3 プログラマブル・スレッシュホールド・ポートの応用 189                                     |

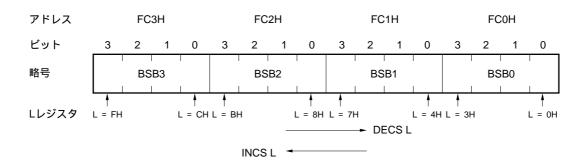

| 6.6                  | <b>ピット・シーケンシャル・パッファ</b> 190                                            |

|                      |                                                                        |

| 第7章                  | <b>割り込み機能とテスト機能</b> 192                                                |

|                      |                                                                        |

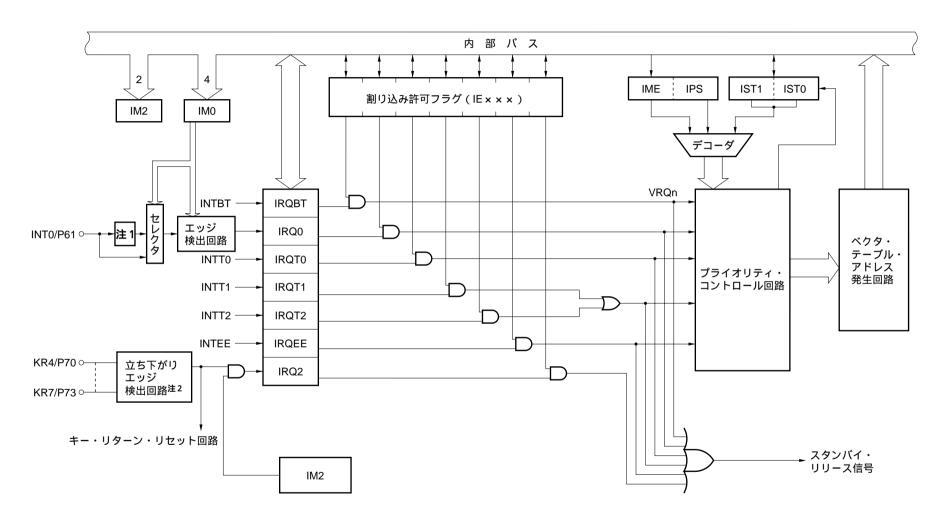

|                      | <b>割り込み制御回路の構成</b> 192                                                 |

|                      | 割り込みソースの種類とベクタ・テーブル 194                                                |

|                      | 割り込み機能を制御する各種ハードウエア 196                                                |

| 7.4                  |                                                                        |

|                      | 多重割り込み処理制御 204                                                         |

|                      | ベクタ・アドレス共用割り込み処理 206                                                   |

|                      | 割り込み処理までのマシン・サイクル 208<br>割り込みの効果的な使い方 210                              |

|                      | 割り込みの応用 210                                                            |

|                      | テスト機能 218                                                              |

| 7.10                 | 7.10.1 テスト・ソースの種類 218                                                  |

|                      | 7.10.1                                                                 |

|                      |                                                                        |

| 第8章                  | スタンバイ機能 221                                                            |

|                      |                                                                        |

| 8.1                  | スタンバイ・モードの設定および動作状態 223                                                |

| 8.2                  | スタンパイ・モードの解除 225                                                       |

| 8.3                  | <b>スタンバイ・モード解除後の動作</b> 229                                             |

| 8.4                  | スタンバイ・モードの応用 229                                                       |

|                      |                                                                        |

| 第9草                  | リセット機能 234                                                             |

| 0.4                  |                                                                        |

|                      | リセット機能の構成および動作 234                                                     |

| 9.2                  | ウォッチドッグ・フラグ(WDF),キー・リターン・フラグ(KRF) 238                                  |

| 笙1∩音                 | マスク・オプション 240                                                          |

| <b>₩</b> 10 <b>∓</b> | (X) 3)) a) 240                                                         |

| 10. <b>1</b>         | <b>端子のマスク・オプション</b> 240                                                |

| 10. 1                | 10.1.1 P70/KR4-P73/KR7のマスク・オプション 240                                   |

|                      | 10.1.2 RESET端子のマスク・オプション 240                                           |

| 10. <b>2</b>         | 発振安定ウエイト時間のマスク・オプション 240                                               |

|                      |                                                                        |

| 第11章                 | <b>命令セット</b> 241                                                       |

|                | 11.1.1 GETI命令 241                   |

|----------------|-------------------------------------|

|                | 11.1.2 ビット操作命令 242                  |

|                | 11.1.3 たてづみ命令 242                   |

|                | 11.1.4 進数補正命令 243                   |

|                | 11.1.5 スキップ命令とスキップに要するマシン・サイクル数 244 |

| 11. <b>2</b>   | <b>命令セットとそのオペレーション</b> 244          |

| 11. <b>3</b>   | <b>各命令の命令コード</b> 255                |

| 11. <b>4</b>   | <b>命令機能と応用</b> 261                  |

|                | 11.4.1 転送命令 262                     |

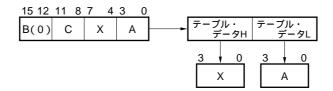

|                | 11.4.2 テーブル参照命令 270                 |

|                | 11.4.3 ビット転送命令 274                  |

|                | 11.4.4 演算命令 275                     |

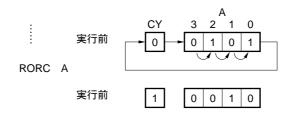

|                | 11.4.5 アキュームレータ操作命令 283             |

|                | 11.4.6 増減命令 284                     |

|                | 11.4.7 比較命令 286                     |

|                | 11.4.8 キャリー・フラグ操作命令 288             |

|                | 11.4.9 メモリ・ビット操作命令 289              |

|                | 11.4.10 分岐命令 293                    |

|                | 11. 4 .11 サブルーチン・スタック制御命令 297       |

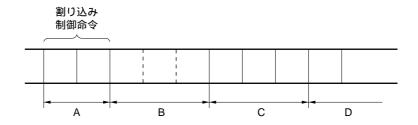

|                | 11.4.12 割り込み制御命令 302                |

|                | 11.4.13 入出力命令 303                   |

|                | 11.4.14 CPU制御命令 304                 |

|                | 11.4.15 特殊命令 305                    |

|                |                                     |

| 付録A            | 開発ツール 309                           |

| 付録B            | <b>マスク</b> ROM <b>発注の手順</b> 313     |

| / <del>-</del> |                                     |

| 19 郵 し         | 命令索引 314                            |

| C. 1           | <b>命令索引(機能別)</b> 314                |

|                | 命令索引(アルファベット順) 317                  |

|                |                                     |

| 付録D            | <b>ハードウエア索引</b> 320                 |

|                | ハードウエア索引 (50音順) 320                 |

| D. 2           | ハードウエア索引 (アルファベット順) 323             |

| 付録E            | <b>改版履歴</b> 325                     |

11.1 特徴的な命令 ... 241

# 図の目次 (1/3)

| 図番号          | タイトル , ページ                             |

|--------------|----------------------------------------|

| 3 - 1        | MBE=0のモードとMBE=1のモードの使い分け 35            |

| 3 - 2        | データ・メモリの構成と,各アドレシング・モードのアドレシング範囲 37    |

| 3 - 3        | スタティックRAMのアドレス更新方法 42                  |

| 3 - 4        | レジスタ・バンクの使い分け例 49                      |

| 3 - 5        | 汎用レジスタの構成(4ビット処理の場合) 51                |

| 3 - 6        | 汎用レジスタの構成(8ビット処理の場合) 52                |

| 3 - 7        | μPD754244 I/Oマップ 55                    |

| 4 - 1        | スタック・バンク選択レジスタのフォーマット 64               |

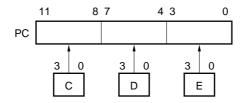

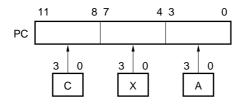

| 4 - 2        | プログラム・カウンタの構成 65                       |

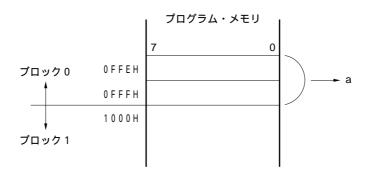

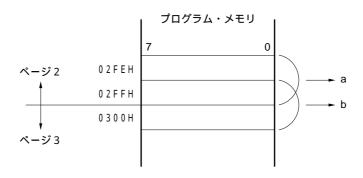

| 4 - 3        | プログラム・メモリ・マップ 67                       |

| 4 - 4        | データ・メモリ・マップ 70                         |

| 4 - 5        | 汎用レジスタの構成 72                           |

| 4 - 6        | レジスタ・ペアの構成 72                          |

| 4 - 7        | アキュームレータ 73                            |

| 4 - 8        | スタック・ポインタおよびスタック・バンク選択レジスタの構成 74       |

| 4 - 9        | スタック・メモリへ退避されるデータ (Mk モード) 75          |

| 4 - 10       | スタック・メモリから復帰されるデータ(Mk モード) 75          |

| 4 - 11       | スタック・メモリへ退避されるデータ(Mk モード) 76           |

| 4 - 12       | スタック・メモリから復帰されるデータ (Mk モード) 76         |

| 4 - 13       | プログラム・ステータス・ワードの構成 77                  |

| 4 - 14       | バンク選択レジスタの構成 81                        |

| 5 <b>–</b> 1 | EEPROMライト・コントロール・レジスタのフォーマット 84        |

| 5 <b>–</b> 2 | EEPROM読み出し操作時のEEPROMライト・コントロール・レジスタ 87 |

| 5 <b>–</b> 3 | EEPROM書き込み操作時のEEPROMライト・コントロール・レジスタ 88 |

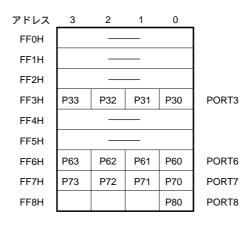

| 6 - 1        | ディジタル・ポートのデータ・メモリ・アドレス 91              |

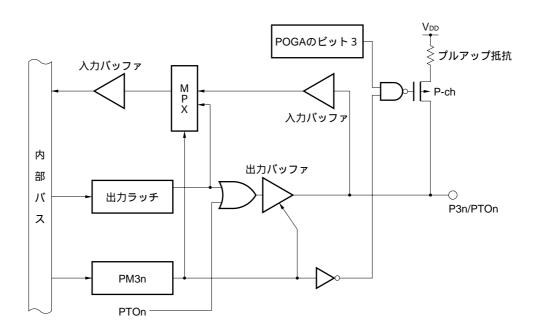

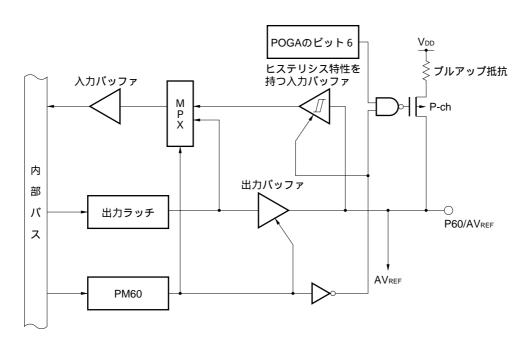

| 6 - 2        | P3nの構成 ( n = 0-2 ) 93                  |

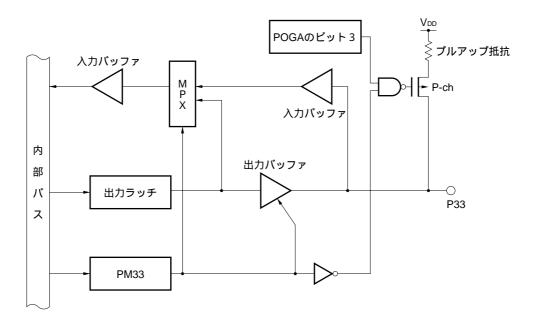

| 6 - 3        | P33の構成 93                              |

| 6 - 4        | P60の構成 94                              |

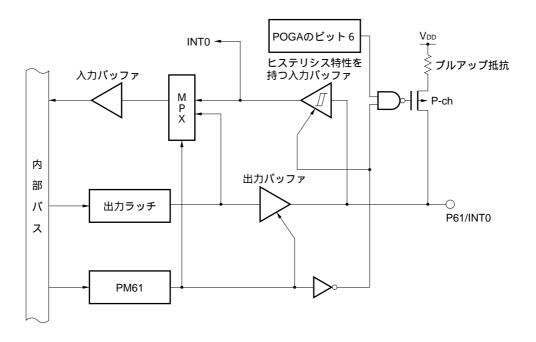

| 6 - 5        | P61の構成 94                              |

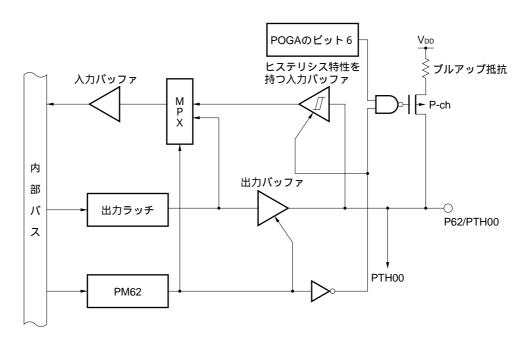

| 6 - 6        | P62の構成 95                              |

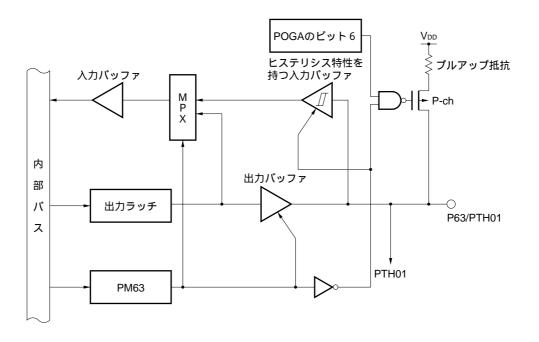

| 6 <b>-</b> 7 | P63の構成 95                              |

# 図の目次 (2/3)

| 図番号          | タイトル , ページ                               |

|--------------|------------------------------------------|

| 6 — 8        | P7nの構成 ( n = 0 - 3 ) 96                  |

| 6 <b>-</b> 9 | P80の構成 96                                |

| 6 - 10       | 各ポート・モード・レジスタのフォーマット 98                  |

| 6 - 11       | プルアップ抵抗指定レジスタのフォーマット 103                 |

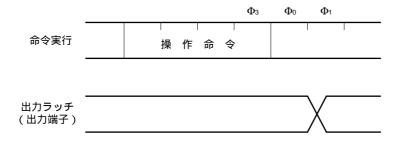

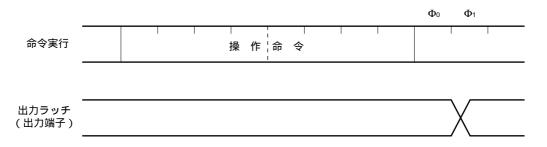

| 6 - 12       | ディジタル入出力ポートの入出力タイミング 104                 |

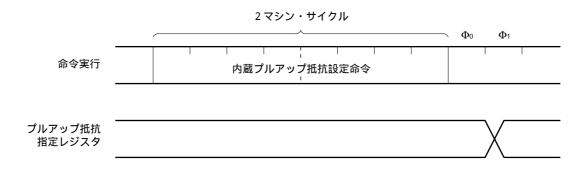

| 6 - 13       | ソフトウエアによる内蔵プルアップ抵抗のONタイミング 105           |

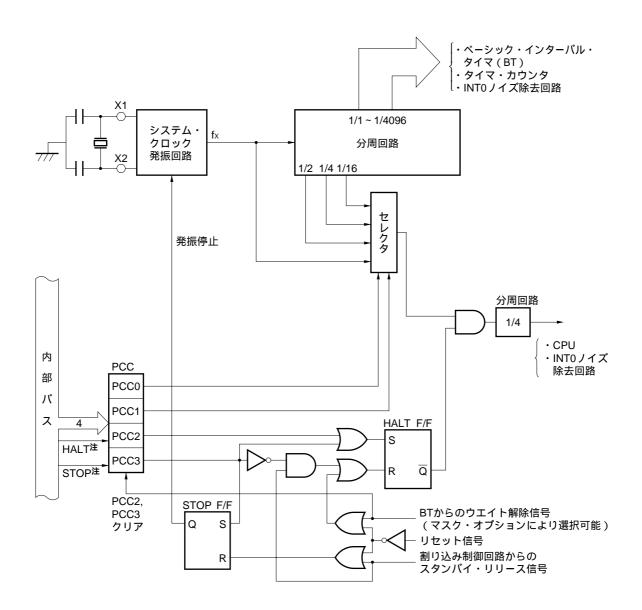

| 6 - 14       | クロック発生回路のブロック図 106                       |

| 6 - 15       | プロセッサ・クロック・コントロール・レジスタのフォーマット 110        |

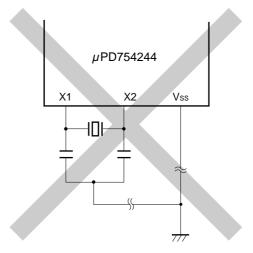

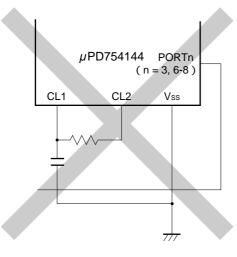

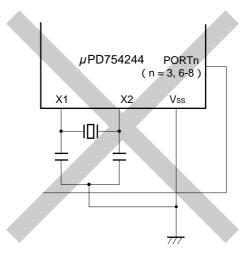

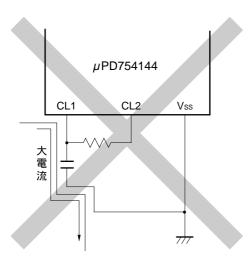

| 6 - 16       | RC発振の外付け回路 111                           |

| 6 - 17       | クリスタル / セラミック発振の外付け回路 111                |

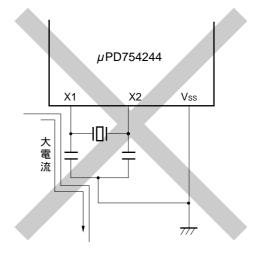

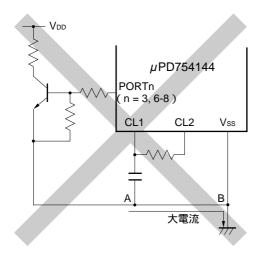

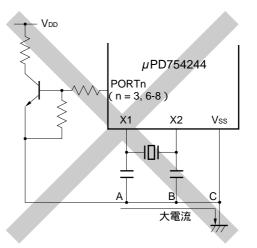

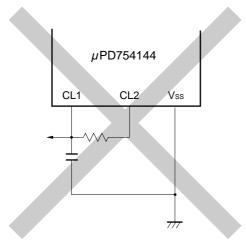

| 6 - 18       | 発振子の接続回路の悪い例 112                         |

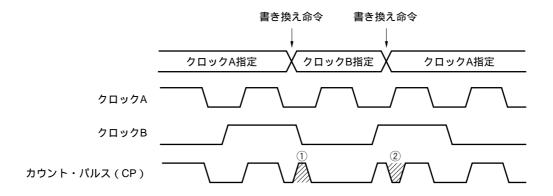

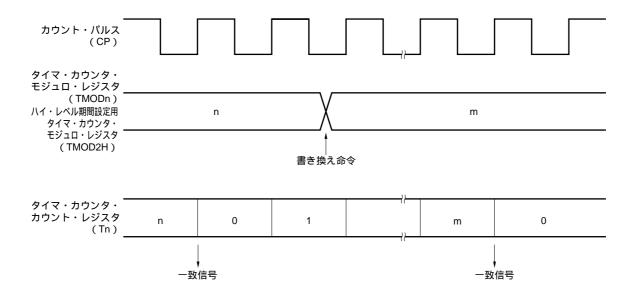

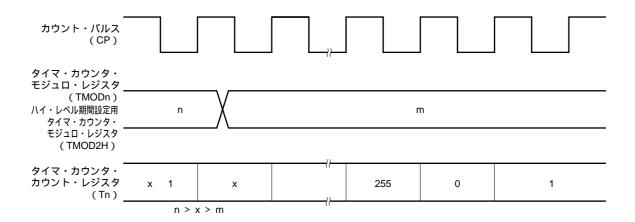

| 6 - 19       | CPUクロックの切り替え例 116                        |

| 6 - 20       | ベーシック・インターバル・タイマ / ウォッチドッグ・タイマのブロック図 117 |

| 6 - 21       | ベーシック・インターバル・タイマ・モード・レジスタのフォーマット 119     |

| 6 - 22       | ウォッチドッグ・タイマ許可フラグ(WDTM)のフォーマット 120        |

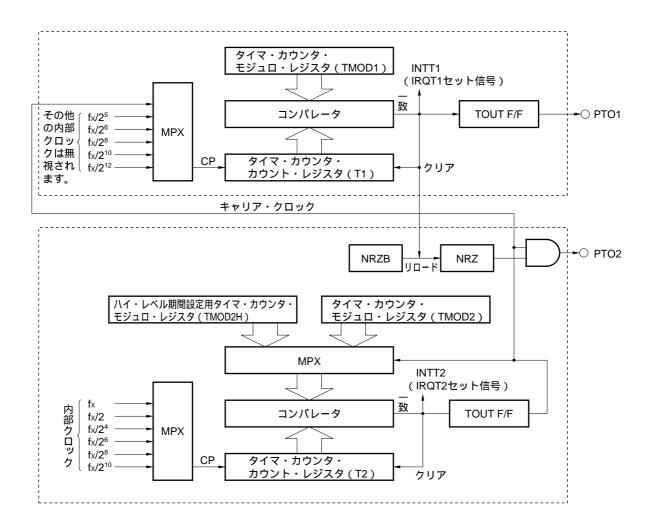

| 6 - 23       | タイマ・カウンタ(チャネル 0 )のブロック図 127              |

| 6 - 24       | タイマ・カウンタ(チャネル1)のブロック図 128                |

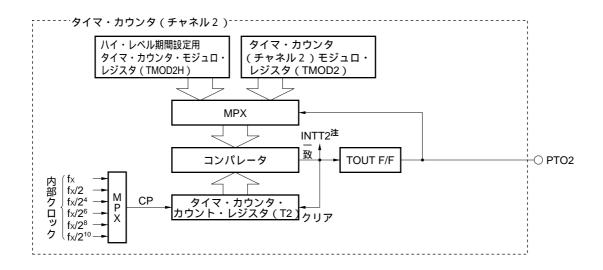

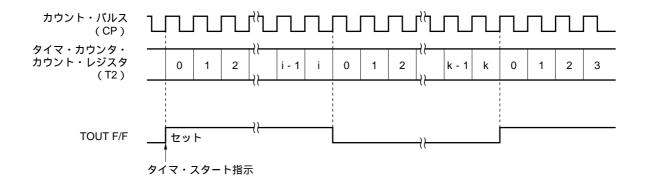

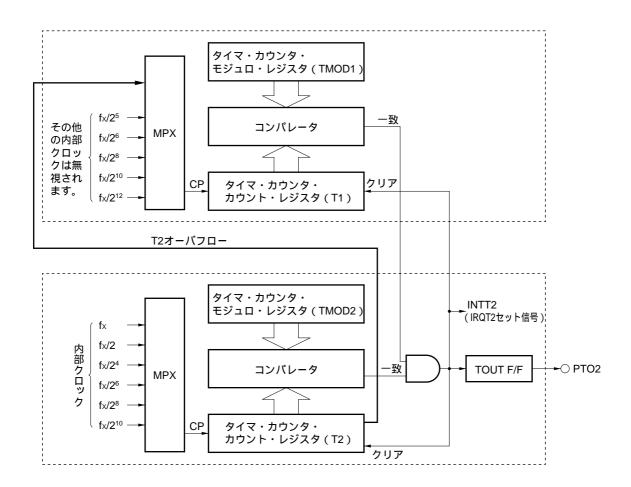

| 6 - 25       | タイマ・カウンタ(チャネル 2 )のブロック図 129              |

| 6 - 26       | タイマ・カウンタ・モード・レジスタ(チャネル0)のフォーマット 131      |

| 6 - 27       | タイマ・カウンタ・モード・レジスタ(チャネル1)のフォーマット 133      |

| 6 - 28       | タイマ・カウンタ・モード・レジスタ(チャネル2)のフォーマット 135      |

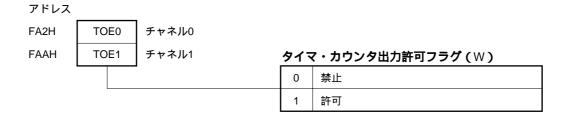

| 6 - 29       | タイマ・カウンタ出力許可フラグのフォーマット 137               |

| 6 - 30       | タイマ・カウンタ・コントロール・レジスタのフォーマット 138          |

| 6 - 31       | タイマ・カウンタ・モード・レジスタの設定 140                 |

| 6 - 32       | タイマ・カウンタ・コントロール・レジスタの設定 143              |

| 6 - 33       | タイマ・カウンタ出力許可フラグの設定 143                   |

| 6 - 34       | タイマ・カウント動作時の構成 148                       |

|              | カウント動作時のタイミング 148                        |

|              | タイマ・カウンタ・モード・レジスタの設定 151                 |

| 6 - 37       | タイマ・カウンタ・コントロール・レジスタの設定 152              |

|              | PWMパルス・ジェネレータ動作時の構成 154                  |

|              | PWMパルス・ジェネレータ動作時のタイミング 154               |

| 6 - 40       | タイマ・カウンタ・モード・レジスタの設定 157                 |

| 6 - 41       | タイマ・カウンタ・コントロール・レジスタの設定 158              |

# 図の目次(3/3)

| 図番号           | タイトル , ページ                                    |

|---------------|-----------------------------------------------|

| 6 - 42        | タイマ・カウント動作時の構成 162                            |

| 6 - 43        | カウント動作時のタイミング 163                             |

| 6 - 44        | タイマ・カウンタ・モード・レジスタの設定(n=1,2) 166               |

| 6 - 45        | タイマ・カウンタ出力許可フラグの設定 167                        |

| 6 - 46        | タイマ・カウンタ・コントロール・レジスタの設定 167                   |

| 6 - 47        | キャリア・ジェネレータ動作時の構成 170                         |

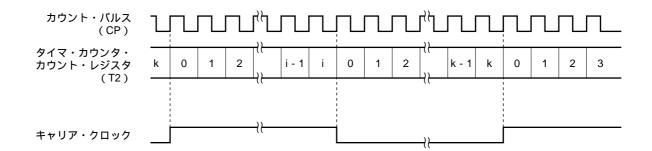

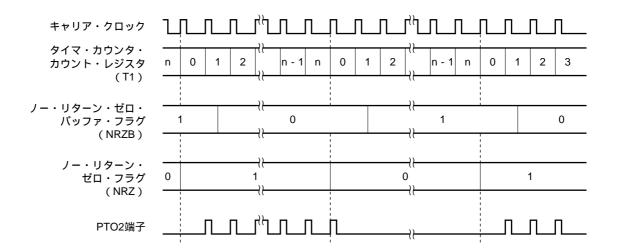

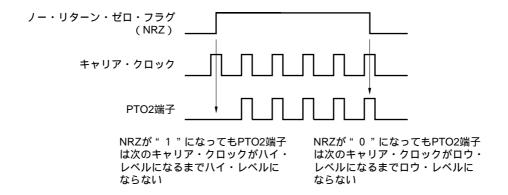

| 6 - 48        | キャリア・ジェネレータ動作時のタイミング 171                      |

| 6 - 49        | プログラマブル・スレッシュホールド・ポートのブロック図 187               |

| 6 - 50        | プログラマブル・スレッシュホールド・ポート・モード・レジスタ(PTHM ) のフォーマット |

|               | 188                                           |

| 6 - 51        | プログラマブル・スレッシュホールド・ポートの応用例 189                 |

| 6 <b>-</b> 52 | ビット・シーケンシャル・バッファのフォーマット 190                   |

|               |                                               |

| 7 - 1         | 割り込み制御回路ブロック図 193                             |

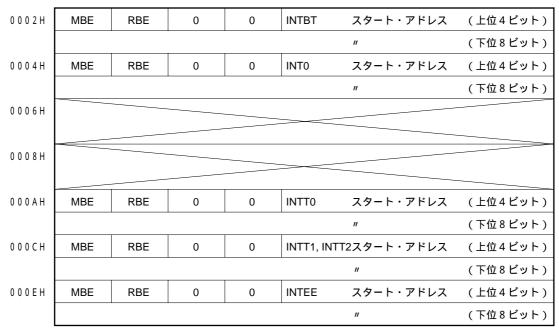

| 7 - 2         | 割り込みベクタ・テーブル 195                              |

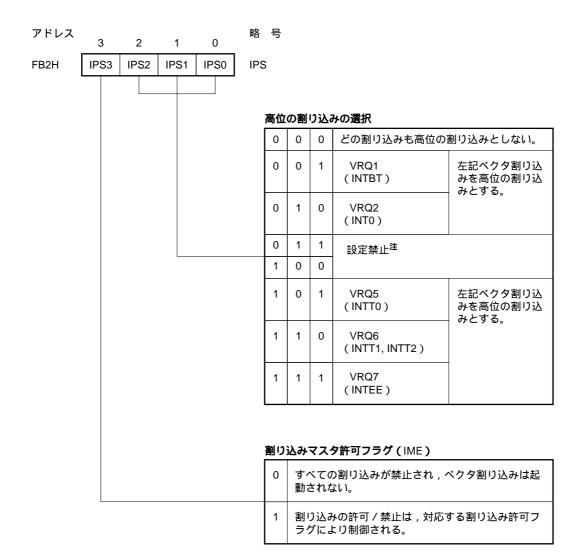

| 7 - 3         | 割り込みプライオリティ選択レジスタ 198                         |

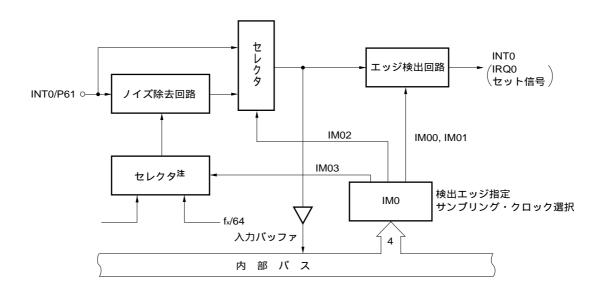

| 7 - 4         | INTOの構成 200                                   |

| 7 - 5         | ノイズ除去回路の入出力タイミング 200                          |

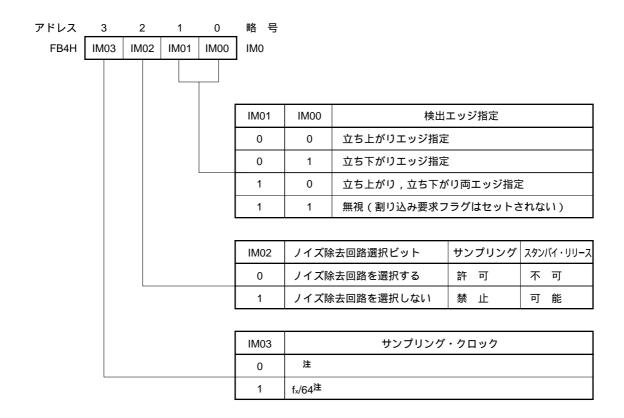

| 7 - 6         | INTOエッジ検出モード・レジスタ(IMO)のフォーマット 201             |

| 7 - 7         | 割り込み処理シーケンス 203                               |

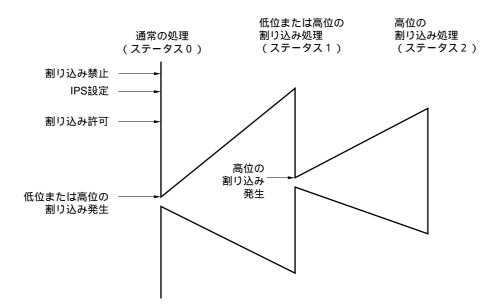

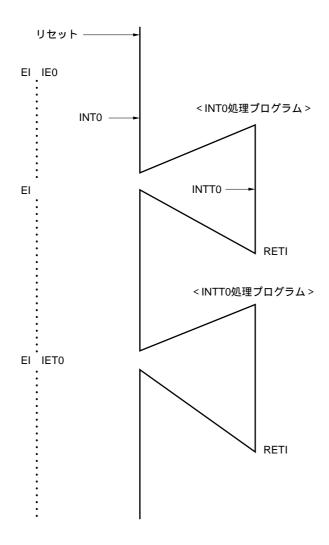

| 7 - 8         | 高位の割り込みによる多重割り込み 204                          |

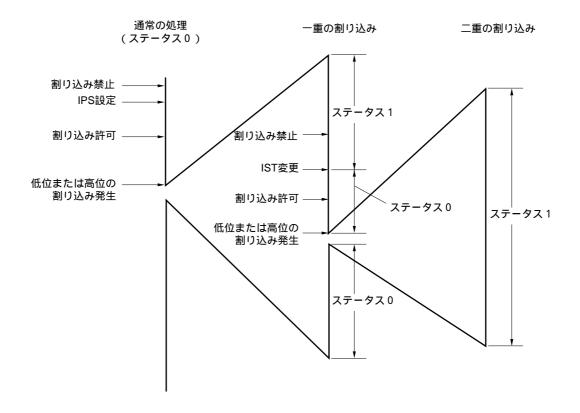

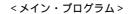

| 7 - 9         | 割り込みステータス・フラグの変更による多重割り込み 205                 |

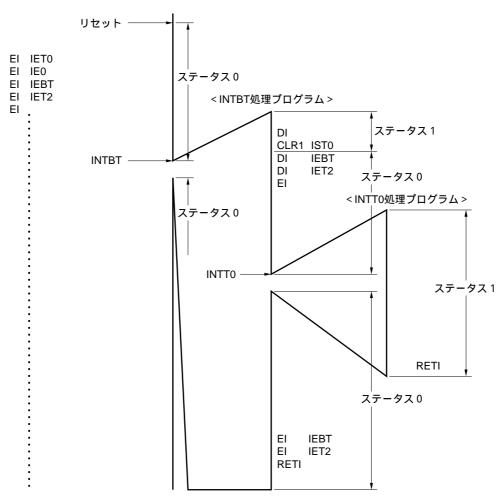

| 7 - 10        | KR4-KR7のブロック図 219                             |

| 7 - 11        | INT2エッジ検出モード・レジスタ(IM2)のフォーマット 220             |

|               |                                               |

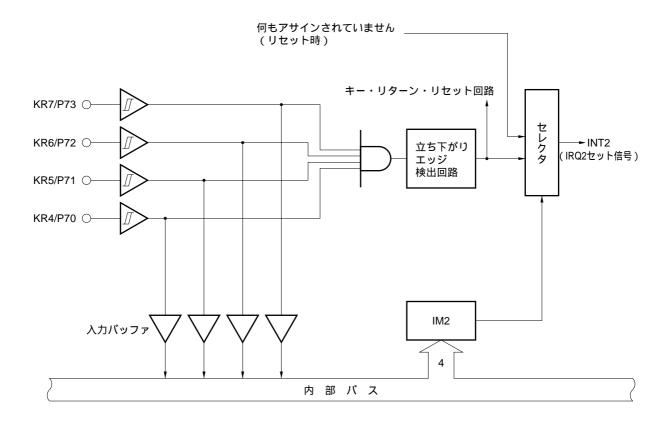

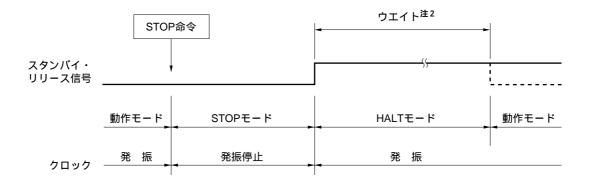

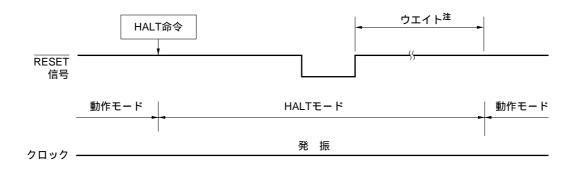

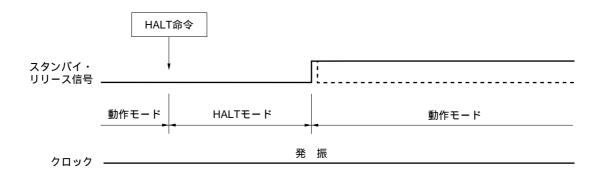

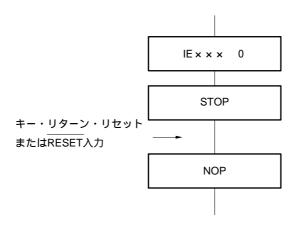

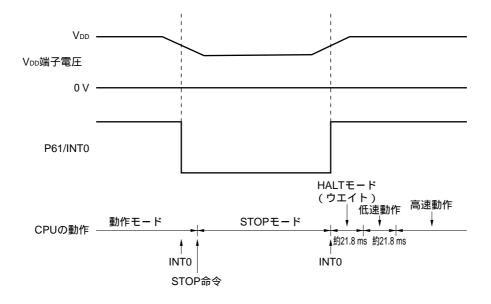

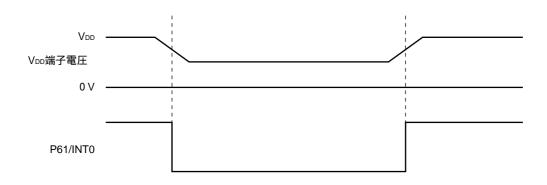

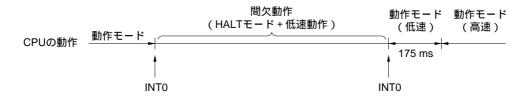

| 8 - 1         | スタンバイ・モードの解除動作 225                            |

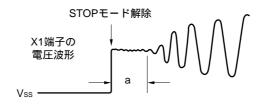

| 8 - 2         | STOPモード解除時のウエイト時間 227                         |

| 8 - 3         | キー・リターン・リセットまたはRESET入力によるSTOPモードの解除 228       |

|               |                                               |

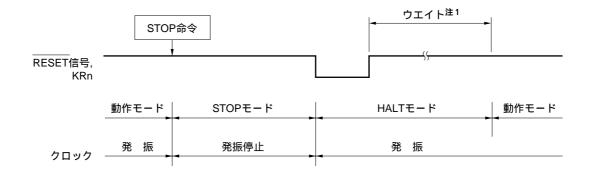

| 9 - 1         | リセット機能の構成 234                                 |

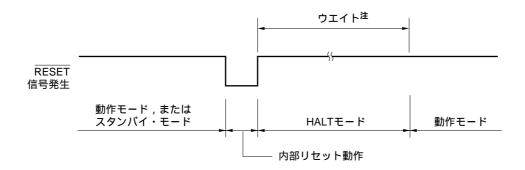

| 9 - 2         | RESET信号発生によるリセット動作 235                        |

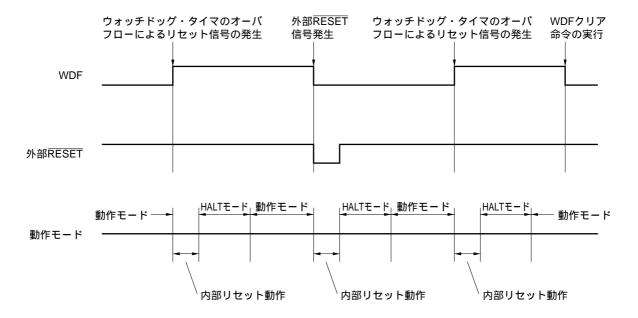

| 9 - 3         | 各信号発生時におけるWDFの動作 238                          |

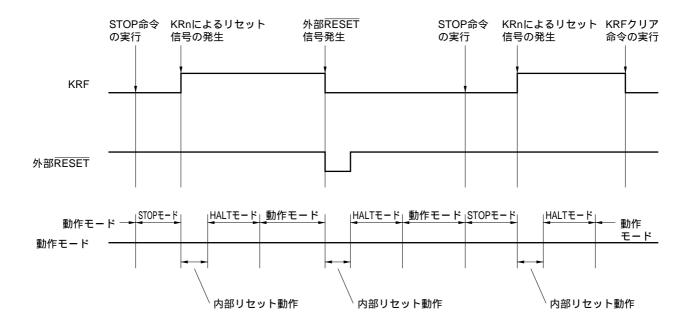

| 9 - 4         | 各信号発生時におけるKRFの動作 239                          |

# 表の目次 (1/2)

| 表番号          | タイトル , ページ                                            |

|--------------|-------------------------------------------------------|

| 2 - 1        | ディジタル入出力ポートの端子機能一覧 26                                 |

| 2 - 2        | ポート端子以外の端子機能一覧 27                                     |

| 2 - 3        | 未使用端子の処理一覧 33                                         |

|              |                                                       |

| 3 - 1        | アドレシング・モード 38                                         |

| 3 - 2        | RBE, RBSと選択されるレジスタ・バンク 48                             |

| 3 - 3        | 通常ルーチンと割り込みルーチンでのレジスタ・バンクの使い分けの例 48                   |

| 3 - 4        | 周辺ハードウエア操作時に適用可能なアドレシング・モード 53                        |

|              |                                                       |

| 4 - 1        |                                                       |

|              | SBSで選択されるスタック・エリア 73                                  |

|              | スタック動作時に退避 / 復帰されるPSWのフラグ 77                          |

|              | キャリー・フラグ操作命令 78                                       |

| 4 - 5        |                                                       |

|              | MBE, MBSと選択されるメモリ・バンク 81<br>RBE, RBSと選択されるレジスタ・バンク 82 |

| 4 - 7        | RDE, RDSC送がC110レンステ・ハンケ 02                            |

| 5 <b>–</b> 1 | EEPROMの制御に関する割り込み 85                                  |

| 6 - 1        | ディジタル・ポートの種類と特徴 92                                    |

| 6 - 2        | 入出力端子操作命令一覧表 100                                      |

| 6 - 3        | 入出力ポート操作時の動作 102                                      |

| 6 - 4        | プルアップ抵抗内蔵の指定法 103                                     |

| 6 - 5        | CPUクロックの切り替えに要する最大時間 115                              |

| 6 - 6        | モード一覧 126                                             |

| 6 - 7        | 分解能と最長設定時間(8ビット・タイマ・カウンタ・モードの場合) 144                  |

| 6 - 8        | 分解能と最長設定時間(16ビット・タイマ・カウンタ・モードの場合) 159                 |

|              |                                                       |

|              | 割り込みソースの種類 194                                        |

| -            | 割り込み要求フラグのセット信号 197                                   |

|              | IST1, IST0と割り込み処理状態 202                               |

|              | 共用割り込みの判別 206                                         |

|              | テスト・ソースの種類 218                                        |

|              | テスト要求フラグのセット信号 218                                    |

|              | KR4-KR7端子とKRREN端子およびテスト機能 220                         |

# 表の目次(2/2)

| 表番号  | タイトル , ページ     |

|------|----------------|

| NH J | 7 1 1 70 1 . 7 |

- 8 1 スタンバイ・モード時の各動作状態 ... 223

- 8 2 BTMによるウエイト時間の選択 ... 227

- 9 1 各ハードウエアのリセット後の状態 ... 236

- 9-2 各信号に対するWDF, KRFの内容 ... 238

- 10 1 マスク・オプションの選択 ... 240

- 11 1 ビット操作アドレシングの種類と指定可能な範囲 ... 242

### 第1章 概 説

μPD754144, 754244は,豊富な製品展開を誇る75Xシリーズの後継品種75XLシリーズの 4 ビット・シングルチップ・マイクロコンピュータです。

$\mu$  PD754144, 754244は , 75XシリーズのEEPROM内蔵製品である  $\mu$  PD75048に比べて , CPU機能を拡張し , 低電圧1.8 Vでの高速動作を可能にしています。

小型のプラスチックSSOP (7.62 mm (300)) を用意しています。 次に特徴を示します。

- ・低電圧動作可能: VDD=1.8~6.0 V

- ・低電圧 (1.8 V) 動作可能な128ビットのEEPROMを内蔵 (16 x 8 ビット)

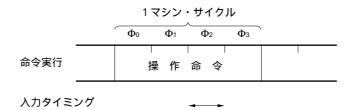

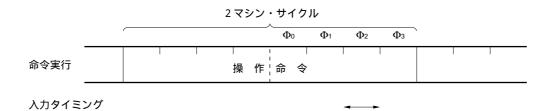

- ・高速動作とパワー・セーブに有利な命令実行時間可変機能

μ PD754144: RC発振回路(抵抗, コンデンサは外付け)

4 , 8 , 16 , 64 μs (fcc = 1.0 MHz動作時)

μPD754244: クリスタル / セラミック発振回路

0.95, 1.91, 3.81, 15.3 μs (fx = 4.19 MHz動作時)

0.67, 1.33, 2.67, 10.7 μs (fx = 6.0 MHz動作時)

- ・タイマを4チャネル内蔵

- ・キーレス・エントリ用のキー・リターン・リセット機能を内蔵

- ・小型パッケージ(20ピン・プラスチックSSOP(7.62 mm(300)))を用意

#### 応用分野

- ・キーレス・エントリなどの自動車電装,小型データ・キャリアなど

- 備考 このマニュアルでは、特に機能面での違いがないかぎり、 $\mu$  PD754244(クリスタル / セラミック 発振、fx)を代表品種として記述してあります。  $\mu$  PD754144(RC発振、fcc)のマニュアルとして使用する場合は、 $\mu$  PD754244を  $\mu$  PD754144に、fxをfccに読み替えて使用してください。

# 1.1 機能概要

| 項目        |         | μ PD754144                               |                               | μ PD754244                  |  |  |

|-----------|---------|------------------------------------------|-------------------------------|-----------------------------|--|--|

| 命令実行時間    |         | • 4, 8,                                  | , 16, 64 µs(fcc = 1.0 MHz動作時) |                             |  |  |

|           |         |                                          |                               | (fx = 4.19 MHz動作時)          |  |  |

|           |         |                                          |                               | • 0.67, 1.33, 2.67, 10.7 µs |  |  |

|           |         |                                          |                               | (fx = 6.0 MHz動作時)           |  |  |

| 内蔵メモリ     | マスクROM  | 4096×                                    | 4096×8ビット (0000H-0FFFH)       |                             |  |  |

|           | RAM     | 128 × 4                                  | ビット ( 000H-07FH )             |                             |  |  |

|           | EEPROM  | 16 × 8                                   | ビット(400H-41FH)                |                             |  |  |

| システム・クロッ  | ク発振回路   | RC発振                                     | 回路                            | クリスタル / セラミック発振回路           |  |  |

|           |         | (抵抗                                      | , コンデンサは外付け)                  |                             |  |  |

| 汎用レジスタ    |         | ・4ビ                                      | ット操作時:8個×4バンク                 |                             |  |  |

|           |         | ・8 ビット操作時: 4 個× 4 バンク                    |                               |                             |  |  |

| 入出力ポート    | CMOS入力  | 4本                                       | マスク・オプションによるプルアップ抵抗区          | <b>紅抗内蔵可能</b>               |  |  |

|           | CMOS入出力 | 9本                                       | ソフトウエアによる内蔵プルアップ抵抗の技          | 接続指定可能                      |  |  |

|           | 合計      | 13本                                      |                               |                             |  |  |

| タイマ       |         | 4チャネル                                    |                               |                             |  |  |

|           |         | ・8 ビット・タイマ・カウンタ:3 チャネル                   |                               |                             |  |  |

|           |         | (16ビット・タイマ・カウンタとして使用可能)                  |                               |                             |  |  |

|           |         | ・ベーシック・インターバル・タイマ / ウォッチドッグ・タイマ : 1 チャネル |                               |                             |  |  |

| プログラマブル   | ・スレッシュ  | 2チャネル                                    |                               |                             |  |  |

| ホールド・ポート  |         |                                          |                               |                             |  |  |

| ビット・シーケンシ | ャル・バッファ | 16ビット                                    |                               |                             |  |  |

| ベクタ割り込み   |         | 外部:1本,内部:5本                              |                               |                             |  |  |

| テスト入力     |         | 外部:1本(キー・リターン・リセット機能あり)                  |                               |                             |  |  |

| スタンバイ機能   |         | STOPE-F/HALTE-F                          |                               |                             |  |  |

| 動作周囲温度    |         | $T_A = -40 \sim +85$                     |                               |                             |  |  |

| 電源電圧      |         | V <sub>DD</sub> = 1.8 ~ 6.0 V            |                               |                             |  |  |

| パッケージ     |         | ・20ピン・プラスチックSOP(7.62 mm(300))            |                               |                             |  |  |

|           |         | ・20ピン・プラスチックSSOP(7.62 mm(300))           |                               |                             |  |  |

# 1.2 オーダ情報

| ジ |

|---|

| シ |

$\mu$  PD754144GS- × × × -BA5 20ピン・プラスチックSOP (7.62 mm (300))  $\mu$  PD754144GS- × × × -GJG 20ピン・プラスチックSOP (7.62 mm (300))  $\mu$  PD754244GS- × × × -BA5 20ピン・プラスチックSOP (7.62 mm (300))  $\mu$  PD754244GS- × × × -GJG 20ピン・プラスチックSOP (7.62 mm (300))

備考 ×××はROMコード番号です。

## **1.3** µPD754144, 754244**の違い**

| 項目             | μ PD754144                         | μ PD754244                                                                         |

|----------------|------------------------------------|------------------------------------------------------------------------------------|

| 命令実行時間         | 4, 8, 16, 64 μs (fcc = 1.0 MHz動作時) | · 0.95, 1.91, 3.81, 15.3 µs                                                        |

|                |                                    | (fx = 4.19 MHz動作時)                                                                 |

|                |                                    | · 0.67, 1.33, 2.67, 10.7 µs                                                        |

|                |                                    | (fx = 6.0 MHz動作時)                                                                  |

| システム・クロック発振回路  | RC発振回路                             | クリスタル / セラミック発振回路                                                                  |

|                | (抵抗,コンデンサは外付け)                     |                                                                                    |

| リセット後起動時間      | 56/fcc                             | マスク・オプションにより,次の2つか                                                                 |

|                | (fcc = 1.0 MHz動作時:56 μs)           | ら選択可能                                                                              |

|                |                                    | ・2 <sup>17</sup> /f <sub>x</sub> (fx = 4.19 MHz動作時:31.3 ms,                        |

|                |                                    | fx = 6.0 MHz動作時:21.8 ms)                                                           |

|                |                                    | ・2 <sup>15</sup> /f <sub>x</sub> (fx = 4.19 MHz動作時:7.81 ms,                        |

|                |                                    | fx = 6.0 MHz動作時:5.46 ms)                                                           |

| スタンバイ・モード解除時間  | 2º/fcc                             | BTMの設定により,次の4つから選択可能                                                               |

|                |                                    | 2 <sup>20</sup> /fx, 2 <sup>17</sup> /fx, 2 <sup>15</sup> /fx, 2 <sup>13</sup> /fx |

| 端子接続 2番ピン,3番ピン | CL1, CL2                           | X1 , X2                                                                            |

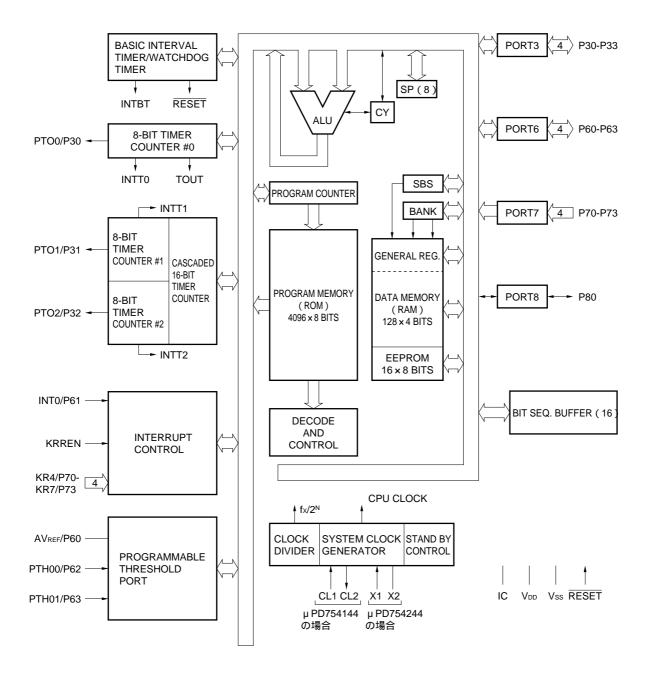

## 1.4 プロック図

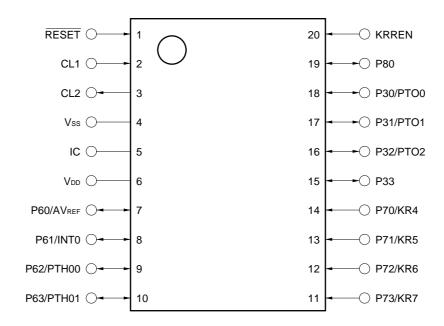

## 1.5 端子接続図 (Top View)

μPD754144**の端子接続図**

- ・20ピン・プラスチックSOP (7.62 mm (300)) μPD754144GS-XXX-BA5

- ・20ピン・プラスチックSSOP (7.62 mm (300)) μPD754144GS-XXX-GJG

IC: Internally Connected (VDDに直接接続してください)

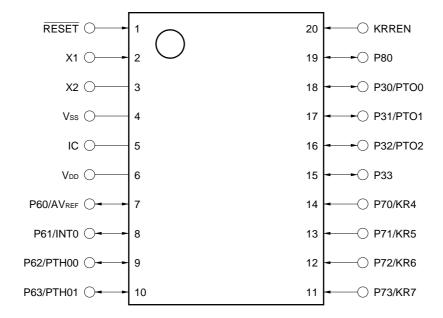

#### μPD754244**の端子接続図**

- ・20ピン・プラスチックSOP (7.62 mm (300))

- μ PD754244GS-XXX-BA5

- ・20ピン・プラスチックSSOP (7.62 mm (300))

- μPD754244GS-XXX-GJG

IC: Internally Connected (VDDに直接接続してください)

#### 端子名称

P30-P33 : Port 3

P60-P63 : Port 6

P70-P73 : Port 7

P80 : Port 8

KR4-KR7 : Key Return 4-7

INT0 : External Vectored Interrupt 0

PTH00, PTH01: Programmable Threshold Port Analog Input 0, 1

PTO0-PTO2 : Programmable Timer Output 0-2

KRREN : Key Return Reset Enable

CL1, CL2 : RC Oscillator

X1, X2 : Crystal/ceramic Oscillator

IC : Internally Connected

RESET : Reset

AVREF : Analog Reference

Vss : Ground

VDD : Positive Power Supply

# 第2章 端子機能

# **2**. **1** μ PD754244**の端子機能一覧**

表2-1 ディジタル入出力ポートの端子機能一覧

|      |     |       |                             | 8<br>ビ |       | 入出力                |

|------|-----|-------|-----------------------------|--------|-------|--------------------|

| 端子名称 | 入出力 | 兼用端子  | 機能                          | ッ      | リセット時 | 回路                 |

|      |     |       |                             | 1/0    |       | TYPE <sup>注1</sup> |

| P30  | 入出力 | PTO0  | プログラマブル4ビット入出力ポート(PORT3)。   | ×      | 入 力   | E-B                |

| P31  |     | PTO1  | ビット単位で入力/出力指定可能。            |        |       |                    |

| P32  |     | PTO2  | 4 ビット単位で,ソフトウエアにより内蔵プルアッ    |        |       |                    |

| P33  |     | -     | プ抵抗の接続を指定可能。                |        |       |                    |

| P60  | 入出力 | AVREF | プログラマブル4ビット入出力ポート(PORT6)。   | ×      | 入 力   | F-A                |

| P61  |     | INT0  | ビット単位で入力/出力指定可能。            |        |       |                    |

| P62  |     | PTH00 | 4 ビット単位で,ソフトウエアにより内蔵プルアッ    |        |       |                    |

| P63  |     | PTH01 | プ抵抗の接続を指定可能 <sup>注2</sup> 。 |        |       |                    |

|      |     |       | P61/INT0はノイズ除去回路を選択可能。      |        |       |                    |

| P70  | 入力  | KR4   | 4ビット入力ポート(PORT7)。           | ×      | 入 力   | <b>B</b> -A        |

| P71  |     | KR5   | ビット単位にプルアップ抵抗を内蔵可能(マスク・     |        |       |                    |

| P72  |     | KR6   | オプション)。                     |        |       |                    |

| P73  |     | KR7   |                             |        |       |                    |

| P80  | 入出力 | -     | 1 ビット入出力ポート(PORT8)。         | ×      | 入 力   | F-A                |

|      |     |       | ソフトウエアにより内蔵プルアップ抵抗の接続を指     |        |       |                    |

|      |     |       | 定可能。                        |        |       |                    |

注1. 印はシュミット・トリガ入力を示します。

<sup>2.</sup> プログラマブル・スレッシュホールド・ポートを使用する場合,内蔵プルアップ抵抗の接続を指定しないでください。

表2-2 ポート端子以外の端子機能一覧

|                 |     |         |                                       |          |     |    | 入出力               |

|-----------------|-----|---------|---------------------------------------|----------|-----|----|-------------------|

| 端子名称            | 入出力 | 兼用端子    | 機能                                    |          | リセッ | 卜時 | 回 路               |

|                 |     |         |                                       |          |     |    | TYPE <sup>注</sup> |

| PTO0            | 出力  | P30     | タイマ・カウンタ出力。                           |          | 入   | カ  | E-B               |

| PTO1            |     | P31     |                                       |          |     |    |                   |

| PTO2            |     | P32     |                                       |          |     |    |                   |

| INT0            | 入力  | P61     | エッジ検出ベクタ割り込み入力                        | ノイズ除去回路  | 入   | カ  | F-A               |

|                 |     |         | (検出エッジ選択可能)。                          | 付き / 非同期 |     |    |                   |

|                 |     |         | ノイズ除去回路を選択可能。                         | 選択可      |     |    |                   |

| KR4-KR7         | 入力  | P70-P73 | 立ち下がリエッジ検出テスタブル入力。                    |          | 入   | カ  | <b>B</b> -A       |

| PTH00           | 入力  | P62     | スレッシュホールド電圧可変 2 ビット・フ                 | アナログ入力。  | 入   | カ  | F-A               |

| PTH01           |     | P63     |                                       |          |     |    |                   |

| KRREN           | 入力  | -       | キー・リターン・リセット・イネーブル。                   |          | 入   | カ  | B                 |

|                 |     |         | STOPモードでKRREN = ハイ・レベルのとき, KRnの立ち     |          |     |    |                   |

|                 |     |         | 下がりエッジでリセット信号が発生。                     |          |     |    |                   |

| AVREF           | 入力  | P60     | 基準電圧入力。                               |          | 入   | カ  | F-A               |

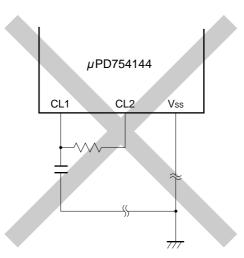

| CL1             | 入力  | -       | μ PD754144のみ内蔵。                       |          | -   |    | -                 |

| CL2             | 出力  |         | システム・クロック発振用R, C接続端子。外部クロックを          |          |     |    |                   |

| OLZ             | Ш   |         | 入力することはできません。                         |          |     |    |                   |

| X1              | 入力  | -       | μ PD754244のみ内蔵。                       |          | -   |    | -                 |

|                 |     |         | システム・クロック発振用クリスタル / セラミック接続端          |          |     |    |                   |

| X2              | -   |         | 子。外部クロックの場合,X1へ入力しX2にその逆相を入           |          |     |    |                   |

|                 |     |         | 力。                                    |          |     |    |                   |

| RESET           | 入力  | -       | システム・リセット入力 ( ロウ・レベル・アクティブ ) 。        |          | -   |    | <b>B</b> -A       |

|                 |     |         | プルアップ抵抗を内蔵可能(マスク・オプション)。              |          |     |    |                   |

| IC              | -   | -       | Internally Connected. Vppに直接接続してください。 |          | -   |    | -                 |

| V <sub>DD</sub> | -   | -       | 正電源。                                  |          | -   |    | -                 |

| Vss             | -   | -       | グランド電位。                               |          | -   |    | -                 |

注 印はシュミット・トリガ入力を示します。

### 2.2 端子機能の説明

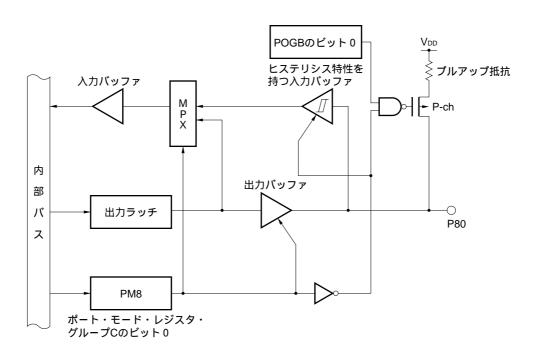

## 2.2.1 P30-P33 (PORT3)...PTO0-PTO2兼用入出力 P60-P63 (PORT6)...AVREF, INT0, PTH00, PTH01兼用入出力 P80 (PORT8)....入出力

出力ラッチ付き 4 ビットの入出力ポート(ポート 3 , 6 ) , および出力ラッチ付き 1 ビットの入出力ポート(ポート 8 ) です。

ポート3,6は入出力ポートの機能のほかに,次のような機能を兼用しています。

ポート3:タイマ・カウンタ出力(PTO0-PTO2)

ポート6:プログラマブル・スレッシュホールド・ポート基準電圧入力(AVREF)

ベクタ割り込み入力(INTO)

スレッシュホールド可変電圧入力 (PTH00, PTH01)

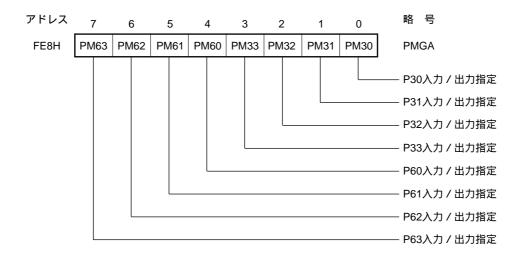

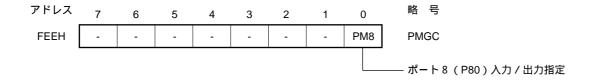

ポート3,6の入出力のモード選択はポート・モード・レジスタ・グループA(PMGA),ポート8の入出力のモード選択はポート・モード・レジスタ・グループC(PMGC)により設定します。ポート3,6は,ビット単位で設定できます。

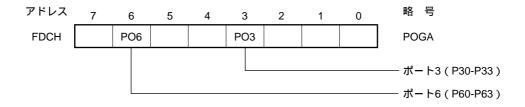

また,ポート 3 , 6 , 8 はソフトウエアにより内蔵プルアップ抵抗の接続を指定することができます。プルアップ抵抗指定レジスタ (POGA, POGB) を操作して行います。ポート 3 , 6 は 4 ビット単位で指定します。ポート 8 は 1 ビット単位で指定します。

ポート3,6は4ビット単位またはビット単位での入出力が可能です。8ビット単位での操作はできません。

RESET信号の発生により,入力モードになります。

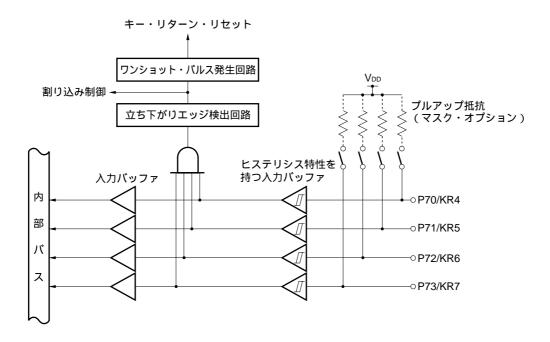

### 2.2.2 P70-P73 (PORT7) ... KR4-KR7兼用入力

4ビットの入力ポートです。

入力ポートの機能のほかにキー割り込み入力(KR4-KR7)の機能を兼用しています。

各端子は兼用端子の動作にかかわらず、常に入力となっています。また、ノイズによる誤動作を防ぐため、シュミット・トリガ入力になっています。

マスク・オプションにより、ビット単位でプルアップ抵抗の内蔵を指定できます。

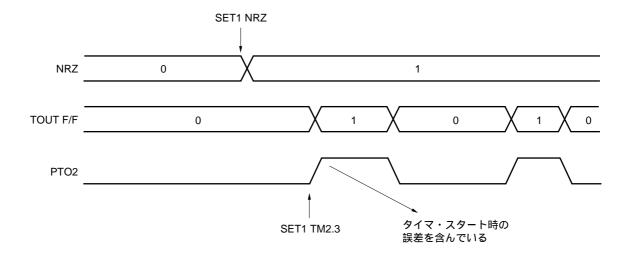

#### 2.2.3 PTO0-PTO2...ポート3兼用出力

タイマ・カウンタ0-2の出力端子です。方形波パルスを出力します。タイマ・カウンタの信号を出力する場合は,出力ラッチを"0"にクリアし,ポート・モード・レジスタ・グループA(PMGA)のポート3のビットを出力モード"1"にセットします。

タイマ・スタート命令により, TOUT F/Fの出力は"0"にクリアされます。

詳細は6.4.2(3)タイマ・カウンタ動作(8ビット時)を参照してください。

#### 2.2.4 INTO...ポート6兼用入力

エッジ検出ベクタ割り込み入力端子で、INTOはノイズ除去回路を選択できます。エッジ検出モード・レジスタ(IMO)により、検出エッジの選択ができます。

#### (1) INTO (IMOのビット0,1)

- (a) 立ち上がりエッジ・アクティブ

- (b) 立ち下がりエッジ・アクティブ

- (c) 立ち上がりおよび立ち下がりの両エッジ・アクティブ

- (d)外部割り込み信号入力禁止

INTOは非同期入力であり、CPUの動作クロックに関係なく一定のハイ・レベル幅を持つ入力があれば受け付けられます。また、ソフトウエアにより、ノイズ除去回路付きにすることができ、ノイズ除去を行うサンプリング・クロックを2段階に変えることができます。この場合、CPU動作クロックによって受け付けられる信号の幅は異なります。

RESET信号発生により,IMOは"0"にクリアされ,立ち上がりエッジ・アクティブが選択されます。

INTOは,STOPモード,HALTモードの解除に利用できます。ただし,ノイズ除去回路選択時には,INTOによるSTOPモード,HALTモードの解除はできません。

INTOは,シュミット・トリガ入力になっています。

#### 2.2.5 KR4-KR7...ポート7兼用入力

キー割り込み入力端子です。KR4-KR7は,並列立ち下がりエッジ検出割り込み入力端子です。 エッジ検出モード・レジスタ(IM2)に従って割り込みソースを "KR4-KR7"に指定できます。 RESET信号発生により,ポート7の入力モードになります。

#### 2.2.6 KRREN

キー・リターン・リセット機能の選択端子です。常に入力となっています。

KRREN端子がハイ・レベルでSTOPモードのときは, KR4/P70-KR7/P73端子の立ち下がり入力により,システム・リセットが発生します。また,このときSTOPモードを解除します。

KRREN端子がロウ・レベルのときは, KR4/P70-KR7/P73端子は通常の入力端子またはスタンバイの解除となります。

#### 2.2.7 PTH00, PTH01...ポート6兼用入力

プログラマブル・スレッシュホールド・ポート (スレッシュホールド電圧可変アナログ入力ポート)の入力端子です。

プログラマブル・スレッシュホールド・ポート・モード・レジスタ (PTHM) の設定により, スレッシュホールド電圧を16段階に変化させることができます。

#### 2.2.8 AVREF...ポート6兼用入力

基準電圧入力端子です。 プログラマブル・スレッシュホールド・ポート用のアナログ基準電圧を入力します。

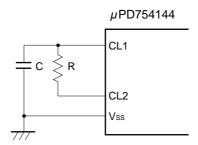

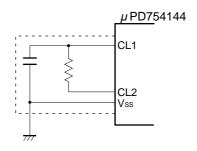

#### **2.2.9** CL1, CL2 (μPD754144**のみ**)

システム・クロック発振回路のRC発振回路用抵抗(R),コンデンサ(C)接続端子です。 外部クロックを入力することはできません。

RC発振

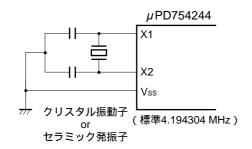

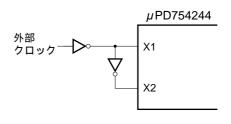

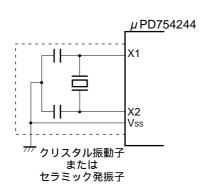

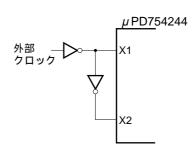

#### **2**. **2**.10 X1, X2 (μPD754244**のみ**)

システム・クロック発振用クリスタル / セラミック接続端子です。 外部クロックを入力することも可能です。

#### (a) クリスタル/セラミック発振

#### (b)外部クロック

#### 2.2.11 RESET

ロウ・レベル・アクティブのリセット入力端子です。

RESET入力は非同期入力であり、動作クロックに無関係に一定のロウ・レベル幅を持つ信号が入力されると、RESET信号が発生し、すべての動作に優先してシステム・リセットがかかります。

通常のCPUのイニシャライズ / スタートのほかに , STOPモード , HALTモードの解除にも使用します。 RESET入力はシュミット・トリガ入力になっています。

マスク・オプションにより、プルアップ抵抗の内蔵を指定できます。

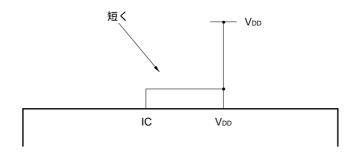

#### 2.2.12 IC

IC (Internally Connected) 端子は,当社出荷時に µ PD754244を検査するためのテスト・モードに設定するための端子です。通常動作時には,IC端子はVDD端子に直接接続し,その配線長を極力短くしてください。

IC端子とVoo端子間の配線の引き回しが長い場合や、IC端子に外来ノイズが加わった場合などで、IC端子とVoo端子間に電位差が生じたときには、お客様のプログラムが正常に動作しないことがあります。

IC端子はVooに直接接続してください

### 2.2.13 VDD

正電源供給端子です。

#### 2.2.14 Vss

GND電位です。

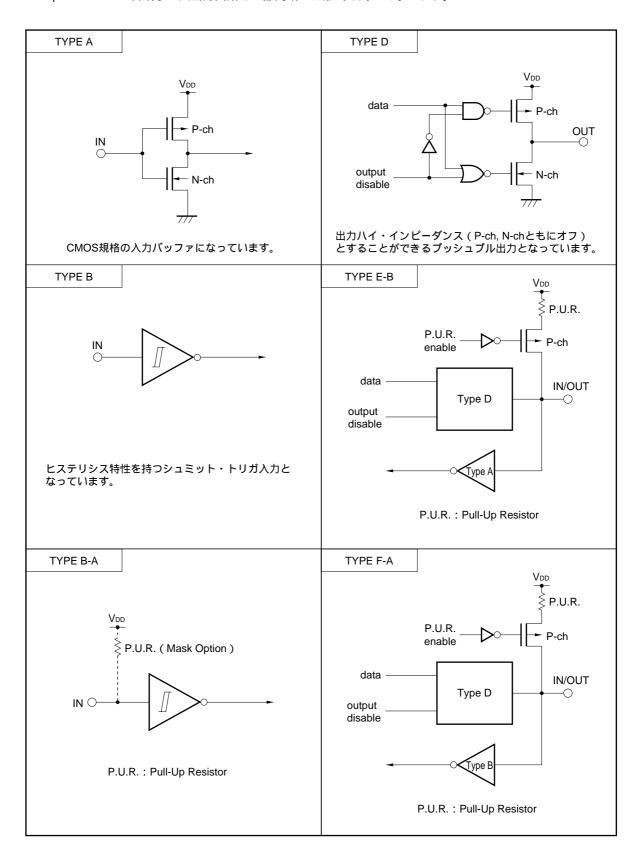

### 2.3 端子の入出力回路

μPD754244の各端子の入出力回路を一部簡略した形式を用いて示します。

# 2.4 未使用端子の処理について

表2-3 未使用端子の処理一覧

| 端         | 子 | 推奨接続方法                               |

|-----------|---|--------------------------------------|

| P30/PTO0  |   | 入力状態:個別に抵抗を介して,VssまたはVpdに接続          |

| P31/PTO1  |   | 出力状態:オープン                            |

| P32/PTO2  |   |                                      |

| P33       |   |                                      |

| P60/AVREF |   |                                      |

| P61/INT0  |   |                                      |

| P62/PTH00 |   |                                      |

| P63/PTH01 |   |                                      |

| P70/KR4   |   | Vppに接続                               |

| P71/KR5   |   |                                      |

| P72/KR6   |   |                                      |

| P73/KR7   |   |                                      |

| P80       |   | 入力状態:個別に抵抗を介して,VssまたはVppに接続          |

|           |   | 出力状態:オープン                            |

| KRREN     |   | Vooに接続すると,STOPモード時にKRn端子の立ち下がりエッジで内部 |

|           |   | リセット信号を発生します。                        |

|           |   | Vssに接続すると,STOPモード時にKRn端子の立ち下がりエッジを検出 |

|           |   | しても内部リセット信号は発生しません。                  |

| IC        |   | Vppに直接接続                             |

## 第3章 アーキテクチャの特徴とメモリ・マップ

μPD754244に採用されている75XLのアーキテクチャは以下の特徴を持っています。

- ・内蔵RAM最大4Kワード×4ビット(12ビット・アドレス)

- ・周辺ハードウエアの拡張性

この優れた特徴を実現するため,以下の方式を採用しています。

- (1) データ・メモリのバンク構成

- (2)汎用レジスタのバンク構成

- (3)メモリ・マップトI/O

本章では,これらについて解説します。

### 3.1 データ・メモリのバンク構成とアドレシング・モード

#### 3.1.1 データ・メモリのバンク構成

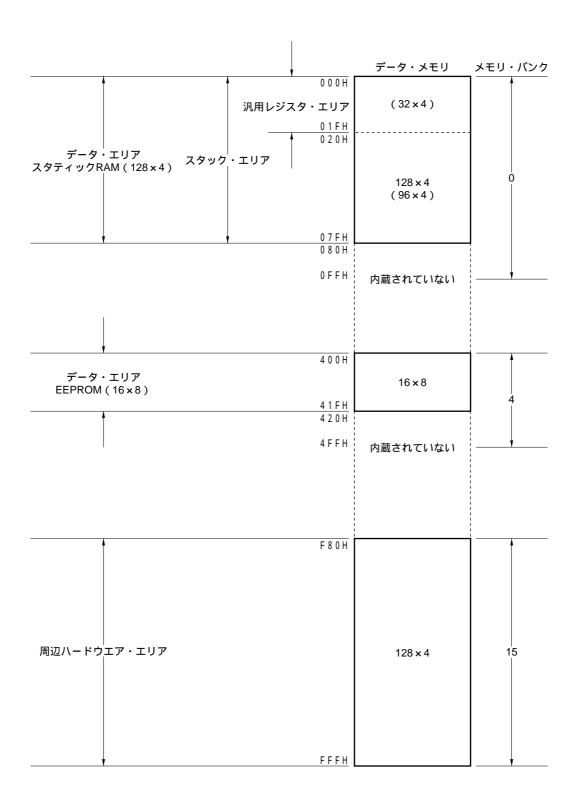

$\mu$  PD754244ではデータ・メモリ空間のメモリ・バンク 0 の000H-07FH番地にスタティックRAMが内蔵されています。また,EEPROM( $16\times8$ ビット)がメモリ・バンク 4 の400H-41FH番地に,周辺ハードウエア(入出力ポートやタイマなど)がメモリ・バンク15のF80H-FFFH番地に割り付けられています。

$\mu$  PD754244は,12ビット・アドレス(4Kワード×4ビット)のデータ・メモリ空間をアドレシングするために,下位8ビット・アドレスは命令によって直接あるいは間接に指定し,上位4ビット・アドレスをメモリ・バンクによって指定するメモリ・バンク構成となっています。

このメモリ・バンク (MB)を指定するために,以下のハードウエアが内蔵されています。

- ・メモリ・バンク許可フラグ (MBE)

- ・メモリ・バンク選択レジスタ (MBS)

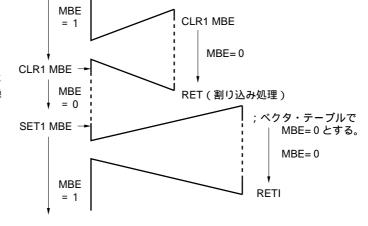

MBSはメモリ・バンクを選択するレジスタで,メモリ・バンク0,4,15が設定できます。MBEはMBSで選択されたメモリ・バンクを有効とするか否かを決定するフラグです。図3-1に示すようにMBEが0の場合には指定されるメモリ・バンク(MB)はMBSにかかわらず固定されますが,MBEが1の場合にはMBSの設定によってメモリ・バンクを切り替え,データ・メモリ空間を拡張することができます。

データ・メモリ空間のアドレシングにあたっては、通常はMBE=1とし、MBSで指定されたメモリ・バンクのデータ・メモリを操作しますが、プログラムの各処理でMBE=0のモードとMBE=1のモードを使い分けることにより、効率よくプログラムすることができます。

|           | 適合するプログラムの処理            | 効 果             |

|-----------|-------------------------|-----------------|

| MBE=0のモード | 割り込み処理                  | MBSの退避/復帰が不要になる |

|           | 内蔵ハードウエア操作とスタティックRAM操作を | MBSの変更が不要になる    |

|           | 繰り返す処理                  |                 |

|           | サブルーチン処理                | MBSの退避/復帰が不要になる |

| MBE=1のモード | 通常のプログラム処理              |                 |

図3-1 MBE=0のモードとMBE=1のモードの使い分け

内蔵ハードウエアと スタティックRAM操 作を繰り返す。

**備考** ----- MBE=1のとき, ----- MBE=0のとき。

MBEは,サブルーチン処理時に自動的に退避/復帰されますから,サブルーチン処理中でも自由に変更できます。また,割り込み処理時には,自動的に退避/復帰されるとともに,割り込みベクタ・テーブルの設定によって,割り込み処理開始と同時に割り込み処理中のMBEを指定することができます。したがって,高速の割り込み処理に有利です。

MBSをサブルーチン処理あるいは割り込み処理で変更する場合は, PUSH/POP命令によって退避/復帰します。

MBEの設定は, SET1命令/CLR1命令で行います。MBSの設定は, SEL命令により行います。

例1.MBEをクリアし,メモリ・バンクを固定する。

CLR1 MBE ; MBE 0

2.メモリ・バンク4を選択する。

SET1 MBE ; MBE 1 SEL MB4 ; MBS 4

### 3.1.2 データ・メモリのアドレシング・モード

$\mu$  PD754244に採用されている75XLシリーズのアーキテクチャでは,データ・メモリ空間を,処理するデータのビット長ごとに効率よくアドレシングするために,表 3 - 1 にまとめたように 7 種類のアドレシング・モードが用意されており,効率のよいプログラミングが可能となります。

#### (1)1ビット直接アドレシング (mem.bit)

全データ・メモリ空間の各ビットを,命令のオペランドで直接に指定するアドレシング・モードです。

指定されるメモリ・バンク(MB)は、MBE=0のモードでは、オペランドで指定されたアドレスが 00H-7FHの場合MB=0に、アドレスが80H-FFHの場合MB=15に固定されます。したがって、MBE=0の モードでは000H-07FHのデータ・エリアと、F80H-FFFHの周辺ハードウエア・エリアの両方をアドレシングすることができます。

MBE=1のモードでは,MB=MBSとなり,指定できるデータ・メモリ空間を拡張することができます。

このアドレシング・モードは,ビットのセット,リセット命令(SET1/CLR1),ビットのテスト命令(SKT/SKF)の4つの命令に適用できます。

#### **例** FLAG1をセット, FLAG2をリセット, FLAG3が0であるかテストする。

FLAG1 EQU 03FH.1 ; 3FH番地ビット 1 FLAG2 EQU 057H.2 ; 57H番地ビット 2 FLAG3 EQU 077H.0 ; 77H番地ビット 0

SET1 MBE ; MBE 1

SEL MB0 ; MBS 0

SET1 FLAG1 ; FLAG1 1

CLR1 FLAG2 ; FLAG2 0

SKF FLAG3 ; FLAG3 = 0 ?

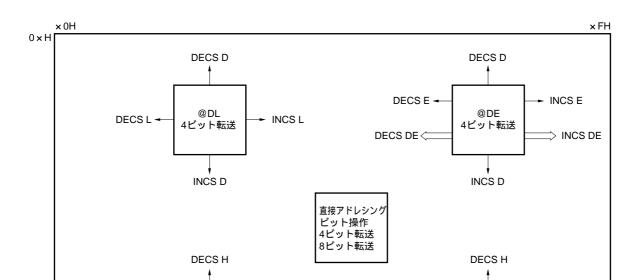

図3-2 データ・メモリの構成と,各アドレシング・モードのアドレシング範囲

|                               | アドレシング                      | ブ・モード                     |         | em<br>n. bit                         |         | HL<br>nem. bit | @DE<br>@DL | スタック・<br>アドレシング | fmem. bit | pmem. @L |

|-------------------------------|-----------------------------|---------------------------|---------|--------------------------------------|---------|----------------|------------|-----------------|-----------|----------|

|                               | メモリ・バンク                     | 7許可フラグ                    | MBE = 0 | MBE = 1                              | MBE = 0 | MBE = 1        | -          | -               | -         | -        |

| 0 0 0 H<br>0 1 F H<br>0 2 0 H |                             | 汎用レジスタ・<br>エリア<br>ア(SRAM) |         | MBS = 0                              |         | MBS = 0        |            | SBS = 0         |           |          |

| 0 7 F H                       | メモリ・                        |                           |         |                                      |         |                |            |                 |           |          |

| 0 F F H                       | 、内蔵されて<br>いない ▼             | ,                         |         |                                      |         |                |            |                 |           |          |

| 4 0 0 H<br>4 1 F H            | データ・<br>(EEPROI             |                           |         | MBS = 4                              |         | MBS = 4        |            |                 |           |          |

|                               | メモリ・/<br>メモリ・/<br>ト 内蔵されて   | バンク 4                     |         | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |         |                |            |                 |           |          |

| 4FFH                          | いない                         | ,                         |         | <br>                                 |         |                |            |                 |           |          |

| F 8 0 H                       |                             |                           |         |                                      |         |                |            |                 |           |          |

|                               |                             |                           |         |                                      |         |                |            |                 |           |          |

| F B 0 H<br>F B F H<br>F C 0 H | <br>周辺ハードウ:<br>- (メモリ・/<br> |                           |         | MBS = 15                             |         | MBS = 15       |            |                 |           |          |

|                               |                             |                           |         |                                      |         |                |            |                 |           |          |

| FF0H<br>FFFH                  | _                           |                           |         |                                      |         |                |            |                 |           |          |

備考 - : don't care

### 注意 EEPROMが操作できる命令は次に示す8ビット操作命令だけです。

MOVXA, @HLXCHXA, @HLMOVXA, memXCHXA, memMOV@HL, XASKEXA, @HL

MOV mem, XA

表3-1 アドレシング・モード

| アドレシング・モード  | 表現形式         | 指定されるアドレス                               |

|-------------|--------------|-----------------------------------------|

| 1ビット        | mem.bit      | MBとmemで示されるアドレスの , bitで示されるビット。         |

| 直接アドレシング    |              | ・MBE = 0のとき                             |

|             |              | mem = 00H-7FHのとき : MB = 0               |

|             |              | mem = 80H-FFHのとき : MB = 15              |

|             |              | ・MBE = 1のとき : MB=MBS                    |

| 4ビット        | mem          | MBとmemで示されるアドレス。                        |

| 直接アドレシング    |              | ・MBE = 0のとき                             |

|             |              | mem = 00H-7FHのとき : MB = 0               |

|             |              | mem = 80H-FFHのとき : MB = 15              |

|             |              | ・MBE = 1のとき : MB = MBS                  |

| 8ビット        |              | MBとmemで示されるアドレス (memは偶数アドレス)。           |

| 直接アドレシング    |              | ・MBE = 0のとき                             |

|             |              | mem = 00H-7FHのとき : MB = 0               |

|             |              | mem = 80H-FFHのとき : MB = 15              |

|             |              | ・MBE = 1のとき : MB = MBS                  |

| 4 ビット・レジスタ  | @HL          | MBとHLで示されるアドレス。                         |

| 間接アドレシング    |              | ただし,MB=MBE・MBS                          |

|             | @HL+         | MBとHLで示されるアドレス。ただし,MB = MBE・MBS         |

|             | @HL -        | HL + は , アドレシングのあとLレジスタを自動的にインクリメント。    |

|             |              | HL - は , アドレシングのあとLレジスタを自動的にデクリメント。     |

|             | @DE          | メモリ・バンク 0 の , DEで示されるアドレス。              |

|             | @DL          | メモリ・バンク 0 の , DLで示されるアドレス。              |

| 8 ビット・レジスタ  | @HL          | MBとHLで示されるアドレス (Lレジスタの内容は偶数)。           |

| 間接アドレシング    |              | ただし,MB=MBE・MBS                          |

| ビット操作       | fmem.bit     | fmemで示されるアドレスの , bitで示されるビット。           |

| アドレシング      |              | fmem = FB0H-FBFH(割り込み関係のハードウエア)         |

|             |              | FF0H-FFFH ( I/Oポート )                    |

|             | pmem.@L      | pmemの上位10ビットとLレジスタの上位2ビットで示されるアドレスの,    |

|             |              | Lレジスタの下位 2 ビットで示されるビット。                 |

|             |              | ただし, pmem = FC0H-FFFH                   |

|             | @H + mem.bit | MBとHそしてmemの下位 4 ビットで示されるアドレスの, bitで示される |

|             |              | ビット。                                    |

|             |              | ただし,MB = MBE・MBS                        |

| スタック・アドレシング | -            | メモリ・バンク 0 の , SPで示されるアドレス。              |

#### (2) 4 ビット直接アドレシング (mem)

全データ・メモリ空間を 4 ビット単位で , 命令のオペランドによって直接に指定するアドレシング・モードです。

1 ビット直接アドレシングと同様に, MBE=0のモードでは,指定できる領域が,000H-07FHのデータ・エリアとF80H-FFFHの周辺ハードウエア・エリアに固定されます。MBE=1のモードでは, MB=MBSとなって,指定できるデータ・メモリ空間は全空間に拡張されます。

このアドレシング・モードは, MOV/XCH/INCS/IN/OUT命令に適用されます。

#### (3) 8 ビット直接アドレシング (mem)

全データ・メモリ空間を 8 ビット単位で , 命令のオペランドによって直接に指定するアドレシング・モードです。

オペランドで指定できるアドレスは偶数アドレスであり,オペランドで指定されたアドレスの4ビット・データと,プラス1されたアドレスの4ビット・データがペアとなって,8ビット・アキュームレータ(XAレジスタ・ペア)との間で8ビット処理されます。

指定されるメモリ・バンクは,4ビット直接アドレシングと同じです。

このアドレシング・モードは, MOV/XCH/IN/OUT命令に適用されます。

#### (4) 4 ビット・レジスタ間接アドレシング (@rpa)

データ・メモリ空間を命令のオペランドで指定されたデータ・ポインタ(汎用レジスタのレジスタ・ペア)によって4ビット単位で間接に指定するアドレシング・モードです。

データ・ポインタとしては,MB=MBE・MBSの指定によって全データ・メモリ空間を指定できるHL レジスタ・ペアとMBE,MBSの指定にかかわらず常にメモリ・バンク0に固定されているDEレジスタ・ペア/DLレジスタ・ペアの3種類があります。使用するデータ・メモリのバンクによってデータ・ポインタを使い分けることによって効率のよいプログラムが可能となります。

HLレジスタ・ペアを指定した場合には,命令実行と同時にLレジスタを+1または-1するオートインクリメント/オートデクリメント・モードがあり,プログラム・ステップの短縮につながります。

#### **例** 50H-57Hのデータを60H-67Hに転送する。

DATA1 EQU 57H

DATA2 EQU 67H

SET1 MBE

SEL MB0

MOV D, #DATA1 SHR 4

MOV HL, #DATA2 AND 0FFH ; HL 17H

LOOP: MOV A, @DL ; A (DL)

XCH A, @HL ; A (HL)

DECS L ; L L-1

BR LOOP

データ・ポインタとしてHLレジスタ・ペアを使用するアドレシング・モードは,データの転送,演算,比較,入出力などに幅広く適用されます。DE,DLレジスタ・ペアを使用するアドレシング・モードは,MOV/XCH命令に適用されます。

また,汎用レジスタあるいはレジスタ・ペアの増減命令と組み合わせることによって,図3-3に示されるようにデータ・メモリ空間のアドレスを自由自在に更新することができます。

#### **例1**.50H-57Hのデータと60H-67Hのデータを比較する。

DATA1 EQU 57H

DATA2 EQU 67H

SET1 MBE

SEL MB0

MOV D, #DATA1 SHR 4

MOV HL, #DATA2 AND 0FFH

LOOP: MOV A, @DL

SKE A, @HL; A=(HL)?

BR NO ; NO

DECS L ; YES, L L - 1

BR LOOP

#### 2.004H-07FHのデータ・メモリを0クリアする。

CLR1 RBE

CLR1 MBE

MOV XA, #00H

MOV HL, #04H

LOOP: MOV @HL, A; (HL) A

INCS L ; L L + 1

BR LOOP

INCS H ; H H + 1

NOP

SKE H, #08H

BR LOOP

► オートインクリメント

► INCS L

⇒ INCS HL

@H+mem. bit

ビット操作

INCS H

図3-3 スタティックRAMのアドレス更新方法

オートデクリメント 🔫

F×H

DECS L -

DECS HL <

@HL

4ビット操作

8ビット操作

INCS H

#### (5)8ビット・レジスタ間接アドレシング(@HL)

全データ・メモリ空間を 8 ビット単位で , データ・ポインタ (HLレジスタ・ペア ) により間接に指定するアドレシング・モードです。

データ・ポインタのビット 0 ( L レジスタのビット 0 ) を 0 にしたアドレスの 4 ビット・データとプラス 1 されたアドレスの 4 ビット・データがペアとなって,8 ビット・アキュームレータ(XAレジスタ)との間で,8 ビット処理されます。

指定されるメモリ・バンクは4ビット・レジスタ間接アドレシングでHLレジスタを指定した場合と同じで,MB=MBE・MBSとなります。このアドレシング・モードは,MOV/XCH/SKE命令に適用されます。

**例1**.タイマ・カウンタ0のカウント・レジスタ(T0)値が30H,31H番地のデータと等しいかど うか比較する。

DATA EQU 30H

CLR1 MBE

MOV HL, #DATA

MOV XA, TO ; XA カウント・レジスタ 0

SKE XA, @HL ; XA = (HL)?

2.004H-07FHのデータ・メモリを0クリアする。

CLR1 RBE

CLR1 MBE

MOV XA, #00H

MOV HL, #04H

LOOP: MOV @HL, XA ; (HL) XA

INCS L

INCS L

BR LOOP

INCS H

NOP

SKE H, #08H

BR LOOP

#### (6)ビット操作アドレシング

全データ・メモリ空間の各ビットに対し,ビット操作(ブーリアン処理,ビット転送など)を行うためのアドレシング・モードです。

1 ビット直接アドレシングがビットのセット / リセット / テスト命令にしか適用できないのに対し , このアドレシングではAND1/OR1/XOR1命令によるブーリアン処理 , SKTCLR命令によるテスト & リセットなど , 多彩なビット操作が可能になります。

ビット操作アドレシングには,次に示す3つの方法があり,使用するデータ・メモリ・アドレスによって使い分けることができます。

#### (a)特定アドレス・ビット直接アドレシング (fmem.bit)

このアドレシング・モードは,周辺ハードウエアのうち入出力ポートや割り込み関係のフラグなど,特にビット操作をよく使うハードウエアをメモリ・バンクの設定に無関係にいつでも操作できるようにするためのアドレシングです。したがって,このアドレシングを適用できるデータ・メモリ・アドレスは,入出力ポートをマッピングしてあるFFOH-FFFHと,割り込み関係のハードウエアをマッピングしてあるFBOH-FBFHとなっています。この2つのデータ・メモリ領域にあるハードウエアは,MBSおよびMBEの設定にかかわらず,いつでも自由に直接アドレシングでビット操作することができます。

**例1.**タイマ0割り込み要求フラグ(IRQT0)をテストし,セットされていたら要求フラグを クリアし,P63をリセットする。

SKTCLR IRQT0 ; IRQT0=1?

BR NO ; NO CLR1 PORT6.3 ; YES

2.P30とP71の端子がともに1であれば,P63をリセットする。

(i) SET1 CY ; CY 1

AND1 CY, PORT3.0 ; CY P30

AND1 CY, PORT7.1; CY P71

SKT CY ; CY=1?

BR SETP

CLR1 PORT6.3 ; P63 0

:

SETP: SET1 PORT6.3 ; P63 1

:

(ii) SKT PORT3.0 ; P30=1?

BR SETP

SKT PORT7.1 ; P71=1?

BR SETP

CLR1 PORT6.3 ; P63 0

:

SETP: SET1 PORT6.3 ; P63 1

# (b)特定アドレス・ピット・レジスタ間接アドレシング (pmem.@L)

このアドレシング・モードは周辺ハードウエアのうち入出力ポートなどの各ビットをレジスタ間接指定し、連続的に操作するためのアドレシングです。このアドレシングを適用できるデータ・メモリ・アドレスはFCOH-FFFHとなっています。

このアドレシング・モードは,データ・メモリ・アドレス12ビットの上位10ビット・アドレスをオペランドで直接指定し,下位2ビット・アドレスとビット・アドレスはLレジスタによって間接指定します。

このアドレシングも, MBE, MBSの設定に無関係にいつでもビット操作することができます。

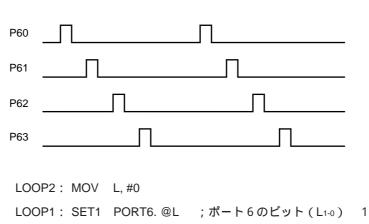

例 ポート6の各ビットに順にパルス出力する。

CLR1 PORT6.@L ;ポート6のビット(L1-0) 0

INCS L

SKE L,#4H

BR LOOP1

BR LOOP2

#### (c) 特殊 1 ビット直接アドレシング (@H + mem.bit)

このアドレシング・モードは,全データ・メモリ空間の各ビットに対し,ビット操作を可能に するためのアドレシングです。

このアドレシングでは、MB=MBE・MBSで指定されるメモリ・バンクのデータ・メモリ・アドレスの上位4ビット・アドレスをHレジスタで間接指定し、下位4ビット・アドレスとビット・アドレスはオペランドで直接指定します。このアドレシングによってすべてのデータ・メモリの各ビットに対し多彩なビット操作が可能となります。

**例** 30H番地のビット3 (FLAG1)と31H番地のビット0 (FLAG2)がともに0かともに1 なら32H番地のビット2 (FLAG3)をリセットする。

FLAG1 EQU 30H.3

FLAG2 EQU 31H.0

FLAG3 EQU 32H.2

SEL MB0

MOV H, #FLAG1 SHR 6

CLR1 CY ; CY 0

OR1 CY, @H+FLAG1 ; CY CY FLAG1

XOR1 CY, @H+FLAG2; CY CY  $\forall$  FLAG2

SET1 @H+FLAG3 ; FLAG3 1

SKT CY ; CY=1?

CLR1 @H+FLAG3 ; FLAG3 0

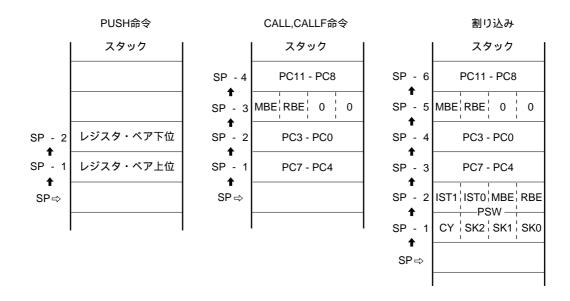

#### (7)スタック・アドレシング

このアドレシング・モードは,割り込み処理時,サブルーチン処理時の退避/復帰動作のためのアドレシングです。

このアドレシングでは,データ・メモリ・バンク0の,スタック・ポインタ(8ビット)で示されるアドレスが指定されます。

このアドレシングは,割り込み処理時,サブルーチン処理時のほかPUSH/POP命令によるレジスタの退避/復帰にも適用されます。

#### 例1.サブルーチン処理でレジスタを退避/復帰する。

SUB: PUSH XA

PUSH HL

PUSH BS ; MBSとRBSの退避

:

POP BS

POP HL

POP XA

RET

2.HLレジスタ・ペアの内容をDEレジスタ・ペアに転送する。

PUSH HL

POP DE ; DE HL

3. [XABC] のレジスタで示されるアドレスへ分岐する。

PUSH BC

PUSH XA

RET ; XABC番地へ分岐

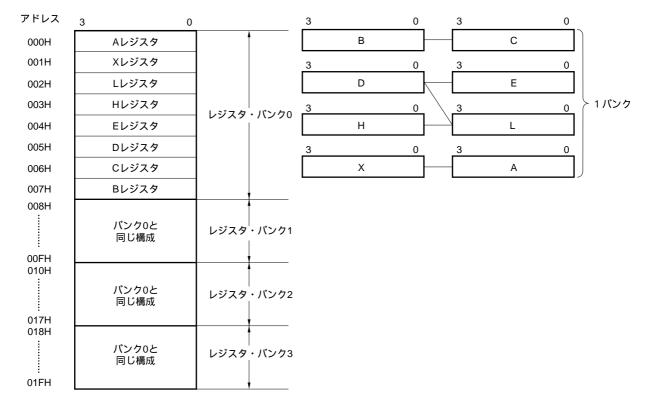

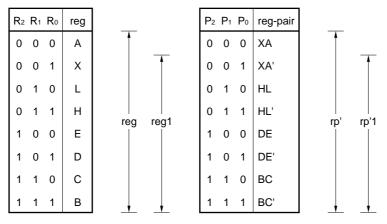

## 3.2 汎用レジスタのバンク構成

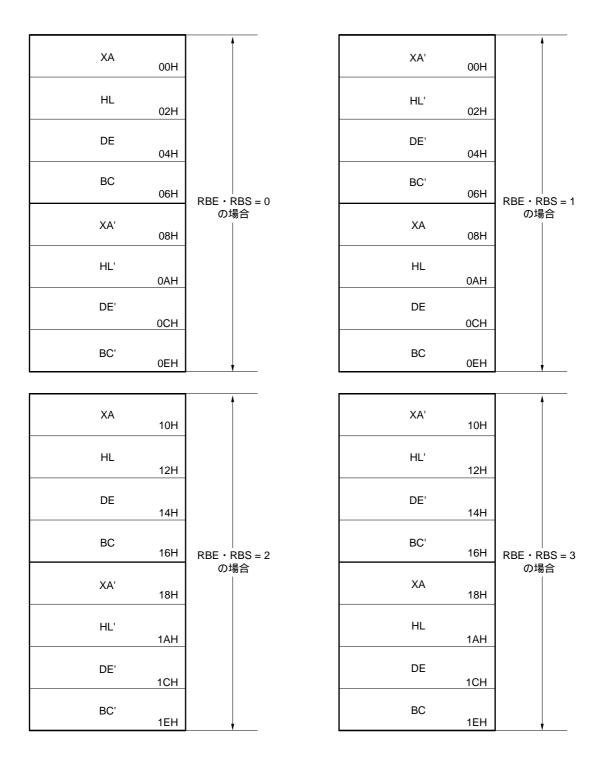

$\mu$  PD754244は,X,A,B,C,D,E,H,Lの8つの汎用レジスタを1バンクとして,4つのレジスタ・バンクを内蔵しています。この汎用レジスタ・エリアはデータ・メモリのメモリ・バンク0の00H-1FH番地にマッピングされています(**図3-5 汎用レジスタの構成(4ビット処理の場合)**参照)。この汎用レジスタのバンクを指定するためにレジスタ・バンク許可フラグ(RBE)とレジスタ・バンク選択レジスタ(RBS)が内蔵されています。RBSはレジスタ・バンクを選択するためのレジスタで,RBEはRBSで選択されたレジスタ・バンクを有効とするか否かを決定するフラグです。命令実行の際に有効となるレジスタ・バンク(RB)は,次のようになります。

RB = RBE · RBS

**RBS** RBE レジスタ・バンク 2 0 0 バンク0に固定 0 × × バンク0を選択 バンク1 " 1 バンク2 ″ 1 0 バンク3 " 1 1

表3-2 RBE, RBSと選択されるレジスタ・バンク

\_\_\_\_ 0に固定

備考 x:don't care

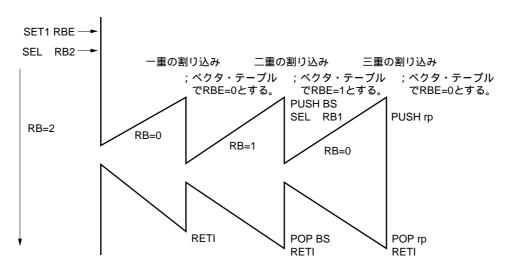

RBEは、サブルーチン処理時に自動的に退避/復帰されますので、サブルーチン処理中に自由に設定することができます。また、割り込み処理時は、自動的に退避/復帰されるとともに、割り込みベクタ・テーブルの設定によって、割り込み処理開始と同時に、割り込み処理中のRBEを設定することができます。したがって、表3-3に示すように、通常処理と割り込み処理で、レジスタ・バンクを使い分ければ、一重割り込みでは、汎用レジスタの退避/復帰は不要、二重割り込みでは、RBSの退避/復帰のみとなり、割り込み処理の高速化が図れます。

表3-3 通常ルーチンと割り込みルーチンでのレジスタ・バンクの使い分けの例

| 通常の処理        | RBE=1とし,レジスタ・バンク2,3を使用する。 |

|--------------|---------------------------|

| 1 重割り込み処理    | RBE=0とし,レジスタ・バンク 0 を使用する。 |

| 2 重割り込み処理    | RBE=1とし,レジスタ・バンク 1 を使用する。 |

|              | (このとき,RBSの退避/復帰が必要)       |

| 3 重以上の割り込み処理 | PUSH, POPでレジスタ退避 / 復帰をする。 |

図3-4 レジスタ・バンクの使い分け例

メイン・プログラム

RBSを,サブルーチン処理あるいは割り込み処理で変更する場合は,PUSH/POP命令によって退避/復帰します。

RBEの設定は、SET1/CLR1命令によって行います。RBSの設定は、SEL命令により行います。

例 SET1 RBE ; RBE 1

CLR1 RBE ; RBE 0

SEL RB0 ; RBS 0

SEL RB3 ; RBS 3

μPD754244に内蔵されている汎用レジスタ・エリアは,4ビット・レジスタとしての使用のほかに,レジスタ・ペアによる8ビット・レジスタとして使用ができ,8ビット・マイコンに匹敵する転送,演算,比較,増減命令によって,汎用レジスタ中心のプログラミングが可能となります。

#### (1)4ビット・レジスタとして使用する場合

汎用レジスタ・エリアを 4 ビット・レジスタとして使用する場合には , 図3 - 5 に示すように , RB=RBE・RBSで指定されたレジスタ・バンクの X , A , B , C , D , E , H , L , 計 8 個の汎用レジスタを使うことができます。このうち A レジスタは 4 ビット・アキュームレータとして , 4 ビット・データの転送 , 演算 , 比較等に中心的な働きをします。ほかの汎用レジスタは , アキュームレータとの転送 , 比較 , 増減ができます。

#### (2)8ビット・レジスタとして使用する場合

汎用レジスタ・エリアを8ビット・レジスタとして使用する場合には、図3-6に示すように、RB=RBE・RBSで指定されたレジスタ・バンクのレジスタ・ペアをXA, BC, DE, HLとし、レジスタ・パンク(RB)のビット0を反転したレジスタ・バンクのレジスタ・ペアをXA', BC', DE', HL'として計8個の8ビット・レジスタを使うことができます。このうちXAレジスタ・ペアは、8ビット・アキュームレータとして、8ビット・データの転送、演算、比較などに中心的な働きをします。ほかのレジスタ・ペアは、アキュームレータとの転送、演算、比較、増減ができます。また、HLレジスタ・ペアは、主にデータ・ポインタとして機能します。DE, DLレジスタ・ペアも補助的なデータ・ポインタとして機能します。

**例1.** INCS HL ; HL HL+1, HL=00Hでスキップ

ADDS XA, BC ; XA XA+BC, キャリーでスキップ

SUBC DE', XA ; DE' DE' - XA - CY

MOV XA, XA'; XA XA'

MOVT XA, @PCDE ; XA (PC11-8+DE) ROM, テーブル参照

SKE XA,BC ; XA=BCならスキップ

2.タイマ・カウンタ 0 のカウント・レジスタ (TO) の値がBC'レジスタ・ペアの値より大きい かどうかをテストし大きくなるまで待つ。

CLR1 MBE

NO: MOV XA, TO ; カウント・レジスタ読み取り

SUBS XA, BC'; XA BC'?

BR YES ; YES

BR NO ; NO

図3-5 汎用レジスタの構成(4ビット処理の場合)

| х | 01H | А | 00H |                            |

|---|-----|---|-----|----------------------------|

| Н | 03H | L | 02H | レジスタ・バンク0<br>(RBE・RBS = 0) |

| D | 05H | E | 04H |                            |

| В | 07H | С | 06H |                            |

| х | 09H | А | 08H |                            |

| н | 0BH | L | 0AH | レジスタ・バンク1                  |

| D | 0DH | Е | 0CH | ( RBE • RBS = 1 )          |

| В | 0FH | С | 0EH |                            |

| Х | 11H | А | 10H |                            |

| н | 13H | L | 12H | レジスタ・バンク2                  |

| D | 15H | Е | 14H | ( RBE • RBS = 2 )          |

| В | 17H | С | 16H |                            |

| Х | 19H | А | 18H |                            |

| Н | 1BH | L | 1AH | レジスタ・バンク3                  |

| D | 1DH | E | 1CH | (RBE · RBS = 3)            |

| В | 1FH | С | 1EH |                            |

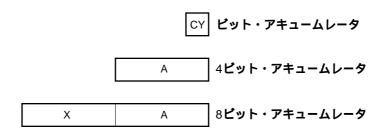

図3-6 汎用レジスタの構成(8ビット処理の場合)

## 3.3 メモリ・マップトI/O

$\mu$  PD754244は,図3-2に示したようにデータ・メモリ空間上のF80H-FFFH番地に入出力ポートやタイマなどの周辺ハードウエアをマッピングしたメモリ・マップトI/Oを採用しています。このため,周辺ハードウエアを制御する特別な命令はなく,すべてメモリ操作命令により制御します(一部,プログラムをわかりやすくするためのハードウエア制御のニモニックが用意してあります)。

周辺ハードウエアを操作する場合は表3-4のようなアドレシング・モードが使用できます。

表3-4 周辺ハードウエア操作時に適用可能なアドレシング・モード

|         | 適用可能なアドレシング・モード                       | 適用可能なハードウエア            |

|---------|---------------------------------------|------------------------|

| ビット操作   | MBE=0,または(MBE=1,MBS=15)として            | ビット操作可能なすべての           |

|         | 直接アドレシングmem. bitで指定                   | ハードウエア                 |

|         | MBE, MBSにかかわらず,                       | IST1, IST0, MBE, RBE   |

|         | 直接アドレシングfmem.bitで指定                   | IE×××, IRQ×××, PORTn.× |

|         | MBE, MBSにかかわらず,                       | BSBn. x                |

|         | 間接アドレシングpmem.@Lで指定                    | PORTn. x               |

| 4 ビット操作 | MBE=0,または(MBE=1,MBS=15)として            | 4 ビット操作可能なすべての         |

|         | 直接アドレシングmemで指定                        | ハードウエア                 |

|         | (MBE = 1, MBS = 15) として               |                        |

|         | レジスタ間接アドレシング@HLで指定                    |                        |

| 8 ビット操作 | MBE = 0,または(MBE = 1,MBS = 15)として直接アドレ | 8 ビット操作可能なすべての         |

|         | シングmemで指定。ただし,memは偶数アドレス              | ハードウエア                 |

|         | MBE = 1 , MBS = 15としてレジスタ間接アドレシング@HLで |                        |

|         | 指定。ただし , Lレジスタの内容は偶数                  |                        |

例 CLR1 MBE ; MBE=0

SET1 TM0.3 ; タイマ0のスタート

EI IEO ; INTOの許可 DI IET1 ; INTT1の禁止

SKTCLR IRQ2 ; INT2要求フラグのテスト・アンド・クリア

SET1 PORT3. @L ; ポート3のセット IN A, PORT6 ; A ポート6

図3 - 7にµPD754244のI/Oマップをまとめます。

同図における項目の意味は次のようになっています。

略号......内蔵されたハードウエアのアドレスを示すネームです。

命令のオペランド欄に記述できます。

R/W......該当するハードウエアが,読み出し/書き込み可能かどうかを示します。

R/W : 読み出し(Read)/書き込み(Write)可能

R : 読み出し (Read ) のみ

W:書き込み(Write)のみ

操作可能なビット数..........該当するハードウエアを操作する場合に,適用可能な処理ビット数を示し

ます。

: その欄で使用している単位(1/4/8ビット)でのビットの操作が可能。

: 一部のビットのみ操作が可能。操作の可能なビットについては備考欄

を参照してください。

- : その欄で使用している単位(1/4/8ビット)でのビットの操作が不可

能。

ビット操作アドレシング......該当するハードウエアをビット操作する場合に,適用可能なビット操作アドレシングを示します。

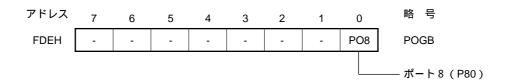

### 図3-7 µPD754244 I/Oマップ(1/8)

| 71117 | )                   |                       | 名称(略号    | )        | DAA | 操作可  | 『能なビ | ット数  | ビット操作    | /# +×             |

|-------|---------------------|-----------------------|----------|----------|-----|------|------|------|----------|-------------------|

| アドレス  | b3                  | b2                    | b1       | b0       | R/W | 1ビット | 4ビット | 8ビット | アドレシング   | 備考                |

| F80H  | スタック・               | ポインタ(                 | SP)      |          | R/W | -    | -    |      | -        | ビット 0 は<br>0 に固定  |

|       |                     |                       |          |          |     |      |      |      |          |                   |

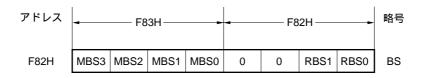

| F82H  |                     | バンク選択<br>             |          | RBS)     | R   | -    |      |      | -        | 注1                |

| F83H  | L                   | 【レジスタ( <br><br>、ンク選択レ |          | <br>(S)  |     | -    |      |      |          |                   |

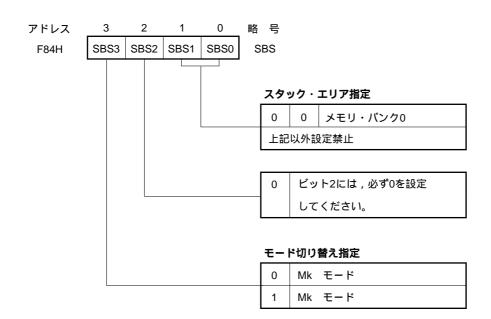

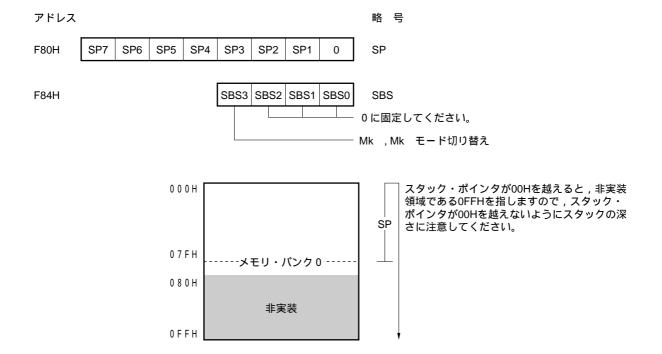

| F84H  | スタック・               | バンク選択                 | レジスタ(8   | SBS)     | R/W | -    |      | -    | -        |                   |

| F85H  | ベーシック・イ             | ンターバル・タイ              | (マ・モード・レ | ジスタ(BTM) | W   |      |      | -    | mem. bit | ビット3のみ<br>ビット操作可能 |

| F86H  | ベーシック               | ・インター                 | バル・タイマ   | ₹(BT)    | R   | -    | -    |      | -        |                   |

|       |                     |                       |          |          |     |      |      |      |          |                   |

| F88H  | タイマ・カ               | 1ウンタ2ハ                | イ・レベル    | 期間設定用    | R/W | -    | -    |      | _        |                   |

|       | モジュロ・               | レジスタ(                 | TMOD2H)  |          |     |      |      |      |          |                   |

| F8AH  | 非実装                 |                       |          |          |     |      |      |      |          |                   |

| F8BH  | WDTM <sup>注 2</sup> | -                     | -        | -        | W   |      | -    | -    | mem. bit |                   |

| F8CH  | 非実装                 |                       |          |          |     |      |      |      |          |                   |

| F8FH  |                     |                       |          |          |     |      |      |      |          |                   |

注1.4ビット操作では、RBSおよびMBSとして別々に操作可能。

8ビット操作では,BSとして操作可能。

MBS, RBSへの書き込みは , それぞれSEL MBn (n=0 , 4 , 15), SEL RBn (n=0-3) 命令で行って ください。

2.WDTM:ウォッチドッグ・タイマ許可フラグ(W);一度セットすると命令ではクリアできません。

図3-7 µPD754244 I/Oマップ(2/8)

| 71117 | ハードウエア名称(略号)                        | DAM | 操作可  | 丁能なビッ | ット数  | ビット操作  | /# #¥             |

|-------|-------------------------------------|-----|------|-------|------|--------|-------------------|

| アドレス  | b3 b2 b1 b0                         | R/W | 1ビット | 4ビット  | 8ビット | アドレシング | 備考                |

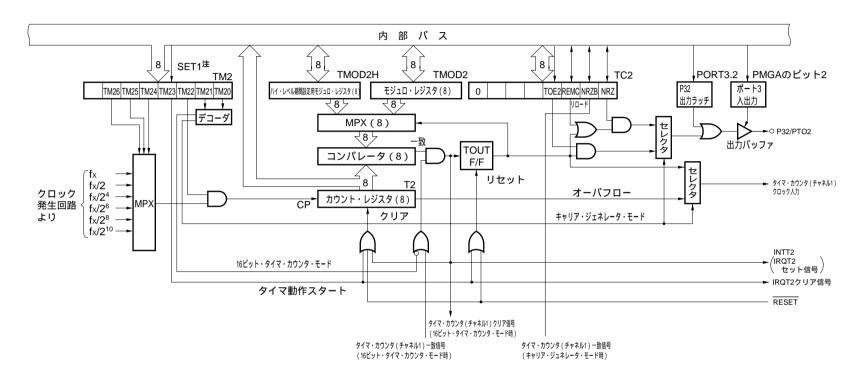

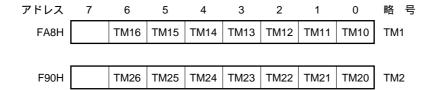

| F90H  | タイマ・カウンタ 2 モード・レジスタ                 | R/W | (W)  | -     |      | -      | ビット 3 のみビット操作可能   |

|       | (TM2)                               |     | -    | -     |      | -      |                   |

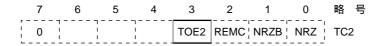

| F92H  | TOE2 REMC NRZB NRZ                  | R/W |      |       |      | -      | ビット 3 は<br>W のみ可能 |

|       | タイマ・カウンタ 2 コントロール・レジスタ( TC2 )  <br> |     | -    | -     |      | -      | ビット3には<br>0のみ記述可能 |

| F94H  | タイマ・カウンタ 2 カウント・レジスタ                | R   | -    | -     |      | -      |                   |

|       | (T2)                                |     |      |       |      |        |                   |

| F96H  | タイマ・カウンタ2モジュロ・レジスタ                  | R/W | -    | -     |      | -      |                   |

|       | (TMOD2)                             |     |      |       |      |        |                   |

| F98H  | 非実装                                 |     |      |       |      |        |                   |

図3-7 µPD754244 I/Oマップ(3/8)

| マドレフ | J                  | \- ドウエア | 名称(略号  | )    | DAA | 操作可  | 可能など、 | ット数  | ビット操作    | 備考                  |

|------|--------------------|---------|--------|------|-----|------|-------|------|----------|---------------------|

| アドレス | b3                 | b2      | b1     | b0   | R/W | 1ビット | 4ビット  | 8ビット | アドレシング   | 備考                  |

| FA0H | タイマ・               | カウンタ(   | 0 モード・ | レジスタ | R/W | (W)  | -     |      | mem. bit | ビット 3 のみ<br>ビット操作可能 |

|      | (TM0)              |         |        |      |     | -    | -     |      | -        |                     |

| FA2H | TOE0 <sup>注1</sup> | -       | -      | -    | W   |      | -     | -    | mem. bit |                     |

| FA3H | 非実装                |         |        |      |     |      |       |      |          |                     |

| FA4H | タイマ・:              | カウンタ 0  | カウント・  | レジスタ | R   | -    | -     |      | -        |                     |

|      | (T0)               |         |        |      |     |      |       |      |          |                     |

| FA6H | タイマ・:              | カウンタ 0  | モジュロ・  | レジスタ | R/W | -    | _     |      | -        |                     |

|      | (TMOD0             | )       |        |      |     |      |       |      |          |                     |

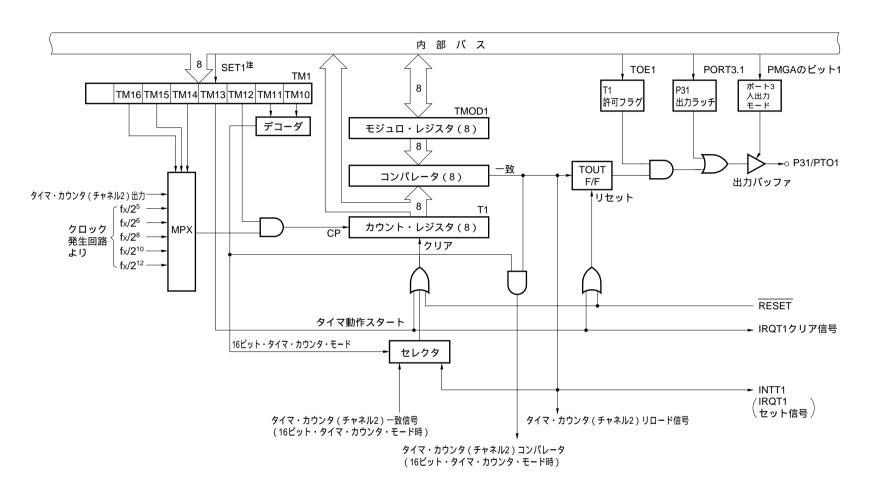

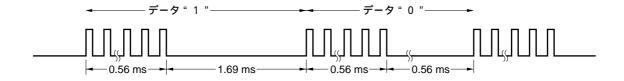

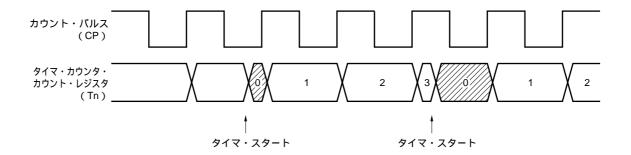

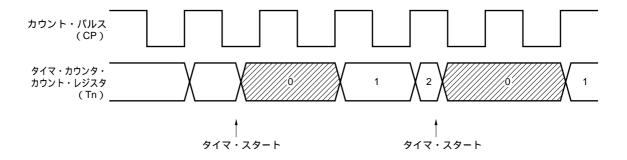

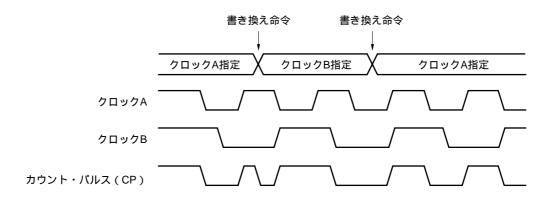

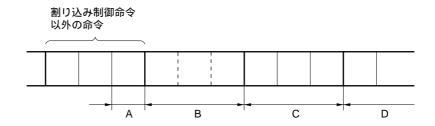

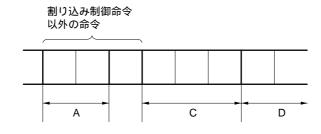

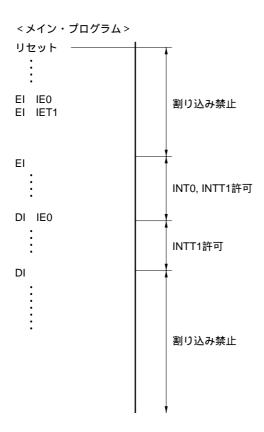

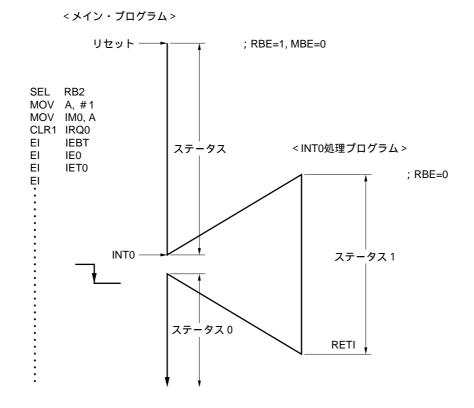

| FA8H | タイマ・               | カウンタ    | 1モード・  | レジスタ | R/W | (W)  | -     |      | mem. bit | ビット 3 のみ<br>ビット操作可能 |