# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

78K0/KF1+

8ビット・シングルチップ・マイクロコンピュータ

μPD78F0148H μPD78F0148H(A) μPD78F0148H(A1) μPD78F0148HD (メ モ)

# 目次要約

| 第1章         | 概 説 17                                            |

|-------------|---------------------------------------------------|

| 第2章         | <b>端子機能</b> 30                                    |

| <b>第</b> 3章 | CPU <b>アーキテクチャ</b> 45                             |

| <b>第</b> 4章 | <b>ポート機能</b> 74                                   |

| <b>第</b> 5章 | 外部パス・インタフェース 109                                  |

| 第6章         | <b>クロック発生回路</b> 120                               |

| <b>第</b> 7章 | 16ピット・タイマ/イベント・カウンタ00, 01 147                     |

| 第8章         | 8 <b>ビット・タイマ / イベント・カウンタ</b> 50, 51 193           |

| 第9章         | 8 <b>ビット・タイマ</b> H0, H1 212                       |

| 第10章        | 時計用タイマ 238                                        |

| 第11章        | ウォッチドッグ・タイマ 244                                   |

| 第12章        | <b>クロック出力 / ブザー出力制御回路</b> 255                     |

| 第13章        | A/D <b>コンバータ</b> 260                              |

| 第14章        | シリアル・インタフェースUART0 283                             |

| 第15章        | シリアル・インタフェースUART6 305                             |

| 第16章        | シリアル・インタフェースCSI10, CSI11 345                      |

| 第17章        | シリアル・インタフェースCSIA0 366                             |

| 第18章        | <b>乗除算器</b> 409                                   |

| 第19章        | 割り込み機能 419                                        |

| 第20章        | <b>キー割り込み機能</b> 439                               |

| 第21章        | ス <b>タンバイ機能</b> 441                               |

| 第22章        | リ <b>セット機能</b> 456                                |

| 第23章        | クロック・モニタ 464                                      |

| 第24章        | <b>パワーオン・クリア回路</b> 471                            |

| 第25章        | <b>低電圧検出回路</b> 475                                |

| 第26章        | オプション・バイト 487                                     |

| 第27章        | フラッシュ・メモリ 490                                     |

| 第28章        | <b>オンチップ・ディバグ機能(</b> μ PD78F0148HD <b>のみ)</b> 517 |

| 第29章        | <b>命令セットの概要</b> 519                               |

| 第30章        | <b>電気的特性(標準品,(A)水準品)</b> 534                      |

| 第31章        | <b>電気的特性((A1)水準品)</b> 556                         |

| 第32章        | <b>外 形 図</b> 573                                  |

| 第33章        | <b>半田付け推奨条件</b> 575                               |

| 第34章        | <b>ウエイトに関する注意事項</b> 577                           |

| 付録A         | 開発ツール 580                                         |

| <b>付録</b> B | <b>ターゲット・システム設計上の注意</b> 587                       |

| 付録C         | <b>レジスタ索引</b> 589                                 |

| 付録D         | <b>注意事項一覧</b> 597                                 |

| 付録E         | <b>改版履歴</b> 618                                   |

# CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また, MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

#### 置源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については,その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

Windows, Windows NTおよびWindows XPは ,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

SuperFlash®は,米国Silicon Storage Technology, Inc.の米国,日本などの国における登録商標です。

注意:本製品はSilicon Storage Technology, Inc.からライセンスを受けたSuperFlash®を使用しています。

- ◆本資料に記載されている内容は2005年12月現在のもので、今後、予告なく変更することがあります。 量産設計の際には最新の個別データ・シート等をご参照ください。

- ◆文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切その責を負いません。

- 当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- ◆本資料に記載された回路,ソフトウエアおよびこれらに関する情報は,半導体製品の動作例,応用例を 説明するものです。お客様の機器の設計において,回路,ソフトウエアおよびこれらに関する情報を使 用する場合には,お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し,当社は,一切その責を負いません。

- 当社は、当社製品の品質、信頼性の向上に努めておりますが、当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命、身体および財産に対する損害の危険を最小限度にするために、冗長設計、延焼対策設計、誤動作防止設計等安全設計を行ってください。

当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

(注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2) 本事項において使用されている「当社製品」とは、(1) において定義された当社の開発,製造

M8E 02.11

# はじめに

対象者 このマニュアルは78K0/KF1+の機能を理解し、その応用システムや応用プログラムを設計、開発する ユーザのエンジニアを対象としています。

対象製品は,次に示す各製品です。

• 78K0/KF1+ : μPD78F0148H, 78F0148H(A), 78F0148H(A1), 78F0148HD

**目 的** このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

構 成 78K0/KF1+のマニュアルは,このマニュアルと命令編(78K/0シリーズ共通)の2冊に分かれています。

78K0/KF1+ ユーザーズ・マニュアル 78K/0シリーズ ユーザーズ・マニュアル 命令編

端子機能

内部ブロック機能

割り込み

その他の内蔵周辺機能

電気的特性

CPU機能

命令セット

命令の説明

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

(A) 水準品, (A1) 水準品のマニュアルとしてお使いになる方へ

標準製品と(A)水準品,(A1)水準品は品質水準のみが異なります。(A)水準品,(A1)水準品については品名を次のように読み替えてください。

•  $\mu$  PD780148H  $\mu$  PD780148H(A) , 780148H(A1)

一通りの機能を理解しようとするとき

目次に従って読んでください。本文欄外の 印は,本版で改訂された主な箇所を示しています。 この" "をPDF上でコピーして「検索する文字列」に指定することによって,改版箇所を容易に 検索できます。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がRA78K0では予約語に、CC78K0では #pragma sfr指令で、sfr変数として定義されているものです。

レジスタ名が分かっていてレジスタの詳細を確認するとき

付録C レジスタ索引を利用してください。

78K/0シリーズの命令機能の詳細を知りたいとき

別冊の78K/0シリーズ ユーザーズ・マニュアル 命令編(U12326J)を参照してください。

注意 このマニュアル中の使用例は,一般電子機器用の『標準』品質水準用に作成してあります。『特別』品質水準を要求する用途にこのマニュアル中の使用例を使用する場合は,実際に使用する各部分および回路について,その品質水準についてご検討のうえご使用ください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : ××× (端子, 信号名称に上線)

注 : 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

### 78K0/KF1+と78K0/KF1の違い

|        | シリーズ名         | 78K0/KF1+           | 78K0/KF1                           |

|--------|---------------|---------------------|------------------------------------|

| 項 目    |               |                     |                                    |

| マスクROM | 製品            | なし                  | あり                                 |

| フラッシ   | 電源            | 単電源                 | 二電源                                |

| ュ・メモリ  | セルフ・プログラミング機能 | あり                  | なし                                 |

| 製品     | オプション・バイト     | 内蔵発振器停止可 / 不可を選択    | なし                                 |

| オンチップ・ | ディバグ機能搭載品     | あり (μPD78F0148HD)   | なし                                 |

| レギュレータ | 7             | なし                  | あり                                 |

| パワーオン・ | クリア機能         | 2.1 V±0.1 V (固定)    | 2.85 V ± 0.15 Vまたは3.5 V ± 0.2 V選択可 |

| 最小命令実行 | <b>丁時間</b>    | 0.125 μs(16 MHz動作時) | 0.166 μs(12 MHz動作時)                |

### 関連資料

関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

### デバイスの関連資料

| 資料名                                         | 資料      | 播号      |

|---------------------------------------------|---------|---------|

|                                             | 和 文     | 英 文     |

| 78K0/KF1+ ユーザーズ・マニュアル                       | このマニュアル | U16819E |

| 78K0/KF1 ユーザーズ・マニュアル                        | U15947J | U15947E |

| 78K/0シリーズ ユーザーズ・マニュアル 命令編                   | U12326J | U12326E |

| 78K0/Kx1+ ユーザーズ・マニュアル フラッシュ・メモリ・セルフ・プログラミング | U16701J | U16701E |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 開発ツール (ソフトウエア) の資料 (ユーザーズ・マニュアル)

| 資料 名                        |                | 資料      | 番号      |

|-----------------------------|----------------|---------|---------|

|                             |                | 和 文     | 英 文     |

| RA78K0 Ver.3.80 アセンブラ・パッケージ | 操作編            | U17199J | U17199E |

|                             | 言語編            | U17198J | U17198E |

|                             | 構造化アセンブリ言語編    | U17197J | U17197E |

| CC78K0 Ver.3.70 Cコンパイラ      | 操作編            | U17201J | U17201E |

|                             | 言語編            | U17200J | U17200E |

| SM+ システム・シミュレータ             | 操作編            | U17246J | U17246E |

|                             | ユーザ・オープン・インタフェ | U17247J | U17247E |

|                             | ース編            |         |         |

| ID78K0-QB Ver.2.90 統合ディバッガ  | 操作編            | U17437J | U17437E |

| PM plus Ver.5.20            |                | U16934J | U16934E |

# 開発ツール (ハードウエア) の資料 (ユーザーズ・マニュアル)

| 資料名                           |        | 資料 | 番号     |   |

|-------------------------------|--------|----|--------|---|

|                               | 和      | 文  | 英      | 文 |

| QB-78K0KX1H インサーキット・エミュレータ    | U17081 | J  | U17081 | E |

| QB-78K0MINI オンチップ・ディバグ・エミュレータ | U17029 | J  | U17029 | E |

### フラッシュ・メモリ書き込み用の資料

| 資料名                                |         | 資料 | 番号      |   |

|------------------------------------|---------|----|---------|---|

|                                    | 和       | 文  | 英       | 文 |

| PG-FP4 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U15260J |    | U15260I | = |

### その他の資料

| 資料名                                                   |         | 資料 | 番号      |   |

|-------------------------------------------------------|---------|----|---------|---|

|                                                       | 和       | 文  | 英       | 文 |

| SEMICONDUCTOR SELECTION GUIDE -Products and Packages- | X13769X |    |         |   |

| 半導体デバイス 実装マニュアル                                       | 注       |    |         |   |

| NEC半導体デバイスの品質水準                                       | C11531J |    | C11531E | Ξ |

| NEC半導体デバイスの信頼性品質管理                                    | C10983J |    | C10983E | Ξ |

| 静電気放電(ESD)破壊対策ガイド                                     | C11892J |    | C11892  | Ξ |

| 半導体 品質 / 信頼性ハンドブック                                    | C12769J |    | -       |   |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                              | U11416J |    | -       |   |

# 注 「半導体デバイス実装マニュアル」のホーム・ページ参照

和文:http://www.necel.com/pkg/ja/jissou/index.html 英文:http://www.necel.com/pkg/en/mount/index.html

# 注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 目 次

| 第1章         | 概 説 17                                                |

|-------------|-------------------------------------------------------|

| 4 4         | A土 体的 4フ                                              |

| 1. 1        | 特 徴 17<br>応用分野 18                                     |

|             | ルルボカジ 10<br>オーダ情報 18                                  |

|             | 端子接続図 (Top View ) 19                                  |

|             | Kx1 <b>シリーズの展開</b> 21                                 |

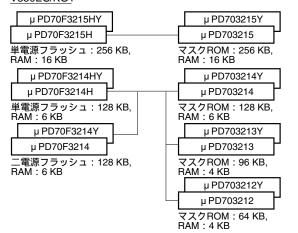

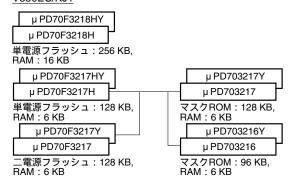

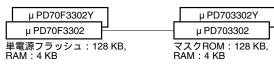

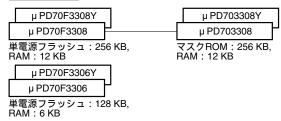

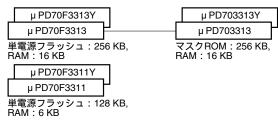

|             | 1. 5. 1 78K0/Kx1, 78K0/Kx1+の製品展開 21                   |

|             | 1. 5. 2 V850ES/Kx1, V850ES/Kx1+の製品展開 24               |

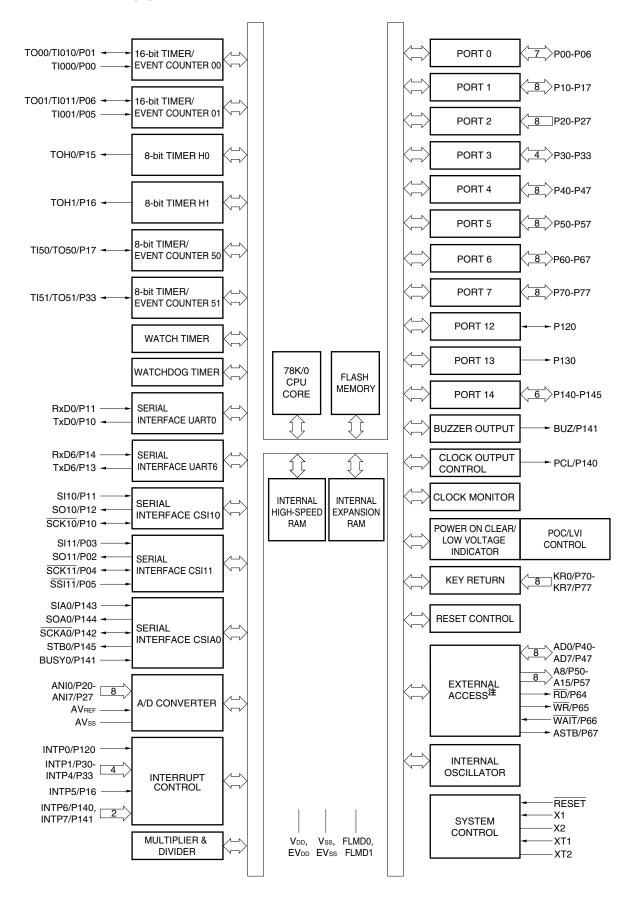

| 1. 6        | プロック図 27                                              |

| 1. 7        | <b>機能概要</b> 28                                        |

|             |                                                       |

| 第2章         | 端子機能 30                                               |

| 2. 1        |                                                       |

|             | <b>端子機能一覧</b> 30<br><b>端子機能の説明</b> 34                 |

| 2. 2        | 2. 2. 1 P00-P06 (Port 0) 34                           |

|             | 2. 2. 2 P10-P17 (Port 1) 35                           |

|             | 2. 2. 3 P20-P27 (Port 2) 36                           |

|             | 2. 2. 4 P30-P33 (Port 3) 36                           |

|             | 2. 2. 5 P40-P47 (Port 4) 37                           |

|             | 2. 2. 6 P50-P57 (Port 5) 37                           |

|             | 2. 2. 7 P60-P67 ( Port 6 ) 37                         |

|             | 2. 2. 8 P70-P77 (Port 7) 38                           |

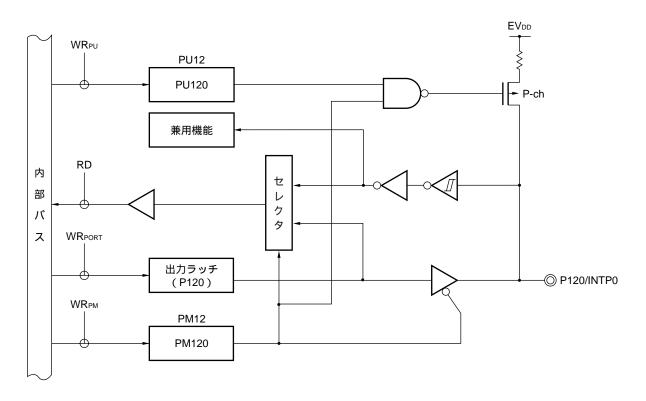

|             | 2. 2. 9 P120 ( Port 12 ) 38                           |

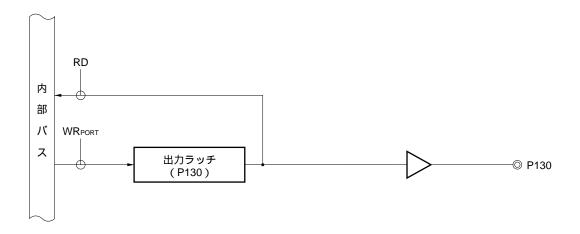

|             | 2. 2. 10 P130 (Port 13) 38                            |

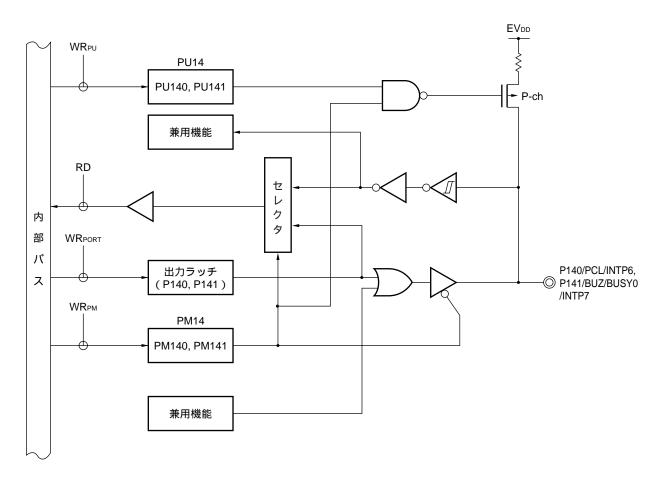

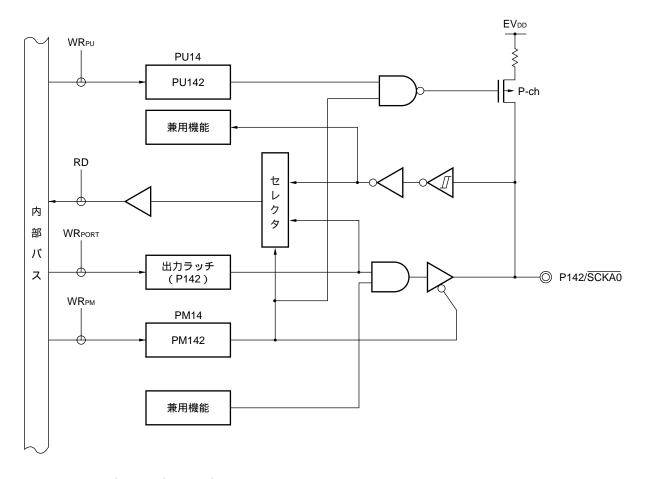

|             | 2. 2. 11 P140-P145 ( Port 14 ) 38                     |

|             | 2. 2. 12 AVREF 39                                     |

|             | 2. 2. 13 AVss 40                                      |

|             | 2. 2. 14 RESET 40                                     |

|             | 2. 2. 15 X1, X2 40                                    |

|             | 2. 2. 16 XT1, XT2 40                                  |

|             | 2. 2. 17 VDD, EVDD 40                                 |

|             | 2. 2. 18 Vss, EVss 40                                 |

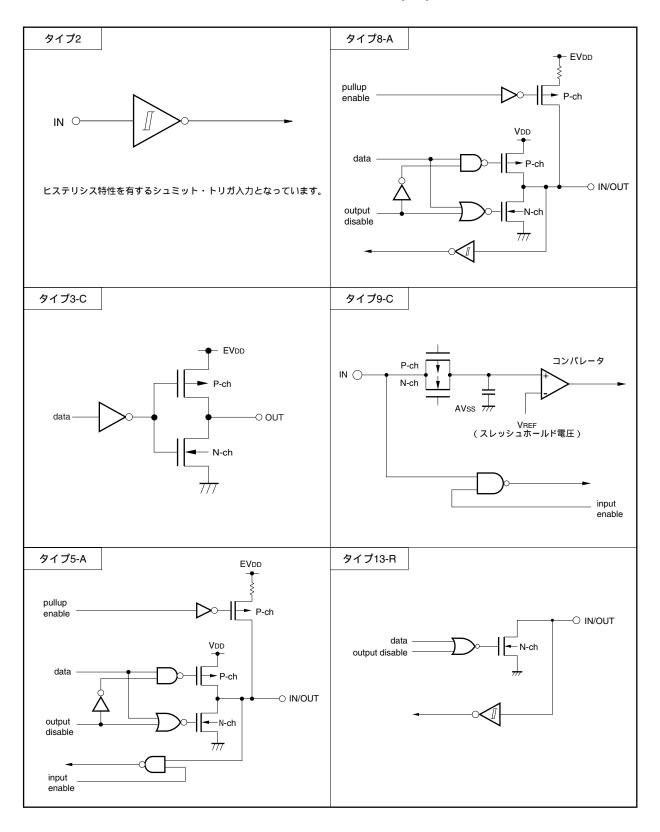

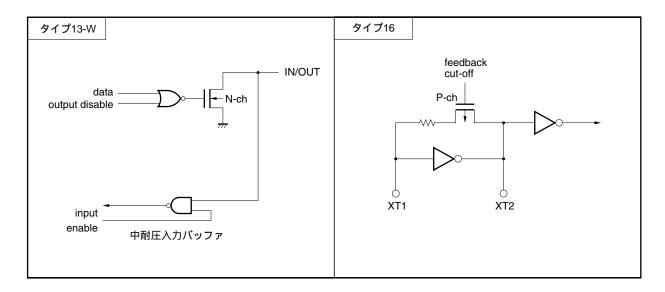

| 2.2         | 2. 2. 19 FLMD0, FLMD1 40<br>端子の入出力回路と未使用端子の処理 41      |

| 2. 3        | 城于の八山万回路と不使用城于の処理 41                                  |

| <b>第</b> 3章 | CPU <b>アーキテクチャ</b> 45                                 |

| 0.4         | メエリ交明 45                                              |

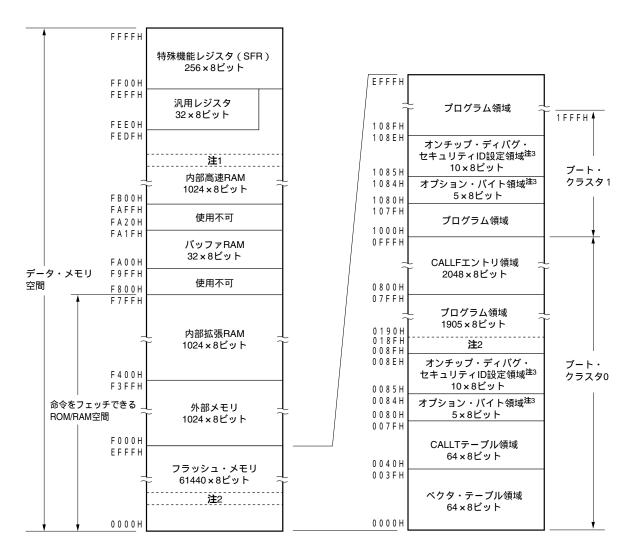

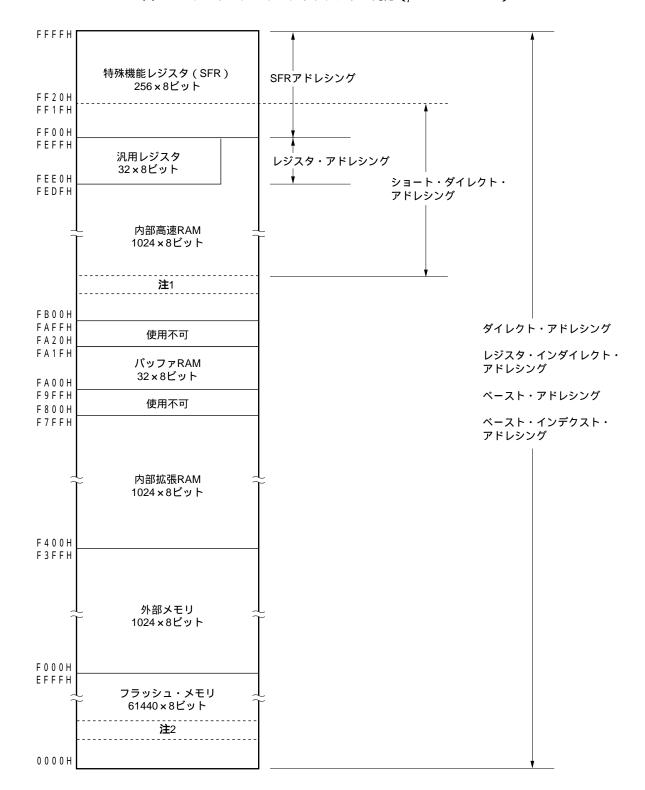

| J. T        | <b>メモリ空間</b> 45<br>3. 1. 1 内部プログラム・メモリ空間 48           |

|             | 3.1.1 内部フログフム・メモリ空間 46<br>3.1.2 内部データ・メモリ空間 49        |

|             | 3.1.3 特殊機能レジスタ (SFR: Special Function Register) 領域 49 |

|             | 3.1.3 特殊機能レンスク(GFR:Special Function Register)模域 49    |

| 3. 2                 | プロセッサ・レジスタ 52                                                                                                                                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 3. 2. 1 制御レジスタ 52                                                                                                                                                                                                                                                            |

|                      | 3. 2. 2 汎用レジスタ 55                                                                                                                                                                                                                                                            |

|                      | 3. 2. 3 特殊機能レジスタ (SFR: Special Function Register) 57                                                                                                                                                                                                                         |

| 3. 3                 | 命令アドレスのアドレシング 62                                                                                                                                                                                                                                                             |

|                      | 3. 3. 1 レラティブ・アドレシング 62                                                                                                                                                                                                                                                      |

|                      | 3.3.2 イミーディエト・アドレシング 63                                                                                                                                                                                                                                                      |

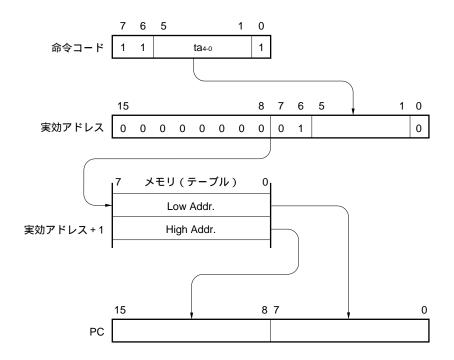

|                      | 3.3.3 テーブル・インダイレクト・アドレシング 64                                                                                                                                                                                                                                                 |

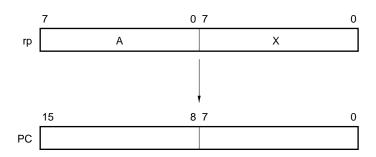

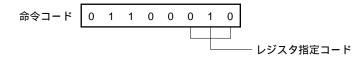

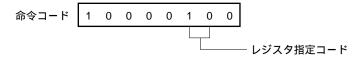

|                      | 3. 3. 4 レジスタ・アドレシング 64                                                                                                                                                                                                                                                       |

| 3. 4                 | オペランド・アドレスのアドレシング 65                                                                                                                                                                                                                                                         |

|                      | 3.4.1 インプライド・アドレシング 65                                                                                                                                                                                                                                                       |

|                      | 3.4.2 レジスタ・アドレシング 66                                                                                                                                                                                                                                                         |

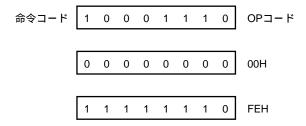

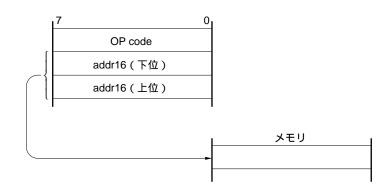

|                      | 3. 4. 3 ダイレクト・アドレシング 67                                                                                                                                                                                                                                                      |

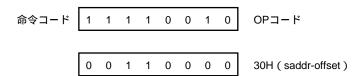

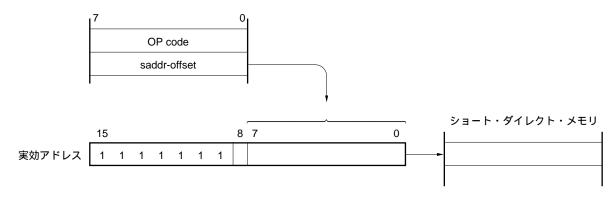

|                      | 3.4.4 ショート・ダイレクト・アドレシング 68                                                                                                                                                                                                                                                   |

|                      | 3. 4. 5 特殊機能レジスタ (SFR) アドレシング 69                                                                                                                                                                                                                                             |

|                      | 3. 4. 6 レジスタ・インダイレクト・アドレシング 70                                                                                                                                                                                                                                               |

|                      | 3.4.7 ベースト・アドレシング 71                                                                                                                                                                                                                                                         |

|                      | 3.4.8 ベースト・インデクスト・アドレシング 72                                                                                                                                                                                                                                                  |

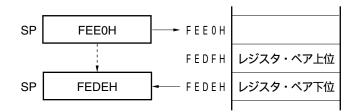

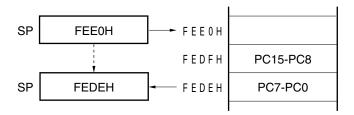

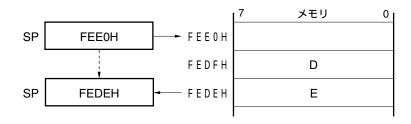

|                      | 3.4.9 スタック・アドレシング 73                                                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                              |

| 第4章                  | ポート機能 74                                                                                                                                                                                                                                                                     |

|                      |                                                                                                                                                                                                                                                                              |

|                      |                                                                                                                                                                                                                                                                              |

| 4. 1                 | <b>ポートの機能</b> 74                                                                                                                                                                                                                                                             |

|                      | ポートの機能 74<br>ポートの構成 77                                                                                                                                                                                                                                                       |

|                      |                                                                                                                                                                                                                                                                              |

|                      | ポートの構成 77                                                                                                                                                                                                                                                                    |

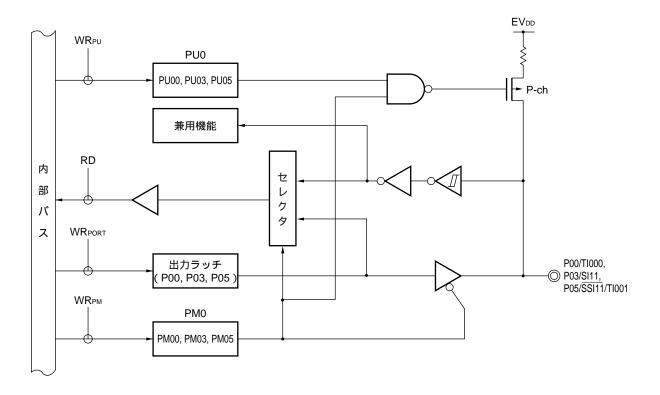

|                      | <b>ポートの構成</b> 77<br>4.2.1 ポート0 78                                                                                                                                                                                                                                            |

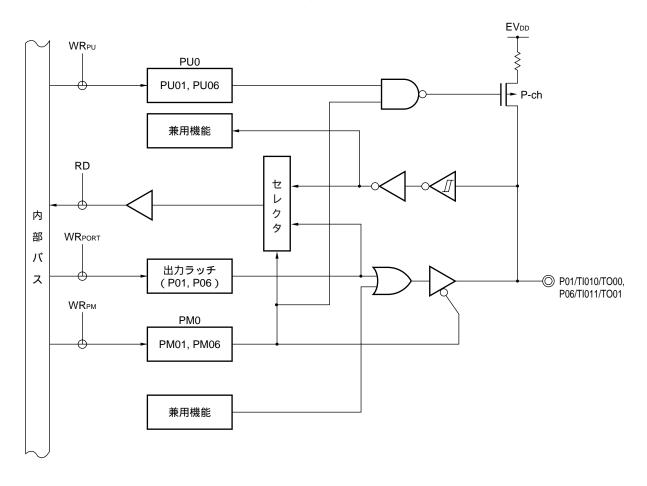

|                      | ポートの構成 77<br>4.2.1 ポート0 78<br>4.2.2 ポート1 82                                                                                                                                                                                                                                  |

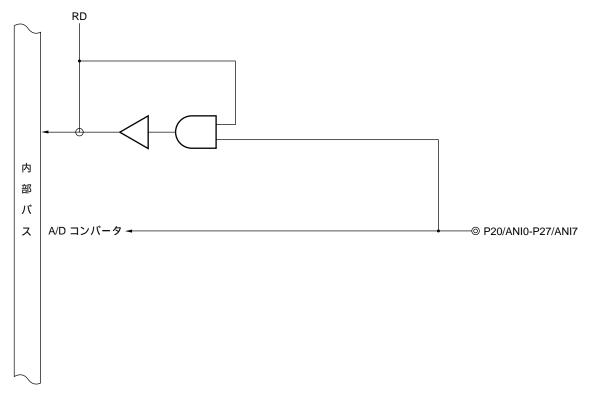

|                      | ポートの構成 77<br>4.2.1 ポート0 78<br>4.2.2 ポート1 82<br>4.2.3 ポート2 87                                                                                                                                                                                                                 |

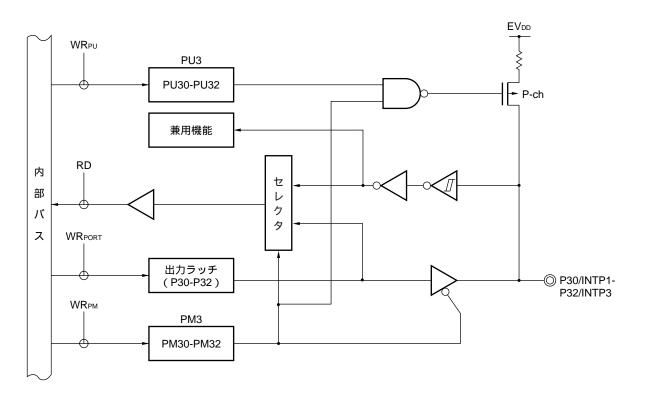

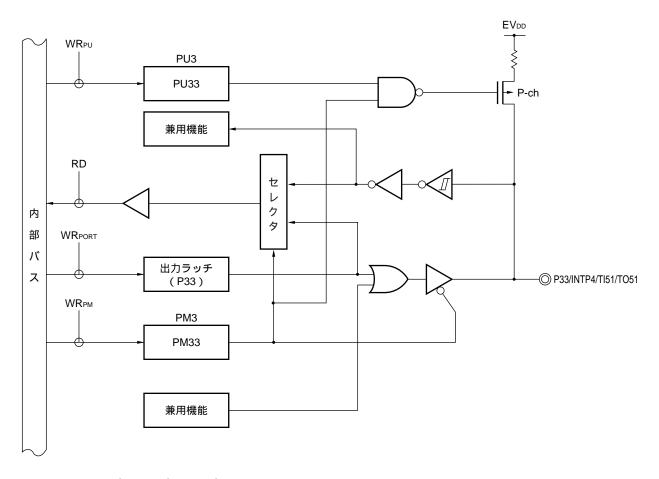

|                      | ポートの構成 77<br>4.2.1 ポート0 78<br>4.2.2 ポート1 82<br>4.2.3 ポート2 87<br>4.2.4 ポート3 88                                                                                                                                                                                                |

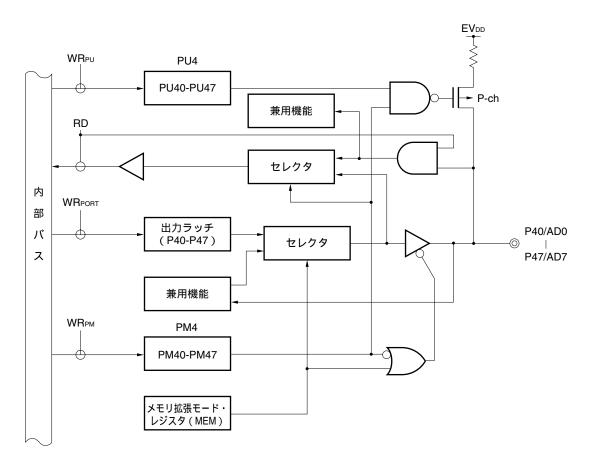

|                      | ポートの構成 77<br>4.2.1 ポート0 78<br>4.2.2 ポート1 82<br>4.2.3 ポート2 87<br>4.2.4 ポート3 88<br>4.2.5 ポート4 90                                                                                                                                                                               |

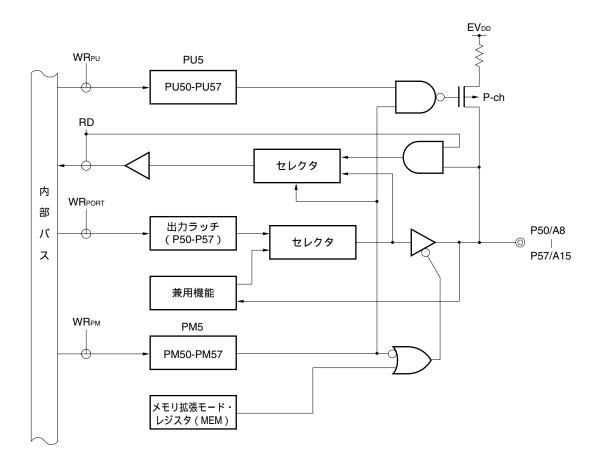

|                      | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91                                                                                                                                                                                |

|                      | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92                                                                                                                                                                  |

|                      | ポートの構成 77 4. 2. 1 ポート0 78 4. 2. 2 ポート1 82 4. 2. 3 ポート2 87 4. 2. 4 ポート3 88 4. 2. 5 ポート4 90 4. 2. 6 ポート5 91 4. 2. 7 ポート6 92 4. 2. 8 ポート7 95                                                                                                                                    |

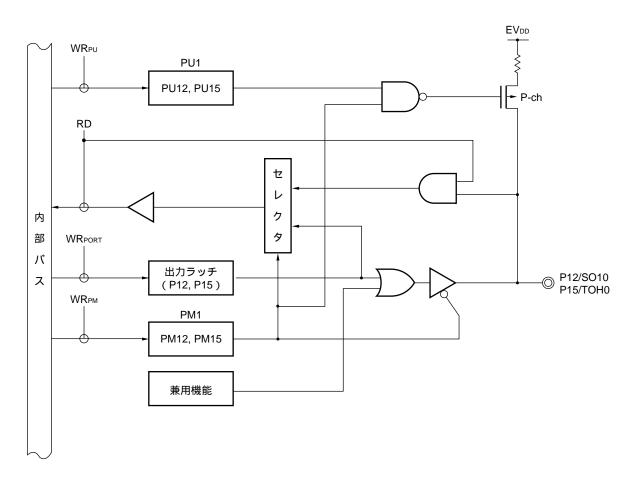

|                      | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96                                                                                                                                     |

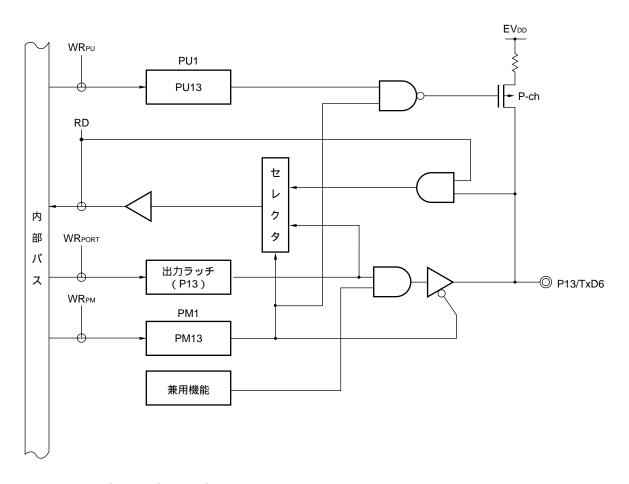

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97                                                                                                                     |

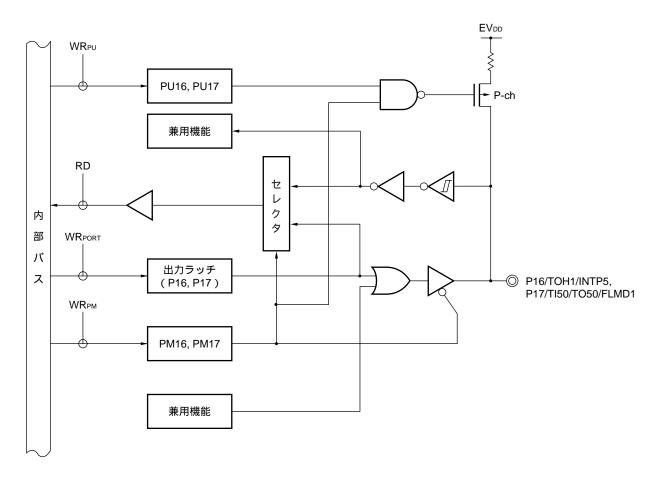

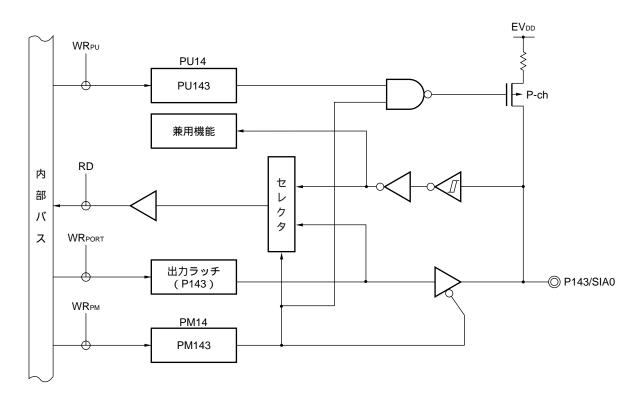

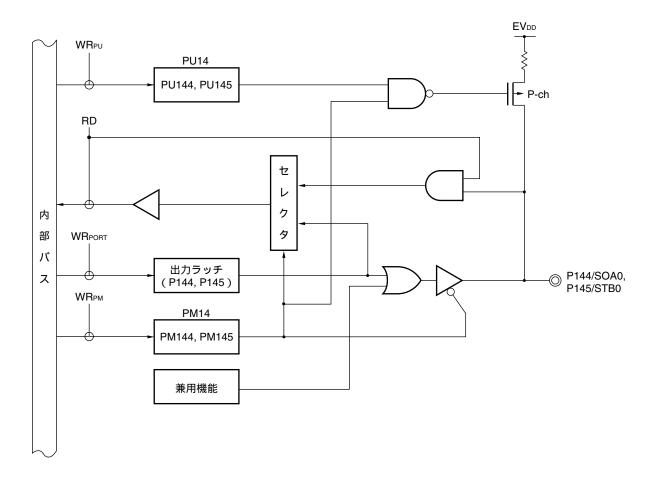

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97                                                                                                     |

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97 ポート機能を制御するレジスタ 102                                                                                  |

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 オート機能を制御するレジスタ 102 ポート機能の動作 108                                                                                     |

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97 ポート機能を制御するレジスタ 102 ポート機能の動作 108 4.4.1 入出力ポートへの書き込み 108                                              |

| 4. 2                 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97 ポート機能を制御するレジスタ 102 ポート機能の動作 108 4.4.1 入出力ポートへの書き込み 108                                              |

| 4. 2<br>4. 3<br>4. 4 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97 ポート機能を制御するレジスタ 102 ポート機能の動作 108 4.4.1 入出力ポートへの書き込み 108                                              |

| 4. 2<br>4. 3<br>4. 4 | ポートの構成 77 4.2.1 ポート0 78 4.2.2 ポート1 82 4.2.3 ポート2 87 4.2.4 ポート3 88 4.2.5 ポート4 90 4.2.6 ポート5 91 4.2.7 ポート6 92 4.2.8 ポート7 95 4.2.9 ポート12 96 4.2.10 ポート13 97 4.2.11 ポート14 97 ポート機能を制御するレジスタ 102 ポート機能の動作 108 4.4.1 入出力ポートへの書き込み 108 4.4.2 入出力ポートからの読み出し 108 4.4.3 入出力ポートでの演算 108 |

# 第

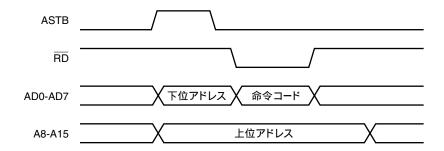

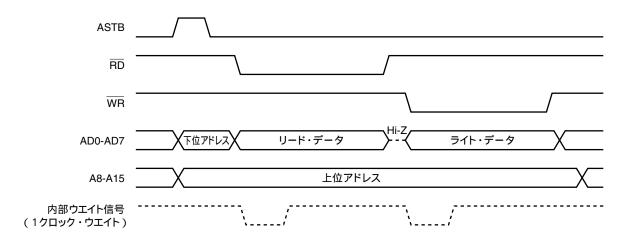

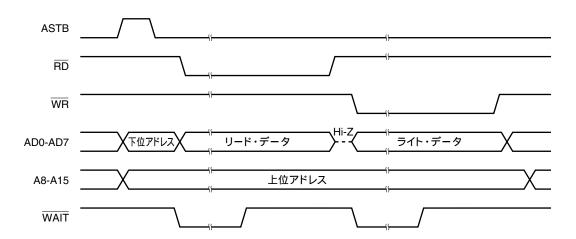

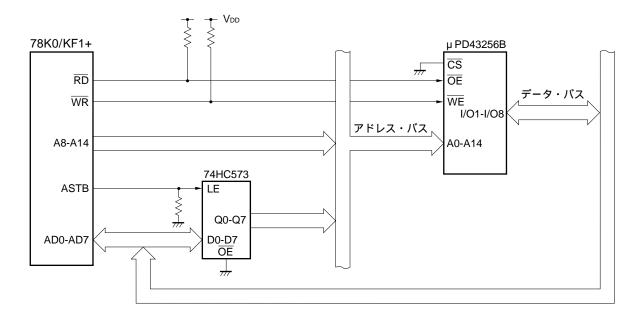

- 5.1 **外部パス・インタフェース** ... 109

- 5.2 外部パス・インタフェース機能を制御するレジスタ ... 112

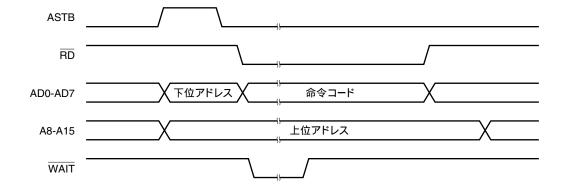

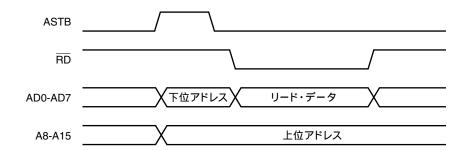

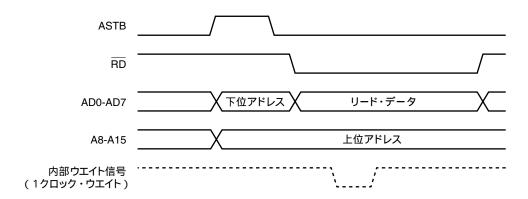

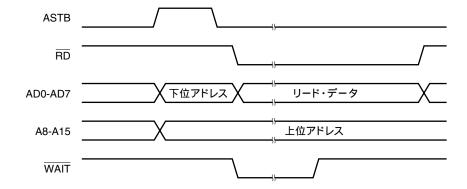

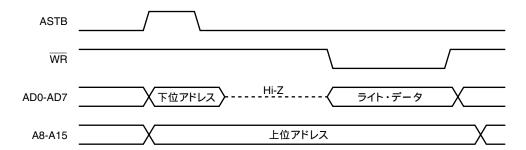

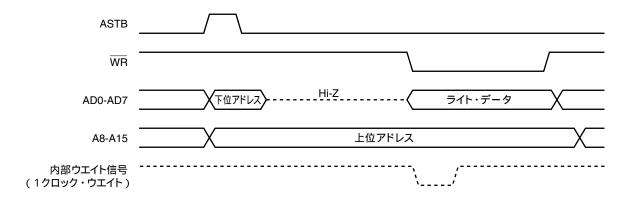

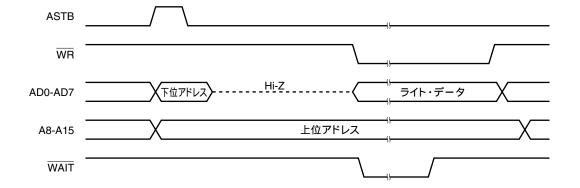

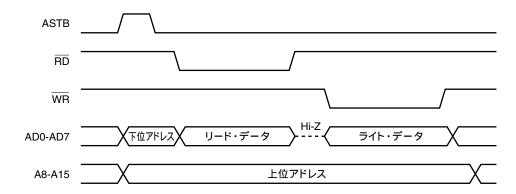

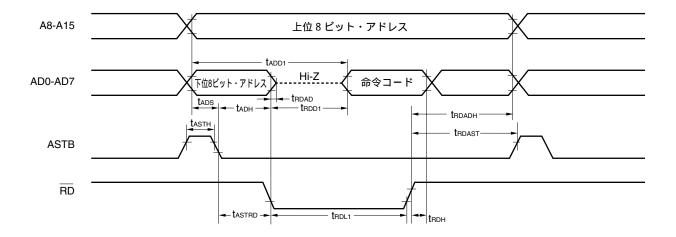

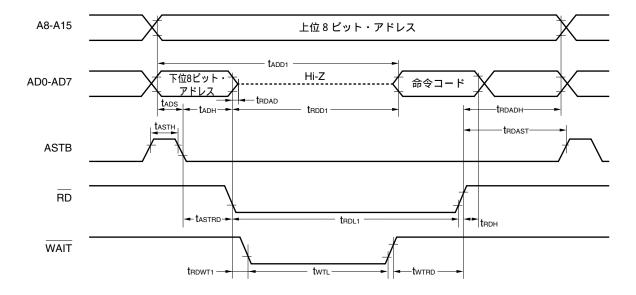

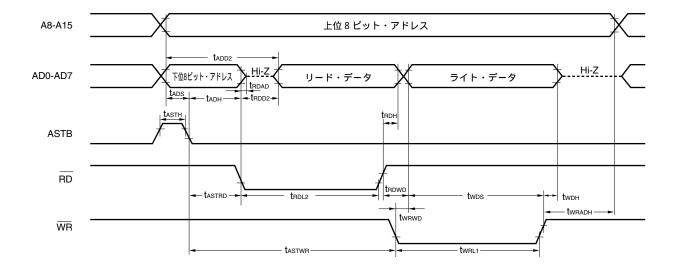

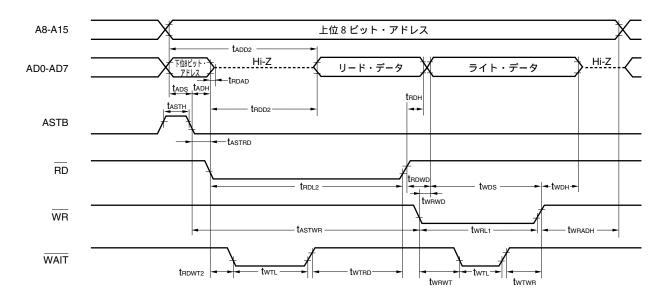

- 5.3 外部パス・インタフェース機能のタイミング ... 114

- 5.4 メモリとの接続例 ... 119

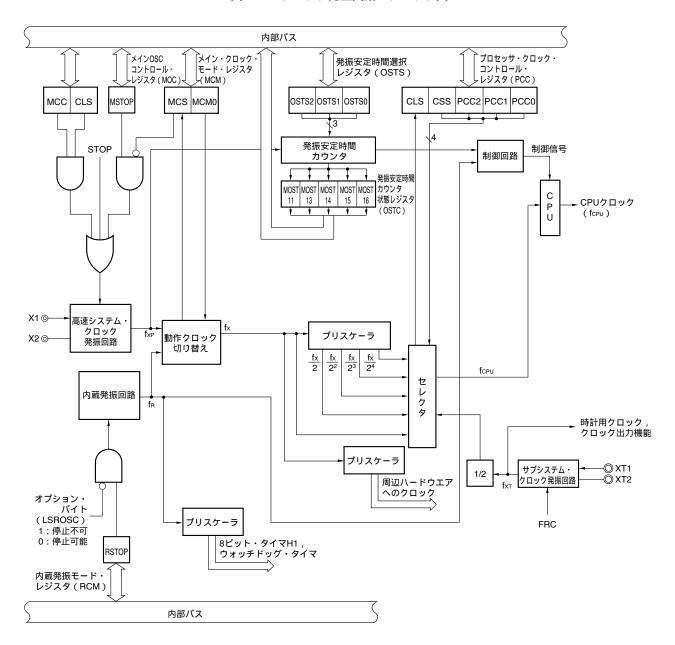

| <b>第</b> 6章 | <b>クロック発生回路</b> 120                                        |

|-------------|------------------------------------------------------------|

| 6. 1        | <b>クロック発生回路の機能</b> 120                                     |

|             | クロック発生回路の構成 120                                            |

|             | クロック発生回路を制御するレジスタ 122                                      |

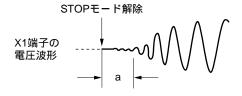

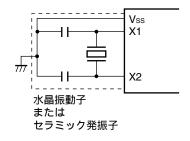

|             | システム・クロック発振回路 129                                          |

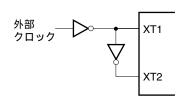

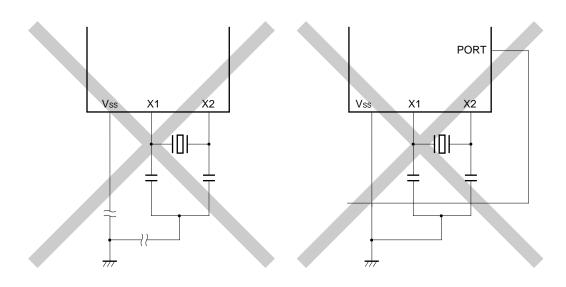

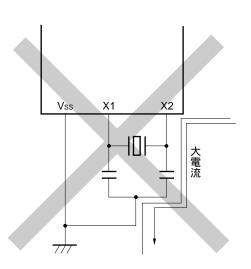

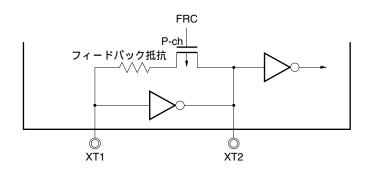

| <b>0</b>    | 6. 4. 1 高速システム・クロック発振回路 129                                |

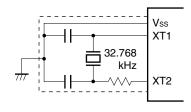

|             | 6.4.2 サプシステム・クロック発振回路 129                                  |

|             | 6.4.3 サブシステム・クロックを使用しない場合 132                              |

|             | 6.4.4 内蔵発振回路 132                                           |

|             | 6.4.5 プリスケーラ 132                                           |

| 6.5         | クロック発生回路の動作 133                                            |

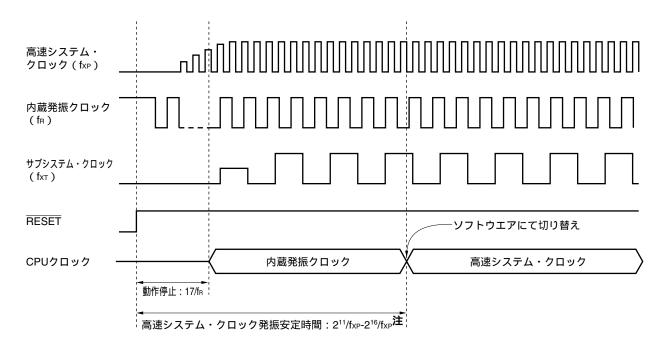

|             | ウロック元王白品の動作 … 133<br>内蔵発振クロックと高速システム・クロックの切り替えに要する時間 … 140 |

|             | CPU <b>クロックの切り替えに要する時間</b> 141                             |

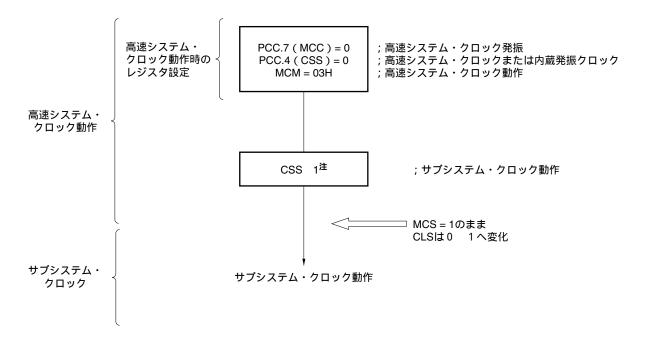

|             | クロック切り替えのフロー・チャートとレジスタ設定 142                               |

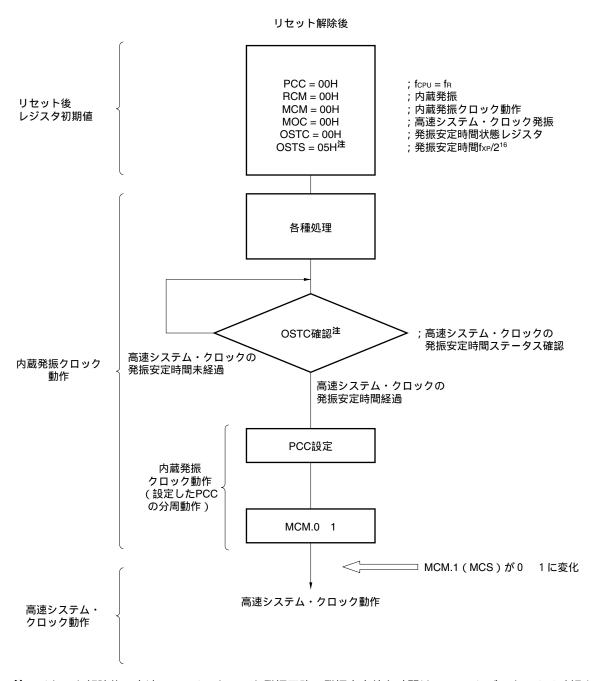

| 0. 0        | 6.8.1 内蔵発振クロックから高速システム・クロックへの切り替え 142                      |

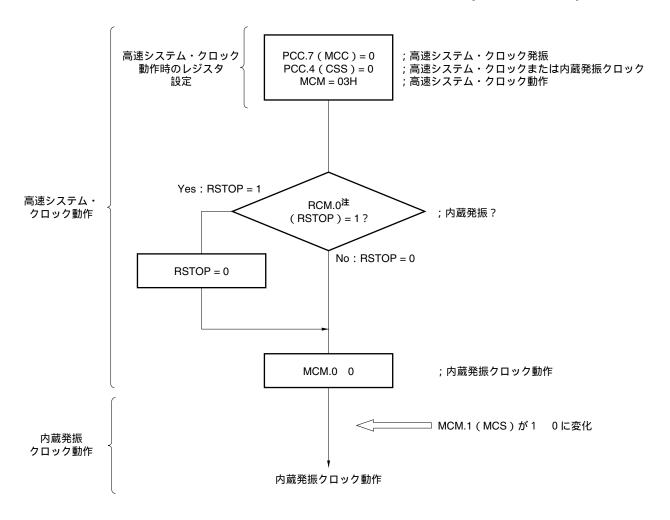

|             | 6.8.2 高速システム・クロックから内蔵発振クロックへの切り替え 143                      |

|             |                                                            |

|             |                                                            |

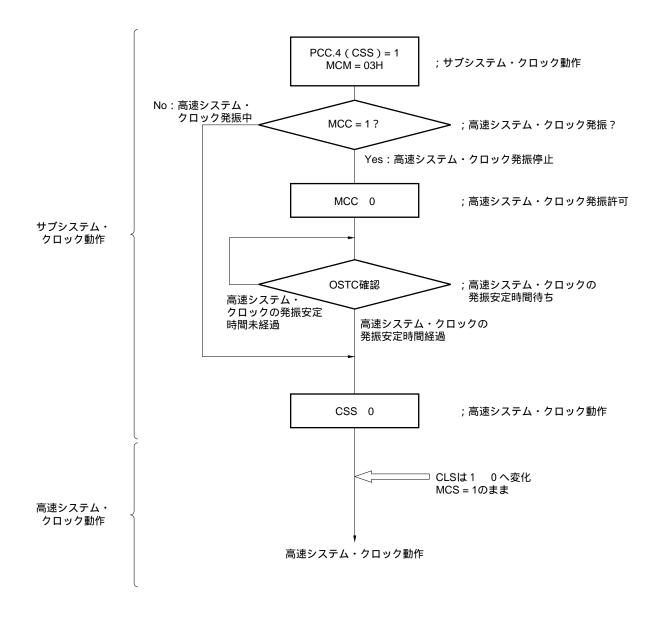

|             | 6.8.4 サブシステム・クロックから高速システム・クロックへの切り替え 145                   |

|             | 6. 8. 5 レジスタ設定 146                                         |

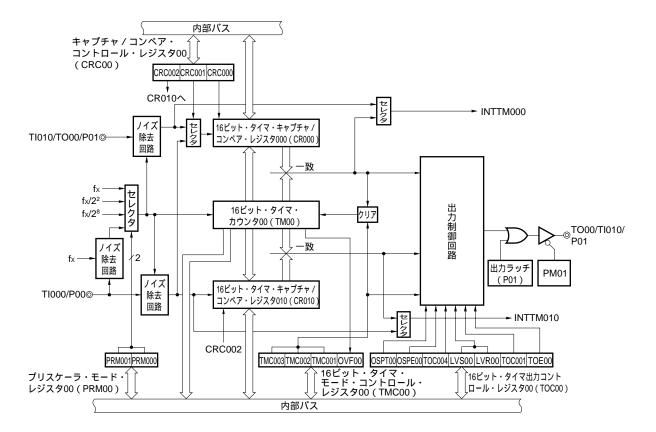

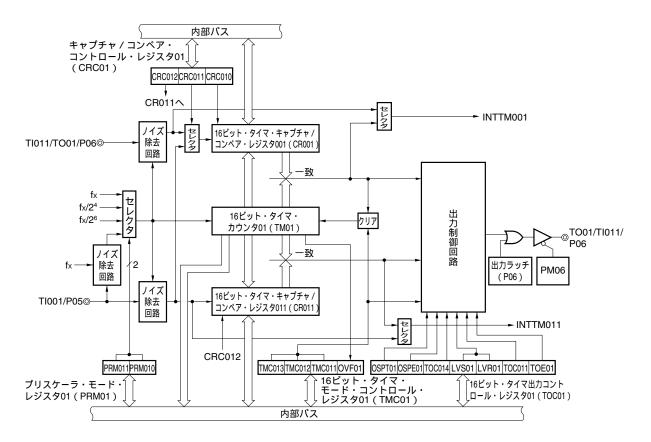

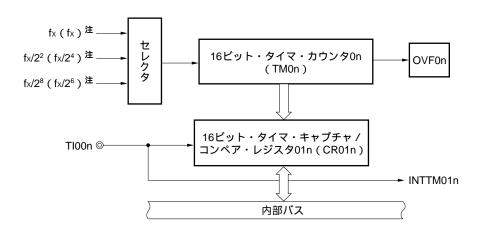

| 第7章         | 16 <b>ピット・タイマ / イベント・カウンタ</b> 00, 01 147                   |

| 7. 1        | 16 <b>ピット・タイマ / イベント・カウンタ</b> 00, 01 <b>の機能</b> 147        |

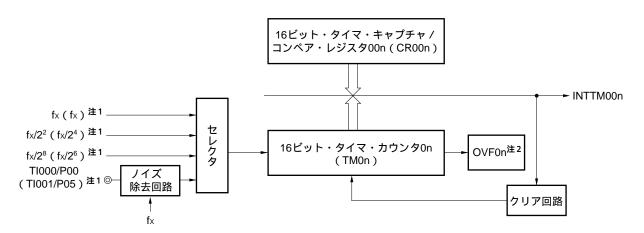

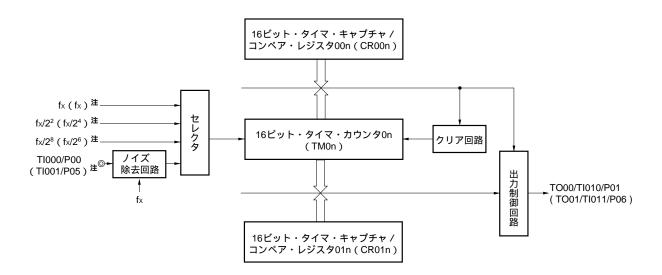

| 7. 2        | 16 <b>ピット・タイマ / イベント・カウンタ</b> 00, 01 <b>の構成</b> 148        |

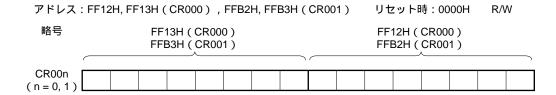

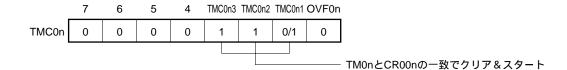

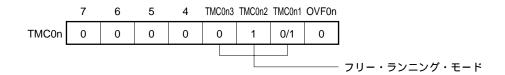

| 7. 3        | 16 <b>ビット・タイマ/イベント・カウンタ</b> 00,01 <b>を制御するレジスタ</b> 153     |

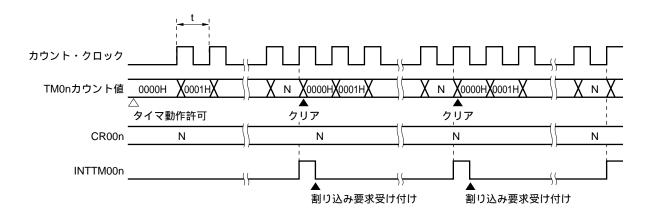

| 7. 4        | 16 <b>ピット・タイマ/イベント・カウンタ</b> 00, 01 <b>の動作</b> 164          |

|             | 7. 4. 1 インターバル・タイマとしての動作 164                               |

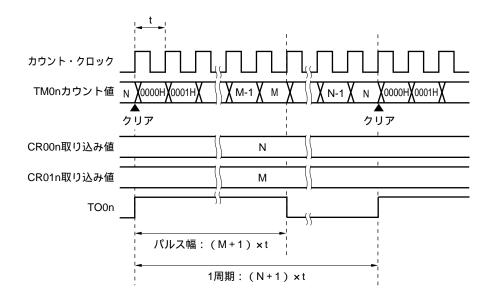

|             | 7. 4. 2 PPG出力としての動作 167                                    |

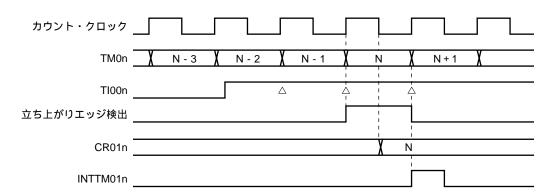

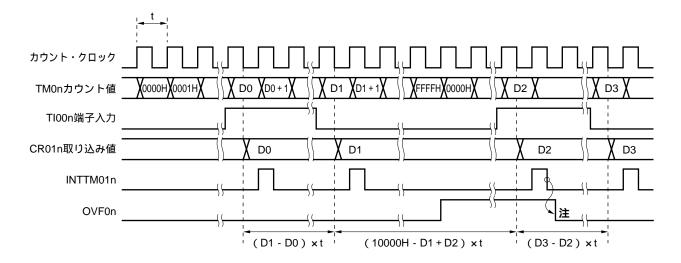

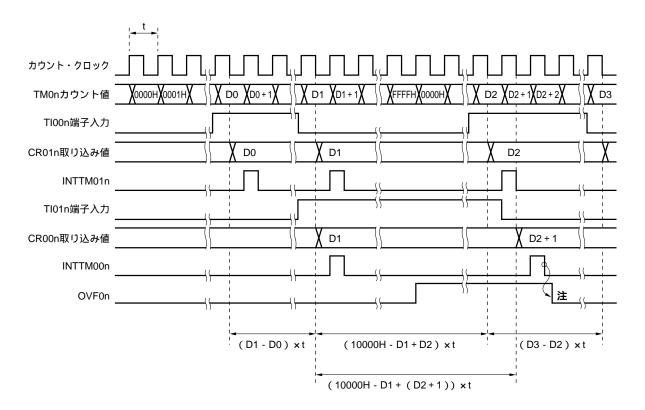

|             | 7.4.3 パルス幅測定としての動作 170                                     |

|             | 7.4.4 外部イベント・カウンタとしての動作 178                                |

|             | 7.4.5 方形波出力としての動作 181                                      |

|             | 7.4.6 ワンショット・パルス出力としての動作 183                               |

| 7. 5        | 16 <b>ビット・タイマ / イベント・カウンタ</b> 00, 01 <b>の注意事項</b> 189      |

| <b>笙</b> 요音 | 8 <b>ピット・タイマ</b> /イベント・カウン <b>タ</b> 50, 51 193             |

| <b>710</b>  |                                                            |

| 8. 1        | 8 <b>ピット・タイマ / イベント・カウンタ</b> 50, 51 <b>の機能</b> 193         |

| 8. 2        | 8 <b>ピット・タイマ / イベント・カウンタ</b> 50, 51 <b>の構成</b> 195         |

| 8. 3        | 8 <b>ピット・タイマ / イベント・カウンタ</b> 50, 51 <b>を制御するレジスタ</b> 197   |

| 8. 4        | 8 <b>ピット・タイマ / イベント・カウンタ</b> 50, 51 <b>の動作</b> 202         |

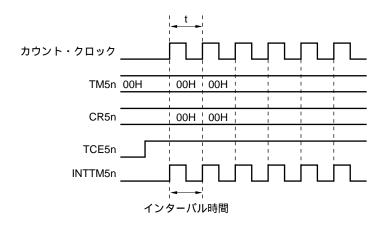

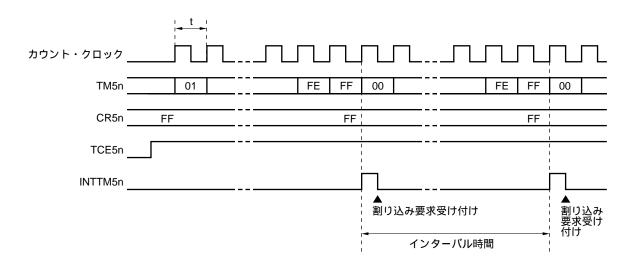

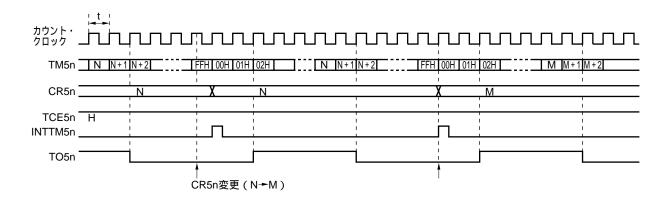

|             | 8. 4. 1 インターバル・タイマとしての動作 202                               |

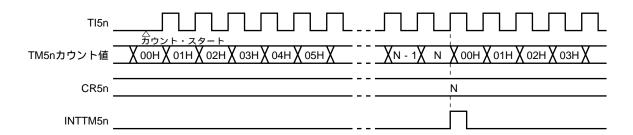

|             | 8.4.2 外部イベント・カウンタとしての動作 205                                |

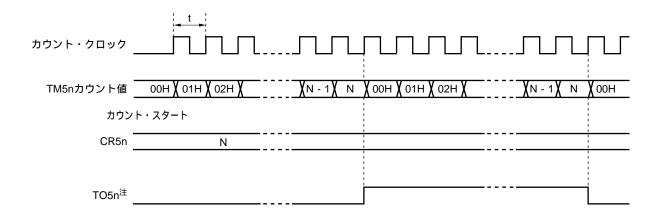

8.4.3 方形波出力としての動作 ... 206 8.4.4 PWM出力としての動作 ... 207

8.5 8ビット・タイマ/イベント・カウンタ50,51の注意事項 ... 211

# 第9章 8ビット・タイマHO, H1 ... 212

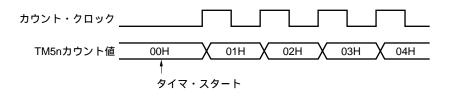

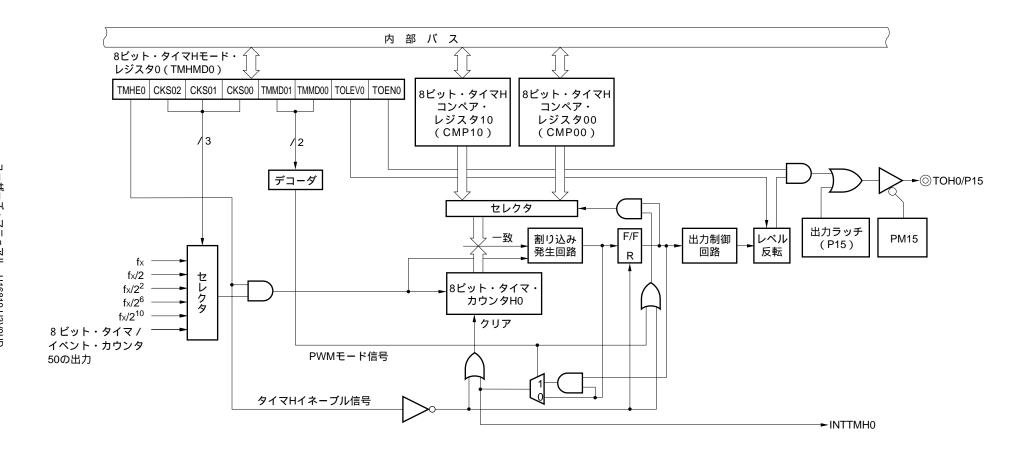

- 9.1 8**ビット・タイマ**H0, H1**の機能** ... 212

- 9.2 8**ビット・タイマ**H0, H1**の構成** ... 212

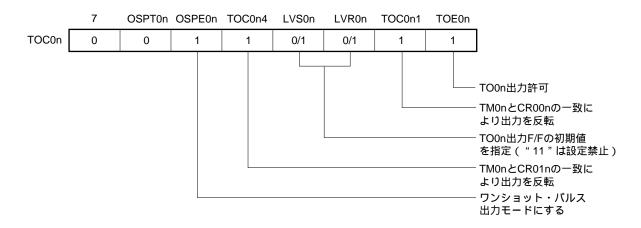

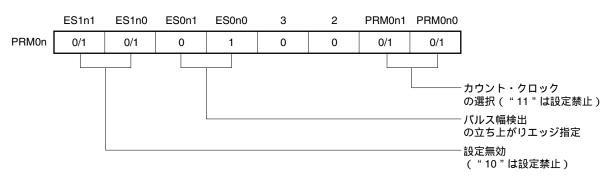

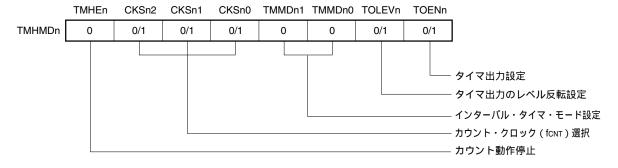

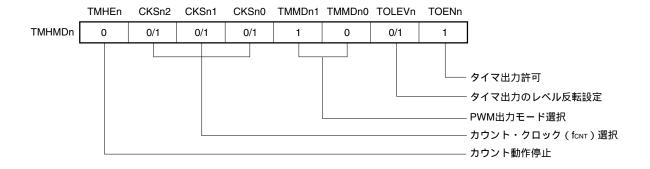

- 9.3 8ビット・タイマH0, H1を制御するレジスタ ... 216

- 9.4 8**ビット・タイマ**H0. H1**の動作** ... 222

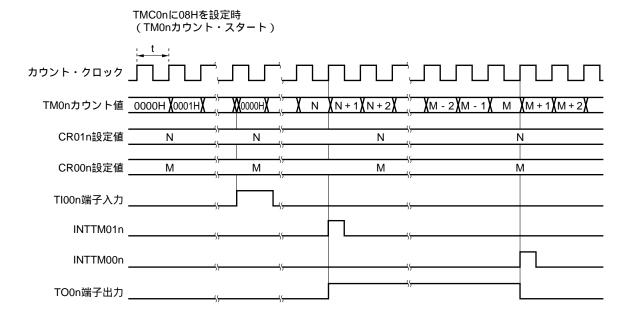

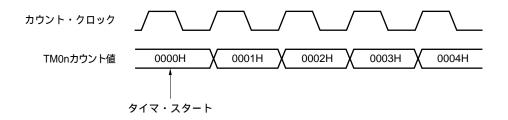

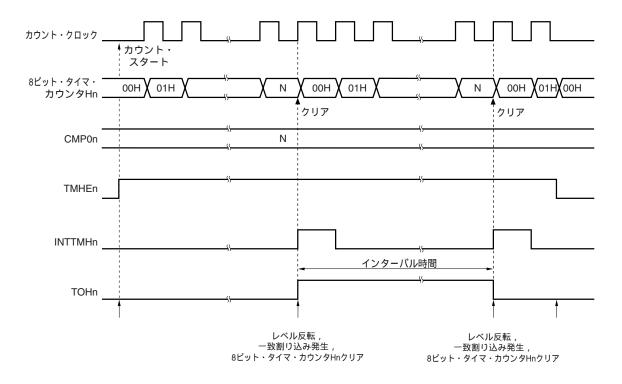

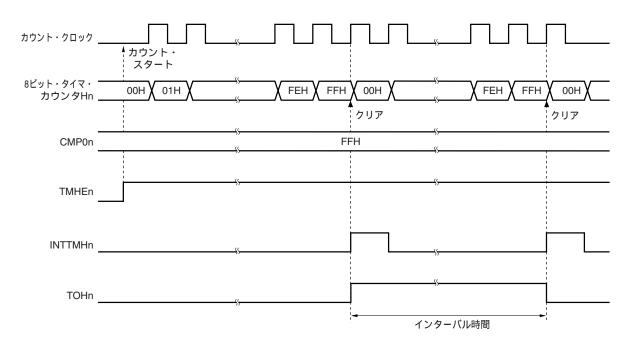

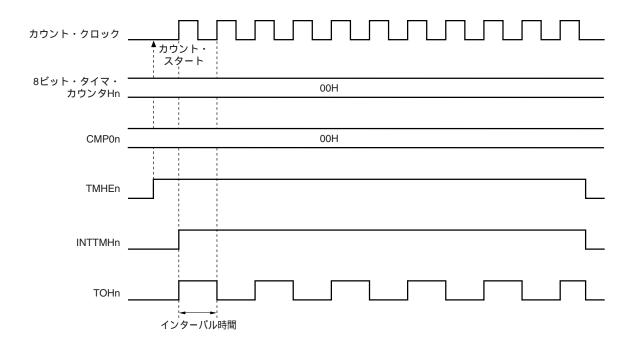

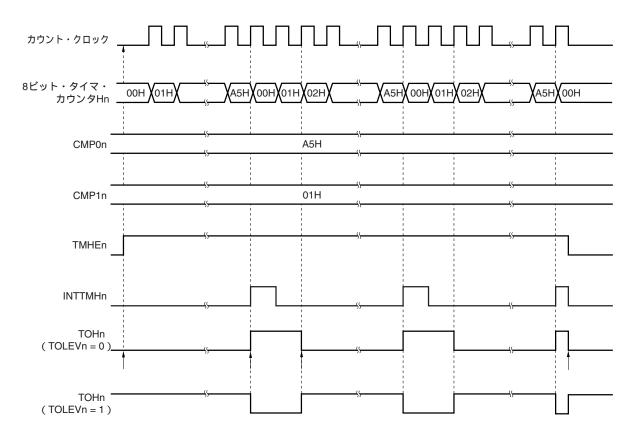

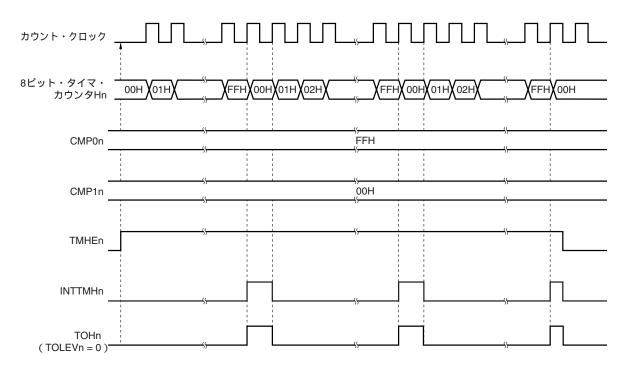

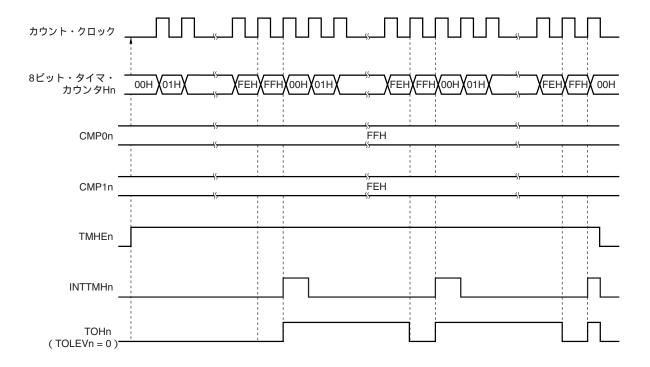

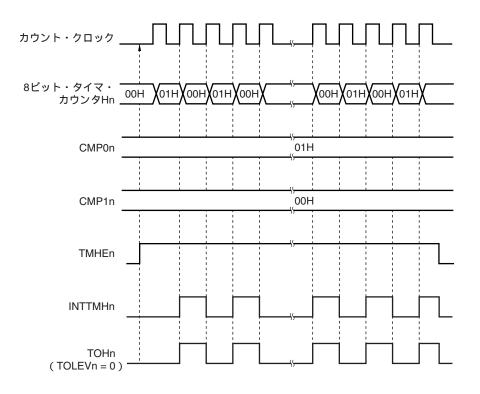

- 9.4.1 インターバル・タイマ/方形波出力としての動作 ... 222

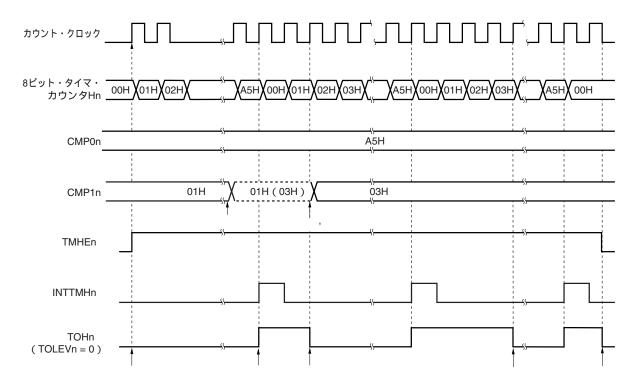

- 9.4.2 PWM出力モードとしての動作 ... 225

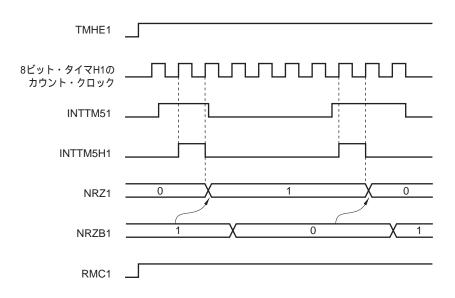

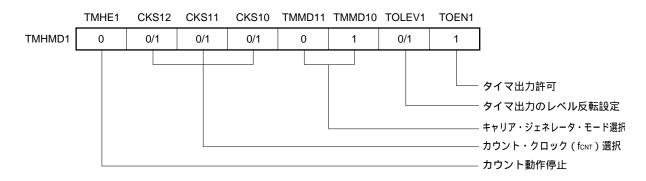

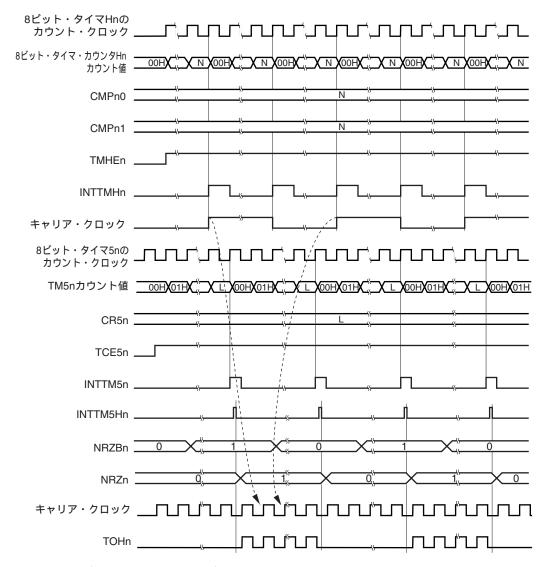

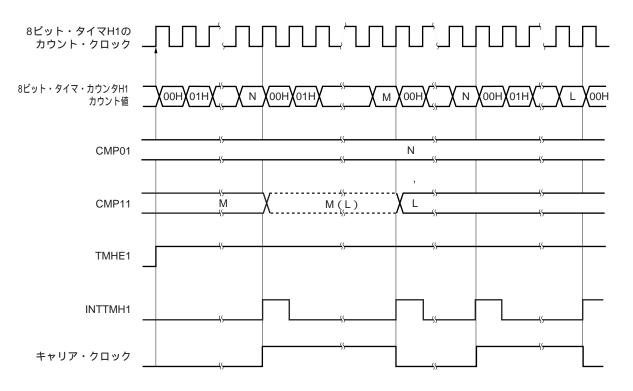

- 9.4.3 キャリア・ジェネレータ・モードとしての動作(8ビット・タイマH1のみ) ... 231

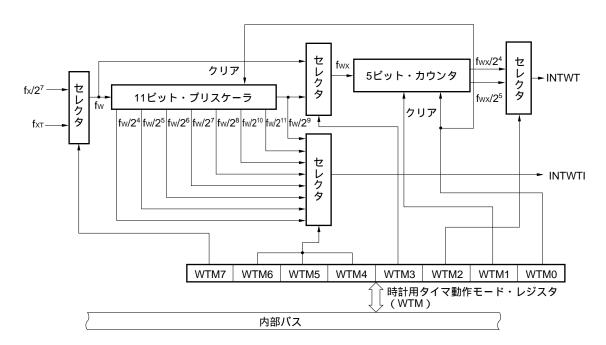

### 第10章 時計用タイマ ... 238

- 10.1 時計用タイマの機能 ... 238

- 10.2 時計用タイマの構成 ... 239

- 10.3 時計用タイマを制御するレジスタ ... 240

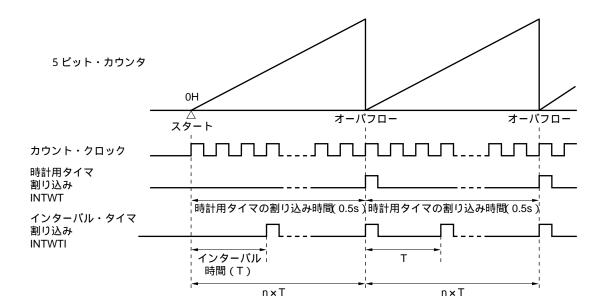

- 10.4 時計用タイマの動作 ... 241

- 10.4.1 時計用タイマとしての動作 ... 241

- 10.4.2 インターバル・タイマとしての動作 ... 242

- 10.5 時計用タイマの注意事項 ... 243

# 第11章 ウォッチドッグ・タイマ ... 244

- 11.1 ウォッチドッグ・タイマの機能 ... 244

- 11.2 ウォッチドッグ・タイマの構成 ... 246

- 11.3 ウォッチドッグ・タイマを制御するレジスタ ... 247

- 11.4 **ウォッチドッグ・タイマの動作** ... 250

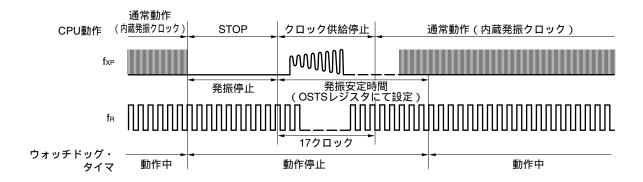

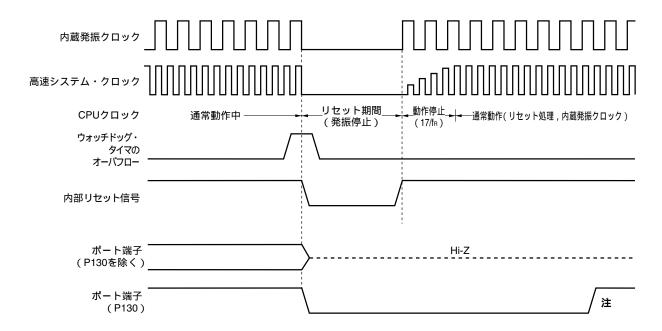

- 11. 4. 1 オプション・バイトで「内蔵発振器は停止不可」を選択した場合のウォッチドッグ・ タイマ動作 ... 250

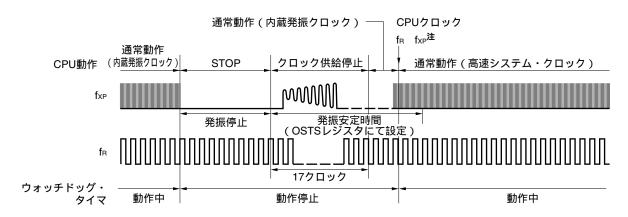

- 11. 4. 2 オプション・バイトで「内蔵発振器はソフトウエアにより停止可能」を選択した場合のウォッチドッグ・タイマ動作 ... 251

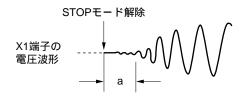

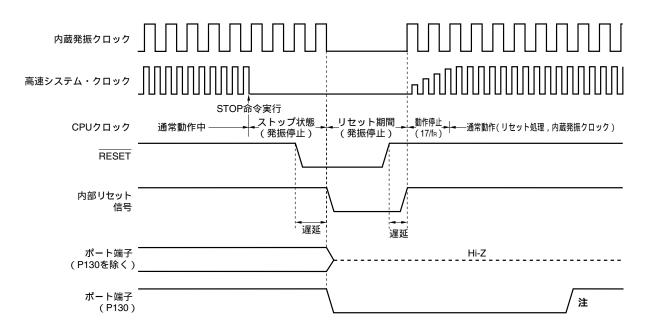

- 11.4.3 STOPモード時の動作(オプション・バイトで「内蔵発振器はソフトウエアにより 停止可能」を選択した場合) ... 252

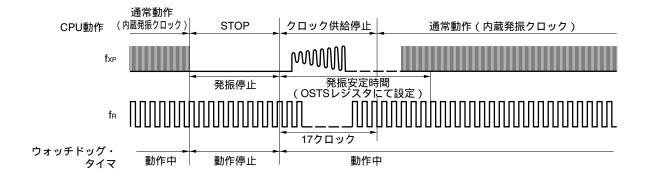

- 11. 4. 4 HALTモード時の動作(オプション・バイトで「内蔵発振器はソフトウエアにより 停止可能」を選択した場合) ... 254

### 第12章 クロック出力 / ブザー出力制御回路 ... 255

- 12.1 クロック出力/ブザー出力制御回路の機能 ... 255

- 12.2 クロック出力/ブザー出力制御回路の構成 ... 256

- 12.3 クロック出力 / ブザー出力制御回路を制御するレジスタ ... 256

- 12.4 クロック出力/ブザー出力制御回路の動作 ... 259

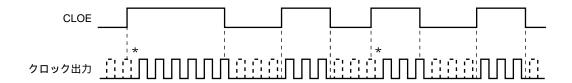

- 12.4.1 クロック出力としての動作 ... 259

- 12.4.2 ブザー出力としての動作 ... 259

# 第13章 A/D**コンバータ** ... 260

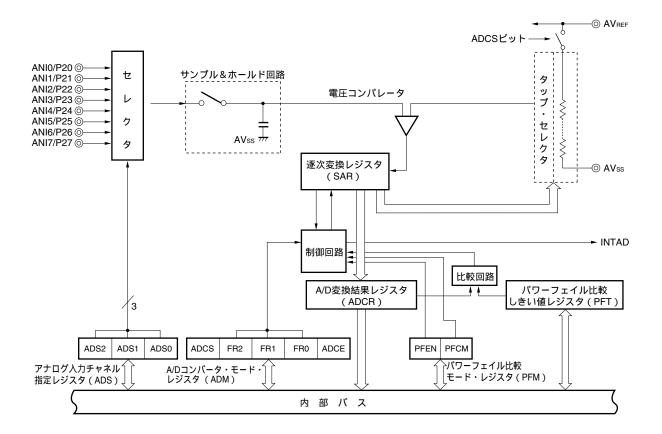

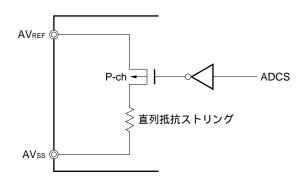

- 13.1 A/D**コンバータの機能** ... 260

- 13.2 A/D**コンバータの構成** ... 261

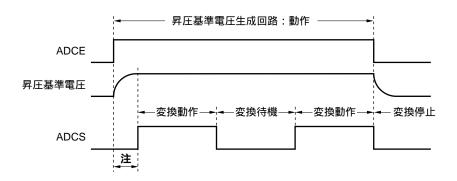

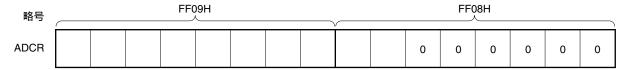

- 13.3 A/Dコンパータで使用するレジスタ ... 263

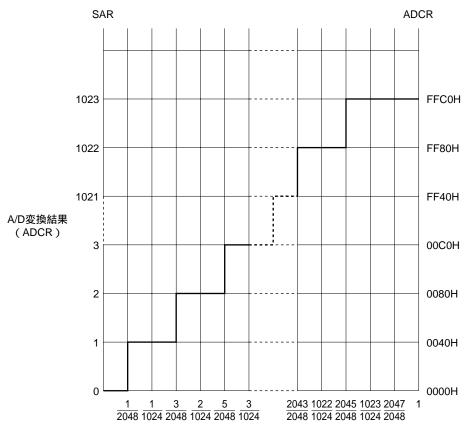

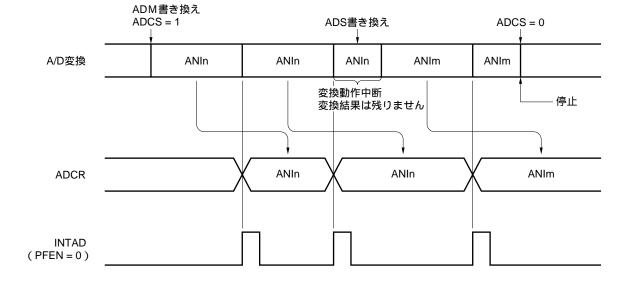

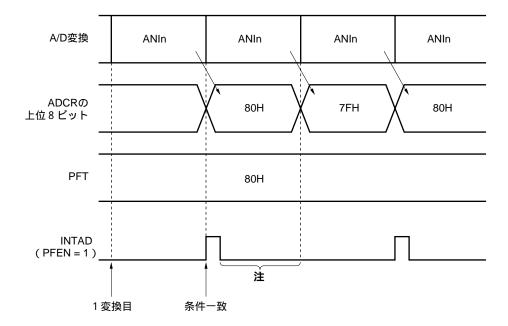

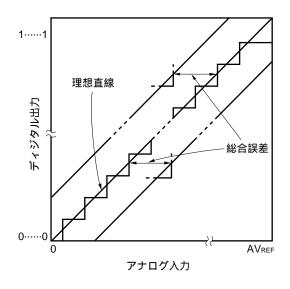

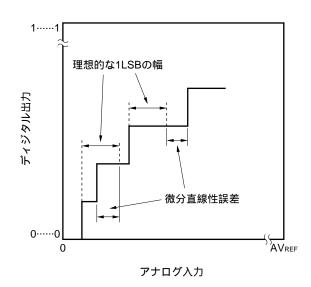

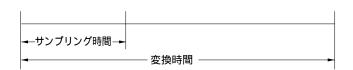

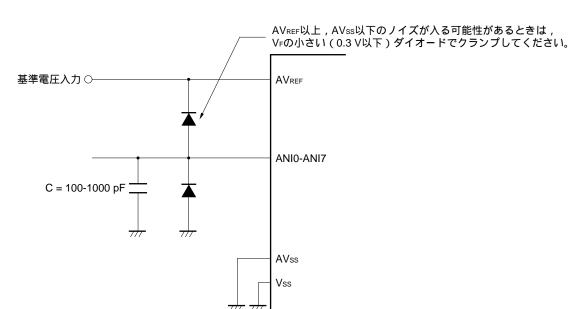

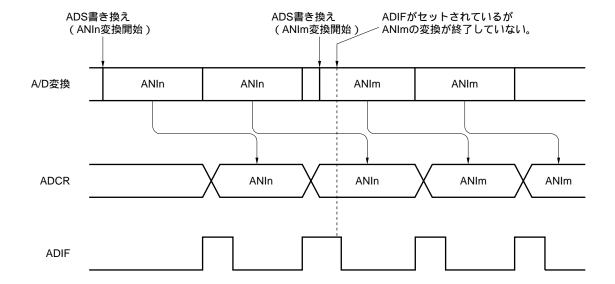

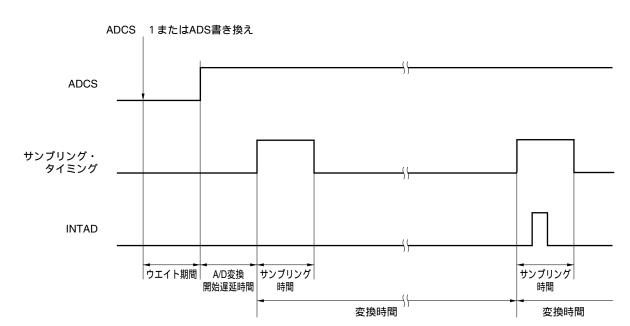

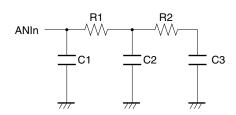

| 13. 5                   | A/D <b>コンバータの動作</b> 268<br>13. 4. 1 A/Dコンバータの基本動作 268<br>13. 4. 2 入力電圧と変換結果 270<br>13. 4. 3 A/Dコンバータの動作モード 271<br>A/D <b>コンバータ特性表の読み方</b> 275<br>A/D <b>コンバータの注意事項</b> 278                       |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 第14章                    | シリアル・インタフェースUART0 283                                                                                                                                                                            |

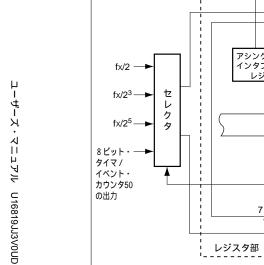

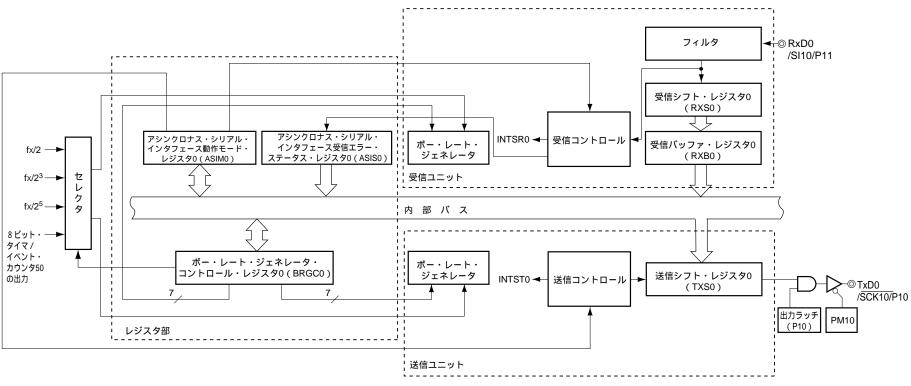

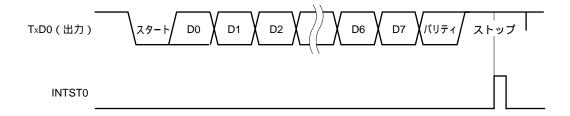

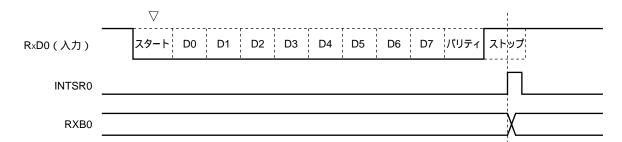

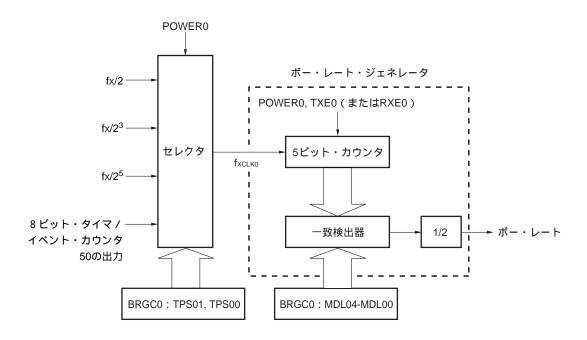

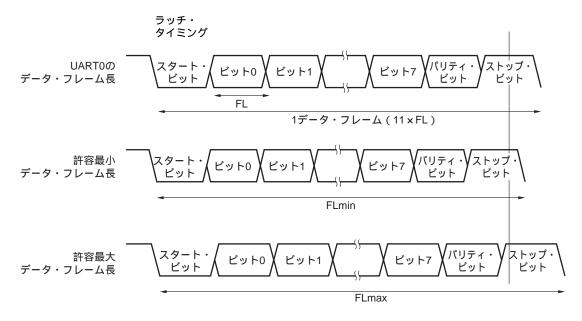

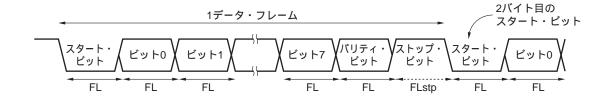

| 14. 2<br>14. 3          | シリアル・インタフェースUARTOの機能283シリアル・インタフェースUARTOの構成284シリアル・インタフェースUARTOを制御するレジスタ287シリアル・インタフェースUARTOの動作29214. 4. 1動作停止モード29214. 4. 2アシンクロナス・シリアル・インタフェース(UART)モード29314. 4. 3専用ボー・レート・ジェネレータ299           |

| <b>第</b> 15 <b>章</b>    | シリアル・インタフェースUART6 305                                                                                                                                                                            |

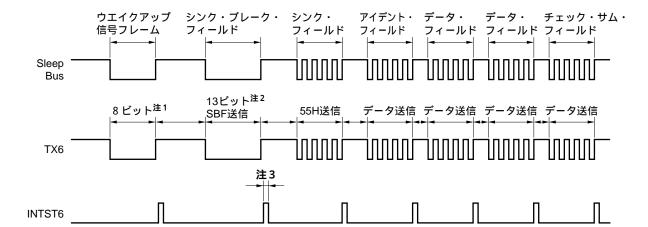

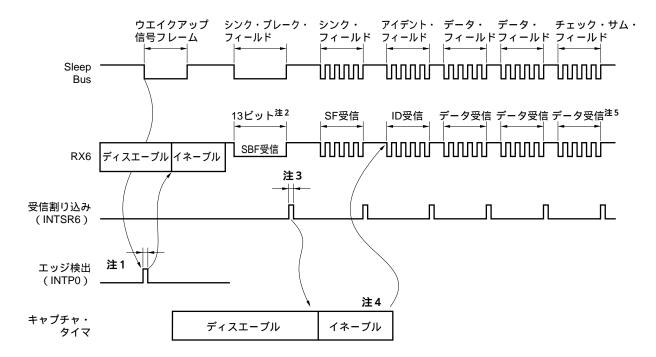

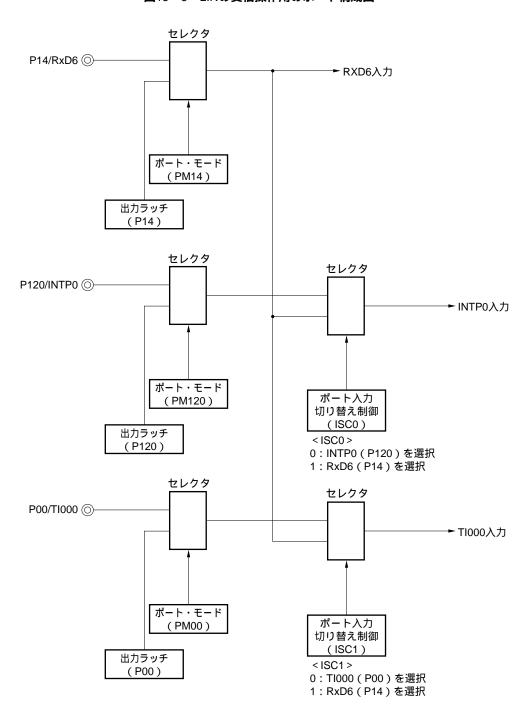

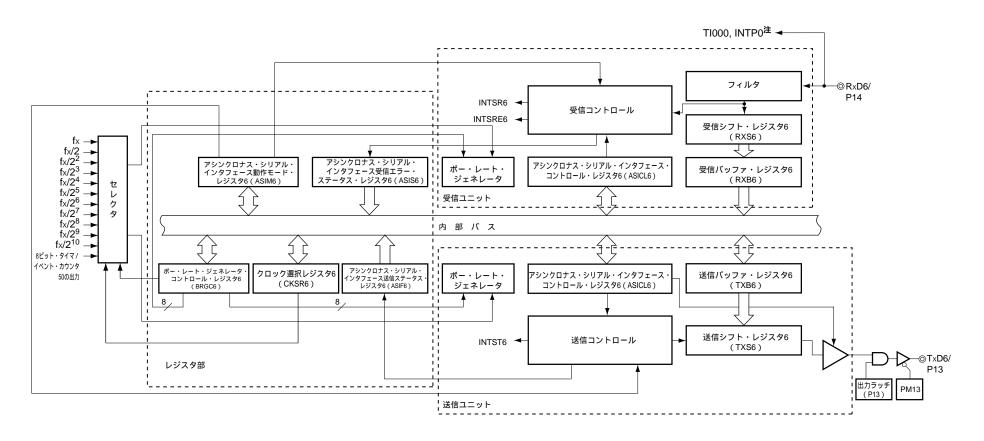

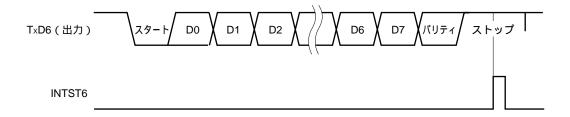

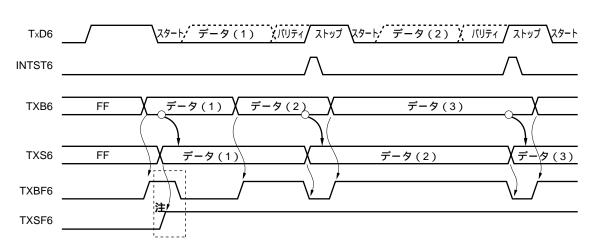

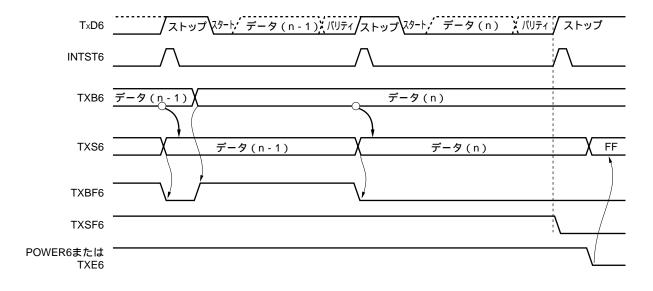

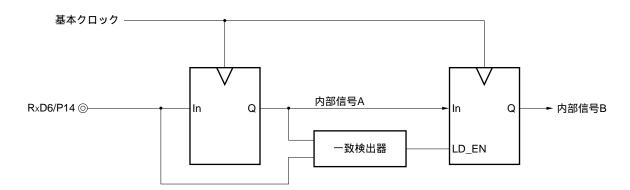

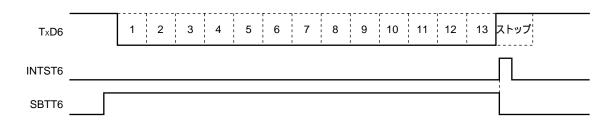

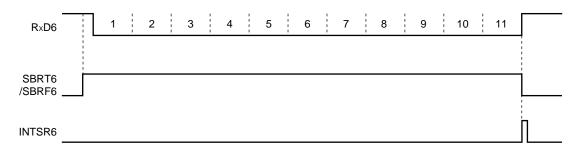

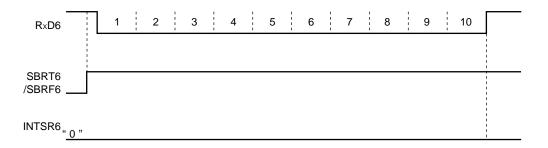

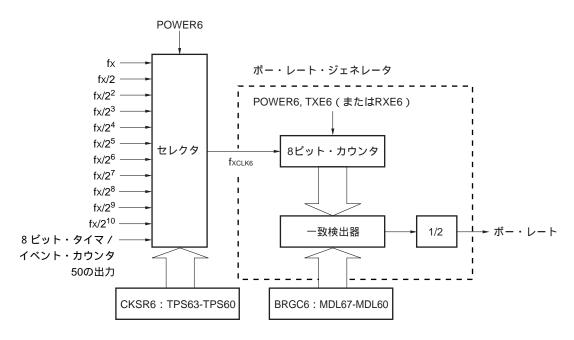

| 15. 2<br>15. 3          | シリアル・インタフェースUART6の機能305シリアル・インタフェースUART6の構成310シリアル・インタフェースUART6を制御するレジスタ313シリアル・インタフェースUART6の動作32415. 4. 1動作停止モード32415. 4. 2アシンクロナス・シリアル・インタフェース(UART)モード32515. 4. 3専用ボー・レート・ジェネレータ339           |

| <b>第</b> 16 <b>章</b>    | シリアル・インタフェースCSI10, CSI11 345                                                                                                                                                                     |

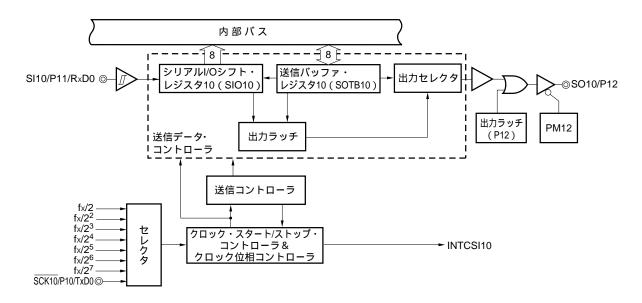

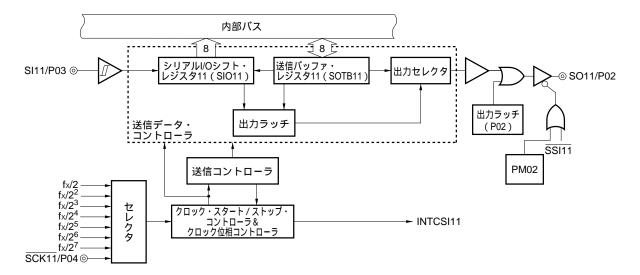

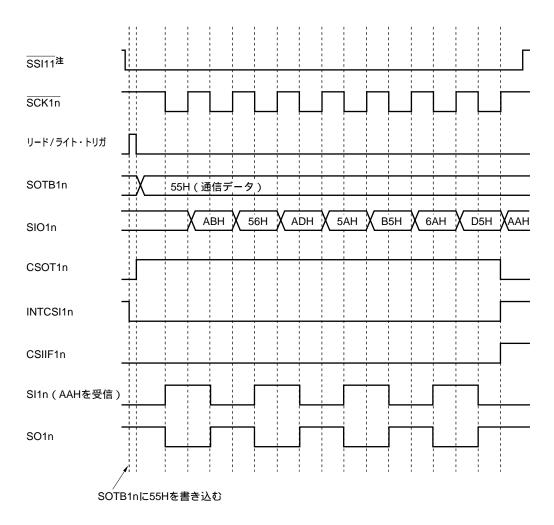

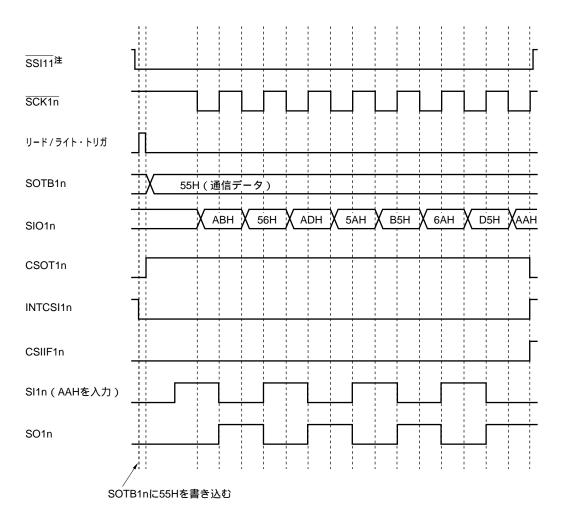

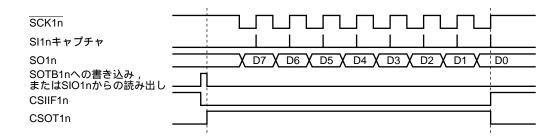

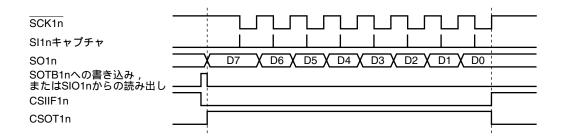

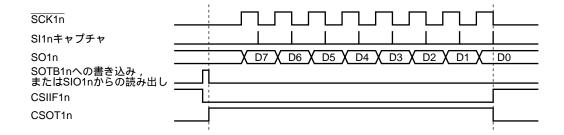

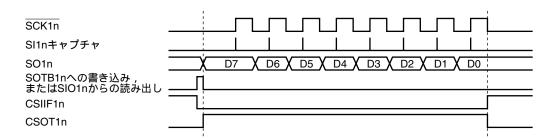

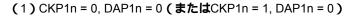

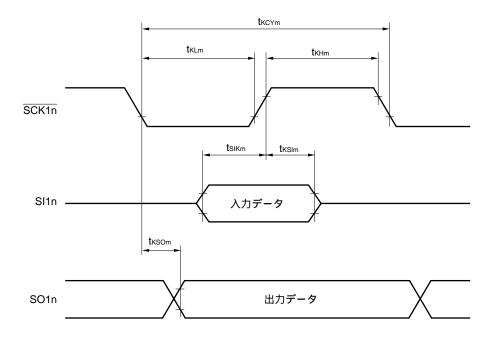

| 16. 2<br>16. 3          | シリアル・インタフェースCSI10, CSI11の機能 345<br>シリアル・インタフェースCSI10, CSI11の構成 346<br>シリアル・インタフェースCSI10, CSI11を制御するレジスタ 348<br>シリアル・インタフェースCSI10, CSI11の動作 355<br>16.4.1 動作停止モード 355<br>16.4.2 3線式シリアルI/Oモード 356 |

| 第17章                    | シリアル・インタフェースCSIA0 366                                                                                                                                                                            |

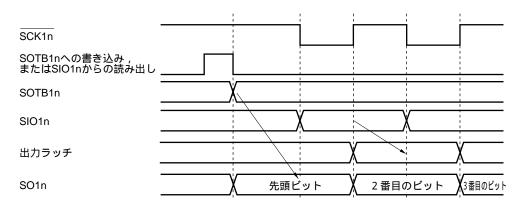

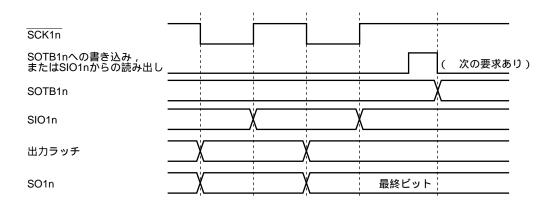

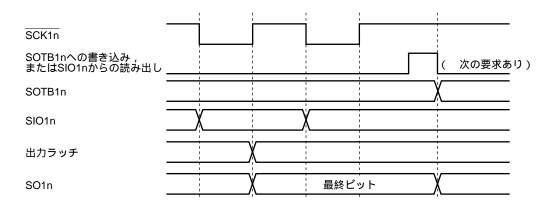

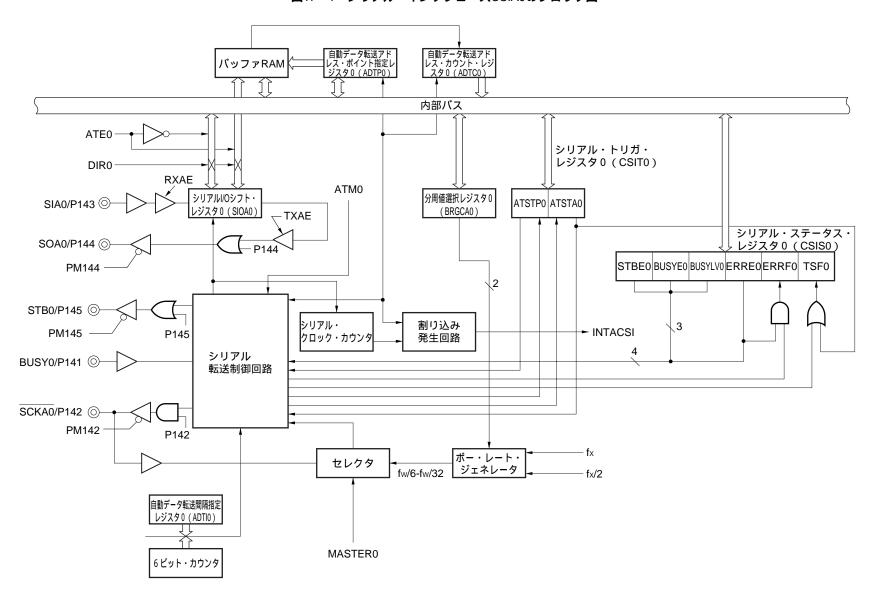

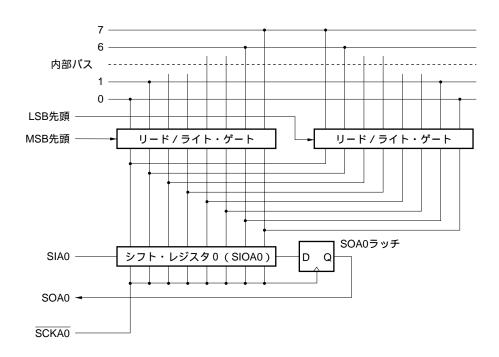

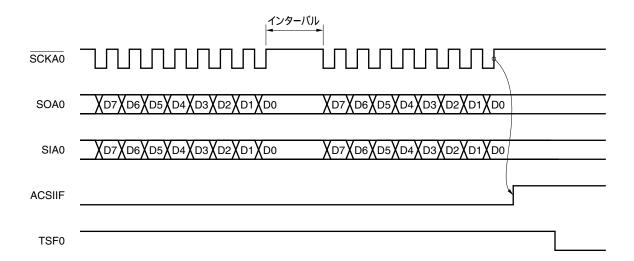

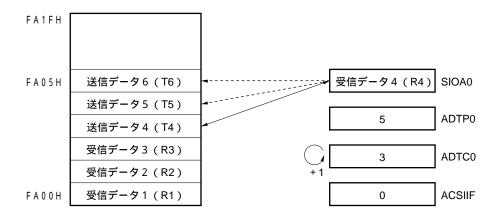

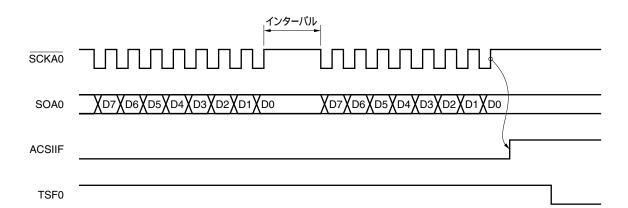

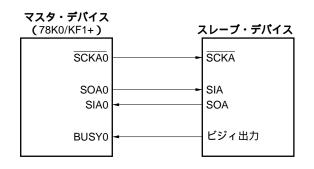

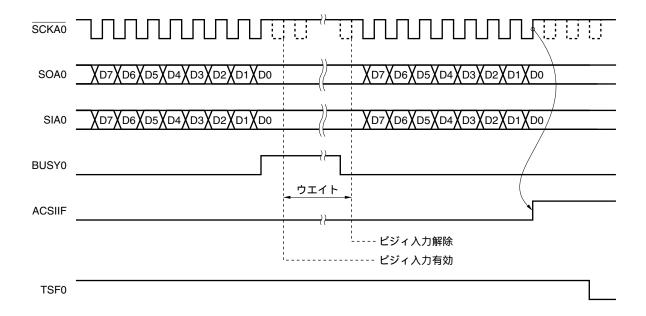

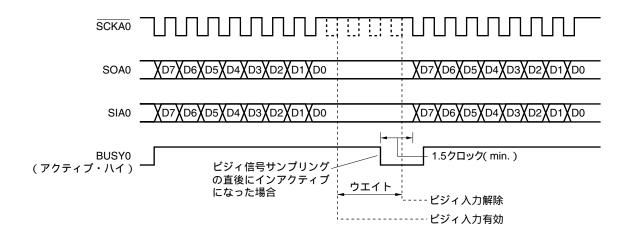

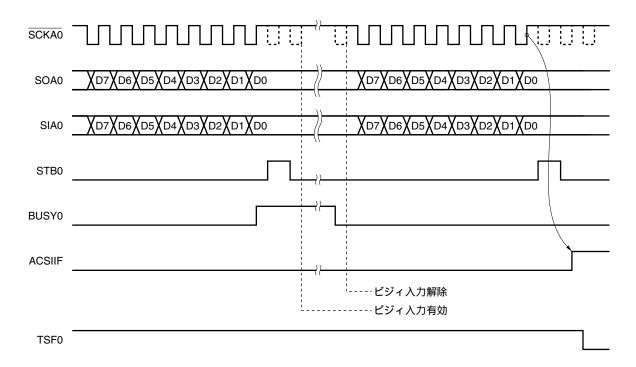

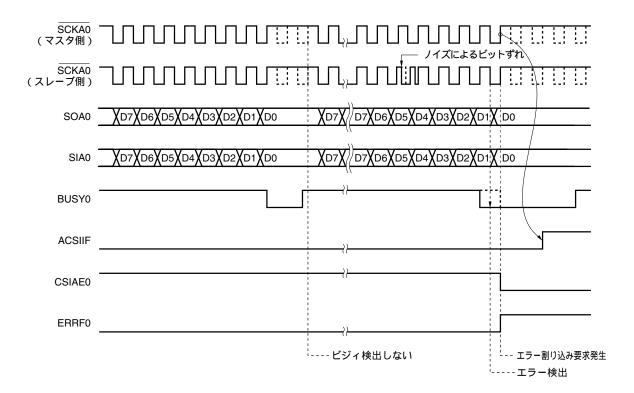

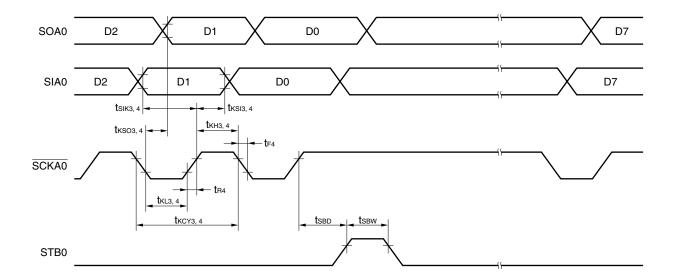

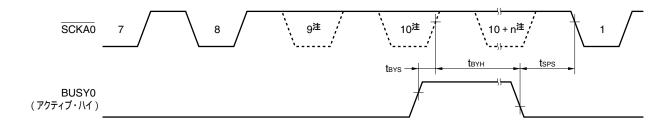

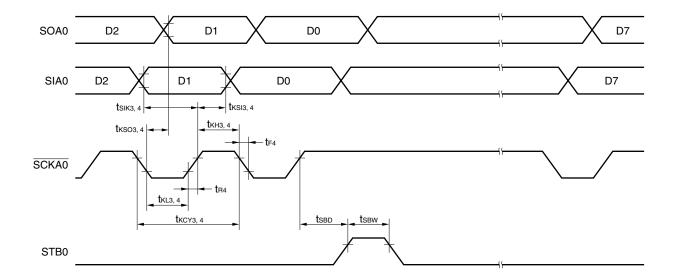

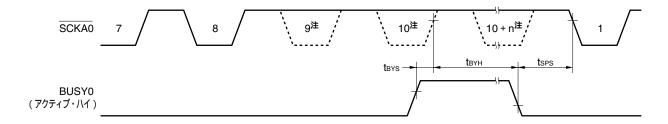

| 17. 2<br>17. 3<br>17. 4 | シリアル・インタフェースCSIA0の機能 366シリアル・インタフェースCSIA0の構成 367シリアル・インタフェースCSIA0を制御するレジスタ 369シリアル・インタフェースCSIA0の動作 37817. 4. 1動作停止モード 37817. 4. 23線式シリアルI/Oモード 37817. 4. 3自動送受信機能付き3線式シリアルI/Oモード 384             |

| 第18章                    | <b>乗除算器</b> 409                                                                                                                                                                                  |

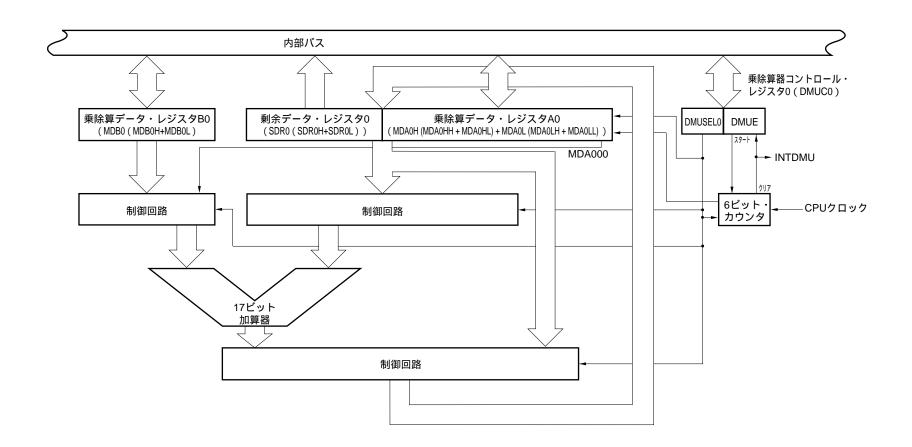

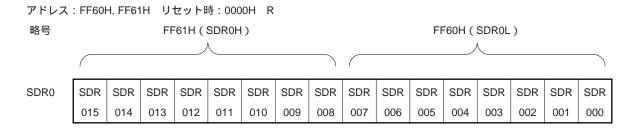

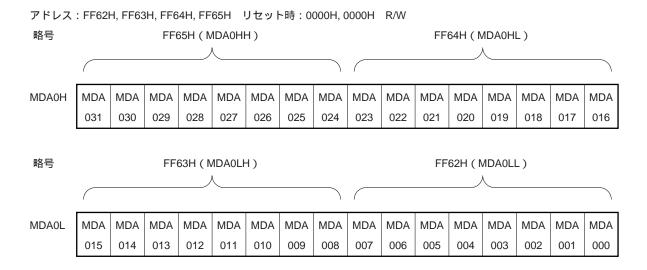

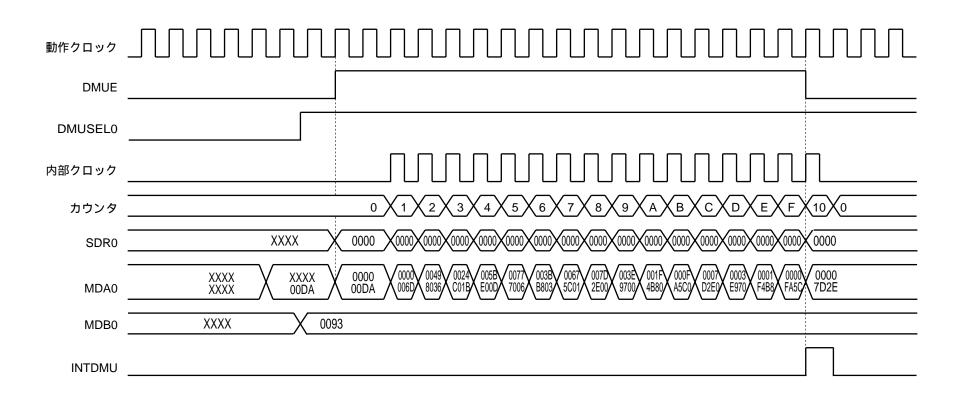

18.1 乗除算器の機能 ... 409

| 18. 2                                                                                        | <b>乗除算器の構成</b> 409                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18. 3                                                                                        | 乗除算器を制御するレジスタ 414                                                                                                                                                                                                                                                                             |

|                                                                                              | <b>乗除算器の動作</b> 415                                                                                                                                                                                                                                                                            |

|                                                                                              | 18. 4. 1 乗算動作 415                                                                                                                                                                                                                                                                             |

|                                                                                              | 18. 4. 2 除算動作 417                                                                                                                                                                                                                                                                             |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

| 第19章                                                                                         | 割り込み機能 419                                                                                                                                                                                                                                                                                    |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

| 19. 1                                                                                        | 割り込み機能の種類 419                                                                                                                                                                                                                                                                                 |

| 19. 2                                                                                        | <b>割り込み要因と構成</b> 419                                                                                                                                                                                                                                                                          |

| 19. 3                                                                                        | 割り込み機能を制御するレジスタ 424                                                                                                                                                                                                                                                                           |

| 19. 4                                                                                        | 割り込み処理動作 432                                                                                                                                                                                                                                                                                  |

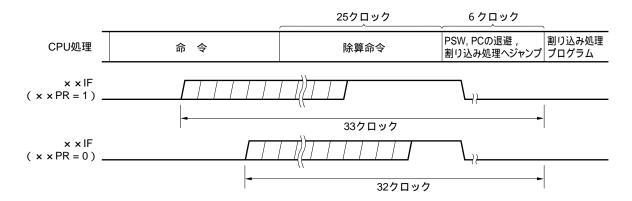

|                                                                                              | 19. 4. 1 マスカブル割り込み要求の受け付け動作 432                                                                                                                                                                                                                                                               |

|                                                                                              | 19.4.2 ソフトウエア割り込み要求の受け付け動作 435                                                                                                                                                                                                                                                                |

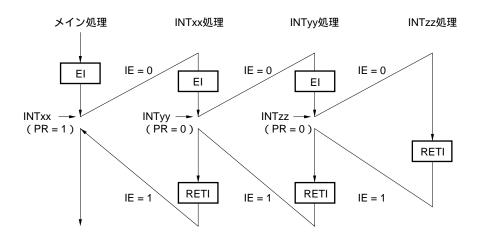

|                                                                                              | 19. 4. 3 多重割り込み処理 435                                                                                                                                                                                                                                                                         |

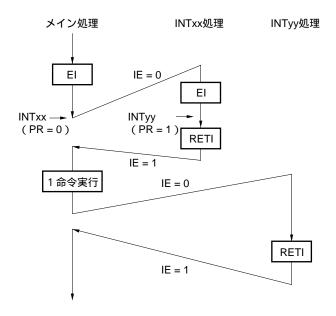

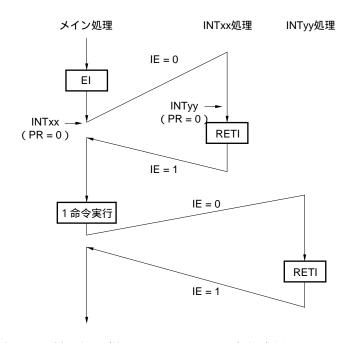

|                                                                                              | 19. 4. 4 割り込み要求の保留 438                                                                                                                                                                                                                                                                        |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

| 第20章                                                                                         | キー割り込み機能 439                                                                                                                                                                                                                                                                                  |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

| 20. 1                                                                                        | <b>キー割り込みの機能</b> 439                                                                                                                                                                                                                                                                          |

| 20. 2                                                                                        | <b>キー割り込みの構成</b> 439                                                                                                                                                                                                                                                                          |

| 20. 3                                                                                        | <b>キー割り込みを制御するレジスタ</b> 440                                                                                                                                                                                                                                                                    |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

| 第21章                                                                                         | ス <b>タンパイ機能</b> 441                                                                                                                                                                                                                                                                           |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

|                                                                                              |                                                                                                                                                                                                                                                                                               |

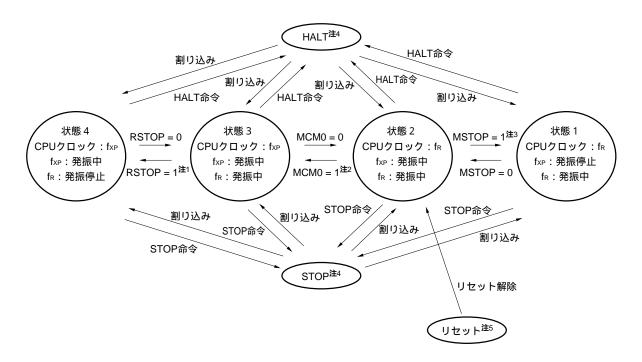

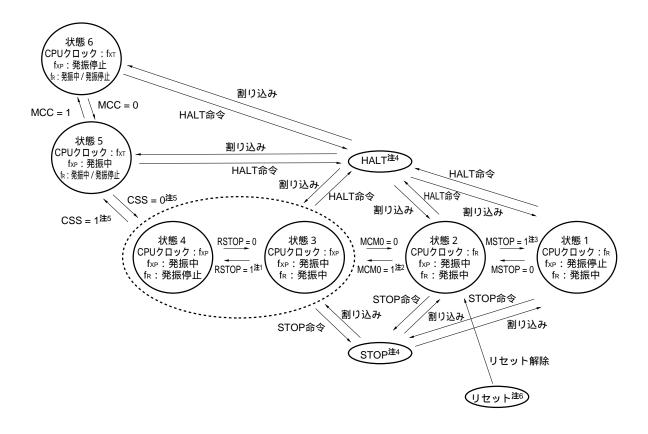

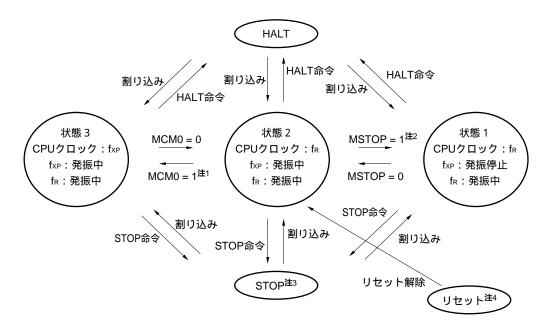

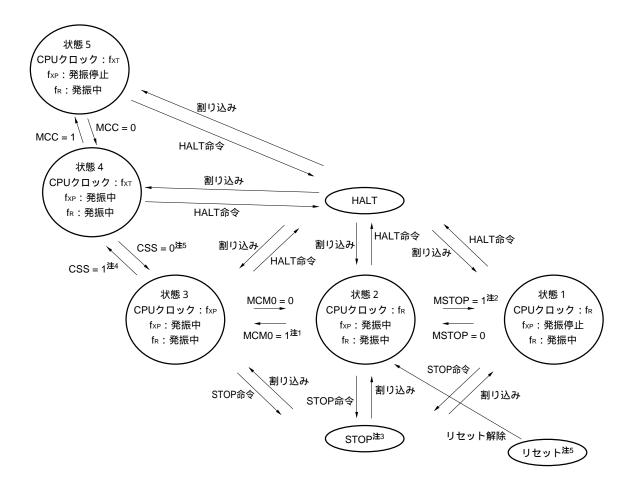

| 21. 1                                                                                        | スタンパイ機能と構成 441                                                                                                                                                                                                                                                                                |

| 21. 1                                                                                        | <b>スタンバイ機能と構成</b> 441<br>21.1.1 スタンバイ機能 441                                                                                                                                                                                                                                                   |

| 21. 1                                                                                        |                                                                                                                                                                                                                                                                                               |

|                                                                                              | 21. 1. 1 スタンバイ機能 441                                                                                                                                                                                                                                                                          |

|                                                                                              | 21. 1. 1 スタンバイ機能 441<br>21. 1. 2 スタンバイ機能を制御するレジスタ 443                                                                                                                                                                                                                                         |

|                                                                                              | 21. 1. 1 スタンバイ機能 441<br>21. 1. 2 スタンバイ機能を制御するレジスタ 443<br>スタンバイ機能の動作 446                                                                                                                                                                                                                       |

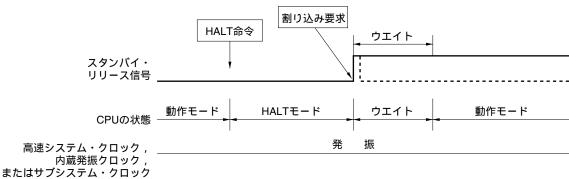

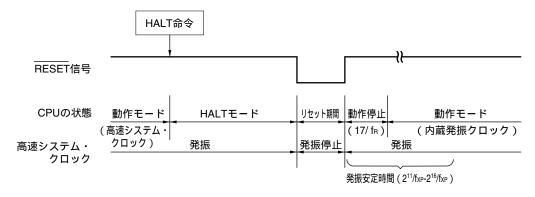

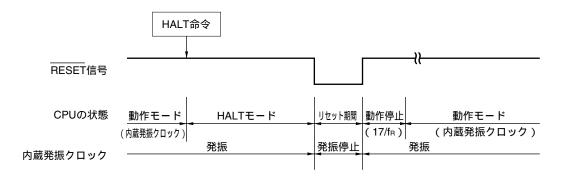

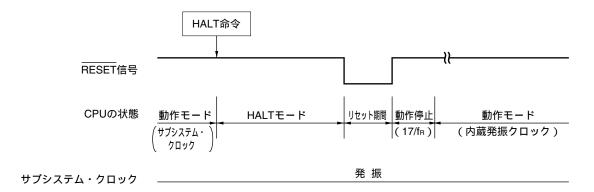

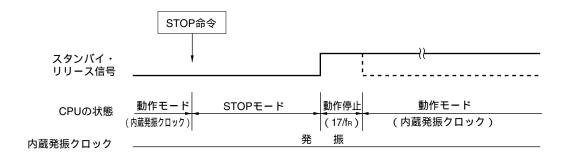

|                                                                                              | 21. 1. 1スタンバイ機能44121. 1. 2スタンバイ機能を制御するレジスタ443スタンバイ機能の動作44621. 2. 1HALTモード446                                                                                                                                                                                                                  |

| 21. 2                                                                                        | 21. 1. 1スタンバイ機能44121. 1. 2スタンバイ機能を制御するレジスタ443スタンバイ機能の動作44621. 2. 1HALTモード446                                                                                                                                                                                                                  |

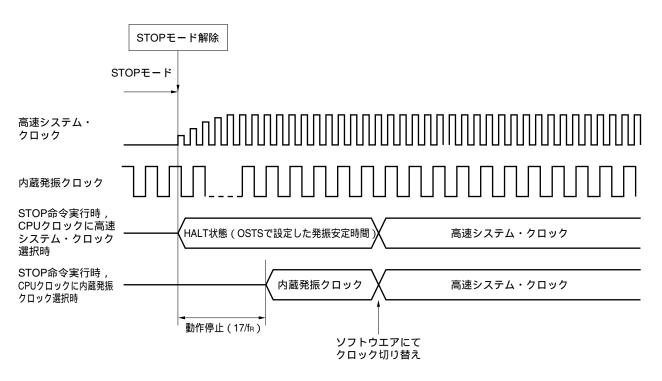

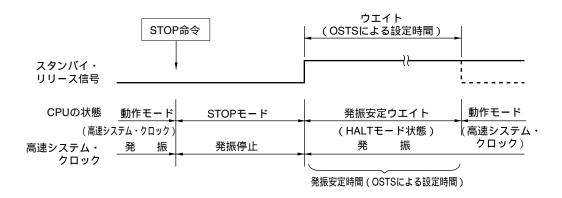

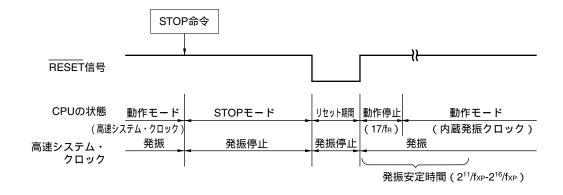

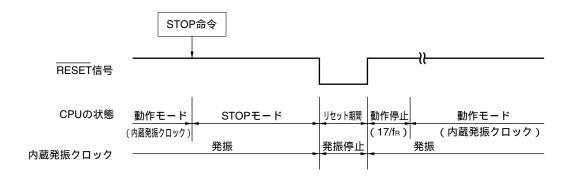

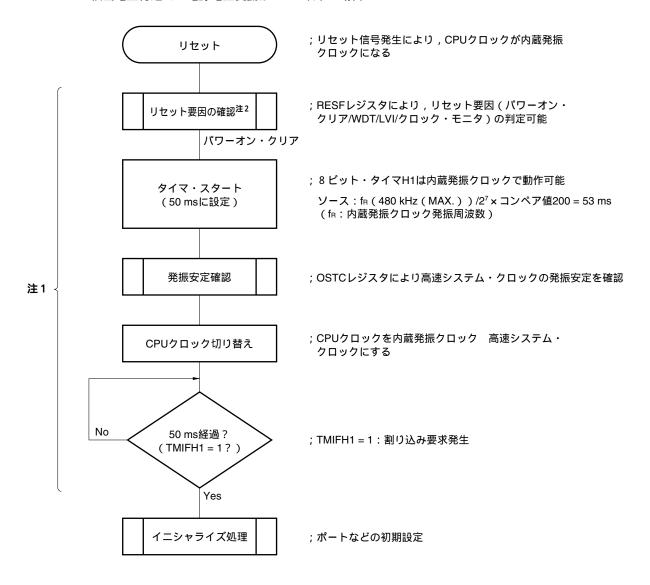

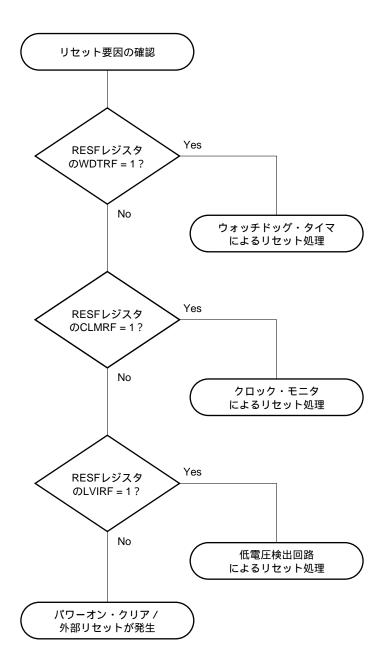

| 21. 2<br><b>第</b> 22 <b>章</b>                                                                | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456                                                                                                                                                                       |

| 21. 2<br><b>第</b> 22 <b>章</b>                                                                | 21. 1. 1       スタンバイ機能        441         21. 1. 2       スタンバイ機能を制御するレジスタ        443         スタンバイ機能の動作        446         21. 2. 1       HALTモード        446         21. 2. 2       STOPモード        451                                                                                        |

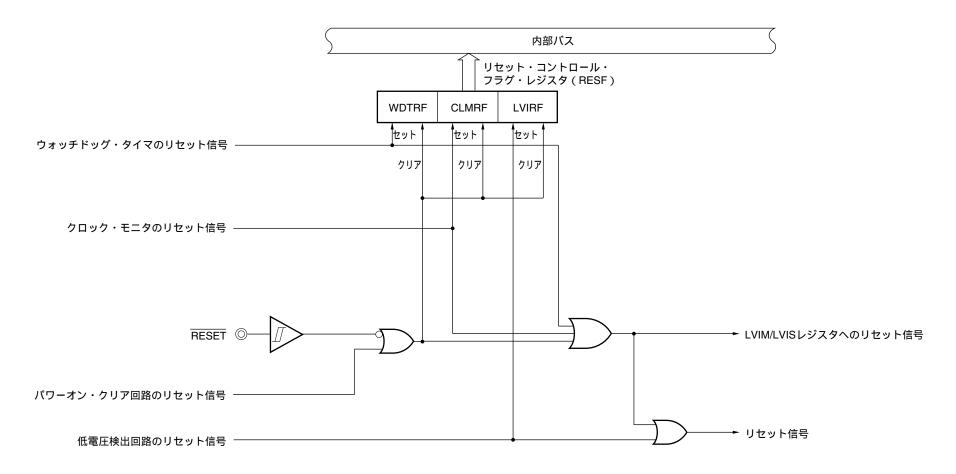

| 21. 2<br><b>第22章</b><br>22. 1                                                                | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463                                                                                                                                                  |

| 21. 2<br><b>第22章</b><br>22. 1                                                                | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456                                                                                                                                                                       |

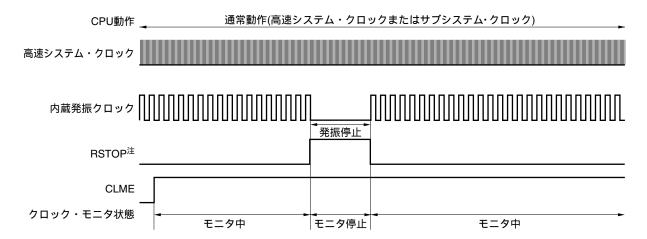

| 第22章<br>22.1<br>第23章                                                                         | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタ 464                                                                                                                                    |

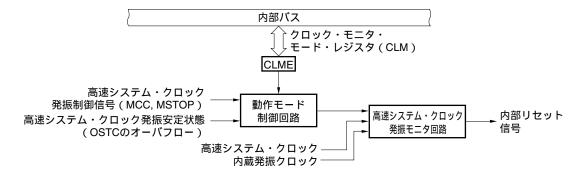

| 第22章<br>22.1<br>第23章<br>23.1                                                                 | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタ 464  クロック・モニタの機能 464                                                                                                                   |

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2                                                      | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタ 464 クロック・モニタの機能 464 クロック・モニタの構成 464                                                                                                    |

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3                                             | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタを制御するレジスタ 465                                                                                           |

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3                                             | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタ 464 クロック・モニタの機能 464 クロック・モニタの構成 464                                                                                                    |

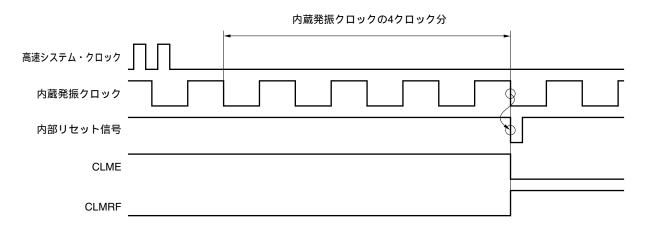

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3<br>23. 4                                    | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンパイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの制成 464 クロック・モニタの動作 466                                                                 |

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3<br>23. 4                                    | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタを制御するレジスタ 465                                                                                           |

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3<br>23. 4                                    | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463  クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの動作 466  パワーオン・クリア回路 471                                                |

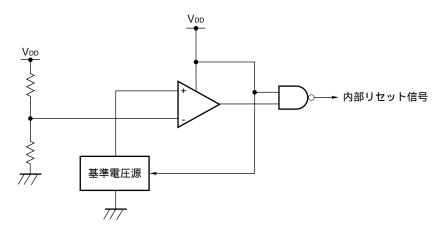

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3<br>23. 4<br>第24章                            | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463 クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの動作 466 パワーオン・クリア回路 471 パワーオン・クリア回路の機能 471                               |

| 第22章<br>22.1<br>第23章<br>23.1<br>23.2<br>23.3<br>23.4<br>第24章<br>24.1<br>24.2                 | 21. 1. 1 スタンバイ機能 … 441 21. 1. 2 スタンバイ機能を制御するレジスタ … 443 スタンバイ機能の動作 … 446 21. 2. 1 HALTモード … 446 21. 2. 2 STOPモード … 451  リセット機能 … 456  リセット要因を確認するレジスタ … 463  クロック・モニタ … 464 クロック・モニタの構成 … 464 クロック・モニタの構成 … 464 クロック・モニタの動作 … 466  パワーオン・クリア回路 … 471 パワーオン・クリア回路の機能 … 471 パワーオン・クリア回路の構成 … 472 |

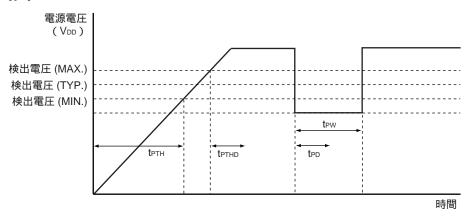

| 第22章<br>22. 1<br>第23章<br>23. 1<br>23. 2<br>23. 3<br>23. 4<br>第24章<br>24. 1<br>24. 2<br>24. 3 | 21. 1. 1 スタンバイ機能 441 21. 1. 2 スタンバイ機能を制御するレジスタ 443 スタンバイ機能の動作 446 21. 2. 1 HALTモード 446 21. 2. 2 STOPモード 451  リセット機能 456  リセット要因を確認するレジスタ 463 クロック・モニタの機能 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの構成 464 クロック・モニタの動作 466 パワーオン・クリア回路 471 パワーオン・クリア回路の機能 471                               |

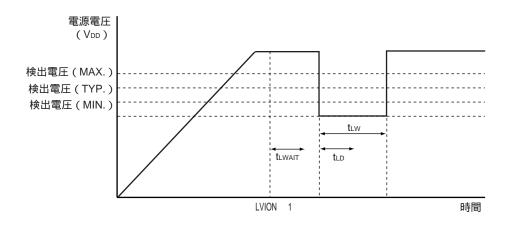

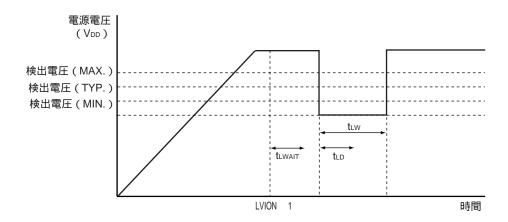

| 第25章                 | <b>低電圧検出回路</b> 475                                |

|----------------------|---------------------------------------------------|

| 25. 1                | 低電圧検出回路の機能 475                                    |

| 25. 2                | <b>低電圧検出回路の構成</b> 475                             |

| 25. 3                | 低電圧検出回路を制御するレジスタ 476                              |

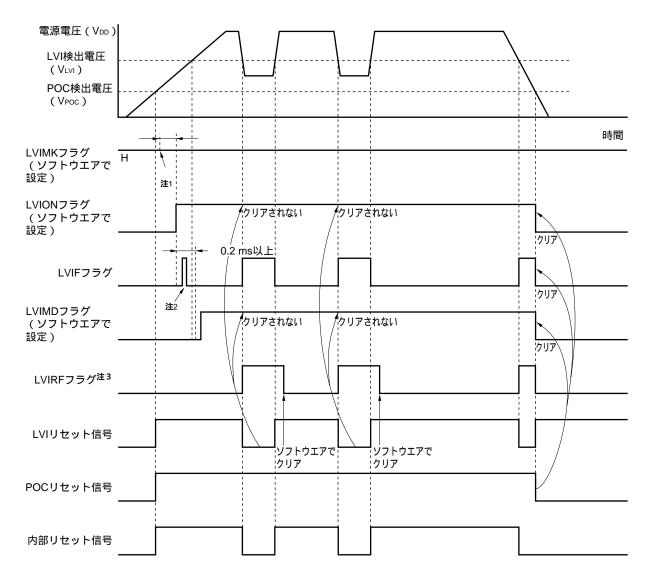

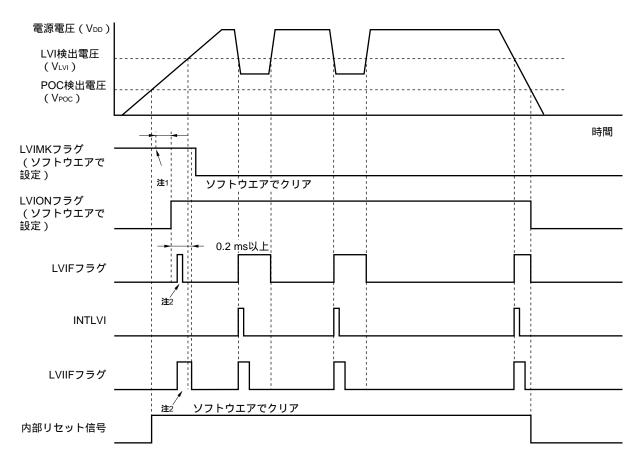

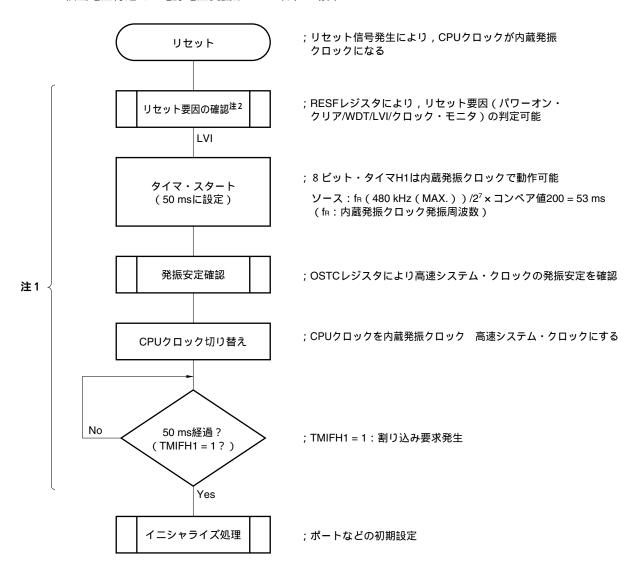

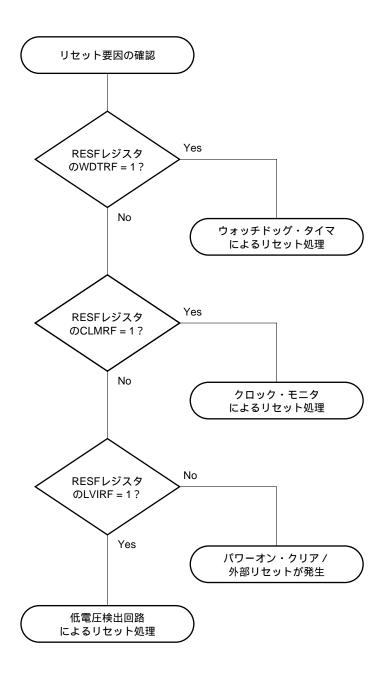

| 25. 4                | <b>低電圧検出回路の動作</b> 479                             |

| 25. 5                | <b>低電圧検出回路の注意事項</b> 483                           |

| 第26章                 | オプション・バイト 487                                     |

| 26. 1                | オプション・バイトの機能 487                                  |

| 26. 2                | オプション・バイトのフォーマット 487                              |

| <b>第</b> 27 <b>章</b> | フラッシュ・メモリ 490                                     |

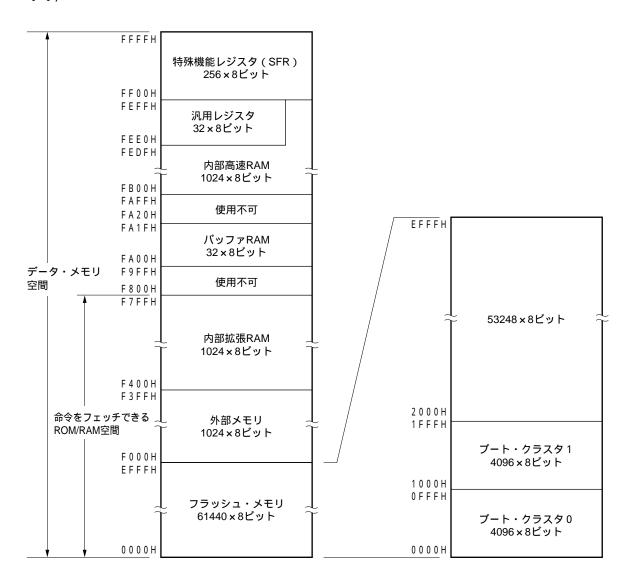

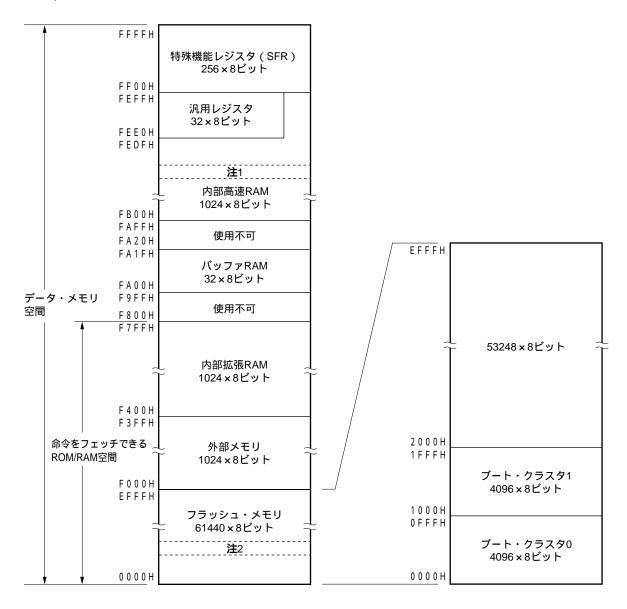

| 27. 1                | メモリ・サイズ切り替えレジスタ 491                               |

| 27. 2                | <b>内部拡張</b> RAM <b>サイズ切り替えレジスタ</b> 492            |

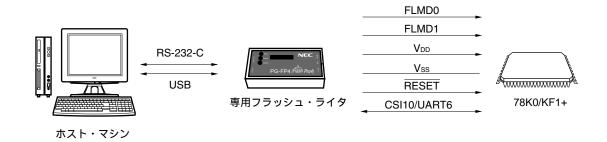

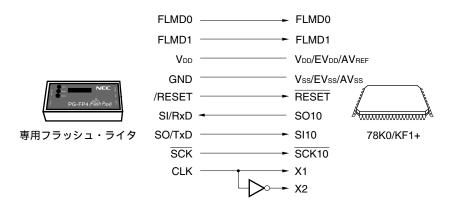

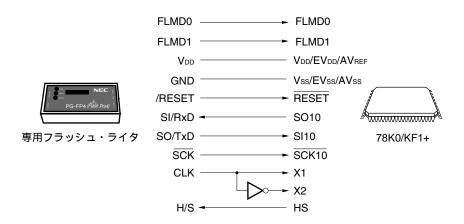

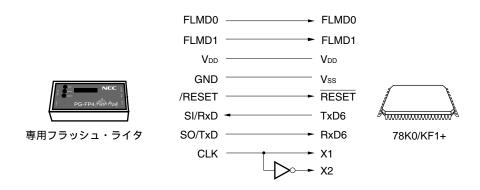

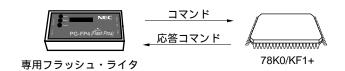

| 27. 3                | フラッシュ・ライタによる書き込み方法 493                            |

| 27. 4                | プログラミング環境 497                                     |

| 27. 5                | 通信方式 497                                          |

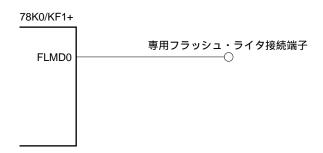

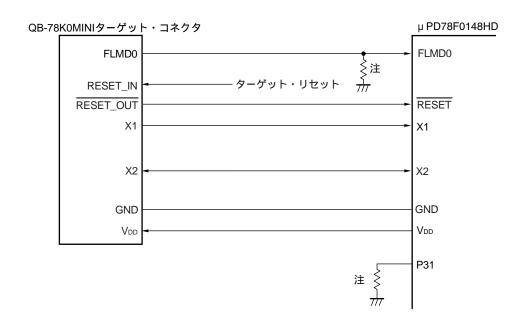

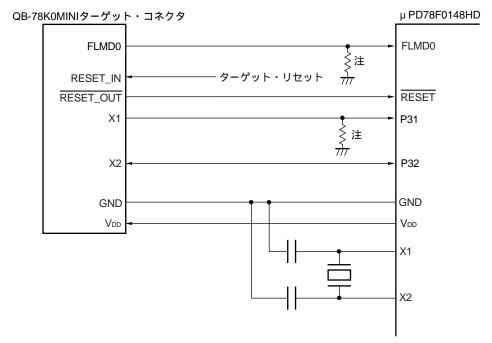

| 27. 6                | オンボード上の端子処理 500                                   |

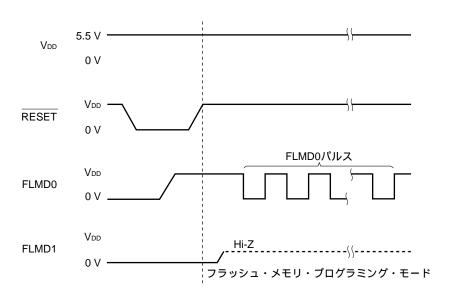

|                      | 27. 6. 1 FLMD0端子 500                              |

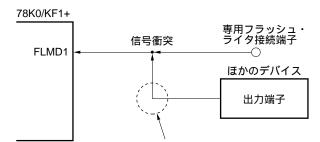

|                      | 27. 6. 2 FLMD1端子 500                              |

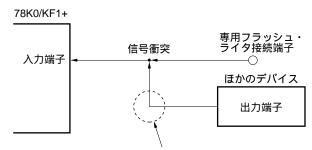

|                      | 27. 6. 3 シリアル・インタフェース端子 501                       |

|                      | 27. 6. 4 RESET端子 503                              |

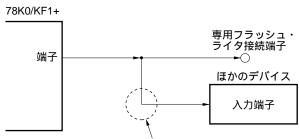

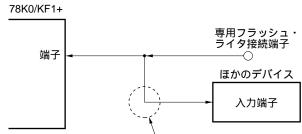

|                      | 27. 6. 5 ポート端子 503                                |

|                      | 27. 6. 6 その他の信号端子 503                             |

|                      | 27. 6. 7 電源 503                                   |

| 27. 7                | プログラミング方法 504                                     |

|                      | 27. 7. 1 フラッシュ・メモリ制御 504                          |

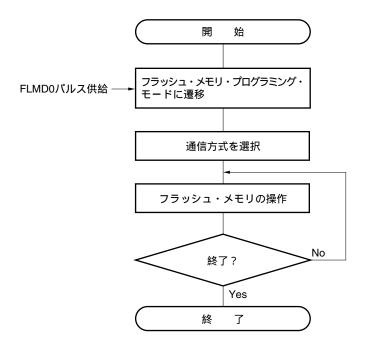

|                      | 27. 7. 2 フラッシュ・メモリ・プログラミング・モード 505                |

|                      | 27. 7. 3 通信方式の選択 506                              |

|                      | 27. 7. 4 通信コマンド 506                               |

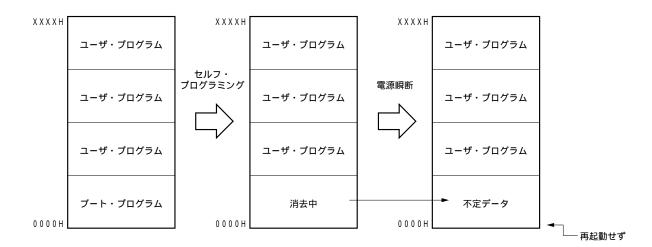

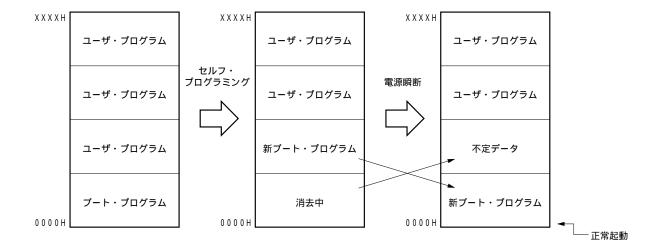

| 27. 8                | セルフ書き込みによるフラッシュ・メモリ・プログラミング 508                   |

|                      | 27. 8. 1 セルフ・プログラミング機能で使用するレジスタ 509               |

| 27. 9                | プート・スワップ機能 513                                    |

|                      | 27. 9. 1 ブート・スワップ機能の概要 513                        |

|                      | 27. 9. 2 メモリ・マップとブート領域 515                        |

| 第28章                 | <b>オンチップ・ディバグ機能(</b> μ PD78F0148HD <b>のみ)</b> 517 |

| 28. 1                | オンチップ・ディバグ・セキュリティID 518                           |

| 第29章                 | <b>命令セットの概要</b> 519                               |

| 29. 1                | 凡 例 520                                           |

|                      | 29. 1. 1 オペランドの表現形式と記述方法 520                      |

|                      | 29. 1. 2 オペレーション欄の説明 521                          |

|                      | 29. 1. 3 フラグ動作欄の説明 521                            |

- 29.2 オペレーション一覧 ... 522

- 29.3 アドレシング別命令一覧 ... 530

第30章 **電気的特性(標準品,(A)水準品)** ... 534

第31章 **電気的特性((A1)水準品)** ... 556

第32章 外形図 ... 573

**第33章 半田付け推奨条件** ... 575

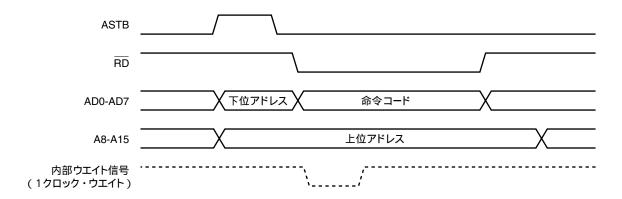

第34章 ウエイトに関する注意事項 ... 577

- 34.1 ウエイトに関する注意事項 ... 577

- 34.2 ウエイトが発生する周辺ハードウエア ... 578

- 34.3 ウエイト発生例 ... 579

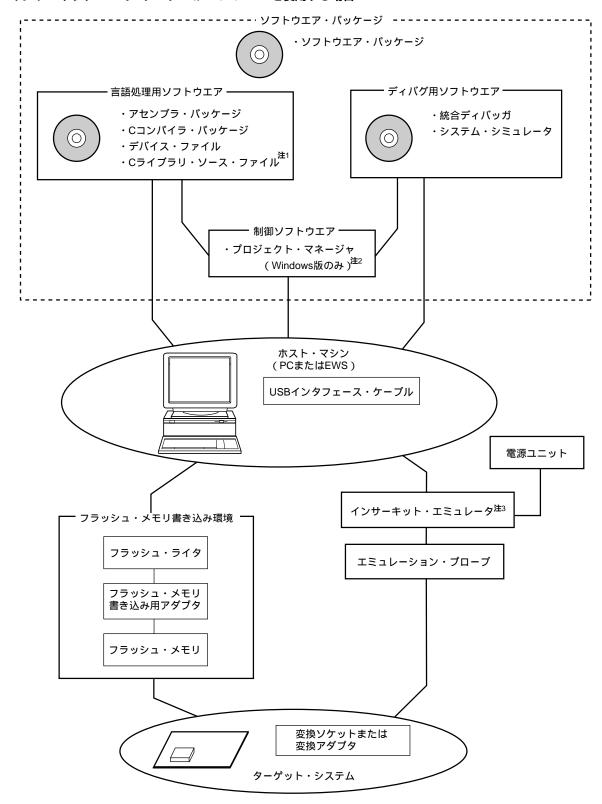

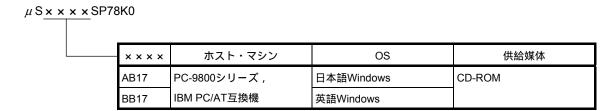

### 付録A 開発ツール ... 580

- A. 1 ソフトウエア・パッケージ ... 583

- A. 2 **言語処理用ソフトウエア** ... 583

- A. 3 **制御ソフトウエア** ... 584

- A. 4 フラッシュ・メモリ書き込み用ツール ... 584

- A. 5 **ディバグ用ツール(ハードウエア)** ... 585 A. 5. 1 インサーキット・エミュレータ QB-78K0KX1Hを使用する場合 ... 585 A. 5. 2 オンチップ・ディバグ・エミュレータ QB-78K0MINIを使用する場合 ... 586

- A. 6 ディバグ用ツール(ソフトウエア) ... 586

### 付録B ターゲット・システム設計上の注意 ... 587

### 付録C レジスタ索引 ... 589

- C.1 レジスタ索引 (50音順) ... 589

- C. 2 レジスタ索引 (アルファペット順) ... 593

**付録D** 注意事項一覧 ... 597

# **付録E 改版履歴** ... 618

- E. 1 本版で改訂された主な箇所 ... 618

- E. 2 前版までの改版履歴 ... 618

# 第1章 概 説

# 1.1 特 徵

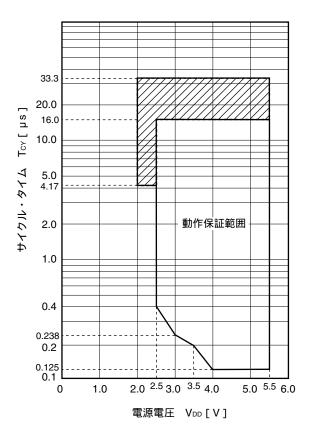

高速( $0.125~\mu$  s:高速システム・クロック16 MHz動作時)から超低速( $122~\mu$  s:サプシステム・クロック 32.768~kHz動作時)まで最小命令実行時間を変更可能

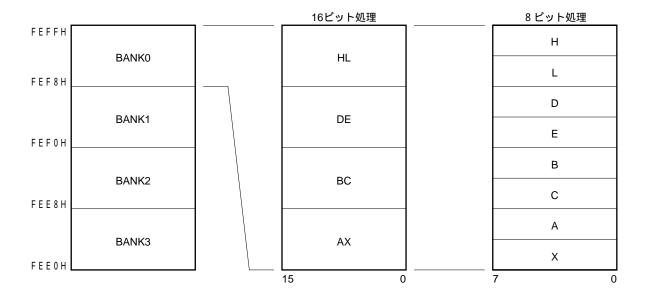

汎用レジスタ:8ビット×32レジスタ(8ビット×8レジスタ×4バンク)

#### ROM, RAM容量

| 項目                | プログラム・    | ・メモリ                 | データ・    | ・メモリ                 |

|-------------------|-----------|----------------------|---------|----------------------|

| 品名                | (ROM      | )                    | 内部高速RAM | 内部拡張RAM              |

| $\mu$ PD78F0148H, | フラッシュ・メモリ | 60 Kバイト <sup>注</sup> | 1024バイト | 1024バイト <sup>注</sup> |

| 78F0148HD         |           |                      |         |                      |

注 メモリ・サイズ切り替えレジスタ (IMS) と内部拡張RAMサイズ切り替えレジスタ (IXS) により,内部フラッシュ・メモリ,内部拡張RAM容量の変更可能。

単電源のフラッシュ・メモリ内蔵

セルフ・プログラミング内蔵 (ブート・スワップ機能あり)

オンチップ・ディバグ機能内蔵 (μPD78F0148HDのみ)

バッファRAM: 32バイト(自動送受信機能付き3線式シリアルI/Oモードの転送用として使用可能)

外部メモリ拡張空間:64 Kバイト(外部バス・インタフェース機能内蔵<sup>注1</sup>)

パワーオン・クリア (POC)回路,低電圧検出(LVI)回路内蔵

内蔵発振器によるCPUディフォールト・スタートにより、ショート・スタート・アップが可能

内蔵発振器によるクロック・モニタ機能内蔵

ウォッチドッグ・タイマ (内蔵発振クロックで動作可能)内蔵

#### 乗除算器内蔵

キー割り込み機能内蔵

クロック出力 / ブザー出力制御回路内蔵

I/Oポート:67本(N-chオープン・ドレーン:4本)

タイマ:8チャネル

シリアル・インタフェース:4チャネル

(UART (LIN (Local Interconnect Network) -bus対応):1チャネル, CSI:1チャネル,

CSI/UART<sup>注2</sup>:1チャネル,自動送受信付きCSI:1チャネル)

10ビット分解能A/Dコンバータ:8チャネル

#### 電源電圧:

・標準品 , (A) 水準品: Vdd = 2.5~5.5 V (内蔵発振クロック / サプシステム・クロック使用時: Vdd = 2.0~5.5 V<sup>i33</sup>)

・ (A1) 水準品 : VDD = 2.7 ~ 5.5 V (内蔵発振クロック使用時: VDD = 2.0 ~ 5.5 V<sup>注3</sup>)

#### 動作周囲温度:

・標準品, (A)水準品: TA = -40~+85

・(A1)水準品 : T<sub>A</sub> = -40~+110

注1. (A1) 水準品は,外部バス・インタフェース機能を使用できません。

- 2. 端子を兼用しているため、どちらかを選択して使用します。

- 3. パワーオン・クリア (POC) 回路の検出電圧 (VPOC) が2.1 V ± 0.1 Vのため, 2.2 ~ 5.5 Vの電圧範囲で使用してください。

# 1.2 応用分野

#### 自動車実装

- ・Body電装系のシステム制御(パワー・ウインドウ,キーレス・エントリ受信など)

- ・制御系のサブマイコン

ホーム・オーディオ,カー・オーディオ

#### AV機器

PC周辺機器(キーボードなど)

#### 家電製品

- ・エアコン室外機

- ・電子レンジ,炊飯器

#### 産業機器

- ・ポンプ

- ・自動販売機

- FA ( Factory Automation )

# 1.3 オーダ情報

・フラッシュ・メモリ製品

| オーダ名称                                | パッケージ                           | 品質水準          |

|--------------------------------------|---------------------------------|---------------|

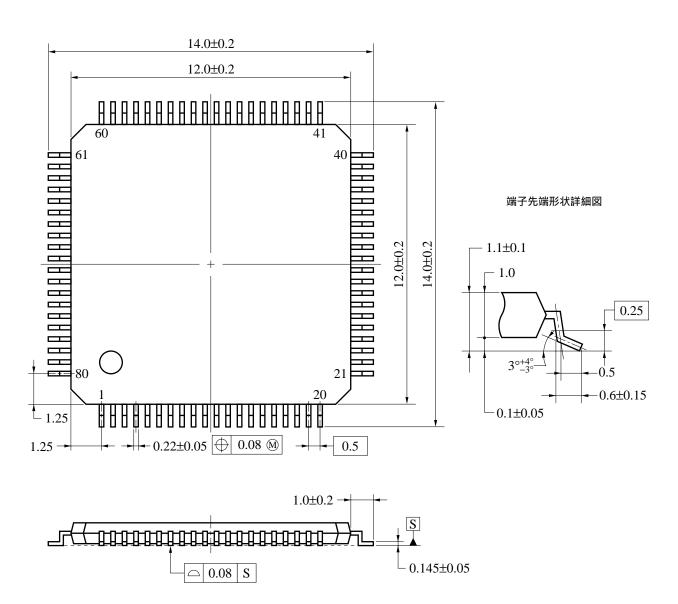

| μPD78F0148HGK-9EU                    | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | 標準(一般電子機器用)   |

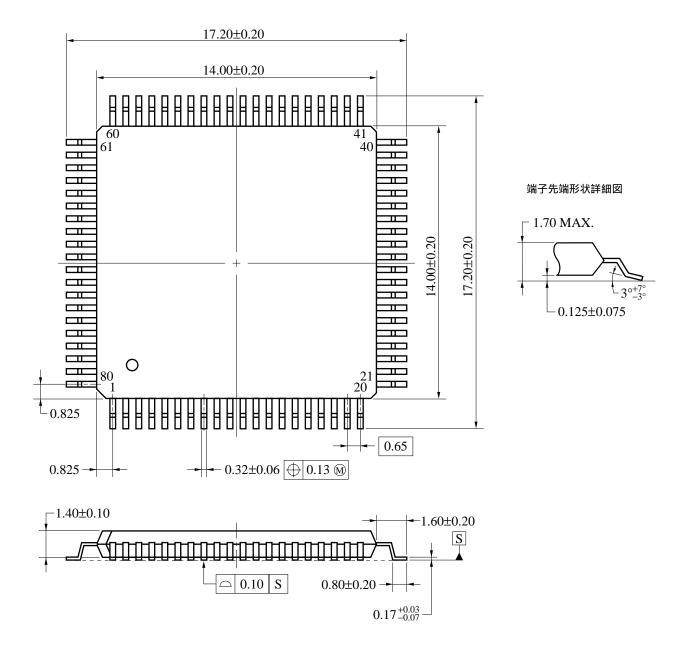

| $\mu$ PD78F0148HGC-8BT               | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HGK-9EU-A             | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HGC-8BT-A             | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HDGK-9EU $^{$         | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HDGC-8BT $^{$         | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HDGK-9EU-A $^{$       | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HDGC-8BT-A $^{\cong}$ | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HGK(A)-9EU            | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | 特別(高信頼度電子機器用) |

| $\mu$ PD78F0148HGC(A)-8BT            | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HGK(A)-9EU-A          | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HGC(A)-8BT-A          | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HGK(A1)-9EU           | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HGC(A1)-8BT           | 80ピン・プラスチックQFP(14x14)           | "             |

| $\mu$ PD78F0148HGK(A1)-9EU-A         | 80ピン・プラスチックTQFP(ファインピッチ)(12x12) | "             |

| $\mu$ PD78F0148HGC(A1)-8BT-A         | 80ピン・プラスチックQFP(14x14)           | "             |

注 ES (Engineering Sample) 品のみ。プログラム評価用としてご使用ください。

備考 オーダ名称末尾「-A」の製品は,鉛フリー製品です。

品質水準とその応用分野の詳細については当社発行の資料「NEC 半導体デバイスの品質水準」 (資料番号 C11531J)をご覧ください。

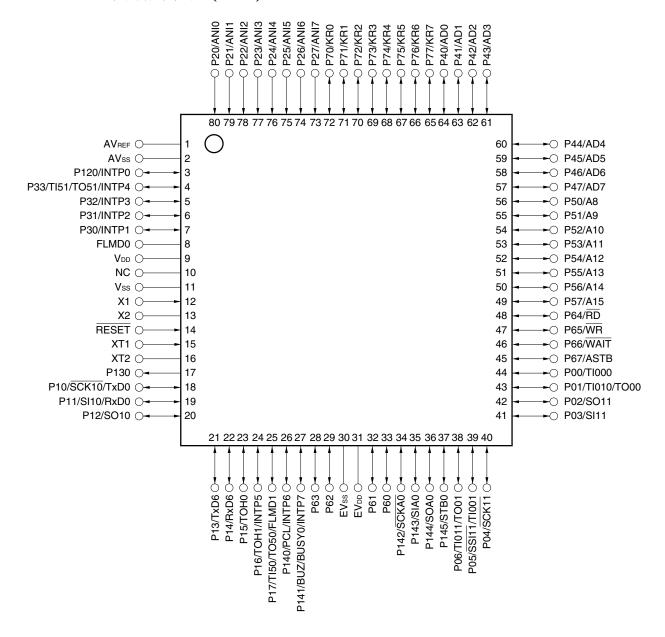

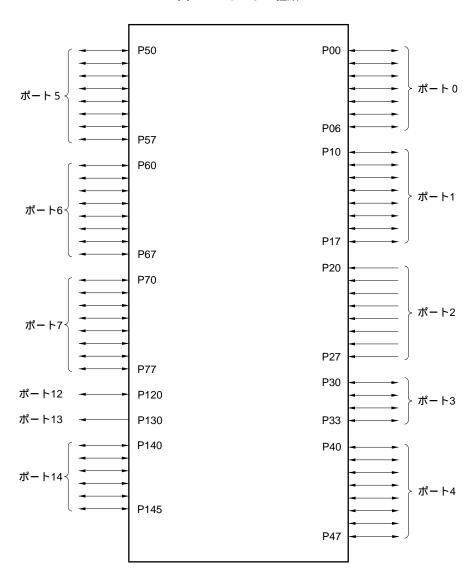

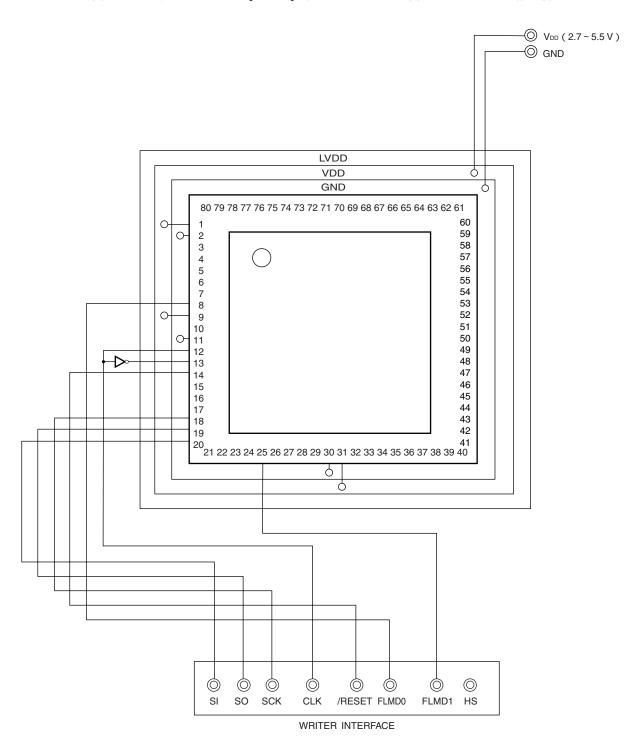

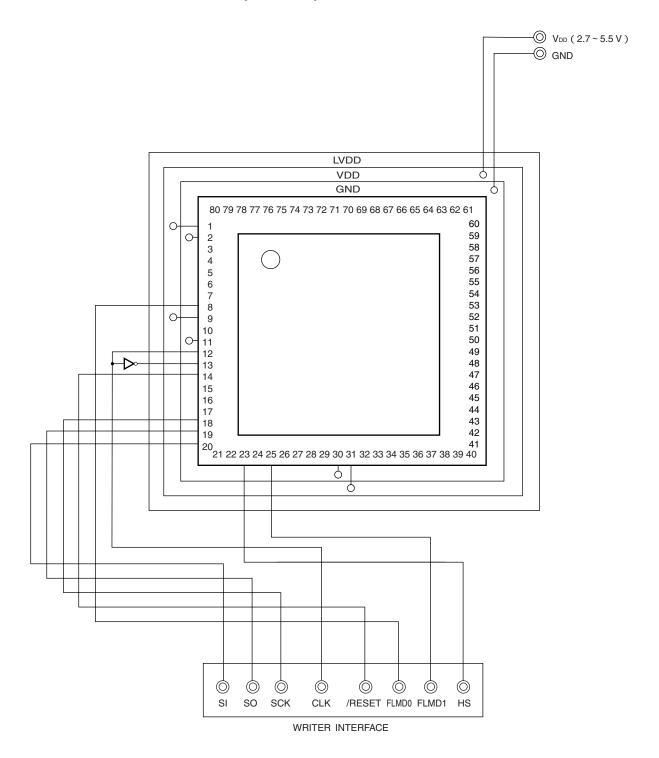

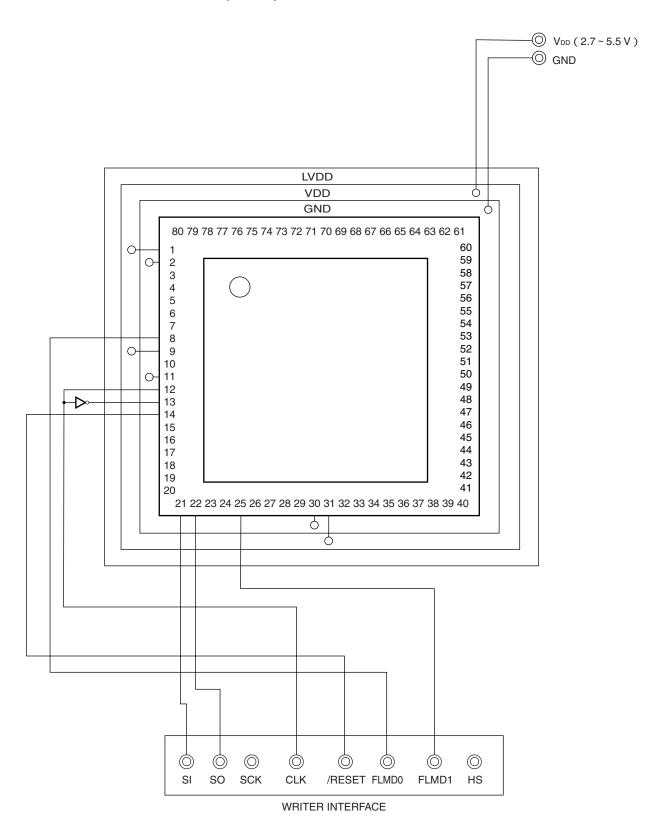

# 1. 4 **端子接続図 (**Top View )

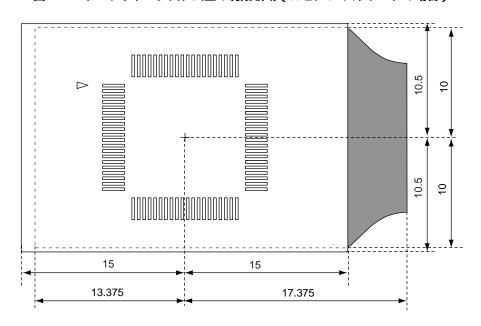

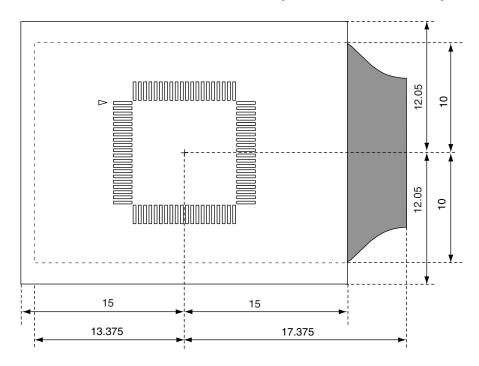

- ・80ピン・プラスチックTQFP (ファインピッチ) (12x12)

- ・80ピン・プラスチックQFP (14x14)

注意 AVss端子はVssに接続してください。

#### 端子名称

A8-A15 : Address Bus PCL : Programmable Clock Output

AD0-AD7 : Address/Data Bus RESET : Reset

ANI0-ANI7 : Analog Input RxD0, RxD6 : Receive Data ASTB : Address Strobe  $\overline{\text{RD}}$  : Read Strobe

AV<sub>REF</sub>: Analog Reference Voltage SCK10, SCK11,

AVss : Analog Ground SCKAO : Serial Clock Input/Output

BUSY0 : Serial Busy Input SI10, SI11, SIA0 : Serial Data Input

BUZ : Buzzer Output SO10, SO11,

EV<sub>DD</sub> : Power Supply for Port SOA1 : Serial Data Output

EVss : Ground for Port : Serial Interface Chip Select Input

FLMD0, FLMD1 : Flash Programming Mode STB0 : Serial Strobe

INTP0-INTP7 : External Interrupt Input Ti000, Ti010,

KR0-KR7 : Key Return Ti001, Ti011,

NC : Non-connection TI50, TI51 : Timer Input

P00-P06 : Port 0 T000, T001, P10-P17 : Port 1 T050, T051,

P20-P27

: Port 2

TOH0, TOH1

: Timer Output

P30-P33

: Port 3

TxD0, TxD6

: Transmit Data

P40-P47

: Port 4

VDD

: Power Supply

P50-P57

: Port 5

Vss

: Ground

P60-P67

: Port 6

WAIT

: Wait

P70-P77 : Port 7 WR : Write Strobe

P120 : Port 12 X1, X2 : Crystal Oscillator (High-speed

P130 : Port 13 System Clock)

P140-P145 : Port 14 XT1, XT2 : Crystal Oscillator (Subsystem Clock)

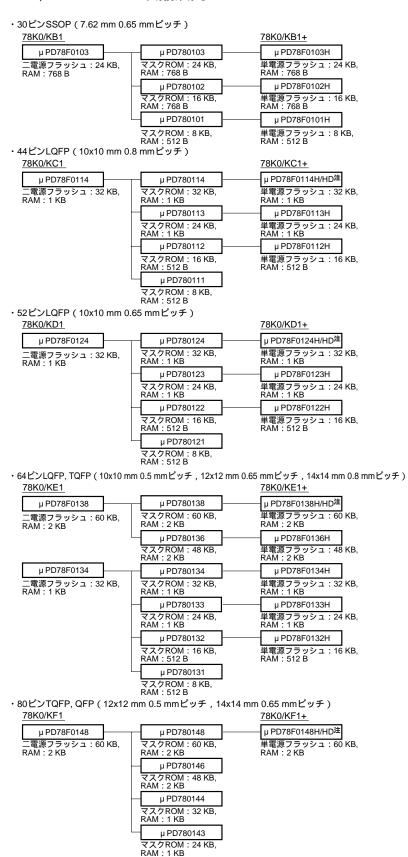

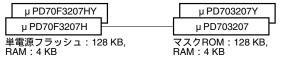

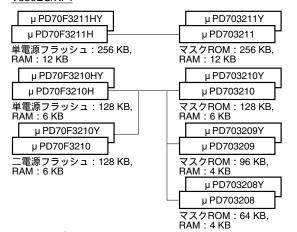

# 1.5 Kx1シリーズの展開

# 1.5.1 78K0/Kx1, 78K0/Kx1+の製品展開

注 オンチップ・ディバグ機能搭載品です。

# 78K0/Kx1の機能一覧を次に示します。

|        | 愛 称                  | 78    | K0/K        | B1     | 78                                           | 3K0/K         | C1      | 78      | 3K0/KI              | <b>D1</b> |                     | 78                         | 3K0/K   | E1     |        | 78   | 3K0/K    | F1  |

|--------|----------------------|-------|-------------|--------|----------------------------------------------|---------------|---------|---------|---------------------|-----------|---------------------|----------------------------|---------|--------|--------|------|----------|-----|

| ピン数    |                      | 3     | 30ピン        | ,      |                                              | 44ピン          | ,       | ;       | 52ピン                | ,         |                     | (                          | 64ピン    | ,      |        |      | 80ピン     | ,   |

| 内部     | マスクROM               | 8     | 16 /        | -      | 8 /                                          | 24/           | -       | 8 /     | 24 /                | -         | 8 /                 | 24 /                       | -       | 48 /   | -      | 24 / | 48 /     | -   |

| メモリ    |                      |       | 24          |        | 16                                           | 32            |         | 16      | 32                  |           | 16                  | 32                         |         | 60     |        | 32   | 60       |     |

| (Kバイト) | フラッシュ・メモリ            | -     |             | 24     |                                              | <u> </u><br>- | 32      |         | <u> </u><br>-       | 32        |                     | -                          | 32      | -      | 60     |      | <u> </u> | 60  |

|        | RAM                  | 0.5   | 0.          | 75     | 0.5                                          |               | 1       | 0.5     | ,                   | 1         | 0.5                 | ,                          | 1       | :      | <br>2  | 1    |          | 2   |

| 電源電圧   | <u> </u>             |       |             |        |                                              |               |         | \       | / <sub>DD</sub> = 2 | 2.5 ~ 5   | .5 V <sup>注1</sup>  | ,2                         |         |        |        |      | l        |     |

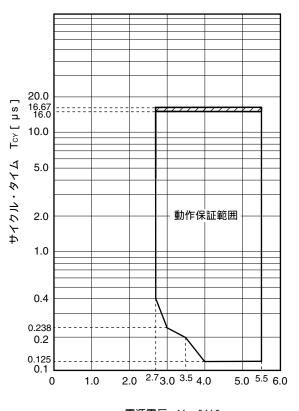

|        | <br>·実行時間            | 0.166 | μs (1       | 2 MHz, | V <sub>DD</sub> = 4                          | .0 ~ 5.5      | 5V時)    |         |                     |           | <sub>DD</sub> に接    |                            |         |        |        |      |          |     |

|        |                      | 0.2 μ | s (10       | MHz, ∖ | / <sub>DD</sub> = 3                          | .5 ~ 5.       | 5 V時)   | 0.166   | δμs(                | 12 M      | Hz, Vo              | D = 4.0                    | 0 ~ 5.5 | 5 V時)  | )      |      |          |     |

|        |                      | 0.238 | μs( 8.3     | 38 MHz | , V <sub>DD</sub> =                          | 3.0 ~ 5.      | .5 V時)  | 0.2 μ   | s (10               | ) MHz     | , V <sub>DD</sub> = | 3.5 ~                      | 5.5 V   | '時)    |        |      |          |     |

|        |                      | 0.4 μ | s(5N        | ИHz, V | op = 2.5                                     | 5 ~ 5.5       | V時)     | 0.238   | 3μs(                | 8.38      | MHz, \              | <b>√</b> <sub>DD</sub> = ; | 3.0 ~ 5 | 5.5 V⊪ | 寺)     |      |          |     |

|        |                      |       |             |        | 0.4 μs (5 MHz, V <sub>DD</sub> = 2.5~5.5 V時) |               |         |         |                     |           |                     |                            |         |        |        |      |          |     |

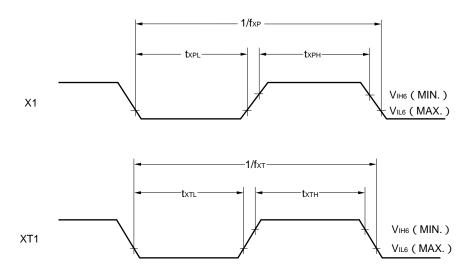

| クロック   | X1入力                 |       |             |        |                                              |               |         |         | 2 -                 | ~ 12 M    | lHz                 |                            |         |        |        |      |          |     |

|        | サブ                   |       | -           |        |                                              |               |         |         |                     |           | 32.76               | 8 kHz                      |         |        |        |      |          |     |

|        | 内蔵発振                 |       |             |        |                                              |               |         |         | 240 k               | Hz ( T    | YP.)                |                            |         |        |        |      |          |     |

| ポート    | CMOS入出力              |       | 17          |        |                                              | 19            |         |         | 26                  |           |                     |                            | 38      |        |        |      | 54       |     |

|        | CMOS入力               |       | 4           |        |                                              |               |         |         |                     |           |                     | 8                          |         |        |        | 1    |          |     |

|        | CMOS出力               |       |             |        |                                              |               |         |         |                     | 1         |                     |                            |         |        |        |      |          |     |

|        | N-chオープン・ド           |       | -           |        |                                              |               |         |         |                     |           |                     | 4                          |         |        |        |      |          |     |

|        | レーン入出力               |       |             |        |                                              |               |         |         |                     |           |                     |                            |         |        |        |      |          |     |

| タイマ    | 16ビット(TMO)           |       |             |        |                                              | 1             | ch      |         |                     |           |                     |                            | 2       | ch     |        | 1 ch | 2        | ch  |

|        | 8ビット(TM5)            |       | 1 ch        |        |                                              |               |         |         |                     |           | 2                   | ch                         |         |        |        | 1    | ı        |     |

|        | 8ビット(TMH)            |       |             |        |                                              |               |         |         |                     | 2 ch      |                     |                            |         |        |        |      |          |     |

|        | 時計用                  |       | -           |        |                                              |               |         |         |                     |           | 1                   | ch                         |         |        |        |      |          |     |

|        | WDT                  |       |             |        |                                              |               |         |         |                     | 1 ch      |                     |                            |         |        |        |      |          |     |

| シリア    | 3線式CSI <sup>注3</sup> |       |             |        |                                              | 1             | ch      |         |                     |           |                     |                            | 2       | ch     |        | 1 ch | 2        | ch  |

| ル・イン   | 自動送受信3線式CSI          |       |             |        |                                              |               |         |         | -                   |           |                     |                            |         |        |        |      | 1ch      |     |

| タフェー   | UART <sup>注3</sup>   | -     |             |        |                                              |               |         |         |                     | 1         | ch                  |                            |         |        |        |      |          |     |

| ス      | LIN-bus対応UART        |       |             |        |                                              |               |         |         |                     | 1 ch      |                     |                            |         |        |        |      |          |     |

| 10ビット  | ·A/Dコンバータ            |       | 4 ch        |        |                                              |               |         |         |                     |           | 8                   | ch                         |         |        |        |      |          |     |

| 割り込み   | 外部                   |       | 6           |        |                                              | 7             |         |         | 8                   |           |                     |                            | 9       |        |        |      | 9        |     |

|        | 内部                   | 11    | 1           | 2      |                                              |               | 1       | 5       |                     |           | 16                  |                            | 1       | 19     |        | 17   | 2        | 20  |

| キー・リ   | ターン入力                |       | -           |        |                                              | 4ch           |         |         |                     |           |                     |                            | 8ch     |        |        |      | 1        |     |

| リセット   | RESET端子              |       |             |        |                                              |               |         |         |                     | あり        |                     |                            |         |        |        |      |          |     |

|        | POC                  |       |             | 2.8    | 85 V ±                                       | 0.15          | V/3.5 ' | V ± 0.2 | 20 V (              | マスク       | 7・オ                 | プショ                        | ンに。     | より選    | 択可能    | ŧ)   |          |     |

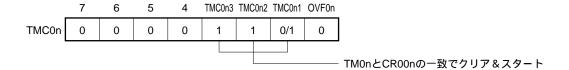

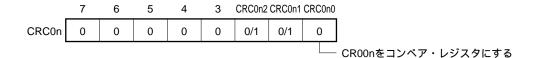

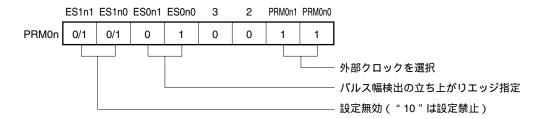

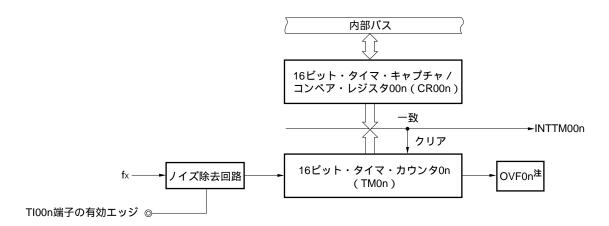

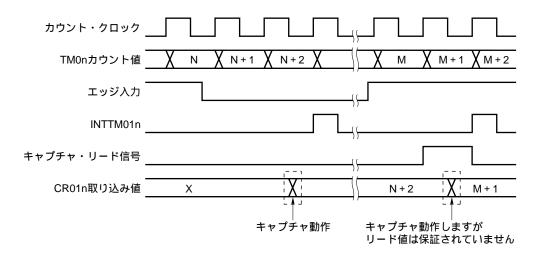

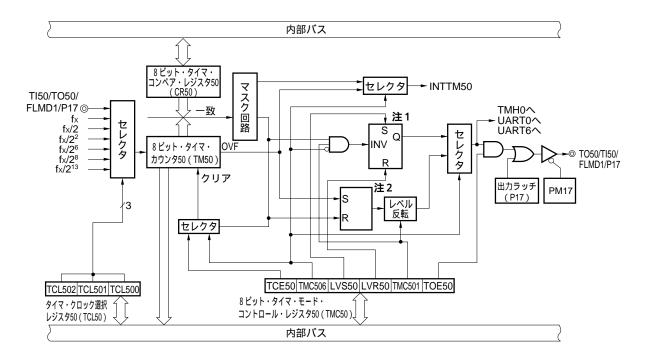

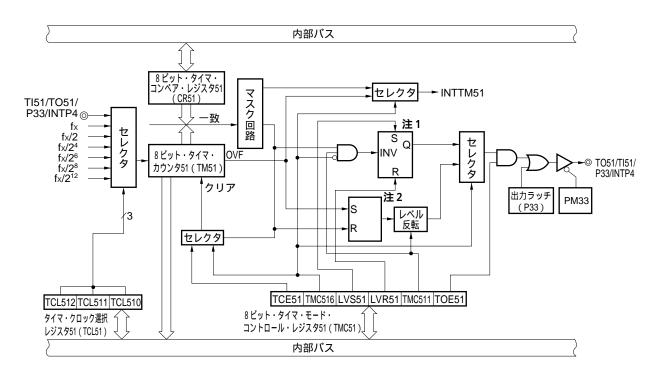

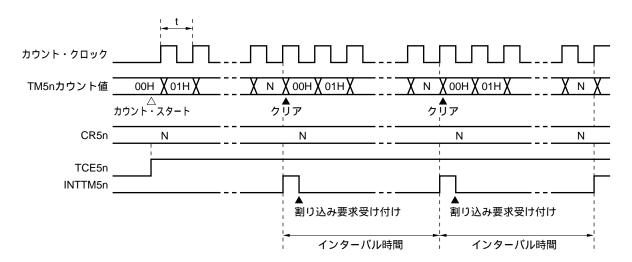

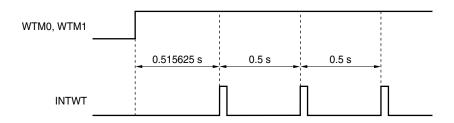

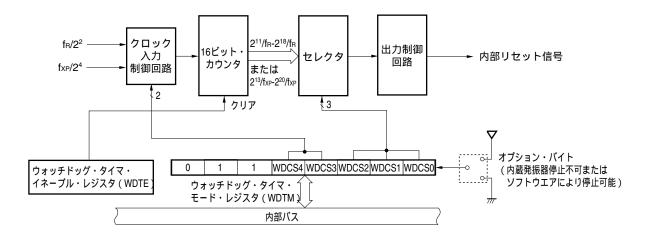

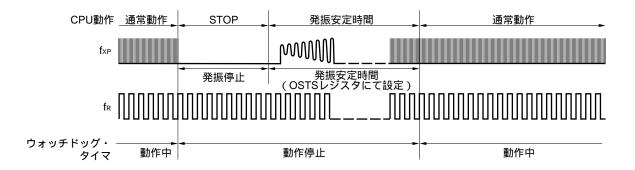

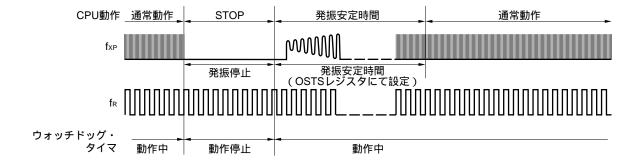

|        | LVI                  | 2.85  | V/3.1       | V/3.3  | 8 V ± 0                                      | .15 V/        | /3.5 V/ | 3.7 V/  | 3.9 V/              | 4.1 V/    | 4.3 V :             | ± 0.2 √                    | /(ソ:    | フトウ    | エアに    | こよりi | 選択可      | 能)  |