### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

32

# SH-3、SH-3E、SH3-DSP

ソフトウェアマニュアル ルネサス32ビットRISCマイクロコンピュータ SuperH™ RISC engineファミリ

#### 安全設計に関するお願い -

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、 誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した 冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### ■ 本資料ご利用に際しての留意事項 -

- 1. 本資料は、お客様が用途に応じた適切なルネサステクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサステクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報 は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。

### 製品に関する一般的注意事項

#### 1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。

2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。

未使用の入力端子は、入力をプルアップかプルダウンによって、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は,製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシステムが誤動作を起こさないようにシステム設計を行ってください。

リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザープアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられています。 これらのレジスタをアクセスしたときの動作および継続する動作については、保証できませんので、アクセス しないようにしてください。

### はじめに

SH-3、SH-3E、SH3-DSP は、RISC タイプの CPU により、高性能な演算処理を実現し、システム構成に必要な周辺機能を集積すると同時に、携帯用機器に不可欠な低消費電力を同時に実現する新世代シングルチップ RISC マイコンです。

SH-3、SH-3E、SH3-DSP の CPU は、RISC (Reduced instruction set computer) タイプの命令セットを持っており、基本命令は1命令1ステート(1システムクロックサイクル)で動作するので、命令実行速度が向上しています。また内部32ビット構成を採っていてデータ処理能力を強化しています。

また、SH-3E は単精度浮動小数点演算をサポートし、さらに PCAPI 完全準拠の倍精度浮動小数点演算もエミュレーションします。SH-3E の命令は IEEE754 規格に対応した浮動小数点演算のサブセットとなっています。

このソフトウェアマニュアルは、SH-3、SH-3E、SH3-DSPの命令の詳細について記載しています。 命令の動作やアーキテクチャを知るために使ってください。SH-3、SH-3E、SH3-DSPの特長であるパ イプラインの動作についても述べてあります。

ハードウェアについては、ハードウェアマニュアルをごらんください。

## マニュアルの構成

このマニュアルの構成を表1に示します。また、記載項目と記載章節との関係を表2に示します。

表 1 マニュアルの構成

| 区分         |            | 章名                | 内容                                                      |

|------------|------------|-------------------|---------------------------------------------------------|

| 概要         | 1. 特·      | 長                 | CPU の特長                                                 |

| アーキテクチャ(1) | 2. プ       | ログラミングモデル         | 汎用レジスタ、コントロールレジスタ、システム<br>レジスタの種類と構成                    |

|            | 3. デ       | ータ形式              | レジスタとメモリ上のデータ形式                                         |

|            | 4. 浮       | 動小数点演算ユニット        | FPU のレジスタ構成、FPU 例外                                      |

|            | 5. DS<br>転 | SP の演算機能とデータ<br>送 | 固定小数点演算、整数演算、論理演算、乗算、シフト演<br>算、飽和演算などの DSP 演算の概要、繰り返し制御 |

| 命令の概要      | 6. 命       | 令の特長              | 命令の特長、アドレッシングモード、命令形式                                   |

|            | 7. 命       | 令セット              | 分類順の命令概要、アルファベット順命令一覧                                   |

| 命令の詳細      | 8. 各       | 命令の説明             | アルファベット順の各命令の動作                                         |

| アーキテクチャ(2) | 9. 処       | 理状態               | 低消費電力モードなどの処理状態                                         |

### 表2 項目と関連する章名

| 区分      | 表2 項目と関連を<br>項目   | 章名                  |

|---------|-------------------|---------------------|

|         | ****              |                     |

| 概要と特長   | CPU の特長           | 1. 特長               |

|         | 命令の特長             | 6.1 RISC タイプ命令セット   |

|         | パイプライン            | 10.1 パイプラインの基本構成    |

|         |                   | 10.2 スロットとパイプラインの流れ |

| アーキテクチャ | レジスタの構成           | 2. プログラミングモデル       |

|         | データ形式             | 3. データ形式            |

|         | 浮動小数点演算ユニット       | 4. 浮動小数点演算ユニット      |

|         | DSP               | 5. DSP の演算機能とデータ転送  |

|         | 処理状態、リセット状態、      | 9. 処理状態             |

|         | 例外処理状態、バス権解放状態、   |                     |

|         | プログラム実行状態、        |                     |

|         | 低消費電力モード、スリープモード、 |                     |

|         | スタンバイモード          |                     |

|         | パイプライン動作          | 10. パイプライン動作        |

| 命令の概要   | 命令の特長             | 6. 命令の特長            |

|         | アドレッシングモード        | 6.2 アドレッシングモード      |

|         | 命令形式              | 6.3 命令形式            |

| 命令一覧    | 命令セット             | 7.1 分類順命令セット        |

|         |                   | 7.2 アルファベット順命令セット   |

| 命令の詳細   | 命令の動作詳細           | 8. 各命令の説明           |

|         |                   | 10.7 各命令のパイプラインの動作  |

|         | 命令実行ステート数         | 10.3 命令実行ステート数      |

## 本版で改訂された箇所

| 修正項目 | ページ | 修正箇所                         |

|------|-----|------------------------------|

| 全体   | -   | 社名変更による変更                    |

|      |     | (修正前)日立製作所 → (修正後)ルネサス テクノロジ |

## 目次

| 第1: | 章 概要                               |             |

|-----|------------------------------------|-------------|

| 1.1 | SH-3 CPU の特長                       | 1-1         |

| 1.2 | SH3-DSP の特長                        | 1-3         |

| 第2  | 章 プログラミングモデル                       |             |

| 2.1 | 概要                                 | 2-1         |

| 2.2 | 汎用レジスタ                             | 2-8         |

| 2.3 | コントロールレジスタ                         | 2-10        |

| 2.4 | システムレジスタ                           | 2-11        |

| 2.5 | レジスタの初期値                           |             |

| 第3  | 章 データ形式                            |             |

| 3.1 |                                    | 3-1         |

| 3.2 | メモリ上でのデータ形式                        |             |

| 3.3 | イミディエイトデータのデータ形式                   |             |

| 3.4 | DSP タイプデータ形式(SH3-DSP のみ)           |             |

|     | 章 浮動小数点演算ユニット(SH-3E のみ)            | 5-3         |

| 4.1 | 概要                                 | <i>1</i> _1 |

| 4.2 |                                    |             |

| 4.2 | 4.2.1 浮動小数点レジスタ                    |             |

|     | 4.2.1 / 字動小数点レジスタ                  |             |

|     | 4.2.3 浮動小数点ステータス/コントロールレジスタ (FPSCR |             |

| 4.3 | 浮動小数点フォーマット                        |             |

|     | 4.3.1 浮動小数点数フォーマット                 | 4-4         |

|     | 4.3.2 非数 ( NaN )                   |             |

|     | 4.3.3 非正規化数の値                      |             |

| 4.4 | 4.3.4 その他の特殊な値について<br>浮動小数点例外モデル   |             |

| 7.7 | 4.4.1 イネーブル状態の例外                   |             |

|     | 4.4.2 ディスエーブル状態の例外                 |             |

|     | 4.4.3 FPU の例外事象とコード                |             |

|     | 4.4.4 メモリ内の浮動小数点データの配置             |             |

|     | 4.4.5 特殊オペランドを伴う算術演算               | 4-6         |

| 4.5  | CPU との同期化                                   | 4-7  |

|------|---------------------------------------------|------|

| 第5章  | 章 DSP の演算機能とデータ転送(SH3-DSP のみ)               |      |

| 5.1  | ALU 固定小数点演算                                 | 5-2  |

| 5.2  | ALU 整数演算                                    | 5-7  |

| 5.3  | ALU 論理演算                                    | 5-9  |

| 5.4  | 固定小数点乗算                                     | 5-11 |

| 5.5  | シフト演算                                       | 5-13 |

|      | 5.5.1 算術シフト演算                               | 5-13 |

|      | 5.5.2 論理シフト演算                               |      |

| 5.6  | MSB 検出命令                                    |      |

| 5.7  | 丸め処理                                        |      |

| 5.8  | 状態選択ビット (CS)と DSP 状態ビット (DC)                | 5-24 |

| 5.9  | オーバフロー防止機能(飽和演算)                            | 5-25 |

| 5.10 | データ転送                                       | 5-26 |

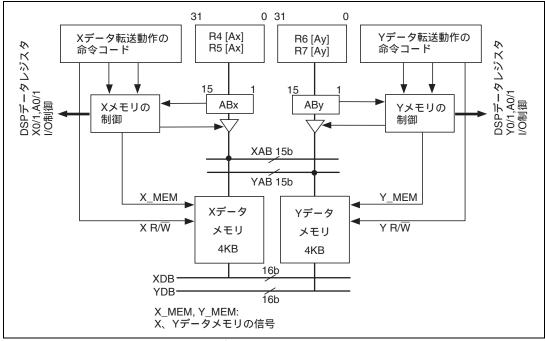

|      | 5.10.1 X、Y メモリデータ転送                         |      |

|      | 5.10.2 シングルデータ転送                            |      |

| 5.11 | オペランド競合                                     |      |

| 5.12 | DSP 繰り返し(ループ)制御                             |      |

|      | 5.12.1 注意事項                                 |      |

| 5.13 | 条件付き命令とデータ転送                                | 5-37 |

|      | 章 命令の特長                                     |      |

| 6.1  | RISC タイプ命令セット                               |      |

|      | 6.1.1 16 ビット固定長命令                           |      |

|      | 6.1.2 1命令/1ステート                             |      |

|      | 6.1.3 データサイズ                                |      |

|      | 6.1.5 遅延分岐                                  |      |

|      | 6.1.6 乗算 / 積和演算                             |      |

|      | 6.1.7 Tビット                                  |      |

|      | 6.1.8 イミディエイトデータ                            |      |

|      | 6.1.9 絶対アドレス                                |      |

|      | 6.1.10 16 ビット / 32 ビットディスプレースメント            |      |

| 6.2  | 6.1.11       特権命令         CPU 命令のアドレッシングモード |      |

| 6.3  | DSP データアドレッシング (SH3-DSP のみ)                 |      |

| 0.5  | 6.3.1 X、Y データアドレッシング                        |      |

|      | 6.3.2 シングルデータアドレッシング                        |      |

|      | 6.3.3 モジュロアドレッシング                           |      |

|      | 6.3.4 DSP アドレッシング動作                         |      |

| 6.4  | CPU 命令の命令形式                                 | 6-13 |

| 6.5  | DSP 命令の命令形式 ( SH3-DSP のみ )                  | 6-15 |

|      | 6.5.1 ダブル、シングルデータ転送命令                       | 6-16 |

|      |                                             |      |

|     | 6.5.2  | 並行処理命令                                      | 6-17 |

|-----|--------|---------------------------------------------|------|

| 第 7 | 章 命令   | セット                                         |      |

| 7.1 | 分類順    | 命令セット                                       | 7-1  |

|     | 7.1.1  | データ転送命令                                     | 7-5  |

|     | 7.1.2  | 算術演算命令                                      |      |

|     | 7.1.3  | <br>論理演算命令                                  |      |

|     | 7.1.4  | シフト命令                                       |      |

|     | 7.1.5  | 分岐命令                                        | 7-9  |

|     | 7.1.6  | システム制御命令                                    | 7-10 |

|     | 7.1.7  | 浮動小数点命令(SH-3E のみ)                           | 7-12 |

|     | 7.1.8  | FPU システムレジスタに関連する CPU 命令 ( SH-3E のみ )       | 7-13 |

|     | 7.1.9  | DSP 機能をサポートする CPU 命令(SH3-DSP のみ)            | 7-13 |

| 7.2 | アルフ    | アベット順命令セット                                  | 7-15 |

| 7.3 | DSP デ  | ・<br>ータ転送命令の命令セット(SH3-DSP のみ)               | 7-23 |

|     | 7.3.1  | ダブルデータ転送命令(X メモリデータ)                        | 7-23 |

|     | 7.3.2  | ダブルデータ転送命令(Y メモリデータ)                        | 7-24 |

|     | 7.3.3  | シングルデータ転送命令                                 |      |

| 7.4 | DSP 演  | 算命令の命令セット ( SH3-DSP のみ )                    |      |

|     | 7.4.1  | ALU 算術演算命令                                  | 7-28 |

|     | 7.4.2  | ALU 論理演算命令                                  |      |

|     | 7.4.3  | 固定小数点乗算命令                                   |      |

|     | 7.4.4  | シフト演算命令                                     |      |

|     | 7.4.5  | システム制御命令                                    |      |

|     | 7.4.6  | NOPX と NOPY の命令コード                          |      |

| 第8: | 章 各命   | 令の説明                                        |      |

| 8.1 | 命令説    | 明のフォーム                                      | 8-1  |

| 8.2 | 命令の    | 説明 (SH-3、SH-3E、SH3-DSP に共通する CPU 命令の説明)     | 8-5  |

|     | 8.2.1  | ADD ADD binary:算術演算命令                       | 8-5  |

|     | 8.2.2  | ADDC ADD with Carry: 算術演算命令                 |      |

|     | 8.2.3  | ADDV ADD with V flag overflow check: 算術演算命令 |      |

|     | 8.2.4  | AND AND logical:論理演算命令                      |      |

|     | 8.2.5  | BF Branch if False:分岐命令                     |      |

|     | 8.2.6  | BF/S Branch if False with delay Slot:分岐命令   |      |

|     | 8.2.7  | BRA BRAnch:分岐命令                             |      |

|     | 8.2.8  | BRAF BRAnch Far:分岐命令                        |      |

|     | 8.2.9  | BSR Branch to SubRoutine: 分岐命令              | 8-16 |

|     | 8.2.10 | BSRF Branch to SubRoutine Far: 分岐命令         |      |

|     | 8.2.11 | BT Branch if True:分岐命令                      |      |

|     | 8.2.12 | BT/S Branch if True with delay Slot:分岐命令    |      |

|     | 8.2.13 | CLRMAC CLeaR MAC register:システム制御命令          |      |

|     | 8.2.14 | CLRS CLeaR Sbit:システム制御命令                    |      |

|     | 8.2.15 | CLRT CLeaR Tbit:システム制御命令                    |      |

|     | 8.2.16 | CMP/cond CoMPare conditionally: 算術演算命令      |      |

|     | 8.2.17 | DIVOS DIVide (step0) as Signed: 算術演算命令      |      |

|     | 8.2.18 | DIV0U DIVide(step0) as Unsigned: 算術演算命令     |      |

| 8.2.19 | DIV1 DIVide 1 step:算術演算命令                           |       |

|--------|-----------------------------------------------------|-------|

| 8.2.20 | DMULS.L Double-length MULtiply as Signed: 算術演算命令    | 8-35  |

| 8.2.21 | DMULU.L Double-length MULtiply as Unsigned: 算術演算命令  |       |

| 8.2.22 | DT Decrement and Test: 算術演算命令                       |       |

| 8.2.23 | EXTS EXTend as Signed: 算術演算命令                       | 8-40  |

| 8.2.24 | EXTU EXTend as Unsigned: 算術演算命令                     | 8-41  |

| 8.2.25 | JMP JuMP: 分岐命令                                      |       |

| 8.2.26 | JSR Jump to SubRoutine: 分岐命令                        | 8-43  |

| 8.2.27 | LDC LoaD to Control register:システム制御命令               | 8-45  |

| 8.2.28 | LDRE LoaD effective address to RE register:システム制御命令 | 8-50  |

| 8.2.29 | LDRS LoaD effective address to RS register:システム制御命令 | 8-51  |

| 8.2.30 | LDS LoaD to System register:システム制御命令                |       |

| 8.2.31 | LDTLB Load PTEH/PTEL to TLB:システム制御命令                |       |

| 8.2.32 | MAC.L Multiply and ACcumulate Long:算術演算命令           | 8-57  |

| 8.2.33 | MAC Multiply and ACcumulate Word:算術演算命令             |       |

| 8.2.34 | MOV MOVe data:データ転送命令                               |       |

| 8.2.35 | MOV MOVe immediate data:データ転送命令                     |       |

| 8.2.36 | MOV MOVe peripheral data:データ転送命令                    | 8-69  |

| 8.2.37 | MOV MOVe structure data:データ転送命令                     | 8-72  |

| 8.2.38 | MOVA MOVe effective Address:データ転送命令                 |       |

| 8.2.39 | MOVT MOVe T bit:データ転送命令                             |       |

| 8.2.40 | MUL.L MULtiply Long:算術演算命令                          |       |

| 8.2.41 | MULS.W MULtiply as Signed Word: 算術演算命令              |       |

| 8.2.42 | MULU.W MULtiply as Unsigned Word: 算術演算命令            | 8-79  |

| 8.2.43 | NEG NEGate: 算術演算命令                                  |       |

| 8.2.44 | NEGC NEGate with Carry: 算術演算命令                      | 8-81  |

| 8.2.45 | NOP No Operation:システム制御命令                           |       |

| 8.2.46 | NOT NOT-logical complement: 論理演算命令                  | 8-83  |

| 8.2.47 | OR OR logical: 論理演算命令                               |       |

| 8.2.48 | PREF PREFetch data to the cache:システム制御命令            |       |

| 8.2.49 | ROTCL ROTate with Carry Left:シフト命令                  | 8-87  |

| 8.2.50 | ROTCR ROTate with Carry Right: シフト命令                |       |

| 8.2.51 | ROTL ROTate Left:シフト命令                              |       |

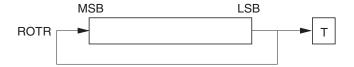

| 8.2.52 | ROTR ROTate Right: シフト命令                            |       |

| 8.2.53 | RTE ReTurn from Exception:システム制御命令                  |       |

| 8.2.54 | RTS ReTurn from SubRoutine: 分岐命令                    | 8-93  |

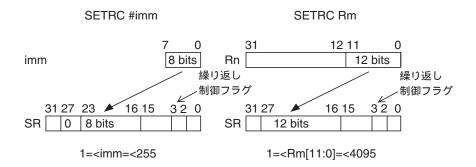

| 8.2.55 | SETRC SET reperat count RC:システム制御命令                 |       |

| 8.2.56 | SETS SET Sbit: システム制御命令                             |       |

| 8.2.57 | SETT SET T bit: システム制御命令                            |       |

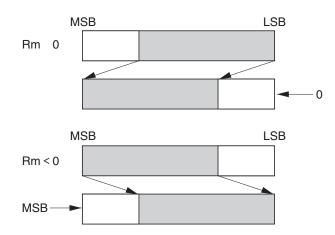

| 8.2.58 | SHAD SHift Arithemetic Dynamically:シフト命令            |       |

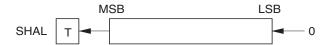

| 8.2.59 | SHAL SHift Arithmetic Left:シフト命令                    |       |

| 8.2.60 | SHAR SHift Arithmetic Right: シフト命令                  |       |

| 8.2.61 | SHLD SHift Logical Dynamically:シフト命令                |       |

| 8.2.62 | SHLL SHift Logical Left:シフト命令                       |       |

| 8.2.63 | SHLLn n bits SHift Logical Left:シフト命令               |       |

| 8.2.64 | SHLR SHift Logical Right: シフト命令                     |       |

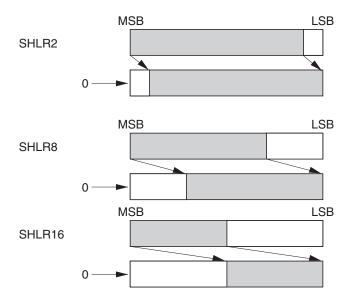

| 8.2.65 | SHLRn n bits SHift Logical Right:シフト命令              | 8-109 |

|     | 8.2.66 | SLEEP SLEEP:システム制御命令                                         |       |

|-----|--------|--------------------------------------------------------------|-------|

|     | 8.2.67 | STC Store Control register:システム制御命令                          | 8-112 |

|     | 8.2.68 | STS STore System register:システム制御命令                           | 8-117 |

|     | 8.2.69 | SUB SUBtract binary: 算術演算命令                                  | 8-121 |

|     | 8.2.70 | SUBC SUBtract with Carry: 算術演算命令                             | 8-122 |

|     | 8.2.71 | SUBV SUBtract with(Vflag)underflow check: 算術演算命令             | 8-123 |

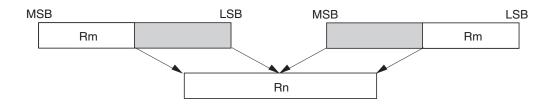

|     | 8.2.72 | SWAP SWAP register halves:データ転送命令                            | 8-124 |

|     | 8.2.73 | TAS Test And Set:論理演算命令                                      | 8-126 |

|     | 8.2.74 | TRAPA TRAP Always:システム制御命令                                   | 8-127 |

|     | 8.2.75 | TST TeST logical:論理演算命令                                      | 8-128 |

|     | 8.2.76 | XOR eXclusive OR logical:論理演算命令                              | 8-130 |

|     | 8.2.77 | XTRCT eXTRaCT:データ転送命令                                        | 8-132 |

| 8.3 | 浮動小数   | 数点命令と FPU に関連する CPU 命令(SH-3E のみ)                             | 8-133 |

|     | 8.3.1  | FABS Floating point ABSolute value:浮動小数点命令                   | 8-135 |

|     | 8.3.2  | FADD Floating point ADD:浮動小数点命令                              |       |

|     | 8.3.3  | FCMP Floating point Compare: 浮動小数点命令                         |       |

|     | 8.3.4  | FDIV Floating point DIVide: 浮動小数点命令                          |       |

|     | 8.3.5  | FLDIO Floating point LoaD Immediate 0: 浮動小数点命令               |       |

|     | 8.3.6  | FLDI1 Floating point LoaD Immediate 1: 浮動小数点命令               | 8-146 |

|     | 8.3.7  | FLDS Floating point LoaD to System register: 浮動小数点命令         |       |

|     | 8.3.8  | FLOAT FLOAting point Convert from Integer: 浮動小数点命令           |       |

|     | 8.3.9  | FMAC Floating point Multiply ACcumulate: 浮動小数点命令             |       |

|     | 8.3.10 | FMOV Floating point MOVe: 浮動小数点命令                            |       |

|     | 8.3.11 | FMUL Floating point MULtiply: 浮動小数点命令                        |       |

|     | 8.3.12 | FNEG Floating point NEGate: 浮動小数点命令                          |       |

|     | 8.3.13 | FSQRT Floating point SQuare RooT: 浮動小数点命令                    |       |

|     | 8.3.14 | FSTS Floating point STore from System register: 浮動小数点 命令     |       |

|     | 8.3.15 | FSUB Floating point SUBtract: 浮動小数点命令                        |       |

|     | 8.3.16 | FTRC Floating point TRuncate and Convert to integer: 浮動小数点命令 |       |

|     | 8.3.17 | LDS Load to FPU System register: FPU に関する CPU 命令             |       |

|     | 8.3.18 | STS STore from FPU System register: FPU に関する CPU 命令          |       |

| 8.4 |        | - 夕転送命令の説明 ( SH3-DSP のみ )                                    |       |

| 0.1 | 8.4.1  |                                                              | 0 171 |

|     | 8.4.1  | MOVS MOVe Single data between memory and dsp register:       | 0 177 |

|     | 0.43   | DSP データ転送命令                                                  |       |

|     | 8.4.2  | MOVX MOVe between X memory and dsp register: DSP データ転送命令     |       |

|     | 8.4.3  | MOVY MOVe between Y memory and dsp register: DSP データ転送命令     |       |

|     | 8.4.4  | NOPX No access OPeration for X memory: DSP データ転送命令           |       |

| 0.5 | 8.4.5  | NOPY No access OPeration for Y memory: DSP データ転送命令           |       |

| 8.5 |        | 算命令の説明                                                       |       |

|     | 8.5.1  | PABS ABSolute: DSP 算術演算命令                                    |       |

|     | 8.5.2  | [if cc] PADD ADDition with Condition: DSP 算術演算命令             |       |

|     | 8.5.3  | PADD PMULS ADDition & MULtiply Signed by Signed: DSP 算術演算命令  |       |

|     | 8.5.4  | PADDC ADDition with Carry: DSP 算術演算命令                        |       |

|     | 8.5.5  | [if cc] PAND logical AND: DSP 論理演算命令                         |       |

|     | 8.5.6  | [if cc] PCLR CLeaR: DSP 算術演算命令                               |       |

|     | 8.5.7  | PCMP CoMPare two data: DSP 算術演算命令                            | 8-210 |

|     |        |                                                              |       |

|      | 8.5.8  | [if cc] PCOPY COPY with Condition: DSP 算術演算命令                 | 8-212 |

|------|--------|---------------------------------------------------------------|-------|

|      | 8.5.9  | [if cc] PDEC DECrement by 1: DSP 算術演算命令                       | 8-215 |

|      | 8.5.10 | [if cc] PDMSB Detect MSB with Condition: DSP 算術演算命令           | 8-218 |

|      | 8.5.11 | [if cc] PINC INCrement by 1 with Condition: DSP 算術演算命令        |       |

|      | 8.5.12 | [if cc] PLDS LoaD System register: DSP システム制御命令               |       |

|      | 8.5.13 | PMULS MULtiply Signed by Signed: DSP 算術演算命令                   |       |

|      | 8.5.14 | [if cc] PNEG NEGate: DSP 算術演算命令                               |       |

|      | 8.5.15 | [if cc] POR logical OR: DSP 論理演算命令                            |       |

|      | 8.5.16 | PRND RouNDing: DSP 算術演算命令                                     |       |

|      | 8.5.17 | [if cc] PSHA SHift Arithmetically with Condition: DSP 算術シフト命令 |       |

|      | 8.5.18 | [if cc] PSHL SHift Logically with condition: DSP 論理シフト命令      |       |

|      | 8.5.19 | [if cc] PSTS STore System register: DSP システム制御命令              |       |

|      | 8.5.20 | [if cc] PSUB SUBtract with Condition: DSP 算術演算命令              |       |

|      | 8.5.21 | PSUBPMULS: SUBtraction & MULtiply Signed by Signed DSP 算術演算命令 |       |

|      | 8.5.22 | PSUBC SUBtract with Carry: DSP 算術演算命令                         |       |

|      | 8.5.23 | [if cc] PXOR logical eXclusive OR: DSP 論理演算命令                 | 8-255 |

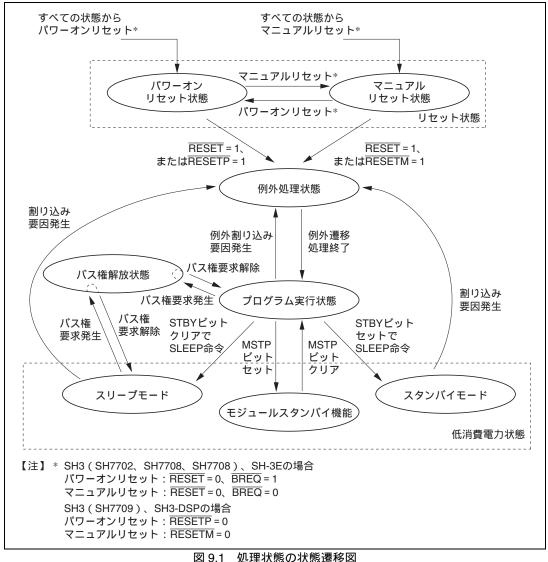

| 第9章  | 5 処理状  | 忧態                                                            |       |

| 9.1  | 処理状態   | <u> </u>                                                      | 9-1   |

|      | 9.1.1  | リセット状態                                                        | 9-2   |

|      | 9.1.2  | 例外処理状態                                                        | 9-2   |

|      | 9.1.3  | プログラム実行状態                                                     | 9-2   |

|      | 9.1.4  | 低消費電力状態                                                       | 9-2   |

|      | 9.1.5  | バス権解放状態                                                       | 9-2   |

| 9.2  | 低消費電   | [力状態                                                          | 9-3   |

|      | 9.2.1  | スリープモード                                                       | 9-3   |

|      | 9.2.2  | スタンバイモード                                                      |       |

|      | 9.2.3  | モジュールスタンバイ機能                                                  |       |

|      | 9.2.4  | ハードウェアスタンバイモード                                                |       |

| 笙 10 | 音 パイ   | プライン動作                                                        |       |

|      |        | テインの基本構成                                                      | 10.1  |

| 10.1 |        |                                                               |       |

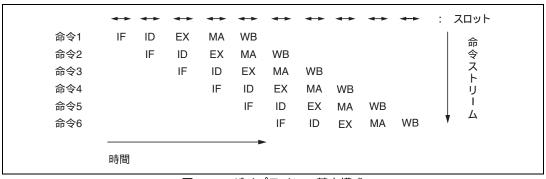

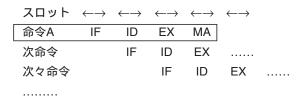

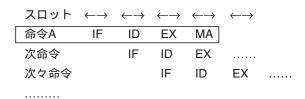

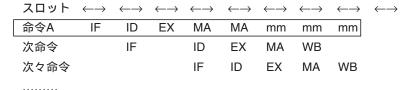

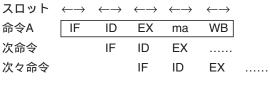

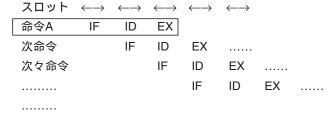

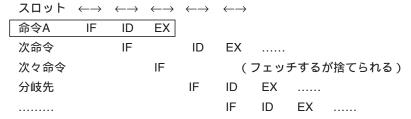

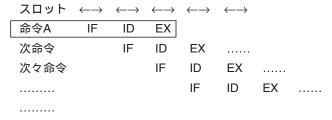

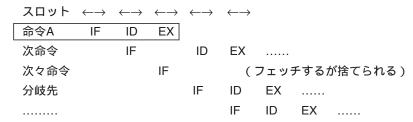

|      | 10.1.1 | 5 段パイプライン                                                     |       |

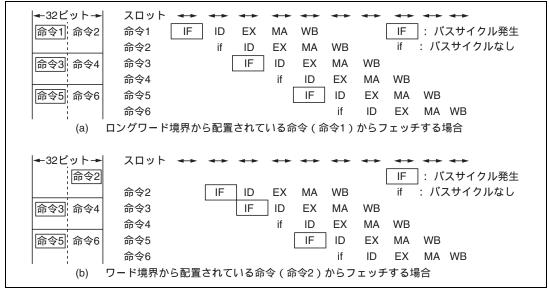

|      | 10.1.2 | スロットとパイプラインの流れ                                                |       |

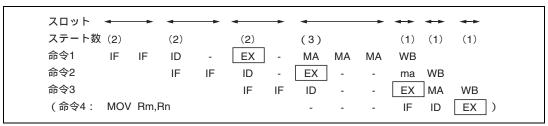

|      | 10.1.3 | 1 スロットの実行にかかるステート数                                            |       |

| 40.0 | 10.1.4 | _ 命令実行ステート数                                                   |       |

| 10.2 |        | 生                                                             |       |

|      | 10.2.1 | 命令フェッチ(IF)とメモリアクセス(MA)の競合                                     |       |

|      | 10.2.2 | メモリロード命令による競合                                                 |       |

|      | 10.2.3 | SR 更新命令による競合                                                  |       |

|      | 10.2.4 | 乗算器アクセスによる競合                                                  |       |

|      | 10.2.5 | FPU の競合 ( SH-3E のみ )                                          |       |

|      | 10.2.6 | DSP データ演算命令とストア命令の競合 ( SH3-DSP のみ )                           | 10-11 |

|      | 10.2.7 | DSP レジスタ間転送とメモリ・ロード / ストア動作の競合                                | 10.15 |

| 10.2 |        | (SH3-DSP のみ)                                                  |       |

| 10.3 | ノログラ   | ラミングの指針                                                       |       |

|      | 10.3.1 | 競合の種類と命令との対応                                                  | 10-13 |

|      | 10.3.2  | 命令実行速度の向上                 | 10-16 |

|------|---------|---------------------------|-------|

|      | 10.3.3  | ステート数                     | 10-16 |

| 10.4 | 各命令0    | Dパイプラインの動作                | 10-17 |

|      | 10.4.1  | データ転送命令                   | 10-27 |

|      | 10.4.2  | 算術演算命令                    |       |

|      | 10.4.3  | 論理演算命令                    | 10-35 |

|      | 10.4.4  | シフト命令                     | 10-38 |

|      | 10.4.5  | 分岐命令                      | 10-40 |

|      | 10.4.6  | システム制御命令                  | 10-44 |

|      | 10.4.7  | 例外処理                      | 10-55 |

|      | 10.4.8  | FPU 命令のパイプライン (SH-3E のみ ) | 10-58 |

|      | 10.4.9  | DSP データ転送命令 (SH3-DSP のみ ) | 10-60 |

|      | 10.4.10 | DSP 演算命令(SH3-DSP のみ)      | 10-64 |

| 付    | 録       |                           |       |

| A.   | 命令コー    | - F                       | 1     |

|      | A.1     | アドレッシングモード別命令セット          | 1     |

|      | A.2     | 命令形式別命令セット                | 15    |

|      | A.3     | オペレーションコードマップ             |       |

| B.   | パイプラ    | ライン動作と競合                  |       |

|      |         |                           |       |

### 1. 概要

### 1.1 SH-3 CPU の特長

SH-3、SH-3E、SH3-DSP の CPU は、RISC (Reduced instruction set computer ) タイプの命令セットを持っており、基本命令は 1 命令 1 ステート (1 システムクロックサイクル ) で動作するので、命令実行速度が飛躍的に向上しています。また内部 32 ビット構成を採用しておりデータ処理能力を強化しています。

SH-3、SH-3E、SH3-DSP CPU の特長を表 1.1 に示します。

表 1.1 SH-3 SH-3F SH3-DSP CPUの特長

|           | 表 1.1 SH-3、SH-3E、SH3-DSP CPU の特長                    |

|-----------|-----------------------------------------------------|

| 項目        | 特長                                                  |

| アーキテクチャ   | • ルネサス テクノロジオリジナルアーキテクチャ                            |

|           | ● 内部 32 ビット構成                                       |

| 汎用レジスタマシン | • 汎用レジスタ 32 ビット×16 本                                |

|           | (バンクレジスタ 32 ビット×8 本)                                |

|           | • コントロールレジスタ 32 ビット×5 本                             |

|           | ● システムレジスタ 32 ビット×4本 (SH-3)、                        |

|           | 32 ビット×6本 ( SH-3E )                                 |

| 命令セット     | • 命令長は 16 ビット固定長、これによるコード効率の向上                      |

|           | <ul><li>ロード・ストア・アーキテクチャ(基本/論理演算はレジスタ間で実行)</li></ul> |

|           | • 遅延分岐方式の採用で、分岐時のパイプラインの乱れを軽減                       |

|           | • C 言語指向の命令セット                                      |

| 命令実行時間    | • 基本命令は1命令/1ステート                                    |

| アドレス空間    | • 論理アドレス空間 最大 4G バイト                                |

| 乗算器内蔵     | <ul><li>32×32→64の乗算を2(~5)ステートで実行、</li></ul>         |

|           | 32×32+64→64 の積和演算を 2 ( ~5 ) ステートで実行                 |

| パイプライン    | • 5段パイプライン方式                                        |

| 処理状態      | <ul><li>リセット状態</li></ul>                            |

|           | • 例外処理状態                                            |

|           | • プログラム実行状態                                         |

|           | • 低消費電力状態                                           |

|           | • バス権解放状態                                           |

| 低消費電力状態   | • スリープモード                                           |

|           | • スタンバイモード                                          |

|           | • モジュールスタンバイ機能                                      |

### 1. 概要

| 項目            | 特長                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPU (SH-3Eのみ) | <ul> <li>単精度浮動小数点フォーマット</li> <li>IEEE754 規格のデータタイプのサプセット</li> <li>無効演算例外およびゼロによる除算例外(IEEE754 規格準拠)</li> <li>ゼロ方向への丸め処理(IEEE754 規格準拠)</li> <li>汎用レジスタファイル 32 ビット×16 の浮動小数点レジスタ</li> <li>基本命令 実行ピッチ:1 サイクル/レイテンシー:2 サイクル(FADD / FSUB / FMUL)</li> <li>FMAC(浮動小数点数積和演算)<br/>実行ビッチ:1 サイクル/レイテンシー:2 サイクル</li> <li>FDIV / FSQRT サポート</li> <li>FLDIO / FLDI1 (Load constant 0/1) サポート</li> </ul> |

### 1.2 SH3-DSP の特長

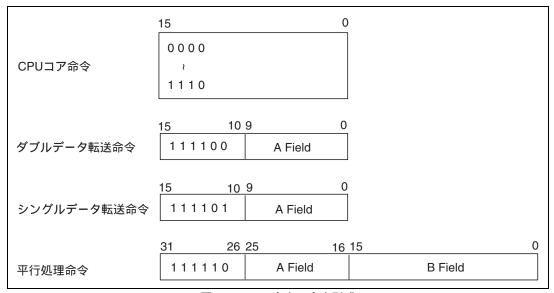

SH3 CPU は、16 ビット長のみの命令を持っています。SH3-DSP は基本的には同じ 16 ビット長の命令を持ち、DSP タイプの命令を並行処理するために、32 ビット長の DSP タイプの命令が追加されています。SH3 CPU は標準のノイマン型アーキテクチャですが、SH3-DSP は拡張ハーバード型アーキテクチャの DSP データバスを持っています。

SH3-DSP に追加された特長を表 1.2 に示します。

表 1.2 SH3-DSP の追加された特長

| 7.5        | 衣 1.2 3円3-D3F の足加された付支                            |

|------------|---------------------------------------------------|

| 項目         | 特長                                                |

| DSP ユニット   | ● 乗算器                                             |

|            | ● 算術演算器(ALU:Arithmetic Logic Unit)                |

|            | <b>●</b> バレルシフタ                                   |

|            | • DSP レジスタ                                        |

|            | ● MSB 検知                                          |

| 乗算器        | ● 16 ビット×16 ビット→32 ビット (符号付き固定小数点)                |

|            | ● 1 サイクル乗算器                                       |

| DSP レジスタ   | • 40 ビットデータレジスタ×2 本                               |

|            | • 32 ビットデータレジスタ×6 本                               |

|            | ● モジュロレジスタ (MOD、32 ビット ) をコントロールレジスタに追加           |

|            | • リピートカウンタ (RC)をステータスレジスタ (SR) に追加                |

|            | ● 繰り返し開始レジスタ (RS、32 ビット)、繰り返し終了レジスタ (RE、32 ビッ     |

|            | ト)をコントロールレジスタに追加                                  |

| DSP データパス  | ● 拡張ハーバード型アーキテクチャ                                 |

|            | <ul><li>● 2 つのデータバスおよび 1 つの命令バスを同時にアクセス</li></ul> |

| 内蔵メモリ      | • 16K バイト RAM                                     |

| 並行処理       | • 最大 4 つの並行処理                                     |

|            | ● ALU演算、乗算、および2つのロードまたはストア                        |

| アドレス演算器    | • 2つのアドレス演算器                                      |

|            | • 2つのメモリをアクセスするためのアドレス演算                          |

| DSP データ    | • インクリメント、デクリメントおよびインデクス                          |

| アドレッシングモード | <ul><li>それぞれモジュロアドレッシング付きまたはなし</li></ul>          |

| 繰り返し制御     | • ゼロオーバヘッド繰り返し(ループ)制御                             |

| 命令セット      | <ul><li>16 ビット長または32 ビット長</li></ul>               |

|            | - 16 ビット長(ロードまたはストアだけの場合)                         |

|            | - 32 ビット長 ( ALU 演算、乗算を含む場合 )                      |

|            | • DSP レジスタをアクセスする SH マイコン命令を追加                    |

| パイプライン     | • 5段パイプライン方式                                      |

|            | • 最後の第5ステージは WB ステージと DSP ステージ兼用                  |

|            | ·                                                 |

1-4

### 2. プログラミングモデル

### 2.1 概要

#### (1) 処理モード

処理モードにはユーザモードと特権モードの2つがあります。通常はユーザモードで動作し、例外が発生または割り込みを受け付けると特権モードになります。レジスタには、汎用レジスタ、システムレジスタ、コントロールレジスタがあり、アクセスできるレジスタはそれぞれの処理モードで異なります。

### (2) 汎用レジスタ

汎用レジスタには、R0 から R15 まで 16 本のレジスタがあります。汎用レジスタ R0 から R7 は、バンクレジスタで、処理モードで切り替えることができます。

特権モードのとき、ステータスレジスタ(SR)のレジスタバンクビット(RB)により、汎用レジスタとしてアクセスできるレジスタとできないレジスタが決められます。汎用レジスタとしてアクセスできないレジスタは、コントロールレジスタのロード命令(LDC)とストア命令(STC)でアクセスします。

RB ビットが 1 のとき、つまりバンク 1 が選ばれているとき、バンク 1 の汎用レジスタ  $R0\_BANK1$  から  $R7\_BANK1$  とバンクに関係ない R8 から R15 との合計 16 本のレジスタが汎用レジスタ R0 から R15 としてアクセスすることができ、バンク 0 の汎用レジスタ  $R0\_BANK0$  から  $R7\_BANK0$  の 8 本のレジスタは LDC/STC 命令でアクセスします。RB ビットが 0 のとき、つまりバンク 0 が選ばれているときは、バンク 0 の汎用レジスタ  $R0\_BANK0$  から  $R7\_BANK0$  とバンクに依存しない R8 から R15 との合計 16 本のレジスタが汎用レジスタ  $R0\_BANK1$  から R15 としてアクセスすることができ、バンク 1 の汎用レジスタ 16 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160 160

ユーザモードのときは、バンク 0 の汎用のレジスタ  $R0_BANK0$  から  $R7_BANK0$  とバンクに依存しない R8 から R15 との合計 16 本のレジスタが汎用レジスタ R0 から R15 としてアクセスすることができ、バンク 1 の汎用レジスタ  $R0_BANK1$  から  $R7_BANK1$  の 8 本のレジスタはアクセスできません。 SH3-DSP で DSP 拡張機能が有効なとき、DSP タイプの命令では、16 の汎用レジスタの内の 8 つのレジスタが X、Y データメモリおよび L バスを使うデータメモリ(シングルデータ)のアドレッシングに使われます。

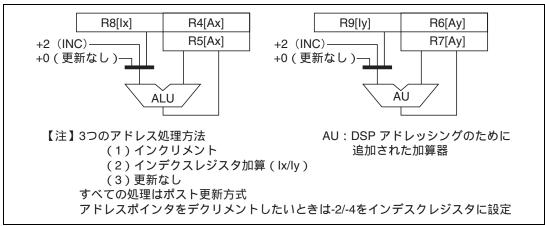

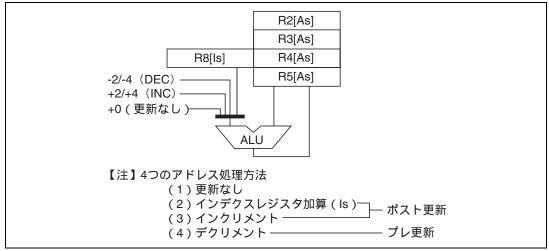

DSP タイプの命令は  $X \ge Y$  データメモリを同時にアクセスできます。 $X \ge Y$  データメモリのアドレスを指定するために、2 組のアドレスポインタがあります。

#### (3) コントロールレジスタ

コントロールレジスタには、処理モードで共通のグローバルベースレジスタ(GBR)とステータスレジスタ(SR)があり、特権モードのみアクセスできる退避ステータスレジスタ(SSR)、退避プログラムカウンタ(SPC)、ベクタベースレジスタ(VBR)があります。ステータスレジスタには、特権モードでのみアクセスできるビット(たとえばRBビット)があります。

#### (4) システムレジスタ

システムレジスタには、積和レジスタ(MACH/MACL)、プロシージャレジスタ(PR)、プログラムカウンタ(PC)あり、処理モードに関係しません。

#### (5) 浮動小数点レジスタと FPU に関するシステムレジスタ (SH-3E のみ)

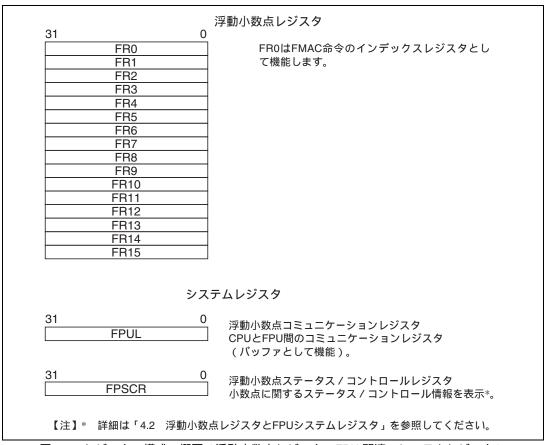

浮動小数点レジスタには FR0 から FR15 までの 16 本のレジスタがあります。これらは単精度浮動小数点数演算のソース / ディスティネーションレジスタとして使用します。

FPU に関するシステムレジスタには、浮動小数点コミュニケーションレジスタ (FPUL)と浮動小数点ステータス / コントロールレジスタ (FPSCR)があり、FPU-CPU 間の通信や例外処理の設定を行います。

処理モード別のレジスタ構成を図 2.1、図 2.2 に示します。FPU レジスタの詳細は「第 4 章 浮動 小数点演算ユニット」を参照してください。

| 31             | 0 |

|----------------|---|

| R0_BANK0*1, *2 |   |

| R1_BANK0*2     |   |

| R2_BANK0*2     |   |

| R3_BANK0*2     |   |

| R4_BANK0*2     |   |

| R5_BANK0*2     |   |

| R6_BANK0*2     |   |

| R7_BANK0*2     |   |

| R8             |   |

| R9             |   |

| R10            |   |

| R11            |   |

| R12            |   |

| R13            |   |

| R14            |   |

| R15            |   |

| 31 |        | 0 |

|----|--------|---|

|    | FR0*3  |   |

|    | FR1*3  |   |

|    | FR2*3  |   |

|    | :      |   |

|    | FR15*3 |   |

| L SR    |  |

|---------|--|

| FPSCR*3 |  |

| GBR    |

|--------|

| MACH   |

| MACL   |

| FPUL*3 |

| PR     |

| PC |  |

|----|--|

- 【注】\*1 R0レジスタは、インデックス付きレジスタ間接アドレッシングモードと インデックス付きGBR間接アドレッシングモードのインデックスレジス タとして使われます。命令によってはソース / ディスティネーションレ ジスとして使用できるのがR0レジスタのみというものもあります。

- \*2 R0~R7はバンクレジスタで、ユーザモード時はバンク0が使用されます。

- \*3 これらのレジスタはSH-3Eにのみ存在し、浮動小数点数演算に使用されます。 FRO~FR15、FPSCR、FPULについての詳細は、「第4章 浮動小数点演算 ユニット」を参照してください。

図 2.1 ユーザモード時のプログラミングモデル

| 3                                               | 31 0                                 | 31 0               |   |  |

|-------------------------------------------------|--------------------------------------|--------------------|---|--|

|                                                 | R0_BANK1*1, *2                       | R0_BANK0*1, *2     |   |  |

|                                                 | R1_BANK1*2                           | R1_BANK0*2         |   |  |

|                                                 | R2_BANK1*2                           | R2_BANK0*2         |   |  |

|                                                 | R3_BANK1*2                           | R3_BANK0*2         |   |  |

|                                                 | R4_BANK1*2                           | R4_BANK0*2         |   |  |

|                                                 | R5_BANK1*2                           | R5_BANK0*2         |   |  |

|                                                 | R6_BANK1*2                           | R6_BANK0*2         |   |  |

|                                                 | R7_BANK1*2                           | R7_BANK0*2         |   |  |

|                                                 | R8                                   | R8                 |   |  |

| <br>                                            | R9                                   | R9                 |   |  |

| <del> </del>                                    | R10                                  | R10                |   |  |

|                                                 | R11                                  | R11                |   |  |

|                                                 | R12                                  | R12                |   |  |

|                                                 | R13                                  | R13                |   |  |

|                                                 | R14                                  | R14                |   |  |

|                                                 | R15                                  | R15                |   |  |

|                                                 |                                      |                    |   |  |

| Г                                               | FR0*4                                | FR0*4              |   |  |

| T                                               | FR1*4                                | FR1*4              |   |  |

| T                                               | FR2*4                                | FR2*4              |   |  |

|                                                 |                                      |                    |   |  |

|                                                 | :                                    |                    |   |  |

|                                                 | :                                    | :                  |   |  |

|                                                 | FR15*4                               | FR15               |   |  |

| _                                               |                                      |                    |   |  |

| 3                                               | 31 0                                 | 31 0               |   |  |

|                                                 | SR                                   | SR                 |   |  |

|                                                 | SSR                                  | SSR                |   |  |

|                                                 | FPSCR*4                              | FPSCR*4            |   |  |

|                                                 |                                      |                    |   |  |

| _                                               |                                      |                    |   |  |

|                                                 | GBR                                  | GBR                |   |  |

|                                                 | MACH                                 | MACH               |   |  |

|                                                 | MACL                                 | MACL               |   |  |

|                                                 | FPUL*4                               | FPUL*4             |   |  |

|                                                 | PR                                   | PR                 |   |  |

|                                                 | VBR                                  | VBR                |   |  |

| _                                               | DC                                   | DC.                |   |  |

|                                                 | PC<br>CDC                            | PC                 |   |  |

| L                                               | SPC                                  | SPC                |   |  |

|                                                 |                                      |                    |   |  |

|                                                 | R0_BANK0*1, *3                       | R0_BANK1*1, *3     |   |  |

| 1                                               | R1_BANK0*3                           | R1_BANK1*3         |   |  |

|                                                 | R2_BANK0*3                           | R2_BANK1*3         |   |  |

|                                                 | R3_BANK0*3                           | R3_BANK1*3         |   |  |

|                                                 | R4_BANK0*3                           | R4_BANK1*3         |   |  |

|                                                 | R5_BANK0*3                           | R5_BANK1*3         |   |  |

| 1                                               | R6_BANK0*3                           | R6_BANK1*3         |   |  |

|                                                 | R7_BANK0*3                           | R7_BANK1*3         |   |  |

|                                                 | (b)特権モードのレジスタ構成                      | (c)特権モードのレジスタ構成    |   |  |

|                                                 | (RB=1)                               | (RB=0)             |   |  |

|                                                 | -                                    | -                  |   |  |

| r s-                                            | t】*1 B0レジスタけ インデック                   | 7.7.付きしジスタ問炷アドレッシン | グ |  |

| 【注】*1 R0レジスタは、インデックス付きレジスタ間接アドレッシング             |                                      |                    |   |  |

| モードとインデックス付きGBR間接アドレッシングモードのインデックスしぶてのトレス使われます。 |                                      |                    |   |  |

| ンデックスレジスタとして使われます。                              |                                      |                    |   |  |

| *2 R0~R7レジスタはパンクレジスタで、特権モード時には、SRレ              |                                      |                    |   |  |

| ジスタのRBビットでどちらのパンクかを決めます。                        |                                      |                    |   |  |

| 0のときバンク0                                        |                                      |                    |   |  |

| 1のときバンク1                                        |                                      |                    |   |  |

|                                                 | *3 LDC/STC命令でのみアクセスされます。SRレジスタのRBピット |                    |   |  |

|                                                 | でどちらのパンクかを決めます。                      |                    |   |  |

|                                                 | 0のときパンク1                             |                    |   |  |

| 1のときパンク0                                        |                                      |                    |   |  |

| *4 これらのレジスタはSH-3Eにのみ存在し、浮動小数点演算に使用              |                                      |                    |   |  |

|                                                 |                                      |                    | m |  |

|                                                 |                                      | PSCR、FPULについての詳細は、 |   |  |

|                                                 | · 弗4早 净 別小                           | 1ニット」を参照してください。    |   |  |

|                                                 |                                      |                    |   |  |

図 2.2 特権モード時のレジスタ構成

#### (6) DSP レジスタと DSP に関するコントロールレジスタ (SH3-DSP のみ)

DSP ユニットには DSP レジスタとして 8 つのデータレジスタと 1 つのコントロールレジスタがあります。

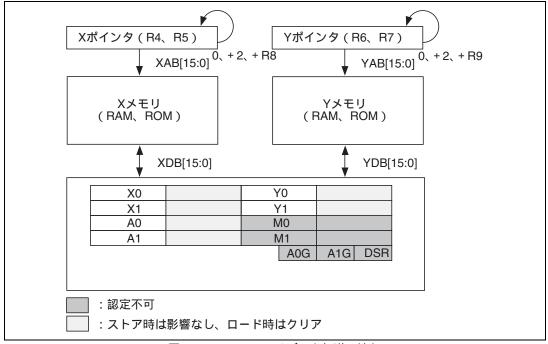

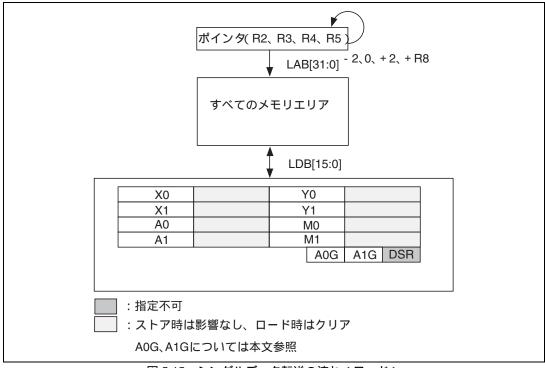

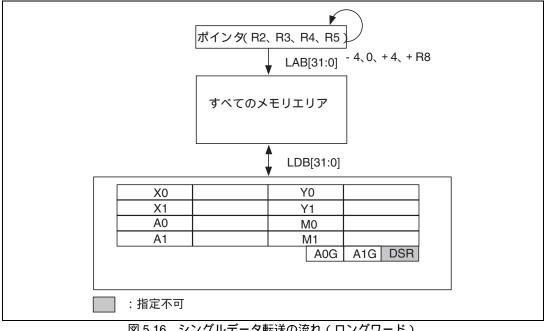

DSP データレジスタは 2 本の 40 ビット長の A0、A1 レジスタと、6 本の 32 ビット長の M0、M1、X0、X1、Y0、Y1 レジスタがあります。 <math>A0、A1 レジスタには、それぞれ 8 ビットのガードビット、A0G、A1G があります。

DSP データレジスタは、DSP 命令のオペランドとして DSP データのデータ転送、データ処理に使われます。DSP データレジスタをアクセスする命令には、DSP データ処理、X、Y データ転送処理、の 3 つのタイプがあります。

コントロールレジスタは 32 ビット長の DSP ステータスレジスタ (DSR: DSP status register)で、演算結果を表します。DSR レジスタには演算結果を表すビット、符号付き大ビット (GT: Signed greater than )、ゼロビット(Z: Zeo value )、負値ビット(N: Negative value )、オーバフロービット(V: overflow )、DSP 状態ビット (DC: DSP condition ) と、DC ビットの設定を制御する状態選択ビット (CS: Condition select ) があります。

DC ビットは状態フラグの一つを表し、SuperH マイコン CPU コアの T ビットとよく似ています。 条件付き DSP タイプ命令の場合、DSP データ処理は、DC ビットに従って実行が制御されます。この 制御は DSP ユニットでの実行にだけ関係し、DSP レジスタだけが更新されます。アドレス計算や、 ロード / ストア命令などの SuperH マイコンの CPU コアの実行命令には関係しません。コントロール ビット CS (ビット 2 から 0) は DC ビットを設定する状態を指定します。

DSP タイプ命令には、無条件 DSP タイプ命令と条件付き DSP タイプ命令があります。無条件 DSP タイプのデータ処理は、PMULS、MOVX、MOVY、MOVS 命令を除いて、状態ビットと DC ビットを更新します。条件付き DSP タイプ命令は DC ビットの状態によって実行されますが、実行された場合も実行されない場合も DSR レジスタは更新されません。

DSP レジスタを図 2.3 に示します。DSR レジスタのビットの機能を表 2.1 に示します。

| 39 32 | ,31 O                                       |                      |

|-------|---------------------------------------------|----------------------|

| A0G   | A0                                          | DSPデータレジスタ           |

| A1G   | A1                                          |                      |

|       | MO                                          |                      |

|       | M1                                          |                      |

|       | X0                                          |                      |

|       | X1                                          |                      |

|       | Y0                                          |                      |

|       | Y1                                          |                      |

|       |                                             |                      |

|       | 31 8 7 6 5 4 3 2 1 0<br>GT Z N V CS[2:0] DC | DSPステータスレジスタ ( DSR ) |

図 2.3 DSP レジスタの構成

| ビット    | 名称(略称)         | 機能                                   |

|--------|----------------|--------------------------------------|

| 31 ~ 8 | 予約ビット          | 0:常に0が読み出されます                        |

|        |                | 書き込む値も0にしてください。                      |

| 7      | 符号付き大ビット       | 演算結果が正(ゼロをのぞく)、またはオペランド1がオペランド2より大き  |

|        | (GT)           | いことを示します。                            |

|        |                | 1:演算結果が正、またはオペランド1がオペランド2より大きい       |

| 6      | ゼロビット(Z)       | 演算結果がゼロ(0)、またはオペランド1がオペランド2と等しいことを示  |

|        |                | します。                                 |

|        |                | 1:演算結果がゼロ(0)、または等しい                  |

| 5      | 負値ビット(N)       | 演算結果が負、またはオペランド1がオペランド2より小さいことを示します。 |

|        |                | 1:演算結果が負、またはオペランド 1 がオペランド 2 より小さい   |

| 4      | オーバフロービット      | 演算結果がオーバフローしたことを示します。                |

|        | (V)            | 1:演算結果がオーバフロー                        |

| 3~1    | 状態選択ビット(CS)    | DC ビットに設定する演算結果状態を選択するためのモードを指定します。  |

|        |                | 110、111 は指定しないでください。                 |

|        |                | 000:キャリ/ボローモード                       |

|        |                | 001:負値モード                            |

|        |                | 010:ゼロモード                            |

|        |                | 011:オーバフローモード                        |

|        |                | 100:符号付き大モード                         |

|        |                | 101:符号付き以上モード                        |

| 0      | DSP 状態ビット (DC) | CS ビットで指定されたモードで演算結果の状態を設定します。       |

|        |                | 0:指定されたモードの状態が成立しない(不成立)             |

|        |                | 1:指定されたモードの状態が成立                     |

表 2.1 DSR レジスタのビット

DSR レジスタは CPU コア命令ではシステムレジスタとして取り扱われます。DSR レジスタとのデータ転送は次のようにロード / ストア命令があります。

STS DSR,Rn;

STS.L DSR,@-Rn;

LDS Rn,DSR;

LDS.L @Rn+,DSR;

A0、X0、X1、Y0、Y1 レジスタも CPU コア命令ではシステムレジスタとして取り扱われます。 DSP に関するコントロールレジスタには、繰り返し開始レジスタ (RS: Repeat start register)、繰り返し終了レジスタ (RE: Repeat end register)、モジュロレジスタ (MOD: Modulo register) の 3 本があります。

RS レジスタと RE レジスタはプログラムの繰り返し (ループ) を制御するために使います。SR レジスタの繰り返しカウンタ (RC: Repeat counter) に繰り返し回数を指定し、RS レジスタに繰り返し開始アドレスを指定し、RE レジスタに繰り返し終了アドレスを指定します。ただし、RS レジスタと RE レジスタに格納されるアドレスの値は、繰り返しの物理的な開始アドレス、終了アドレスとは値が必ずしも同じとは限りません。

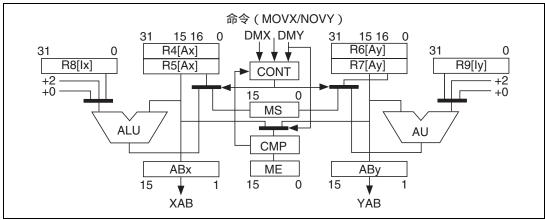

MOD レジスタは繰り返しデータのバッファリングのためのモジュロアドレッシングに使います。 SR レジスタの DMX または DMY でモジュロアドレッシングの指定をし、MOD レジスタの上位 16 ビットにモジュロ終了アドレス (ME) を指定し、下位 16 ビットにモジュロ開始アドレス (MS) を指定します。なお、DMX と DMY ビットは同時にモジュロアドレッシングを指定することはできません。モジュロアドレッシングは 16 X、Y データ転送命令 (MOVX、MOVY) のとき可能です。シング

ルデータ転送命令 (MOVS) ではできません。 図 2.5 にコントロールレジスタを示します。

#### 汎用レジスタ 2.2

汎用レジスタの構成を図2.4に示します。

| ( |

|---|

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

R12 R13 R14 R15 0 汎用レジスタ

リセット後は不定になります。

31

04

### FR0\*3 FR1\*3 FR2\*3 FR3\*3 FR4\*3 FR5\*3 FR6\*3 FR7\*3 FR8\*3 FR9\*3 FR10\*3 FR11\*3 FR12\*3 FR13\*3 FR14\*3 FR15\*3

0 浮動小数点データレジスタ

FMAC命令では、FR0を乗数値の設定に使用します。

- 【注】\*1 R0レジスタは、インデックス付きレジスタ間 接アドレッシングモードとインデックス付き GBR間接アドレッシングモードのインデック スレジスタとして使われます。ある命令で は、R0だけがソースレジスタ、デスティネー ションレジスタになります。

- \*2 R0~R7レジスタはバンクレジスタです。 特権モードでは、どちらのバンク(R0\_ BANK0~R7\_BANK0またはR0\_BANK1~ R7\_BANK1)を汎用レジスタとしてアクセス するかをSRレジスタのRBビットで決めます。

- \*3 これらのレジスタはSH-3Eにのみ存在し、浮 動小数点演算に使用されます。FR0~FR15に ついての詳細は、「第4章 浮動小数点演算 ユニット」を参照してください。

- \*4 SH3-DSPでDSP命令拡張機能が有効のとき、 DSP命令でメモリアドレスレジスタ、インデ ックスレジスタとして使われます。

図 2.4 レジスタの構成の概要(汎用レジスタ)

アセンブラでは R2、R3、...、R9 の記号名 (シンボル) を使います。もし DSP タイプの命令のためのレジスタの役割を明示した名前にしたいときは、レジスタの別名 (エイリアス、alias) を使います。アセンブラで次のように書きます。

Ix: .REG (R8)

名前 Ix が R8 の別名になります。そのほか次のように別名を付けます。

Ax0: .REG (R4)

Ax1: .REG (R5)

Ix: .REG (R8)

Ay0: .REG (R6)

Ay1: .REG (R7)

Ix: .REG (R9)

As0: .REG (R4); これはシングルデータ転送のために別名が必要なときの定義です。

As1: .REG (R5); これはシングルデータ転送のために別名が必要なときの定義です。

As2: .REG (R2); これはシングルデータ転送のために別名が必要なときの定義です。

As3: .REG (R3); これはシングルデータ転送のために別名が必要なときの定義です。 Is: .REG (R8); これはシングルデータ転送のために別名が必要なときの定義です。

### 2.3 コントロールレジスタ

コントロールレジスタの構成を図 2.5 に示します。

```

退避ステータスレジスタ (SSR)

例外発生時にSRレジスタの内容を格納し

例外処理ルーチンから命令の流れに戻るための

処理状態を表示。

SSR

リセット後は不定です。

退避プログラムカウンタ(SPC)

例外発生時にPCレジスタの内容を格納し

例外処理が終了したときの戻りアドレスを表示。

リセット後は不定です。

SPC

グローバルベースレジスタ(GBR)

GBR開接アドレッシングモードのベースアドレスを格納し

GBR開接アドレッシングモードは内蔵周辺モジュールの

レジスタ領域のデータ転送および論理演算に使われます。

GBRレジスタはユーザモードでもアクセスできます。

リセットを化する定ちで

GBB

リセット後は不定です。

ベクタベースレジスタ (VBR)

例外処理ベクタ領域のベースアドレスを格納。

リセットでH'00000000に初期化されます。

VBR

繰り返し開始レジスタ (RS)

31

RF

繰り返し終了レジスタ (RE)

31

1615

モジュロレジスタ (MOD)

ME

ME:モジュロ終了アドレス ( Modulo End Address )

MS: モジュロ開始アドレス (Modulo Start Address)

【記号説明】

処理モードビット。

処理モードを表示します。

1のとき特権モード、0のときユーザモード。

例外、割り込みが発生すると1になります。

リセットで1に初期化されます。

レジスタパンクビット。

RO-RTレジスタはパンクレジスタです。

特権モードで使用する3ル用レジスタRO-R7のパンクを決めます。

1のときRO BANK1-R7 BANK1とR8-R15が汎用レジスタになり、

RO BANK0-R7 BANK0はLOC/STC命令でアクセスできます。

0のときRO BANK0-R7 BANK0はCR8-R15が汎用レジスタになり、

RO BANK1-R7 BANK1はLDC/STC命令でアクセスできます。

例外、割り込みが発生すると1になります。

MD:

RB:

UUJ と音化し多れ以口・ドノ BANK1はLDC/ST CS 令でアクセスできます。

例外、割り込みが発生すると1になります。

リセットで1に初期化されます。

日と: プロックビット。

にのとき、例外、割り込みの発生を抑止します。

詳細は、第5章例外処理を参照してください。

のときは、例外、割り込みみを受け付けます。

例外、割り込みが発生すると1になります。

リセットで1の場所となります。

リセットの1のときに、例外、割り込みを受け付けます。

リンシャンに対別化されます。

リンシャンに対別化されます。

リンシャンに対別化されます。

リントランタ・繰り返し(ループ)制御の繰り返し回数を指定します(2~4095)。

DSPではフェートが1のとうとのようでは、1: ソメモリアドレスポインタ、Ay (R6、R7)に対し、モジュロアドレッシング指定。1: ソメモリアドレスポインタ、Ay (R6、R7)に対し、モジュロアドレッシングモードが有効になります。

DMX: スポインタ用モジュロアドレッシングモドが有効になります。

コンムシャンでモードが有効になります。

別込みマスクビット。割り込みマスクビット。割り込みマスクビット。割り込みマスクビット。割り込みマスクビット。割り込みマスクビット。割り込みマスクビット。割り込みアスクレベルを表す4ビットデータです。割り込みが発生しても、割り込みアプ付けレベルに変化しません。

Sビット

RF1, 0:

Tビット・

[注]

M、Q、S、Tビットはユーザモードで専用命令によってセット / クリアが可能です。

リセット後は不定です。

他のビットはすべて特権モードで読み出し、書き込みが可能です。

*: SH3-DSP以外では0になります。

```

図 2.5 レジスタの構成の概要(コントロールレジスタ)

### 2.4 システムレジスタ

システムレジスタの構成を図 2.6 に示します。 システムレジスタは LDS / STS 命令でアクセスします。

| システムレジスタ                                      |                                                                                          |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| MACH MACL                                     | 積和上位、下位レジスタ(MACH/L)<br>乗算、積和演算の結果を格納。<br>リセット後は不定になります。                                  |  |  |  |

| 31 0<br>FPUL*                                 | 浮動小数点コミュニケーションレジスタ(FPUL)<br>CPUとFPU間のコミュニケーションレジスタと<br>してバッファの役割をもちます。<br>リセット後は不定になります。 |  |  |  |

| 31 0<br>PR                                    | プロシージャレジスタ(PR)<br>サブルーチンプロシージャから戻り先アドレスを格納。<br>リセット後は不定になります。                            |  |  |  |

| 31 0<br>PC                                    | プログラムカウンタ(PC)<br>現在実行中の命令の開始アドレスの4番地(2命令)先を表示。<br>リセットでH'A000 0000に初期化されます。              |  |  |  |

| 31 0 FPSCR*                                   | 浮動小数点ステータス/コントロールレジスタ(FPSCR)<br>浮動小数点演算のステータスの格納、および情報制御を行います。<br>リセット後は不定になります。         |  |  |  |

| 【注】FPUL、FPSCRについては「第4章 浮動小数点演算ユニット」を参照してください。 |                                                                                          |  |  |  |

図 2.6 システムレジスタの構成

### 2.5 レジスタの初期値

リセット後のレジスタの値を表 2.2 に示します。

表 2.2 レジスタの初期値

| 区分         | レジスタ                                                     | 初期値                                                                                 |

|------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|

| 汎用レジスタ     | R0 ~ R15                                                 | 不定                                                                                  |

|            | FR0 ~ FR15*1                                             | 不定                                                                                  |

| コントロールレジスタ | SR                                                       | 13~  10 は 1111(H'F)、MD は 1、RB は 1、BL は 1、RC、DMY、DMX は 0(SH3-DSP のみ)、予約ビットは 0、その他は不定 |

|            | GBR                                                      | 不定                                                                                  |

|            | VBR                                                      | H'0000 0000                                                                         |

|            | SSR、SPC                                                  | 不定                                                                                  |

|            | RS* <sup>2</sup> 、RE* <sup>2</sup>                       | 不定                                                                                  |

|            | MOD*2                                                    | 不定                                                                                  |

| システムレジスタ   | MACH、MACL、PR、<br>FPSCR* <sup>1</sup> 、FPUL* <sup>1</sup> | 不定                                                                                  |

|            | PC                                                       | H'A000 0000                                                                         |

| DSP レジスタ*² | A0、A0G、A1、A1G、M0、<br>M1、X0、X1、Y0、Y1                      |                                                                                     |

|            | DSR                                                      | H'0000 0000                                                                         |

<sup>【</sup>注】 \*1 これらのレジスタは、SH-3E のみ存在し、浮動小数点演算に使用されます。 FR0~FR15、FPSCR、FPULについての詳細は、「4.2 浮動小数点レジスタと FPU システムレジスタ」を参照してください。

\*2 これらのレジスタは、SH3-DSP にのみ存在します。

# 3. データ形式

## 3.1 レジスタのデータ形式

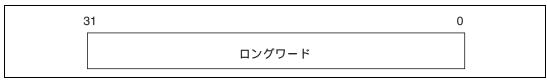

レジスタオペランドのデータサイズは常にロングワード (32 ビット) (図 3.1) です。メモリ上のデータをレジスタへロードするとき、メモリオペランドのデータサイズがバイト (8 ビット)、もしくはワード (16 ビット) の場合は、ロングワードに符号拡張し、レジスタに格納します。

図 3.1 ロングワードオペランド

## 3.2 メモリ上でのデータ形式

バイト、ワード、ロングワードのデータ形式があります。

ワードオペランドはワード境界(2バイト刻みの偶数番地)から、ロングワードオペランドはロングワード境界(4バイト刻みの偶数番地)からアクセスしてください。これを守らない場合には、アドレスエラーになります。バイトはどの番地からでもアクセスできます。

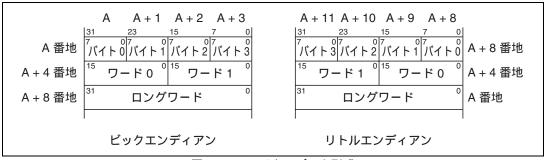

データフォーマットは、ビックエンディアン、またはリトルエンディアンのバイト順を選択可能です。パワーオンリセット時に外部ピン(MD5 ピン)で設定してください。MD5 ピンがローレベルの場合ビックエンディアンに、MD5 ピンがハイレベルの場合リトルエンディアンに設定されます。エディアンは動的には変更できません。ただしビット位置は常に最上位(most-significant)から最下位(least- significant)へ左から右へ減少するように番号が付けられています。すなわち 32 ビットのロングワードでは、一番左のビット、ビット 31 が最上位ビットで、一番右のビット、ビット 0 が最下位ビットです。

メモリ上のデータ形式を図 3.2 に示します。リトルエンディアンモードのときは、バイト長 (8 ビット)で書き込んだデータはバイト長で読み出してください。ワード長 (16 ビット)で書き込んだデータはワード長で読み出してください。

図 3.2 メモリ上のデータ形式

## 3.3 イミディエイトデータのデータ形式

バイトのイミディエイトデータは命令コードの中に配置します。

MOV、ADD、CMP/EQ 命令ではイミディエイトデータを符号拡張後、レジスタとロングワードで演算します。一方、TST、AND、OR、XOR 命令ではイミディエイトデータをゼロ拡張後、ロングワードで演算します。したがって、AND 命令でイミディエイトデータを用いると、デスティネーションレジスタの上位 24 ビットは常にクリアされます。

ワードとロングワードのイミディエイトデータは命令コードの中に配置せず、メモリ上のテーブルに配置します。メモリ上のテーブルは、ディスプレースメント付き PC 相対アドレッシングモードを使ったイミディエイトデータのデータ転送命令(MOV)で、参照します。

具体例については、「6.1.8 イミディエイトデータ」を参照してください。

## 3.4 DSP タイプデータ形式 (SH3-DSP のみ )

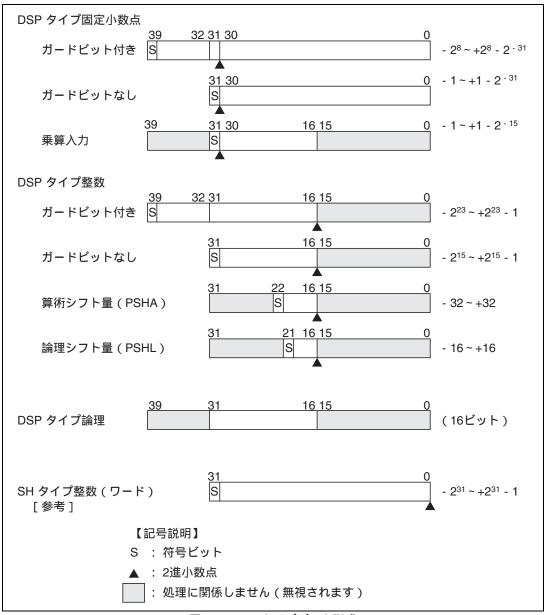

SH3-DSP には命令に対応して 3 つの異なるデータ形式があります。固定小数点データ形式、整数データ形式、論理データ形式です。

DSP タイプの固定小数点データ形式はビット 31 とビット 30 の間に 2 進小数点があります。ガードビット付き、ガードビットなし、乗算入力の 3 種類があり、それぞれ有効ビット長と表せる値の範囲が異なります。

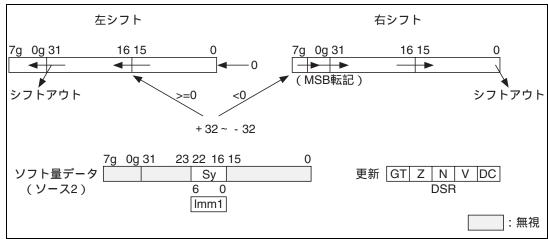

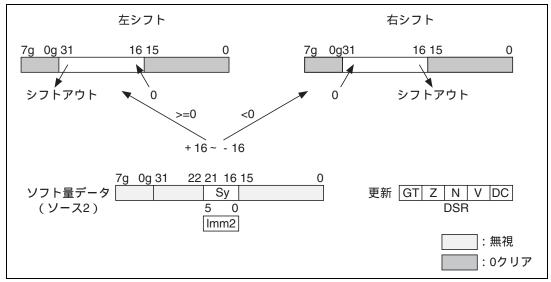

DSP タイプの整数データ形式はビット 16 とビット 15 の間に 2 進小数点があります。ガードビット付き、ガードビットなし、シフト量の 3 種類があり、それぞれ有効ビット長と表せる値の範囲が異なります。算術シフト (PSHA)のシフト量は 7 ビットの領域で  $-64 \sim +63$  までを表せますが、実際に有効なのは  $-32 \sim +32$  までの値です。同様に論理シフトのシフト量は 6 ビットの領域ですが、実際に有効なのは  $-16 \sim +16$  までの値です。

DSP タイプの論理データ形式は小数点がありません。

データ形式とデータの有効な長さは命令と DSP レジスタによって決まります。

3 つの DSP タイプのデータ形式とその 2 進少数点の位置、および参考として SH タイプのデータ形式を図 3.3 に示します。

図 3.3 DSP タイプデータ形式

# 4. 浮動小数点演算ユニット (SH-3E のみ)

## 4.1 概要

SH-3E は、浮動小数点演算ユニット (FPU) を内蔵しています。FPU のレジスタ構成を図 4.1 に示します。

図 4.1 レジスタの構成の概要 (浮動小数点レジスタ、FPU 関連のシステムレジスタ)

## 4.2 浮動小数点レジスタと FPU システムレジスタ

## 4.2.1 浮動小数点レジスタ

SH-3E は 16 本の 32 ビット単精度浮動小数点レジスタをもっています。レジスタ指定は常に 4 ビットで行います。アセンブリ言語では、浮動小数点レジスタは、FR0、FR1、FR2、・・・などのように指定します。FR0 は FMAC 命令のインデックスとして機能します。

## 4.2.2 浮動小数点コミュニケーションレジスタ (FPUL)

FPU と CPU 間で転送される情報は、整数ユニットの MACL、MACH に類似した 1 本のコミュニケーションレジスタ FPUL を介して転送されます。整数形式と浮動小数点形式とは異なるため、SH-3Eではこのコミュニケーションレジスタを設けています。32 ビット FPUL はシステムレジスタで、CPU側からは LDS、STS 命令によりアクセスされます。

## 4.2.3 浮動小数点ステータス/コントロールレジスタ(FPSCR)

SH-3E は、浮動小数点ステータス/コントロールレジスタ(FPSCR)を備えており、このレジスタは、LDS、STS 命令によりアクセスするシステムレジスタとして機能します(図 4.2)。FPSCR は、ユーザプログラムによる書き込みが可能です。FPSCR は、プロセスコンテキストの一部であり、コンテキスト切り替え時にはセーブする必要があります。また、プロシジャコール時にも、セーブする必要がある場合があります。

FPSCR は、32 ビットのレジスタで、丸めモード、非正規化数の扱い方、および FPU 例外に関する詳細制御情報を示します。

SH-3Eでは、これらの扱いに関しては以下のモードのみサポートします。

- 丸めモード:0方向への丸めモードのみサポート

- 非正規化数の取り扱い: 非正規化数がソースまたはデスティネーションオペランドにある場合、この値は常に0とみなされます。

- FPU 例外:

ゼロ除算例外 ( Divide by Zero : Z )

無効演算例外 (Invalid: V) をサポートします。

| 31  | 19 | 18 | 17 | 1615 | 14 |   | 12 11 10  | 9 | 7   | 7 6 | 5   | 4 |   | 2 | 1 | 0 |

|-----|----|----|----|------|----|---|-----------|---|-----|-----|-----|---|---|---|---|---|

|     |    |    |    | 要因   |    |   | イネー<br>ブル |   |     | J   | ラグ  |   |   |   |   |   |

| 0 — | 0  | 1  | 0  | cvcz | 0  | 0 | 0 EV EZ   | 0 | 0 0 | ) F | /FZ | 0 | 0 | 0 | 0 | 1 |

#### 【記号説明】

CV: 無効演算要因ビット

1:現在の命令実行中に無効演算例外が発生したことを示します。

0:無効演算例外が発生していないことを示します。

CZ: ゼロ除算要因ビット

1:現在の命令実行中に0による除算例外が発生したことを示します。

0:0による除算例外が発生していないことを示します。

EV: 無効演算例外イネーブルビット

1:無効演算例外の発生を許可

0:無効演算例外は発生を許可せず、結果としてqNaNを返します。

EZ: ゼロ除算例外イネーブルビット

1:0による除算例外の発生を許可

0:0による除算例外の発生を許可せず、結果としてqNaNを返します。

FV: 無効演算例外フラグビット

1:命令の実行中に無効演算例外が発生したことを示します。

0:無効演算例外は発生していないことを示します。

FZ: ゼロ除算例外フラグビット

1:命令の実行中に0による除算例外が発生したことを示します。

0:0による除算例外は発生していないことを示します。

上記ビット以外の各ビットはすべて図のように予約されており、この値はLDS命令でも書き換えることはできません。

図 4.2 浮動小数点ステータス / コントロールレジスタ

要因フィールド中のビットは、そのとき実行中の命令の例外要因を示します。要因ビットは浮動小数点命令によって変更されます。これらのビットは、単一の命令の実行期間中に例外状態が発生するか否かにより、"1"または"0"になります。

イネーブルフィールド中のビットは、イネーブルにする例外の種類を指定します。すなわち例外処理に流れを変更することを可能にします。イネーブルビットと対応する要因ビットが、そのとき実行中の命令よりセットされれば、例外が発生します。

フラグフィールド中のビットは一連の命令の実行中に発生したすべての例外を、累積して格納するのに使用されます。

これらのビットは、いったん命令によってセットされると、その後の命令によってリセットされません。このフィールド中のビットは、FPSCRに対して明示的にストア動作を行うことによってのみ、リセットすることができます。

浮動小数点例外取扱の詳細は「4.4 浮動小数点例外モデル」を参照してください。

## 4.3 浮動小数点フォーマット

### 4.3.1 浮動小数点数フォーマット

SH-3E は単精度浮動小数点演算をサポートしています。浮動小数点フォーマットは IEEE754 浮動 小数点規格完全準拠です。

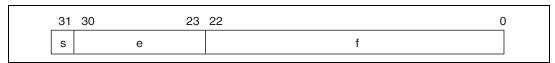

浮動小数点数は、次の3つのフィールドにより構成されます。

- 符号部 s

- 指数部 e

- 仮数部 f

指数はバイアスされます。すなわち、

e=E+bias

の形式をとります。

バイアスされていない指数 E の範囲は、 $E_{min}$ -1 から  $E_{max}$ +1 となります。2 つの値( $E_{min}$ -1 と  $E_{max}$ +1)は以下のように識別されます。 $E_{min}$ -1 は、ゼロ(符号は正負の双方とも)および非正規化数を表し、 $E_{max}$ +1 は、正負の無限大および非数(NaN:Not a Number)を表します。単精度演算では、バイアス値は 127、 $E_{min}$ は-126、そして  $E_{max}$ は 127 となります。

図 4.3 浮動小数点数のフォーマット

浮動小数点数の値 v は、次のように決定されます。

$E==E_{max}+1$  かつ f!=0 ならば、符号 s に関係なく v は非数(NaN)  $E==E_{max}+1$  かつ f:=0 ならば、v=(-1) s (infinity) [正または負の無限大]

E<sub>min</sub><=E<=E<sub>max</sub>ならば、v=(-1) <sup>s</sup>2<sup>E</sup>(1.f) 〔正規化数〕

E==E<sub>min</sub>-1 かつ f!=0 ならば、v=(-1)<sup>s</sup> 2<sup>Emin</sup>(0.f) [非正規化数]

$E==E_{min}-1$  かつ f==0 ならば、 $v=(-1)^{s}$  0〔正または負のゼロ〕

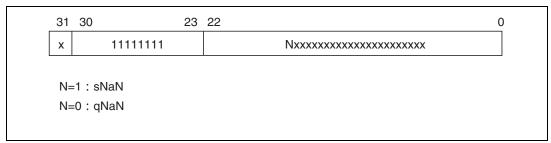

## 4.3.2 非数(NaN)

単精度演算値における非数 (NaN) の表現では、ビット  $22 \sim 0$  のうち少なくとも 1 つのビットが 1 になります。ビット 22 が 1 であれば、シグナリング NaN (sNaN) を示します。ビット 22 が 0 であれば、その値はクワイアット NaN (qNaN) です。

非数 ( NaN ) のビットパターンを下図に示します。図中のビット N は sNaN では 1 になり、qNaN では 0 になります。x は don't care のビットを示しています。ただし、ビット  $22 \sim 0$  のうち少なくとも 1 つのビットは 1 になります。

非数(NaN)では、符号ビットは、don't care になります。

図 4.4 NaN ビットパターン

浮動小数点値を生成する演算に非数 (sNaN)を入力した場合、

- FPSCR レジスタの EV ビットが 0 であれば、演算結果(出力)は qNaN となります。

- FPSCR レジスタの EV ビットが 1 であれば、無効演算例外が発生します。この場合は、演算のデスティネーション側のレジスタの内容は変更されません。

浮動小数点値を生成する演算に qNaN を入力し、かつ sNaN がその演算に入力されていない場合、FPSCR レジスタの EV ビットのセットとは無関係に、出力は常に qNaN となります。そしてこのとき 例外は発生しません。

### 4.3.3 非正規化数の値

非正規化数の浮動小数点数の値は、バイアスされた指数が 0、仮数部が 1/2-ゼロでヒドゥンビットが 0 として表現されます。 SH-3E の浮動小数点演算ユニットでは、非正規化数 ( オペランドソースまたは演算結果 ) は、値を生成する浮動小数点演算 ( コピー以外の演算 ) では画一的に 0 にフラッシュされます。

### 4.3.4 その他の特殊な値について

SH-3E は IEEE754 規格に定められた浮動小数点表現に準拠しています。IEEE754 規格で規定されている浮動小数点数の値の表現には、表 4.1 に示すように 7 種類の異なる種類の特殊な値があります。

| 20 11 12 12 13 13 13 13 13 13 13 13 13 13 13 13 13 | 1 0 1 113221-013 013341-012-0133 |  |  |  |  |  |

|----------------------------------------------------|----------------------------------|--|--|--|--|--|

| 值                                                  | 表現                               |  |  |  |  |  |

| +0.0                                               | 0x0000000                        |  |  |  |  |  |

| -0.0                                               | 0x80000000                       |  |  |  |  |  |

| 非正規化数                                              | 「4.3.3 非正規化数の値」参照                |  |  |  |  |  |

| +INF                                               | 0x7F800000                       |  |  |  |  |  |

| -INF                                               | 0xFF800000                       |  |  |  |  |  |

| qNaN(クワイアット NaN)                                   | 「4.3.2 非数(NaN)」参照                |  |  |  |  |  |

| sNaN(シグナリング NaN)                                   | 「4.3.2 非数 ( NaN ) 」参照            |  |  |  |  |  |

表 4.1 IFFE754 規格で規定されている単精度における特殊な値の表現

## 4.4 浮動小数点例外モデル

### 4.4.1 イネーブル状態の例外

無効演算およびゼロによる除算例外の双方は、FPSCR 内の該当例外のイネーブルビット(EV または EZ ビット)をセットすることでイネーブル状態になります。FPU により発生する例外はすべて、FPU 例外事象としてマッピングされています。個々の例外の意味は、システムレジスタ FPSCR を読み出し、そこに保持されている情報を解析して、ソフトウェアにより決定することになります。

### 4.4.2 ディスエーブル状態の例外

FPSCR 内のイネーブルビット EV がセットされていなければ、無効演算は結果として qNaN を生成します (FCMP と FTRC を除く)。イネーブルビット EZ がセットされていなければ、ゼロによる除算は現在の式の符号 (+もしくは-) を付けた無限値を返します。

他の IEEE754 規格に定められている不正確 (inexact)、オーバフロー、アンダーフローの浮動小数点例外は、SH-3E ではサポートしていません。この様な場合 SH-3E は以下の動作をします。

• オーバフローは、フォーマットにおいて絶対値が表現可能な最大値となる有限数で、かつ正しい符号をもった数を生成します。アンダーフローは、正しい符号をもったゼロを生成します。もし演算結果が不正確である場合は、デスティネーションレジスタは、その不正確な結果を格納することになります。

### 4.4.3 FPU の例外事象とコード

FPU 例外(無効除算およびゼロによる除算例外)は、同一の一般例外事象すなわち FPU 例外として、H'0x0120 番地にマッピングされます。また、システムレジスタ FPUL、FPSCR に関するロードおよびストア命令では、通常のメモリ管理一般例外が発生します。

### 4.4.4 メモリ内の浮動小数点データの配置

単精度浮動小数点データは、4 バイト境界のメモリ上に配置されます。すなわち、SH-3E のロング整数と同一の形式で配置されます。

#### 4.4.5 特殊オペランドを伴う算術演算

特殊オペランド (qNaN、sNaN、+INF、-INF、+0、-0) を伴う算術演算はすべて、IEEE754 規格の規定に従っています。

## 4.5 CPU との同期化

#### (1) CPU との同期化

浮動小数点演算命令と CPU 命令は、プログラム順序に従って順番に実行されていきますが、実行サイクルの相違により動作完了がプログラムの順番どおりにならない場合があります。浮動小数点演算命令が FPU リソースのみをアクセスする場合は、CPU との同期化は必要ありませんし、FPU 命令に続く CPU 命令は、FPU 動作の完了以前に動作を終えることができます。 それゆえ、最適化されたプログラムにおいては、FDiv のような長い実行サイクルを要する浮動小数点演算命令の実行サイクルを見かけ上隠すことが可能です。 一方、CPU リソースにアクセスする FCMP のような浮動小数点演算命令は、プログラム順序を保証する同期化が必要になります。

#### (2) 同期化を必要とする浮動小数点命令

ロード、ストア、比較、および FPUL にアクセスする命令は、CPU リソースにアクセスするため、同期化が必要となります。ロード、ストア命令は、汎用レジスタを参照します。ポストインクリメントロードとプリデクリメントストアは、汎用レジスタの内容を変更します。比較は T ビットを変更します。FPUL にアクセスする命令は FPUL を参照するか、内容を変更します。これらの参照と変更は CPU と同期をとる必要があります。

#### (3) 例外発生時のプログラム順序の保持

浮動小数点命令は、続く CPU 命令が動作完了する前に動作完了することはありません。また、FPU 例外は、続く CPU 命令が動作完了する以前に検出され、FPU 例外が発生した場合には、続く CPU 命令はキャンセルされます。

浮動小数点命令実行中に、続く命令で例外が発生した場合、その浮動小数点命令は実行を続け、その間 FPU リソースは他の命令によりアクセスされません。他の命令によるアクセスは、浮動小数点演算命令の完了を待って行われます。これはプログラム順序を保証するためです。

4. 浮動小数点演算ユニット (SH-3E のみ)

## 5. DSP の演算機能とデータ転送(SH3-DSP のみ)

DSP の演算とデータ転送には次のものがあります。

(1) ALU固定小数点演算:

固定小数点データ40ビット (ガードビット付き)または32ビット (ガードビットなし)の固定小数点算術演算です。加減算、比較命令などがあります。

(2) ALU整数演算:

整数データ24ビット (ガードビット付き)または16ビット (ガードビットなし)の整数算術演算です。インクリメント、デクリメント命令があります。

(3) ALU論理演算:

論理データ16ビットの論理演算です。論理積、論理和、排他的論理和があります。

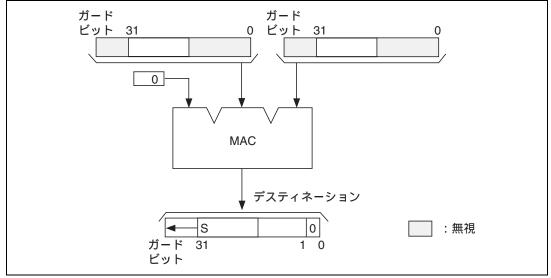

(4) 固定小数点乗算:

固定小数点データ上位16ビットの固定小数点乗算(算術演算)です。DCビットなどの状態ビットは更新されません。

(5) シフト演算:

算術シフト演算と論理シフト演算があります。算術シフト演算は固定小数点データ40ビット (ガードビット付き)または32ビット(ガードビットなし)の算術シフトです。論理シフト 演算は論理データ16ビットの論理演算です。算術シフト演算のシフト量は - 32~+32(負は右シフト、正は左シフト)、論理シフト演算のシフト量は - 16~+16です。

(6) MSB検出命令:

データを正規化するためのシフト量を求める演算です。固定小数点データ40ビット(ガードビット付き)または32ビット(ガードビットなし)のMSBビット位置を整数データ24ビット(ガードビット付き)または16ビット(ガードビットなし)で求めます。

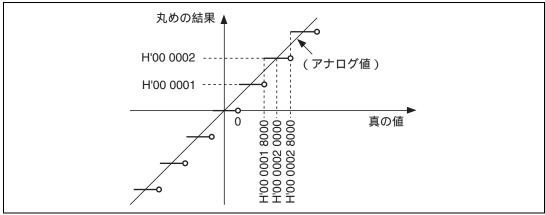

(7) 丸め演算:

固定小数点データ40ビット (ガードビット付き)を24ビットに、または32ビット (ガードビットなし)を16ビットに丸めます。

(8) データ転送:

X、Yメモリから16ビットデータをロード、ストアするX、Yデータ転送と、すべてのメモリから16ビット、または32ビットデータをロード、ストアするシングルデータ転送とがあります。X、Yデータ転送は2つの処理を同時に並行して処理することができます。DCビットなどの状態ビットは更新されません。

演算命令には、無条件演算命令と、DC ビットを判定して実行する条件付き命令があります。DC ビットなどの状態ビットは、条件付き命令では更新されません。DC ビットなどの状態ビットは、算術演算、論理演算、算術シフト、論理シフトで、それぞれ設定が異なります。MSB 検出命令、丸め演算での DC ビットなどの状態ビットの設定は、算術演算として設定されます。

算術演算にはオーバフロー防止機能(飽和演算)があります。SR レジスタの S ビットで飽和演算を指定すると、演算結果がオーバフローしたとき最大値(正)または最小値(負)が格納されます。S ビット機能は、ALU、シフト、乗算のすべての算術演算に有効です。

## 5.1 ALU 固定小数点演算

#### (1) 演算機能

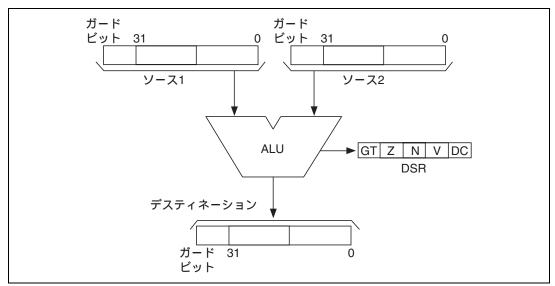

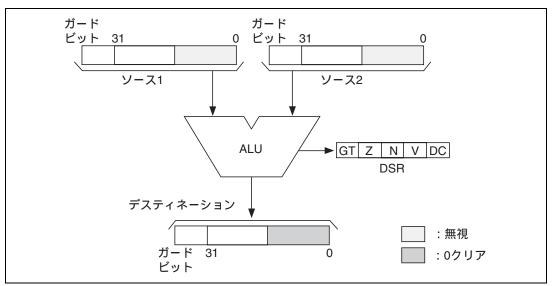

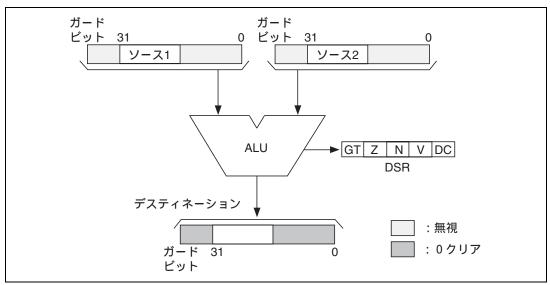

ALU 固定小数点算術演算は、基本の精度 32 ビットにガードビット 8 ビットを加えた 40 ビットで演算されます。ソースオペランドがガードビットなしのレジスタのときは、その符号ビットがガードビットに拡張されて転記されます。デスティネーションオペランドがガードビットのないレジスタのときは、演算結果の下位 32 ビットがデスティネーションレジスタに格納されます。

ALU 固定小数点算術演算はレジスタ間で実行されます。ソースおよびデスティネーションレジスタはそれぞれ独立に DSP レジスタから選べます。選ばれたレジスタにガードビットがあるときは、ガードビットを含めてこれらの演算が実行されます。これらの演算の実行はパイプラインの流れの最後の DSP ステージで実行されます。

ALU 算術演算が実行されるときはいつでも、DSR レジスタの DC、N、Z、V、GT ビットが演算結果によって更新されます。しかし条件付き命令の場合は、指定された状態になっても状態ビットは更新されません。無条件命令の場合は、演算結果に従って更新されます。

DC ビットに反映させる状態は、CS  $\{2:0\}$  ビットによって選択されます。ただし、PADDC 命令と PSUBC 命令の DC ビットは、CS ビットの設定に関係なく更新されます。PADDC 命令ではキャリフラグとして更新され、PSUBC 命令ではボローフラグとして更新されます。

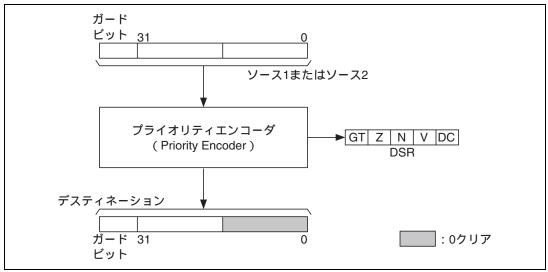

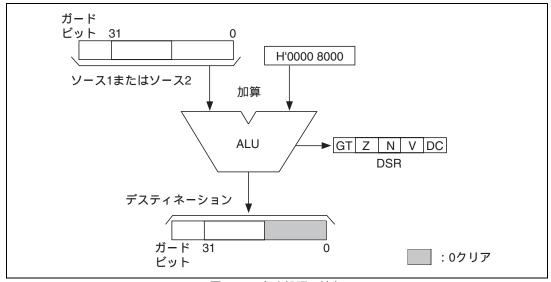

ALU 固定小数点算術演算の流れを図 5.1 に示します。

図 5.1 ALU 固定小数点算術演算の流れ

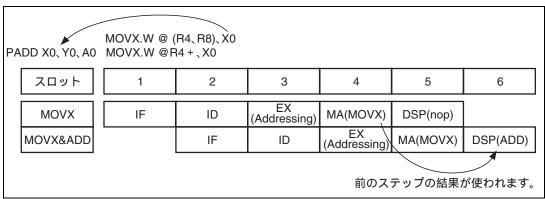

メモリ読み出しのデスティネーションオペランドと ALU 演算のソースオペランドを同じにし、ALU 演算と同じ行にデータ転送命令のプログラムを書いた場合は、メモリアクセスステージ(MA)でメモリからロードされるデータは、ALU 演算命令のソースオペランドとしては使われません。この場合、先に実行された命令の結果が ALU 演算のソースオペランドとして使われ、そのあとで、データロード命令のデスティネーションオペランドとして更新されます。この流れを図 5.2 に示します。

図 5.2 処理の流れの例

### (2) 命令とオペランド

ALU 固定小数点算術演算の種類を表 5.1 に示します。それぞれのオペランドとレジスタとの対応を表 5.2 に示します。

| ニーモニック | 機能      | ソース 1 | ソース 2 | デスティネーション |

|--------|---------|-------|-------|-----------|

| PADD   | 加算      | Sx    | Sy    | Dz ( Du ) |

| PSUB   | 減算      | Sx    | Sy    | Dz ( Du ) |

| PADDC  | キャリ付き加算 | Sx    | Sy    | Dz        |

| PSUBC  | ボロー付き減算 | Sx    | Sy    | Dz        |

| PCMP   | 比較      | Sx    | Sy    | _         |

| PCOPY  | データ複写   | Sx    |       | Dz        |

|        |         | _     | Sy    | Dz        |

| PABS   | 絶対値     | Sx    |       | Dz        |

|        |         | _     | Sy    | Dz        |

| PNEG   | 符号反転    | Sx    |       | Dz        |

|        |         | _     | Sy    | Dz        |

| PCLR   | ゼロクリア   | _     | _     | Dz        |

表 5.1 ALU 固定小数点算術演算の種類

|       | 代 のに がたの 国たり 気が弁 門次弁のり ブント こび ブバッ このがん |     |     |     |     |     |     |     |  |  |  |

|-------|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| オペランド | X0                                     | X1  | Y0  | Y1  | M0  | M1  | A0  | A1  |  |  |  |

| Sx    | Yes                                    | Yes |     |     |     |     | Yes | Yes |  |  |  |

| Sy    |                                        |     | Yes | Yes | Yes | Yes |     |     |  |  |  |

| Dz    | Yes                                    | Yes | Yes | Yes | Yes | Yes | Yes | Yes |  |  |  |

| Du    | Yes                                    |     | Yes |     |     |     | Yes | Yes |  |  |  |

表 5.2 ALU 固定小数点算術演算のオペランドとレジスタとの対応

【注】 Yes:オペランドに使えるレジスタです

Du : 乗算と組み合わされる場合のオペランドです

#### (3) DC ビット

DC ビットは、DSR レジスタの CS2 ~ CS0 ビット(Condition selection、状態選択)の指定に従って、次のようになります。

#### (a) $+ v U / \pi U - E - F$ : $CS2 \sim CS0 = 000$

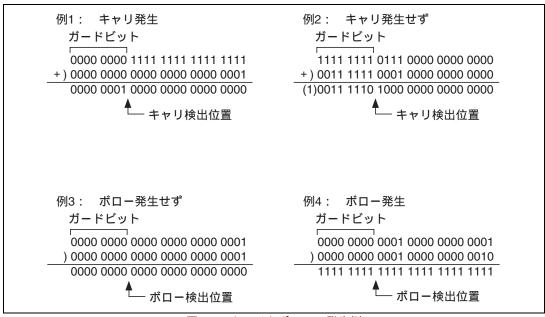

DC ビットは演算の結果、MSB (Most significant bit) ビットからキャリまたはボローが発生したことを表します。ガードビットは関係ありません。このモードはデフォルト (default) です。キャリとボローの発生例を図 5.3 に示します。

図 5.3 キャリとボローの発生例

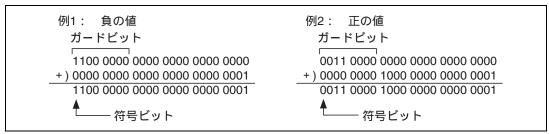

#### (b) 負値モード: CS2~CS0=001

DC ビットは演算結果の MSB ビットの値と同じです。結果が負の値のとき DC ビットは 1 になります。ゼロまたは正の値のとき DC ビットは 0 になります。ALU 算術演算は常に 40 ビットで演算します。そのため正か負かの符号ビットは、デスティネーションオペランドの MSB ビットではなく、演算結果のガードビットを含めた MSB ビットで判定されます。正負の判定例を図 5.4 に示します。このモードの DC ビットは、状態ビットの N ビットの値と同じです。

図 5.4 正負の判定例

#### (c) ゼロ値モード: CS2~CS0=010

DC ビットは演算結果がゼロかどうかを表します。結果がゼロのとき DC ビットは 1 になり、結果がゼロでないとき DC ビットは 0 になります。このモードの DC ビットは、状態ビットの DC ビットの値と同じです。

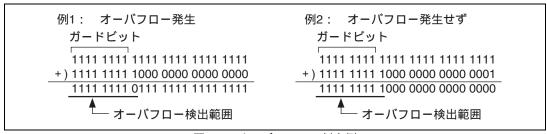

#### (d) オーバフローモード: CS2~CS0=011

DC ビットは演算の結果、オーバフローが発生したかどうかを表します。演算の結果がガードビットを除いて、デスティネーションレジスタの範囲を超えた場合、DC ビットが 1 にセットされます。 DC ビットは、ガードビットがあっても、ガードビットがないと考えてオーバフローを判定します。 そのため大きな数がガードビットを使う場合は DC ビットが常に 1 にセットされます。このモードの DC ビットは、状態ビットの V ビットの値と同じです。オーバフローの判定例を図 5.5 に示します。

図 5.5 オーバフローの判定例

### (e) 符号付き大モード: CS2~CS0=100

DC ビットは比較命令 PCMP の判定結果、ソース 1 データ (符号付き)がソース 2 データ (符号付き)より大きいかどうかを表します。ソース 1 データがソース 2 データより大きいときは比較の結果が正の値になるため、このモードは負値モードと似ています。しかしソース 1 データがソース 2 デー

タより大きいときでも、デスティネーションオペランドの範囲を超えたときは、比較の結果の符号が負の値になります。DC ビットはこの場合更新されます。このモードの DC ビットは、状態ビットのGT ビットの値と同じです。このモードでの DC ビットを式で定義すると次のようになります。ただし、VR は結果がガードビット領域も含めてデスティネーションオペランドの表示範囲を超えた場合に真となる値です。

DC  $\forall v = \{ (N \forall v + VR) \mid Z \forall v + \}$

DC ビットは、このモードで PCMP 命令を実行させると、SH コア命令の CMP/GT 命令の結果を表す T ビットと同じ値になります。このモードでは、PCMP 命令以外でも上記定義に従って DC ビットは更新されます。

#### (f) 符号付き以上モード: CS2~CS0=101

DC ビットは、比較命令 PCMP の実行結果、ソース 1 データ(符号付き)がソース 2 データ(符号付き)より大きいかまたは等しいか、あるいはそうでないかを表します。そのため PCMP 命令は、このモードで DC ビットを判定するまえに、実行されます。このモードは、等しいかどうかを除いて符号付き大モードと似ています。このモードでの DC ビットを式で定義すると次のようになります。ただし、VR は結果がガードビット領域も含めてデスティネーションオペランドの表示範囲を超えた場合に真となる値です。

DC ビット= ~ (N ビット VR)

DC ビットは、このモードで PCMP 命令を実行させると、SH コア命令の CMP/GE 命令の結果を表す T ビットと同じ値になります。このモードでは、PCMP 命令以外でも上記定義に従って DC ビットは更新されます。

#### (4) 状態ビット

状態ビットは次のように設定されます。

N ビット (Negative bit、負値ビット) は CS ビットで負値モードを指定したときの DC ビットの値と同じです。演算結果が負の値のとき N ビットは 1 になります。ゼロまたは正の値のとき N ビットは 0 になります。

Z ビット ( Zero bit、ゼロビット ) は CS ビットでゼロ値モードを指定したときの DC ビットの値と同じです。結果がゼロのとき Z ビットは 1 になり、結果がゼロでないとき Z ビットは 0 になります。

V ビット ( Overflow bit、オーバフロービット ) V ビットは CS ビットでオーバフローモードを指定したときの DC ビットの値と同じです。演算の結果、カードビットを除くデスティネーションレジスタの範囲を超えた場合、V ビットが 1 にセットされます。それ以外は 0 にクリアされます。

GT ビット (Greater than bit、符号付き大ビット) は CS ビットで符号付き大モードを指定したときの DC ビットの値と同じです。比較の結果、ソース 1 データがソース 2 データより大きいとき、GT ビットが 1 にセットされます。それ以外は 0 にクリアされます。

#### (5) オーバフロー防止機能(飽和演算)

SR レジスタの S ビットを 1 にセットすると、DSP ユニットで実行されるすべての ALU 算術演算で、オーバフロー防止機能が実行されます。演算結果がオーバフローしたとき最大値 (  $\pm$  ) または最小値 (  $\pm$  ) が格納されます。

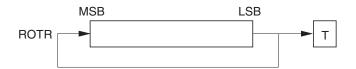

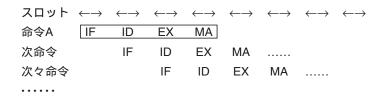

## 5.2 ALU 整数演算