## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

H8S/2258 グループ、H8S/2239 グループ、 H8S/2238 グループ、H8S/2237 グループ、 H8S/2227 グループ

ハードウェアマニュアル ルネサス16 ビットシングルチップマイクロコンピュータ H8Sファミリ/H8S/2200 シリーズ

| H8S/2258  | HD64F2258   | H8S/2236R | HD6432236R  |

|-----------|-------------|-----------|-------------|

|           | HD6432258   |           | HD6432236RW |

|           | HD6432258W  | H8S/2237  | HD6472237   |

| H8S/2256  | HD6432256   |           | HD6432237   |

|           | HD6432256W  | H8S/2235  | HD6432235   |

| H8S/2239  | HD64F2239   | H8S/2233  | HD6432233   |

|           | HD6432239   | H8S/2227  | HD64F2227   |

|           | HD6432239W  |           | HD6432227   |

| H8S/2238B | HD64F2238B  | H8S/2225  | HD6432225   |

|           | HD6432238B  | H8S/2224  | HD6432224   |

|           | HD6432238BW | H8S/2223  | HD6432223   |

| H8S/2238R | HD64F2238R  |           |             |

|           | HD6432238R  |           |             |

|           | HD6432238RW |           |             |

| H8S/2236B | HD6432236B  |           |             |

|           | HD6432236BW |           |             |

### 本資料ご利用に際しての留意事項。

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負いません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10. 弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が 発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作 が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において 冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェ ア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システム としての安全検証をお願いいたします。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故につきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業 窓口までご照会ください。

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項 については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の記載が優 先するものとします。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる 一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてくだ

### 5. 製品間の相違について

さい。

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

## 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品ご使用上の注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 本版で改訂された箇所

改訂来歴は、前版の記載内容について訂正された主な箇所についてまとめたものです。改訂内容のすべてについて記載したものではありませんので、詳細については、本書の本文上でご確認ください。

- 5. 目次

- 6. 概要

- 7. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュールごとに異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、 などの節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認のうえ設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 8. レジスター覧

- 9. 電気的特性

- 10. 付録

- 製品型名、外形寸法など

- 11. 索引

## はじめに

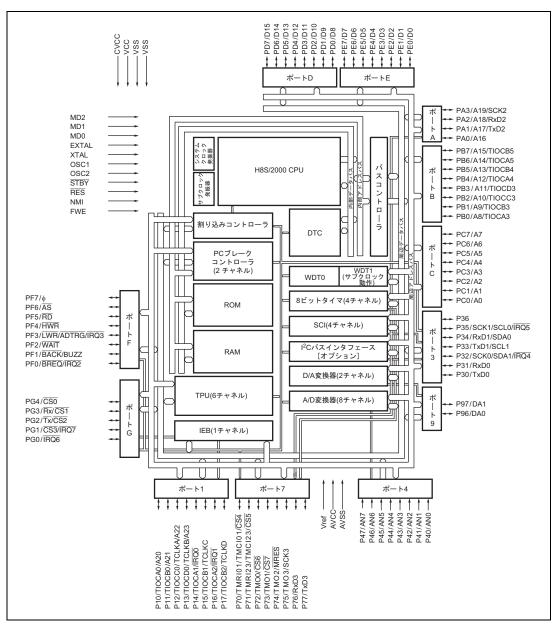

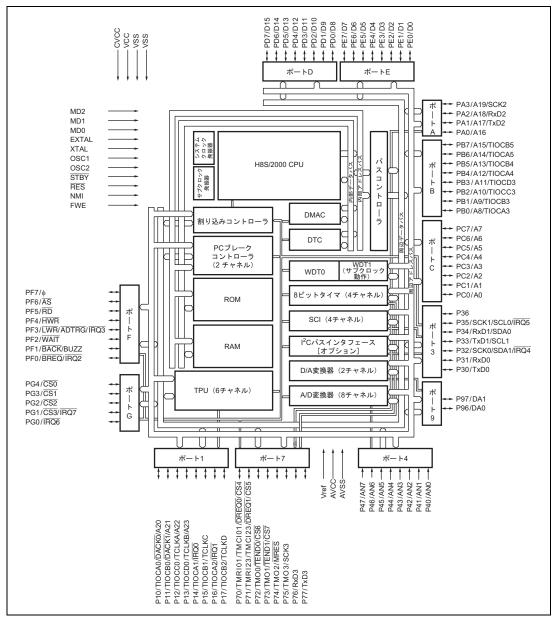

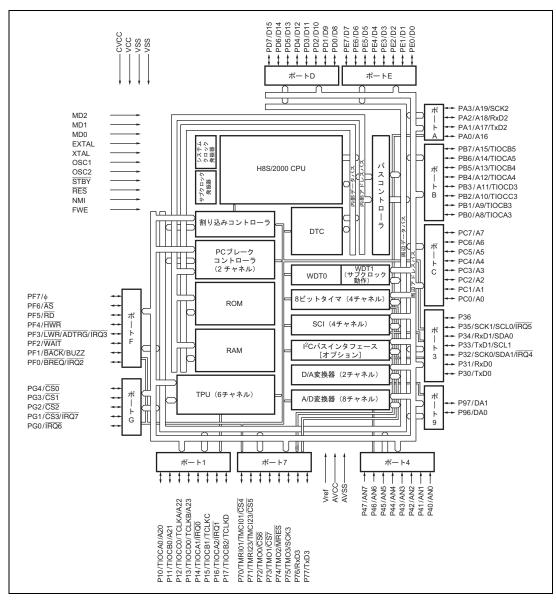

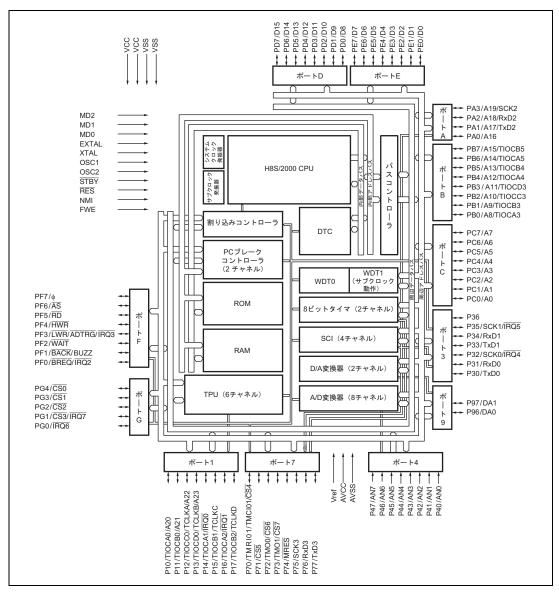

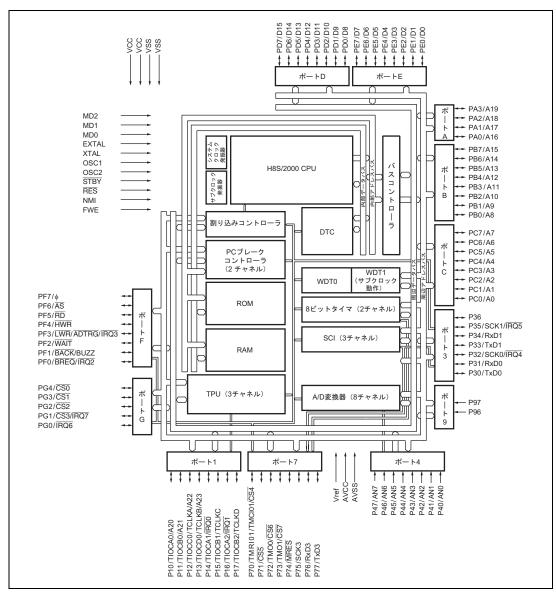

H8S/2238 グループ、H8S/2239 グループ、H8S/2238 グループ、H8S/2237 グループ、H8S/2227 グループは、内部 32 ビット構成の H8S/2000 CPU を核にして、システム構成に必要な周辺機能を集積した高性能マイクロコンピュータです。

内蔵 ROM は、単一電源フラッシュメモリ ( $F-ZTAT^{TM*}$ )、マスク ROM 版があり、仕様流動性の高い応用機器、量産初期から本格的量産の各状況に応じた、迅速かつ柔軟な対応が可能です。各製品の内蔵周辺機能を以下に示します。

【注】 \* F-ZTAT は (株) ルネサス テクノロジの商標です。

### • 内蔵周辺機能一覧

| グループ名                           | H8S/2258  | H8S/2239  | H8S/2238  | H8S/2237   | H8S/2227 |

|---------------------------------|-----------|-----------|-----------|------------|----------|

|                                 | グループ      | グループ      | グループ      | グループ       | グループ     |

| 製品名                             | H8S/2258  | H8S/2239  | H8S/2238B | H8S/2237   | H8S/2227 |

|                                 | H8S/2256  |           | H8S/2238R | H8S/2235   | H8S/2225 |

|                                 |           |           | H8S/2236B | H8S/2233   | H8S/2224 |

|                                 |           |           | H8S/2236R |            | H8S/2223 |

| バスコントローラ (BSC)                  | (16 ビット)  | (16 ビット)  | (16 ビット)  | (16ビット)    | (16ビット)  |

| データトランスファコントローラ                 |           |           |           |            |          |

| (DTC)                           |           |           |           |            |          |

| DMA コントローラ ( DMAC )             |           |           |           |            |          |

| PC ブレークコントローラ (PBC)             | ×2        | ×2        | ×2        | ×2         | ×2       |

| 16 ビットタイマパルスユニット                | × 6       | ×6        | ×6        | ×6         | ×3       |

| (TPU)                           |           |           |           |            |          |

| 8 ビットタイマ ( TMR )                | × 4       | × 4       | × 4       | <b>x</b> 2 | ×2       |

| ウォッチドッグタイマ (WDT)                | ×2        | ×2        | ×2        | <b>x</b> 2 | ×2       |

| シリアルコミュニケーション                   | × 4       | × 4       | × 4       | × 4        | ×3       |

| インタフェース (SCI)                   |           |           |           |            |          |

| I <sup>2</sup> C バスインタフェース(IIC) | ×2(オプション) | ×2(オプション) | ×2(オプション) |            |          |

| D/A 変換器                         | ×2        | ×2        | ×2        | ×2         |          |

| A/D 変換器 アナログ入力                  | ×8        | ×8        | ×8        | ×8         | ×8       |

| IEBus™*コントローラ(IEB)              | ×1        |           |           |            |          |

【注】 \* IEBus (Inter Equipment Bus ) は NEC エレクトロニクスの商標です。

対象者 このマニュアルは、H8S/2258 グループ、H8S/2239 グループ、H8S/2238 グループ、H8S/2237 グループ、H8S/2237 グループを用いた応用システムを設計するユーザを対象としています。 このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

目的 このマニュアルは、H8S/2258 グループ、H8S/2239 グループ、H8S/2238 グループ、H8S/2237 グループ、H8S/2237 グループのハードウェア機能と電気的特性をユーザに理解していただくことを目的にしています。なお、実行命令の詳細については、「H8S/2600 シリーズ、H8S/2000 シリーズ ソフトウェアマニュアル」に記載していますのであわせてご覧ください。

### 読み方

機能全体を理解しようとするとき

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき

別冊の「H8S/2600シリーズ、H8S/2000シリーズ ソフトウェアマニュアル」を参照してください。

• レジスタ名が分かっていて、詳細機能を知りたいとき

本書の後ろに「索引」があります。索引からページ番号を検索してください。

「第26章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

凡例 レジスタ表記 : 16 ビットタイマパルスユニット、シリアルコミュニケーションインタフェースなど、

同一または類似した機能が複数チャネルに存在する場合に次の表記を使用します。

XXX\_N (XXX は基本レジスタ名称、N はチャネル番号)

ビット表記順 : 左側が上位ビット、右側が下位ビット

数字の表記 : 2 進数は B'xxxx、16 進数は H'xxxx、10 進数は xxxx

信号の表記:ローアクティブの信号にはオーババーを付けます。xxxx

関連資料一覧 ウェブサイトに最新資料を掲載しています。入手された資料が最新版であるかを確認してください。

( http://japan. renesas.com / )

H8S/2258グループ、H8S/2239グループ、H8S/2238グループ、H8S/2237グループ、H8S/2227グループに関するユーザーズマニュアル

| 資料名                                                      | 資料番号       |

|----------------------------------------------------------|------------|

| H8S/2258 グループ、H8S/2239 グループ、H8S/2238 グループ、H8S/2237 グループ、 | 本マニュアル     |

| H8S/2227 グループ ハードウェアマニュアル                                |            |

| H8S/2600 シリーズ、H8S/2000 シリーズ ソフトウェアマニュアル                  | RJJ09B0143 |

## 開発ツール関連ユーザーズマニュアル

| 資料名                                                                             | 資料番号       |

|---------------------------------------------------------------------------------|------------|

| H8S、H8/300 シリーズ C/C++コンパイラ、アセンブラ、最適化リンケージエディタ<br>コンパイラパッケージ Ver.6.01 ユーザーズマニュアル | RJJ10J2552 |

| High-performance Embedded Workshop ユーザーズマニュアル                                   | RJJ10J2550 |

### • アプリケーションノート

| 資料名                                        | 資料番号            |

|--------------------------------------------|-----------------|

| H8S、H8/300 シリーズ C/C++コンパイラパッケージアプリケーションノート | RJJ05B0558      |

| F-ZTAT マイコンテクニカル Q&A                       | ADJ - 502 - 055 |

# 本版で改訂された箇所

| 修正項目                 | ページ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 修正                                            |               |                          |

|----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|--------------------------|

| 1.3.2 動作モード別ピン配      | 1-20 ~ | 表を修正                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

| 置一覧                  | 1-23   | ピン番号                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 端子名           |                          |

| 表 1.1 H8S/2258 グループの |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - F4 €- F5                                    | モード6          | モード7 フラッシュ<br>メモリライタ     |

| 動作モード別ピン配置一覧         |        | FP-100B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |               | モード*                     |

|                      | 1-23   | 注を追加                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

|                      | 1-25   | 【注】* NC は開放とし                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | してください。                                       |               |                          |

| 表 1.2 H8S/2239 グループの | 1-24   | 表を修正                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

| 動作モード別ピン配置一覧         |        | ピン番号                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 端子名           |                          |

|                      |        | TFP-100B TBP-112A * TFP-100BV TBP-112AV * | モード4 モード                                      | 5 E-F6        | モード7 フラッシュ<br>メモリ        |

|                      |        | TFP-100G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |               | ライタモード                   |

|                      |        | TFP-100GV<br>FP-100B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

|                      |        | FP-100BV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |               |                          |

|                      | 1-25 ~ | 表を修正                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

|                      | 1-28   | ピン番号                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 端子名           |                          |

|                      |        | TFP-100B TBP-112A *1 TFP-100BV TBP-112AV *1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | モード4 モード                                      | 5 モード6        | モード7 フラッシュ<br>メモリ        |

|                      |        | TFP-100G<br>TFP-100GV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |               | ライタモード* <sup>2</sup>     |

|                      |        | FP-100B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |               |                          |

|                      |        | FP-100BV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |               |                          |

|                      | 1-28   | 注を修正                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

|                      |        | 【注】*1 HD64F2239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9のみです。                                        |               |                          |

|                      |        | *2 NC は開放 d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | としてください。                                      |               |                          |

| 表 1.3 H8S/2238 グループの | 1-30 ~ | 表を修正                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

| 動作モード別ピン配置一覧         | 1-33   | ピン番号<br>TFP-100B FP-100A * <sup>1</sup> BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P-112 *2                                      | 端子名           | 100 = 107                |

|                      |        | TFP-100BV FP-100AV*1 BP-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -112V *²                                      | モード5 モー       | ード6 モード7 フラッシュ<br>メモリ    |

|                      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P-112A* <sup>2</sup><br>P-112AV* <sup>2</sup> |               | ライタ<br>モード* <sup>4</sup> |

|                      |        | FP-100B<br>FP-100BV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |               |                          |

|                      |        | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |               |                          |

|                      | 1-33   | 注を追加                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |               |                          |

|                      |        | 【注】 *4 NC は開放る                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | としてください。                                      |               |                          |