# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

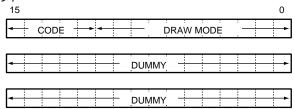

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# 資料中の「日立製作所」、「日立XX」等名称の株式会社ルネサス テクノロジへの変更について

2003年4月1日を以って三菱電機株式会社及び株式会社日立製作所のマイコン、ロジック、アナログ、ディスクリート半導体、及びDRAMを除くメモリ(フラッシュメモリ・SRAM等)を含む半導体事業は株式会社ルネサス テクノロジに承継されました。従いまして、本資料中には「日立製作所」、「株式会社日立製作所」、「日立半導体」、「日立XX」といった表記が残っておりますが、これらの表記は全て「株式会社ルネサス テクノロジ」に変更されておりますのでご理解の程お願い致します。尚、会社商標・ロゴ・コーポレートステートメント以外の内容については一切変更しておりませんので資料としての内容更新ではありません。

ルネサステクノロジ ホームページ (http://www.renesas.com)

2003年4月1日 株式会社ルネサス テクノロジ カスタマサポート部

# ご注意

#### 安全設計に関するお願い

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただく ための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが 所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の 使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサス テクノロジ は責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の 記述誤りに起因する損害がお客様に生じた場合には、ルネサス テクノロジはその責 任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサス テクノロジ、ルネサス販売または特約店までご照会ください。

# HD64413A Q2SD

ユーザーズマニュアル SuperH™ RISC engine 周辺 LSI

HD64413A

Quick 2D Graphics Renderer with Synchronous DRAM Interface

# ご注意

- 1 本書に記載の製品及び技術のうち「外国為替及び外国貿易法」に基づき安全保障貿易管理関連貨物・技術に該当するものを輸出する場合,または国外に持ち出す場合は日本国政府の許可が必要です。

- 2 本書に記載された情報の使用に際して,弊社もしくは第三者の特許権,著作権,商標権, その他の知的所有権等の権利に対する保証または実施権の許諾を行うものではありませ ん。また本書に記載された情報を使用した事により第三者の知的所有権等の権利に関わ る問題が生じた場合,弊社はその責を負いませんので予めご了承ください。

- 3 製品及び製品仕様は予告無く変更する場合がありますので,最終的な設計,ご購入,ご 使用に際しましては,事前に最新の製品規格または仕様書をお求めになりご確認ください。

- 4 弊社は品質・信頼性の向上に努めておりますが、宇宙、航空、原子力、燃焼制御、運輸、 交通、各種安全装置、ライフサポート関連の医療機器等のように、特別な品質・信頼性 が要求され、その故障や誤動作が直接人命を脅かしたり、人体に危害を及ぼす恐れのあ る用途にご使用をお考えのお客様は、事前に弊社営業担当迄ご相談をお願い致します。

- 5 設計に際しては,特に最大定格,動作電源電圧範囲,放熱特性,実装条件及びその他諸条件につきましては,弊社保証範囲内でご使用いただきますようお願い致します。保証値を越えてご使用された場合の故障及び事故につきましては,弊社はその責を負いません。また保証値内のご使用であっても半導体製品について通常予測される故障発生率,故障モードをご考慮の上,弊社製品の動作が原因でご使用機器が人身事故,火災事故,その他の拡大損害を生じないようにフェールセーフ等のシステム上の対策を講じて頂きますようお願い致します。

- 6 本製品は耐放射線設計をしておりません。

- 7 本書の一部または全部を弊社の文書による承認なしに転載または複製することを堅くお 断り致します。

- 8 本書をはじめ弊社半導体についてのお問い合わせ,ご相談は弊社営業担当迄お願い致します。

## 製品に関する一般的注意事項

#### 1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。接続された場合については保証できません。

2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放 状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて 誤動作を起こす恐れがあります。

未使用の入力端子は、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は,製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路 は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によっ てシステムが誤動作を起こさないようにシステム設計を行ってください。

リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられ ている場合があります。

これらのレジスタをアクセスしたときの動作および継続する動作については、保証できません ので、アクセスしないようにしてください。

# 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品に関する一般的注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 端子

- ・端子構成

- ・ピン配置図

- ・端子機能説明

- 7. UGM アーキテクチャ

- ディスプレイリスト

各コマンドの説明の構成は、機能、コマンドフォーマット、説明、例

等の節で構成されています。

- 9. レジスタ

- ・レジスタ一覧

- ・各レジスタの説明

- 6. 使用上の注意事項

- 7. 電気的特性

- 8. 付録

# はじめに

Q2SD ( Quick 2D Graphics Renderer with Synchronous DRAM Interface ) は、シンプル、リアルタイム、およびアップグレードをコンセプトとした CPU グラフィックアクセラレータクイックシリーズ ( Q シリーズ ) の SDRAM インタフェース対応 2D グラフィックレンダラーです。 Q2SD は、描画、表示、ビデオ入力機能を 1 チップに集積したマルチメディア応用向け高性能グラフィックスレンダリング LSI です。

対象者 このマニュアルは、Q2SDを用いた応用システムを設計するユーザーを対象としています。 このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

目的 このマニュアルは、Q2SDのハードウェア機能と電気的特性をユーザーに理解して頂くことを目的にしています。今回の改訂版では、ビデオ入力機能説明の充実、アプリケーションノートの掲載、また、お客様からご質問を頂いた内容について見直ししました。

読み方 目次にしたがって読んでください。

本書は、大きく分類すると、概要、端子説明、UGMアーキテクチャ、 ディスプレイリスト、レジスタ説明、使用上の注意事項の順に構成されています。

凡例 数字の表記:2進数はB'xxxx、16進数はH'xxxx

信号の表記:ローアクティブの信号にはオーバーバーを付けます。xxxx

関連資料一覧 ウェブ・サイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://www.hitachisemiconductor.com/jp/)

#### • アプリケーションノート

| 資料名                      | 資料番号        |

|--------------------------|-------------|

| HD64413AQ2SD アプリケーションノート | ADJ-502-079 |

# 目次

| 1.  | 概要   |                                  | 1-1  |

|-----|------|----------------------------------|------|

| 1.1 | 特·   | Ē                                | 1-2  |

| 1.2 | 製    | 品仕樣                              | 1-7  |

| 1.3 | ブ    | ロック図                             | 1-8  |

| 1.4 | 処:   | 里状態                              | 1-10 |

| 1.  | .4.1 | パワーオン                            | 1-10 |

| 1.  | .4.2 | 初期状態(規定の電源を投入したとき)               | 1-10 |

| 1.  | .4.3 | リセット状態(RESET 端子に Low レベルを入力したとき) | 1-11 |

| 1.  | .4.4 | UGM 初期化状態                        | 1-11 |

| 1.  | .4.5 | 通常動作状態                           | 1-11 |

| 2.  | 端子   |                                  | 2-1  |

| 2.1 | 端-   | 子構成                              | 2-1  |

| 2.2 | ピ    | ン配置図                             | 2-2  |

| 2.3 | 端    | 子機能                              | 2-3  |

| 2.4 | シ    | ステム制御端子                          | 2-8  |

| 2.  | .4.1 | 動作モード端子                          | 2-8  |

| 2.  | .4.2 | クロック端子                           | 2-8  |

| 2.  | .4.3 | リセット端子                           | 2-9  |

| 2.  | .4.4 | 電源端子                             | 2-10 |

| 2.5 | CP   | Uインタフェース端子                       | 2-11 |

| 2.  | .5.1 | CPU ライト                          | 2-11 |

| 2.  | .5.2 | CPU リード                          | 2-11 |

| 2.  | .5.3 | DMA ライト                          | 2-12 |

| 2.  | .5.4 | 割り込み                             | 2-13 |

| 2.6 | UC   | GMインタフェース端子                      | 2-13 |

| 2.7 | 表    | 示インタフェース端子                       | 2-14 |

| 2.  | .7.1 | 表示信号出力                           | 2-14 |

| 2.  | .7.2 | ビデオエンコーダインタフェース                  | 2-14 |

| 2.  | .7.3 | CRT インタフェース                      | 2-14 |

| 2.  | .7.4 | D/A コンバータ                        | 2-14 |

| 2.8 | ビ    | デオ取り込みインタフェース端子                  | 2-16 |

| 2.  | .8.1 | ビデオ取り込みインタフェース                   | 2-16 |

| 3. UG  | M アーキテクチャ                | 3-1  |

|--------|--------------------------|------|

| 3.1    | 特長                       | 3-1  |

| 3.2    | Q2SDアクセス                 | 3-2  |

| 3.2.1  | UGM アクセスの優先順位            | 3-2  |

| 3.2.2  | CPU の UGM アクセス           | 3-2  |

| 3.2.3  | DMAC の UGM アクセス          | 3-3  |

| 3.2.4  | Q2SD の UGM アクセス          | 3-3  |

| 3.2.5  | CPU のレジスタアクセス            | 3-3  |

| 3.2.6  | レジスタの更新                  | 3-4  |

| 3.2.7  | バイト入れ替え機能                | 3-6  |

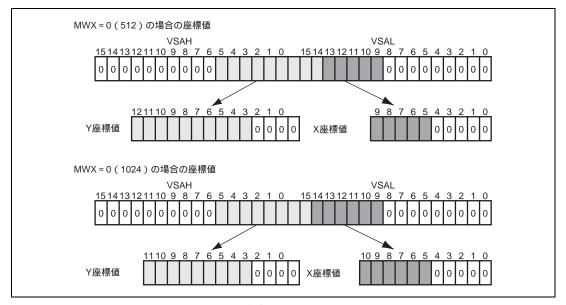

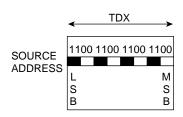

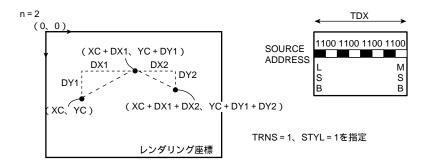

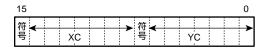

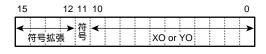

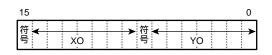

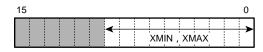

| 3.2.8  | 2 次元画像データ変換機能            | 3-7  |

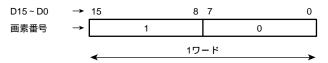

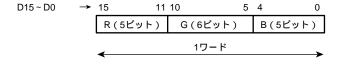

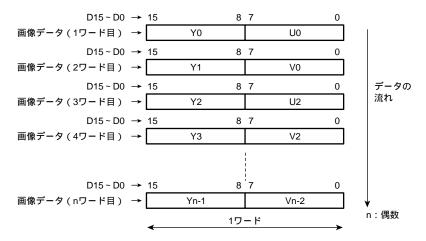

| 3.2.9  | 入力データフォーマット              | 3-11 |

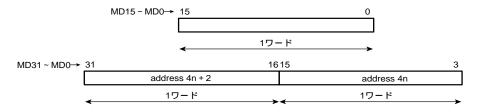

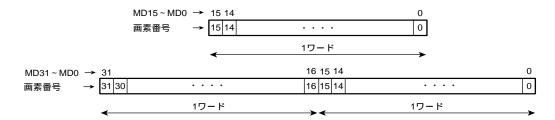

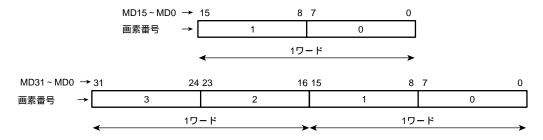

| 3.2.10 | UGM 上のデータフォーマット          | 3-14 |

| 3.2.11 | 内部データフォーマット              | 3-16 |

| 3.2.12 | 割り込み出力機能                 | 3-17 |

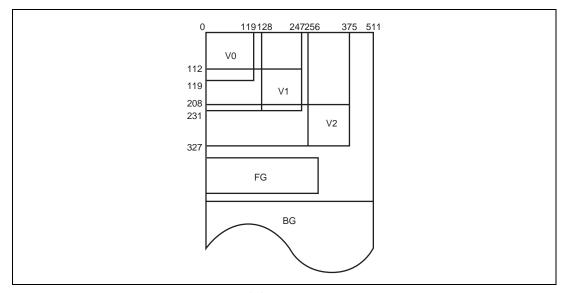

| 3.3    | ユニファイドグラフィックスメモリ ( UGM ) | 3-18 |

| 3.3.1  | メモリアドレス                  | 3-18 |

| 3.3.2  | メモリマップ                   | 3-22 |

| 3.3.3  | 座標系                      | 3-24 |

| 3.3.4  | ダブルバッファ制御                | 3-31 |

| 3.3.5  | リフレッシュ制御                 | 3-37 |

| 3.4    | 表示                       | 3-38 |

| 3.4.1  | 表示画面の設定                  | 3-38 |

| 3.4.2  | 表示画面の合成                  | 3-40 |

| 3.4.3  | 表示走查方式                   | 3-43 |

| 3.4.4  | 表示同期方式                   | 3-50 |

| 3.4.5  | 表示画面の色展開                 | 3-53 |

| 3.5    | レンダリング                   | 3-54 |

| 3.5.1  | コマンド                     | 3-54 |

| 3.5.2  | 画像データの参照                 | 3-56 |

| 3.5.3  | レンダリング属性                 | 3-59 |

| 3.5.4  | コマンドフェッチ                 | 3-66 |

| 3.5.5  | Q2SD 内部バッファについて          | 3-68 |

| 3.6    | ビデオ取り込み機能                | 3-69 |

| 3.6.1  | ビデオ取り込み制御                | 3-69 |

| 3.6.2  | ビデオ取り込みモード               | 3-71 |

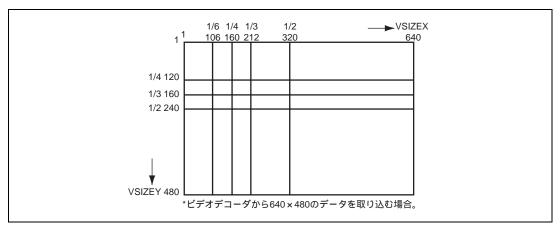

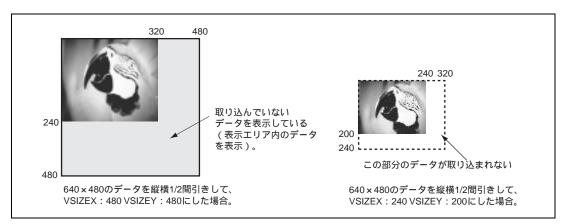

| 3.6.3  | ビデオ取り込み画像の縮小             | 3-76 |

| 3.6.4  | ビデオ取り込み位置の設定             | 3-77 |

| 3.6.5  | ビデオ取り込みデータの形式            | 3-79 |

| 3.6.6  | YCbCr データと RGB データ       | 3-81 |

|        |                          |      |

| 3.7   | ビデオ表示機能                | 3-82 |

|-------|------------------------|------|

| 3.7.1 | ビデオ面の表示                | 3-82 |

| 3.7.2 | 表示走査モードとビデオ取り込みモードとの関係 | 3-82 |

|       |                        |      |

| 4. ディ | ィスプレイリスト               | 4-1  |

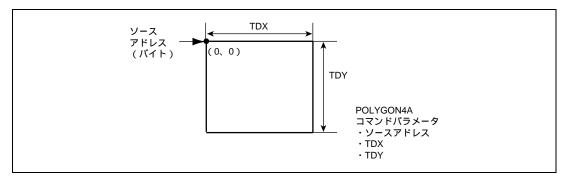

| 4.1   | 4頂点面描画コマンド             | 4-2  |

| 4.1.1 | POLYGON4A              | 4-2  |

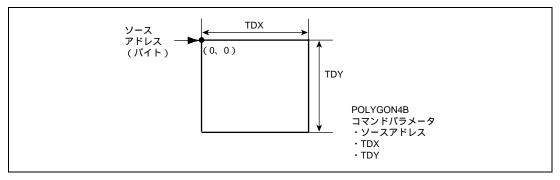

| 4.1.2 | POLYGON4B              | 4-6  |

| 4.1.3 | POLYGON4C              | 4-9  |

| 4.2   | 線描画                    | 4-11 |

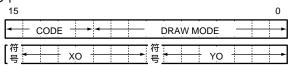

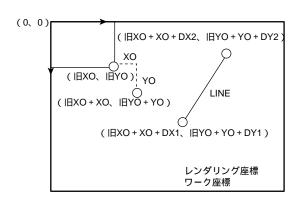

| 4.2.1 | LINE                   | 4-11 |

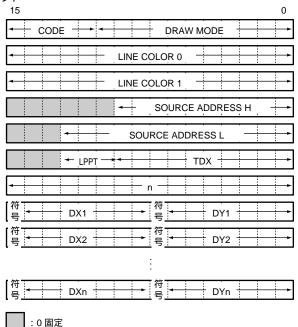

| 4.2.2 | RLINE                  | 4-13 |

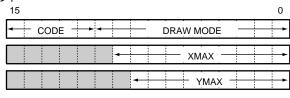

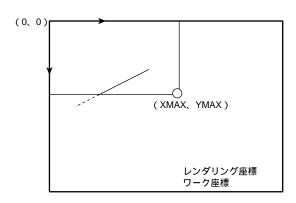

| 4.2.3 | PLINE                  | 4-15 |

| 4.2.4 | RPLINE                 | 4-17 |

| 4.3   | ワーク面描画コマンド             | 4-19 |

| 4.3.1 | FTRAP                  | 4-19 |

| 4.3.2 | RFTRAP                 | 4-21 |

| 4.3.3 | CLRW                   | 4-23 |

| 4.4   | ワーク線描画                 | 4-25 |

| 4.4.1 | LINEW                  | 4-25 |

| 4.4.2 | RLINEW                 | 4-27 |

| 4.5   | レジスタ設定コマンド             | 4-29 |

| 4.5.1 | MOVE                   | 4-29 |

| 4.5.2 | RMOVE                  | 4-31 |

| 4.5.3 | LCOFS                  | 4-32 |

| 4.5.4 | RLCOFS                 | 4-34 |

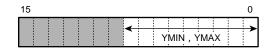

| 4.5.5 | SCLIP                  | 4-36 |

| 4.5.6 | UCLIP                  | 4-38 |

| 4.5.7 | WPR                    | 4-40 |

| 4.6   | シーケンス制御コマンド            | 4-42 |

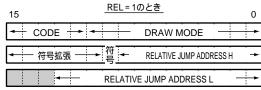

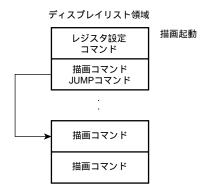

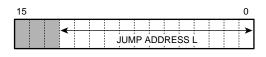

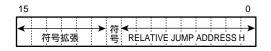

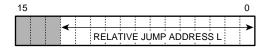

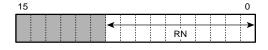

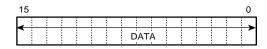

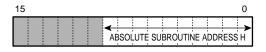

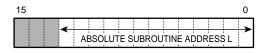

| 4.6.1 | JUMP                   | 4-42 |

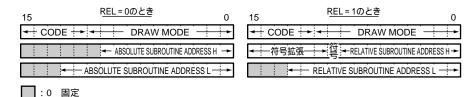

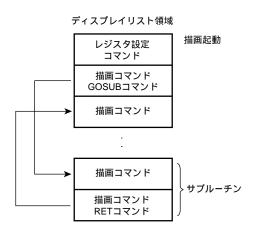

| 4.6.2 | GOSUB                  | 4-44 |

| 4.6.3 | RET                    |      |

| 4.6.4 | NOP3                   | 4-47 |

| 4.6.5 | VBKEM                  | 4-48 |

| 4.6.6 | TRAP                   | 4-49 |

| 5. レシ | ジスタ                    | F_1  |

|       |                        |      |

| 5.1   | レジスター覧                 |      |

| 5.2   | インタフェース制御レジスタ          | 5-4  |

| 5.2.1  | システム制御レジスタ(SYSR)           | 5-4  |

|--------|----------------------------|------|

| 5.2.2  | ステータスレジスタ (SR)             | 5-8  |

| 5.2.3  | ステータスレジスタクリアレジスタ(SRCR)     | 5-11 |

| 5.2.4  | 割り込み許可レジスタ(IER)            | 5-12 |

| 5.2.5  | メモリモードレジスタ ( MEMR )        | 5-14 |

| 5.2.6  | 表示モードレジスタ(DSMR)            | 5-15 |

| 5.2.7  | 表示モード 2 レジスタ ( DSMR2 )     | 5-18 |

| 5.2.8  | レンダリングモードレジスタ(REMR)        | 5-20 |

| 5.2.9  | 入力データ変換モードレジスタ(IEMR)       | 5-22 |

| 5.2.10 | ビデオ取り込みモードレジスタ(VIMR)       | 5-24 |

| 5.3    | メモリ制御レジスタ                  | 5-27 |

| 5.3.1  | 表示サイズレジスタ(DSR)             | 5-27 |

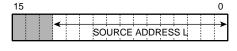

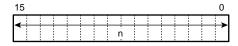

| 5.3.2  | 表示開始アドレスレジスタ(DSAR)         | 5-28 |

| 5.3.3  | ディスプレイリスト開始アドレスレジスタ(DLSAR) | 5-29 |

| 5.3.4  | 多値ソース領域開始アドレスレジスタ(SSAR)    | 5-29 |

| 5.3.5  | ワーク領域開始アドレスレジスタ(WSAR)      | 5-30 |

| 5.3.6  | 背景開始座標レジスタ(BGSR)           | 5-30 |

| 5.3.7  | ビデオ領域開始アドレスレジスタ(VSAR)      | 5-31 |

| 5.3.8  | ビデオウィンドウサイズレジスタ(VSIZER)    | 5-32 |

| 5.3.9  | カーソル領域開始アドレスレジスタ(CSAR)     | 5-33 |

| 5.3.10 | 描画開始アドレスレジスタ ( RSAR )      | 5-34 |

| 5.4    | 表示制御レジスタ                   | 5-35 |

| 5.4.1  | 表示ウィンドウレジスタ(DSWR )         |      |

| 5.4.2  | 水平同期パルス幅レジスタ(HSWR)         | 5-36 |

| 5.4.3  | 水平走査周期レジスタ(HCR)            | 5-37 |

| 5.4.4  | 垂直同期位置レジスタ(VSPR)           | 5-37 |

| 5.4.5  | 垂直走査周期レジスタ(VCR)            | 5-37 |

| 5.4.6  | 表示オフ時出力レジスタ(DOOR )         |      |

| 5.4.7  | 色検出レジスタ(CDER)              |      |

| 5.4.8  | 等化パルス幅レジスタ(EQWR)           |      |

| 5.4.9  | セパレーション幅レジスタ(SPWR)         | 5-40 |

| 5.4.10 |                            |      |

| 5.4.11 | カーソル表示開始位置レジスタ ( CSR )     |      |

| 5.4.12 | カラーパレットレジスタ(CP000R~CP255R) | 5-43 |

| 5.5    | レンダリング制御レジスタ               |      |

| 5.5.1  | コマンドステータスレジスタ ( CSTR )     | 5-45 |

| 5.5.2  | カレントポインタレジスタ(CURR)         | 5-46 |

| 5.5.3  | ローカルオフセットレジスタ(LCOR)        |      |

| 5.5.4  | ユーザクリップエリアレジスタ(UCLR)       |      |

| 5.5.5  | システムクリップエリアレジスタ(SCLR)      | 5-48 |

| 5.5.6  | リターンアドレスレジスタ(RTNR)                  | 5-48 |

|--------|-------------------------------------|------|

| 5.5.7  | カラーオフセットレジスタ(COLOR)                 | 5-49 |

| 5.6    | データ転送制御レジスタ                         | 5-50 |

| 5.6.1  | DMA 転送開始アドレスレジスタ(DMASR)             | 5-50 |

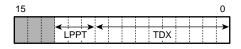

| 5.6.2  | DMA 転送語数レジスタ(DMAWR)                 | 5-51 |

| 5.6.3  | 画像データ転送開始アドレスレジスタ(ISAR)             | 5-52 |

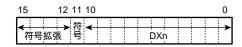

| 5.6.4  | 画像データサイズレジスタ(IDSR)                  | 5-53 |

| 5.6.5  | 画像データエントリレジスタ(IDER)                 | 5-53 |

| 6. 使用  | 上の注意事項                              | 6-1  |

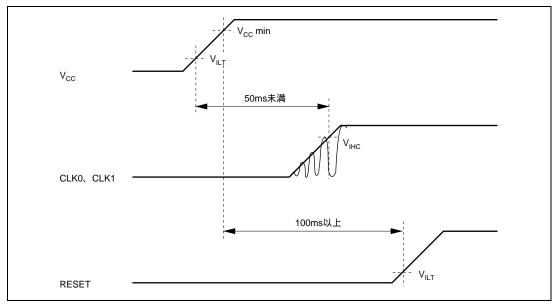

| 6.1    | パワーオンシーケンス                          | 6-1  |

| 6.2    | 64MビットSDRAM (×16タイプ)使用について          | 6-1  |

| 6.3    | CPUインタフェースユニットのFIFOについて             | 6-2  |

| 6.4    | ビデオ取り込み開始タイミングについて                  | 6-2  |

| 6.5    | リニア形式ソースを用いた描画について                  | 6-3  |

| 6.6    | Q2SDが設定するUGM用SDRAMのモードレジスタ値について     | 6-4  |

| 7. 電気  | 的特性                                 | 7-1  |

| 7.1    | 絶対最大定格                              | 7-1  |

| 7.2    | 推奨動作条件                              | 7-1  |

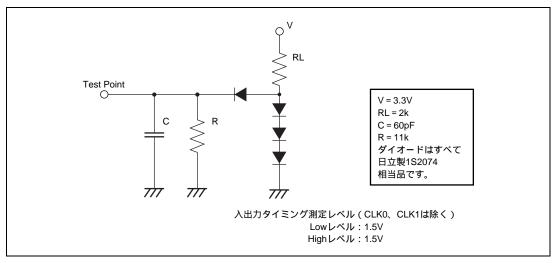

| 7.3    | 電気的特性測定方法                           | 7-2  |

| 7.3.1  | タイミング測定法                            | 7-2  |

| 7.3.2  | テスト負荷回路(全出力、全入出力端子)                 | 7-2  |

| 7.4    | 電気的特性                               | 7-3  |

| 7.4.1  | DC 特性                               | 7-3  |

| 7.4.2  | AC 特性                               | 7-4  |

| 7.5    | タイミングチャート                           | 7-10 |

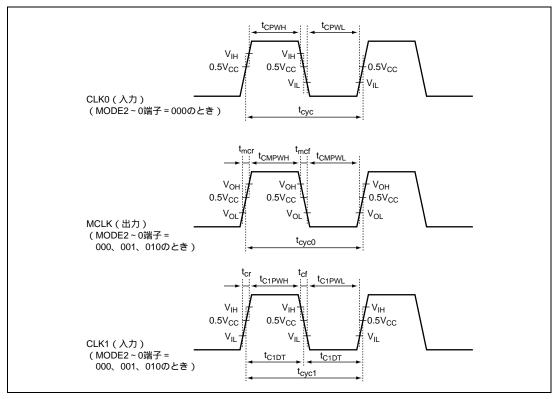

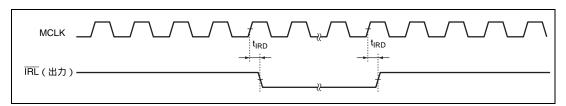

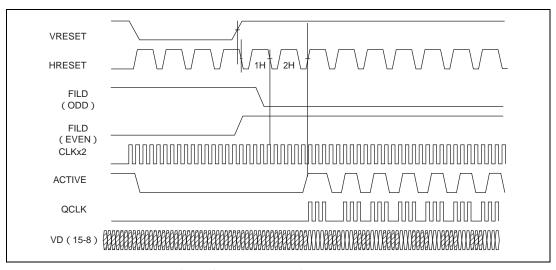

| 7.5.1  | クロック                                | 7-10 |

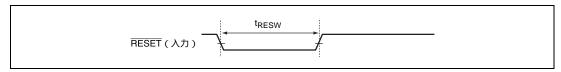

| 7.5.2  | リセットタイミング                           | 7-10 |

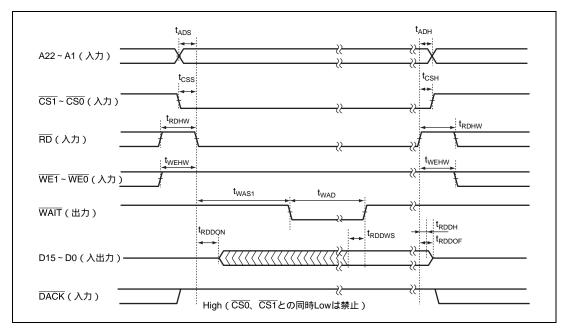

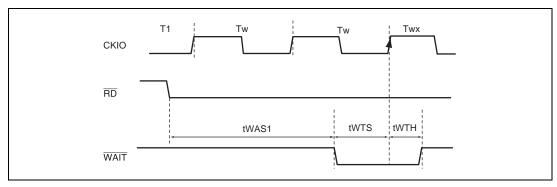

| 7.5.3  | CPU リードサイクルタイミング                    | 7-11 |

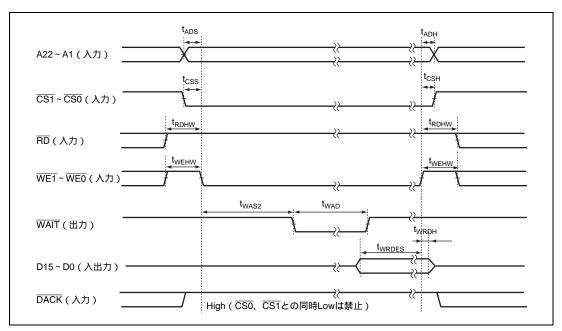

| 7.5.4  | CPU ライトサイクルタイミング                    | 7-11 |

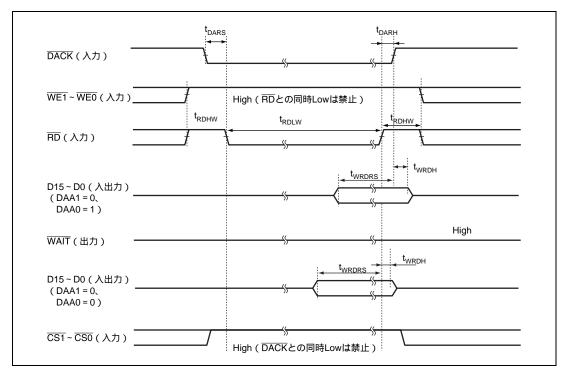

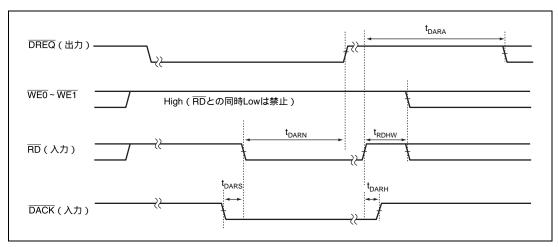

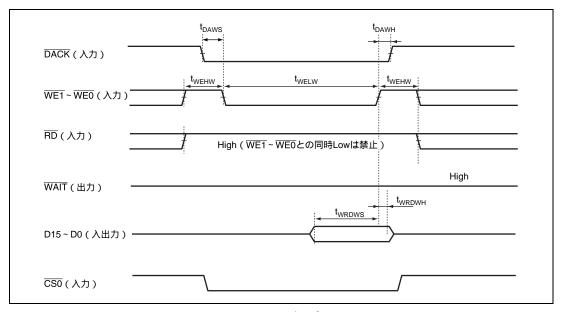

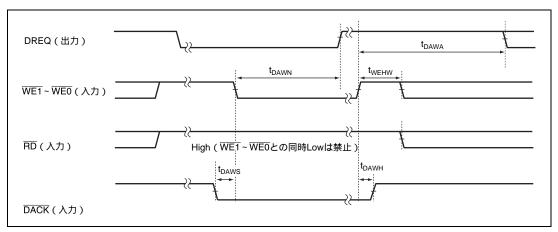

| 7.5.5  | DMA ライトサイクルタイミング ( DMAC Q2SD )      | 7-12 |

| 7.5.6  | 割り込み出力タイミング                         | 7-14 |

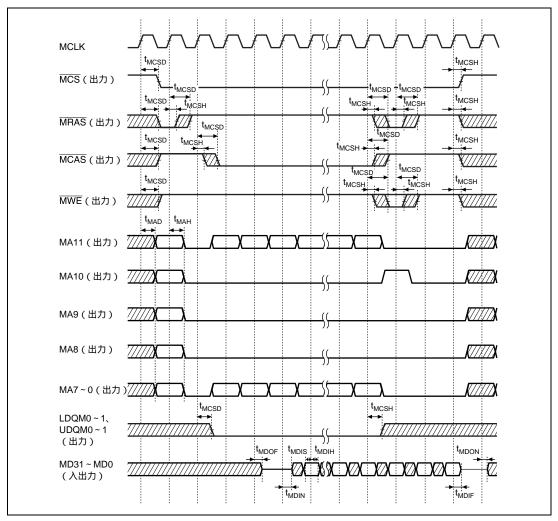

| 7.5.7  | UGM リードサイクルタイミング                    | 7-14 |

| 7.5.8  | UGM ライトサイクルタイミング                    |      |

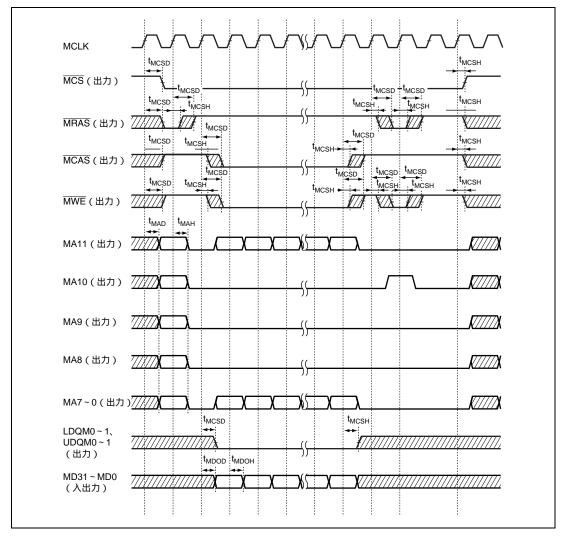

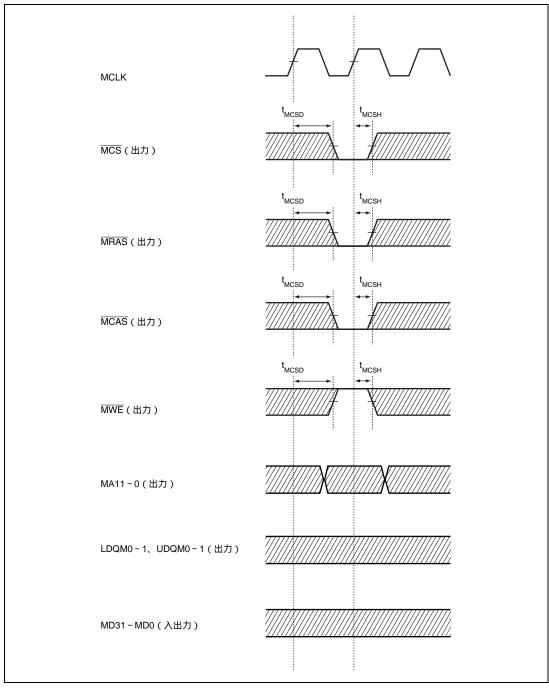

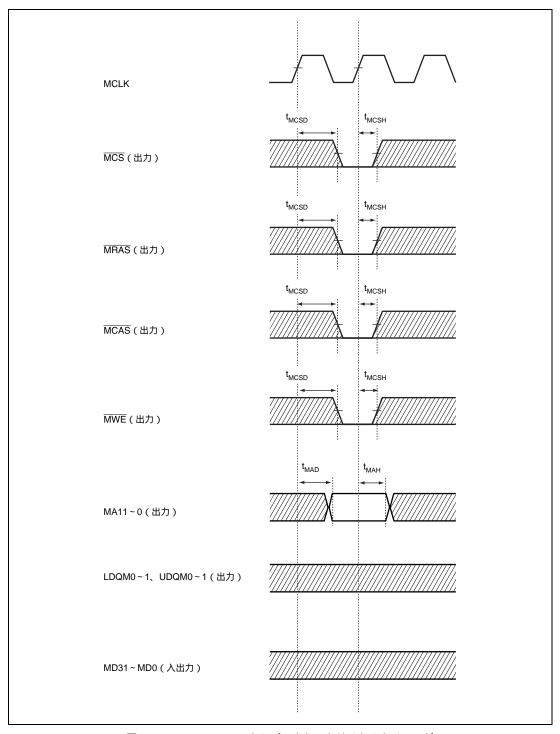

| 7.5.9  | UGM リフレッシュサイクルタイミング・モードレジスタセットタイミング | 7-16 |

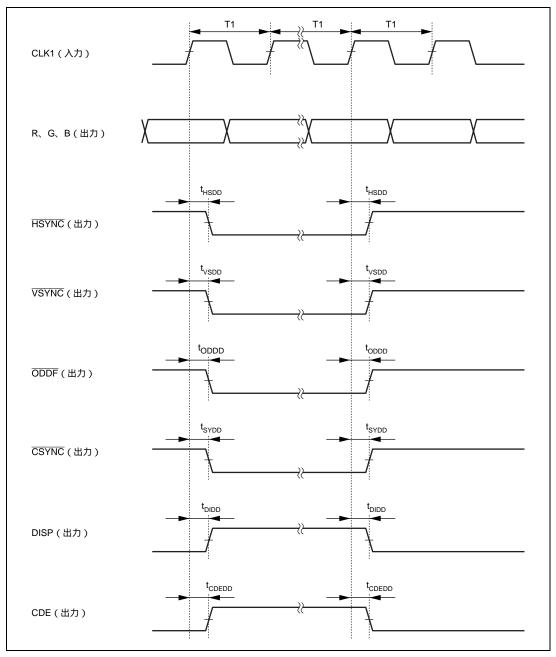

| 7.5.10 | マスタモード表示タイミング                       | 7-18 |

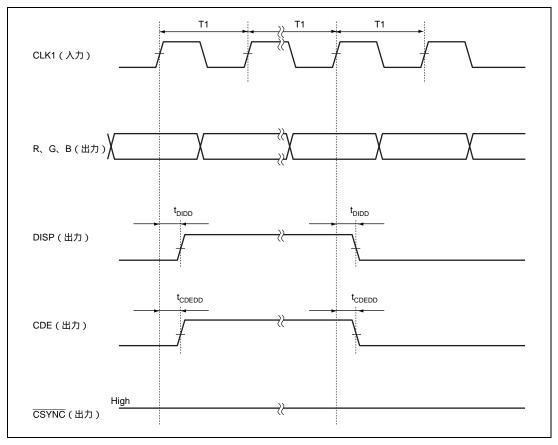

| 7.5.11 | TV 同期モード表示タイミング                     | 7-19 |

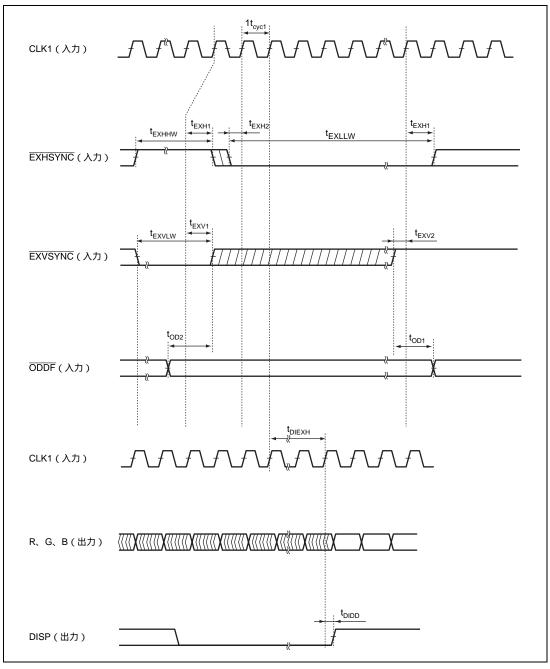

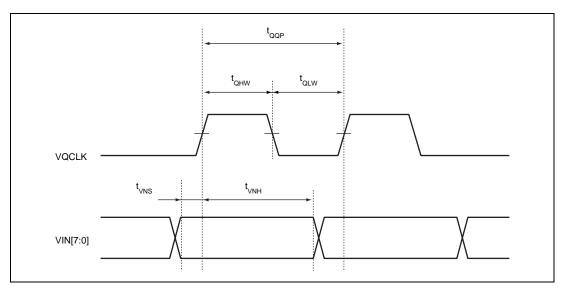

| 7.5.12 | ビデオインタフェースタイミング                     | 7-21 |

| 付録                                | 付録-1  |

|-----------------------------------|-------|

| A. レジスタの初期値                       | 付録-1  |

| A.1 レジスタのハードウェアリセット時の初期値          | 付録-1  |

| B. コマンドとパラメータ                     |       |

| B.1 コマンドとレンダリング属性の関係              | 付録-2  |

| B.2 コマンドのコマンドコード                  | 付録-3  |

| B.3 コマンドのパラメータ仕様                  | 付録-4  |

| C. 直線描画アルゴリズム                     | 付録-11 |

| D. パッケージ外形寸法図                     | 付録-13 |

| E. 表示動作クロックと画面合成について              | 付録-14 |

| F. SuperH.システム構成例                 | 付録-18 |

| F.1 クロックの決定                       | 付録-19 |

| F.2 ソフトウェアウェイトの設定                 | 付録-19 |

| F.3 接続時の注意事項                      | 付録-20 |

| F.4 アドレスマップドレジスタの初期化手順            | 付録-20 |

| F.5 メモリ割り当て                       | 付録-21 |

| F.5.1 HD64413Aのメモリマッピング           | 付録-21 |

| F.5.2 UGMにおける領域の配置例               | 付録-22 |

| F.5.3 UGMにおけるアドレスの連続性             | 付録-24 |

| F.6 UGMへのデータ転送における注意事項            | 付録-24 |

| G. 表示制御例                          | 付録-25 |

| G.1 表示サイズの決め方                     | 付録-25 |

| G.2 表示画面の選択方法                     | 付録-25 |

| G.3 同期信号の設定方法                     | 付録-26 |

| G.4 表示制御に関連するレジスタ値の設定および変更方法      | 付録-29 |

| G.4.1 カラーパレットの設定方法                | 付録-29 |

| G.4.2 同期モードの移行手順                  | 付録-29 |

| G.5 カーソル表示の行い方                    | 付録-30 |

| H. 描画制御例                          | 付録-31 |

| H.1 描画の開始方法例                      | 付録-31 |

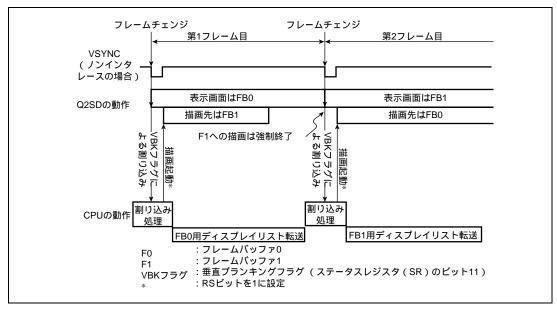

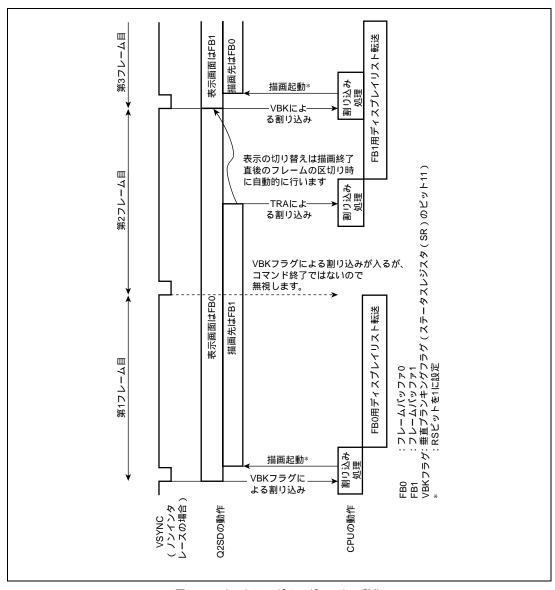

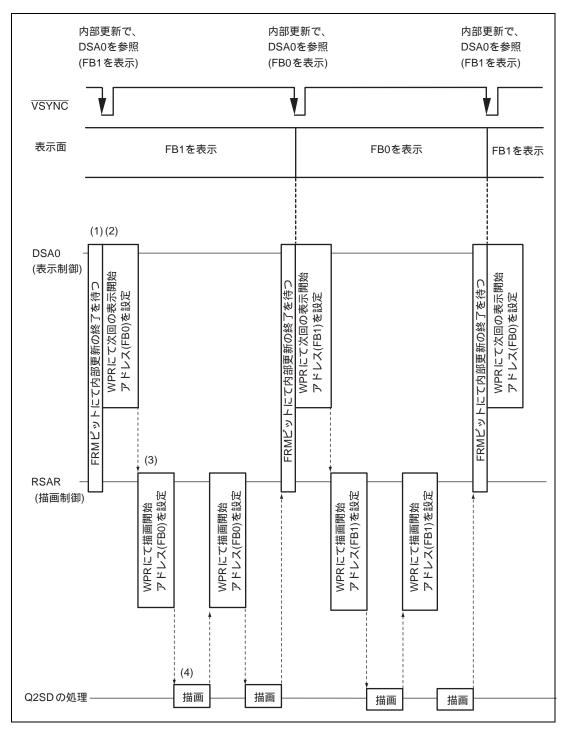

| H.2 内部更新でフレームチェンジを行う方法例           | 付録-32 |

| H.3 描画コマンドの使用例                    | 付録-34 |

| H.3.1 多角形の描画                      | 付録-34 |

| H.3.2 任意の形の描画                     | 付録-34 |

| H.3.3 円・楕円の描画                     | 付録-34 |

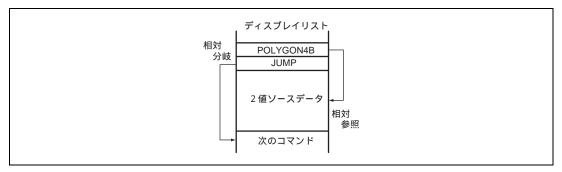

| H.3.4 ソースデータを使用した描画               | 付録-35 |

| H.3.5 3次元空間を表現させる方法               | 付録-35 |

| H.4 描画コマンドを使用する際の注意事項             | 付録-36 |

| H.4.1 ローカルオフセットとカレントポインタの関係に関する注意 | 付録-36 |

| H.4.2 相対系コマンドを使用する際の注意            | 付録-36 |

| H.4.3 ソースデータを使用する際の注意                | 付録-37 |

|--------------------------------------|-------|

| H.5 描画処理を支援する機能                      | 付録-38 |

| H.5.1 描画の中断・再開                       | 付録-38 |

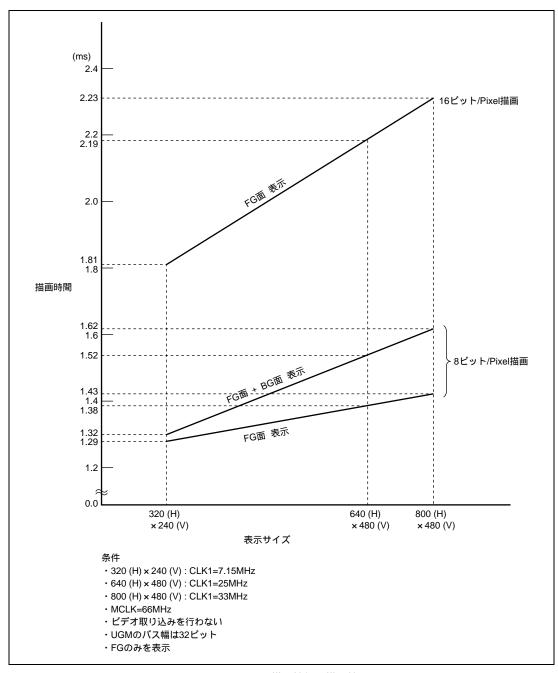

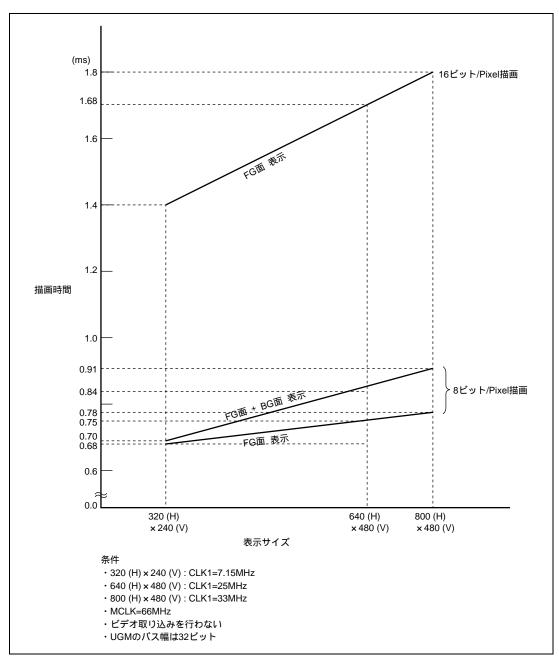

| I. 描画性能                              | 付録-40 |

| J. ビデオ取り込み機能の使用例                     | 付録-43 |

| J.1 ビデオ取り込み設定例                       | 付録-43 |

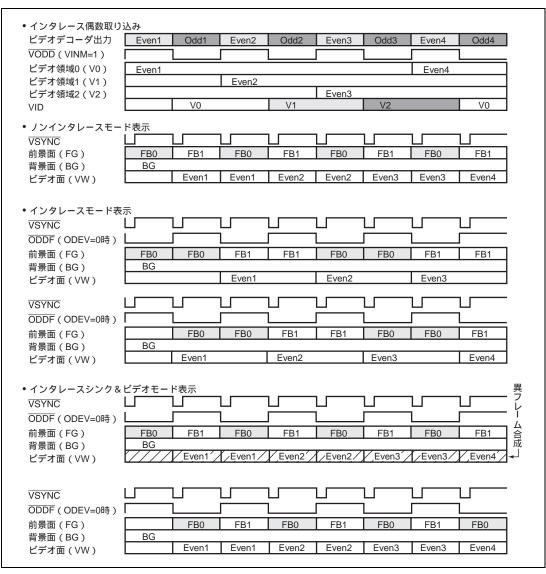

| J.1.1 インタレース合成取り込み例                  | 付録-43 |

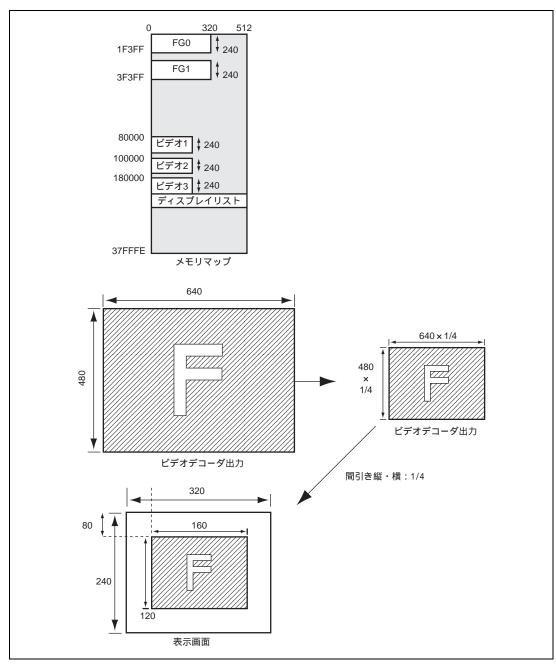

| J.1.2 ビデオデータのサイズ変更例                  | 付録-45 |

| J.2 ビデオ取り込みデータの利用例                   | 付録-47 |

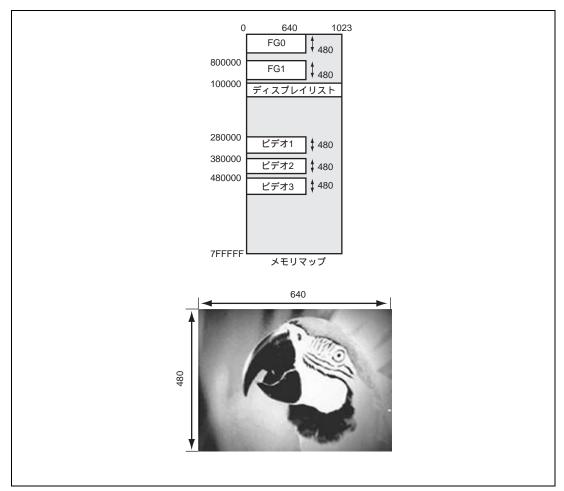

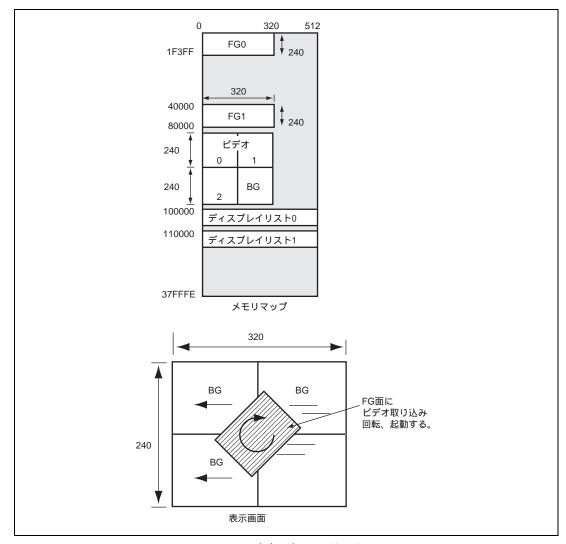

| J.2.1 ビデオ取り込みデータをリアルタイムビデオ面として表示する方法 | 付録-47 |

| J.2.2 ビデオ取り込みデータを多値ソースとして利用する方法      | 付録-47 |

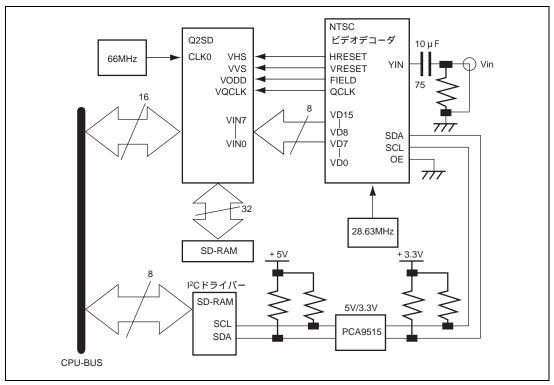

| J.3 ビデオデコーダ                          | 付録-53 |

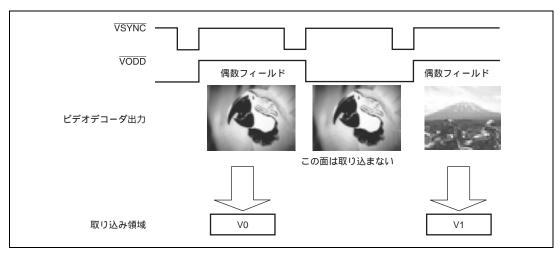

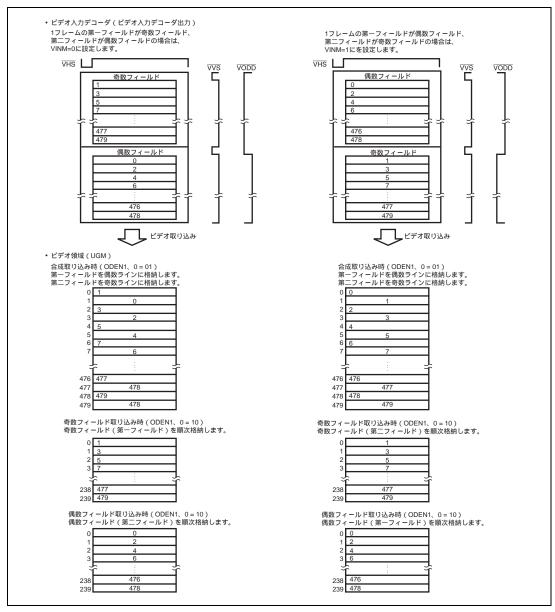

| J.3.1 ビデオデコーダのフィールド制御                | 付録-53 |

| J3.2 ビデオデコーダの設定                      | 付録-54 |

| K. 製品ラインナップ                          | 付録-55 |

# 図目次

| 1. | 概要                      |                                                                        |      |

|----|-------------------------|------------------------------------------------------------------------|------|

|    | 図1.1                    | システム構成例                                                                | 1-1  |

|    | 図1.2                    | システムの小型化を可能にするUGMアーキテクチャ                                               | 1-2  |

|    | 図1.3                    | システムバスインタフェースの一元化                                                      | 1-2  |

|    | 図1.4                    | ダブルバッファ                                                                | 1-3  |

|    | 図1.5                    | グラフィックスアクセラレータ                                                         | 1-4  |

|    | 図1.6                    | グラフィックス処理のパイプライン化                                                      | 1-4  |

|    | 図1.7                    | 表示合成機能                                                                 | 1-5  |

|    | 図1.8                    | デジタルビデオデータの取り込み                                                        | 1-5  |

|    | 図1.9                    | 3Dアルゴリズムを使用したときのデータの流れ                                                 | 1-6  |

|    | 図1.10                   | 内部ブロック図                                                                | 1-9  |

|    | 図1.11                   | 状態遷移図                                                                  | 1-10 |

| 2  | 端子                      |                                                                        |      |

| ۷. | <sup>- 如丁</sup><br>図2.1 | 端子構成                                                                   | 2-1  |

|    | 図2.2                    | ポリート                                                                   |      |

|    | 図2.3                    | CAP1、CAP2端子接続回路例                                                       |      |

|    | 図2.4                    | 端子近くの電源間バイパスコンデンサの接続                                                   |      |

|    | 図2.5                    | REXT、CBU、CBL端子接続回路例                                                    |      |

|    | 図2.6                    | ビデオ取り込み端子接続例                                                           |      |

| _  |                         |                                                                        |      |

| 3. |                         | <sup>7</sup> ーキテクチャ<br>UGMを使用したシステム構成例                                 | 2.1  |

|    |                         | UGMを使用したシステム構成例<br>CPUメモリ空間に対するUGMのマッピング例                              |      |

|    |                         | CPUメモリ全間に対するUGMのマッピング例                                                 |      |

|    | 図3.3                    | Marian                                                                 |      |

|    | 図3.4<br>図3.5            | 回家アークを換機能                                                              |      |

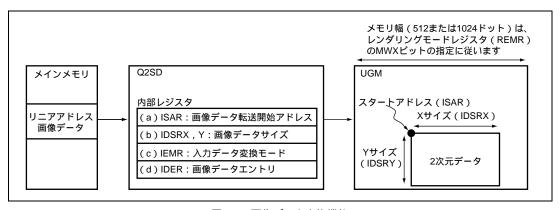

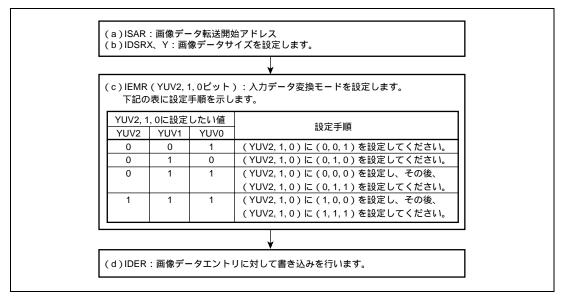

|    | 図3.6                    | 10V、10V RGB复換時のレジスタ設定于順                                                |      |

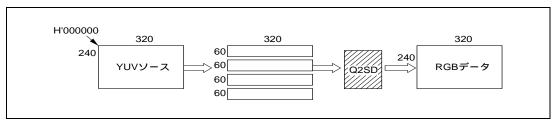

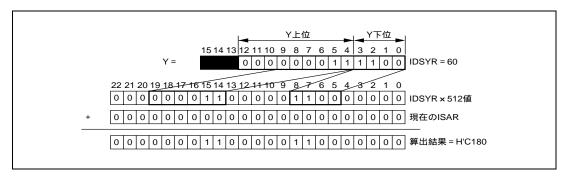

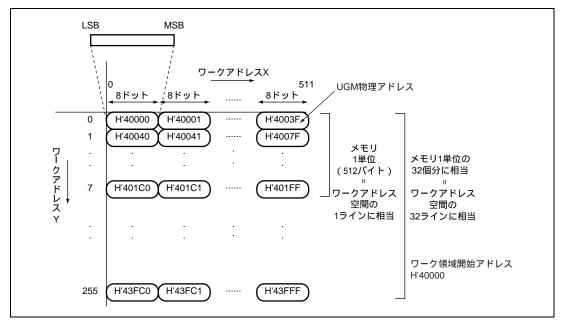

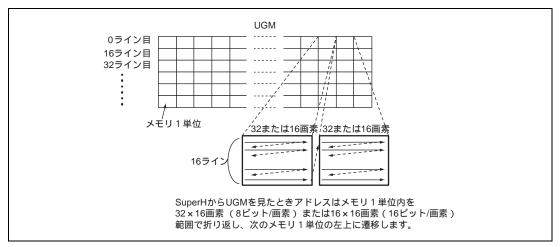

|    | 図3.7                    | 320×2400 1 0 v ) ーラを4回のDMA_1 0 v C UGMに転送することの設定例<br>メモリ1単位(512バイト)の構成 |      |

|    | 図3.7<br>図3.8            | UGMのアドレス進行                                                             |      |

|    | 図3.9                    | UGM切アドレス (バイト) と2次元論理アドレスとの対応                                          |      |

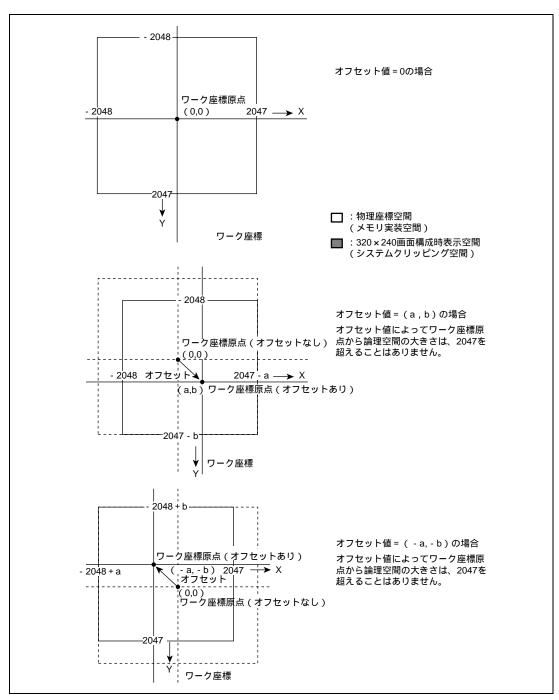

|    | 図3.10                   | ワークアドレス空間                                                              |      |

|    | 図3.10                   | リーケアドレス                                                                |      |

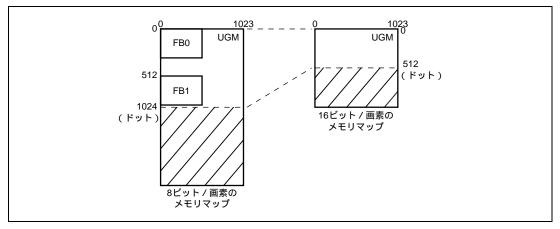

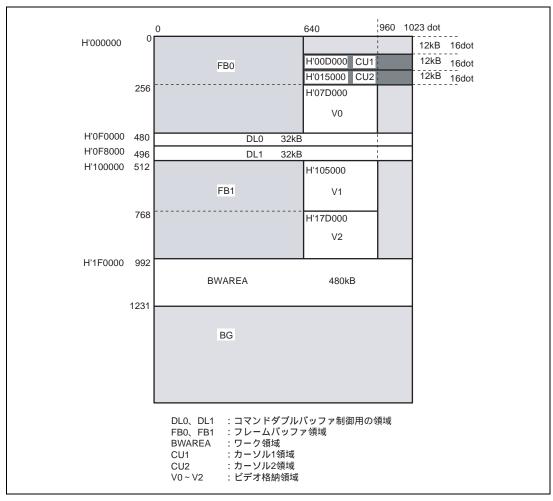

|    | 図3.11                   | びMM程/アトレス (ハイド) と ラーグ/アトレスとの対心<br>メモリマップ例 (16ビット/画素時 画面サイズ640×480相当時)  |      |

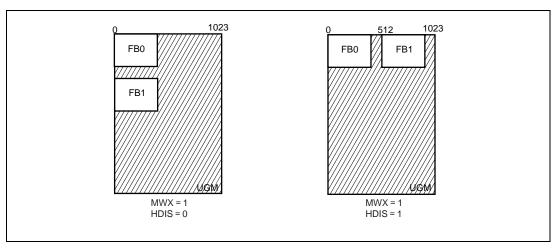

|    | 図3.12                   | 8ビット/画素と16ビット/画素の関係                                                    |      |

|    | 図3.13                   | 800年7回系と1009F7回系の関係<br>HDIS = 1のフレームバッファFB1の配置                         |      |

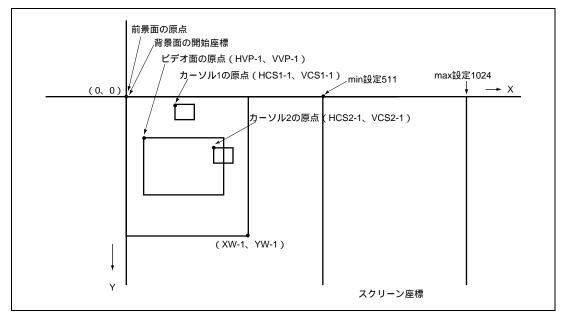

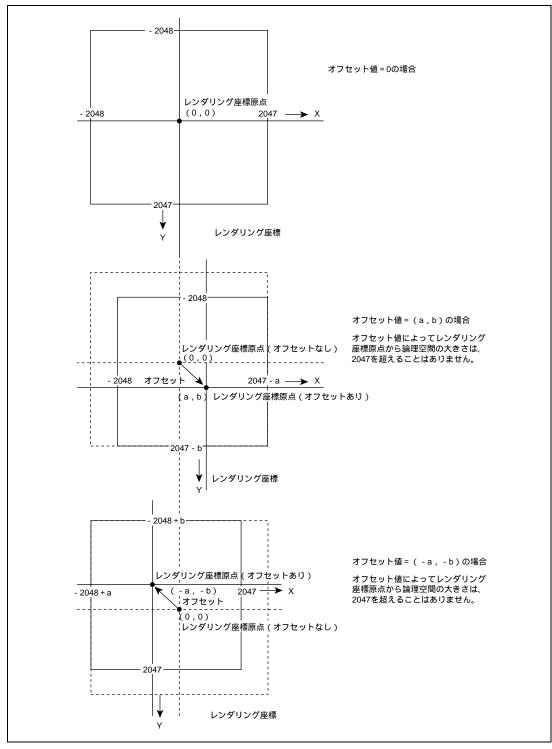

|    | 図3.14                   | スクリーン座標                                                                |      |

|    | 図3.15<br>図3.16          | スクリーノ座標                                                                |      |

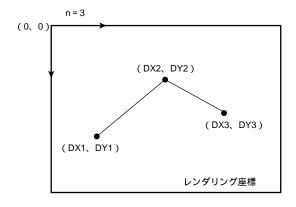

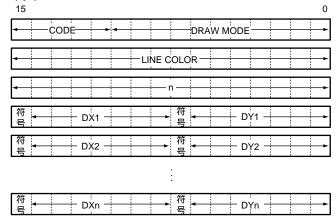

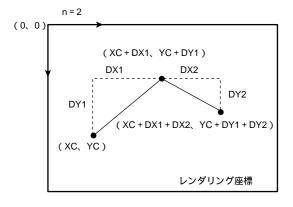

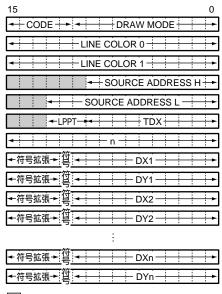

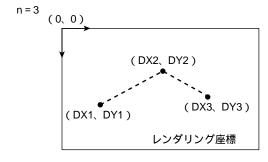

|    | 図3.16<br>図3.17          | レンダリンク座標                                                               |      |

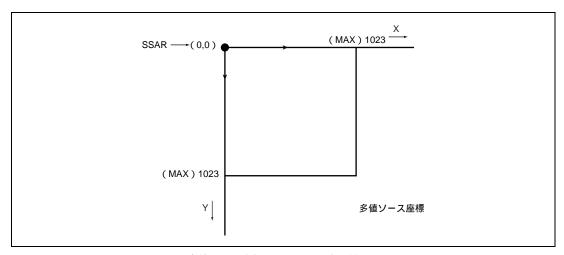

|    | 図3.17<br>図3.18          | 多値ソース座標(LNi=0、2次元論理アトレス)                                               |      |

|    | 図3.18<br>図3.19          | 多値ソース座標(LNI=1、リーアアトレス)<br>2値ソース座標                                      |      |

|    | 四3.19                   | ∠⊫ノ ̄ヘ圧伝                                                               | 3-28 |

| 図3.20   | ワーク座標                                | 3-29 |

|---------|--------------------------------------|------|

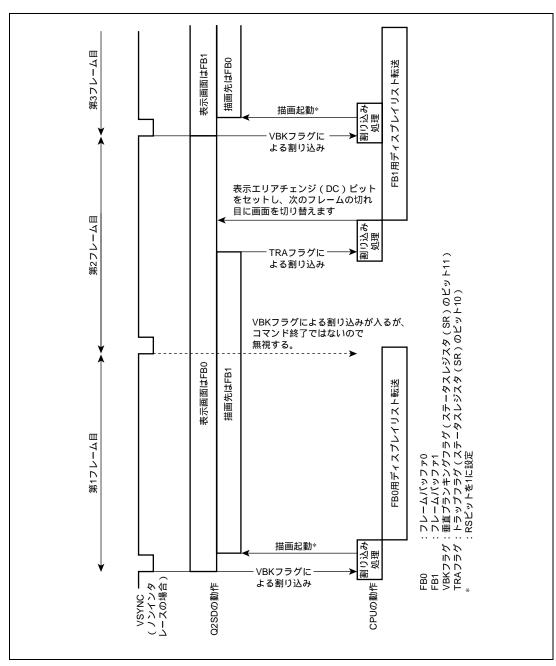

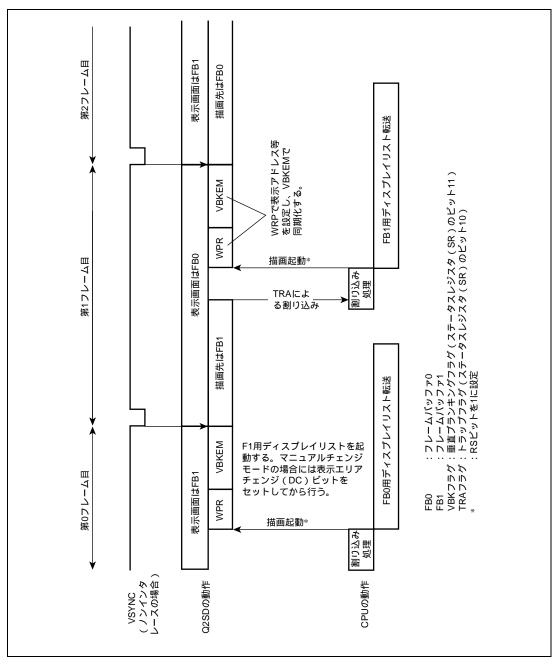

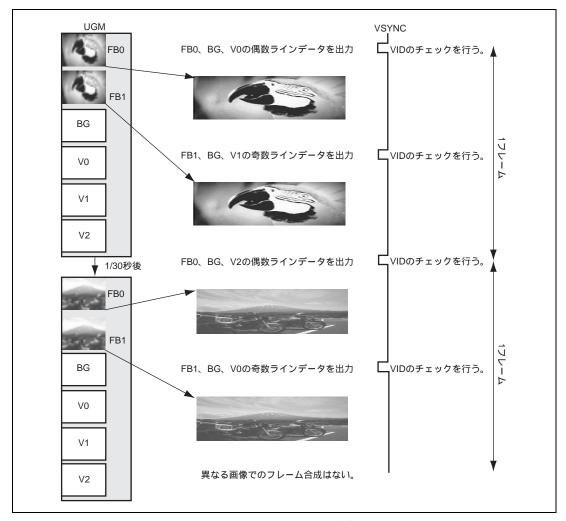

| 図3.21   | オートディスプレイチェンジモードの動作                  | 3-32 |

| 図3.22   | オートレンダリングモードの動作                      | 3-33 |

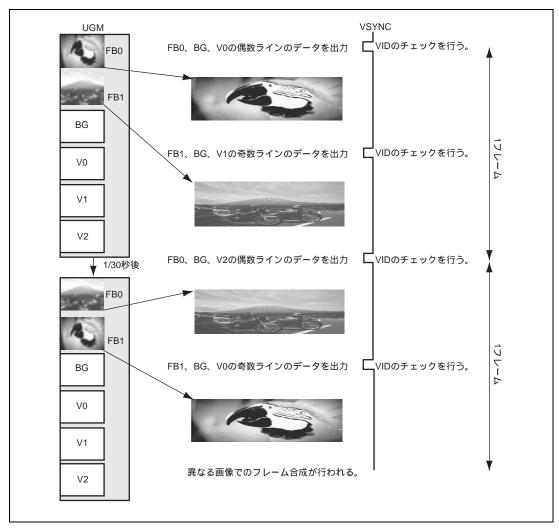

| 図3.23   | マニュアルディスプレイチェンジモードの動作                | 3-35 |

| 図3.24   | VBKEMコマンドによる動作                       | 3-36 |

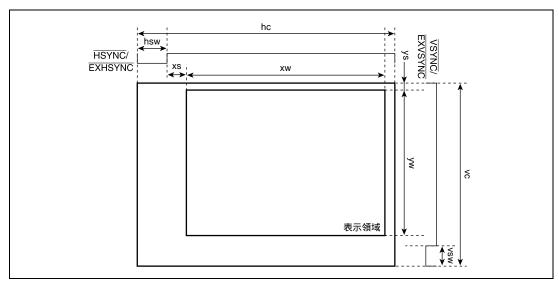

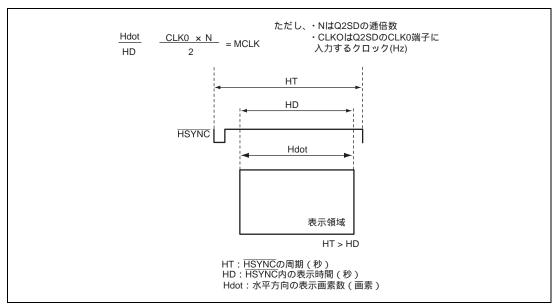

| 図3.25   | 表示タイミング                              | 3-38 |

| 図3.26   | Q2SDの画面表示構成                          | 3-40 |

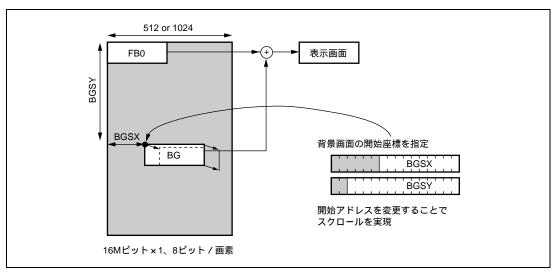

| 図3.27   | 背景画面の単純スクロール (WRAP=0)の例              | 3-42 |

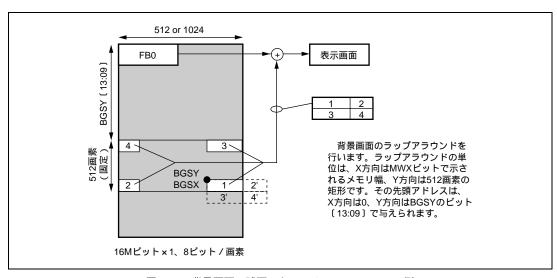

| 図3.28   | 背景画面の球面スクロール(WRAP=1)の例               | 3-42 |

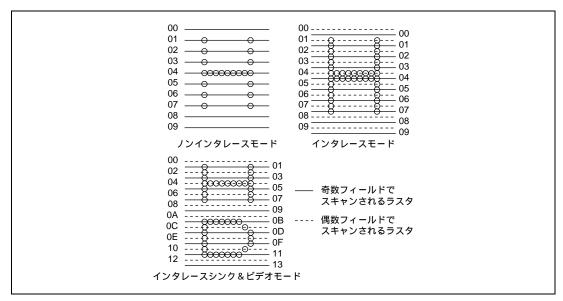

| 図3.29   | ラスタスキャン制御の表示例                        | 3-43 |

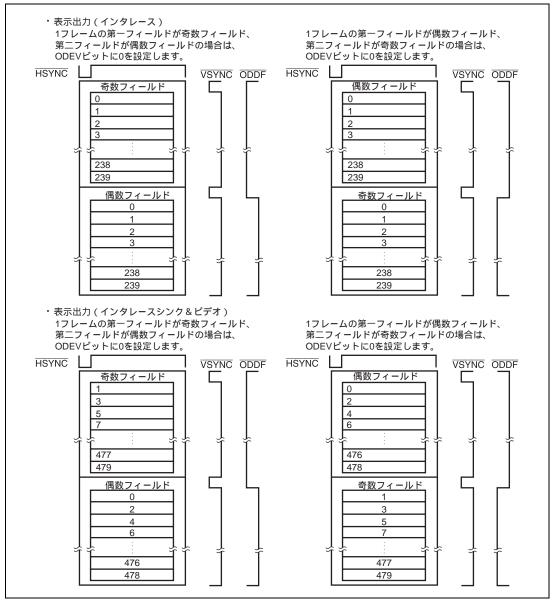

| 図3.30   | インタレースシンク方式の表示                       | 3-44 |

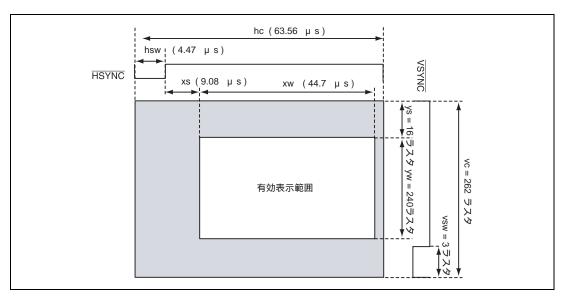

| 図3.31   | ノンインタレース方式の表示                        | 3-45 |

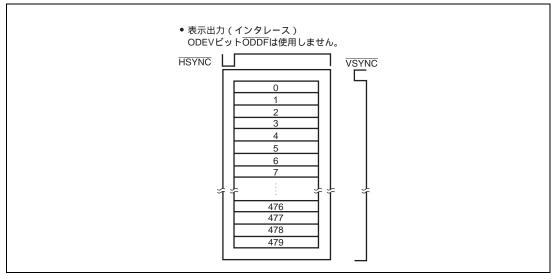

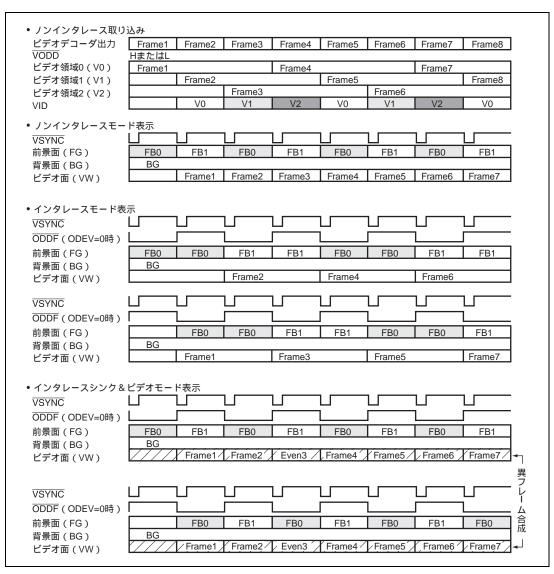

| 図3.32   | ノンインタレースモード表示出力                      | 3-46 |

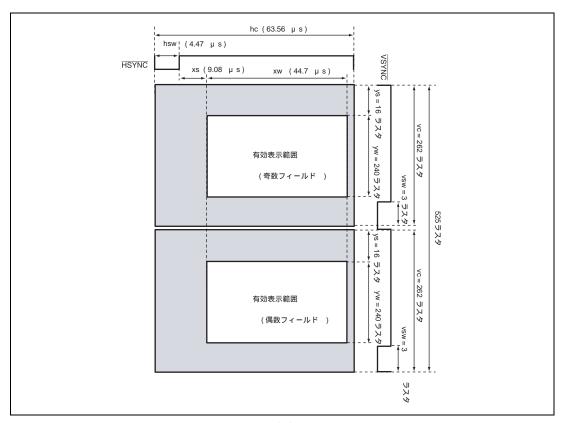

| 図3.33   | インタレースモード表示出力                        | 3-47 |

| 図3.34 ( | (1) インタレースシンク&ビデオモード出力               | 3-48 |

| 図3.34 ( | ( 2 ) インタレースシンク&ビデオモードの出力            | 3-49 |

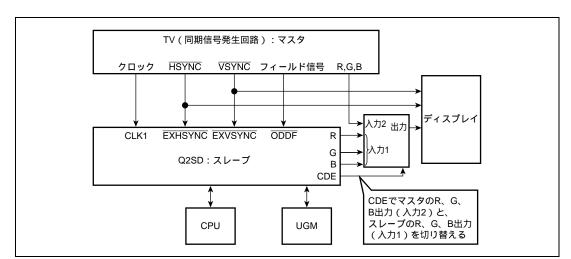

| 図3.35   | TV同期モード時の信号の流れ                       | 3-51 |

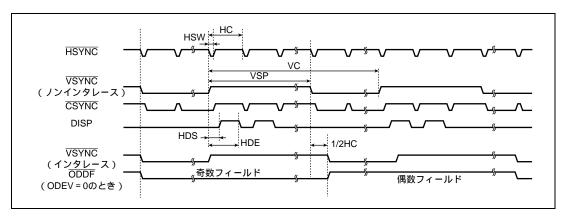

| 図3.36   | 表示タイミング                              | 3-52 |

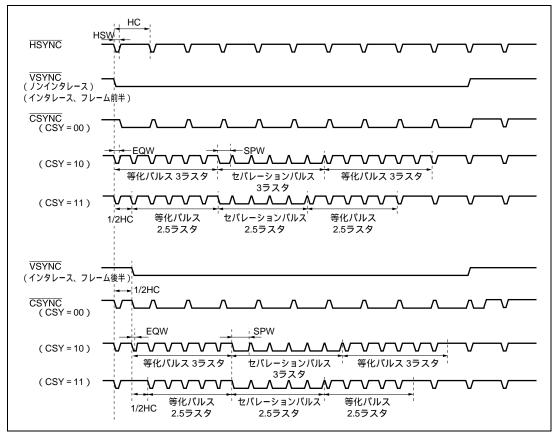

| 図3.37   | CSYNC出力波形                            | 3-52 |

| 図3.38   | 描画機能                                 |      |

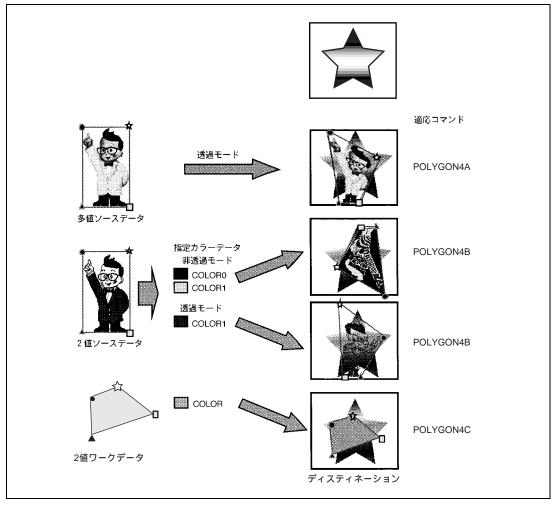

| 図3.39   | POLYGON4系転送データの組み合わせ例                | 3-56 |

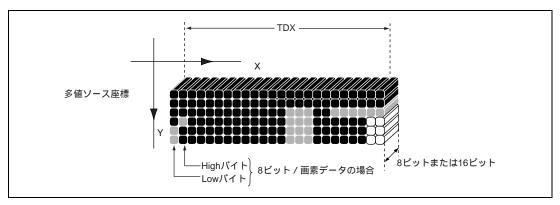

| 図3.40   | 多値ソースデータの構成                          |      |

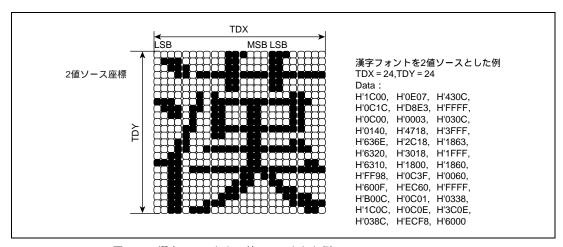

| 図3.41   | 漢字フォントを2値ソースとした例 (TDX = 24、TDY = 24) | 3-57 |

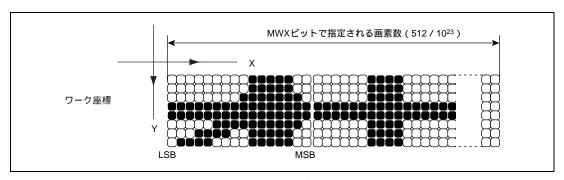

| 図3.42   | 2値ワークデータの構成                          | 3-58 |

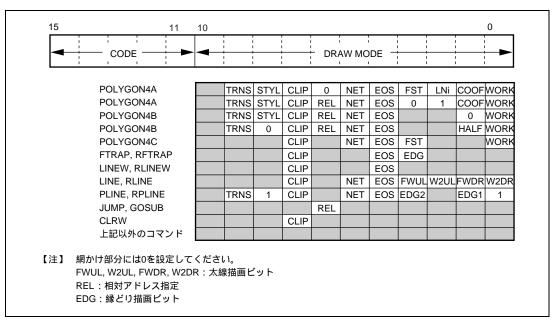

| 図3.43   | レンダリング属性のビット配置                       | 3-59 |

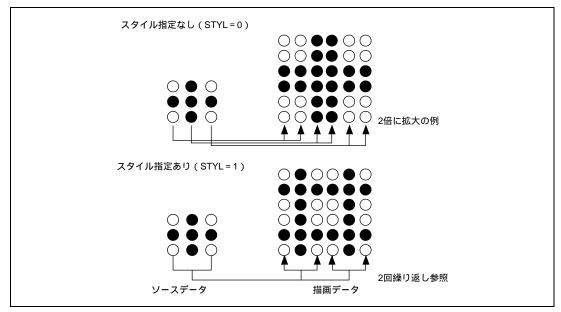

| 図3.44   | ソーススタイル指定例                           | 3-60 |

| 図3.45   | クリッピング指定例                            | 3-61 |

| 図3.46   | イープンオッドセレクト指定例                       | 3-61 |

| 図3.47   | 太線描画の例(線幅4の描画例)ただし、FWUL=1かつFWDR=1    | 3-63 |

| 図3.48   | ディスプレイリスト例                           |      |

| 図3.49   | 背景面に対する描画の中断・再開タイミング例                | 3-67 |

| 図3.50   | Q2SD内のバッファ更新                         | 3-68 |

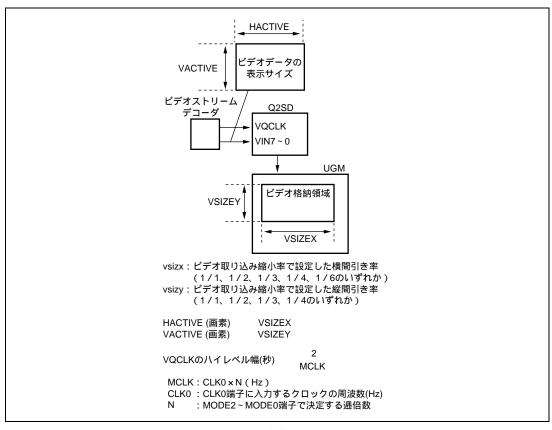

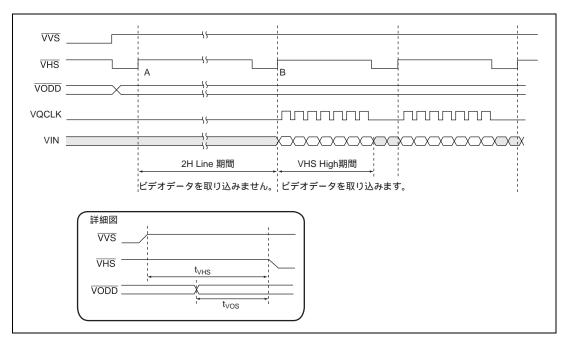

| 図3.51   | ビデオ取り込み信号                            |      |

| 図3.52   | ビデオ取り込みタイミング                         |      |

| 図3.53   | 取り込み状態                               | 3-70 |

| 図3.54   | 表示状態                                 |      |

| 図3.55   | ビデオ格納領域                              |      |

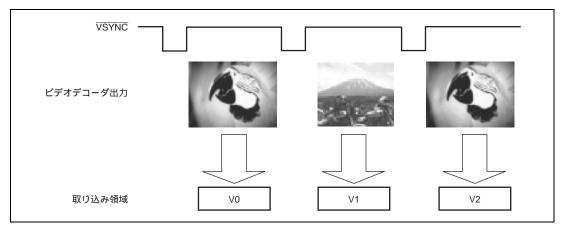

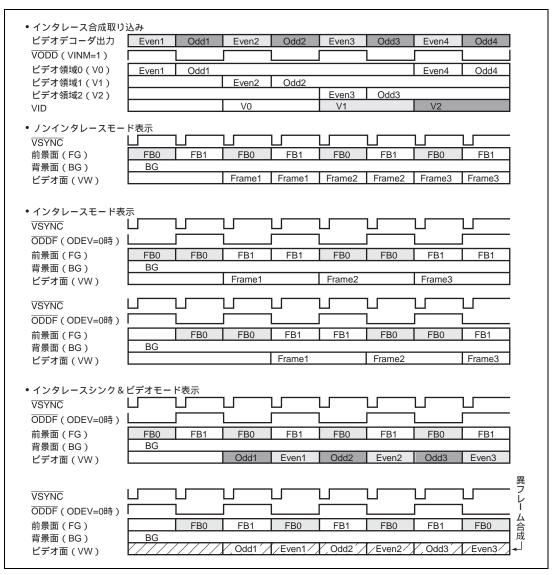

|         | インタレース取り込み                           |      |

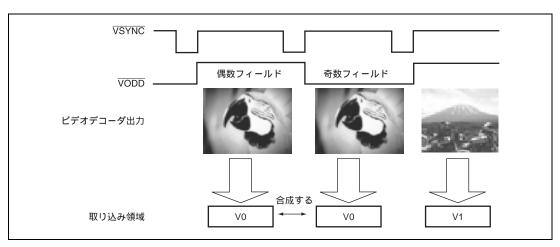

|         | インタレース合成取り込み                         |      |

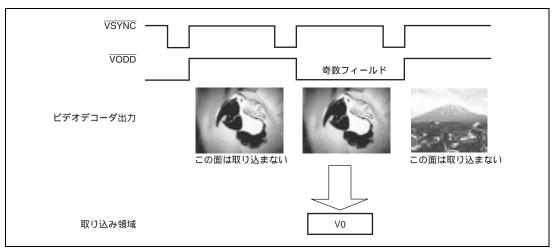

|         | インタレース取り込み(奇数)                       |      |

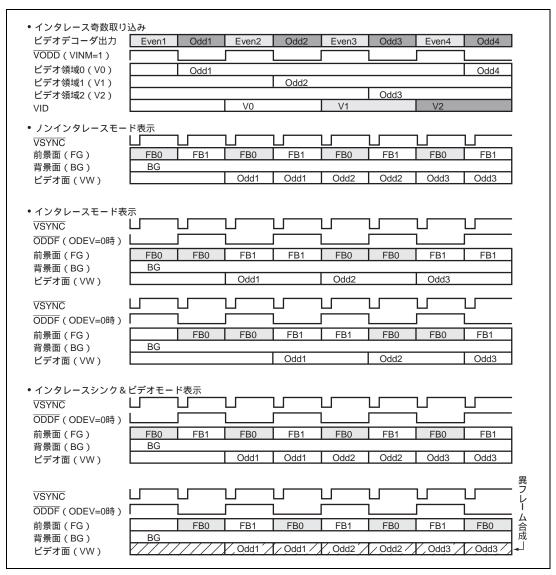

| 図3.59   | インタレース取り込み(偶数)                       |      |

| 図3.60   | インタレースのビデオ入力フィールド取り扱い指定              |      |

| 図3.61   | ビデオ取り込み時の間引き                         |      |

| 図3.62   | ビデオ取り込み時の間引き設定の失敗                    |      |

| 図3.63   | ビデオ取り込み領域の設定                         |      |

| 図3.64   | ビデオ取り込み領域設定例                         |      |

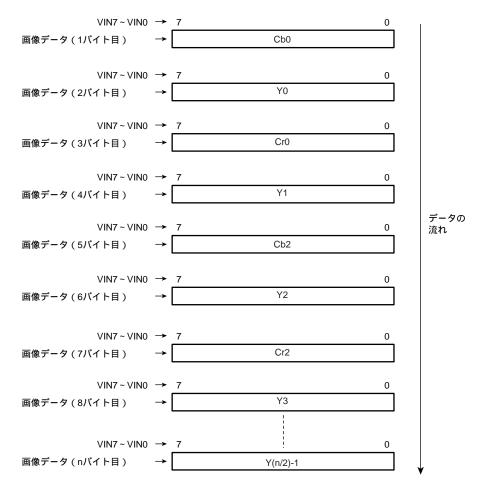

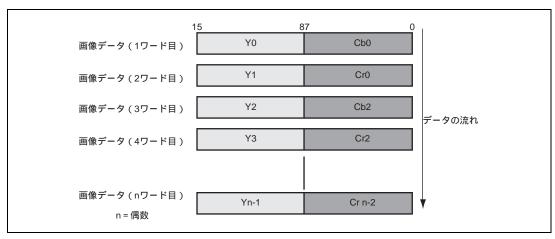

| 図3.65   | YCbCr 4:2:2データの流れ                    | 3-79 |

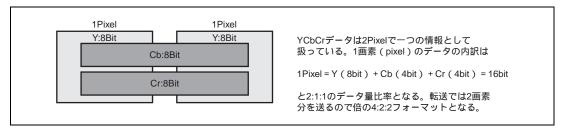

|                                               | 図3.66 YCbCr 4:2:2データの形式                      | 3-79  |

|-----------------------------------------------|----------------------------------------------|-------|

|                                               | 図3.67 YCbCr RGB变换                            |       |

|                                               | 図3.68 RGBデータ (16ビット/画素)                      | 3-81  |

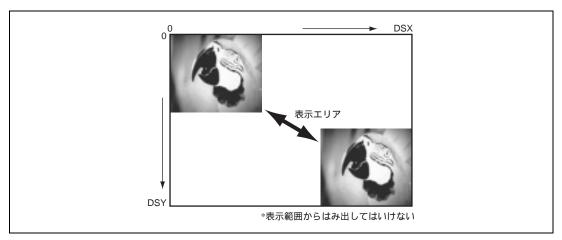

|                                               | 図3.69 ビデオ画面表示位置                              |       |

|                                               | 図3.70 インタレースモード取り込みと表示との相関                   |       |

|                                               | 図3.71 インタレース合成モード取り込みと表示との相関                 |       |

|                                               | 図3.72 インタレース奇数モード取り込みと表示との相関                 |       |

|                                               | 図3.73 インタレース偶数モード取り込みと表示との相関                 |       |

|                                               |                                              |       |

| 6.                                            | 使用上の注意事項                                     |       |

|                                               | 図6.1 パワーオンシーケンス                              |       |

|                                               | 図6.2 ビデオインタフェースタイミング                         | 6-2   |

| 7                                             | 命气的排土                                        |       |

| 7.                                            | 電気的特性                                        | 7.0   |

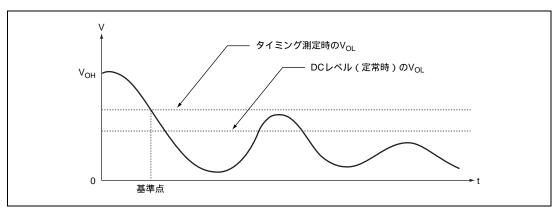

|                                               | 図7.1 V <sub>o.</sub> のタイミング測定基準              | 7.2   |

|                                               | 図7.2 テスト負荷回路                                 |       |

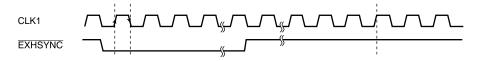

|                                               | 図7.3 入力クロック                                  |       |

|                                               | 図7.4 リセットタイミング                               |       |

|                                               | 図7.5 CPUリードサイクルタイミング (CPU Q2SD) ハードウェアウェイトあり |       |

|                                               | 図7.6 CPUライトサイクルタイミング (CPU Q2SD) ハードウェアウェイトあり |       |

|                                               | 図7.7(1) DMAライトサイクルタイミング(シングルアドレス、DMAC Q2SD)  |       |

|                                               | 図7.7(2) DMAライトサイクルタイミング(シングルアドレス、DMAC Q2SD)  |       |

|                                               | 図7.7(3) DMAライトサイクルタイミング(デュアルアドレス、DMAC Q2SD)  |       |

|                                               | 図7.7(4) DMAライトサイクルタイミング (デュアルアドレス、DMAC Q2SD) |       |

|                                               | 図7.8 割り込み出力タイミング                             |       |

|                                               | 図7.9 UGMリードサイクルタイミング                         |       |

|                                               | 図7.10 UGMライトサイクルタイミング                        |       |

|                                               | 図7.11(1) UGMリフレッシュサイクルタイミング                  |       |

|                                               | 図7.11(2) UGMモードレジスタセットサイクルタイミング              |       |

|                                               | 図7.12 マスタモード表示タイミング                          | 7-18  |

|                                               | 図7.13(1) TV同期モード表示タイミング                      |       |

|                                               | 図7.13(2) TV同期モード表示タイミング                      | 7-20  |

|                                               | 図7.14(1) ビデオインタフェースタイミング                     | 7-21  |

|                                               | 図7.14(2) ビデオインタフェースタイミング                     | 7-21  |

| <u>, , , , , , , , , , , , , , , , , , , </u> | A=                                           |       |

| 付釒                                            |                                              |       |

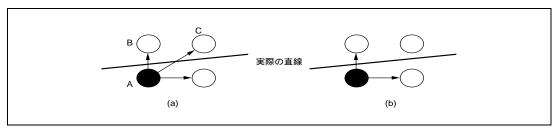

| C.                                            | 直線描画アルゴリズム                                   |       |

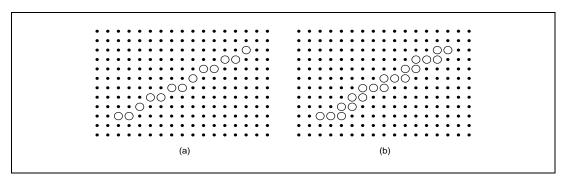

|                                               | 図C.1 ラスタディスプレイ上での直線の2つの表現                    | 付録-11 |

|                                               | 図C.2 (a) 8点法と(b) 4点法の比較                      |       |

|                                               | 図C.3 (a) 8点法描画と(b) 4点法描画の描画点決定プロセスの比較        | 付録-12 |

|                                               |                                              |       |

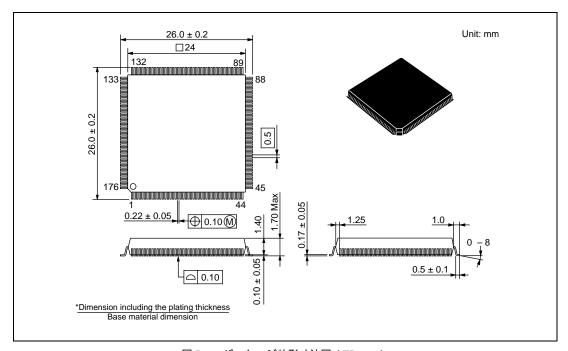

| D.                                            | パッケージ外形寸法図                                   |       |

|                                               | 図D.1 パッケージ外形寸法図 (FP-176)                     | 付録-13 |

| F.                                            | SuperH.システム構成例                               |       |

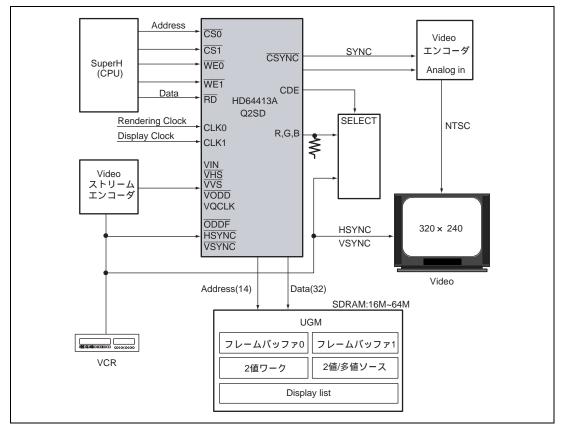

|                                               | 図F.1 システム構成例                                 | 付緑-18 |

|                                               | 図F.2 インタフェースタイミング例                           |       |

|                                               | 図F.3 メモリマッピング例                               |       |

|                                               | ——————————————————————————————————————       | 1     |

|    | 図F.4         | UGMメモリマップ                                        | 付録-23 |

|----|--------------|--------------------------------------------------|-------|

|    | <b>図</b> F.5 | UGMのアドレス遷移概要                                     | 付録-24 |

|    | <del>_</del> | Man Pol                                          |       |

| G. | 表示制          |                                                  |       |

|    | 図G.1         | 24.3.7 1 4- 7 1/3                                |       |

|    |              | ノンインタレースモード時の表示タイミング例                            |       |

|    | 図G.3         | インタレースシンク&ビデオモード時の表示タイミング例                       | 付録-28 |

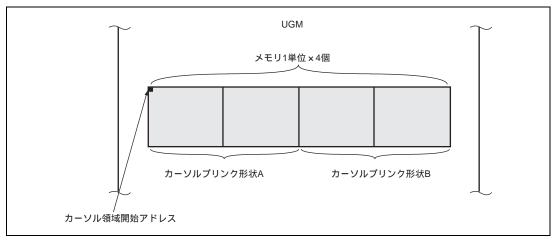

|    | 図G.4         | カーソル割当て                                          | 付録-30 |

| H. | 描画制          | 御例                                               |       |

|    | 図H.1         | DBF = 0時の表示・描画制御タイミングチャート                        | 付録-33 |

|    |              | 参照・分岐例                                           |       |

|    |              |                                                  |       |

| I. | 描画性          | 能                                                |       |

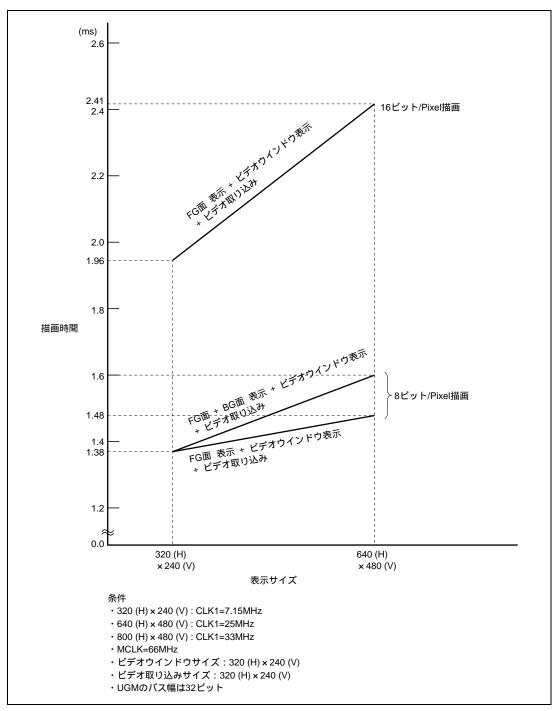

|    | 図I.1         | FST = 0のときのPOYLGON4Cの描画性能(描画範囲: 320(H) × 240(V)) | 付録-40 |

|    | <b>図</b> I.2 | FST = 1のときのPOYLGON4Cの描画性能(描画範囲: 320(H) × 240(V)) | 付録-41 |

|    | <b>図</b> I.3 | FST = 0のPOYLGON4Cの描画性能(描画範囲:320(H) × 240(V))     | 付録-42 |

| J. | ビデオ          | 取り込み機能の使用例                                       |       |

|    | 図J.1         | インタレース合成取り込み                                     | 付録-44 |

|    | 図J.2         | 縦1/4横1/4間引きインタレース合成取り込み                          |       |

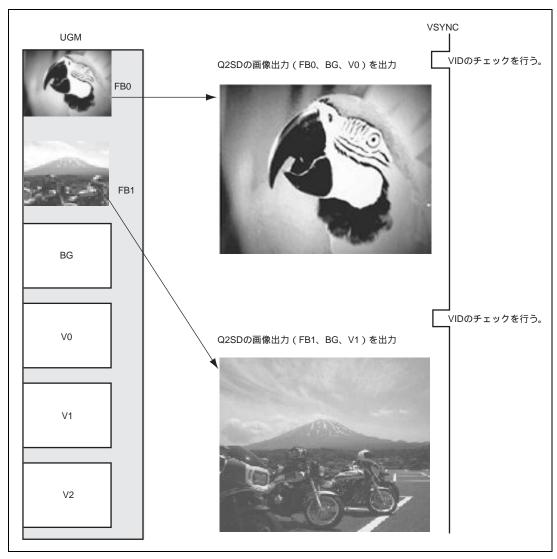

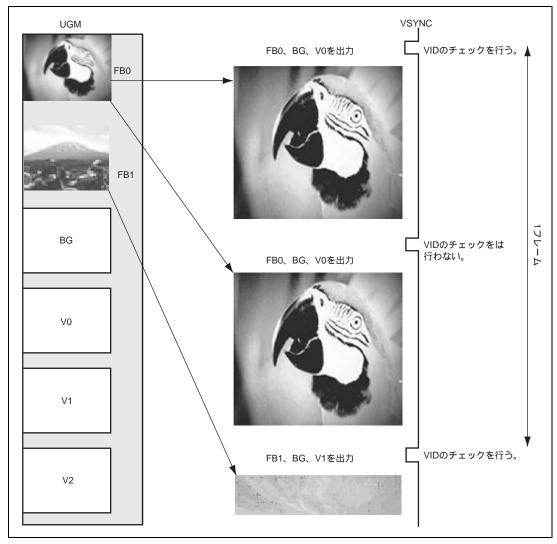

|    | <b>図</b> J.3 | ビデオデータの利用例                                       | 付録-49 |

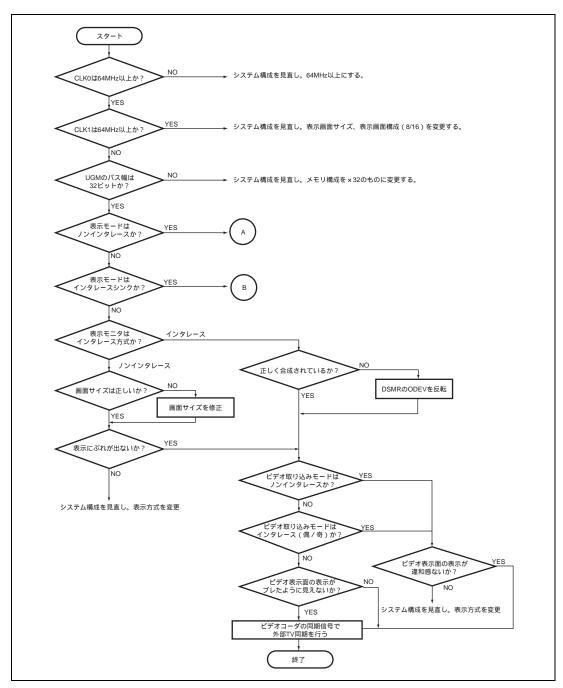

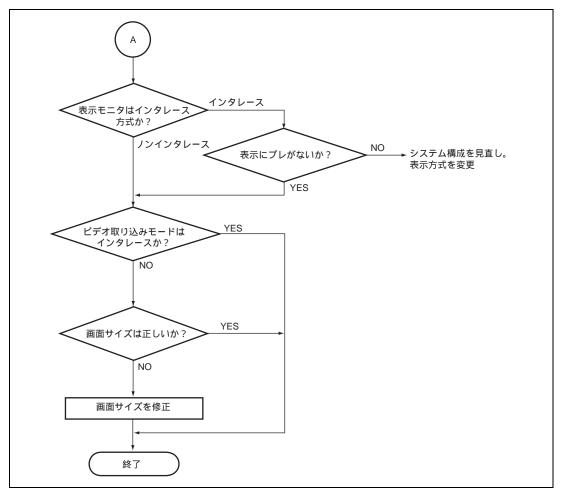

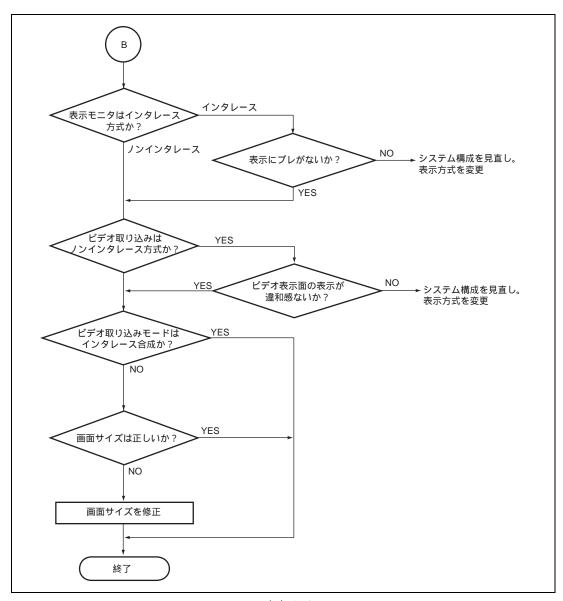

|    | <b>図</b> J.4 | Q2SDビデオ設定フロー (1)                                 | 付録-50 |

|    | 図J.5         | Q2SDビデオ設定フロー (2)                                 | 付録-51 |

|    | <b>図</b> J.6 | Q2SDビデオ設定フロー (3)                                 |       |

|    | 図J.7         | 取り込み回路構成例                                        |       |

|    | <b>図</b> J.8 | デコーダのインタレースデータの出力タイミング例                          | 付録-54 |

# 表目次

| 1. | 概要    |                                       |                 |

|----|-------|---------------------------------------|-----------------|

|    | 表1.1  | 製品仕様                                  |                 |

|    | 表1.2  | リセット直後の端子状態                           | 1-11            |

| _  | ᅭ     |                                       |                 |

| 2. | 端子    | 111 - 7 186 AP                        |                 |

|    | 表2.1  | 端子機能                                  |                 |

|    | 表2.2  | 動作モードの選択                              |                 |

|    | 表2.3  | 入力クロックと動作周波数                          | 2-9             |

| 3. | UGM : | アーキテクチャ                               |                 |

|    | 表3.1  | 内部更新機能付きレジスタ                          | 3-5             |

|    | 表3.2  | 割り込み出力機能                              |                 |

|    | 表3.3  | リフレッシュサイクル数の設定                        |                 |

|    | 表3.4  | リフレッシュサイクル数見積例                        |                 |

|    | 表3.5  | 表示画面で定義した変数                           |                 |

|    | 表3.6  | レジスタ設定値対応表                            | 3-39            |

|    | 表3.7  | 背景画面に関するレジスタ設定                        | 3-42            |

|    | 表3.8  | Q2SDの表示とモニタの選択                        | 3-45            |

|    | 表3.9  | コマンドー覧表                               |                 |

|    | 表3.10 | 大線描画の設定                               | 3-63            |

|    | 表3.11 | 8Bit Pixel Interface                  | 3-79            |

|    | 表3.12 |                                       | 3-87            |

|    |       |                                       |                 |

| 4. |       | プレイリスト                                |                 |

|    | 表4.1  | コマンドー覧表                               | 4-1             |

| 5. | レジス   | 9                                     |                 |

| ٠. |       | ・・<br>レジスタマップ                         | 5-1             |

|    |       | ビット構成                                 |                 |

|    |       | YUVモード設定                              |                 |

|    | 表5.4  | ビデオ取り込み間引き率の設定                        |                 |

|    |       |                                       |                 |

| 7. | 電気的   |                                       |                 |

|    | 表7.1  | 絶対最大定格                                |                 |

|    | 表7.2  | 推奨動作条件                                |                 |

|    | 表7.3  | DC特性                                  |                 |

|    | 表7.4  | 入力クロック(MODE2~0端子=000、001、010:逓倍ONの場合) |                 |

|    | 表7.5  | リセット                                  |                 |

|    | 表7.6  | CPUリードサイクル                            |                 |

|    | 表7.7  | CPUライトサイクル                            |                 |

|    | 表7.8  | DMAライトサイクル                            |                 |

|    | 表7.9  | 割り込み出力                                | 7- <del>6</del> |

|     | 表7.10      | UGMリードサイクル                           | 7-7     |

|-----|------------|--------------------------------------|---------|

|     | 表7.11      | UGMライトサイクル                           | 7-7     |

|     | 表7.12      | UGMリフレッシュサイクル・モードレジスタセットサイクル         | 7-7     |

|     | 表7.13      | マスタ表示モード                             | 7-8     |

|     | 表7.14      | TV同期表示モード                            | 7-8     |

| , , | <b>^</b> 7 |                                      |         |

| 付   | 録          |                                      |         |

| A.  | レジス・       | タの初期値                                |         |

|     | 表A.1レ      | ・ジスタのハードウェアリセット時の初期値                 | 付録-1    |

| В.  | コマン        | ドとパラメータ                              |         |

|     | 表B.1       | コマンドとレンダリング属性の関係表                    | 付録-2    |

|     | 表B.2       | コマンドのコマンドコード表                        | 付録-3    |

| E.  | 表示動作       | <b>乍クロックと画面合成について</b>                |         |

|     | 表E.1       | UGMバス幅×32ビット、Q2SD動作周波数:66MHzの場合      | 付録-14   |

|     | 表E.2       | UGMバス幅×32ビット、Q2SD動作周波数:60MHzの場合      | 付録-15   |

|     | 表E.3       | UGMバス幅×32ビット、Q2SD動作周波数:50MHzの場合      | 付録-15   |

|     | 表E.4       | UGMバス幅×32ビット、Q2SD動作周波数:40MHzの場合      |         |

|     | 表E.5       | UGMバス幅×16ビット、Q2SD動作周波数:66MHzの場合      |         |

|     | 表E.6       | UGMバス幅×16ビット、Q2SD動作周波数:60MHzの場合      | 付録-17   |

|     | 表E.7       | UGMバス幅×16ビット、Q2SD動作周波数:50MHzの場合      | 付録-17   |

|     | 表E.8       | UGMバス幅×16ビット、Q2SD動作周波数:40MHzの場合      | 付録-17   |

| G.  | 表示制        | 卸例                                   |         |

|     | 表G.1       | 变数設定例((TVM1、0)=(0、0)、(SCM1、0)=(0、0)) | 付録-26   |

|     | 表G.2       | レジスタ設定例((TVM1、0)=(0、0)、(SCM1、0)=(0、0 |         |

|     | 表G.3       | 変数の設定例((TVM1、0)=(0、0)、(SCM1、0)=(1、1) | )付録-28  |

|     | 表G.4       | レジスタ設定例((TVM1、0)=(0、0)、(SCM1、0)=(1、1 | ))付録-29 |

| Н.  | 描画制        | 卸例                                   |         |

|     | 表H.1       | DBFと表示面 (FG)の関係                      | 付録-32   |

# 1. 概要

Q2SD ( Quick 2D Graphics Renderer with Synchronous DRAM Interface ) は、シンプル、リアルタイム、およびアップグレードをコンセプトとした CPU グラフィックアクセラレータクイックシリーズ( Q シリーズ )の SDRAM インタフェース対応 2D グラフィックレンダラーです。

Q2SD は、ユニファイドグラフィックスメモリ(Unified Graphics Memory、以下 UGM と略します。)の採用、60 画面 / 秒の高速描画性能で描画バッファと表示バッファをフレーム単位で切り替えるダブルバッファの採用、およびビデオ取り込み機能の採用により、画像用メモリの最小化(最小構成 16M ビット SDRAM1 個)、グラフィックスと自然画とビデオ画像の一元的扱い、リアルタイムソフト 3D グラフィックス描画を実現しました。ジオメトリ演算(CPU)とレンダリング演算(Q2SD)の分離により、システムパスの使用効率の向上も実現しました。

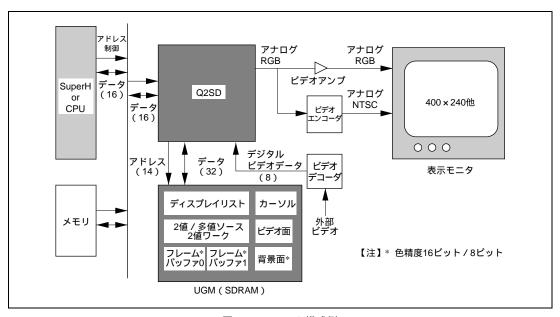

Q2SD は、描画、表示、ビデオ取り込み機能を 1 チップに集積したマルチメディア応用向け高性能グラフィックスレンダリング LSI です。 Q2SD のシステム構成例を図 1.1 に示します。

図 1.1 システム構成例

# 1.1 特長

### シンプル(システム構成の最適化)

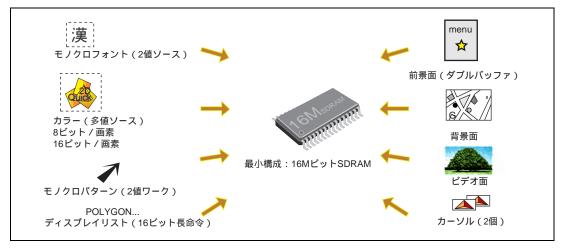

- (1) ユニファイドグラフィックスメモリ (UGM) アーキテクチャ採用

- 画像データの一元的扱い[UGMアーキテクチャ]。形式が異なるデータを同一のUGM上に格納し、それらを管理できます(図1.2参照)。

- UGMの必要最小限化

UGM最小構成: 16ビットデータバス16MビットシンクロナスDRAM(SDRAM) × 1個

図 1.2 システムの小型化を可能にする UGM アーキテクチャ

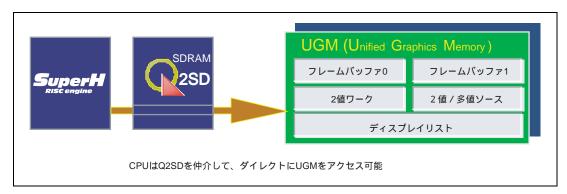

• UGMをCPUのメモリ空間に配置

インタフェースの一元化のため、CPUインタフェース回路を内蔵し、UGMをCPUのメモリ空間に配置しました(図1.3参照)。これによりCPUのUGM管理が容易に行えます。

図 1.3 システムバスインタフェースの一元化

### リアルタイム

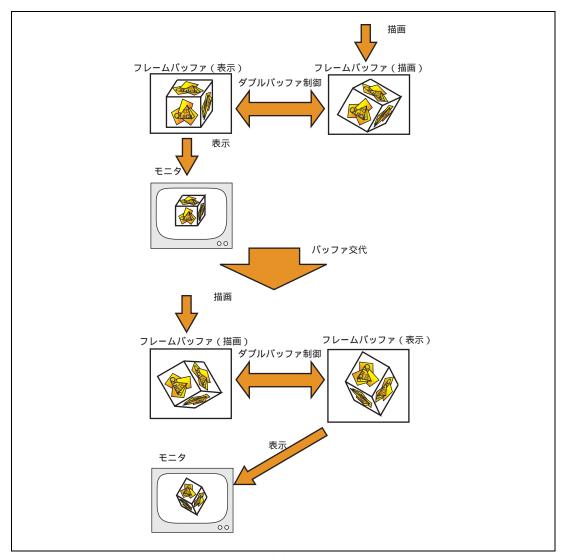

### (1) ダブルバッファ採用

描画バッファと表示バッファをフレームまたはフィールド単位で切り替えるダブルバッファの採用により、 表示処理と高速描画処理を同時に行え、リアルタイム動作の表現が実現できます(図 1.4 参照)。

図 1.4 ダブルバッファ

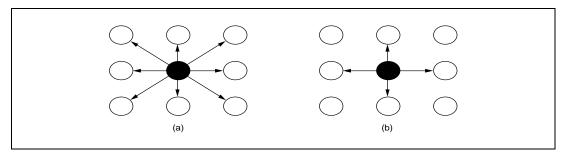

#### (2) グラフィックスアクセラレータ

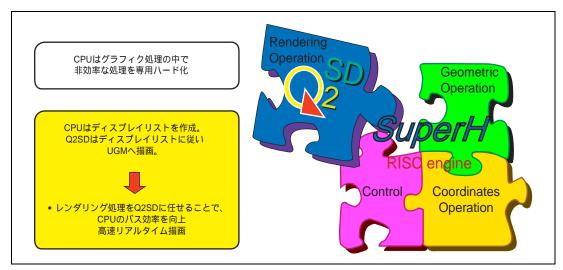

Q2SD は、グラフィックス処理の中 CPU では非効率な処理を専用ハード化し、CPU バスの効率向上と、高速リアルタイム描画を実現しました(図 1.5 参照)。

図 1.5 グラフィックスアクセラレータ

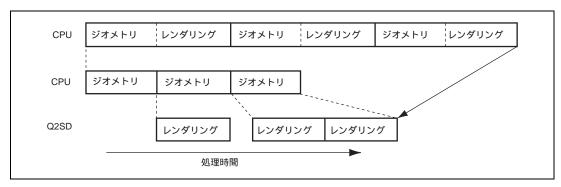

#### (3) グラフィックス処理のパイプライン化

グラフィックス処理が、CPU のジオメトリ処理と Q2SD のレンダリング処理によるパイプライン化で、一層の高速処理が実現できます(図 1.6 参照)。

図 1.6 グラフィックス処理のパイプライン化

#### (4) ライトオンリー描画の採用

ライト動作のみの描画方式 (ライトオンリー描画)を採用し、描画性能を向上させました。

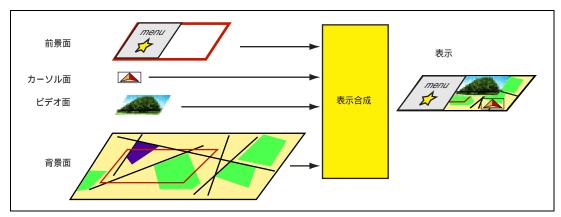

#### (5) 表示合成機能

変更のある画像のみ変更を行えるので再描画の時間が短縮できます(図1.7参照)。

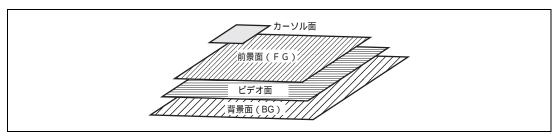

図 1.7 表示合成機能

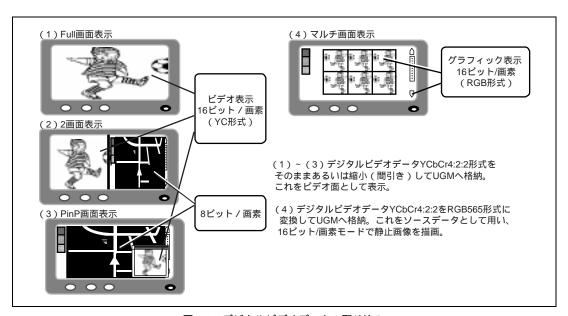

#### (6) デジタルビデオデータの取り込み

多彩な表現でのデジタルビデオ画像のリアルタイム表現ができます。

図 1.8 デジタルビデオデータの取り込み

#### (7) SDRAM 対応

UGM に SDRAM を使用可能です。これにより、Q2SD は UGM にバーストアクセスが行え、高速な描画を行えます。

## アップグレード

## (1) アルゴリズムのアップグレード

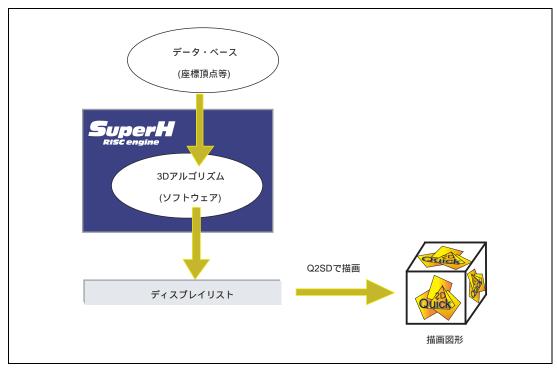

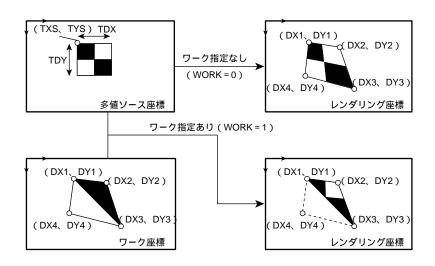

Q2SD の描画体系は、座標等の整頓されたデータベースをもとに、CPU で座標変換等のアルゴリズムを実行し、その演算結果を図形として表現する描画体系になっています。これにより、データベースの変更を行わず、アルゴリズムをアップグレードするだけで、様々な形の図形が表現できます(図 1.9 参照)。

図 1.9 3D アルゴリズムを使用したときのデータの流れ

#### (2) 描画システムのアップグレード

Q2SD は Q シリーズとしてシリーズ化されています。ユーザの用途に合わせてシリーズから選択できます。 また、ユーザの必要に応じて、Q2SD または CPU との組み合わせを変更することで、描画システムのアップグレードを図れます。

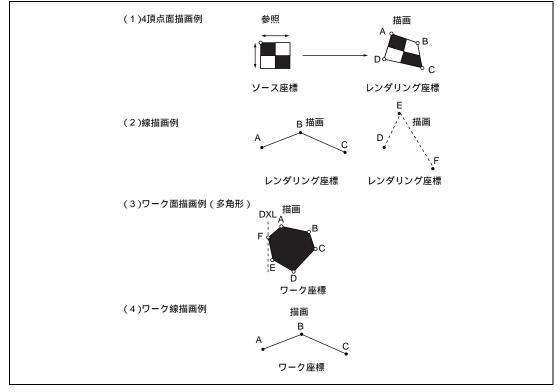

#### (3) アプリケーションインタフェースの整合性

Q2SD では描画コマンドを厳選し、描画コマンドを 4 種類 (4 頂点面描画、線描画、ワーク面描画およびワーク線描画)で構成しました。これにより、アプリケーション内部において、描画コマンドに依存する部分を低減でき、アプリケーション間のインタフェースの整合性の向上を図れます。

# 1.2 製品仕様

Q2SD の製品仕様を表 1.1 に示します。

表 1.1 製品仕様

| 項目    |                                                                        |                       | 機能/性能                                                                                     |

|-------|------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|

| 描画    | 描画性能                                                                   |                       | ポリゴン性能(20×25 画素)<br>91000 個 / 秒                                                           |

|       |                                                                        |                       | (2 画面合成時 60000 個 / 秒)                                                                     |

|       |                                                                        |                       | ライン性能(10画素)120万本/秒<br>(2画面合成時)(40万本/秒)                                                    |

|       | 色表現<br>描画コマンド<br>レジスタ設定コマンド                                            |                       | ソース:1、8、16 ビット/画素、描画:8、16 ビット/画素<br>ワーク:2 値                                               |

|       |                                                                        |                       | 4 頂点面描画、線描画、ワーク面描画、ワーク線描画                                                                 |

|       |                                                                        |                       | カレントポインタ設定、ローカルオフセット設定、クリッピング、<br>特定のアドレスマップドレジスタ設定                                       |

|       | シーケンス制御コ                                                               | コマンド                  | ジャンプ、サブルーチン、垂直帰線期間待ち、ノーオペレーション、<br>ディスプレイリスト終了。                                           |

| 表示    | 画面サイズ例                                                                 |                       | 320×240、400×240、480×240、640×480、NTSC、PAL など                                               |

|       | CRT 走査方式                                                               |                       | ノンインタレース、インタレース、インタレースシンク&ビデオ                                                             |

|       | 外部同期                                                                   |                       | マスタ、TV 同期                                                                                 |

|       | カラーパレット                                                                |                       | 26 万色中同時 256 色表示                                                                          |

|       | カーソル                                                                   |                       | 32×32 画素、2 個、カラーパレット中から表示色を選択可                                                            |

|       | 表示面                                                                    |                       | 前景面、背景面、ビデオ面                                                                              |

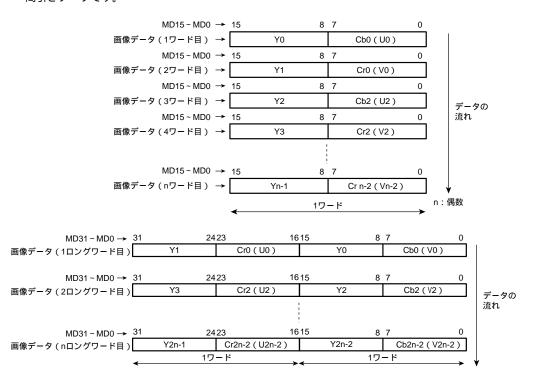

| ビデオ取り | ビデオ取り込み                                                                |                       | 8 ビットマルチプレクス YCbCr 4:2:2 ディジタル入力                                                          |

| システム  | 描画系内部動作最大クロック周波数<br>(Q2SD動作クロック周波数)<br>表示系内部動作クロック周波数<br>(表示動作クロック周波数) |                       | 66MHz×1、33MHz×2、16.5MHz×4(逓倍器使用)                                                          |

|       |                                                                        |                       | 動作周波数 / 2 (最大 33MHz)                                                                      |

|       | SH<br>インタフェース                                                          | コマンド / データ転送          | DMA 転送(シングルアドレス、デュアルアドレス)、<br>または CPU で行う                                                 |

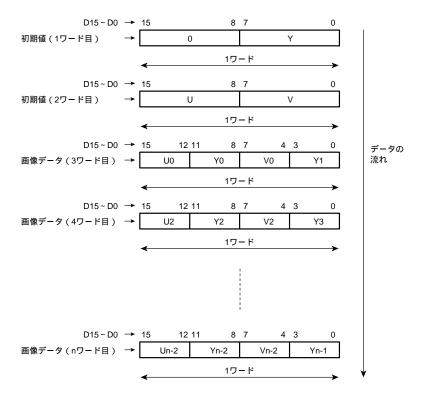

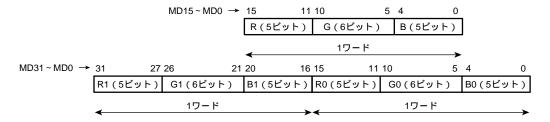

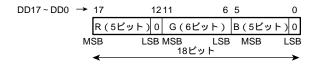

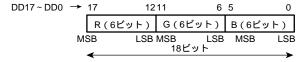

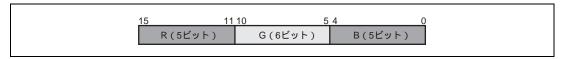

|       |                                                                        | YUV RGB 変換            | 入力 16 ピット 4:2:2 ( Y, U, V 各 8 ピット ) 、<br>出力 16 ピット ( R:5, G:6, B:5 ピット )                  |

|       |                                                                        | YUV RGB 変換            | 入力 8 ビット(d-Y, d-U, d-V 各 4 ビット)、<br>出力 16 ビット(R:5, G:6, B:5 ビット)                          |

|       |                                                                        | 割り込み出力                | TV 同期信号エラーフラグ、フレームフラグ、DMA フラグ、<br>コマンドエラーフラグ、垂直ブランキングフラグ、<br>トラップフラグ、コマンド中断フラグ、描画中断フラグ    |

|       |                                                                        | SuperH 対応             | 3.3V 動作の SuperH の SRAM エリア等に配置可能                                                          |

|       | UGM<br>インタフェース                                                         | 32/16 ビットバス幅<br>SDRAM | 最小 16M ビット(16M ビット(×16)1 個、16M ビット(×16)<br>2 個並列、64M ビット(×16)1 個、64M ビット(×32)1 個より<br>選択) |

| 項目           |     |             | 機能/性能                                                          |

|--------------|-----|-------------|----------------------------------------------------------------|

| システム         | DAC | アナログ RGB 出力 | RGB 各 6 ビット分解能(ただし、YCbCr 形式で UGM に格納された<br>ビデオについては、8 ビット分解能)  |

| プロセス / パッケージ |     |             | 0.35 ミクロン CMOS / 176 ピン LQFP                                   |

| 電源電圧 / 温度範囲  |     |             | 3.3V±0.3V/0 ~70<br>(-40 ~85 の特別仕様品については、別途弊社営業担当者へお問い合わせください。) |

## 1.3 ブロック図

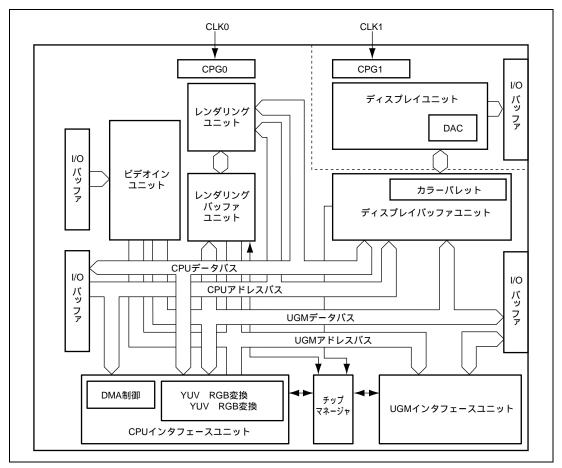

Q2SD の内部ブロック図を図 1.10 に示します。各ブロックは次のような機能を持っています。

• CPUインタフェースユニット

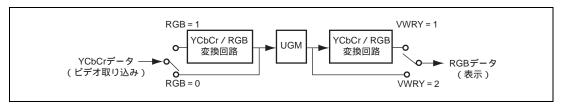

CPUによるUGMアクセス、CPUによるQ2SD内蔵レジスタアクセス、外部DMACによるUGMライトアクセス制御を行います。入力データ YUV (26万色)、またはYUV (26万色)をRGB (6万色)データに変換し、UGMに格納します。割り込み出力を行います。

• UGMインタフェースユニット

UGMとして使用するSDRAMの接続に関する制御を行います。

• チップマネージャ

UGMアーキテクチャにおける各ユニットの動作を調停するユニットです。

• クロックジェネレータ (CPG0、CPG1)

CPG0でQ2SD動作クロックを生成し、各ユニットに供給します(ディスプレイユニットを除く)。CPG1で表示ドットクロックを生成し、ディスプレイユニットに供給します。

• レンダリングユニット

UGM上のディスプレイリストのフェッチと解釈と実行を行います。

レンダリングバッファユニット

レンダリングユニットのUGMアクセスの効率向上のため、データ/アドレスをバッファリングします。

• ディスプレイユニット

CRTの制御信号の生成とアナログRGB信号の出力を行います。

• ディスプレイバッファユニット

前景面、背景面、ビデオ面、カーソル面の表示合成を行います。表示タイミングに従ってUGM上の表示データをアクセスします。カラーパレット(各色6ビット)により、8ビット/画素のデータを、色変換テーブルに基づき262,144色中256色のRGBデータに変換します。また、ビデオ面のデータがYCbCrデータの場合、RGBデータに変換します。

• ビデオインユニット

4:2:2YCbCrデータを取り込み、YCbCrまたはRGB形式でUGMに格納します。間引き処理による画像の縮小取り込みが行えます。

図 1.10 内部ブロック図

# 1.4 処理状態

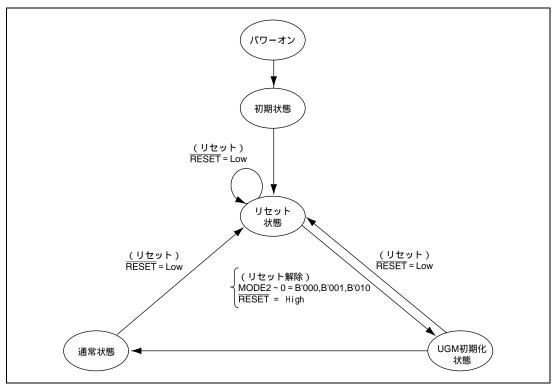

Q2SD の処理状態には、パワーオン、初期状態、リセット状態、UGM 初期状態、通常状態があります。 状態遷移図を、図 1.11 に示します。

図 1.11 状態遷移図

## 1.4.1 パワーオン

「6.1 パワーオンシーケンス」を参照してください。

# 1.4.2 初期状態(規定の電源を投入したとき)

内部状態が不定になります。

レジスタ: 不定入出力端子: 不定

• 出力端子: Low / Highレベル出力

## 1.4.3 リセット状態(RESET 端子に Low レベルを入力したとき)

リセット直後の Q2SD の端子状態を表 1.2 に示します。 $\overline{\text{RESET}}$  端子が Low レベルのとき、UGM に対してリフレッシュを行いません。 $\overline{\text{RESET}}$  の立ち上がり時点で、MODE2  $\sim$  0 のレベルを取り込みます。このとき、MODE2  $\sim$  0 は B'000、B'001、B'010 のいずれかにレベル固定してください。他の組み合わせはテストモードとなりますので使用しないでください。

入出力端子入力状態D0~D15\*、VSYNC/EXVSYNC、HSYNC/EXHSYNC、ODDF出力端子Low レベル出力MD0~MD31出力端子Low レベル出力DISP、CDEHigh レベル出力DREQ、IRL、WAITLow / High レベル出力CSYNC、MA0~MA13、MWE、MRAS、MCAS、LDQM0、LDQM1、UDQM0、UDQM1、MCLK

表 1.2 リセット直後の端子状態

### 1.4.4 UGM 初期化状態

UGM として使用する SDRAM の初期化を行います。初期化については、「6.6 Q2SD が設定する UGM 用SDRAM のモードレジスタ値について」を参照してください。

#### 1.4.5 通常動作状態

通常動作状態です。描画コマンドの実行や表示制御を行います。

<sup>【</sup>注】 \* RD が Low レベル入力のときは、D0~D15 端子は出力状態になります。

# 2. 端子

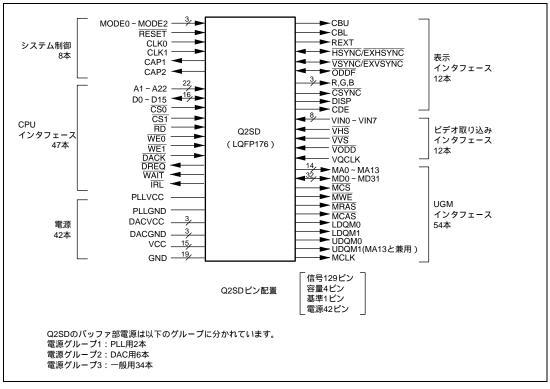

# 2.1 端子構成

Q2SD の端子構成を図 2.1 に示します。

使用しない入力端子は非アクティブになるようにプルアップまたはプルダウンしてください。

図 2.1 端子構成

# 2.2 ピン配置図

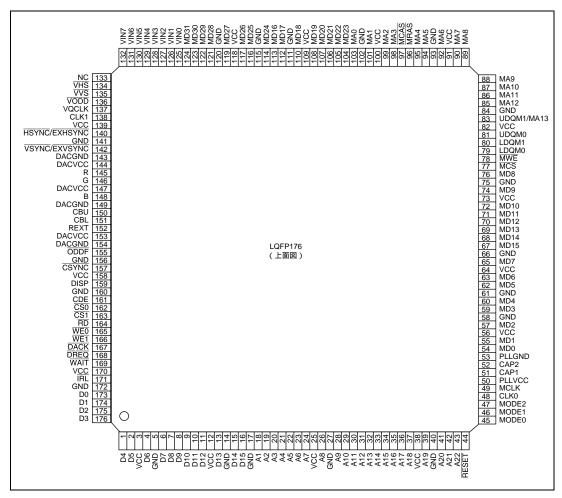

Q2SD のピン配置図を図 2.2 に示します。

図 2.2 ピン配置図

# 2.3 端子機能

Q2SD の端子機能を表 2.1 に示します。

表 2.1 端子機能

| 分類      | 記号    | ピン番号 | 入出力 | 機能          |

|---------|-------|------|-----|-------------|

| システム制御  | MODE0 | 45   | 入力  | 動作モード端子 0   |

|         | MODE1 | 46   | 入力  | 動作モード端子 1   |

|         | MODE2 | 47   | 入力  | 動作モード端子 2   |

|         | CLK0  | 48   | 入力  | Q2SD 動作クロック |

|         | CLK1  | 138  | 入力  | 表示動作クロック    |

|         | RESET | 44   | 入力  | リセット        |

|         | CAP1  | 51   | 出力  | 逓倍回路用外部容量端子 |

|         | CAP2  | 52   | 出力  | 逓倍回路用外部容量端子 |

| CPU     | A1    | 18   | 入力  | CPU アドレス 1  |

| インタフェース | A2    | 19   | 入力  | CPU アドレス 2  |

|         | A3    | 20   | 入力  | CPU アドレス 3  |

|         | A4    | 21   | 入力  | CPU アドレス 4  |

|         | A5    | 22   | 入力  | CPU アドレス 5  |

|         | A6    | 23   | 入力  | CPU アドレス 6  |

|         | A7    | 24   | 入力  | CPU アドレス 7  |

|         | A8    | 26   | 入力  | CPU アドレス 8  |

|         | A9    | 28   | 入力  | CPU アドレス 9  |

|         | A10   | 29   | 入力  | CPU アドレス 10 |

|         | A11   | 30   | 入力  | CPU アドレス 11 |

|         | A12   | 31   | 入力  | CPU アドレス 12 |

|         | A13   | 32   | 入力  | CPU アドレス 13 |

|         | A14   | 33   | 入力  | CPU アドレス 14 |

|         | A15   | 34   | 入力  | CPU アドレス 15 |

|         | A16   | 35   | 入力  | CPU アドレス 16 |

|         | A17   | 36   | 入力  | CPU アドレス 17 |

|         | A18   | 37   | 入力  | CPU アドレス 18 |

|         | A19   | 39   | 入力  | CPU アドレス 19 |

|         | A20   | 41   | 入力  | CPU アドレス 20 |

|         | A21   | 42   | 入力  | CPU アドレス 21 |

|         | A22   | 43   | 入力  | CPU アドレス 22 |

|         | D0    | 173  | 入出力 | CPU データ 0   |

|         | D1    | 174  | 入出力 | CPU データ 1   |

| 分類      | 記号                | ピン番号 | 入出力 | 機能                       |

|---------|-------------------|------|-----|--------------------------|

| CPU     | D2                | 175  | 入出力 | CPU データ 2                |

| インタフェース | D3                | 176  | 入出力 | CPU データ 3                |

|         | D4                | 1    | 入出力 | CPU データ 4                |

|         | D5                | 2    | 入出力 | CPU データ 5                |

|         | D6                | 4    | 入出力 | CPU データ 6                |

|         | D7                | 6    | 入出力 | CPU データ 7                |

|         | D8                | 7    | 入出力 | CPU データ 8                |

|         | D9                | 8    | 入出力 | CPU データ 9                |

|         | D10               | 9    | 入出力 | CPU データ 10               |

|         | D11               | 10   | 入出力 | CPU データ 11               |

|         | D12               | 11   | 入出力 | CPU データ 12               |

|         | D13               | 13   | 入出力 | CPU データ 13               |

|         | D14               | 15   | 入出力 | CPU データ 14               |

|         | D15               | 16   | 入出力 | CPU データ 15               |

|         | CS0               | 162  | 入力  | チップ選択 0 ( UGM )          |

|         | CS1               | 163  | 入力  | チップ選択 1 (内部レジスタ)         |

|         | RD                | 164  | 入力  | リードストローブ                 |

|         | WE0               | 165  | 入力  | 書き込みパルス 0 (下位側)          |

|         | WE1               | 166  | 入力  | 書き込みパルス1(上位側)            |

|         | DACK              | 167  | 入力  | DMA アクノリッジ               |

|         | DREQ              | 168  | 出力  | DMA リクエスト                |

|         | WAIT              | 169  | 出力  | CPU ウェイト                 |

|         | ĪRL               | 171  | 出力  | 割り込み要求                   |

| 表示      | CBU               | 150  | 出力  | DAC 用外部容量端子              |

| インタフェース | CBL               | 151  | 出力  | DAC 用外部容量端子              |

|         | REXT              | 152  | 出力  | DAC 用外部リファレンス端子          |

|         | R                 | 145  | 出力  | 表示データアナログ出力 R            |

|         | G                 | 146  | 出力  | 表示データアナログ出力 G            |

|         | В                 | 148  | 出力  | 表示データアナログ出力 B            |

|         | CSYNC             | 157  | 出力  | コンポジット同期出力信号             |

|         | HSYNC/<br>EXHSYNC | 140  | 入出力 | 水平同期出力 / 外部水平同期入力        |

|         | VSYNC/<br>EXVSYNC | 142  | 入出力 | 垂直同期出力 / 外部垂直同期入力        |

|         | DISP              | 159  | 出力  | 表示期間を示す信号(表示期間 High レベル) |

|         | CDE               | 161  | 出力  | 色検出(特定色出力時 High レベル)     |

|         | ODDF              | 155  | 入出力 | 奇数フィールドを示す信号             |

|         |                   |      |     | (奇数時 Low レベル)            |

| 分類      | 記号    | ピン番号 | 入出力 | 機能                    |

|---------|-------|------|-----|-----------------------|

| ビデオ取り込み | VIN0  | 125  | 入力  | ビデオ入力データ 0            |

| インタフェース | VIN1  | 126  | 入力  | ビデオ入力データ1             |

|         | VIN2  | 127  | 入力  | ビデオ入力データ2             |

|         | VIN3  | 128  | 入力  | ビデオ入力データ3             |

|         | VIN4  | 129  | 入力  | ビデオ入力データ4             |

|         | VIN5  | 130  | 入力  | ビデオ入力データ5             |

|         | VIN6  | 131  | 入力  | ビデオ入力データ 6            |

|         | VIN7  | 132  | 入力  | ビデオ入力データ7             |

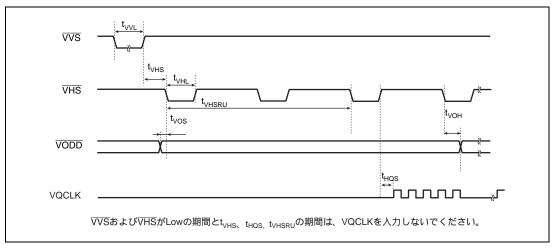

|         | VHS   | 134  | 入力  | ビデオ水平同期入力             |

|         | VVS   | 135  | 入力  | ビデオ垂直同期入力             |

|         | VODD  | 136  | 入力  | ビデオ入力奇数フィールドを示す信号     |

|         | VQCLK | 137  | 入力  | ビデオ入力有効データ取り込みクロック    |

| UGM     | MA0   | 103  | 出力  | メモリアドレス 0             |

| インタフェース | MA1   | 101  | 出力  | メモリアドレス 1             |

|         | MA2   | 99   | 出力  | メモリアドレス 2             |

|         | MA3   | 98   | 出力  | メモリアドレス 3             |

|         | MA4   | 95   | 出力  | メモリアドレス 4             |

|         | MA5   | 94   | 出力  | メモリアドレス 5             |

|         | MA6   | 92   | 出力  | メモリアドレス 6             |

|         | MA7   | 90   | 出力  | メモリアドレス 7             |

|         | MA8   | 89   | 出力  | メモリアドレス 8             |

|         | MA9   | 88   | 出力  | メモリアドレス 9             |

|         | MA10  | 87   | 出力  | メモリアドレス 10            |

|         | MA11  | 86   | 出力  | メモリアドレス 11            |

|         | MA12  | 85   | 出力  | メモリアドレス 12            |

|         | MA13  | 83   | 出力  | メモリアドレス 13(UDQM1 と兼用) |

|         | MD0   | 54   | 入出力 | メモリデータ 0              |

|         | MD1   | 55   | 入出力 | メモリデータ1               |

|         | MD2   | 57   | 入出力 | メモリデータ2               |

|         | MD3   | 59   | 入出力 | メモリデータ3               |

|         | MD4   | 60   | 入出力 | メモリデータ4               |

|         | MD5   | 62   | 入出力 | メモリデータ5               |

|         | MD6   | 63   | 入出力 | メモリデータ 6              |

|         | MD7   | 65   | 入出力 | メモリデータ7               |

|         | MD8   | 76   | 入出力 | メモリデータ8               |

|         | MD9   | 74   | 入出力 | メモリデータ 9              |

|         | MD10  | 72   | 入出力 | メモリデータ 10             |

|         | MD11  | 71   | 入出力 | メモリデータ 11             |

| 分類      | 記号    | ピン番号 | 入出力 | 機能                         |

|---------|-------|------|-----|----------------------------|

| UGM     | MD12  | 70   | 入出力 | メモリデータ 12                  |

| インタフェース | MD13  | 69   | 入出力 | メモリデータ 13                  |

|         | MD14  | 68   | 入出力 | メモリデータ 14                  |

|         | MD15  | 67   | 入出力 | メモリデータ 15                  |

|         | MD16  | 113  | 入出力 | メモリデータ 16                  |

|         | MD17  | 112  | 入出力 | メモリデータ 17                  |

|         | MD18  | 110  | 入出力 | メモリデータ 18                  |

|         | MD19  | 108  | 入出力 | メモリデータ 19                  |

|         | MD20  | 107  | 入出力 | メモリデータ 20                  |

|         | MD21  | 106  | 入出力 | メモリデータ 21                  |

|         | MD22  | 105  | 入出力 | メモリデータ 22                  |

|         | MD23  | 104  | 入出力 | メモリデータ 23                  |

|         | MD24  | 114  | 入出力 | メモリデータ 24                  |

|         | MD25  | 116  | 入出力 | メモリデータ 25                  |

|         | MD26  | 117  | 入出力 | メモリデータ 26                  |

|         | MD27  | 119  | 入出力 | メモリデータ 27                  |

|         | MD28  | 121  | 入出力 | メモリデータ 28                  |

|         | MD29  | 122  | 入出力 | メモリデータ 29                  |

|         | MD30  | 123  | 入出力 | メモリデータ 30                  |

|         | MD31  | 124  | 入出力 | メモリデータ 31                  |

|         | MCS   | 77   | 出力  | メモリチップ選択                   |

|         | MWE   | 78   | 出力  | メモリ書き込みパルス                 |

|         | MRAS  | 96   | 出力  | ロウ選択信号                     |

|         | MCAS  | 97   | 出力  | カラム選択信号                    |

|         | LDQM0 | 79   | 出力  | 下位ワード下位パイト入出力マスク           |

|         | LDQM1 | 80   | 出力  | 下位ワード上位バイト入出力マスク           |

|         | UDQM0 | 81   | 出力  | 上位ワード下位バイト入出力マスク           |

|         | UDQM1 | 83   | 出力  | 上位ワード上位バイト入出力マスク(MA13 と兼用) |

|         | MCLK  | 49   | 出力  | メモリクロック                    |

| 電源      | VCC   | 3    | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 12   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 25   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 38   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 56   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 64   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 73   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 82   | 電源  | バッファ / 内部用 VDD             |

|         | VCC   | 91   | 電源  | バッファ / 内部用 VDD             |

| 分類  | 記号     | ピン番号 | 入出力  | 機能                           |

|-----|--------|------|------|------------------------------|

| 電源  | VCC    | 100  | 電源   | バッファ / 内部用 VDD               |

|     | VCC    | 109  | 電源   | バッファ / 内部用 VDD               |

|     | VCC    | 118  | 電源   | バッファ / 内部用 VDD               |

|     | VCC    | 139  | 電源   | バッファ / 内部用 VDD               |

|     | VCC    | 158  | 電源   | バッファ / 内部用 VDD               |

|     | VCC    | 170  | 電源   | バッファ / 内部用 VDD               |

|     | GND    | 5    | グランド | バッファ用 VSS                    |

|     | GND    | 14   | グランド | バッファ用 VSS                    |

|     | GND    | 27   | グランド | バッファ用 VSS                    |

|     | GND    | 40   | グランド | バッファ用 VSS                    |

|     | GND    | 58   | グランド | バッファ用 VSS                    |

|     | GND    | 66   | グランド | バッファ用 VSS                    |

|     | GND    | 75   | グランド | バッファ用 VSS                    |

|     | GND    | 84   | グランド | バッファ用 VSS                    |

|     | GND    | 93   | グランド | バッファ用 VSS                    |

|     | GND    | 102  | グランド | バッファ用 VSS                    |

|     | GND    | 111  | グランド | バッファ用 VSS                    |

|     | GND    | 120  | グランド | バッファ用 VSS                    |

|     | GND    | 141  | グランド | バッファ用 VSS                    |

|     | GND    | 160  | グランド | バッファ用 VSS                    |

|     | GND    | 172  | グランド | バッファ用 VSS                    |

|     | GND    | 17   | グランド | 内部用 VSS                      |

|     | GND    | 61   | グランド | 内部用 VSS                      |

|     | GND    | 115  | グランド | 内部用 VSS                      |

|     | GND    | 156  | グランド | 内部用 VSS                      |

|     | PLLVCC | 50   | 電源   | 逓倍回路用 VDD                    |

|     | PLLGND | 53   | グランド | 逓倍回路用 VSS                    |

|     | DACVCC | 144  | 電源   | DAC用VDD                      |

|     | DACVCC | 147  | 電源   | DAC用VDD                      |

|     | DACVCC | 153  | 電源   | DAC用VDD                      |

|     | DACGND | 143  | グランド | DAC用VSS                      |

|     | DACGND | 149  | グランド | DAC用VSS                      |

|     | DACGND | 154  | グランド | DAC用VSS                      |

| その他 | NC     | 133  |      | No-Connection(何も接続しないでください)。 |

## 2.4 システム制御端子

## 2.4.1 動作モード端子

(MODE0, MODE1, MODE2)

Q2SD のシステム動作を決定します、リセット立ち上げ時にモードが確定します。リセット立ち上げ以降のモード変更はできません。

| MODE2 | MODE1 | MODE0 | 説 明                                        |

|-------|-------|-------|--------------------------------------------|

| L     | L     | L     | 通常動作状態になります。逓倍 ON。外部入力クロックは、デューティフリーとなります。 |

|       |       |       | 外部入力クロックの1倍の周波数のクロックが内部動作クロックになります。        |

| L     | L     | Н     | 通常動作状態になります。逓倍 ON。外部入力クロックは、デューティフリーとなります。 |

|       |       |       | 外部入力クロックの2倍の周波数のクロックが内部動作クロックになります。        |

| L     | Н     | L     | 通常動作状態になります。逓倍 ON。外部入力クロックは、デューティフリーとなります。 |

|       |       |       | 外部入力クロックの4倍の周波数のクロックが内部動作クロックになります。        |

| L     | Н     | Н     | 設定禁止                                       |

| Н     | *     | *     | 設定禁止                                       |

表 2.2 動作モードの選択

【記号説明】H : High レベル L : Low レベル

\* : High レベル、Low レベルいずれでも可

## 2.4.2 クロック端子

(CLK0, CLK1, CAP1, CAP2)

Q2SD のクロックは、CLK0 と CLK1 の 2 系統があります。CLK0 端子には Q2SD 動作クロックの基準となる クロックを、CLK1 端子には表示動作クロックをそれぞれ入力します。

Q2SD 動作クロックは、描画動作をはじめとする Q2SD が動作を行うための基本クロックです。UGM のアクセスも Q2SD 動作クロックを基本としています。Q2SD 内部に Q2SD 動作クロック用の逓倍回路を内蔵しており、CLKO 端子に、Q2SD 動作クロックの 1 倍、1/2 倍、1/4 倍を選択して入力することが可能です。

表示動作クロックは、表示動作を行うための基本クロックで、表示ドットクロック、表示データの出力制御、水平/垂直同期信号の生成に使用されます。

これらの関係を表 2.3 に示します。

| クロック入力端子 | クロック種別                         | 動作クロック                                        |

|----------|--------------------------------|-----------------------------------------------|

| CLK0     | 右記のいずれかが Q2SD 動作クロック<br>になります。 | 周波数は、CLK0 の周波数の 1 倍で、デューティが 50%に<br>補正されたクロック |

|          |                                | 周波数は、CLK0 の周波数の 2 倍で、デューティが 50%に<br>補正されたクロック |

|          |                                | 周波数は、CLK0 の周波数の 4 倍で、デューティが 50%に<br>補正されたクロック |

| CLK1     | 右記が表示動作クロックになります。              | 周波数は、CLK1 の周波数の 1 倍のクロック                      |

表 2.3 入力クロックと動作周波数

Q2SD 動作クロックと表示動作クロックは、以下の範囲で自由に設定することが可能です。したがって、表示 装置の特性に左右されず、最大速度で描画動作を行うことができます。

- Q2SD動作クロック周波数 表示動作クロックの2倍の周波数

- 表示動作クロック周波数 33MHz

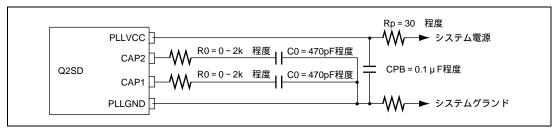

CAP1、CAP2 は、逓倍回路用の外部容量端子です。CAP1、CAP2 端子の接続回路例を図 2.3 に示します。 内蔵 PLL の発振安定用の容量 C0 および抵抗 R0 は CAP0 端子の近くに置き、他の信号線と交差させないでください。C0 のグランドは PLLGND から供給してください。C0 は PLL チャージポンプの外部容量で、R0 はチャージポンプへのノイズ低減用の抵抗です。

図 2.3 CAP1、CAP2 端子接続回路例

## 2.4.3 リセット端子

## ( RESET )

ハードウェアリセットを入力します。Low レベルでハードウェアリセット状態となります。 端子は表 1.2 の様になり、レジスタは初期値になります。

## 2.4.4 電源端子

( VCC, GND, PLLVCC, PLLGND, DACVCC, DACGND )

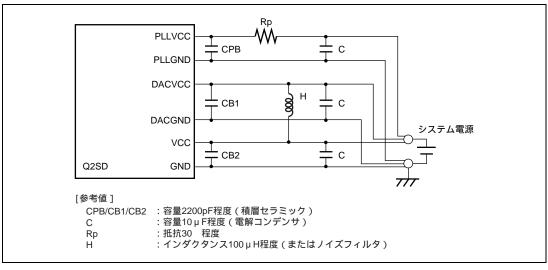

通常電源端子、DAC 電源端子および PLL 電源端子には、3.3V を接続します。通常電源端子および DAC 電源端子は複数ありますが、すべての端子に電源を供給してください。

通常電源(VCC、GND)、PLL 電源(PLLVCC、PLLGND)、DAC 電源(DACVCC、DACGND)は、ボードの電源供給元から分離し、できるだけ端子の近くにバイパスコンデンサ CPB および CB1、CB2 を必ず挿入してください。

特に DAC 出力電圧は、1 ステップが微少電圧ですので、外部から入り込んでくるノイズをできるだけ小さくする必要があります。そこで CPB、CB1、CB2 の他に、各電源と GND 間に最低 1 個づつの電解コンデンサ(10μF程度)を挿入することをお奨めします。また、DAC のラッチアップ対策として、電源間の電位を同じにすることと、高周波ノイズの流入を防止するため、インダクタンス (100μH程度) かイズフィルタを DACVCC と VCC間に挿入することをお奨めします。

図 2.4 端子近くの電源間バイパスコンデンサの接続

# 2.5 CPU インタフェース端子

(A22~A1, D15~D0, CS0, CS1, RD, WE0, WE1, DACK, DREQ, WAIT, IRL)

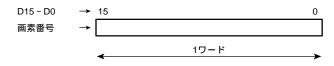

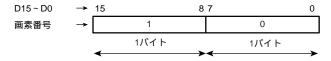

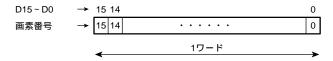

#### 2.5.1 CPU ライト

CPU は、UGM または Q2SD 内部レジスタをアクセスすることができます。UGM のアクセス時は  $\overline{\text{CSO}}$  に Low レベルを、Q2SD 内部レジスタのアクセス時は  $\overline{\text{CSI}}$  に Low レベルを入力します。 $\overline{\text{CSO}}$  と  $\overline{\text{CSI}}$  を同時に Low レベルにしないでください。UGM または Q2SD 内部レジスタのアドレスは、A1 ~ A22 に入力します。Q2SD の A22 ~ A1 端子には、メモリモードレジスタ(MEMR)で指定した範囲の UGM アドレスを入力しますが、16M ビットのメモリを 1 個使用する場合は、A22 ~ A21 端子が Low レベルになるように、16M ビットのメモリを 2 個使用する場合は、A22 端子が Low レベルになるように配線してください。アドレスは、バイトアドレスです。Q2SD は、レジスタに対してはワード(2 バイト)アクセスのみ使用できます。UGM に対してはワードアクセス、バイトアクセスが使用できます。ワードアクセスにおいては、 $\overline{\text{WEO}}$ 、 $\overline{\text{WEI}}$  の両方に Low レベルを入力してください。バイトアクセスにおいては、ビット 7 ~ 0 に対するアクセスでは  $\overline{\text{WEO}}$ 、ビット 15 ~ 8 に対するアクセスでは  $\overline{\text{WEI}}$  を Low レベルとしてください。

Q2SD は、Q2SD の内部動作による CPU アクセスの延期を WAIT 信号によって CPU に知らせます。ただし、Q2SD の WEO、WEI 信号の High レベル幅の規定上、CPU の外部パス動作周波数は、Q2SD の内部動作周波数と同じか、または低く設定してください。Q2SD の WAIT 信号は、上記 CSO または CSI の Low レベルと、RD、WEO、または WEI の Low レベルを検出してから最大 3 サイクル後に、出力パッファディレイ(MAX 15ns)を経てアサートされます。CPU と Q2SD の周波数比、および周期、非同期等のシステムの仕様に応じて Super Hのソフトウェアウェイト数を調整してください。

なお、SuperH では、初期値で  $\overline{\text{CS}}$  端子が入力ポートとなる製品があります。この信号を Q2SD の  $\overline{\text{CSO}}$  または  $\overline{\text{CSI}}$  信号と直接接続する場合、リセット時の電圧レベルが不安定にならないように SuperH の  $\overline{\text{CS}}$  端子を外部でプルアップしてください。

RDY 信号でインタフェースを行う SuperH を使用する場合、Q2SD の WAIT 信号を反転させて、その信号をRDY 信号として使用してください。

WAIT 信号は Q2SD をアクセスしたときに最小で 1 tcyc0 出力されます。

#### 2.5.2 CPU U - F

ライト動作と基本的に同じです。読み出しは、ワード単位です。ライト動作時は $\overline{\text{WE0}}$ 、 $\overline{\text{WEI}}$  によりライト動作を示しますが、リード動作時は $\overline{\text{RD}}$  の Low レベルによりリード動作を示します。

## 2.5.3 DMA ライト

CPU は、DMAC を用いて UGM または Q2SD アドレスマップドレジスタ (画像データエントリレジスタ IDE )をサイクルスチールでライト DMA アクセスすることができます。 DMA アクセスを行うためには、DMA 転送開始アドレス、DMA 転送語数、システム制御レジスタ (SYSR)の DMA モード、DMA アドレスモードの設定が必要です。 DMA モードの設定後、Q2SD は準備が整いしだい DREQ 信号を Low レベルにします。 DMAC はこれを受けて DACK 信号を Low レベルにし、DMA アクセスを開始します。 DMA アクセスは、ワード単位です。

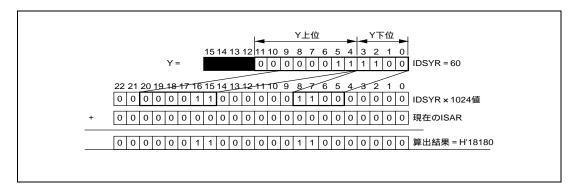

入力データ変換モードレジスタ (IEMR)の YUV モード (YUV2、YUV1、YUV0)を B'000 にしたときに DMA ライトを行う場合には DMA モード (DMA1、DMA0)を B'01 (UGM への DMA 転送)に、YUV モードを B'000 以外にしたときに DMA ライトを行う場合には DMA モードを B'11 (画像データエントリレジスタ (IDER)への DMA 転送)に設定します。

システム制御レジスタ (SYSR)の DMA アドレスモード (DAAI、DAA0)を B'00 または B'01 に設定した場合、シングルアドレス転送のタイミングで転送を行います。 DMA アドレスモードを B'10 に設定した場合、デュアルアドレス転送のタイミングで転送を行います。このときの Q2SD へのアクセスは、 $\overline{DACK}$ を Low レベルにすることにより行ってください。 $\overline{CSO}$  は無視されます。

UGM アクセス時は DMA モードを B'01 に、Q2SD アドレスマップドレジスタ(画像データエントリレジスタ IDER)のアクセス時は DMA モードを B'11 に設定します。他のアドレスマップドレジスタにはアクセスできません。Q2SD は、DMA 転送開始アドレス(DMASH、L)に設定されたディスティネーションアドレス(UGM アドレス)から DMA 転送語数(DMAWH、L)に設定されたワード数の転送を行います。Q2SD は内蔵のアドレスカウンタで UGM のアドレスを制御します。外部から入力されたアドレスは使用しません。

DMA 転送終了後、再度 DMA モードの設定を行うときは、ステータスレジスタの DMF ビットが 1 になった (DMA 転送終了) ことを確認してから行ってください。

なお、SuperH 外部バス上の SDRAM から Q2SD へのシングル DMA 転送では、 $\overline{\text{RD}}$  信号の立ち上がりに対する D0~D15 のセットアップ( $t_{wrders}$ )を Q2SD の動作クロックの 2 サイクル以上必要とするため、SuperH 外部バス 動作周波数は動作クロック周波数の 1/2 以下でなければなりません。

- (1)デュアルアドレスモードで DMA 転送を行う場合の SuperH の設定

- 書き込みサイクルでDACKを出力

- ローアクティブでDACKを出力

- ディスティネーションアドレスは固定させる(UGMの任意のアドレスを設定)

- ソースアドレスは増加させる

- 外部リクエスト、デュアルアドレスモード

- DREQは立ち下がりエッジ検出

- サイクルスチールモード

(2) シングルアドレスモードで DMA 転送を行う場合の SuperH の設定

- リードサイクルでDACKを出力

- ローアクティブでDACKを出力

- ディスティネーションアドレスは固定させる

- ソースアドレスは増加させる

- 外部リクエスト、シングルアドレスモード

- DREQは立ち下がりエッジ検出

- サイクルスチールモード

なお、SuperH では、初期値で  $\overline{DACK}$  端子がアクティブハイとなる製品があります。この場合には、DACK 端子を初期値(アクティブハイ)のままとし、外付け回路で  $\overline{DACK}$  端子の信号を反転したものを Q2SD の  $\overline{DACK}$  端子に接続してください。

#### 2.5.4 割り込み

Q2SD は、内部要因により SuperH に対して割り込みを要求します。割り込み要因は、割り込み許可レジスタ (IER)により設定します。

# 2.6 UGM インタフェース端子

(MA0~MA13, MD0~MD31, MCS, MWE, MRAS, MCAS, LDQM0, LDQM1, UDQM0, UDQM1, MCLK)

Q2SD は、SDRAM を UGM とします。 Q2SD は、SDRAM の直結インタフェースを持っています。 ただし、SDRAM の CKE 端子は High レベル固定とし、データ幅が 16 ビットの SDRAM を 1 個だけ接続する場合は、MD0~MD15 の端子を使用してください。 MD16~MD31 端子は開放としてください。

SDRAM の動作モード(書き込みモード、CAS レイテンシ、バーストタイプ、バースト長)は、Q2SD が電源 投入の立ち上がり後、自動的に設定します。リフレッシュはオートリフレッシュモードを用いて行い、プリチャージは、オールバンクプリチャージコマンド(PALL)を用いて行います。

## 2.7 表示インタフェース端子

表示インタフェース端子から出力される信号はすべて、表示動作クロックに同期しています。

## 2.7.1 表示信号出力

(R, G, B)

RGB アナログ表示信号を出力します。画素のデータ分解能は、RGB 各 6 ビットです。表示期間外では、画像データ (R、G、B) が H'000 に相当するレベルになります。

#### 2.7.2 ビデオエンコーダインタフェース

( CSYNC )

コンポジットシンク(CSYNC)を出力します。また、マスタモード時、コンポジットシンクに等化パルスを付加させることもできます。

## 2.7.3 CRT インタフェース

( HSYNC, EXHSYNC, VSYNC, EXVSYNC, DISP, CDE, ODDF)

HSYNC/EXHSYNC、VSYNC/EXVSYNC、ODDF 端子で、水平同期信号、垂直同期信号、インタレース制御のための現フィールドが偶数か奇数かを示す信号を入出力します。Q2SD が同期マスタの場合はこれら端子を出力とし、外部装置(TV、ビデオ)に同期を合わせるときは、入力にします。リセット時は、入力になっているので、これらの端子を無意味の方向にレベル固定すること(プルアップ)が必要です。マスタ(出力)かTV 同期(入力)かの設定は表示モードレジスタ(DSMR)のTV 同期モード(TVMI、TVM0)で行います。

CDE 端子は UGM 上の表示領域の特定色を検出すると H を出力します。特定色の設定は色検出レジスタ CDER で行います。 CDE 信号を、外部に設ける外部ビデオ / Q2 グラフィックス画像の選択回路の選択信号に用いることで、1 画素単位での外部ビデオと Q2 グラフィックス画像の表示合成ができます。 DISP 端子は表示期間を示します。 表示期間は H を出力します。

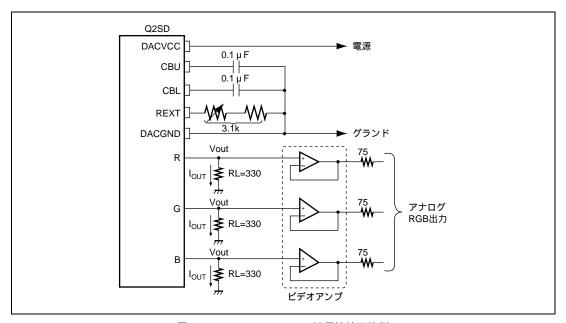

#### 2.7.4 D/A コンバータ

(CBU, CBL, REXT)

D/A コンバータは、表示データに対してリニアに変化します。CBU、CBL、REXT には、所定の抵抗および容量を接続してください。

R、G、B の出力端子には、負荷抵抗 RL を接続してください。出力電流 Iout の最大値 Ioutmax と REXT との関係は次式で与えられます。

REXT =  $(2.842/Ioutmax) \times DACVCC$

負荷抵抗 RLに Ioutmax の電流が流れたときの出力振幅を Vout とすると、

REXT =  $(2.842/(Vout/RL)) \times DACVCC$

となります。

したがって、RL=330 、DACVCC=3.3Vのとき、Vout=1VPPを得るためには、REXT=3.1k となります。

なお、出力最大電流 Ioutmax は 2.0mA から 3.0mA の範囲で使用してください。

D/A コンバータは 8 ビットの分解能力を持っていますが、動的整定誤差は、負荷抵抗 RL、出力端子負荷容量(配線分とビデオアンプ入力容量の合計) C、および表示動作周波数 f で決まります。

たとえば、RL = 330 、C = 20 pF、f = 33 MHz とすると、下記の式を満足するときの n の値が、このときの D/A コンバータの精度になります。

$$\exp\left(\frac{-1}{RL\cdot C\cdot f}\right) \le \frac{1}{2^n}$$

ただし、nは整数

つまりこのときの n は 6 になりますので、D/A コンバータの精度は 6 ビット精度(動的整定誤差は、 $\frac{1}{2}$  = 1.56%フルスケール)になります。

図 2.5 REXT、CBU、CBL 端子接続回路例

# 2.8 ビデオ取り込みインタフェース端子

(VINO~VIN7, VHS, VVS, VODD, VQCLK)

## 2.8.1 ビデオ取り込みインタフェース

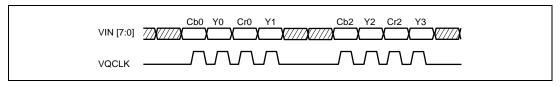

$VIN0 \sim VIN7$  には、VQCLK に同期した 8 ビット YCbCr 4:2:2 ビデオデータを入力してください。 VQCLK は有効なデータがあるときのみ、データと 1 対で入力するようにしてください。

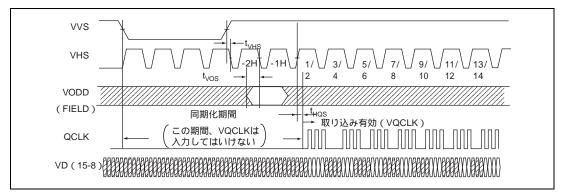

VHS、VVS には水平、垂直同期信号を入力してください。これらの信号により、データ取り込み開始位置が決まります。 VODD はビデオデータのフィールドを示す記号を入力してください。Low レベルは奇数フィールドを、High レベルは偶数フィールドを示します。 VODD の極性が NTSCC ビデオデコーダと一致しない場合は、ビデオデコーダの設定を変更するか、外部で極性反転回路を挿入してください。

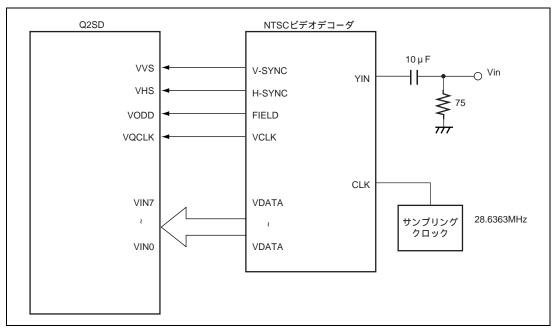

図 2.6 ビデオ取り込み端子接続例

# 3. UGM アーキテクチャ

# 3.1 特長

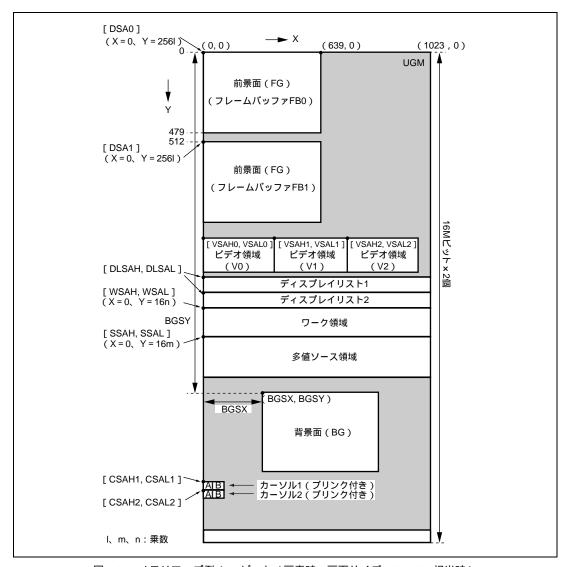

Q2SD に接続されるユニファイドグラフィックスメモリ(UGM)は、以下の目的のために使用されます。

- 前景面(FG)、背景面(BG)、カーソル面の各領域

Q2SDの描画および表示を行う領域です。前景面はダブルバッファ構成(フレームバッファ0:FB0、フレームバッファ1:FB1)となっています。

- ディスプレイリスト領域

Q2SDのコマンドリストの格納領域です。Q2SDは、この領域のコマンドをフェッチしながら描画を行います。

- ワーク領域、ソース領域、レンダリング領域等

ワーク領域は、塗りつぶしや、型抜き用のパターンの格納およびFTRAPコマンド描画領域です。2値ソース 領域は、フォントデータの格納領域です。多値ソース領域は、自然画やアイコン等の格納領域です。レン ダリング領域は、DSARレジスタおよびRSARレジスタで指定されるレンダリング実行領域です。

- ビデオ領域

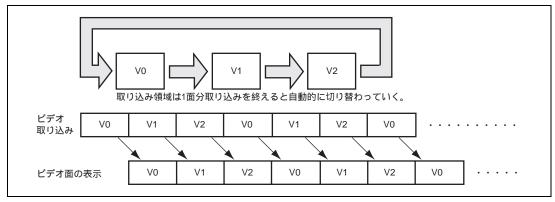

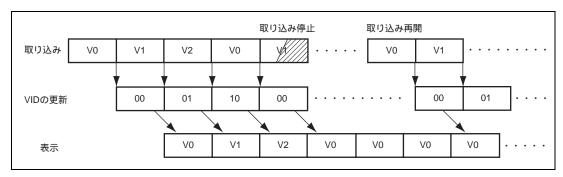

ビデオ取り込み機能で取り込んだビデオデータを3面分格納する領域です(1面の大きさはビデオウィンドウサイズになります)。

- その他

UGMは、CPUの主記憶領域の一部に割り当てることができるため、上記の他にもCPUの作業領域などに使用することができます。

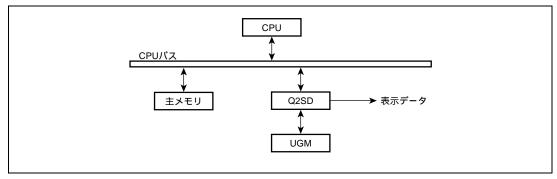

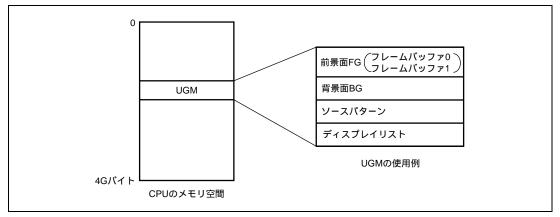

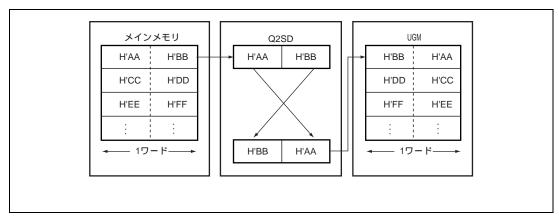

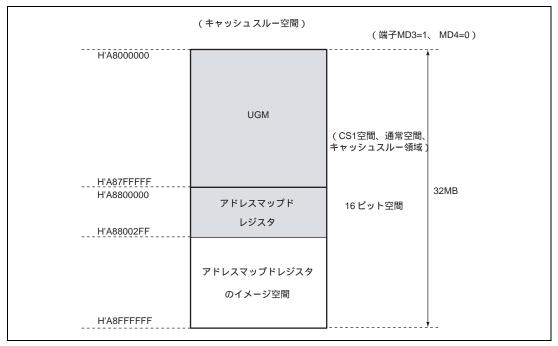

UGM を使用したシステム構成例を図 3.1 に、CPU メモリ空間に対する UGM のマッピング例を図 3.2 に示します。

図 3.1 UGM を使用したシステム構成例

図 3.2 CPU メモリ空間に対する UGM のマッピング例

## 3.2 Q2SD アクセス

## 3.2.1 UGM アクセスの優先順位

UGM のアクセス優先順位は、以下のようになります。

- 1. リフレッシュ

- 2. 表示

- 3. ビデオ取り込み

- 4. CPU

- 5. その他(コマンドフェッチ、描画、ソース参照等)

Q2SD は、それぞれが並行して処理を可能とするため一定の期間アクセスを行った後、他の要求元にアクセス権を渡します。たとえば、3つの要因がアクセスを要求している場合は、それぞれが交代してアクセスします。

## 3.2.2 CPU の UGM アクセス

UGM は、CPU のメモリ空間の一部として扱います。

ライト動作の場合は、32 バイトの内蔵 FIFO に空きがある場合は最小のウェイトサイクルでアクセス可能です。

リード動作の場合は、数サイクル~数十サイクルのウェイトが入ります。ウェイトサイクル数は、Q2SD動作クロックと表示動作クロックの関係や画面サイズにより異なります。

FIFO 内に蓄積されたデータの UGM へのストア実行は、システム制御レジスタ (SYSR)のレンダリングスタートビット(RS)が 1 セットされたとき、CPU からの UGM アクセスが 32tcyc0 期間以上アクセスなかったとき、FIFO がいっぱいになったとき、CPU からの UGM リードアクセスがあったときに起こります。

また、CPU に MMU 付きの SuperH を用いた場合は、UGM を SuperH の通常空間で SRAM モードでマッピングしてください。

## 3.2.3 DMAC の UGM アクセス

DMAC を用いて、CPU バスに接続されたメモリと UGM との間でのデータ転送が可能です。この DMA 転送は、ディスプレイリストや画像データの転送に使用することができます。

DMA 転送の場合は、Q2SD 内蔵のアドレスカウンタで UGM のアドレスを制御します。転送アドレスモードは、シングルアドレスモード、デュアルアドレスモードが可能です。ただし、バスモードはサイクルスチールモードのみで、バーストモードはサポートしていません。「2.5.3 DMA ライト」を参照してください。

## 3.2.4 Q2SD の UGM アクセス

UGM としては、SDRAM を用い、Q2SD と直接接続します。SDRAM を用いることにより、Q2SD は 1 サイクル (動作クロック)単位でメモリアクセスが可能となります。

UGM として使用可能な SDRAM は、最大 2 つ (バス幅が $\times$  16 の場合)までで、電源電圧が 3.3V、Q2SD の電気的特性と初期化シーケンスを満足するメモリです。メモリ構成は下記が使用可能です。

- 1. 容量64Mビット(1Mビット×16×4バンク構成)

- 2. 容量64Mビット(512kビット×32×4バンク構成)

- 3. 容量16Mビット(512kビット×16×2バンク構成)

メモリの種類は、メモリモードレジスタ (MEMR)で設定します。

## 3.2.5 CPU のレジスタアクセス

Q2SD は、CPU のバイトアドレス空間上( $H'000 \sim H'7FE$ ) にマッピングされるアドレスマップドレジスタを内蔵しています。インタフェース制御レジスタ、メモリ制御レジスタ、表示制御レジスタ(含カラーパレット)、レンダリング制御レジスタ、データ転送制御レジスタから構成されています。カラーパレットのアクセスはロングワードアクセスのみ有効になります。それ以外のレジスタのアクセスは、ワードアクセスになります。アドレス指定は、 $\overline{CSI}$  端子 = 0 の状態で、 $A22 \sim A1$  端子からアドレスを入力することで行います。

リザーブとなっているアドレスには、読み出し/書き込みは行わないでください。読み出し/書き込みを行うとアドレスマップドレジスタの値が失われ、Q2SDの動作が不定になることがあります。

また、Q2SD は UGM へのアクセス権を管理するため、CPU が UGM をアクセスする前に CPU にてアドレスマップドレジスタに初期値を設定しておく必要があります。

以下に設定手順を示します。

- 1. システム制御レジスタに (SYSR) 初期値を設定します。このとき、SRES = 0、DRES = 1、DEN = 0を設定します。

- 2. そのほかのレジスタに初期値を設定してください。

- 3. SRES = 0、DRES = 0に設定します。

また、ビデオ制御関連のレジスタのビデオ領域開始アドレスレジスタ0~2(VSAR0~2)、ビデオウィンドウサイズレジスタ(VSIZER)、ビデオ取り込みモードレジスタ(VIMR)は、ビデオ取り込み動作に対して外部更新であるため、その書き換えは、ビデオ取り込みモードレジスタ(VIMR)のビデオ取り込みイネーブルビット(VIE)に0を設定した状態で行ってください。これは、VIMR の VIE ビット以外のビットを変更するときも同様です。以下に手順を示します。

- 1. VIMRのVIEビットを0に設定します。このとき、VIEビット以外のビットは、その時点で設定されている値を保持してください。

- 2. VVSの1周期を経過した後に、VSAR0~2、VSIZER、VIMRのVIEビット以外の変更を行ってください。

- 3. VIMRのVIEビットを1に設定してください。このとき、VIEビット以外のビットは、その時点で設定されている値を保持してください。

#### 3.2.6 レジスタの更新

#### (1) 外部更新

外部更新とは、CPU がアドレスマップドレジスタに設定した値が、CPU のアクセス終了後に反映されることをいいます。また、表示制御に関係するレジスタで、外部更新により設定値を更新するレジスタ(たとえばカラーパレットレジスタ)は、ステータスレジスタ(SR)の VBK フラグ、および FRM フラグが垂直方向のブランキング期間を示している間に書き換えれば、表示がちらつくことなく書き換えられます。

#### (2) 内部更新

内部更新とは、アドレスマップドレジスタに設定された値が、Q2SDの内部の更新タイミングで反映されることをいいます。このため、内部更新機能付きレジスタの場合、CPUが表示タイミングを意識せずに表示動作に関するアドレスマップドレジスタを書き換えても、表示のちらつきを生じさせないようにすることができます。

内部更新は、システム制御レジスタ (SYSR)の DRES ビット = 1 の期間、およびフレームの先頭で行います。表示モードレジスタ (DSMR)の WRAP ビット、BG ビット、およびインタレースシンク&ビデオモードにおける BGSX、BGSY は、フィールドの先頭においても内部更新が行われます。更新のタイミングは、DSMR のテレビ同期モードが、TVM1 = 0、TVM0 = 0(マスタモード)のときは  $\overline{\text{VSYNC}}$  の立ち下がり設定時となり、TVM1 = 1、TVM0 = 0 (TV 同期モード)のときは  $\overline{\text{EXVSYNC}}$  の立ち下がり検出時となります。また、TVM1 = 0、TVM0 = 1 (同期切り替えモード)のときは、内部更新を行いません。

内部更新機能付きのアドレスマップドレジスタを表 3.1 に示します。これらのレジスタの初期設定は、DRES ビット = 1 の期間に行ってください。ただし、表示開始アドレスレジスタ 0 (DSARO)、表示開始アドレスレジスタ 1 (DSA1R)、およびレンダリングモードレジスタ (REMR)のグラフィックビットモードビット (GBM)は、表示動作のとき内部更新となります。描画動作のときは外部更新となります。

また、ビデオ領域開始アドレス(VSAR0~2)、ビデオ表示位置(VPR)、ビデオウィンドウサイズ(VSIZE)は、表示動作のときは、内部更新となり、ビデオ取り込み動作中のときは外部更新となります。

## 表 3.1 内部更新機能付きレジスタ

## Q2制御レジスタ

| アドレス<br>A[10:0] | 名 称           | 略称    | 内部更新機能を持つビット |

|-----------------|---------------|-------|--------------|

| H'000           | システム制御レジスタ    | SYSR  | DEN (ビット 13) |

| H'00A           | 表示モードレジスタ     | DSMR  | WRAP (ビット11) |

|                 |               |       | BG (ビット10)   |

| H'00C           | レンダリングモードレジスタ | REMR  | GBM (ビット2~0) |

| H'056           | 表示モード2レジスタ    | DSMD2 | 全ビット         |

## メモリ制御レジスタ

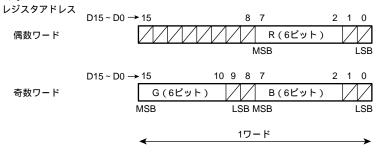

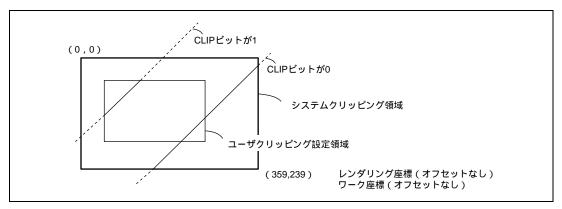

| アドレス<br>A[10:0] | 名 称            | 略称    | 内部更新機能を持つビット |