## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

## ユーザーズ・マニュアル

# μPD178048 サブシリーズ

8 ピット・シングルチップ・マイクロコンピュータ

μPD178046 μPD178048 μPD178F048 (メ モ)

### 目次要約

第1章 概 説 ... 25 第 2 章 端子機能 ... 33 **第3章** CPU**アーキ**テクチャ ... 43 第4章 ポート機能 ... 75 **第5章 クロック発生回路** ... 93 第6章 8ビット・タイマ/イペント・カウンタ (TM5) ... 101 第7章 8ビット・タイマ (TM20) ... 119 第8章 8ビット・イベント・カウンタ (TM21) ... 127 **第9章 8ピット・リモコン・タイマ(TM9)** ... 135 第10章 ペーシック・タイマ (BTM1) ... 141 **第11章 ウォッチドッグ・タイマ** ... 145 第12章 A/D**コンバータ** ... 153 第13章 シリアル・インタフェース(IIC1) ... 171 第14章 シリアル・インタフェース(SIO3) ... 213 **第**15**章 8ビット**PWM ... 221 第16章 14**ビット**PWM ... 229 第17章 OSDコントローラ ... 237 第18章 ROMコレクション ... 263 第19章 割り込み機能 ... 273 第20章 スタンバイ機能 ... 295 第21章 リセット機能 ... 303 **第**22章 μPD178F048 ... 311

第23章 命令セットの概要 ... 319

付 録 ... 335

#### CMOSデバイスの一般的注意事項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース,または導電性の緩衝材,金属ケースなどを利用し,組み立て工程にはアースを施してください。プラスチック板上に放置したり,端子を触ったりしないでください。

また, MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入 時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作 やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

#### EEPROMは,日本電気株式会社の商標です。

WindowsおよびWindowsNTは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。 PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは, 米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

イーサネットは,米国ゼロックス社の商標です。

NEWS, NEWS-OSは, ソニー株式会社の商標です。

OSF/Motifは, Open Software Foundation, Inc.の商標です。

TRONは, The Realtime Operating system Nucleusの略称です。

ITRONは, Industrial TRONの略称です。

本製品のうち,外国為替および外国貿易管理法の規定により規制貨物等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

★ 非該当品: μPD178F048GK-BE9

ユーザ判定品: μ PD178046GK-×××-BE9, 178048GK-×××-BE9

注意: μ PD178048サブシリーズはI<sup>2</sup>Cバス・インタフェース回路を内蔵しています。

I<sup>2</sup>Cバス・インタフェースを使用される場合には,カスタム・コードをご発注いただく時に,事前にその旨ご申告下さい。申告に基づき,以下の特典が受けられます。

日本電気株式会社のI<sup>2</sup>Cバス対応部品をご購入いただくことにより,これらの部品をI<sup>2</sup>Cシステムに使用する実施権がフィリップス社I<sup>2</sup>C特許に基づき許諾されることになります。ただし,これらのI<sup>2</sup>Cシステムはフィリップス社によって設定されたI<sup>2</sup>C標準規格に合致しているものとします。

Purchase of NEC I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- 本資料の内容は予告なく変更することがありますので,最新のものであることをご確認の上ご使用ください。

- 文書による当社の承諾なしに本資料の転載複製を禁じます。

- 本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんのでご了承ください。

- ◆本資料に記載された回路,ソフトウエア,及びこれらに付随する情報は,半導体製品の動作例,応用例を説明するためのものです。従って,これら回路・ソフトウエア・情報をお客様の機器に使用される場合には,お客様の責任において機器設計をしてください。これらの使用に起因するお客様もしくは第三者の損害に対して,当社は一切その責を負いません。

- 当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

M7 98.8

### 本版で改訂された主な箇所

| 箇 所           | 内容                                             |

|---------------|------------------------------------------------|

| 全 般           | 64ピン・シュリンクDIPの削除                               |

|               | (GND0, GND1端子の記述削除)                            |

| p.57, 335-341 | ・インサーキット・エミュレータIE-78001-R-Aの削除(IE-78K0-NSのみ対応) |

|               | ・統合ディバッガID78K0の削除(ID78K0-NSのみ対応)               |

| p.259-261     | 17. <b>5</b> OSD <b>コントローラ使用上の注意</b>           |

|               | ・VRAM書き込みの流れを変更                                |

|               | ・対策例 2 を変更                                     |

| p.314-318     | 22.3 フラッシュ・メモリ・プログラミング                         |

|               | ・IIC1方式を疑似 3 線式に変更                             |

|               | ・フラッシュ書き込み時の注意事項を追加                            |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

### はじめに

- **対象者** このマニュアルは, μ PD178048サブシリーズの機能を理解し, その応用システムや応用プログラムを設計, 開発するユーザのエンジニアを対象としています。

- **目** 的 このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

- 構 成 μPD178048サブシリーズのマニュアルは,このマニュアルと命令編(78K/0シリーズ共通)の2冊に分かれています。

μ PD178048サブシリーズ ユーザーズ・マニュアル 78K/0シリーズ ユーザーズ・マニュアル 命令編

端子機能

内部ブロック機能

割り込み

その他の内蔵周辺機能

CPU機能

命令セット

命令の説明

- 読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

- 一通りの機能を理解しようとするとき

目次に従って読んでください。

μ PD178048サブシリーズの命令機能の詳細を知りたいとき

別冊の78K/0シリーズ ユーザーズ・マニュアル 命令編(U12326J)を参照してください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がDF178048、RA78K0では予約語に、CC78K0 ではsfrbit.hというヘッダ・ファイルで定義済みとなっているものです。

μPD178048サブシリーズの電気的特性を知りたいとき

別冊のデータ・シートを参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : ××× (端子, 信号名称に上線)

注 : 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数...××××または××××B

10進数...×××× 16進数...××××H

**関連資料** 関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめご 了承ください。

#### デバイスの関連資料

#### μPD178048**サブシリーズの関連資料**

| 資 料 名                          |   | 資料番号    |         |

|--------------------------------|---|---------|---------|

|                                |   | 和文      | 英文      |

| μ PD178046, 178048 ペーパ・マシン     |   | U13183J | U13183E |

| μPD178F048 ペーパ・マシン             |   | U13056J | U13056E |

| μPD178048サブシリーズ ユーザーズ・マニュア     | ル | このマニュアル | 作成予定    |

| 78K/0シリーズ ユーザーズ・マニュアル 命令編      |   | U12326J | U12326E |

| 78K/0シリーズ インストラクション活用表         |   | U10903J | -       |

| 78K/0シリーズ インストラクション・セット        |   | U10904J | -       |

| 78K/0シリーズ アプリケーション・ノート 基礎編     |   | U12704J | U12704E |

| 78K/0, 78K/0Sシリーズ アプリケーション・ノート |   | U14458J | U14458E |

| フラッシュ・メモリ書き込み編                 |   |         |         |

#### ★ 開発ツールの関連資料 (ユーザーズ・マニュアル)

| 資 料 名                         |             | 資料番号    |          |

|-------------------------------|-------------|---------|----------|

|                               |             | 和文      | 英 文      |

| RA78KO アセンブラ・パッケージ            | 操作編         | U11802J | U11802E  |

|                               | 言語編         | U11801J | U11801E  |

|                               | 構造化アセンブリ言語編 | U11789J | U11789E  |

| RA78Kシリーズ 構造化アセンブラ・プリプロセッサ    |             | U12323J | EEU-1402 |

| CC78K0 Cコンパイラ                 | 操作編         | U11517J | U11517E  |

|                               | 言語編         | U11518J | U11518E  |

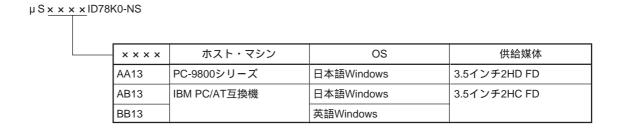

| IE-78K0-NS                    |             | U13731J | U13731E  |

| IE-178048-NS-EM1              |             | 作成予定    | 作成予定     |

| ID78K0-NS 統合ディバッガ Windows™ベース | レファレンス編     | U12900J | U12900E  |

| SM78K0 システム・シミュレータ Windowsベース | レファレンス編     | U10181J | U10181E  |

| SM78Kシリーズ システム・シミュレータ         | 外部部品ユーザオープン | U10092J | U10092E  |

|                               | インタフェース仕様編  |         |          |

#### 組み込み用ソフトウエアの関連資料 (ユーザーズ・マニュアル)

| 資 料 名               |         | 資料      | 番号      |

|---------------------|---------|---------|---------|

|                     |         | 和文      | 英 文     |

| 78K/0シリーズ リアルタイムOS  | 基礎編     | U11537J | U11537E |

|                     | インストール編 | U11536J | U11536E |

| 78K/0シリーズ用OS MX78K0 | 基礎編     | U12257J | U12257E |

#### その他の関連資料

| 資 料 名                                                        | 資料      | 資料番号    |  |

|--------------------------------------------------------------|---------|---------|--|

|                                                              | 和文      | 英文      |  |

| SEMICONDUCTOR SELECTION GUIDE Products & Packages ( CD-ROM ) | X13769X |         |  |

| 半導体デバイス 実装マニュアル                                              | C10535J | C10535E |  |

| NEC半導体デバイスの品質水準                                              | C11531J | C11531E |  |

| NEC半導体デバイスの信頼性品質管理                                           | C10983J | C10983E |  |

| 静電気放電(ESD)破壊対策ガイド                                            | C11892J | C11892E |  |

| 半導体 品質 / 信頼性ハンドブック                                           | C12769J | -       |  |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                                     | U11416J | -       |  |

#### 注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

(メ モ)

## 目 次

| 第1章 概 説              | 25                                              |

|----------------------|-------------------------------------------------|

| 1.1 特 徵              | 25                                              |

| 1.2 応用分野             |                                                 |

| 1.3 オーダ情             |                                                 |

|                      | 図(Top View) 27                                  |

|                      | DTS <b>シリーズの展開</b> 29                           |

| 1.6 ブロック<br>1.7 機能概要 |                                                 |

| 1./ 放形机头             | 31                                              |

| 第2章 端子機能             | 33                                              |

| 2.1 端子機能             |                                                 |

|                      | <b>の説明</b> 35                                   |

| 2.2.1                |                                                 |

|                      | P10-P13 ( Port1 ) 35                            |

|                      | P20-P23 ( Port2 ) 35<br>P40-P47 ( Port4 ) 36    |

|                      | P50-P54 (Port5) 36                              |

|                      | P60-P67 (Port6 ) 36                             |

|                      | P70-P77 (Port7) 36                              |

|                      | P130-P134 ( Port13 ) 37                         |

|                      | VSYNC 37                                        |

| 2.2.10               | HSYNC 37                                        |

| 2.2.11               |                                                 |

|                      | G 37                                            |

|                      | В 37                                            |

| 2.2.14               |                                                 |

|                      | BLANK 37                                        |

|                      | OSC1, OSC2 37<br>RESET 38                       |

| 2.2.17               |                                                 |

|                      | VDD 38                                          |

|                      | GND00, GND10, GND01, GND11 38                   |

|                      | VDDPORT 38                                      |

| 2 . 2 .22            | GNDPORT 38                                      |

|                      | NC 38                                           |

|                      | Vpp (μPD178F048のみ) 38                           |

|                      | IC (マスクROM製品のみ) 39                              |

| 2.3 端子の入             | 出力回路と未使用端子の処理 40                                |

| 第3章 CPU <b>ア</b> ー   | ・キテクチャ 43                                       |

| 3.1 メモリ空             | <b>間</b> 43                                     |

| 3.1.1                | 内部プログラム・メモリ空間 47                                |

|                      | 内部データ・メモリ空間 48                                  |

| 3.1.3                | 特殊機能レジスタ (SFR: Special Function Register) 領域 48 |

| 3.2                                     | プロセッサ・レジスタ 52                                    |    |

|-----------------------------------------|--------------------------------------------------|----|

|                                         | 3.2.1 制御レジスタ 52                                  |    |

|                                         | 3.2.2 汎用レジスタ 55                                  |    |

|                                         | 3.2.3 特殊機能レジスタ(SFR: Special Function Register) 5 | 57 |

| 3.3                                     | <b>命令アドレスのアドレシング</b> 61                          |    |

|                                         | 3.3.1 レラティブ・アドレシング 61                            |    |

|                                         | 3.3.2 イミーディエト・アドレシング 62                          |    |

|                                         | 3.3.3 テーブル・インダイレクト・アドレシング 63                     |    |

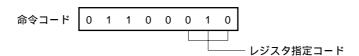

|                                         | 3.3.4 レジスタ・アドレシング 64                             |    |

| 3 4                                     | オペランド・アドレスのアドレシング 65                             |    |

| • • • • • • • • • • • • • • • • • • • • | 3.4.1 インプライド・アドレシング 65                           |    |

|                                         | 3.4.2 レジスタ・アドレシング 66                             |    |

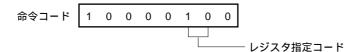

|                                         | 3.4.3 ダイレクト・アドレシング 67                            |    |

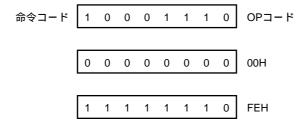

|                                         | 3.4.4 ショート・ダイレクト・アドレシング 68                       |    |

|                                         |                                                  |    |

|                                         | 3.4.5 特殊機能レジスタ (SFR) アドレシング 70                   |    |

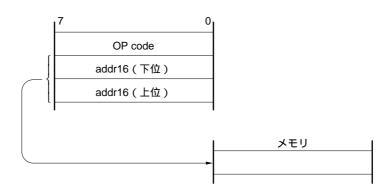

|                                         | 3.4.6 レジスタ・インダイレクト・アドレシング 71                     |    |

|                                         | 3.4.7 ベースト・アドレシング 72                             |    |

|                                         | 3.4.8 ベースト・インデクスト・アドレシング 73                      |    |

|                                         | 3.4.9 スタック・アドレシング 73                             |    |

|                                         | معناها ا                                         |    |

| <b>弗4</b> 草                             | <b>ポート機能</b> 75                                  |    |

|                                         | 10 1 a MAA                                       |    |

|                                         | <b>ポートの機能</b> 75                                 |    |

| 4.2                                     | ポートの構成 77                                        |    |

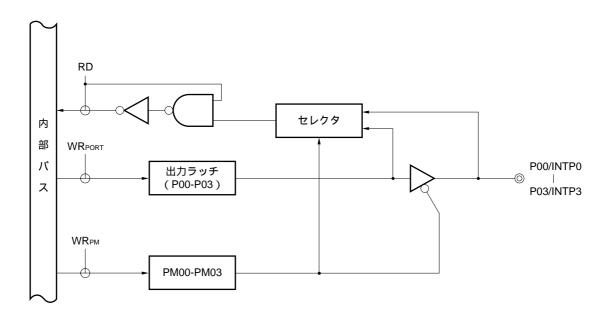

|                                         | 4.2.1 ポート0 77                                    |    |

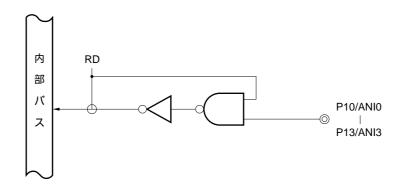

|                                         | 4.2.2 ポート1 79                                    |    |

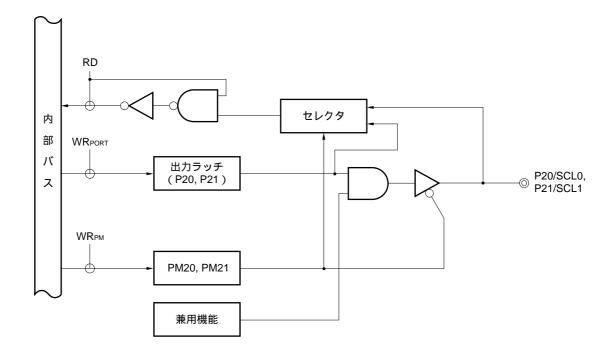

|                                         | 4.2.3 ポート2 80                                    |    |

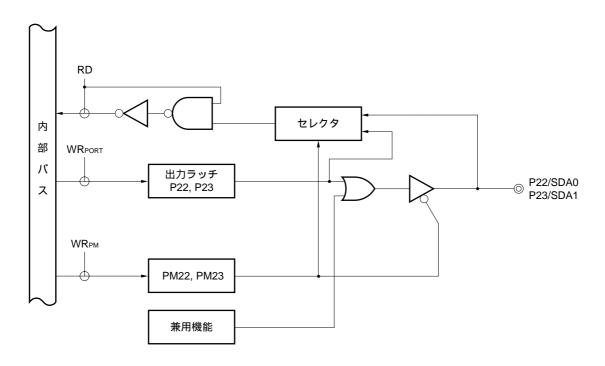

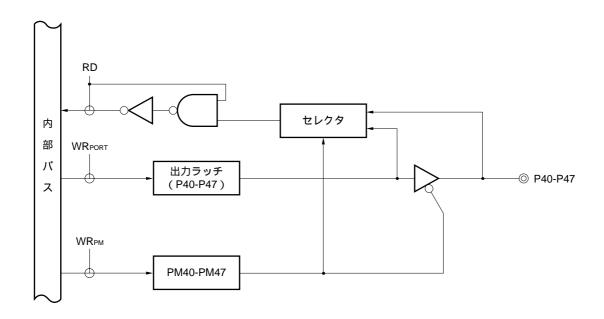

|                                         | 4.2.4 ポート4 82                                    |    |

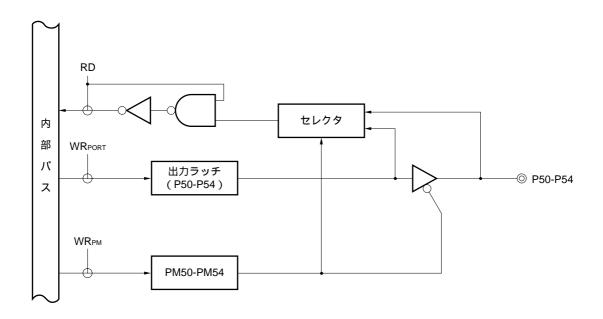

|                                         | 4.2.5 ポート5 83                                    |    |

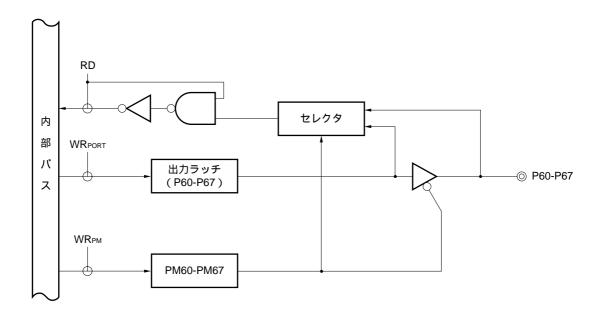

|                                         | 4.2.6 ポート6 84                                    |    |

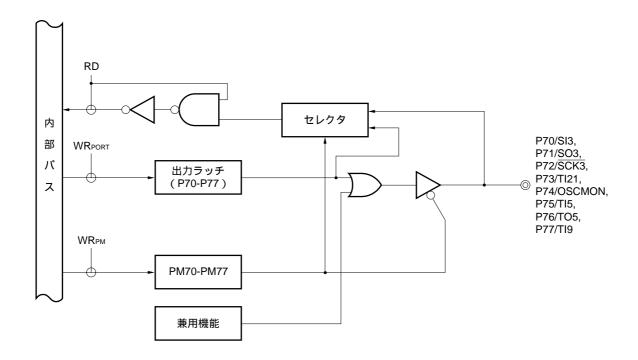

|                                         | 4.2.7 ポート7 85                                    |    |

|                                         | 4.2.8 ポート13 86                                   |    |

| 4.3                                     | ポート機能を制御するレジスタ 87                                |    |

| 4.4                                     | ポート機能の動作 90                                      |    |

|                                         | 4.4.1 入出力ポートへの書き込み 90                            |    |

|                                         | 4.4.2 入出力ポートからの読み出し 90                           |    |

|                                         | 4.4.3 入出力ポートでの演算 91                              |    |

|                                         |                                                  |    |

| 第5章                                     | <b>クロック発生回路</b> 93                               |    |

|                                         |                                                  |    |

| 5.1                                     | <b>クロック発生回路の機能</b> 93                            |    |

|                                         | <b>クロック発生回路の構成</b> 93                            |    |

|                                         | クロック発生回路を制御するレジスタ 94                             |    |

|                                         | システム・クロック発振回路 95                                 |    |

| J. <del>T</del>                         | 5.4.1 システム・クロック発振回路 95                           |    |

|                                         |                                                  |    |

| E F                                     | 5.4.2 分周回路 97                                    |    |

|                                         | クロック発生回路の動作 98                                   |    |

| 5.0                                     | システム・クロックとCPUクロックの設定の変更 … 99                     | 00 |

|                                         | 5.6.1 システム・クロックとCPUクロックの切り替えに要する時間               | 99 |

|                                         |                                                  |    |

3.1.4 データ・メモリ・アドレシング ... 49

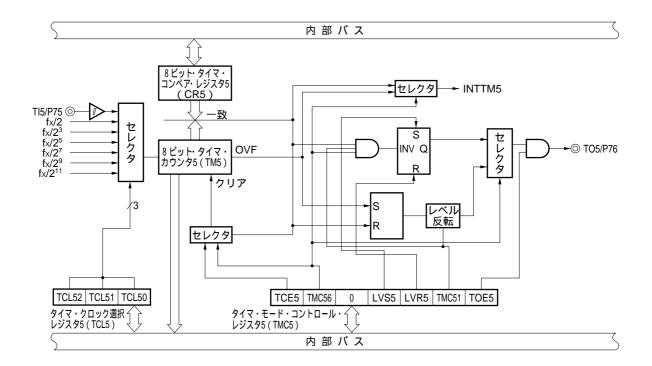

| 第6章          | 8 ビット・タイマ / イベント・カウンタ (TM5) 101                      |

|--------------|------------------------------------------------------|

| 6.1          | <b>8 ビット・タイマ / イベント・カウンタ (</b> TM5 <b>) の機能</b> 101  |

| 6.2          | <b>8 ビット・タイマ / イベント・カウンタ (</b> TM5 <b>) の構成</b> 102  |

| 6.3          | <b>8 ビット・タイマ / イベント・カウンタ (TM5) を制御するレジスタ</b> 103     |

| 6.4          | <b>8 ビット・タイマ / イベント・カウンタ (</b> TM5 <b>) の動作</b> 106  |

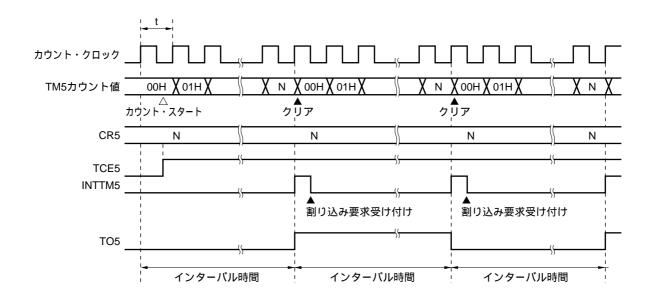

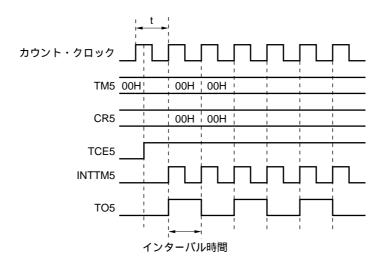

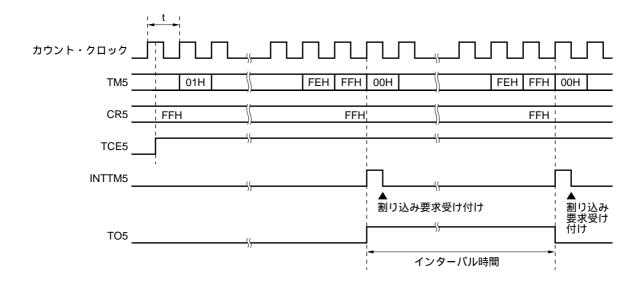

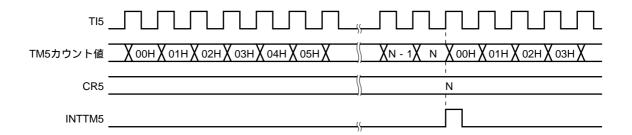

|              | 6.4.1 インターバル・タイマ(8ビット)としての動作 106                     |

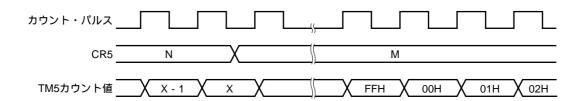

|              | 6.4.2 外部イベント・カウンタとしての動作 110                          |

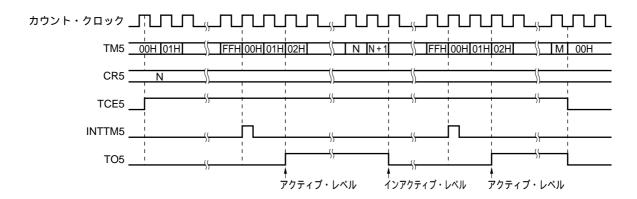

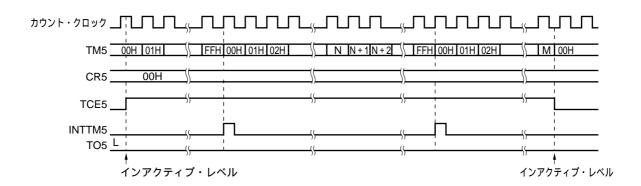

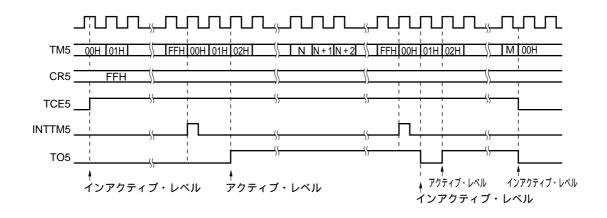

|              | 6.4.3 方形波出力(8ビット分解能)としての動作 111                       |

|              | 6.4.4 8 ビットPWM出力としての動作 112                           |

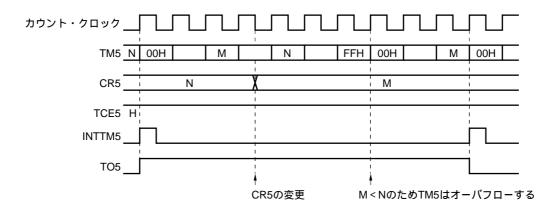

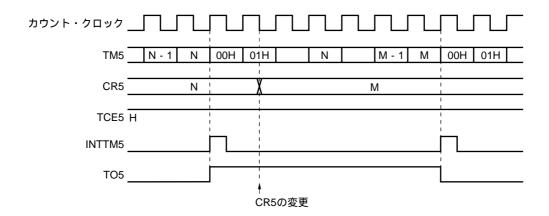

| 6.5          | <b>8 ビット・タイマ / イベント・カウンタ (</b> TM5) <b>の注意事項</b> 115 |

| 第7章          | 8 ピット・タイマ (TM20) 119                                 |

| 7.1          | <b>8 ビット・タイマ (</b> TM20 <b>) の機能</b> 119             |

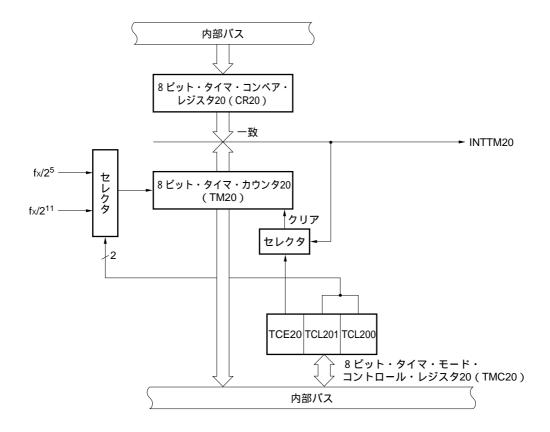

| 7.2          | <b>8 ビット・タイマ (</b> TM20 <b>) の構成</b> 119             |

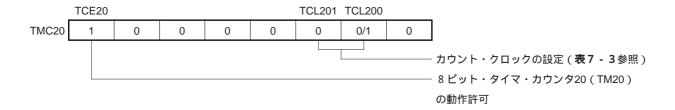

| 7.3          | <b>8 ビット・タイマ (</b> TM20 <b>) を制御するレジスタ</b> 121       |

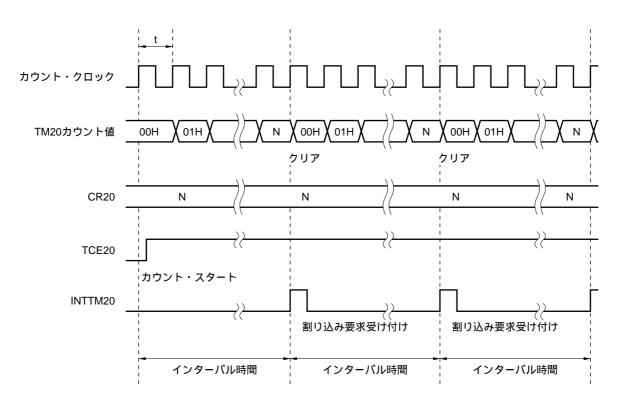

| 7.4          | <b>8 ビット・タイマ (</b> TM20 <b>) の動作</b> 122             |

| 7.5          | <b>8 ビット・タイマ (</b> TM20 <b>) の注意事項</b> 124           |

| 第8章          | 8 ピット・イベント・カウンタ (TM21) 127                           |

| 8.1          | <b>8 ビット・イベント・カウンタ (</b> TM21 <b>) の機能</b> 127       |

| 8.2          | <b>8 ビット・イベント・カウンタ(</b> TM21 <b>)の構成</b> 127         |

| 8.3          | <b>8 ビット・イベント・カウンタ (</b> TM21 <b>) を制御するレジスタ</b> 129 |

| 8.4          | <b>8 ビット・イベント・カウンタ(</b> TM21 <b>)の動作</b> 130         |

| 8.5          | <b>8 ビット・イベント・カウンタ(</b> TM21 <b>)の注意事項</b> 132       |

| 第9章          | <b>8 ピット・リモコン・タイマ (</b> TM9) 135                     |

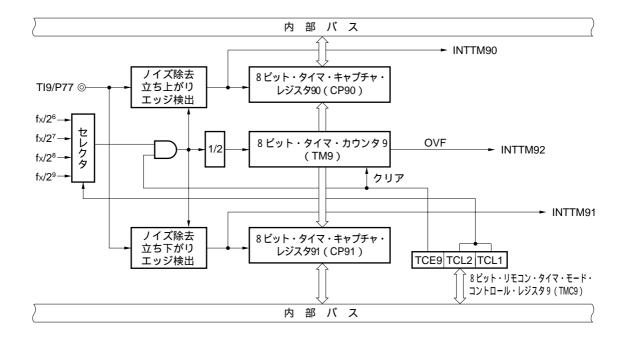

| 9.1          | <b>8 ビット・リモコン・タイマ (</b> TM9 <b>) の機能</b> 135         |

| 9.2          | <b>8 ビット・リモコン・タイマ (</b> TM9 <b>) の構成</b> 135         |

|              | <b>8 ビット・リモコン・タイマ (</b> TM9) <b>を制御するレジスタ</b> 136    |

| 9.4          | <b>8 ビット・リモコン・タイマ (</b> TM9 <b>) の動作</b> 138         |

| 9.5          | <b>8 ビット・リモコン・タイマ (</b> TM9 <b>) の注意事項</b> 139       |

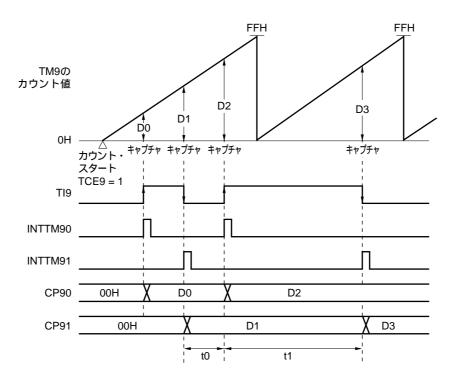

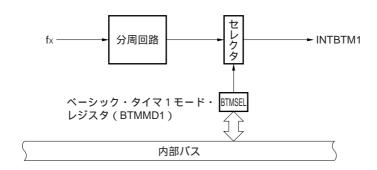

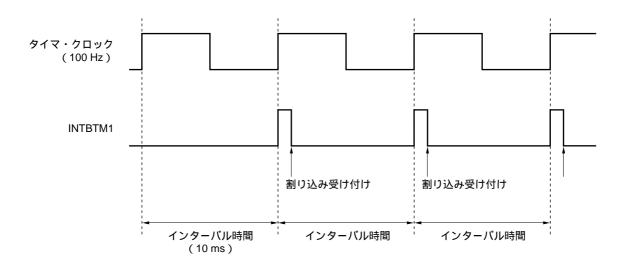

| 第10章         | ベーシック・タイマ (BTM1) 141                                 |

| 10. <b>1</b> | <b>ベーシック・タイマ (</b> BTM1 <b>) の機能</b> 141             |

| 10. <b>2</b> | <b>ベーシック・タイマ(</b> BTM1 <b>)の構成</b> 141               |

| 10. <b>3</b> | <b>ベーシック・タイマ (</b> BTM1 <b>) を制御するレジスタ</b> 142       |

| 10. <b>4</b> | <b>ベーシック・タイマ(</b> BTM1 <b>)の動作</b> 143               |

| 10. <b>5</b> | <b>ベーシック・タイマ (</b> BTM1 <b>) の注意事項</b> 144           |

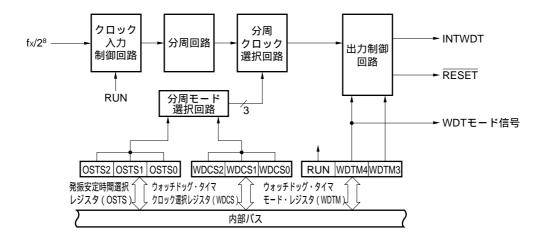

| 第11章         | <b>ウォッチドッグ・タイマ</b> 145                               |

| 11. <b>1</b> | ウォッチドッグ・タイマの機能 145                                   |

| 11. <b>2</b> | <b>ウォッチドッグ・タイマの構成</b> 147                            |

| 11. <b>3</b> | <b>ウォッチドッグ・タイマを制御するレジスタ</b> 147                      |

| 11. <b>4</b> | <b>ウォッチドッグ・タイマの動作</b> 150                            |

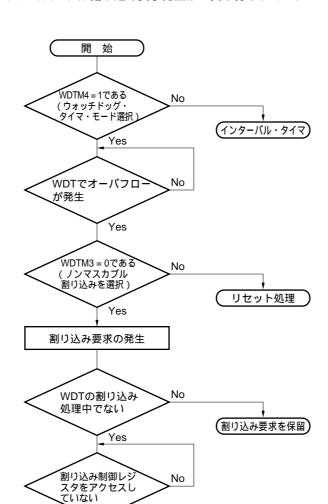

|              | 11.4.1 ウォッチドッグ・タイマとしての動作 150                         |

|              | 11.4.2 インターバル・タイマとしての動作 151                          |

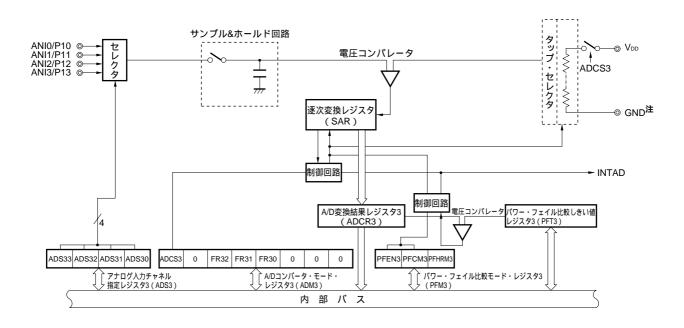

| <b>第</b> 12 <b>章</b>                                         | A/D <b>コンバータ</b> 153                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12. <b>2</b><br>12. <b>3</b><br>12. <b>4</b>                 | A/D <b>コンパータの機能</b> … 153<br>A/D <b>コンパータの構成</b> … 153<br>A/D <b>コンパータを制御するレジスタ</b> … 156<br>A/D <b>コンパータの動作</b> … 159<br>12.4.1 A/Dコンバータの基本動作 … 159<br>12.4.2 入力電圧と変換結果 … 161<br>12.4.3 A/Dコンバータの動作モード … 162<br>A/D <b>コンパータの注意事項</b> … 168            |

| 第13章                                                         | シリアル・インタフェース (IIC1) 171                                                                                                                                                                                                                                 |

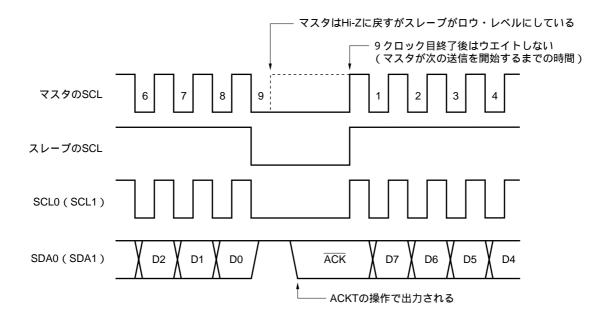

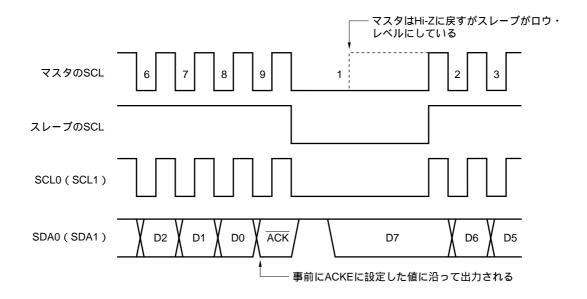

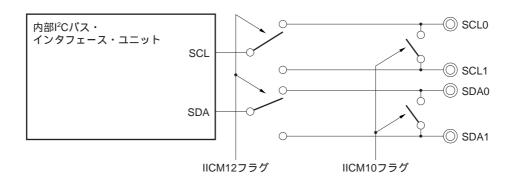

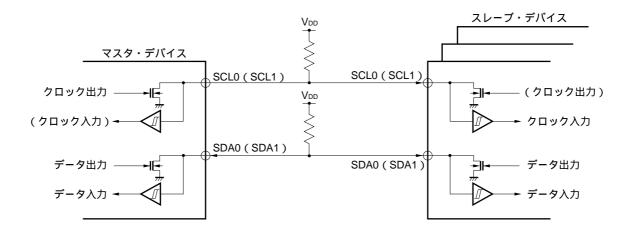

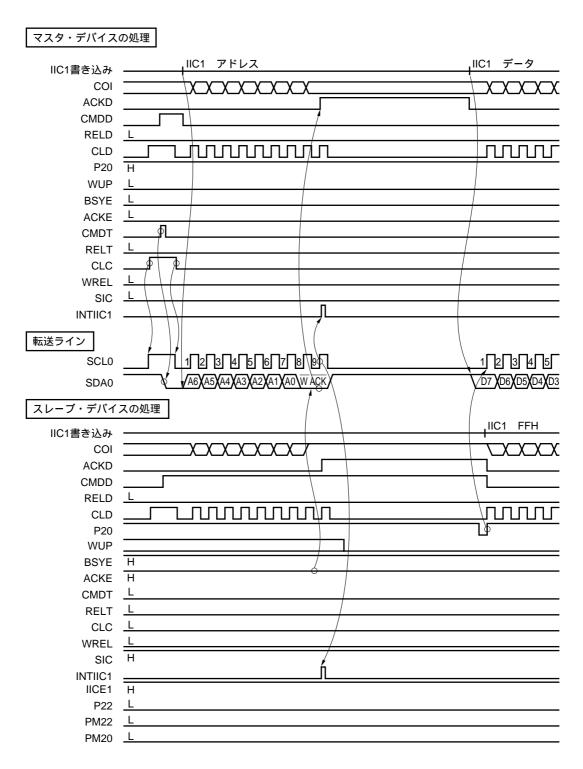

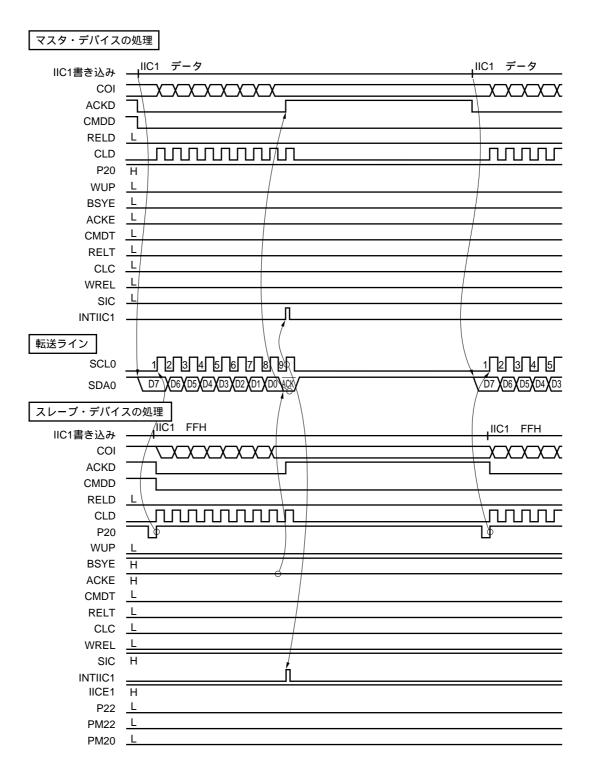

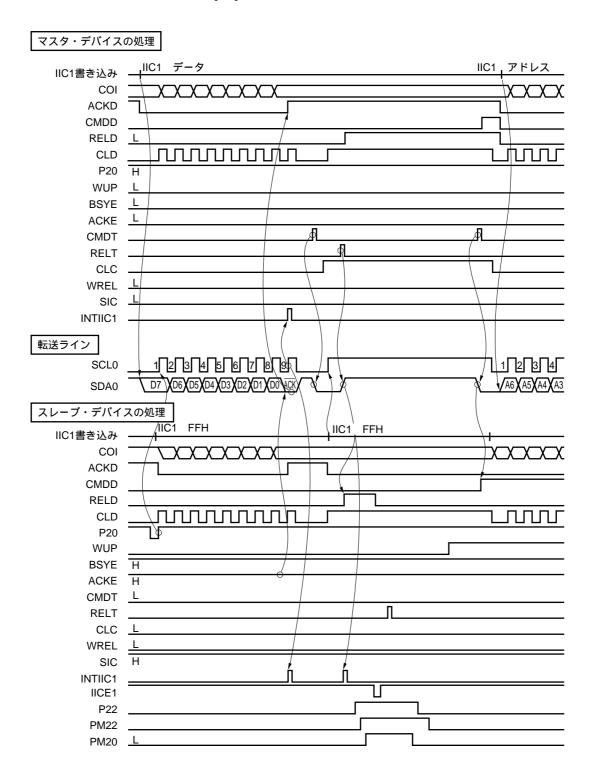

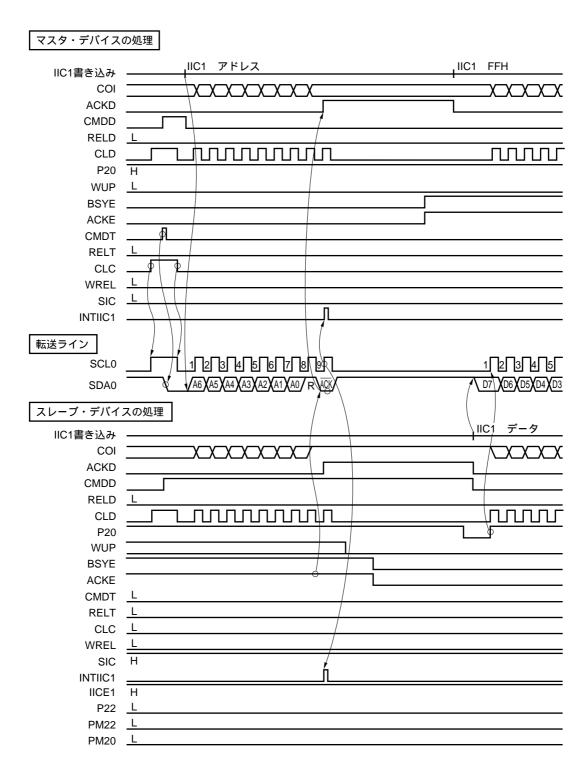

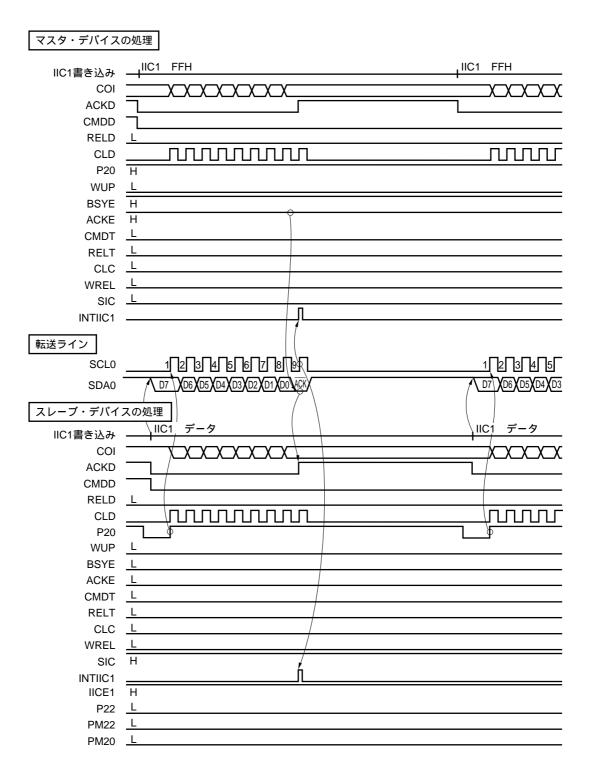

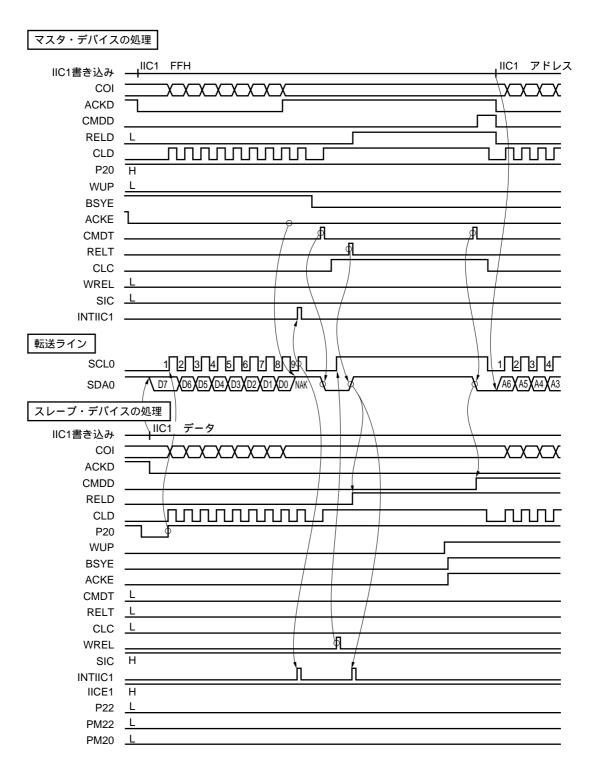

| 13. <b>2</b><br>13. <b>3</b>                                 | シリアル・インタフェース (IIC1) の機能 171シリアル・インタフェース (IIC1) の構成 173シリアル・インタフェース (IIC1) を制御するレジスタ 178シリアル・インタフェース (IIC1) の動作 18513.4.1 動作停止モード 18513.4.2 I²Cバス・モードの動作 18613.4.3 I²Cバス・モード使用時の注意事項 20813.4.4 I²Cバス・モード使用時の制限事項 21013.4.5 SCL0/P20, SCL1/P21端子出力の操作 212 |

| 第14章                                                         | シリアル・インタフェース(SIO3) 213                                                                                                                                                                                                                                  |

| 14. <b>2</b><br>14. <b>3</b>                                 | シリアル・インタフェース (SIO3) の機能 213<br>シリアル・インタフェース (SIO3) の構成 214<br>シリアル・インタフェース (SIO3) を制御するレジスタ 215<br>シリアル・インタフェース (SIO3) の動作 217<br>14.4.1 動作停止モード 217<br>14.4.2 3線式シリアルI/Oモード 218                                                                        |

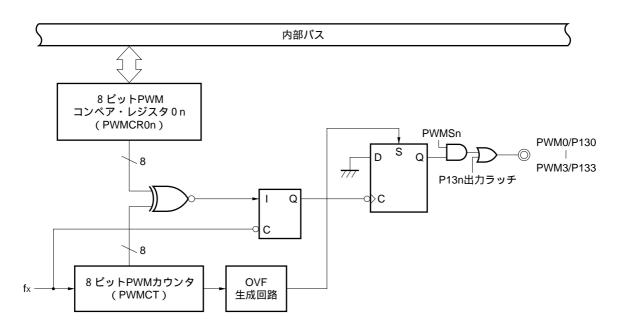

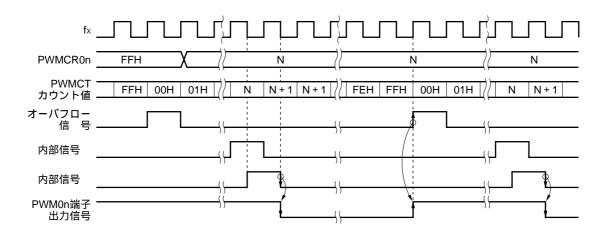

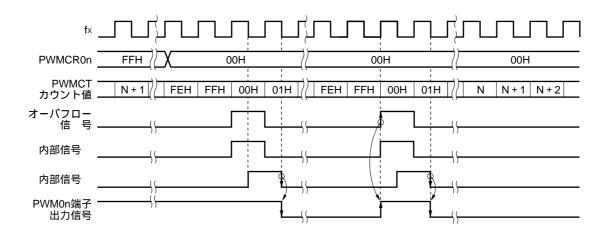

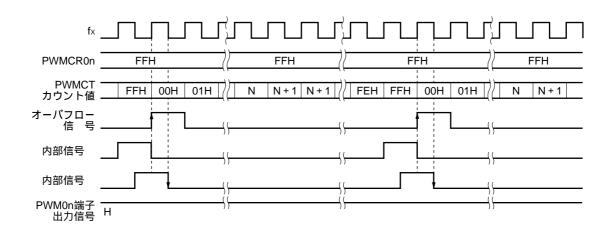

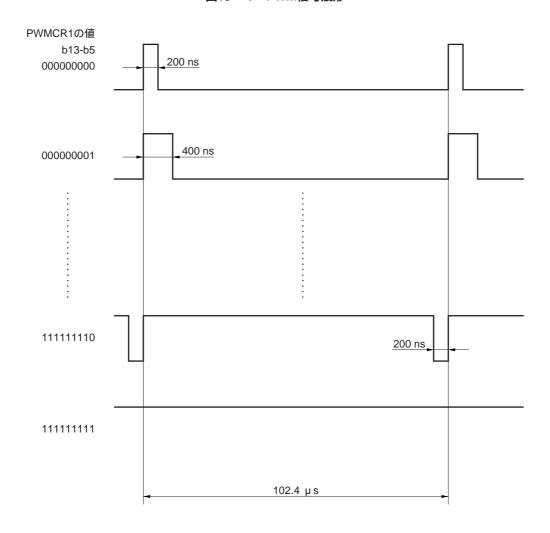

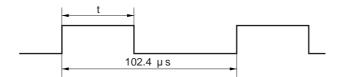

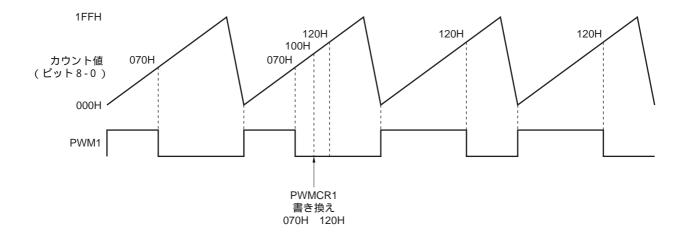

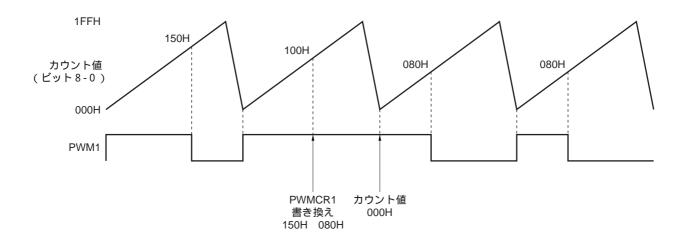

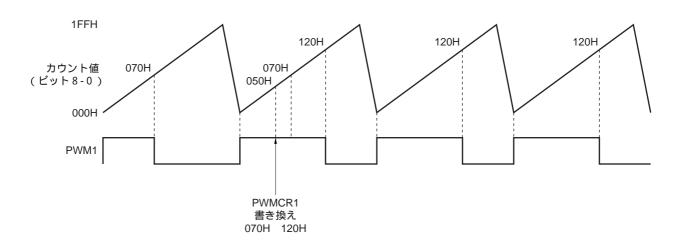

| <b>第</b> 15 <b>章</b>                                         | 8 ビットPWM 221                                                                                                                                                                                                                                            |

| 15. <b>2</b><br>15. <b>3</b><br>15. <b>4</b><br>15. <b>5</b> | 8 ビットPWMの機能 221<br>8 ビットPWMの構成 221<br>8 ビットPWMを制御するレジスタ 223<br>8 ビットPWMの動作 224<br>8 ビットPWMの注意事項 227                                                                                                                                                     |

|                                                              |                                                                                                                                                                                                                                                         |

| 16. <b>1</b> | 14 <b>ビット</b> [ | PWM <b>の機能</b> 229       |

|--------------|-----------------|--------------------------|

| 16. <b>2</b> | 14 <b>ビット</b> F | PWM <b>の構成</b> 229       |

| 16. <b>3</b> | 14 <b>ビット</b> F | PWM <b>を制御するレジスタ</b> 231 |

| 16. <b>4</b> | 14 <b>ビット</b> F | PWM <b>の動作</b> 232       |

|              | 16.4.1          | 14ビットPWMの出力信号 232        |

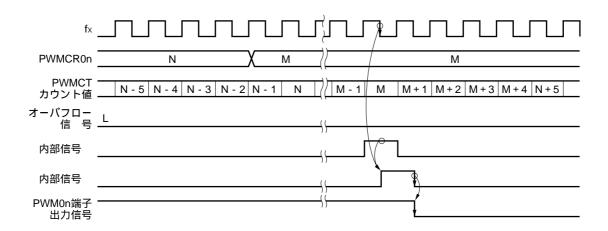

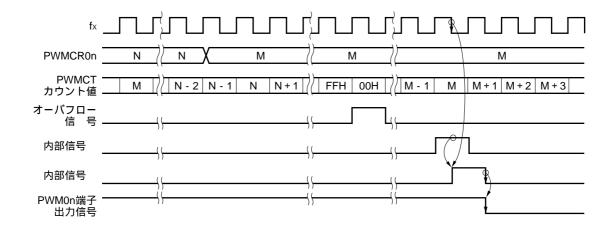

|              | 16.4.2          | 14ビットPWMの動作タイミング         |

|              | 16.4.3          | スタンバイ時の動作 235            |

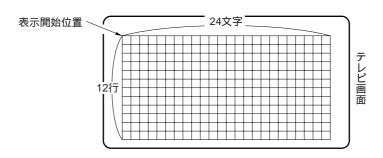

### 第17章 OSDコントローラ ... 237 17. 1 OSD**コントローラの機能** ... 237 17.2 OSDコントローラの構成 ... 239 17.3 OSDコントローラを制御するレジスタ ... 241 17.4 OSD**コントローラの動作** ... 251 17.4.1 背景モード ... 251 17.4.2 縁取り制御 ... 251 17.4.3 リセットとVRAM一括解除 ... 253 17.4.4 通常TVモードと倍速TVモード ... 254 17.4.5 表示開始位置制御 ... 255 17.4.6 VRAMの構成 ... 256 17.4.7 文字の表示 ... 257 17.4.8 ハーフ・ブランキング ... 258 17.5 OSD**コントローラ使用上の注意** ... 259 17.5.1 VRAMへの書き込みタイミング ... 259 第18章 ROMコレクション ... 263 18.1 ROMコレクションの機能 ... 263 18.2 ROMコレクションの構成 ... 263 18.3 ROMコレクションを制御するレジスタ ... 265 18.**4** ROM**コレクションの使用方法** ... 267 18.5 ROMコレクションの使用例 ... 269 18.**6 プログラム実行フロー** ... 270 18.7 ROMコレクションの注意事項 ... 272 第19章 割り込み機能 ... 273 19.1 割り込み機能の種類 ... 273 19.2 割り込み要因と構成 ... 273 19.3 割り込み機能を制御するレジスタ ... 277 19.4 割り込み処理動作 ... 283 19.4.1 ノンマスカブル割り込み要求の受け付け動作 ... 283 19.4.2 マスカブル割り込み要求の受け付け動作 ... 286 19.4.3 ソフトウエア割り込み要求の受け付け動作 ... 289 19.4.4 多重割り込み処理 ... 290 19.4.5 割り込み要求の保留 ... 293 第20章 スタンバイ機能 ... 295 20.1 スタンバイ機能と構成 ... 295 20.1.1 スタンバイ機能 ... 295 20.1.2 スタンバイ機能を制御するレジスタ ... 296 20.2 スタンバイ機能の動作 ... 297 20.2.1 HALTモード ... 297 20.2.2 STOPモード ... 300

#### 第21章 リセット機能 ... 303

21.1 リセット機能 ... 303 21.2 停電検出機能 ... 309

#### **第**22章 μPD178F048 ... 311

- 22.1 メモリ・サイズ切り替えレジスタ (IMS) ... 312

- 22. **2** 内部拡張RAMサイズ切り替えレジスタ(IXS) ... 313

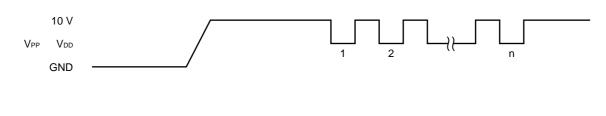

- 22.3 フラッシュ・メモリ・プログラミング ... 314

- 22.3.1 通信方式の選択 ... 314

- 22.3.2 フラッシュ・メモリ・プログラミングの機能 ... 315

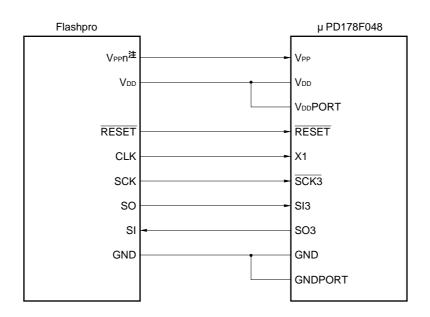

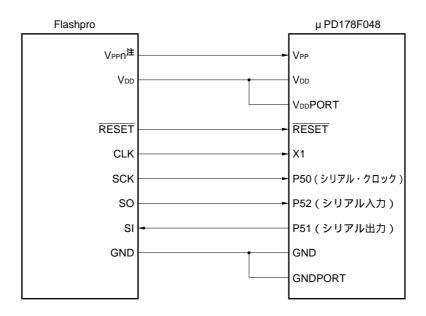

- 22.3.3 Flashpro の接続 ... 315

- 22.3.4 Flashpro (PG-FP3)での設定例 ... 317

- 22.3.5 フラッシュ書き込み時の注意事項 ... 318

#### 第23章 命令セットの概要 ... 319

- 23.1 凡 例 ... 320

- 23.1.1 オペランドの表現形式と記述方法 ... 320

- 23.1.2 オペレーション欄の説明 ... 321

- 23.1.3 フラグ動作欄の説明 ... 321

- 23.2 オペレーション一覧 ... 322

- 23.3 アドレシング別命令一覧 ... 331

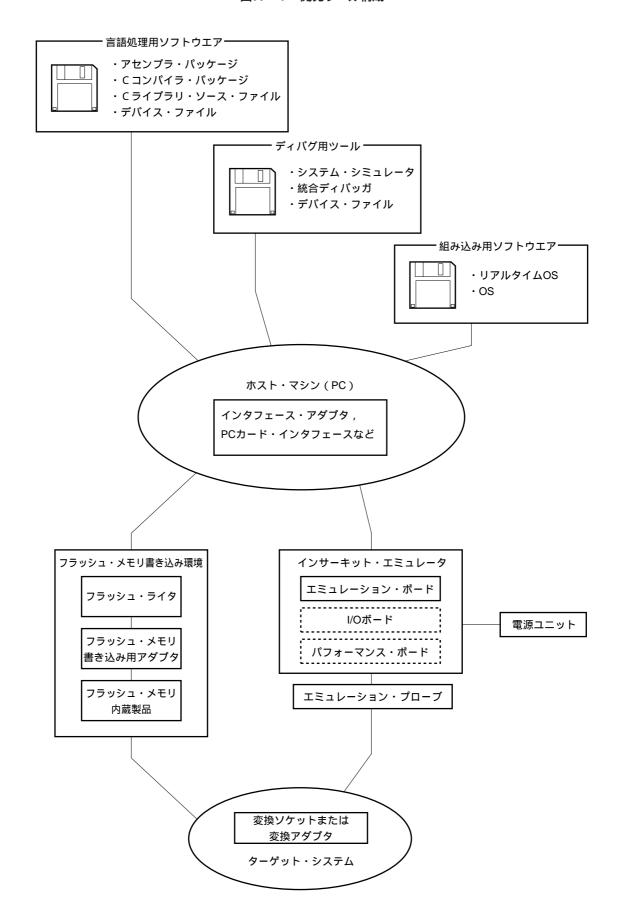

#### 付録A 開発ツール ... 335

- A.1 言語処理用ソフトウエア ... 337

- A.2 フラッシュ・メモリ書き込み用ツール ... 338

- A.3 ディバグ用ツール ... 339

- A.3.1 ハードウエア ... 339

- A.3.2 ソフトウエア ... 340

#### 付録 B 組み込み用ソフトウエア ... 343

#### 付録 C レジスタ索引 ... 345

- C.1 レジスタ索引(50音順) ... 345

- C.2 レジスタ索引(アルファベット順) ... 348

- **★ 付録 D 改版履歴** ... 351

### 図の目次(1/5)

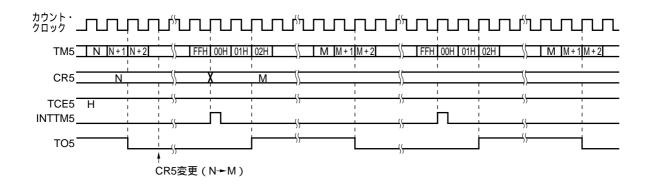

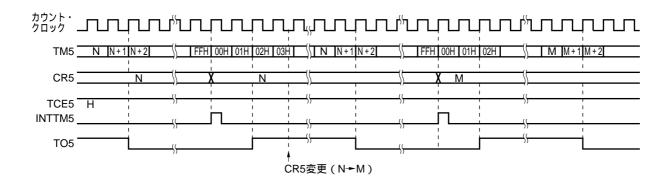

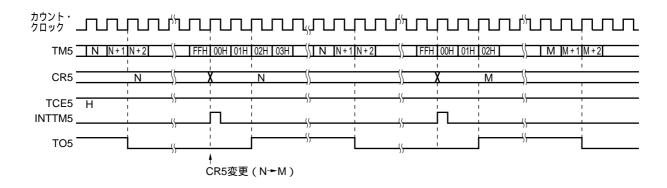

図番号 タイトル,ページ 端子の入出力回路一覧 ... 41 3 - 1 メモリ・マップ(µPD178046) ... 44 3 - 2 メモリ・マップ(µPD178048) ... 45 3 - 3 メモリ・マップ(µPD178F048) ... 46 3 - 4 データ・メモリのアドレシング(μPD178046) ... 49 3 - 5 データ・メモリのアドレシング(μPD178048) ... 50 3 - 6 データ・メモリのアドレシング(µPD178F048) ... 51 3-7 プログラム・カウンタの構成 ... 52 3-8 プログラム・ステータス・ワードの構成 ... 52 3-9 スタック・ポインタの構成 ... 54 3-10 スタック・メモリへ退避されるデータ ... 54 3-11 スタック・メモリから復帰されるデータ ... 55 3-12 汎用レジスタの構成 ... 56 4-1 ポートの種類 ... 75 4 - 2 P00-P03のブロック図 ... 78 4 - 3 P10-P13のブロック図 ... 79 4 - 4 P20. P21のブロック図 ... 80 4 - 5 P22, P23のブロック図 ... 81 4 - 6 P40-P47のブロック図 ... 82 4 - 7 P50-P54のブロック図 ... 83 4 - 8 P60-P67のブロック図 ... 84 4 - 9 P70-P77のブロック図 ... 85 4 - 10 P130-P134のブロック図 ... 86 4-11 ポート・モード・レジスタのフォーマット ... 89 5 - 1 クロック発生回路のブロック図 ... 93 5-2 プロセッサ・クロック・コントロール・レジスタのフォーマット ... 94 5-3 システム・クロック発振回路の外付け回路 ... 95 5 - 4 発振子の接続の悪い例 ... 96 8 ビット・タイマ / イベント・カウンタ (TM5)のブロック図 ... 101 6 - 2 タイマ・クロック選択レジスタ5(TCL5)のフォーマット ... 103 6 - 3 8ビット・タイマ・モード・コントロール・レジスタ5(TMC5)のフォーマット ... 105 6 - 4 インターバル・タイマ動作のタイミング ... 107 6-5 外部イベント・カウンタ動作のタイミング(立ち上がりエッジ指定時) ... 110 6 - 6 方形波出力動作のタイミング ... 111 6 - 7 PWM出力の動作タイミング ... 113 6 - 8 CR5変更による動作のタイミング ... 114

## 図の目次 (2/5)

| 図番号    | タイトル , ページ                                             |

|--------|--------------------------------------------------------|

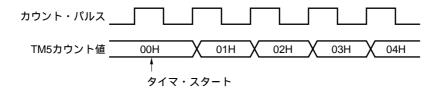

| 6 - 9  | 8 ビット・タイマ・カウンタ 5 のスタート・タイミング 115                       |

| -      | タイマ・カウント動作中のコンペア・レジスタの変更後のタイミング 116                    |

| 0 - 10 | ライマ・カランド動作中のコンベア・レンスタの女更後のライミング 110                    |

| 7 - 1  | 8 ビット・タイマ(TM20)のブロック図 120                              |

| 7 - 2  | 8 ビット・タイマ・モード・コントロール・レジスタ20 ( TMC20 ) のフォーマット 121      |

| 7 - 3  | インターバル・タイマ動作時の 8 ビット・タイマ・モード・コントロール・レジスタ20 ( TMC20 ) の |

|        | 設定内容 122                                               |

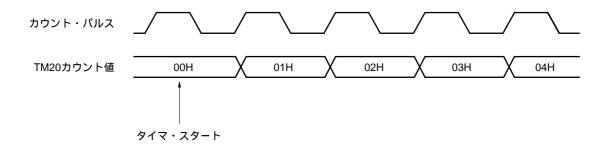

| 7 - 4  | インターバル・タイマ動作のタイミング 123                                 |

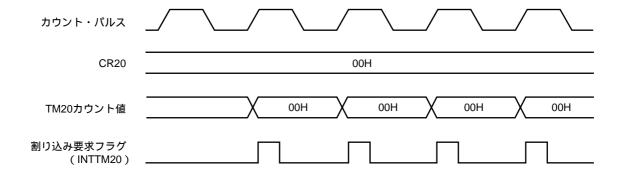

| 7 - 5  | 8 ビット・タイマ・カウンタ20のスタート・タイミング 124                        |

| 7 - 6  | インターバル・タイマとしての動作時のタイミング 124                            |

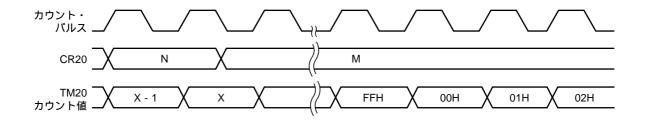

| 7 - 7  | タイマ・カウント動作中のコンペア・レジスタの変更後のタイミング 125                    |

|        |                                                        |

| 8 - 1  | 8 ビット・イベント・カウンタ(TM21)のブロック図 128                        |

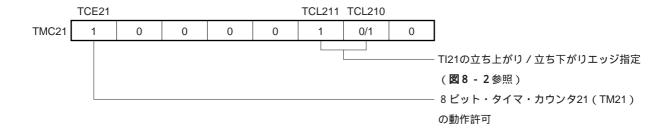

| 8 - 2  | 8 ビット・タイマ・モード・コントロール・レジスタ21 ( TMC21 ) のフォーマット 129      |

| 8 - 3  | 外部イベント・カウンタ動作時の 8 ビット・タイマ・モード・コントロール・レジスタ21の           |

|        | 設定内容 130                                               |

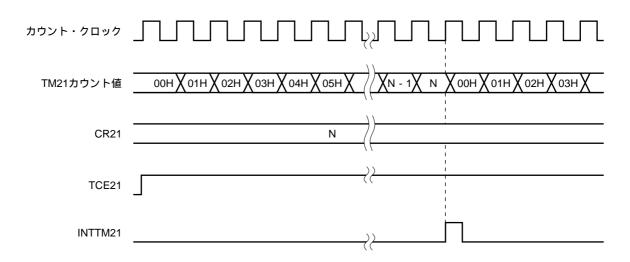

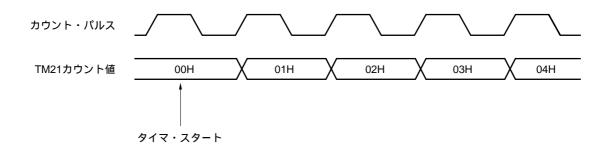

| 8 - 4  | 外部イベント・カウンタ動作のタイミング(立ち上がりエッジ指定時) 131                   |

| 8 - 5  | 8 ビット・タイマ・カウンタ21のスタート・タイミング 132                        |

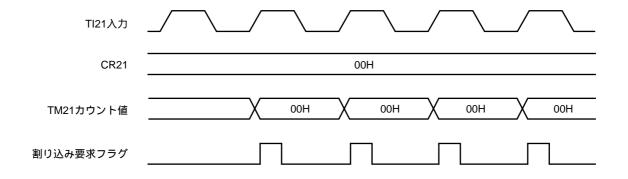

| 8 - 6  | 外部イベント・カウンタとしての動作時のタイミング 132                           |

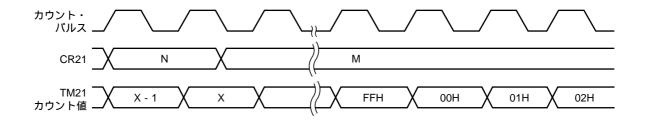

| 8 - 7  | タイマ・カウント動作中のコンペア・レジスタの変更後のタイミング 133                    |

|        |                                                        |

|        | 8 ビット・リモコン・タイマ(TM9)のプロック図 135                          |

|        | 8 ビット・リモコン・タイマ・モード・コントロール・レジスタ 9 (TMC9)のフォーマット 136     |

| 9 - 3  | パルス幅測定のタイミング 138                                       |

| 10 - 1 | ベーシック・タイマ(BTM1)のブロック図 141                              |

| 10 - 2 | ベーシック・タイマ 1 モード・レジスタ(BTMMD1)のフォーマット 142                |

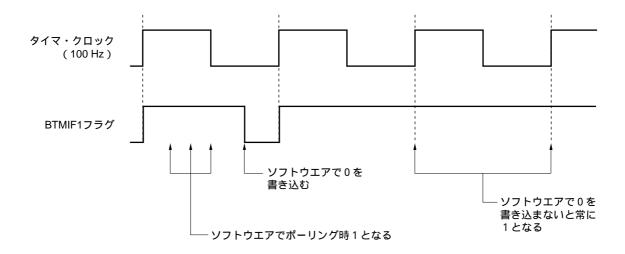

| 10 - 3 | ベーシック・タイマ動作のタイミング 1 (10 ms設定時(BTMSEL = 1 )) 143        |

| 10 - 4 | BTMIF1フラグをポーリングする場合の動作タイミング(10 ms設定時(BTMSEL = 1 )) 143 |

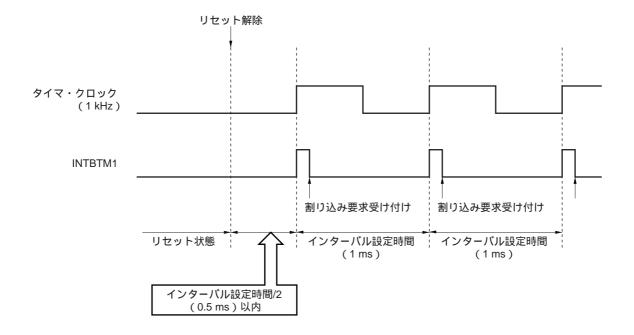

| 10 - 5 | ベーシック・タイマ動作のタイミング 2 (1 ms設定時(BTMSEL = 0 )) 144         |

|        |                                                        |

| 11 - 1 | ウォッチドッグ・タイマのブロック図 145                                  |

| 11 - 2 | ウォッチドッグ・タイマ・クロック選択レジスタ(WDCS)のフォーマット 147                |

| 11 - 3 | ウォッチドッグ・タイマ・モード・レジスタ ( WDTM ) のフォーマット 148              |

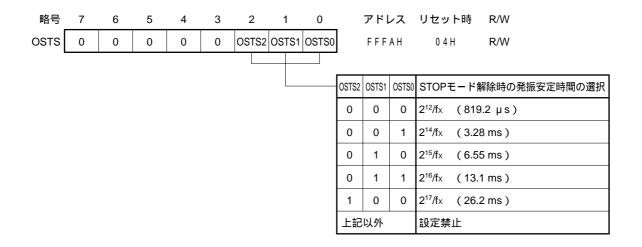

| 11 - 4 | 発振安定時間選択レジスタ(OSTS)のフォーマット 149                          |

|        |                                                        |

|        | A/Dコンバータのブロック図 154                                     |

|        | A/Dコンバータ・モード・レジスタ3 (ADM3)のフォーマット 156                   |

|        | アナログ入力チャネル指定レジスタ3(ADS3)のフォーマット 157                     |

| 12 - 4 | パワー・フェイル比較モード・レジスタ3(PFM3)のフォーマット 158                   |

## 図の目次(3/5)

| 図番号     | タイトル , ページ                                |

|---------|-------------------------------------------|

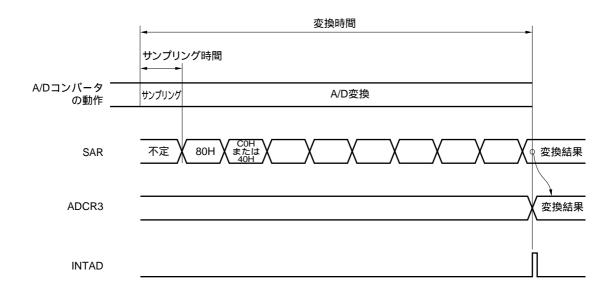

| 12 - 5  | A/Dコンバータの基本動作 160                         |

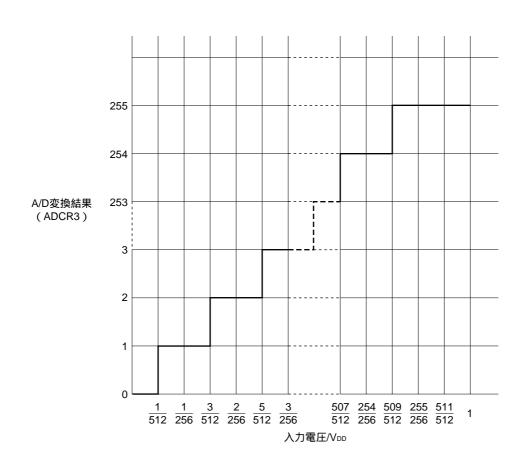

| 12 - 6  | アナログ入力電圧とA/D変換結果の関係 161                   |

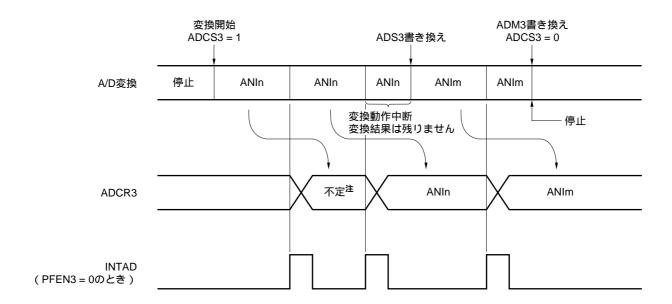

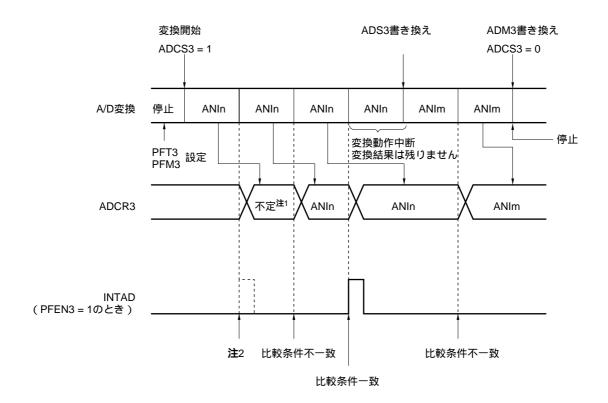

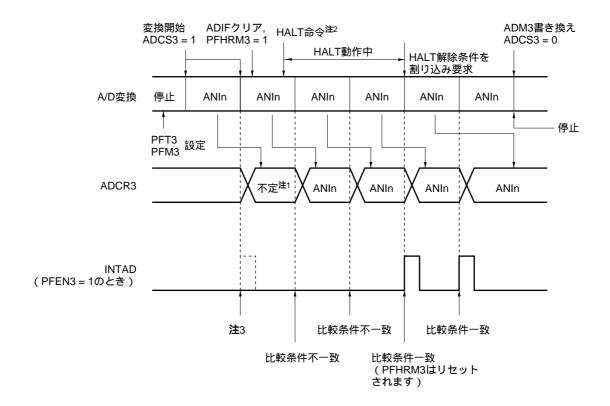

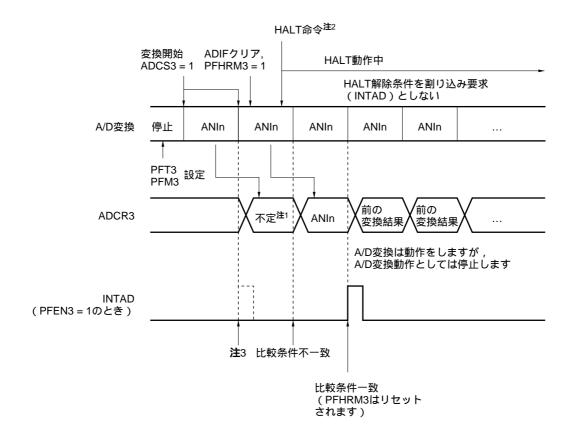

| 12 - 7  | A/D変換動作 163                               |

| 12 - 8  | パワー・フェイル比較しきい値レジスタ3(PFT3) 164             |

| 12 - 9  | パワー・フェイル比較モードによるA/D変換動作 165               |

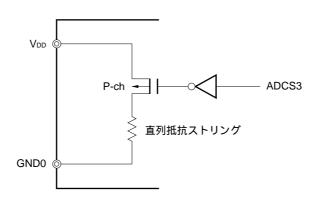

| 12 - 10 | スタンバイ・モード時の消費電流を低減させる方法例 168              |

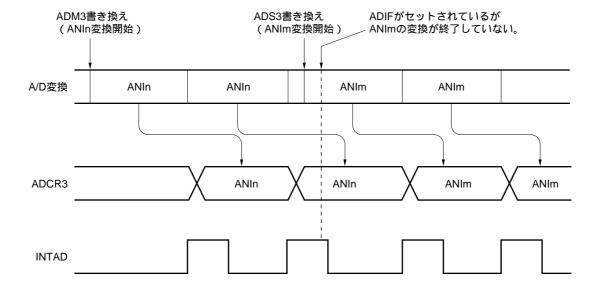

| 12 - 11 | A/D変換終了割り込み要求発生タイミング 169                  |

|         |                                           |

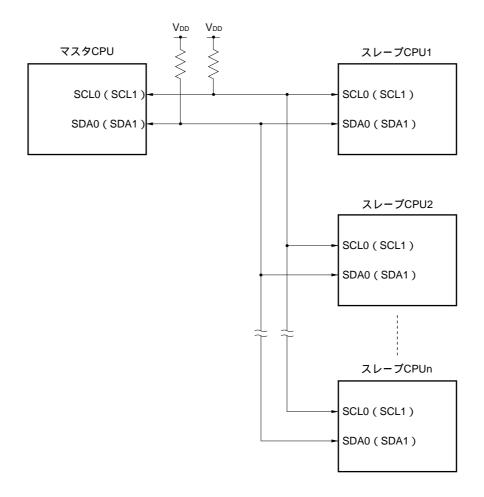

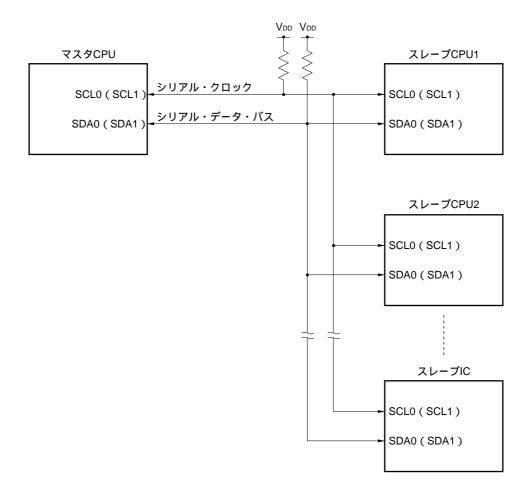

| 13 - 1  | I <sup>2</sup> Cバスによるシリアル・バス構成例 172       |

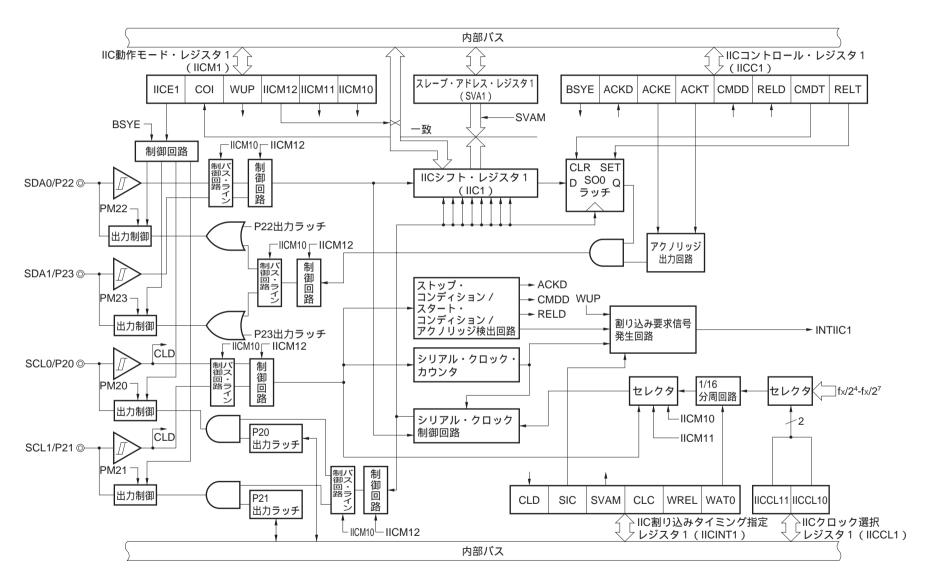

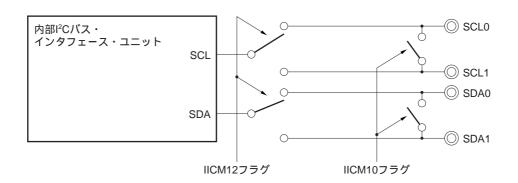

| 13 - 2  | シリアル・インタフェース(IIC1)のブロック図 174              |

| 13 - 3  | IICクロック選択レジスタ1(IICCL1)のフォーマット 178         |

| 13 - 4  | IIC動作モード・レジスタ 1 (IICM1)のフォーマット 179        |

| 13 - 5  | IICコントロール・レジスタ1(IICC1)のフォーマット 181         |

| 13 - 6  | IIC割り込みタイミング指定レジスタ 1 (IICINT1)のフォーマット 183 |

| 13 - 7  | I <sup>2</sup> Cバスによるシリアル・バス構成例 186       |

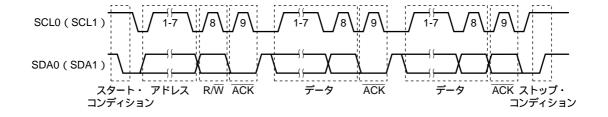

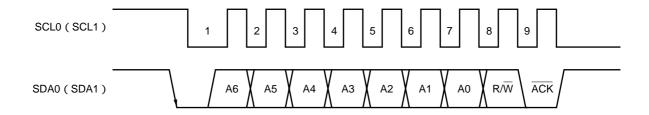

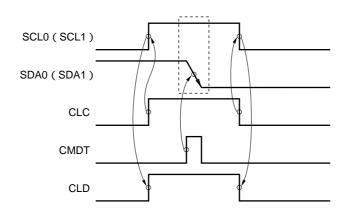

| 13 - 8  | I <sup>2</sup> Cバスのシリアル・データ転送タイミング 187    |

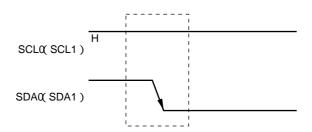

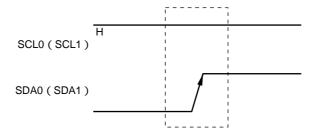

| 13 - 9  | スタート・コンディション 188                          |

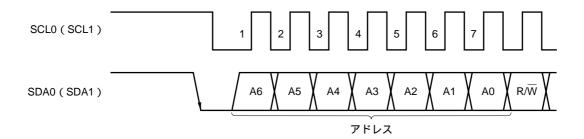

| 13 - 10 | アドレス 189                                  |

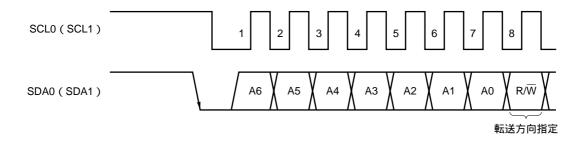

| 13 - 11 | 転送方向指定 189                                |

| 13 - 12 | アクノリッジ信号 190                              |

| 13 - 13 | ストップ・コンディション 190                          |

| 13 - 14 | ウエイト信号 191                                |

| 13 - 15 | 端子構成図 199                                 |

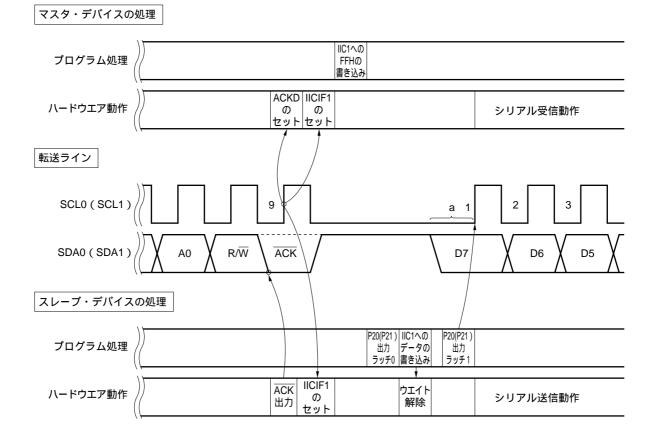

| 13 - 16 | マスタ スレープ通信例 201                           |

| 13 - 17 | スレーブ マスタ通信例 204                           |

|         | スタート・コンディションの出力 208                       |

|         | スレープのウエイト解除(送信時) 209                      |

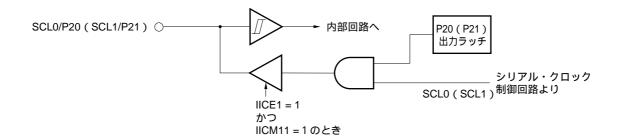

| 13 - 20 | SCL0/P20(SCL1/P21)端子の構成 212               |

| 11 - 1  | シリアル・インタフェース ( SIO3 ) のブロック図 213          |

|         | シリアル動作モード・レジスタ3 (CSIM3)のフォーマット 215        |

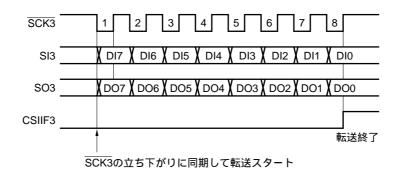

|         | 3 線式シリアルI/Oモードのタイミング 219                  |

| 14 - 3  |                                           |

| 15 - 1  | 8 ビットPWMのブロック図(PWM00-PWM03) 222           |

| 15 - 2  | PWM出力セレクト・レジスタ(PWMS)のフォーマット 223           |

| 15 - 3  | 8 ビットPWMの動作タイミング 225                      |

|         |                                           |

|         | 14ビットPWMのブロック図(PWM1) 230                  |

| 16 - 2  | 14ビットPWMコンペア・レジスタ(PWMCR1)のフォーマット 230      |

| 16 - 3  | PWM出力セレクト・レジスタ(PWMS)のフォーマット 231           |

## 図の目次 (4/5)

| 図番号     | タイトル , ページ                                     |

|---------|------------------------------------------------|

| 16 - 4  | PWM信号波形 232                                    |

|         |                                                |

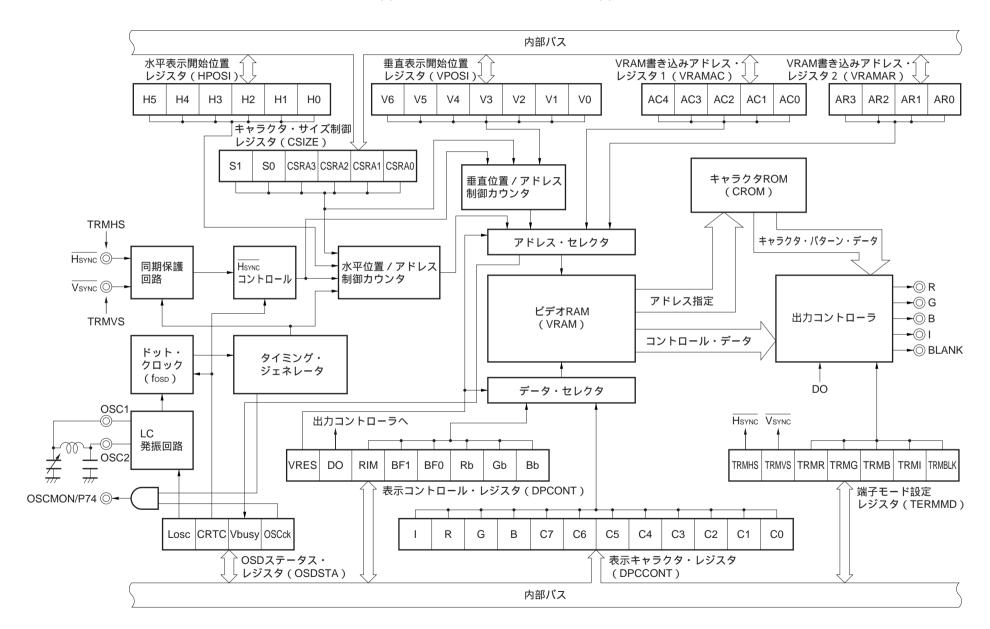

| 17 - 1  | OSDコントローラのブロック図 240                            |

| 17 - 2  | 表示コントロール・レジスタ(DPCONT)のフォーマット 241               |

| 17 - 3  | OSDステータス・レジスタ(OSDSTA)のフォーマット 242               |

| 17 - 4  | 水平表示開始位置レジスタ(HPOSI)のフォーマット 244                 |

| 17 - 5  | 垂直表示開始位置レジスタ(VPOSI)のフォーマット 245                 |

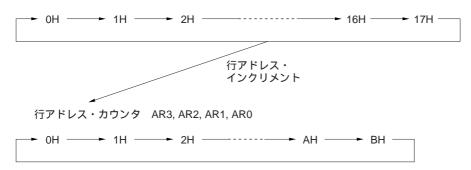

| 17 - 6  | VRAM書き込みアドレス・レジスタ1(VRAMAC)のフォーマット 246          |

| 17 - 7  | VRAM書き込みアドレス・レジスタ 2 (VRAMAR)のフォーマット 247        |

| 17 - 8  | キャラクタ・サイズ制御レジスタ(CSIZE)のフォーマット 248              |

| 17 - 9  | 端子モード設定レジスタ(TERMMD)のフォーマット 249                 |

| 17 - 10 | 表示キャラクタ・レジスタ(DPCCONT)のフォーマット 250               |

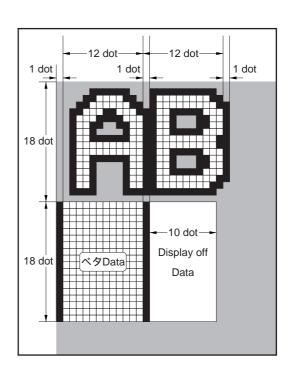

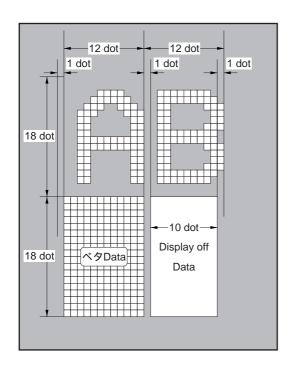

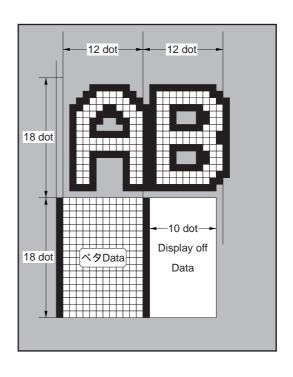

| 17 - 11 | 各背景モード,縁取りの表示例 252                             |

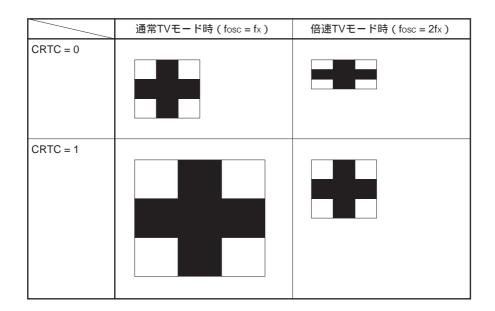

| 17 - 12 | 通常TVモード時と倍速モード時の表示例 254                        |

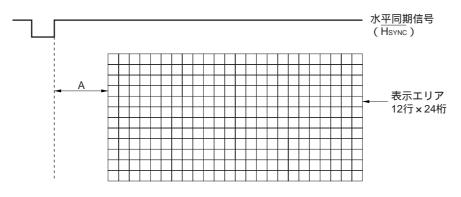

| 17 - 13 | 水平表示開始位置 255                                   |

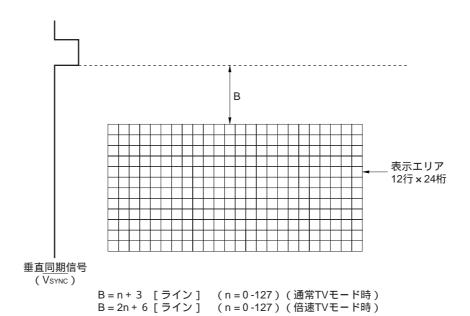

| 17 - 14 | 垂直表示開始位置 255                                   |

| 17 - 15 | VRAMの構成 256                                    |

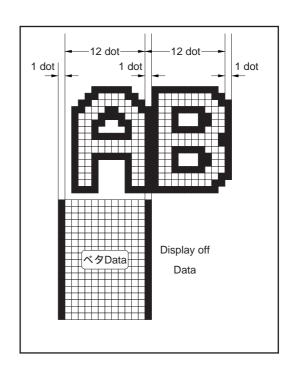

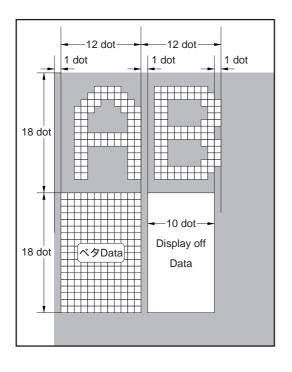

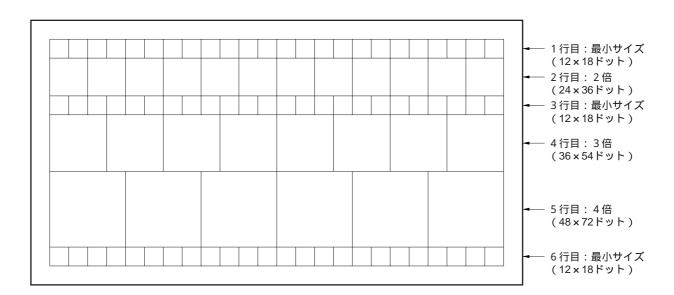

| 17 - 16 | 文字サイズ混在時の表示画面例 257                             |

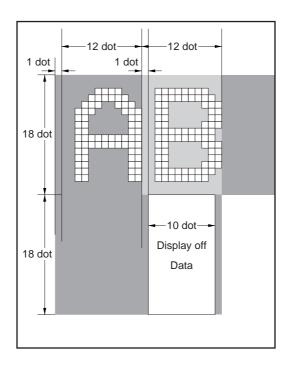

| 17 - 17 | ハーフ・ブランキング表示例 258                              |

| 17 - 18 | VRAMインタフェース部プロック図 259                          |

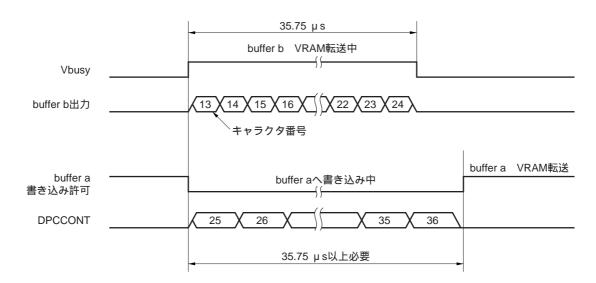

| 17 - 19 | VRAM転送タイミング 260                                |

|         |                                                |

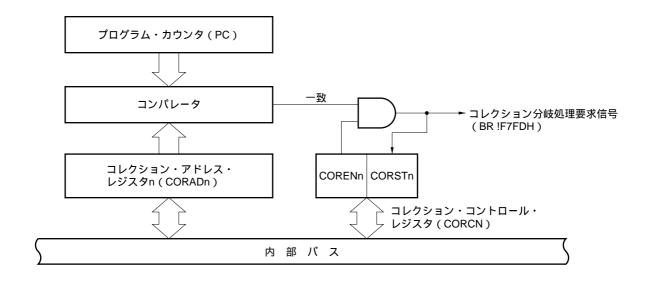

| 18 - 1  | ROMコレクションのブロック図 264                            |

| 18 - 2  | コレクション・アドレス・レジスタ 0 , 1 のフォーマット 264             |

| 18 - 3  | コレクション・コントロール・レジスタ(CORCN)のフォーマット 266           |

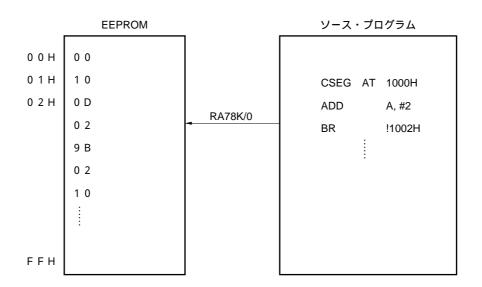

| 18 - 4  | EEPROMへの格納例(修正箇所が 1 つの場合) 267                  |

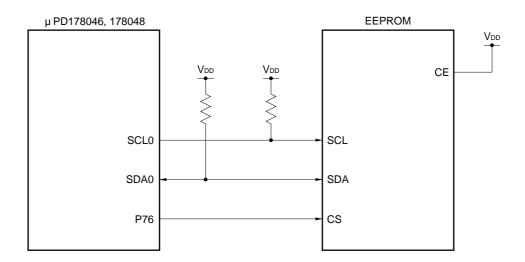

| 18 - 5  | EEPROMとの接続例(シリアル・インタフェース(IIC1)を使用した場合) 267     |

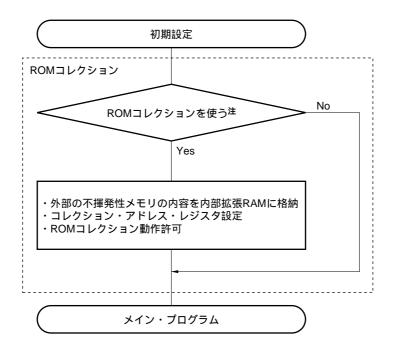

| 18 - 6  | 初期設定ルーチン 268                                   |

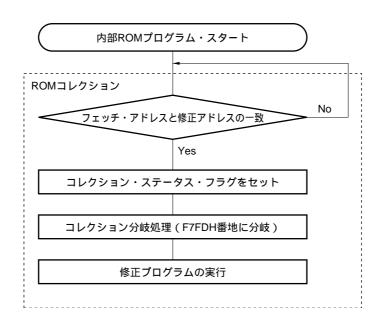

| 18 - 7  | ROMコレクションの動作 269                               |

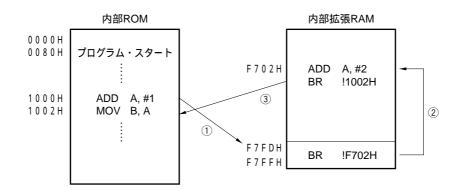

| 18 - 8  | ROMコレクションの使用例 269                              |

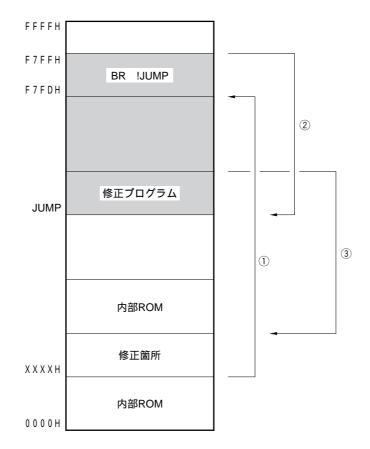

| 18 - 9  | プログラム遷移図(修正箇所が1つの場合) 270                       |

| 18 - 10 | プログラム遷移図(修正箇所が2つの場合) 271                       |

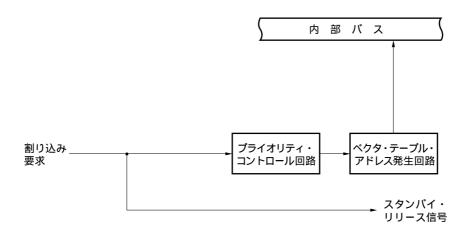

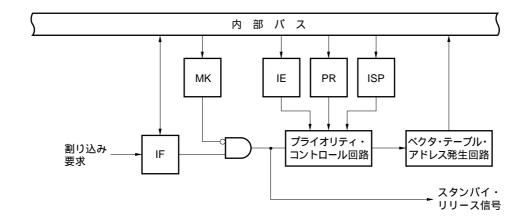

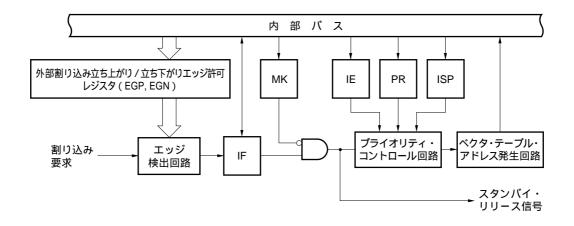

| 19 - 1  | 割り込み機能の基本構成 275                                |

| 19 - 2  | 割り込み要求フラグ・レジスタ(IF0L, IF0H)のフォーマット 278          |

| 19 - 3  | 割り込みマスク・フラグ・レジスタ(MKOL, MKOH)のフォーマット 279        |

| 19 - 4  | 優先順位指定フラグ・レジスタ(PR0L, PR0H)のフォーマット 280          |

| 19 - 5  | 外部割り込み立ち上がりエッジ許可レジスタ(EGP),外部割り込み立ち下がりエッジ許可レジスタ |

|         | (EGN)のフォーマット 281                               |

19 - 6 プログラム・ステータス・ワード (PSW) の構成 ... 282

## 図の目次 (5/5)

| 図番号     | タイトル , ページ                           |

|---------|--------------------------------------|

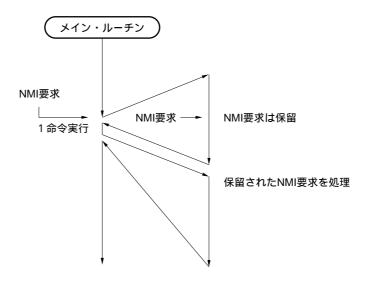

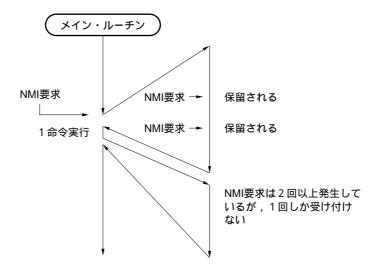

| 19 - 7  | ノンマスカブル割り込み要求発生から受け付けまでのフロー・チャート 284 |

| 19 - 8  | ノンマスカブル割り込み要求の受け付けタイミング 284          |

| 19 - 9  | ノンマスカブル割り込み要求の受け付け動作 285             |

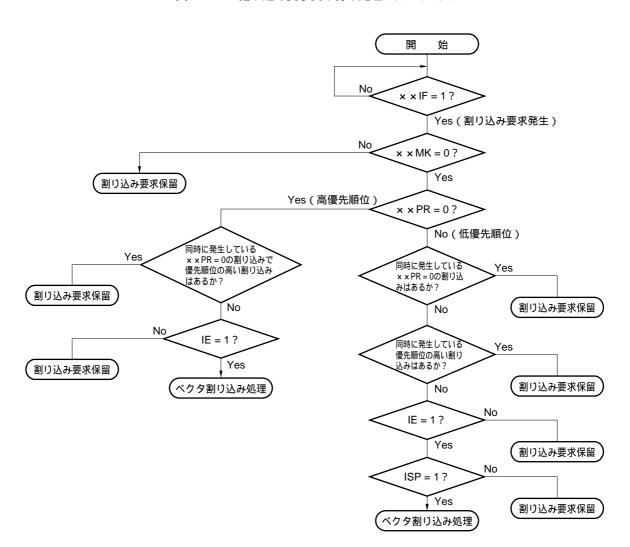

| 19 - 10 | 割り込み要求受け付け処理アルゴリズム 287               |

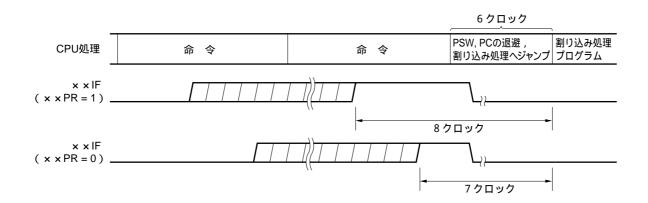

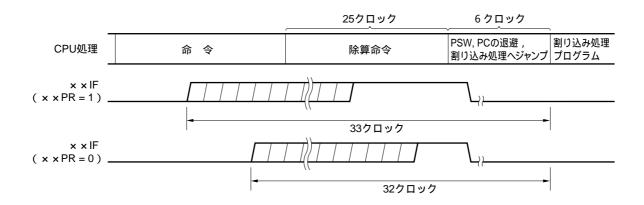

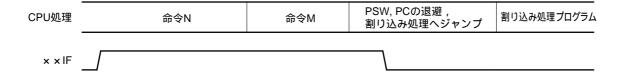

| 19 - 11 | 割り込み要求の受け付けタイミング(最小時間) 288           |

| 19 - 12 | 割り込み要求の受け付けタイミング(最大時間) 288           |

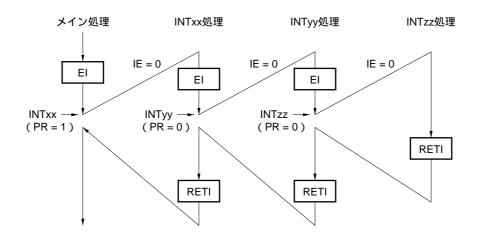

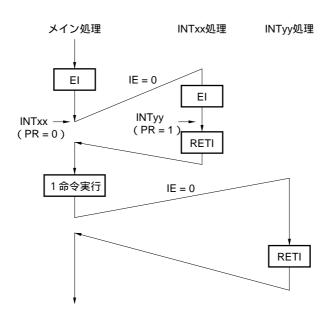

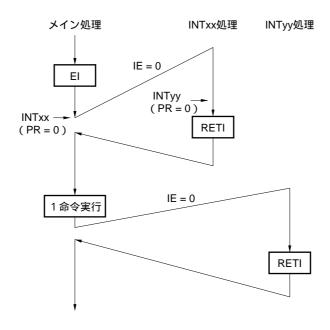

| 19 - 13 | 多重割り込みの例 291                         |

| 19 - 14 | 割り込み要求の保留 293                        |

| 20 - 1  | 発振安定時間選択レジスタ ( OSTS ) のフォーマット 296    |

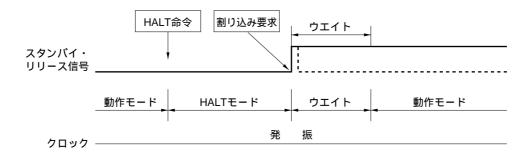

| 20 - 2  | HALTモードの割り込み要求発生による解除 298            |

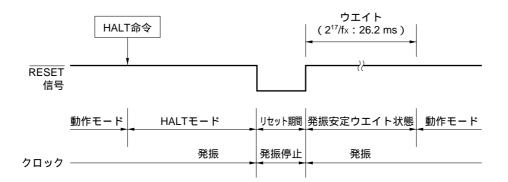

| 20 - 3  | HALTモードのRESET入力による解除 299             |

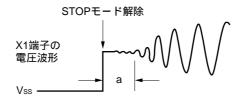

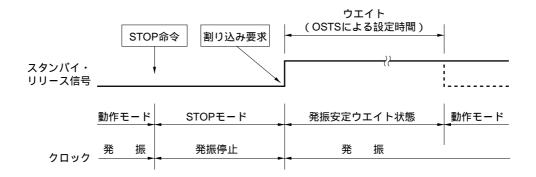

| 20 - 4  | STOPモードの割り込み要求発生による解除 301            |

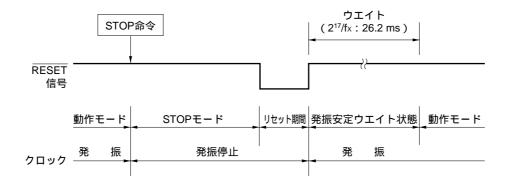

| 20 - 5  | STOPモードのRESET入力による解除 302             |

| 21 - 1  | リセット機能のブロック図 304                     |

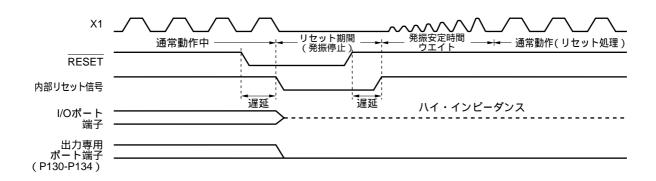

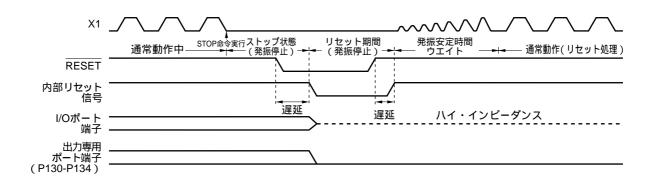

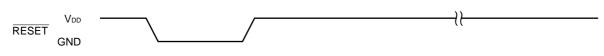

| 21 - 2  | RESET入力によるリセット・タイミング 305             |

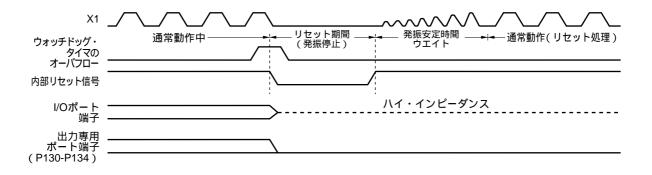

| 21 - 3  | ウォッチドッグ・タイマのオーバフローによるリセット・タイミング 305  |

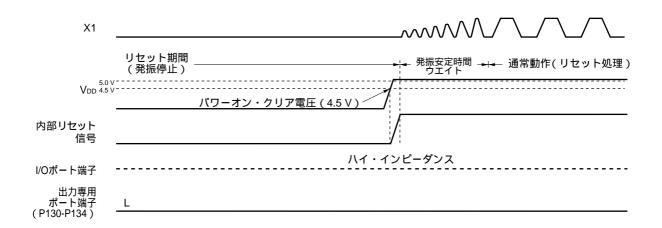

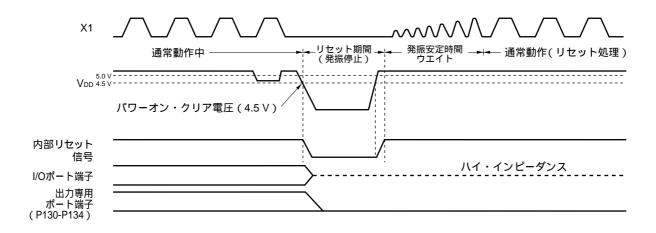

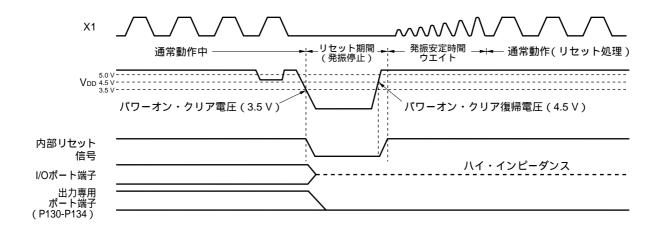

| 21 - 4  | パワーオン・クリアによるリセット・タイミング 306           |

| 21 - 5  | POCステータス・レジスタ (POCS)のフォーマット 309      |

| 21 - 6  | POC電圧選択レジスタ(POCV)のフォーマット 309         |

| 22 - 1  | メモリ・サイズ切り替えレジスタ(IMS)のフォーマット 312      |

| 22 - 2  | 内部拡張RAMサイズ切り替えレジスタ(IXS)のフォーマット 313   |

| 22 - 3  | 通信方式選択フォーマット 314                     |

| 22 - 4  | 3 線式シリアルI/O方式でのFlashpro の接続 315      |

| 22 - 5  | 疑似 3 線式でのFlashpro の接続 316            |

| 22 - 6  | エリア・アドレス選択画面 318                     |

| A - 1   | 開発ツール構成 336                          |

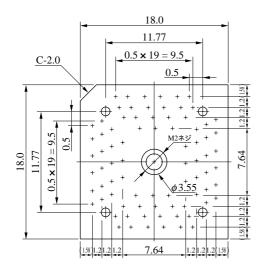

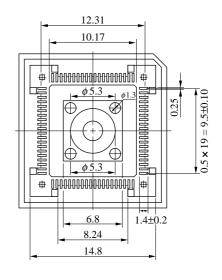

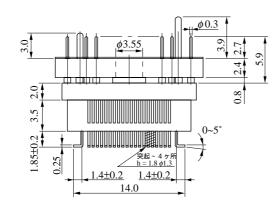

| A - 2   | TGK-080SDW 外形図(参考)(単位:mm) 341        |

## 表の目次 (1/2)

| 表番号    | タイトル , ページ                          |

|--------|-------------------------------------|

| 2 - 1  | 各端子の入出力回路タイプと未使用端子の処理 40            |

|        |                                     |

| 3 - 1  | ベクタ・テープル 47                         |

| 3 - 2  | 汎用レジスタの絶対アドレス対照表 55                 |

| 3 - 3  | 特殊機能レジスター覧 58                       |

|        |                                     |

|        | ポートの機能 76                           |

|        | ポートの構成 77                           |

| 4 - 3  | 兼用機能使用時のポート・モード・レジスタ,出力ラッチの設定 88    |

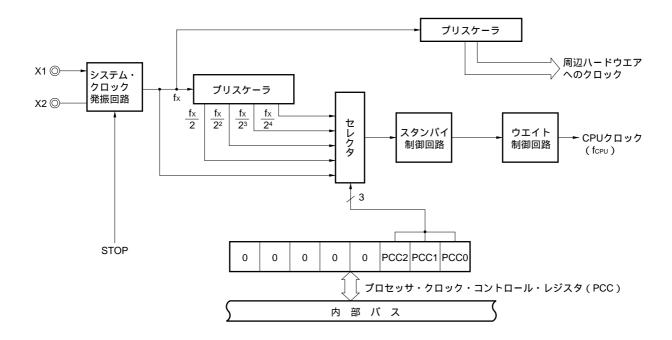

| 5 - 1  | クロック発生回路の構成 93                      |

|        | CPUクロックの切り替えに要する最大時間 99             |

| J 2    |                                     |

| 6 - 1  | 8 ビット・タイマ / イベント・カウンタ(TM5)の構成 102   |

|        |                                     |

| 7 - 1  | 8 ビット・タイマ(TM20 ) のインターバル時間 119      |

| 7 - 2  | 8 ビット・タイマ (TM20)の構成 119             |

| 7 - 3  | 8 ビット・タイマ(TM20 ) のインターバル時間 122      |

|        |                                     |

| 8 - 1  | 8 ビット・イベント・カウンタ(TM21)の構成 127        |

|        |                                     |

| 9 - 1  | 8 ビット・リモコン・タイマ(TM9)の構成 135          |

| 40.4   |                                     |

| 10 - 1 | ベーシック・タイマ(BTM1)の構成 141              |

| 11 - 1 | ウォッチドッグ・タイマの暴走検出時間 146              |

|        | インターバル時間 146                        |

| 11 - 3 | ウォッチドッグ・タイマの構成 147                  |

| 11 - 4 | ウォッチドッグ・タイマの暴走検出時間 150              |

| 11 - 5 | インターバル・タイマのインターバル時間 151             |

|        |                                     |

| 12 - 1 | A/Dコンバータの構成 153                     |

|        |                                     |

| 13 - 1 | シリアル・インタフェース(IIC1)の構成 173           |

| 13 - 2 | シリアル・インタフェース(IIC1)の割り込み要求信号の発生 177  |

| 13 - 3 | I <sup>2</sup> Cバス・モードにおける各種の信号 198 |

|        |                                     |

| 14 - 1 | シリアル・インタフェース(SIO3)の構成 214           |

|        |                                     |

| 15 - 1 | 8 ビットPWMの構成 221                     |

## 表の目次(2/2)

| 表番号    | タイトル , ページ                  |

|--------|-----------------------------|

| 16 - 1 | 14ビットPWMの構成 229             |

| 16 - 2 | PWM1端子の出力信号 233             |

| 17 - 1 | OSDコントローラの構成 239            |

| 18 - 1 | ROMコレクションの構成 263            |

| 19 - 1 | 割り込み要因一覧 274                |

| 19 - 2 | 割り込み要求ソースに対する各種フラグ 277      |

| 19 - 3 | マスカブル割り込み要求発生から処理までの時間 286  |

| 19 - 4 | 割り込み処理中に多重割り込み可能な割り込み要求 290 |

| 20 - 1 | HALTモード時の動作状態 297           |

| 20 - 2 | HALTモードの解除後の動作 299          |

| 20 - 3 | STOPモード時の動作状態 300           |

| 20 - 4 | STOPモードの解除後の動作 302          |

| 21 - 1 | 各ハードウエアのリセット後の状態 307        |

| 22 - 1 | μ PD178F048とマスクROM製品の違い 311 |

| 22 - 2 | メモリ・サイズ切り替えレジスタの設定値 312     |

| 22 - 3 | 通信方式一覧 314                  |

| 22 - 4 | フラッシュ・メモリ・プログラミングの主な機能 315  |

| 22 - 5 | Flashpro (PG-FP3)での設定例 317  |

| 23 - 1 | オペランドの表現形式と記述方法 320         |

(メ モ)

### 第1章 概 説

### 1.1 特 徵

#### 大容量ROM, RAM内蔵

| 項目         | プログラム・メモリ   | キャラクタROM | データ・メモリ |         | ビデオRAM |

|------------|-------------|----------|---------|---------|--------|

| 品名         | (ROM)       | (CROM)   | 内部高速RAM | 内部拡張RAM | (VRAM) |

| μPD178046  | 48 Kバイト     | 6912バイト  | 512バイト  | 512バイト  | 432バイト |

| μPD178048  | 60 Kバイト     |          |         |         |        |

| μPD178F048 | 60 Kバイト     |          |         |         |        |

|            | (フラッシュ・メモリ) |          |         |         |        |

システム制御に適した命令セット

- ・全アドレス空間でビット処理可能

- ・乗除算命令内蔵

汎用入出力ポート:46本

8 ビット分解能A/Dコンバータ: 4 チャネルシリアル・インタフェース : 3 チャネル・12Cバス $^{1}$ ・モード : 2 チャネル・ 3 線式シリアル1/Oモード : 1 チャネル

注 I<sup>2</sup>C バス・モードを使用した場合 (周辺ハードウエアを使用せず,プログラムで実現した場合も含む),マスク 発注時に当社販売員に連絡してください。

タイマ:6チャネル

・ベーシック・タイマ (タイマ・キャリー (100 Hz))

: 1 チャネル

・8 ビット・タイマ / イベント・カウンタ

: 1 チャネル

・8 ビット・タイマ

: 1 チャネル

・8 ビット・イベント・カウンタ

: 1 チャネル

・8 ビット・リモコン・タイマ

: 1 チャネル

・ウォッチドッグ・タイマ

: 1 チャネル

PWM出力:5チャネル

・8 ビットPWM出力 : 4 チャネル ・14ビットPWM出力 : 1 チャネル OSD ( On Screen Dispiay ) コントローラ内蔵

ROMコレクション内蔵 ベクタ割り込み要因: 17

・マスカブル割り込み要因 : 16 ・ソフトウエア割り込み要因 : 1

インストラクション・サイクル: 0.4/0.8/1.6/3.2/6.4 μs (5.0 MHz水晶振動子使用)

電源電圧: V<sub>DD</sub> = 4.5~5.5 V パワーオン・クリア回路内蔵

## 1.2 応用分野

TV

## ★ 1.3 オーダ情報

| オーダ名称                                    | パッケージ                                | 内部ROM     |

|------------------------------------------|--------------------------------------|-----------|

| μ PD178046GK- × × × -BE9                 | 80ピン・プラスチックTQFP(12×12 mm, 0.5 mmピッチ) | マスクROM    |

| $\mu$ PD178048GK- $\times$ $\times$ -BE9 | II .                                 | "         |

| μ PD178F048GK-BE9                        | II .                                 | フラッシュ・メモリ |

備考 ×××はROMコード番号です。またI<sup>2</sup>Cバス使用時はROMコード番号はE××になります。

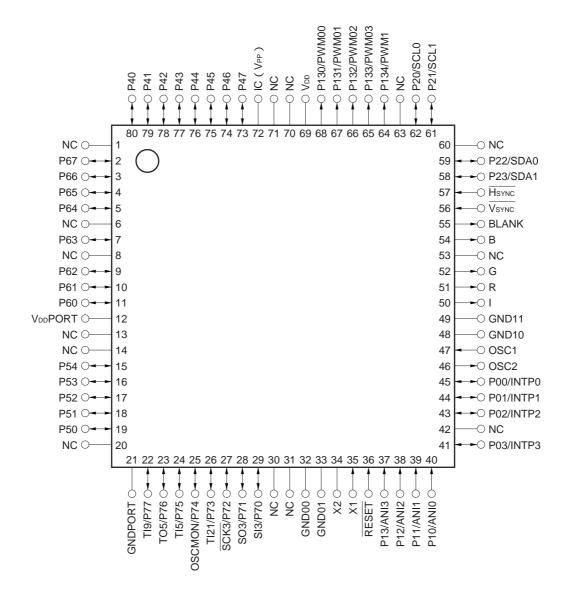

### 1.4 端子接続図 (Top View)

μ PD178F048GK-BE9

・80ピン・プラスチックTQFP(12×12 mm, 0.5 mmピッチ) μ PD178046GK-×××-BE9 μ PD178048GK-×××-BE9

- 注意1.IC (Internally Connected), Vpp端子は, GND00, GND01, GND10, GND11のいずれかに直接接続してください。

- 2. VDDPORT端子はVDD端子と同電位にしてください。

- 3. GNDPORT端子はGND00, GND01, GND10, GND11のいずれかと同電位にしてください。

**備考**( )内は µ PD178F048のとき

#### 端子名称

G

ANI0-ANI3 : A/Dコンバータ入力 P70-P77 : ポート 7 В : 文字信号出力

**BLANK** : ブランキング信号出力 PWM00-PWM03:8ビットPWM出力

GND00, GND10,

GND01, GND11 : グランド

GNDPORT : ポート用グランド HSYNC : 水平同期信号入力 ı : 文字信号出力

:内部接続

: 文字信号出力

IC

INTP0-INTP3 : インタラプト入力

NC : ノンコネクション

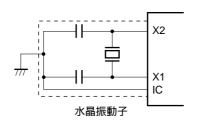

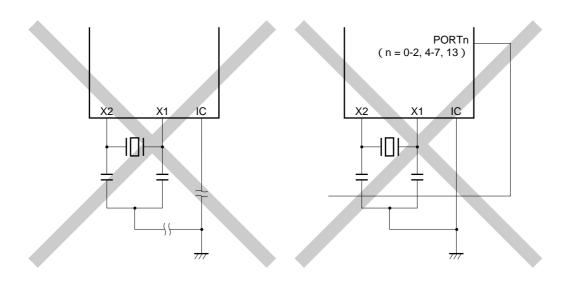

OSC1, OSC2 : OSDドット・クロック発振用LC接続

**OSCMON** : OSDクロック出力

: ポート0 P00-P03 P10-P13 : ポート1 P20-P23 : ポート2 P40-P47 : ポート4

P50-P54 : ポート5 P60-P67 : ポート6

P130-P134 : ポート13

PWM1 : 14ビットPWM出力

R : 文字信号出力

RESET : リセット入力

SCK3 :シリアル・クロック入力/出力 SCL0, SCL1 :シリアル・クロック入力/出力 SDA0, SDA1 : シリアル・データ入力/出力

SI3 : シリアル・データ入力 : シリアル・データ出力 SO3

TI5, TI9, TI21 :8ビット・タイマ・クロック入力

TO5 :8ビット・タイマ出力

$V_{DD}$ :電源

**VDDPORT** : ポート用電源

$V_{PP}$ : プログラミング電源 VSYNC : 垂直同期信号入力

X1. X2 : システム・クロック発振用水晶振動子

接続

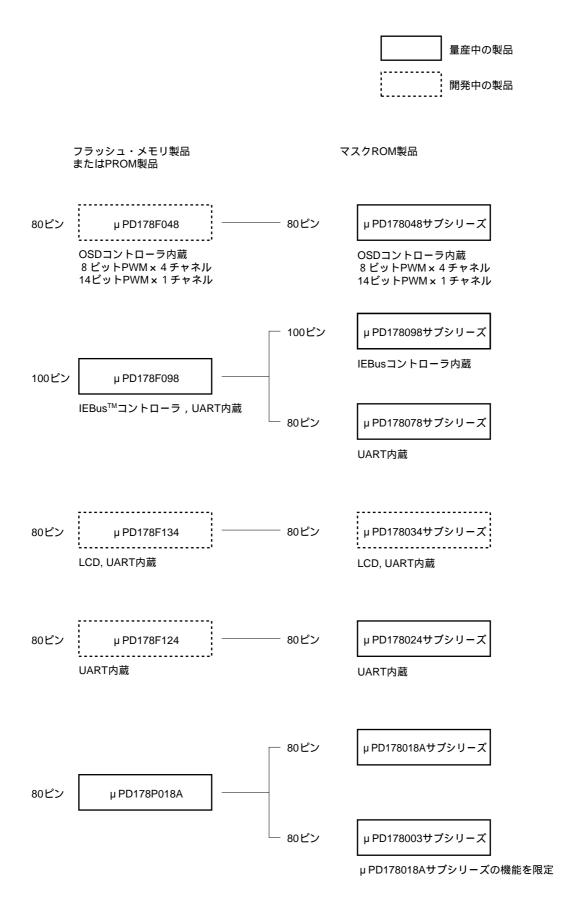

### ★ 1.5 8 ビットDTSシリーズの展開

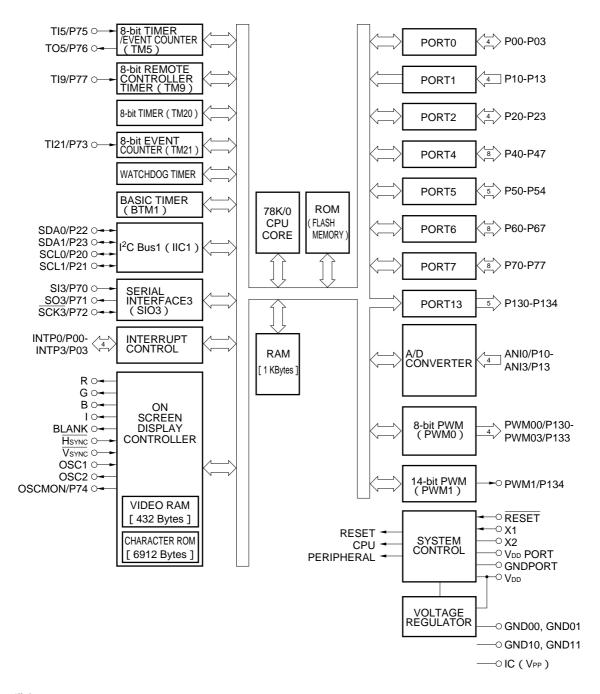

### ★ 1.6 プロック図

備考1.内部ROM容量は製品によって異なります。

**2**.( )はμPD178F048のとき

## 1.7 機能概要

(1/2)

|          | 品名       | μ PD178046                           | μ PD178048              | μ PD178F048          |  |  |

|----------|----------|--------------------------------------|-------------------------|----------------------|--|--|

| 項目       |          |                                      |                         |                      |  |  |

| 内部       | ROM      | 48 Kバイト(マスクROM)                      | 60 Kバイト(マスクROM)         | 60 Kバイト( フラッシュ・メモリ ) |  |  |

| メモリ      | キャラクタROM | 6912バイト (256キャラクタ)                   | )                       |                      |  |  |

|          | (CROM)   |                                      |                         |                      |  |  |

|          | 高速RAM    | 512バイト                               |                         |                      |  |  |

|          | 拡張RAM    | 512バイト                               |                         |                      |  |  |

|          | ビデオRAM   | 432バイト(最大12×24文字)                    | )                       |                      |  |  |

|          | (VRAM)   |                                      |                         |                      |  |  |

| 汎用レジスタ   | ,        | 8ビット×32レジスタ(8ビ                       | ット×8レジスタ×4バンク)          |                      |  |  |

| 最小命令実行   | 時間       | 0.4 μs/0.8 μs/1.6 μs/3.2 μs          | /6.4 μs ( 5.0 MHz水晶振動子使 | <b>浦</b> )           |  |  |

| 命令セット    |          | ・16ビット演算                             |                         |                      |  |  |

|          |          | ・乗除算(8ビット×8ビッ                        | ト , 16ビット÷ 8 ビット)       |                      |  |  |

|          |          | ・ビット操作(セット,リセット,テスト,プール演算)           |                         |                      |  |  |

|          |          | ・BCD補正 など                            |                         |                      |  |  |

| 1/0ポート   |          | 合計                                   | : 46本                   |                      |  |  |

|          |          | ·CMOS入力                              | : 4本                    |                      |  |  |

|          |          | ・CMOS入出力                             | : 37本                   |                      |  |  |

|          |          | ・N-chオープン・ドレーン出力 : 5 本               |                         |                      |  |  |

| A/Dコンバー? | タ        | 8 ビット分解能×4 チャネル                      |                         |                      |  |  |

| シリアル・イ   | ンタフェース   | ・I <sup>2</sup> Cバス・モード <sup>注</sup> | : 2チャネル (シフト            | ・レジスタ:1 チャネル )       |  |  |

|          |          | ・3 線式シリアルI/Oモード                      | : 1チャネル                 |                      |  |  |

| タイマ      |          | ・ベーシック・タイマ(タイ                        | マ・キャリー(100 Hz))         | : 1チャネル              |  |  |

|          |          | ・8 ビット・タイマ / イベン                     | ト・カウンタ                  | : 1チャネル              |  |  |

|          |          | ・8 ビット・タイマ                           |                         | : 1チャネル              |  |  |

|          |          | ・8 ビット・イベント・カウン                      | ソタ                      | : 1チャネル              |  |  |

|          |          | ・8ビット・リモコン・タイ                        | 7                       | : 1チャネル              |  |  |

|          |          | ・ウォッチドッグ・タイマ                         |                         | : 1チャネル              |  |  |

注 I<sup>2</sup>Cバス方式を使用した場合(周辺ハードウエアを使用せず,プログラムで実現した場合も含む),マスク発注時に当社販売員に連絡してください

(2/2)

|         | 品名         | μPD178046                                                           | μ PD178048 | μ PD178F048 |  |  |

|---------|------------|---------------------------------------------------------------------|------------|-------------|--|--|

| 項目      |            |                                                                     |            |             |  |  |

| PWM出力   |            | ・8 ビットPWM×4チャネル                                                     |            |             |  |  |

|         |            | ・14ビットPWM×1チャネル                                                     |            |             |  |  |

| OSD     | 表示文字数      | 1 画面最大288文字 (12行×24                                                 | 桁 )        |             |  |  |

| コントローラ  | 文字の種類      | 256種類 ( CROMに内蔵 )                                                   |            |             |  |  |

|         | 文字形式       | 12(幅)×18(高さ)ドット                                                     |            |             |  |  |

|         | 文字サイズ      | 1 x 1 , 2 x 2 , 3 x 3 , 4 x                                         | : 4から選択可能  |             |  |  |

|         | 文字色        | 8色                                                                  |            |             |  |  |

|         | 文字枠        | 画面単位で,文字枠あり/なしを選択可能                                                 |            |             |  |  |

|         | 背景         | 背景なし/ヌキ/ベタを選択可能。また背景色(8色)の指定可能。                                     |            |             |  |  |

|         | ハーフ・ブランキング | 文字単位で指定可能                                                           |            |             |  |  |

| ROMコレクシ | ョン         | 2 箇所                                                                |            |             |  |  |

| ベクタ     | マスカブル      | 内部:11,外部:5                                                          |            |             |  |  |

| 割り込み    | ノンマスカブル    | 内部: 1                                                               |            |             |  |  |

| 要因      | ソフトウエア     | 1                                                                   |            |             |  |  |

| スタンバイ機  | 能          | · HALTE- F                                                          |            |             |  |  |

|         |            | ·STOPE-F                                                            |            |             |  |  |

| リセット    |            | ・RESET端子によるリセット                                                     |            |             |  |  |

|         |            | ・ウォッチドッグ・タイマによる内部リセット                                               |            |             |  |  |

|         |            | ・パワーオン・クリア回路によるリセット                                                 |            |             |  |  |

|         |            | ・4.5 V <sup>注</sup> 未満または3.5 V <sup>注</sup> 未満の検出(CPU動作時および電源電圧投入時) |            |             |  |  |

|         |            | ・パワーオン・クリア電圧を選択可能(4.5 V/3.5 V)                                      |            |             |  |  |

| 電源電圧    |            | V <sub>DD</sub> = 4.5 ~ 5.5 V                                       |            |             |  |  |

| パッケージ   |            | 80ピン・プラスチックTQFP ( 12 × 12 mm, 0.5 mmピッチ )                           |            |             |  |  |

注 これらの電圧は最大値であり,実際にはそれぞれの電圧より低い電圧でリセットがかかります(**第**21**章 リセット機能**を参照)。

## 第2章 端子機能

## 2.1 端子機能一覧

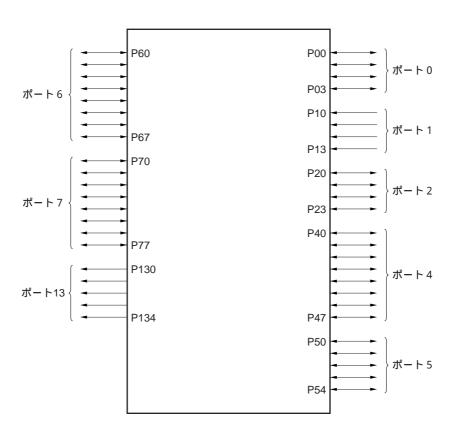

#### (1)ポート端子

| 端子名称      | 入出力 | 機能                          | リセット時 | 兼用端子        |

|-----------|-----|-----------------------------|-------|-------------|

| P00-P03   | 入出力 | ポート0。                       | 入力    | INTP0-INTP3 |

|           |     | 4 ビット入出力ポート。                |       |             |

|           |     | 1 ビット単位で入力 / 出力の指定可能。       |       |             |

| P10-P13   | 入力  | ポート1。                       | 入力    | ANI0-ANI3   |

|           |     | 4 ビット入力ポート。                 |       |             |

| P20, P21  | 入出力 | ポート2。                       | 入力    | SCL0, SCL1  |

| Dan Dan   | _   | 4 ビット入出力ポート。                |       | CDAO CDA4   |

| P22, P23  |     | 1 ビット単位で入力 / 出力の指定可能。       |       | SDA0, SDA1  |

| P40-P47   | 入出力 | ポート4。                       | 入力    | -           |

|           |     | 8 ビット入出力ポート。                |       |             |

|           |     | 1 ビット単位で入力 / 出力の指定可能。       |       |             |

| P50-P54   | 入出力 | ポート5。                       | 入力    | -           |

|           |     | 5 ビット入出力ポート。                |       |             |

|           |     | 1 ビット単位で入力 / 出力の指定可能。       |       |             |

| P60-P67   | 入出力 | ポート6。                       | 入力    | -           |

|           |     | 8 ビット入出力ポート。                |       |             |

|           |     | 1 ビット単位で入力 / 出力の指定可能。       |       |             |

| P70       | 入出力 | ポート7。                       | 入力    | SI3         |

| P71       |     | 8 ビット入出力ポート。                |       | SO3         |

| P72       |     | 1 ビット単位で入力 / 出力の指定可能。       |       | SCK3        |

| P73       |     |                             |       | TI21        |

| P74       |     |                             |       | OSCMON      |

| P75       |     |                             |       | TI5         |

| P76       |     |                             |       | TO5         |

| P77       |     |                             |       | TI9         |

| P130-P133 | 出力  | ポート13。                      | ロウ・レ  | PWM00-PWM03 |

| D424      | _   | 5 ビット出力ポート。                 | ベル出力  | DVA/A44     |

| P134      |     | N-chオープン・ドレーン出力ポート( 5 V耐圧)。 |       | PWM1        |

### (2)ポート以外の端子

| 端子名称            | 入出力 | 機能                                         | טע               | リセット時 | 兼用端子      |

|-----------------|-----|--------------------------------------------|------------------|-------|-----------|

| INTP0-INTP3     | 入力  | 有効エッジ(立ち上がりエッジ,立ち下が「                       | リエッジ , 立ち上がりおよび  | 入力    | P00-P03   |

|                 |     | 立ち下がりの両エッジ)指定可能な外部マ                        |                  |       |           |

| SI3             | 入力  | シリアル・インタフェースのシリアル・データ入力                    |                  |       | P70       |

| SO3             | 出力  | シリアル・インタフェースのシリアル・デ                        | データ出力            | 入力    | P71       |

| SDA0, SDA1      | 入出力 | シリアル・インタフェースのシリ N-chオ                      | ナープン・ドレーン入出力     | 入力    | P22, P23  |

|                 |     | アル・データ入力 / 出力                              |                  |       |           |

| SCK3            | 入出力 | シリアル・インタフェースのシリアル・ク                        | 7ロック入力/出力        | 入力    | P72       |

| SCL0, SCL1      | 入出力 | N-chオ                                      | ナープン・ドレーン入出力     | 入力    | P20, P21  |

| TI5             | 入力  | 8ビット・タイマ / イベント・カウンタ ( 1                   | TM5 ) への外部カウント・ク | 入力    | P75       |

|                 |     | ロック入力                                      |                  |       |           |

| TI9             |     | 8 ビット・リモコン・タイマ (TM9)へのタ                    | 外部カウント・クロック入力    |       | P77       |

| TI21            |     | 8 ビット・イベント・カウンタ ( TM21 ) /<br>入力           | への外部カウント・クロック    |       | P73       |

| TO5             | 出力  | 8 ビット・タイマ / イベント・カウンタ (                    | (TM5)出力          | 入力    | P76       |

| ANI0-ANI3       | 入力  | A/Dコンバータのアナログ入力                            |                  | 入力    | P10-P13   |

| PWM00-          | 出力  | 8 ビットPWM出力 N-chオ                           | ナープン・ドレーン入出力     | ロウ・レ  | P130-P133 |

| PWM03           |     |                                            |                  | ベル出力  |           |

| PWM1            |     | 14ビットPWM出力                                 |                  |       | P134      |

| OSCMON          | 出力  | OSDクロック出力                                  |                  | 入力    | P74       |

| Vsync           | 入力  | OSD垂直同期信号入力                                |                  | 入力    | -         |

| Hsync           |     | OSD水平同期信号入力                                |                  |       | -         |

| R               | 出力  | OSDキャラクタおよび背景のRED出力                        |                  | ロウ・レ  | -         |

| G               |     | OSDキャラクタおよび背景のGREEN出力                      |                  | ベル出力  | -         |

| В               |     | OSDキャラクタおよび背景のBLUE出力                       |                  |       | -         |

| I               |     | OSDキャラクタおよび背景のヌキ・モード時の文字背景出力               |                  |       | -         |

| BLANK           |     | OSDブランキング信号出力                              |                  |       | -         |

| RESET           | 入力  | システム・リセット入力                                |                  | -     | -         |

| X1              | 入力  | システム・クロック発振用水晶振動子接続                        | ±                | -     | -         |

| X2              | -   |                                            |                  | -     | -         |

| OSC1            | 入力  | OSDドット・クロック発振用LC接続                         |                  | -     | -         |

| OSC2            | 出力  |                                            |                  | -     | -         |

| V <sub>DD</sub> | -   | 正電源                                        |                  | -     | -         |

| GND00, GND10,   | -   | グランド                                       |                  | -     | -         |

| GND01, GND11    |     |                                            |                  |       |           |

| VddPORT         | -   | ポート用正電源                                    |                  | -     | -         |

| GNDPORT         | -   | ポート用グランド                                   |                  | -     | -         |

| NC              | -   | 内部に接続していません。GND00, GND01, GND10, GND11のいずれ |                  | -     | -         |

|                 |     | かに接続(オープンも可)してください。                        |                  |       |           |

| IC              | -   | 内部接続されています。GND00, GND01, GND10, GND11のいずれか |                  | -     | -         |

|                 |     | に直接接続してください                                |                  |       |           |

| V <sub>PP</sub> | -   | プログラム書き込み/ベリファイ時の高電圧印加。通常動作モード時は           |                  | -     | -         |

|                 |     | GND00, GND01, GND10, GND11のいずれかに直接接続してくださ  |                  |       |           |

|                 |     | l Io                                       |                  |       |           |

# 2.2 端子機能の説明

## 2.2.1 P00-P03 (Port0)

4 ビットの入出力ポートです。入出力ポートのほかに,外部割り込み要求入力機能があります。 1 ビット単位で次のような動作モードを指定できます。

## (1)ポート・モード

4ビットの入出力ポートとして機能します。

ポート・モード・レジスタ 0 ( PM0 ) により , 1 ビット単位で入力ポートまたは出力ポートに指定できます。

#### (2) コントロール・モード

外部割り込み要求入力端子(INTP0-INTP3)として機能します。

INTPO-INTP3は,有効エッジ(立ち上がりエッジ,立ち下がりエッジ,立ち上がりおよび立ち下がりの両エッジ)指定可能な外部割り込み要求入力端子です。

# 2.2.2 P10-P13 (Port1)

4 ビットの入力ポートです。入力ポートのほかにA/Dコンバータのアナログ入力機能があります。

1ビット単位で次のような動作モードを指定できます。

#### (1)ポート・モード

4ビットの入力ポートとして機能します。

#### (2) コントロール・モード

A/Dコンバータのアナログ入力端子(ANIO-ANI3)として機能します。

# 2.2.3 P20-P23 (Port2)

4 ビットの入出力ポートです。入出力ポートのほかにシリアル・インタフェースのデータ入出力,クロック入出力機能があります。

1ビット単位で次のような動作モードを指定できます。

# (1)ポート・モード

4 ビットの入出力ポートとして機能します。ポート・モード・レジスタ 2 (PM2)により, 1 ビット単位で入力ポートまたは出力ポートに指定できます。

#### (2) コントロール・モード

シリアル・インタフェースのデータ入出力,クロック入出力として機能します。

#### ( a ) SDA0, SDA1

シリアル・インタフェース(IIC1)のシリアル・データの入出力端子です。

#### ( b ) SCL0, SCL1

シリアル・インタフェース(IIC1)のシリアル・クロックの入出力端子です。

## 2.2.4 P40-P47 (Port4)

8ビットの入出力ポートです。

ポート・モード・レジスタ4 (PM4)により、1ビット単位で入力ポートまたは出力ポートに指定できます。

### 2.2.5 P50-P54 (Port5)

5ビットの入出力ポートです。

ポート・モード・レジスタ5 (PM5)により、1ビット単位で入力ポートまたは出力ポートに指定できます。

## 2.2.6 P60-P67 (Port6)

8ビットの入出力ポートです。

ポート・モード・レジスタ6 (PM6)により、1ビット単位で入力ポートまたは出力ポートに指定できます。

#### 2.2.7 P70-P77 (Port7)

8 ビットの入出力ポートです。入出力ポートのほかにシリアル・インタフェースのデータ入出力,クロック入出力,タイマの入出力,OSDクロック出力機能があります。

## (1)ポート・モード

8 ビットの入出力ポートとして機能します。ポート・モード・レジスタ7 (PM7) により , 1 ビット単位で入力ポートまたは出力ポートに指定できます。

#### (2) コントロール・モード

シリアル・インタフェースのデータ入出力,クロック入出力,タイマの入出力,OSDクロックの出力として機能します。

#### (a) SI3, SO3

シリアル・インタフェースのシリアル・データ入出力端子です。

## ( **b** ) SCK3

シリアル・インタフェースのシリアル・クロック入出力端子です。

#### (c) TI9

8 ビット・リモコン・タイマの入力端子です。

#### (d) TI5, TI21

8ビット・タイマ/イベント・カウンタへの入力端子です。

### (e) TO5

タイマ出力端子です。

# (f) OSCMON

OSDクロック出力端子です。

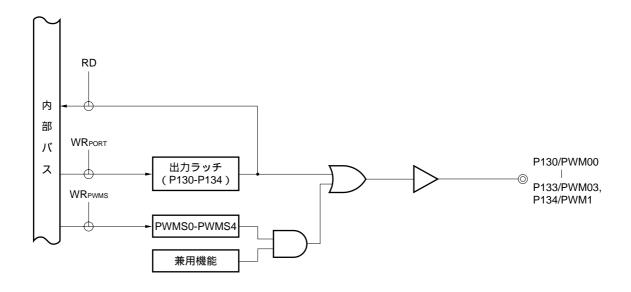

# **2.2.8** P130-P134 (Port13)

5 ビットの出力ポートです。出力ポートのほかにPWM出力機能があります。 1 ビット単位で次のような動作モードを指定できます。

#### (1)ポート・モード

5 ビットの出力ポートとして機能します。

#### (2)コントロール・モード

PWMの出力(PWM00-PWM03, PWM1)として機能します。

## 2.2.9 VSYNC

OSD垂直同期信号の入力端子です。

# 2.2.10 HSYNC

OSD水平同期信号の入力端子です。

#### 2.2.11 R

OSDキャラクタおよび背景のRED出力端子です。

### 2.2.12 G

OSDキャラクタおよび背景のGREEN出力端子です。

## **2**.**2**.13 B

OSDキャラクタおよび背景のBLUE出力端子です。

### 2.2.14 I

背景ヌキ・モード時の文字背景出力端子です。

## 2.2.15 BLANK

OSDブランキング信号出力端子です。

# 2.2.16 OSC1, OSC2

OSD用ドット・クロック発振用LC接続端子です。

# 2.2.17 RESET

ロウ・アクティブのシステム・リセット入力端子です。

# 2.2.18 X1, X2

システム・クロック発振用水晶振動子接続端子です。

# 2.2.19 VDD

正電源供給端子です。

# ★ 2.2.20 GND00, GND10, GND01, GND11

グランド電位端子です。

# 2.2.21 VDDPORT

ポート用正電源供給端子です。VDD端子と同電位にしてください。

## 2.2.22 GNDPORT

ポート用グランド電位端子です。GND端子注と同電位にしてください。

## 2.2.23 NC

NC (Non-connection)は内部接続をしていません。GND端子注に接続してください(オープンも可能)。

# **2**.**2**.24 VPP ( μPD178F048**のみ** )

フラッシュ・メモリ・プログラミング・モード設定およびプログラム書き込み / ベリファイ時の高電圧印加端 子です。

通常動作モード時は, GND端子注に直接接続してください。

注 GND端子とは, GND00, GND10, GND01, GND11端子のいずれかを指します。

# 2.2.25 IC (マスクROM製品のみ)

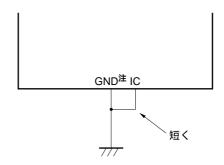

IC (Internally Connected ) 端子は,当社出荷時に  $\mu$  PD178048サブシリーズを検査するためのテスト・モード に設定するための端子です。通常動作モード時には,IC端子をGND端子 $^{2}$ に直接接続し,その配線長を極力短くしてください。

IC端子とGND端子 $^{\pm}$ 間の配線の引き回しが長い場合や,IC端子に外来ノイズが加わった場合などで,IC端子とGND端子 $^{\pm}$ 間に電位差が生じたときには,お客様のプログラムが正常に動作しないことがあります。

IC端子をGND端子<sup>注</sup>に直接接続してください。

注 GND端子とは, GND00, GND10, GND01, GND11端子のいずれかを指します。

# 2.3 端子の入出力回路と未使用端子の処理

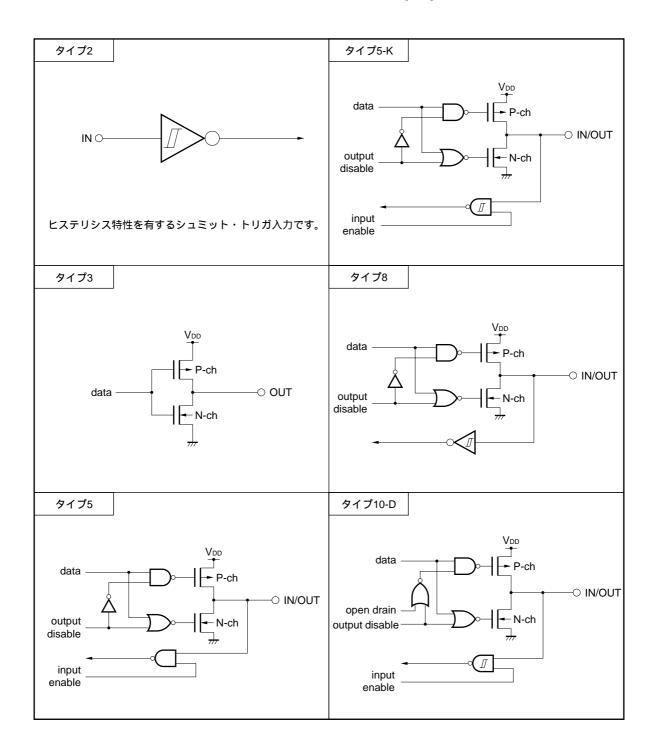

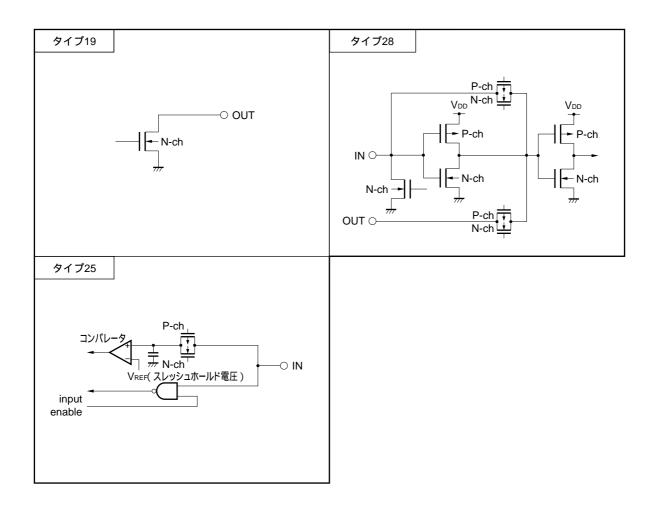

各端子の入出力回路タイプと,未使用端子の処理を表2-1に示します。 また,各タイプの入出力回路の構成は,図2-1を参照してください。

## 表2-1 各端子の入出力回路タイプと未使用端子の処理

| 端子名                 | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法                                          |

|---------------------|----------|-----|------------------------------------------------------|

| P00/INTP0-P03/INTP3 | 8        | 入出力 | ソフトウエアで汎用入力ポートに設定して,個別に抵抗を介して,                       |

|                     |          |     | GND00, GND10, GND01, GND11, GNDPORTのいずれかに接続し         |

|                     |          |     | てください。                                               |

| P10/ANI0-P13/ANI3   | 25       | 入力  | 個別に抵抗を介して, VDD, VDDPORT, GND00, GND10, GND01,        |

|                     |          |     | GND11, GNDPORTのいずれかに接続してください。                        |

| P20/SCL0, P21/SCL1  | 10-D     | 入出力 | ソフトウエアで汎用入力ポートに設定して,個別に抵抗を介して,                       |

| P22/SDA0, P23/SDA1  |          |     | VDD, VDDPORT, GND00, GND10, GND01, GND11, GNDPORTOL1 |

| P40-P47             | 5        |     | ずれかに接続してください。                                        |

| P50-P54             | -        |     |                                                      |

| P60-P67             |          |     |                                                      |

| P70/SI3             | 5-K      |     |                                                      |

| P71/SO3             | 5        |     |                                                      |

| P72/SCK3            | 5-K      |     |                                                      |

| P73/Tl21            | -        |     |                                                      |

| P74/OSCMON          | 5        |     |                                                      |

| P75/TI5             | 5-K      |     |                                                      |

| P76/TO5             | 5        |     |                                                      |

| P77/TI9             | 5-K      |     |                                                      |

| P130/PWM00          | 19       | 出力  | ソフトウエアでロウ・レベル出力に設定して,オープンにしてくだ                       |

| -P133/PWM03         |          |     | さい。                                                  |

| P134/PWM1           |          |     |                                                      |

| VSYNC               | 2        | 入力  | 個別に抵抗を介して,GND00, GND10, GND01, GND11のいずれ             |

| Hsync               |          |     | かに接続してください。                                          |

| R                   | 3        | 出力  | ソフトウエアでOSD表示をオフに設定してから,オープンにしてく                      |

| G                   |          |     | ださい。                                                 |

| В                   |          |     |                                                      |

| I                   |          |     |                                                      |

| BLANK               |          |     |                                                      |

| RESET               | 2        | 入力  | -                                                    |

| OSC1                | 28       | 入力  | ソフトウエアでLC発振をオフに設定してから,オープンにしてくだ                      |

|                     |          |     | さい。                                                  |

| OSC2                | 1        | 出力  | オープンにしてください。                                         |

| IC                  | -        | -   | GND00, GND10, GND01, GND11のいずれかに直接接続してくだ             |

| VPP(μPD178F048のみ)   |          |     | さい。                                                  |

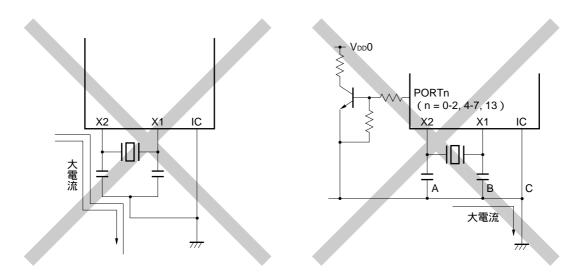

図2-1 端子の入出力回路一覧(1/2)

**備考** VDDおよびGNDは,すべてポート部への正電源およびグランド電位です。それぞれVDDPORT,GNDPORTと読み替えてください。

図2-1 端子の入出力回路一覧(2/2)

**備考** VDDおよびGNDは,すべてポート部への正電源およびグランド電位です。それぞれVDDPORT,GNDPORTと読み替えてください。

# 第3章 CPUアーキテクチャ

# 3.1 メモリ空間

メモリ・サイズ切り替えレジスタ(IMS)と内部拡張RAMサイズ切り替えレジスタ(IXS)の初期値は,それぞれ CFH, 0CHですが,各製品ごとに次に示す値を設定する必要があります。

| 製品名        | IMS            | IXS |

|------------|----------------|-----|

| μPD178046  | 4CH            | ОВН |

| μ PD178048 | 4FH            |     |

| μPD178F048 | マスクROM製品に対応した値 |     |

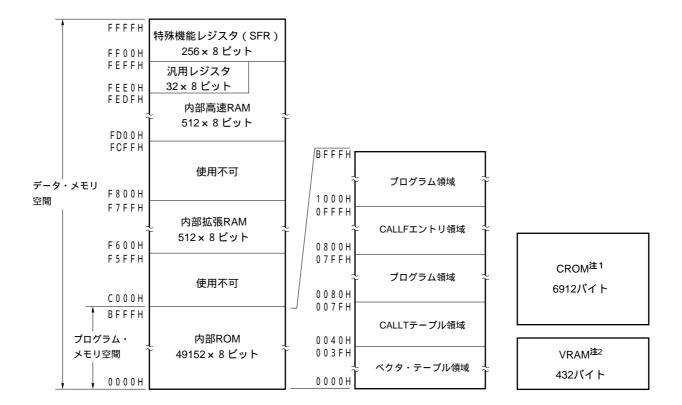

### **(1)** μPD178046

メモリ・サイズ切り替えレジスタ (IMS) と内部拡張RAMサイズ切り替えレジスタ (IXS) の値をそれぞれ 4CH, 0BHに設定して使用してください (初期値は, CFH, 0CH)。

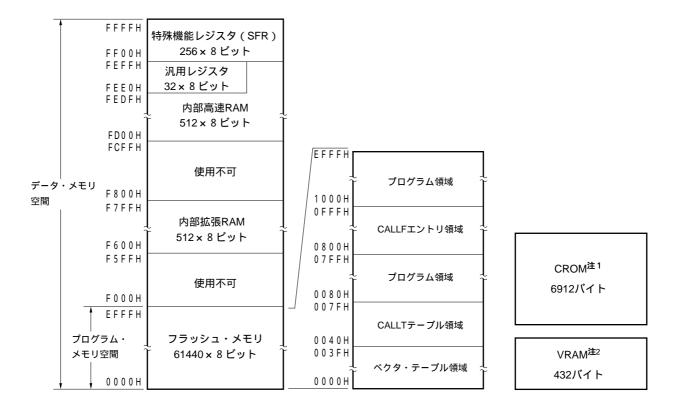

図3-1 メモリ・マップ (µPD178046)

- 注1.CROMはプログラムではリードできません。

- 2. VRAMはSFRを介してライトできます。

#### (2) µPD178048

メモリ・サイズ切り替えレジスタ (IMS) と内部拡張RAMサイズ切り替えレジスタ (IXS) の値をそれぞれ 4FH, 0BHに設定して使用してください (初期値は, CFH, 0CH)。

図3-2 メモリ・マップ (µPD178048)

- 注1.CROMはプログラムではリードできません。

- 2. VRAMはSFRを介してライトできます。

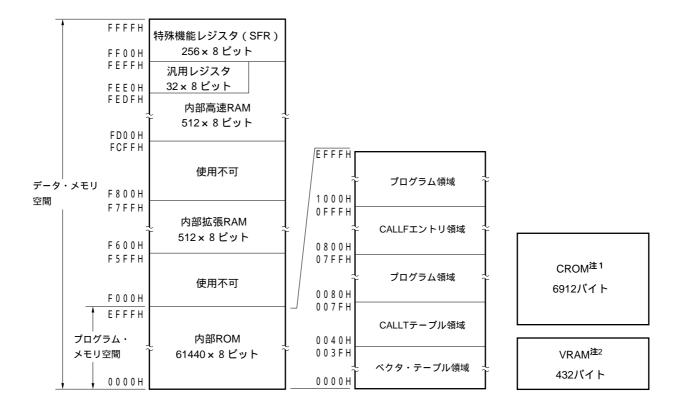

#### (3) $\mu$ PD178F048

メモリ・サイズ切り替えレジスタ (IMS) の値をマスクROM製品に対応した値に,内部拡張RAMサイズ切り替えレジスタ (IXS) の値を0BHに設定して使用してください(初期値は,CFH,0CH)。

図3-3 メモリ・マップ (µPD178F048)

- 注1.CROMはプログラムではリードできません。

- 2. VRAMはSFRを介してライトできます。

# 3.1.1 内部プログラム・メモリ空間

$\mu$  PD178046は49152 × 8 ビット ,  $\mu$  PD178048は61440 × 8 ビット構成のマスクROM ,  $\mu$  PD178F048は61440 × 8 ビット構成のフラッシュ・メモリとなっています。プログラムおよびテーブル・データなどを格納します。 通常 , プログラム・カウンタ ( PC ) でアドレスします。

内部プログラム・メモリ空間には,次に示す領域を割り付けています。

# (1)ベクタ・テーブル領域

0000H-003FHの64バイト領域はベクタ・テーブル領域として予約されています。ベクタ・テーブル領域には、リセット入力、各割り込み要求発生により分岐するときのプログラム・スタート・アドレスを格納しておきます。16ビット・アドレスのうちの下位8ビットが偶数アドレスに、上位8ビットが奇数アドレスに格納されます。

表3-1 ベクタ・テーブル

| 123 - 1 - 177 | 7 770    |

|---------------|----------|

| ベクタ・テーブル・アドレス | 割り込み要因   |

| 0000H         | リセット入力   |

| 0004H         | INTWDT   |

| 0006H         | INTP0    |

| 0008H         | INTP1    |

| 000AH         | INTP2    |

| 000CH         | INTP3    |

| 000EH         | INTTM90  |

| 0010H         | INTTM91  |

| 0012H         | INTVSYNC |

| 0014H         | INTTM21  |

| 0016H         | INTIIC1  |

| 0018H         | INTTM92  |

| 001AH         | INTCSI3  |

| 001CH         | INTTM5   |

| 001EH         | INTTM20  |

| 0020H         | INTBTM1  |

| 0022H         | INTAD    |

| 003EH         | BRK      |

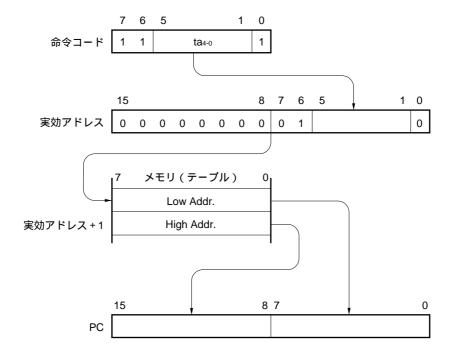

#### (2) CALLT命令テーブル領域

0040H-007FHの64バイト領域には,1バイト・コール命令(CALLT)のサブルーチン・エントリ・アドレスを格納できます。

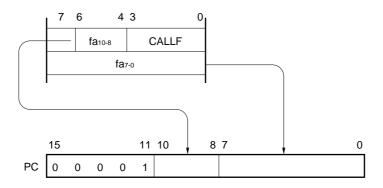

#### (3) CALLF命令エントリ領域

0800H-0FFFHの領域は,2バイト・コール命令(CALLF)で直接サブルーチン・コールできます。

# 3.1.2 内部データ・メモリ空間

μPD178048サブシリーズは,次に示すRAMを内蔵しています。

#### **(1)内部高速**RAM

$512 \times 8$  ビット構成となっています。このうちFEE0H-FEFFHの32バイトの領域には,8 ビット・レジスタ 8 個を 1 バンクとする汎用レジスタが,4 バンク割り付けられています。

また,内部高速RAMはスタック・メモリ領域としても使用できます。

#### **(2)内部拡張**RAM

F600H-F7FFHの512バイトの領域に,内部拡張RAMが割り付けられています。

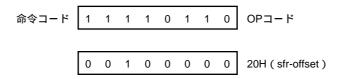

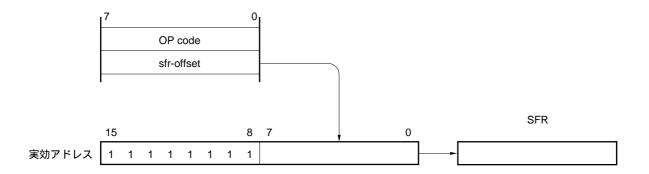

# 3.1.3 特殊機能レジスタ (SFR: Special Function Register) 領域

FF00H-FFFFHの領域には,オン・チップ周辺ハードウエアの特殊機能レジスタ(SFR)が割り付けられています(3.2.3 特殊機能レジスタ(SFR: Special Function Register)の表3-3 特殊機能レジスタ一覧参照)。

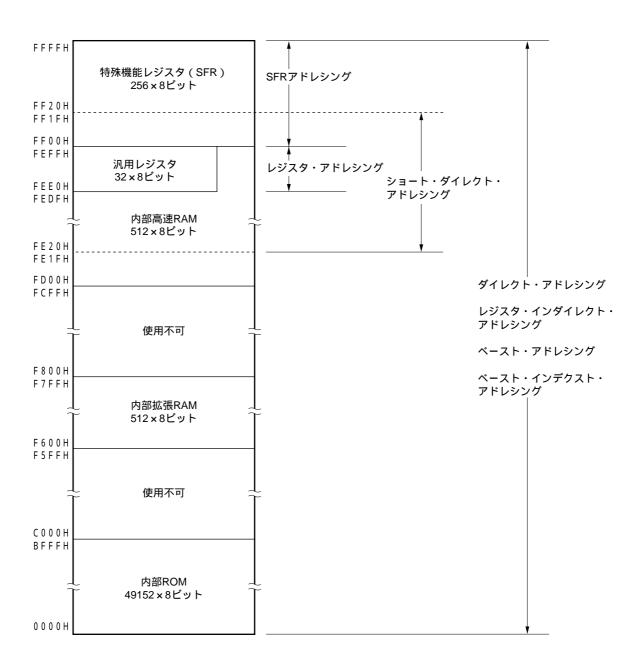

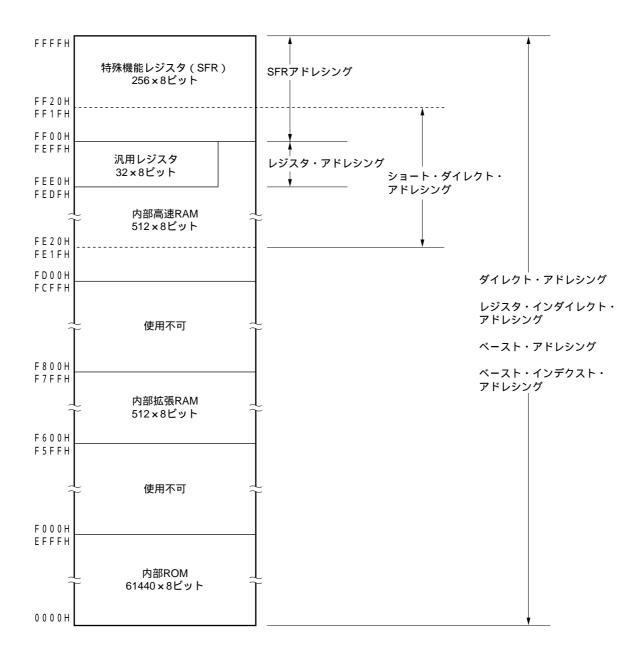

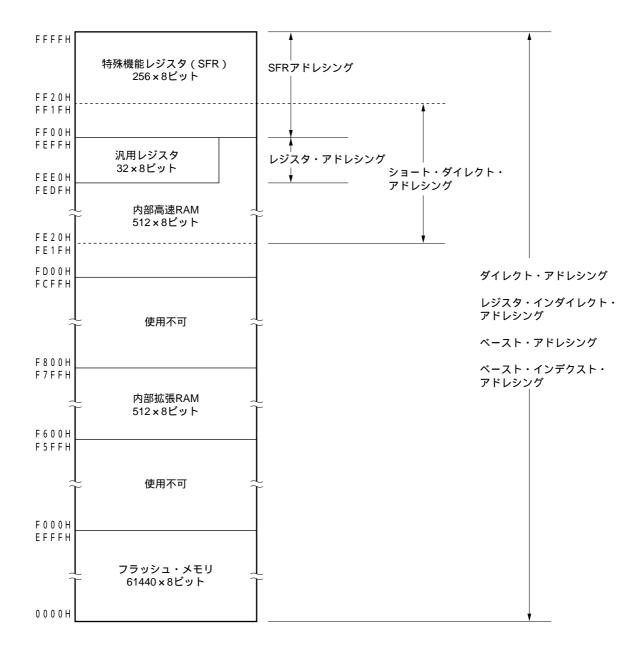

# 3.1.4 データ・メモリ・アドレシング

次に実行する命令のアドレスを指定したり,命令を実行する際に操作対象となるレジスタやメモリなどのアドレスを指定する方法をアドレシングといいます。

次に実行する命令のアドレスはプログラム・カウンタ (PC)によりアドレスされます (詳細については, 3.3 命令アドレスのアドレシングを参照してください)。

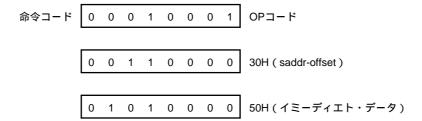

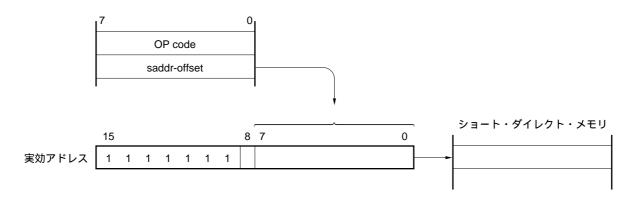

一方,命令を実行する際に操作対象となるメモリのアドレシングについて,μPD178048サブシリーズでは,その操作性などを考慮して豊富なアドレシング・モードを備えています。特にデータ・メモリを内蔵している領域 (FD00H-FFFFH)では,特殊機能レジスタ(SFR)や汎用レジスタなど,それぞれの持つ機能にあわせて特有のアドレシングが可能です。図3-4から図3-6にデータ・メモリのアドレシングを示します。各アドレシングの詳細については,3.4 オペランド・アドレスのアドレシングを参照してください。

図3 - 4 データ・メモリのアドレシング (µPD178046)

## 図3 - 5 データ・メモリのアドレシング (µPD178048)

## 図3 - 6 データ・メモリのアドレシング (µPD178F048)

# 3.2 プロセッサ・レジスタ

μPD178048サブシリーズは,次のプロセッサ・レジスタを内蔵しています。

## 3.2.1 制御レジスタ

プログラム・シーケンス,ステータス,スタック・メモリの制御など専用の機能を持ったレジスタです。制御レジスタには,プログラム・カウンタ(PC),プログラム・ステータス・ワード(PSW),スタック・ポインタ(SP)があります。

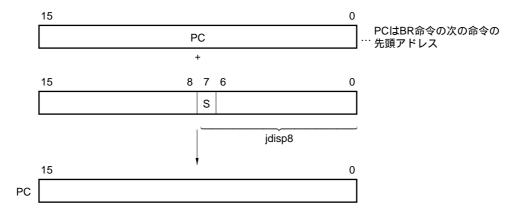

### (1) プログラム・カウンタ (PC)

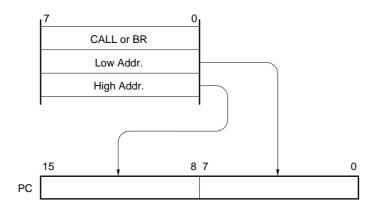

プログラム・カウンタは,次に実行するプログラムのアドレス情報を保持する16ビット・レジスタです。 通常動作時には,フェッチする命令のバイト数に応じて,自動的にインクリメントされます。分岐命令実 行時には,イミーディエト・データやレジスタの内容がセットされます。

リセット入力により,0000Hと0001H番地のリセット・ベクタ・テーブルの値がプログラム・カウンタに セットされます。

図3-7 プログラム・カウンタの構成

|    | 15   |      |      |      |      |      |     |     |     |     |     |     |     |     |     | 0   |  |

|----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| РС | PC15 | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |  |

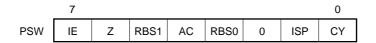

### (2) プログラム・ステータス・ワード (PSW)

プログラム・ステータス・ワードは,命令の実行によってセット,リセットされる各種フラグで構成される8ビット・レジスタです。

プログラム・ステータス・ワードの内容は、割り込み要求発生時およびPUSH PSW命令の実行時に自動的にスタックされ、RETB、RETI命令およびPOP PSW命令の実行時に自動的に復帰されます。

リセット入力により,02Hになります。

図3-8 プログラム・ステータス・ワードの構成

#### (a)割り込み許可フラグ(IE)

CPUの割り込み要求受け付け動作を制御するフラグです。

IE = 0のときは割り込み禁止(DI)状態となり, ノンマスカブル割り込み以外の割り込み要求はすべて禁止されます。

IE = 1のときは割り込み許可(EI)状態となります。このとき割り込み要求の受け付けは、インサービス・プライオリティ・フラグ(ISP)、各割り込み要因に対する割り込みマスク・フラグおよび優先順位指定フラグにより制御されます。

このフラグは,DI命令の実行または割り込み要求の受け付けでリセット(0)され,EI命令の実行によりセット(1)されます。

#### (b)ゼロ・フラグ(Z)

演算結果がゼロのときセット(1)され,それ以外のときにリセット(0)されるフラグです。

#### (c) レジスタ・パンク選択フラグ (RBS0, RBS1)

4個のレジスタ・バンクのうちの1つを選択する2ビットのフラグです。

SEL RBn命令の実行によって選択されたレジスタ・バンクを示す2ビットの情報が格納されています。

#### (d)補助キャリー・フラグ(AC)

演算結果が,ビット3からキャリーがあったとき,またはビット3へのボローがあったときセット(1) され,それ以外のときリセット(0)されるフラグです。

#### (e) インサービス・プライオリティ・フラグ(ISP)

受け付け可能なマスカブル・ベクタ割り込みの優先順位を管理するフラグです。ISP = 0のときは優先順位指定フラグ・レジスタ(PROL, PROH)(19.3(3)優先順位指定フラグ・レジスタ(PROL, PROH)参照)で低位に指定されたベクタ割り込み要求は受け付け禁止となります。なお,実際に割り込み要求が受け付けられるかどうかは,割り込み許可フラグ(IE)の状態により制御されます。

#### (f) キャリー・フラグ(CY)

加減算命令実行時のオーバフロー,アンダフローを記憶するフラグです。また,ローテート命令実行時は シフト・アウトされた値を記憶し,ビット演算命令実行時には,ビット・アキュームレータとして機能しま す。

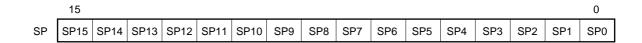

#### (3) スタック・ポインタ(SP)

メモリのスタック領域の先頭アドレスを保持する16ビットのレジスタです。スタック領域としては内部高速RAM領域(FD00H-FEFFH)のみ設定可能です。

図3-9 スタック・ポインタの構成

スタック・メモリへの書き込み(退避)動作に先立ってデクリメントされ,スタック・メモリからの読み取り(復帰)動作のあとインクリメントされます。

各スタック動作によって退避/復帰されるデータは図3-10,3-11のようになります。

注意 SPの内容はリセット入力により,不定になりますので,必ず命令実行前にイニシャライズしてく ださい。

図3-10 スタック・メモリへ退避されるデータ

|         | PUSH rp命令 | CA      | ALL, CALLF, CALLT命 | 令       | 割り込み,BRK命令 |

|---------|-----------|---------|--------------------|---------|------------|

|         |           |         |                    | SP SP-3 |            |

| SP SP-2 |           | SP SP-2 |                    | SP - 3  | PC7-PC0    |

| SP - 2  | レジスタ・ペア下位 | SP - 2  | PC7-PC0            | SP - 2  | PC15-PC8   |

| SP - 1  | レジスタ・ペア上位 | SP - 1  | PC15-PC8           | SP - 1  | PSW        |

| SP      |           | SP      |                    | SP      |            |

|         |           |         |                    |         |            |

POP rp命令 RET命令 RETI, RETB命令

SP レジスタ・ペア下位 SP PC7-PC0 SP PC7-PC0

SP+1 レジスタ・ペア上位 SP+1 PC15-PC8 SP+1 PC15-PC8

SP SP+2

図3-11 スタック・メモリから復帰されるデータ

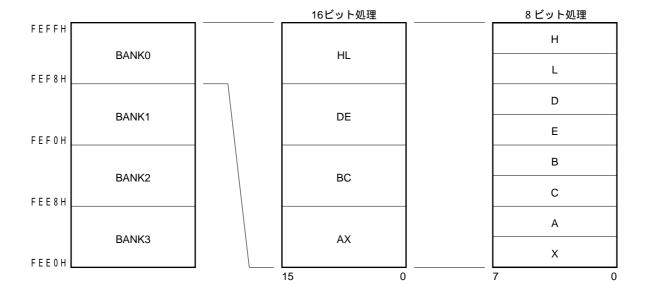

# 3.2.2 汎用レジスタ

SP SP+2

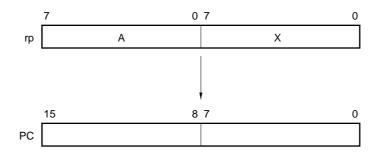

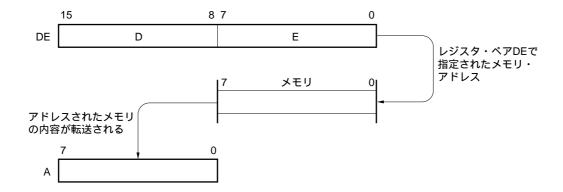

汎用レジスタは,データ・メモリの特定番地(FEE0H-FEFFH)にマッピングされており,8ビット・レジスタ8個(X, A, C, B, E, D, L, H)を1バンクとして4バンクのレジスタで構成されています。

各レジスタは,それぞれ8ビット・レジスタとして使用できるほか,2個の8ビット・レジスタをペアとして16ビット・レジスタとしても使用できます(AX, BC, DE, HL)。

また,機能名称(X, A, C, B, E, D, L, H, AX, BC, DE, HL)のほか,絶対名称(R0-R7, RP0-RP3)ででも記述できます。

命令実行時に使用するレジスタ・バンクは、CPU制御命令(SEL RBn)によって設定します。 4 レジスタ・バンク構成になっていますので、通常処理で使用するレジスタと割り込み時で使用するレジスタをバンクごとに切り替えることにより、効率のよいプログラムを作成できます。

| バンク名  | レジ   | スタ   | 絶対ア   | 7ドレ | ノス | バンク名  | レジ   | スタ   | 絍 | 対 | アト | レ | コ |

|-------|------|------|-------|-----|----|-------|------|------|---|---|----|---|---|

|       | 機能名称 | 絶対名称 |       |     |    |       | 機能名称 | 絶対名称 |   |   |    |   |   |

| BANK0 | Н    | R7   | F E   | F F | Н  | BANK2 | Н    | R7   | F | Е | Е  | F | Н |

|       | L    | R6   | F E I | F E | Н  |       | L    | R6   | F | Е | Е  | Е | Н |

|       | D    | R5   | FEI   | F D | Н  |       | D    | R5   | F | Е | Е  | D | Н |

|       | E    | R4   | FEI   | F C | Н  |       | E    | R4   | F | Е | Е  | С | Н |

|       | В    | R3   | F E I | F B | Н  |       | В    | R3   | F | Е | Е  | В | Н |

|       | С    | R2   | F E I | F A | Н  |       | С    | R2   | F | Е | Е  | Α | Н |

|       | А    | R1   | F E   | F 9 | Н  |       | Α    | R1   | F | Е | Е  | 9 | Н |

|       | X    | R0   | F E   | F 8 | Н  |       | X    | R0   | F | Е | Е  | 8 | Н |

| BANK1 | Н    | R7   | F E   | F 7 | Н  | BANK3 | Н    | R7   | F | Е | Е  | 7 | Н |

|       | L    | R6   | F E   | F 6 | Н  |       | L    | R6   | F | Е | Е  | 6 | Н |

|       | D    | R5   | F E   | F 5 | Н  |       | D    | R5   | F | Е | Е  | 5 | Н |

|       | E    | R4   | FE    | F 4 | Н  |       | E    | R4   | F | Е | Е  | 4 | Н |

|       | В    | R3   | F E   | F 3 | Н  |       | В    | R3   | F | Е | Е  | 3 | Н |

|       | С    | R2   | FE    | F 2 | Н  |       | С    | R2   | F | Е | Е  | 2 | Н |

|       | А    | R1   | FE    | F 1 | Н  |       | А    | R1   | F | Е | Е  | 1 | Н |

|       | Х    | R0   | FE    | F C | Н  |       | X    | R0   | F | Е | Е  | 0 | Н |

表3-2 汎用レジスタの絶対アドレス対照表

**PSW**

SP + 2

SP SP+3

# 図3-12 汎用レジスタの構成

# (a)絶対名称

|           |       |     | 16ビット処理 | <br>8 ビット処理 |

|-----------|-------|-----|---------|-------------|

| FEFFH     | DANKO |     | DDo     | R7          |