# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

$\mu$ PD98410

( NEASCOT - X10<sup>™</sup> )

1.2G ATM SWITCH LSI

資料番号 S12523JJ2V1UM00 (第 2 版 ) 発行年月 November 1998 NS CP(K)

[メモ]

# 目 次 要 約

第1章 概 説 ... 17

第 2 章 端子機能 ... 21

第 3 章 機能概要 ... 41

第4章 内部レジスタ ... 127

第5章 JTAG パウンダリ・スキャン ... 177

第6章 使用制限事項 ... 193

第7章 FAQ (Frequently Asked Questions)... 203

### CMOSデバイスの一般的注意事項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してV∞またはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

NEASCOT-X10 は,日本電気株式会社の商標です。

本製品は外国為替および外国貿易管理法の規定により戦略物資等(または役務)に該当しますので, 日本国外に輸出する場合には,同法に基づき日本国政府の輸出許可が必要です。

本資料に掲載の応用回路および回路定数は、例示的に示したものであり、量産設計を対象とするものではありません。

#### 本資料の内容は,後日変更する場合があります。

文書による当社の承諾なしに本資料の転載複製を禁じます。

本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的所有権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんのでご了承ください。

当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で , 特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は , 必ず事前に当社販売窓口までご相談頂きますようお願い致します。

この製品は耐放射線設計をしておりません。

## 本版で改訂された主な箇所

| ページ            | 内 容                                          |  |  |  |  |

|----------------|----------------------------------------------|--|--|--|--|

|                | 第3章                                          |  |  |  |  |

| p.45 , 47 , 96 | 3.2.1 ポーリング概要 , 3.2.2 セル出力時のポーリング , 3.6.2 使用 |  |  |  |  |

|                | するカウンタ,フラグ(3) 説明の追加                          |  |  |  |  |

| p.110          | 3.9.10 カウント・オーバ検出 追加                         |  |  |  |  |

| p.129          | 4.2 レジスタ・マップ 追加                              |  |  |  |  |

| p.177          | 第5章 JTAG パウンダリ・スキャン 追加                       |  |  |  |  |

| p.193          | 第6章 使用制限事項 追加                                |  |  |  |  |

| p.203          | 第7章 FAQ (Frequently Asked Questions ) 追加     |  |  |  |  |

本文欄外の 印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

# はじめに

- 対象者 このマニュアルは , μPD98410 の機能を理解し , それを用いたアプリケーション・システムを設計 するエンジニアを対象としています。

- **旬 的** このマニュアルは,次の構成に示すμPD98410 の持つハードウエア機能をユーザに理解していた だくことを目的としています。

- 構 成 このマニュアルは,次の内容で構成されています。

- 概 説

- ・端子機能

- ・機能概要

- ・内部レジスタ

- ・JTAG バウンダリ・スキャン

- ·使用制限事項

- FAQ ( Frequently Asked Questions )

- 読み方 このマニュアルの読者には、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

- 一通りµPD98410 の機能を理解しようとするとき 目次に従ってお読みください。

- μPD98410 の動作について何か不明な点があるとき第7章 FAQ (Frequently Asked Questions) をお読みください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : XXX\_B ( 端子, 信号名称に\_B )

メモリ・マップのアドレス : 上部 - 上位, 下部 - 下位

注: 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考: 本文の補足説明

数の表記 : 2 進数...XXXX または XXXXB

10 進数...XXXX

16 進数...XXXXH または XXXXh

関連資料 関連資料は暫定の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじ めご了承ください。

● パンフレット: S12131J

● デ-タ・シ-ト: S12624J

● アプリケ - ション・ノ - ト: S13107J

# 目 次

| <b>邦</b>   早 | 版 at 17                      |

|--------------|------------------------------|

|              |                              |

|              | 特 徴 17                       |

| 1.2          | オーダ情報 17                     |

| 1.3          | システム構成例(用途) 18               |

| 1.4          | ブロック図 19                     |

| 1.5          | 端子構成図 20                     |

|              |                              |

| 第2章          | 端子機能 21                      |

|              |                              |

| 2.1          | 端子概要図(Bottom View) 21        |

| 2.2          | 端子配置 23                      |

| 2.3          | 端子機能 29                      |

|              | 2.3.1 パワ - ・サプライ 29          |

|              | 2.3.2 UTOPIA インタフェ - ス 30    |

| 2.4          | メモリ・インタフェース信号 34             |

|              | 2.4.1 マイクロプロセッサ・インタフェース信号 36 |

|              | 2.4.2 JTAG 38                |

|              | 2.4.3 その他 38                 |

| 2.5          | 未使用端子の処理方法 39                |

| 2.6          | リセット時の端子の状態 40               |

|              |                              |

| 第3章          | 機能概要 41                      |

|              |                              |

| 3.1          | UTOPIA インタフェ - ス 41          |

| 0.1          |                              |

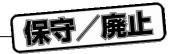

3.1.1 入力ポ - ト・インタフェ - ス ... 42

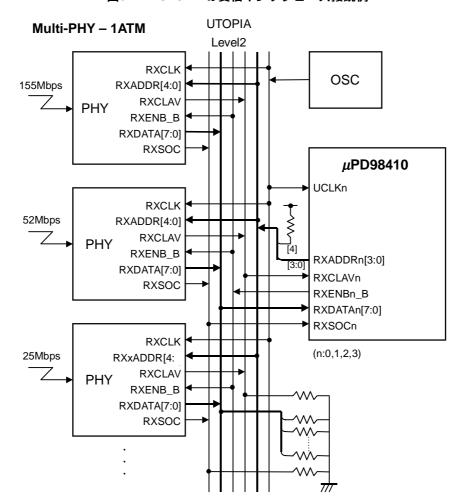

3.1.2 出力ポ - ト・インタフェ - ス ... 43

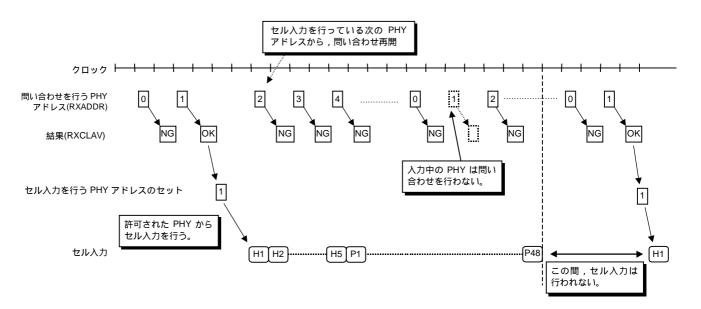

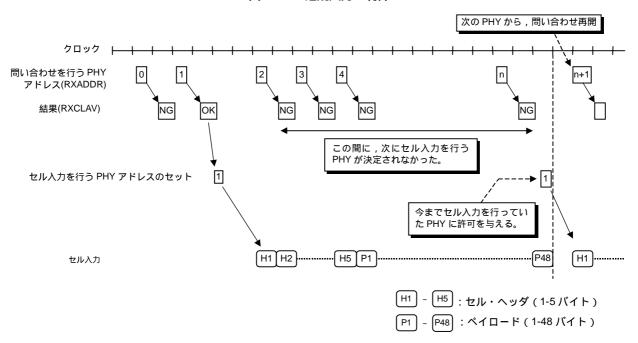

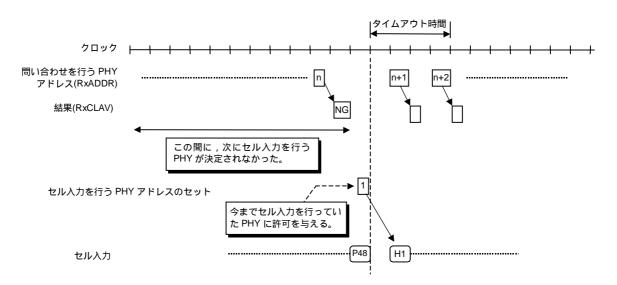

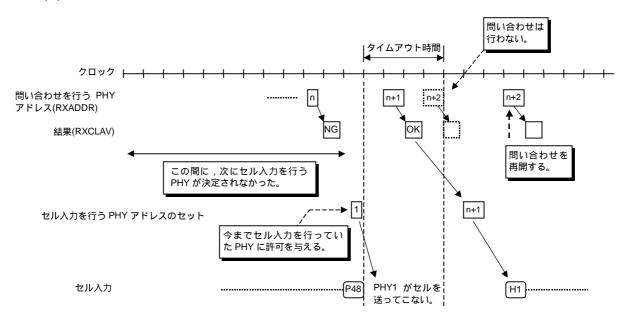

3.2.2 セル出力時のポーリング ... 46 3.2.3 セル入力時のポーリング ... 52

3.2 ポ・リング ... 44

3.3 ヘッダ変換 ... 58

3.2.1 ポ・リング概要 ... 44

#### 9

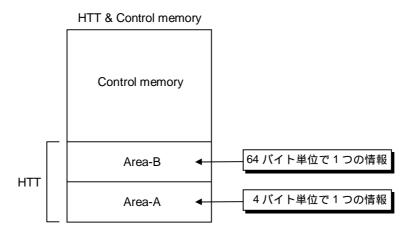

|     | 3.3.1  | HTT ( ヘッダ変換テーブル ) メモリ・マップ 58                                 |

|-----|--------|--------------------------------------------------------------|

|     | 3.3.2  | 概 要 59                                                       |

|     | 3.3.3  | HTT の形式 62                                                   |

|     | 3.3.4  | HTT へのアクセス方法 65                                              |

|     | 3.3.5  | ヘッダ変換の流れ 70                                                  |

|     | 3.3.6  | RM セルの際の HTT へのアクセス 74                                       |

| 3.4 | キュ     | 制御 77                                                        |

|     | 3.4.1  | シングルキャスト 77                                                  |

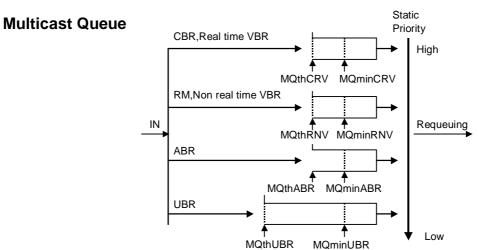

|     | 3.4.2  | マルチキャスト 78                                                   |

|     | 3.4.3  | 輻輳制御 79                                                      |

|     | 3.4.4  | クラス別セル廃棄 84                                                  |

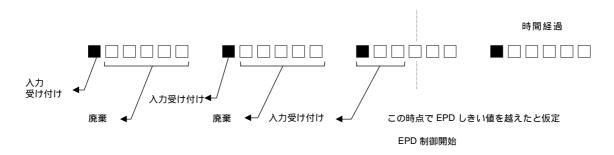

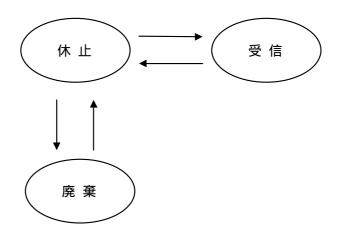

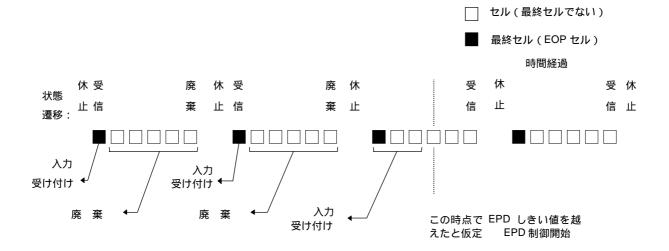

|     | 3.4.5  | EPD ( Early Packet Discard ) 85                              |

|     | 3.4.6  | PPD 制御(Partial Packet Discard) 87                            |

|     | 3.4.7  | 最小キュー長 88                                                    |

| 3.5 | ABF    | R 輻輳制御 91                                                    |

|     | 3.5.1  | EFCI (Explicit Forward Congestion Indicator) 91              |

|     | 3.5.2  | RM セル CI/NI マージング (Resource Management Cell CI/NI Congestion |

|     |        | Indication Marking ) 91                                      |

|     | 3.5.3  | RM セル・マージ(Resource Management Cell Merge) 92                 |

| 3.6 | WF     | Q(Weighted Fairness Queue) 93                                |

|     | 3.6.1  | 概 要 93                                                       |

|     | 3.6.2  | 使用するカウンタ,フラグ 93                                              |

| 3.7 | 'ピー    | ク・レート・シェーピング機能 96                                            |

|     | 3.7.1  | 概 要 96                                                       |

|     | 3.7.2  | 詳 細 98                                                       |

| 3.8 | 連続     | 送信 102                                                       |

| 3.9 | 割り     | 込み要求 106                                                     |

|     | 3.9.1  | パリティ・エラー 106                                                 |

|     | 3.9.2  | 入力ポート・オーバラン 106                                              |

|     | 3.9.3  | キュー・ポインタ・エラー 106                                             |

|     | 3.9.4  | キャスト・カウンタ・エラー 107                                            |

|     | 3.9.5  | セル・バッファ・メモリ不足 107                                            |

|     | 3.9.6  | コントロール・メモリ不足 107                                             |

|     | 3.9.7  | HEC/CRC エラー 108                                              |

|     | 3.9.8  | ヘッダ変換エラー 108                                                 |

|     | 3.9.9  | バッファしきい値越え 109                                               |

|     | 3 0 10 | カウント・オーバ給出 109                                               |

| 3.1         | 0 モニ   | タリング 110                                            |

|-------------|--------|-----------------------------------------------------|

|             | 3.10.1 | モニタ・レジスタ 110                                        |

|             | 3.10.2 | しきい値越えによるセル廃棄カウント 110                               |

|             | 3.10.3 | ヘッダ変換エラーによるセル廃棄カウント 111                             |

|             |        | HEC エラー , CRC エラーよるセル廃棄カウント 111                     |

|             |        | コントロール / セル・バッファ・メモリ不足によるセル廃棄カウント 112               |

|             |        | 受信セル数のカウント 112                                      |

| 3.1         |        | <b>イクロプロセッサ・インタフェース 113</b>                         |

|             |        | I/O マッピング,メモリ・マッピング 114                             |

|             |        | 32 ビット多重型同期バス (HSEL = Low) 117                      |

| 2.4         |        | 16 ビット分離型非同期バス(HSEL = High) 119                     |

| 3.1         |        | 『メモリ・インタフェース 122                                    |

|             |        | HTT & コントロール・メモリ・インタフェース 122<br>セル・バッファ・インタフェース 123 |

|             | 3.12.2 | ピル・バッファ・インタフェース 123                                 |

| <u>~~</u>   | ᆂᅁ     | 1 >> 7 A 407                                        |

| <b>第4</b> 早 | 名      | レジスタ 127                                            |

|             |        |                                                     |

|             |        | <b>スタ一覧 127</b>                                     |

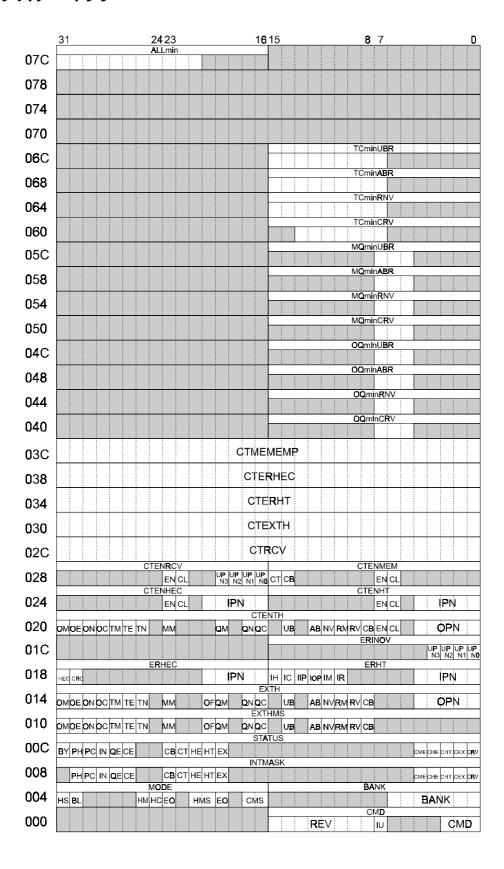

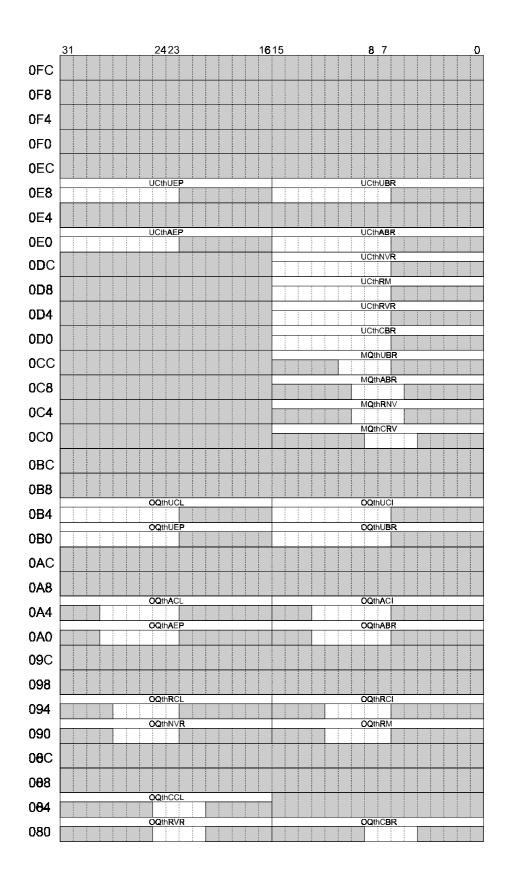

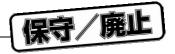

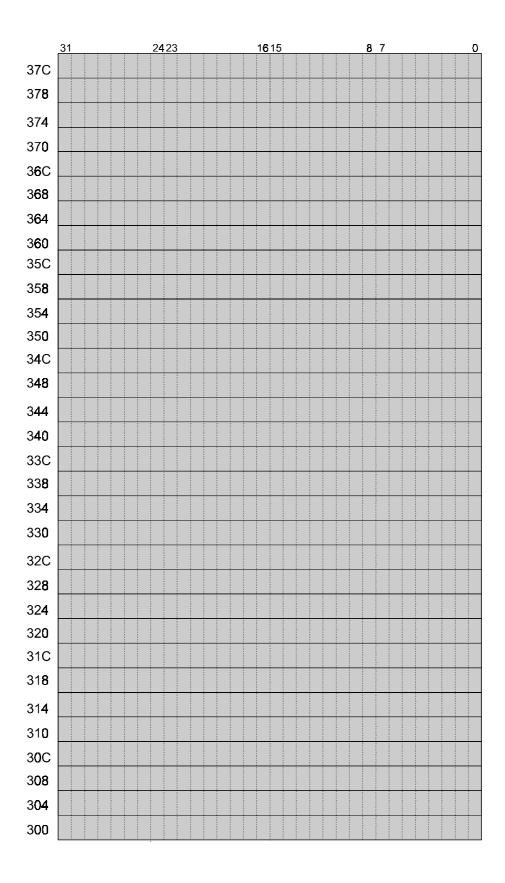

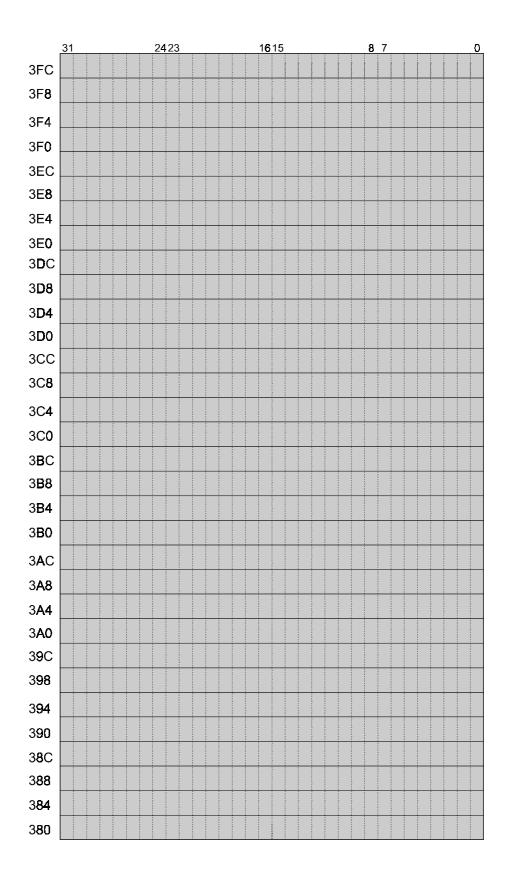

|             |        | スタ・マップ 129                                          |

| 4.3         | 3 レジス  | <b>く夕機能説明 137</b>                                   |

|             | 4.3.1  | コマンド・レジスタ (0000h) 137                               |

|             | 4.3.2  | メモリ・バンク・レジスタ(0004h) 138                             |

|             | 4.3.3  | メモリ・モード・レジスタ (0006h) 138                            |

|             | 4.3.4  | 割り込みマスク・レジスタ (0008h) 140                            |

|             | 4.3.5  | ステータス・レジスタ(000Ch) 141                               |

|             | 4.3.6  | しきい値越え廃棄表示マスク・レジスタ(0010h) 143                       |

|             | 4.3.7  | しきい値越え廃棄表示レジスタ(0014h) 143                           |

|             | 4.3.8  | ヘッダ変換エラー廃棄表示レジスタ(0018h) 146                         |

|             | 4.3.9  | HEC/CRC エラー廃棄表示レジスタ(001Ah) 148                      |

|             | 4.3.10 | 入力ポート・オーバラン・エラー廃棄表示レジスタ(001Ch) 149                  |

|             |        | しきい値越え廃棄セル・カウント・イネーブル・レジスタ(0020h) 150               |

|             |        | ヘッダ変換エラー廃棄セル・カウント・イネーブル・レジスタ (0024h) 151            |

|             |        | HEC/CRC エラー廃棄セル・カウント・イネーブル・レジスタ (0026h) 152         |

|             |        |                                                     |

|             | 4.3.14 | コントロール / セル・バッファ・メモリ不足廃棄セル・カウント・イネーブル・              |

レジスタ(0028h) ... 153

| 4.3.15 | 受信セル・カウント・イネーブル・レジスタ(002Ah) 154                           |

|--------|-----------------------------------------------------------|

| 4.3.16 | 受信セル・カウント・レジスタ(002Ch) 155                                 |

| 4.3.17 | しきい値越え廃棄セル・カウント・レジスタ(0030h) 156                           |

| 4.3.18 | ヘッダ変換エラー廃棄セル・カウント・レジスタ(0034h) 157                         |

| 4.3.19 | HEC/CRC エラー廃棄セル・カウント・レジスタ(0038h) 158                      |

| 4.3.20 | コントロール / セル・バッファ・メモリ不足廃棄セル・カウント・レジスタ( 003Ch )             |

|        | 159                                                       |

| 4.3.21 | 出力キュー最小しきい値レジスタ(0040h, 0044h, 0048h, 004Ch) 160           |

| 4.3.22 | マルチキャスト・キュー最小しきい値レジスタ(0050h, 0054h, 0058h, 005Ch)         |

|        | 161                                                       |

| 4.3.23 | TC(Total Cell)カウンタ最小しきい値レジスタ(0060h, 0064h, 0068h, 006Ch)  |

|        | 162                                                       |

| 4.3.24 | 総セル数最小しきい値レジスタ(007Eh) 163                                 |

| 4.3.25 | 出力キュー最大しきい値レジスタ(0080h, 0082h, 0090h, 0092h, 00A0h, 00B0h) |

|        | 164                                                       |

| 4.3.26 | 出力キューEPD しきい値レジスタ(00A2, 00B2h) 165                        |

| 4.3.27 | 出力キューEFCI しきい値レジスタ(0094h, 00A4h, 00B4h) 166               |

| 4.3.28 | 出力キューCLP しきい値レジスタ(0086h, 0096h, 00A6h, 00B6h) 167         |

| 4.3.29 | マルチキャスト・キュー最大しきい値レジスタ ( 00C0h, 00C4h, 00C8h, 00CCh )      |

|        | 168                                                       |

| 4.3.30 | UC(Used Cell)カウンタ最大しきい値レジスタ(00D0h, 00D4h,00D8h,           |

|        | 00DCh, 00E0h, 00E8h) 169                                  |

| 4.3.31 | UC(Used Cell)カウンタ EPD しきい値レジスタ(00E2h, 00EAh) 170          |

| 4.3.32 | ポート・コンフィギュレーション・レジスタ 171                                  |

| 4.3.33 | クラス優先制御レジスタ 173                                           |

| 4.3.34 | 周期カウント・レジスタ(01FCh) 174                                    |

| 4.3.35 | ヘッダ変換コンフィギュレーション・レジスタ 175                                 |

|        |                                                           |

# 第5章 JTAG パウンダリ・スキャン ... 177

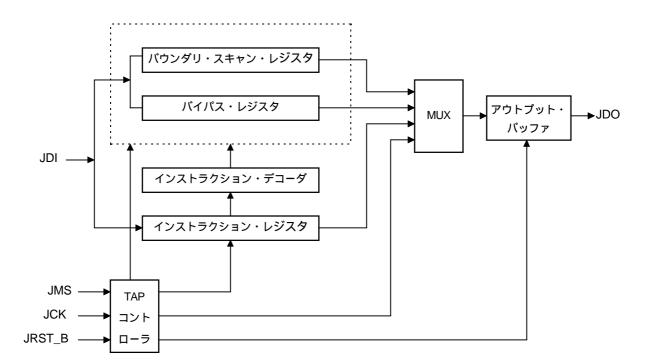

- 5.1 特 徵 ... 177

- 5.2 パウンダリ・スキャン回路内部構成 ... 178

- 5.2.1 インストラクション・レジスタ (Instruction register) ... 178

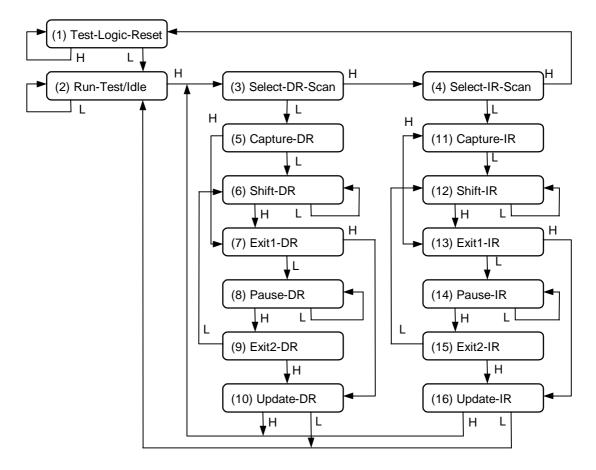

- 5.2.2 TAP コントローラ (Test Access Port controller) ... 179

- 5.2.3 バイパス・レジスタ (Bypass register) ... 179

| 5.2.4   | バウンダリ・スキャン・レジスタ(Boundary Scan register) 180 |

|---------|---------------------------------------------|

| 5.3 端子树 | <b>幾能 179</b>                               |

| 5.3.1   | JCK 端子(JTAG Clock pin) 179                  |

| 5.3.2   | JMS 端子(JTAG Mode Select pin) 179            |

| 5.3.3   | JDI 端子(JTAG Data Input pin) 179             |

| 5.3.4   | JDO 端子(JTAG Data Output pin) 179            |

| 5.3.5   | JRST_B 端子(JTAG Reset pin) 179               |

| 5.4 動作説 | 胡 180                                       |

| 5.4.1   | TAP コントローラ 180                              |

| 5.4.2   | TAP コントローラ状態 180                            |

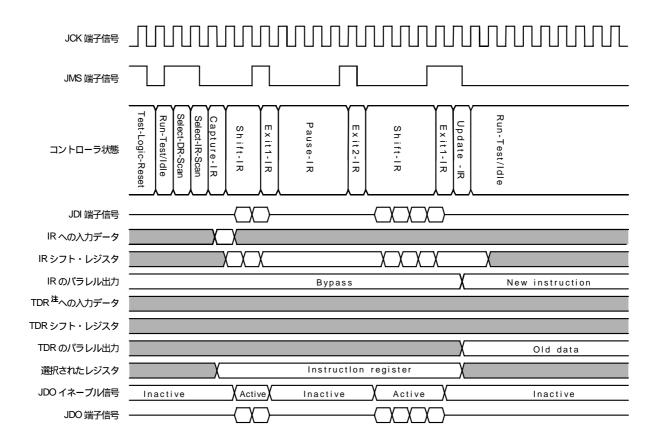

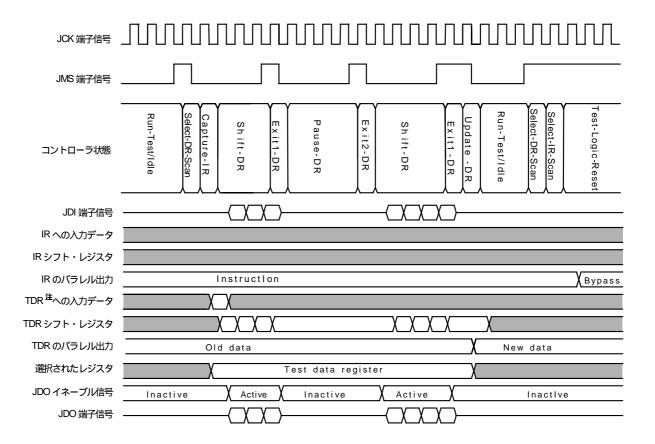

| 5.5 TAP | コントローラ動作 187                                |

| 5.6 TAP | コントローラの初期化 190                              |

| 5.7 イン  | ストラクション・レジスタ 190                            |

| 5.7.1   | BYPASS 命令 191                               |

| 5.7.2   | EXTEST 命令 191                               |

| 5.7.3   | バウンダリ・スキャン・データ・ビット定義 192                    |

|         |                                             |

| 第6章 使用制 | <b>则限事項 193</b>                             |

|         |                                             |

| 6.1 制限項 | 目 193                                       |

| 6.2 制限  | <b>事項説明 194</b>                             |

第7章 FAQ (Frequently Asked Questions) ... 203

# 図の目次 (1/2)

| 図番号    | タイトル , ページ                              |

|--------|-----------------------------------------|

| 3 - 1  | UTOPIA の受信インタフェース接続例 42                 |

| 3 - 2  | UTOPIA の送信インタフェース接続例 43                 |

| 3 - 3  | μPD98410 の構成要素 44                       |

| 3 - 4  | クロック関係 46                               |

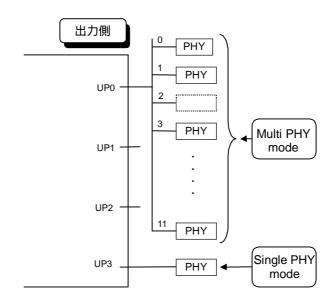

| 3 - 5  | シングル PHY モードとマルチ PHY モード 46             |

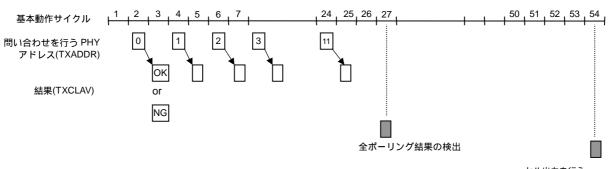

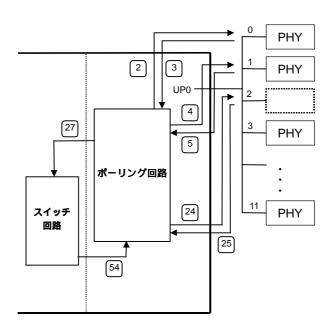

| 3 - 6  | ポーリング制御と基本動作サイクルの関係(マルチ PHY モード時) 47    |

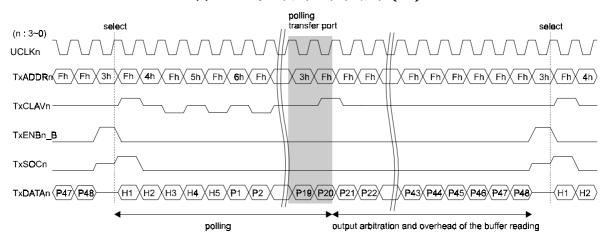

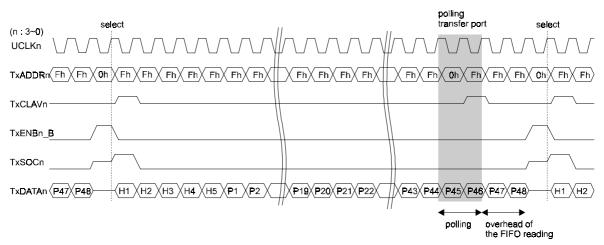

| 3 - 7  | セル出力中のポーリング動作 48                        |

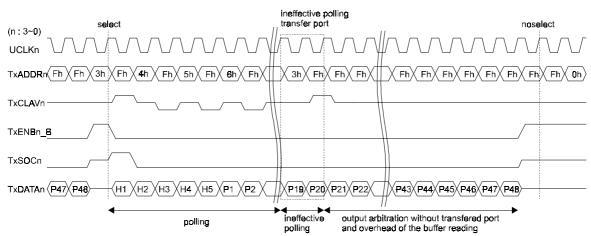

| 3 - 8  | セル出力中のポーリング動作 49                        |

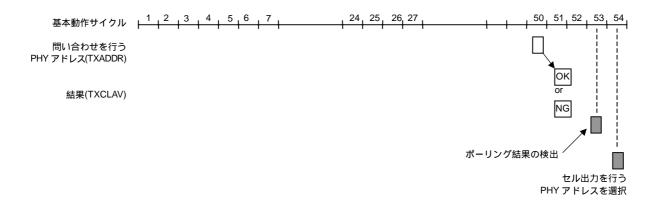

| 3 - 9  | ポーリング制御と基本動作サイクルの関係(シングル PHY モード時) 50   |

| 3 - 10 | 連続出力の制御 51                              |

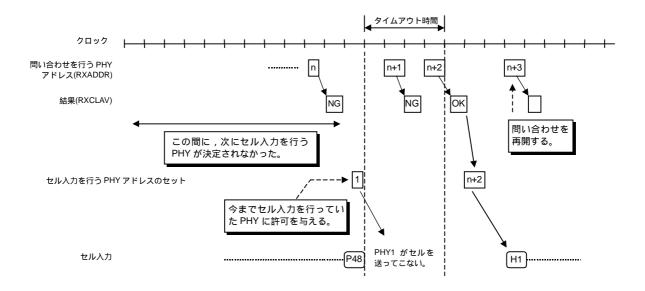

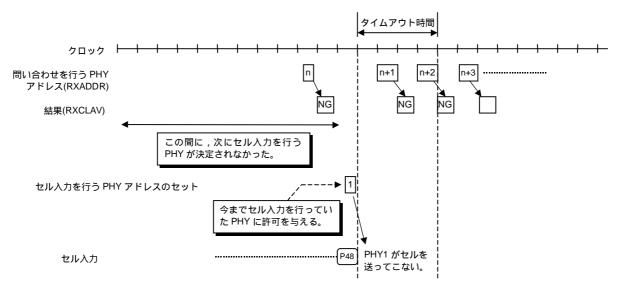

| 3 - 11 | セル入力時のポーリング基本動作 52                      |

| 3 - 12 | ポーリング制御と基本動作サイクルの関係(セル入力時) 52           |

| 3 - 13 | セル入力の基本タイミング 1 53                       |

| 3 - 14 | セル入力の基本タイミング 2 54                       |

| 3 - 15 | 連続入力における転送レートの低下 54                     |

| 3 - 16 | 連続入力の制御 55                              |

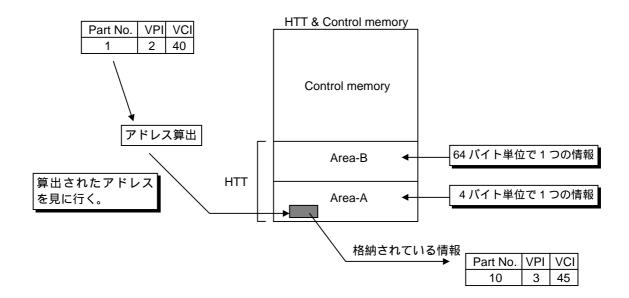

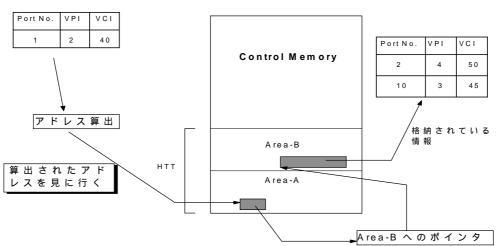

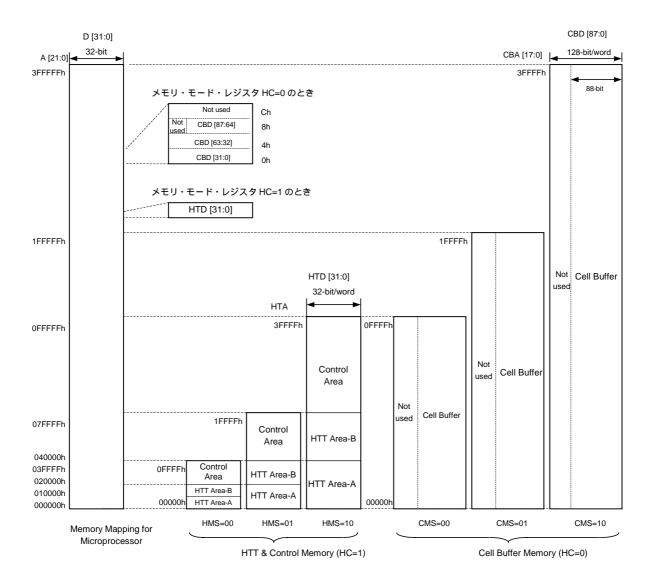

| 3 - 17 | HTT &コントロール・メモリ・マップ 58                  |

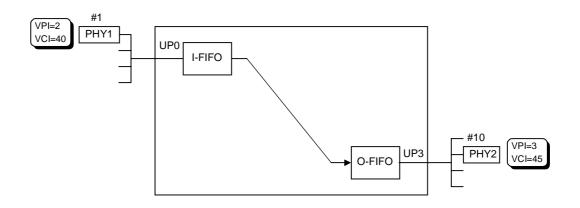

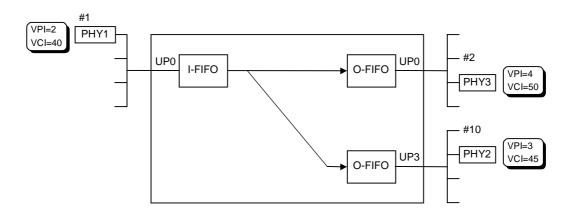

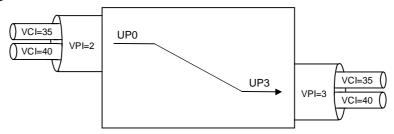

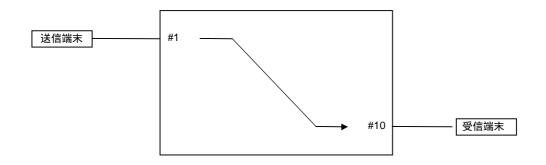

| 3 - 18 | シングルキャストの例 59                           |

| 3 - 19 | HTT ( ヘッダ変換テーブル ) 59                    |

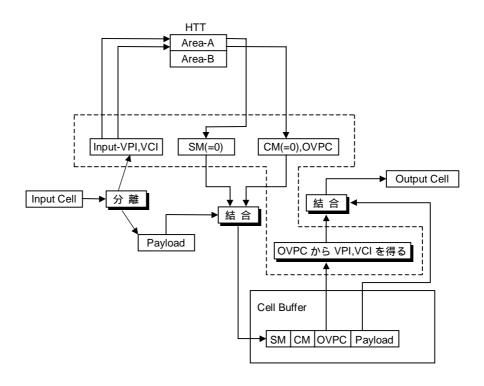

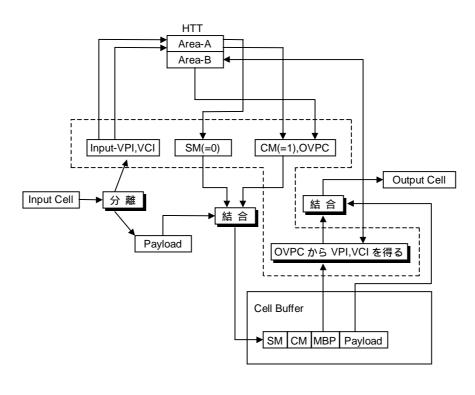

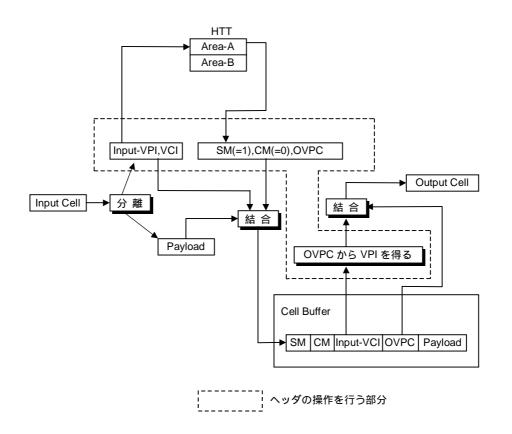

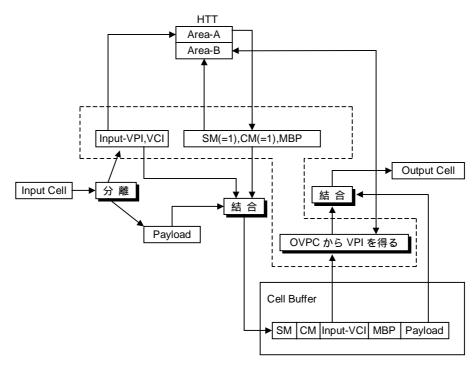

| 3 - 20 | シングルキャスト時のヘッダ変換情報の流れ 60                 |

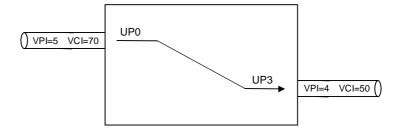

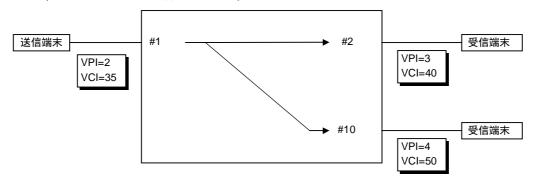

| 3 - 21 | マルチキャストの例 61                            |

| 3 - 22 | マルチキャスト時のヘッダ変換情報の流れ 61                  |

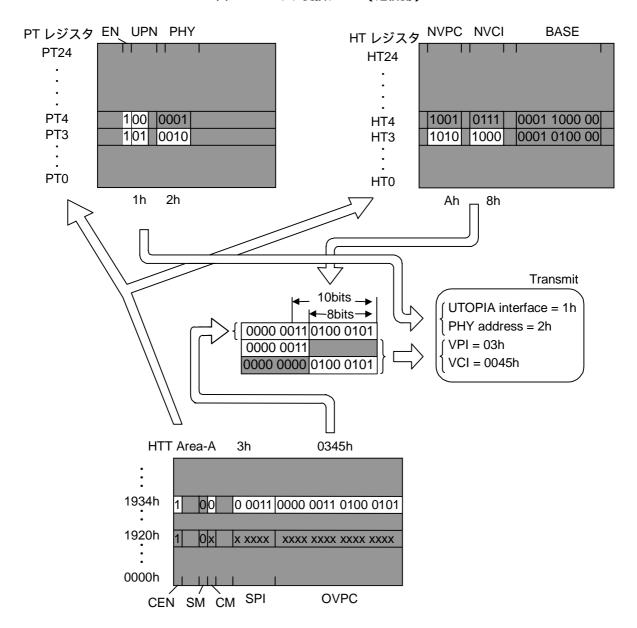

| 3 - 23 | HTT Area-A フォーマット 62                    |

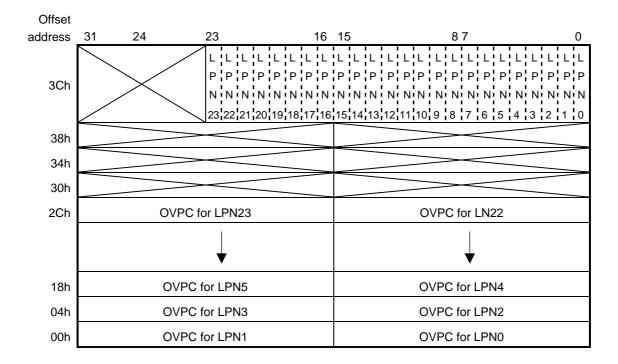

| 3 - 24 | HTT Area-B フォーマット 64                    |

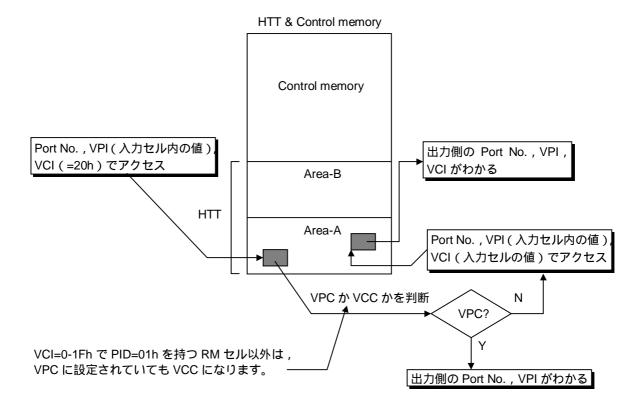

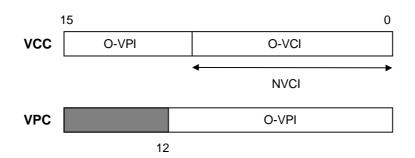

| 3 - 25 | VP コネクションと VC コネクション 65                 |

| 3 - 26 | VPC と VCC の HTT へのアクセスの違い(シングルキャスト時) 67 |

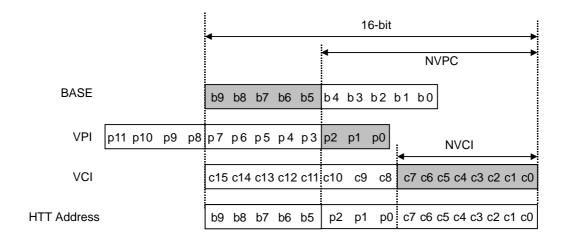

| 3 - 27 | HTT アドレスの求め方 68                         |

| 3 - 28 | OVPC の設定形式 69                           |

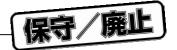

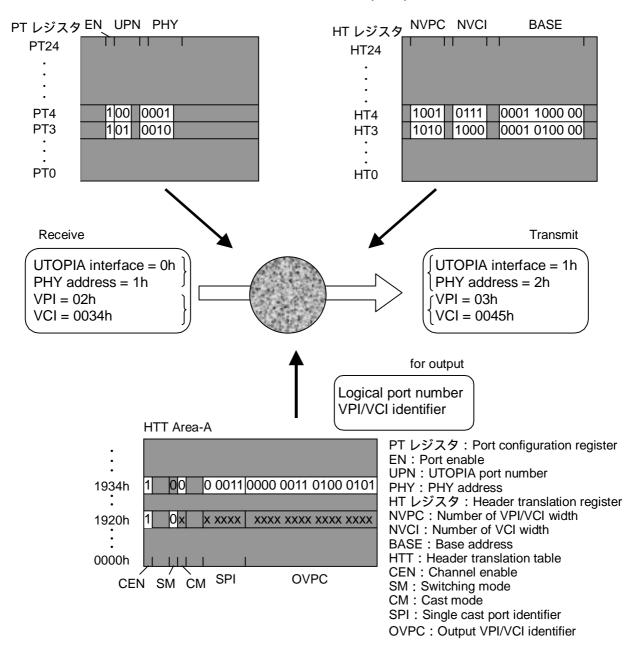

| 3 - 29 | VCS,シングルキャスト時のヘッダ変換の流れ 70               |

| 3 - 30 | VCC,マルチキャスト時のヘッダ変換の流れ 71                |

| 3 - 31 | VPC,シングルキャスト時のヘッダ変換の流れ 72               |

| 3 - 32 | VPC,マルチキャスト時のヘッダ変換の流れ 73                |

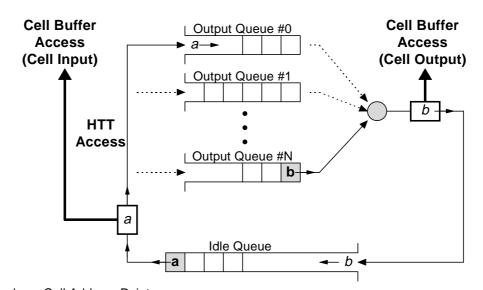

| 3 33   | カル・アドレスのキューイング(シングルキャスト) 77             |

# 図の目次(2/2)

| 図番号    | タイトル , ページ                               |

|--------|------------------------------------------|

| 3 - 34 | セル・アドレスのキューイング(マルチキャスト) 78               |

| 3 - 35 | サービス・クラス別キューとカウンタ 81                     |

| 3 - 36 | EPD 制御が有効の場合 85                          |

| 3 - 37 | EPD 制御有効の場合の状態遷移 86                      |

| 3 - 38 | EPD 制御による状態遷移 86                         |

| 3 - 39 | PPD 制御の状態遷移 88                           |

| 3 - 40 | RM Cell 構成 (ATM Forum TM Ver. 4.0) 91    |

| 3 - 41 | 出力キューとカウンタ 93                            |

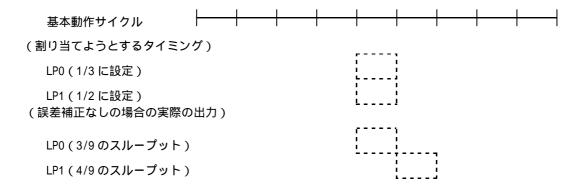

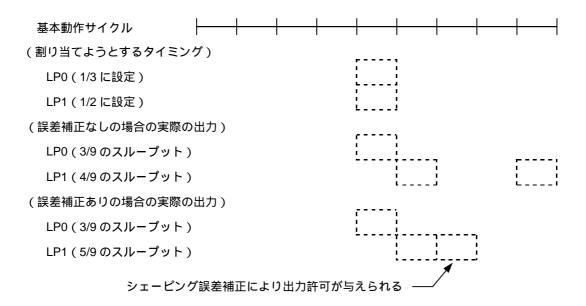

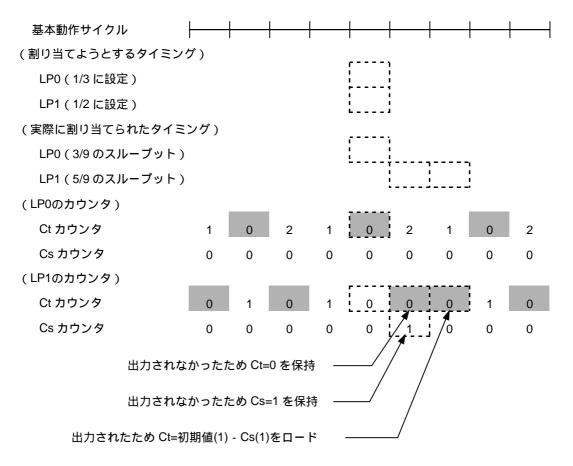

| 3 - 42 | 内部基本サイクルと各 UTOPIA インタフェースの出力許可タイミング関係 96 |

| 3 - 43 | ● PD98410 と端末との接続例 97                    |

| 3 - 44 | ポーリング・タイミング(a) 103                       |

| 3 - 45 | ポーリング・タイミング(b) 104                       |

| 3 - 46 | ポーリング・タイミング(c) 105                       |

| 3 - 47 | I/O レジスタ・マッピング 115                       |

| 3 - 48 | HTT & コントロール・メモリ,セル・バッファ・メモリ・マッピング 116   |

| 3 - 49 | 32 ビット多重型同期バスのアクセス・タイミング 118             |

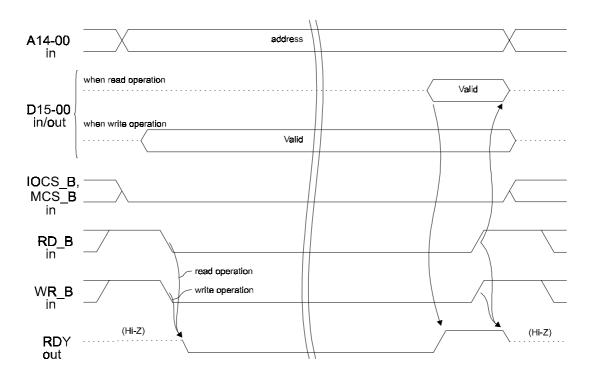

| 3 - 50 | 16 ビット分離型非同期バスのアクセス・タイミング 120            |

| 3 - 51 | 16 ビット分離型非同期バスのメモリ・マップ 121               |

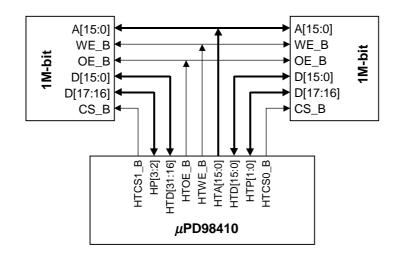

| 3 - 52 | HTT &コントロール・メモリ接続例(最小構成) 122             |

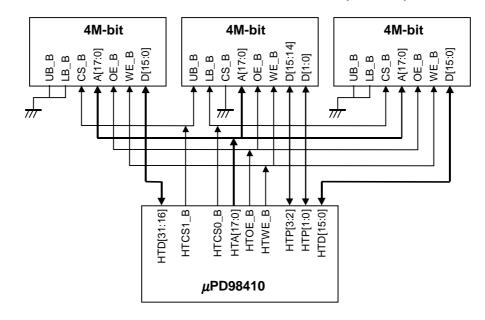

| 3 - 53 | HTT &コントロール・メモリ接続例(最大構成) 123             |

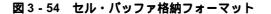

| 3 - 54 | セル・バッファ格納フォーマット 124                      |

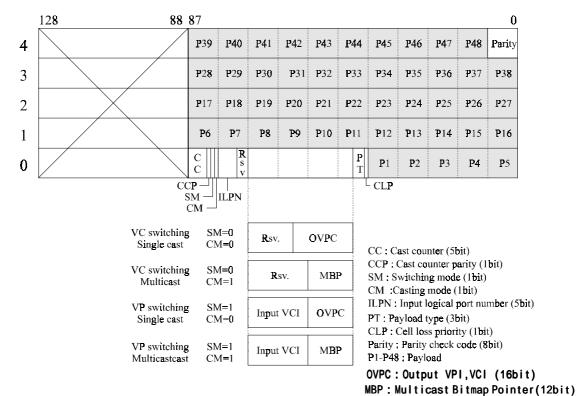

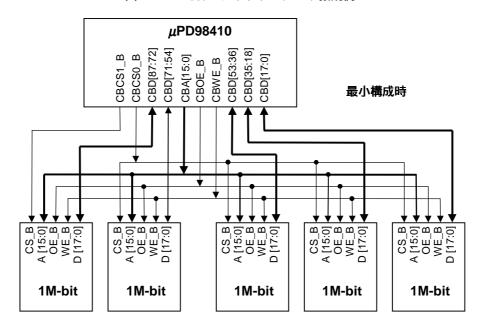

| 3 - 55 | セル・バッファ・メモリ接続例 125                       |

|        |                                          |

| 5 - 1  | バウンダリ・スキャン回路ブロック図 178                    |

| 5 - 2  | TAP コントローラの状態 180                        |

| 5 - 3  | コントローラ状態での動作タイミング 181                    |

| 5 - 4  | テスト・ロジックの動作(インストラクション・スキャン) 188          |

| 5 - 5  | テスト・ロジックの動作(データ・スキャン) 189                |

# 表の目次

| 表番号    | タイトル , ページ                                               |

|--------|----------------------------------------------------------|

|        |                                                          |

| 2 - 1  | 受信インタフェース信号 30                                           |

| 2 - 2  | 送信インタフェース信号 32                                           |

| 2 - 3  | HTT & コントロール・メモリ・インタフェース信号 34                            |

| 2 - 4  | セル・バッファ・メモリ・インタフェース信号 35                                 |

| 2 - 5  | マイクロプロセッサ・インタフェース 36                                     |

| 2 - 6  | 32 ビット多重型同期インタフェース 36                                    |

| 2 - 7  | 16 ビット分離型非同期インタフェース 37                                   |

| 2 - 8  | JTAG インタフェース信号 38                                        |

| 2 - 9  | その他のインタフェース信号 38                                         |

| 2 - 10 | 未使用端子の処理方法 39                                            |

| 2 - 11 | リセット時の端子の状態 40                                           |

|        |                                                          |

| 3 - 1  | 最大転送速度と UTOPIA クロック・レート 41                               |

| 3 - 2  | 総セル数に関するセル廃棄しきい値 84                                      |

| 3 - 3  | 出力キュー長に関するセル廃棄しきい値 84                                    |

| 3 - 4  | マルチキャスト・キュー長に関するセル廃棄しきい値 85                              |

| 3 - 5  | 総セル数(Used Cell Counter)に関する最小キュー長 88                     |

| 3 - 6  | クラス別総セル数(Total Cell Counter for each class)に関する最小キュー長 88 |

| 3 - 7  | 出力キュー長に関する最小キュー長 89                                      |

| 3 - 8  | マルチキャスト・キュー長に関する最小キュー長 89                                |

| 3 - 9  | しきい値の分類と名称 90                                            |

| 3 - 10 | 出力キュー長に関する EFCI しきい値 91                                  |

| 3 - 11 | 出力キュー長に関する CI しきい値 92                                    |

| 3 - 12 | 接続する PHY とµPD98410 へのモード設定 102                           |

| 3 - 13 | マイクロプロセッサ・インタフェース端子 113                                  |

| 3 - 14 | アクセス対象の選択 114                                            |

| 3 - 15 | アクセス対象別のアクセス・ビット幅 114                                    |

|        |                                                          |

| 5 - 1  | それぞれのコントローラ状態における動作 187                                  |

|        |                                                          |

| 7 - 1  | ヘッダ変換フロー(全体) 211                                         |

| 7 - 2  | ヘッダ変換フロー(受信側) 212                                        |

| 7 - 3  | ヘッダ変換フロー ( 送信側 ) 213                                     |

| 7 - 4  | HT レジスタ設定例 214                                           |

7-5 HTT メモリ・マッピング例 ... 215

## 第1章 概 説

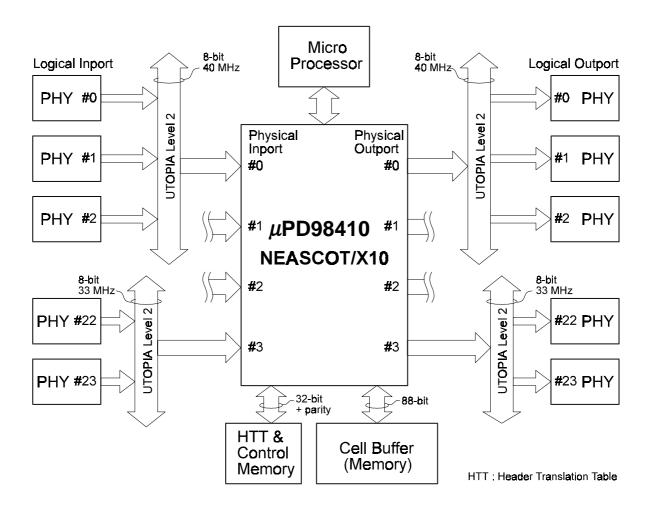

$\mu$ PD98410(NEASCOT-X10)は,ATM スイッチ機能を 1 チップに搭載した LSI で,4 つの UTOPIA Level2 インタフェースを持ち,マルチ PHY 接続を利用して 24 x 24 回線をスイッチングできます。また,共有バッファ方式 ノンブロッキング型スイッチを採用し,外部接続の SRAM をセルのバッファリングに使用して,スイッチ容量 1.2Gbps を実現します。

### 1.1 特 徵

ATM FORUM UNI Version 3.1 & 4.0 に準拠

1 チップですべてのスイッチ機能を実現

ノンブロッキングでスイッチ容量 1.2 Gbps を実現

4 つの UTOPIA level2 (8 ビット / 40MHz ) インタフェ - スを介して, 24 の論理ポ - トのスイッチングが可能

マルチスピ - ド対応 (155Mbps, 52Mbps, 25Mbps, etc.)

16K/32K/64K VP/VC と 1K/2K/4K マルチキャスト VP/VC をサポ・ト

標準 SRAM を使用した共有バッファ・ア・キテクチャ

セル·バッファ容量 12.8K/25.6K/51.2K セル

4 つの QOS クラス (CBR, VBR, ABR, UBR)をサポ・ト

ABR トラフィック制御 (バイナリ・モ・ド)

EPD (Early Packet Discard), PPD (Partial Packet Discard)をサポート

+3.3V 単一電源(+5V TTL レベル信号と直接接続も可能)

テスト機能: JTAG (IEEE 1149.1) サポ-ト

## 1.2 オーダ情報

オーダ名称 パッケージ

μPD98410S2-K6

580 ピン・プラスチック BGA (45 x 45 mm)

## 1.3 システム構成例(用途)

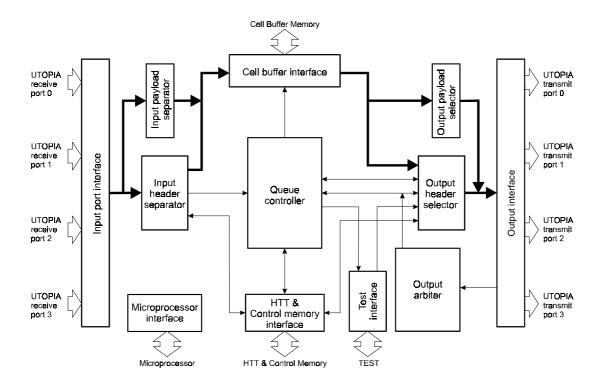

$\mu$ PD98410 は,マイクロプロセッサとセル・バッファ格納用 SRAM およびヘッダ変換テーブル(HTT) / コントロール情報格納用 SRAM を下図のように接続して,ATM レイヤにおけるセル・スイッチング機能を実現できます。

# 1.4 プロック図

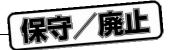

### 1.5 端子構成図

### 第2章 端子機能

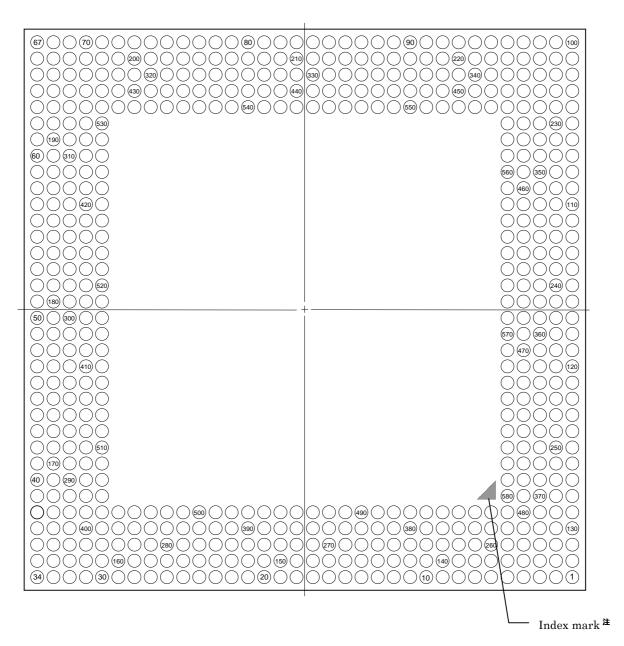

### 2.1 端子概要図 (Bottom View )

580 ピン BGA パッケージ

注 Index mark は, Top View に印されています。

#### 端子名称

(1) Power (4) CPU Interface

V<sub>DD</sub> : Supply Voltage HSEL : Host Bus Mode Select

GND : Ground IOCS\_B : I/O Chip Select

MCS\_B : Memory Chip Select

( 2 ) UTOPIA RDY\_B,RDY: I/O Ready , Memory Ready

RXADDR\*3-RXADDR\*0 : Receive Address INT : Interrupt Request

RXDATA\*7-RXDATA\*0 : Receive Data Bus HCLK : Host Clock

RXSOC3-RXSOC0 : Receive Start of Cell AD31-AD0 : Address and Data

RXENB3\_B-RXENB0\_B: Receive Enable Data Transfers R/W\_B: Read/Write

RXCLAV3-RXCLAV0 : Receive Cell Buffer Available UWE\_B : Upper Word Enable

UCLK3-UCLK0 : UTOPIA Clock A15-A0 : Address

TXADDR\*3-TXADDR\*0 : Transmit Address D15-D0 : Data

TXDATA\*7-TXDATA\*0 : Transmit Data Bus WR\_B : Write Strobe

TXSOC3-TXSOC0 : Transmit Start of Cell RD\_B : Read Strobe

TXENB3 B-TXENB0 B : Transmit Enable Data

TXCLAV3-TXCLAV0 : Transmit Cell Buffer Available ( 5 ) JTAG

JDI : JTAG Data Input

( 3 ) Memory Interface JDO : JTAG Data Output

HTA17-HTA0 : HTT Memory Address JCK : JTAG Data Clock

HTD31-HTD0 : HTT Memory Data Bus JMS : JTAG Mode Select

HTP3-HTP0 : HTT Memory Data Bus Parity JRST\_B : JTAG Reset

HTCS1\_B,HTCS0\_B: HTT Memory Chip Select

HTWE\_B : HTT Memory Write Enable (6) Other

HTOE\_B : HTT Memory Output Enable SWCLK : System Clock

CBA17-CBA0 : Cell Buffer Memory Address RESET\_B : Hardware Reset

CBD87-CBD0 : Cell Buffer Memory Data Bus IC : Internal Connected

CBWE\_B : Cell Buffer Memory Write Enable PU : Pull-up

CBOE\_B : Cell Buffer Memory Output Enable

\*=0-3

# 2.2 端子配置

(1/6)

|      |          |     |      |          |     |      |           | (1/6) |

|------|----------|-----|------|----------|-----|------|-----------|-------|

| 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O | 端子番号 | 端子名       | I/O   |

| 1    | GND      |     | 37   | CBD72    | I/O | 73   | RXDATA05  | I     |

| 2    | GND      |     | 38   | CBD69    | I/O | 74   | $V_{DD}$  |       |

| 3    | IC       | 0   | 39   | CBD66    | I/O | 75   | GND       |       |

| 4    | IC       | 0   | 40   | CBD63    | I/O | 76   | RXCLAV0   | I     |

| 5    | CG       | I   | 41   | IC       | 0   | 77   | $V_{DD}$  |       |

| 6    | IC       | 0   | 42   | CBD58    | I/O | 78   | TXADDR01  | 0     |

| 7    | JRST_B   | I   | 43   | CBD56    | I/O | 79   | TXENB0_B  | 0     |

| 8    | RXDATA36 | I   | 44   | CBD51    | I/O | 80   | TXDATA04  | 0     |

| 9    | RXDATA32 | I   | 45   | CBD49    | I/O | 81   | TXDATA00  | 0     |

| 10   | IC       | 0   | 46   | CBD46    | I/O | 82   | RXDATA26  | I     |

| 11   | RXSOC3   | I   | 47   | CBWE_B   | 0   | 83   | $V_{DD}$  |       |

| 12   | RXADDR31 | 0   | 48   | CBA17    | 0   | 84   | RXDATA25  | I     |

| 13   | TXADDR31 | 0   | 49   | GND      |     | 85   | GND       |       |

| 14   | TXENB3_B | 0   | 50   | CBA13    | 0   | 86   | GND       |       |

| 15   | $V_{DD}$ |     | 51   | IC       | 0   | 87   | RXCLAV2   | - 1   |

| 16   | TXDATA32 | 0   | 52   | CBA9     | 0   | 88   | RXADDR21  | 0     |

| 17   | TXDATA30 | 0   | 53   | CBA7     | 0   | 89   | TXADDR21  | 0     |

| 18   | TXDATA31 | 0   | 54   | CBA4     | 0   | 90   | TXCLAV2   | I     |

| 19   | RXDATA17 | I   | 55   | CBA0     | 0   | 91   | GND       |       |

| 20   | RXDATA13 | 1   | 56   | CBD41    | I/O | 92   | TXDATA23  | 0     |

| 21   | RXDATA10 | I   | 57   | CBD37    | I/O | 93   | TXDATA20  | 0     |

| 22   | RXENB1_B | 0   | 58   | CBD35    | I/O | 94   | IOCS_B    | I     |

| 23   | $V_{DD}$ |     | 59   | CBD30    | I/O | 95   | RDY_B/RDY | 0     |

| 24   | RXADDR10 | 0   | 60   | $V_{DD}$ |     | 96   | CG        | I     |

| 25   | GND      |     | 61   | CBD24    | I/O | 97   | CG        | I     |

| 26   | $V_{DD}$ |     | 62   | CBD20    | I/O | 98   | IC        | 0     |

| 27   | TXDATA15 | 0   | 63   | CBD17    | I/O | 99   | GND       |       |

| 28   | TXDATA11 | 0   | 64   | CBD15    | I/O | 100  | GND       |       |

| 29   | CBD86    | I/O | 65   | GND      |     | 101  | GND       |       |

| 30   | CBD84    | I/O | 66   | GND      |     | 102  | IC        | 0     |

| 31   | CBD80    | I/O | 67   | GND      |     | 103  | $V_{DD}$  |       |

| 32   | $V_{DD}$ |     | 68   | GND      |     | 104  | AD18/ A2  | I/O   |

| 33   | GND      |     | 69   | CBD10    | I/O | 105  | AD14/ D14 | I/O   |

| 34   | GND      |     | 70   | CBD7     | I/O | 106  | AD10/ D10 | I/O   |

| 35   | GND      |     | 71   | CBD4     | I/O | 107  | AD6/ D6   | I/O   |

| 36   | CBD74    | I/O | 72   | CBD2     | I/O | 108  | AD3/ D3   | I/O   |

| _    |          |     |      |          |     | _    |           |       |

(2/6)

|      |                 |     | ı    |          |     | Į.   |          | (2/6) |

|------|-----------------|-----|------|----------|-----|------|----------|-------|

| 端子番号 | 端子名             | I/O | 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O   |

| 109  | AD1/D1          | I/O | 146  | TXDATA36 | 0   | 183  | CBA2     | 0     |

| 110  | HTA14           | 0   | 147  | TXDATA33 | 0   | 184  | CBD42    | I/O   |

| 111  | $V_{DD}$        |     | 148  | TXDATA34 | 0   | 185  | CBD38    | I/O   |

| 112  | HTA9            | 0   | 149  | GND      |     | 186  | $V_{DD}$ |       |

| 113  | $V_{DD}$        |     | 150  | RXDATA15 | 1   | 187  | CBD33    | I/O   |

| 114  | GND             |     | 151  | RXDATA12 | 1   | 188  | CBD28    | I/O   |

| 115  | HTCS1_B         | 0   | 152  | $V_{DD}$ |     | 189  | CBD26    | I/O   |

| 116  | GND             |     | 153  | RXCLAV1  | 1   | 190  | CBD23    | I/O   |

| 117  | HTCS0_B         | 0   | 154  | RXADDR11 | 0   | 191  | GND      |       |

| 118  | $V_{DD}$        |     | 155  | TXADDR12 | 0   | 192  | $V_{DD}$ |       |

| 119  | HTD29           | I/O | 156  | TXCLAV1  | I   | 193  | CBD13    | I/O   |

| 120  | HTD26           | I/O | 157  | TXDATA17 | 0   | 194  | CBD12    | I/O   |

| 121  | HTD23           | I/O | 158  | TXDATA13 | 0   | 195  | GND      |       |

| 122  | HTD20           | I/O | 159  | TXDATA10 | 0   | 196  | CBD9     | I/O   |

| 123  | HTD16           | I/O | 160  | $V_{DD}$ |     | 197  | CBD8     | I/O   |

| 124  | HTD15           | I/O | 161  | CBD82    | I/O | 198  | IC       | 0     |

| 125  | HTD10           | I/O | 162  | CBD78    | I/O | 199  | $V_{DD}$ |       |

| 126  | $V_{DD}$        |     | 163  | CBD77    | I/O | 200  | RXDATA06 | I     |

| 127  | HTD5            | I/O | 164  | GND      |     | 201  | RXDATA03 | 1     |

| 128  | HTD2            | I/O | 165  | CBD76    | I/O | 202  | RXDATA01 | I     |

| 129  | SWCLK           | I   | 166  | CBD73    | I/O | 203  | RXSOC0   | I     |

| 130  | $V_{DD}$        |     | 167  | $V_{DD}$ |     | 204  | RXADDR02 | 0     |

| 131  | GND             |     | 168  | CBD67    | I/O | 205  | TXADDR03 | 0     |

| 132  | GND             |     | 169  | IC       | 0   | 206  | TXCLAV0  | 1     |

| 133  | GND             |     | 170  | CBD62    | I/O | 207  | TXDATA06 | 0     |

| 134  | CG              | 1   | 171  | CBD59    | I/O | 208  | TXDATA02 | 0     |

| 135  | CG              | 1   | 172  | CBD57    | I/O | 209  | $V_{DD}$ |       |

| 136  | IC              | 0   | 173  | CBD53    | I/O | 210  | RXDATA27 |       |

| 137  | $V_{DD}$        |     | 174  | $V_{DD}$ |     | 211  | RXDATA23 | I     |

| 138  | GND             |     | 175  | GND      |     | 212  | RXDATA21 | I     |

| 139  | V <sub>DD</sub> |     | 176  | CBCS1_B  | 0   | 213  | RXENB2_B | 0     |

| 140  | RXDATA34        | 1   | 177  | $V_{DD}$ |     | 214  | RXADDR23 | 0     |

| 141  | RXDATA30        | 1   | 178  | CBA15    | 0   | 215  | TXADDR23 | 0     |

| 142  | V <sub>DD</sub> |     | 179  | CBOE_B   | 0   | 216  | TXADDR20 | 0     |

| 143  | RXADDR33        | 0   | 180  | CBA11    | 0   | 217  | TXENB2_B | 0     |

| 144  | TXADDR33        | 0   | 181  | $V_{DD}$ |     | 218  | TXDATA25 | 0     |

| 145  | TXCLAV3         | 1   | 182  | CBA6     | 0   | 219  | TXDATA22 | 0     |

(3/6)

|      |          |     | 1    | Ī        | 1   |      | I               | (3/6) |

|------|----------|-----|------|----------|-----|------|-----------------|-------|

| 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O | 端子番号 | 端子名             | I/O   |

| 220  | HCLK     | 1   | 256  | IC       | I/O | 293  | V <sub>DD</sub> |       |

| 221  | MCS_B    | I   | 257  | IC       | I/O | 294  | CBD54           | I/O   |

| 222  | R/W_B/   | 1   | 258  | GND      |     | 295  | CBD52           | I/O   |

|      | WR_B     |     | 259  | GND      |     | 296  | CBD48           | I/O   |

| 223  | AD31/A15 | I/O | 260  | JDI      | I   | 297  | CBD47           | I/O   |

| 224  | AD28/A12 | I/O | 261  | JCK      | I   | 298  | CBD45           | I/O   |

| 225  | AD27/A11 | I/O | 262  | RXDATA37 | I   | 299  | CBCS0_B         | 0     |

| 226  | GND      |     | 263  | RXDATA33 | I   | 300  | CBA16           | 0     |

| 227  | AD25/A9  | I/O | 264  | RXDATA31 | I   | 301  | CBA12           | 0     |

| 228  | AD22/A6  | I/O | 265  | RXENB3_B | 0   | 302  | CBA10           | 0     |

| 229  | AD20/A4  | I/O | 266  | RXADDR32 | 0   | 303  | CBA5            | 0     |

| 230  | AD16/A0  | I/O | 267  | RXADDR30 | 0   | 304  | GND             |       |

| 231  | AD12/D12 | I/O | 268  | TXADDR32 | 0   | 305  | CBA1            | 0     |

| 232  | AD8/D8   | I/O | 269  | TXSOC3   | 0   | 306  | GND             |       |

| 233  | $V_{DD}$ |     | 270  | TXDATA37 | 0   | 307  | CBD39           | I/O   |

| 234  | AD2/ D2  | I/O | 271  | $V_{DD}$ |     | 308  | CBD34           | I/O   |

| 235  | GND      |     | 272  | RXDATA14 | I   | 309  | GND             |       |

| 236  | HTA12    | 0   | 273  | GND      |     | 310  | CBD29           | I/O   |

| 237  | GND      |     | 274  | RXDATA11 | I   | 311  | CBD25           | I/O   |

| 238  | HTA6     | 0   | 275  | IC       | 0   | 312  | CBD21           | I/O   |

| 239  | HTA4     | 0   | 276  | RXSOC1   | 1   | 313  | CBD18           | I/O   |

| 240  | HTA1     | 0   | 277  | RXADDR13 | 0   | 314  | CBD14           | I/O   |

| 241  | HTA3     | 0   | 278  | TXADDR13 | 0   | 315  | CBD11           | I/O   |

| 242  | HTOE_B   | 0   | 279  | TXADDR10 | 0   | 316  | GND             |       |

| 243  | HTD31    | I/O | 280  | TXENB1_B | 0   | 317  | CBD5            | I/O   |

| 244  | HTD28    | I/O | 281  | TXDATA14 | 0   | 318  | CBD1            | I/O   |

| 245  | HTD24    | I/O | 282  | TXDATA12 | 0   | 319  | RXDATA07        | ı     |

| 246  | GND      |     | 283  | CBD85    | I/O | 320  | RXDATA04        | I     |

| 247  | HTD17    | I/O | 284  | GND      |     | 321  | RXDATA00        | ı     |

| 248  | $V_{DD}$ |     | 285  | CBD79    | I/O | 322  | RXENB0_B        | 0     |

| 249  | HTD13    | I/O | 286  | GND      |     | 323  | RXADDR01        | 0     |

| 250  | HTD8     | I/O | 287  | $V_{DD}$ |     | 324  | TXADDR02        | 0     |

| 251  | HTD7     | I/O | 288  | CBD70    | I/O | 325  | TXADDR00        | 0     |

| 252  | HTD4     | I/O | 289  | CBD68    | I/O | 326  | TXSOC0          | 0     |

| 253  | HTD0     | I/O | 290  | CBD65    | I/O | 327  | TXDATA05        | 0     |

| 254  | RESET_B  | I   | 291  | GND      |     | 328  | TXDATA03        | 0     |

| 255  | IC       | I/O | 292  | GND      |     | 329  | RXDATA24        | I     |

(4/6)

|      | ı               | -   |      | ı               | -   | III  | ı        | (4/6)                                 |

|------|-----------------|-----|------|-----------------|-----|------|----------|---------------------------------------|

| 端子番号 | 端子名             | I/O | 端子番号 | 端子名             | I/O | 端子番号 | 端子名      | I/O                                   |

| 330  | RXDATA20        | I   | 368  | HTD9            | I/O | 406  | CBD60    | I/O                                   |

| 331  | UCLK2           | I   | 369  | HTD6            | I/O | 407  | CBD55    | I/O                                   |

| 332  | RXSOC2          | I   | 370  | GND             |     | 408  | GND      |                                       |

| 333  | RXADDR22        | 0   | 371  | $V_{DD}$        |     | 409  | CBD50    | I/O                                   |

| 334  | GND             |     | 372  | IC              | I/O | 410  | $V_{DD}$ |                                       |

| 335  | TXADDR22        | 0   | 373  | IC              | 0   | 411  | CBD44    | I/O                                   |

| 336  | TXSOC2          | 0   | 374  | $V_{DD}$        |     | 412  | $V_{DD}$ |                                       |

| 337  | TXDATA26        | 0   | 375  | CG              | I   | 413  | CBA14    | 0                                     |

| 338  | $V_{DD}$        |     | 376  | JDO             | 0   | 414  | $V_{DD}$ |                                       |

| 339  | V <sub>DD</sub> |     | 377  | JMS             | I   | 415  | CBA8     | 0                                     |

| 340  | HSEL            | I   | 378  | RXDATA35        | I   | 416  | $V_{DD}$ |                                       |

| 341  | V <sub>DD</sub> |     | 379  | GND             |     | 417  | CBA3     | 0                                     |

| 342  | AD30/A14        | I/O | 380  | UCLK3           | I   | 418  | CBD43    | I/O                                   |

| 343  | AD29/A13        | I/O | 381  | RXCLAV3         | I   | 419  | CBD40    | I/O                                   |

| 344  | AD26/A10        | I/O | 382  | GND             |     | 420  | CBD36    | I/O                                   |

| 345  | AD23/A7         | I/O | 383  | TXADDR30        | 0   | 421  | CBD32    | I/O                                   |

| 346  | AD19/A3         | I/O | 384  | $V_{DD}$        |     | 422  | CBD31    | I/O                                   |

| 347  | GND             |     | 385  | TXDATA35        | 0   | 423  | CBD27    | I/O                                   |

| 348  | AD13/D13        | I/O | 386  | $V_{DD}$        |     | 424  | CBD22    | I/O                                   |

| 349  | AD09/D09        | I/O | 387  | RXDATA16        | I   | 425  | CBD19    | I/O                                   |

| 350  | AD7/D7          | I/O | 388  | $V_{DD}$        |     | 426  | CBD16    | I/O                                   |

| 351  | AD4/D4          | I/O | 389  | UCLK1           | I   | 427  | IC       | 0                                     |

| 352  | HTA17           | 0   | 390  | V <sub>DD</sub> |     | 428  | CBD6     | I/O                                   |

| 353  | HTA15           | 0   | 391  | GND             |     | 429  | CBD3     | I/O                                   |

| 354  | HTA11           | 0   | 392  | RXADDR12        | 0   | 430  | CBD0     | I/O                                   |

| 355  | HTA10           | 0   | 393  | TXADDR11        | 0   | 431  | GND      |                                       |

| 356  | HTA8            | 0   | 394  | TXSOC1          | 0   | 432  | RXDATA02 | I                                     |

| 357  | HTA5            | 0   | 395  | TXDATA16        | 0   | 433  | UCLK0    | I                                     |

| 358  | HTA2            | 0   | 396  | GND             |     | 434  | RXADDR03 | 0                                     |

| 359  | HTWE_B          | 0   | 397  | CBD87           | I/O | 435  | RXADDR00 | 0                                     |

| 360  | HTP3            | I/O | 398  | CBD83           | I/O | 436  | GND      |                                       |

| 361  | HTD27           | I/O | 399  | CBD81           | I/O | 437  | TXDATA07 | 0                                     |

| 362  | GND             |     | 400  | CBD75           | I/O | 438  | $V_{DD}$ |                                       |

| 363  | HTP2            | I/O | 401  | CBD71           | I/O | 439  | TXDATA01 | 0                                     |

| 364  | HTD21           | I/O | 402  | GND             |     | 440  | $V_{DD}$ |                                       |

| 365  | HTD18           | I/O | 403  | IC              | 0   | 441  | RXDATA22 | I                                     |

| 366  | HTD14           | I/O | 404  | CBD64           | I/O | 442  | $V_{DD}$ |                                       |

| 367  | HTD11           | I/O | 405  | CBD61           | I/O | 443  | $V_{DD}$ |                                       |

|      |                 |     |      | ·               |     |      |          | · · · · · · · · · · · · · · · · · · · |

(5/6)

|      |                 |     |      |          |     |      |          | ( 5/6 ) |

|------|-----------------|-----|------|----------|-----|------|----------|---------|

| 端子番号 | 端子名             | I/O | 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O     |

| 444  | $V_{DD}$        |     | 481  | $V_{DD}$ |     | 518  | GND      |         |

| 445  | RXADDR20        | 0   | 482  | GND      |     | 519  | $V_{DD}$ |         |

| 446  | $V_{DD}$        |     | 483  | $V_{DD}$ |     | 520  | GND      |         |

| 447  | TXDATA27        | 0   | 484  | GND      |     | 521  | $V_{DD}$ |         |

| 448  | TXDATA24        | 0   | 485  | $V_{DD}$ |     | 522  | GND      |         |

| 449  | TXDATA21        | 0   | 486  | GND      |     | 523  | $V_{DD}$ |         |

| 450  | GND             |     | 487  | $V_{DD}$ |     | 524  | GND      |         |

| 451  | INT             | 0   | 488  | GND      |     | 525  | $V_{DD}$ |         |

| 452  | UWE_B/RD_B      | 1   | 489  | $V_{DD}$ |     | 526  | GND      |         |

| 453  | GND             |     | 490  | GND      |     | 527  | $V_{DD}$ |         |

| 454  | AD24/A8         | I/O | 491  | $V_{DD}$ |     | 528  | GND      |         |

| 455  | AD21/A5         | I/O | 492  | GND      |     | 529  | $V_{DD}$ |         |

| 456  | AD17/A1         | I/O | 493  | $V_{DD}$ |     | 530  | GND      |         |

| 457  | AD15/D15        | I/O | 494  | GND      |     | 531  | $V_{DD}$ |         |

| 458  | AD11/D11        | I/O | 495  | $V_{DD}$ |     | 532  | GND      |         |

| 459  | GND             |     | 496  | GND      |     | 533  | $V_{DD}$ |         |

| 460  | AD5/D5          | I/O | 497  | $V_{DD}$ |     | 534  | GND      |         |

| 461  | AD0/D0          | I/O | 498  | GND      |     | 535  | $V_{DD}$ |         |

| 462  | HTA16           | 0   | 499  | $V_{DD}$ |     | 536  | GND      |         |

| 463  | HTA13           | 0   | 500  | GND      |     | 537  | $V_{DD}$ |         |

| 464  | V <sub>DD</sub> |     | 501  | $V_{DD}$ |     | 538  | GND      |         |

| 465  | HTA7            | 0   | 502  | GND      |     | 539  | $V_{DD}$ |         |

| 466  | $V_{DD}$        |     | 503  | $V_{DD}$ |     | 540  | GND      |         |

| 467  | HTA0            | 0   | 504  | GND      |     | 541  | $V_{DD}$ |         |

| 468  | $V_{DD}$        |     | 505  | $V_{DD}$ |     | 542  | GND      |         |

| 469  | HTD30           | I/O | 506  | GND      |     | 543  | $V_{DD}$ |         |

| 470  | $V_{DD}$        |     | 507  | $V_{DD}$ |     | 544  | GND      |         |

| 471  | HTD25           | I/O | 508  | GND      |     | 545  | $V_{DD}$ |         |

| 472  | HTD22           | I/O | 509  | $V_{DD}$ |     | 546  | GND      |         |

| 473  | HTD19           | I/O | 510  | GND      |     | 547  | $V_{DD}$ |         |

| 474  | HTP1            | I/O | 511  | $V_{DD}$ |     | 548  | GND      |         |

| 475  | HTD12           | I/O | 512  | GND      |     | 549  | $V_{DD}$ |         |

| 476  | GND             |     | 513  | $V_{DD}$ |     | 550  | GND      |         |

| 477  | HTP0            | I/O | 514  | GND      |     | 551  | $V_{DD}$ |         |

| 478  | HTD3            | I/O | 515  | $V_{DD}$ |     | 552  | GND      |         |

| 479  | HTD1            | I/O | 516  | GND      |     | 553  | $V_{DD}$ |         |

| 480  | PU              | 1   | 517  | $V_{DD}$ |     | 554  | GND      |         |

(6/6)

| 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O | 端子番号 | 端子名      | I/O |

|------|----------|-----|------|----------|-----|------|----------|-----|

| 555  | $V_{DD}$ |     | 564  | GND      |     | 573  | $V_{DD}$ |     |

| 556  | GND      |     | 565  | $V_{DD}$ |     | 574  | GND      |     |

| 557  | $V_{DD}$ |     | 566  | GND      |     | 575  | $V_{DD}$ |     |

| 558  | GND      |     | 567  | $V_{DD}$ |     | 576  | GND      |     |

| 559  | $V_{DD}$ |     | 568  | GND      |     | 577  | $V_{DD}$ |     |

| 560  | GND      |     | 569  | $V_{DD}$ |     | 578  | GND      |     |

| 561  | $V_{DD}$ |     | 570  | GND      |     | 579  | $V_{DD}$ |     |

| 562  | GND      |     | 571  | $V_{DD}$ |     | 580  | GND      |     |

| 563  | $V_{DD}$ |     | 572  | GND      |     |      |          |     |

# 2.3 端子機能

$\mu$ PD98410 は 3.3V 動作デバイスですが , 5V TTL インタフェ - スを持つ PHY デバイス , CPU やメモリと直接接続可能です。

## 2.3.1 パワ - ・サプライ

| 端子名      | 端子番号                                                                  | I/O | 機能            |

|----------|-----------------------------------------------------------------------|-----|---------------|

| $V_{DD}$ | 15, 23, 26, 32, 60, 74, 77, 83, 103, 111, 113, 118, 126, 130, 137,    | -   | +3.3V±5%の電源を供 |

|          | 139, 142, 152, 160, 167, 174, 177, 181, 186, 192, 199, 209, 233,      |     | 給する端子です。      |

|          | 248, 271, 287, 293, 338, 339, 341, 371, 374, 384, 386, 388, 390,      |     |               |

|          | 410, 412, 414, 416, 438, 440, 442, 443, 444, 446, 464, 466, 468,      |     |               |

|          | 470, 481, 483, 485, 487, 489, 491, 493, 495, 497, 499, 501, 503,      |     |               |

|          | 505, 507, 509, 511, 513, 515, 517, 519, 521, 523, 525, 527, 529,      |     |               |

|          | 531, 533, 535, 537, 539, 541, 543, 545, 547, 549, 551, 553, 555,      |     |               |

|          | 557, 559, 561, 563, 565, 567, 569, 571, 573, 575, 577, 579            |     |               |

| GND      | 1, 2, 25, 33, 34, 35, 49, 65, 66, 67, 68, 75, 85, 86,91,99, 100 ,101, | -   | グランド端子です。     |

|          | 114, 116, 131, 132, 133, 138, 149, 164, 175, 191, 195, 226, 235,      |     |               |

|          | 237, 246, 258, 259, 273, 284, 286, 291, 292, 304, 306, 309, 316,      |     |               |

|          | 334, 347, 362, 370, 379, 382, 391, 396, 402, 408, 431, 436, 450,      |     |               |

|          | 453, 459, 476, 482, 484, 486, 488, 490, 492, 494, 496, 498, 500,      |     |               |

|          | 502, 504, 506, 508, 510, 512, 514, 516, 518, 520, 522, 524, 526,      |     |               |

|          | 528, 530, 532, 534, 536, 538, 540, 542, 544, 546, 548, 550, 552,      |     |               |

|          | 554, 556, 558, 560, 562, 564, 566, 568, 570, 572, 574, 576, 578,      |     |               |

|          | 580                                                                   |     |               |

### 2.3.2 UTOPIA インタフェ - ス

$\mu$ PD98410 は , PHY レイヤと ATM レイヤ間のインタフェースとして UTOPIA Level 2(セル・レベル転送)を採用しています。表 2 - 1 , 2 - 2 にインタフェース信号を示します。

表 2-1 受信インタフェース信号 (1/2)

| 記号        | 端子番号                        | I/O | 機能                                                                |

|-----------|-----------------------------|-----|-------------------------------------------------------------------|

| RXADDR03- | 434, 204, 323, 435          | 0   | 受信インタフェース 0 番のマルチ PHY 選択アドレス                                      |

| RXADDR00  |                             |     | RXADDR03 が MSB です。                                                |

| RXDATA07- | 319, 200, 73, 320, 201,     | I   | 受信インタフェース 0 番のセル・データ入力                                            |

| RXDATA00  | 432, 202, 321               |     | PHY レイヤ・デバイスからバイト単位で入力します。                                        |

|           |                             |     | μPD98410 は UCLK0 の立ち上がりエッジに同期してデータ                                |

|           |                             |     | を読み込みます。RXDATA07 が MSB です。                                        |

| RXSOC0    | 203                         | 1   | 受信インタフェース 0 番のセル転送スタート信号                                          |

|           |                             |     | PHY レイヤ・デバイスからセル・データの 1 バイト目に同期                                   |

|           |                             |     | して入力される信号です。                                                      |

| RXENB0_B  | 322                         | 0   | 受信インタフェース 0 番の転送イネーブル信号                                           |

|           |                             |     | μPD98410 が次のクロック・サイクルで受信可能であること                                   |

|           |                             |     | を PHY レイヤ・デバイスに示します。                                              |

| RXCLAV0   | 76                          | I   | 受信インタフェース 0 番のセル転送有効信号                                            |

|           |                             |     | 現在のセル転送終了後, µPD98410 に供給するセルがないこ                                  |

|           |                             |     | とを通知する信号を入力します。                                                   |

| UCLK0     | 433                         | I   | 受信インタフェース 0 番の UTOPIA クロック入力                                      |

|           |                             |     | このクロックの立ち上がりエッジに同期してデータの送受                                        |

|           |                             |     | 信を行います。                                                           |

| RXADDR13- | 277, 392, 154, 24           | 0   | 受信インタフェース 1 番のマルチ PHY 選択アドレス                                      |

| RXADDR10  |                             |     | RXADDR13 が MSB です。                                                |

| RXDATA17- | 19, 387, 150, 272, 20, 151, | I   | 受信インタフェース 1 番のセル・データ入力                                            |

| RXDATA10  | 274, 21                     |     | PHY レイヤ・デバイスからバイト単位で入力します。                                        |

|           |                             |     | μPD98410 は UCLK1 の立ち上がりエッジに同期してデータ                                |

| DVOCO4    | 070                         |     | を読み込みます。RXDATA17 が MSB です。                                        |

| RXSOC1    | 276                         | I   | 受信インタフェース 1 番のセル転送スタート信号<br> <br>  PHY レイヤ・デバイスからセル・データの 1 バイト目に同 |

|           |                             |     | 期して入力される信号です。                                                     |

| RXENB1_B  | 22                          | 0   | 受信インタフェース 1 番の転送イネーブル信号                                           |

| LVCIADI_D |                             | J   | μPD98410 が次のクロック・サイクルで受信可能であこと                                    |

|           |                             |     | を PHY レイヤ・デバイスに示します。                                              |

| RXCLAV1   | 153                         | ı   | 受信インタフェース 1 番のセル転送有効信号                                            |

|           |                             |     | 現在のセル転送終了後, µPD98410 に供給するセルがないこ                                  |

|           |                             |     | とを通知する信号を入力します。                                                   |

| UCLK1     | 389                         | ı   | 受信インタフェース 1 番の UTOPIA クロック入力                                      |

|           |                             |     | このクロックの立ち上がりエッジに同期してデータの送受                                        |

|           |                             |     | 信を行います。                                                           |

### 表 2-1 受信インタフェース信号 (2/2)

| 記号        | 端子番号                           | I/O | 機能                                |

|-----------|--------------------------------|-----|-----------------------------------|

| RXADDR23- | 214, 333, 88, 445              | 0   | 受信インタフェース 2 番のマルチ PHY 選択アドレス      |

| RXADDR20  |                                |     | RXADDR23 が MSB です。                |

| RXDATA27- | 210, 82, 84, 329, 211, 441,    | ı   | 受信インタフェース 2 番のセル・データ入力            |

| RXDATA20  | 212, 330                       |     | PHY レイヤ・デバイスからバイト単位で入力します。        |

|           |                                |     | μPD98410 は UCLK2 の立ち上がりエッジに同期してデー |

|           |                                |     | タを読み込みます。RXDATA27 が MSB です。       |

| RXSOC2    | 332                            | ı   | 受信インタフェース 2 番のセル転送スタート信号          |

|           |                                |     | PHY レイヤ・デバイスからセル・データの1バイト目に 同     |

|           |                                |     | 期して入力される信号です。                     |

| RXENB2_B  | 213                            | 0   | 受信インタフェース 2 番の転送イネーブル信号           |

|           |                                |     | μPD98410が次のクロック・サイクルで受信可能であるこ     |

|           |                                |     | とを PHY レイヤ・デバイスに示します。             |

| RXCLAV2   | 87                             | I   | 受信インタフェース 2 番のセル転送有効信号            |

|           |                                |     | 現在のセル転送終了後, µPD98410に供給するセルがない    |

|           |                                |     | ことを通知する信号を入力します。                  |

| UCLK2     | 331                            | I   | 受信インタフェース 2 番の UTOPIA クロック入力      |

|           |                                |     | このクロックの立ち上がりエッジに同期してデータの送         |

|           |                                |     | 受信を行います。                          |

| RXADDR33- | 143, 266, 12, 267              | 0   | 受信インタフェース3番のマルチ PHY 選択アドレス        |

| RXADDR30  |                                |     | RXADDR33 が MSB です。                |

| RXDATA37- | 262, 8, 378, 140, 263, 9, 264, | 1   | 受信インタフェース 3 番のセル・データ入力            |

| RXDATA30  | 141                            |     | PHY レイヤ・デバイスからバイト単位で入力します。        |

|           |                                |     | μPD98410 は UCLK3 の立ち上がりエッジに同期してデー |

|           |                                |     | タを読み込みます。RXDATA37 が MSB です。       |

| RXSOC3    | 11                             | I   | 受信インタフェース3番のセル転送スタート信号            |

|           |                                |     | PHY レイヤ・デバイスからセル・データの 1 バイト目に     |

|           |                                |     | 同期して入力される信号です。                    |

| RXENB3_B  | 265                            | 0   | 受信インタフェース 3 番の転送イネーブル信号           |

|           |                                |     | μPD98410 が次のクロック・サイクルで受信可能であるこ    |

|           |                                |     | とを PHY レイヤ・デバイスに示します。             |

| RXCLAV3   | 381                            | I   | 受信インタフェース 3番のセル転送有効信号             |

|           |                                |     | 現在のセル転送終了後 , µPD98410 に供給するセルがない  |

|           |                                |     | ことを通知する信号を入力します。                  |

| UCLK3     | 380                            | I   | 受信インタフェース 3 番の UTOPIA クロック入力      |

|           |                                |     | このクロックの立ち上がりエッジに同期してデータの送         |

|           |                                |     | 受信を行います。                          |

### 表 2 - 2 送信インタフェース信号 (1/2)

| 記号        | 端子番号                         | I/O | 機能                                |

|-----------|------------------------------|-----|-----------------------------------|

| TXADDR03- | 205, 324, 78, 325            | 0   | 送信インタフェース 0 番のマルチ PHY 選択アドレス      |

| TXADDR00  |                              |     | TXADDR03 が MSB です。                |

| TXDATA07- | 437, 207, 327, 80, 328, 208, | 0   | 送信インタフェース 0 番のセル・データ出力            |

| TXDATA00  | 439, 81                      |     | PHY レイヤ・デバイスへバイト単位で出力します。         |

|           |                              |     | μPD98410 は UCLK0 の立ち上がりエッジに同期してデー |

|           |                              |     | タを出力します。TXDATA07 が MSB です。        |

|           |                              |     | (3ステート・バッファ)                      |

| TXSOC0    | 326                          | 0   | 送信インタフェース 0 番のセル転送スタート信号          |

|           |                              |     | 送信セル・データの1バイト目に同期して出力される信         |

|           |                              |     | 号です。                              |

|           |                              |     | (3ステート・バッファ)                      |

| TXENB0_B  | 79                           | 0   | 送信インタフェース 0 番の転送イネーブル信号           |

|           |                              |     | 現在のクロック・サイクルでデータが出力されているこ         |

|           |                              |     | とを PHY レイヤ・デバイスに示します。             |

| TXCLAV0   | 206                          | I   | 送信インタフェース 0 番のセル転送有効信号            |

|           |                              |     | 現在のセル転送終了後,次の 1 セル・データをすべて受       |

|           |                              |     | け取れることを通知する信号を入力します。              |

| TXADDR13- | 278, 155, 393, 279           | 0   | 送信インタフェース 1 番のマルチ PHY 選択アドレス      |

| TXADDR10  |                              |     | TXADDR13 が MSB です。                |

| TXDATA17- | 157, 395, 27, 281, 158, 282, | 0   | 送信インタフェース 1 番のセル・データ出力            |

| TXDATA10  | 28, 159                      |     | PHY レイヤ・デバイスへバイト単位で出力します。         |

|           |                              |     | μPD98410 は UCLK1 の立ち上がりエッジに同期してデー |

|           |                              |     | タを出力します。TXDATA17 が MSB です。        |

|           |                              |     | (3ステート・バッファ)                      |

| TXSOC1    | 394                          | 0   | 送信インタフェース 1 番のセル転送スタート信号          |

|           |                              |     | 送信セル・データの1バイト目に同期して出力される信         |

|           |                              |     | 号です。(3 ステート・バッファ)                 |

| TXENB1_B  | 280                          | 0   | 送信インタフェース 1 番の転送イネーブル信号           |

|           |                              |     | 現在のクロック・サイクルでデータが出力されているこ         |

|           |                              |     | とを PHY レイヤ・デバイスに示します。             |

| TXCLAV1   | 156                          | I   | 送信インタフェース 1 番のセル転送有効信号            |

|           |                              |     | 現在のセル転送終了後,次の 1 セル・データをすべて受       |

|           |                              |     | け取れることを通知する信号を入力します。              |

### 表 2-2 送信インタフェース信号 (2/2)

| 記号        | 端子番号                         | I/O | 機能                                |

|-----------|------------------------------|-----|-----------------------------------|

| TXADDR23- | 215, 335, 89, 216            | 0   | 送信インタフェース 2 番のマルチ PHY 選択アドレス      |

| TXADDR20  |                              |     | TXADDR23 が MSB です。                |

| TXDATA27- | 447, 337, 218, 448, 92, 219, | 0   | 送信インタフェース 2 番のセル・データ出力            |

| TXDATA20  | 449, 93                      |     | PHY レイヤ・デバイスへバイト単位で出力します。         |

|           |                              |     | μPD98410 は UCLK2 の立ち上がりエッジに同期してデー |

|           |                              |     | タを出力します。TXDATA27 が MSB です。        |

|           |                              |     | (3ステート・バッファ)                      |

| TXSOC2    | 336                          | 0   | 送信インタフェース 2 番のセル転送スタート信号          |

|           |                              |     | 送信セル・データの1バイト目に同期して出力される信         |

|           |                              |     | 号です。                              |

|           |                              |     | (3ステート・バッファ)                      |

| TXENB2_B  | 217                          | 0   | 送信インタフェース 2 番の転送イネーブル信号           |

|           |                              |     | 現在のクロック・サイクルでデータが出力されているこ         |

|           |                              |     | とを PHY レイヤ・デバイスに示します。             |

| TXCLAV2   | 90                           | 1   | 送信インタフェース 2 番のセル転送有効信号            |

|           |                              |     | 現在のセル転送終了後,次の 1 セル・データをすべて受       |

|           |                              |     | け取れることを通知する信号を入力します。              |

| TXADDR33- | 144, 268, 13, 383            | 0   | 送信インタフェース3番のマルチ PHY 選択アドレス        |

| TXADDR30  |                              |     | TXADDR33 が MSB です。                |

| TXDATA37- | 270, 146, 385, 148, 147, 16, | 0   | 送信インタフェース3番のセル・データ出力              |

| TXDATA30  | 18, 17                       |     | PHY レイヤ・デバイスへバイト単位で出力します。         |

|           |                              |     | μPD98410 は,UCLK3 の立ち上がりエッジに同期して   |

|           |                              |     | データを出力します。TXDATA37 が MSB です。      |

|           |                              |     | (3ステート・バッファ)                      |

| TXSOC3    | 269                          | 0   | 送信インタフェース 3 番のセル転送スタート信号          |

|           |                              |     | 送信セル・データの1バイト目に同期して出力される信         |

|           |                              |     | 号です。 (3ステート・バッファ)                 |

| TXENB3_B  | 14                           | 0   | 送信インタフェース 3 番の転送イネーブル信号           |

|           |                              |     | 現在のクロック・サイクルでデータが出力されているこ         |

|           |                              |     | とを PHY レイヤ・デバイスに示します。             |

| TXCLAV3   | 145                          | I   | 送信インタフェース3番のセル転送有効信号              |

|           |                              |     | 現在のセル転送終了後,次の1セル・データをすべて受         |

|           |                              |     | け取れることを通知する信号を入力します。              |

## 2.4 メモリ・インタフェース信号

$\mu$ PD98410 は,2種類のメモリ・インタフェースを持ちます。一方の HTT&コントロール・メモリにはセルの ヘッダ変換テーブルとセル・バッファへのアドレス・ポインタを格納し,もう一方のセル・バッファ・メモリ にはセル・データを格納します。表 2 - 3 に HTT&コントロール・メモリのインタフェース信号を示します。また,表 2 - 4 にセル・バッファ・メモリのインタフェース信号を示します。

表 2-3 HTT & コントロール・メモリ・インタフェース信号

| 記号         | 端子番号                                    | I/O | 機能                        |

|------------|-----------------------------------------|-----|---------------------------|

| HTA17-HTA0 | 352, 462, 353, 110, 463, 236, 354, 355, | 0   | アドレス出力                    |

|            | 112, 356, 465, 238, 357, 239, 241, 358, |     |                           |

|            | 240, 467                                |     |                           |

| HTD31-HTD0 | 243, 469, 119, 244, 361, 120, 471, 245, | I/O | データ入出力バス (32-bit/word 単位) |

|            | 121, 472, 364, 122, 473, 365, 247, 123, |     | (プルダウン抵抗付き)               |

|            | 124, 366, 249, 475, 367, 125, 368, 250, |     |                           |

|            | 251, 369, 127, 252, 478, 128, 479, 253  |     |                           |

| HTP3-HTP0  | 360, 363, 474, 477                      | I/O | パリティ入出力 (プルダウン抵抗付き)       |

| HTCS1_B,   | 115                                     | 0   | チップ・セレクト信号                |

| HTCS0_B    | 117                                     |     |                           |

| HTWE_B     | 359                                     | 0   | ライト・イネーブル信号               |

| HTOE_B     | 242                                     | 0   | 出力イネーブル信号                 |

# 表 2-4 セル・バッファ・メモリ・インタフェース信号

| 記号          | 端子番号                                  | I/O | 機能                       |

|-------------|---------------------------------------|-----|--------------------------|

| CBA17- CBA0 | 48, 300, 178, 413, 50, 301, 180, 302, | 0   | アドレス出力                   |

|             | 52, 415, 53, 182, 303, 54, 417, 183,  |     |                          |

|             | 305, 55                               |     |                          |

| CBD87- CBD0 | 397, 29, 283, 30, 398, 161, 399, 31,  | I/O | データ・バス(88-bit / word 単位) |

|             | 285, 162, 163, 165, 400, 36, 166, 37, |     | (プルダウン抵抗付き)              |

|             | 401, 288, 38, 289, 168, 39, 290, 404, |     |                          |

|             | 40, 170, 405, 406, 171, 42, 172, 43,  |     |                          |

|             | 407, 294, 173, 295, 44, 409, 45, 296, |     |                          |

|             | 297, 46, 298, 411, 418, 184, 56, 419, |     |                          |

|             | 307, 185, 57, 420, 58, 308, 187, 421, |     |                          |

|             | 422, 59, 310, 188, 423, 189, 311, 61, |     |                          |

|             | 190, 424, 312, 62, 425, 313, 63, 426, |     |                          |

|             | 64, 314, 193, 194, 315, 69, 196, 197, |     |                          |

|             | 70, 428, 317, 71, 429, 72, 318, 430   |     |                          |

| CBCS1_B,    | 176                                   | 0   | チップ・セレクト信号               |

| CBCS0_B     | 299                                   |     |                          |

| CBWE_B      | 47                                    | 0   | ライト・イネーブル信号              |

| CBOE_B      | 179                                   | 0   | 出力イネーブル信号                |

# 2.4.1 マイクロプロセッサ・インタフェース信号

$\mu$ PD98410 は,2種類のマイクロプロセッサ・インタフェースをサポートしています。

- (1)32 ビット・アドレス・データ多重型同期バス

- (2)16ビット・アドレス・データ分離型非同期バス

使用するモードにより,一部の端子機能が変わります。

表2-5 マイクロプロセッサ・インタフェース

| 記号     | 端子番号 | I/O | 機能                          |

|--------|------|-----|-----------------------------|

| HSEL   | 340  | 1   | マイクロプロセッサ・インタフェース選択信号       |

|        |      |     | ハードウエア・リセット時に , HSEL がロウ・レベ |

|        |      |     | ルのときは 32 ビット多重型同期バス , ハイ・レベ |

|        |      |     | ルのときは 16 ビット分離型非同期バスが選択され   |

|        |      |     | ます。                         |

| IOCS_B | 94   | 1   | I/O チップ・セレクト信号              |

| MCS_B  | 221  | ı   | メモリ・チップ・セレクト信号              |

| INT    | 451  | 0   | 割り込み要求信号                    |

表 2-6 32 ビット多重型同期インタフェース

| 記号       | 端子番号                               | I/O | 機能                          |

|----------|------------------------------------|-----|-----------------------------|

| HCLK     | 220                                | Ι   | マイクロプロセッサ・バス・クロック(8M-33MHz) |

| AD31-AD0 | 223, 342, 343, 224, 225, 344, 227, | I/O | アドレス / データ・バス               |

|          | 454, 345, 228, 455, 229, 346, 104, |     |                             |

|          | 456, 230, 457, 105, 348, 231, 458, |     |                             |

|          | 106, 349, 232, 350, 107, 460, 351, |     |                             |

|          | 108, 234, 109, 461                 |     |                             |

| R/W_B    | 222                                | _   | リード / ライト選択信号               |

| UWE_B    | 452                                | I   | 上位ワード・イネーブル信号               |

| RDY_B    | 95                                 | 0   | レディ信号 (3 ステート・バッファ )        |

# 表 2-7 16 ビット分離型非同期インタフェース

| 記号        | 端子番号                               | I/O | 機能                                     |

|-----------|------------------------------------|-----|----------------------------------------|

| HCLK      | 220                                | 1   | GND に接続するか,V <sub>DD</sub> にプルアップしてくださ |

|           |                                    |     | ١١ <sub>°</sub>                        |

| A15       | 223                                | I   | GND に接続するか,V <sub>DD</sub> にプルアップしてくださ |

|           |                                    |     | ۱۱ <sub>0</sub>                        |

| A14 -A0   | 342, 343, 224, 225, 344, 227, 454, | 1   | アドレス入力                                 |

|           | 345, 228, 455, 229, 346, 104, 456, |     |                                        |

|           | 230                                |     |                                        |

| D15 -D0   | 457, 105, 348, 231, 458, 106, 349, | I/O | データ・バス                                 |

|           | 232, 350, 107, 460, 351, 108, 234, |     |                                        |

|           | 109, 461                           |     |                                        |

| WR_B      | 222                                | I   | ライト・ストローブ信号                            |

| RD_B      | 452                                | I   | リード・ストローブ信号                            |

| RDY_B,RDY | 95                                 | 0   | レディ信号 (3 ステート・バッファ )                   |

# 2.4.2 JTAG

表 2 - 8 JTAG インタフェース信号

| 記号     | 端子番号 | I/O | 機能                             |

|--------|------|-----|--------------------------------|

| JDI    | 260  | I   | JTAG シリアル・データ入力                |

| JDO    | 376  | 0   | JTAG シリアル・データ出力 ( 通常時 , オープン ) |

|        |      |     | (3ステート・バッファ)                   |

| JCK    | 261  | I   | JTAG シリアル・クロック入力               |

| JMS    | 377  | I   | JTAG モード・セレクト信号                |

| JRST_B | 7    | I   | JTAG リセット信号                    |

# 2.4.3 その他

表 2 - 9 その他のインタフェース信号

| 記号      | 端子番号                                | I/O | 機能                          |

|---------|-------------------------------------|-----|-----------------------------|

| SWCLK   | 129                                 | I   | システム・クロック入力(8-33MHz)        |

| RESET_B | 254                                 | ı   | ハードウエア・リセット信号               |

|         |                                     |     | (シュミット入力バッファ)               |

| CG      | 5, 96, 97, 134, 135, 375,           | ı   | 常時,GND に接続                  |

| PU      | 480                                 | 1   | 常時 , V <sub>DD</sub> にプルアップ |

| IC      | 3, 4, 6, 10, 41, 98, 102, 136, 169, | 0   | 内部接続信号(常時,オープン)             |

|         | 198, 255, 256, 257, 275, 372, 373,  |     |                             |

|         | 403, 427                            |     |                             |

# 2.5 未使用端子の処理方法

表 2 - 10 未使用端子の処理方法

| 端子名               | I/O            | 未使用時の推奨接続方法                              |

|-------------------|----------------|------------------------------------------|

| RXDATA07-RXDATA00 | I              | GND に接続                                  |

| RXDATA17-RXDATA10 |                |                                          |

| RXDATA27-RXDATA20 |                |                                          |

| RXDATA37-RXDATA30 |                |                                          |

| RXSOC3-RXSOC0     | I              | GND に接続                                  |

| RXCLAV3-RXCLAV0   | I              | GND に接続                                  |

| UCLK3-UCLK0       | I              | GND に接続                                  |

| TXCLAV3-TXCLAV0   | I              | GND に接続                                  |

| HTD31-HTD0        | I/O(プルダウン抵抗付き) | オープン                                     |

| HTP3-HTP0         | I/O(プルダウン抵抗付き) | オープン                                     |

| CBD87-CBD0        | I/O(プルダウン抵抗付き) | オープン                                     |

| HSEL              | I              | 32 ビット多重型同期バス使用時 GND に接続                 |

|                   |                | 16 ビット分離型非同期バス使用時 V <sub>DD</sub> にプルアップ |

| HCLK              | I              | V <sub>DD</sub> にプルアップまたは GND に接続        |

| IOCS_B            | I              | V <sub>DD</sub> にプルアップ                   |

| MCS_B             | I              | V <sub>DD</sub> にプルアップ                   |

| AD31-AD0          | I/O            | V <sub>DD</sub> にプルアップ                   |

| A15-A0            | I              | GND に接続                                  |

| D15-D0            | I/O            | V <sub>DD</sub> にプルアップ                   |

| R/W_B / WR_B      | I              | V <sub>DD</sub> にプルアップ                   |

| UWE_B/RD_B        | I              | V <sub>DD</sub> にプルアップ                   |

| JDI               | I              | GND に接続                                  |

| JCK               | I              | GND に接続                                  |

| JMS               | I              | GND に接続                                  |

| JRST_B            | I              | GND に接続                                  |

| 全出力端子             | 0              | オ - プン                                   |

# 2.6 リセット時の端子の状態

表 2 - 11 リセット時の端子の状態

| 端子名               | I/O               | リセット時の端子状態 |

|-------------------|-------------------|------------|

| RXADDR03-RXADDR00 | 0                 | ハイ・レベル     |

| RXADDR13-RXADDR10 |                   |            |

| RXADDR23-RXADDR20 |                   |            |

| RXADDR33-RXADDR30 |                   |            |

| RXENB3_B-RXENB0_B | 0                 | ハイ・レベル     |

| TXADDR03-TXADDR00 | 0                 | ハイ・レベル     |

| TXADDR13-TXADDR10 |                   |            |

| TXADDR23-TXADDR20 |                   |            |

| TXADDR33-TXADDR30 |                   |            |

| TXDATA07-TXDATA00 | O(3ステート・バッファ)     | H-iZ       |

| TXDATA17-TXDATA10 |                   |            |

| TXDATA27-TXDATA20 |                   |            |

| TXDATA37-TXDATA30 |                   |            |

| TXSOC3-TXSOC0     | O(3ステート・バッファ)     | Hi-Z       |

| TXENB3_B-TXENB0_B | 0                 | ハイ・レベル     |

| HTA17-HTA0        | 0                 | ロウ・レベル     |

| HTCS1_B, HTCS0_B  | 0                 | ハイ・レベル     |

| HTWE_B            | 0                 | ハイ・レベル     |

| HTOE_B            | 0                 | ハイ・レベル     |

| HTP3-HTP0         | I/O ( プルダウン抵抗付き ) | ロウ・レベル     |

| HTD31-HTD0        | I/O ( プルダウン抵抗付き ) | ロウ・レベル     |

| CBD87-CBD0        | I/O ( プルダウン抵抗付き ) | ロウ・レベル     |

| CBA17-CBA0        | 0                 | ロウ・レベル     |

| CBOE_B            | 0                 | ハイ・レベル     |

| CBWE_B            | 0                 | ハイ・レベル     |

| CBCS1_B, CBCS0_B  | 0                 | ハイ・レベル     |

| INT               | 0                 | ロウ・レベル     |

| RDY               | O(3ステート・バッファ)     | Hi-Z       |

| AD31-AD0          | I/O               | Hi-Z       |

| D15-D0            | I/O               | Hi-Z       |

| JDO               | O(3ステート・バッファ)     | Hi-Z       |

# 第3章 機能概要

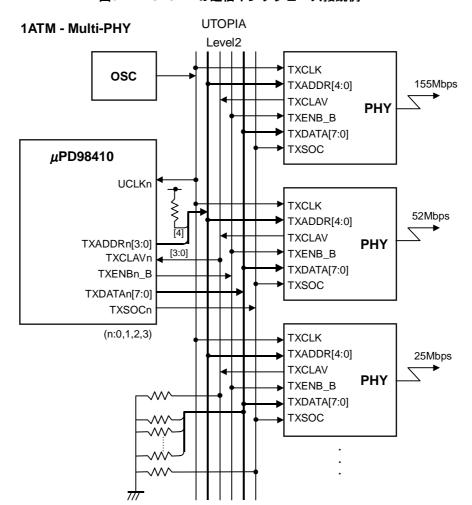

$\mu$ PD98410は,ヘッダ変換機能を持つ共有バッファ方式ノンブロッキング型ATMスイッチです。回線インタフェースはUTOPIA Level 2に準拠しており,マルチPHY接続により速度の異なる回線を24回線まで接続できます。スイッチング時には外部SRAMに設定されるヘッダ変換テーブルを参照して,同時に最大64Kコネクション(メモリ最大実装時)までヘッダ変換を行うことができます。共有バッファには外部SRAMを使用し,最大51.2Kセル(メモリ最大実装時)まで蓄えることができます。

またµPD98410では, EPD (Early Packet Discard), PPD (Partial Packet Discard), 優先セル廃棄制御およびABR (Available Bit Rate)トラフィック制御による転送品質制御を行います。

# 3.1 UTOPIAインタフェ - ス

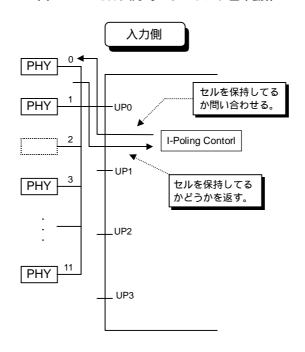

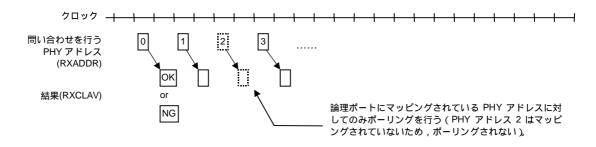

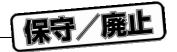

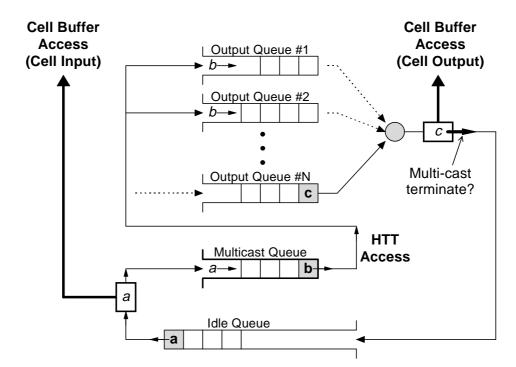

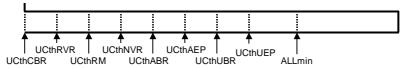

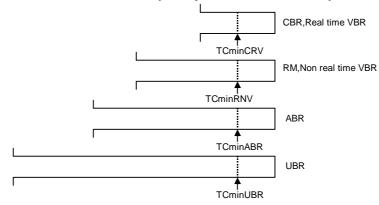

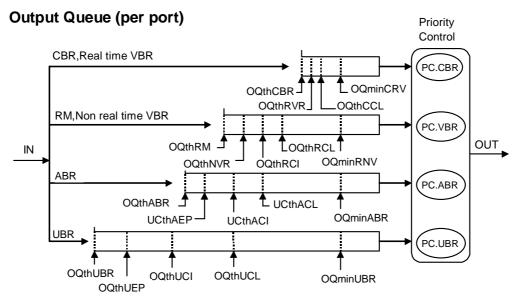

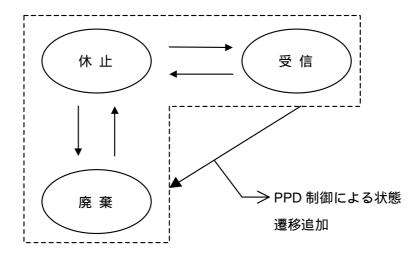

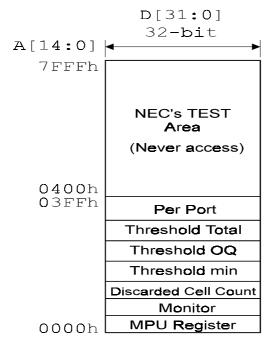

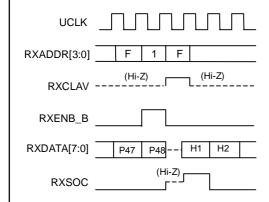

$\mu$ PD98410は, UTOPIA Level 2に準拠したUTOPIAインタフェースを4つ持っています。サポートしているのは,シングルATM-マルチPHY,8ビット・データ幅,セル・レベル・ハンドシェークのインタフェースです。オクテット・レベル・ハンドシェークはサポートしていません。