### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# V850/SV1

32ビット・シングルチップ・マイクロコンピュータ

# ハードウエア編

μPD703038

μPD703038Y μPD703039 μPD703039Y μPD703040 μPD703040Y μPD703041 μPD703041Y μPD70F3038 μPD70F3038Y

μPD70F3040

μPD70F3040Y

資料番号 U14462JJ2V1UD00 (第2版) 発行年月 August 2005 N CP(K) [メ モ]

### 目次要約

| 第2章         | <b>端子機能</b> 42                      |

|-------------|-------------------------------------|

| <b>第</b> 3章 | CPU <b>機能</b> 67                    |

| <b>第</b> 4章 | <b>バス制御機能</b> 100                   |

| <b>第</b> 5章 | 割り込み/例外処理機能 117                     |

| <b>第</b> 6章 | <b>クロック発生機能</b> 150                 |

| 第7章         | <b>タイマ/カウンタ機能</b> 167               |

| <b>第</b> 8章 | 時計用タイマ機能 271                        |

| <b>第</b> 9章 | <b>ウォッチドッグ・タイマ機能</b> 277            |

| 第10章        | <b>シリアル・インタフェース機能</b> 285           |

| 第11章        | A/D <b>コンパータ</b> 386                |

| 第12章        | DMA <b>機能</b> 421                   |

| 第13章        | <b>リアルタイム出力機能(</b> RTO <b>)</b> 431 |

| 第14章        | PWM <b>機能</b> 440                   |

| 第15章        | Vsync/Hsync <b>分離回路</b> 452         |

| 第16章        | キー・リターン機能 469                       |

| 第17章        | ポート機能 471                           |

| 第18章        | リ <b>セット機能</b> 545                  |

| 第19章        | ROM <b>コレクション機能</b> 546             |

| 第20章        | フラッシュ・メモリ 550                       |

| 第21章        | <b>電気的特性</b> 567                    |

| 第22章        | 外形図 592                             |

| 第23章        | 半田付け推奨条件 594                        |

| 付録A         | <b>レジスタ索引</b> 597                   |

| <b>付録</b> B | <b>命令セット一覧</b> 605                  |

| 付録C         | <b>総合索引</b> 612                     |

| <b>付録</b> D | 改版履歴 622                            |

|             |                                     |

第1章 イントロダクション ... 30

### CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

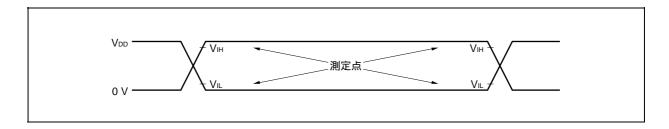

CMOSデバイスの入力がノイズなどに起因して、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

本製品のうち,外国為替及び外国貿易法の規定により規制貨物等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

非該当品 : μ PD70F3038, 70F3038Y, 70F3040, 70F3040Y

ユーザ判定品: µPD703038, 703038Y, 703039, 703039Y, 703040, 703040Y, 703041Y

- ◆本資料に記載されている内容は2005年7月現在のもので、今後、予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- 当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- ●本資料に記載された回路,ソフトウエアおよびこれらに関する情報は,半導体製品の動作例,応用例を 説明するものです。お客様の機器の設計において,回路,ソフトウエアおよびこれらに関する情報を使 用する場合には,お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し,当社は,一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。 意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

(注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは、(1)において定義された当社の開発、製造製品をいう。

M8E 02.11

### 本版で改訂された主な箇所(1/2)

| 箇 所   | 内 容                                                                    |

|-------|------------------------------------------------------------------------|

| 全般    | 製品(μPD703038, 703038Y, 70F3038, 70F3038Y)を追加                           |

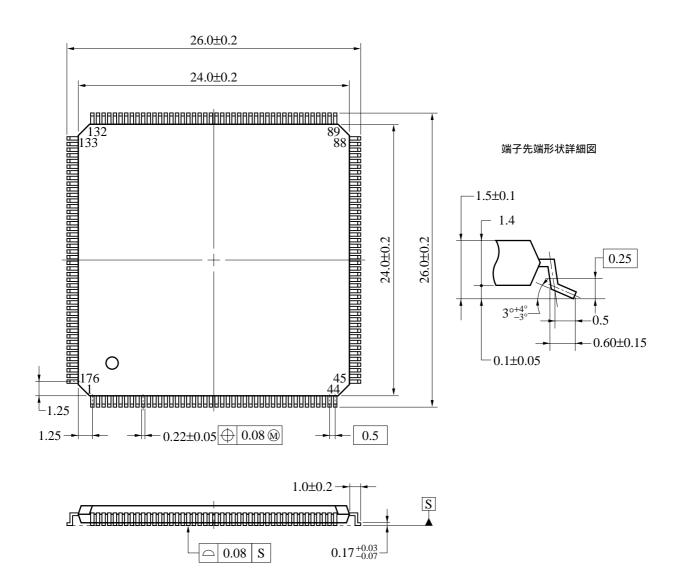

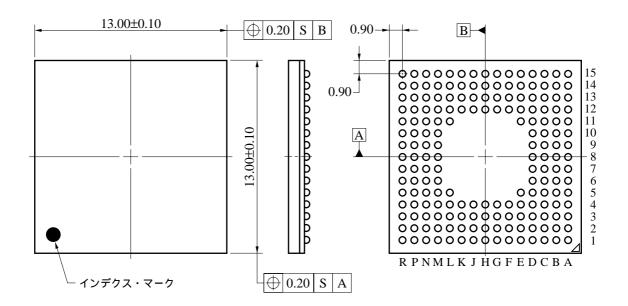

| 全般    | パッケージ (180ピン・プラスチックFBGA) を追加                                           |

| p.31  | 最小命令実行時間を変更                                                            |

| p.33  | 1.3 応用分野を変更                                                            |

| p.40  | 1.6.2(6) クロック・ジェネレータの記述を変更                                             |

| p.50  | 2.2 <b>端子状態</b> を変更                                                    |

| p.61  | 2.3(21)CLKOUT(Clock Out)を追加                                            |

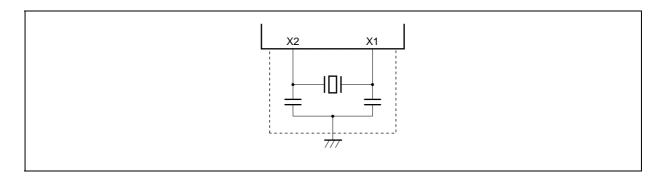

| p.63  | 2.4 <b>端子の入出力回路タイプ,入出力バッファ電源と未使用時の処理</b> のXT1, XT2端子の記述を               |

|       | 変更                                                                     |

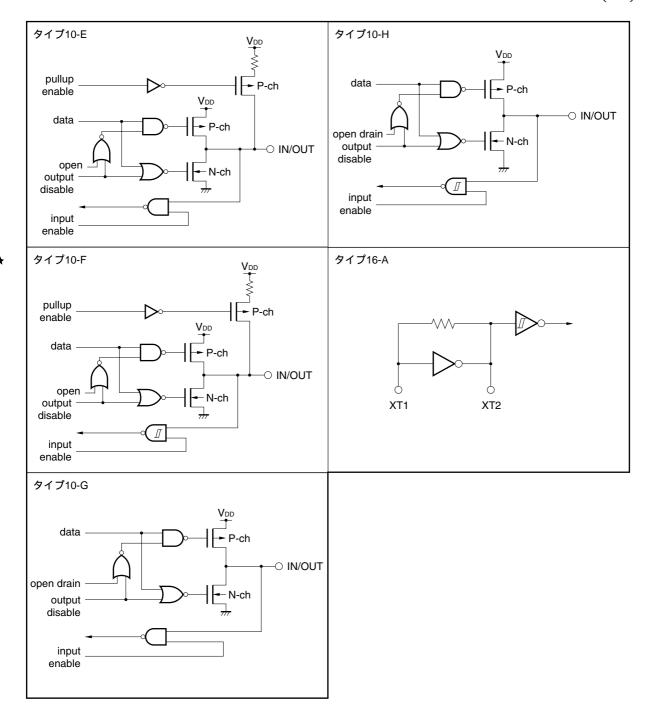

| p.65  | 2.5 <b>端子の入出力回路</b> にタイプ16 - Aを追加                                      |

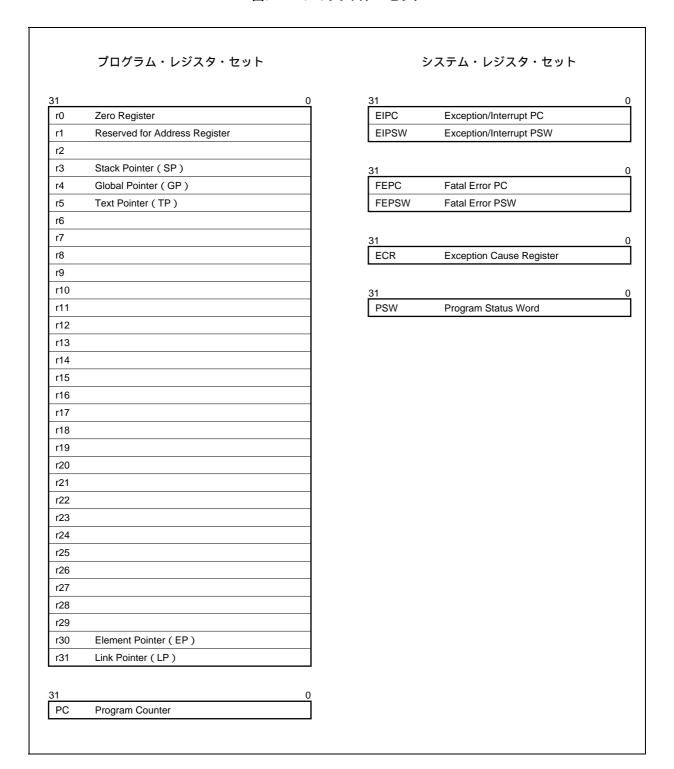

| p.69  | 3.2.1 <b>プログラム・レジスタ・セット</b> のr2レジスタの記述を変更                              |

| p.85  | 3.4.6(1) メモリ拡張モード・レジスタ (MM) に注を追加                                      |

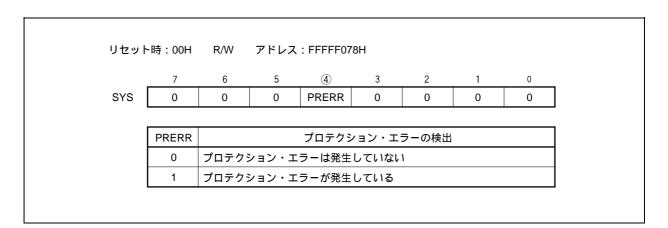

| p.99  | 3.4.9(2)システム・ステータス・レジスタ (SYS) に備考を追加                                   |

| p.116 | 4.9 <b>バスの優先順位</b> の記述を変更                                              |

| p.124 | 5.2.4 <b>外部割り込み要求入力端子のノイズ除去</b> の記述を変更                                 |

| p.126 | 5.2.5 <b>外部割り込み要求入力端子のエッジ検出機能</b> の記述を変更                               |

| p.133 | 5.3.4 <b>割り込み制御レジスタ (</b> xxICn <b>)</b> の記述を変更                        |

| p.147 | 5.8.1 EI <b>命令後の割り込み要求有効タイミング</b> を追加                                  |

| p.149 | 5.9 DMA <b>転送時の割り込み制御レジスタのピット操作命令</b> を追加                              |

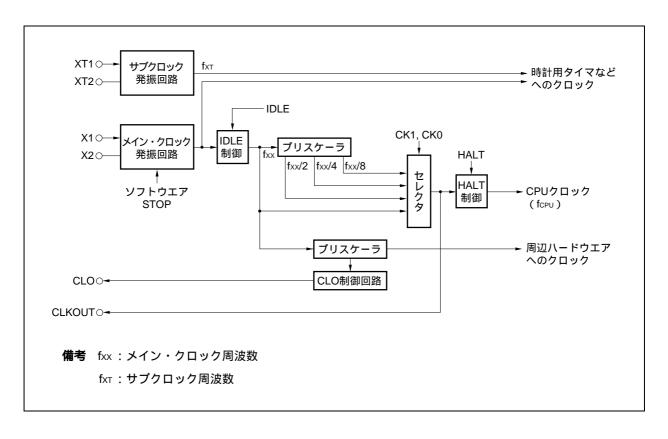

| p.150 | 6.1 概 要の記述を変更                                                          |

| p.151 | <b>図</b> 6 - 1 <b>クロック発生機能</b> を変更                                     |

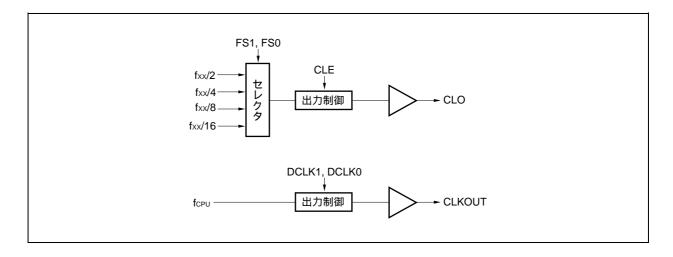

| p.152 | 6.3 <b>クロック出力機能</b> の記述を変更                                             |

| p.154 | 6. 4. 1 プロセッサ・クロック・コントロール・レジスタ (PCC) を変更                               |

| p.157 | 6.5.1 概 要を変更                                                           |

| p.159 | <b>表</b> 6 - 1 HALT <b>モード時の動作状態</b> を変更                               |

| p.165 | 6.6 発振安定時間の確保を変更                                                       |

| p.166 | 6.7 <b>パワー・セープ機能に関する注意事項</b> を追加                                       |

| p.228 | <b>図</b> 7 - 36 PPG <b>出力の構成図</b> を追加                                  |

| p.228 | 図7 - 37 PPG <b>出力動作のタイミング</b> を追加                                      |

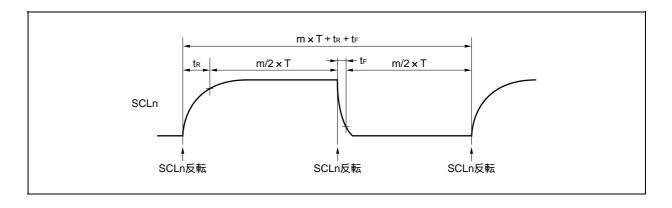

| p.307 | 10. 3. 2 <b>(</b> 5 <b>)</b> I <sup>2</sup> Cn <b>の転送クロックの設定方法</b> を追加 |

| p.308 | 表10 - 3 <b>選択クロックの設定</b> を変更                                           |

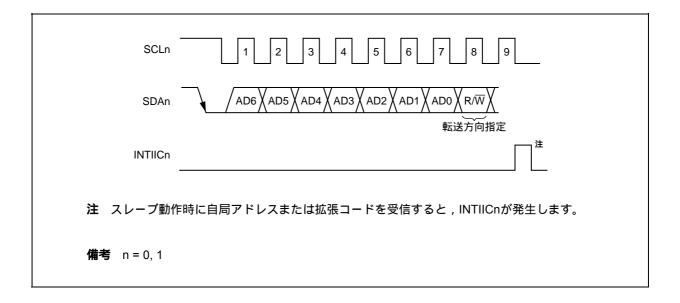

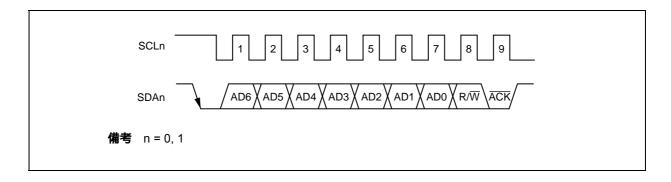

| p.318 | 10. 3. 5 I <sup>2</sup> C <b>割り込み要求(</b> INTIICn <b>)</b> を変更          |

| p.362 | 10. 4. 3 (2) アシンクロナス・シリアル・インタフェース・モードを変更                               |

| p.367 | 表10 - 9 メイン・クロックとボー・レートの関係を変更                                          |

| p.381 | 10.5.3 動作を変更                                                           |

| p.394 | 11.3.4 入力電圧と変換結果を追加                                                    |

| p.416 | 11.9 A/D <b>コンバータ特性表の読み方</b> を追加                                       |

| p.422 | 12.3 構成を追加                                                             |

| p.429 | 12.5 動作を追加                                                             |

| p.430 | 12.6 注 意を追加                                                            |

| p.437 | 13.5 使用方法を変更                                                           |

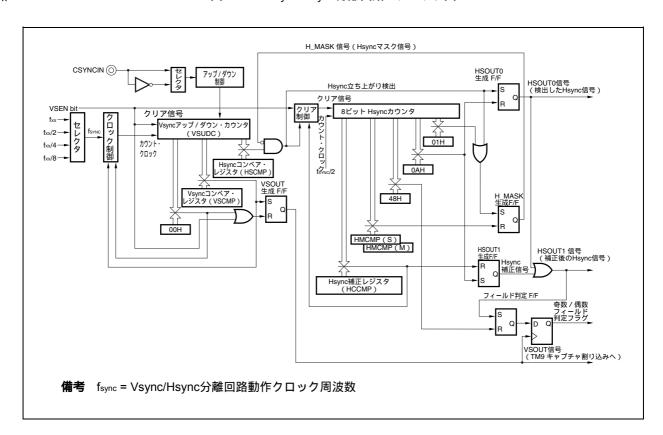

| p.452 | 図15 - 1 Vsync/Hsync <b>分離回路のブロック図</b> を変更                              |

| p.469 | <b>第</b> 16 <b>章 キー・リターン機能</b> を追加                                     |

| p.503 | 17. 2. 8 <b>(1)</b> P9 <b>端子の機能</b> に注意を追加                             |

### 本版で改訂された主な箇所(2/2)

| 箇 所                            | 内 容                                                                       |

|--------------------------------|---------------------------------------------------------------------------|

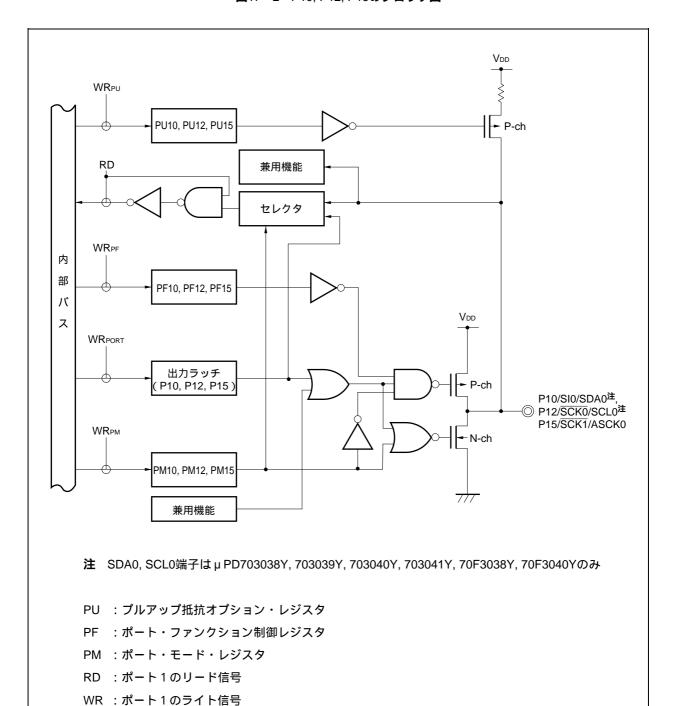

| p.507                          | 17. 2. 9 <b>(1)</b> P10 <b>端子の機能</b> に注意を追加                               |

| p.529                          | 17. 2. 14 <b>(1)</b> P15 <b>端子の機能</b> に注意を追加                              |

| p.541                          | 表17 - 19 ポート端子を兼用端子として使用する場合の設定を変更                                        |

| p.544                          | 17.4 <b>ポート機能の動作</b> を追加                                                  |

| p.550                          | 第20章 フラッシュ・メモリに注意を追加                                                      |

| p.551                          | 20. 1. 1 消去単位を追加                                                          |

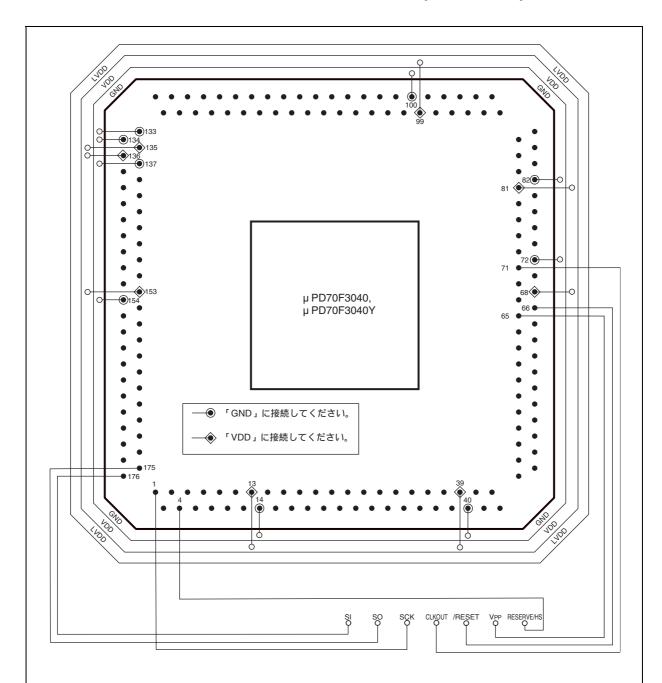

| p.553                          | <b>図</b> 20 - 1 V850/SV1 <b>フラッシュ書き込み用アダプタ(</b> FA-180FBGA)を追加            |

| p.554                          | 表20 - 1 V850/SV1 <b>フラッシュ書き込み用アダプタ (</b> FA-180FBGA) <b>の配線表</b> を追加      |

| p.555                          | <b>図</b> 20 - 2 V850/SV1 <b>フラッシュ書き込み用アダプタ(</b> FA-176GM-UEU <b>)</b> を追加 |

| p.556                          | 表20 - 2 V850/SV1 <b>フラッシュ書き込み用アダプタ (</b> FA-176GM-UEU <b>) の配線表</b> を追加   |

| p.558                          | 20.4 (3) CSIO+HSを追加                                                       |

| p.558                          | 表20 - 3 専用フラッシュ・ライタ (PG-FP3) の信号生成を変更                                     |

| p.560                          | 表20 - 4 <b>各シリアル・インタフェースが使用する端子</b> を変更                                   |

| p.567                          | <b>第</b> 21 <b>章 電気的特性</b> を追加                                            |

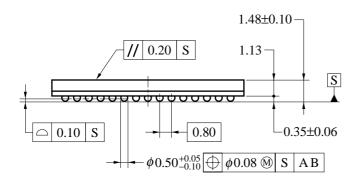

| p.592                          | <b>第</b> 22 <b>章 外形図</b> を追加                                              |

| p.594                          | 第23章 半田付け推奨条件を追加                                                          |

| p.622                          | <b>付録</b> D <b>改版履歴</b> を追加                                               |

| 修正版(U14462JJ2V1UD00)で改訂された主な箇所 |                                                                           |

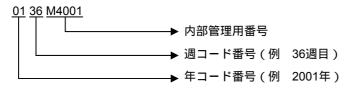

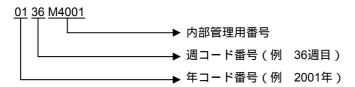

| p.33                           | 1.4 オーダ情報を変更                                                              |

| p.595, 596                     | 第23章 半田付け推奨条件を変更                                                          |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

### はじめに

- 対象者 このマニュアルは , V850/SV1 (μ PD703038, 703038Y, 703039, 703039Y, 703040, 703040Y, 703041, 703041Y, 70F3038, 70F3038Y, 70F3040, 70F3040Y) の機能を理解し , それを用いた応用システムを設計するユーザを対象とします。

- **的** このマニュアルは,次の構成に示すハードウエア機能をユーザに理解していただくことを目的としています。

- 構 成 V850/SV1のユーザーズ・マニュアルは ,ハードウエア編( このマニュアル )と ,アーキテクチャ編( V850 シリーズ ユーザーズ・マニュアル アーキテクチャ編) の2冊に分かれています。

ハードウエア編

- ・端子機能

- ·CPU機能

- ・内蔵周辺機能

- ・フラッシュ・メモリ・プログラミング

- ・電気的特性

アーキテクチャ編

- ・データ・タイプ

- ・レジスタ・セット

- ・命令形式と命令セット

- ・割り込みと例外

- ・パイプラインの動作

- 読み方 このマニュアルの読者には、電気、論理回路、およびマイクロコンピュータに関する一般知識を必要とします。

レジスタ名が分かっていて,レジスタの詳細を確認するとき **付録**A **レジスタ索引**を利用してください。

機能名などが分かっていて、その詳細を確認するとき

付録C 総合索引を利用してください。

命令機能の詳細を理解しようとするとき

別冊のV850**シリーズ ユーザーズ・マニュアル アーキテクチャ編**を参照してください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは,そのビット名称がデバイス・ファイルで予約語に定義されているものです。

一通りV850/SV1の機能を理解しようとするとき 目次に従ってお読みください。

V850/SV1の電気的特性を知りたいとき

第21章 電気的特性を参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : xxx (端子,信号名称に上線)

メモリ・マップのアドレス:上部-上位,下部-下位 注: 本文中に付けた注の説明

注意: 気を付けて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数 ... xxxxまたはxxxxB

10進数 ... xxxx 16進数 ... xxxxH

2のべき数を示す接頭語(アドレス空間,メモリ容量):

K(キロ):  $2^{10}$  = 1024 M(メガ):  $2^{20}$  = 1024<sup>2</sup> G(ギガ):  $2^{30}$  = 1024<sup>3</sup>

**関連資料** 関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめ ご了承ください。

#### V850/SV1**に関する資料**

| 資料名                           | 資料番号    |

|-------------------------------|---------|

| V850シリーズ ユーザーズ・マニュアル アーキテクチャ編 | U10243J |

| V850/SV1 ユーザーズ・マニュアル ハードウエア編  | このマニュアル |

#### 開発ツールに関する資料(ユーザーズ・マニュアル)

| 資料                                | 名                  | 資料番号    |

|-----------------------------------|--------------------|---------|

| IE-703002-MC(インサーキット・エミュレータ)      |                    | U11595J |

| IE-703040-MC-EM1(V850/SV1用インサーキット | ・エミュレータ・オプション・ボード) | U14337J |

| CA850 Ver.2.50 Cコンパイラ・パッケージ       | 操作編                | U16053J |

|                                   | C言語編               | U16054J |

|                                   | PM plus編           | U16055J |

|                                   | アセンブリ言語編           | U16042J |

| ID850 Ver.2.50 統合ディバッガ            | 操作編                | U16217J |

| RX850 Ver.3.13以上 リアルタイムOS         | 基礎編                | U13430J |

|                                   | インストレーション編         | U13410J |

|                                   | テクニカル編             | U13431J |

| RX850 Pro Ver.3.15 リアルタイムOS       | 基礎編                | U13773J |

|                                   | インストレーション編         | U13774J |

|                                   | テクニカル編             | U13772J |

| RD850 Ver.3.01 タスク・ディバッガ          |                    | U13737J |

| RD850 Pro Ver.3.01 タスク・ディバッガ      |                    | U13916J |

| AZ850 Ver.3.0 システム・パフォーマンス・アナライザ  |                    | U14410J |

| PG-FP3 フラッシュ・メモリ・プログラマ            |                    | U13502J |

| PG-FP4 フラッシュ・メモリ・プログラマ            |                    | U15260J |

## 目 次

| 第1章  | イントロダクション 30                             |

|------|------------------------------------------|

| 1. 1 | 概 説 30                                   |

| 1. 2 | 特 徵 31                                   |

|      | <b>応用分野</b> 33                           |

|      | <b>オーダ情報</b> 33                          |

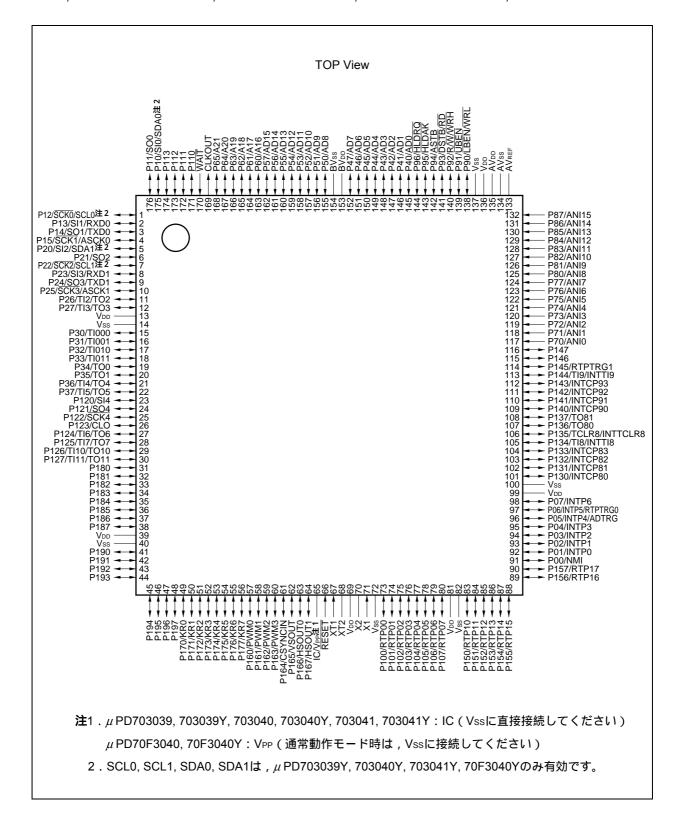

|      | <b>端子接続図</b> 34                          |

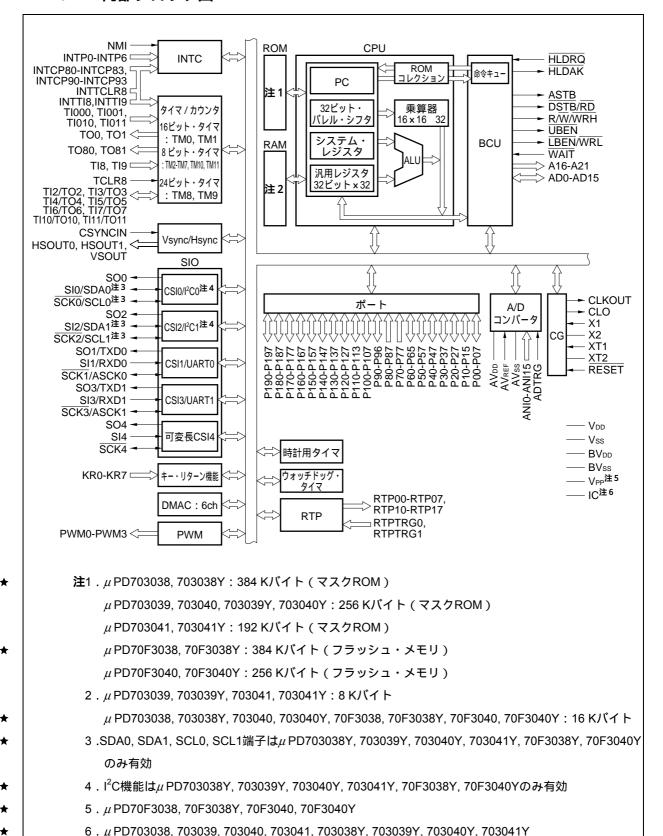

| 1. 6 | 機能プロック構成 38                              |

|      | 1.6.1 内部プロック図 38                         |

|      | 1. 6. 2 内部ユニット 39                        |

| 第2章  | <b>端子機能</b> 42                           |

| 2. 1 | <b>端子機能一覧</b> 42                         |

| 2. 2 | <b>端子状態</b> 50                           |

|      | 端子機能の説明 51                               |

|      | 端子の入出力回路タイプ,入出力バッファ電源と未使用時の処理 63         |

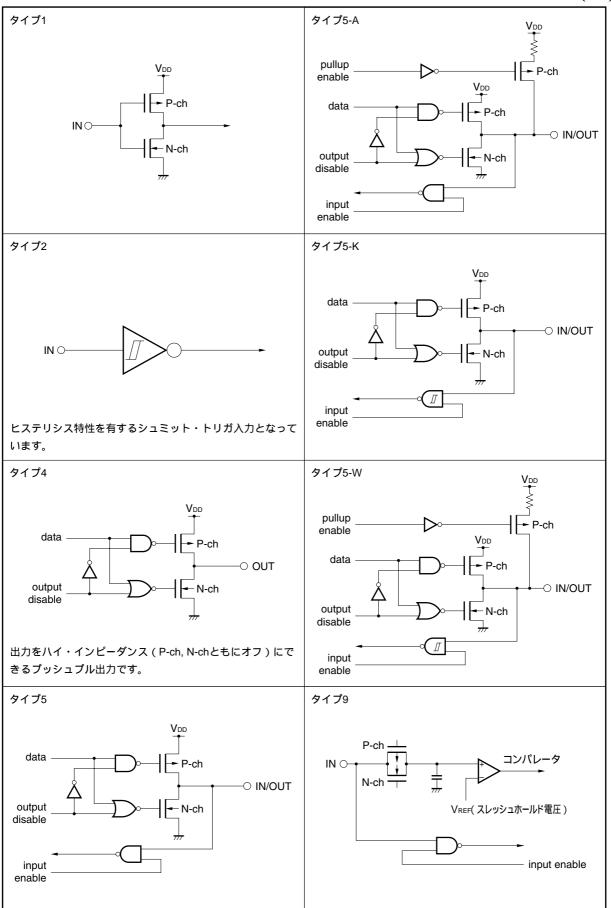

| 2. 5 | <b>端子の入出力回路</b> 65                       |

| 第3章  | CPU <b>機能</b> 67                         |

| 3. 1 | 特 徵 67                                   |

| 3. 2 | CPU <b>レジスタ・セット</b> 68                   |

|      | 3.2.1 プログラム・レジスタ・セット 69                  |

|      | 3.2.2 システム・レジスタ・セット 70                   |

|      | 動作モード 73                                 |

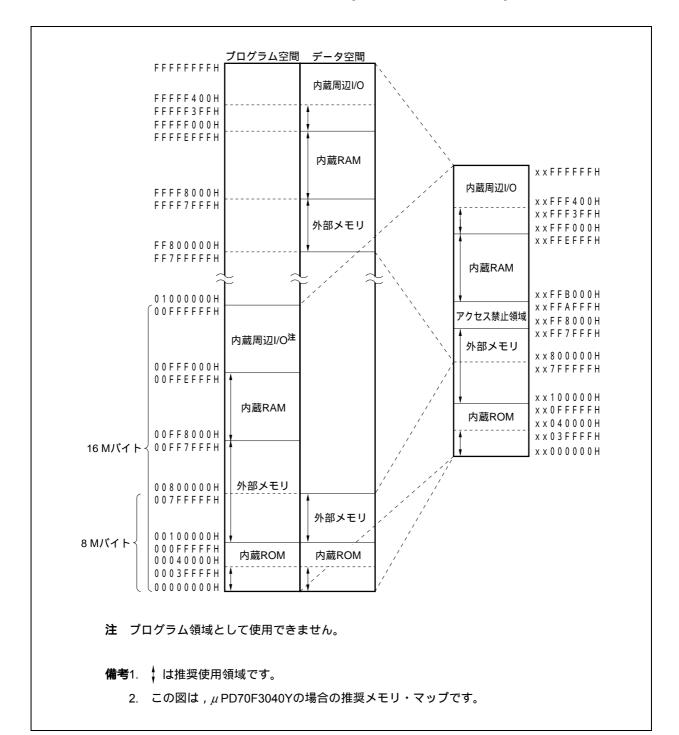

| 3. 4 | <b>アドレス空間</b> 74<br>3. 4. 1 CPUアドレス空間 74 |

|      | 3.4.2 イメージ 75                            |

|      | 3.4.3 CPUアドレス空間のラップ・アラウンド 76             |

|      | 3.4.4 メモリ・マップ 77                         |

|      | 3. 4. 5 領 域 78                           |

|      | 3.4.6 外部拡張モード 85                         |

|      | 3. 4. 7 アドレス空間の推奨使用方法 86                 |

|      | 3. 4. 8 周辺I/Oレジスタ 88                     |

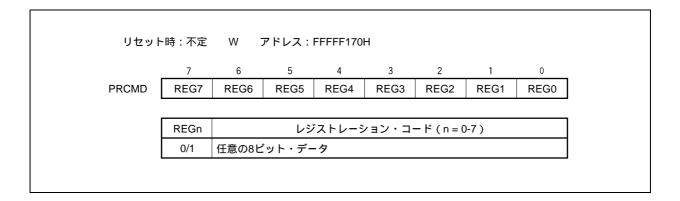

|      | 3. 4. 9 特定レジスタ 96                        |

| 第4章  | <b>バス制御機能</b> 100                        |

| 4. 1 | 特 徵 100                                  |

|      | バス制御端子と制御レジスタ 100                        |

|      | 4. 2. 1 バス制御端子 100                       |

|      | 4. 2. 2 制御レジスタ 101                       |

4.3 **パス・アクセス** ... 101

- 4.3.1 アクセス・クロック数 ... 101 4.3.2 バス幅 ... 101 4.4 メモリ・ブロック機能 ... 103 4.5 ウエイト機能 ... 104 4.5.1 プログラマブル・ウエイト機能 ... 104 4.5.2 外部ウエイト機能 ... 105 4.5.3 プログラマブル・ウエイトと外部ウエイトの関係 ... 105 4.6 アイドル・ステート挿入機能 ... 106 4.7 パス・ホールド機能 ... 107 4.7.1 機能概要 ... 107 4.7.2 バス・ホールド手順 ... 108 4.7.3 パワー・セーブ・モード時の動作 ... 108 4.8 パス・タイミング ... 109 4.9 バスの優先順位 ... 116 4.10 境界動作条件 ... 116 4. 10. 1 プログラム空間 ... 116 4. 10. 2 データ空間 ... 116 **第5章 割り込み/例外処理機能** ... 117 5.1 概 要 ... 117 5.1.1 特 徵 ... 117 5.2 ノンマスカブル割り込み ... 120 5.2.1 動 作 ... 121 5.2.2 復 帰 ... 123 5.2.3 NPフラグ ... 124 5.2.4 外部割り込み要求入力端子のノイズ除去 ... 124 5.2.5 外部割り込み要求入力端子のエッジ検出機能 ... 126 5.3 マスカブル割り込み ... 127 5.3.1 動 作 ... 127 5.3.2 復 帰 ... 129 5.3.3 マスカブル割り込みの優先順位 ... 130 5.3.4 割り込み制御レジスタ (xxlCn)... 133 5.3.5 インサービス・プライオリティ・レジスタ (ISPR)... 137 5.3.6 IDフラグ ... 138 5. 3. 7 ウォッチドッグ・タイマ・モード・レジスタ (WDTM)... 138 5.4 ソフトウエア例外 ... 139 5.4.1 動 作 ... 139 5.4.2 復 帰 ... 140 5.4.3 EPフラグ ... 141 5.5 例外トラップ ... 141 5.5.1 不正命令コード ... 141 5.5.2 動 作 ... 142

- 5.6.2 多重割り込み ... 144 5.7 **応答時間** ... 146

5.6 **優先順位指定** ... 144

5.8 割り込みが受け付けられない期間 ... 147

5.6.1 割り込みと例外の優先順位 ... 144

5.5.3 復 帰 ... 143

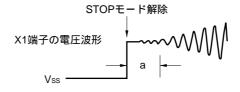

5.8.1 EI命令後の割り込み要求有効タイミング ... 147 5.9 DMA**転送時の割り込み制御レジスタのビット操作命令** ... 149 第6章 クロック発生機能 ... 150 6.1 概 要 ... 150 成 ... 151 6.2 構 6.3 クロック出力機能 ... 152 6.3.1 CLKOUT信号 ... 152 6.3.2 CLO信号 ... 153 6.4 制御レジスタ ... 154 6.4.1 プロセッサ・クロック・コントロール・レジスタ(PCC)... 154 6.4.2 クロック出力モード・レジスタ (CLOM)... 155 6.4.3 パワー・セーブ・コントロール・レジスタ (PSC) ... 156 6.4.4 発振安定時間選択レジスタ(OSTS)... 157 6.5 パワー・セーブ機能 ... 157 6.5.1 概 要 ... 157 6.5.2 HALTモード ... 158 6.5.3 IDLEモード ... 161 6.5.4 ソフトウエアSTOPモード ... 163 6.6 発振安定時間の確保 ... 165 6.7 パワー・セーブ機能に関する注意事項 ... 166 第7章 タイマ/カウンタ機能 ... 167 7.1 24**ビット・タイマ (**TM8, TM9**)**... 167 要 ... 167 7.1.1 概 7.1.2 V850/SV1とV854の24ビット・タイマ動作の違い ... 168 7.1.3 機 能 ... 170 成 ... 172 7. 1. 4 構 7.1.5 タイマ8,9制御レジスタ ... 175 7.1.6 分周器 ... 183 7.2 24ビット・タイマ (TM8) の動作 ... 186 7.2.1 カウント動作 ... 186 7.2.2 カウント・クロック選択 ... 187 7.2.3 オーバフロー ... 188 7.2.4 タイマのクリア/スタート ... 189 7.2.5 キャプチャ動作 ... 192 7.2.6 コンペア動作 ... 195 7.3 24ビット・タイマ (TM9) の動作 ... 197 7.3.1 カウント動作 ... 197 7.3.2 カウント・クロック選択 ... 198 7.3.3 オーバフロー ... 199 7.3.4 タイマのクリア/スタート ... 200 7.3.5 キャプチャ動作 ... 201

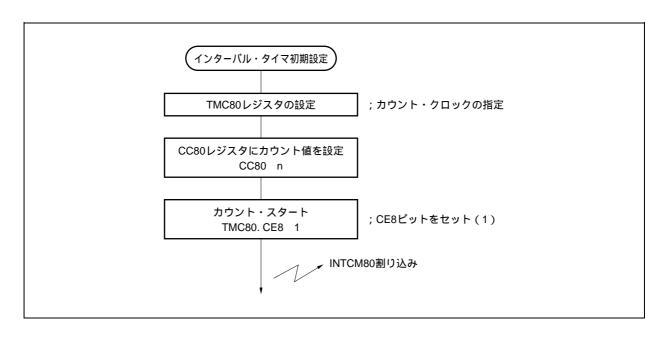

7.3.6 コンペア動作 ... 202 7.4 24**ビット・タイマの応用例** ... 203 7.5 24**ビット・タイマの注意事項** ... 210 7.6 16**ビット・タイマ (**TM0, TM1**)** ... 212

|             | 7. 6. 1 概  要 212                                    |

|-------------|-----------------------------------------------------|

|             | 7. 6. 2 機  能 212                                    |

|             | 7. 6. 3 構   成  214                                  |

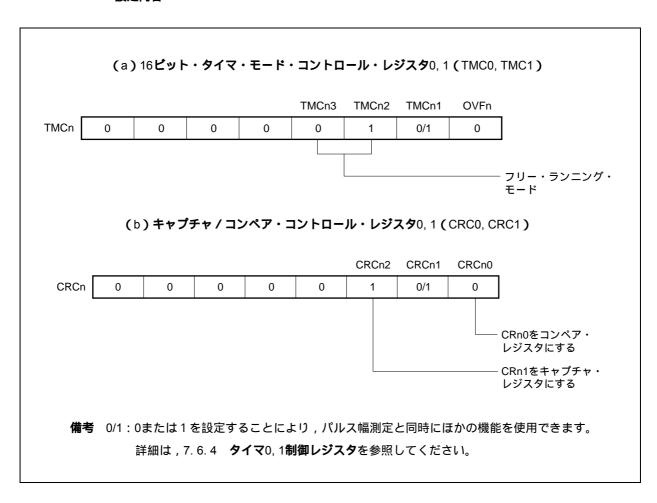

|             | 7. 6. 4 タイマ0, 1制御レジスタ 217                           |

| 7. 7        | 16 <b>ビット・タイマの動作</b> 225                            |

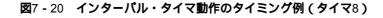

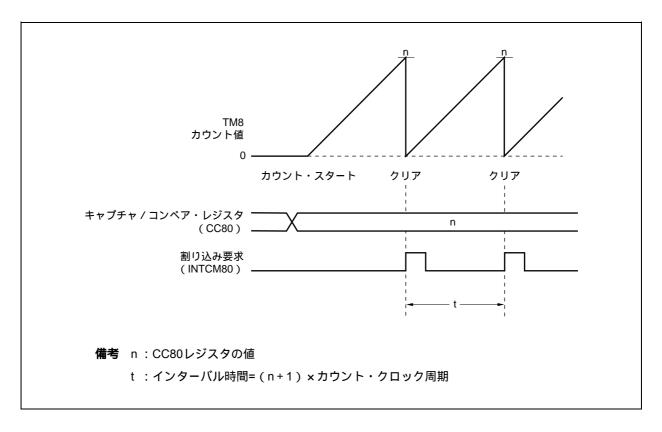

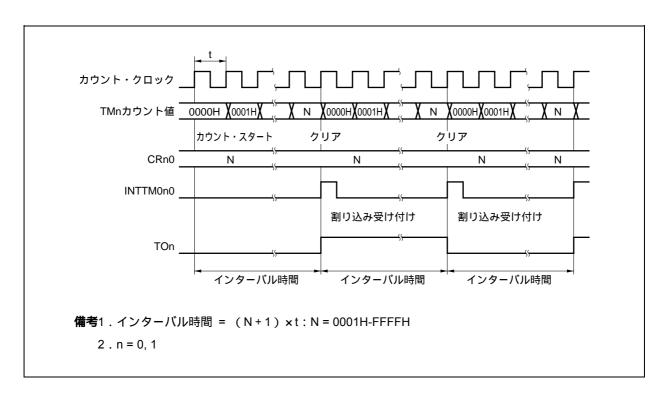

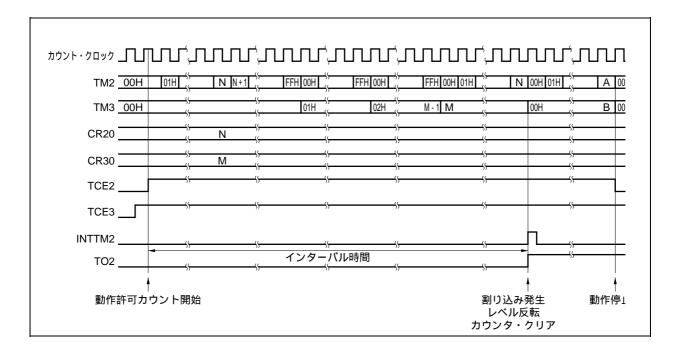

|             | 7.7.1 インターバル・タイマ(16ビット)としての動作 225                   |

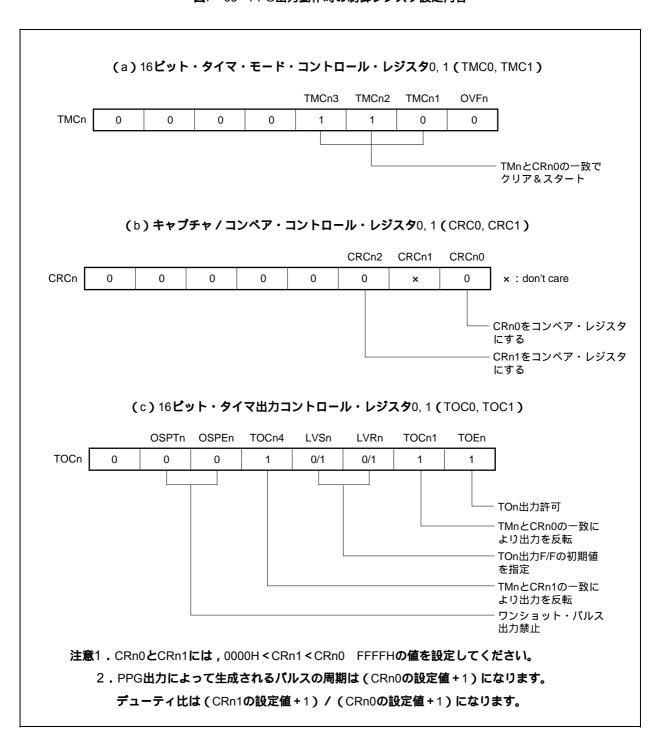

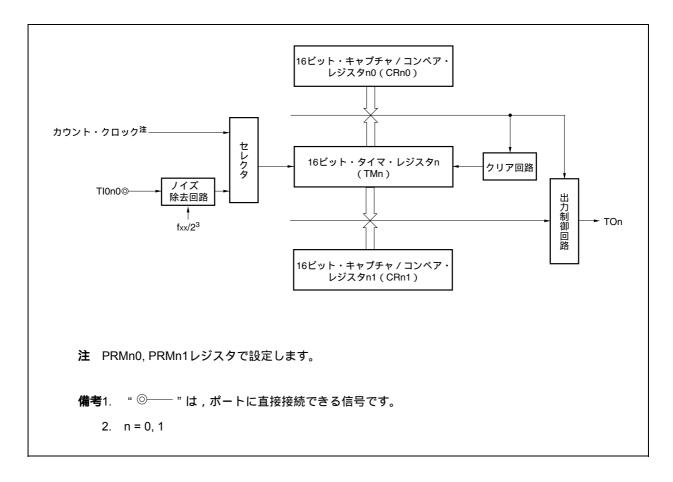

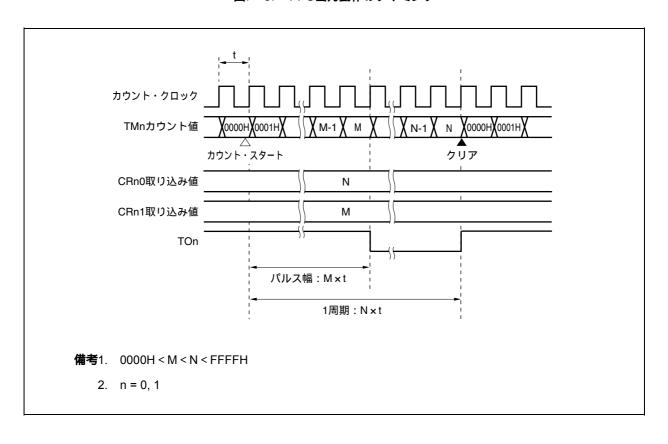

|             | 7.7.2 PPG出力としての動作 227                               |

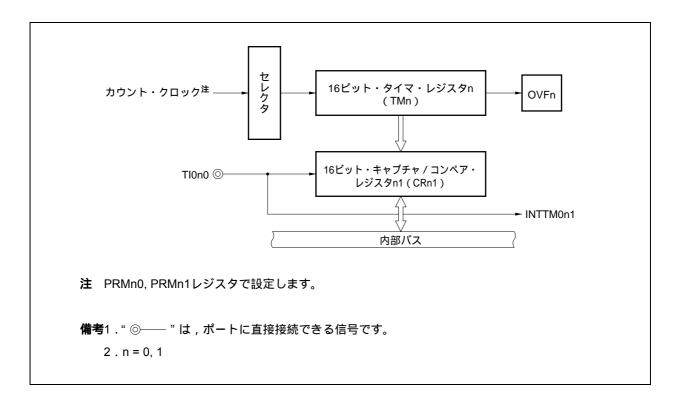

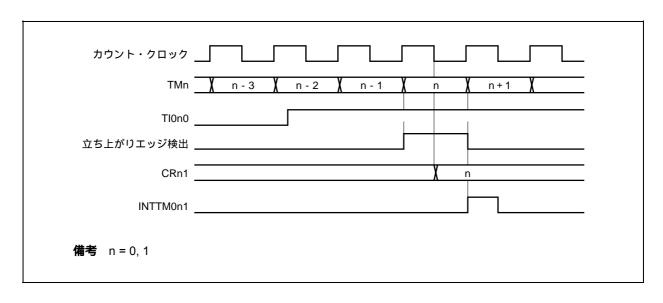

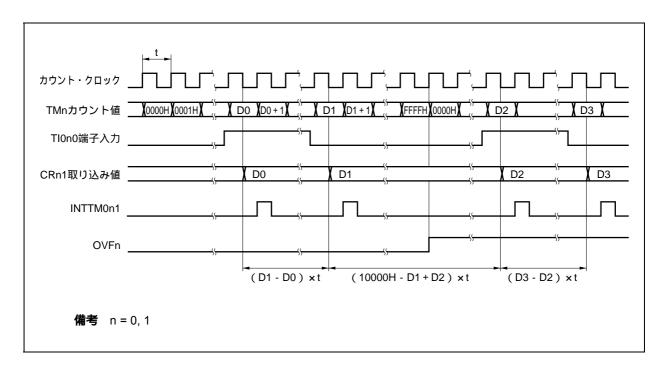

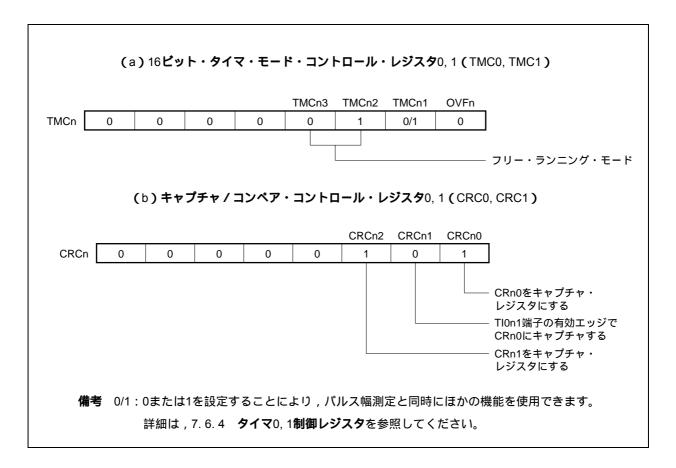

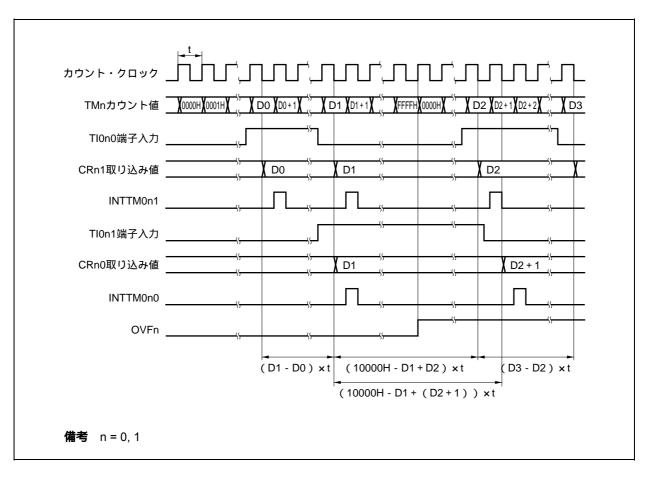

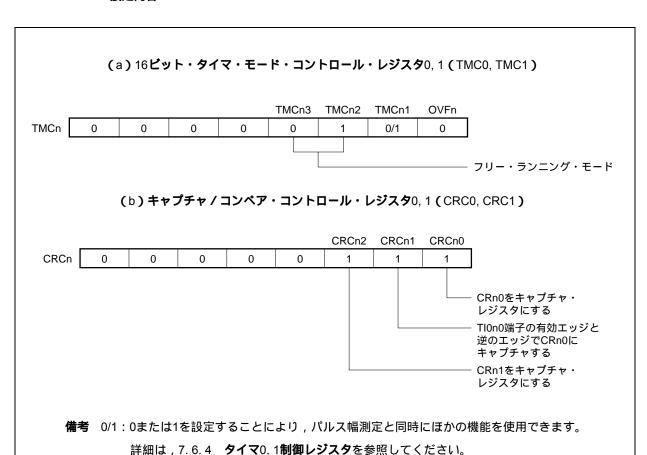

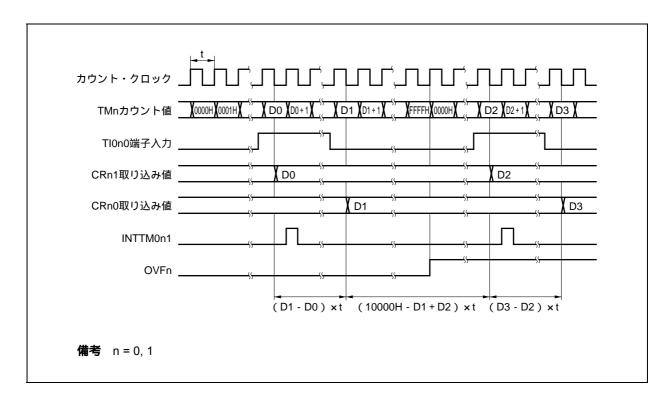

|             | 7.7.3 パルス幅測定としての動作 229                              |

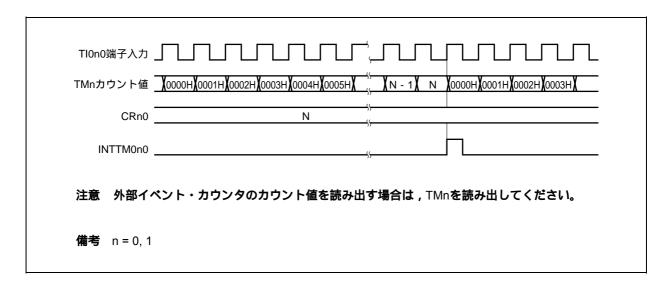

|             | 7. 7. 4 外部イベント・カウンタとしての動作 236                       |

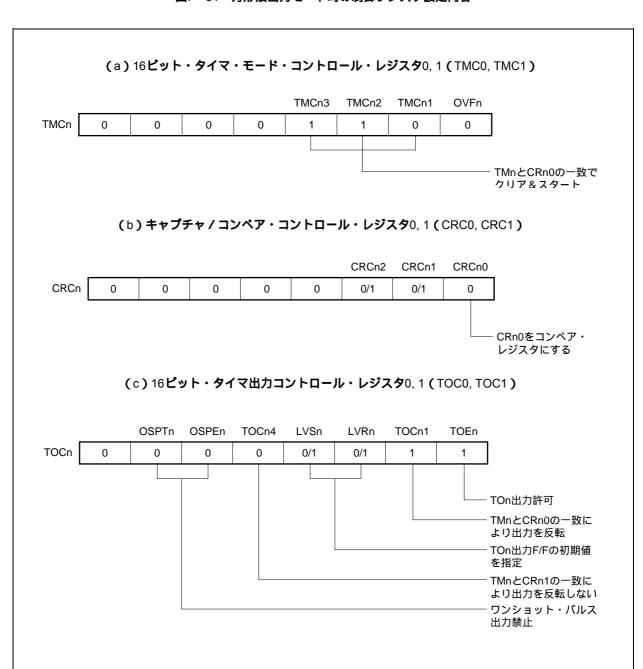

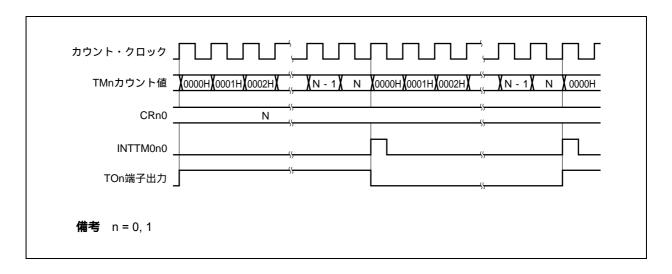

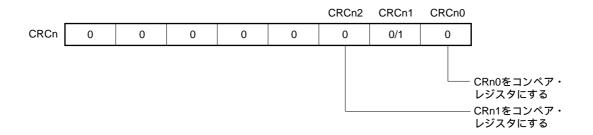

|             | 7. 7. 5 方形波出力としての動作 238                             |

|             | 7. 7. 6 ワンショット・パルス出力としての動作 239                      |

|             | 7. 7. 7 注意事項 244                                    |

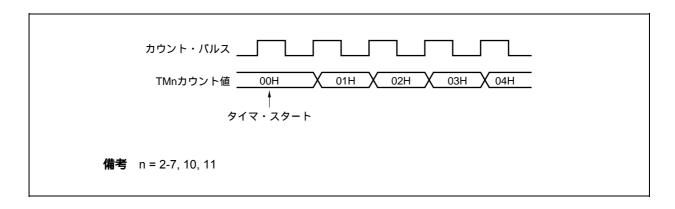

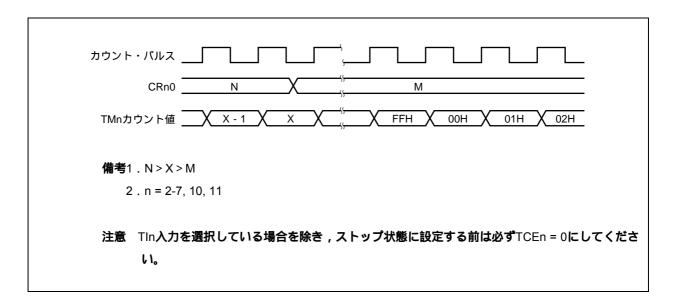

| 7. 8        | 8 <b>ビット・タイマ (</b> TM2-TM7, TM10, TM11 <b>)</b> 250 |

|             | 7. 8. 1 機 能 250                                     |

|             | 7. 8. 2 構 成 251                                     |

|             | 7.8.3 タイマn制御レジスタ 253                                |

| 7. 9        | 8 <b>ビット・タイマの動作</b> 260                             |

|             | 7.9.1 インターバル・タイマ (8ビット) としての動作 260                  |

|             | 7. 9. 2 外部イベント・カウンタとしての動作 263                       |

|             | 7.9.3 方形波出力(8ビット分解能)としての動作 264                      |

|             | 7. 9. 4 8ビットPWM出力としての動作 265                         |

|             | 7.9.5 インターバル・タイマ (16ビット) としての動作 268                 |

|             | 7.9.6 注意事項 270                                      |

|             |                                                     |

| <b>第</b> 8章 | 時計用タイマ機能 271                                        |

| 0.4         | ₩ <b>क</b> 074                                      |

| 8. 1        | 概 要 271<br>機 能 271                                  |

|             | 機 成 272                                             |

|             | 制御レジスタ 273                                          |

|             | 動作 … 275                                            |

| 0. 5        | 8.5.1 時計用タイマとしての動作 275                              |

|             | 8.5.2 インターバル・タイマとしての動作 275                          |

|             | 8.5.3 注意事項 276                                      |

|             | 0. 0. 0 /工志事员 270                                   |

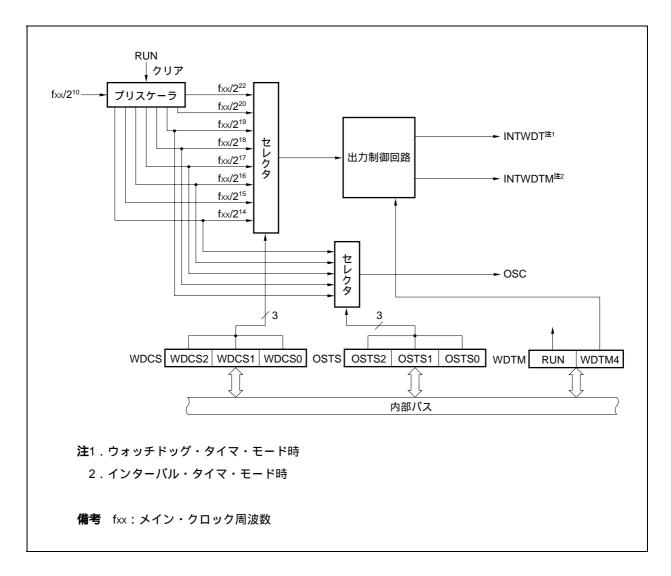

| <b>第</b> 9章 | <b>ウォッチドッグ・タイマ機能</b> 277                            |

|             |                                                     |

|             | 機 能 277                                             |

|             | 構成 279                                              |

|             | ウォッチドッグ・タイマ制御レジスタ 279                               |

| 9. 4        | 動 作 282                                             |

|             | 9.4.1 ウォッチドッグ・タイマとしての動作 282                         |

| • -         | 9.4.2 インターバル・タイマとしての動作 283                          |

| 9. 5        | スタンパイ機能制御レジスタ 284                                   |

| 第10章        | シリアル・インタフェース機 <b>能</b> 285                          |

|             |                                                     |

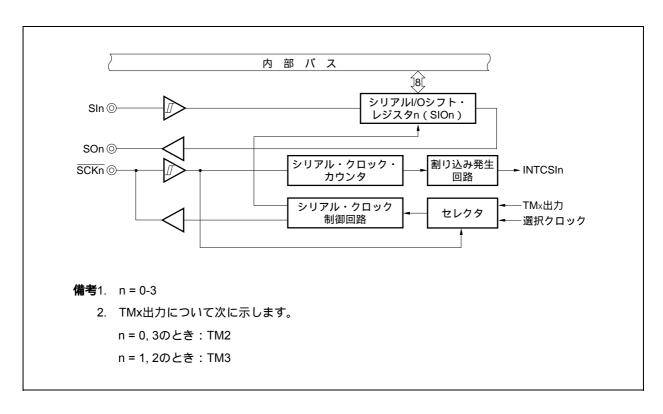

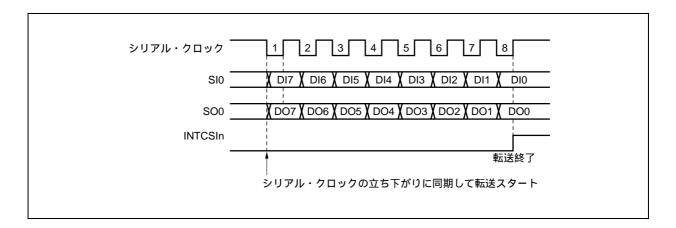

# 10.2 3線式シリアルI/O (CSI0-CSI3)... 285

10.1 概 要 ... 285

```

10. 2. 1 構

成 ... 286

10.2.2 CSIn制御レジスタ ... 287

10.2.3 動

作 ... 290

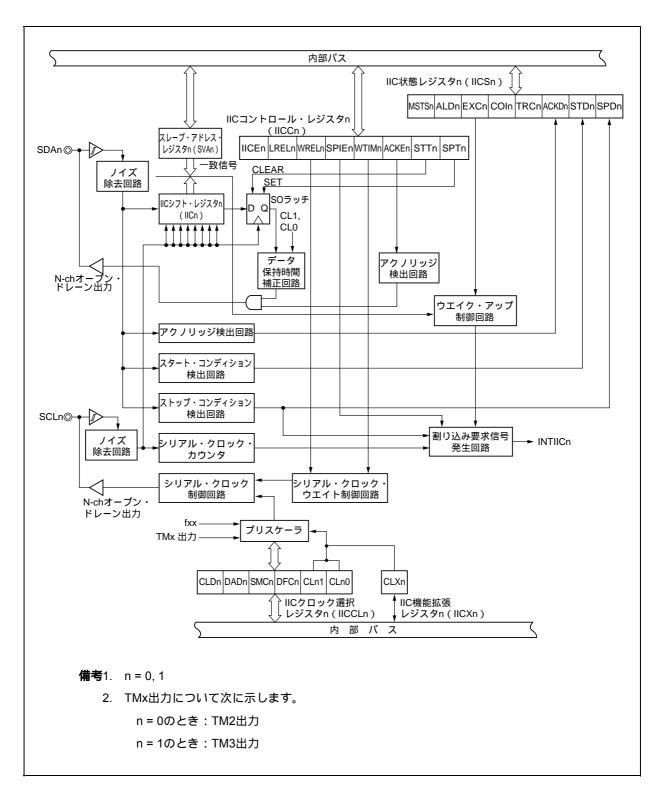

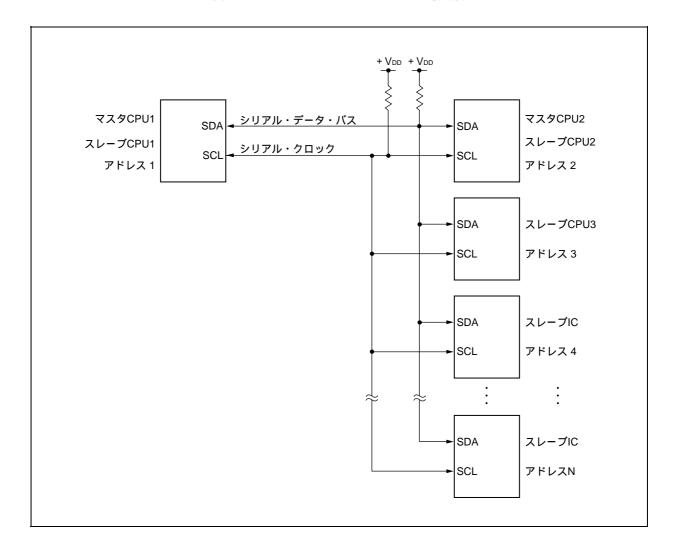

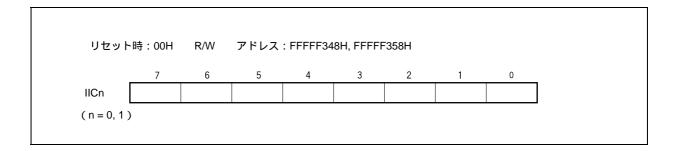

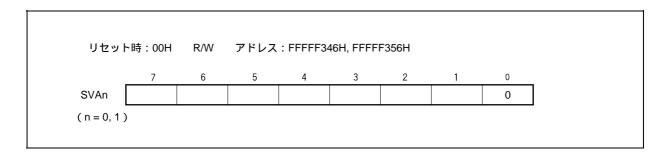

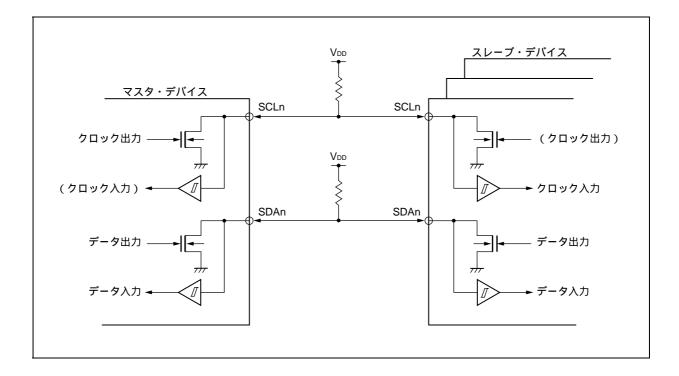

10.3 I<sup>2</sup>Cバス ... 293

成 ... 296

10.3.1 構

10.3.2 I<sup>2</sup>C制御レジスタ ... 298

10.3.3 I<sup>2</sup>Cバス・モードの機能 ... 310

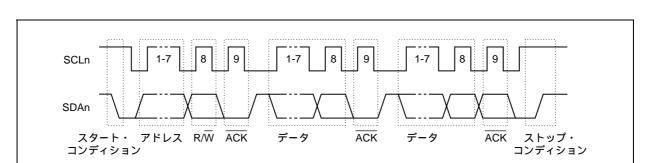

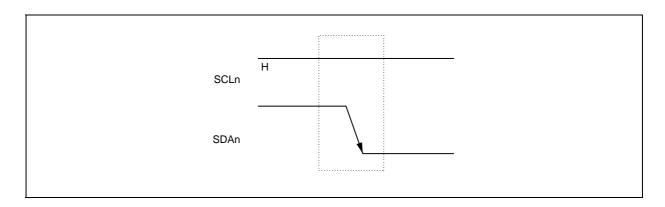

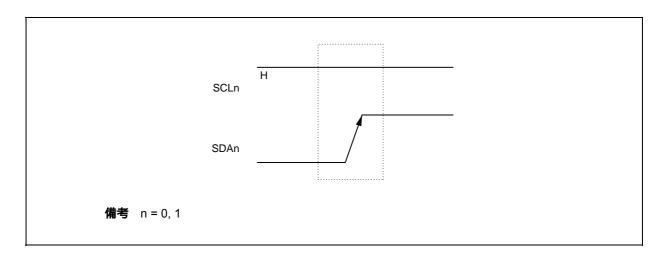

10.3.4 I<sup>2</sup>Cバスの定義および制御方法 ... 311

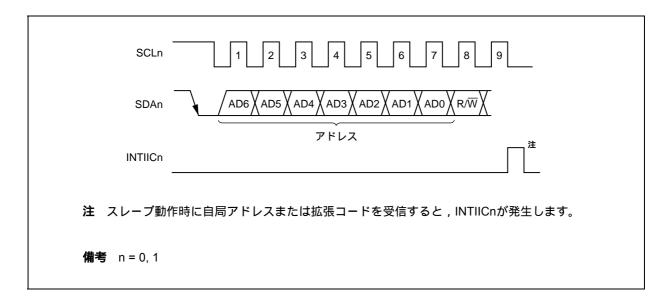

10.3.5 I<sup>2</sup>C割り込み要求(INTIICn)... 318

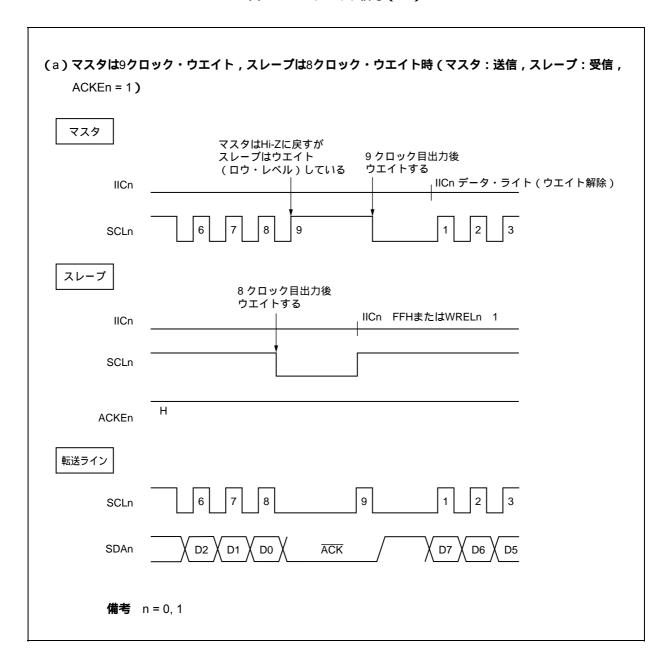

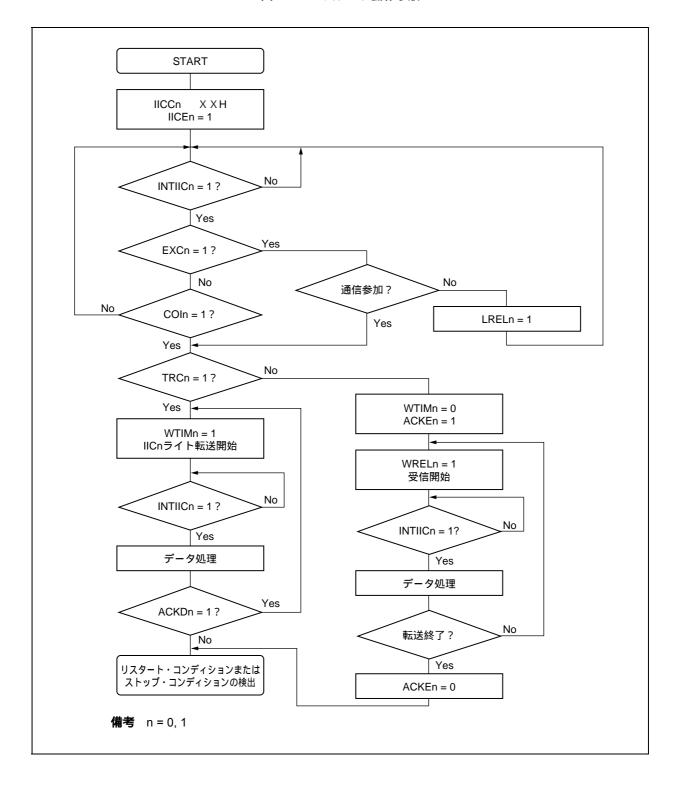

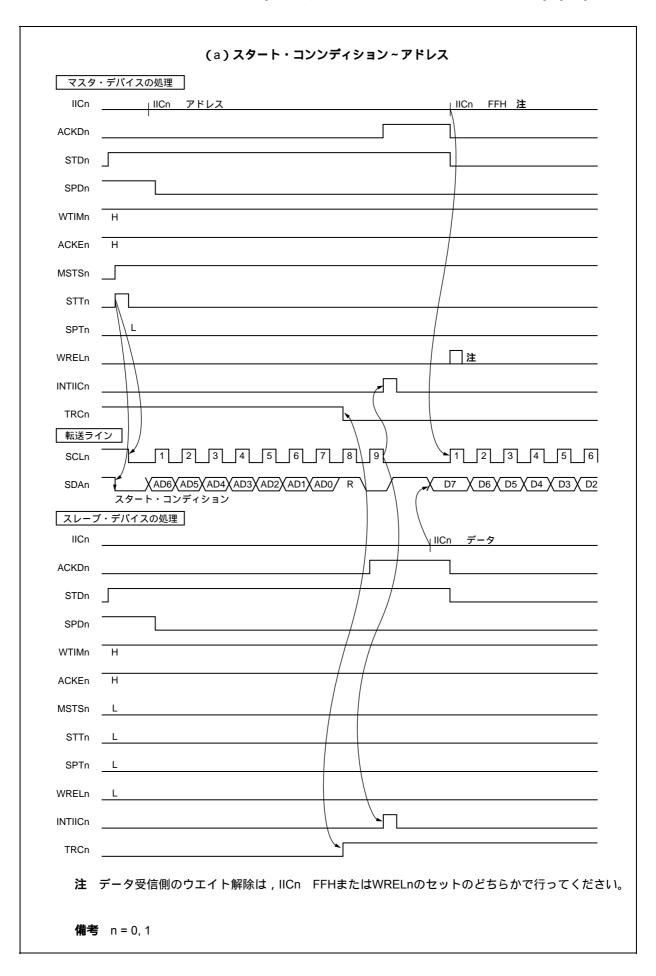

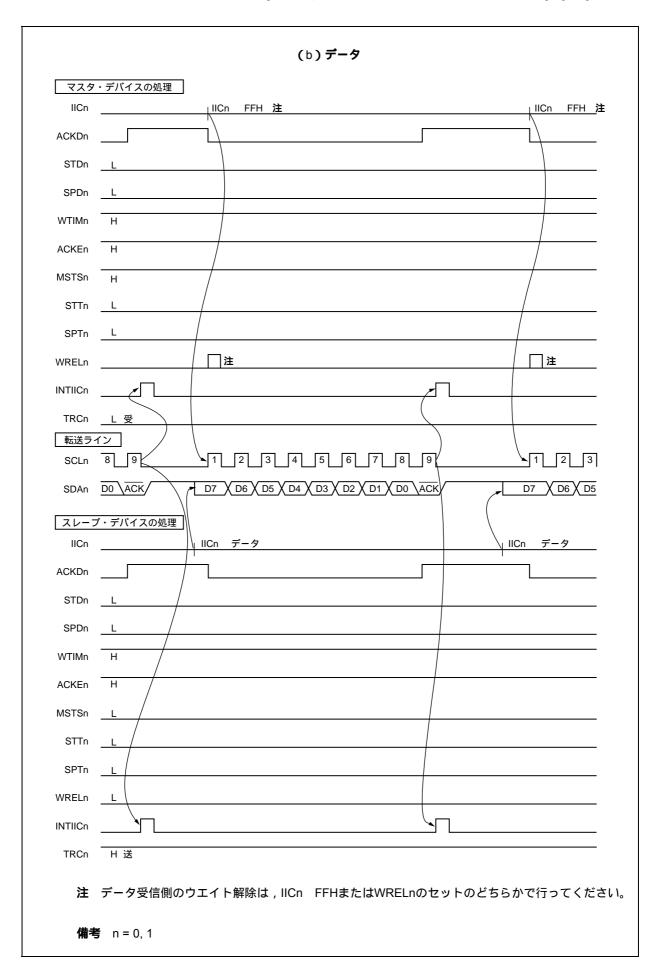

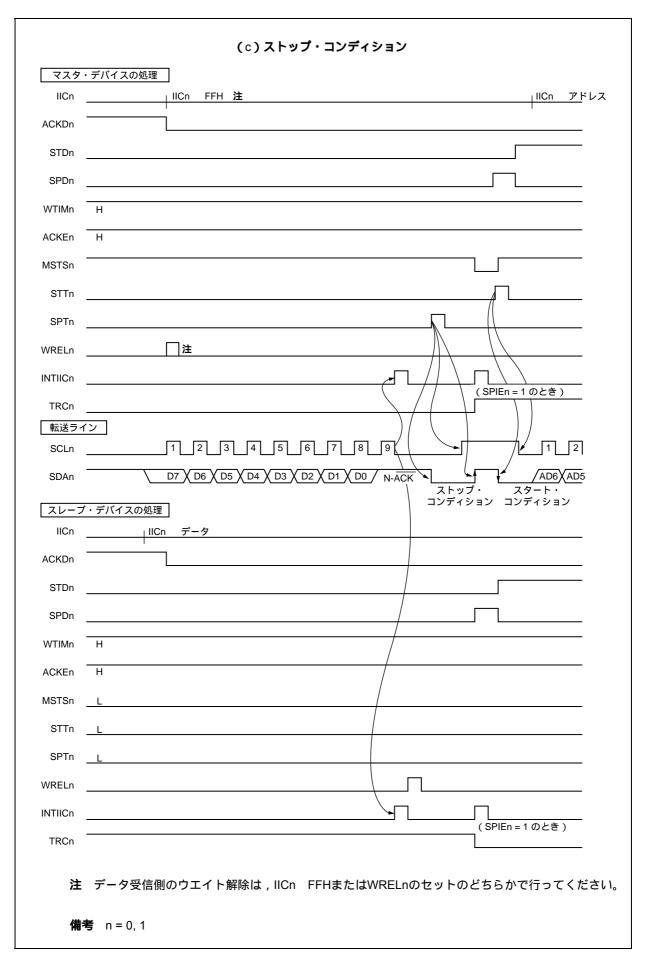

10.3.6 割り込み要求 (INTIICn) 発生タイミングおよびウエイト制御 ... 336

10.3.7 アドレスの一致検出方法 ... 337

10.3.8 エラーの検出 ... 337

10.3.9 拡張コード ... 337

10.3.10 アービトレーション ... 338

10.3.11 ウエイク・アップ機能 ... 339

10.3.12 通信予約 ... 340

10.3.13 注意事項 ... 343

10.3.14 通信動作 ... 344

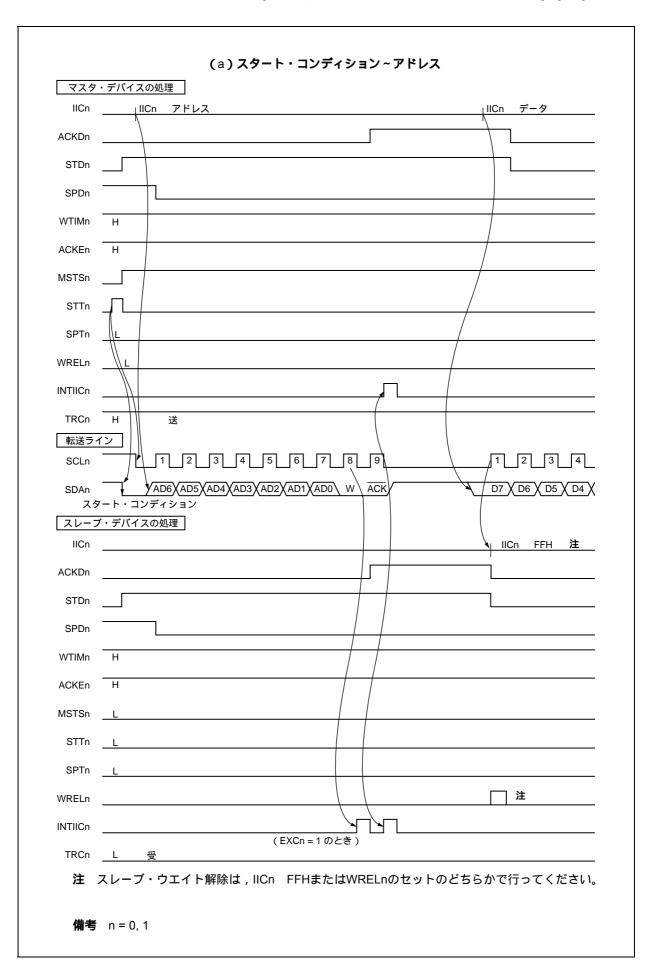

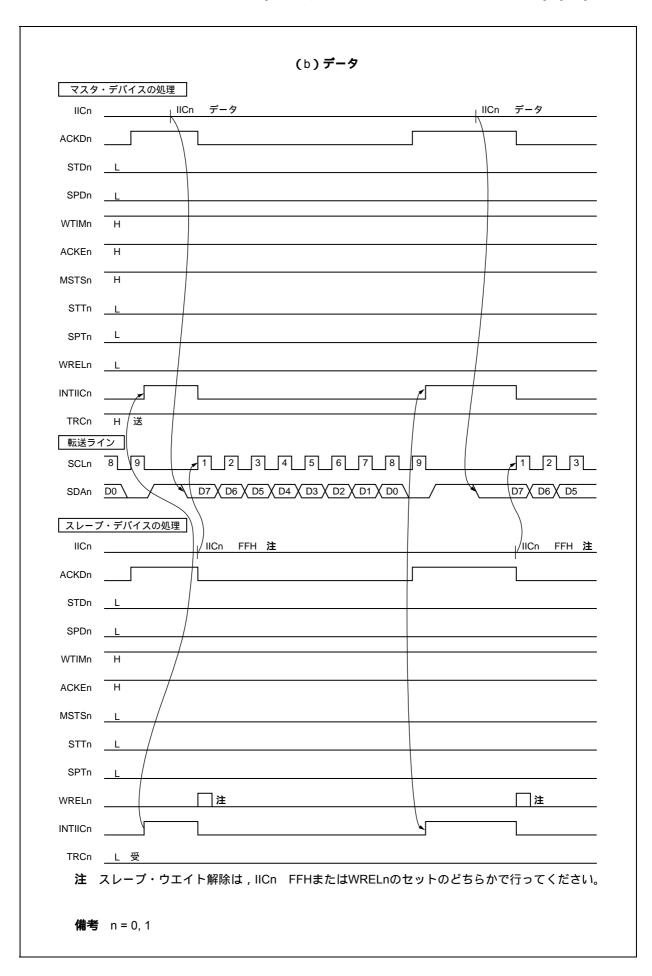

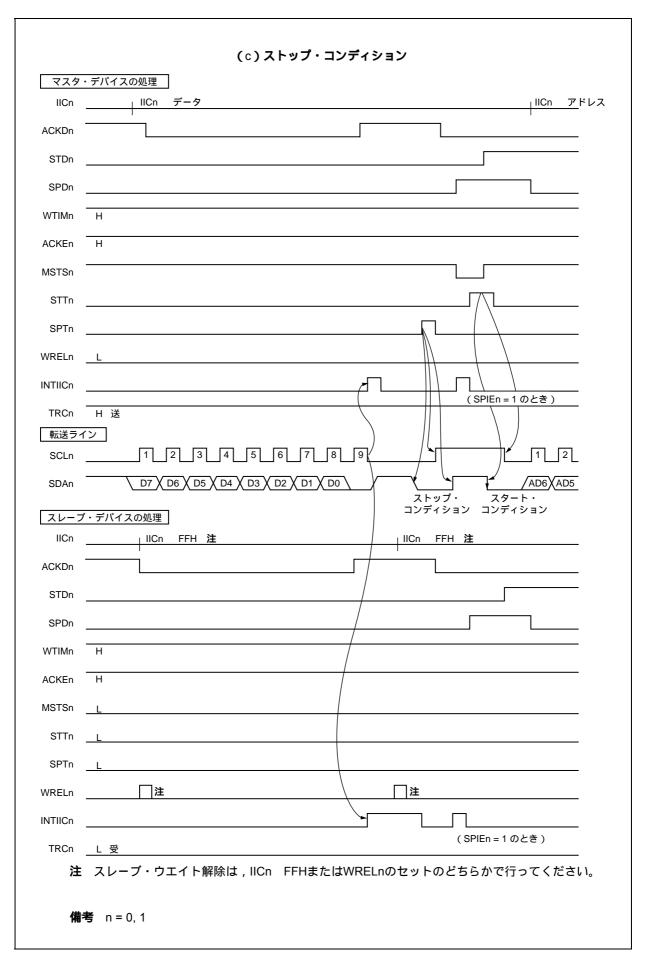

10.3.15 データ通信のタイミング ... 346

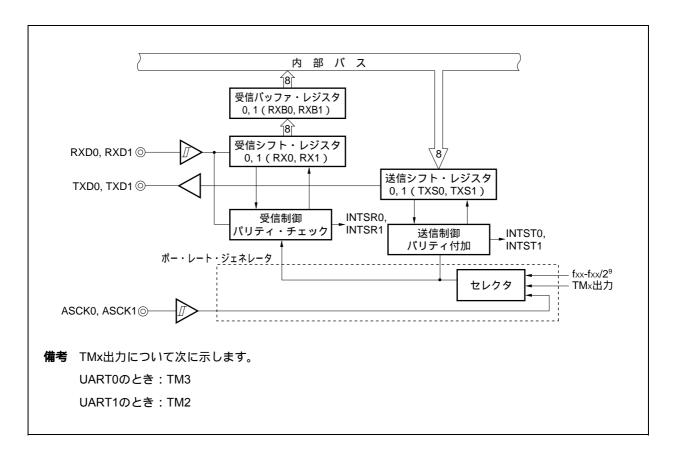

10.4 アシンクロナス・シリアル・インタフェース (UARTO, UART1) ... 353

10.4.1 構 成 ... 353

10.4.2 UARTn制御レジスタ ... 355

10.4.3 動 作 ... 361

10.4.4 スタンバイ機能 ... 373

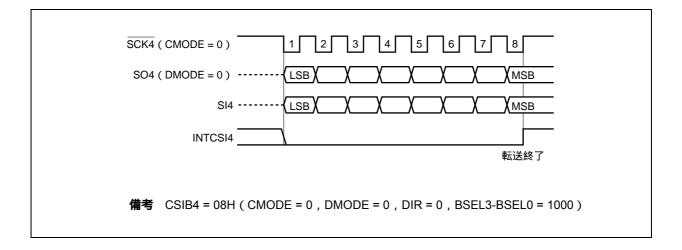

10.5 3線式可変長シリアルI/O (CSI4)... 374

10.5.1 構 成 ... 374

10.5.2 CSI4制御レジスタ ... 377

10.5.3 動 作 ... 381

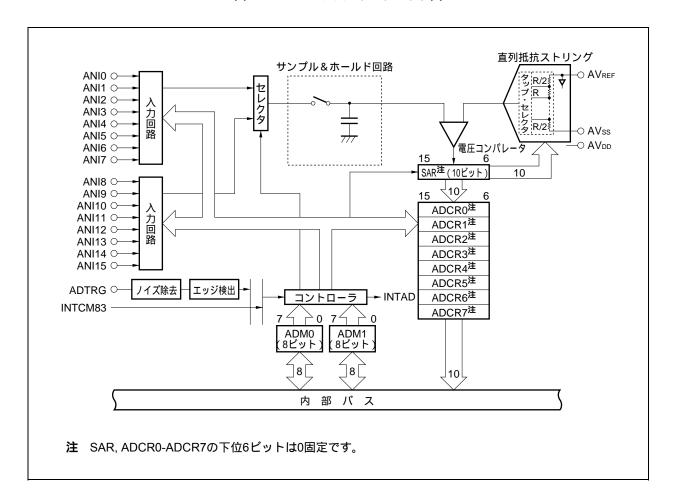

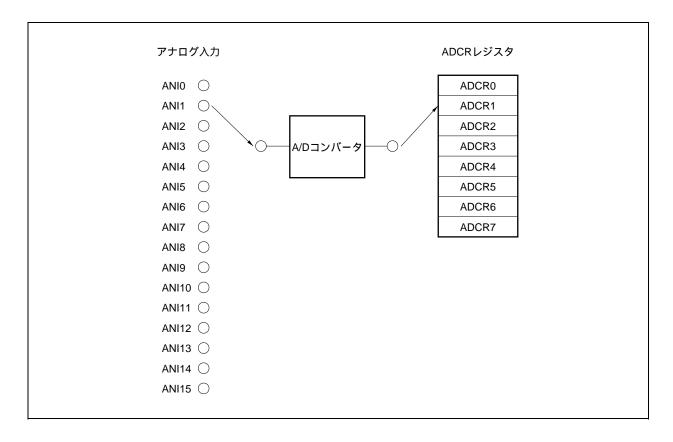

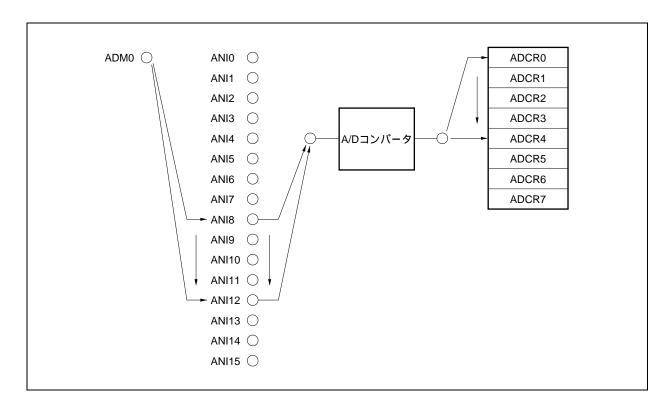

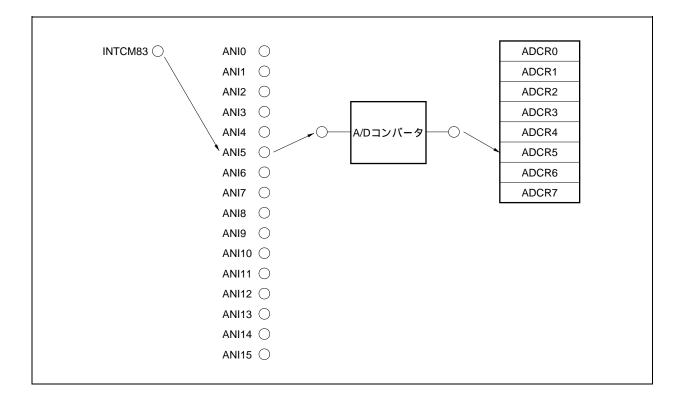

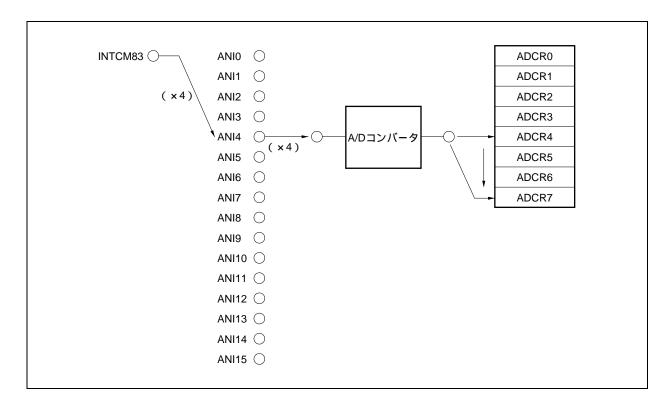

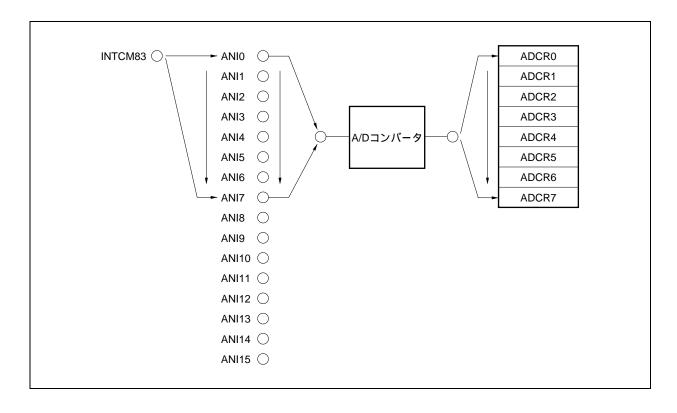

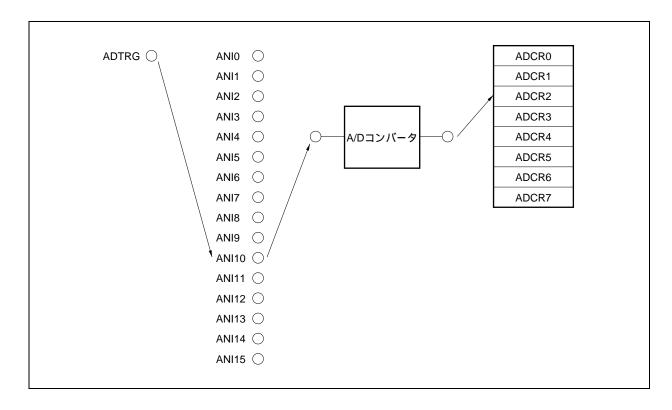

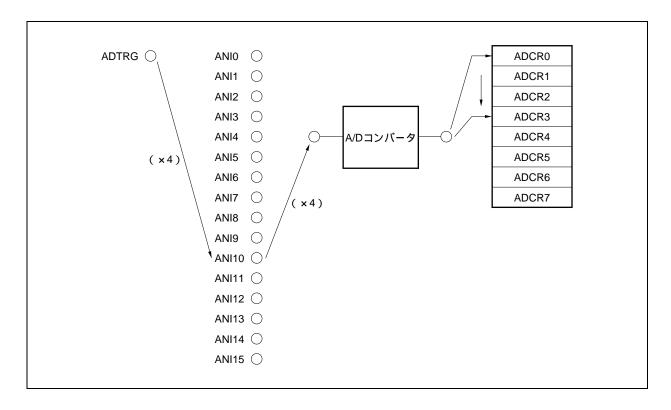

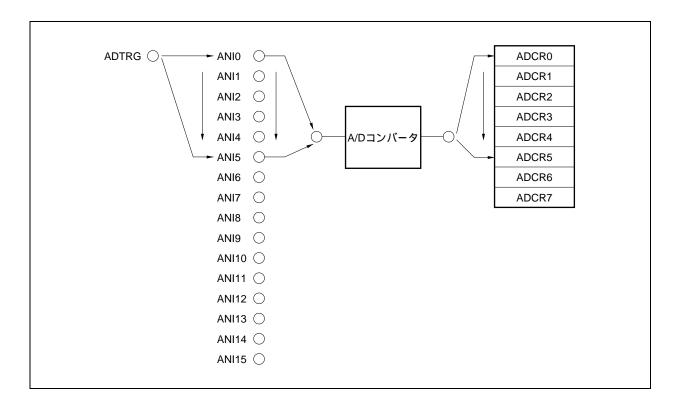

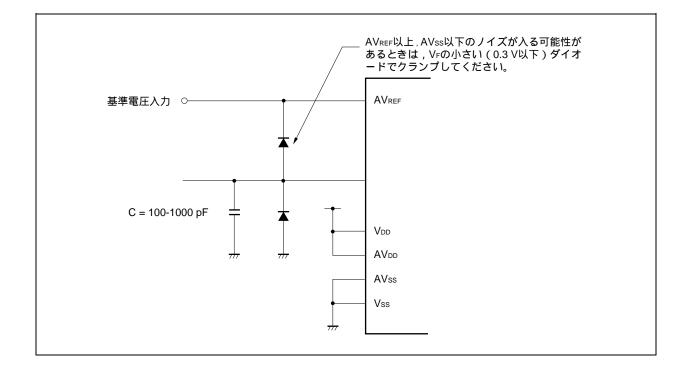

第11章 A/Dコンパータ ... 386

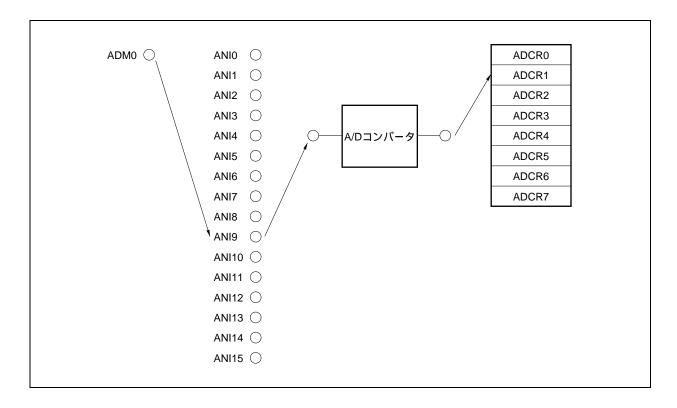

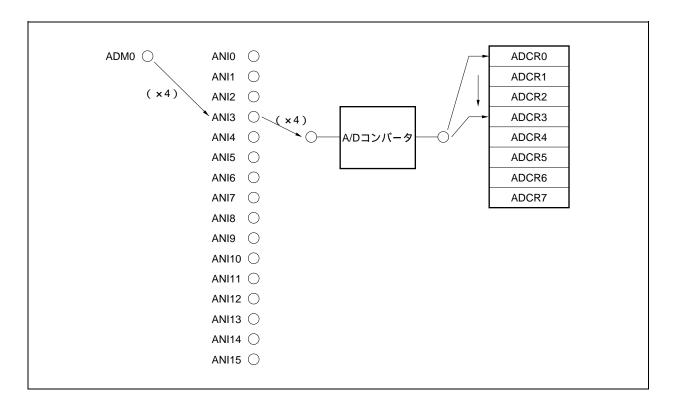

11.1 概 要 ... 386

11.2 構

成 ... 386

11.3 制御レジスタ ... 389

11.3.1 A/Dコンバータ・モード・レジスタ0(ADM0)... 389

11.3.2 A/Dコンバータ・モード・レジスタ1(ADM1)... 391

11.3.3 A/D変換結果レジスタ0-7 (ADCR0-ADCR7)... 393

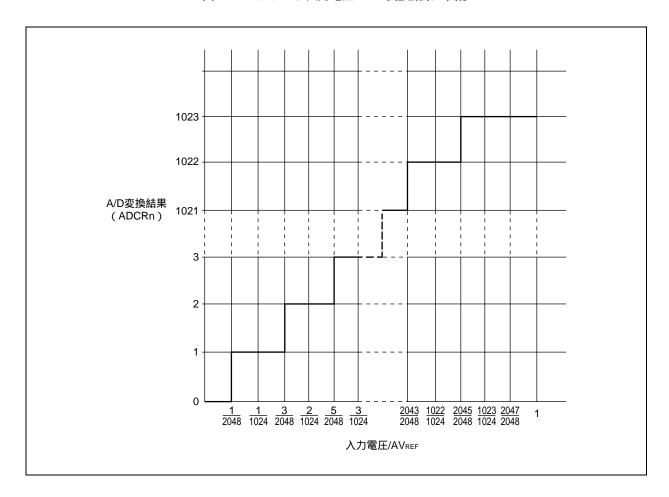

11.3.4 入力電圧と変換結果 ... 394

11.4 動 作 ... 395

11.4.1 基本動作 ... 395

11.4.2 動作モードとトリガ・モード ... 395

11.5 A/Dトリガ・モード時の動作 ... 401

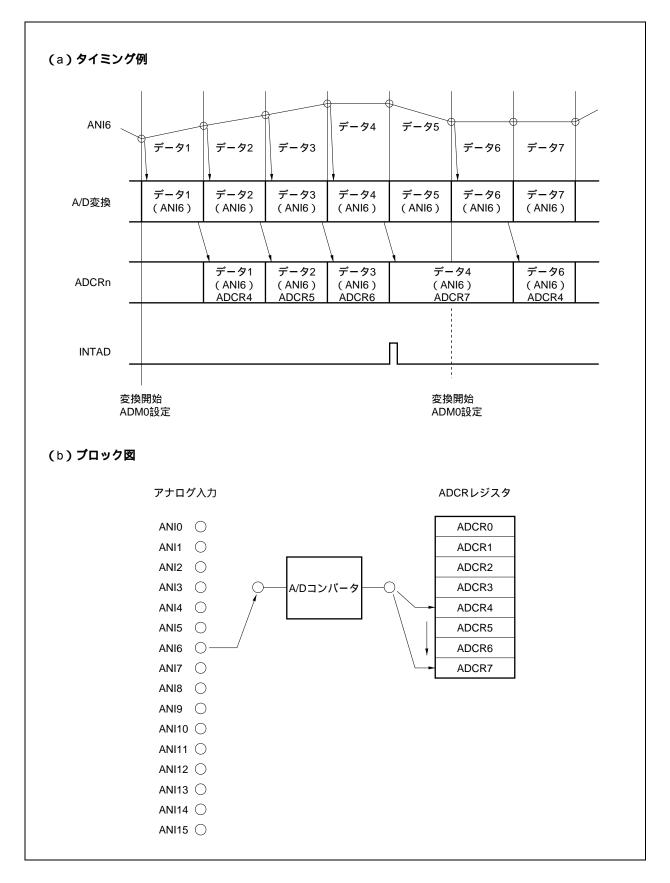

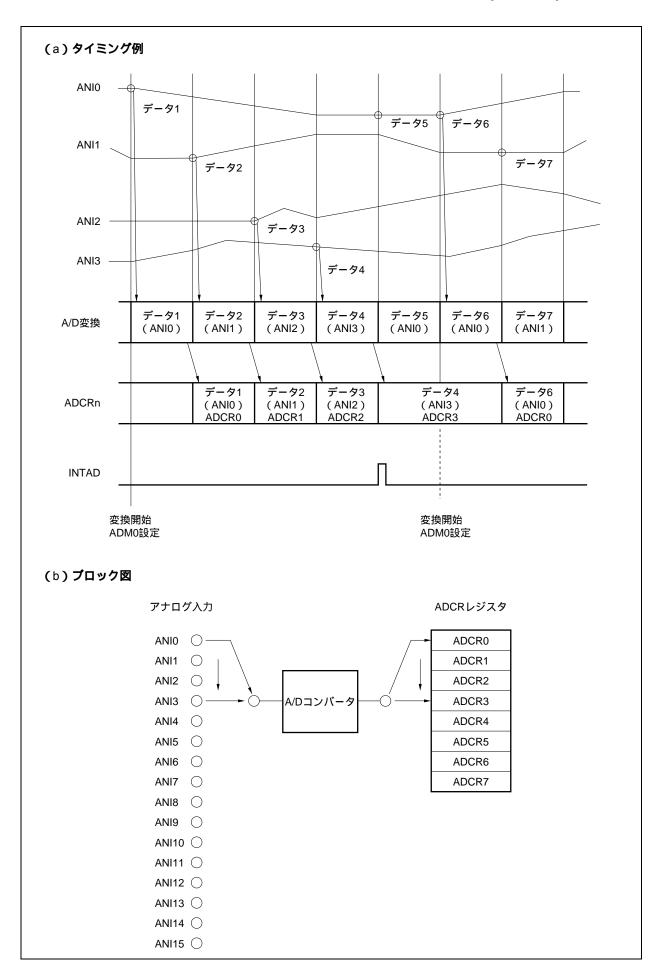

11.5.1 セレクト・モードの動作 ... 401

11.5.2 スキャン・モードの動作 ... 404

11.6 タイマ・トリガ・モード時の動作 ... 405

11.6.1 セレクト・モードの動作 ... 405

11.6.2 スキャン・モードの動作 ... 408

11.7 外部トリガ・モード時の動作 ... 409

11.7.1 セレクト・モードの動作 ... 409

```

|   |       | 11. 7. 2 スキャン・モードの動作 412                            |

|---|-------|-----------------------------------------------------|

|   | 11. 8 | 動作上の注意事項 413                                        |

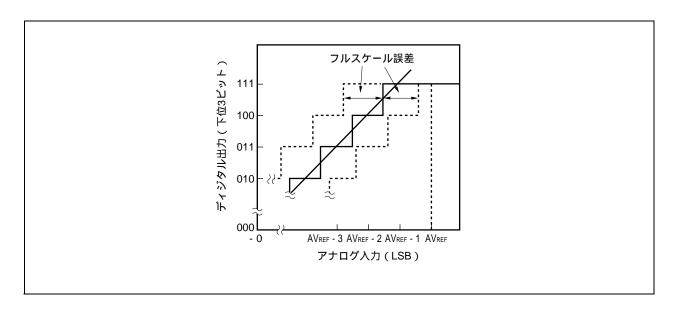

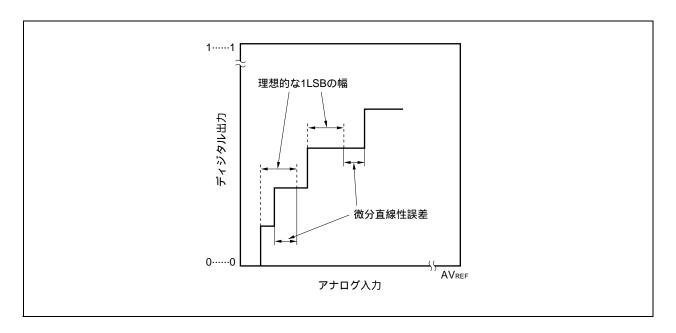

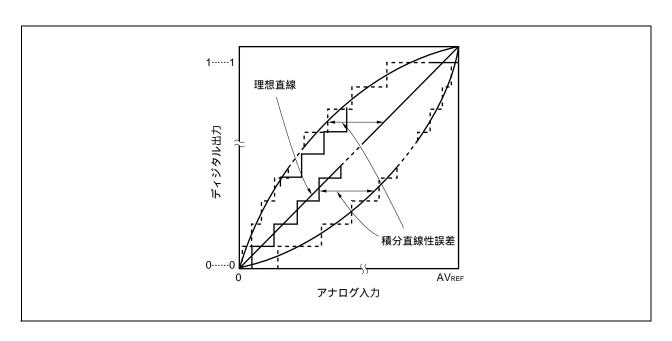

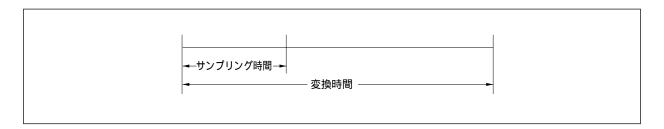

| * | 11. 9 | A/D <b>コンバータ特性表の読み方</b> 416                         |

|   |       |                                                     |

|   | 第12章  | DMA <b>機能</b> 421                                   |

|   | 40.4  | All Air (a)                                         |

|   |       | 機 能 421                                             |

| * |       | <b>特 徵</b> 421                                      |

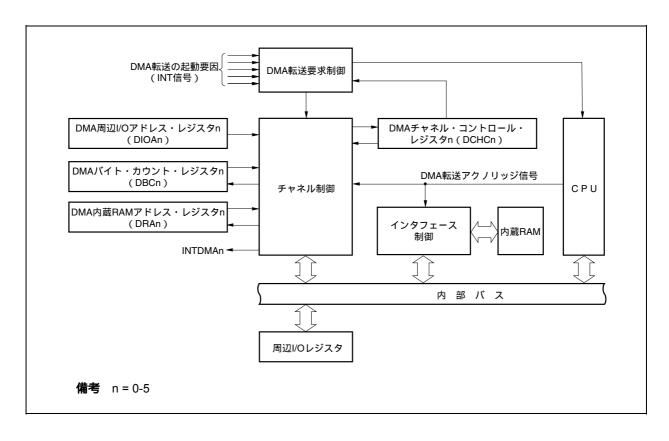

| * |       | 構成 422                                              |

|   | 12. 4 | <b>制御レジスタ</b> 423                                   |

|   |       | 12.4.1 DMA周辺I/Oアドレス・レジスタ0-5 (DIOA0-DIOA5) 423       |

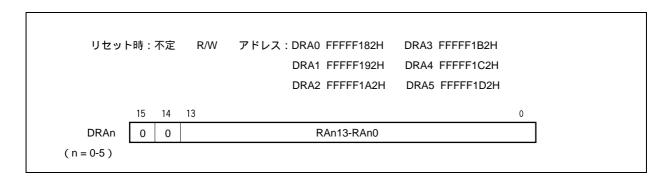

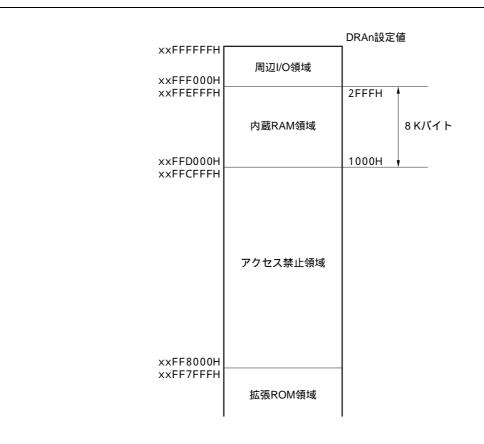

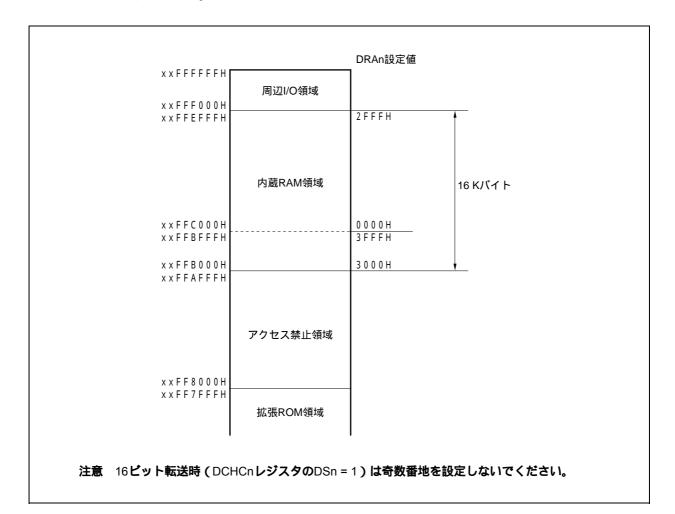

|   |       | 12. 4. 2 DMA内蔵RAMアドレス・レジスタ0-5 ( DRA0-DRA5 ) 423     |

|   |       | 12. 4. 3 DMAバイト・カウント・レジスタ0-5 ( DBC0-DBC5 ) 426      |

|   |       | 12. 4. 4 DMAチャネル・コントロール・レジスタ0-5 ( DCHC0-DCHC5 ) 427 |

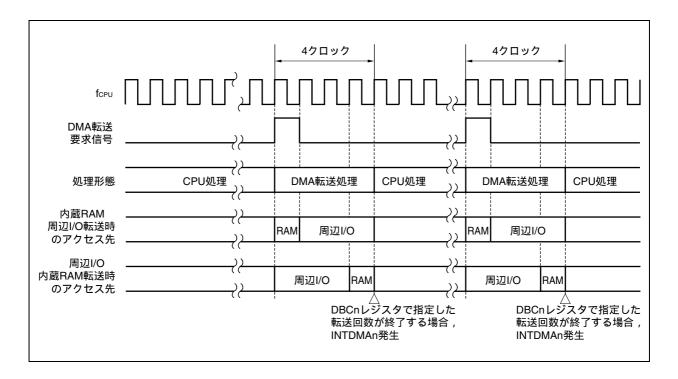

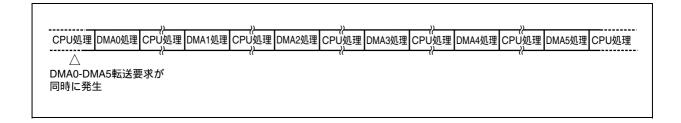

| * | 12. 5 | 動 作 429                                             |

| * | 12. 6 | 注 意 430                                             |

|   |       |                                                     |

|   | 第13章  | <b>リアルタイム出力機能(</b> RTO <b>)</b> 431                 |

|   |       |                                                     |

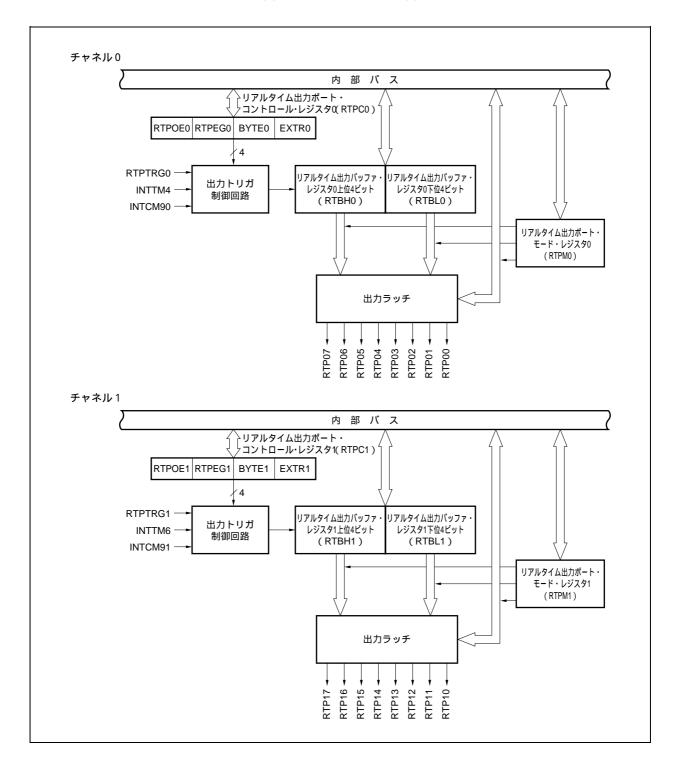

|   | 13. 1 | 機 能 431                                             |

|   | 13. 2 | <b>特 徵</b> 431                                      |

|   | 13. 3 | 構 成 432                                             |

|   | 13. 4 | <b>制御レジスタ</b> 435                                   |

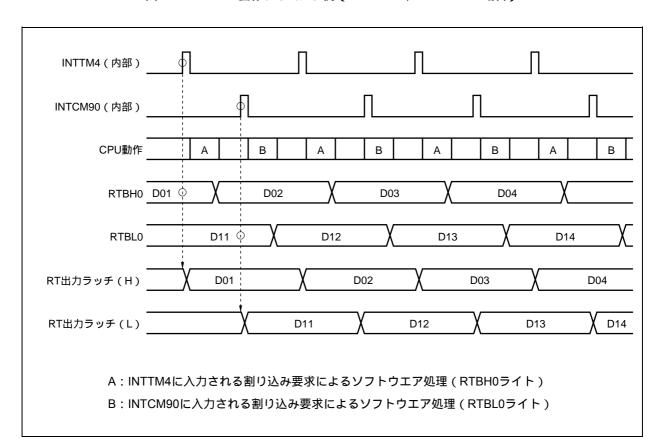

|   | 13. 5 | <b>使用方法</b> 437                                     |

|   | 13. 6 | <b>動 作</b> 438                                      |

|   | 13. 7 | 注意事項 439                                            |

|   |       |                                                     |

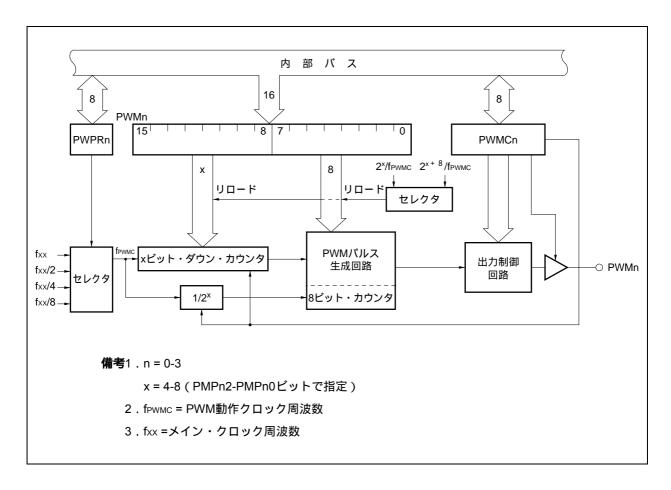

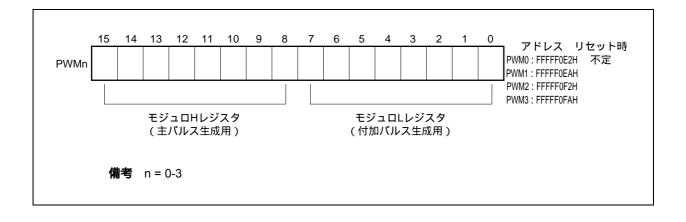

|   | 第14章  | PWM <b>機能</b> 440                                   |

|   |       |                                                     |

|   | 14. 1 |                                                     |

|   |       | 構 成 440                                             |

|   |       | <b>制御レジスタ</b> 442                                   |

|   | 14. 4 | <b>動 作</b> 445                                      |

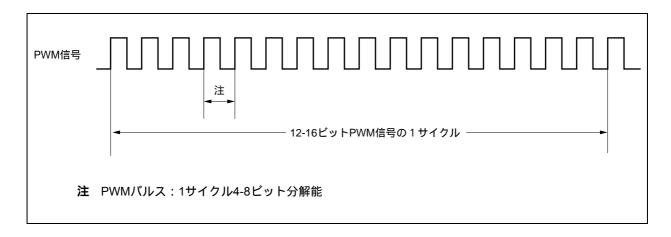

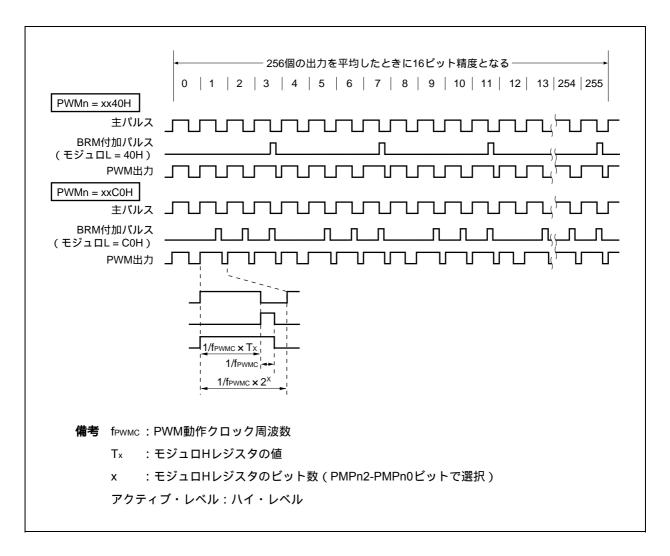

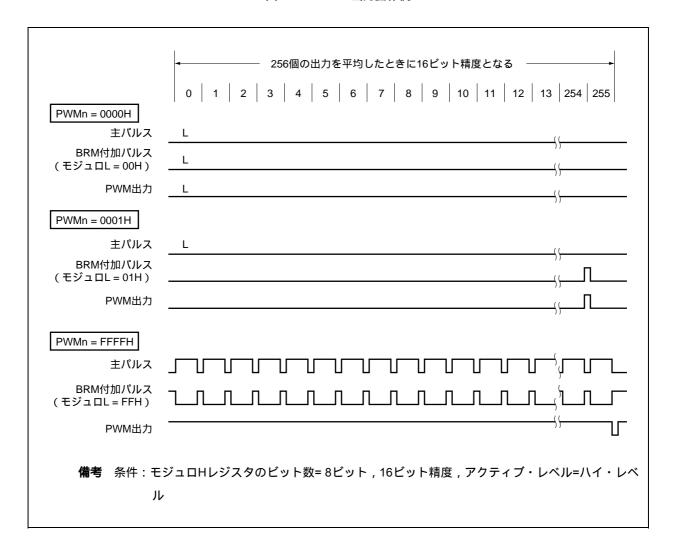

|   |       | 14. 4. 1 PWM基本動作 445                                |

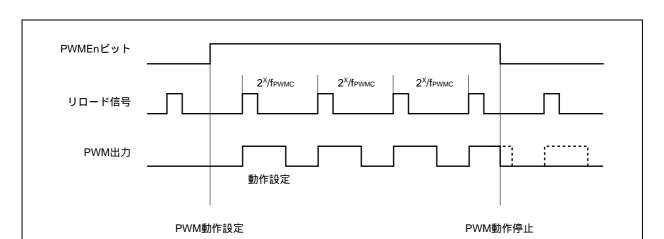

|   |       | 14. 4. 2 PWM動作の許可 / 禁止 448                          |

|   |       | 14. 4. 3 PWMパルスのアクティブ・レベルの指定 449                    |

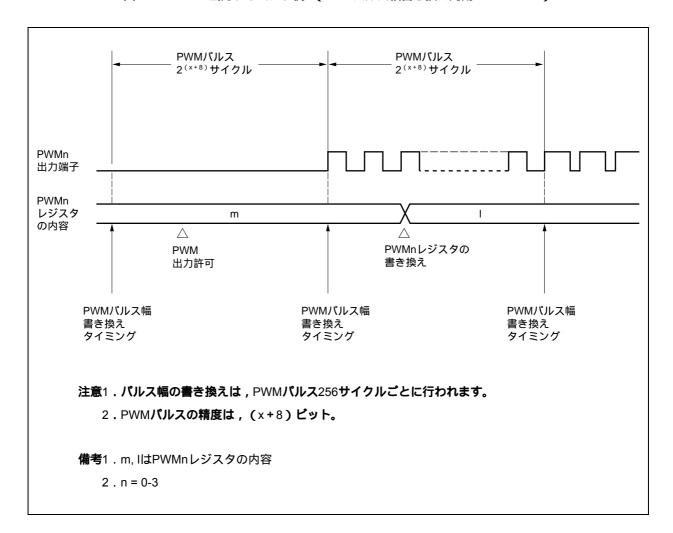

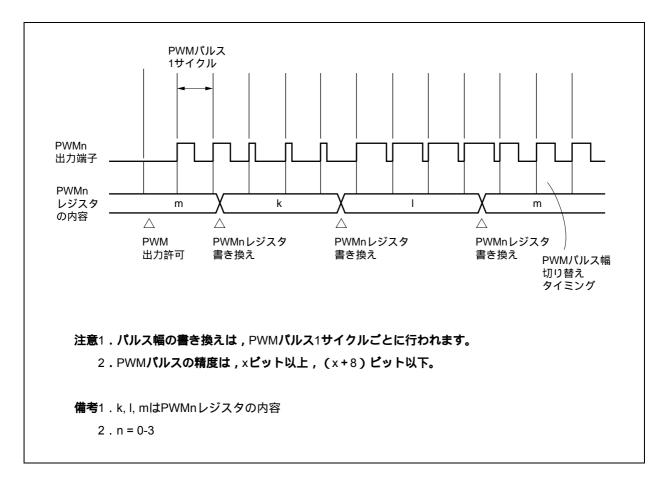

|   |       | 14. 4. 4 PWMパルス幅書き換え周期の指定 450                       |

|   |       | 14. 4. 5 繰り返し周波数 451                                |

|   |       |                                                     |

|   | 第15章  | Vsync/Hsync <b>分離回路</b> 452                         |

|   |       |                                                     |

|   |       | 概 要 452                                             |

|   |       | 構 成 453                                             |

|   | 15. 3 | <b>制御レジスタ</b> 455                                   |

|   | 15. 4 | <b>動 作</b> 456                                      |

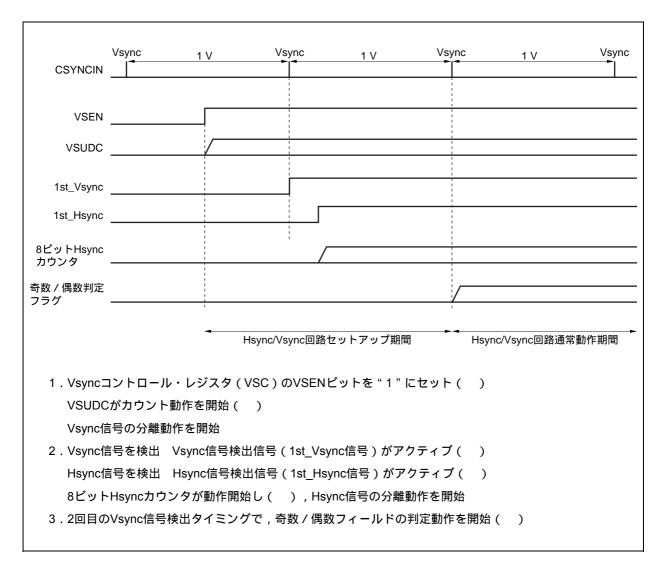

15.4.4 起動時の動作 ... 461

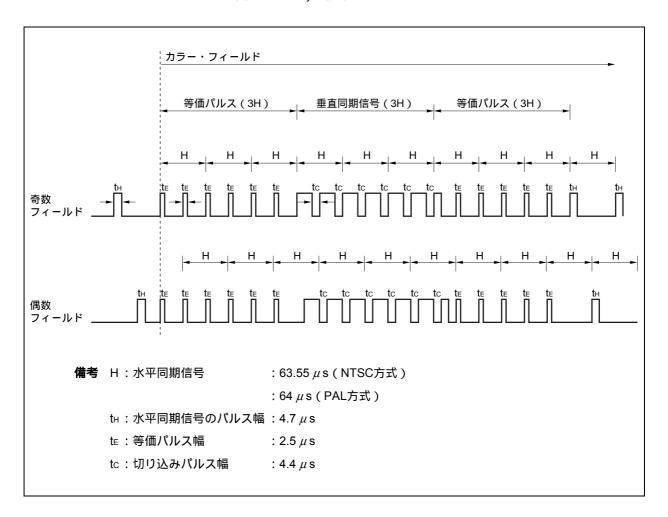

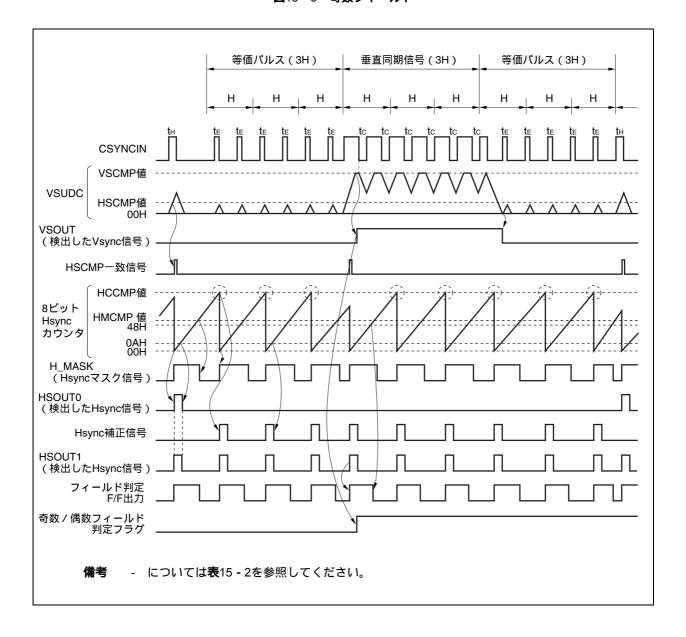

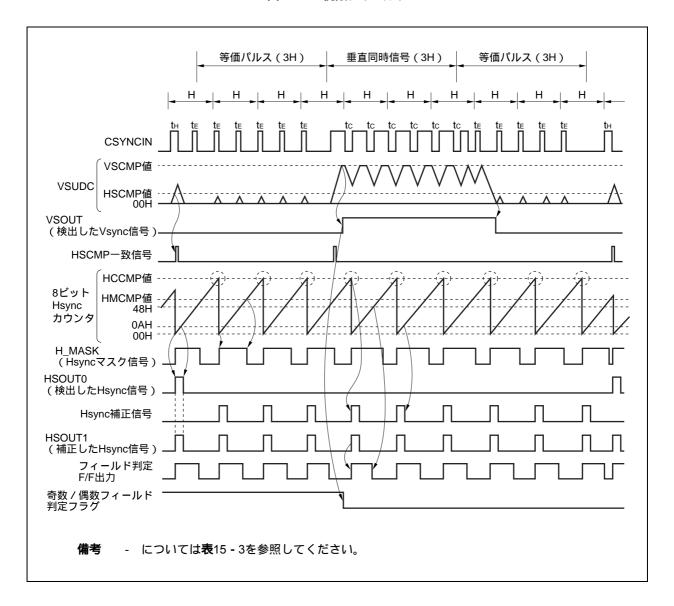

15. 4. 1Csync信号のフォーマット...45615. 4. 2奇数フィールド時の基本動作...45715. 4. 3偶数フィールド時の基本動作...459

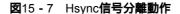

|   |                      | 15. 4. 6 Hsync信号分離動作 463                               |

|---|----------------------|--------------------------------------------------------|

|   |                      | 15. 4. 7 Hsync信号マスク動作 465                              |

|   |                      | 15. 4. 8 Hsync信号自己生成動作 466                             |

|   |                      | 15. 4. 9 奇数フィールド / 偶数フィールド判定動作 467                     |

|   |                      | 10. 1. 0 -JXX > 1 /V1 / II-JXX > 1 /V1 / JXE ± J/1 101 |

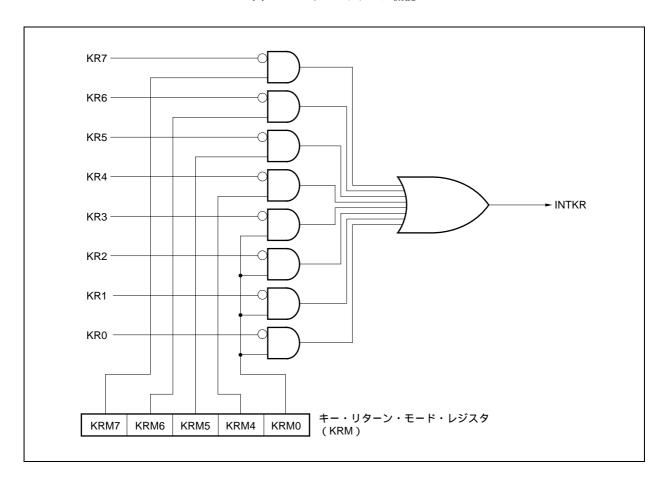

| * | <b>第</b> 16章         | <b>キー・リターン機能</b> 469                                   |

|   | 16. 1                | 機 能 469                                                |

|   | 16. 2                | 特 徵 469                                                |

|   | 16. 3                | <b>制御レジスタ</b> 470                                      |

|   | <b>笙</b> 17音         | <b>ポート機能</b> 471                                       |

|   | オバチ                  | יון או און און און און און און און און או              |

|   | 17. 1                | 各ポートの構成 471                                            |

|   |                      | <b>各ポートの端子機能</b> 471                                   |

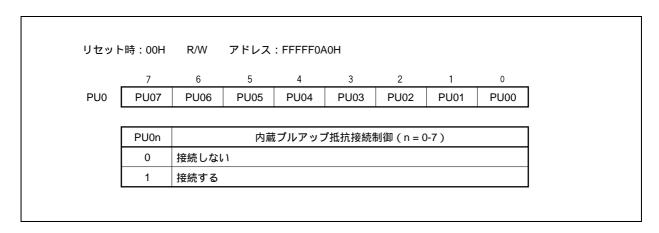

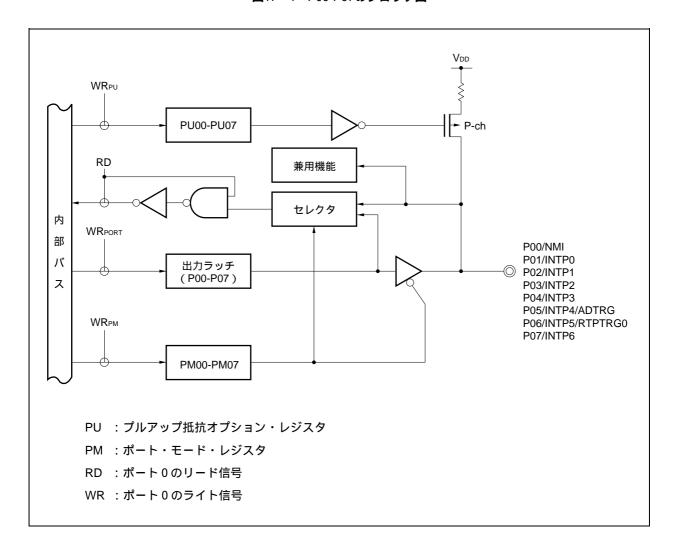

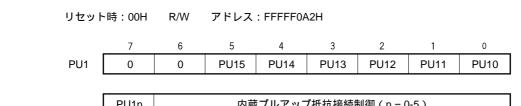

|   |                      | 17. 2. 1 ポート0 471                                      |

|   |                      | 17. 2. 2 ポート1 476                                      |

|   |                      | 17. 2. 3 ポート2 482                                      |

|   |                      | 17. 2. 4 ポート3 489                                      |

|   |                      | 17. 2. 5 ポート4 , ポート5 494                               |

|   |                      | 17. 2. 6 ポート6 497                                      |

|   |                      |                                                        |

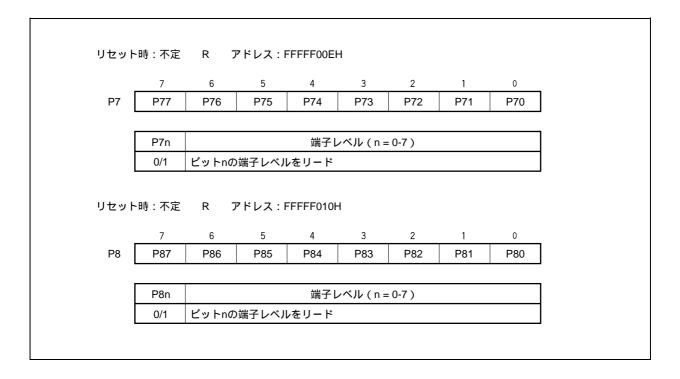

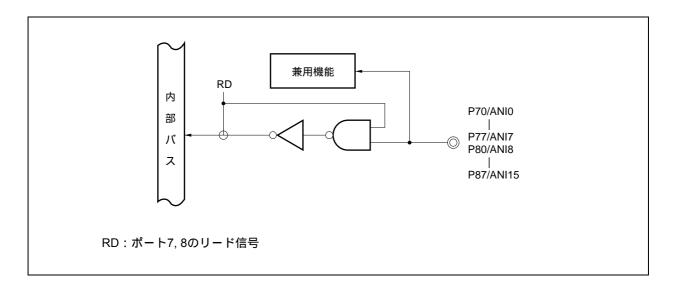

|   |                      | 17. 2. 7 ポート7, ポート8 500                                |

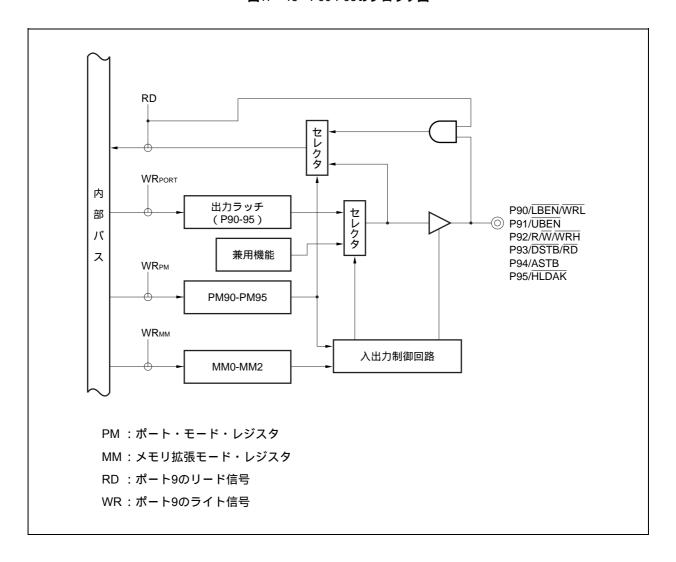

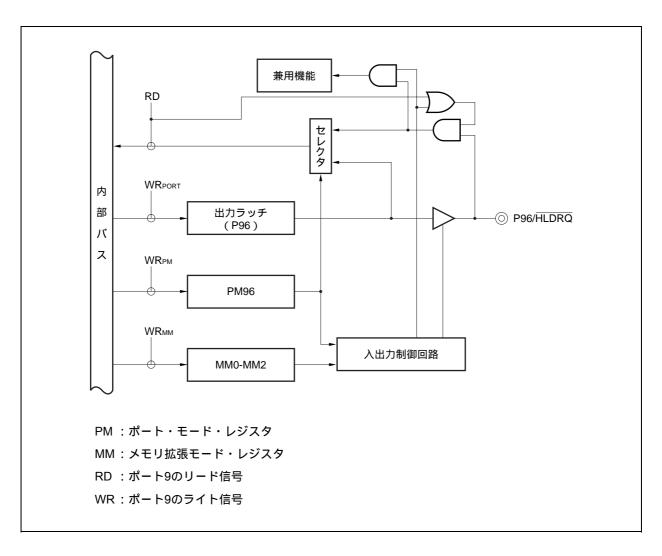

|   |                      | 17. 2. 8 ポート9 502                                      |

|   |                      | 17. 2. 9 ポート10 506                                     |

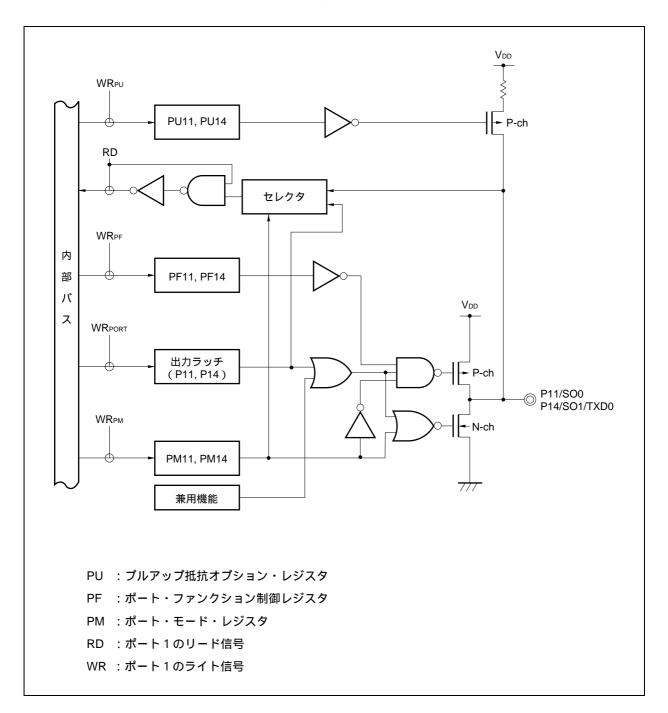

|   |                      | 17. 2. 10 ポート11 510                                    |

|   |                      | 17. 2. 11 ポート12 512                                    |

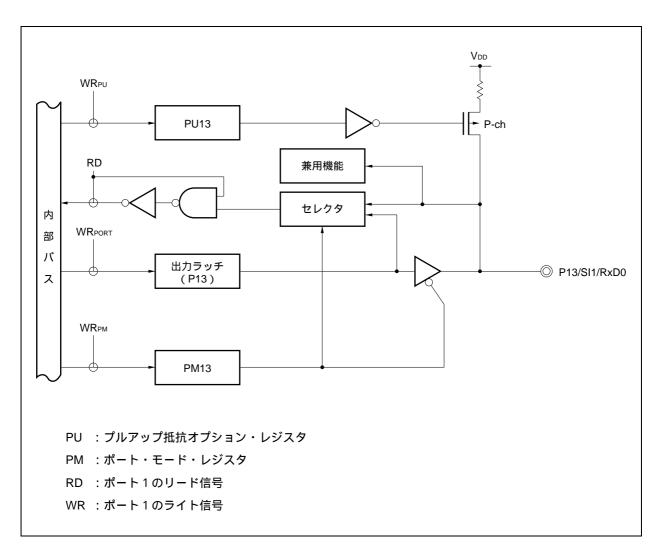

|   |                      | 17. 2. 12 ポート13 513                                    |

|   |                      | 17. 2. 13 ポート14 523                                    |

|   |                      | 17. 2. 14 ポート15 528                                    |

|   |                      | 17. 2. 15 ポート16 531                                    |

|   |                      | 17. 2. 16 ポート17 534                                    |

|   |                      | 17. 2. 17 ポート18 537                                    |

|   |                      | 17. 2. 18 ポート19 539                                    |

|   | 17. 3                | ポート端子を兼用端子として使用する場合の設定 541                             |

| * | 17. 4                | ポート機能の動作 544                                           |

|   |                      | 17. 4. 1 入出力ポートへの書き込み … 544                            |

|   |                      | 17.4.2 入出力ポートからの読み出し 544                               |

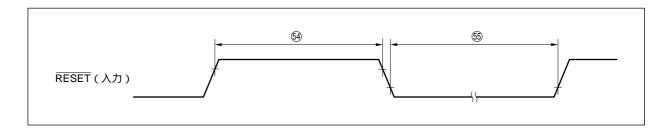

|   | <b>第</b> 18 <b>章</b> | リセット機能 545                                             |

|   |                      |                                                        |

|   |                      | 概 要 545                                                |

|   | 18. 2                | <b>端子動作</b> 545                                        |

|   | <del> </del>         |                                                        |

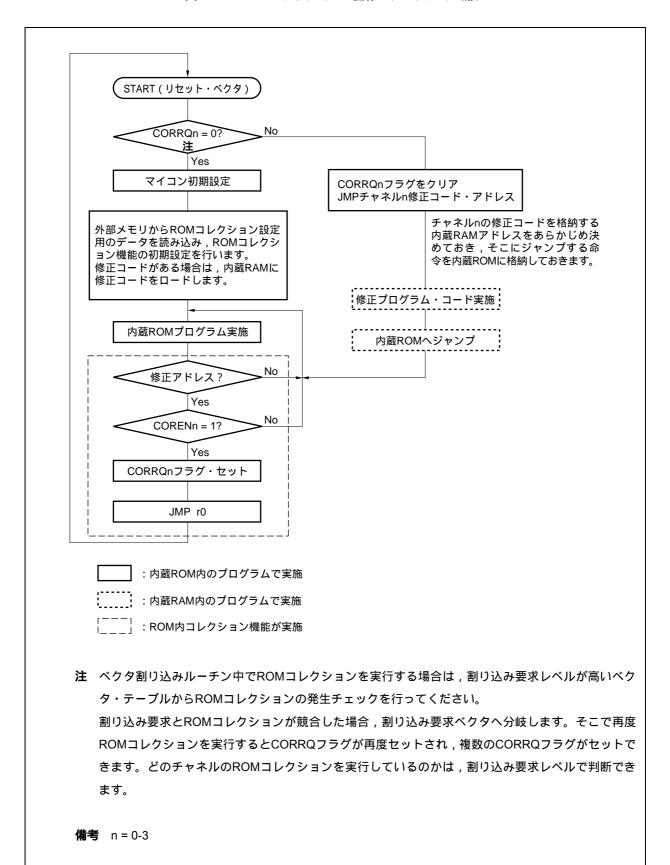

|   | 第19章                 | ROM <b>コレクション機能</b> 546                                |

|   |                      |                                                        |

|   |                      | 概 要 546                                                |

|   | 19. 2                | ROMコレクション周辺I/Oレジスタ 547                                 |

|   |                      | 19. 2. 1 コレクション・コントロール・レジスタ (CORCN) 547                |

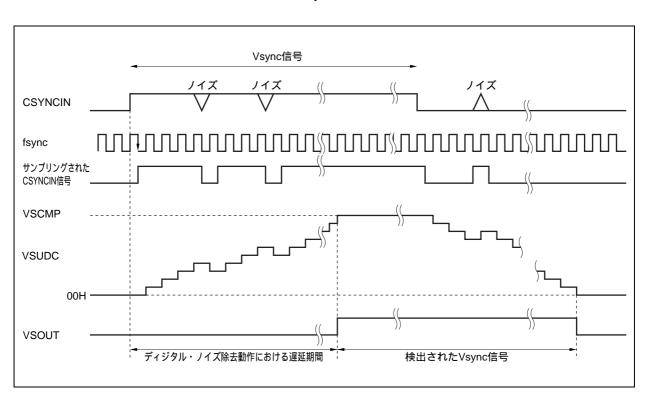

15. 4. 5 Vsync信号分離動作 ... 462

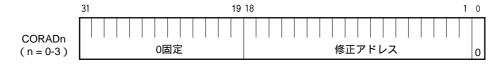

- 19.2.2 コレクション要求レジスタ (CORRQ)... 547

- 19. 2. 3 コレクション・アドレス・レジスタ0-3 (CORAD0-CORAD3)... 548

#### 第20章 フラッシュ・メモリ … 550

- 20.1 特 徵 ... 550

- ★ 20.1.1 消去単位 ... 551

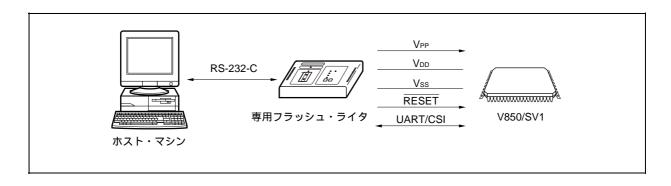

- 20.2 フラッシュ・ライタによる書き込み方法 ... 552

- 20.3 プログラミング環境 ... 556

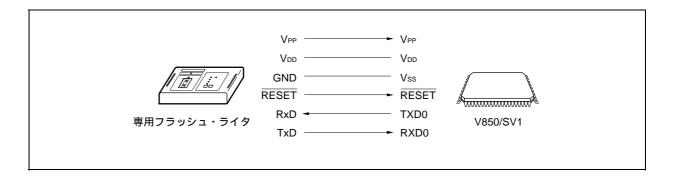

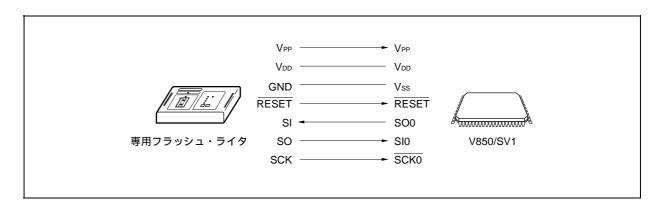

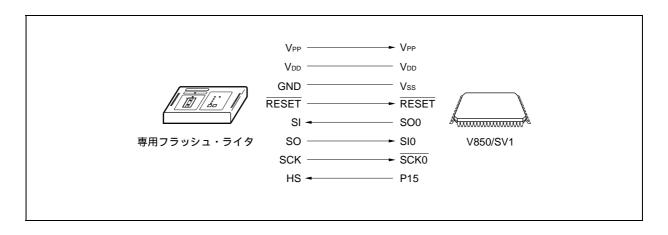

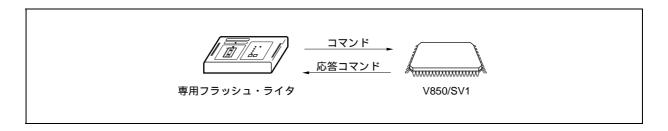

- 20.4 通信方式 ... 557

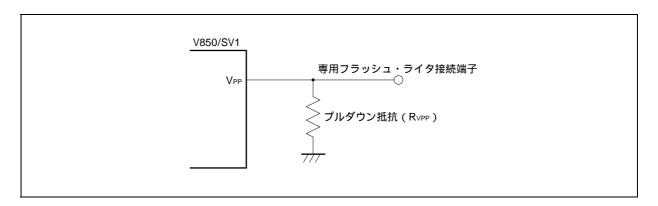

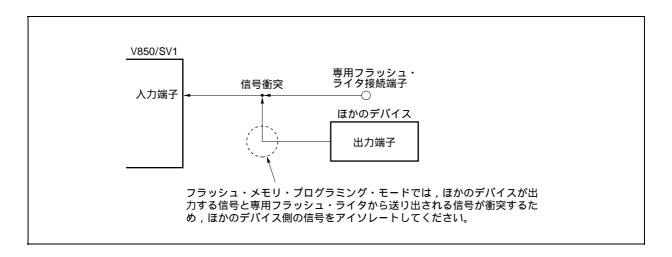

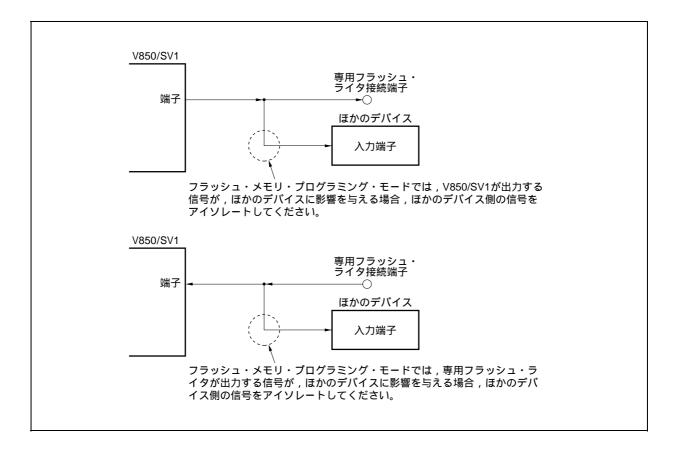

- 20.5 **端子処理** ... 559

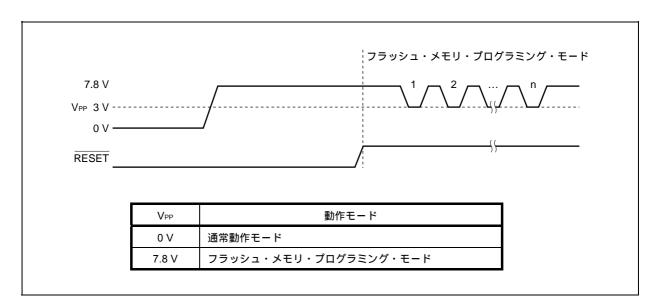

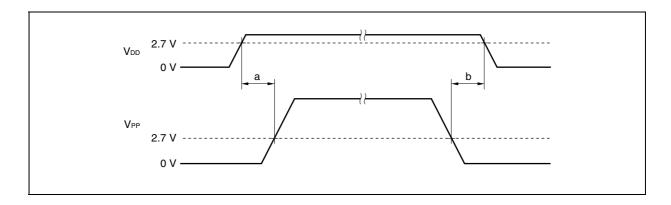

- 20.5.1 VPP端子 ... 559

- 20.5.2 シリアル・インタフェース端子 ... 560

- 20. 5. 3 RESET端子 ... 562

- 20.5.4 ポート端子(NMIを含む)... 562

- 20.5.5 その他の信号端子 ... 562

- 20.5.6 電 源 ... 562

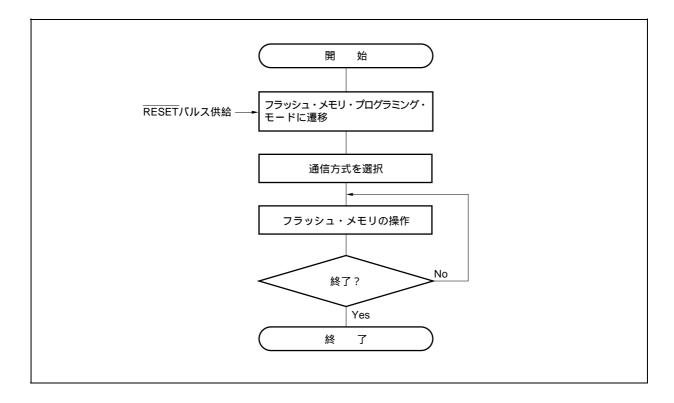

- 20.6 プログラミング方法 ... 563

- 20.6.1 フラッシュ・メモリ制御 ... 563

- 20.6.2 フラッシュ・メモリ・プログラミング・モード ... 564

- 20.6.3 通信方式の選択 ... 564

- 20.6.4 通信コマンド ... 565

- 20.6.5 使用する資源 ... 566

- ★ **第21章 電気的特性** ... 567

- ★ **第**22**章 外 形 図** ... 592

- ★ 第23章 半田付け推奨条件 ... 594

- 付録A レジスタ索引 ... 597

- 付録B 命令セット一覧 ... 605

- **付録C 総合索引** ... 612

- C. 1 50音で始まる語句の索引 ... 612

- C. 2 数字, アルファベットで始まる語句の索引 ... 617

- ★ **付録**D **改版履歴** ... 622

## 図の目次 (1/8)

| 図番号    | タイトル , ページ                                                                                  |

|--------|---------------------------------------------------------------------------------------------|

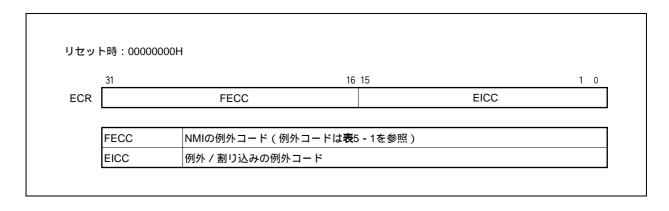

| 3 - 1  | CPUレジスタ・セット 68                                                                              |

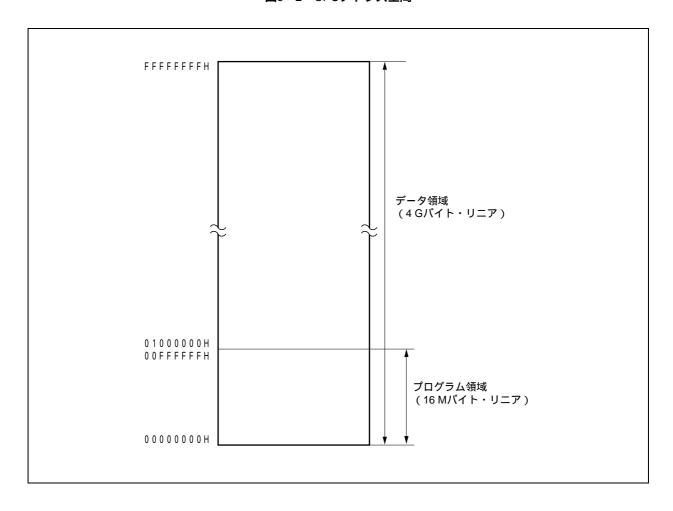

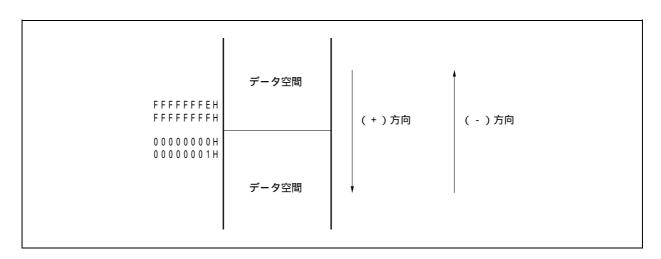

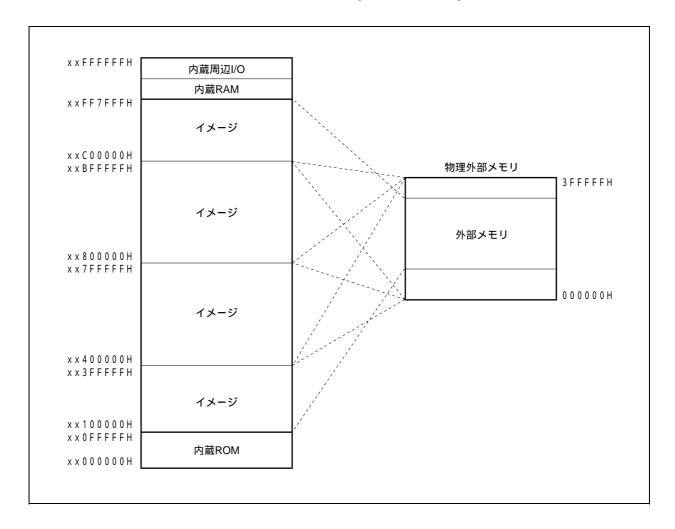

| 3 - 2  | CPUアドレス空間 74                                                                                |

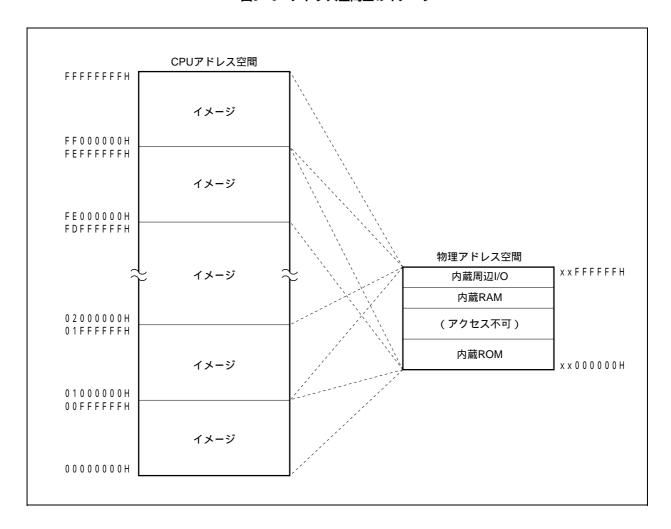

| 3 - 3  | アドレス空間上のイメージ 75                                                                             |

| 3 - 4  | プログラム空間 76                                                                                  |

| 3 - 5  | データ空間 76                                                                                    |

| 3 - 6  | メモリ・マップ 77                                                                                  |

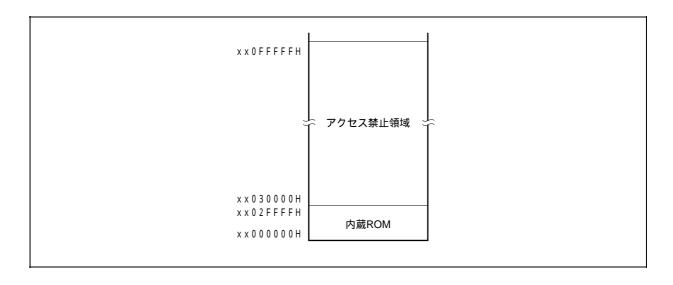

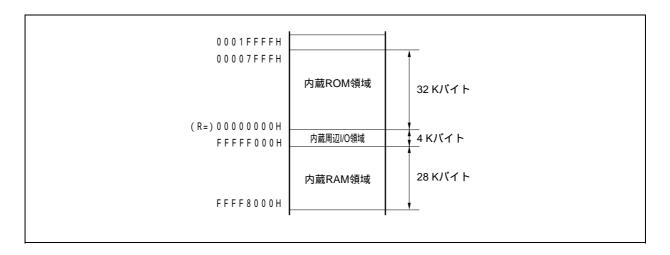

| 3 - 7  | 内蔵ROM領域(192 Kバイト) 78                                                                        |

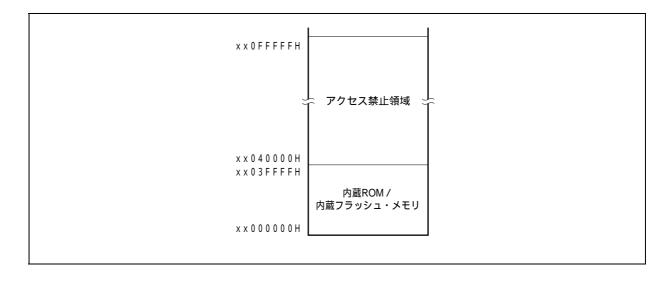

| 3 - 8  | 内蔵ROM / 内蔵フラッシュ・メモリ領域(256 Kバイト) 78                                                          |

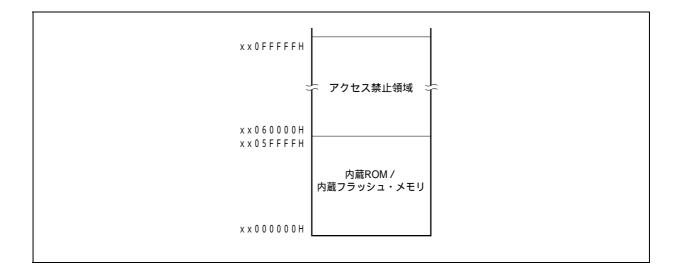

| 3 - 9  | 内蔵ROM / 内蔵フラッシュ・メモリ領域(384 Kバイト) 79                                                          |

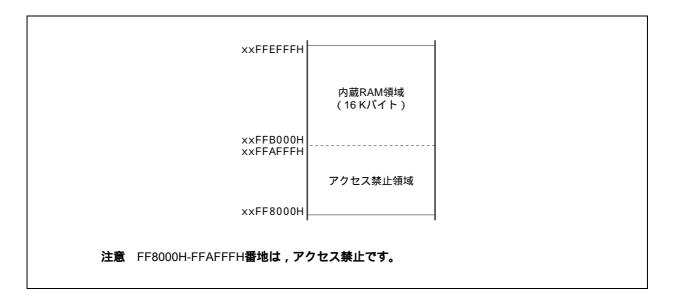

| 3 - 10 | 内蔵RAM領域( $\mu$ PD703038, 703038Y, 703040, 703040Y, 70F3038, 70F3038Y, 70F3040, 70F3040Y) 81 |

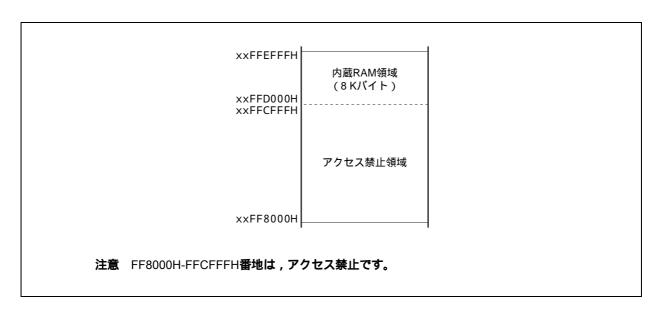

| 3 - 11 | 内蔵RAM領域(μPD703039, 703039Y, 703041, 703041Y) 81                                             |

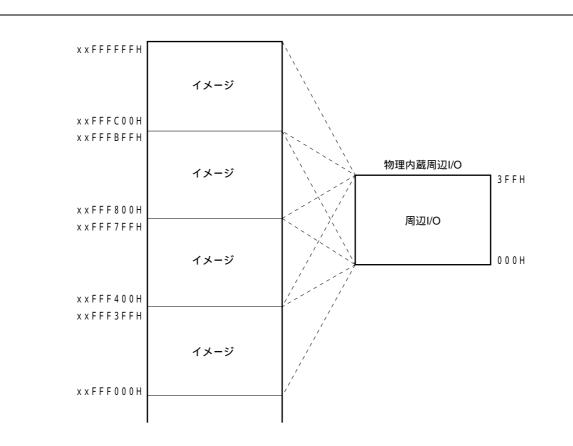

| 3 - 12 | 内蔵周辺I/O領域 82                                                                                |

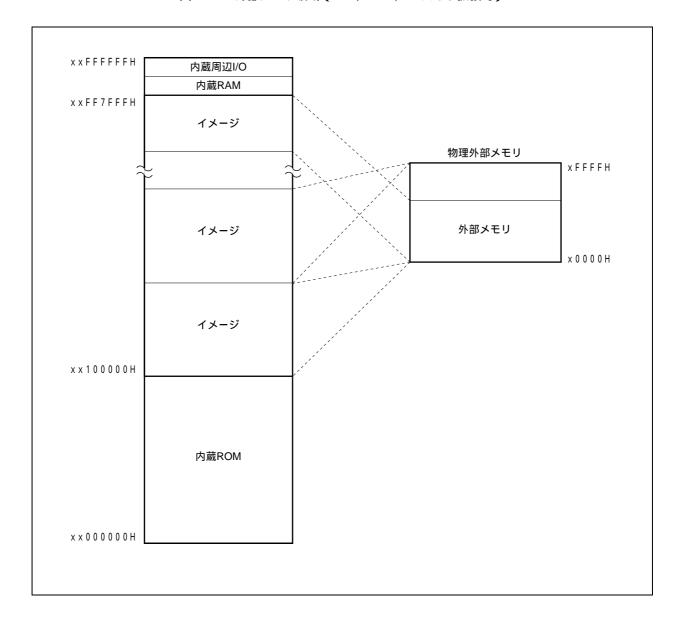

| 3 - 13 | 外部メモリ領域(64 K, 256 K, 1 Mバイト拡張時) 83                                                          |

| 3 - 14 | 外部メモリ領域(4 Mバイト拡張時) 84                                                                       |

| 3 - 15 | ラップ・アラウンドを利用した応用例 86                                                                        |

| 3 - 16 | 推奨メモリ・マップ例(フラッシュ・メモリ内蔵品) 87                                                                 |

|        |                                                                                             |

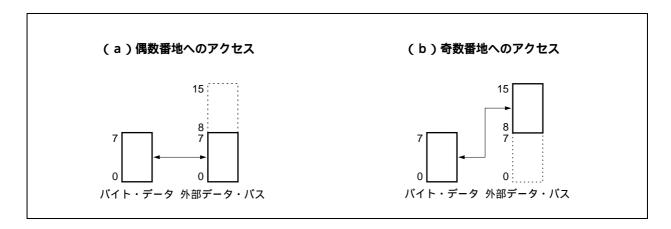

| 4 - 1  | バイト・アクセス (8ビット) 102                                                                         |

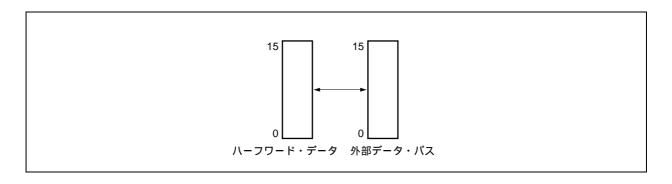

| 4 - 2  | ハーフワード・アクセス(16ビット) 102                                                                      |

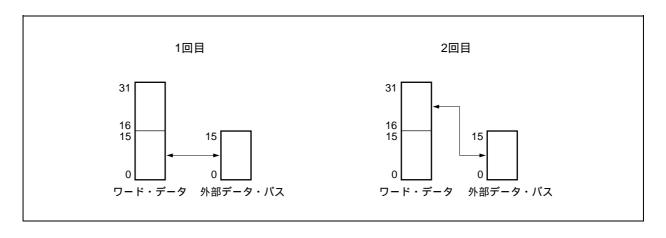

| 4 - 3  | ワード・アクセス(32ビット) 102                                                                         |

| 4 - 4  | メモリ空間 103                                                                                   |

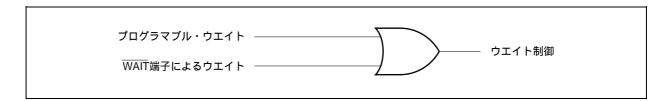

| 4 - 5  | ウエイト制御 105                                                                                  |

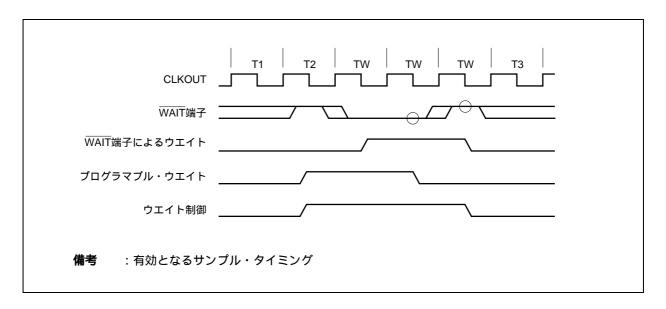

| 4 - 6  | ウエイト挿入例 105                                                                                 |

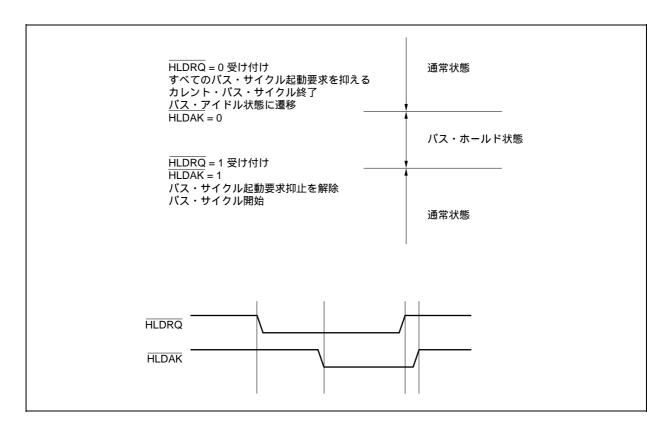

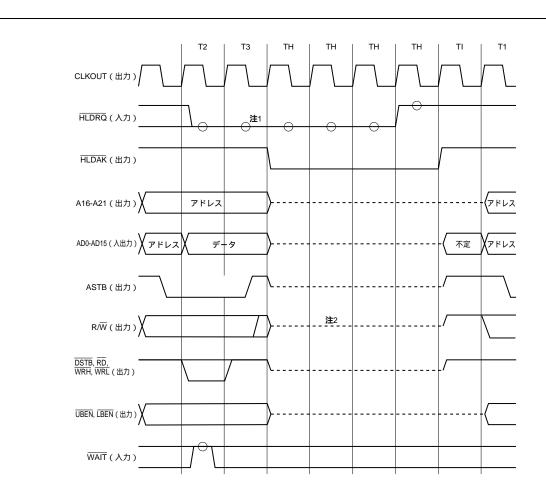

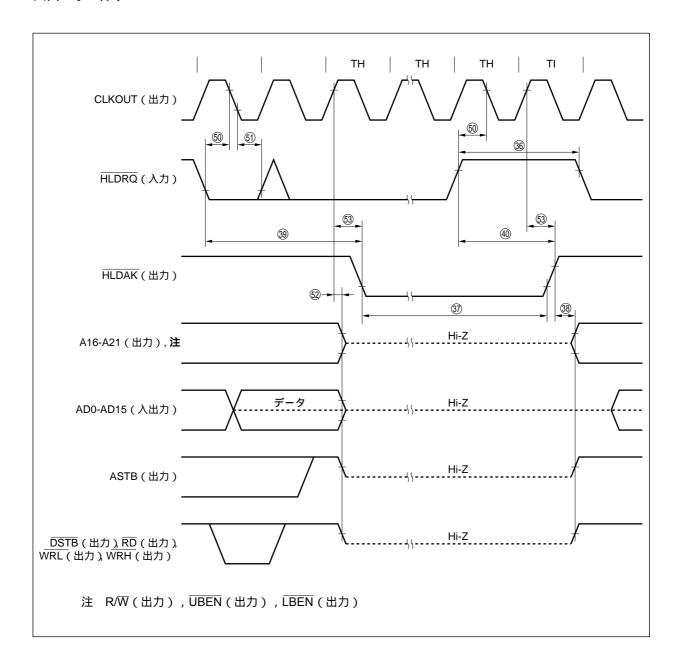

| 4 - 7  | バス・ホールド手順 108                                                                               |

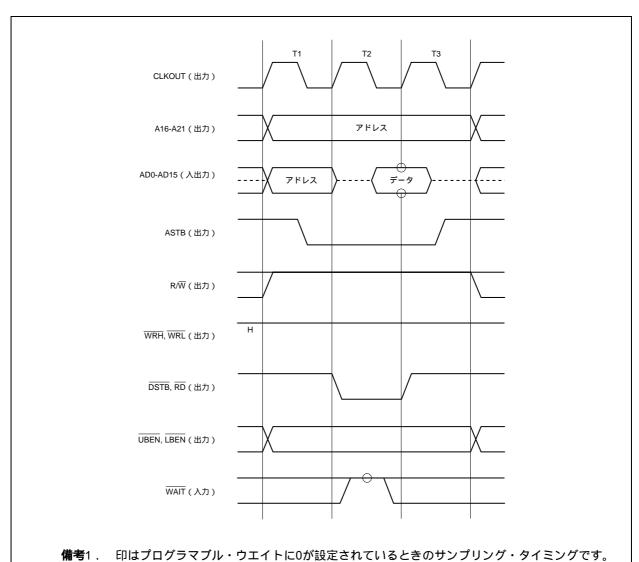

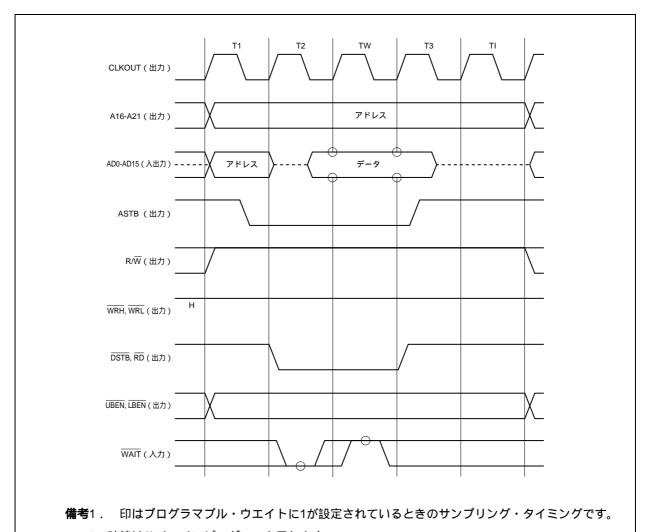

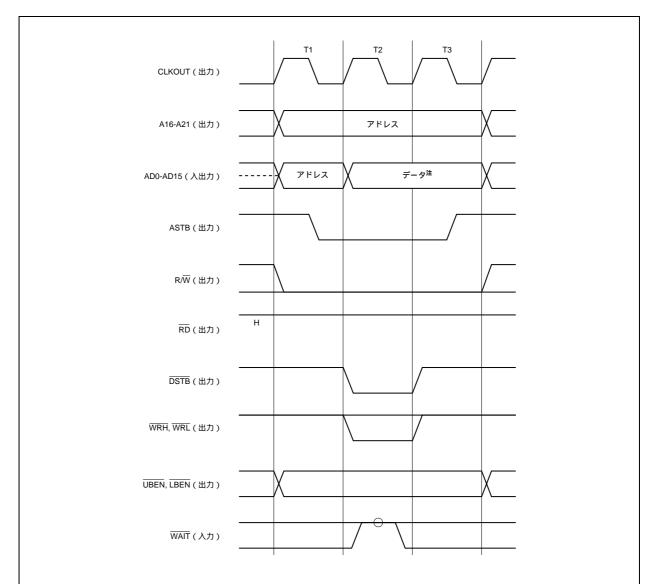

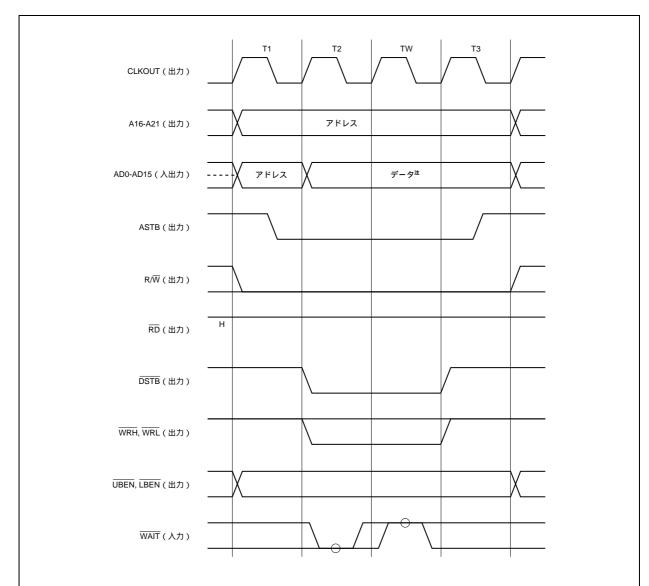

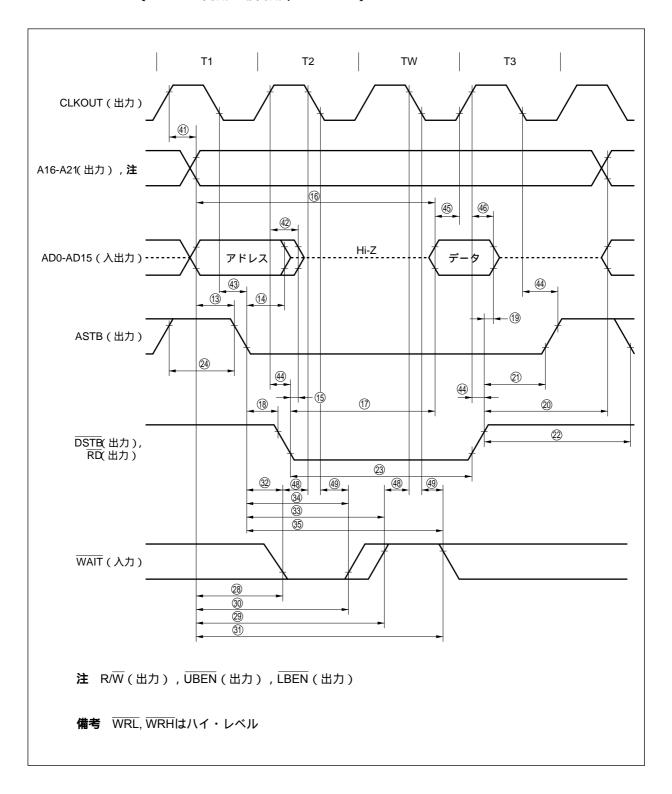

| 4 - 8  | メモリ・リード(0ウエイト) 109                                                                          |

| 4 - 9  | メモリ・リード(1ウエイト) 110                                                                          |

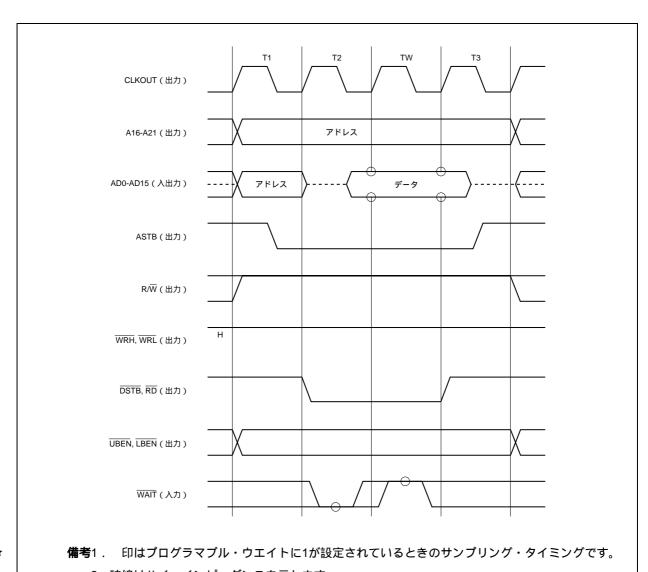

| 4 - 10 | メモリ・リード ( 0ウエイト , アイドル・ステート ) 111                                                           |

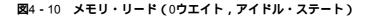

| 4 - 11 | メモリ・リード(1ウエイト , アイドル・ステート) 112                                                              |

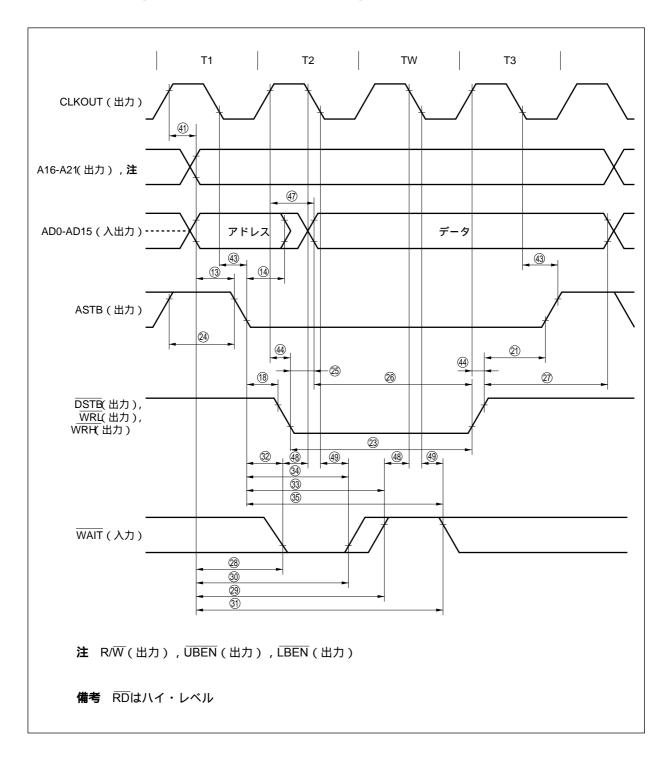

| 4 - 12 | メモリ・ライト(0ウエイト) 113                                                                          |

| 4 - 13 | メモリ・ライト(1ウエイト) 114                                                                          |

| 4 - 14 | バス・ホールド・タイミング 115                                                                           |

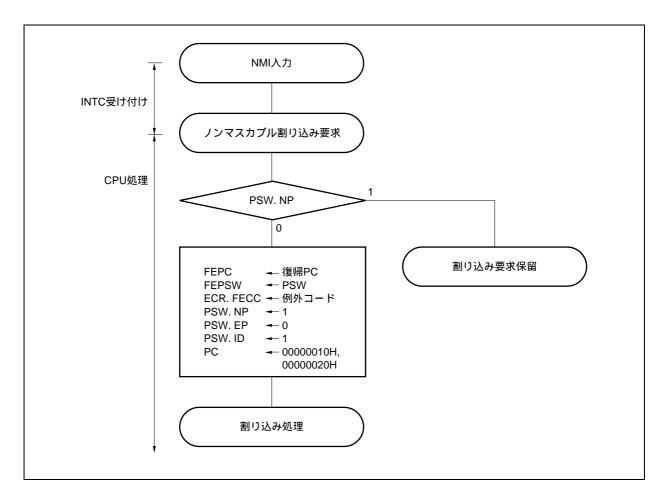

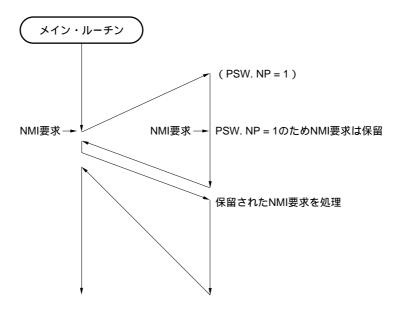

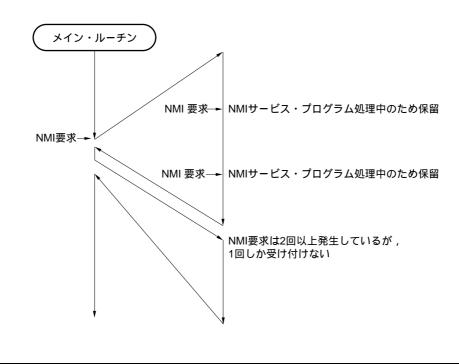

| 5 - 1  | ノンマスカブル割り込みの処理形態 121                                                                        |

| 5 - 2  | ノンマスカブル割り込み要求の受け付け動作 122                                                                    |

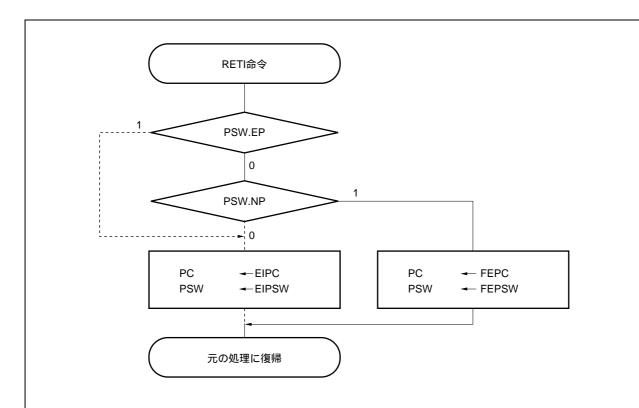

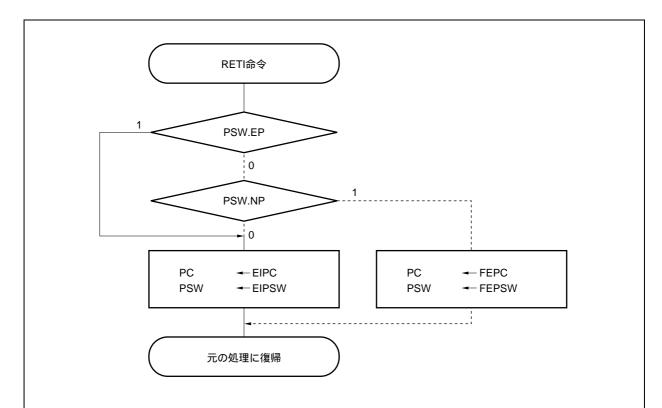

| 5 - 3  | RETI命令の処理形態 123                                                                             |

| 5 - 4  | マスカブル割り込みの処理形態 128                                                                          |

| 5 - 5  | RETI命令の処理形態 129                                                                             |

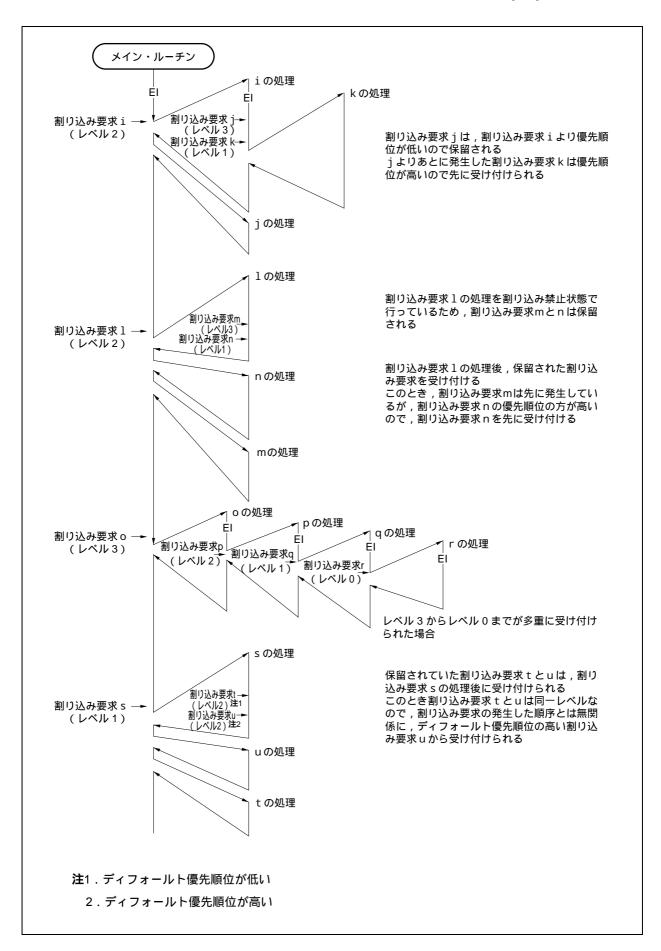

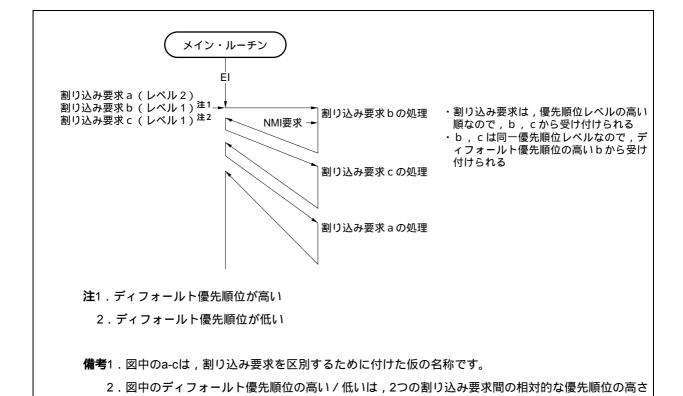

| 5 - 6  | 割り込み処理中にほかの割り込み要求が発生した場合の処理例 131                                                            |

## 図の目次 (2/8)

| 図番号              | タイトル , ページ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 - 7            | 同時発生した割り込み要求の処理例 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

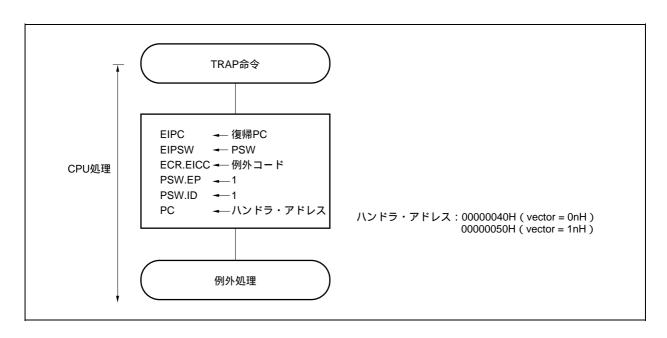

| 5 - 8            | ソフトウエア例外の処理形態 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

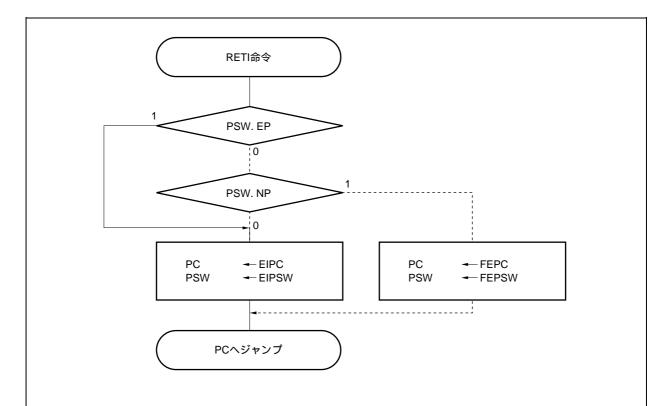

| 5 - 9            | RETI命令の処理形態 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

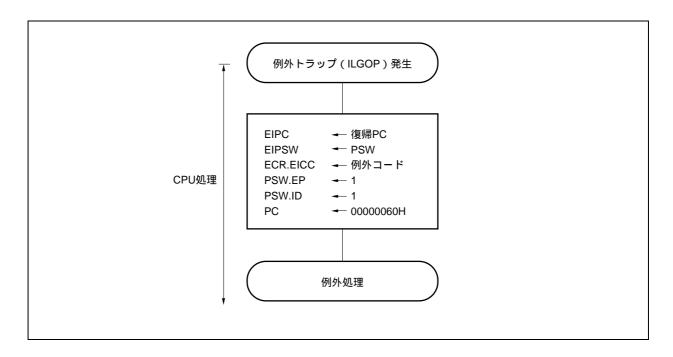

| 5 - 10           | 例外トラップの処理形態 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5 - 11           | RETI命令の処理形態 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

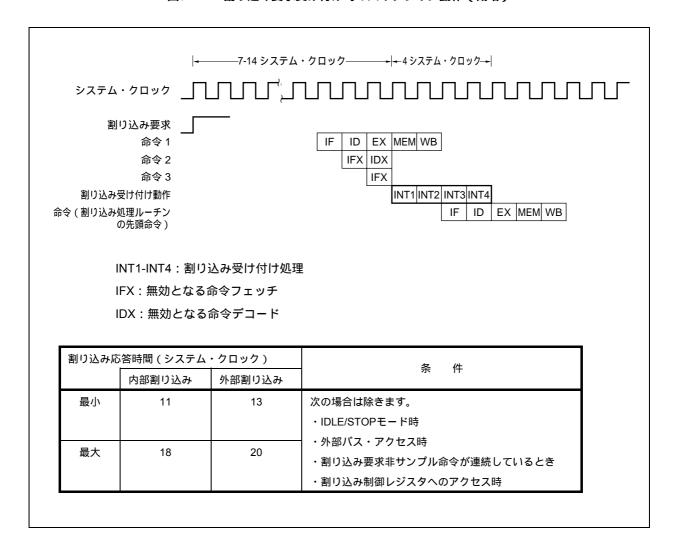

| 5 - 12           | 割り込み要求受け付け時のパイプライン動作(概略) 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5 - 13           | パイプラインの流れと要求発生のタイミング 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 - 1            | クロック発生機能 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6 - 2            | クロック出力機能のブロック図 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

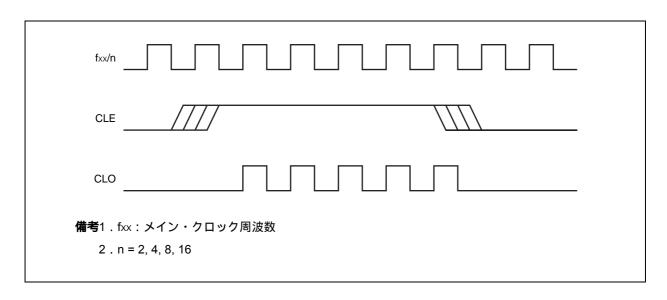

| 6 - 3            | CLO信号のタイミング 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

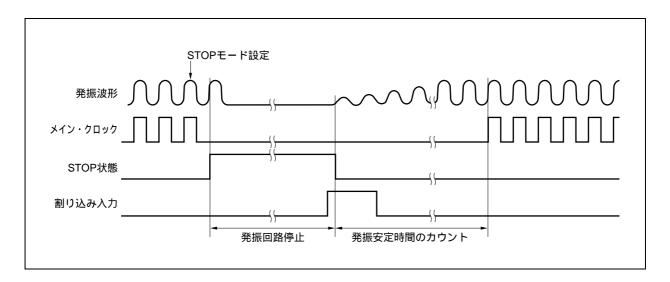

| 6 - 4            | 発振安定時間の確保 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

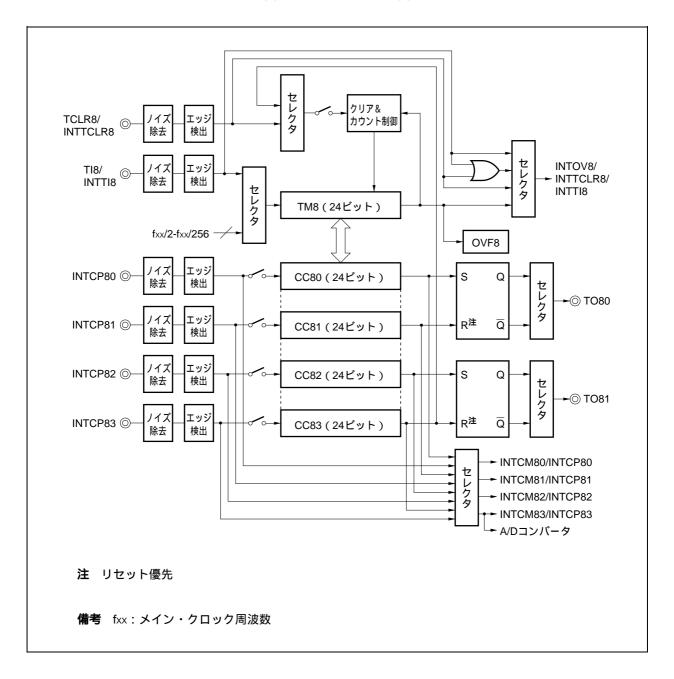

| 7 - 1            | TM8のブロック図 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

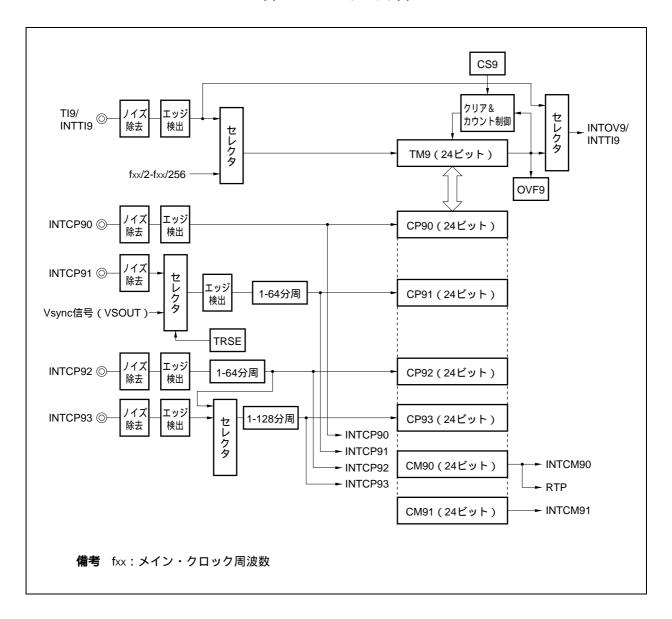

| 7 - 2            | TM9のブロック図 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7 - 3            | INTCP9m入力 ( m = 1-3 ) 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

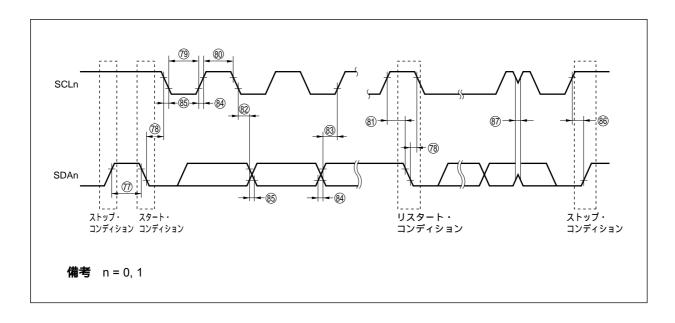

| 7 - 4            | 分周器 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |