# RL78/G1E

ユーザーズマニュアル ハードウェア編

Smart Analog IC 内蔵 16 ビット・マイクロコントローラ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、予告なしに、本資料に記載した製品または仕様を変更することがあります。

ルネサス エレクトロニクスのホームページなどにより公開される最新情報を御確認ください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、 応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアお よびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これ らの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負い ません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、 各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件 その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の 故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネ サス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する 会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

#### CMOSデバイスの一般的注意事項

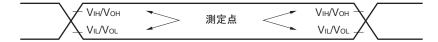

- (1) 入力端子の印加波形:入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。 CMOSデバイスの入力がノイズなどに起因して、VIL(MAX.)からVIH(MIN.)までの領域にとどまるような場合 は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、VIL(MAX.)からVIH(MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

- (2) 未使用入力の処理: CMOSデバイスの未使用端子の入力レベルは固定してください。未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpDまたはGNDに接続することが有効です。資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

- (3) 静電気対策: MOSデバイス取り扱いの際は静電気防止を心がけてください。MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、MOSデバイスを実装したボードについても同様の扱いをしてください。

- (4) 初期化以前の状態 電源投入時、MOSデバイスの初期状態は不定です。電源投入時の端子の出力状態や入出力設定、レジスタ内容などは保証しておりません。ただし、リセット動作やモード設定で定義している項目については、これらの動作ののちに保証の対象となります。リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

- (5) 電源投入切断順序 内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には、原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により、内部素子に過電圧が印加され、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

- (6) 電源OFF時における入力信号 当該デバイスの電源がOFF状態の時に、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

## このマニュアルの使い方

対 象 者 このマニュアルは、RL78/G1Eの機能を理解し、その応用システムや応用プログラムを設計、開発するユーザのエンジニアを対象としています。

対象製品は、次に示す各製品です。

・64 ピン: R5F10FLx (x = C, D, E) ・80 ピン: F5F10FMx (x = C, D, E)

- 目 的 このマニュアルは、次の構成に示す機能をユーザに理解していただくことを目的としています。

- 構 成 RL78/G1E のマニュアルは、このマニュアルと RL78/G1A ユーザーズ・マニュアル、および RL78 ファミリユーザーズ・マニュアルの 3 冊に分かれています。

RL78/G1E ユーザーズ・マニュアル ハードウェア編

• 端子機能

・内部ブロック機能

• 内蔵周辺機能

電気的特性

RL78/G1A ユーザーズ・マニュアル ハードウェア編

• 端子機能

・内部ブロック機能

割り込み

・その他の内蔵周辺機能

・電気的特性

RL78 ファミリ ユーザーズ・マニュアル ソフトウェア編

• CPU 機能

・命令セット

命令の説明

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコントローラの一般知識を必要とします。

- □一通りの機能を理解しようとするとき

- →目次に従って読んでください。本文欄外の★印は、本版で改訂された主な箇所を示しています。 この"★"を PDF 上でコピーして「検索する文字列」に指定することによって、改版箇所を容易に 検索できます。

- ロレジスタ・フォーマットの見方

- →ビット番号を口で囲んでいるものは、そのビット名称がアセンブラでは予約語に、コンパイラでは #pragma sfr 指令で、sfr 変数として定義されているものです。

- □マイクロコントローラ部の機能詳細を知りたいとき

- →別冊の RL78/G1A ユーザーズ・マニュアル ハードウェア編 (R01UH0305J) を参照してください。

- □RL78/G1Aマイクロコントローラの命令機能の詳細を知りたいとき

- →別冊の RL78 ファミリ ユーザーズ・マニュアル ソフトウェア編 (R01US0015J) を参照してください。

凡 例 データ表記の重み : 左が上位桁、右が下位桁

アクティブ・ロウの表記: XXX (端子, 信号名称に上線)

注:本文中につけた注の説明

注意 : 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…XXXXまたはXXXXB

10進数···XXXX 16進数···XXXXH

#### 関連資料

関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

#### デバイスの関連資料

| 資 料 名                         | 資料番号       |            |  |

|-------------------------------|------------|------------|--|

|                               | 和文         | 英 文        |  |

| RL78/G1E ユーザーズ·マニュアル ハードウェア編  | このマニュアル    | R01UH0353E |  |

| RL78/G1A ユーザーズ・マニュアル ハードウェア編  | R01UH0305J | R01UH0305E |  |

| RL78 ファミリ ユーザーズ・マニュアル ソフトウェア編 | R01US0015J | R01US0015E |  |

#### フラッシュ・メモリ書き込み用の資料(ユーザーズ・マニュアル)

| 資料名                    | 資料番号       |            |  |

|------------------------|------------|------------|--|

|                        | 和文         | 英文         |  |

| PG-FP5 フラッシュ・メモリ・プログラマ | R02UT0008J | R02UT0008E |  |

#### その他の資料

| 資 料 名                     |            | 資料番号       |  |

|---------------------------|------------|------------|--|

|                           | 和文         | 英 文        |  |

| ルネサス マイクロコンピュータ RL78 ファミリ | R01CS0003J | R01CS0003E |  |

| 半導体パッケージ 実装マニュアル          | 注          |            |  |

| NEC 半導体デバイスの品質水準          | C11531J    | C11531E    |  |

| 静電気放電 (ESD) 破壊対策ガイド       | C11892J    | C11892E    |  |

| 信頼性ハンドブック                 | R51ZZ0001C | R51ZZ0001E |  |

## 注 「半導体パッケージ実装マニュアル」のホーム・ページ参照

和文: http://japan.renesas.com/products/package/manual/index.jsp 英文: http://www.renesas.com/products/package/manual/index.jsp

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには、必ず最新の資料をご使用ください。

すべての商標および登録商標は、それぞれの所有者に帰属します。

EEPROMは、ルネサス エレクトロニクス株式会社の登録商標です。

SuperFlash は、米国 Silicon Storage Technology, Inc.の米国、日本などの国における登録商標です。

注意: 本製品は Silicon Storage Technology, Inc.からライセンスを受けた SuperFlash®を使用しています。

## 目次

| 第1章 概            | 説                  | 1  |

|------------------|--------------------|----|

| 1.1 特            | 徵                  | 1  |

| 1.1.1            | マイクロコントローラ部        | 1  |

| 1.1.2            | アナログ部              | 3  |

| 1.2 型名           | 一覧                 | 4  |

| 1.3 端子           | 接続図(Top View)      | 5  |

| 1.3.1            | 64 ピン製品            | 5  |

| 1.3.2            | 80 ピン製品            | 6  |

| 1.4 端子           | -名称                | 7  |

| 1.5 ブロ           | ック図                | 9  |

| 1.5.1            | 64 ピン製品            | 9  |

| 1.5.2            | 80 ピン製品            | 12 |

| 1.6 機能           | 概要                 | 15 |

| <b>かっキ 地っ</b> り  | 6 Jal-             | 40 |

|                  | 能                  |    |

|                  | クロコントローラ部の端子機能     |    |

| 2.1.1            | ポート機能              |    |

|                  | 64ピン製品             |    |

| 2.1.1.2<br>2.1.2 | 80ピン製品<br>ポート以外の機能 |    |

| 2.1.2.1          | 製品別の搭載機能           |    |

|                  | 機能説明               |    |

|                  |                    |    |

| 2.2.1            | 64 ピン製品            | 32 |

| 2.2.2            | 80 ピン製品            | 33 |

| 2.3 未使           | 用端子の処理             | 34 |

| 2.4 端子           | -ブロック図             | 36 |

| 2.5 端子           | 機能の説明              | 48 |

| 2.5.1            | ポート 0 (P00-P04)    | 48 |

| 2.5.2            | ポート1 (P10-P15)     | 50 |

| 2.5.3            | ポート 2(P20-P24)     | 52 |

| 2.5.4            | ポート4 (P40-P42)     | 53 |

| 2.5.5            | ポート 5(P50, P51)    | 54 |

| 2.5.6            | ポート7 (P70-P73)     | 55 |

| 2.5.7            | ポート 12(P121, P122) | 56 |

| 2.5.8  | ポート 13(P130, P137)                                             | 57 |

|--------|----------------------------------------------------------------|----|

| 2.5.9  | ポート 14(P140)                                                   | 58 |

| 2.5.10 | AVDD, AVSS, VDD, VSS                                           | 59 |

| 2.5.11 | RESET                                                          | 59 |

| 2.5.12 | REGC                                                           | 59 |

| 2.5.13 | AV <sub>DD3</sub>                                              | 60 |

| 2.5.14 | SC_IN                                                          | 60 |

| 2.5.15 | CLK_SYNCH                                                      | 60 |

| 2.5.16 | SYNCH_OUT                                                      | 60 |

| 2.5.17 | AGND2                                                          | 60 |

| 2.5.18 | GAINAMP_OUT                                                    | 60 |

| 2.5.19 | GAINAMP_IN                                                     | 60 |

| 2.5.20 | MPXIN10, MPXIN11, MPXIN20, MPXIN21, MPXIN30, MPXIN31, MPXIN40, |    |

|        | MPXIN41, MPXIN50, MPXIN51, MPXIN60, MPXIN61                    |    |

| 2.5.21 | AMP1_OUT, AMP2_OUT, AMP3_OUT                                   | 60 |

| 2.5.22 | DAC1_OUT, DAC2_OUT, DAC3_OUT, DAC4_OUT                         | 60 |

| 2.5.23 | VREFIN1, VREFIN2, VREFIN3, VREFIN4                             | 60 |

| 2.5.24 | AGND1                                                          | 61 |

| 2.5.25 | AV <sub>DD1</sub>                                              | 61 |

| 2.5.26 | AGND3                                                          | 61 |

| 2.5.27 | BGR_OUT                                                        | 61 |

| 2.5.28 | AV <sub>DD2</sub>                                              | 61 |

| 2.5.29 | LDO_OUT                                                        | 61 |

| 2.5.30 | TEMP_OUT                                                       | 61 |

| 2.5.31 | ARESET                                                         | 61 |

| 2.5.32 | DV <sub>DD</sub>                                               | 61 |

| 2.5.33 | SCLK                                                           | 61 |

| 2.5.34 | SDO                                                            | 61 |

| 2.5.35 | SDI                                                            | 62 |

| 2.5.36 | <u>CS</u>                                                      | 62 |

| 2.5.37 | DGND                                                           | 62 |

| 2.5.38 | HPF_OUT                                                        | 62 |

| 2.5.39 | CLK_HPF                                                        | 62 |

| 2.5.40 | CLK_LPF                                                        | 62 |

| 2.5.41 | AGND4                                                          | 62 |

| 2.5.42 | LPF_OUT                                                        | 62 |

| 2.5.43 | I.C                                                            | 62 |

| 第3章 マイク  | ロコントローラ部                                          | 63  |

|----------|---------------------------------------------------|-----|

| 3.1 概    | 要                                                 | 63  |

| 3.2 RL78 | 8/G1A(64ピン製品)との機能比較                               | 64  |

| 3.3 CPU  | <br> アーキテクチャ                                      | 68  |

| 3.3.1    | メモリ空間                                             | 68  |

| 3.3.2    | プロセッサ・レジスタ                                        | 68  |

| 3.3.2.1  | 制御レジスタ                                            |     |

| 3.3.2.2  | 汎用レジスタ                                            |     |

| 3.3.2.3  | ES, CSレジスタ                                        | 68  |

| 3.3.2.4  | 特殊機能レジスタ(SFR:Special Function Register)           | 69  |

| 3.3.2.5  | 拡張特殊機能レジスタ(2nd SFR:2nd Special Function Register) | 77  |

| 3.3.3    | 命令アドレスのアドレッシング                                    | 89  |

| 3.3.4    | 処理データ・アドレスに対するアドレッシング                             | 89  |

| 3.4 ポー   | ト機能                                               | 90  |

| 3.4.1    | ポートの機能                                            | 90  |

| 3.4.2    | ポートの構成                                            | 90  |

| 3.4.2.1  | ポート0                                              | 91  |

| 3.4.2.2  | ポート1                                              |     |

| 3.4.2.3  | ポート2                                              | 91  |

| 3.4.2.4  | ポート3                                              | 92  |

| 3.4.2.5  | ポート4                                              | 92  |

| 3.4.2.6  | ポート5                                              | 92  |

|          | ポート6                                              |     |

|          | ポート7                                              |     |

|          | ポート12                                             |     |

|          | ポート13                                             |     |

|          | ポート14                                             |     |

|          | ポート15                                             |     |

| 3.4.3    | ポート機能を制御するレジスタ                                    |     |

|          | ポート・モード・レジスタ (PMxx)                               |     |

|          | ポート・レジスタ(Pxx)                                     |     |

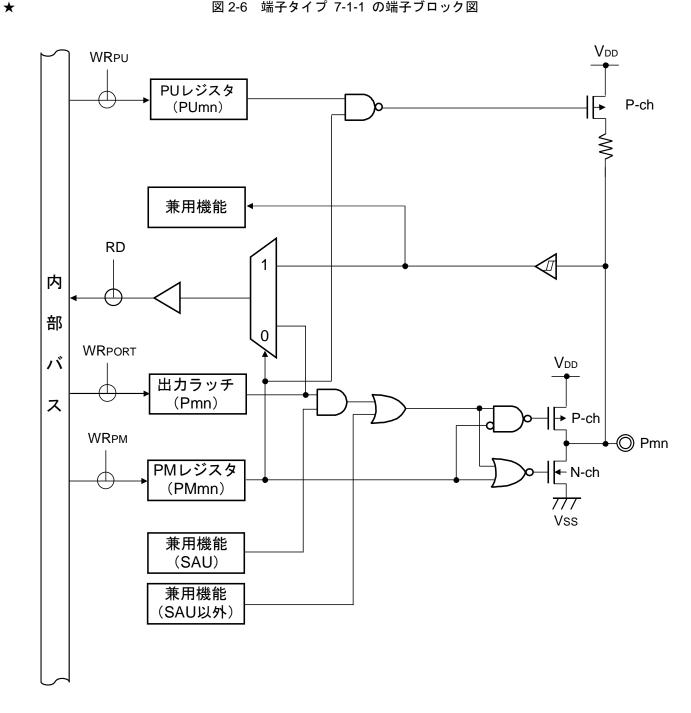

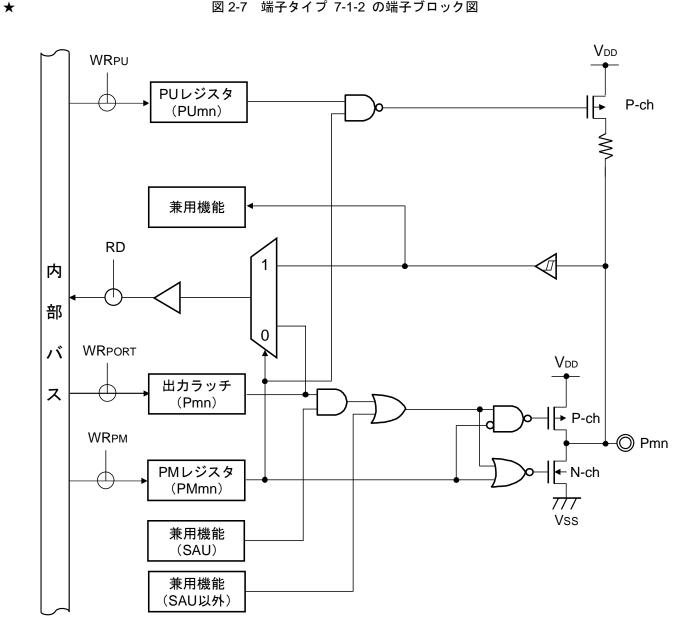

|          | プルアップ抵抗オプション・レジスタ(PUxx)ポート・入力モード・レジスタ(PIMxx)      |     |

|          | ポート・出力モード・レジスタ(POMxx)                             |     |

|          | ポート・モード・コントロール・レジスタ(PMCxx)                        |     |

|          | A/Dポート・コンフィギュレーション・レジスタ(ADPC)                     |     |

|          | 周辺I/Oリダイレクション・レジスタ(PIOR)                          |     |

|          | グローバル・デジタル・インプット・ディスエーブル・レジスタ(GDIDIS)             |     |

|          | グローバル・アナログ・インプット・ディスエーブル・レジスタ(GAIDIS)             |     |

| 3.4.4    | ポート機能の動作                                          | 103 |

| 3.4.4.1  | 入出力ポートへの書き込み                                      | 103 |

| 3.4.4.2 | 入出力ポートからの読み出し                          | 103  |

|---------|----------------------------------------|------|

| 3.4.4.3 | 入出力ポートでの演算                             | 103  |

| 3.4.4.4 | EVDD≦VDDによる異電位(1.8 V系,2.5 V系,3 V系)対応   | 103  |

| 3.4.4.5 | 入出力バッファによる異電位(1.8 V系, 2.5 V系, 3 V 系)対応 | 104  |

| 3.4.5   | 兼用機能使用時のレジスタ設定                         | 106  |

| 3.4.6   | ポート機能使用時の注意事項                          | 106  |

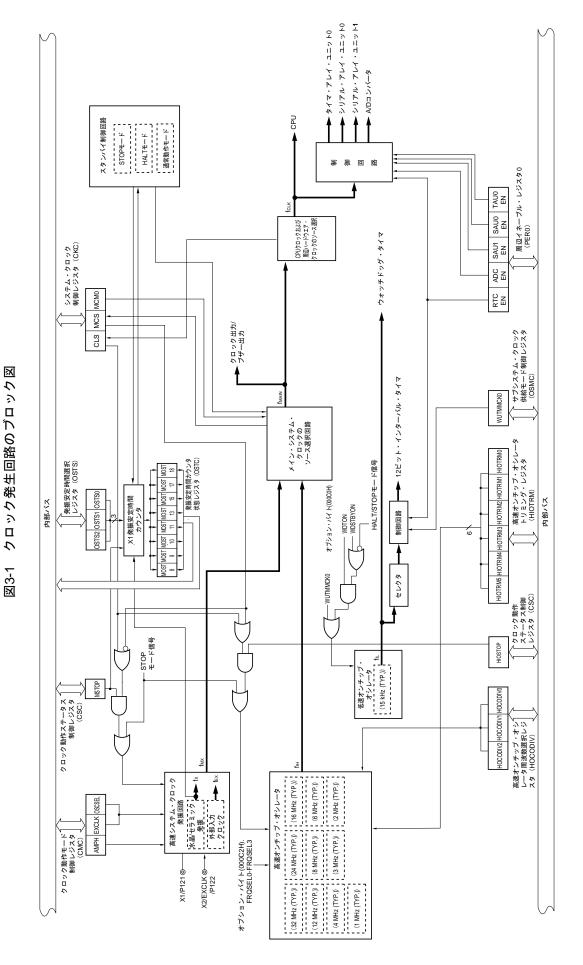

| 3.5 クロ  | コック発生回路                                | 107  |

| 3.5.1   | クロック発生回路の機能                            | 107  |

| 3.5.2   | クロック発生回路の構成                            | 109  |

| 3.5.3   | クロック発生回路を制御するレジスタ                      | 112  |

| 3.5.3.1 | クロック動作モード制御レジスタ(CMC)                   | 112  |

| 3.5.3.2 |                                        |      |

| 3.5.3.3 | クロック動作ステータス制御レジスタ(CSC)                 | 114  |

| 3.5.3.4 | 発振安定時間カウンタ状態レジスタ(OSTC)                 | 115  |

| 3.5.3.5 | 発振安定時間選択レジスタ(OSTS)                     | 115  |

| 3.5.3.6 | 周辺イネーブル・レジスタ0(PER0)                    | 116  |

| 3.5.3.7 | サブシステム・クロック供給モード制御レジスタ(OSMC)           | 117  |

| 3.5.3.8 | 高速オンチップ・オシレータ周波数選択レジスタ(HOCODIV)        | 117  |

| 3.5.3.9 | 高速オンチップ・オシレータ・トリミング・レジスタ(HIOTRM)       | 117  |

| 3.5.4   | システム・クロック発振回路                          | 118  |

| 3.5.5   | クロック発生回路の動作                            | 118  |

| 3.5.6   | クロックの制御                                | 118  |

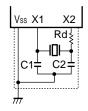

| 3.5.7   | 発振子と発振回路定数                             | 119  |

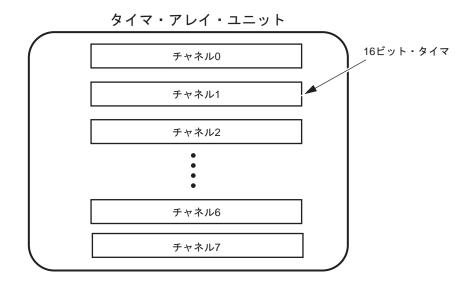

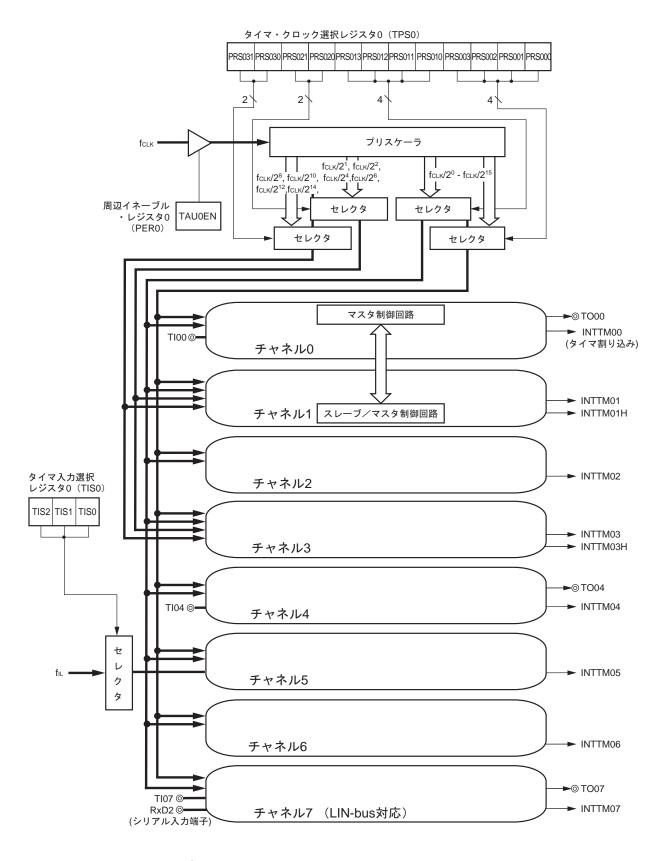

| 3.6 タイ  | イマ・アレイ・ユニット                            | 123  |

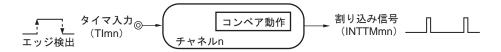

| 3.6.1   | タイマ・アレイ・ユニットの機能                        | 125  |

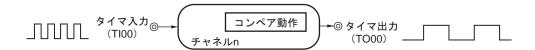

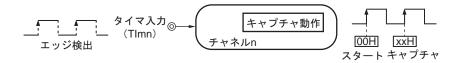

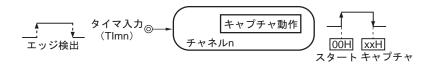

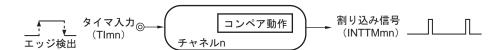

| 3.6.1.1 | 単独チャネル動作機能                             | 125  |

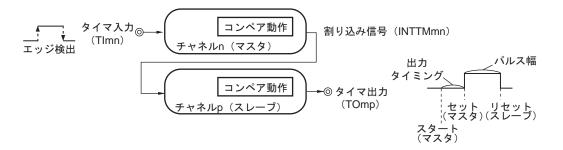

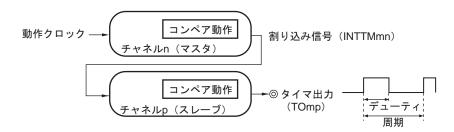

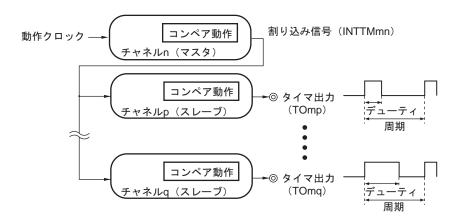

| 3.6.1.2 | 複数チャネル連動動作機能                           | 127  |

| 3.6.1.3 | 8ビット・タイマ動作機能(チャネル1, 3のみ)               | 128  |

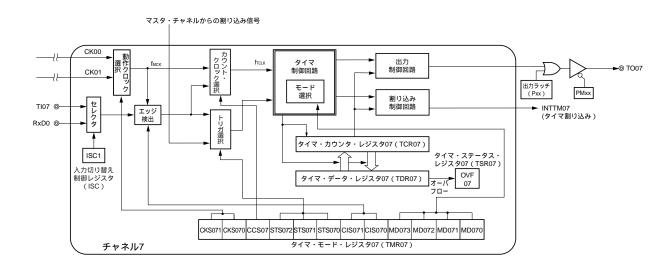

| 3.6.1.4 | LIN-bus対応機能(ユニット0のチャネル7のみ)             | 129  |

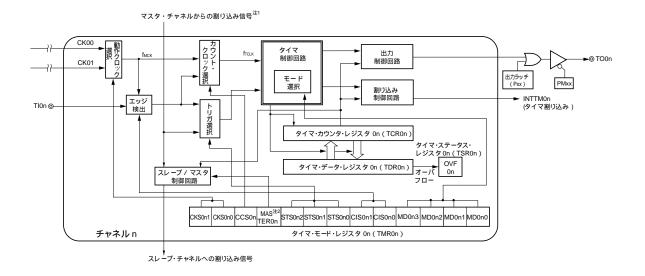

| 3.6.2   | タイマ・アレイ・ユニットの構成                        | 130  |

| 3.6.2.1 | タイマ・カウンタ・レジスタmn(TCRmn)                 | 134  |

| 3.6.2.2 | タイマ・データ・レジスタmn(TDRmn)                  | 134  |

| 3.6.3   | タイマ・アレイ・ユニットを制御するレジスタ                  | 135  |

| 3.6.3.1 | 周辺イネーブル・レジスタ0(PER0)                    | 135  |

| 3.6.3.2 | タイマ・クロック選択レジスタm(TPSm)                  | 135  |

| 3.6.3.3 | タイマ・モード・レジスタmn(TMRmn)                  | 136  |

| 3.6.3.4 | タイマ・ステータス・レジスタmn(TSRmn)                | 141  |

| 3.6.3.5 | タイマ・チャネル許可ステータス・レジスタm(TEm)             | 141  |

| 3.6.3.6 | タイマ・チャネル開始レジスタm(TSm)                   | 141  |

| 3.6.3.7 | タイマ・チャネル停止レジスタm(TTm)                   | 141  |

| 2620    | タイプ 7 中選択し、ジフタの(TISO)                  | 1.11 |

| 3.6   | 3.3.9 | タイマ出力許可レジスタm(TOEm)            | 142 |

|-------|-------|-------------------------------|-----|

| 3.6   | 3.10  | タイマ出力レジスタm(TOm)               | 142 |

| 3.6   | 3.11  | タイマ出力レベル・レジスタm(TOLm)          | 143 |

| 3.6   | 3.12  | タイマ出力モード・レジスタm(TOMm)          | 143 |

|       |       | 入力切り替え制御レジスタ (ISC)            |     |

|       |       | ノイズ・フィルタ許可レジスタ1(NFEN1)        |     |

|       |       | タイマ入出力端子のポート機能を制御するレジスタ       |     |

| 3.6.4 |       | タイマ・アレイ・ユニットの基本ルール            |     |

| 3.6.5 | 5     | カウンタの動作                       |     |

| 3.6.6 | 3     | チャネル出力(TOmn 端子)の制御            | 146 |

| 3.6.7 | 7     | タイマ入力(TImn)の制御                | 146 |

| 3.6.8 | 3     | タイマ・アレイ・ユニットの単独チャネル動作機能       | 146 |

| 3.6.9 | 9     | タイマ・アレイ・ユニットの複数チャネル連動動作機能     | 146 |

| 3.6.  | 10    | タイマ・アレイ・ユニット使用時の注意事項          | 146 |

| 3.7   | リア    | ゚ルタイム・クロック                    | 147 |

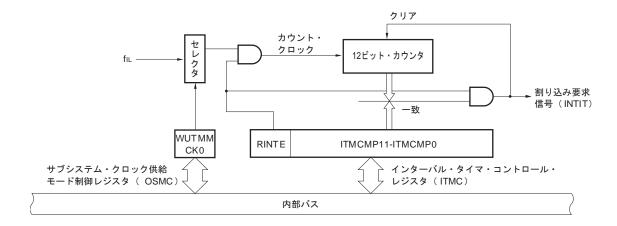

| 3.8   | 12 E  | ゙゙ット・インターバル・タイマ               | 148 |

| 3.8.  | l     | 12 ビット・インターバル・タイマの機能          | 148 |

| 3.8.2 | 2     | 12 ビット・インターバル・タイマの構成          | 148 |

| 3.8.3 | 3     | 12 ビット・インターバル・タイマを制御するレジスタ    | 149 |

| 3.8   | 3.3.1 | 周辺イネーブル・レジスタ0(PERO)           |     |

| 3.8   | 3.3.2 | サブシステム・クロック供給モード制御レジスタ(OSMC)  |     |

| 3.8   | 3.3.3 | インターバル・タイマ・コントロール・レジスタ(ITMC)  | 149 |

| 3.8.4 | 1     | 12 ビット・インターバル・タイマの動作          | 150 |

| 3.9   | クロ    | ック出力/ブザー出力制御回路                | 151 |

| 3.9.  | l     | クロック出力/ブザー出力制御回路の機能           | 151 |

| 3.9.2 | 2     | クロック出力/ブザー出力制御回路の構成           | 152 |

| 3.9.3 | 3     | クロック出力/ブザー出力制御回路を制御するレジスタ     | 152 |

| 3.9   | .3.1  | クロック出力選択レジスタ0(CKS0)           | 153 |

| 3.9   | .3.2  | クロック出力/ブザー出力端子のポート機能を制御するレジスタ | 154 |

| 3.9.4 | 1     | クロック出力/ブザー出力制御回路の動作           | 154 |

| 3.9.5 | 5     | クロック出力/ブザー出力制御回路の注意事項         | 154 |

| 3.10  | ウォ    | ッチドッグ・タイマ                     | 155 |

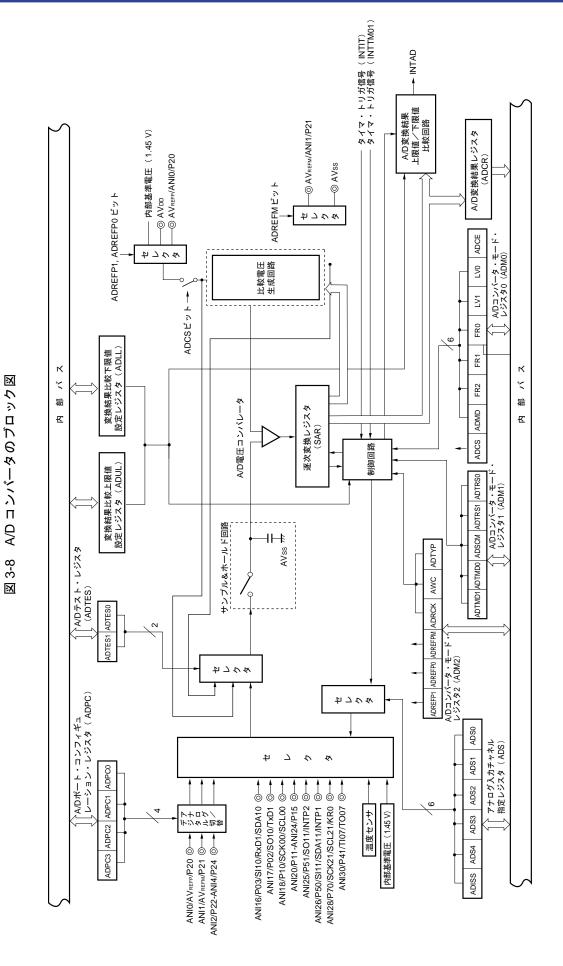

| 3.11  | A/D   | コンバータ                         | 156 |

| 3.11  | .1    | A/D コンバータの機能                  | 156 |

| 3.11  | .2    | A/D コンバータの構成                  | 159 |

| 3.11  | .3    | A/D コンバータを制御するレジスタ            |     |

| 3.1   | 1.3.1 | 周辺イネーブル・レジスタ0(PERO)           |     |

|       |       | A/Dコンバータ・モード・レジスタ0 (ADM0)     |     |

|       |       | A/Dコンバータ・モード・レジスタ1(ADM1)      |     |

|       |       | Δ/Dコンバータ・エード・レジスタ2 (ΔDM2)     | 163 |

| 3.11.3. | 5 12ビットA/D変換結果レジスタ(ADCR)                  | 163 |

|---------|-------------------------------------------|-----|

| 3.11.3. | 6 8ビットA/D変換結果レジスタ (ADCRH)                 | 163 |

| 3.11.3. | 7 アナログ入力チャネル指定レジスタ(ADS)                   | 164 |

| 3.11.3. | 8 変換結果比較上限値設定レジスタ(ADUL)                   | 168 |

| 3.11.3. | 9 変換結果比較下限値設定レジスタ(ADLL)                   | 168 |

| 3.11.3. |                                           |     |

| 3.11.3. | 11 アナログ入力端子のポート機能を制御するレジスタ                |     |

| 3.11.4  | A/D コンバータの変換動作                            | 169 |

| 3.11.5  | 入力電圧と変換結果                                 | 169 |

| 3.11.6  | A/D コンバータの動作モード                           | 169 |

| 3.11.7  | A/D コンバータの設定フロー・チャート                      | 169 |

| 3.11.8  | SNOOZE モード機能                              | 169 |

| 3.11.9  | A/D コンバータ特性表の読み方                          | 169 |

| 3.11.10 | A/D コンバータの注意事項                            | 169 |

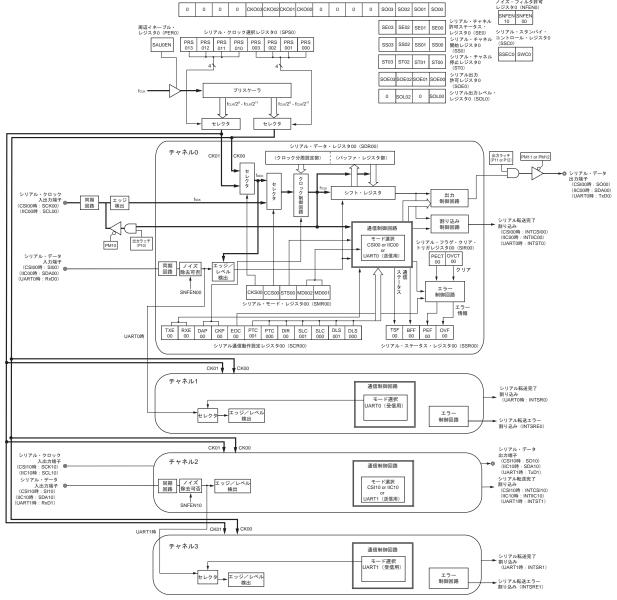

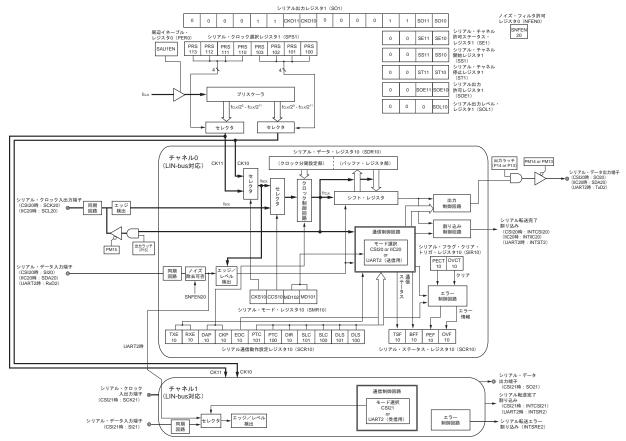

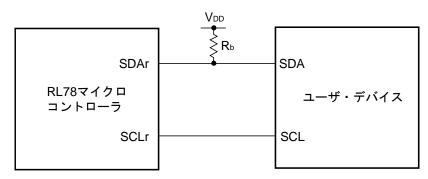

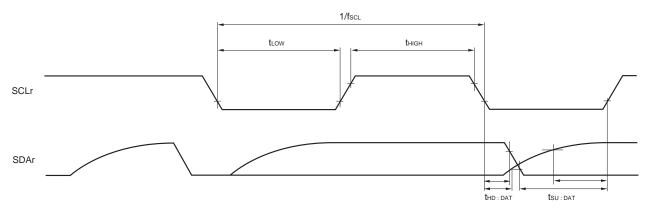

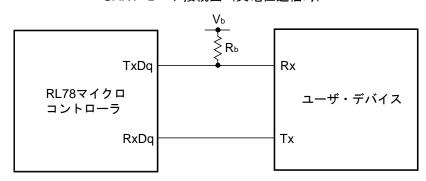

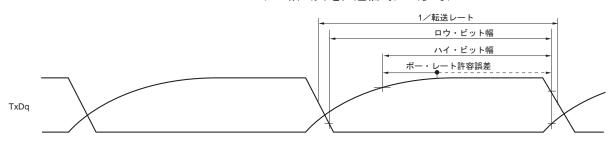

| 3.12 シリ | Jアル・アレイ・ユニット                              | 170 |

| 3.12.1  |                                           |     |

| -       | 1 3線シリアルI/O(CSI00, CSI10, CSI20, CSI21)   |     |

|         | 2 UART (UART0-UART2)                      |     |

|         | 3 簡易I <sup>2</sup> C(IIC00, IIC10, IIC20) |     |

|         | シリアル・アレイ・ユニットの構成                          |     |

|         | 1 シフト・レジスタ                                |     |

|         | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |     |

| 3.12.3  |                                           |     |

| 3 12 3  | 1 周辺イネーブル・レジスタ0(PERO)                     |     |

|         | - /ji /ge -                               |     |

|         | 3 シリアル・モード・レジスタmn(SMRmn)                  |     |

|         | 4 シリアル通信動作設定レジスタmn(SCRmn)                 |     |

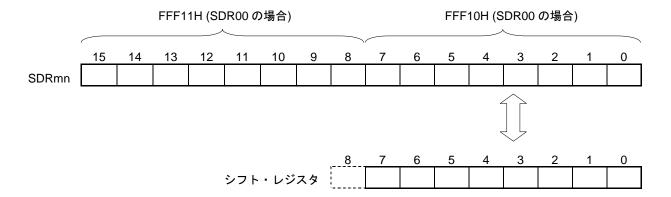

|         | 5 シリアル・データ・レジスタmn(SDRmn)の上位7ビット           |     |

| 3.12.3. | 。<br>6 シリアル・フラグ・クリア・トリガ・レジスタmn(SIRmn)     | 187 |

| 3.12.3. | 7 シリアル・ステータス・レジスタmn(SSRmn)                | 187 |

| 3.12.3. | 8 シリアル・チャネル開始レジスタm(SSm)                   | 187 |

| 3.12.3. | 9 シリアル・チャネル停止レジスタm(STm)                   | 187 |

| 3.12.3. | 10 シリアル・チャネル許可ステータス・レジスタm(SEm)            | 187 |

| 3.12.3. | 11 シリアル出力許可レジスタm(SOEm)                    | 187 |

| 3.12.3. | 12 シリアル出カレジスタm(SOm)                       | 187 |

| 3.12.3. | 13 シリアル出力レベル・レジスタm(SOLm)                  | 188 |

| 3.12.3. |                                           |     |

| 3.12.3. |                                           |     |

| 3.12.3. |                                           |     |

| 3.12.3. | 17 シリアル入出力端子のポート機能を制御するレジスタ               | 189 |

| 2 12 /  | 動作停止モード                                   | 190 |

| 3.12       | 2.5    | 3 線シリアル I/O(CSI00, CSI10, CSI20, CSI21)通信の動作             | 190  |

|------------|--------|----------------------------------------------------------|------|

| 3.12       | 2.6    | UART(UART0-UART2)通信の動作                                   | 190  |

| 3.12       | 2.7    | LIN 通信の動作                                                | 190  |

| 3.12       | 2.8    | 簡易 I <sup>2</sup> C(IIC00, IIC10, IIC20)通信の動作            | 190  |

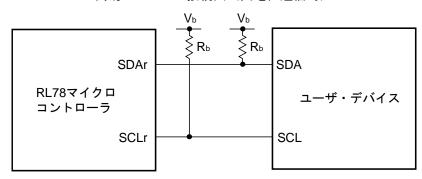

| 3.13       | シリ     | アル・インタフェースIICA                                           | 191  |

| 3.14       | 乗除     | 積和算器                                                     | 192  |

| 3.15       | DMA    | <b>\</b> コントローラ                                          | 193  |

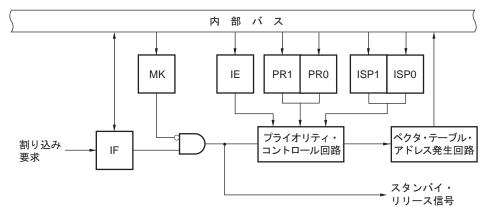

| 3.16       | 割り     | 込み機能                                                     | .194 |

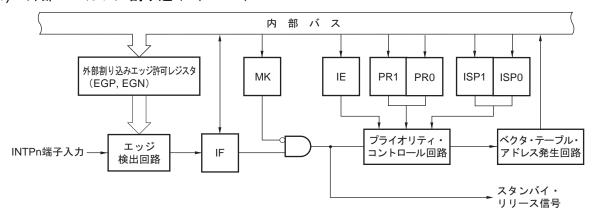

| 3.16       | 5.1    | 割り込み機能の種類                                                | 194  |

| 3.16       | 6.2    | 割り込み要因と構成                                                | 194  |

| 3.16       | 5.3    | 割り込み機能を制御するレジスタ                                          | 200  |

| 3.         | 16.3.1 | 割り込み要求フラグ・レジスタ(IF0L, IF0H, IF1L, IF1H, IF2L, IF2H)       | 205  |

| 3.         | 16.3.2 | 割り込みマスク・フラグ・レジスタ(MK0L, MK0H, MK1L, MK1H, MK2L,MK2H)      | .207 |

| 3.         | 16.3.3 | 優先順位指定フラグ・レジスタ(PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, |      |

|            |        | PR10L, PR10H, PR11L, PR11H, PR12L, PR12H)                | 209  |

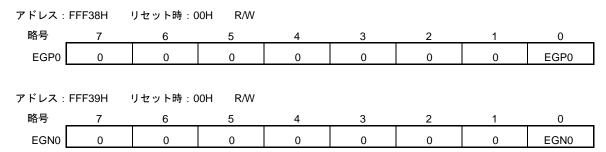

| 3.         | 16.3.4 | 外部割り込み立ち上がりエッジ許可レジスタ (EGPO), 外部割り込み立ち下がりエッジ              |      |

| •          |        | 許可レジスタ(EGN0)                                             |      |

| 3.<br>3.16 |        | プログラム・ステータス・ワード(PSW)<br>割り込み処理動作                         |      |

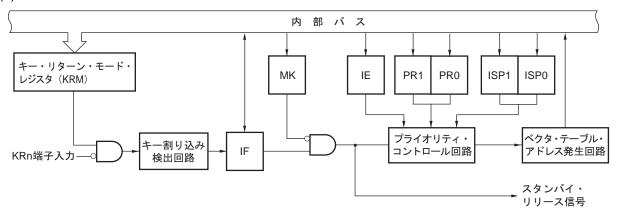

|            |        | 割り込み機能                                                   |      |

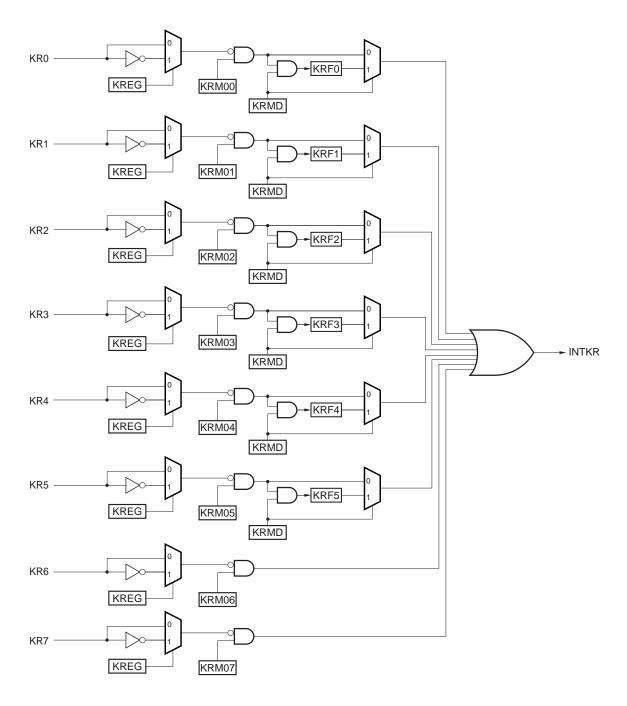

| 3.17       |        | キー割り込みの機能                                                |      |

| 3.17       |        | キー割り込みの構成                                                |      |

| 3.17       |        | キー割り込みを制御するレジスタ                                          |      |

| _          | -      | キー・リターン・コントロール・レジスタ(KRCTL)                               |      |

|            |        | キー・リターン・モード・レジスタ0 (KRM0)                                 |      |

|            |        | キー・リターン・フラグ・レジスタ(KRF)                                    |      |

|            |        | ポート・モード・レジスタ0-2, 7(PM0-PM2, PM7)                         |      |

|            |        | 周辺I/Oリダイレクション・レジスタ(PIOR)                                 |      |

| 3.17       | 7.4    | キー割り込み機能の動作                                              | 219  |

| 3.18       | スタ     | ンバイ機能                                                    | 220  |

| 3.19       | リセ     | ット機能                                                     | 221  |

| 3.20       | パワ     | ーオン・リセット回路                                               | 222  |

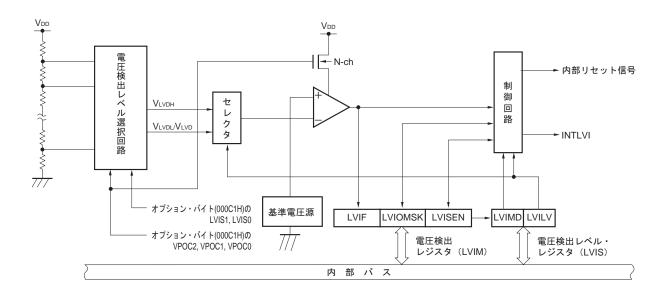

| 3.21       | 電圧     | 検出回路                                                     | 223  |

| 3.2        | 1.1    | 電圧検出回路の機能                                                | 223  |

| 3.21       | 1.2    | 電圧検出回路の構成                                                |      |

| 3.21       | 1.3    | 電圧検出回路を制御するレジスタ                                          |      |

|            |        | 電圧検出レジスタ(LVIM)                                           |      |

|            |        | 電圧検出レベル・レジスタ(LVIS)                                       |      |

| 3.2        | 1.4    | 電圧検出回路の動作                                                | 228  |

| 3.21       | 1.5    | 電圧検出回路の注意事項                                              | 228  |

| 3.22 安全  | ≧機能                                        | 229  |

|----------|--------------------------------------------|------|

| 3.22.1   | 安全機能の概要                                    | 229  |

| 3.22.2   | 安全機能で使用するレジスタ                              | 230  |

| 3.22.3   | 安全機能の動作                                    | 230  |

| 3.22.3.1 | │ フラッシュ・メモリCRC演算機能(高速CRC)                  | 230  |

| 3.22.3.2 | 2 CRC演算機能(汎用CRC)                           | 230  |

| 3.22.3.3 | 3 RAMパリティ・エラー検出機能                          | 230  |

|          | 1 RAMガード機能                                 |      |

|          | 5 SFRガード機能                                 |      |

|          | 3 不正メモリ・アクセス検出機能                           |      |

|          | <sup>7</sup> 周波数検出機能                       |      |

|          | 3 A/Dテスト機能                                 |      |

|          | デュレータ                                      |      |

| 3.24 オス  | プション・バイト                                   |      |

| 3.24.1   | - · · · - · · · · · · · · · · · · · · ·    |      |

|          | ユーザ・オプション・バイト(000C0H-000C2H/010C0H-010C2H) |      |

|          | 2 オンチップ・デバッグ・オプション・バイト(000C3H/010C3H)      |      |

| 3.24.2   | ユーザ・オプション・バイトのフォーマット                       |      |

| 3.24.3   | オンチップ・デバッグ・オプション・バイトのフォーマット                |      |

| 3.24.4   | オプション・バイトの設定                               |      |

| 3.25 フラ  | ラッシュ・メモリ                                   | 239  |

| 3.25.1   | フラッシュ・メモリ・プログラマによるシリアル・プログラミング             | 239  |

| 3.25.1.1 | プログラミング環境                                  | 240  |

| 3.25.1.2 | 2 通信方式                                     | 240  |

| 3.25.2   | 外部デバイス(UART 内蔵)によるシリアル・プログラミング             | 241  |

| 3.25.3   | オンボード上の端子処理                                | 241  |

| 3.25.4   | シリアル・プログラミング方法                             | 241  |

| 3.25.5   | PG-FP5 使用時の各コマンド処理時間(参考値)                  | 241  |

| 3.25.6   | セルフ・プログラミング                                | 241  |

| 3.25.7   | セキュリティ設定                                   | 241  |

| 3.25.8   | データ・フラッシュ                                  | 241  |

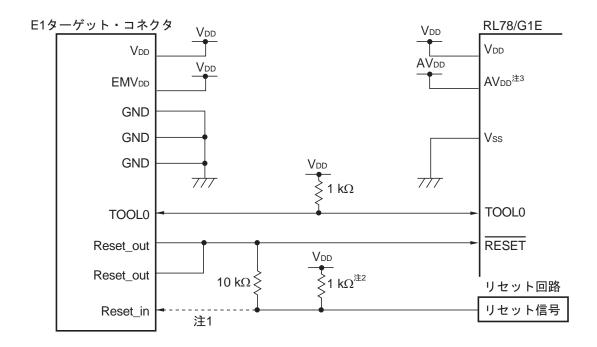

| 3.26 オン  | ノチップ・デバッグ機能                                | 242  |

| 3.26.1   | E1 オンチップデバッギングエミュレータと RL78/G1E の接続         |      |

| 3.26.2   | オンチップ・デバッグ・セキュリティ ID                       |      |

|          | ユーザ資源の確保                                   |      |

|          | - ユーノ貝(Mの能体<br>単補正(BCD)回路                  |      |

|          | E補圧(BCD)回路                                 |      |

| 3.28 命令  | コピットの <b>恢</b> 安                           | 245  |

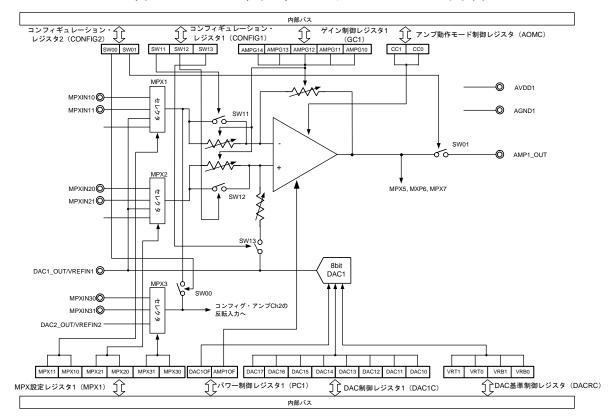

| 第4章 アナロ  | コグ部                                        | 246  |

| 4.4      |                                            | 0.40 |

| 4.1.1 | コンフィギュラブル・アンプの機能概要     | 246 |

|-------|------------------------|-----|

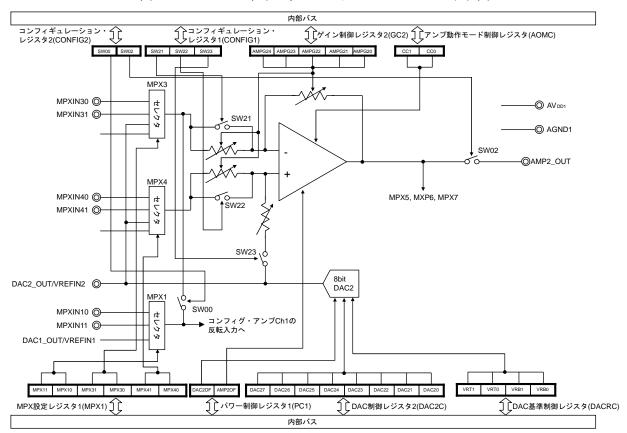

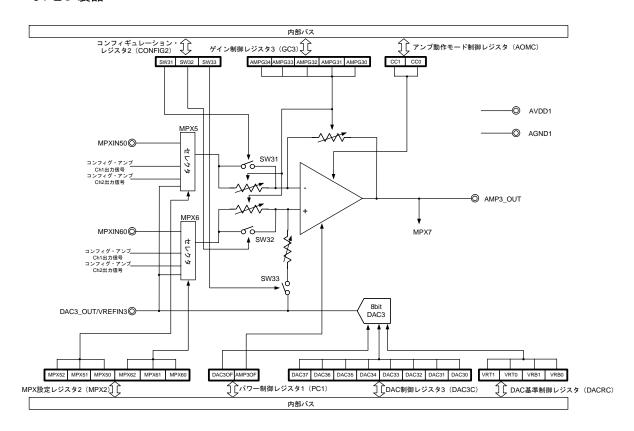

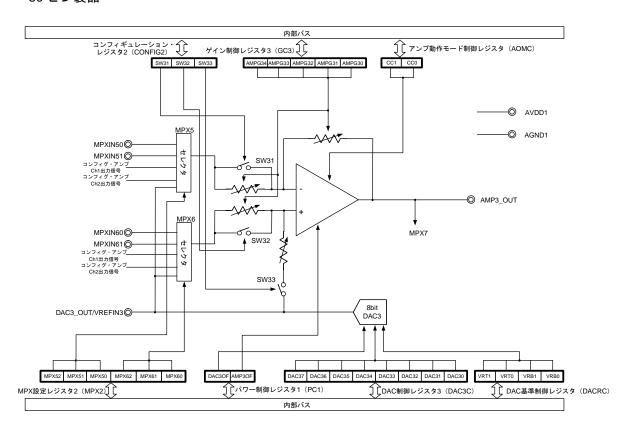

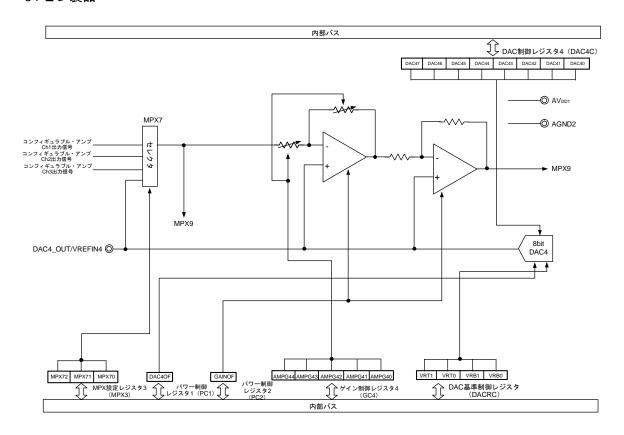

| 4.1.2 | ブロック図                  | 247 |

| 4.1.3 | コンフィギュラブル・アンプを制御するレジスタ | 250 |

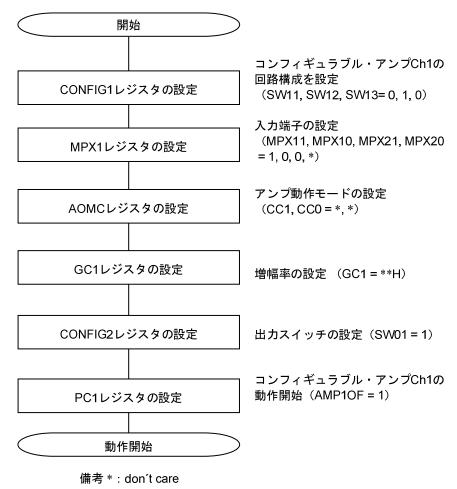

| 4.1.4 | コンフィギュラブル・アンプの動作手順     | 268 |

| 4.2   | ゲイン調整アンプ               | 282 |

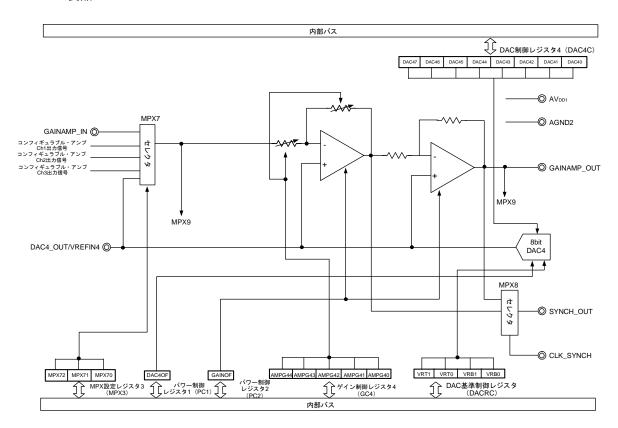

| 4.2.1 | ゲイン調整アンプの機能概要          | 282 |

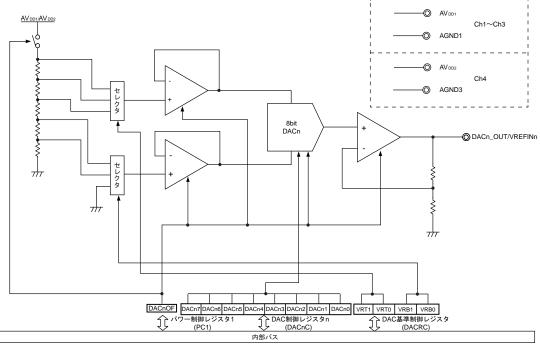

| 4.2.2 | ブロック図                  | 282 |

| 4.2.3 | ゲイン調整アンプを制御するレジスタ      | 284 |

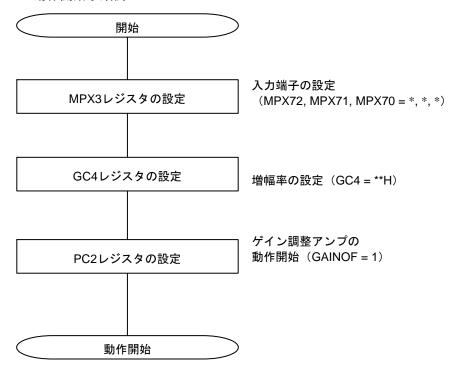

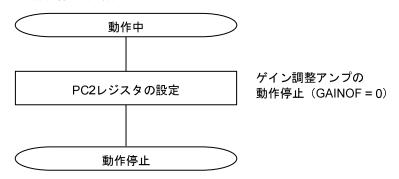

| 4.2.4 | ゲイン調整アンプの動作手順          | 287 |

| 4.3   | D/Aコンバータ               | 288 |

| 4.3.1 | D/A コンバータの機能概要         | 288 |

| 4.3.2 | ブロック図                  | 288 |

| 4.3.3 | D/A コンバータを制御するレジスタ     | 289 |

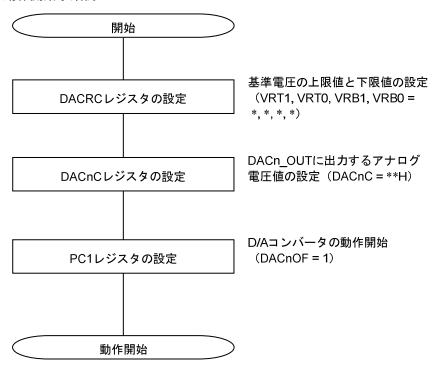

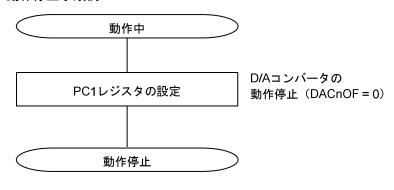

| 4.3.4 | D/A コンバータの動作手順         | 291 |

| 4.3.5 | D/A コンバータ使用上の注意点       | 292 |

| 4.4   | ローパス・フィルタ              | 293 |

| 4.4.1 | ローパス・フィルタの機能概要         | 293 |

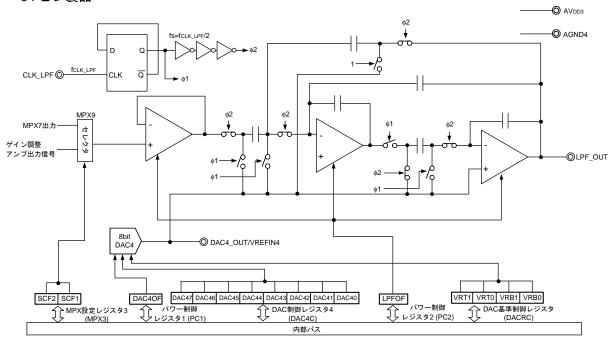

| 4.4.2 | ブロック図                  | 294 |

| 4.4.3 | ローパス・フィルタを制御するレジスタ     | 295 |

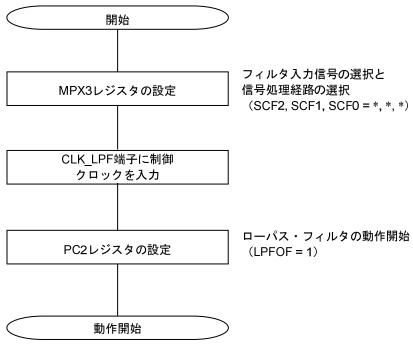

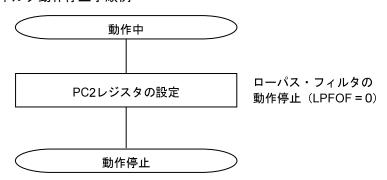

| 4.4.4 | ローパス・フィルタの動作手順         | 297 |

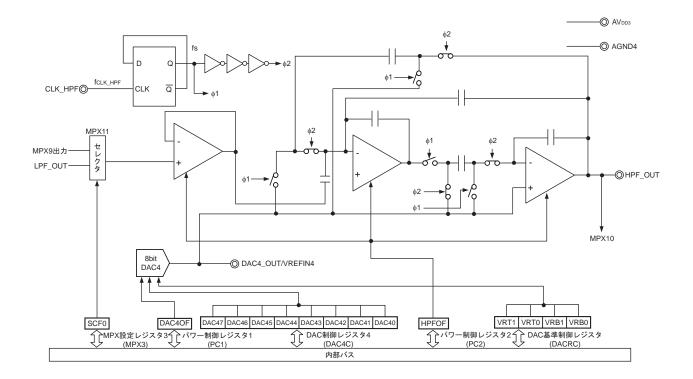

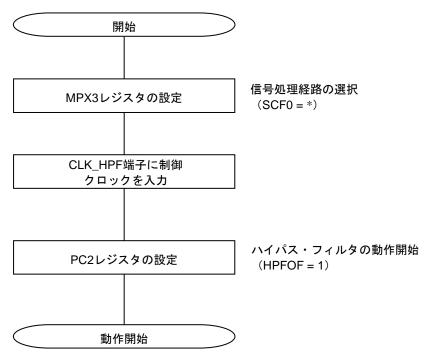

| 4.5   | ハイパス・フィルタ              | 298 |

| 4.5.1 | ハイパス・フィルタの機能概要         | 298 |

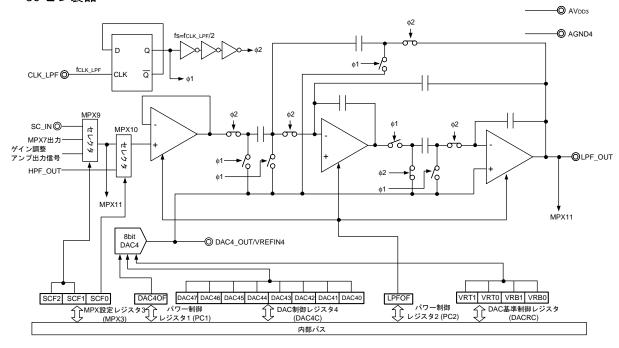

| 4.5.2 | ブロック図                  | 299 |

| 4.5.3 | ハイパス・フィルタを制御するレジスタ     | 300 |

| 4.5.4 | ハイパス・フィルタの動作手順         | 302 |

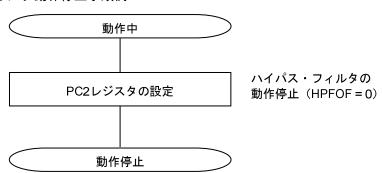

| 4.6   | 温度センサ回路                | 303 |

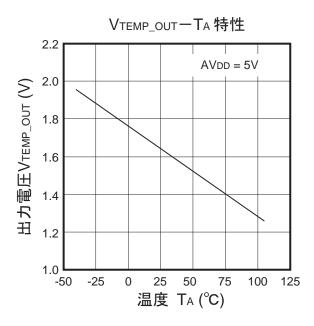

| 4.6.1 | 温度センサ回路の機能概要           | 303 |

| 4.6.2 | ブロック図                  | 303 |

| 4.6.3 | 温度センサ回路を制御するレジスタ       | 304 |

| 4.6.4 | 温度センサ回路の動作手順           | 305 |

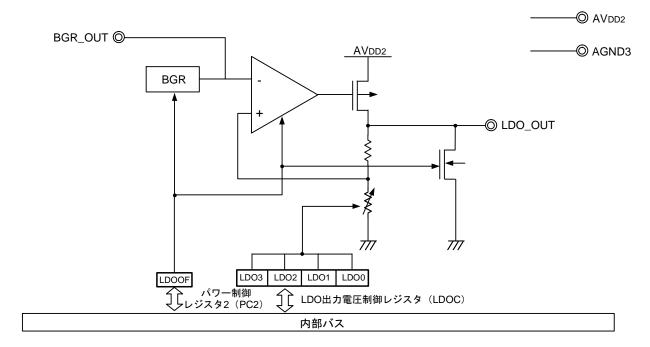

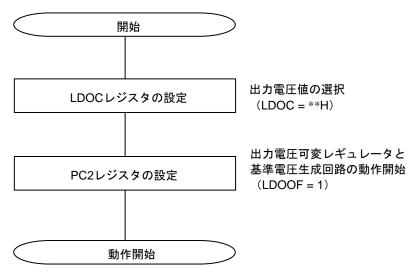

| 4.7   | 出力電圧可変レギュレータ           | 306 |

| 4.7.1 | 出力電圧可変レギュレータの機能概要      | 306 |

| 4.7.2 | ブロック図                  | 306 |

| 4.7.3 | 出力電圧可変レギュレータを制御するレジスタ  | 307 |

| 4.7.4 | 出力電圧可変レギュレータの動作手順      | 309 |

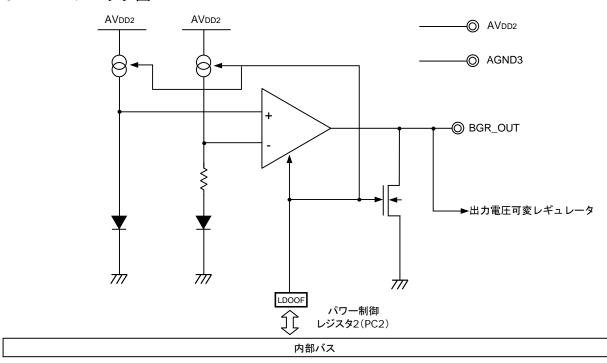

| 4.8   | 基準電圧生成回路               | 310 |

| 4.8.1 | 基準電圧生成回路の機能概要          | 310 |

| 122   | ブロック図                  | 310 |

| 4.8.3   | 基準電圧生成回路を制御するレジスタ                      | 311 |

|---------|----------------------------------------|-----|

| 4.8.4   | 基準電圧生成回路の動作手順                          | 311 |

| 4.8.5   | 基準電圧生成回路使用上の注意点                        | 311 |

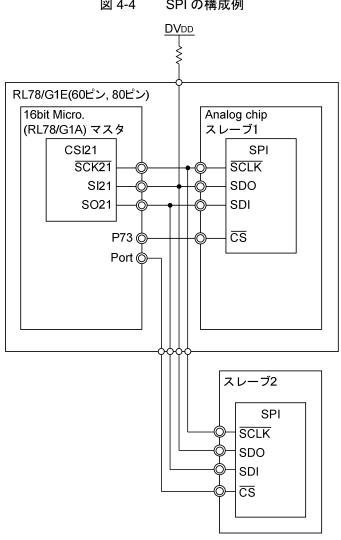

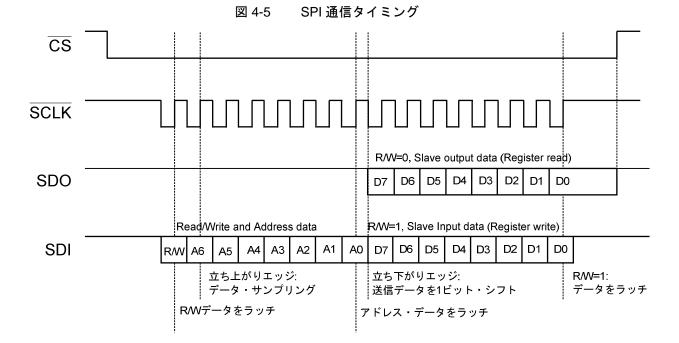

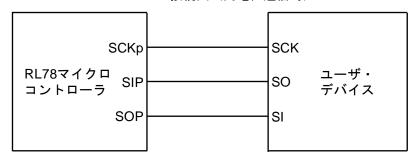

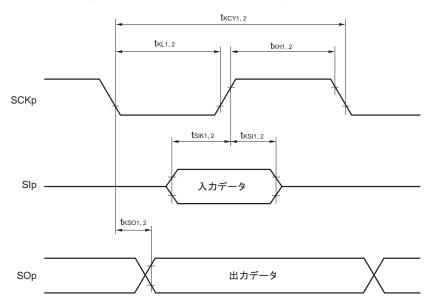

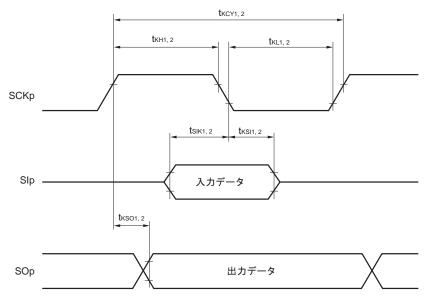

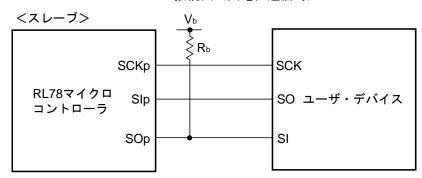

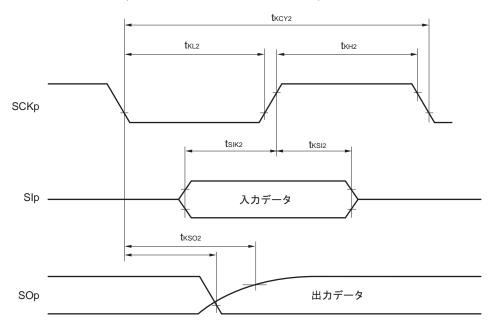

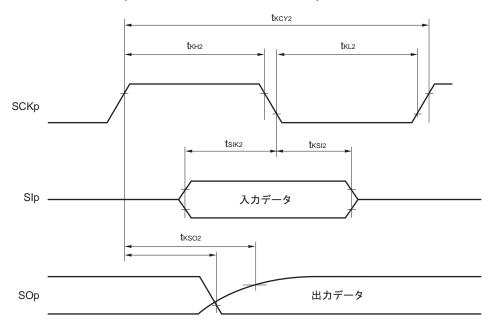

| 4.9 SPI |                                        | 312 |

| 4.9.1   | SPI の機能                                | 312 |

| 4.9.2   | SPI 通信動作                               | 313 |

| 4.10 アナ | -ログ・リセット機能                             | 315 |

| 4.10.1  | アナログ・リセット機能の概要                         | 315 |

| 4.10.2  | アナログ・リセットを制御するレジスタ                     | 318 |

| 第5章 電気的 | 5特性                                    | 319 |

| 5.1 絶対  | ·<br>才最大定格                             | 320 |

| 5.1.1   | マイクロコントローラ部の絶対最大定格                     | 320 |

| 5.1.2   | アナログ部の絶対最大定格                           | 322 |

| 5.1.3   | 絶対最大定格(マイクロコントローラ部,アナログ部共通)            | 322 |

| 5.2 マイ  | <sup>′</sup> クロコントローラ部の電気的特性           | 323 |

| 5.2.1   | 発振回路特性                                 | 323 |

| 5.2.1.1 | X1発振回路特性                               | 323 |

| 5.2.1.2 | オンチップ・オシレータ特性                          | 324 |

| 5.2.2   | DC 特性                                  | 325 |

| 5.2.2.1 | 端子特性                                   | 325 |

| 5.2.2.2 | 電源電流特性                                 | 331 |

| 5.2.3   | AC 特性                                  | 336 |

| 5.2.4   | 周辺機能特性                                 | 341 |

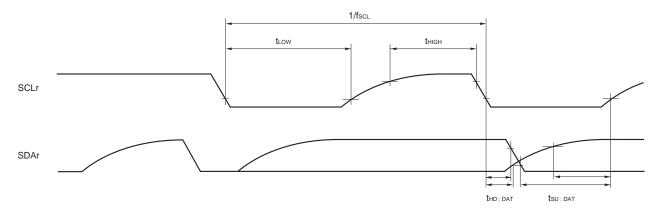

| 5.2.4.1 | シリアル・アレイ・ユニット                          | 341 |

| 5.2.5   | アナログ特性                                 | 371 |

|         | A/Dコンバータ特性                             |     |

|         | 温度センサ/内部基準電圧出力特性                       |     |

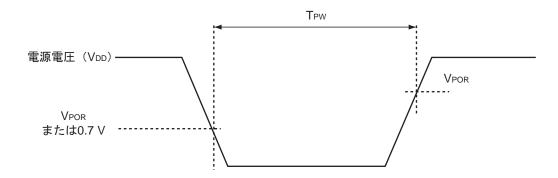

|         | POR回路特性                                |     |

|         | LVD回路特性                                |     |

| 5.2.5.5 | 電源電圧立ち上がり傾き特性                          |     |

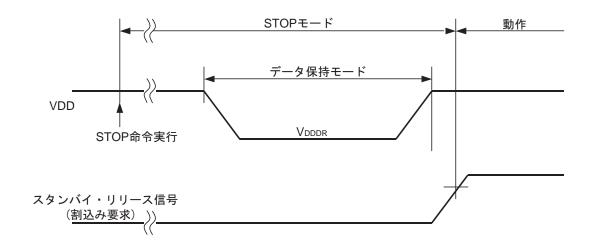

| 5.2.6   | データ・メモリ STOP モード低電源電圧データ保持特性           |     |

| 5.2.7   | フラッシュ・メモリ・プログラミング特性                    |     |

| 5.2.8   | 専用フラッシュ・メモリ・プログラマ通信(UART)              |     |

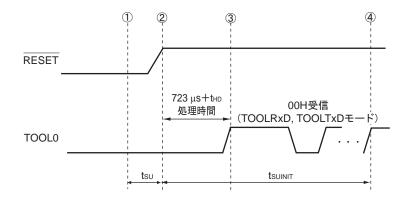

| 5.2.9   | フラッシュ・メモリ・プログラミング・モードの引き込み時のタイミング・スペック |     |

|         | - ログ部の電気的特性                            |     |

| 5.3.1   | アナログ部の動作条件                             |     |

| 5.3.2   | 電源電流特性                                 | 384 |

| 533     | 冬機能の雷気的特性                              | 386 |

|     |         | コンフィギュラブル・アンプ特性          |     |

|-----|---------|--------------------------|-----|

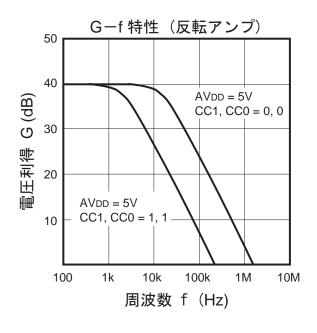

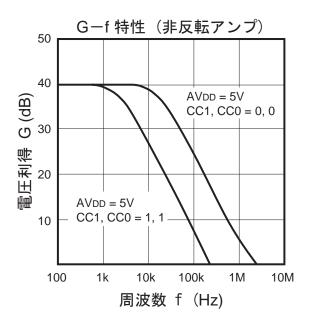

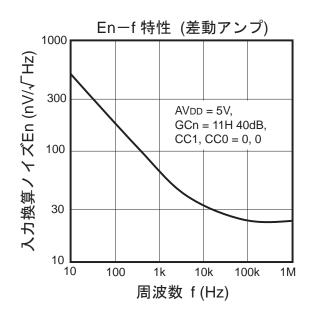

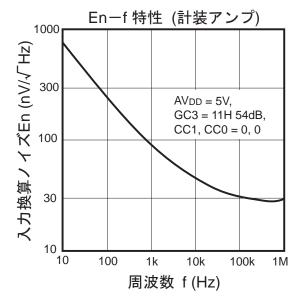

|     | 5.3.3.2 | ゲイン調整アンプ特性               | 396 |

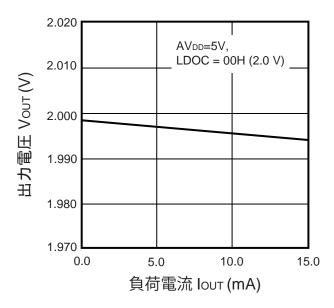

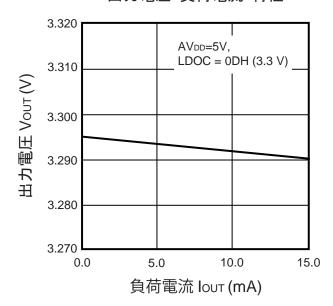

|     | 5.3.3.3 | D/Aコンバータ特性               | 398 |

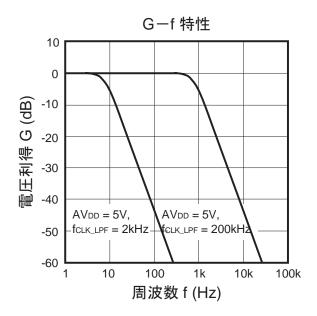

|     | 5.3.3.4 | ローパス・フィルタ回路特性            | 399 |

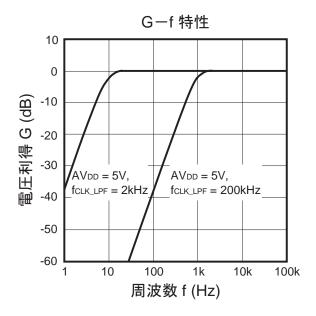

|     |         | ハイパス・フィルタ回路特性            |     |

|     | 5.3.3.6 | 温度センサ回路特性                | 401 |

|     |         | 出力電圧可変レギュレータ特性           |     |

|     | 5.3.3.8 | 基準電圧生成回路特性               | 401 |

|     | 5.3.3.9 | SPI                      | 402 |

| 第 6 | 章 外形図   | ]                        | 404 |

| 付録  | A 特性曲   | 線 (TA = 25°C,TYP.) (参考値) | 406 |

| 付録  | B 改訂履   | 歴                        | 413 |

| В.  | 1 本版で   | <b>收訂された主な箇所</b>         | 413 |

| В.: | 2 前版まっ  | での改版履歴                   | 417 |

## RL78/G1E ルネサスマイクロコンピュータ

R01UH0353JJ0200 Rev.2.00 2014.03.31

## 第1章 概 説

#### ★ 1.1 特 徴

RL78/G1E は、センサ微小信号処理用アナログ・フロントエンド回路として、コンフィギュラブル・アンプ、ゲイン調整アンプ、フィルタ回路、D/A コンバータ、温度センサ回路等を内蔵したアナログチップと 16 ビット・マイクロコントローラを 1 パッケージにした MCP(Multi Chip Package)です。RL78/G1Eの 16 ビット・マイクロコントローラ部は、RL78/G1A(64 ピン製品相当)を搭載しています。

#### 1.1.1 マイクロコントローラ部

スタンバイ機能を用いた低消費電力テクノロジー

- HALTモード

- STOP モード

- SNOOZEモード

#### RL78 CPUコア

- 3 段パイプラインの CISC アーキテクチャ

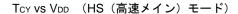

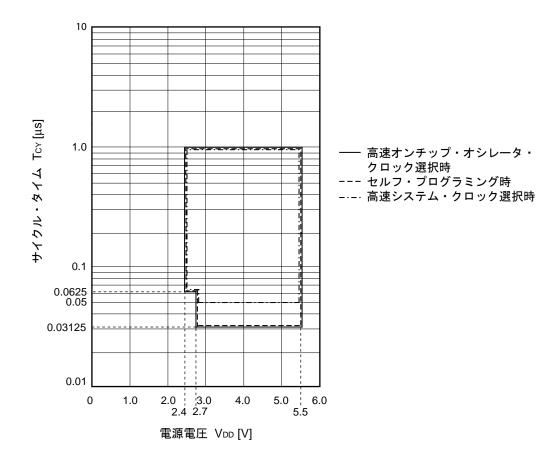

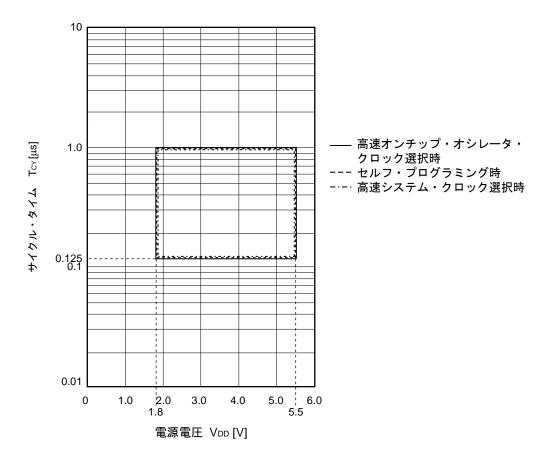

- 最小命令実行時間: 0.03125 μs (高速オンチップ・オシレータ・クロック 32 MHz 動作時) から

0.05 μs (高速システム・クロック 20 MHz 動作時) までを変更可能

- アドレス空間: 1M バイト

- 汎用レジスタ:8ビット・レジスタ×8×4バンク

- 内蔵 RAM: 2 KB~4 KB

### コード・フラッシュ・メモリ

- コード・フラッシュ・メモリ: 32 KB~64 KB

- ブロック・サイズ: 1 KB

- ブロック消去禁止、書き換え禁止(セキュリティ機能)

- オンチップ・デバッグ機能内蔵

- セルフ・プログラミング;ブート・スワップ機能とフラッシュ・シールド・ウィンドウ機能あり

## データ・フラッシュ・メモリ

- データ・フラッシュ・メモリ: 4 KB

- バックグランド・オペレーション(BGO); データ・フラッシュ書き換え中に、プログラム・メモリ内の命令実行が可能

- 書き換え回数: 1,000,000 回(TYP.)

- 書き換え電圧: VDD = 1.8~5.5 V

#### 高速オンチップ・オシレータ

- 32 MHz/24 MHz/16 MHz/12 MHz/8 MHz/6 MHz/4 MHz/3 MHz/2 MHz/1 MHz から選択

- 高精度±1.0 % (VDD = 1.8~5.5 V, TA = −20~+85 °C)

#### 動作周囲温度

• TA = -40~+85 °C (A:民生用途, D:産業用途)

#### 電源電圧範囲

- VDD (マイクロコントローラ部) = 1.6 V~5.5 V

- AVDD(マイクロコントローラ部 A/D コンバータ) = 1.6 V~3.6 V

- AVDDn(アナログ部) = 3.0 V~5.5 V

- DVDD (アナログ部 SPI) = 3.0 V~5.5 V

#### 電源管理とリセット機能

- パワーオン・リセット (POR) 回路内蔵

- 電圧検出(LVD)回路内蔵(割り込み,リセットを3段階で選択)

#### DMA (Direct Memory Access) コントローラ

- 2 チャネル搭載

- 8 ビット/16 ビットの SFR⇔内蔵 RAM 間の転送が 2 クロック

#### 乗除·積和演算器

- 16 ビット×16 ビット = 32 ビット (符号付/符号なし)

- 32 ビット÷32 ビット = 32 ビット (符号なし)

- 16 ビット×16 ビット+32 ビット = 32 ビット (符号付/符号なし)

#### シリアル・インタフェース

• CSI : 2 チャネル (64 ピン製品), 4 チャネル (80 ピン製品)

● UART/UART (LIN-bus 対応) : 2 チャネル/1 チャネル

● 簡易 I<sup>2</sup>C : 1 チャネル (64 ピン製品), 3 チャネル (80 ピン製品)

#### タイマ

16 ビット・タイマ : 8 チャネル

• 12 ビット・インターバル・タイマ : 1 チャネル

● ウォッチドッグ・タイマ : 1 チャネル(専用の低速オンチップ・オシレータ・ク

ロックで動作可能)

#### A/Dコンバータ

- 8/12 ビット分解能 A/D コンバータ

- アナログ入力: 13 チャネル(64 ピン製品), 17 チャネル(80 ピン製品)

- 内部基準電圧(1.45 V)と温度センサを搭載<sup>注</sup>

#### 注. HS(高速メイン)モードのみ選択可能

#### 備考 1. n = 1~3

2. 製品によって、搭載している機能が異なります。1.6 機能概要を参照してください。

#### 入出力ポート

- I/O ポート: 24 本(64 ピン製品), 30 本(80 ピン製品)

- N-ch オープン・ドレイン、TTL 入力バッファ、内蔵プルアップ抵抗の切り替え可能

- 異電位(1.8/2.5/3V系)動作デバイスと接続可能

- キー割り込み機能内蔵

- クロック出力/ブザー出力制御回路内蔵

#### その他

• 10 進補正 (BCD) 回路内蔵

#### ROM, RAM容量

| フラッシュ | データ・  | DAM  | RL78/G1E |          |  |

|-------|-------|------|----------|----------|--|

| ROM   | フラッシュ | RAM  | 64ピン製品   | 80ピン製品   |  |

| 32 KB | 4 KB  | 2 KB | R5F10FLC | R5F10FMC |  |

| 48 KB | 4 KB  | 3 KB | R5F10FLD | R5F10FMD |  |

| 64 KB | 4 KB  | 4 KB | R5F10FLE | R5F10FME |  |

備考 製品により、搭載している機能が異なります。「1.6 機能概要」を参照してください。

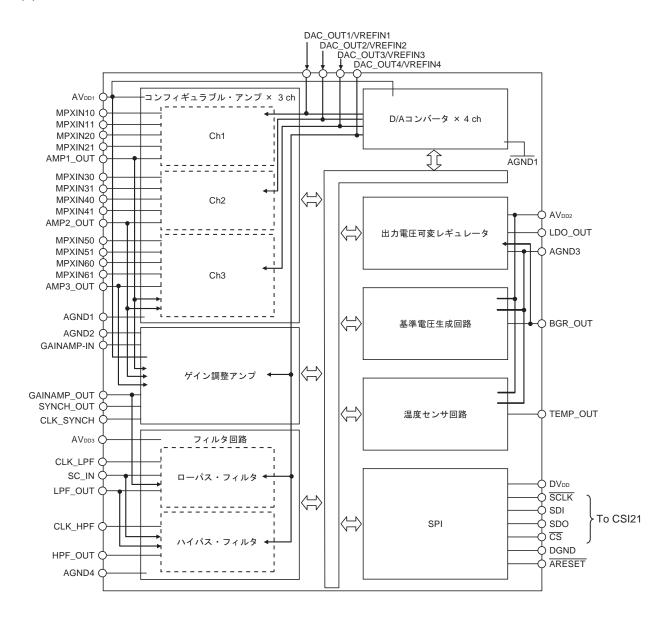

## 1.1.2 アナログ部

- コンフィギュラブル・アンプ: 3 チャネル

- ゲイン調整アンプ: 1 チャネル

- ハイパス・フィルタ: 1 チャネル<sup>注</sup>

- ローパス・フィルタ: 1 チャネル

- D/A コンバータ: 4 チャネル

- 出力電圧可変レギュレータ: 1 チャネル

- 基準電圧生成回路: 1 チャネル

- 温度センサ回路: 1 チャネル

- SPI (アナログ部):1 チャネル

#### 注. 80ピン製品のみ。

備考 製品により、搭載している機能が異なります。「1.6 機能概要」を参照してください。

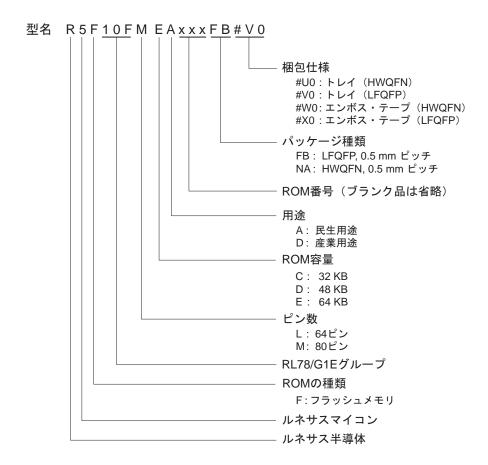

## 1.2 型名一覧

|   | ピン数   | パッケージ              | データ・  | 発注型名                            |

|---|-------|--------------------|-------|---------------------------------|

|   |       |                    | フラッシュ |                                 |

| 7 | 64 ピン | 64 ピン・プラスチック HWQFN | 搭載    | R5F10FLCANA#U0, R5F10FLCANA#W0, |

|   |       | (ファインピッチ) (9×9)    |       | R5F10FLDANA#U0, R5F10FLDANA#W0, |

|   |       |                    |       | R5F10FLEANA#U0, R5F10FLEANA#W0, |

|   |       |                    |       | R5F10FLCDNA#U0, R5F10FLCDNA#W0, |

|   |       |                    |       | R5F10FLDDNA#U0, R5F10FLDDNA#W0, |

|   |       |                    |       | R5F10FLEDNA#U0, R5F10FLEDNA#W0  |

|   | 80 ピン | 80 ピン・プラスチック LFQFP | 搭載    | R5F10FMCAFB#V0, R5F10FMCAFB#X0, |

|   |       | (12×12)            |       | R5F10FMDAFB#V0, R5F10FMDAFB#X0, |

|   |       |                    |       | R5F10FMEAFB#V0, R5F10FMEAFB#X0, |

|   |       |                    |       | R5F10FMCDFB#V0, R5F10FMCDFB#X0, |

|   |       |                    |       | R5F10FMDDFB#V0, R5F10FMDDFB#X0, |

|   |       |                    |       | R5F10FMEDFB#V0, R5F10FMEDFB#X0  |

注意 発注型名は、本マニュアル発行時のものです。

最新の発注型名は、当社ホームページの対象製品ページを必ず参照してください。

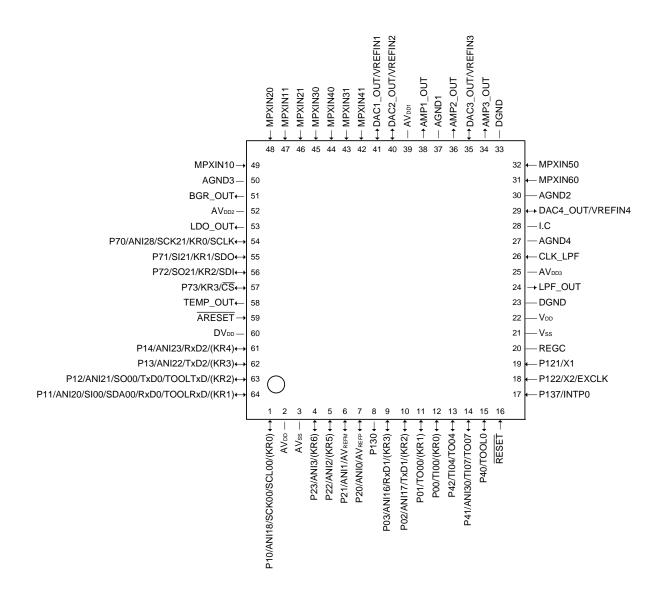

## ★ 1.3 端子接続図(Top View)

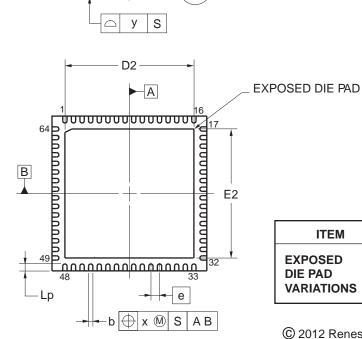

#### 1.3.1 64 ピン製品

64 ピン・プラスチック WQFN (ファインピッチ)  $(9 \times 9)$

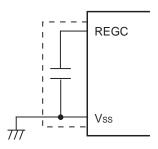

- 注意 1. REGC はコンデンサ (0.47~1μF) を介し、Vss に接続してください。

- 2. VDD, AVDD1, AVDD2, AVDD3, DVDD は同電位としてください。

- 3. Vss, AGND1, AGND2, AGND3, AGND4, DGND は同電位としてください。

- 4. I.C はオープンとしてください。

- 5. LDO\_OUT はコンデンサ(4.7μF: 推奨)を介し, AGND3 に接続してください。

- 6. BGR\_OUT はコンデンサ(0.1μF: 推奨)を介し、AGND3 に接続してください。

- 7. ローパス・フィルタまたはハイパス・フィルタを使用する場合、 DAC4\_OUT/VREFIN4 はコンデンサ(470 pF: 推奨)を介し、AGND1 に接続してください。

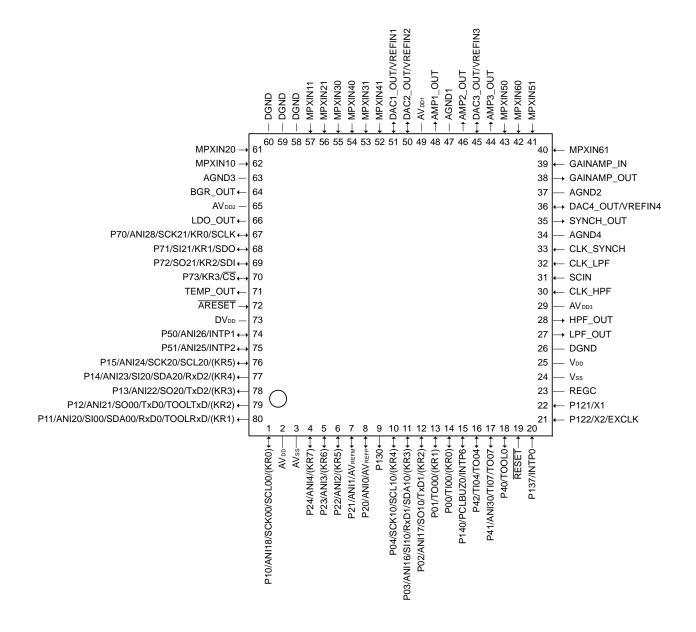

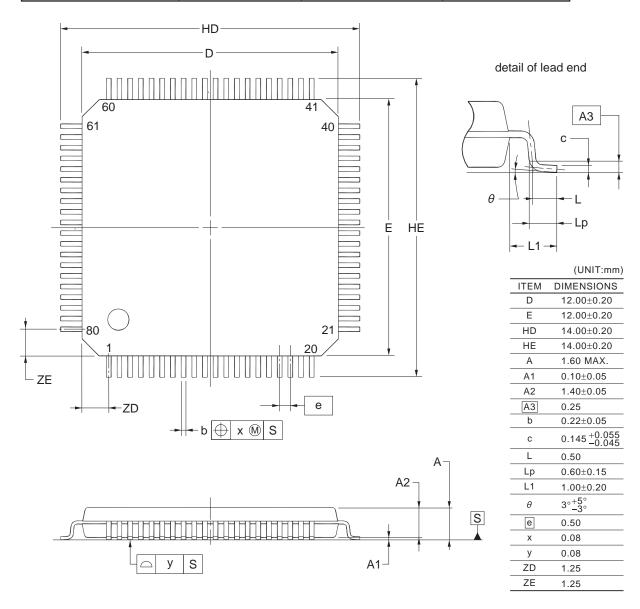

## ★ 1.3.2 80 ピン製品

80 ピン・プラスチック LQFP (ファインピッチ) (12×12)

- 注意 1. REGC はコンデンサ (0.47~1μF) を介し、Vss に接続してください。

- 2. VDD, AVDD1, AVDD2, AVDD3, DVDD は同電位としてください。

- 3. Vss, AGND1, AGND2, AGND3, AGND4, DGND は同電位としてください。

- 4. LDO\_OUT はコンデンサ(4.7μF: 推奨)を介し, AGND3 に接続してください。

- 5. BGR\_OUT はコンデンサ(0.1μF: 推奨)を介し、AGND3 に接続してください。

- 6. ローパス・フィルタまたはハイパス・フィルタを使用する場合、 DAC4\_OUT/VREFIN4 はコンデンサ(470 pF: 推奨)を介し、AGND1 に接続してください。

## ★ 1.4 端子名称

○マイクロコントローラ部

ANIO-ANI4, : Analog Input RxD0-RxD2 : Receive Data ANI16-ANI18, SCK00, SCK10, : Serial Clock Input/Output ANI20-ANI26. SCK20, SCK21 ANI28, ANI30 SCL00, SCL10, : Serial Clock Input/Output **AV**REFM : Analog Reference Voltage SCL<sub>20</sub> SDA00, SDA10, : Serial Data Input/Output Minus  $AV_{REFP}$ : Analog Reference Voltage SDA20 SI00, SI10, : Serial Data Input **EXCLK** SI20, SI21 : External Clock Input SO00, SO10 : Serial Data Output (Main System Clock) INTP0-INTP2 : External Interrupt Input SO20, SO21 TI00, TI04, INTP6 : Timer Input KR0-KR7 : Key Return **TI07** P00-P04 : Port 0 TO00, TO04, : Timer Output P10-P15 : Port 1 TO07 P20-P24 TOOL0 : Data Input/Output for Tool : Port 2 P40-P42 : Port 4 TOOLRxD, : Data Input/Output for External P50, P51 : Port 5 Device P70-P73 : Port 7 **TOOLTXD** P121, P122 : Port 12 TxD0-TxD2 : Transmit Data P130, P137 : Port 13  $V_{\text{DD}}$ : Power Supply P140 : Port 14 : Ground Vss PCLBUZ0 : Programmable Clock Output/ X1, X2 : Crystal Oscillator (Main System Clock) **Buzzer Output REGC** : Regulator Capacitance  $\mathsf{AV}_\mathsf{DD}$ : Analog Power Supply RESET : Reset **AVss** : Analog Ground

## 〇アナログ部

| $O_{I}$           | / pp                                       |                  |                                       |

|-------------------|--------------------------------------------|------------------|---------------------------------------|

| AV <sub>DD1</sub> | : Power supply for configurable            | AMP1_OUT,        | : Configurable amplifier output       |

|                   | amplifiers                                 | AMP2_OUT,        |                                       |

| AV <sub>DD2</sub> | : Power supply for variable output         | AMP3_OUT         |                                       |

|                   | voltage regulator and reference            | DAC1_OUT,        | : D/A converter output                |

|                   | voltage generator                          | DAC2_OUT,        |                                       |

| AV <sub>DD3</sub> | : Power supply for low-pass filter and     | DAC3_OUT,        |                                       |

|                   | high-pass filter                           | DAC4_OUT         |                                       |

| AGND1             | : Ground for configurable amplifiers       | VREFIN1,         |                                       |

| AGND2             | : Ground for gain adjustment amplifier     | VREFIN2,         |                                       |

| AGND3             | : Ground for variable output voltage       | VREFIN3          | : Reference voltage input for         |

|                   | regulator and reference voltage            |                  | configurable amplifier                |

|                   | generator                                  | VREFIN4          | : Reference voltage input for         |

| AGND4             | : Ground for low-pass filter and high-pass |                  | Gain adjustment amplifier,            |

|                   | filter                                     |                  | low-pass filter, and high-pass filter |

| MPXIN10,          | : Multiplexer input                        | SCLK             | : Serial clock input                  |

| MPXIN11,          |                                            | SDO              | : Serial data output                  |

| MPXIN20,          |                                            | SDI              | : Serial data input                   |

| MPXIN21,          |                                            | CS               | : Chip select input                   |

| MPXIN30,          |                                            | TEMP_OUT         | : Temperature sensor output           |

| MPXIN31,          |                                            | ARESET           | : Reset for analog block              |

| MPXIN40,          |                                            | DV <sub>DD</sub> | : Power supply for SPI                |

| MPXIN41,          |                                            | DGND             | : Ground for SPI                      |

| MPXIN50,          |                                            | HPF_OUT          | : High-pass filter output             |

| MPXIN51,          |                                            | CLK_HPF          | : Pin for inputting high-pass filter  |

| MPXIN60,          |                                            |                  | control clock                         |

| MPXIN61           |                                            | CLK_LPF          | : Pin for inputting low-pass filter   |

| SC_IN             | : Input for filter signal processing       |                  | control clock                         |

| CLK_SYNC          | CH : Synchronous detector control clock    | LPF_OUT          | : Low-pass filter output              |

|                   | input                                      | BGR_OUT          | : Reference voltage generator output  |

| SYNCH_OL          | JT : Synchronous detector output           | LDO_OUT          | : Variable output voltage regulator   |

| GAINAMP_          | IN : Gain adjustment amplifier input       | I.C              | : Internal connect                    |

|                   |                                            |                  |                                       |

GAINAMP\_OUT : Gain adjustment amplifier output

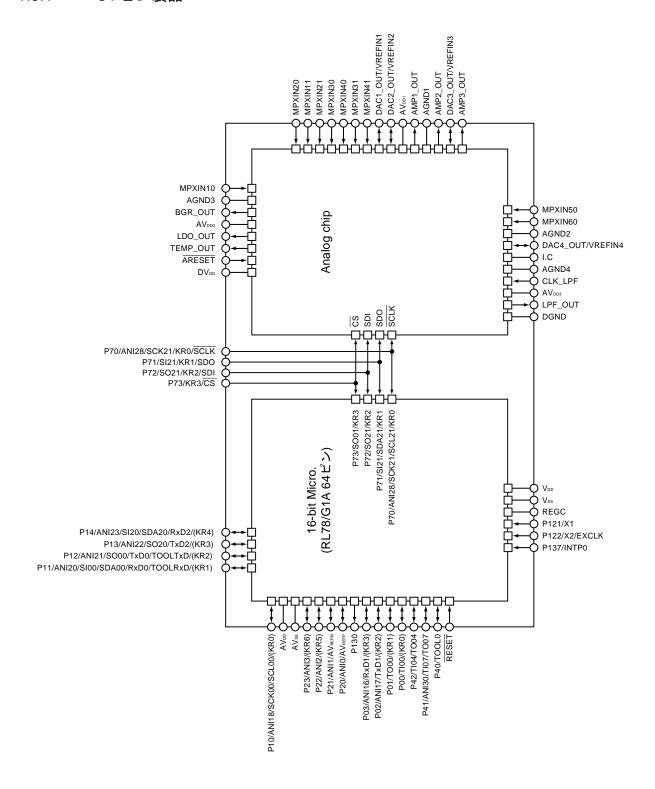

## ★ 1.5 ブロック図

## 1.5.1 64 ピン製品

備考. RL78/G1E (64 ピン製品) は、マイクロコントローラ部とアナログ部の 2 チップを 1 パッケージに搭載した MCP (Multi Chip Package) です。

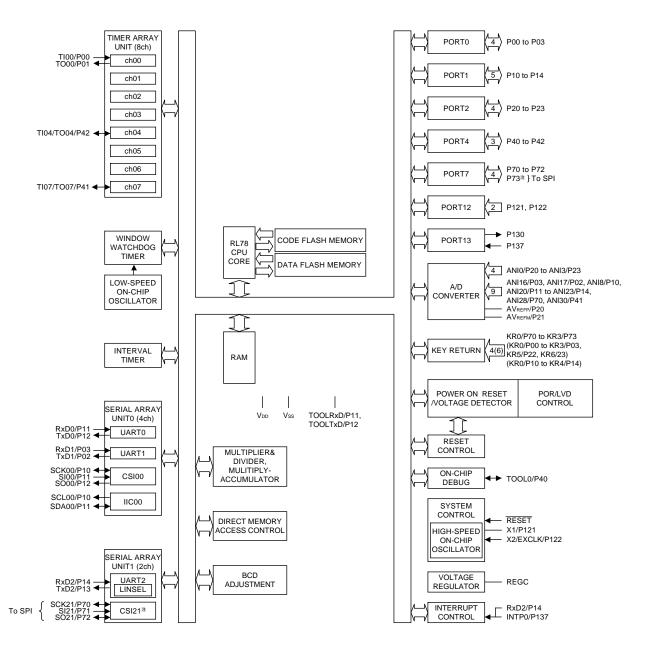

## ★ (1) マイクロコントローラ部ブロック図(64ピン製品)

注 パッケージ内部で接続しています。

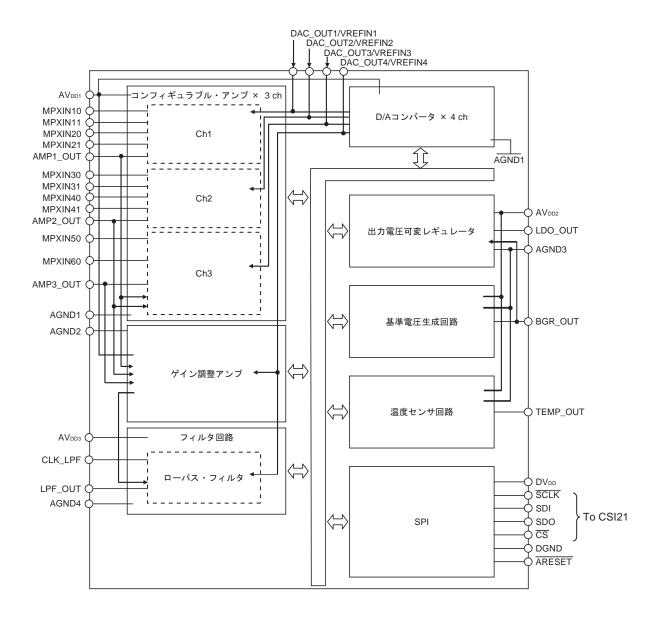

## (2) アナログ部ブロック図(64ピン製品)

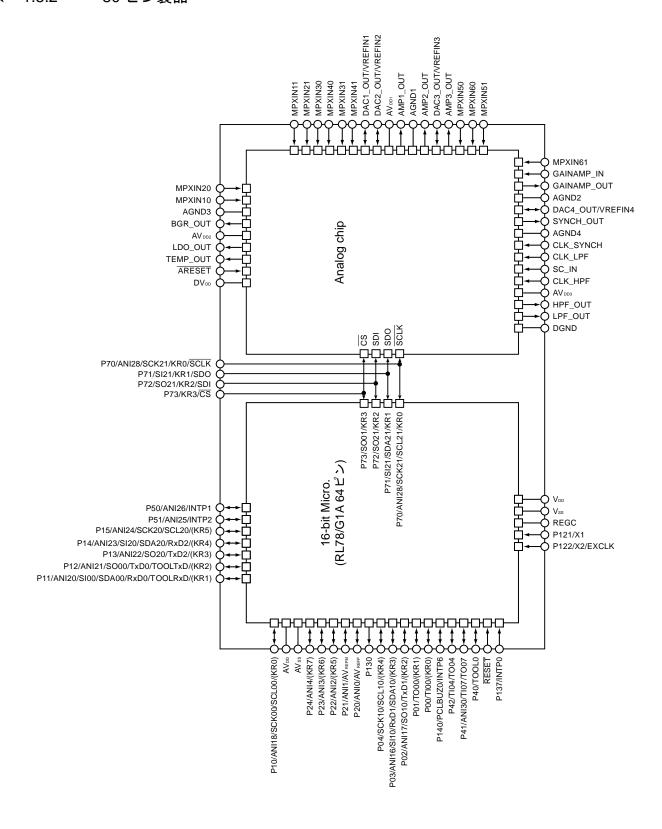

## ★ 1.5.2 80 ピン製品

備考. RL78/G1E (80 ピン製品)は、マイクロコントローラ部とアナログ部の2チップを1パッケージに搭載した MCP (Multi Chip Package)です。

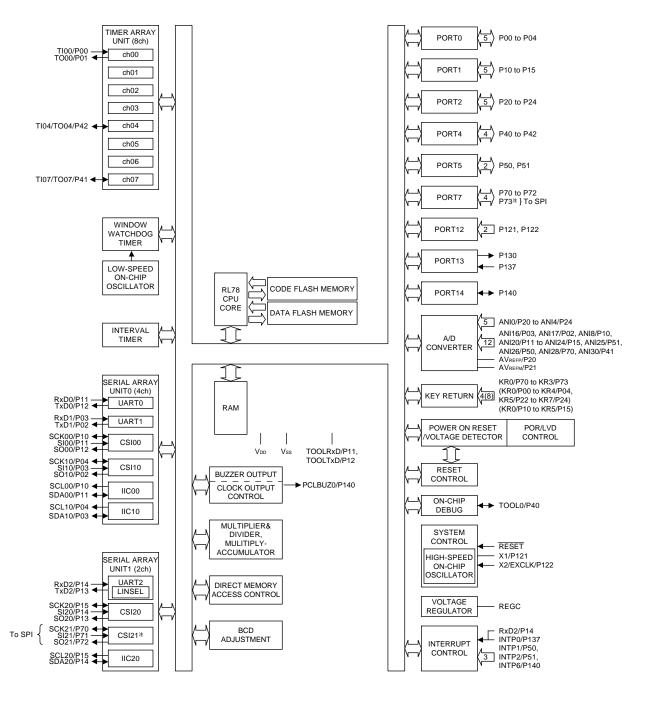

## ★ (1) マイクロコントローラ部ブロック図(80ピン製品)

RENESAS

注. パッケージ内部で接続しています。

## (2) アナログ部ブロック図(80ピン製品)

## ★ 1.6 機能概要

表 1-1 マイクロコントローラ部の機能概要 (1/2)

|               |               | ·                                            |                                  |  |

|---------------|---------------|----------------------------------------------|----------------------------------|--|

| 項目            |               | 64ピン製品                                       | 80ピン製品                           |  |

|               |               | R5F10FLx                                     | R5F10FMx                         |  |

| コード・フラッシュ・メモリ |               | 32 - 64KB                                    | 32 - 64KB                        |  |

| データ・フラ        | ッシュ・メモリ       | 4KB                                          | 4KB                              |  |

| RAM           |               | 2 - 4KB <sup>注1</sup>                        | 2 - 4KB <sup>注1</sup>            |  |

| メモリ空間         |               | 1M/*                                         | \{\rangle \}                     |  |

| メイン・シス        | テム 高速システム・    | X1 (水晶/セラミック) 発振, 外部メイン                      | ・・システム・クロック入力(EXCLK)             |  |

| ・クロック         | クロック          | 1~20 MHz : VDD = 2.7~5.5V, 1~8 MHz           | : VDD = 1.8~2.7V,                |  |

|               |               | 1~4 MHz : VDD = 1.6~1.8V                     |                                  |  |

|               | 高速オンチップ・      | HS(高速メイン)モード:1~32 MHz(V                      | /DD = 2.7~5.5V) ,                |  |

|               | オシレータ・クロック    | HS(高速メイン)モード: 1~16 MHz(V                     | $/DD = 2.4 \sim 5.5 \text{V})$ , |  |

|               |               | LS (低速メイン) モード: 1~8 MHz (VD                  | D = 1.8~5.5V) ,                  |  |

|               |               | LV(低電圧メイン)モード: 1~4 MHz(V                     | VDD = 1.6∼5.5V)                  |  |

| サブシステム        | ・クロック         | -                                            | <u>-</u>                         |  |

| 低速オンチッ        | プ・オシレータ・クロック  | 15kHz                                        | (TYP.)                           |  |

| 汎用レジスタ        |               | (8ビット・レジス                                    | (タ×8) ×4バンク                      |  |

| 最小命令実行        | ·時間           | 0.03125μs(高速オンチップ・オシレータ・クロック:fiн = 32MHz動作時) |                                  |  |

|               |               | 0.05μs(高速システム・クロック:fmx = 20MHz動作時)           |                                  |  |

| 命令セット         |               | ・データ転送(8 / 16ビット)                            |                                  |  |

|               |               | ・加減/論理演算(8 / 16ビット)                          |                                  |  |

|               |               | ・乗算(8ビット×8ビット)                               |                                  |  |

|               |               | ・ローテート、バレル・シフト、ビット操作                         |                                  |  |

|               | Т             | (セット,リセット,テスト,プール演算)など                       |                                  |  |

| I/Oポート        | 合計            | 24                                           | 30                               |  |

|               | CMOS入出力       | 20                                           | 26                               |  |

|               | CMOS入力        | 3                                            | 3                                |  |

|               | CMOS出力        | 1                                            | 1                                |  |

|               | N-chO.D入出力    |                                              |                                  |  |

|               | (6V耐圧)        | _                                            | _                                |  |

| タイマ           | 16ビット・タイマ     | 8チャネル                                        |                                  |  |

|               | ウォッチドッグ・タイマ   | 1チャネル                                        |                                  |  |

|               | リアルタイム・クロック   |                                              |                                  |  |

|               | (RTC)         | -                                            |                                  |  |

|               | 12ビット・インターバル・ | 4エレラロ                                        |                                  |  |

|               | タイマ(IT)       | 1チャネル                                        |                                  |  |

|               | タイマ出力         | 3本(PWM出力:2本 <sup>注2</sup> )                  |                                  |  |

|               | RTC出力         |                                              | <u> </u>                         |  |

|               |               |                                              |                                  |  |

- 注 1. 4 K バイトの場合、セルフ・プログラミング機能およびデータ・フラッシュ機能使用時は約 3 K バイトとなります (詳細は, 3.3 CPU アーキテクチャを参照)。

- 2. 使用チャネルの設定によって、PWM 出力数は変わります(詳細は、3.6 タイマ・アレイ・ユニットを参照)。

#### 表 1-1 マイクロコントローラ部の機能概要 (2/2)

| 項目               |                    | 64ピン製品 80ピン製品                                            |                                  |  |

|------------------|--------------------|----------------------------------------------------------|----------------------------------|--|

|                  |                    | R5F10FLx                                                 | R5F10FMx                         |  |

| クロック出力/ブザー出力     | ]                  |                                                          | 1本                               |  |

|                  |                    |                                                          | • 2.44 kHz, 4.88 kHz, 9.76 kHz,  |  |

|                  |                    | _                                                        | 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz |  |

|                  |                    |                                                          | (メイン・システム・クロック                   |  |

|                  |                    |                                                          | : fmain = 20 MHz動作時)             |  |

| 8/12ビット分解能A/Dコン  | バータ                | 13チャネル                                                   | 17チャネル                           |  |

| シリアル・インタフェース     | ζ.                 | ・64ピン製品                                                  |                                  |  |

|                  |                    | CSI:1チャネル/簡易I <sup>2</sup> C:1チャネル/                      | ´UART:1チャネル                      |  |

|                  |                    | UART: 1チャネル                                              |                                  |  |

|                  |                    | CSI:1チャネル/UART(LIN-bus対応):1チャネル                          |                                  |  |

|                  |                    | ・80ピン製品                                                  |                                  |  |

|                  |                    | CSI: 1チャネル/簡易I <sup>2</sup> C: 1チャネル/                    |                                  |  |

|                  |                    | CSI: 1チャネル/簡易I <sup>2</sup> C: 1チャネル/                    |                                  |  |

|                  |                    | CSI:2チャネル/簡易I <sup>2</sup> C:1チャネル/UART(LIN-bus対応):1チャネル |                                  |  |

|                  | I <sup>2</sup> Cバス | _                                                        |                                  |  |

| 乗除・積和演算器         |                    | 乗算 : 16ビット×16ビット(符号付/符号なし)                               |                                  |  |

|                  |                    | 除算 : 32ビット÷32ビット(符号なし)                                   |                                  |  |

|                  |                    | 積和演算:16ビット×16ビット+32ビット(符号付/符号なし)                         |                                  |  |

| DMAコントローラ        |                    | 2チャネル                                                    |                                  |  |

| ベクタ割り込み要因        | 内部                 | 2                                                        | 5                                |  |

|                  | 外部                 | 2                                                        | 5                                |  |

| キー割り込み           |                    | 4 ch (7) <sup>注1</sup>                                   | 4 ch (8) <sup>注1</sup>           |  |

| リセット             |                    | ・RESET端子によるリセット                                          |                                  |  |

|                  |                    | ・ウォッチドッグ・タイマによる内部リセット                                    |                                  |  |

|                  |                    | ・パワーオン・リセットによる内部リセット                                     |                                  |  |

|                  |                    | ・電圧検出回路による内部リセット                                         |                                  |  |

|                  |                    | ・不正命令の実行による内部リセット <sup>注2</sup>                          |                                  |  |

|                  |                    | ・RAMパリティ・エラーによる内部リセット                                    |                                  |  |

|                  |                    | ・不正メモリ・アクセスによる内部リセット                                     |                                  |  |

| パワーオン・リセット回路<br> |                    | ・パワーオン・リセット: 1.51±0.03V                                  |                                  |  |

|                  |                    | ・パワーダウン・リセット: 1.50±0.03V                                 |                                  |  |

| 電圧検出回路           |                    | 検出レベル: 3段階                                               |                                  |  |

| オンチップ・デバッグ機能     | <b>E</b>           | あり                                                       |                                  |  |

- 注 1. ( )内は周辺 I/O リダイレクション・レジスタ (PIOR) 機能を使用した場合の数です。

- 2. FFH の命令コードを実行したときに発生します。 不正命令の実行によるリセットは、インサーキット・エミュレータやオンチップ・デバッグ・エミュレータによるエミュレーションでは発生しません。

## 表 1-2 アナログ部の機能概要

| 式 1-2 / ) 1 / 印の版化域安 |                                                        |               |  |  |

|----------------------|--------------------------------------------------------|---------------|--|--|

| 項目                   | 64ピン製品                                                 | 80ピン製品        |  |  |

|                      | R5F10FLx                                               | R5F10FMx      |  |  |

| センサ・インタフェース・アンプ      | コンフィギュラフ                                               | ブル・アンプ 3ch    |  |  |

| ゲイン調整アンプ             | 1 ch                                                   | 1 ch(同期検波機能付) |  |  |

| ローパス・フィルタ            | 1                                                      | ch            |  |  |

| ハイパス・フィルタ            | _                                                      | 1 ch          |  |  |

| 8ビットD/Aコンバータ         | 4 ch                                                   |               |  |  |

| 出力電圧可変レギュレータ         | 1 ch                                                   |               |  |  |

| 基準電圧生成回路             | 1                                                      | ch            |  |  |

| 温度センサ回路              | 度センサ回路 1 ch                                            |               |  |  |

| 電源電圧                 | $VDD = 1.6 V \sim 5.5 V$ , $AVDD = 1.6 V \sim 3.6 V$ , |               |  |  |

|                      | $AVDDn = 3.0 V \sim 5.5 V$ , $DVDD = 3.0 V \sim 5.5 V$ |               |  |  |

| 動作周囲温度               | $TA = -40^{\circ}C \sim +85^{\circ}C$                  |               |  |  |

備考 n = 1~3

RL78/G1E 第 2 章 端子機能

## 第2章 端子機能

## 2.1 マイクロコントローラ部の端子機能

RL78/G1E の 16 ビット・マイクロコントローラ部は、RL78/G1A (64 ピン製品) を搭載しておりますが、 一部の端子機能は RL78/G1A (64 ピン製品) とは異なります。マイクロコントローラ部における、RL78/G1E (64 ピン製品、80 ピン製品) と RL78/G1A (64 ピン製品) の端子機能の差異は、次のとおりです。

## ★ (1) ポート機能の比較(64ピン製品)

(1/2)

| RL78/G1E(64 ピン製品) |                     | RL78/G1A(64 ピン製品) |                                     |

|-------------------|---------------------|-------------------|-------------------------------------|

| 機能名称              | 兼用機能                | 機能名称兼用機能          |                                     |

| P00               | 同右                  | P00               | TI00/(KR0)                          |

| P01               | 同右                  | P01               | TO00/(KR1)                          |

| P02               | ANI17/TxD1/(KR2)    | P02               | ANI17/SO10/TxD1/(KR2)               |

| P03               | P03/ANI6/RxD1/(KR3) | P03               | ANI16/SI10/SDA10/RxD1/(KR3)         |

|                   |                     | P04               | SCK10/SCL10/(KR4)                   |

|                   |                     | P05               | TI05/TO05/KR8                       |

|                   |                     | P06               | TI06/TO06/KR9                       |

| P10               | 同右                  | P10               | ANI18/SCK00/SCL00/(KR0)             |

| P11               | 同右                  | P11               | ANI20/SI00/RxD0/TOOLRxD/SDA00/(KR1) |

| P12               | 同右                  | P12               | ANI21/SO00/TxD0/TOOLTxD/(KR2)       |

| P13               | ANI22/TxD2/(KR3)    | P13               | ANI22/SO20/TxD2/(KR3)               |

| P14               | ANI23/RxD2/(KR4)    | P14               | ANI23/SI20/SDA20/RxD2/(KR4)         |

|                   |                     | P15               | ANI24/SCK20/SCL20/(KR5)             |

|                   |                     | P16               | TI01/TO01/INTP5                     |

| P20               | 同右                  | P20               | ANIO/AVREFP                         |

| P21               | 同右                  | P21               | ANI1/AVREFM                         |

| P22               | 同右                  | P22               | ANI2/(KR5)                          |

| P23               | 同右                  | P23               | ANI3/(KR6)                          |

|                   |                     | P24               | ANI4/(KR7)                          |

|                   |                     | P25               | ANI5/(KR8)                          |

|                   |                     | P26               | ANI6/(KR9)                          |

|                   |                     | P27               | ANI7                                |

|                   |                     | P30               | ANI27/SCK11/SCL11/INTP3/RTC1HZ      |

|                   |                     | P31               | ANI29/TI03/TO03/INTP4               |

| P40               | 同右                  | P40               | TOOL0                               |

| P41               | 同右                  | P41               | ANI30/TI07/TO07                     |

| P42               | 同右                  | P42               | TI04/TO04                           |

|                   |                     | P43               | _                                   |

|                   |                     | P50               | ANI26/SI11/SDA11/INTP1              |

|                   |                     | P51               | ANI25/SO11/INTP2                    |

|                   |                     | P60               | SCLA0                               |

|                   |                     | P61               | SDAA0                               |

|                   |                     | P62               | _                                   |

|                   |                     | P63               | _                                   |

★ 備考 上図の() 内の機能は、周辺 I/O リダイレクション・レジスタ (PIOR) の設定により、割り当て可能です。 詳細は、3.4.3.8 周辺 I/O リダイレクション・レジスタ (PIOR) にてフォーマットを参照してください。

(2/2)

|      |                                   |      | ` ,                   |  |  |

|------|-----------------------------------|------|-----------------------|--|--|

|      | RL78/G1E(64 ピン製品)                 |      | RL78/G1A(64 ピン製品)     |  |  |

| 機能名称 | 兼用機能                              | 機能名称 | 兼用機能                  |  |  |

| P70  | ANI28/SCK21/KR0/SCLK <sup>注</sup> | P70  | ANI28/SCK21/SCL21/KR0 |  |  |

| P71  | SI21/KR1/SDO <sup>注</sup>         | P71  | SI21/SDA21/KR1        |  |  |

| P72  | SO21/KR2/SDI <sup>注</sup>         | P72  | SO21/KR2              |  |  |

| P73  | KR3/CS <sup>注</sup>               | P73  | SO01/KR3              |  |  |

|      |                                   | P74  | SI01/SDA01/INTP8/KR4  |  |  |

|      |                                   | P75  | SCK01/SCL01/INTP9/KR5 |  |  |

|      |                                   | P76  | INTP10/KR6            |  |  |

|      |                                   | P77  | INTP11/KR7            |  |  |

|      |                                   | P120 | ANI19                 |  |  |

| P121 | 同右                                | P121 | X1                    |  |  |

| P122 | 同右                                | P122 | X2/EXCLK              |  |  |

|      |                                   | P123 | XT1                   |  |  |

|      |                                   | P124 | XT2/EXCLKS            |  |  |

| P130 | 同右                                | P130 | _                     |  |  |

| P137 | 同右                                | P137 | INTP0                 |  |  |

|      |                                   | P140 | PCLBUZ0/INTP6         |  |  |

|      |                                   | P141 | PCLBUZ1/INTP7         |  |  |

|      |                                   | P150 | ANI8                  |  |  |

|      |                                   | P151 | ANI9/(KR6)            |  |  |

|      |                                   | P152 | ANI10/(KR7)           |  |  |

|      |                                   | P153 | ANI11/(KR8)           |  |  |

|      |                                   | P154 | ANI12/(KR9)           |  |  |

- 注 SCLK, SDO, SDI, CS は、アナログ部の端子機能です。P70-73 は、アナログ部の端子機能を兼用しています。 パッケージ内部で、アナログ部の端子に接続しています。

- ★ 備考 上図の() 内の機能は、周辺 I/O リダイレクション・レジスタ (PIOR) の設定により、割り当て可能です。 詳細は、3.4.3.8 周辺 I/O リダイレクション・レジスタ (PIOR) にてフォーマットを参照してください。

# ★ (2) ポート機能の比較(80ピン製品)

(1/2)

| RL78/G1E(80 ピン製品) |             |      | RL78/G1A(64 ピン製品)                   |  |  |

|-------------------|-------------|------|-------------------------------------|--|--|

| 機能名称              | 兼用機能        | 機能名称 | 兼用機能                                |  |  |

| P00               | 同右          | P00  | TI00/(KR0)                          |  |  |

| P01               | 同右          | P01  | TO00/(KR1)                          |  |  |

| P02               | 同右          | P02  | ANI17/SO10/TxD1/(KR2)               |  |  |

| P03               | 同右          | P03  | ANI16/SI10/SDA10/RxD1/(KR3)         |  |  |

| P04               | 同右          | P04  | SCK10/SCL10/(KR4)                   |  |  |

|                   |             | P05  | TI05/TO05/KR8                       |  |  |

|                   |             | P06  | TI06/TO06/KR9                       |  |  |

| P10               | 同右          | P10  | ANI18/SCK00/SCL00/(KR0)             |  |  |

| P11               | 同右          | P11  | ANI20/SI00/RxD0/TOOLRxD/SDA00/(KR1) |  |  |

| P12               | 同右          | P12  | ANI21/SO00/TxD0/TOOLTxD/(KR2)       |  |  |

| P13               | 同右          | P13  | ANI22/SO20/TxD2/(KR3)               |  |  |

| P14               | 同右          | P14  | ANI23/SI20/SDA20/RxD2/(KR4)         |  |  |

| P15               | 同右          | P15  | ANI24/SCK20/SCL20/(KR5)             |  |  |

|                   |             | P16  | TI01/TO01/INTP5                     |  |  |

| P20               | 同右          | P20  | ANIO/AVREFP                         |  |  |

| P21               | 同右          | P21  | ANI1/AVREFM                         |  |  |

| P22               | 同右          | P22  | ANI2/(KR5)                          |  |  |

| P23               | 同右          | P23  | ANI3/(KR6)                          |  |  |

| P24               | 同右          | P24  | ANI4/(KR7)                          |  |  |

|                   |             | P25  | ANI5/(KR8)                          |  |  |

|                   |             | P26  | ANI6/(KR9)                          |  |  |

|                   |             | P27  | ANI7                                |  |  |

|                   |             | P30  | ANI27/SCK11/SCL11/INTP3/RTC1HZ      |  |  |

|                   |             | P31  | ANI29/TI03/TO03/INTP4               |  |  |

| P40               | 同右          | P40  | TOOL0                               |  |  |

| P41               | 同右          | P41  | ANI30/TI07/TO07                     |  |  |

| P42               | 同右          | P42  | TI04/TO04                           |  |  |

|                   |             | P43  | _                                   |  |  |

| P50               | ANI26/INTP1 | P50  | ANI26/SI11/SDA11/INTP1              |  |  |

| P51               | ANI25/INTP2 | P51  | ANI25/SO11/INTP2                    |  |  |

|                   |             | P60  | SCLA0                               |  |  |

|                   |             | P61  | SDAA0                               |  |  |

|                   |             | P62  | -                                   |  |  |

|                   |             | P63  | _                                   |  |  |

★ 備考 上図の() 内の機能は、周辺 I/O リダイレクション・レジスタ (PIOR) の設定により、割り当て可能です。 詳細は、3.4.3.8 周辺 I/O リダイレクション・レジスタ (PIOR) にてフォーマットを参照してください。

(2/2)

|      |                           |      | (=, =)                |  |  |

|------|---------------------------|------|-----------------------|--|--|

|      | RL78/G1E(80 ピン製品)         |      | RL78/G1A(64 ピン製品)     |  |  |

| 機能名称 | 兼用機能                      | 機能名称 | 兼用機能                  |  |  |

| P70  | ANI28/SCK21/KR0/SCLK 注    | P70  | ANI28/SCK21/SCL21/KR0 |  |  |

| P71  | SI21/KR1/SDO 注            | P71  | SI21/SDA21/KR1        |  |  |

| P72  | SO21/KR2/SDI <sup>注</sup> | P72  | SO21/KR2              |  |  |

| P73  | KR3/CS <sup>注</sup>       | P73  | SO01/KR3              |  |  |

|      |                           | P74  | SI01/SDA01/INTP8/KR4  |  |  |

|      |                           | P75  | SCK01/SCL01/INTP9/KR5 |  |  |

|      |                           | P76  | INTP10/KR6            |  |  |

|      |                           | P77  | INTP11/KR7            |  |  |

|      |                           | P120 | ANI19                 |  |  |

| P121 | 同右                        | P121 | X1                    |  |  |

| P122 | 同右                        | P122 | X2/EXCLK              |  |  |

|      |                           | P123 | XT1                   |  |  |

|      |                           | P124 | XT2/EXCLKS            |  |  |

| P130 | 同右                        | P130 | _                     |  |  |

| P137 | 同右                        | P137 | INTP0                 |  |  |

| P140 | 同右                        | P140 | PCLBUZ0/INTP6         |  |  |

|      |                           | P141 | PCLBUZ1/INTP7         |  |  |

|      |                           | P150 | ANI8                  |  |  |

|      |                           | P151 | ANI9/(KR6)            |  |  |

|      |                           | P152 | ANI10/(KR7)           |  |  |

|      |                           | P153 | ANI11/(KR8)           |  |  |

|      |                           | P154 | ANI12/(KR9)           |  |  |

- 注 SCLK, SDO, SDI, CS は、アナログ部の端子機能です。P70-73 は、アナログ部の端子機能を兼用しています。パッケージ内部で、アナログ部の端子に接続しています。

- ★ 備考 上図の() 内の機能は、周辺 I/O リダイレクション・レジスタ (PIOR) の設定により、割り当て可能です。 詳細は、3.4.3.8 周辺 I/O リダイレクション・レジスタ (PIOR) にてフォーマットを参照してください。

- (3) ポート以外の機能の比較(64ピン製品,80ピン製品共通)

ポート以外の機能の比較に関しては、2.1.2.1 製品別の搭載機能を参照してください。

# 2.1.1 ポート機能

端子の入出力バッファ電源と端子の関係を次に示します。

表 2-1 各端子の入出力バッファ電源

# (1) 64 ピン製品

| 電源               | 対応する端子            |

|------------------|-------------------|

| V <sub>DD</sub>  | ・P20-P23 以外のポート端子 |

|                  | · RESET, REGC     |

| AV <sub>DD</sub> | • P20-P23         |

# (2) 80 ピン製品

| 電源               | 対応する端子            |

|------------------|-------------------|

| V <sub>DD</sub>  | ・P20-P24 以外のポート端子 |

|                  | • RESET, REGC     |

| AV <sub>DD</sub> | • P20-P24         |

### ★ 2.1.1.1 64 ピン製品

端子タイプに関しては、2.4 端子ブロック図を参照してください。

(1/2)

| 機能  | 端子    | 入出力 | リセット時 | 兼用機能            | 機能                                   |

|-----|-------|-----|-------|-----------------|--------------------------------------|

| 名称  | タイプ   |     |       |                 |                                      |

| P00 | 8-1-1 | 入出力 | 入力ポート | TI00/(KR0)      | ポート0。4ビット入出力ポート。                     |

| P01 |       |     |       | TO00/(KR1)      | P00, P01, P03の入力はTTL入力バッファに設定可能。     |

| P02 | 7-3-2 |     | アナログ  | ANI17/TxD1      | P02-P03の出力は、N-chオープン・ドレイン出力(Vdd      |

|     |       |     | 入力ポート | /(KR2)          | 耐圧)に設定可能。                            |

| P03 | 8-3-2 |     |       | ANI16/RxD1      | P02, P03はアナログ入力に設定可能 <sup>注1</sup> 。 |

|     |       |     |       | /(KR3)          | 1ビット単位で入力/出力の指定可能。                   |

|     |       |     |       |                 | 入力ポートでは、ソフトウェアの設定により、内蔵プル            |

|     |       |     |       |                 | アップ抵抗を使用可能。                          |

| P10 | 8-3-2 | 入出力 | アナログ  | ANI18/SCK00     | ポート1。5ビット入出力ポート。                     |

|     |       |     | 入力ポート | /SCL00/(KR0)    | P10, P11, P14の入力はTTL入力バッファに設定可能。     |

| P11 |       |     |       | ANI20/SI00      | P10-P14の出力は、N-chオープン・ドレイン出力(Vdd      |

|     |       |     |       | /RxD0/TOOLRxD   | 耐圧)に設定可能。                            |

|     |       |     |       | /SDA00/(KR1)    | P10-P14はアナログ入力に設定可能 <sup>注1</sup> 。  |

| P12 | 7-3-2 |     |       | ANI21/SO00      | 1ビット単位で入力/出力の指定可能。                   |

|     |       |     |       | /TxD0/TOOLTxD   | 入力ポートでは、ソフトウェアの設定により、内蔵プル            |

|     |       |     |       | /(KR2)          | アップ抵抗を使用可能。                          |

| P13 |       |     |       | ANI22/TxD2      |                                      |

|     |       |     |       | /(KR3)          |                                      |

| P14 | 8-3-2 |     |       | ANI23/RxD2      |                                      |

|     |       |     |       | /(KR4)          |                                      |

| P20 | 4-3-1 | 入出力 | アナログ  | ANIO/AVREFP     | ポート2。4ビット入出力ポート。                     |

| P21 |       |     | 入力ポート | ANI1/AVREFM     | アナログ入力に設定可能 <sup>注2</sup> 。          |

| P22 |       |     |       | ANI2/(KR5)      | 1ビット単位で入力/出力の指定可能。                   |

| P23 |       |     |       | ANI3/(KR6)      |                                      |

| P40 | 7-1-1 | 入出力 | 入力ポート | TOOL0           | ポート4。3ビット入出力ポート。                     |

| P41 | 7-3-1 |     | アナログ  | ANI30/TI07/TO07 | P41はアナログ入力に設定可能 <sup>注1</sup> 。      |

|     |       |     | 入力ポート |                 | 1ビット単位で入力/出力の指定可能。                   |

| P42 | 7-1-1 |     | 入力ポート | TI04/TO04       | 入力ポートでは、ソフトウェアの設定により、内蔵プル            |

|     |       |     |       |                 | アップ抵抗を使用可能。                          |

- ★ 注1. 各端子をデジタル/アナログのいずれにするかは、ポート・モード・コントロール・レジスタ x (PMCx) で設定します (1 ビット単位で設定可能)。

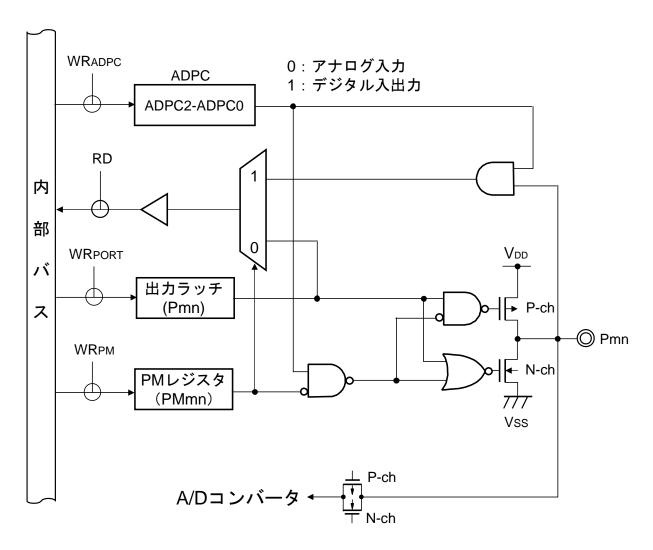

- 2. 各端子をデジタル/アナログのいずれにするかは、A/D ポート・コンフィギュレーション・レジスタ(ADPC)で設定します。

- ★ 備考 上図の() 内の機能は、周辺 I/O リダイレクション・レジスタ(PIOR)の設定により、割り当て可能です。 詳細は、3.4.3.8 周辺 I/O リダイレクション・レジスタ(PIOR)にてフォーマットを参照してください。

(2/2)

| * | 機能    | 端子    | 入出力 | リセット時 | 兼用機能                       | 機能                              |

|---|-------|-------|-----|-------|----------------------------|---------------------------------|

|   | 名称    | タイプ   |     |       |                            |                                 |

|   | P70   | 7-3-1 | 入出力 | アナログ  | ANI28/KR0                  | ポート7。4ビット入出力ポート。                |

|   |       |       |     | 入力ポート | /SCK21/SCLK <sup>注2</sup>  | P70はアナログ入力に設定可能 <sup>注1</sup> 。 |

|   | P71   | 7-1-2 |     | 入力ポート | KR1/SI21/SDO <sup>注2</sup> | 1ビット単位で入力/出力の指定可能。              |

|   | P72   | 7-1-1 |     |       | KR2/SO21/SDI <sup>注2</sup> | 入力ポートでは、ソフトウェアの設定により、内蔵プル       |

|   | P73   |       |     |       | KR3/CS <sup>注2</sup>       | アップ抵抗を使用可能。                     |

|   | P121  | 2-2-1 | 入力  | 入力ポート | X1                         | ポート12。2ビット入力ポート。                |

|   | P122  |       |     |       | X2/EXCLK                   |                                 |

|   | P130  | 1-1-1 | 出力  | 出力ポート | _                          | ポート13。1ビット出力専用ポートと1ビット入力専用ポ     |

|   | P137  | 2-1-2 | 入力  | 入力ポート | INTP0                      | ート。                             |

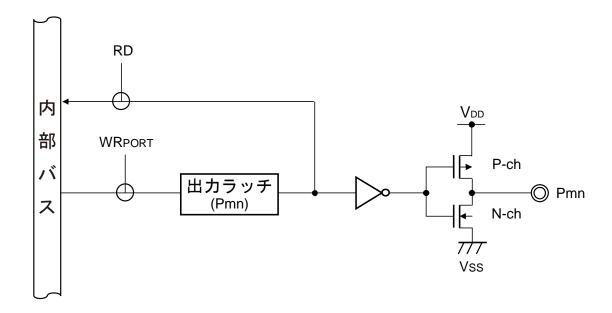

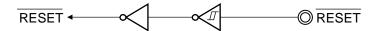

|   | RESET | 2-1-1 | 入力  | _     | _                          | 外部リセット用の入力専用端子。                 |

|   |       |       |     |       |                            | 外部リセットを使用しない場合は、直接または抵抗を        |

|   |       |       |     |       |                            | 介してV <sub>DD</sub> に接続してください。   |

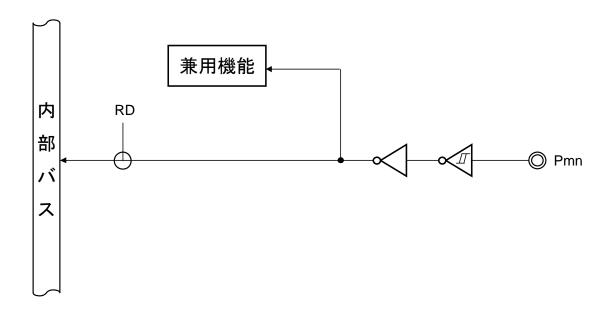

- 注1. 各端子をデジタル/アナログのいずれにするかは、ポート・モード・コントロール・レジスタ x (PMCx) で設定します(1 ビット単位で設定可能)。

- 2. SCLK, SDO, SDI, CS は、アナログ部の端子機能です。P70-73 は、アナログ部の端子機能を兼用していま す。パッケージ内部で、アナログ部の端子に接続しています。

### 2.1.1.2 80 ピン製品

端子タイプに関しては、2.4 端子ブロック図を参照してください。

(1/2)

| 機能<br>名称 | 端子<br>タイプ | 入出力 | リセット時 | 兼用機能                    | 機能                                    |

|----------|-----------|-----|-------|-------------------------|---------------------------------------|

| P00      | 8-1-1     | 入出力 | 入力ポート | TI00/(KR0)              | ポート0。5ビット入出力ポート。                      |

| P01      |           |     |       | TO00/(KR1)              | P00, P01, P03, P04の入力はTTL入力バッファに設定    |

| P02      | 7-3-2     |     | アナログ  | ANI17/SO10              | 可能。P02-P04の出力は、N-chオープン・ドレインは         |

|          |           |     | 入力ポート | /TxD1/(KR2)             | 力(Voo耐圧)に設定可能。                        |

| P03      | 8-3-2     |     |       | ANI16/SI10/RxD1         | P02, P03はアナログ入力に設定可能 <sup>注1</sup> 。  |

|          |           |     |       | /SDA10/(KR3)            | 1ビット単位で入力/出力の指定可能。                    |

| P04      | 8-1-2     |     | 入力ポート | SCK10/SCL10             | 入力ポートでは、ソフトウェアの設定により、内蔵               |

|          |           |     |       | /(KR4)                  | ルアップ抵抗を使用可能。                          |

| P10      | 8-3-2     | 入出力 | アナログ  | ANI18/SCK00             | ポート1。6ビット入出力ポート。                      |

|          |           |     | 入力ポート | /SCL00/(KR0)            | P10, P11, P14-P15の入力はTTL入力バッファに設定     |

| P11      |           |     |       | ANI20/SI00/RxD0         | 可能。P10-P15の出力は、N-chオープン・ドレイン          |

|          |           |     |       | /TOOLRxD                | 力(Voo耐圧)に設定可能。                        |

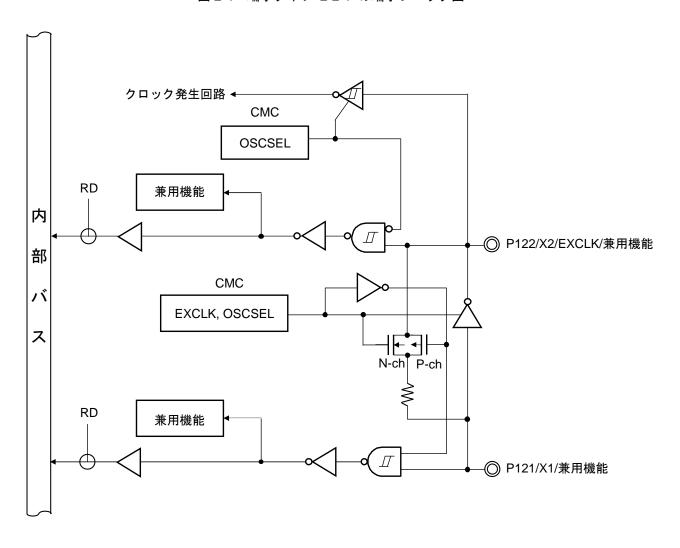

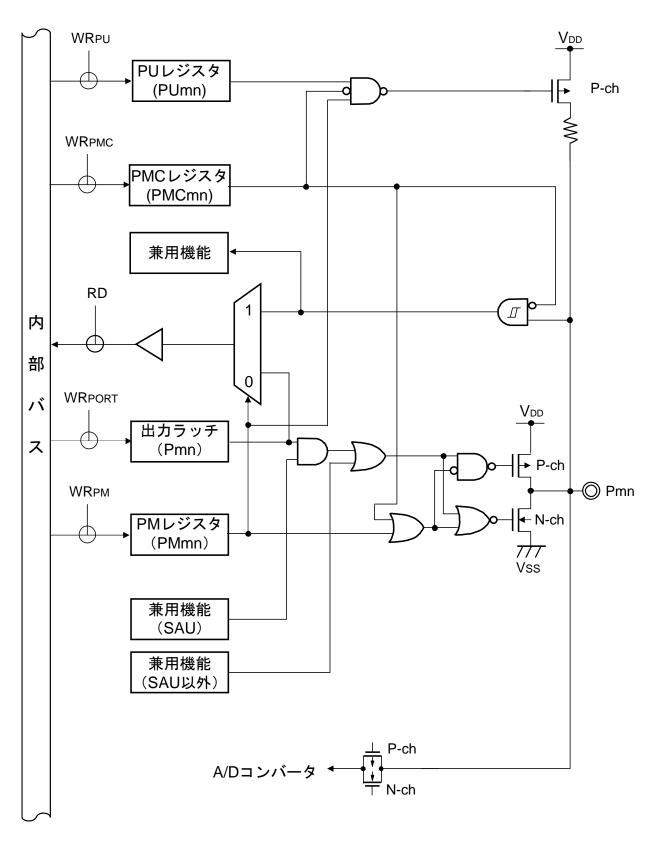

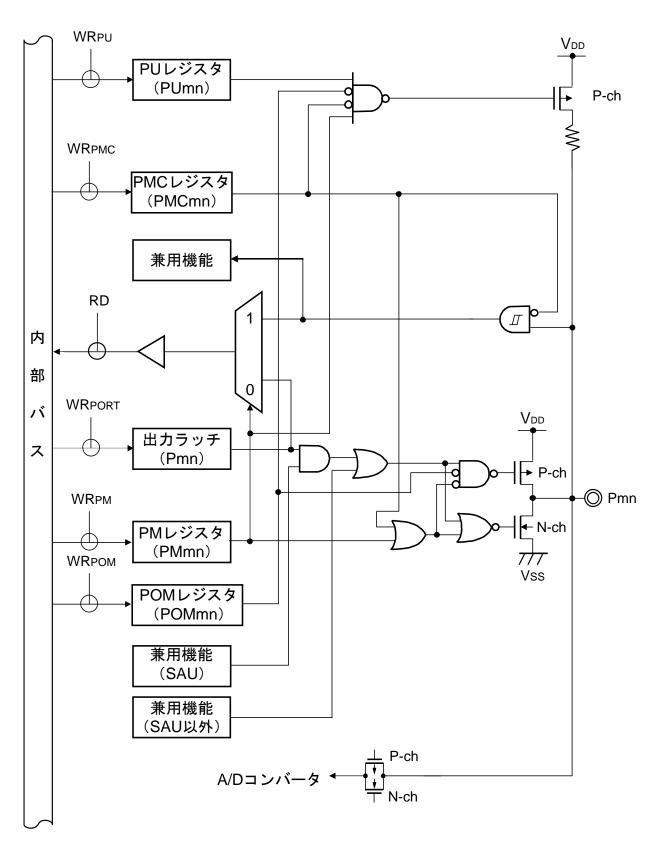

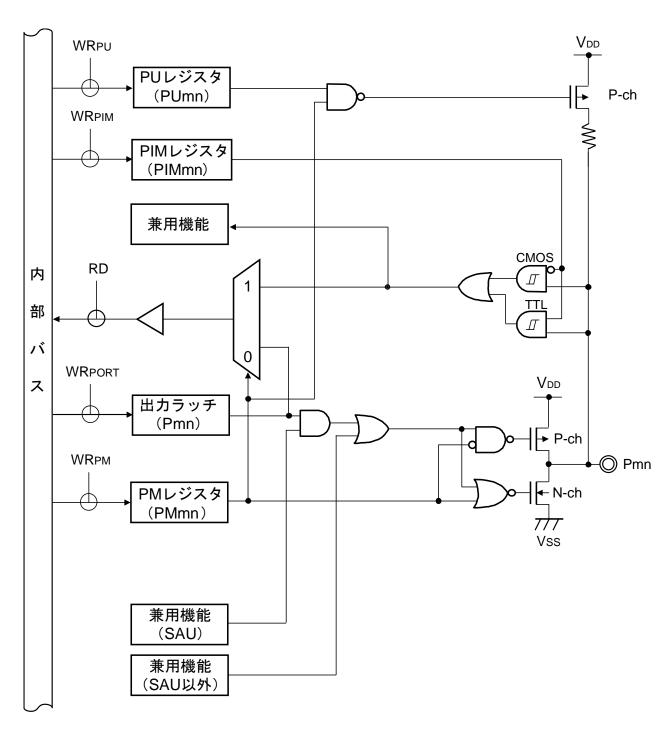

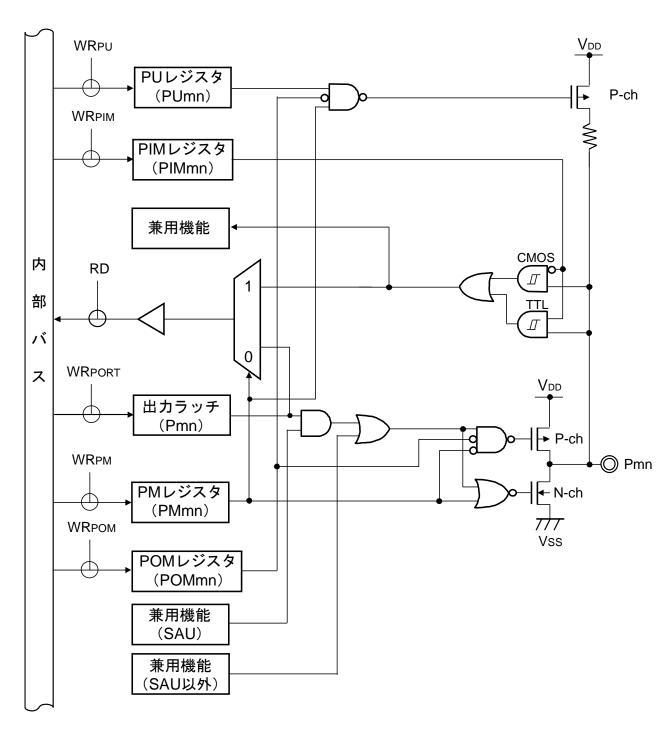

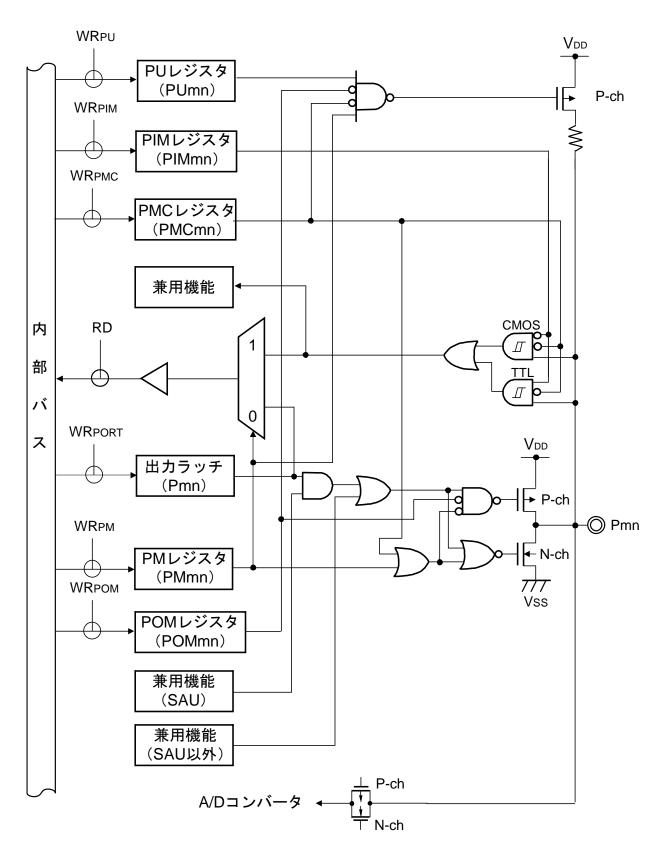

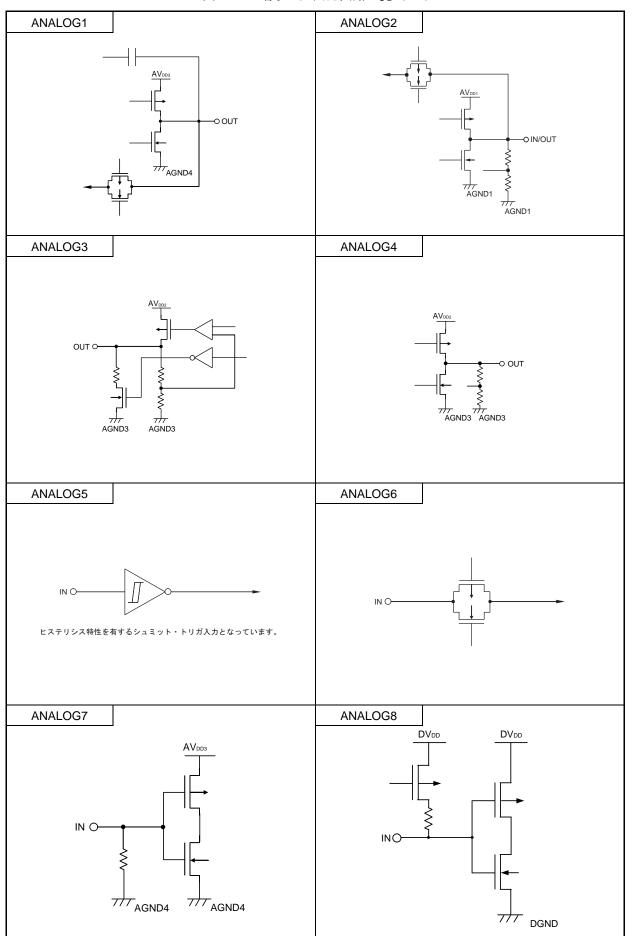

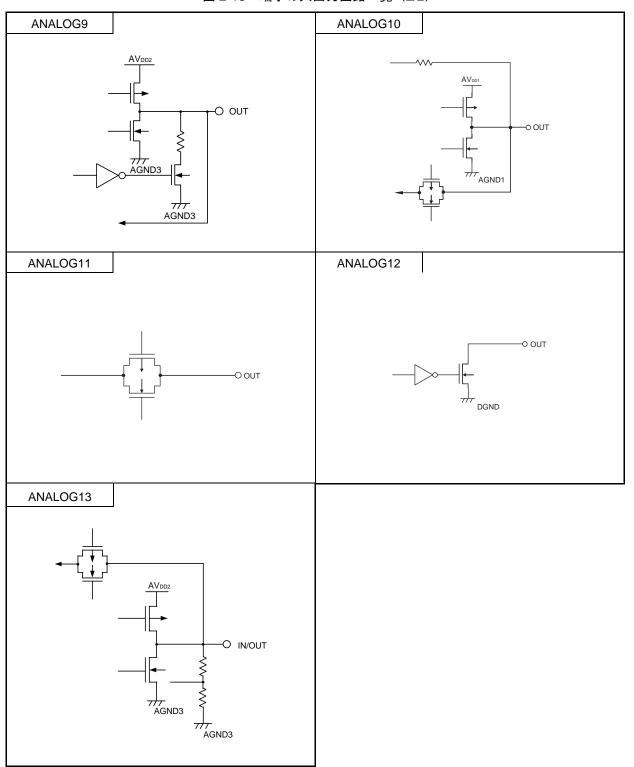

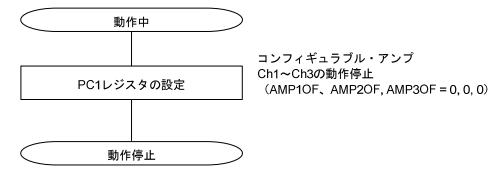

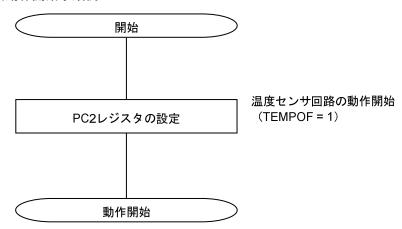

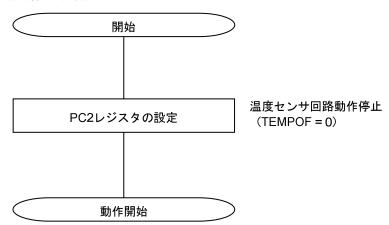

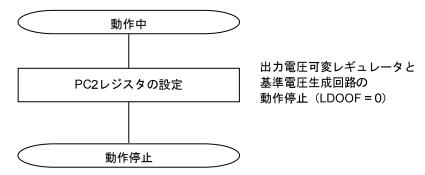

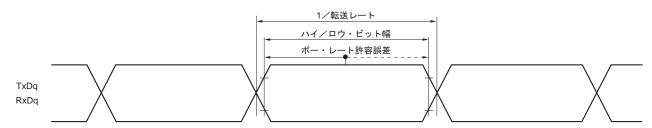

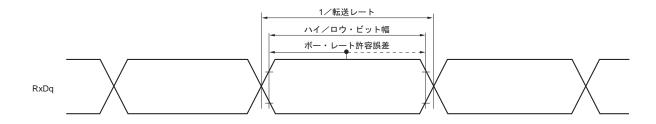

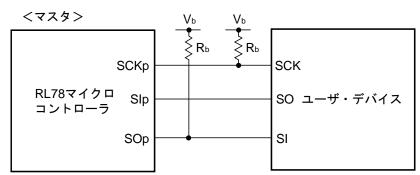

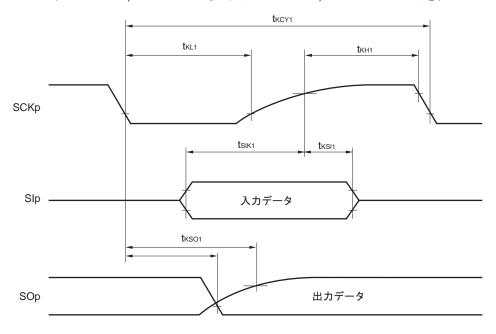

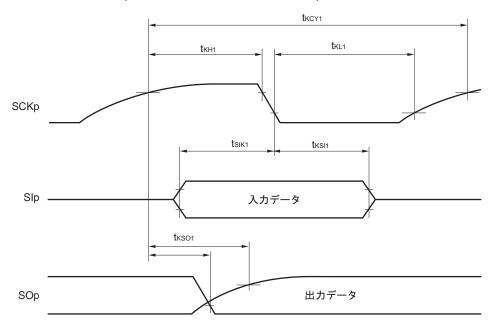

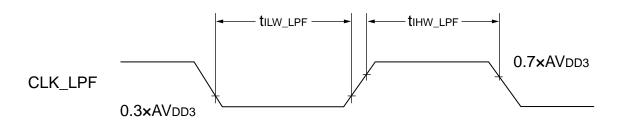

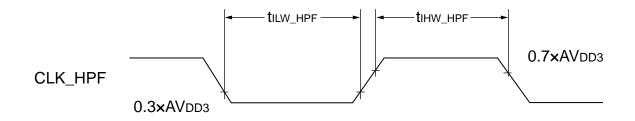

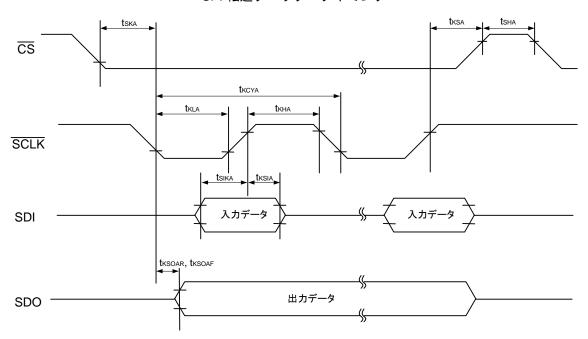

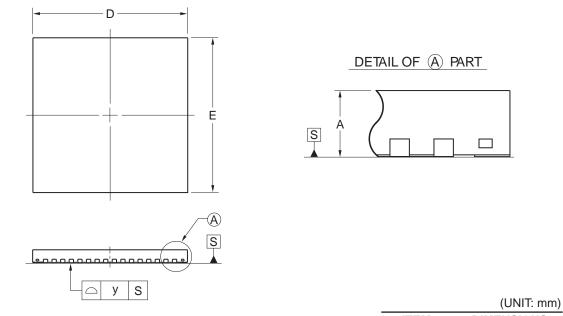

|          |           |     |       | /SDA00/(KR1)            | P10-P15は, アナログ入力に設定可能 <sup>注1</sup> 。 |