# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については 必ず本文の内容をご確認ください。

# HD404889シリーズ

ハードウェアマニュアル ルネサス4ビットシングルチップマイクロコンピュータ HMCS400ファミリ

#### ご注意

#### 安全設計に関するお願い

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサス テクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサス テクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサス テクノロジ半導体製品のご購入に当たりましては、事前にルネサス テクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサス テクノロジホームページ (http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する 損害がお客様に生じた場合には、ルネサス テクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技<mark>術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。</mark>

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサス テクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサス テクノロ ジ、ルネサス販売または特約店までご照会ください。

#### 製品に関する一般的注意事項

1. NC 端子の処理

【注意】NC端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC端子には、何も接続しないようにしてください。

2. 未使用入力端子の処理

【注意】未使用の入力端子は、ハイまたはローレベルに固定してください。

CMOS製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。未使用の入力端子は、入力をプルアップかプルダウンによって、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は,製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシステムが誤動作を起こさないようにシステム設計を行ってください。リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられています。

これらのレジスタをアクセスしたときの動作および継続する動作については、保証できませんので、アクセスしないようにしてください。

# はじめに

HD404889 シリーズは、強力でプログラム生産効率のよい HMCS400 CPU を核に持ち、液晶表示回路をはじめ、A/D コンバータ、多機能タイマなど各種周辺機能を内蔵した 4 ビットマイクロコンピュータです。CD ラジカセなどの AV 機器はもとより、電子ジャー他の家庭電化製品、電話、ページャなどの幅広い分野の表示パネル制御とシステムコントロールに最適です。

周辺機能は独立したモジュールとして開発され、標準化したインタフェースで各モジュールを結合するモジュールアーキテクチャ方式を採用しています。

HD404889 シリーズは、内蔵 ROM 版と PROM 版(ZTAT®版)が用意され、PROM 版は 汎用 PROM ライタを用いて、ユーザサイドで自由にプログラムの書き込みが行えます。 【注】 ZTAT®は、(株)ルネサス テクノロジの登録商標です。

マスク ROM 版および ZTAT®版は、記載しております電気的特性の基準値を十分満足することを確認しています。しかし、製造プロセスの違い、内部の配線パターン等の違いにより、特性上の実力値や動作マージン、ノイズマージン等は異なります。つきましては、いずれの製品におかれましても同等の実機システム評価試験を行い、動作のご確認をお願いいたします。

#### HD404889 シリーズ関連資料

下記の資料は、すべて現在使用できるものですが、在庫が少量のものもあります。 在庫については、(株)ルネサス テクノロジ カスタマサポートセンタ E-mail: csc@renesas.comへお問い合わせください。

| 形名            | データ        | シート   | プログラミングマニュアル |       |  |

|---------------|------------|-------|--------------|-------|--|

|               | 資料 No.     | 発行日   | 資料 No.       | 発行日   |  |

| HD404889 シリーズ | RJJ03B0050 | '03.9 | ADJ-602-037  | '90.3 |  |

#### 機能一覧

| 機能一頁      |                |                                        |

|-----------|----------------|----------------------------------------|

|           | 項目             | HD404889 シリーズ                          |

| ROM       | 容量(ワード)        | 8 / 12 / 16k                           |

| RAM       | 容量(ディジット)      | 1,344                                  |

| I/O       | 本数             | 46                                     |

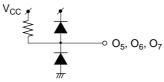

|           | 大電流端子          | ソース 4 本、シンク 8 本                        |

|           | LCD セグメント兼用端子  | 16                                     |

| 割り込み      | 優高             | $\overline{WU}_0 \sim \overline{WU}_3$ |

|           | 先              | ĪNT <sub>o</sub>                       |

|           | 順              | INT₁                                   |

|           | 位              | タイマ A                                  |

|           |                | タイマBまたはタイマD                            |

| (         |                | タイマC                                   |

|           | 低              | シリアルインタフェースまたは A/D                     |

| シリアル      | 本数             | 1                                      |

| インタフェース   | アイドル制御         | 有                                      |

|           | 開始命令           | STS 命令                                 |

| A/D コンバータ | チャネル数          | 6                                      |

| 液晶表示回路    | セグメント数         | 32                                     |

| ブザー出力回路   |                | 有                                      |

| システムクロック  | 発振子            | 外部、セラミック、水晶                            |

| 発振器       | 周波数(MHz)       | 0.4 ~ 1.0 / 1.6 ~ 4.5                  |

|           | 分周比            | 4 または 32                               |

| サブシステム    | 周波数            | 32kHz                                  |

| クロック発振器   | 分周比            | 4/8                                    |

|           | ストップモード時の停止    | 可                                      |

| 低消費電力     | スタンバイモード       | 有                                      |

| モード       | ストップモード        | 有                                      |

|           | サブアクティブモード     | 有                                      |

|           | ウォッチモード        | 有                                      |

| サブアクティブから | らアクティブモードへの    | 可                                      |

| 直接復帰      |                |                                        |

| サブアクティブから | らストップモードへの直接遷移 |                                        |

#### タイマ機能一覧

| 項目  |                 | HD404889 シリーズ |     |   |   |

|-----|-----------------|---------------|-----|---|---|

|     |                 | А             | В   | С | D |

| タイマ | クロックソースプリスケーラS  |               |     |   |   |

|     | クロックソースプリスケーラ W |               |     |   |   |

|     | 外部イベント入力        |               |     |   |   |

|     | (立ち下がり/立ち上がり    |               |     |   |   |

|     | / 両エッジ)         |               |     |   |   |

|     | フリーランニングタイマ     |               |     |   |   |

|     | タイムベース          |               |     |   |   |

|     | イベントカウンタ        |               |     |   |   |

|     | リロード            |               |     |   |   |

|     | ウォッチドッグ         |               |     |   |   |

|     | トグル出力           |               |     |   |   |

|     | PWM             |               |     |   |   |

|     | インプットキャプチャ      |               |     |   |   |

|     |                 | 94            | Cyr |   |   |

# 本版で修正または追加された箇所

# 目次

| 弗 [       | 早                 |                                       |    |

|-----------|-------------------|---------------------------------------|----|

| 1.1       | 概要                |                                       | 3  |

| 1.2       | 内部ブロック図           |                                       | 7  |

| 1.3       | 端子説明              |                                       | 8  |

|           | 1.3.1             | ピン <mark>配置</mark>                    | 8  |

|           | 1.3.2             | 端子機能                                  | 12 |

|           |                   |                                       |    |

| <u>**</u> | · 辛 · / 干 ! ¬ · · | _                                     |    |

| 弗 Z       | 2章 メモリマッ          |                                       |    |

| 2.1       |                   |                                       |    |

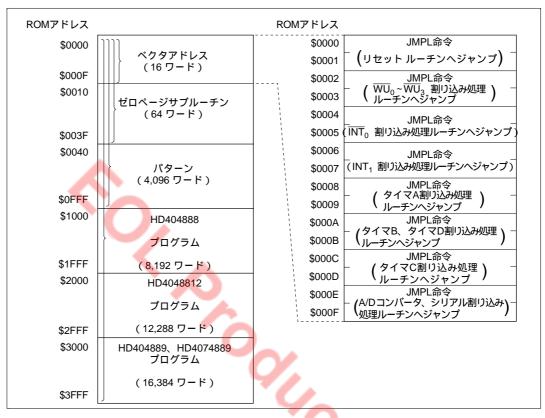

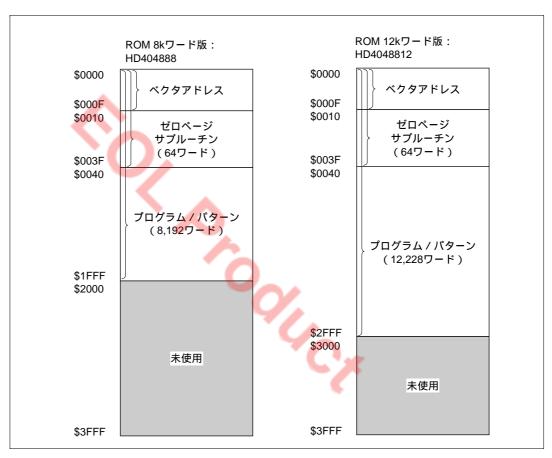

| 2.2       | ROM メモリマップ        |                                       | 19 |

|           | 2.2.1             | ベクタアドレスエリア                            | 19 |

|           | 2.2.2             | ゼロページサブルーチンエリア                        |    |

|           | 2.2.3             | パターンエリア                               | 19 |

|           | 2.2.4             | プログラムエリア                              | 20 |

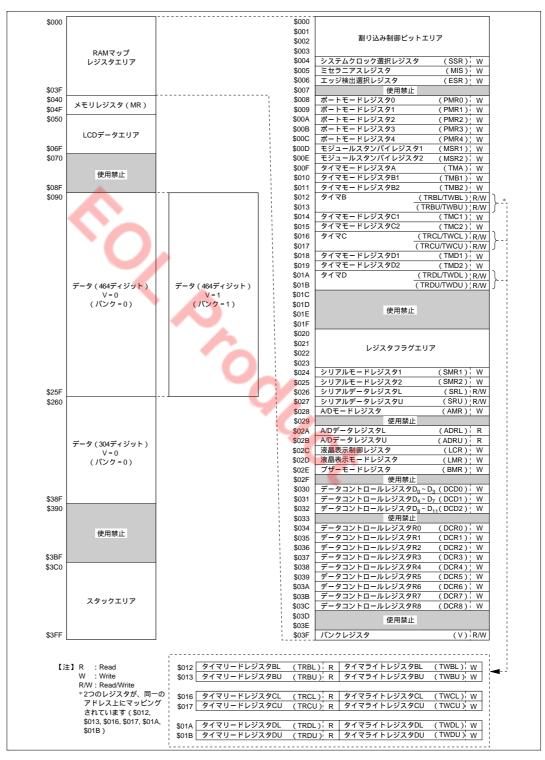

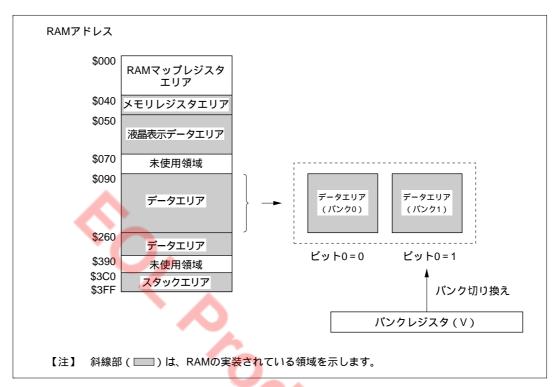

| 2.3       | RAM メモリマップ        |                                       | 21 |

|           | 2.3.1             | RAM マップレジスタエリア                        | 22 |

|           |                   | (1)割り込み制御ビットエリア(\$000~\$003)          | 22 |

|           |                   | (2)特殊レジスタエリア(\$004~\$01F、\$024~\$03F) | 23 |

|           |                   | (3) レジスタフラグエリア (\$020~\$023)          | 25 |

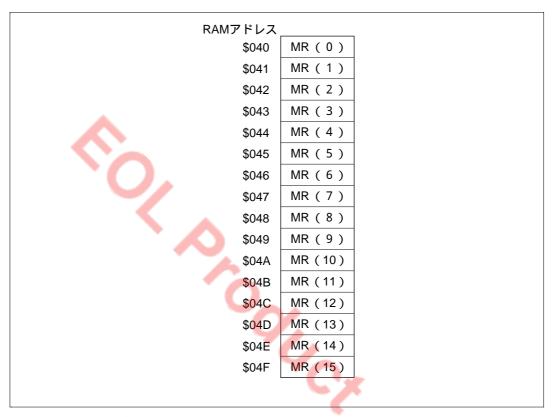

|           | 2.3.2             | メモリレジスタエリア                            | 27 |

|           | 2.3.3             | 液晶表示データエリア                            | 28 |

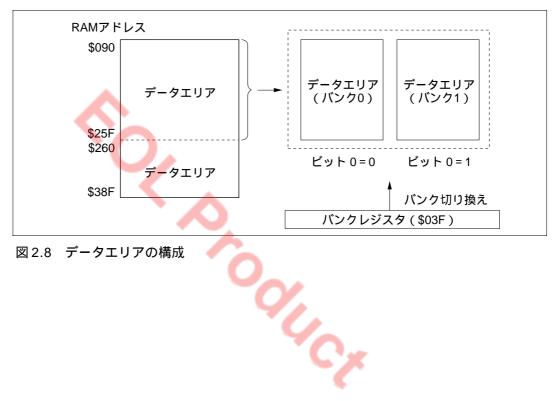

|           | 2.3.4             | データエリア                                | 29 |

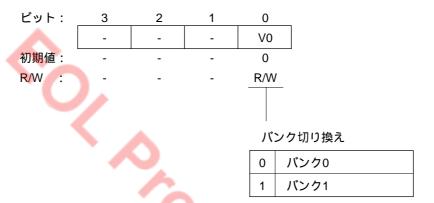

|           |                   | (1) バンクレジスタ (V: \$03F)                | 30 |

|           | 2.3.5             | スタックエリア                               | 31 |

## 第3章 CPU

| 3.1        | 概要        |                                          | 35 |

|------------|-----------|------------------------------------------|----|

|            | 3.1.1     | 特長                                       | 35 |

|            | 3.1.2     | アドレス空間                                   | 36 |

|            | 3.1.3     | レジスタ構成                                   | 36 |

| 3.2        | 各レジスタの説明  |                                          | 37 |

|            | 3.2.1     | アキュムレータ ( A ) 、B レジスタ ( B )              | 37 |

|            | 3.2.2     | W レジスタ ( W ) 、X レジスタ ( X ) 、Y レジスタ ( Y ) | 37 |

|            | 3.2.3     | SPX レジスタ (SPX)、SPY レジスタ (SPY)            | 37 |

|            | 3.2.4     | キャリフラグ ( CA )                            | 37 |

|            | 3.2.5     | ステータスフラグ (ST)                            | 37 |

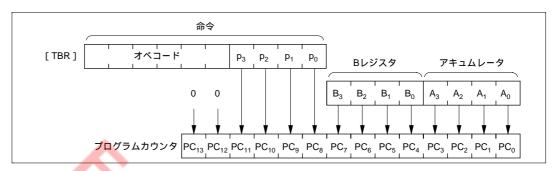

|            | 3.2.6     | プログラムカウンタ(PC)                            | 38 |

|            | 3.2.7     | スタックポインタ (SP)                            | 38 |

| 3.3        | アドレッシングモー | F                                        | 39 |

|            | 3.3.1     | RAM アドレッシングモード                           | 39 |

|            |           | (1)レジスタ間接アドレッシングモード                      | 39 |

|            |           | (2)直接アドレッシングモード                          | 39 |

|            |           | (3)メモリレジスタアドレッシングモード                     | 40 |

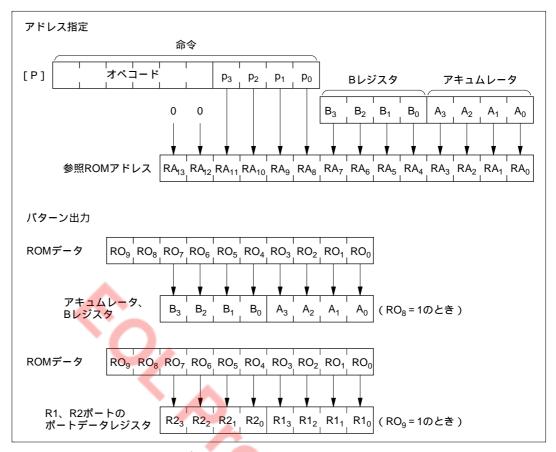

|            | 3.3.2     | ROM アドレッシングモードと P 命令                     | 40 |

|            |           | (1)ダイレクトアドレ <del>ッシングモー</del> ド          | 40 |

|            |           | (2)カレントページアドレ <mark>ッシン</mark> グモード      |    |

|            |           | (3)ゼロページアドレッシングモード                       | 41 |

|            |           | (4)テーブルデータアドレッシングモー <mark>ド</mark>       | 42 |

|            |           | (5)P命令                                   | 42 |

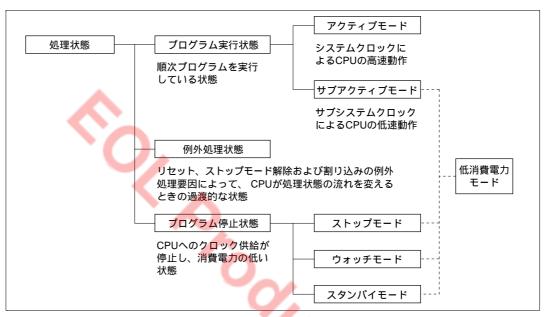

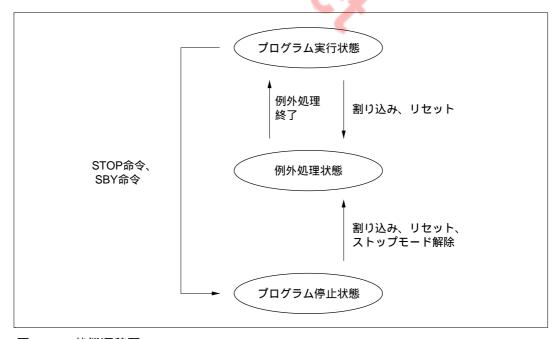

| 3.4        | 処理状態      |                                          | 44 |

|            | 3.4.1     | 概要                                       | 44 |

|            | 3.4.2     | プログラム実行状態                                |    |

|            |           | (1)アクティブモード                              |    |

|            |           | (2)サブアクティブモード                            | 45 |

|            | 3.4.3     | 例外処理状態                                   | 45 |

|            | 3.4.4     | プログラム停止状態                                | 46 |

|            |           | (1)ストップモード                               |    |

|            |           | (2) ウォッチモード                              | 46 |

|            |           | (3) スタンバイモード                             | 46 |

| 笠 4        | 章 例外処理    |                                          |    |

| <b>新</b> 4 | 早则外处理     |                                          |    |

| 4.1        | 概要        |                                          | 49 |

| 4.2 | リセット  |        |                                                                                                                          | 50 |

|-----|-------|--------|--------------------------------------------------------------------------------------------------------------------------|----|

|     |       | 4.2.1  | 概要                                                                                                                       | 50 |

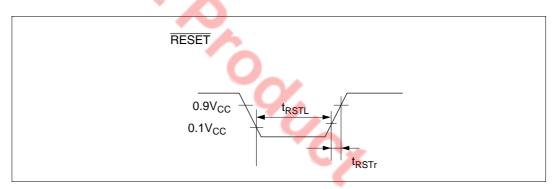

|     |       |        | (1) RESET 端子入力                                                                                                           | 50 |

|     |       |        | (2) ウォッチドッグタイマのオーバフロー                                                                                                    | 50 |

|     |       | 4.2.2  | リセットシーケンス                                                                                                                | 50 |

| 4.3 | ストップモ | 三一ド解除  |                                                                                                                          | 51 |

|     |       | 4.3.1  | 概要                                                                                                                       | 51 |

|     |       | 4.3.2  | ストップモード解除シーケンス(RESET 端子入力による)                                                                                            | 51 |

|     |       | 4.3.3  | ストップモード解除シーケンス                                                                                                           |    |

|     |       |        | ( $\overline{\mathrm{WU}}_{\scriptscriptstyle{0}}$ ~ $\overline{\mathrm{WU}}_{\scriptscriptstyle{3}}$ 端子への立ち下がりエッジ入力による) | 51 |

| 4.4 | リセットま | およびストッ | プモード解除時のレジスタ、フラグの初期値                                                                                                     | 52 |

| 4.5 | 割り込み  |        |                                                                                                                          | 55 |

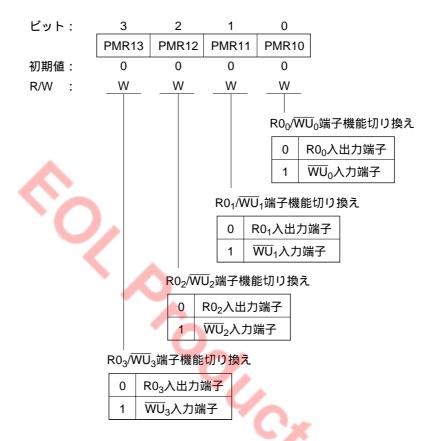

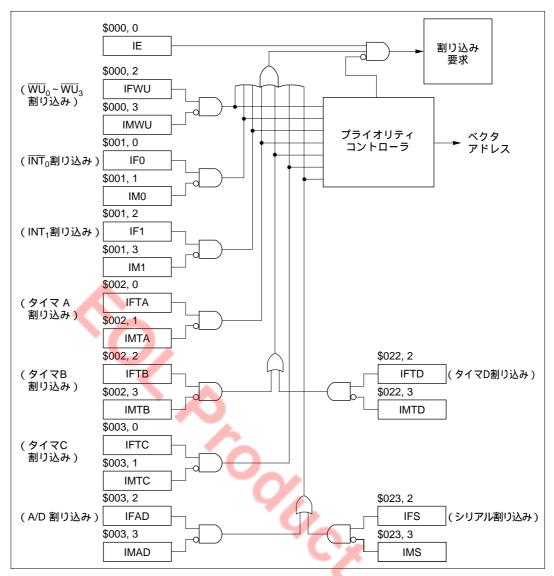

|     |       | 4.5.1  | 概要                                                                                                                       | 55 |

|     |       | 4.5.2  | 各レジスタ、フラグの説明                                                                                                             | 56 |

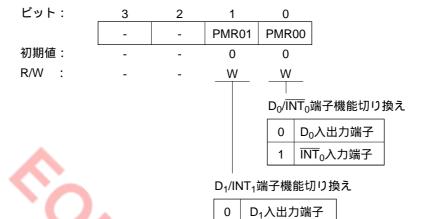

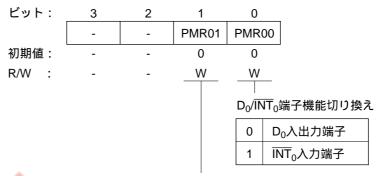

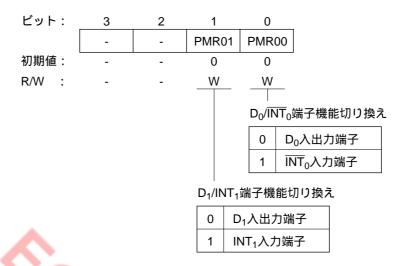

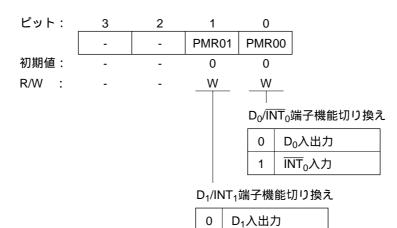

|     |       |        | (1)ポートモードレジスタ0(PMR0:\$008)                                                                                               | 57 |

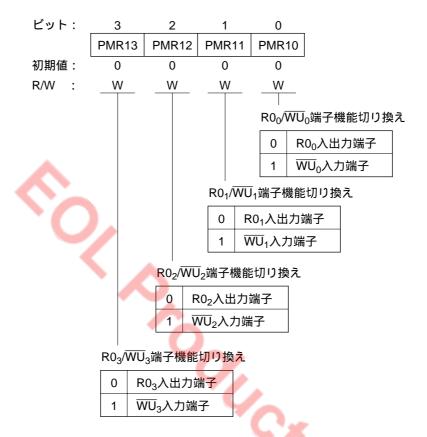

|     |       |        | (2)ポートモードレジスタ1(PMR1:\$009)                                                                                               | 58 |

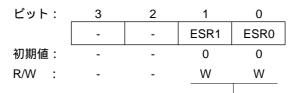

|     |       |        | (3)エッジ検出選択レジスタ(ESR: \$006)                                                                                               | 60 |

|     |       |        | (4)割り込み許可フラグ(IE:\$000,0)                                                                                                 | 60 |

|     |       |        | (5) ウェイクアップ割り込み要求フラグ(IFWU: \$000,2)                                                                                      | 61 |

|     |       |        | (6) ウェイクアップ割り込みマスク(IMWU:\$000,3)                                                                                         | 61 |

|     |       |        | (7)外部割り込み0、1要求フラグ(IF0:\$001,0、IF1:\$001,2)                                                                               | 62 |

|     |       |        | (8)外部割り込み0、1マスク(IMO:\$001,1、IM1:\$001,3)                                                                                 | 62 |

|     |       |        | (9)タイマ A~D割り込み要求フラグ                                                                                                      |    |

|     |       |        | (IFTA: \$002,0、IFTB: \$002,2、IFTC: \$003,0、IFTD: \$022,2)                                                                | 62 |

|     |       |        | (10)タイマ A ~ D 割り込みマスク                                                                                                    |    |

|     |       |        | (IMTA: \$002,1、IMTB: \$002,3、IMTC: \$003,0、IMTD: \$022,3)                                                                | 63 |

|     |       |        | (11)シリアル割り込み要求フラグ(IFS:\$023,2)                                                                                           | 63 |

|     |       |        | (12)シリアル割り込みマスク(IMS: \$023,3)                                                                                            | 64 |

|     |       |        | (13)A/D割り込み要求フラグ(IFAD:\$003,2)                                                                                           | 64 |

|     |       |        | (14) A/D 割り込みマスク (IMAD: \$003,3)                                                                                         | 64 |

|     |       | 4.5.3  | 外部割り込み                                                                                                                   | 65 |

|     |       | 4.5.4  | 内部割り込み                                                                                                                   | 65 |

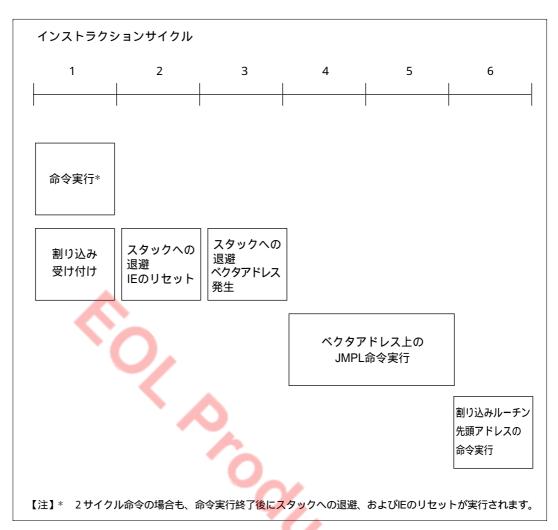

|     |       | 4.5.5  | 割り込み動作                                                                                                                   | 66 |

| 筆5  | 章 低消  | 書雷力∓   | = <b>_ K</b>                                                                                                             |    |

| •   |       |        |                                                                                                                          |    |

| 5.1 |       |        |                                                                                                                          |    |

|     |       | 5.1.1  | 特長                                                                                                                       | 73 |

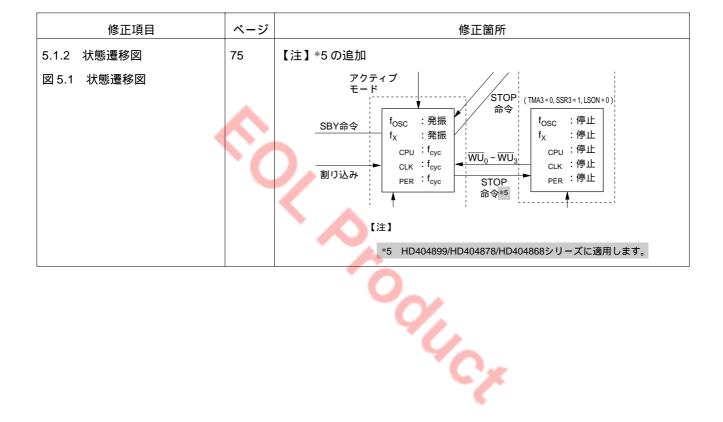

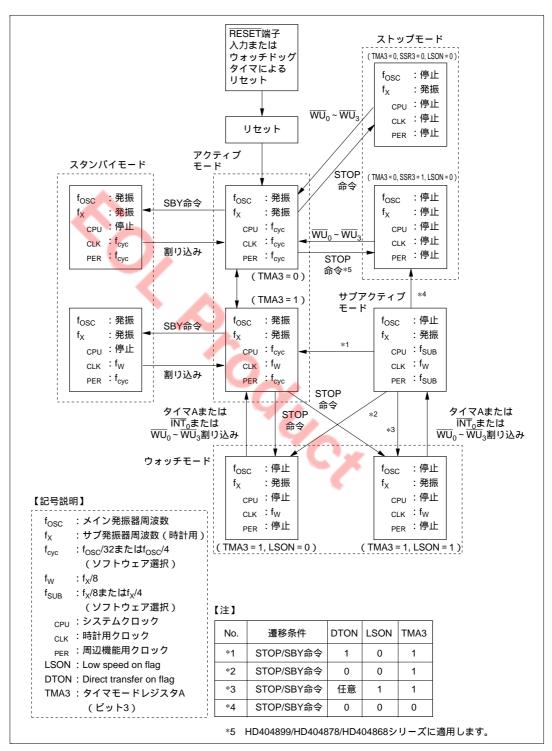

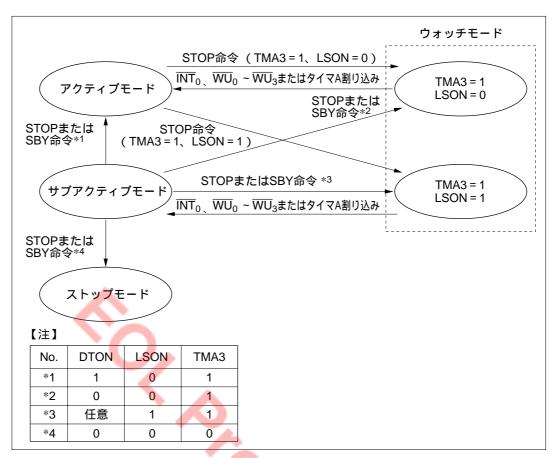

|     | 5.1.2     | 状態遷移図                                                                                                                                                                      | 75 |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 5.1.3     | 端子構成                                                                                                                                                                       | 76 |

|     | 5.1.4     | レジスタ、フラグ構成                                                                                                                                                                 | 76 |

| 5.2 | 各レジスタ、フラグ | 「の説明                                                                                                                                                                       | 77 |

|     | 5.2.1     | ミセラニアスレジスタ ( MIS: \$005 )                                                                                                                                                  | 77 |

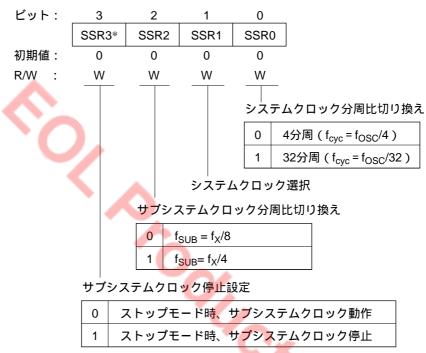

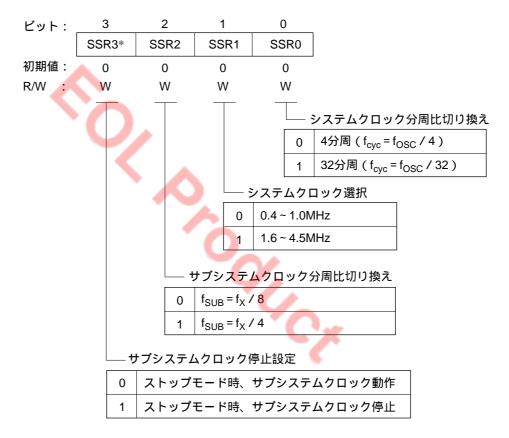

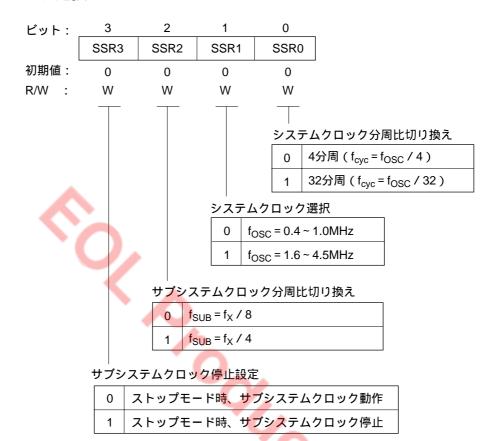

|     | 5.2.2     | システムクロック選択レジスタ(SSR:\$004)                                                                                                                                                  | 79 |

|     | 5.2.3     | タイマモードレジスタ A ( TMA : \$00F )                                                                                                                                               | 81 |

|     | 5.2.4     | ポートモードレジスタ 0 ( PMR0 : \$008 )                                                                                                                                              | 83 |

|     | 5.2.5     | ポートモードレジスタ1 ( PMR1 : \$009 )                                                                                                                                               | 84 |

|     | 5.2.6     | エッジ検出選択レジスタ (ESR: \$006)                                                                                                                                                   | 86 |

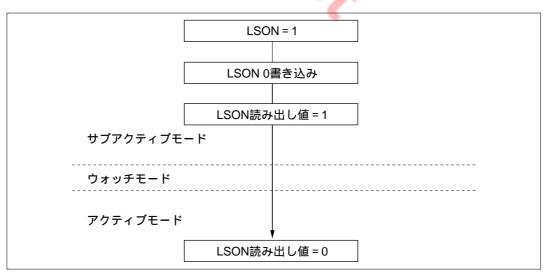

|     | 5.2.7     | ロースピードオンフラグ (LSON: \$020,0)                                                                                                                                                | 87 |

|     | 5.2.8     | DTON フラグ ( DTON: \$020,3 )                                                                                                                                                 | 89 |

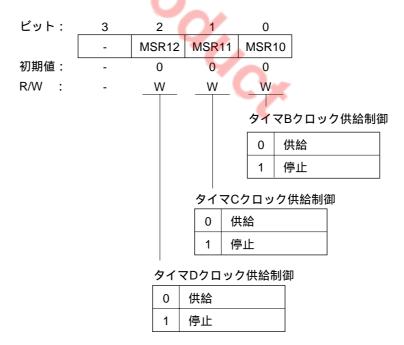

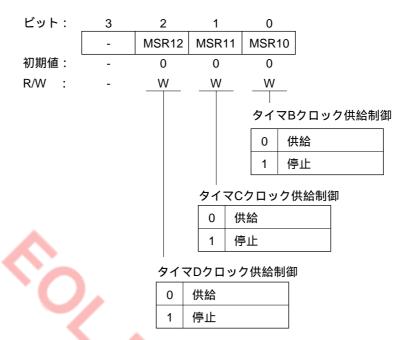

|     | 5.2.9     | モジュールスタンバイレジスタ1(MSR1:\$00D)                                                                                                                                                | 89 |

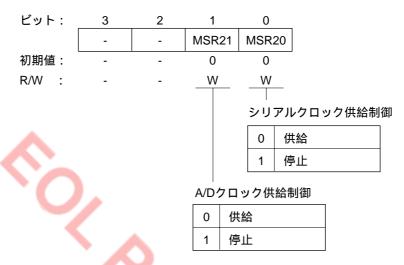

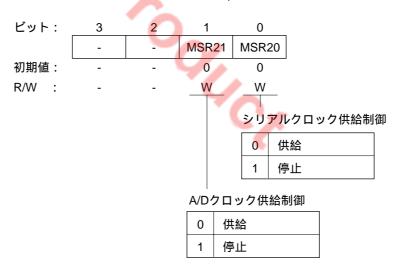

|     | 5.2.10    | モジュールスタンバイレジスタ 2 ( MSR2: \$00E )                                                                                                                                           | 90 |

| 5.3 | スタンバイモード  |                                                                                                                                                                            | 91 |

|     | 5.3.1     | スタンバイモードへの遷移方法                                                                                                                                                             | 91 |

|     | 5.3.2     | スタンバイモード <mark>の解除</mark> 方法                                                                                                                                               | 91 |

|     |           | (1) RESET 端子入力による解除                                                                                                                                                        | 91 |

|     |           | (2)割り込みによる <mark>解除</mark>                                                                                                                                                 | 91 |

| 5.4 | ストップモード   |                                                                                                                                                                            | 93 |

|     | 5.4.1     | ストップモードへの遷移方法                                                                                                                                                              |    |

|     | 5.4.2     | ストップモードの解除方法                                                                                                                                                               | 93 |

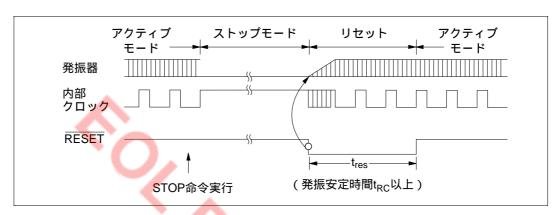

|     |           | (1)RESET 端子入力による解除                                                                                                                                                         | 93 |

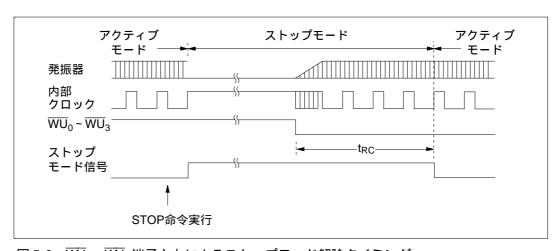

|     |           | (2) $\overline{\mathrm{WU}}_{\scriptscriptstyle{0}}$ ~ $\overline{\mathrm{WU}}_{\scriptscriptstyle{3}}$ 端子入力による解除                                                          | 93 |

|     | 5.4.3     | ストップモード解除後の発振安定時間                                                                                                                                                          | 94 |

|     |           | (1) RESET 端子入力による解除                                                                                                                                                        | 94 |

|     |           | (2) $\overline{\mathrm{WU}}_{\scriptscriptstyle{0}}$ ~ $\overline{\mathrm{WU}}_{\scriptscriptstyle{3}}$ 端子入力による解除                                                          | 94 |

| 5.5 | ウォッチモード   |                                                                                                                                                                            | 95 |

|     | 5.5.1     | ウォッチモードへの遷移方法                                                                                                                                                              | 95 |

|     | 5.5.2     | ウォッチモードの解除方法                                                                                                                                                               | 95 |

|     |           | (1) RESET 端子入力による解除                                                                                                                                                        | 95 |

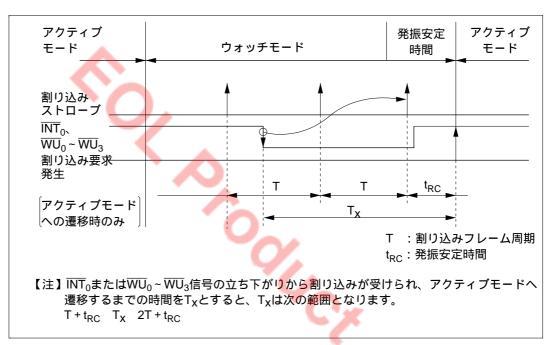

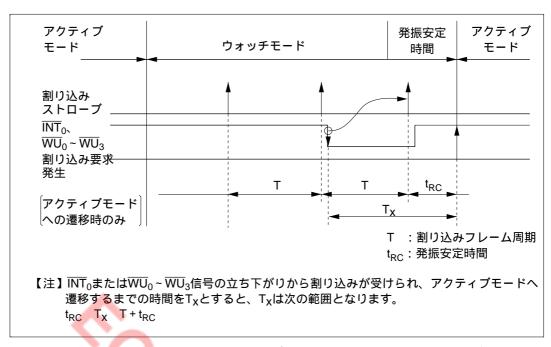

|     |           | $(2)$ $\overline{	ext{INT}}_{\scriptscriptstyle 0}$ 、 $\overline{	ext{WU}}_{\scriptscriptstyle 0}$ ~ $\overline{	ext{WU}}_{\scriptscriptstyle 3}$ 、またはタイマ $A$ 割り込みによる解除 $$ | 95 |

|     | 5.5.3     | ウォッチモード解除後の動作タイミング                                                                                                                                                         | 96 |

| 5.6 | サブアクティブモー | · ۴                                                                                                                                                                        | 98 |

|     | 5.6.1     | サブアクティブモードへの遷移方法                                                                                                                                                           | 98 |

|     | 5.6.2     | サブアクティブモードの解除方法                                                                                                                                                            | 98 |

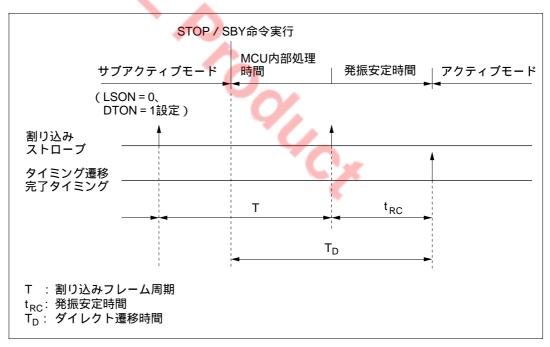

|     | 5.6.3     | ダイレクト遷移時(サブアクティブモードからアクティブモード)の                                                                                                                                            |    |

|     |           | 動作タイミング                                                                                                                                                                    | 99 |

| 5.7  | モジュールスタンバイ機能1 |                                            |     |  |  |  |

|------|---------------|--------------------------------------------|-----|--|--|--|

|      | 5.7.1         | モジュールスタンバイ機能                               | 100 |  |  |  |

|      | 5.7.2         | 使用上の注意                                     | 100 |  |  |  |

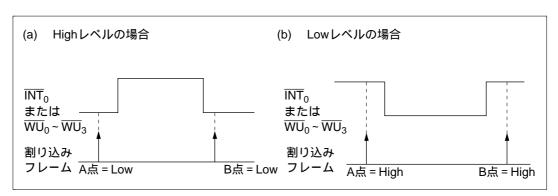

| 5.8  | 割り込みフレーム。     |                                            | 101 |  |  |  |

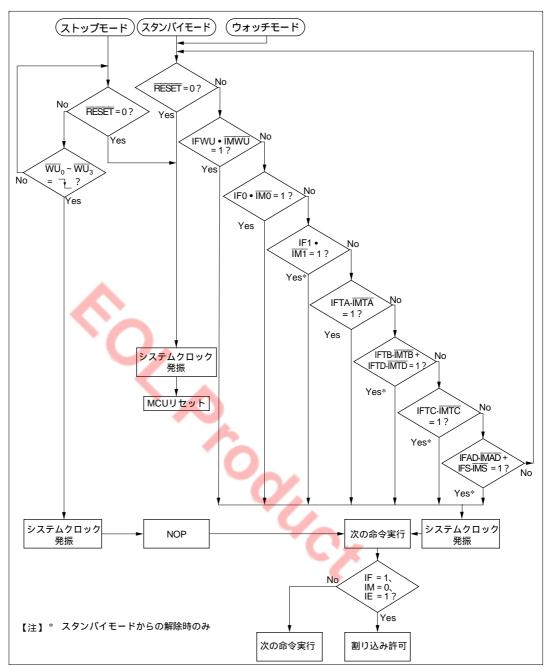

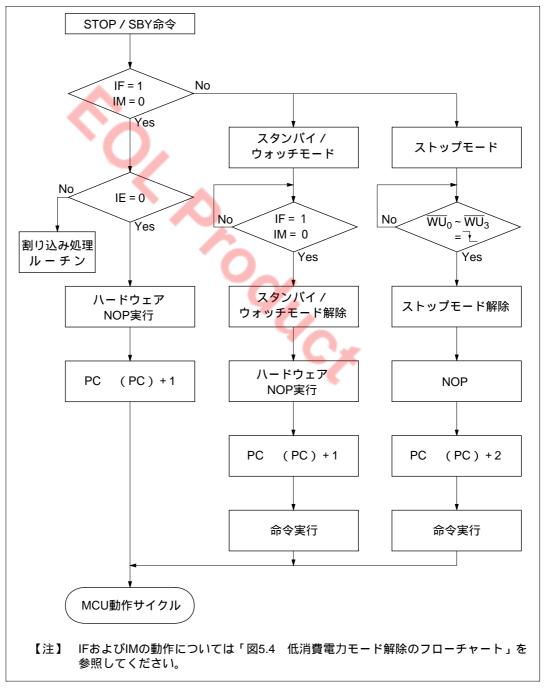

| 5.9  | 低消費電力モード重     | カ作シーケンス                                    | 102 |  |  |  |

| 5.10 | 使用上の注意        |                                            | 103 |  |  |  |

|      | 5.10.1        | 割り込みフレーム                                   | 103 |  |  |  |

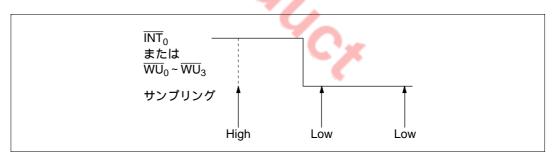

|      | 5.10.2        | WU <sub>0</sub> ~WU <sub>3</sub> 端子機能      | 104 |  |  |  |

| 第6   | 章 I/O ポート     |                                            |     |  |  |  |

| 6.1  | 概要            |                                            |     |  |  |  |

|      | 6.1.1         | 特長                                         |     |  |  |  |

|      | 6.1.2         | 入出力制御                                      |     |  |  |  |

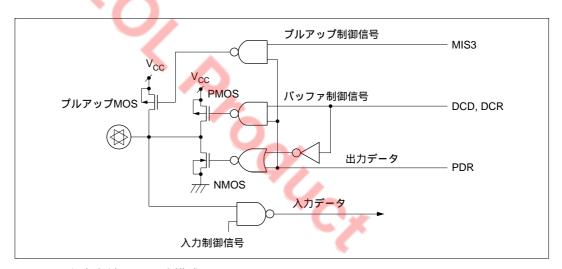

|      |               | (1)入出力端子の回路構成                              |     |  |  |  |

|      |               | (2) プル <mark>ア</mark> ップ MOS 制御            |     |  |  |  |

|      |               | (3) ミセラニアスレジスタ (MIS: \$005)                |     |  |  |  |

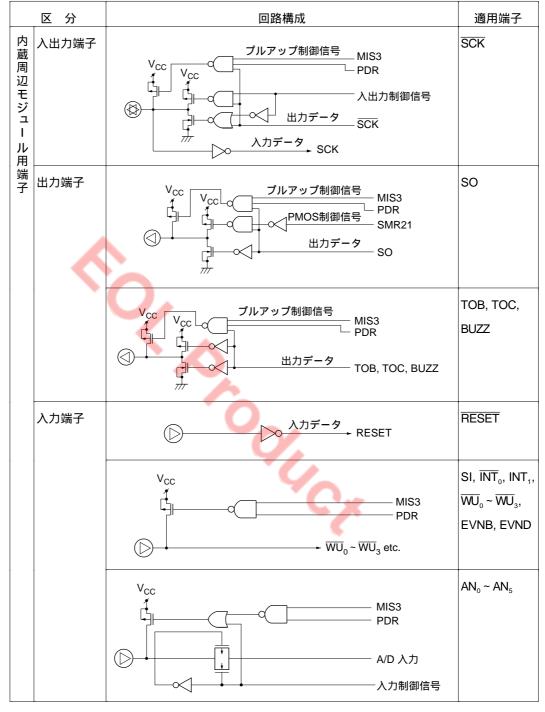

|      | 6.1.3         | 入出力端子の回路構成                                 | 111 |  |  |  |

|      | 6.1.4         | 低消費電力モード時 <mark>のポートの</mark> 状態            | 113 |  |  |  |

|      | 6.1.5         | 未使用端子の処理                                   |     |  |  |  |

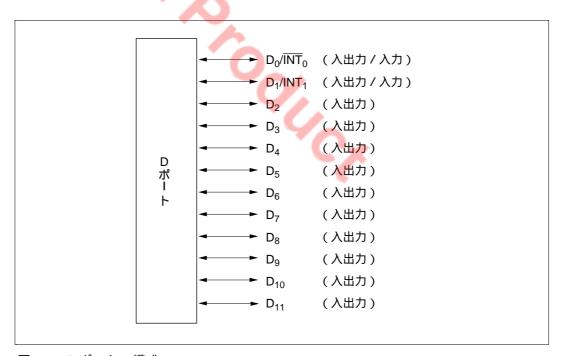

| 6.2  | Dポート          |                                            |     |  |  |  |

|      | 6.2.1         | 概要                                         |     |  |  |  |

|      | 6.2.2         | レジスタの構成と説明                                 |     |  |  |  |

|      |               | (1) ポートデータレジスタ (PDR)                       | 115 |  |  |  |

|      |               | (2) データコントロールレジスタ (DCD0~DCD2: \$030~\$032) | 116 |  |  |  |

|      |               | (3)ポートモードレジスタ0(PMR0:\$008)                 | 117 |  |  |  |

|      | 6.2.3         | 端子機能                                       | 118 |  |  |  |

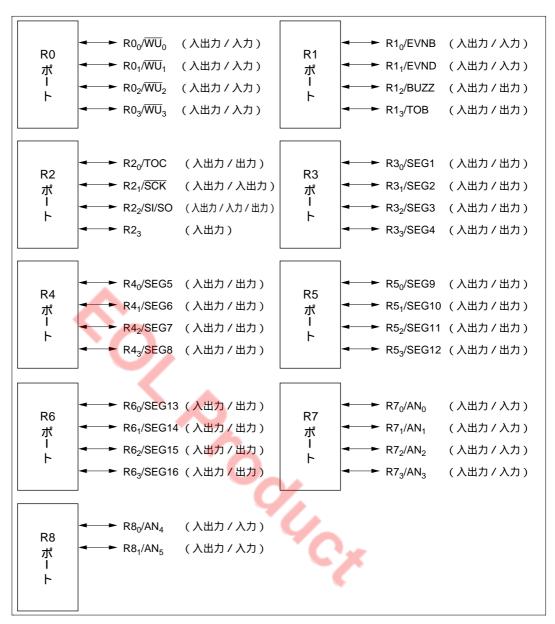

| 6.3  | R ポート         |                                            | 119 |  |  |  |

|      | 6.3.1         | 概要                                         | 119 |  |  |  |

|      | 6.3.2         | レジスタの構成と説明                                 | 121 |  |  |  |

|      |               | (1)ポートデータレジスタ(PDR)                         | 121 |  |  |  |

|      |               | (2) データコントロールレジスタ (DCR0~DCR8: \$034~\$03C) | 122 |  |  |  |

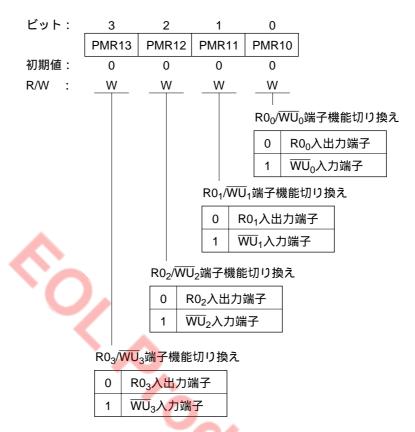

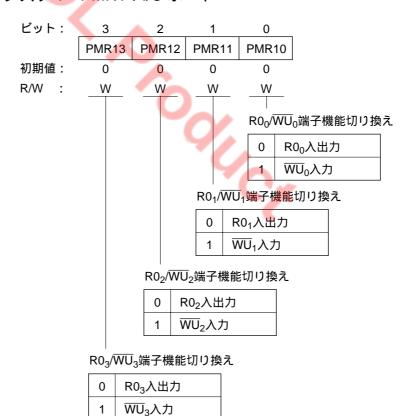

|      |               | (3)ポートモードレジスタ1(PMR1:\$009)                 | 124 |  |  |  |

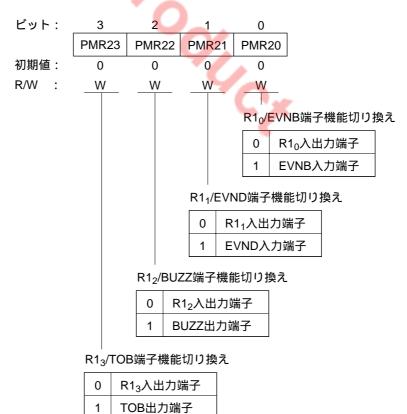

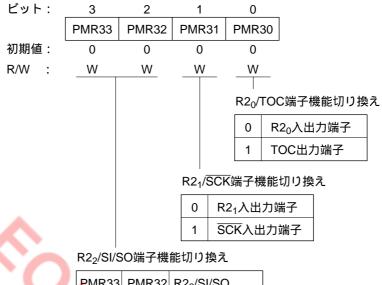

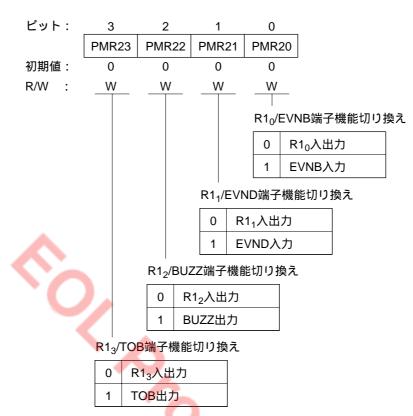

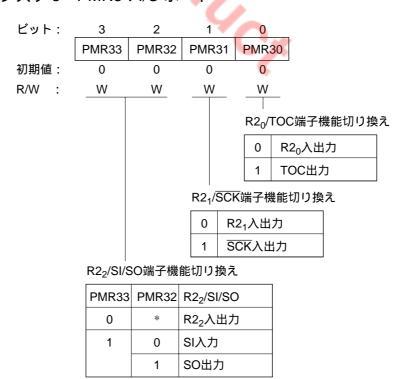

|      |               | (4)ポートモードレジスタ2(PMR2:\$00A)                 | 125 |  |  |  |

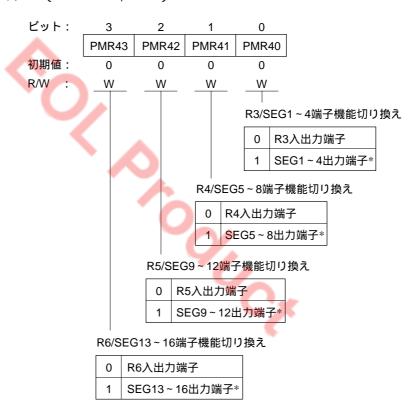

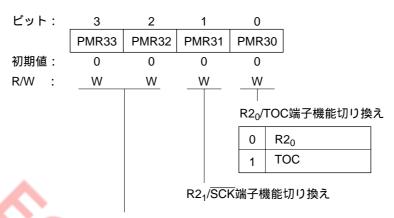

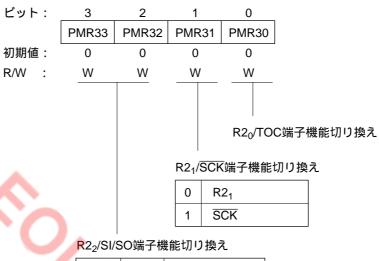

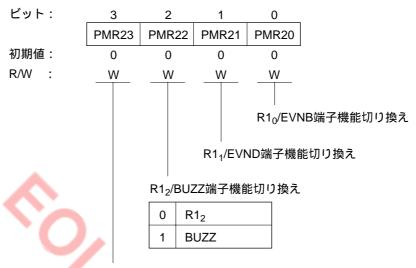

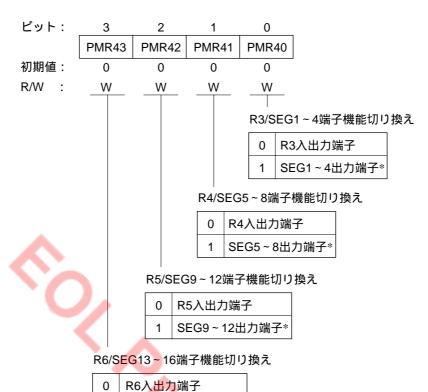

|      |               | (5)ポートモードレジスタ3(PMR3:\$00B)                 | 127 |  |  |  |

|      |               | (6) ポートモードレジスタ4(PMR4: \$00C)               | 128 |  |  |  |

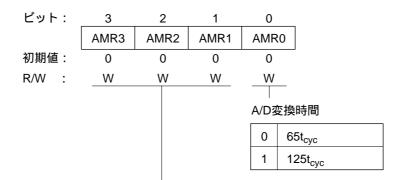

|      |               | (7) A/D モードレジスタ (AMR: \$028)               |     |  |  |  |

|      | 6.3.3         | 端子機能                                       | 131 |  |  |  |

| 6.4                      | 使用上の注意                   |                              | 137  |

|--------------------------|--------------------------|------------------------------|------|

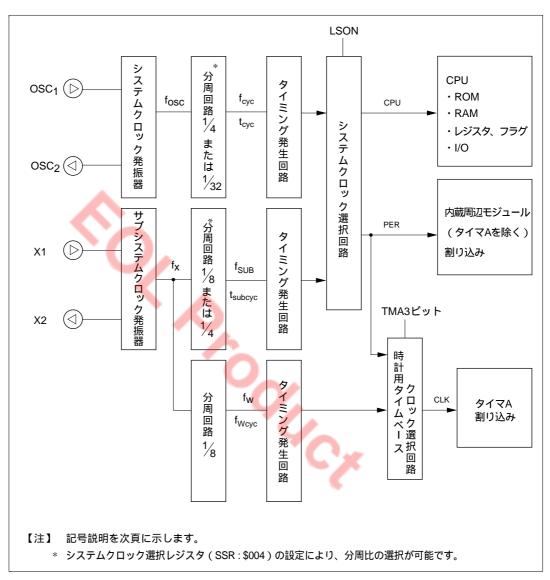

| <b>第7</b>                | '章 発振回路<br><sub>概要</sub> |                              | 1//1 |

| 7.1                      | 7.1.1                    | 特長                           |      |

|                          | 7.1.2                    | ブロック図                        |      |

|                          | 7.1.3                    | 端子構成                         |      |

|                          | 7.1.4                    | レジスタ、フラグ構成                   |      |

| 7.2                      |                          | の説明                          |      |

|                          | 7.2.1                    | システムクロック選択レジスタ (SSR: \$004)  |      |

|                          | 7.2.2                    | ロースピードオンフラグ (LSON: \$020,0)  | 147  |

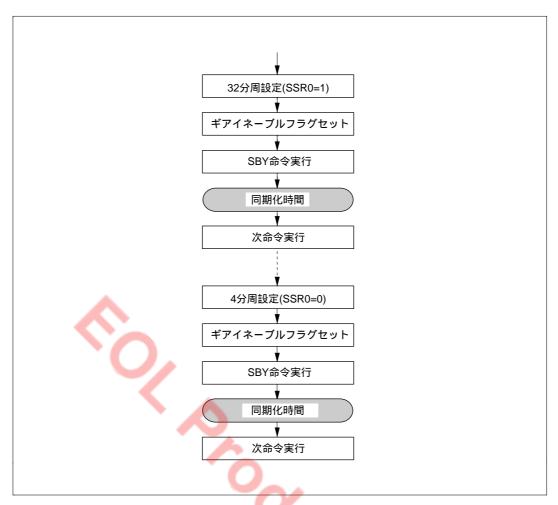

|                          | 7.2.3                    | システムクロック切り換え方法               |      |

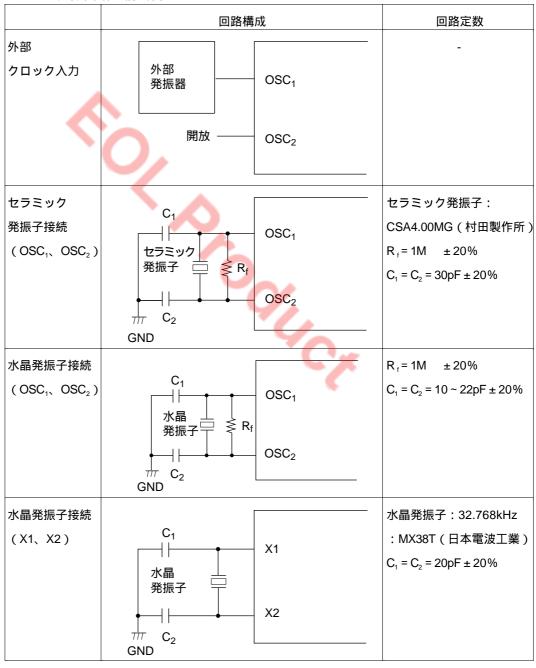

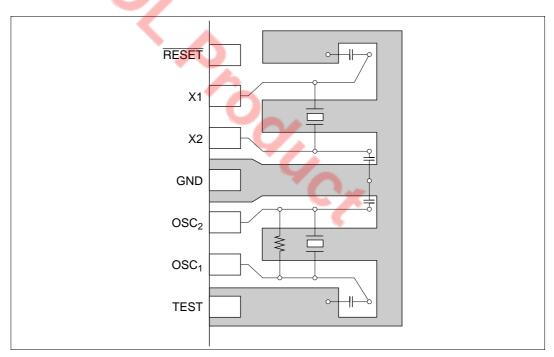

| 7.3                      | 発振子の接続および                | 外部クロック入力方法                   | 149  |

| 7.4                      | 使用上の注意                   |                              | 150  |

| 8.1<br>8.2<br>8.3<br>第 9 | プリスケーラS ( PS             | S)                           | 155  |

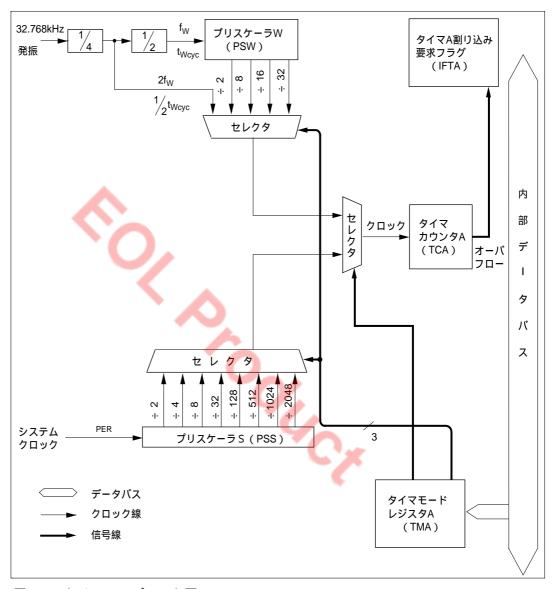

| 9.1                      | 概要                       |                              | 159  |

| <b>7.1</b>               | 9.1.1                    | 特長                           |      |

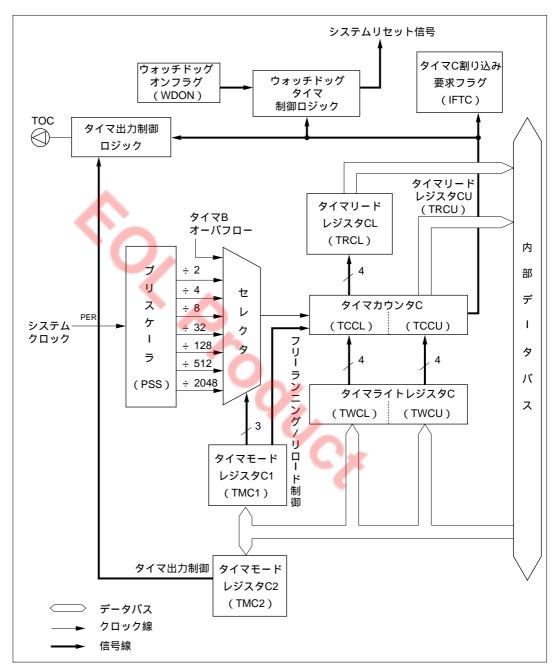

|                          | 9.1.2                    | ブロック図                        |      |

|                          | 9.1.3                    | レジスタ構成                       | 160  |

| 9.2                      | 各レジスタの説明                 |                              |      |

|                          | 9.2.1                    | タイマモードレジスタ A ( TMA : \$00F ) |      |

|                          | 9.2.2                    | タイマカウンタ A(TCA)               |      |

| 9.3                      | 動作説明                     |                              | 164  |

|                          | 9.3.1                    | フリーランニングタイマ                  | 164  |

|                          | 9.3.2                    | 時計用タイムベース動作                  | 164  |

| 9.4                      | 割り込み                     |                              | 165  |

| 9.5                      | 使用上の注意                   |                              | 165  |

# 第 10 章 タイマ B

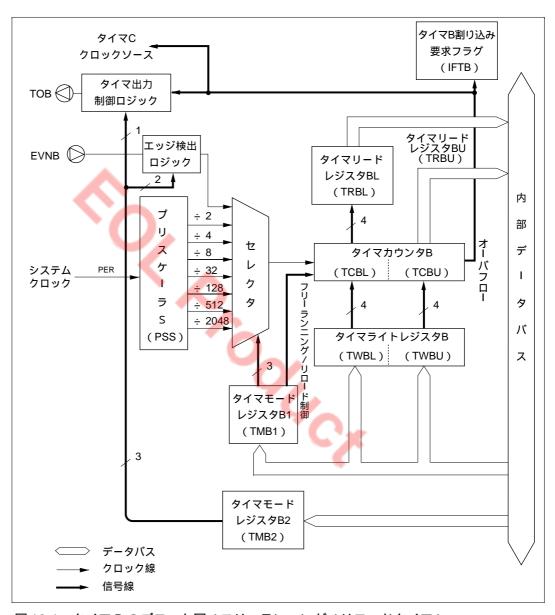

| 10.1     | 概要             |                                              | 169 |

|----------|----------------|----------------------------------------------|-----|

|          | 10.1.          | 1 特長                                         | 169 |

|          | 10.1.          | 2 プロック図                                      | 170 |

|          | 10.1.          | 3 端子構成                                       | 171 |

|          | 10.1.          | 4 レジスタ構成                                     | 171 |

| 10.2     | 各レジスタの説        | 祖                                            | 172 |

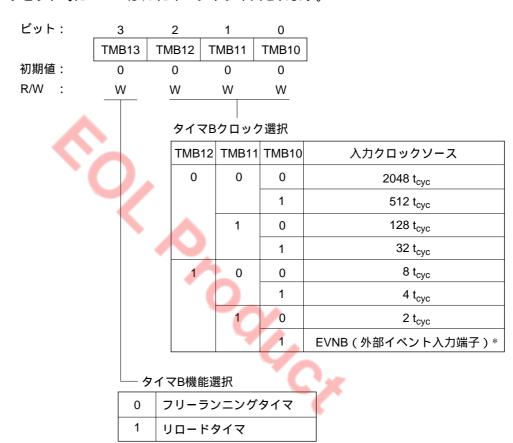

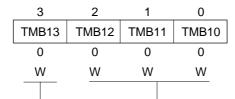

|          | 10.2.          | .1 タイマモードレジスタ B1 (TMB1: \$010)               | 172 |

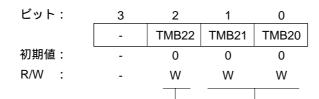

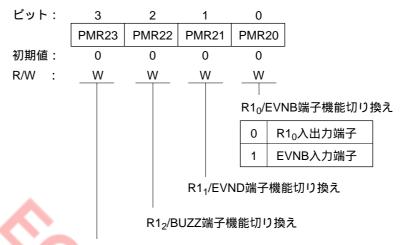

|          | 10.2.          | 2 タイマモードレジスタ B2 (TMB2: \$011)                | 175 |

|          | 10.2.          | 3 タイマカウンタB(TCB)                              | 176 |

|          | 10.2.          | 4 タイマライトレジスタ BL、U (TWBL: \$012、TWBU: \$013)  | 177 |

|          | 10.2.          | .5 タイマリードレジスタ BL、U (TRBL: \$012、TRBU: \$013) | 178 |

|          | 10.2.          | .6 ポートモードレジスタ2(PMR2: \$00A)                  | 179 |

|          | 10.2.          | .7 モジュールスタンバイレジスタ1(MSR1:\$00D)               | 180 |

| 10.3     | 動作説明           |                                              | 181 |

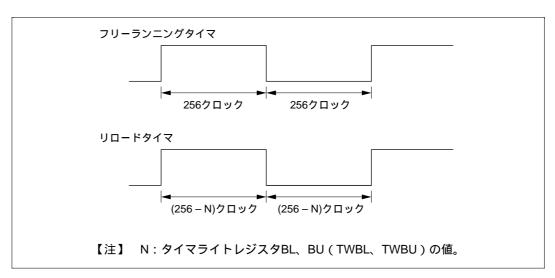

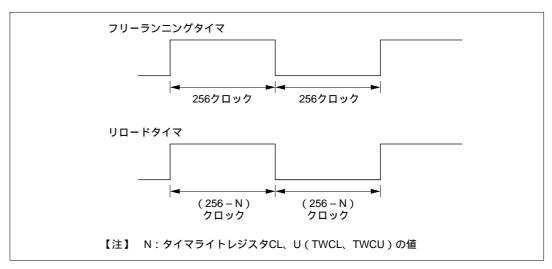

|          | 10.3.          | .1 フリーランニングタイマ動作                             | 181 |

|          | 10.3.          | .2 リロードタイマ動作                                 | 181 |

|          | 10.3.          | .3 外部イベントカウンタ動作                              | 182 |

|          | 10.3.          | .4 タイマ出力動作                                   | 182 |

|          |                | (1) トグル出力モード                                 | 182 |

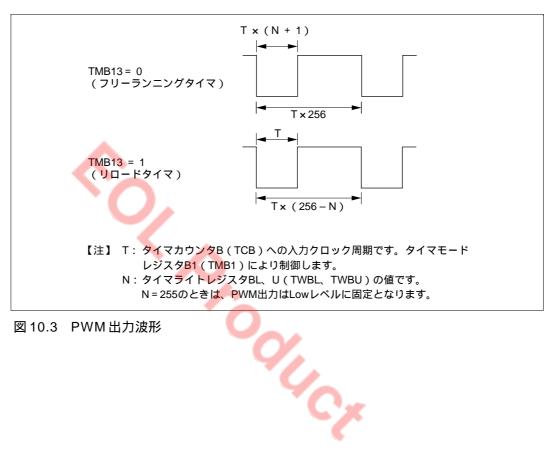

|          |                | (2) PWM 出力モード                                | 183 |

| 10.4     | 割り込み           |                                              | 184 |

| 10.5     | 使用上の注意         |                                              | 184 |

|          |                |                                              |     |

| <u>~</u> | , <del>立</del> |                                              |     |

| 弗 T      | 1章 タイマ         | C                                            |     |

| 11.1     | 概要             |                                              | 187 |

|          | 11.1.          | 1 特長                                         | 187 |

|          | 11.1.          | 2 プロック図                                      | 188 |

|          | 11.1.          | 3 端子構成                                       | 189 |

|          | 11.1.          | 4 レジスタ構成                                     | 189 |

| 11.2     | 各レジスタの説        | 胡                                            | 190 |

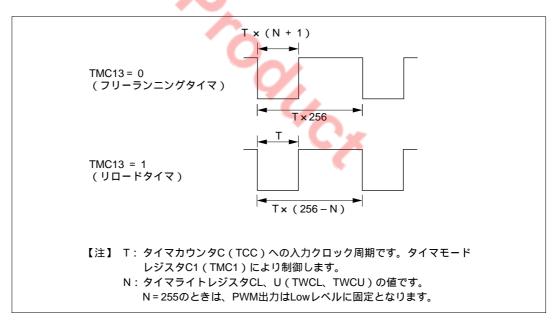

|          | 11.2.          | .1 タイマモードレジスタ C1 (TMC1: \$014)               | 190 |

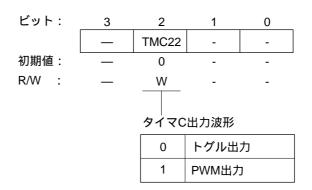

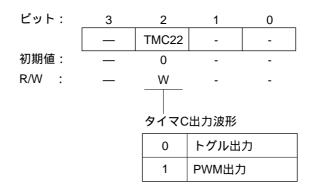

|          | 11.2.          | 2 タイマモードレジスタ C2 (TMC2: \$015)                | 193 |

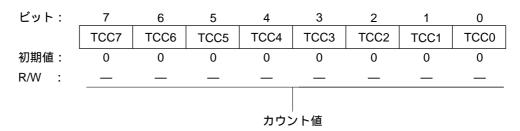

|          | 11.2.          | 3 タイマカウンタ C (TCC)                            | 194 |

|          | 11.2.          | 4 タイマライトレジスタ CL、U (TWCL: \$016、TWCU: \$017)  | 194 |

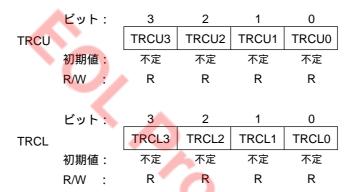

|          | 11.2.          | .5 タイマリードレジスタ CL、U (TRCL: \$016、TRCU: \$017) | 195 |

|          | 11.2.          | 6 ポートモードレジスタ3(PMR3: \$00B)                   | 196 |

|       |          | 11.2.7 | モジュールスタンバイレジスタ1(MSR1: \$00D)              | 197 |

|-------|----------|--------|-------------------------------------------|-----|

|       |          | 11.2.8 | ウォッチドッグオンフラグ ( WDON : \$020,1 )           | 198 |

| 11.3  | 動作説明.    |        |                                           | 199 |

|       |          | 11.3.1 | フリーランニングタイマ動作                             | 199 |

|       |          | 11.3.2 | リロードタイマ動作                                 | 199 |

|       |          | 11.3.3 | 16 ビットタイマ動作                               | 200 |

|       |          | 11.3.4 | ウォッチドッグタイマ動作                              | 200 |

|       |          | 11.3.5 | タイマ出力動作                                   | 200 |

|       |          |        | (1)トグル出力モード                               | 200 |

|       |          |        | (2) PWM 出力モード                             | 201 |

| 11.4  | 割り込み.    |        |                                           | 202 |

| 11.5  | 使用上の流    | 主意     |                                           | 202 |

|       |          |        |                                           |     |

|       | <u>.</u> |        |                                           |     |

| 第 12  | 章 タ      | イマD    |                                           |     |

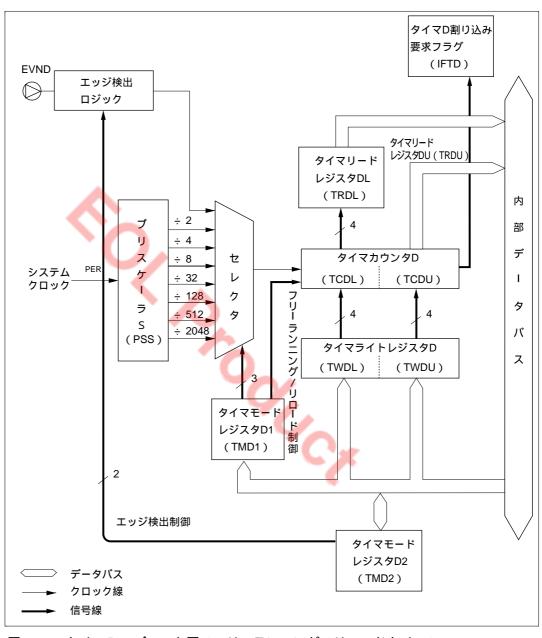

| 12.1  | 概要       |        |                                           | 205 |

|       |          | 12.1.1 | 特長                                        | 205 |

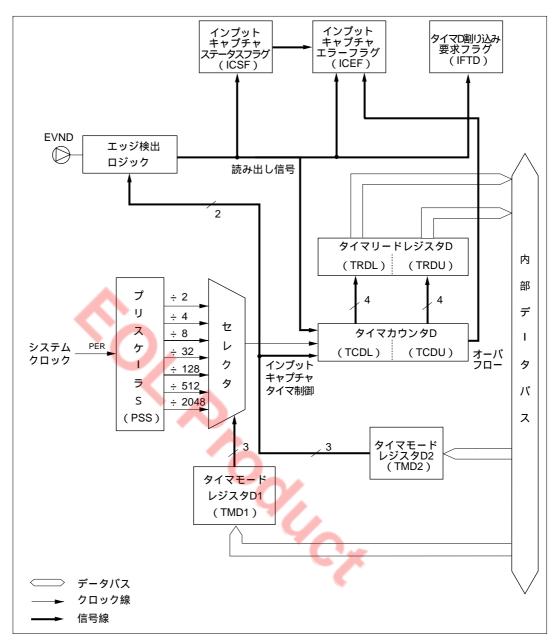

|       |          | 12.1.2 | ブロック図                                     | 206 |

|       |          | 12.1.3 | 端子構成                                      | 208 |

|       |          | 12.1.4 | レジスタ構成                                    | 208 |

| 12.2. | 各レジスク    | タの説明   |                                           | 209 |

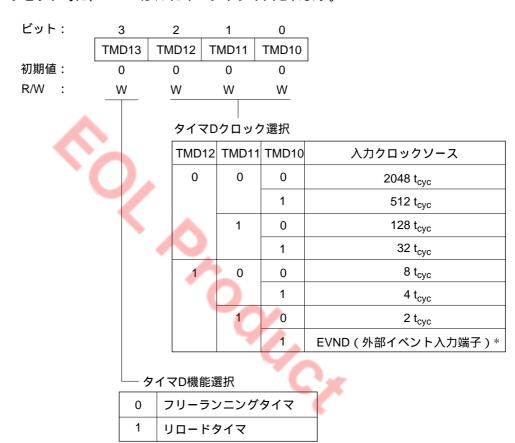

|       |          | 12.2.1 | タイマモードレジスタ D1 (TMD1: \$018)               | 209 |

|       |          | 12.2.2 | タイマモードレジスタ D2 (TMD2: \$019)               | 212 |

|       |          | 12.2.3 | タイマカウンタ D ( TCD )                         | 213 |

|       |          | 12.2.4 | タイマライトレジスタ DL、U (TWDL: \$01A、TWDU: \$01B) | 214 |

|       |          | 12.2.5 | タイマリードレジスタ DL、U (TRDL: \$01A、TRDU: \$01B) | 215 |

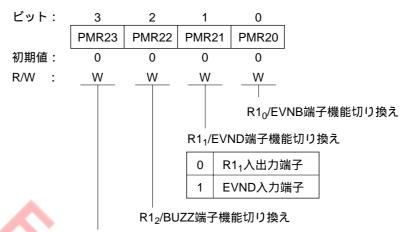

|       |          | 12.2.6 | ポートモードレジスタ2(PMR2: \$00A)                  | 216 |

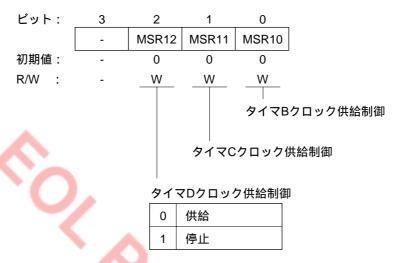

|       |          | 12.2.7 | モジュールスタンバイレジスタ1(MSR1:\$00D)               | 217 |

|       |          | 12.2.8 | インプットキャプチャステータスフラグ ( ICSF: \$021,0 )      | 218 |

|       |          | 12.2.9 | インプットキャプチャエラーフラグ ( ICEF: \$021,1 )        | 218 |

| 12.3  | 動作説明.    |        |                                           | 219 |

|       |          | 12.3.1 | フリーランニングタイマ動作                             | 219 |

|       |          | 12.3.2 | リロードタイマ動作                                 | 219 |

|       |          | 12.3.3 | 外部イベントカウンタ動作                              | 220 |

|       |          | 12.3.4 | インプットキャプチャタイマ動作                           | 220 |

| 12.4  | 割り込み.    |        |                                           | 221 |

| 12.5  | 使用上の流    | 主意     |                                           | 222 |

# 第 13 章 シリアルインタフェース

| 13.1 | 概要              |        |                                       | 225 |

|------|-----------------|--------|---------------------------------------|-----|

|      |                 | 13.1.1 | 特長                                    | 225 |

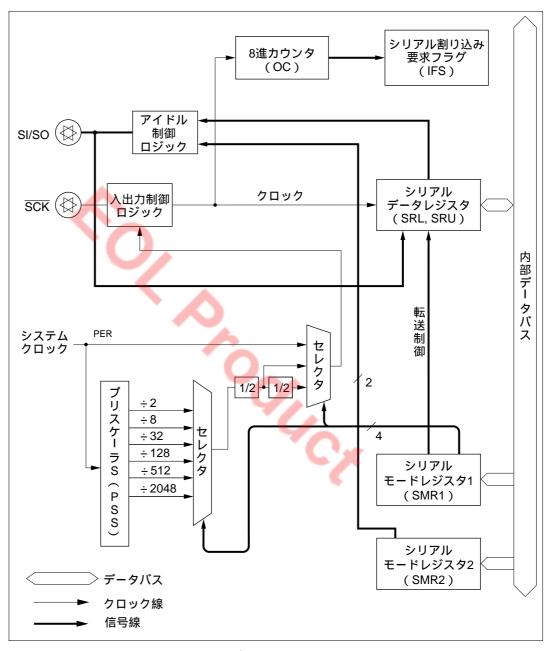

|      |                 | 13.1.2 | ブロック図                                 | 226 |

|      |                 | 13.1.3 | 端子構成                                  | 227 |

|      |                 | 13.1.4 | レジスタ構成                                | 227 |

| 13.2 | 各レジス            | タの説明   |                                       | 228 |

|      |                 | 13.2.1 | シリアルモードレジスタ1(SMR1:\$024)              | 228 |

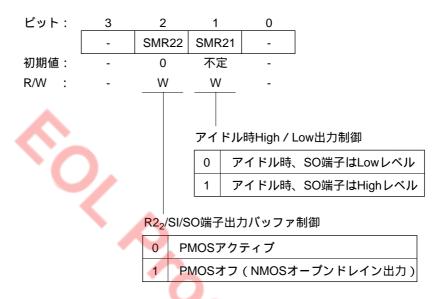

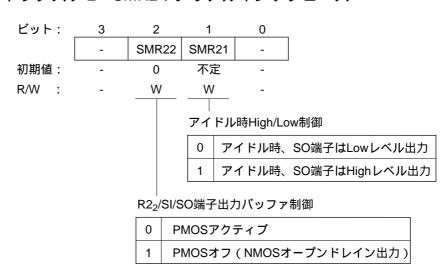

|      |                 | 13.2.2 | シリアルモードレジスタ2(SMR2: \$025)             | 230 |

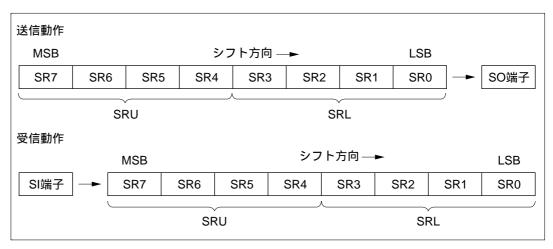

|      |                 | 13.2.3 | シリアルデータレジスタL、U(SRL: \$026、SRU: \$027) | 231 |

|      |                 | 13.2.4 | 8 進カウンタ ( OC )                        | 232 |

|      |                 | 13.2.5 | ポートモードレジスタ3(PMR3: \$00B)              | 233 |

|      |                 | 13.2.6 | モジュールスタンバイレジスタ 2 ( MSR2: \$00E )      | 234 |

| 13.3 | 動作説明            |        |                                       | 235 |

|      |                 | 13.3.1 | 動作モード                                 | 235 |

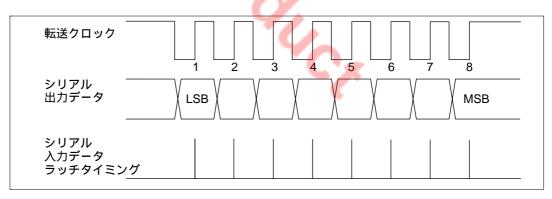

|      |                 | 13.3.2 | シリアルデータのフォーマット                        | 235 |

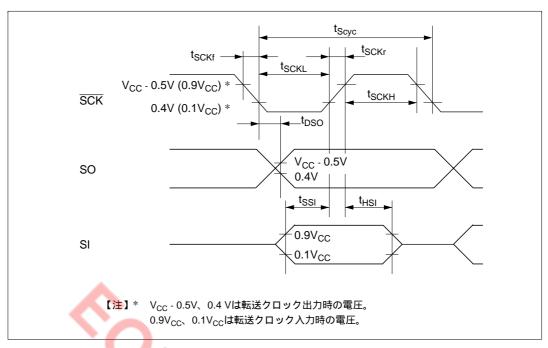

|      |                 | 13.3.3 | 転送クロック                                | 236 |

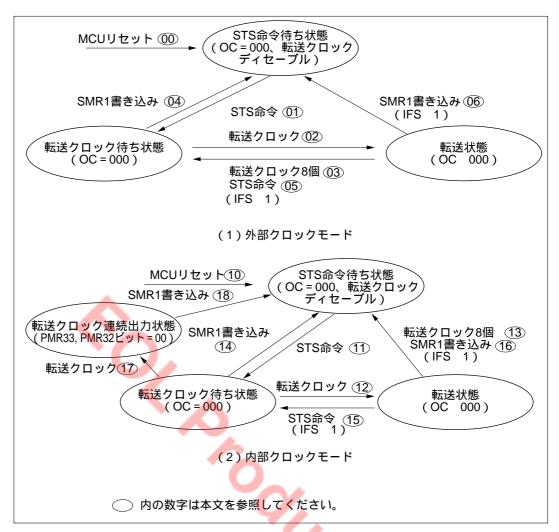

|      |                 | 13.3.4 | 動作状態                                  | 236 |

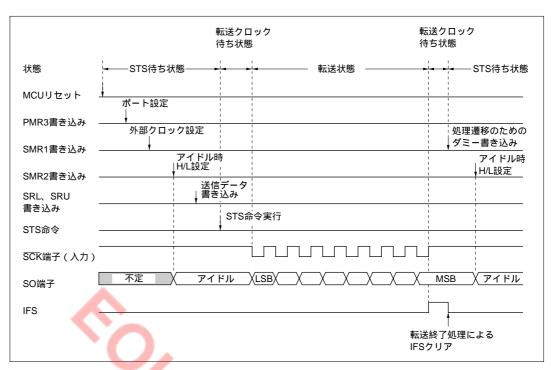

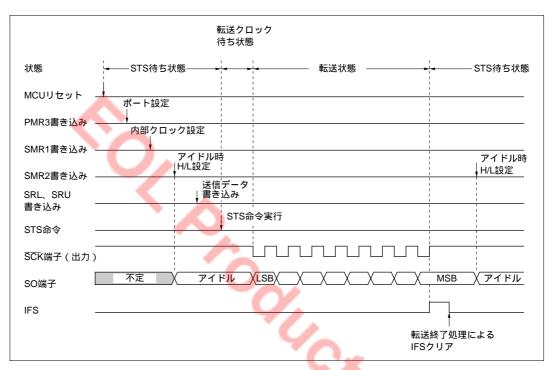

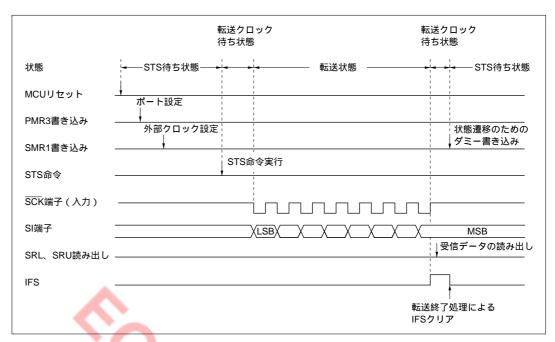

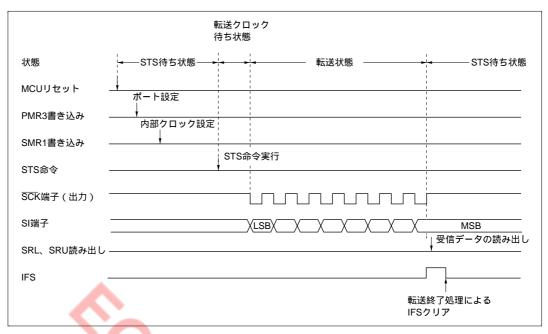

|      |                 |        | (1) STS 命令待ち状態                        | 238 |

|      |                 |        | (2)転送クロック待ち <mark>状態</mark>           | 238 |

|      |                 |        | (3) 転送状態                              | 238 |

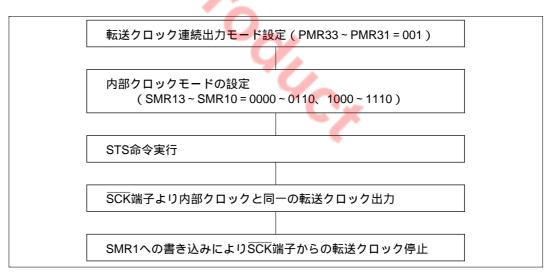

|      |                 |        | (4)転送クロック連続出力状態(内部クロックモードのみ)          | 238 |

|      |                 | 13.3.5 | 送信 / 受信動作                             | 239 |

|      |                 |        | (1)シリアルインタフェースのイニシャライズ                | 239 |

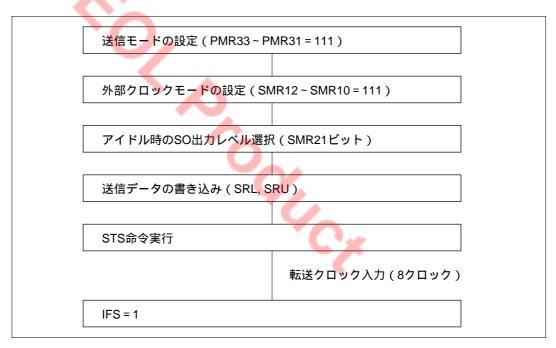

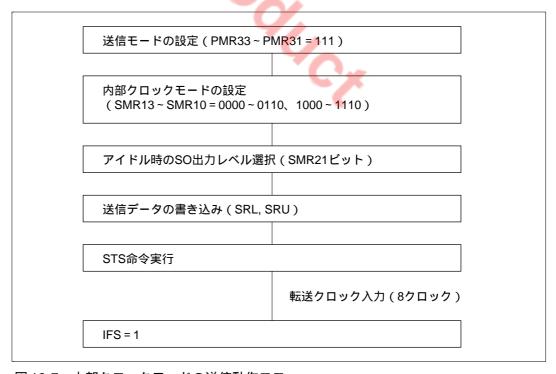

|      |                 |        | (2) データ送信                             | 239 |

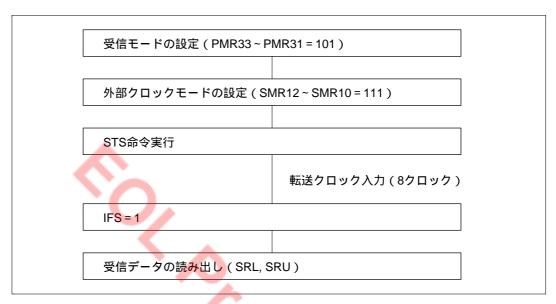

|      |                 |        | (3) データ受信                             | 242 |

|      |                 |        | (4) 転送クロック連続出力動作                      | 244 |

|      |                 | 13.3.6 | アイドル時の Low レベル / High レベル出力の選択        | 245 |

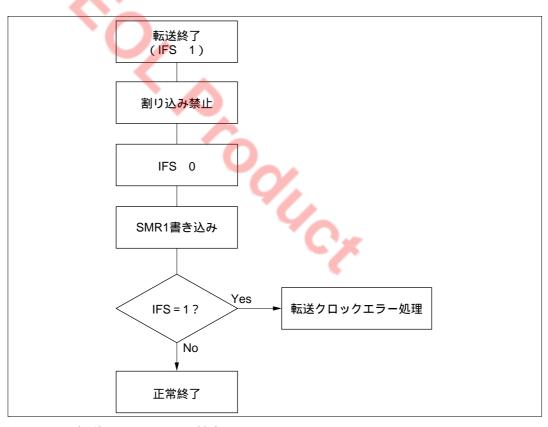

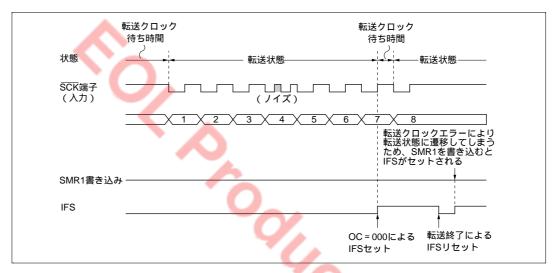

|      |                 | 13.3.7 | 転送クロックエラーの検出(外部クロックモード)               | 245 |

| 13.4 | 割り込み            |        |                                       | 247 |

| 13.5 | 使用上の            | 注意     |                                       | 247 |

|      |                 |        |                                       |     |

| ** 4 | 4 <del>**</del> | D>     | <b>&gt;</b>                           |     |

| 弗 14 | 4章 A/           | ロコンバ   | <b>√</b> −9                           |     |

| 14.1 | 概要              |        |                                       | 251 |

|      |                 | 14.1.1 | 特長                                    | 251 |

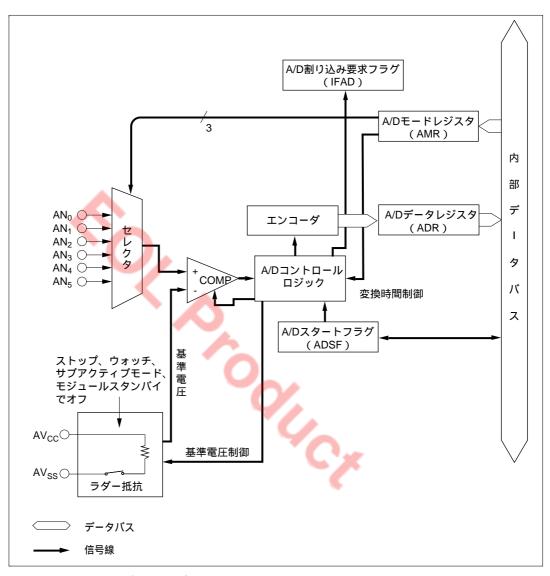

|      |                 | 14.1.2 | ブロック図                                 | 252 |

|      |                 | 14.1.3 | 端子構成                                  | 253 |

|               |       | 14.1.4 | レジスタ、フラグ構成                                   | 253 |

|---------------|-------|--------|----------------------------------------------|-----|

| 14.2          | 各レジスク | タ、フラグσ | )説明                                          | 254 |

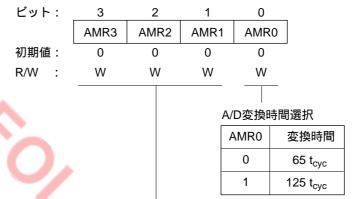

|               |       | 14.2.1 | A/D モードレジスタ (AMR: \$028)                     | 254 |

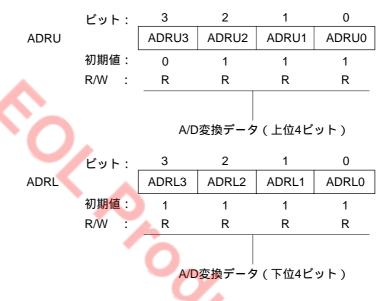

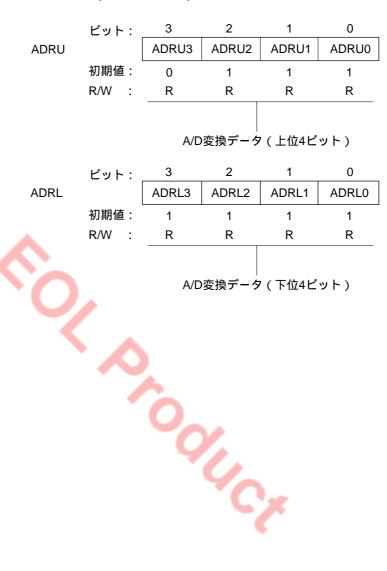

|               |       | 14.2.2 | A/D データレジスタL、U ( ADRL : \$02A、ADRU : \$02B ) | 256 |

|               |       | 14.2.3 | A/D スタートフラグ ( ADSF: \$020, 2 )               | 256 |

|               |       | 14.2.4 | モジュールスタンバイレジスタ 2 (MSR2: \$00E)               | 257 |

| 14.3          | 動作説明  |        |                                              | 258 |

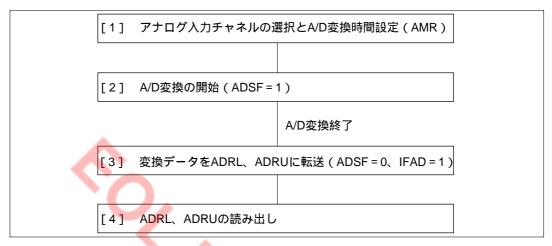

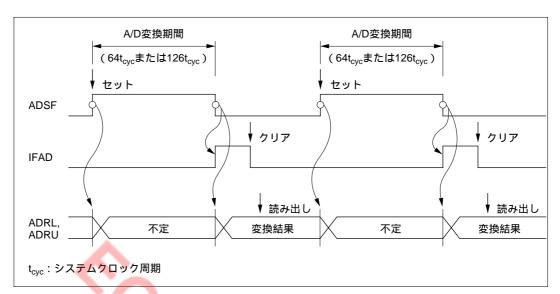

|               |       | 14.3.1 | A/D 变換動作                                     | 258 |

|               |       | 14.3.2 | 低消費電力モード時の動作                                 | 259 |

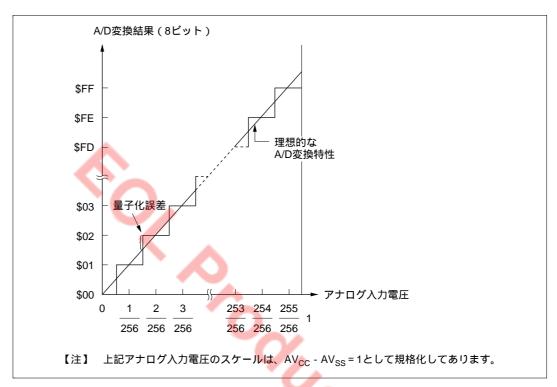

|               |       | 14.3.3 | A/D 変換の精度                                    | 260 |

| 14.4          | 割り込み  |        |                                              | 261 |

| 14.5          | 使用上の温 | 主意     | <u>A</u>                                     | 261 |

|               |       |        |                                              |     |

| 55 4 <b>-</b> |       | =+     | DA.                                          |     |

| 弗 15          | 草次的   | 晶表示回   | 路                                            |     |

| 15.1          | 概要    |        |                                              | 265 |

|               |       | 15.1.1 | 特長                                           | 265 |

|               |       | 15.1.2 | ブロック図                                        | 266 |

|               |       | 15.1.3 | 端子構成                                         | 267 |

|               |       | 15.1.4 | レジスタ構成                                       | 267 |

| 15.2          | 各レジスク | タの説明   |                                              | 268 |

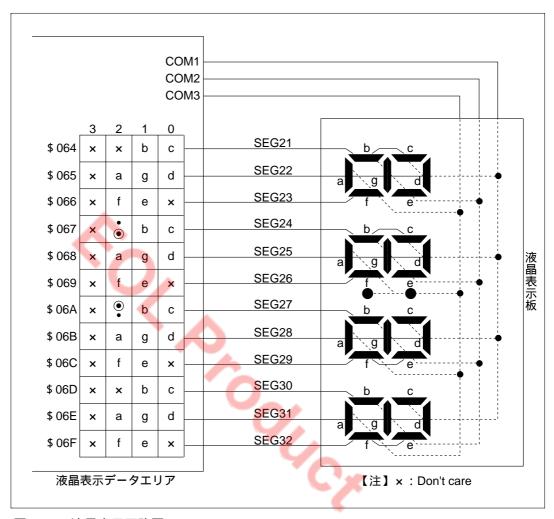

|               |       | 15.2.1 | 液晶表示データエリア ( \$050 ~ \$06F )                 | 268 |

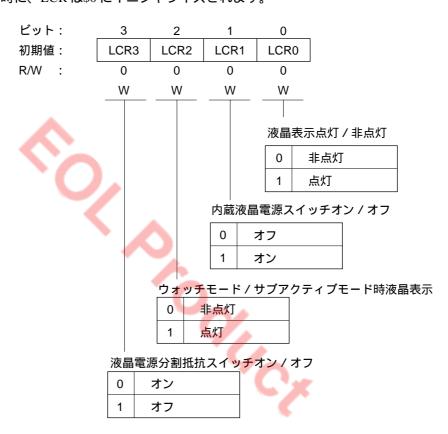

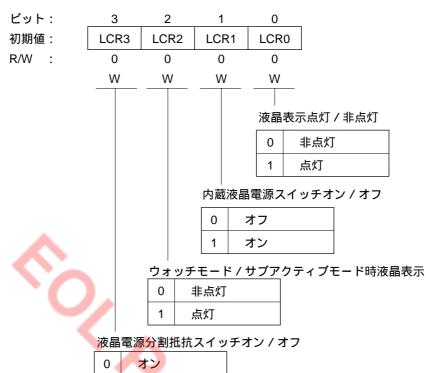

|               |       | 15.2.2 | 液晶表示制御レジスタ (LCR: \$02C)                      | 269 |

|               |       | 15.2.3 | 液晶表示モードレジスタ (LMR: \$02D)                     | 271 |

|               |       | 15.2.4 | ポートモードレジスタ4 ( PMR4 : \$00C )                 | 274 |

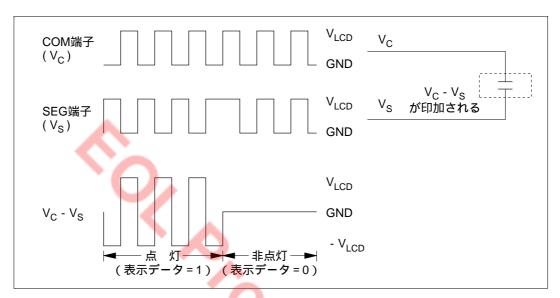

| 15.3          | 動作説明  |        |                                              | 276 |

|               |       | 15.3.1 | 概要                                           | 276 |

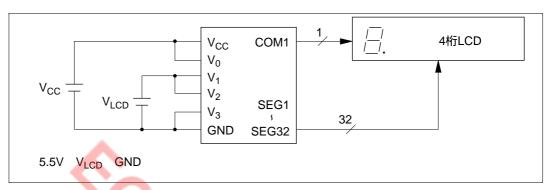

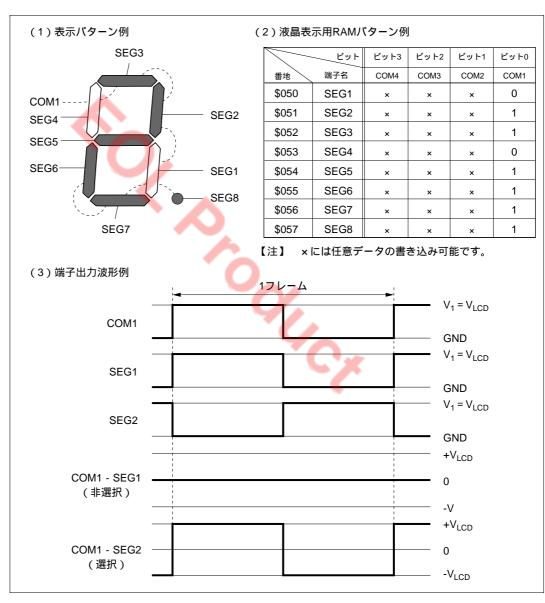

|               |       | 15.3.2 | スタティック駆動                                     | 277 |

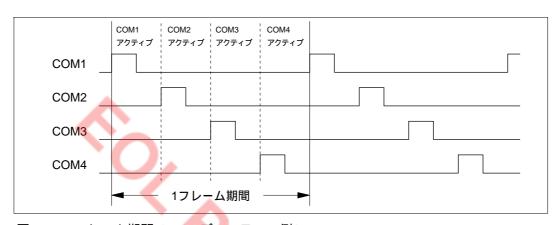

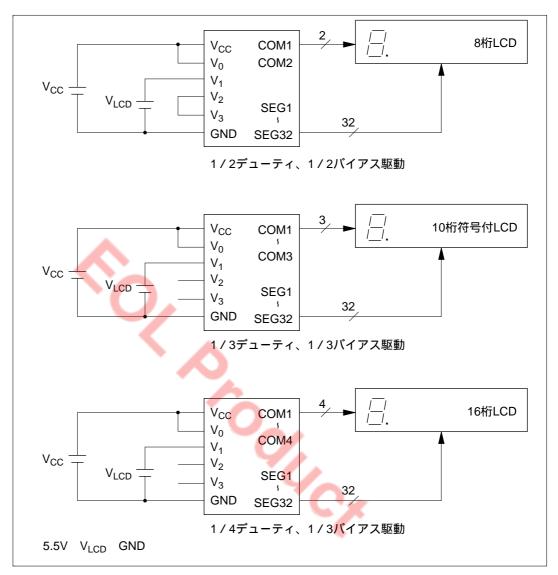

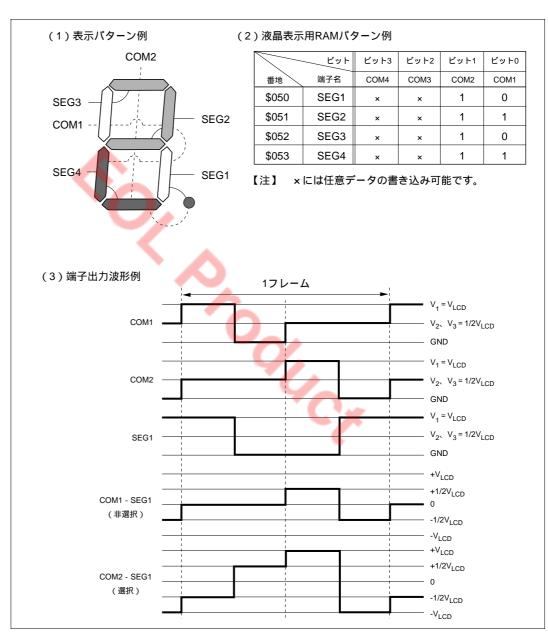

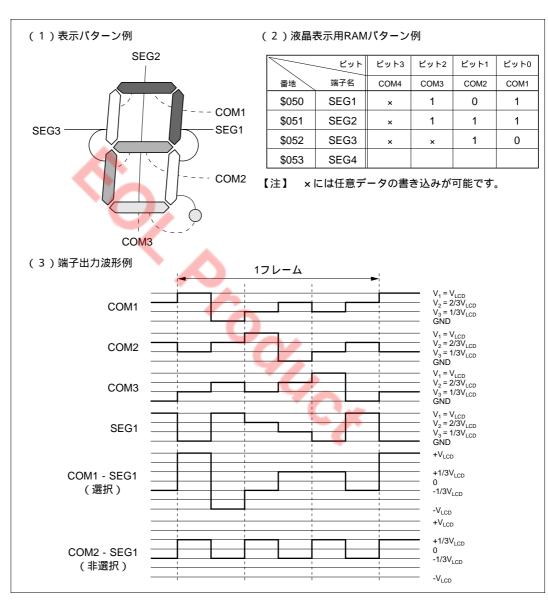

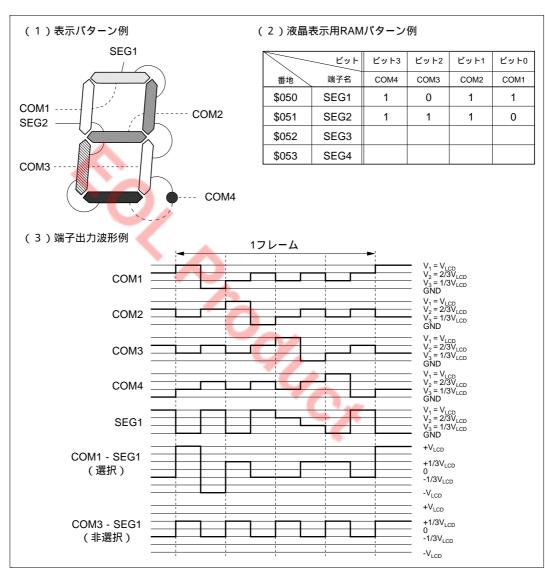

|               |       | 15.3.3 | 時分割駆動 (デューティ1/2、1/3、1/4)                     | 278 |

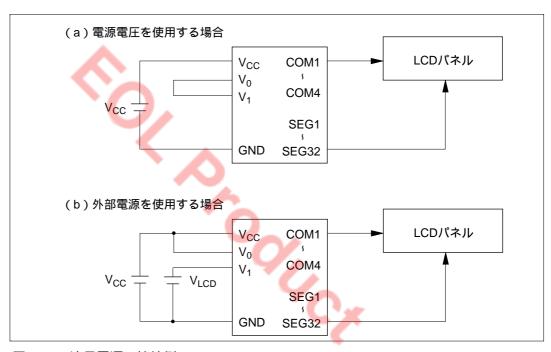

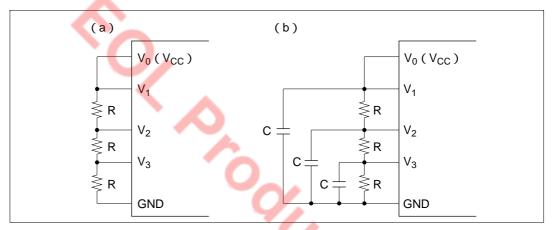

|               |       | 15.3.4 | 液晶電源の設定                                      | 281 |

| 15.4          | 応用回路例 | 列      |                                              | 282 |

|               |       | 15.4.1 | スタティック駆動での表示例(「2.」を表示する場合)                   | 282 |

|               |       | 15.4.2 | 1 / 2 デューティ、1 / 2 バイアス駆動での表示例 (「2.」を表示する場合 ) | 283 |

|               |       | 15.4.3 | 1/3 デューティ、1/3 バイアス駆動での表示例 (「2.」を表示する場合)      | 284 |

|               |       | 15.4.4 | 1/4 デューティ、1/3 バイアス駆動での表示例 (「2.」を表示する場合)      | 285 |

| 15 5          | 使用上の流 | 主音     |                                              | 286 |

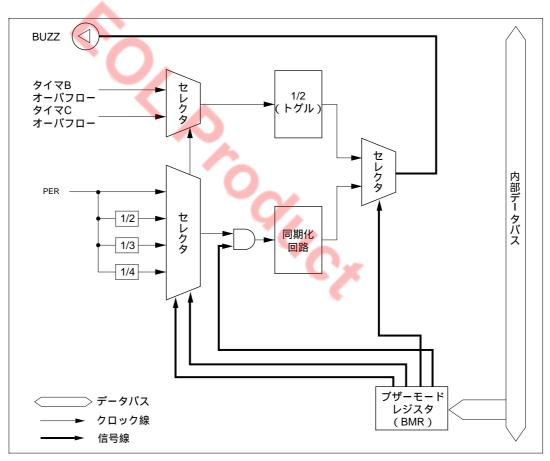

# 第16章 ブザー出力回路

| 16.1         | 概要              |                               | . 289 |

|--------------|-----------------|-------------------------------|-------|

|              | 16.1.1          | 特長                            | . 289 |

|              | 16.1.2          | ブロック図                         | . 289 |

|              | 16.1.3          | 端子構成                          | . 290 |

|              | 16.1.4          | レジスタ構成                        | . 290 |

| 16.2         | レジスタの説明         |                               | . 291 |

|              | 16.2.1          | ブザーモードレジスタ (BMR: \$02E)       | . 291 |

|              | 16.2.2          | ポートモードレジスタ 2 ( PMR2 : \$00A ) | . 293 |

| 16.3         | 動作説明            |                               | . 294 |

|              | 16.3.1          | タイマオーバフローのトグル出力動作             | . 294 |

|              | 16.3.2          | システムクロックの分周クロックパルス出力          | . 294 |

|              |                 |                               |       |

|              |                 |                               |       |

| 第 17         | '章 ROM          |                               |       |

| 17.1         | 概要              |                               | . 297 |

| 17.2         | PROM <b>モード</b> |                               | . 298 |

|              | 17.2.1          | PROM モード                      | . 298 |

|              | 17.2.2          | ソケットアダプタの端子対応とメモリマップ          | . 298 |

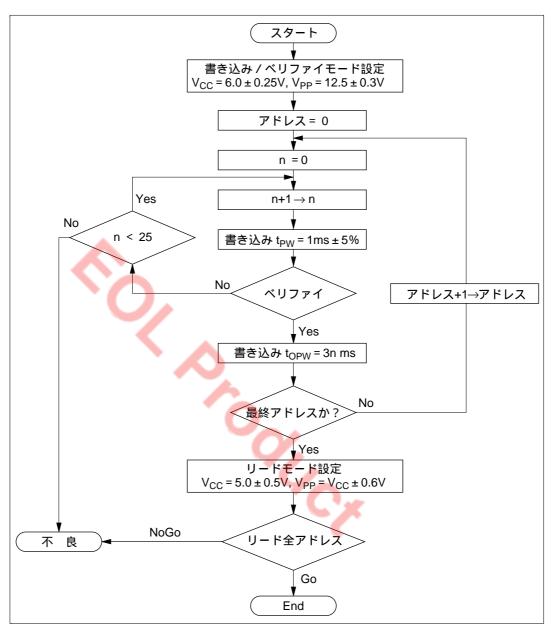

| 17.3         | プログラミング         |                               | . 301 |

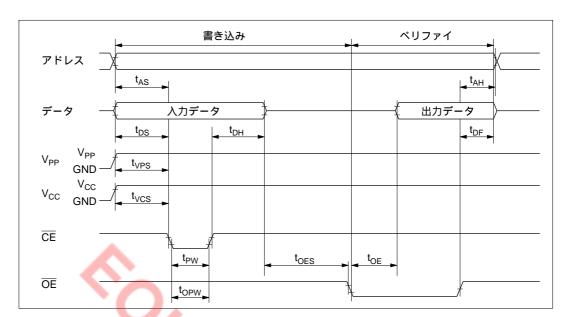

|              | 17.3.1          | 書き込み / ベリファイ                  | . 301 |

|              | 17.3.2          | 書き込み時の注意                      | . 304 |

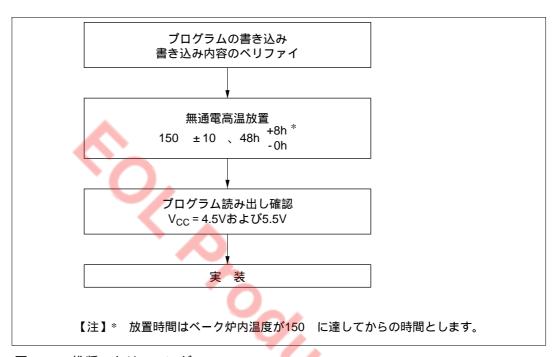

|              | 17.3.3          | 書き込み後の信頼性                     | . 305 |

| 17.4         | ROM 発注時のお願      | 頁U1                           | . 306 |

|              |                 |                               |       |

|              |                 |                               |       |

| 第 18         | 章 RAM           |                               |       |

| 18.1         | 概要              |                               | . 309 |

|              | 18.1.1          | 特長                            | . 309 |

|              | 18.1.2          | RAM メモリマップ                    | . 310 |

|              | 18.1.3          | レジスタ構成                        | . 310 |

| 18.2         | 各レジスタ、フラ        | グの説明                          | . 311 |

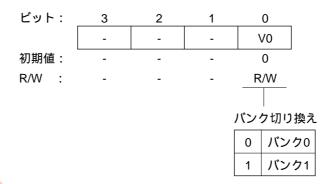

|              | 18.2.1          | バンクレジスタ (V: \$03F)            | . 311 |

| 18.3         | 使用上の注意          |                               | . 311 |

|              |                 |                               |       |

| <b>~</b> ~ - |                 |                               |       |

| 第19          | 章 使用例           |                               |       |

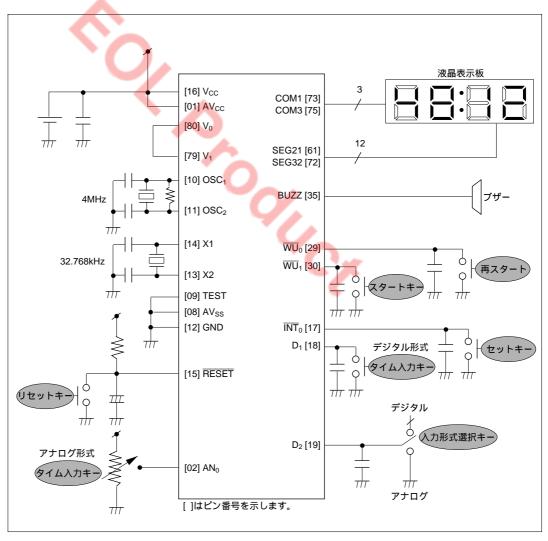

| 19.1         | 概要              |                               | . 315 |

| 19.2 | システム仕様        |                      | 316 |

|------|---------------|----------------------|-----|

| 19.3 | 液晶表示回路図       |                      | 317 |

| 19.4 | レジスタ仕様        |                      | 318 |

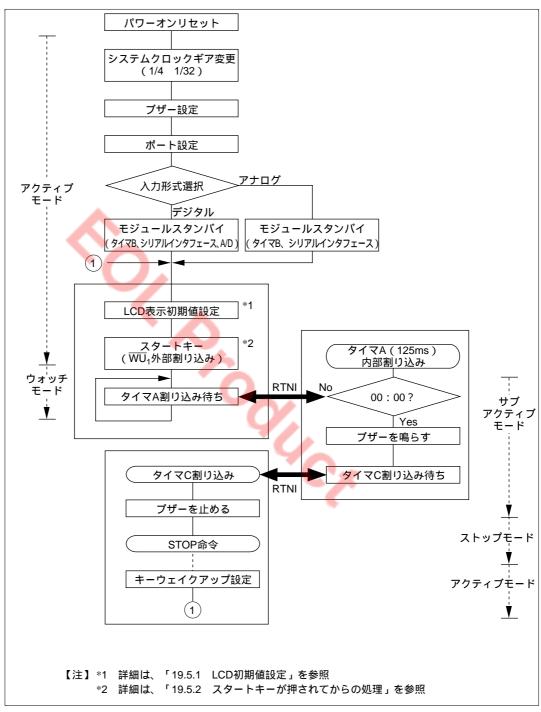

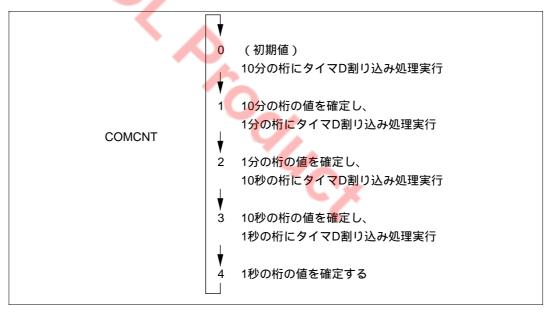

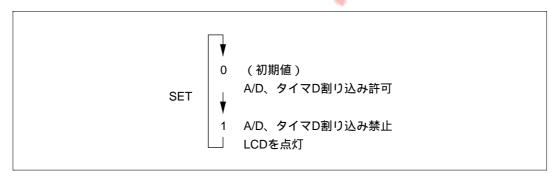

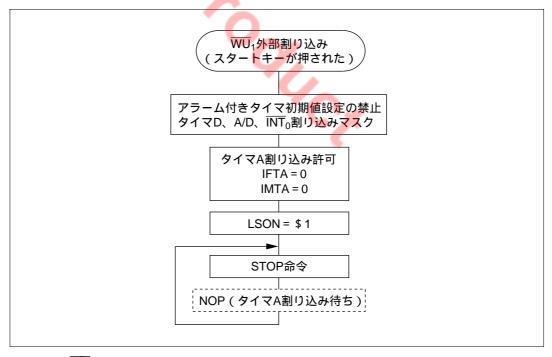

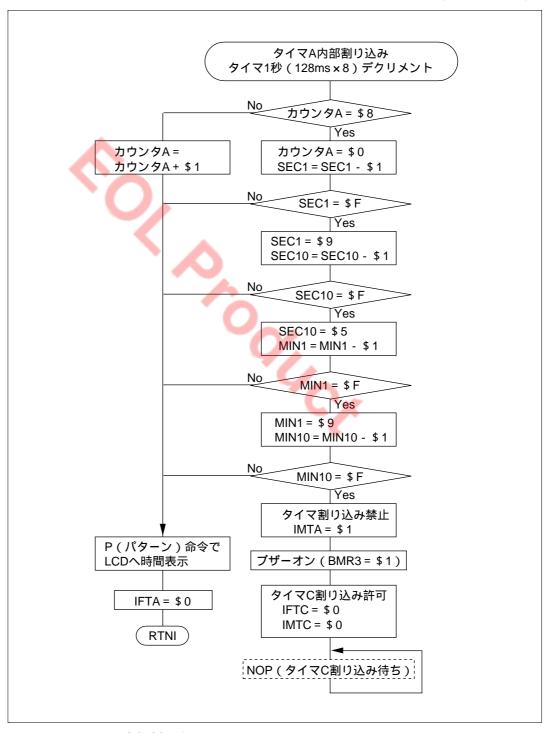

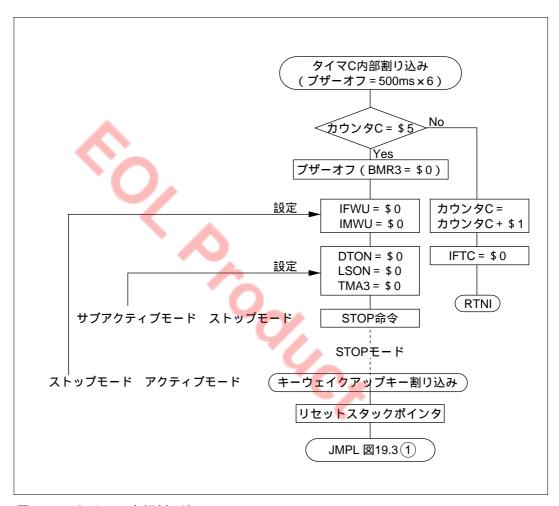

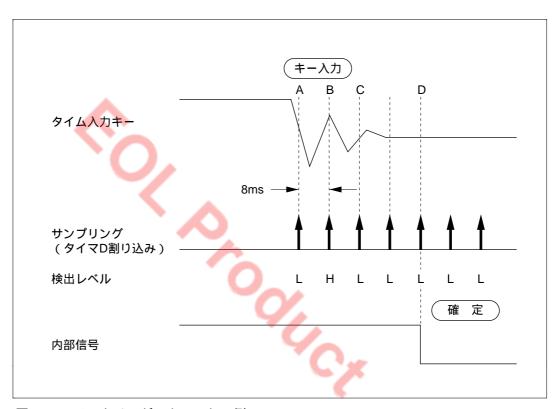

| 19.5 | フローチャート       |                      | 321 |

|      | 19.5.1        | LCD 表示初期值設定          | 322 |

|      | 19.5.2        | スタートキーが押されてからの処理     | 324 |

| 19.6 | 使用上の注意        |                      | 327 |

| 第 20 | ) 章 電気的特性     | <b></b>              |     |

| 20.1 | 絶対最大定格        |                      | 331 |

| 20.2 | 電気的特性         | <u>A</u>             | 332 |

|      | 20.2.1        | DC 特性                | 332 |

|      | 20.2.2        | 内蔵周辺モジュールの特性         | 335 |

|      | 20.2.3        | AC 特性                | 337 |

| 付録   |               |                      |     |

| A.   | 命令            |                      |     |

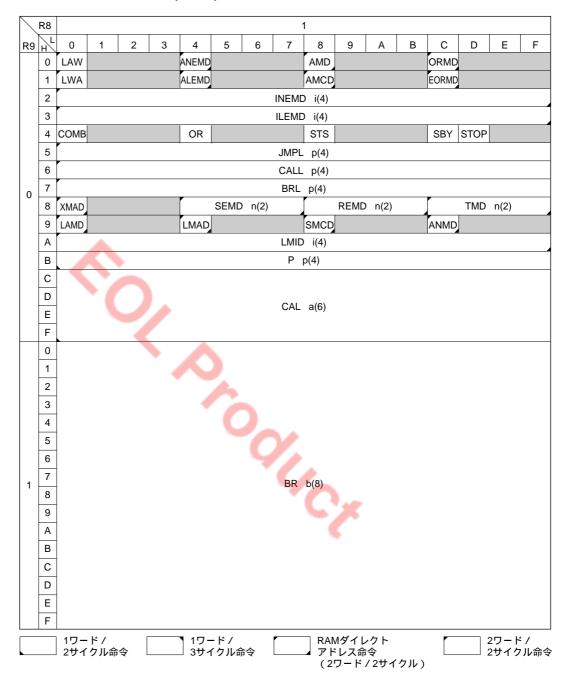

|      | A.1           | 命令一覧                 |     |

|      | A.2           | オペレーションコードマップ        |     |

| B.   | 内部 I/O レジスター覧 | <u></u>              |     |

|      | B.1           | アドレス一覧               |     |

|      | B.2           | 機能一覧                 |     |

| C.   | ROM 発注手順      |                      |     |

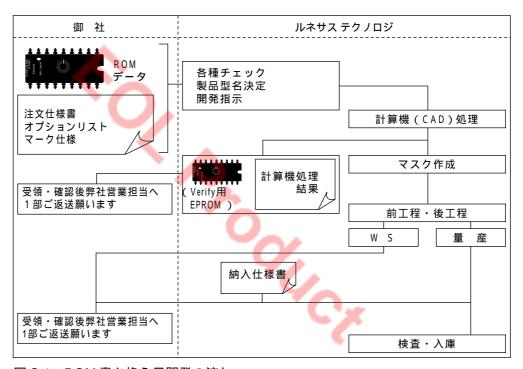

|      | C.1           | ROM 書き換え品開発の流れ(発注手順) | 375 |

|      | C.2           | ROM 発注時の提出物と注意事項     | 376 |

| D.   | オプションリスト      |                      | 377 |

| E.   | 型名一覧          |                      | 379 |

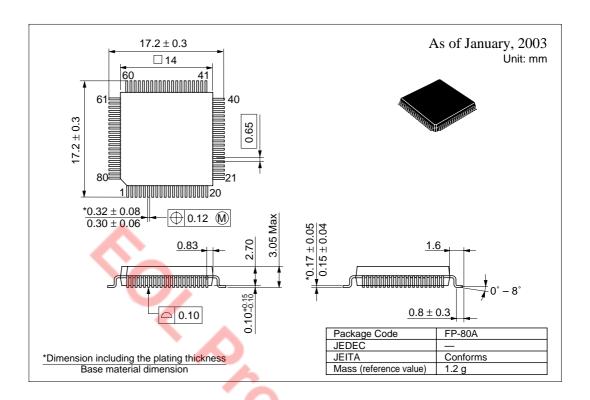

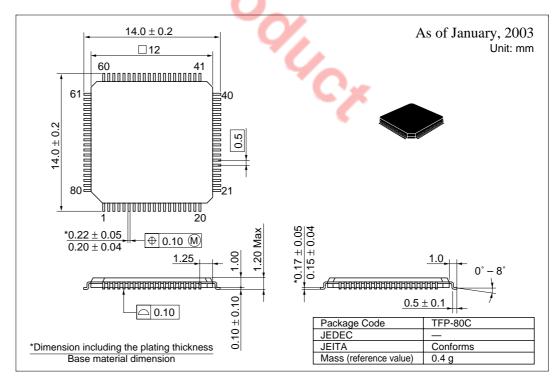

| F.   | 外形寸法図         |                      | 380 |

# 1. 概要

## 第1章 目次

| 1.1 | 概要      | <br>3 |

|-----|---------|-------|

| 1.2 | 内部ブロック図 | <br>  |

| 1.3 | 端子説明    |       |

|     | 1.3.1   |       |

|     | 1.3.2   |       |

|     |         |       |

# 1.1 概要

HD404889 シリーズは、HMCS400 CPU を核にもち、液晶表示回路をはじめ、各種周辺機能を内蔵した 4 ビットマイクロコンピュータユニット (MCU)です。

HD404889 シリーズの製品ラインアップを表 1.1 に、特長を表 1.2 に示します。

表 1.1 製品ラインアップ

| シリーズ     | ROM               | 製品名       | 形名          | ROM    | RAM     | パッケージ   |

|----------|-------------------|-----------|-------------|--------|---------|---------|

|          | タイプ               |           |             | (ワード)  | (ディジット) |         |

| HD404889 | マスク               | HD404888  | HD404888H   | 8,192  | 1,344   | FP-80A  |

|          | ROM               |           | HD404888TE  |        |         | TFP-80C |

|          |                   | HD4048812 | HD4048812H  | 12,288 |         | FP-80A  |

|          |                   |           | HD4048812TE |        |         | TFP-80C |

|          |                   | HD404889  | HD404889H   | 16,384 |         | FP-80A  |

|          |                   |           | HD404889TE  |        |         | TFP-80C |

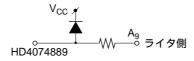

|          | ZTAT <sup>®</sup> | HD4074889 | HD4074889H  | 16,384 |         | FP-80A  |

|          |                   |           | HD4074889TE |        |         | TFP-80C |

【注】 ZTAT<sup>®</sup>は、(株)ルネサス <del>テ</del>クノロジの登録商標です。

表 1.2 特長 (1)

| 項目            | 仕 様                                             |

|---------------|-------------------------------------------------|

| CPU           | ・3 種類の RAM アドレッシングモード                           |

|               | (1)レジスタ間接アドレッシング                                |

|               | (2)直接アドレッシング                                    |

|               | (3)メモリレジスタアドレッシング                               |

|               | ・4 種類の ROM アドレッシングモードと P 命令                     |

|               | (1) ダイレクトアドレッシング                                |

|               | (2) カレントアドレッシング                                 |

|               | (3) ゼロページアドレッシング                                |

|               | (4) テーブルデータアドレッシング                              |

|               | (5) P 命令(ROM データ参照命令)                           |

|               | ・簡潔かつ効率のよい命令セット                                 |

|               | ▶1 サイクルまたは 2 サイクルで実行( リターン命令のみ 3 サイクル )         |

|               | ・最小命令実行時間:0.89 µ s                              |

| ROM           | ・HD404888 : 8,192 ワード                           |

| (1ワード=10ビット)  | ・HD4048812 : 12,288 ワード                         |

|               | ・HD404889 : 16,384 ワード                          |

|               | ・HD40748 <mark>89 : 16,384 ワード</mark>           |

| RAM           | ・1,344 ディジット                                    |

| (1ディジット=4ビット) | ・液晶表示データ用 <mark>デュアルポ</mark> ート RAM を内蔵         |

| I/O ポート       | ・入出力端子 46 本(内 12 <mark>本は大電流端子)</mark>          |

|               | ・全入出力端子にプログラムで <mark>制</mark> 御可能なプルアップ MOS を内蔵 |

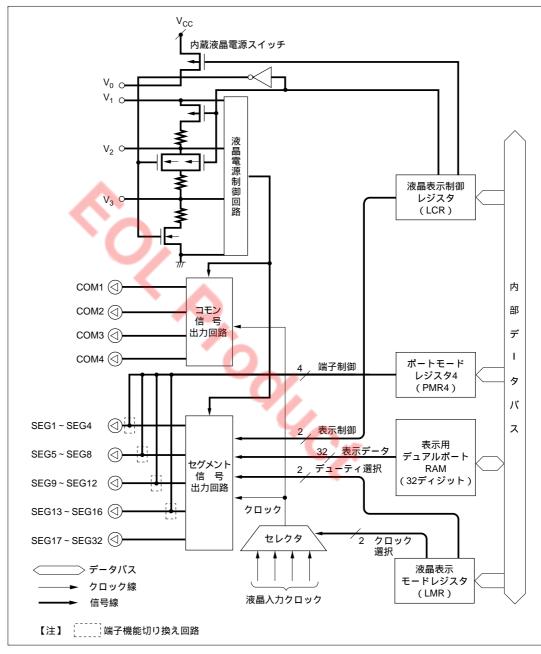

| 液晶表示回路        | ・4 本のコモン信号端子と 32 本のセグメント信号端子                    |

|               | (内 16 本のセグメント信号端子はRポートと兼用)                      |

|               | ・ソフトウェアにより、液晶電源分割抵抗の切り離しが可能                     |

|               | ・4 種類のデューティ(スタティック、1/2、1/3、1/4)、および             |

|               | 4 種類の LCD クロックを選択可能 (32.768kHz 発振をクロックソー        |

|               | スに選択することで、ウォッチモード時にも表示可能)                       |

|               | ・液晶表示用デュアルポート RAM を内蔵し、表示データを自動的に               |

|               | セグメント端子より出力                                     |

表1.2 特長(2)

| 項目          | 仕 様                                           |

|-------------|-----------------------------------------------|

| タイマA        | ・8 ビットフリーランニングタイマ:                            |

|             | システムクロックを分周した8種類の内部クロック、または                   |

|             | 32.768kHz 発振を分周した 5 種類のクロック(時計用タイムベー          |

|             | ス)によるカウントアップが可能。                              |

|             | ・オーバフロー時に割り込み発生可能                             |

| タイマB        | ・8 ビットフリーランニング / リロードタイマ:                     |

|             | 7種類の内部クロック、またはイベント入力によるカウントアップ                |

|             | が可能。イベント入力の検出は、立ち下がりエッジ、立ち上がりエ                |

|             | ッジ、立ち下がり/立ち上がり両エッジの選択が可能。                     |

|             | タイマ出力(トグル出力、PWM 出力)が可能。                       |

|             | ・オーバフロー時に割り込み発生可能。                            |

| タイマC        | - 8 ビットフリーランニング / リロードタイマ:                    |

|             | 8 種類の内部クロックによるカウントアップが可能。                     |

|             | ウォッチドッグタイマ動作が可能。                              |

|             | タイマ出力(トグル出力、PWM 出力)が可能。                       |

|             | ・オーバフロー時に割り込み発生可能。                            |

|             | ・16 ビットモード(タイマBオーバフロー入力可)。                    |

| タイマD        | ・8 ビットフリーランニング / リロードタイマ:                     |

|             | 7 種類の内部クロック、またはイベント入力によるカウントアップ               |

|             | が可能。イベント入力の <mark>検出は、立</mark> ち下がりエッジ、立ち上がりエ |

|             | ッジ、立ち下がり / 立ち上が <mark>り</mark> 両エッジの選択が可能。    |

|             | インプットキャプチャ動作可能。                               |

|             | ・オーバフロー、インプットキャプチャ動作時に割り込み発生可能。               |

| シリアルインタフェース | ・8 ビットクロック同期式シリアルインタフェース ×1 チャネル              |

|             | ・転送クロックは、13 種類の内部クロックまたは外部クロックから選             |

|             | 択可能。                                          |

|             | ・アイドル時のデータ送信端子の High レベル / Low レベル出力制御        |

|             | 可能。                                           |

|             | ・転送終了 / 中断時に割り込み発生可能。                         |

| A/D コンバータ   | ・抵抗ラダー方式による逐次比較形 A/D コンバータ                    |

|             | ・分解能:8ビット                                     |

|             | ・A/D 変換終了時に割り込み発生可能。                          |

|             | ・アナログ入力:6 チャネル(R ポートと兼用)                      |

表1.2 特長(3)

| 項目         | 仕 様                          |

|------------|------------------------------|

| ブザー出力回路    | ・タイマオーバフローのトグル出力可能           |

|            | ・システムクロックの分周クロックパルス出力可能      |

| 割り込み       | ・外部割り込み要因:3要因                |

|            | ・内部割り込み要因:6要因                |

|            | ・割り込みベクタ:8 種類                |

| 低消費電力モード   | ・スタンバイモード                    |

|            | ・ストップモード                     |

|            | ・ウォッチモード                     |

|            | ・サブアクティブモード                  |

| システムクロック   | • 0.4 ~ 1.0MHz, 1.6 ~ 4.5MHz |

| サブシステムクロック | • 32.768kHz                  |

|            |                              |

# 1.2 内部ブロック図

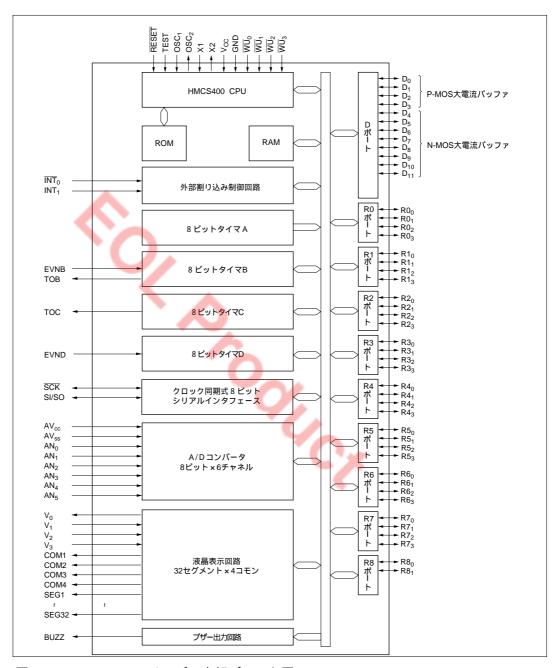

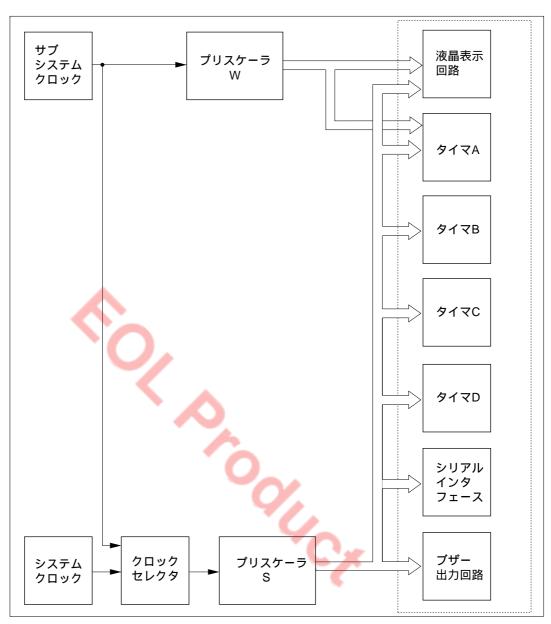

図 1.1 に HD404889 シリーズの内部ブロック図を示します。

図 1.1 HD404889 シリーズの内部ブロック図

## 1.3 端子説明

#### 1.3.1 ピン配置

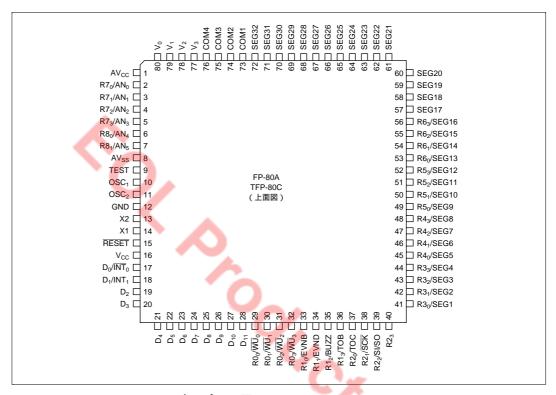

HD404889 シリーズの FP-80A、TFP-80C のピン配置図を図 1.2 に示します。また、表 1.3 にピン配置一覧を示します。

図 1.2 HD404889 シリーズのピン配置図 (FP-80A, TFP-80C)

表 1.3 ピン配置一覧 (1)

| ピン番号    | 端子名                              | 端子機能                         |

|---------|----------------------------------|------------------------------|

| FP-80A  |                                  |                              |

| TFP-80C |                                  |                              |

| 1       | AV <sub>cc</sub>                 | アナログ電源                       |

| 2       | R7 <sub>0</sub> /AN <sub>0</sub> | 入出力ポート / アナログ入力チャネル          |

| 3       | R7₁/AN₁                          | 入出力ポート / アナログ入力チャネル          |

| 4       | R7 <sub>2</sub> /AN <sub>2</sub> | 入出力ポート / アナログ入力チャネル          |

| 5       | R7 <sub>3</sub> /AN <sub>3</sub> | 入出力ポート / アナログ入力チャネル          |

| 6       | R8 <sub>0</sub> /AN <sub>4</sub> | 入出力ポート / アナログ入力チャネル          |

| 7       | R8 <sub>1</sub> /AN <sub>5</sub> | 入出力ポート / アナログ入力チャネル          |

| 8       | AV₅s                             | アナロググランド                     |

| 9       | TEST                             | テスト                          |

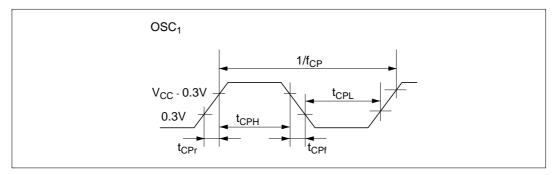

| 10      | OSC <sub>1</sub>                 | システムクロック発振子接続:入力             |

| 11      | OSC <sub>2</sub>                 | システムクロック発振子接続:出力             |

| 12      | GND                              | グランド                         |

| 13      | X2                               | サプシステム発振子接続:出力               |

| 14      | X1                               | サプシステム <mark>発振子接続:入力</mark> |

| 15      | RESET                            | リセット                         |

| 16      | V <sub>cc</sub>                  | 電源                           |

| 17      | D <sub>0</sub> /INT <sub>0</sub> | ソース大電流入出力ポート / 外部割り込み入力      |

| 18      | D <sub>1</sub> /INT <sub>1</sub> | ソース大電流入出力ポート / 外部割り込み入力      |

| 19      | D <sub>2</sub>                   | ソース大電流入出力ポート                 |

| 20      | D <sub>3</sub>                   | ソース大電流入出力ポート                 |

| 21      | D <sub>4</sub>                   | シンク大電流入出力ポート                 |

| 22      | D <sub>5</sub>                   | シンク大電流入出力ポート                 |

| 23      | D <sub>6</sub>                   | シンク大電流入出力ポート                 |

| 24      | D <sub>7</sub>                   | シンク大電流入出力ポート                 |

| 25      | D <sub>8</sub>                   | シンク大電流入出力ポート                 |

| 26      | D <sub>9</sub>                   | シンク大電流入出力ポート                 |

| 27      | D <sub>10</sub>                  | シンク大電流入出力ポート                 |

| 28      | D <sub>11</sub>                  | シンク大電流入出力ポート                 |

| 29      | R0 <sub>0</sub> /WU <sub>0</sub> | 入出力ポート / ウェイクアップ入力           |

| 30      | R0 <sub>1</sub> /WU <sub>1</sub> | 入出力ポート / ウェイクアップ入力           |

表 1.3 ピン配置一覧(2)

| ピン番号    | 端子名                              | 端子機能                    |

|---------|----------------------------------|-------------------------|

| FP-80A  |                                  |                         |

| TFP-80C |                                  |                         |

| 31      | R0 <sub>2</sub> /WU <sub>2</sub> | 入出力ポート / ウェイクアップ入力      |

| 32      | R0 <sub>3</sub> /WU <sub>3</sub> | 入出力ポート / ウェイクアップ入力      |

| 33      | R1 <sub>0</sub> /EVNB            | 入出力ポート / タイマ B イベント入力   |

| 34      | R1₁/EVND                         | 入出力ポート / タイマ D イベント入力   |

| 35      | R1 <sub>2</sub> /BUZZ            | 入出力ポート / ブザー出力          |

| 36      | R1 <sub>3</sub> /TOB             | 入出力ポート / タイマ B 出力       |

| 37      | R2 <sub>0</sub> /TOC             | 入出力ポート / タイマ C 出力       |

| 38      | R2₁/SCK                          | 入出力ポート / シリアル転送クロック入出力  |

| 39      | R2 <sub>2</sub> /SI/SO           | 入出力ポート / シリアルデータ入力 / 出力 |

| 40      | R2 <sub>3</sub>                  | 入出力ポート                  |

| 41      | R3 <sub>0</sub> /SEG1            | 入出力ポート / セグメント信号出力      |

| 42      | R3₁/SEG2                         | 入出力ポート / セグメント信号出力      |

| 43      | R3 <sub>2</sub> /SEG3            | 入出力ポート / セグメント信号出力      |

| 44      | R3 <sub>3</sub> /SEG4            | 入出力ポート / セグメント信号出力      |

| 45      | R4 <sub>0</sub> /SEG5            | 入出力ポート / セグメント信号出力      |

| 46      | R4₁/SEG6                         | 入出力ポート / セグメント信号出力      |

| 47      | R4 <sub>2</sub> /SEG7            | 入出力ポート / セグメント信号出力      |

| 48      | R4 <sub>3</sub> /SEG8            | 入出力ポート / セグメント信号出力      |

| 49      | R5 <sub>0</sub> /SEG9            | 入出力ポート / セグメント信号出力      |

| 50      | R5₁/SEG10                        | 入出力ポート / セグメント信号出力      |

| 51      | R5 <sub>2</sub> /SEG11           | 入出力ポート / セグメント信号出力      |

| 52      | R5 <sub>3</sub> /SEG12           | 入出力ポート / セグメント信号出力      |

| 53      | R6 <sub>0</sub> /SEG13           | 入出力ポート / セグメント信号出力      |

| 54      | R6₁/SEG14                        | 入出力ポート / セグメント信号出力      |

| 55      | R6 <sub>2</sub> /SEG15           | 入出力ポート / セグメント信号出力      |

| 56      | R6 <sub>3</sub> /SEG16           | 入出力ポート / セグメント信号出力      |

| 57      | SEG17                            | セグメント信号出力               |

| 58      | SEG18                            | セグメント信号出力               |

| 59      | SEG19                            | セグメント信号出力               |

| 60      | SEG20                            | セグメント信号出力               |

表 1.3 ピン配置一覧(3)

| ピン番号    | 端子名            | 端子機能      |

|---------|----------------|-----------|

| FP-80A  |                |           |

| TFP-80C |                |           |

| 61      | SEG21          | セグメント信号出力 |

| 62      | SEG22          | セグメント信号出力 |

| 63      | SEG23          | セグメント信号出力 |

| 64      | SEG24          | セグメント信号出力 |

| 65      | SEG25          | セグメント信号出力 |

| 66      | SEG26          | セグメント信号出力 |

| 67      | SEG27          | セグメント信号出力 |

| 68      | SEG28          | セグメント信号出力 |

| 69      | SEG29          | セグメント信号出力 |

| 70      | SEG30          | セグメント信号出力 |

| 71      | SEG31          | セグメント信号出力 |

| 72      | SEG32          | セグメント信号出力 |

| 73      | COM1           | コモン信号出力   |

| 74      | COM2           | コモン信号出力   |

| 75      | сомз           | コモン信号出力   |

| 76      | COM4           | コモン信号出力   |

| 77      | V <sub>3</sub> | 液晶表示回路用電源 |

| 78      | V <sub>2</sub> | 液晶表示回路用電源 |

| 79      | V <sub>1</sub> | 液晶表示回路用電源 |

| 80      | $V_0$          | 液晶表示回路用電源 |

## 1.3.2 端子機能

表 1.4 に端子機能一覧を示します。

表 1.4 端子機能 (1)

| 分類   | 記号                                | 入出力          | 名称および機能                                                                             |

|------|-----------------------------------|--------------|-------------------------------------------------------------------------------------|

| 電源   | V <sub>cc</sub>                   | -            | <u>電源</u>                                                                           |

|      | -                                 |              | システム電源に接続します。                                                                       |

|      | GND                               | -            | <u>グランド</u>                                                                         |

|      |                                   |              | システムグランドに接続します。                                                                     |

|      | AV <sub>cc</sub>                  | -            | アナログ電源                                                                              |

|      |                                   |              | A/D コンバータ用電源端子です。V <sub>cc</sub> 端子にできるかぎり近い                                        |

| 4    |                                   |              | 場所で、V <sub>cc</sub> と同電位になるように接続してください。                                             |

|      | AV <sub>ss</sub>                  | -            | アナロググランド                                                                            |

|      |                                   |              | A/D コンバータ用グランド端子です。 GND 端子にできるかぎり                                                   |

|      |                                   |              | 近い場所で、GND と同電位になるように接続してください。                                                       |

|      | V <sub>0</sub> , V <sub>1</sub> , | ` <u>-</u> / | 液晶表示回路用電源                                                                           |

|      | V <sub>2</sub> , V <sub>3</sub>   |              | 液晶表示回路用電源端子です。電源分割抵抗が内蔵されていま                                                        |

|      |                                   |              | す。                                                                                  |

|      |                                   |              | 電圧条件 <mark>は、V<sub>cc</sub> V<sub>1</sub> V<sub>2</sub> V<sub>3</sub> GNDです。</mark> |

| クロック | OSC <sub>1</sub>                  | 入力           | システムクロック発振子接続端子 1                                                                   |

|      |                                   |              | セラミック発振子、水晶発振子を接続します。または、外部ク                                                        |

|      |                                   |              | ロックを入力することもで <del>き</del> ます。                                                       |

|      |                                   |              | セラミック発振子、水晶発振子を接続する場合、および外部ク                                                        |

|      |                                   |              | ロック入力の場合の接続例については、「第7章 発振回路」                                                        |

|      |                                   |              | を参照してください。                                                                          |

|      | OSC <sub>2</sub>                  | 出力           | システムクロック発振子接続端子 2                                                                   |

|      |                                   |              | セラミック発振子、水晶発振子を接続します。                                                               |

|      |                                   |              | OSC₁端子から外部クロックを入力する場合には、OSC₂端子は                                                     |

|      |                                   |              | 開放にしてください。                                                                          |

|      | X1                                | 入力           | サプシステムクロック発振子接続端子 1                                                                 |

|      |                                   |              | 32.768kHz の水晶発振子を接続します。 サブシステムクロック                                                  |

|      |                                   |              | 発振器を使用しない場合には、V <sub>cc</sub> 電位に固定してください。                                          |

|      | X2                                | 出力           | サブシステムクロック発振子接続端子 2                                                                 |

|      |                                   |              | 32.768kHz の水晶発振子を接続します。 サブシステムクロック                                                  |

|      |                                   |              | 発振器を使用しない場合には、開放としてください。                                                            |

表 1.4 端子機能 (2)

| 分類   | 記号                                | 入出力 | 名称および機能                                |

|------|-----------------------------------|-----|----------------------------------------|

| ポート  | $D_0 \sim D_3$                    | 入出力 | ソース大電流入出力 D ポート                        |

|      |                                   |     | 1 ビットごとにアクセスできる入出力端子です。                |

|      |                                   |     | 最大 10mA のソース電流を各端子に供給できます。             |

|      | D <sub>4</sub> ~ D <sub>11</sub>  | 入出力 | シンク大電流入出力 Dポート                         |

|      |                                   |     | 1 ビットごとにアクセスできる入出力端子です。                |

|      |                                   |     | 最大 15mA のシンク電流を各端子に供給できます。             |

|      | R0 <sub>0</sub> ~ R0 <sub>3</sub> | 入出力 | <u>R0 ポート</u>                          |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R1 <sub>0</sub> ~ R1 <sub>3</sub> | 入出力 | <u>R1 ポート</u>                          |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R2 <sub>0</sub> ~ R2 <sub>3</sub> | 入出力 | R2 ポート                                 |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R3 <sub>0</sub> ~ R3 <sub>3</sub> | 入出力 | <u>R3</u> ポート                          |

|      |                                   | ` / | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R4 <sub>0</sub> ~ R4 <sub>3</sub> | 入出力 | R4 ポート                                 |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R5 <sub>0</sub> ~ R5 <sub>3</sub> | 入出力 | <u>R5 ポート</u>                          |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R6 <sub>0</sub> ~ R6 <sub>3</sub> | 入出力 | R6 ポート                                 |

|      |                                   |     | 4 ビットごとにアク <mark>セスでき</mark> る入出力端子です。 |

|      | R7 <sub>0</sub> ~ R7 <sub>3</sub> | 入出力 | <u>R7 ポート</u>                          |

|      |                                   |     | 4 ビットごとにアクセスできる入出力端子です。                |

|      | R8 <sub>0</sub> , R8 <sub>1</sub> | 入出力 | <u>R8 ポート</u>                          |

|      |                                   |     | 2 ビットごとにアクセスできる入出力端子です。                |

| システム | TEST                              | 入力  | テスト                                    |

| 制御   |                                   |     | 通常は、GND 電位に接続してください。PROM モード設定時        |

|      |                                   |     | に、High レベルとします。                        |

|      |                                   |     | 詳細は、「17.2 PROM モード」を参照してください。          |

|      | RESET                             | 入力  | リセット                                   |

|      |                                   |     | この端子が、Low レベルになるとリセット状態になります。          |

表 1.4 端子機能 (3)

| 分類   | 記号                                     | 入出力 | 名称および機能                                     |

|------|----------------------------------------|-----|---------------------------------------------|

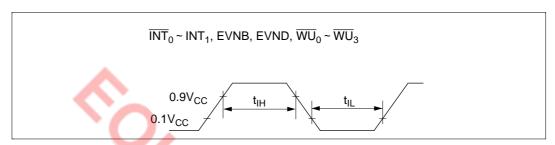

| 割り込み | ĪNT₀, INT₁                             | 入力  | 外部割り込み入力 0、1                                |

|      |                                        |     | INT。は、立ち下がリエッジ検出の外部割り込み入力端子です。              |

|      |                                        |     | INT₁は、立ち下がりエッジ、立ち上がりエッジ、立ち下がり /             |

|      |                                        |     | 立ち上がり両エッジの選択が可能な外部割り込み入力端子で                 |

|      |                                        |     | す。                                          |

| ウェイク | $\overline{WU}_0 \sim \overline{WU}_3$ | 入力  | ウェイクアップ入力0~3                                |

| アップ  |                                        |     | ストップモードおよびウォッチモードを解除するための入力                 |

|      |                                        |     | 端子で、本端子への立ち下がりエッジを検出すると、発振安定                |

|      |                                        |     | 時間を確保してアクティブモードへ遷移します。                      |

| 4    |                                        |     | その他のモードにおいては、立ち下がりエッジ検出の割り込み                |

| · ·  |                                        |     | 入力端子となります。                                  |

| 8ビット | ТОВ                                    | 出力  | タイマB出力                                      |

| タイマ  |                                        |     | タイマBの出力端子です。タイマBオーバフロー時に、トグル                |

|      |                                        | ` / | 出力または PWM 出力を設定できます。                        |

|      | TOC                                    | 出力  | タイマC出力                                      |

|      |                                        |     | タイ <mark>マCの</mark> 出力端子です。タイマCオーバフロー時に、トグル |

|      |                                        |     | 出力、または PWM 出力を設定できます。                       |

|      | EVNB                                   | 入力  | タイマBイベント入力                                  |

|      |                                        |     | タイマ B のイベント入力端子です。外部イベント信号のカウン              |

|      |                                        |     | トは、立ち下がりエッジ、立ち上がりエッジ、立ち下がり/立                |

|      |                                        |     | ち上がり両エッジから選択できます。                           |

|      | EVND                                   | 入力  | タイマロイベント入力                                  |

|      |                                        |     | タイマ D のイベント入力端子です。外部イベント信号のカウン              |

|      |                                        |     | トは、立ち下がりエッジ、立ち上がりエッジ、立ち下がり/立                |

|      |                                        |     | ち上がり両エッジから選択できます。                           |

| シリアル | SCK                                    | 入出力 | シリアル転送クロック入出力                               |

| インタ  |                                        |     | シリアルインタフェースのクロック入出力端子です。                    |

| フェース | SI/SO                                  | 入力/ | シリアルデータ入出力                                  |

|      |                                        | 出力  | シリアルインタフェースのデータ入出力端子です。                     |

表 1.4 端子機能 (4)

| 12 1. 〒 別前 |                                   |     | T                       |

|------------|-----------------------------------|-----|-------------------------|

| 分類         | 記号                                | 入出力 | 名称および機能                 |

| A/D        | AN <sub>0</sub> ~ AN <sub>5</sub> | 入力  | アナログ入力チャネル0~5           |

| コンバータ      |                                   |     | A/D コンバータのアナログ入力端子です。   |

| 液晶表示       | COM1 ~                            | 出力  | <u>コモン信号出力 1 ~ 4</u>    |

| 回路         | COM4                              |     | 液晶表示用コモン信号出力端子です。       |

|            | SEG1~                             | 出力  | <u>セグメント信号出力 1 ~ 32</u> |

|            | SEG32                             |     | 液晶表示用セグメント信号出力端子です。     |

| ブザー出力      | BUZZ                              | 出力  | ブザー出力                   |

|            |                                   |     | ブザー信号出力端子です。            |

|            |                                   |     |                         |

# 2. メモリマップ

# 第2章 目次

| 2.1 | 概要         |                                                      | 19 |

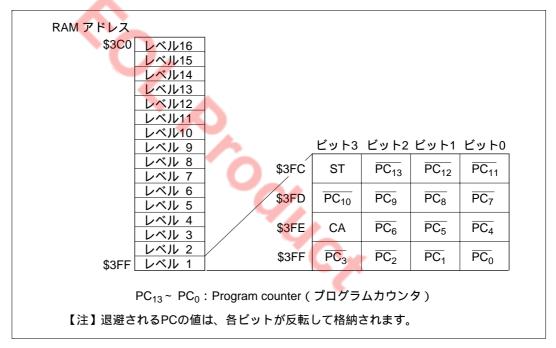

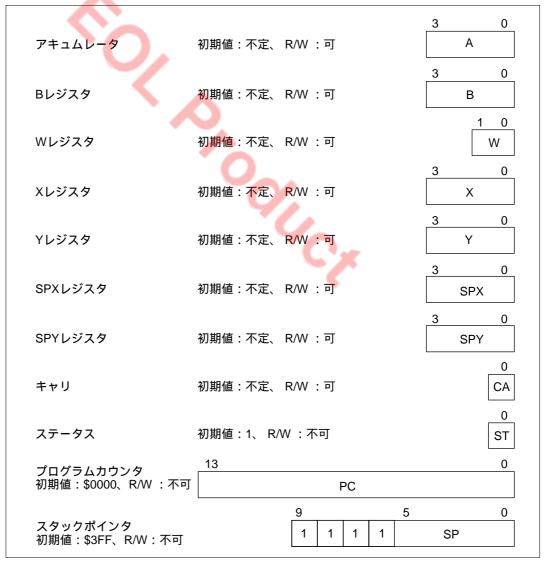

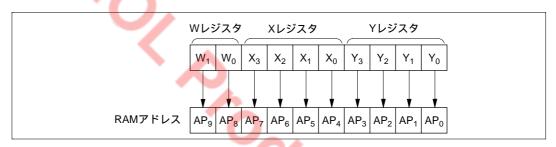

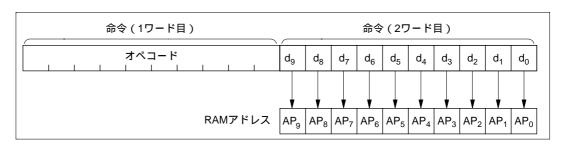

|-----|------------|------------------------------------------------------|----|