## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# H8S/2153 グループ

ハードウェアマニュアル ルネサス16ビットシングルチップマイクロコンピュータ H8S ファミリ/ H8S/2100 シリーズ

H8S/2153 R4F2153

### ■ 本資料ご利用に際しての留意事項。

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10.弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が 発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作 が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において 冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェ ア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システム としての安全検証をお願いいたします。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の 事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、 お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故に つきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会ください。

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザープアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

## 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

## 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品ご使用上の注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュール毎に異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

- 10. 本版で改訂された箇所(改訂版のみ適用)

改定来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改定内容の全てについて記載したものではありませんので、詳細については、本書の本文上で ご確認ください。

11. 索引

## はじめに

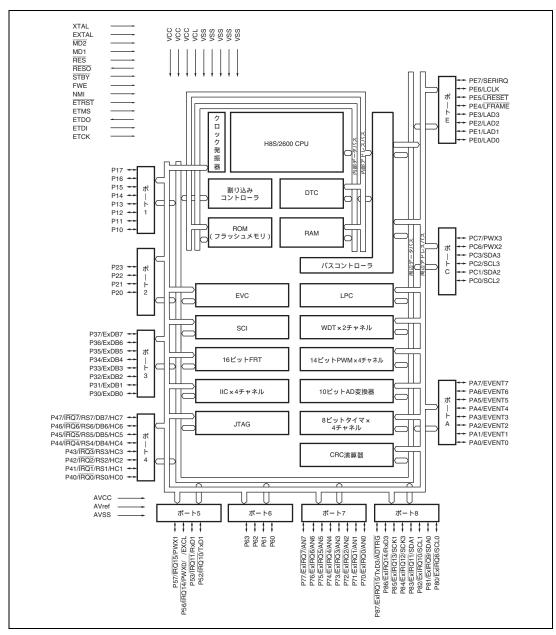

H8S/2153 グループは、ルネサス テクノロジ オリジナルアーキテクチャを採用したH8S/2600 CPU を核にして、システム構成に必要な周辺機能を集積したマイクロコンピュータです。

H8S/2600 CPU は、H8/300CPU および H8/300H CPU の命令に対し、オブジェクトレベルで上位互換を保っていますので、H8/300、H8/300L、H8/300H の各シリーズから容易に移行することができます。

対象者 このマニュアルは、H8S/2153 グループを用いた応用システムを設計するユーザーを対象としています。 このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

目的 このマニュアルは、H8S/2153 グループのハードウェア機能と電気的特性をユーザーに理解して頂くことを目的にしています。なお、実行命令の詳細については、「H8S/2600 シリーズ、H8S/2000 シリーズ ソフトウェアマニュアル」に記載していますので併せて御覧ください。

#### 読み方

• 機能全体を理解しようとするとき。

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき。

別冊の「H8S/2600シリーズ、H8S/2000シリーズ ソフトウェアマニュアル」を参照してください。

• レジスタ名が判っていて、詳細機能を知りたいとき。

本書の後ろに「索引」があります。索引からページ番号を検索してください。

「第23章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

凡例 レジスタ表記 :シリアルコミュニケーションインタフェースなど、同一または類似した機能が複数チ

ャネルに存在する場合に次の表記を使用します。

XXX\_N (XXX は基本レジスタ名称、N はチャネル番号)

ビット表記順 : 左側が上位ビット、右側が下位ビット

数字の表記 : 2 進数は B'xxxx、16 進数は H'xxxx、10 進数は xxxx

信号の表記 : ローアクティブの信号にはオーバーバーを付けます。 xxxx

## 関連資料一覧 ウェブ・サイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://japan.renesas.com/)

## • H8S/2153グループに関するユーザーズマニュアル

| 資料名                                     | 資料番号       |

|-----------------------------------------|------------|

| H8S/2153 グループ ハードウェアマニュアル               | 本マニュアル     |

| H8S/2600 シリーズ、H8S/2000 シリーズ ソフトウェアマニュアル | RJJ09B0143 |

### • 開発ツール関連ユーザーズマニュアル

| 資料名                                                         | 資料番号       |

|-------------------------------------------------------------|------------|

| H8S、H8/300 シリーズ C/C++コンパイラ、アセンブラ、最適化リンケージエディタ<br>ユーザーズマニュアル | RJJ10B0166 |

| H8S、H8/300 シリーズ シミュレータ・デバッガユーザーズマニュアル                       | RJJ10B0219 |

| High-performance Embedded Workshop ユーザーズマニュアル               | RJJ10J2495 |

## • アプリケーションノート

| 資料名                                         | 資料番号            |

|---------------------------------------------|-----------------|

| H8S、H8/300 シリーズ C/C++コンパイラパッケージ アプリケーションノート | RJJ05B0558      |

| H8S シリーズ テクニカル Q&A                          | ADJ - 502 - 065 |

## 目次

| 1. 椎 | 【要                                             | 1-1  |

|------|------------------------------------------------|------|

| 1.1  | 特長                                             | 1-1  |

| 1.2  | ブロック図                                          | 1-3  |

| 1.3  | 端子説明                                           | 1-4  |

| 1.3. | ピン配置図                                          | 1-4  |

| 1.3. | 2 動作モード別ピン配置一覧                                 | 1-5  |

| 1.3. | 3 端子機能                                         | 1-9  |

| 2. 0 | PU                                             | 2-1  |

| 2.1  | 特長                                             | 2-1  |

| 2.1. | 1 H8S/2600 CPU と H8S/2000 CPU との相違点            | 2-2  |

| 2.1. | 2 H8/300 CPU との相違点                             | 2-3  |

| 2.1. | 3 H8/300H CPU との相違点                            | 2-3  |

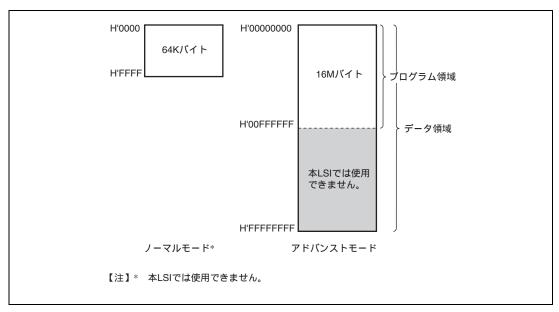

| 2.2  | CPU動作モード                                       | 2-4  |

| 2.2. | I ノーマルモード                                      | 2-4  |

| 2.2. | 2 アドバンストモード                                    | 2-6  |

| 2.3  | アドレス空間                                         | 2-8  |

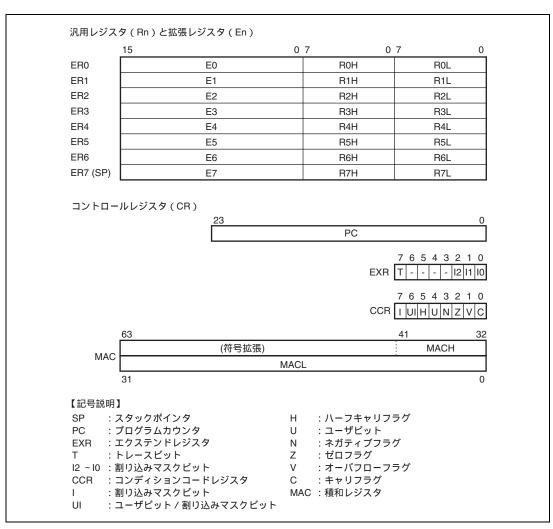

| 2.4  | レジスタの構成                                        | 2-9  |

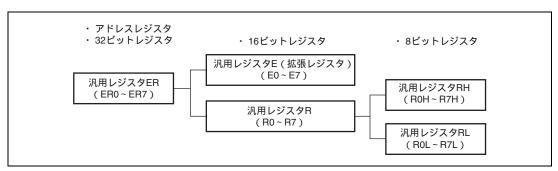

| 2.4. | 1 汎用レジスタ                                       | 2-10 |

| 2.4. | 2 プログラムカウンタ(PC)                                | 2-11 |

| 2.4. | 3 エクステンドレジスタ ( EXR )                           | 2-11 |

| 2.4. | 4 コンディションコードレジスタ(CCR)                          | 2-11 |

| 2.4. | 5                                              | 2-12 |

| 2.4. | 6 CPU 内部レジスタの初期値                               | 2-12 |

| 2.5  | データ形式                                          | 2-13 |

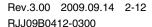

| 2.5. | 1 汎用レジスタのデータ形式                                 | 2-13 |

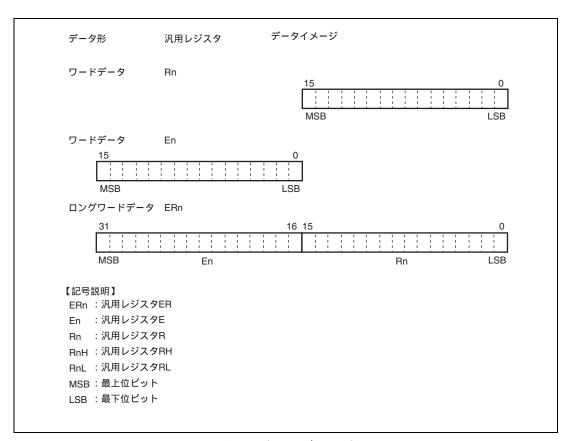

| 2.5. | 2 メモリ上でのデータ形式                                  | 2-15 |

| 2.6  | 命令セット                                          | 2-16 |

| 2.6. | l 命令の機能別一覧                                     | 2-17 |

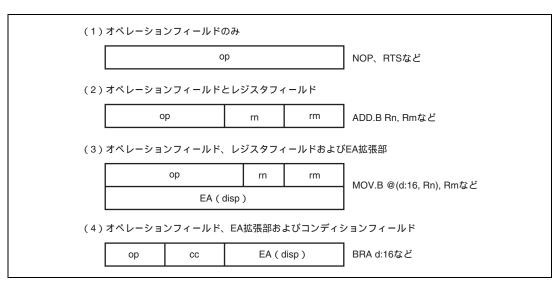

| 2.6. | 2 命令の基本フォーマット                                  | 2-27 |

| 2.7  | アドレッシングモードと実効アドレスの計算方法                         | 2-28 |

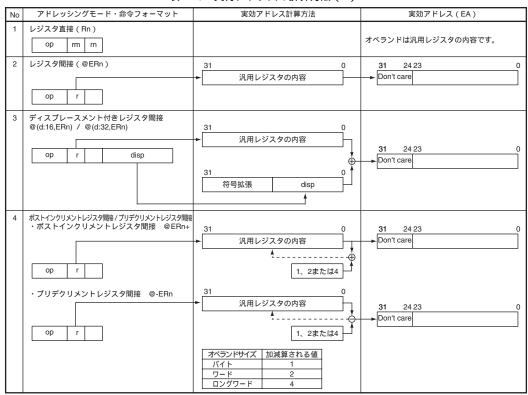

| 2.7. | l レジスタ直接 Rn                                    | 2-28 |

| 2.7. | 2 レジスタ間接 @ERn                                  | 2-28 |

| 2.7. | 3 ディスプレースメント付きレジスタ間接 @ (d:16,ERn)/@ (d:32,ERn) | 2-28 |

| 2.7. | 4 ポストインクリメントレジスタ間接@ERn+/プリデクリメントレジスタ間接@-ERn    | 2-29 |

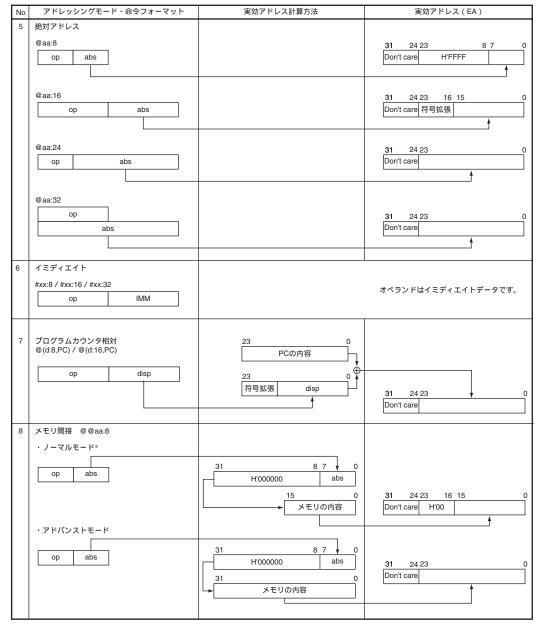

| 2.7.5 | 絶対アドレス @aa:8/@aa:16/@aa:24/@aa:32               | 2-29 |

|-------|-------------------------------------------------|------|

| 2.7.6 | イミディエイト #xx:8/#xx:16/#xx:32                     | 2-30 |

| 2.7.7 | プログラムカウンタ相対 @ (d:8, PC)/@ (d:16, PC)            | 2-30 |

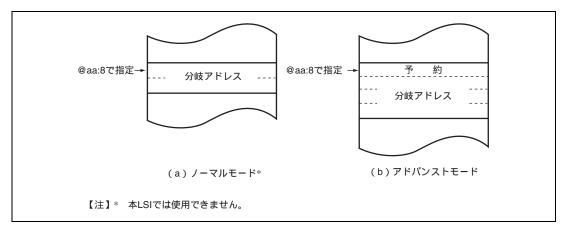

| 2.7.8 | メモリ間接 @@aa:8                                    | 2-30 |

| 2.7.9 | 実効アドレスの計算方法                                     | 2-32 |

| 2.8   | 処理状態                                            | 2-34 |

| 2.9   | 使用上の注意事項                                        | 2-35 |

| 2.9.1 | ビット操作命令                                         | 2-35 |

| 3. MC | CU 動作モード                                        | 3-1  |

| 3.1   | 動作モードの選択                                        | 3-1  |

| 3.2   | レジスタの説明                                         | 3-1  |

| 3.2.1 | モードコントロールレジスタ(MDCR)                             | 3-2  |

| 3.2.2 | システムコントロールレジスタ(SYSCR)                           | 3-2  |

| 3.2.3 | シリアルタイマコントロールレジスタ ( STCR )                      | 3-3  |

| 3.3   | 各動作モードの説明                                       | 3-4  |

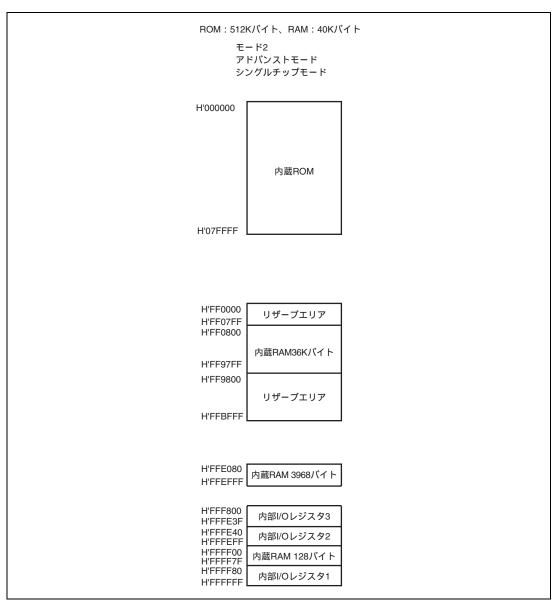

| 3.3.1 | モード 2                                           | 3-4  |

| 3.4   | アドレスマップ                                         | 3-4  |

| 4. 例约 | 小処理                                             | 4-1  |

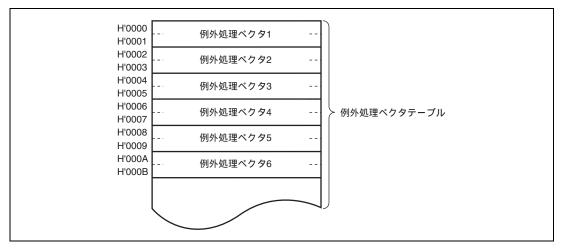

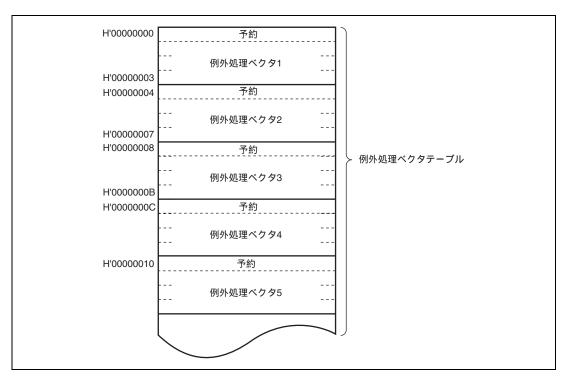

| 4.1   | 例外処理の種類と優先度                                     | 4-1  |

| 4.2   | 例外処理要因とベクタテーブル                                  | 4-1  |

| 4.3   | リセット                                            | 4-3  |

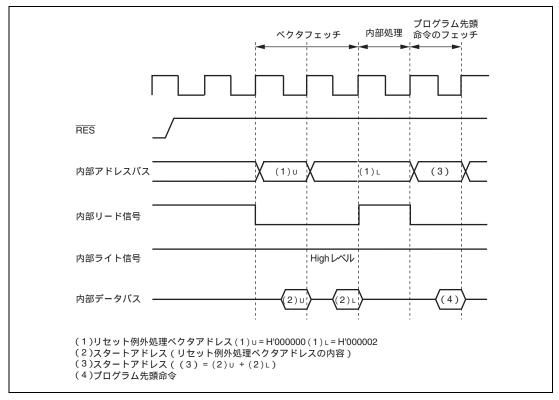

| 4.3.1 | リセット例外処理                                        | 4-3  |

| 4.3.2 | リセット直後の割り込み                                     | 4-4  |

| 4.3.3 | リセット解除後の内蔵周辺機能                                  | 4-4  |

| 4.4   | 割り込み例外処理                                        | 4-4  |

| 4.5   | トラップ命令例外処理                                      | 4-5  |

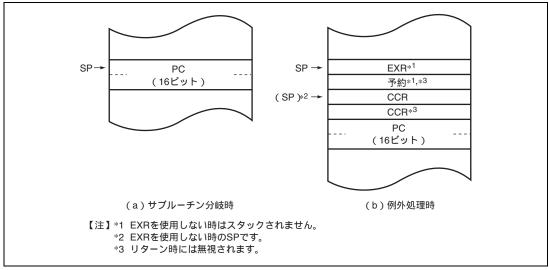

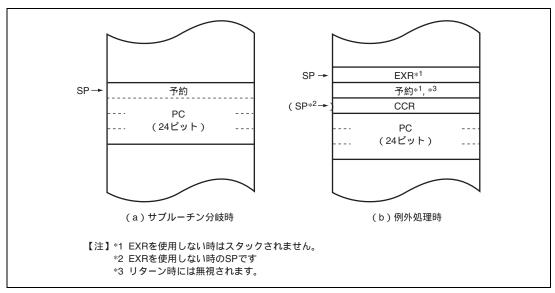

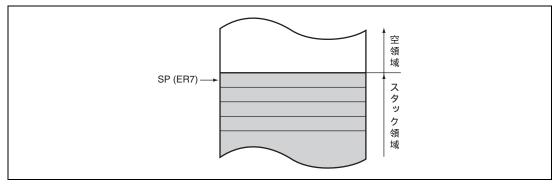

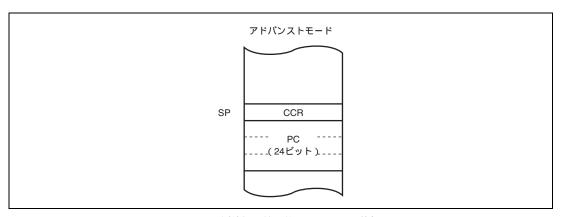

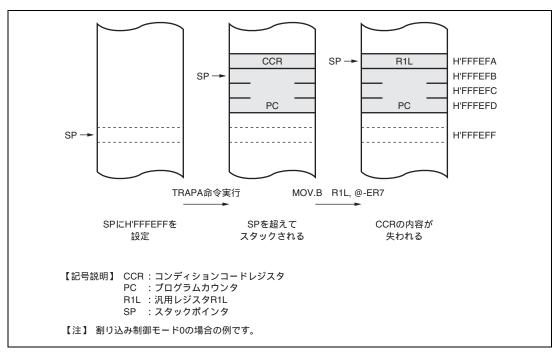

| 4.6   | 例外処理後のスタックの状態                                   | 4-5  |

| 4.7   | 使用上の注意事項                                        | 4-6  |

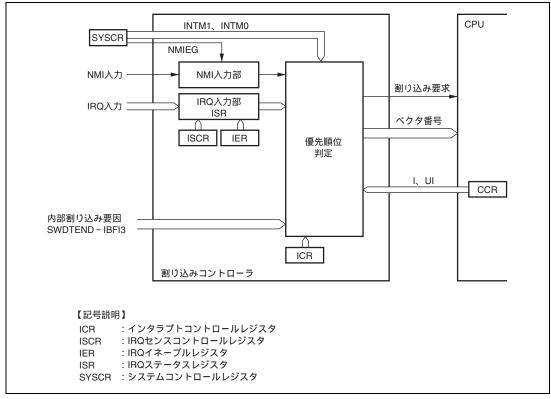

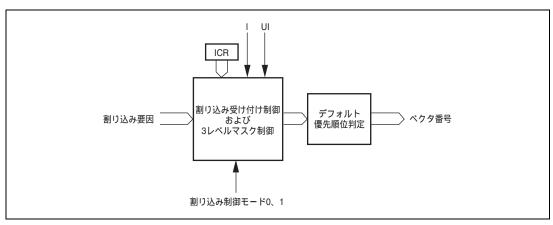

| 5. 割! | 〕込みコントローラ                                       | 5-1  |

| 5.1   | 特長                                              | 5-1  |

| 5.2   | 入出力端子                                           | 5-2  |

| 5.3   | レジスタの説明                                         | 5-3  |

| 5.3.1 | インタラプトコントロールレジスタ A~D(ICRA~ICRD)                 | 5-3  |

| 5.3.2 | アドレスプレークコントロールレジスタ(ABRKCR)                      | 5-4  |

| 5.3.3 | ブレークアドレスレジスタ A~C(BARA~BARC)                     | 5-4  |

| 5.3.4 | IRQ センスコントロールレジスタ (ISCR16H、ISCR16L、ISCRH、ISCRL) | 5-5  |

| 5.3.5 | IRQ イネーブルレジスタ(IER16、IER)                        | 5-7  |

| 5.3.6 | IRQ ステータスレジスタ(ISR16、ISR)                        | 5-8  |

|       |                                                 |      |

| 5.4    | 割り込み要因                             | 5-9  |

|--------|------------------------------------|------|

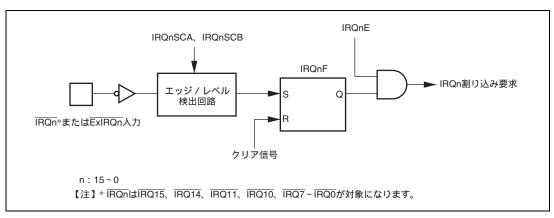

| 5.4.1  | 外部割り込み要因                           | 5-9  |

| 5.4.2  | 内部割り込み要因                           | 5-10 |

| 5.5    | 割り込み例外処理ベクタテーブル                    | 5-10 |

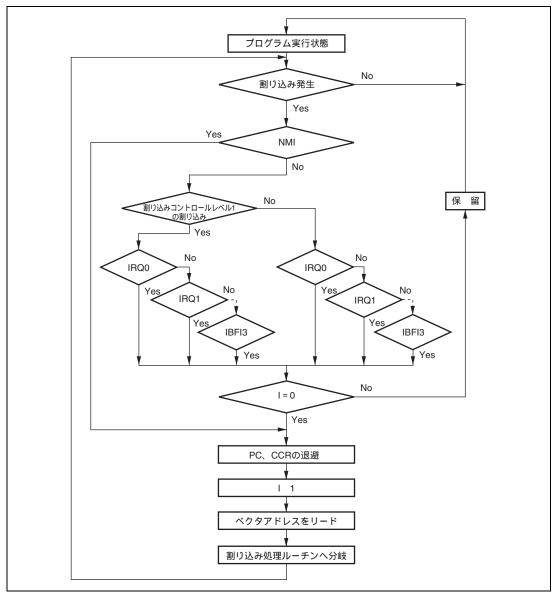

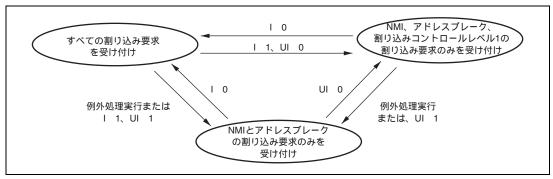

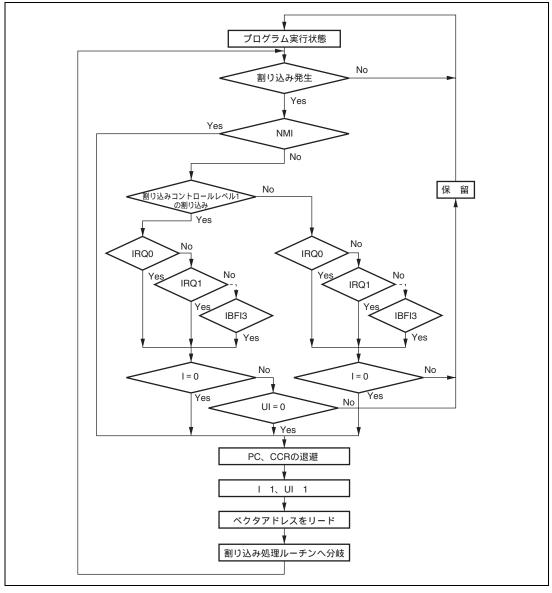

| 5.6    | 割り込み制御モードと割り込み動作                   | 5-12 |

| 5.6.1  | 割り込み制御モード 0                        | 5-14 |

| 5.6.2  | 割り込み制御モード 1                        | 5-16 |

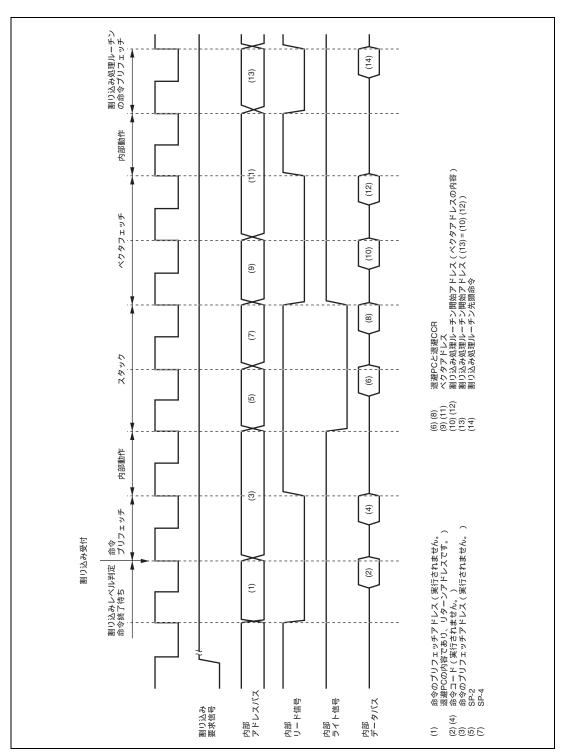

| 5.6.3  | 割り込み例外処理シーケンス                      | 5-18 |

| 5.6.4  | 割り込み応答時間                           | 5-20 |

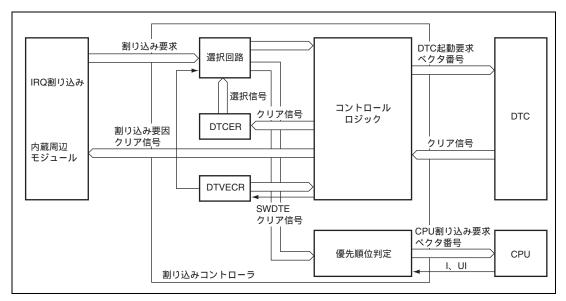

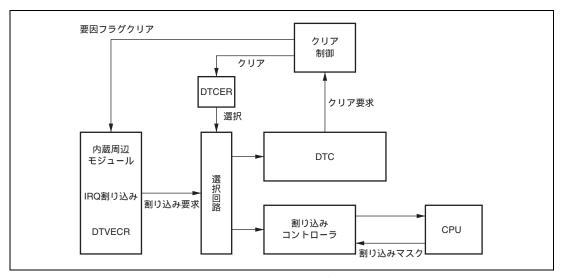

| 5.6.5  | 割り込みによる DTC の起動                    | 5-21 |

| 5.7    | 使用上の注意事項                           | 5-22 |

| 5.7.1  | 割り込みの発生とディスエーブルとの競合                | 5-22 |

| 5.7.2  | 割り込みを禁止している命令                      | 5-23 |

| 5.7.3  | EEPMOV 命令実行中の割り込み                  | 5-23 |

| 5.7.4  | IRQ ステータスレジスタ ( ISR 16、 ISR ) について | 5-23 |

| 6. バス  | スコントローラ(BSC)                       | 6-1  |

| 6.1    | 特長                                 | 6-1  |

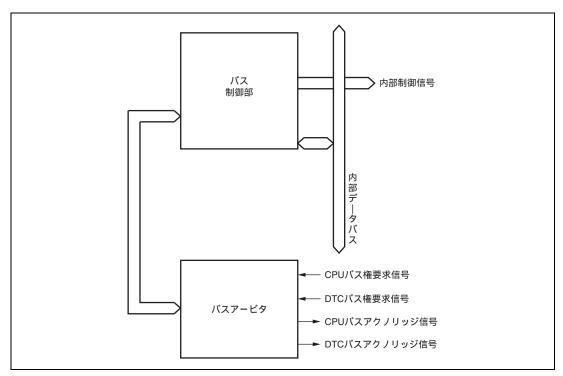

| 6.2    | バスアービトレーション                        | 6-2  |

| 6.2.1  | 概要                                 | 6-2  |

| 6.2.2  | バスマスタの優先順位                         | 6-2  |

| 6.2.3  | バス権移行タイミング                         | 6-2  |

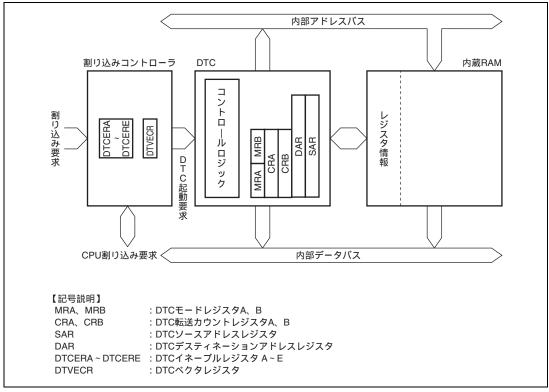

| 7. デ-  | - タトランスファコントローラ(DTC )              | 7-1  |

| 7.1    | 特長                                 | 7-1  |

| 7.2    | レジスタの説明                            |      |

| 7.2.1  | DTC モードレジスタ A(MRA)                 |      |

| 7.2.2  | DTC モードレジスタ B ( MRB )              |      |

| 7.2.3  | DTC ソースアドレスレジスタ(SAR)               |      |

| 7.2.4  | DTC デスティネーションアドレスレジスタ(DAR)         |      |

| 7.2.5  | DTC 転送カウントレジスタ A(CRA)              |      |

| 7.2.6  | DTC 転送カウントレジスタ B(CRB)              |      |

| 7.2.7  | DTC イネーブルレジスタ ( DTCER )            |      |

| 7.2.8  | DTC ベクタレジスタ ( DTVECR )             | 7-7  |

| 7.2.9  | キーボードコンパレータコントロールレジスタ(KBCOMP)      |      |

| 7.2.10 |                                    |      |

| 7.2.11 |                                    |      |

| 7.3    | DTCイベントカウンタ                        |      |

| 7.3.1  | イベントカウンタ処理の優先順位                    | 7-10 |

| 7.3.2  | 使用上の注意事項                           | 7-10 |

| 7.4    | 起動要因                               | 7-11 |

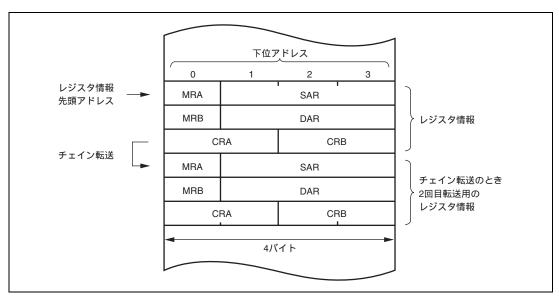

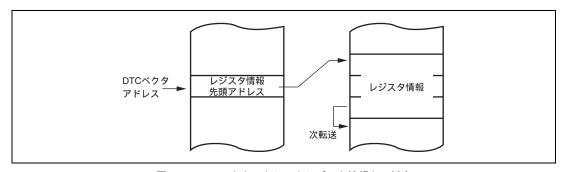

| レジスタ情報の配置とDTCベクタテーブル                  | 7-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

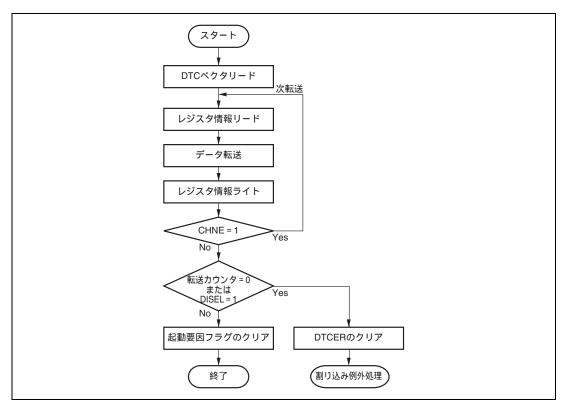

| 動作説明                                  | 7-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

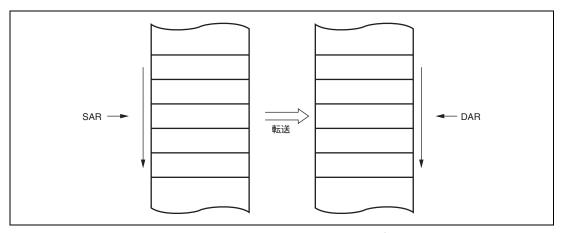

| ノーマル転送モード                             | 7-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

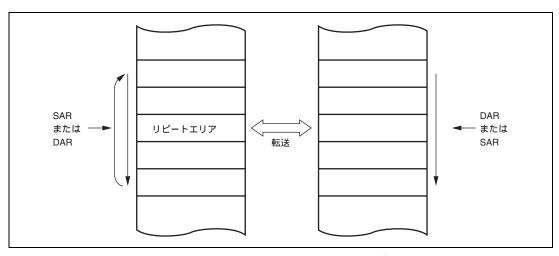

| リピート転送モード                             | 7-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

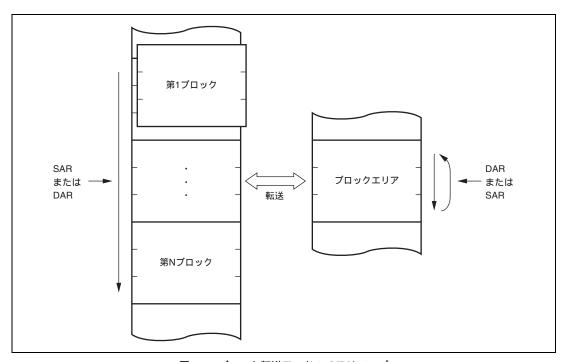

| ブロック転送モード                             | 7-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

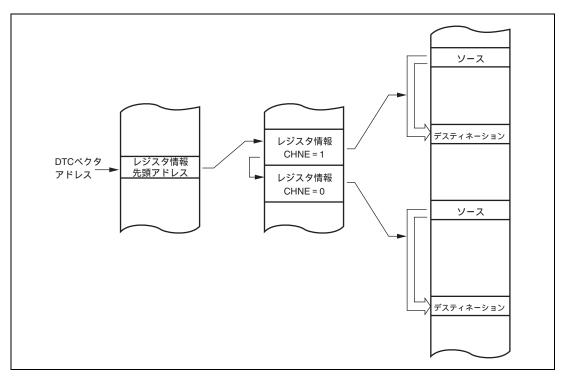

| チェイン転送                                | 7-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 割り込み要因                                | 7-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

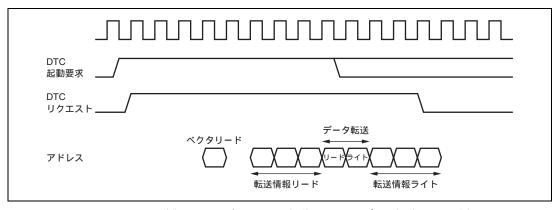

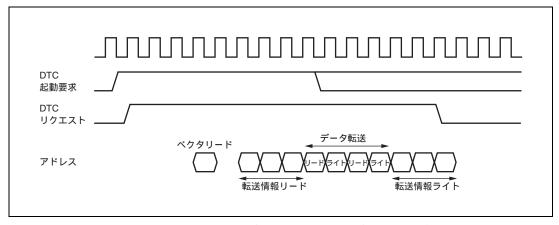

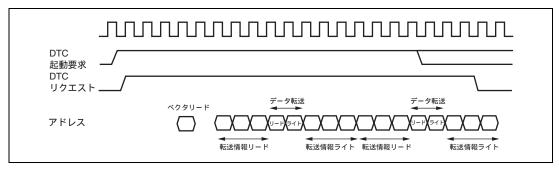

| 動作タイミング                               | 7-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTC 実行ステート数                           | 7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTC使用手順                               | 7-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 割り込みによる起動                             | 7-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ソフトウェアによる起動                           | 7-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTC使用例                                | 7-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ノーマル転送モード                             | 7-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ソフトウェア起動                              | 7-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 使用上の注意事項                              | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| モジュールストップモードの設定                       | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 内蔵 RAM                                | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTCE ビットの設定                           | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCI、IIC および A/D 変換器の割り込み要因による DTC の起動 | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ポート                                   | 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート1                                  | 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 1 データディレクションレジスタ(PIDDR)           | 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 1 データレジスタ(PIDR)                   | 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 1 プルアップ MOS コントロールレジスタ(PIPCR )    | 8-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 1 入力プルアップ MOS の状態                 | 8-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート2                                  | 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 2 データディレクションレジスタ(P2DDR)           | 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 2 データレジスタ(P2DR)                   | 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 2 プルアップ MOS コントロールレジスタ(P2PCR)     | 8-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 2 入力プルアップ MOS の状態                 | 8-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート3                                  | 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 3 データディレクションレジスタ(P3DDR)           | 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 3 データレジスタ ( P3DR )                | 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ポート 3 プルアップ MOS コントロールレジスタ ( P3PCR )  | 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

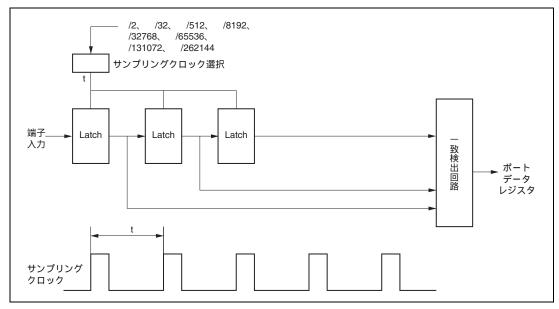

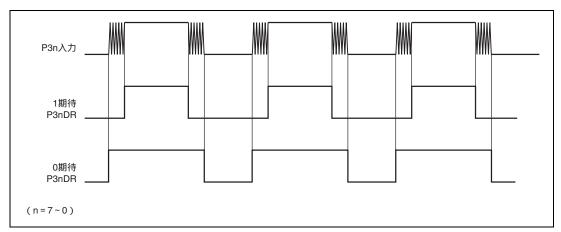

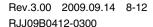

| ノイズキャンセライネーブルレジスタ(P3NCE)              | 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ノイズキャンセラモードコントロールレジスタ(P3NCMC)         | 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ノイズキャンセル周期設定レジスタ(NCCS)                | 8-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 端子機能                                  | 8-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                       | ノーマル転送モード リピート転送モード ブロック転送モード チェイン転送 割り込み要因 動作タイミング DTC 実行ステート数 DTC使用手順 割り込みによる起動 ソフトウェアによる起動 ソフトウェアによる起動  DTC使用例  イーマル転送モード ソフトウェア起動 使用上の注意事項 モジュールストップモードの設定 内蔵 RAM DTCE ピットの設定 SCI、IIC および A/D 変換器の割り込み要因による DTC の起動 ボート ボート1 ボート1 データディレクションレジスタ (PIDDR) ボート1 ブルアップ MOS コントロールレジスタ (PIPCR) ボート1 ブルアップ MOS の状態 ボート2 ボート2 データディレクションレジスタ (P2DR) ボート2 ブルアップ MOS コントロールレジスタ (P2DDR) ボート2 ブルアップ MOS コントロールレジスタ (P2DDR) ボート2 ブルアップ MOS の状態 ボート3 ボート3 データレジスタ (P3DR) ボート3 データディレクションレジスタ (P3DR) ボート3 データティレクションレジスタ (P3DR) ボート3 データティレクションレジスタ (P3DR) ボート3 データティレクションレジスタ (P3DR) ボート3 データレジスタ (P3DR) ボート3 データレジスタ (P3DR) ボート3 データレジスタ (P3DR) バート3 ブルアップ MOS コントロールレジスタ (P3DCR) ノイズキャンセライネーブルレジスタ (P3NCCE) ノイズキャンセラモードコントロールレジスタ (P3NCMC) |

| 8.4    | ポート4                              | 8-12 |

|--------|-----------------------------------|------|

| 8.4.1  | ポート 4 データディレクションレジスタ(P4DDR)       | 8-12 |

| 8.4.2  | ポート 4 データレジスタ(P4DR)               | 8-12 |

| 8.4.3  | ポート 4 プルアップ MOS コントロールレジスタ(P4PCR) | 8-13 |

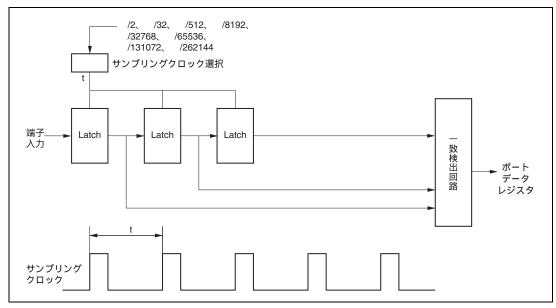

| 8.4.4  | ノイズキャンセライネーブルレジスタ(P4NCE)          | 8-13 |

| 8.4.5  | ノイズキャンセラモードコントロールレジスタ(P4NCMC)     | 8-13 |

| 8.4.6  | ノイズキャンセル周期設定レジスタ(NCCS)            | 8-14 |

| 8.4.7  | 端子機能                              | 8-15 |

| 8.5    | ポート5                              | 8-16 |

| 8.5.1  | ポート 5 データディレクションレジスタ ( P5DDR )    | 8-16 |

| 8.5.2  | ポート 5 データレジスタ ( P5DR )            | 8-16 |

| 8.5.3  | 端子機能                              | 8-17 |

| 8.6    | ポート6                              | 8-19 |

| 8.6.1  | ポート 6 データディレクションレジスタ ( P6DDR )    | 8-19 |

| 8.6.2  | ポート 6 データレジスタ ( P6DR )            | 8-19 |

| 8.6.3  | ポート 6 プルアップ MOS コントロールレジスタ(P6PCR) | 8-20 |

| 8.6.4  | ポート 6 入力プルアップ MOS の状態             | 8-20 |

| 8.7    | ポート7                              | 8-21 |

| 8.7.1  | ポート 7 入力データレジスタ ( P7PIN )         | 8-21 |

| 8.7.2  | 端子機能                              | 8-21 |

| 8.8    | ポート8                              | 8-26 |

| 8.8.1  | ポート 8 データディレクションレジスタ ( P8DDR )    | 8-26 |

| 8.8.2  | ポート 8 データレジスタ ( P8DR )            | 8-26 |

| 8.8.3  | 端子機能                              | 8-27 |

| 8.9    | ポートA                              | 8-30 |

| 8.9.1  | ポート A データディレクションレジスタ(PADDR)       | 8-30 |

| 8.9.2  | ポート A 出力データレジスタ(PAODR)            | 8-30 |

| 8.9.3  | ポート A 入力データレジスタ(PAPIN)            | 8-31 |

| 8.9.4  | 端子機能                              | 8-31 |

| 8.9.5  | 入力プルアップ MOS                       | 8-32 |

| 8.10   | ポートC                              | 8-33 |

| 8.10.1 | ポート C データディレクションレジスタ ( PCDDR )    | 8-33 |

| 8.10.2 | ポート C 出力データレジスタ(PCODR)            | 8-33 |

| 8.10.3 | ポート C 入力データレジスタ(PCPIN)            | 8-34 |

| 8.10.4 | 端子機能                              | 8-34 |

| 8.11   | ポートE                              |      |

| 8.11.1 | ポート E データディレクションレジスタ(PEDDR)       | 8-36 |

| 8.11.2 | ポート E 出力データレジスタ(PEODR)            | 8-36 |

| 8.11.3 | ポート E 入力データレジスタ(PEPIN)            | 8-37 |

| 8.11.4 | 端子機能                              | 8-37 |

| 8.12   | 周辺機能端子の移動                         | 8-40 |

| 8.12.1 | IRQ センスポートセレクトレジスタ 16 ( ISSR16 ) 、       |       |

|--------|------------------------------------------|-------|

|        | IRQ センスポートセレクトレジスタ(ISSR)                 | 8-40  |

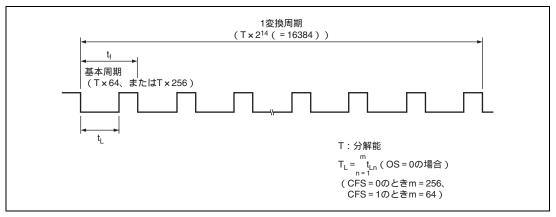

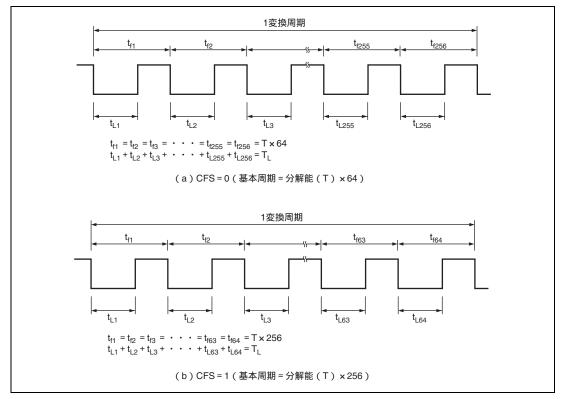

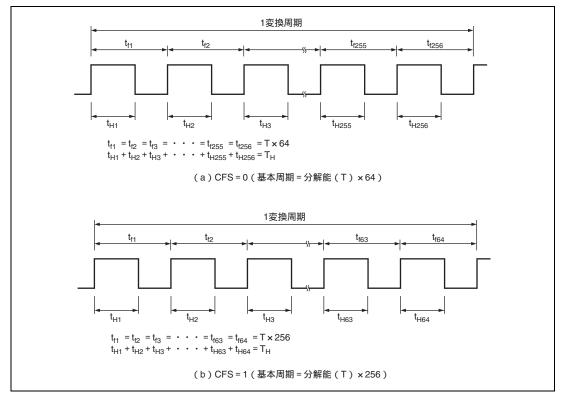

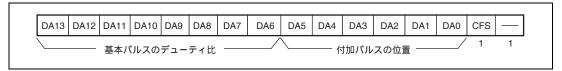

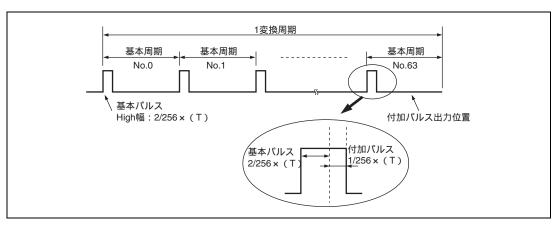

| 9. 14  | ビット PWM タイマ ( PWMX )                     | 9-1   |

| 9.1    | 特長                                       | 9-1   |

| 9.2    | 入出力端子                                    | 9-2   |

| 9.3    | レジスタの説明                                  | 9-3   |

| 9.3.1  | PWMX ( D/A ) カウンタ ( DACNT )              | 9-3   |

| 9.3.2  | PWMX ( D/A ) データレジスタ A、B ( DADRA、DADRB ) | 9-4   |

| 9.3.3  | PWMX ( D/A ) コントロールレジスタ ( DACR )         | 9-6   |

| 9.3.4  | 周辺クロックセレクトレジスタ(PCSR)                     | 9-7   |

| 9.4    | バスマスタとのインタフェース                           | 9-8   |

| 9.5    | 動作説明                                     | 9-9   |

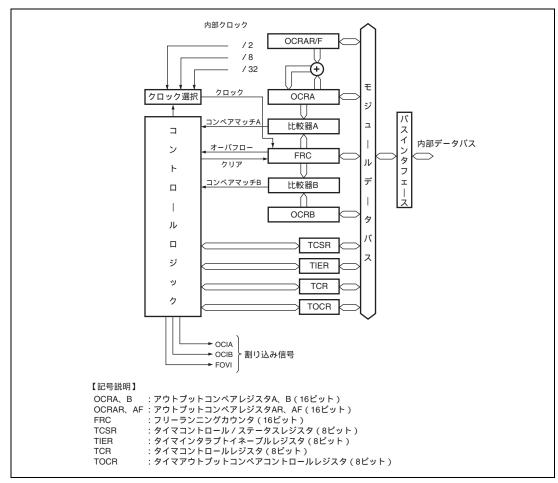

| 10. 16 | ビットフリーランニングタイマ(FRT)                      | 10-1  |

| 10.1   | 特長                                       | 10-1  |

| 10.2   | レジスタの説明                                  | 10-3  |

| 10.2.1 | フリーランニングカウンタ(FRC)                        | 10-3  |

| 10.2.2 | アウトプットコンペアレジスタ A、B(OCRA、OCRB)            | 10-3  |

| 10.2.3 | アウトプットコンペアレジスタ AR、AF ( OCRAR、OCRAF )     | 10-3  |

| 10.2.4 | タイマインタラプトイネーブルレジスタ(TIER)                 | 10-4  |

| 10.2.5 | タイマコントロール / ステータスレジスタ ( TCSR )           | 10-5  |

| 10.2.6 | タイマコントロールレジスタ(TCR)                       | 10-6  |

| 10.2.7 | タイマアウトプットコンペアコントロールレジスタ ( TOCR )         | 10-6  |

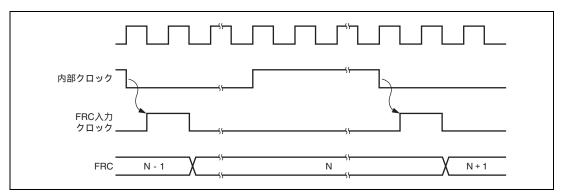

| 10.3   | 動作タイミング                                  | 10-7  |

| 10.3.1 | FRC のカウントタイミング                           | 10-7  |

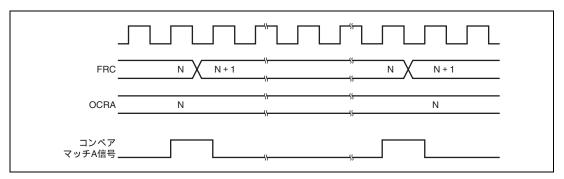

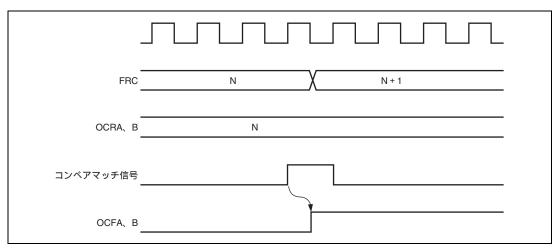

| 10.3.2 | アウトプットコンペア出力タイミング                        | 10-7  |

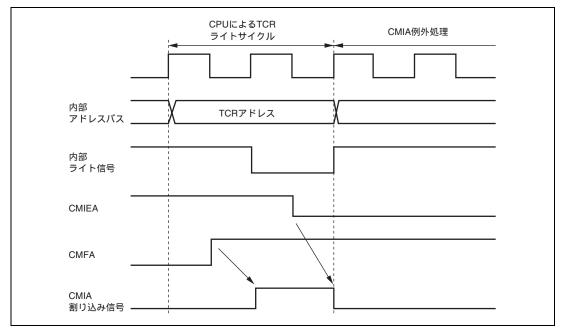

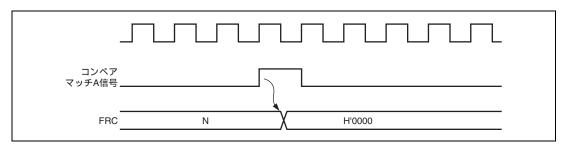

| 10.3.3 | FRC のクリアタイミング                            | 10-8  |

| 10.3.4 | アウトプットコンペア時のフラグセットタイミング                  | 10-8  |

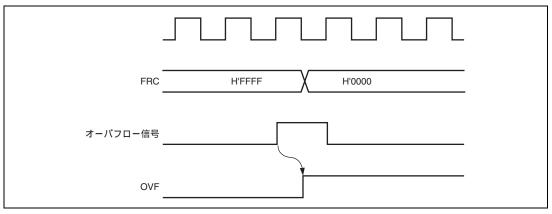

| 10.3.5 | オーバフロー時のフラグセットタイミング                      | 10-9  |

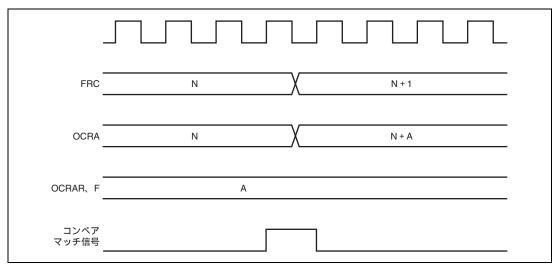

| 10.3.6 | 自動加算タイミング                                | 10-9  |

| 10.4   | 割り込み要因                                   | 10-10 |

| 10.5   | 使用上の注意事項                                 | 10-10 |

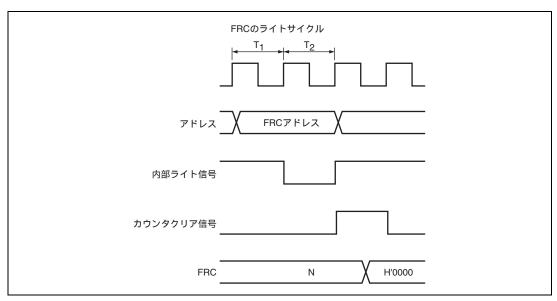

| 10.5.1 | FRC のライトとクリアの競合                          | 10-10 |

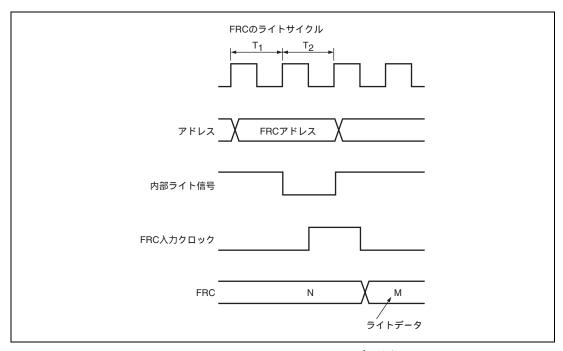

| 10.5.2 | FRC のライトとカウントアップの競合                      | 10-11 |

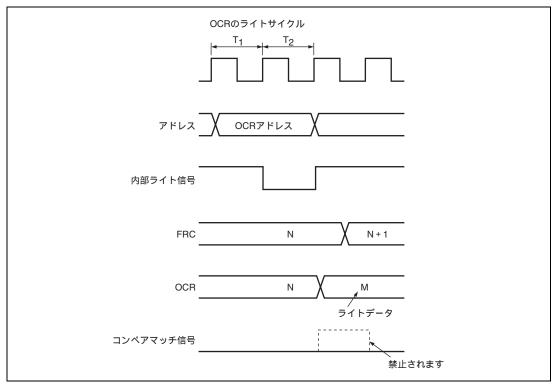

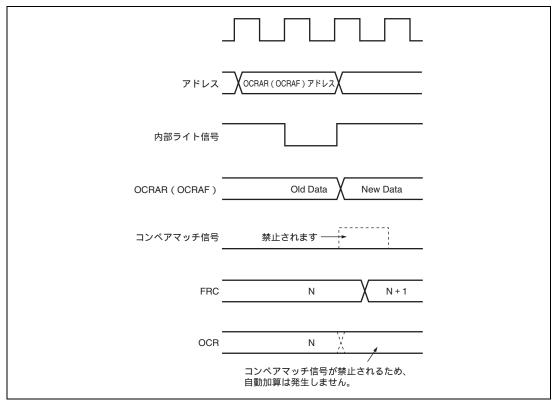

| 10.5.3 | OCR のライトとコンペアマッチの競合                      |       |

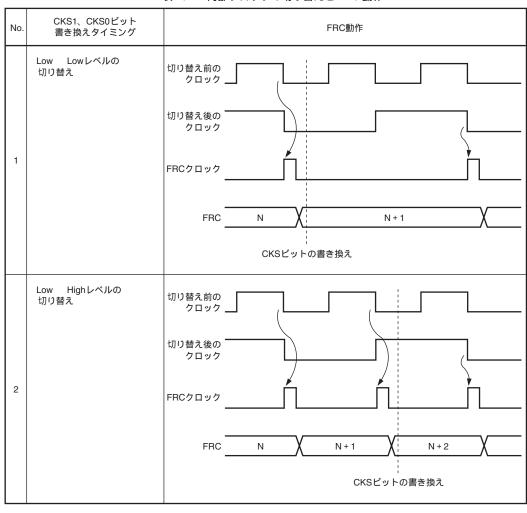

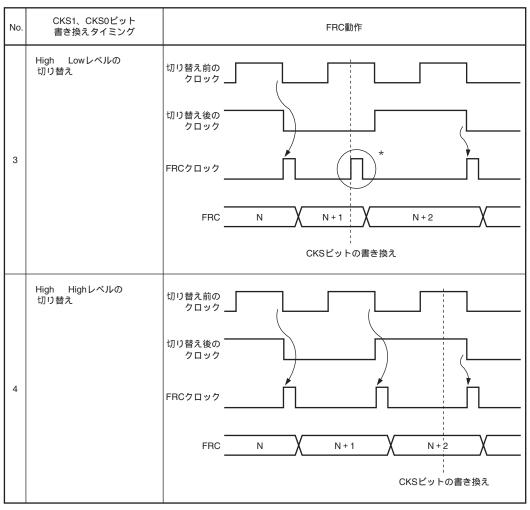

| 10.5.4 | 内部クロックの切り替えとカウンタの動作                      | 10-14 |

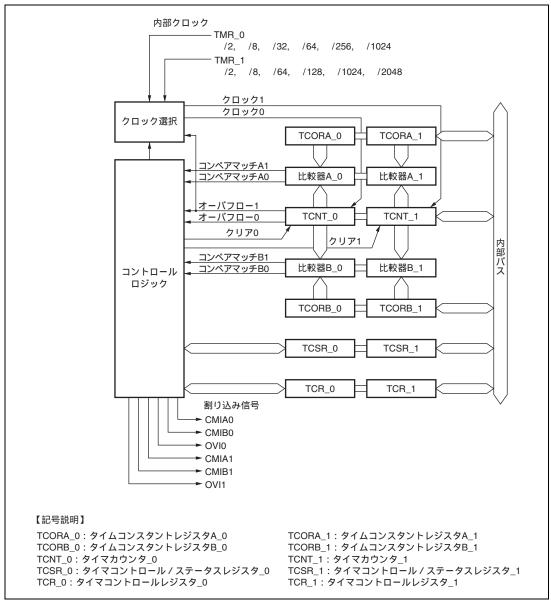

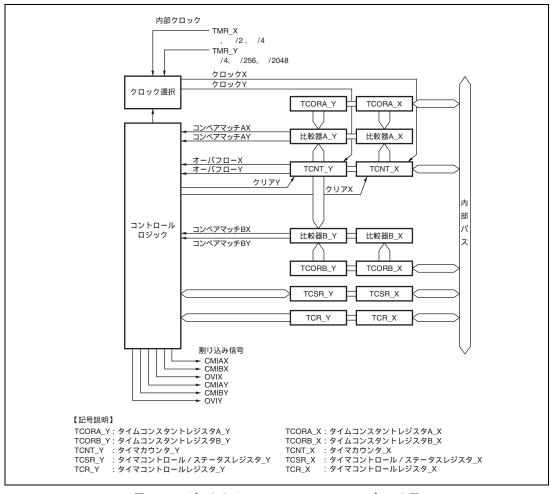

| 11. 8ピ | 「ットタイマ(TMR)                              | 11-1  |

| 11.1   | 特長                                       | 11-1  |

| 11.2   | レジスタの説明                                  | 11-4  |

| 11.2.1         | タイマカウンタ(TCNT)                    | 11-4  |

|----------------|----------------------------------|-------|

| 11.2.2         | タイムコンスタントレジスタ A ( TCORA )        | 11-4  |

| 11.2.3         | タイムコンスタントレジスタ B ( TCORB )        | 11-5  |

| 11.2.4         | タイマコントロールレジスタ ( TCR )            | 11-5  |

| 11.2.5         | タイマコントロール / ステータスレジスタ ( TCSR )   | 11-8  |

| 11.2.6         | タイマコネクションレジスタ S ( TCONRS )       | 11-10 |

| 11.3           | 動作タイミング                          | 11-11 |

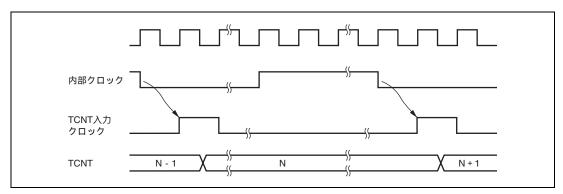

| 11.3.1         | TCNT のカウントタイミング                  | 11-11 |

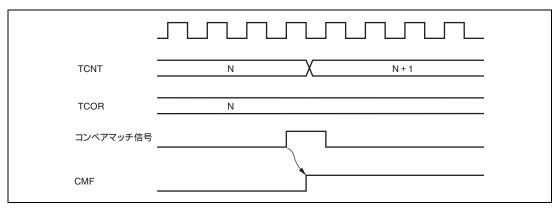

| 11.3.2         | コンペアマッチ時の CMFA、CMFB フラグのセットタイミング | 11-12 |

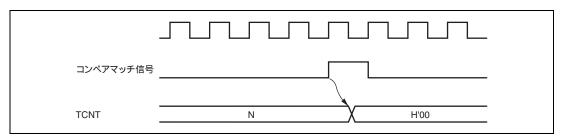

| 11.3.3         | コンペアマッチによるカウンタクリアタイミング           | 11-12 |

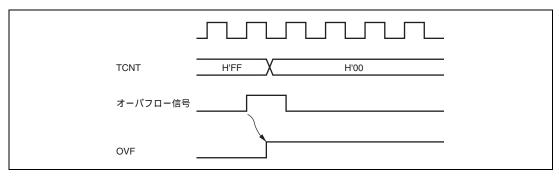

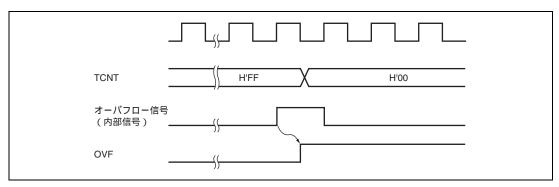

| 11.3.4         | オーバフローフラグ(OVF)のセットタイミング          | 11-13 |

| 11.4           | TMR_0、TMR_1のカスケード接続              | 11-13 |

| 11.4.1         | 16 ビットカウントモード                    | 11-13 |

| 11.4.2         | コンペアマッチカウントモード                   | 11-14 |

| 11.5           | 割り込み要因                           | 11-14 |

| 11.6           | 使用上の注意事項                         | 11-15 |

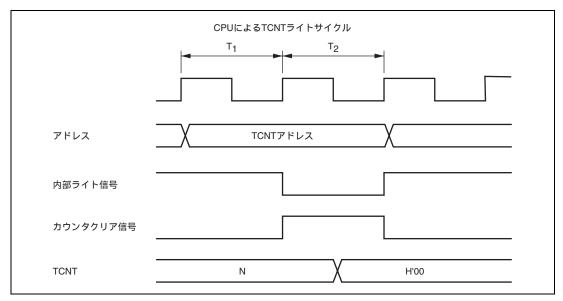

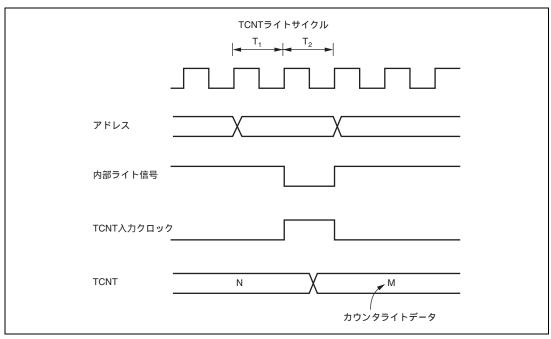

| 11.6.1         | TCNT のライトとカウンタクリアの競合             | 11-15 |

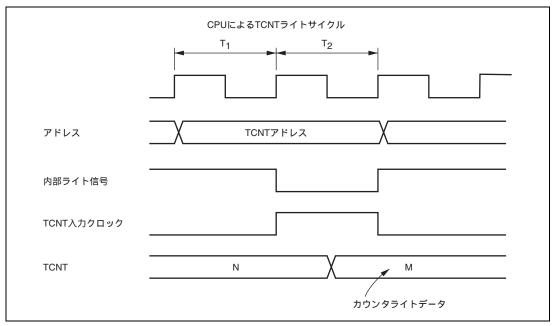

| 11.6.2         | TCNT のライトとカウントアップの競合             | 11-16 |

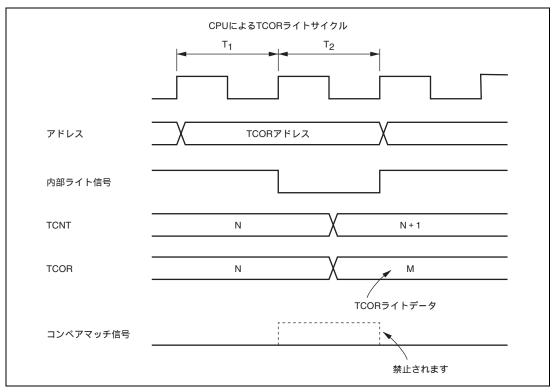

| 11.6.3         | TCOR のライトとコンペアマッチの競合             | 11-17 |

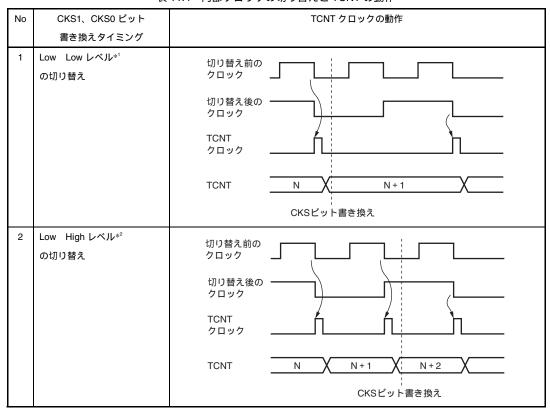

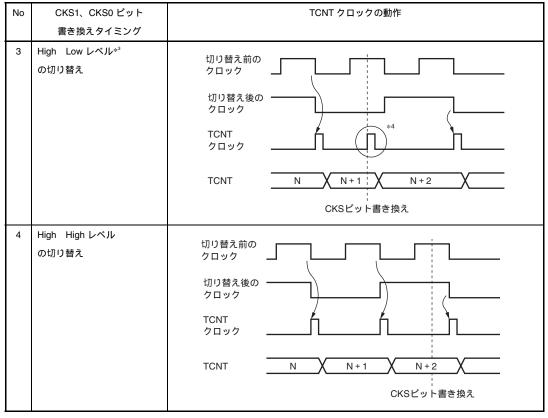

| 11.6.4         | 内部クロックの切り替えと TCNT の動作            | 11-18 |

| 11.6.5         | カスケード接続時のモード設定                   | 11-19 |

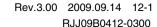

| 12 ウォ          | ッチドッグタイマ(WDT)                    | 12-1  |

|                |                                  |       |

| 12.1           | 特長                               |       |

| 12.2           | 入出力端子                            |       |

| 12.3           | レジスタの説明                          |       |

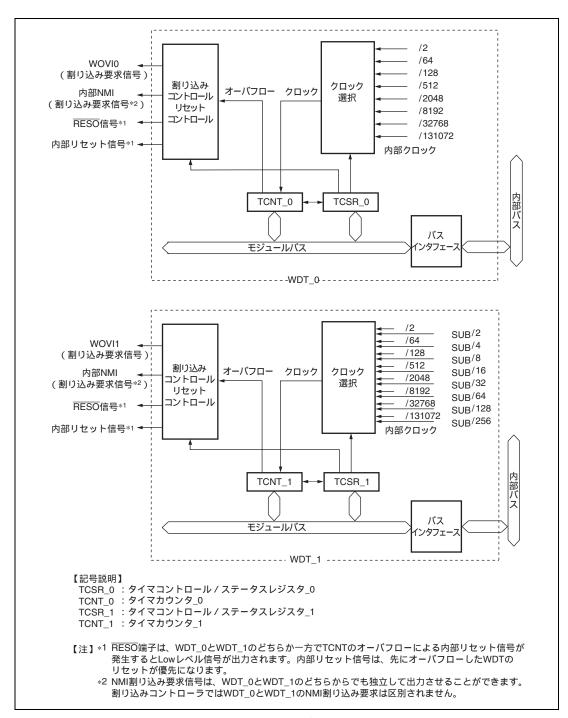

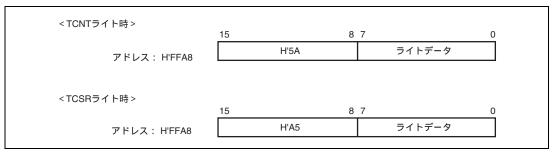

| 12.3.1         | タイマカウンタ(TCNT)                    |       |

| 12.3.2         | タイマコントロール / ステータスレジスタ ( TCSR )   |       |

| 12.4           | 動作説明                             |       |

| 12.4.1         | ウォッチドッグタイマモード                    |       |

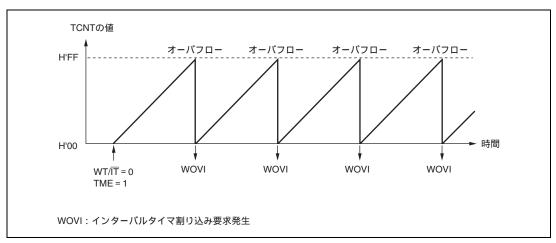

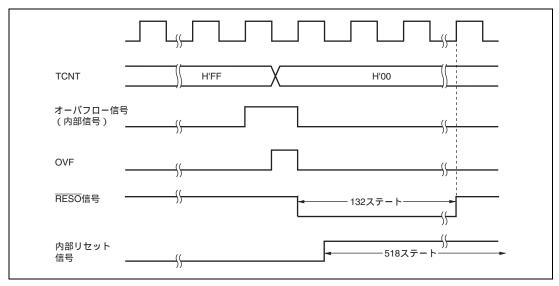

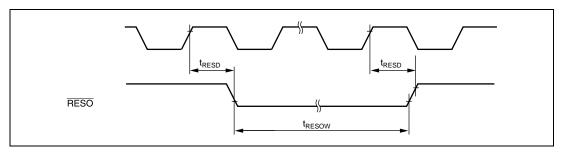

| 12.4.2         | インターバルタイマモード<br>RESO 信号出力タイミング   |       |

| 12.4.3<br>12.5 | 割り込み要因                           |       |

|                | 使用上の注意事項                         |       |

| 12.6           |                                  |       |

| 12.6.1         | レジスタアクセス時の注意事項                   |       |

| 12.6.2         | タイマカウンタ(TCNT)のライトとカウントアップの競合     |       |

| 12.6.3         | CKS2~CKS0 ビットの書き換え               |       |

| 12.6.4         | PSS ビットの書き換え                     |       |

| 12.6.5         | ウォッチドッグタイマモードとインターバルタイマモードの切り替え  |       |

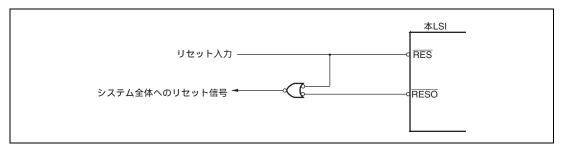

| 12.6.6         | RESO 信号によるシステムのリセット              | 12-12 |

| 13. シリ | Jアルコミュニケーションインタフェース (SCI)               | 13-1  |

|--------|-----------------------------------------|-------|

| 13.1   | 特長                                      | 13-1  |

| 13.2   | 入出力端子                                   | 13-3  |

| 13.3   | レジスタの説明                                 | 13-3  |

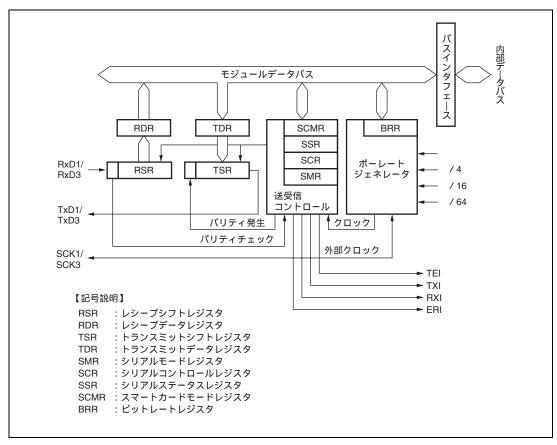

| 13.3.1 | レシープシフトレジスタ ( RSR )                     | 13-4  |

| 13.3.2 | レシープデータレジスタ ( RDR )                     | 13-4  |

| 13.3.3 | トランスミットデータレジスタ(TDR)                     | 13-4  |

| 13.3.4 | トランスミットシフトレジスタ(TSR)                     | 13-4  |

| 13.3.5 | シリアルモードレジスタ(SMR)                        | 13-5  |

| 13.3.6 | シリアルコントロールレジスタ ( SCR )                  | 13-7  |

| 13.3.7 | シリアルステータスレジスタ(SSR)                      | 13-9  |

| 13.3.8 | スマートカードモードレジスタ(SCMR)                    | 13-13 |

| 13.3.9 | ビットレートレジスタ (BRR)                        | 13-14 |

| 13.4   | 調歩同期式モードの動作                             | 13-18 |

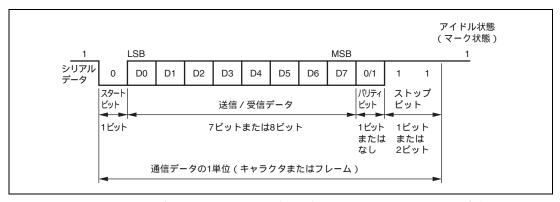

| 13.4.1 | 送受信フォーマット                               | 13-19 |

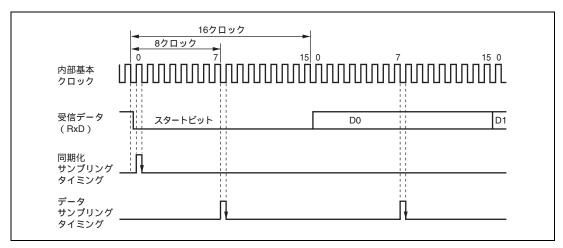

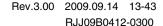

| 13.4.2 | 調歩同期式モードの受信データサンプリングタイミングと受信マージン        | 13-20 |

| 13.4.3 | クロック                                    | 13-21 |

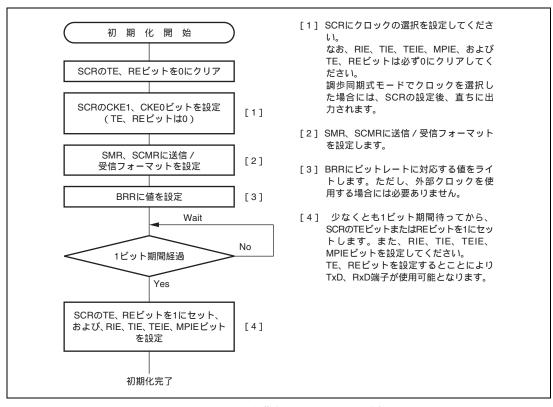

| 13.4.4 | SCI の初期化(調歩同期式)                         | 13-22 |

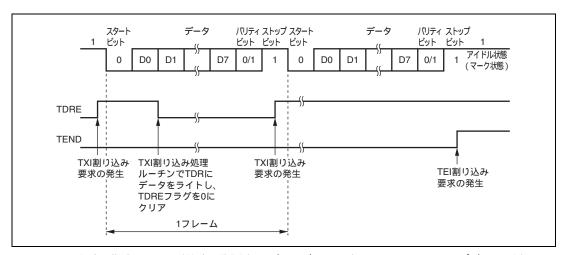

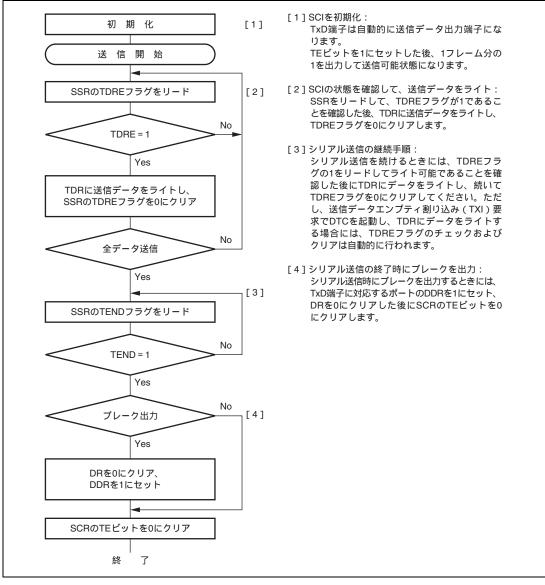

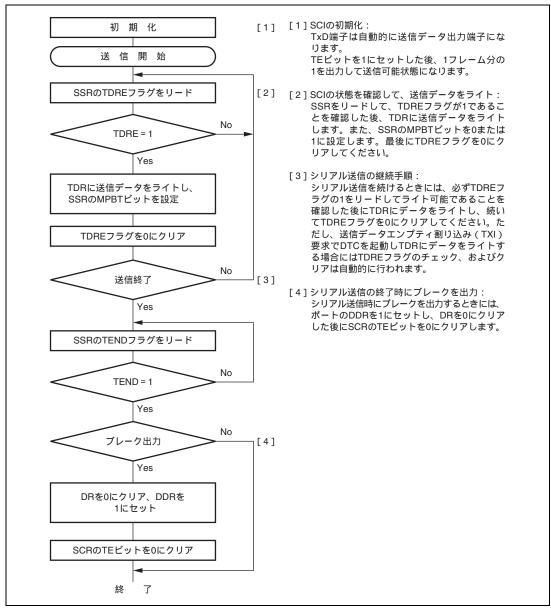

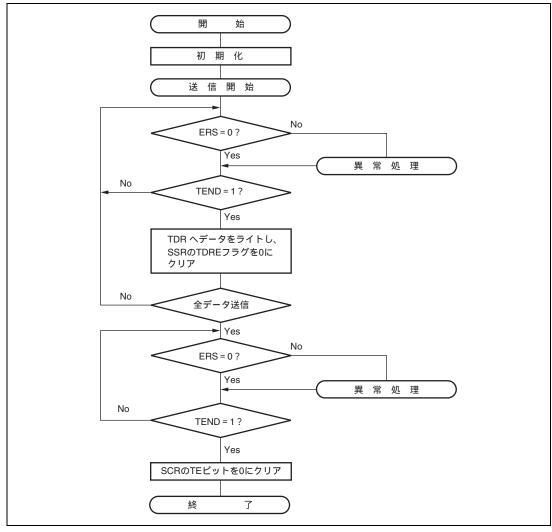

| 13.4.5 | シリアルデータ送信(調歩同期式 )                       | 13-23 |

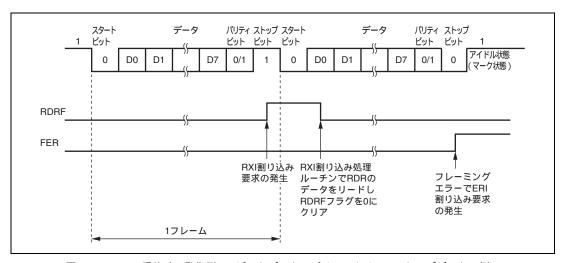

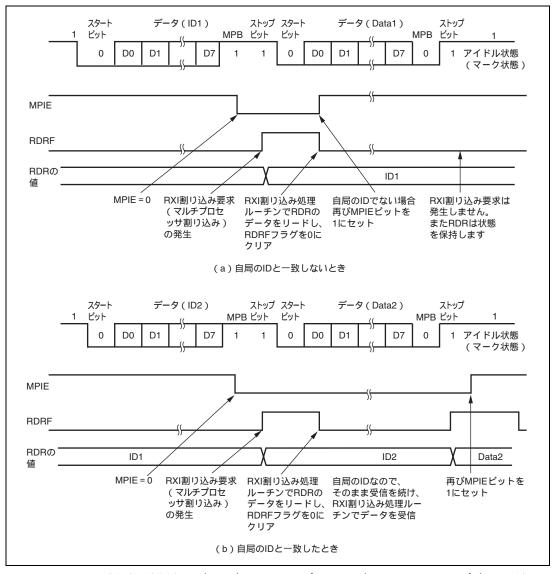

| 13.4.6 | シリアルデータ受信(調歩同期式 )                       | 13-25 |

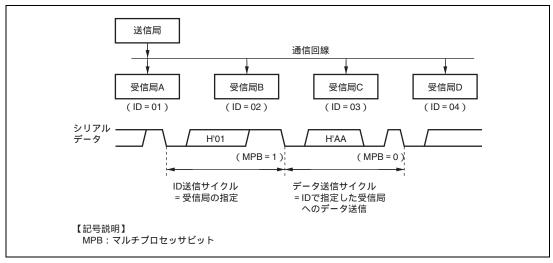

| 13.5   | マルチプロセッサ通信機能                            | 13-28 |

| 13.5.1 | マルチプロセッサシリアルデータ送信                       | 13-29 |

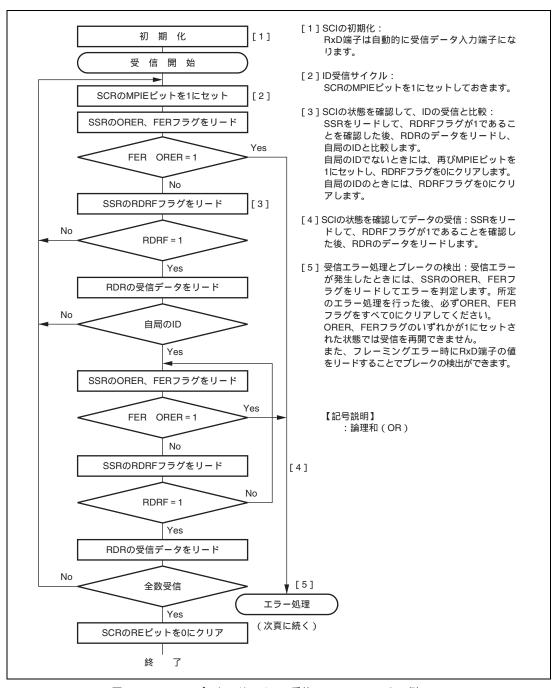

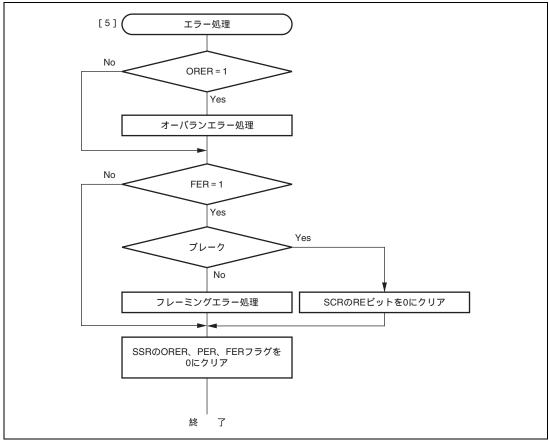

| 13.5.2 | マルチプロセッサシリアルデータ受信                       | 13-30 |

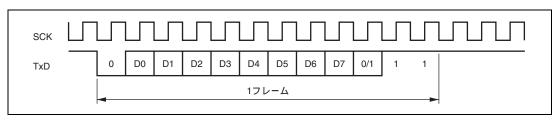

| 13.6   | クロック同期式モードの動作                           | 13-33 |

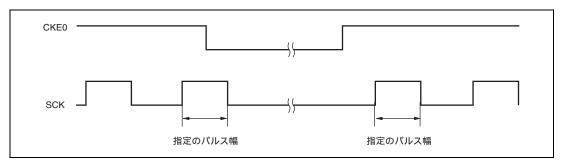

| 13.6.1 | クロック                                    | 13-33 |

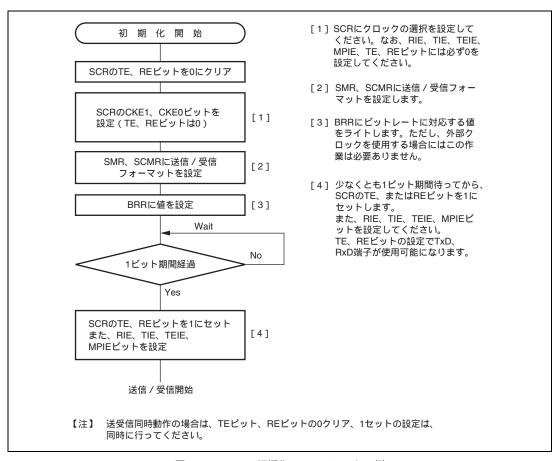

| 13.6.2 | SCI の初期化(クロック同期式)                       | 13-34 |

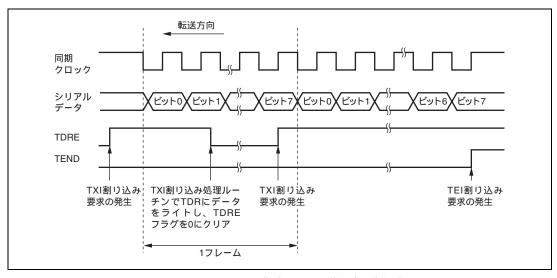

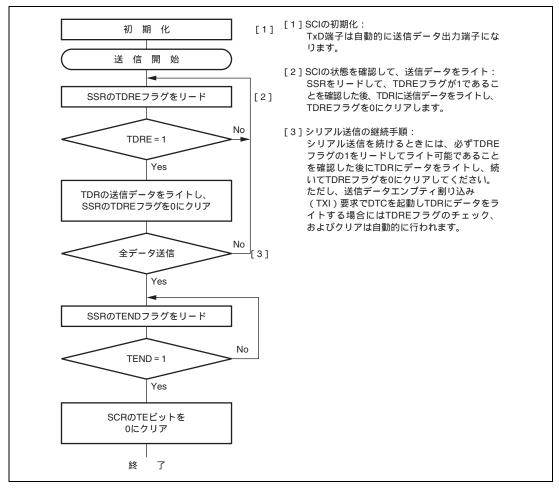

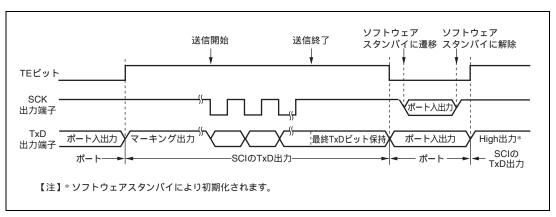

| 13.6.3 | シリアルデータ送信(クロック同期式 )                     | 13-35 |

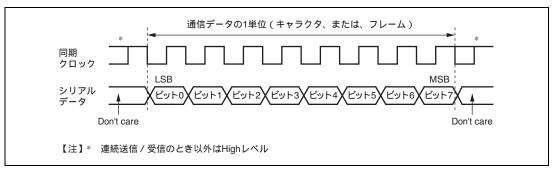

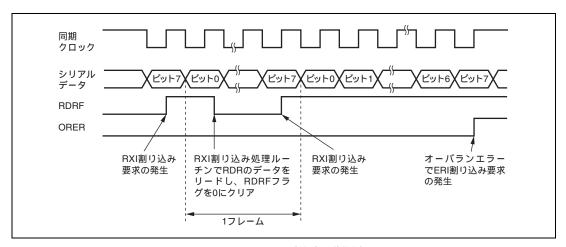

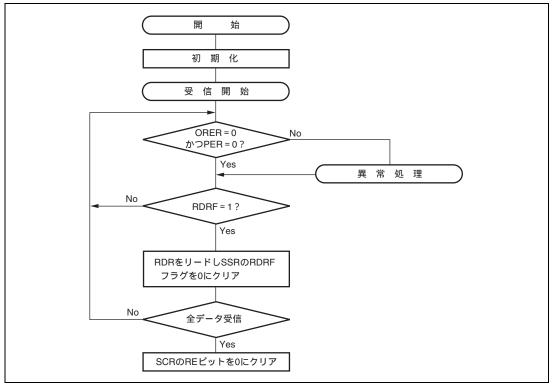

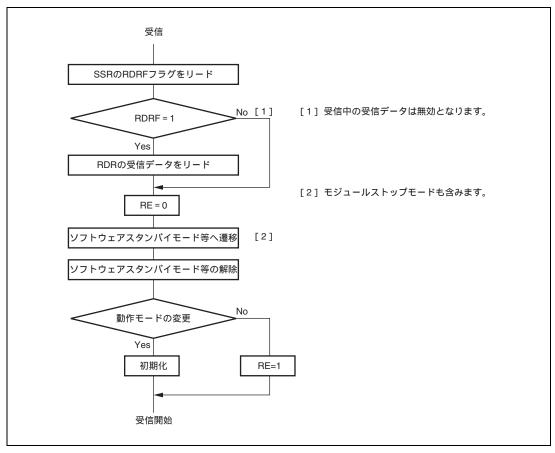

| 13.6.4 | シリアルデータ受信(クロック同期式 )                     | 13-37 |

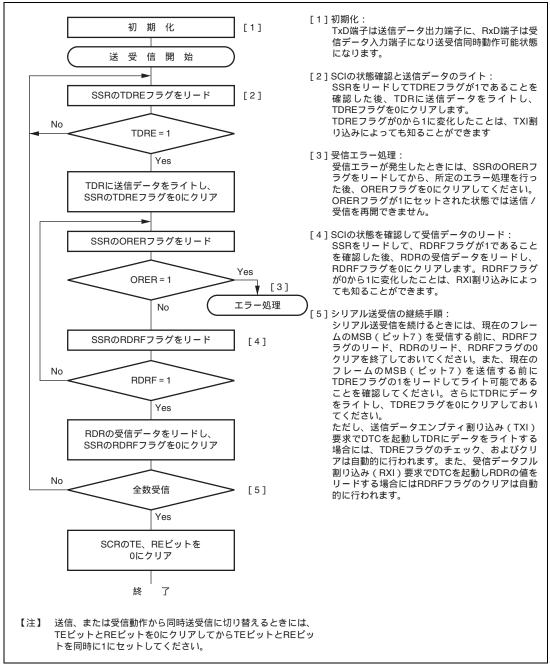

| 13.6.5 | シリアルデータ送受信同時動作 ( クロック同期式 )              | 13-39 |

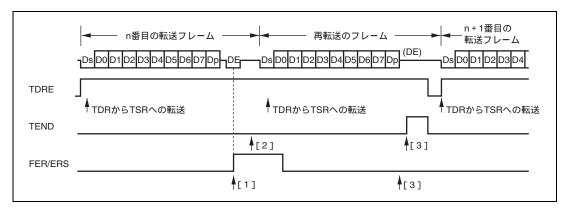

| 13.7   | スマートカードインタフェースの動作説明                     | 13-41 |

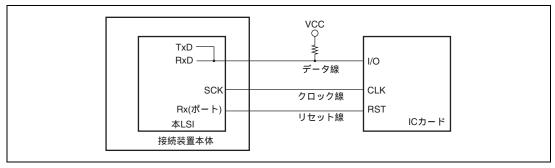

| 13.7.1 | 接続例                                     | 13-41 |

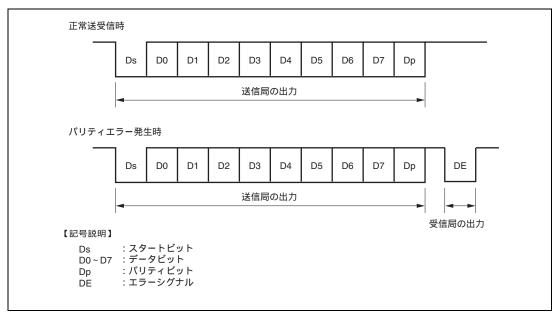

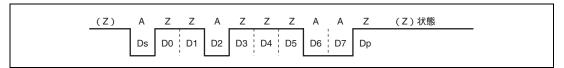

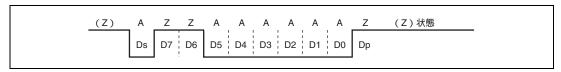

| 13.7.2 | データフォーマット(ブロック転送モード時を除く)                | 13-42 |

| 13.7.3 |                                         |       |

| 13.7.4 | 受信データサンプリングタイミングと受信マージン                 | 13-44 |

| 13.7.5 | • • • • • • • • • • • • • • • • • • • • |       |

| 13.7.6 |                                         |       |

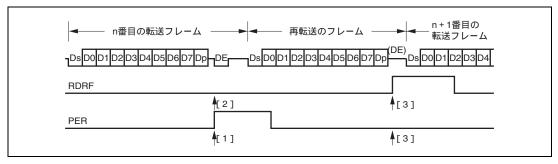

| 13.7.7 | シリアルデータ受信(ブロック転送モードを除く)                 | 13-49 |

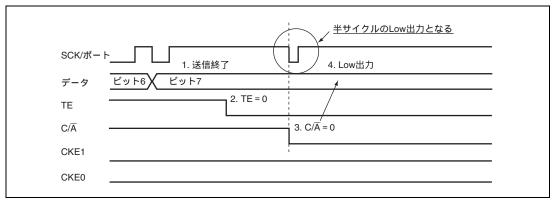

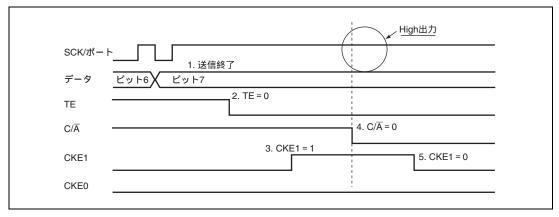

| 13.7.8 | クロック出力制御                                | 13-51 |

| 13.8   | 割り込み要因                                  |       |

| 13.8.1 | 通常のシリアルコミュニケーションインタフェースモードにおける割り込み      | 13-52 |

| 13.8.2                 | スマートカードインタフェースモードにおける割り込み                | 13-53 |

|------------------------|------------------------------------------|-------|

| 13.9                   | 使用上の注意事項                                 | 13-54 |

| 13.9.1                 | モジュールストップモードの設定                          | 13-54 |

| 13.9.2                 | ブレークの検出と処理                               | 13-54 |

| 13.9.3                 | マーク状態とブレークの送り出し                          | 13-54 |

| 13.9.4                 | 受信エラーフラグと送信動作(クロック同期式モードのみ)              | 13-54 |

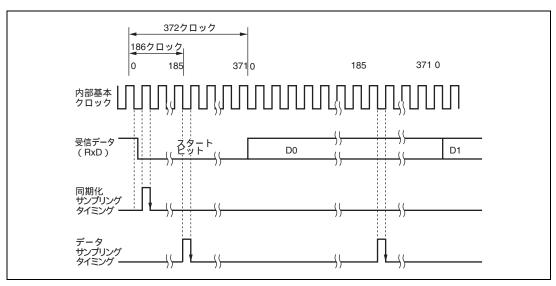

| 13.9.5                 | TDR へのライトと TDRE フラグの関係                   | 13-54 |

| 13.9.6                 | DTC の使用上の制約                              | 13-55 |

| 13.9.7                 | モード遷移時の動作                                |       |

| 13.9.8                 | SCK 端子からポート端子への切り替え                      | 13-59 |

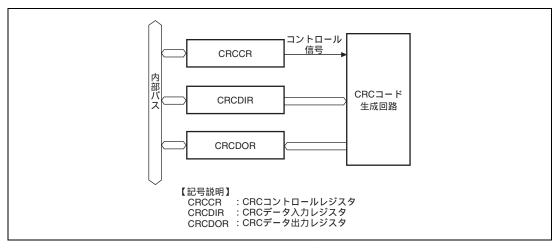

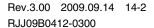

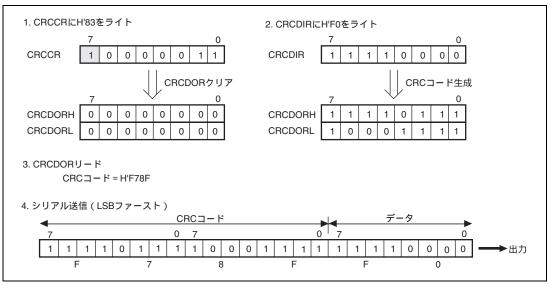

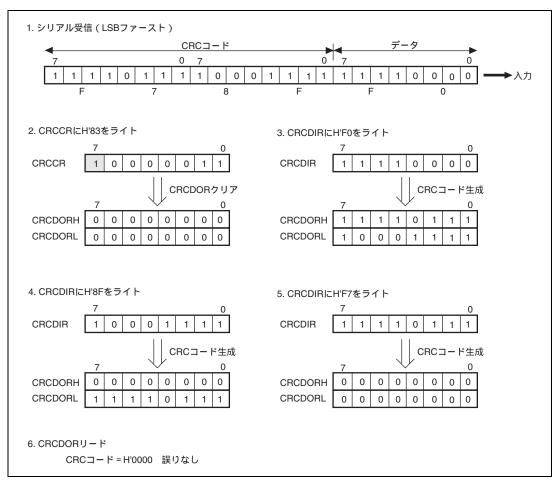

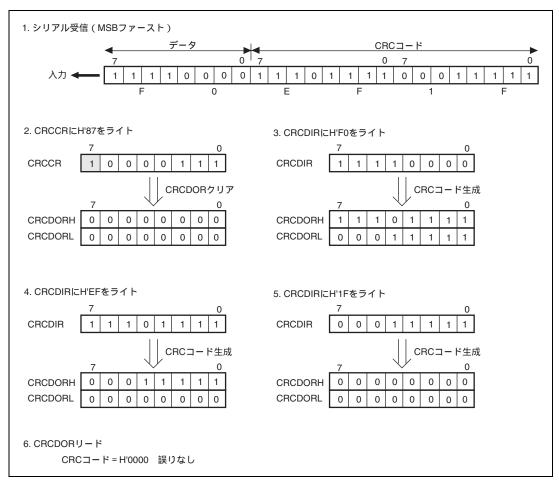

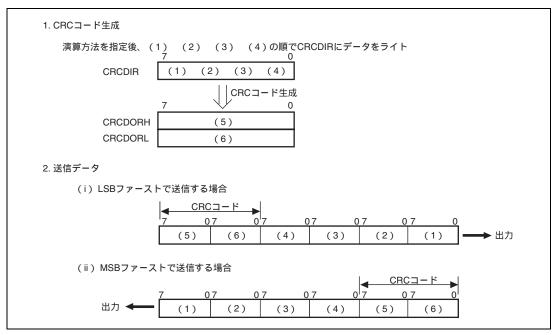

| 14. CR                 | C演算器(CRC)                                | 14-1  |

| 14.1                   | 特長                                       | 14-1  |

| 14.2                   | レジスタの説明                                  | 14-2  |

| 14.2.1                 | CRC コントロールレジスタ ( CRCCR )                 | 14-2  |

| 14.2.2                 | CRC データ入力レジスタ(CRCDIR)                    | 14-2  |

| 14.2.3                 | CRC データ出力レジスタ(CRCDOR)                    | 14-2  |

| 14.3                   | CRC演算器の動作説明                              | 14-3  |

| 14.4                   | CRC演算器使用上の注意事項                           | 14-6  |

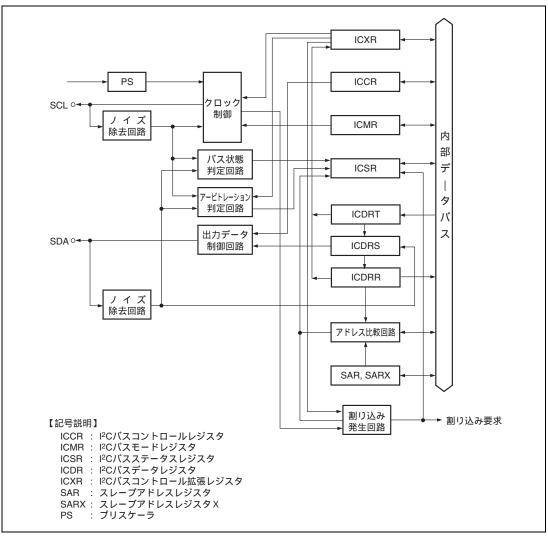

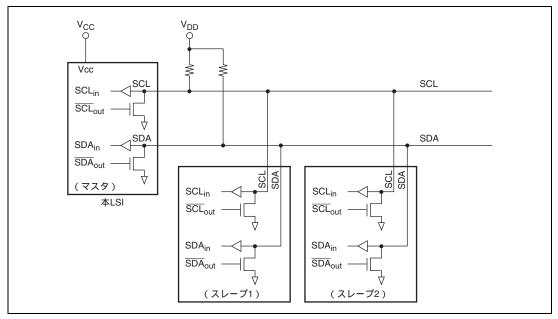

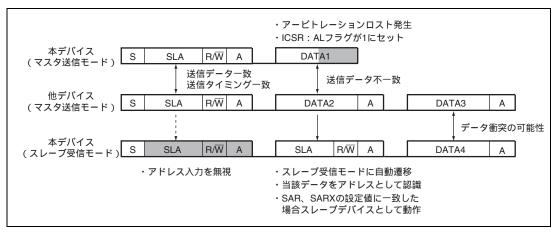

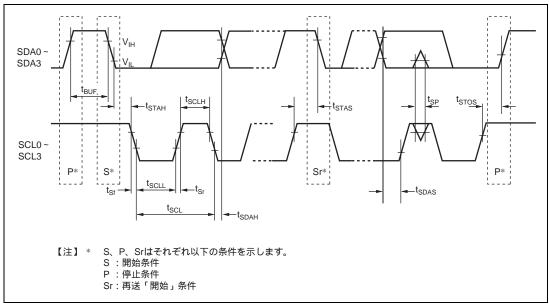

| 15. I <sup>2</sup> C . | パスインタフェース(IIC)                           | 15-1  |

| 15.1                   | 特長                                       |       |

| 15.2                   | 端子構成                                     |       |

| 15.3                   | レジスタの説明                                  |       |

| 15.3.1                 | I <sup>2</sup> C バスデータレジスタ(ICDR)         |       |

| 15.3.2                 | スレープアドレスレジスタ(SAR)                        |       |

| 15.3.3                 | 第 2 スレープアドレスレジスタ ( SARX )                |       |

| 15.3.4                 | ¹ºC バスモードレジスタ(ICMR)                      |       |

| 15.3.5                 | I'C バストランスファレートセレクトレジスタ(IICX3)           |       |

| 15.3.6                 | i'C バスコントロールレジスタ(ICCR)                   |       |

| 15.3.7                 | ピーパスステータスレジスタ(ICSR)                      |       |

| 15.3.8                 | I'C バスコントロール拡張レジスタ(ICXR)                 |       |

| 15.3.9                 | I <sup>2</sup> C SMBus 制御レジスタ (ICSMBCR ) |       |

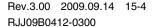

| 15.4                   | 動作説明                                     |       |

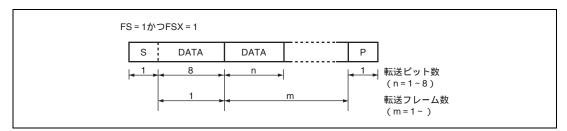

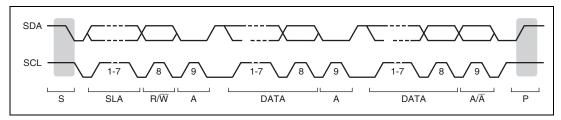

| 15.4.1                 | ¹ºc バスデータフォーマット                          |       |

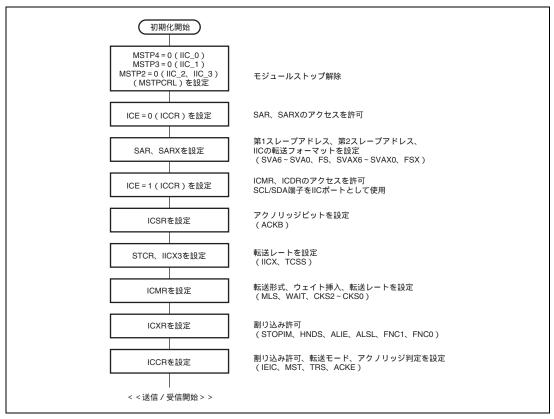

| 15.4.2                 | 初期設定                                     |       |

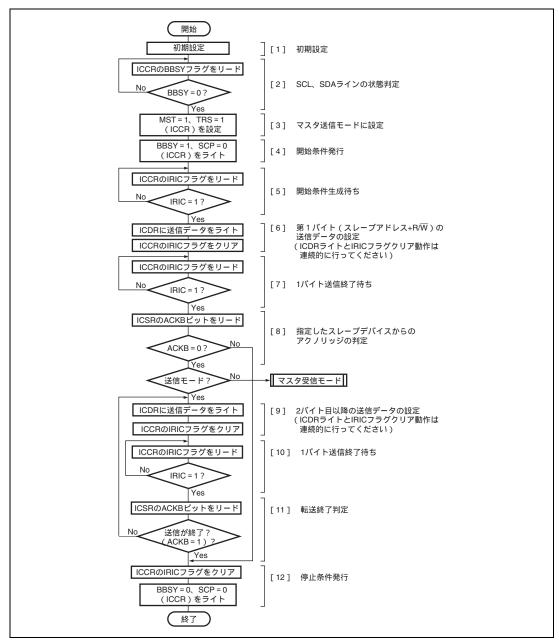

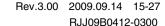

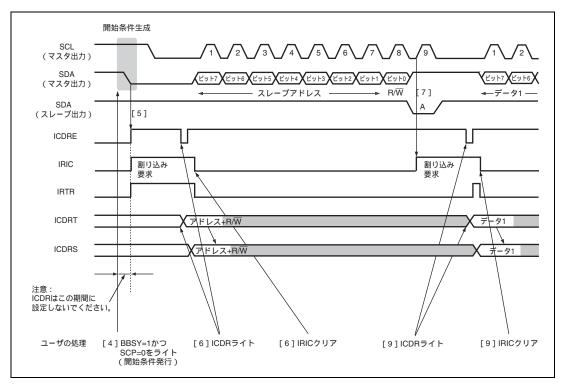

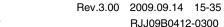

| 15.4.3                 | マスタ送信動作                                  |       |

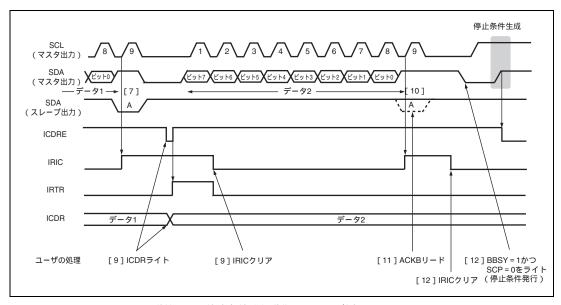

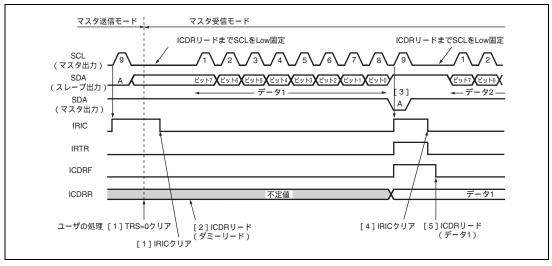

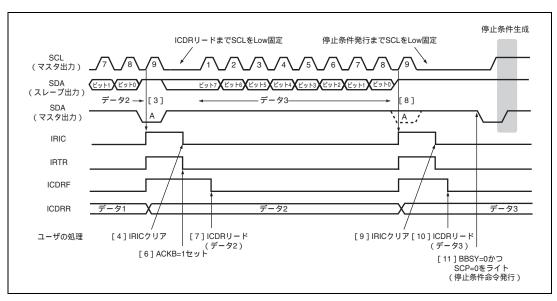

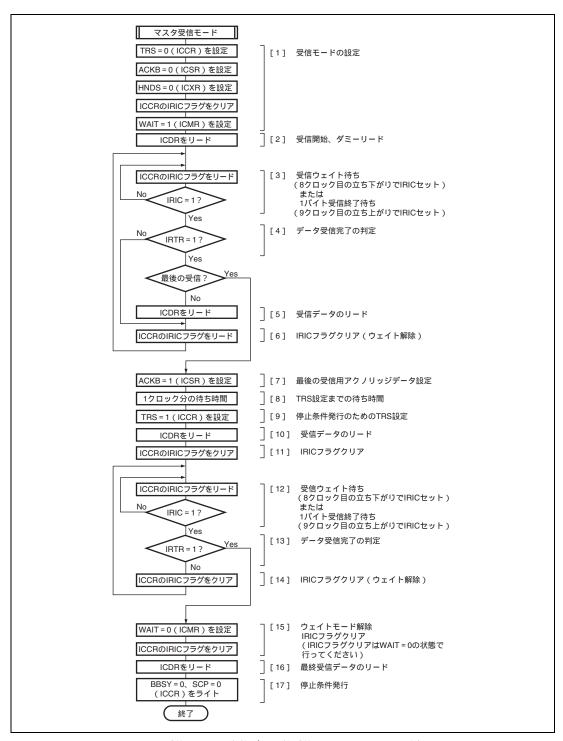

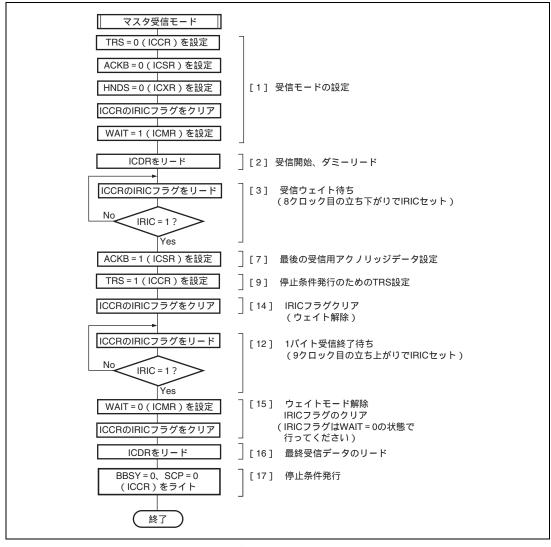

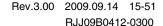

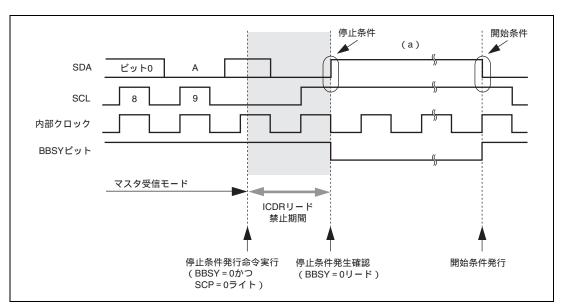

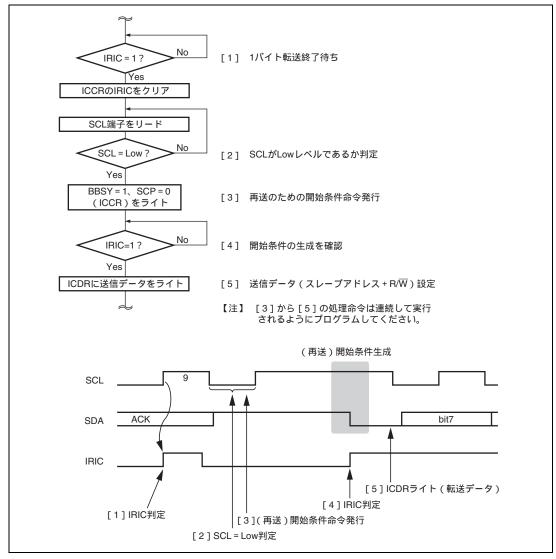

| 15.4.4                 | マスタ受信動作                                  |       |

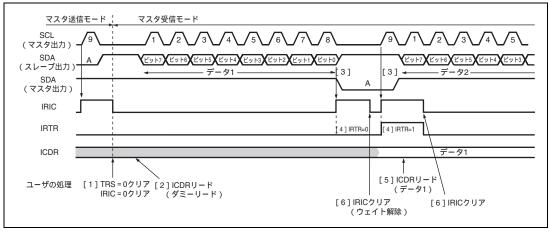

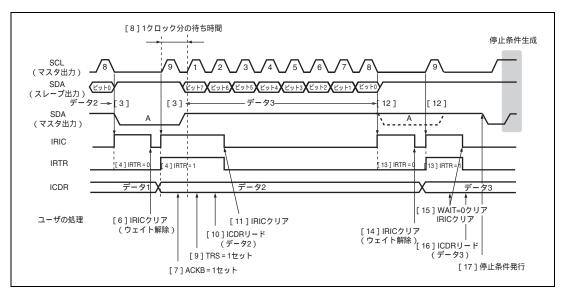

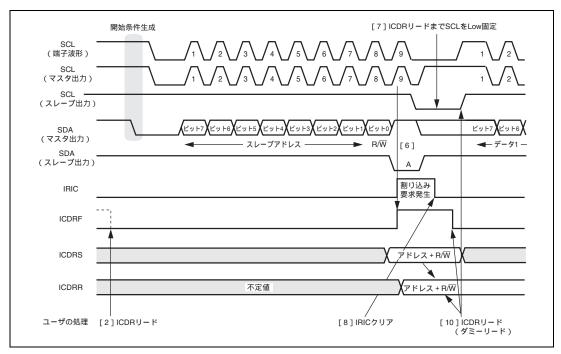

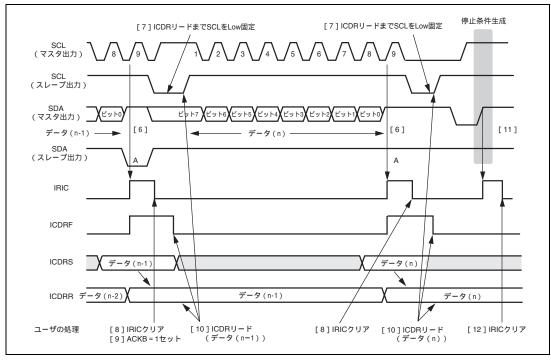

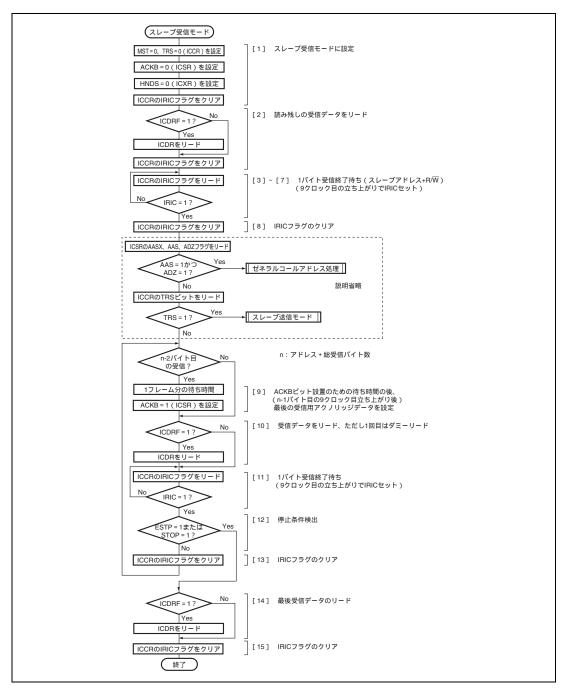

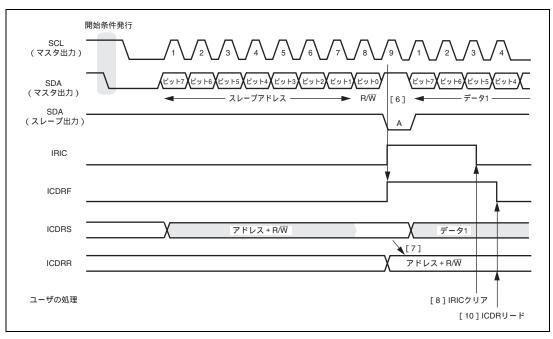

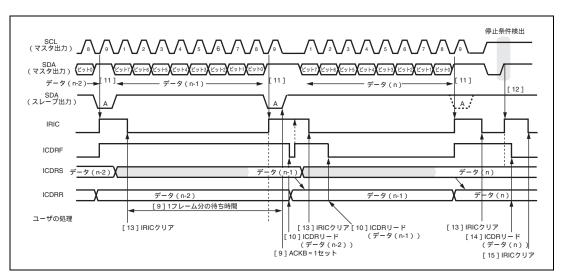

| 15.4.5                 | スレーブ受信動作                                 |       |

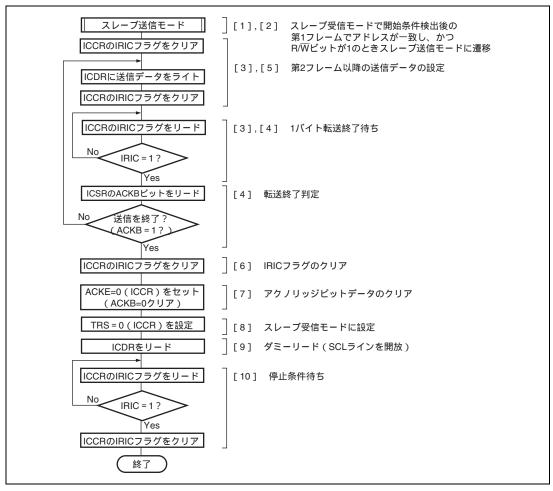

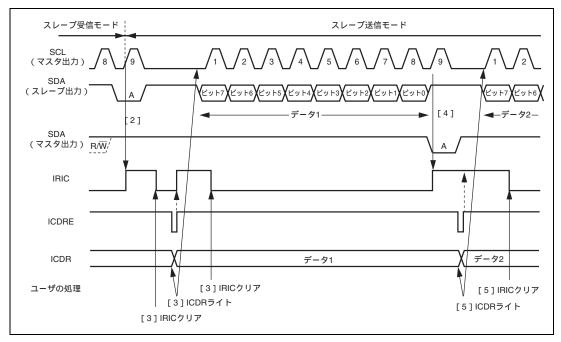

| 15.4.6                 | スレーブ送信動作                                 |       |

|                        |                                          |       |

| 15.4.8  | DTC による動作                                  | 15-50 |

|---------|--------------------------------------------|-------|

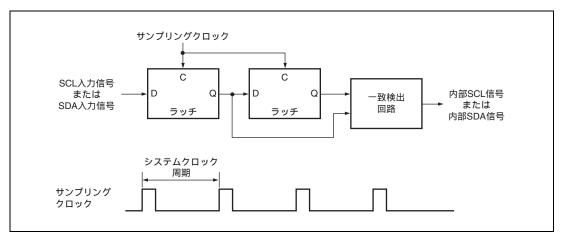

| 15.4.9  | ノイズ除去回路                                    | 15-51 |

| 15.4.10 | 0 内部状態の初期化                                 | 15-51 |

| 15.5    | 割り込み要因                                     | 15-52 |

| 15.6    | 使用上の注意事項                                   | 15-53 |

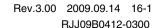

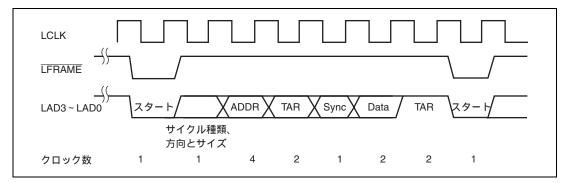

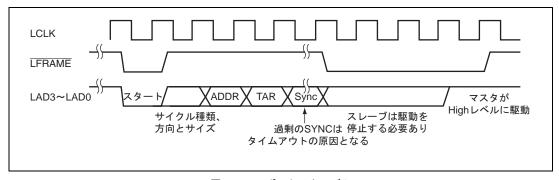

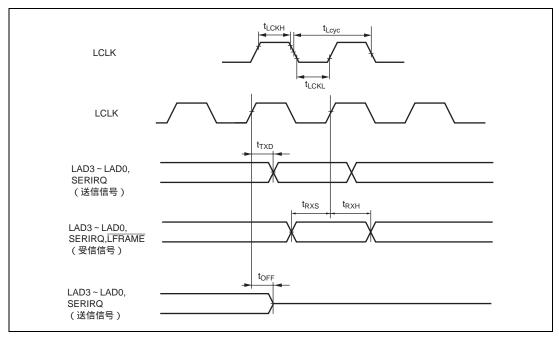

| 16. LPC | C インタフェース(LPC)                             | 16-1  |

| 16.1    | 特長                                         | 16-1  |

| 16.2    | 入出力端子                                      | 16-3  |

| 16.3    | レジスタの説明                                    | 16-4  |

| 16.3.1  | ホストインタフェースコントロールレジスタ 0、1 ( HICR0、HICR1 )   | 16-6  |

| 16.3.2  | ホストインタフェースコントロールレジスタ 2、3 (HICR2、HICR3)     | 16-9  |

| 16.3.3  | ホストインタフェースコントロールレジスタ 4 ( HICR4 )           | 16-11 |

| 16.3.4  | LPC チャネル 1、2 アドレスレジスタ H、L(LADR12H、LADR12L) | 16-12 |

| 16.3.5  | LPC チャネル 3 アドレスレジスタ H、L ( LADR3H、LADR3L )  | 16-13 |

| 16.3.6  | 入力データレジスタ 1~3 (IDR1~IDR3)                  | 16-16 |

| 16.3.7  | 出力データレジスタ 1~3 (ODR1~ODR3)                  | 16-16 |

| 16.3.8  | 双方向データレジスタ 0~15 (TWR0~TWR15)               | 16-16 |

| 16.3.9  | ステータスレジスタ 1~3 (STR1~STR3)                  | 16-17 |

| 16.3.10 | 0 SERIRQ コントロールレジスタ 0 ( SIRQCR0 )          | 16-23 |

| 16.3.1  | 1 SERIRQ コントロールレジスタ 1 ( SIRQCR1 )          | 16-26 |

| 16.3.12 | 2 SERIRQ コントロールレジスタ 2 ( SIRQCR2 )          | 16-30 |

| 16.3.13 | 3 SERIRQ コントロールレジスタ 4 ( SIRQCR4 )          | 16-31 |

| 16.3.14 | 4 SERIRQ コントロールレジスタ 5 ( SIRQCR5 )          | 16-32 |

| 16.3.13 | 5 ホストインタフェースセレクトレジスタ ( HISEL )             | 16-33 |

| 16.3.10 | 6 SMIC フラグレジスタ (SMICFLG)                   | 16-34 |

| 16.3.1  | 7 SMIC コントロールステータスレジスタ ( SMICCSR )         | 16-35 |

| 16.3.18 | 8 SMIC データレジスタ (SMICDTR )                  | 16-35 |

| 16.3.19 | 9 SMIC 割り込みレジスタ 0(SMICIR0)                 | 16-36 |

| 16.3.20 | 0 SMIC 割り込みレジスタ 1(SMICIR1)                 | 16-38 |

| 16.3.2  | 1 BT ステータスレジスタ 0 (BTSR0)                   | 16-39 |

| 16.3.22 | 2 BT ステータスレジスタ 1 (BTSR1)                   | 16-41 |

| 16.3.23 | 3 BT コントロールステータスレジスタ 0 (BTCSR0)            | 16-43 |

| 16.3.2  | 4 BT コントロールステータスレジスタ 1 (BTCSR1)            | 16-44 |

| 16.3.25 | 5 BT コントロールレジスタ (BTCR )                    | 16-45 |

| 16.3.20 | 6 BT データパッファ(BTDTR)                        | 16-48 |

| 16.3.2  | 7 BT 割り込みマスクレジスタ(BTIMSR)                   | 16-48 |

| 16.3.28 | 8 BT FIFO 有効サイズレジスタ 0(BTFVSR0)             | 16-50 |

| 16.3.29 | 9 BT FIFO 有効サイズレジスタ I(BTFVSR1)             | 16-50 |

| 16.4    | 動作説明                                       | 16-51 |

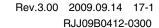

| 16.4.1  | LPC インタフェースの起動                             | 16-51 |

| 16.4.2  | LPC の I/O サイクル                                                                                | 16-52 |

|---------|-----------------------------------------------------------------------------------------------|-------|

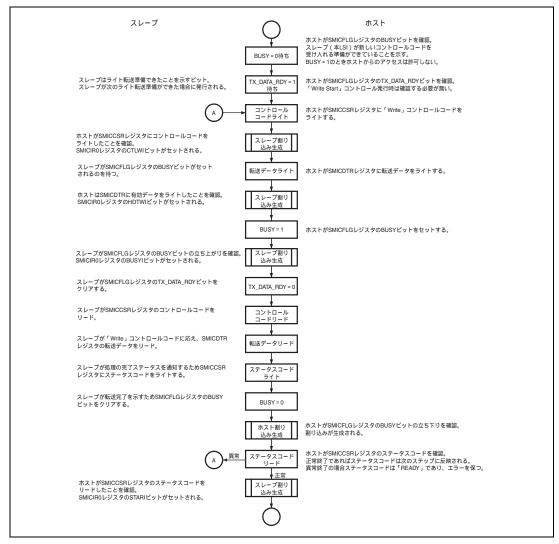

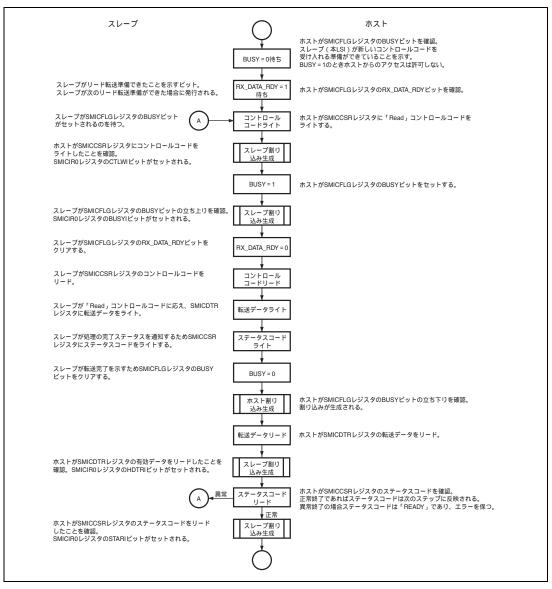

| 16.4.3  | SMIC モードの転送フロー                                                                                | 16-54 |

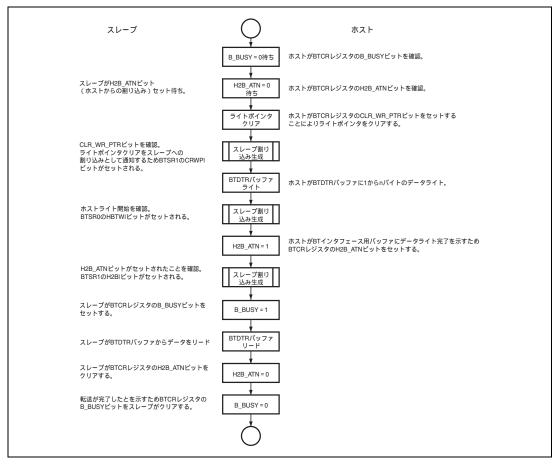

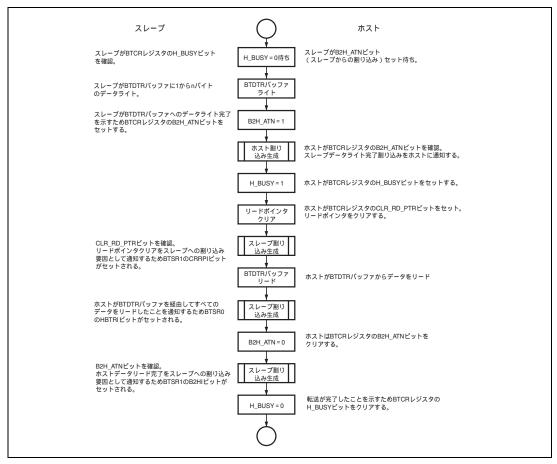

| 16.4.4  | BT モードの転送フロー                                                                                  | 16-56 |

| 16.4.5  | LPC インタフェースのシャットダウン機能                                                                         | 16-58 |

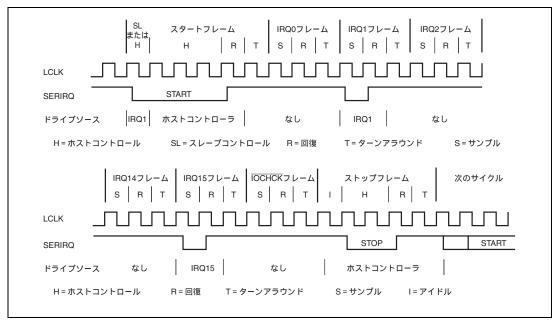

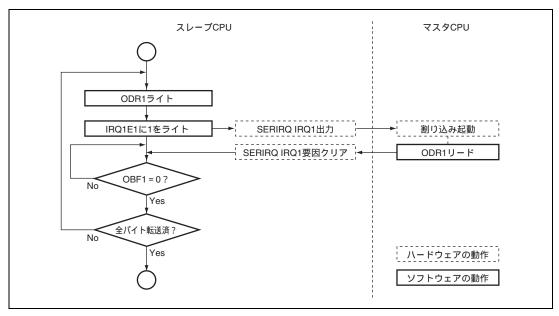

| 16.4.6  | LPC インタフェースのシリアル割り込み動作(SERIRQ )                                                               | 16-60 |

| 16.5    | 割り込み要因                                                                                        | 16-63 |

| 16.5.1  | IBFI1、IBFI2、IBFI3、ERRI                                                                        | 16-63 |

| 16.5.2  | SMI、HIRQ1、HIRQ3、HIRQ4、HIRQ5、HIRQ6、HIRQ7、HIRQ8、HIRQ9、HIRQ10、HIRQ11、HIRQ12、HIRQ13、HIRQ14、HIRQ15 | 16-63 |

| 16.6    | 使用上の注意事項                                                                                      | 16-66 |

| 16.6.1  | データアクセスの競合                                                                                    | 16-66 |

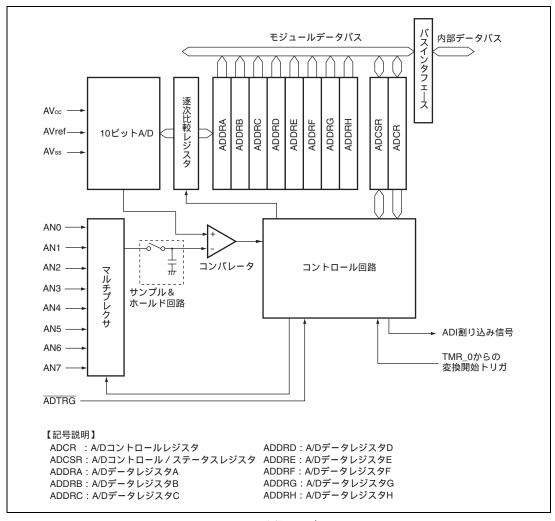

| 17. A/D | / 变換器                                                                                         | 17-1  |

| 17.1    | 特長                                                                                            | 17-1  |

| 17.2    | 入出力端子                                                                                         | 17-3  |

| 17.3    | レジスタの説明                                                                                       | 17-4  |

| 17.3.1  | A/D データレジスタ A~H(ADDRA~ADDRH)                                                                  | 17-4  |

| 17.3.2  | A/D コントロール / ステータスレジスタ(ADCSR)                                                                 | 17-5  |

| 17.3.3  | A/D コントロールレジスタ(ADCR)                                                                          | 17-6  |

| 17.4    | 動作説明                                                                                          | 17-7  |

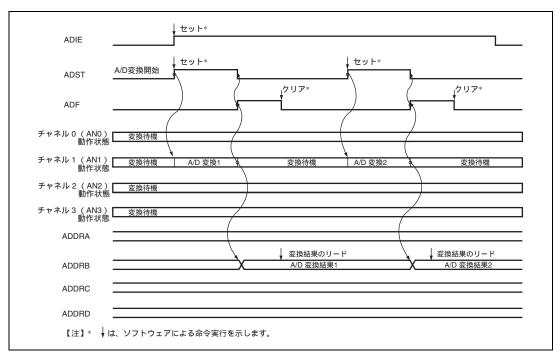

| 17.4.1  | シングルモード                                                                                       | 17-7  |

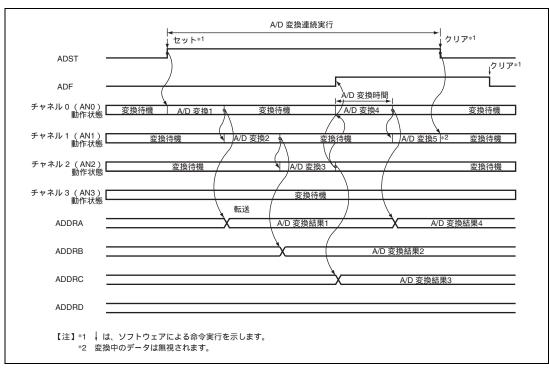

| 17.4.2  | スキャンモード                                                                                       | 17-8  |

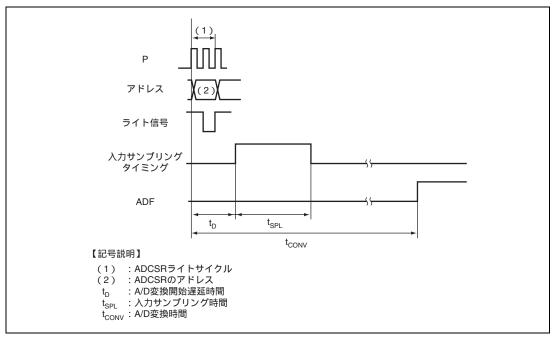

| 17.4.3  | 入力サンプリングと A/D 変換時間                                                                            | 17-9  |

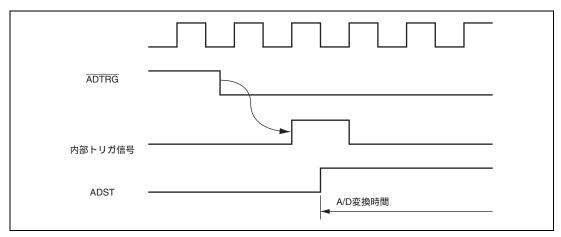

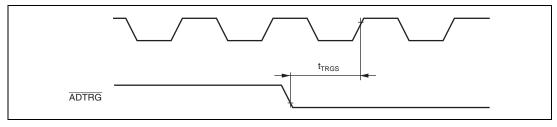

| 17.4.4  | 外部トリガ入力タイミング                                                                                  | 17-11 |

| 17.5    | 割り込み要因                                                                                        | 17-12 |

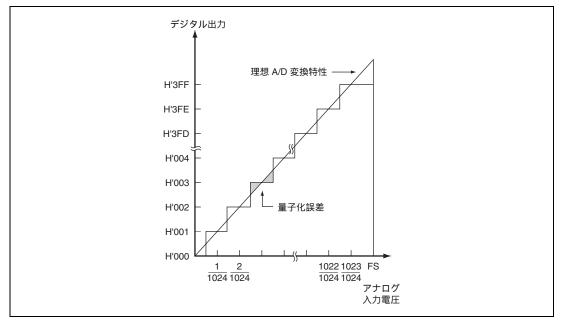

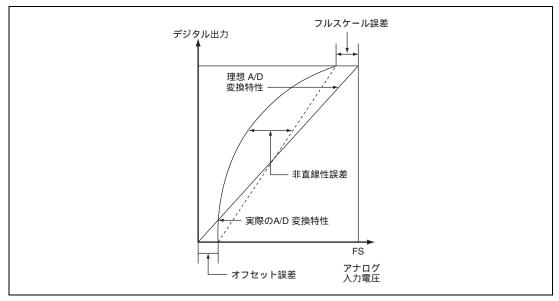

| 17.6    | A/D変換精度の定義                                                                                    | 17-12 |

| 17.7    | 使用上の注意事項                                                                                      | 17-14 |

| 17.7.1  | モジュールストップモードの設定                                                                               | 17-14 |

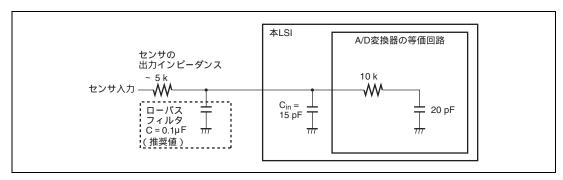

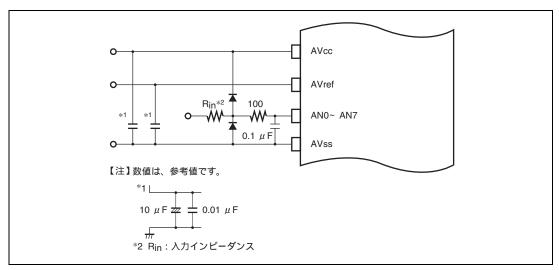

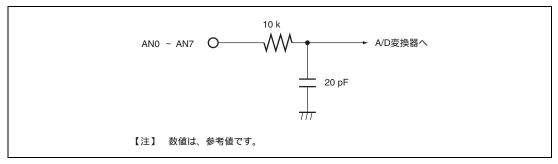

| 17.7.2  | 許容信号源インピーダンスについて                                                                              | 17-14 |

| 17.7.3  | 絶対精度への影響                                                                                      | 17-14 |

| 17.7.4  | アナログ電源端子他の設定範囲                                                                                | 17-15 |

| 17.7.5  | · · · · · · · · · · · · · · · · · · ·                                                         |       |

| 17.7.6  | ノイズ対策上の注意                                                                                     | 17-15 |

| 17.7.7  | ソフトウェアスタンバイ時の A/D 変換保持機能                                                                      | 17-16 |

| 18. RAI | M                                                                                             | 18-1  |

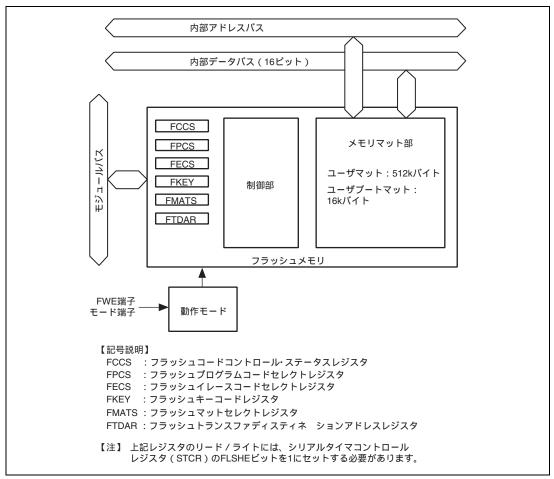

| 19. フラ  | ,<br>ラッシュメモリ                                                                                  | 19-1  |

| 19.1    | 特長                                                                                            | 19-1  |

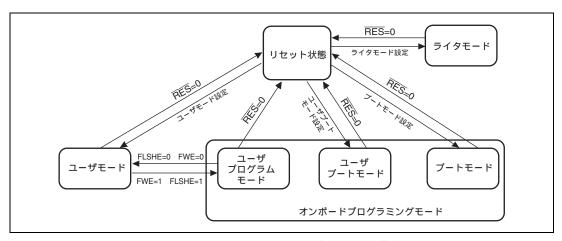

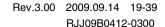

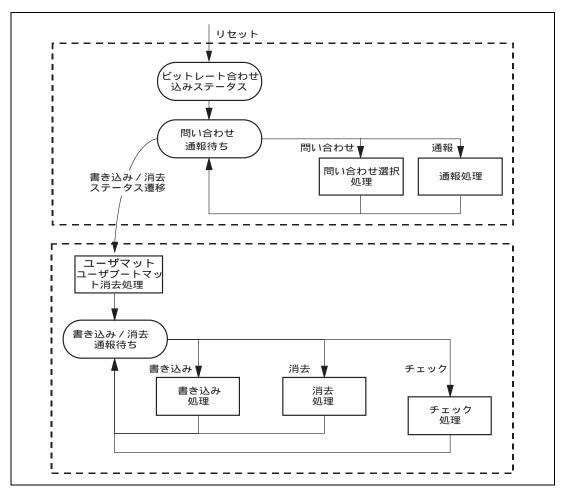

| 19.1.1  | モード遷移図                                                                                        | 19-3  |

| 19.1.2  | モード比較                                                                                         | 19-4  |

|         |                                                                                               |       |

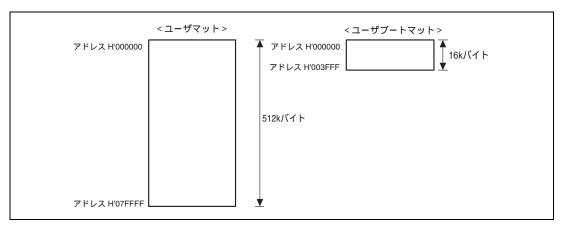

| 19.1.3                                                                                                                     | フラッシュメモリマット構成             | 19-5  |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|

| 19.1.4                                                                                                                     | プロック分割                    | 19-5  |

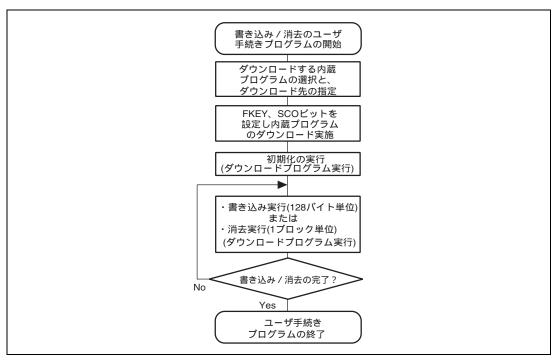

| 19.1.5                                                                                                                     | 書き込み / 消去インタフェース          | 19-7  |

| 19.2                                                                                                                       | 入出力端子                     | 19-9  |

| 19.3                                                                                                                       | レジスタの説明                   | 19-9  |

| 19.3.1                                                                                                                     | 書き込み / 消去インタフェースレジスタ      | 19-10 |

| 19.3.2                                                                                                                     | 書き込み / 消去インタフェースパラメータ     | 19-15 |

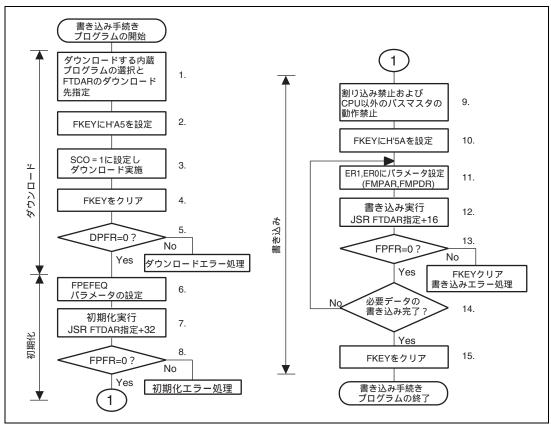

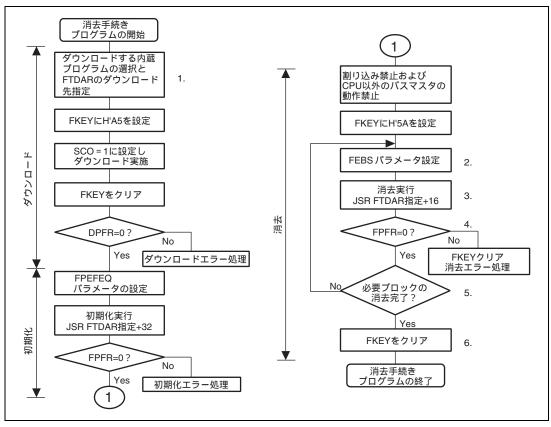

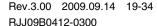

| 19.4                                                                                                                       | オンボードプログラミング              | 19-22 |

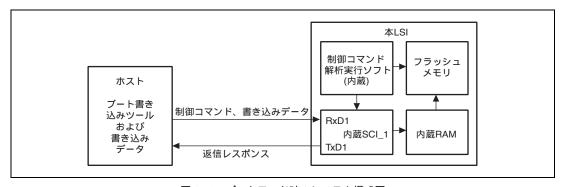

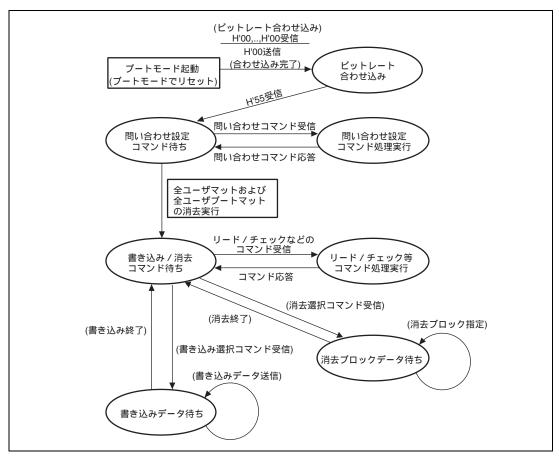

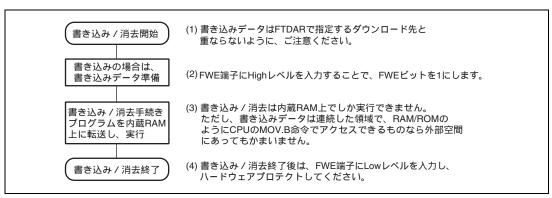

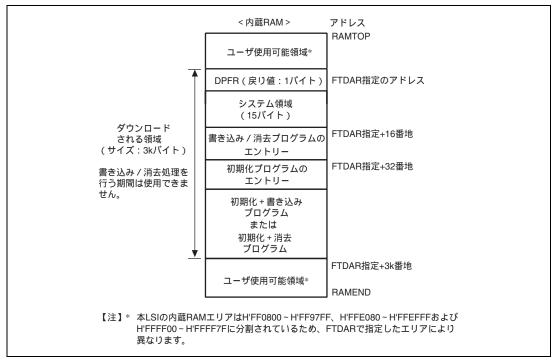

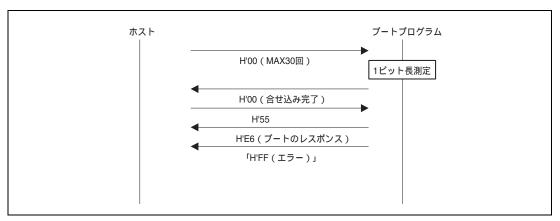

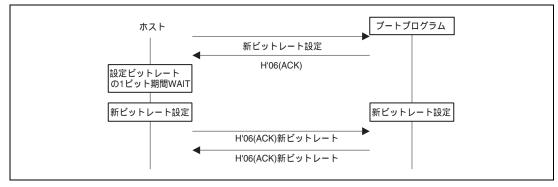

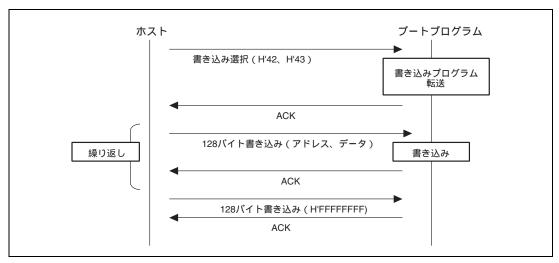

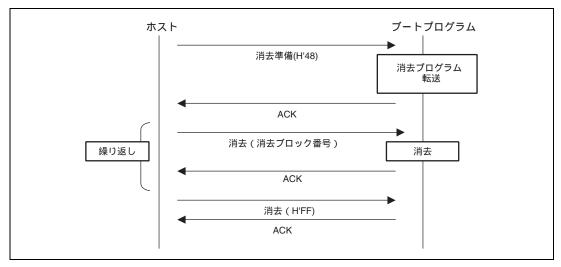

| 19.4.1                                                                                                                     | プートモード                    | 19-22 |

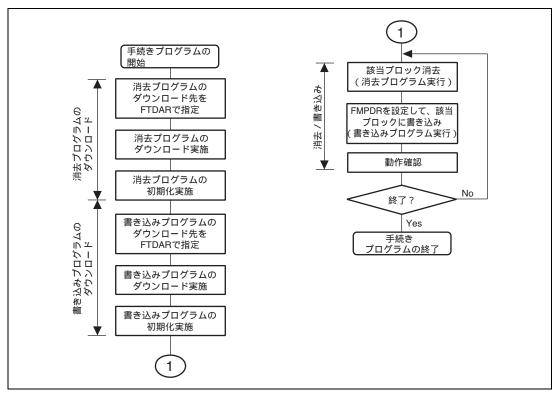

| 19.4.2                                                                                                                     | ユーザプログラムモード               | 19-26 |

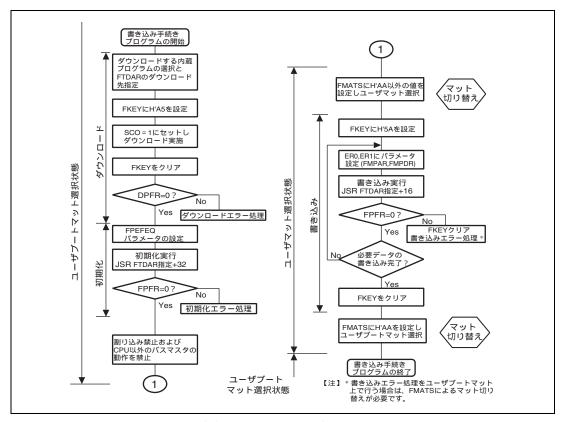

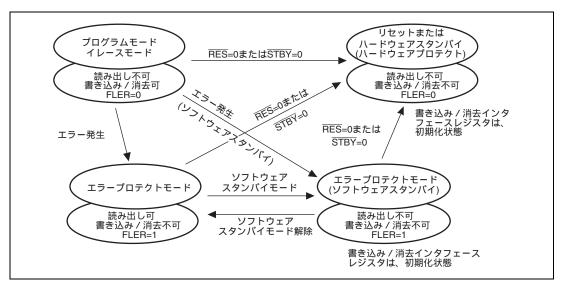

| 19.4.3                                                                                                                     | ユーザブートモード                 | 19-36 |

| 19.4.4                                                                                                                     | 手順プログラム、または書き込みデータの格納可能領域 | 19-39 |

| 19.5                                                                                                                       | プロテクト                     | 19-44 |

| 19.5.1                                                                                                                     | ハードウェアプロテクト               | 19-44 |

| 19.5.2                                                                                                                     | ソフトウェアプロテクト               | 19-44 |

| 19.5.3                                                                                                                     | エラープロテクト                  | 19-45 |

| 19.6                                                                                                                       | ユーザマットとユーザブートマットの切り替え     |       |

| 19.7                                                                                                                       | ライタモード                    |       |

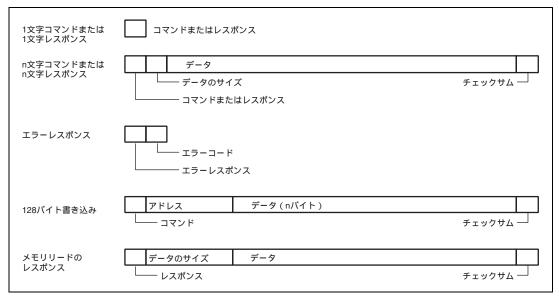

| 19.8                                                                                                                       | ブートモードの標準シリアル通信インタフェース仕様  | 19-47 |

| 19.9                                                                                                                       | 使用上の注意事項                  | 19-69 |

|                                                                                                                            |                           |       |

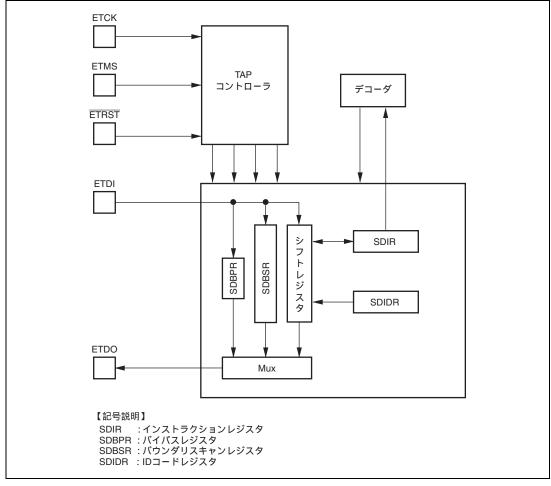

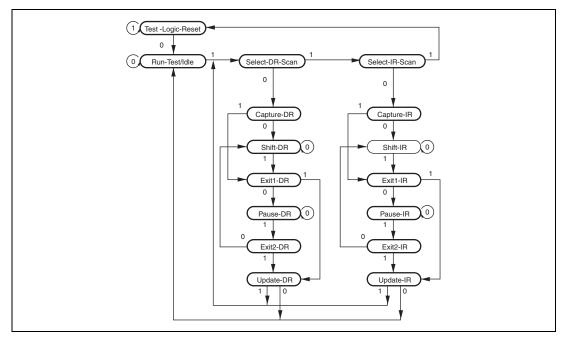

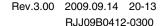

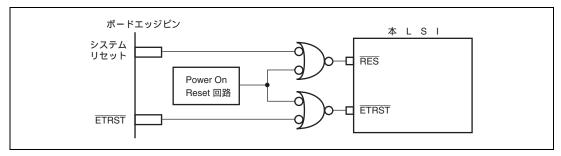

| 20. バウ                                                                                                                     | リンダリスキャン(JTAG)            | 20-1  |

|                                                                                                                            | アンダリスキャン(JTAG)            |       |

| 20.1                                                                                                                       | 特長                        | 20-1  |

| 20.1<br>20.2                                                                                                               | 特長                        | 20-1  |

| 20.1                                                                                                                       | 特長                        |       |

| 20.1<br>20.2<br>20.3                                                                                                       | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1                                                                                             | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2                                                                                   | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3                                                                         | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4                                                               | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4                                                               | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4.1                                                     | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4<br>20.4.1                                             | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4<br>20.4.1<br>20.4.2                                   | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4<br>20.4.1<br>20.4.2<br>20.5<br>20.5.1                 | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4<br>20.4.1<br>20.4.2<br>20.5<br>20.5.1                 | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4.1<br>20.4.2<br>20.5<br>20.5.1<br>20.6                 | 特長                        |       |

| 20.1<br>20.2<br>20.3<br>20.3.1<br>20.3.2<br>20.3.3<br>20.3.4<br>20.4<br>20.4.1<br>20.4.2<br>20.5<br>20.5<br>20.5.1<br>20.6 | 特長                        |       |

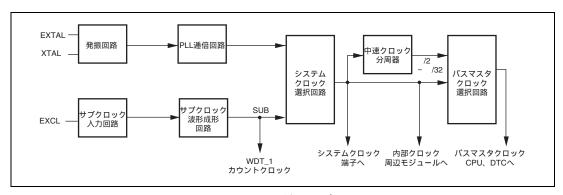

| 21.3    | 中速クロック分周器                      | 21-4  |

|---------|--------------------------------|-------|

| 21.4    | バスマスタクロック選択回路                  | 21-4  |

| 21.5    | サブクロック入力回路                     | 21-4  |

| 21.6    | サブクロック波形成形回路                   | 21-4  |

| 21.7    | クロック選択回路                       | 21-5  |

| 21.8    | 使用上の注意事項                       | 21-5  |

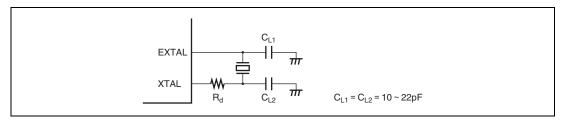

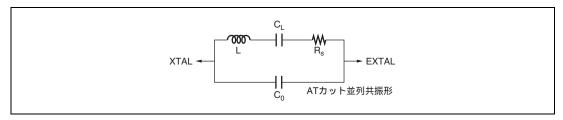

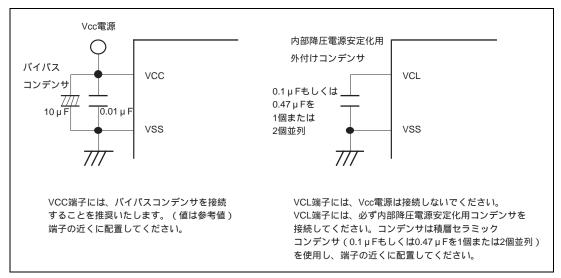

| 21.8.1  | 発振子に関する注意事項                    | 21-5  |

| 21.8.2  | ボード設計上の注意事項                    | 21-5  |

| 21.8.3  | 動作確認時の注意事項                     | 21-5  |

| 22. 低消  | 費電力状態                          | 22-1  |

| 22.1    | レジスタの説明                        | 22-2  |

| 22.1.1  | スタンバイコントロールレジスタ(SBYCR)         |       |

| 22.1.2  | ローパワーコントロールレジスタ(LPWRCR)        |       |

| 22.1.3  | モジュールストップコントロールレジスタ H、L、A      |       |

|         | (MSTPCRH、MSTPCRL、MSTPCRA)      | 22-5  |

| 22.1.4  | サブチップモジュールストップコントロールレジスタ BH、BL |       |

|         | (SUBMSTPBH、SUBMSTPBL)          | 22-6  |

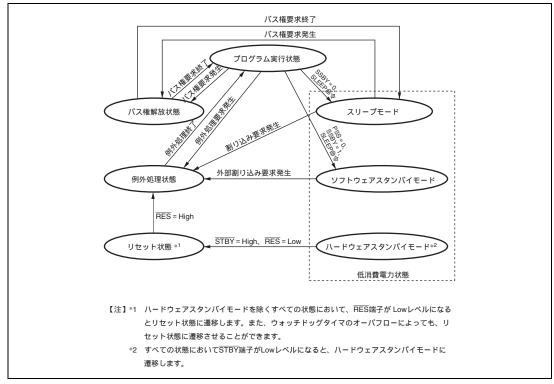

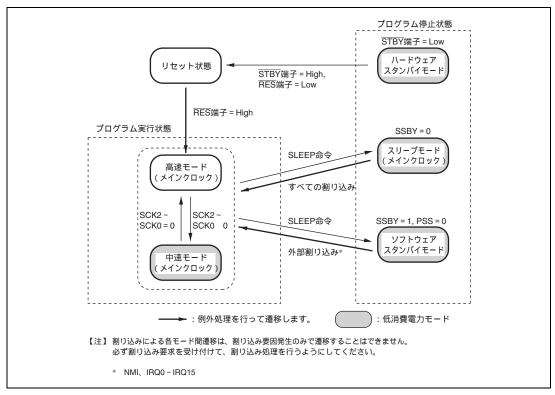

| 22.2    | モード間遷移とLSIの状態                  | 22-7  |

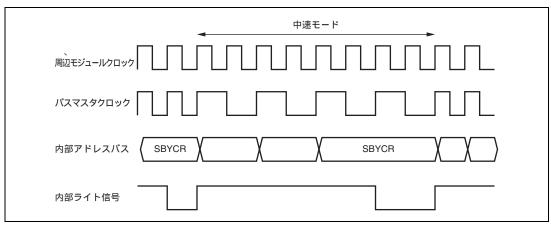

| 22.3    | 中速モード                          | 22-9  |

| 22.4    | スリープモード                        | 22-10 |

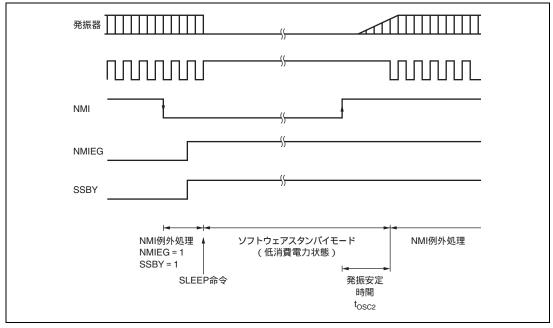

| 22.5    | ソフトウェアスタンバイモード                 | 22-10 |

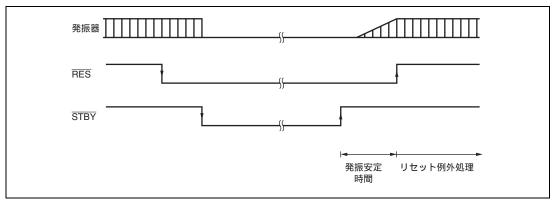

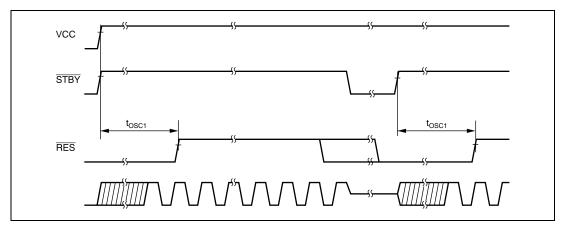

| 22.6    | ハードウェアスタンバイモード                 | 22-12 |

| 22.7    | モジュールストップモード                   | 22-13 |

| 22.8    | 使用上の注意事項                       | 22-13 |

| 22.8.1  | I/O ポートの状態                     | 22-13 |

| 22.8.2  | 発振安定待機中の消費電流                   | 22-13 |

| 22.8.3  | DTC のモジュールストップモードの設定           | 22-13 |

| 22.8.4  | サプクロック使用上の注意事項                 | 22-13 |

| 23. レジ  | スター覧                           | 23-1  |

| 23.1    | レジスタアドレス一覧(アドレス順)              | 23-2  |

| 23.2    | レジスタビット一覧                      |       |

| 23.3    | 各動作モードにおけるレジスタの状態              |       |

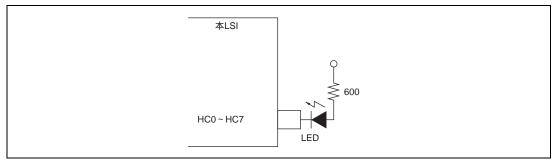

| 24. 電気  | .的特性                           | 24-1  |

| 24.1    | 絶対最大定格                         | 24.1  |

| 24.1    | DC特性                           |       |

| 24.2    | AC特性                           |       |

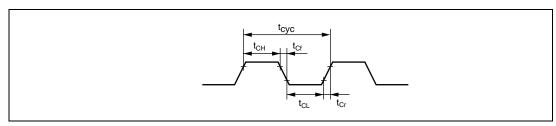

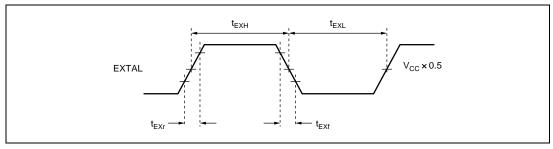

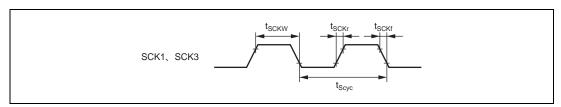

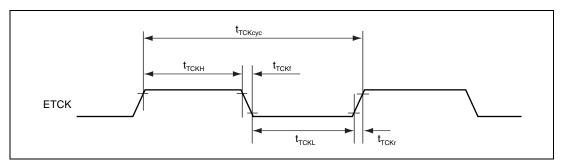

| 24.3.1  | クロックタイミング                      |       |

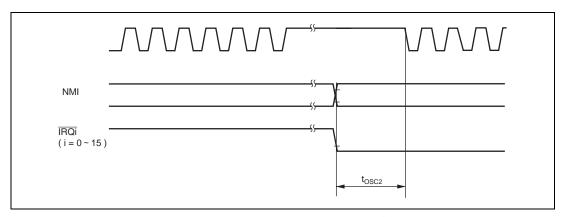

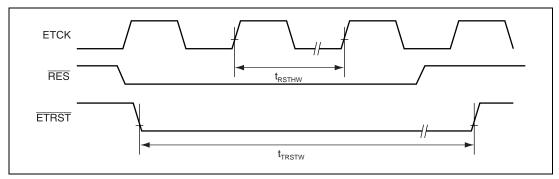

| 24.3.2  | 制御信号タイミング                      |       |

| _ T.J.L | 197 M 1 7 7 1 7 7 7            | ∠¬-)  |

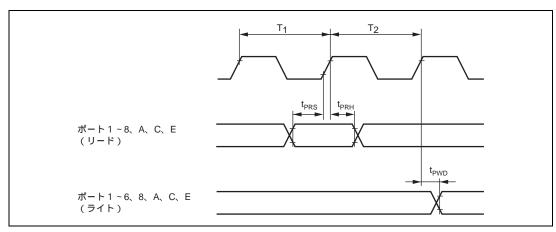

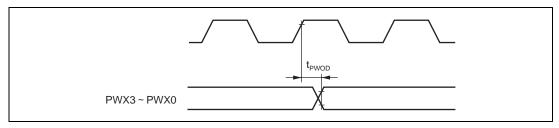

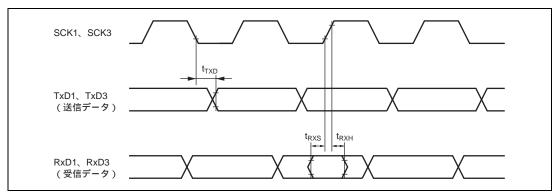

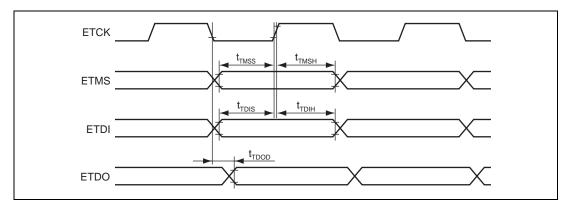

|      | 内蔵周辺モジュールタイミング     |       |

|------|--------------------|-------|

| 24.4 | A/D变換特性            | 24-17 |

| 24.5 | フラッシュメモリ特性         | 24-18 |

| 24.6 | 使用上の注意事項           | 24-19 |

| 付録   |                    | 付録-1  |

| A.   | 各処理状態におけるI/Oポートの状態 | 付録-1  |