改訂一覧は改訂箇所をまとめたものであり、 詳細については必ず本文の内容をご確認ください。

H8S/20103, H8S/20203, H8S/20223, H8S/20115, H8S/20215, H8S/20235 グループ

ユーザーズマニュアル ハードウェア編ルネサス 16 ビットシングルチップマイクロコンピュータ H8S ファミリ/H8S/Tiny シリーズ

| H8S/20103 | R4F20103 |

|-----------|----------|

| H8S/20203 | R4F20203 |

| H8S/20223 | R4F20223 |

| H8S/20115 | R4F20115 |

| H8S/20215 | R4F20215 |

| H8S/20235 | R4F20235 |

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお 断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS 製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI 周辺のノイズが印加され、LSI 内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

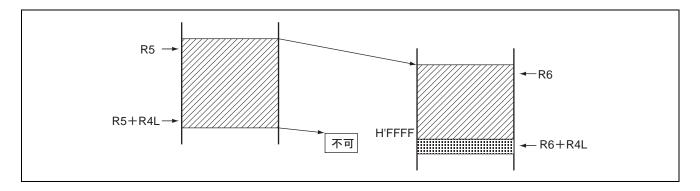

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらの アドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてく ださい。

4. クロックについて

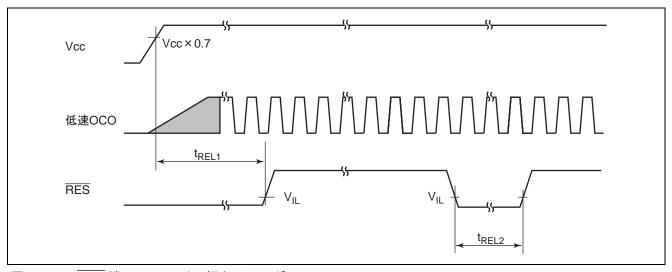

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

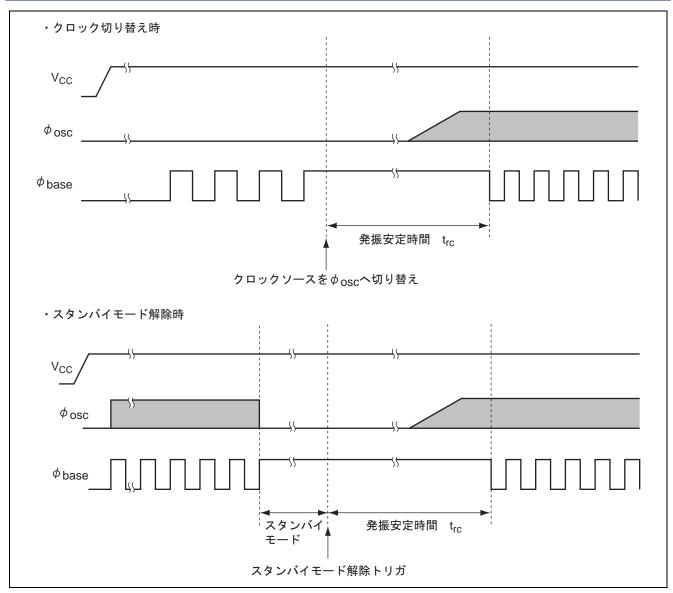

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

同じグループのマイコンでも型名が違うと、内部 ROM、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

## このマニュアルの使い方

## 1. 目的と対象者

このマニュアルは、本マイコンのハードウェア機能と電気的特性をユーザに理解していただくためのマニュアルです。本マイコンを用いた応用システムを設計するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、CPU、システム制御機能、周辺機能、電気的特性、使用上の注意で構成されています。

本マイコンは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中、各章の最後、注意事項の章に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべてを記録したもので はありません。詳細は、このマニュアルの本文でご確認ください。

H8S/20103 グループ、H8S/20203 グループ、H8S/20223 グループ、H8S/20115 グループ、H8S/20215 グループ、H8S/20235 グループでは次のドキュメントを用意しています。ドキュメントは最新版を使用してください。最新版はルネサス エレクトロニクスのホームページに掲載されています。

| ドキュメントの種類                | 記載内容                                                                                | 資料名                                            | 資料番号        |

|--------------------------|-------------------------------------------------------------------------------------|------------------------------------------------|-------------|

| データシート                   | ハードウェアの概要と電気的特性                                                                     | 1                                              | _           |

| ユーザーズマニュアル<br>ハードウェア編    | ハードウェアの仕様(ピン配置、メモリマップ、周辺機能の仕様、電気的特性、タイミング)と動作説明<br>※周辺機能の使用方法はアプリケーションノートを参照してください。 |                                                | 本ユーザーズマニュアル |

| ユーザーズマニュアル<br>ソフトウェア編    | CPU 命令セットの説明                                                                        | H8S/2600 シリーズ、<br>H8S/2000 シリーズ<br>ソフトウェアマニュアル | RJJ09B0143  |

| アプリケーションノート              | 周辺機能の使用方法、応用例<br>参考プログラム<br>アセンブリ言語、C 言語によるプログ<br>ラムの作成方法                           | ルネサス エレクトロニク<br>れています。                         | スホームページに掲載さ |

| RENESAS TECHNICAL UPDATE | 製品の仕様、ドキュメント等に関する 速報                                                                |                                                |             |

## 2. 数や記号の表記

このマニュアルで使用するレジスタ名やビット名、数字や記号の表記の凡例を以下に説明します。

#### (1) 全体的な表記

本文中ではビットの説明をする場合、モジュールやレジスタとの関連を明確にするため、ビット名を「モジュール名・レジスタ名・ビット名」または「レジスタ名・ビット名」と表記している場合があります。

#### (2) レジスタの表記

同一または類似した機能が複数チャネルに存在する場合に「レジスタ名\_チャネル番号」の表記を使用します。 (例) CMCSR\_0: コンペアマッチタイマのチャネル0(\_0) のCMCSRレジスタを示します。

#### (3) 数字の表記

2進数はB'nnnn(明らかに2進数と判断できる場合はB'を省略)、16進数はH'nnnnまたは0xnnnn、10進数はnnnnで表します。

(例) 2進数: B'11または11

16進数: H'EFA0または0xEFA0

10進数:1234

#### (4) ローアクティブの表記

ローアクティブの信号および端子には上線を付けて表記しています。

#### (例) WDTOVF

【注】 上記した図中のビット名や文章は例であり、マニュアルの内容とは関係がありません。

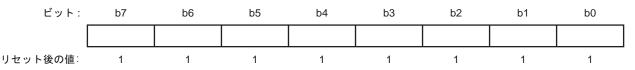

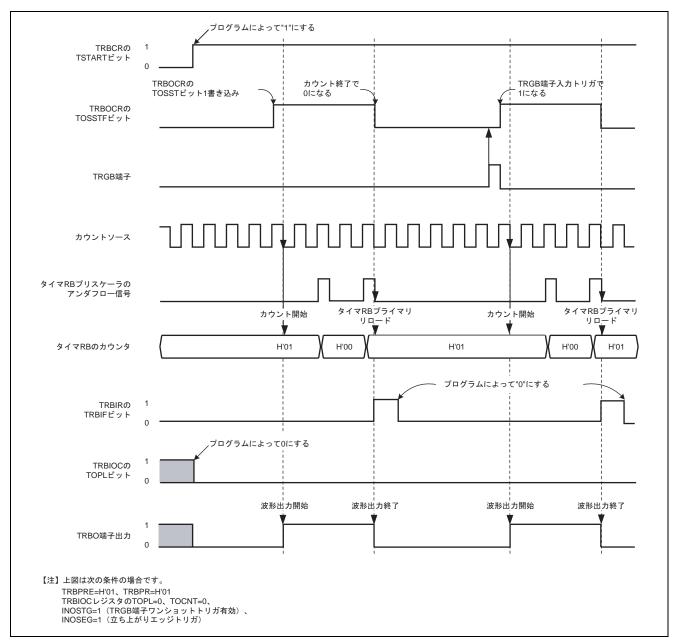

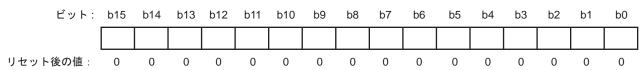

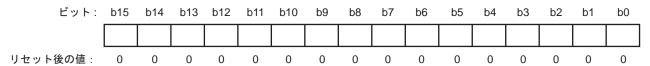

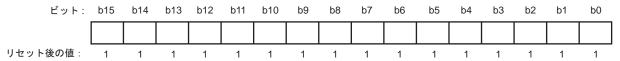

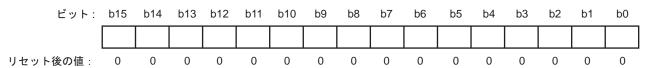

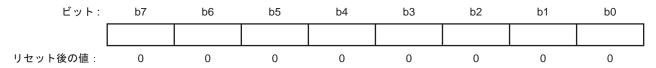

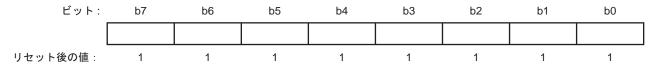

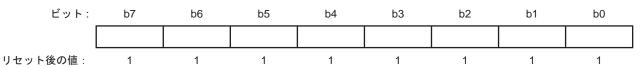

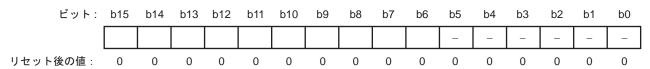

## 3. レジスタの表記

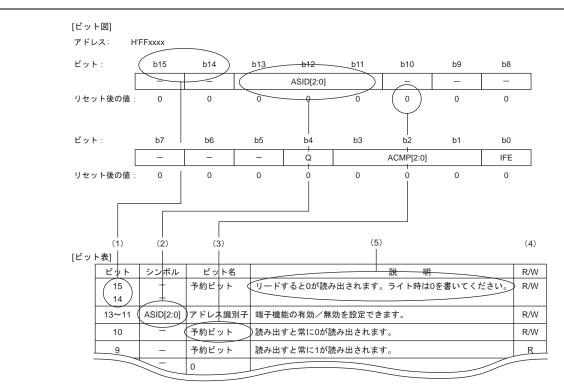

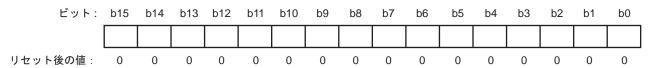

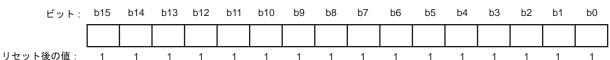

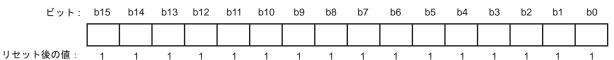

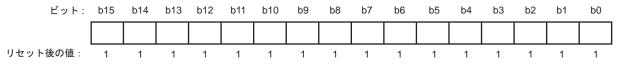

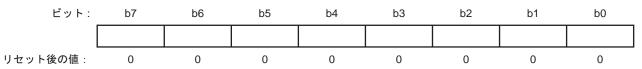

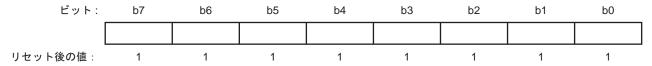

各レジスタの説明には、ビットの並びを示すビット図とビットに設定する内容を説明するビット表があります。

使用する記号、用語を以下に説明します。

【注】 上記した図中のビット名や文章は例であり、マニュアルの内容とは関係がありません。

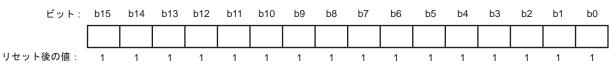

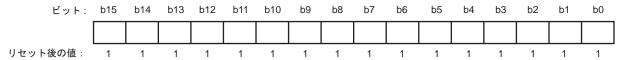

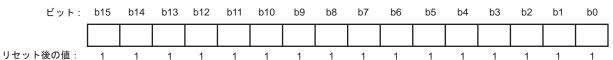

#### (1) ビット

ビット番号を示します。

32ビットレジスタの場合は31から0の順に、16ビットレジスタの場合は15から0の順に示します。

#### (2) シンボル

ビット名またはフィールド名を示します。

フィールドでビット桁数を明示する必要があるときは、ASID[3:0]というように桁数の表記を追加します。

また、リザーブビットの場合は「一」と表記します。

ただし、タイムカウンタなどをはじめとして、ビット名の記載をせずに空白のままとしているものもあります。

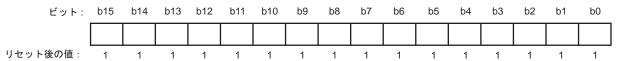

#### (3) リセット後の値

各ビットのパワーオンリセット後の値を初期値として示します。

3 : 初期値は0であることを示します。1 : 初期値は1であることを示します。- : 初期値は不定であることを示します。

#### (4) R/W

各ビットが読み出し可能か、書き込み可能か、または書き込みも読み出しも不可であるかを示します。 使用する表記を以下に説明します。

R/W:読み出しおよび書き込みが可能なビットまたはフィールドです。

R/(W) : 読み出しおよび書き込みが可能なビットまたはフィールドです。

ただし書き込みは、フラグをクリアするための書き込みのみ可能です。

R:読み出しが可能なビットまたはフィールドです。

リザーブビットはすべて「R」と表記します。書き込む必要がある場合は、

ビット表で指定された値を書き込んでください。

W:書き込みが可能なビットまたはフィールドです。

#### (5) 説明

ビットの機能について説明しています。

## 4. 略語および略称の説明

| 略語/略称 | 英語名                                          | 日本語名                       |

|-------|----------------------------------------------|----------------------------|

| ACIA  | Asynchronous Communication Interface Adapter | 調歩同期式通信アダプタ                |

| bps   | bits per second                              | 転送速度を表す単位、ビット/秒            |

| CRC   | Cyclic Redundancy Check                      | 巡回冗長検査                     |

| DMA   | Direct Memory Access                         | CPUの命令を介さずに直接データ転送を行う方式    |

| DMAC  | Direct Memory Access Controller              | DMA を行うコントローラ              |

| GSM   | Global System for Mobile Communications      | FDD-TDMA の第二世代携帯電話の方式      |

| Hi-Z  | High Impedance                               | 回路が電気的に接続されていない状態          |

| IEBus | Inter Equipment bus                          | _                          |

| I/O   | Input/Output                                 | 入出力                        |

| IrDA  | Infrared Data Association                    | 赤外線通信の業界団体または規格            |

| LSB   | Least Significant Bit                        | 最下位ビット                     |

| MSB   | Most Significant Bit                         | 最上位ビット                     |

| NC    | Non-Connection                               | 未接続                        |

| PLL   | Phase Locked Loop                            | 位相同期回路                     |

| PWM   | Pulse Width Modulation                       | パルス幅変調                     |

| SFR   | Special Function Registers                   | 周辺機能を制御するためのレジスタ           |

| SIM   | Subscriber Identity Module                   | ISO/IEC 7816 規定の接触型 IC カード |

| UART  | Universal Asynchronous Receiver/Transmitter  | 調歩同期式シリアルインタフェース           |

| VCO   | Voltage Controlled Oscillator                | 電圧制御発振器                    |

# 目次

| 1. | 概要.   |                                               | 1-1  |

|----|-------|-----------------------------------------------|------|

|    | 1.1   | 特長                                            | 1-1  |

|    | 1.1.1 | 用途                                            | 1-1  |

|    | 1.1.2 | 仕様概要                                          | 1-2  |

|    | 1.2   | 製品一覧                                          | 1-5  |

|    | 1.3   | ブロック図                                         | 1-7  |

|    | 1.4   | ピン配置図                                         | 1-10 |

|    | 1.4.1 | 端子機能                                          | 1-13 |

| 2. | CPU   |                                               | 2-1  |

|    | 2.1   | 特長                                            | 2-1  |

|    | 2.1.1 | H8S/2600 CPU と H8S/2000 CPU との相違点             | 2-2  |

|    | 2.1.2 | H8/300 CPU との相違点                              | 2-2  |

|    | 2.1.3 | H8/300H CPU との相違点                             | 2-3  |

|    | 2.2   | CPU動作モード                                      | 2-4  |

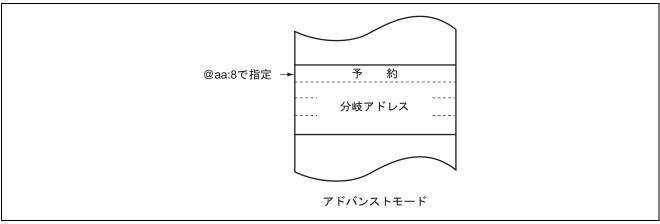

|    | 2.2.1 | アドバンストモード                                     | 2-4  |

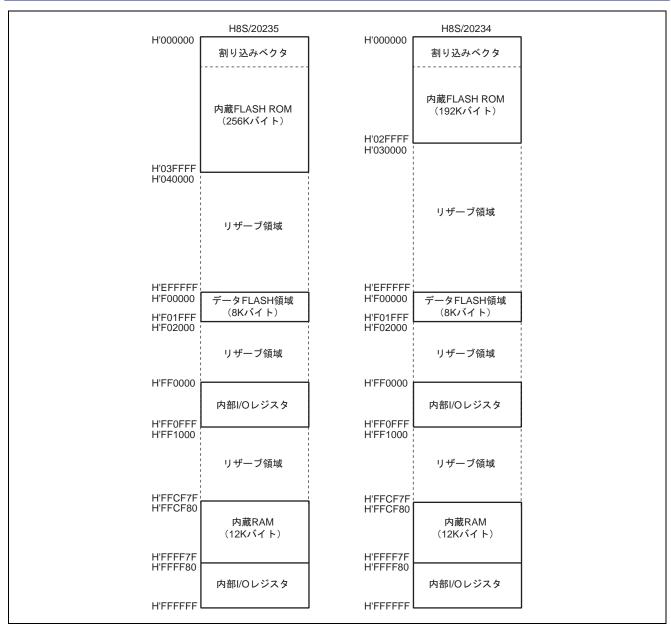

|    | 2.3   | アドレス空間                                        | 2-6  |

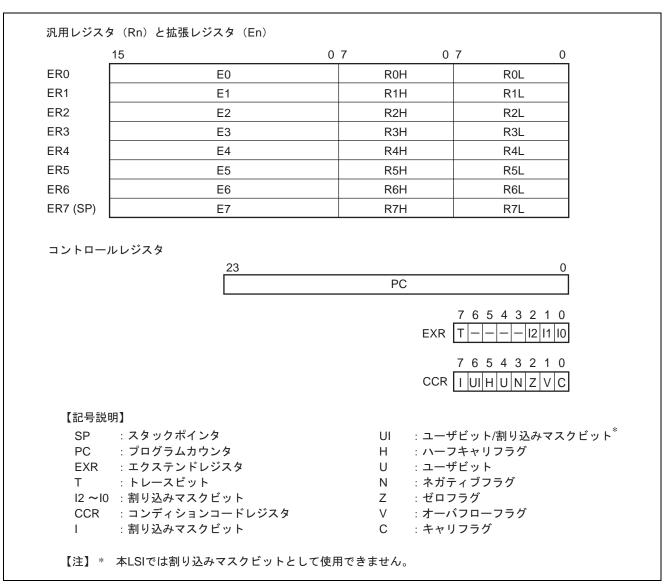

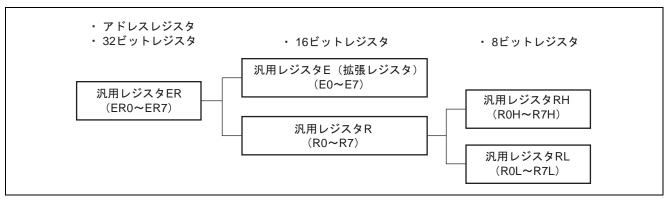

|    | 2.4   | レジスタの構成                                       | 2-12 |

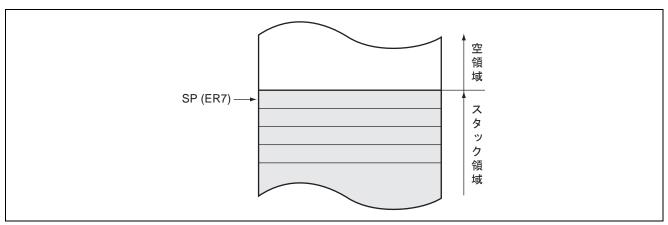

|    | 2.4.1 | 汎用レジスタ                                        | 2-13 |

|    | 2.4.2 | プログラムカウンタ(PC)                                 | 2-14 |

|    | 2.4.3 | エクステンドレジスタ(EXR)                               | 2-14 |

|    | 2.4.4 | コンディションコードレジスタ(CCR)                           | 2-14 |

|    | 2.4.5 | <b>CP</b> U 内部レジスタの初期値                        | 2-16 |

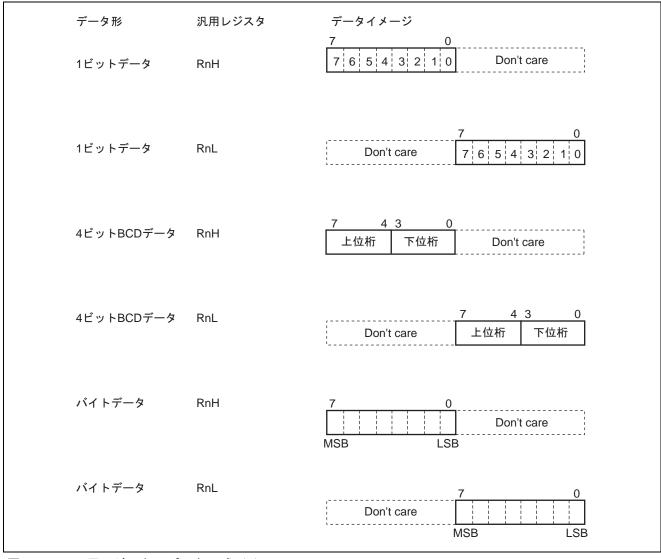

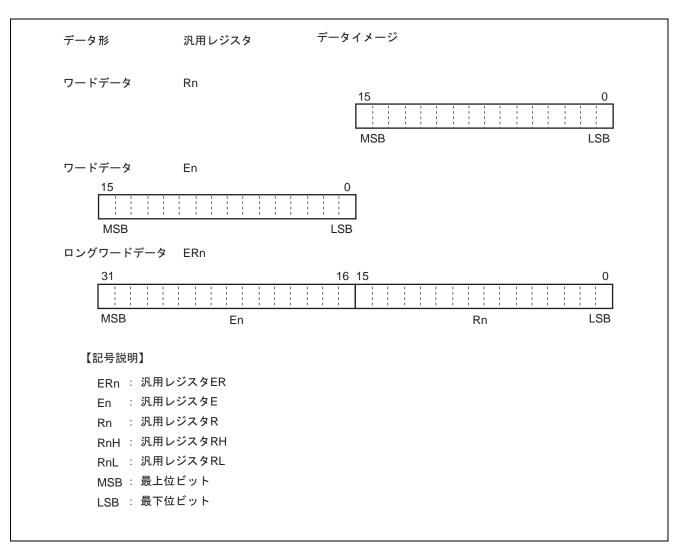

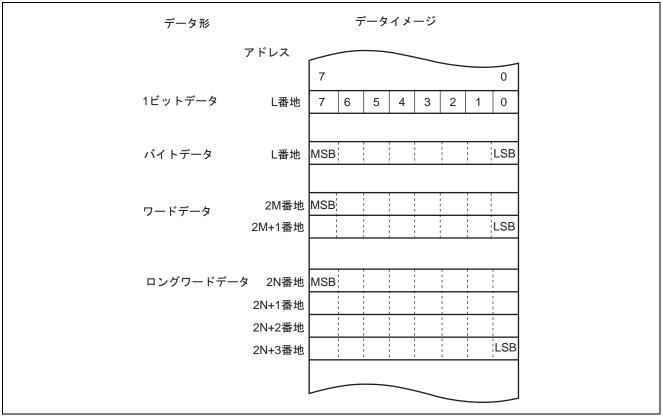

|    | 2.5   | データ形式                                         | 2-17 |

|    | 2.5.1 | 汎用レジスタのデータ形式                                  | 2-17 |

|    | 2.5.2 | メモリ上でのデータ形式                                   | 2-19 |

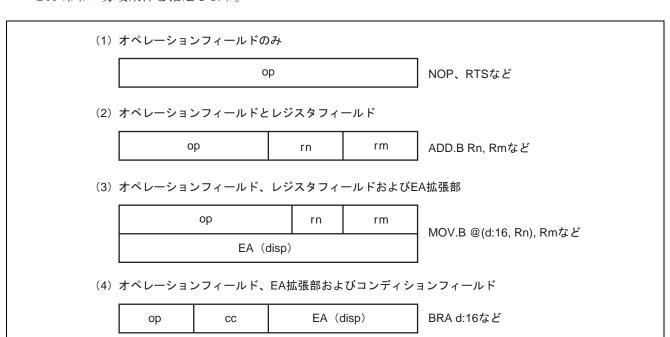

|    | 2.6   | 命令セット                                         | 2-20 |

|    | 2.6.1 | 命令の機能別一覧                                      | 2-21 |

|    | 2.6.2 | 命令の基本フォーマット                                   | 2-30 |

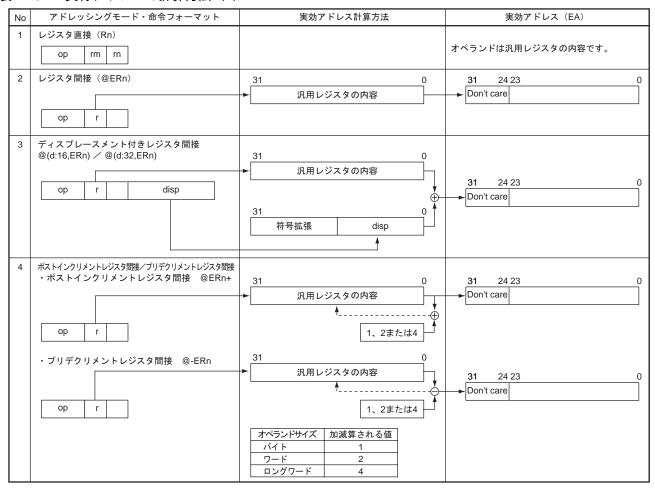

|    | 2.7   | アドレッシングモードと実効アドレスの計算方法                        | 2-31 |

|    | 2.7.1 | レジスタ直接 Rn                                     |      |

|    | 2.7.2 | レジスタ間接 @ERn                                   |      |

|    | 2.7.3 | ディスプレースメント付きレジスタ間接 @ (d:16,ERn) /@ (d:32,ERn) | 2-31 |

|    | 2.7.4 | ポストインクリメントレジスタ間接@ERn+/プリデクリメントレジスタ間接@-ERn     | 2-32 |

|    | 2.7.5 | 絶対アドレス @aa:8/@aa:16/@aa:24/@aa:32     | 2-32 |

|----|-------|---------------------------------------|------|

|    | 2.7.6 | イミディエイト #xx:8/#xx:16/#xx:32           | 2-33 |

|    | 2.7.7 | プログラムカウンタ相対 @ (d:8, PC) /@ (d:16, PC) | 2-33 |

|    | 2.7.8 | メモリ間接 @@aa:8                          | 2-33 |

|    | 2.7.9 | 実効アドレスの計算方法                           | 2-34 |

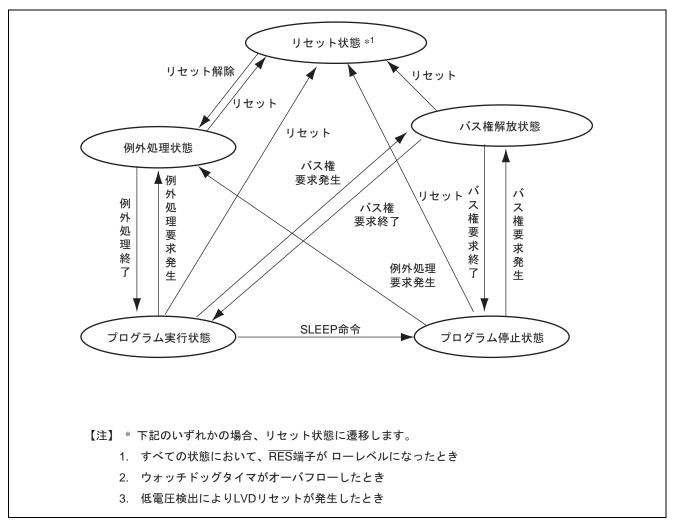

|    | 2.8   | 処理状態                                  | 2-36 |

|    | 2.9   | 使用上の注意事項                              | 2-38 |

|    | 2.9.1 | TAS 命令                                | 2-38 |

|    | 2.9.2 | STM/LDM 命令                            | 2-38 |

|    | 2.9.3 | ビット操作命令                               | 2-38 |

|    | 2.9.4 | EEPMOV 命令                             | 2-39 |

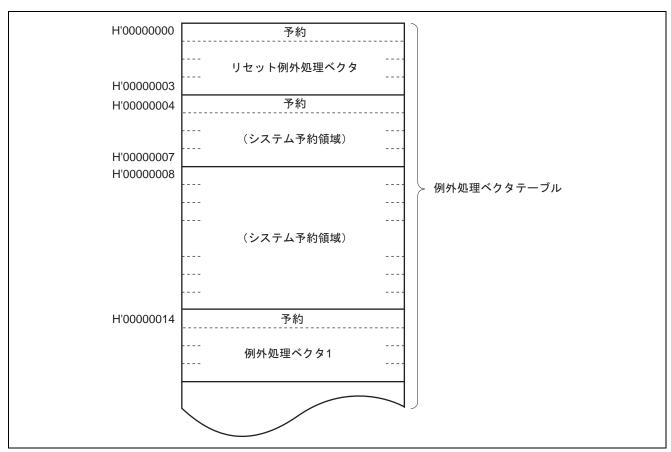

| 3. | 例外    | 心理                                    | 3-1  |

|    | 3.1   | 例外処理の種類と優先度                           | 3-1  |

|    | 3.2   | 例外処理要因とベクタテーブル                        | 3-2  |

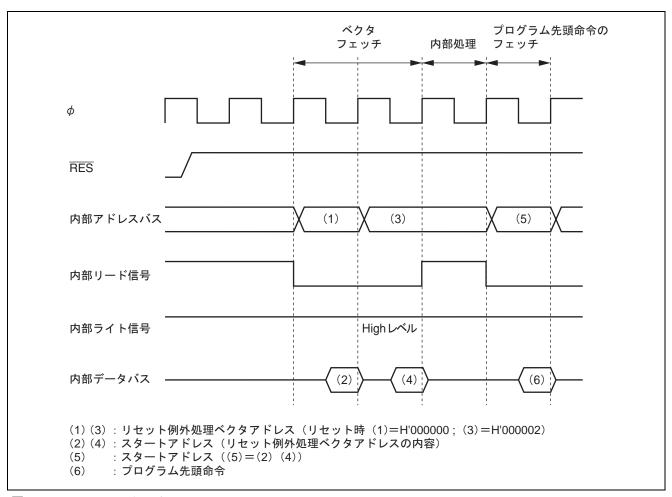

|    | 3.3   | リセット                                  | 3-2  |

|    | 3.3.1 | リセット要因                                | 3-2  |

|    | 3.3.2 | リセット例外処理                              | 3-5  |

|    | 3.3.3 | リセット直後の割り込み                           | 3-6  |

|    | 3.3.4 | リセット解除後の内蔵周辺機能                        | 3-6  |

|    | 3.4   | トレース例外処理                              | 3-6  |

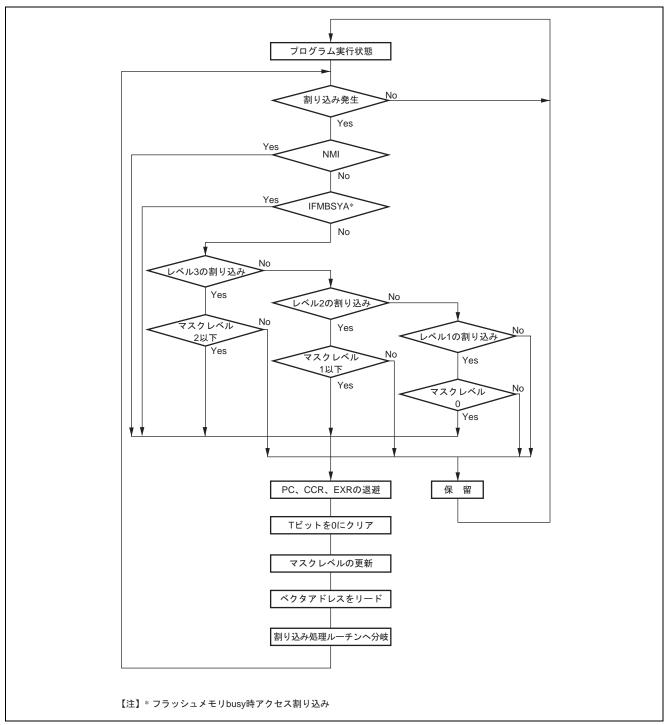

|    | 3.5   | 割り込み例外処理                              | 3-7  |

|    | 3.6   | トラップ命令例外処理                            | 3-7  |

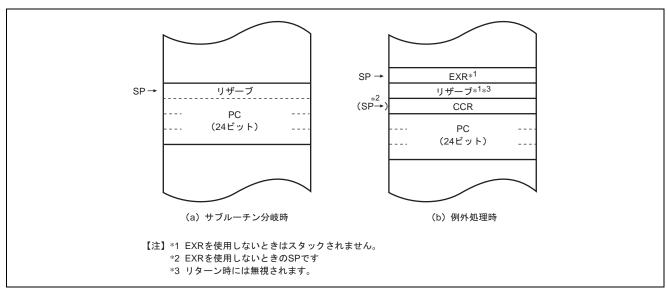

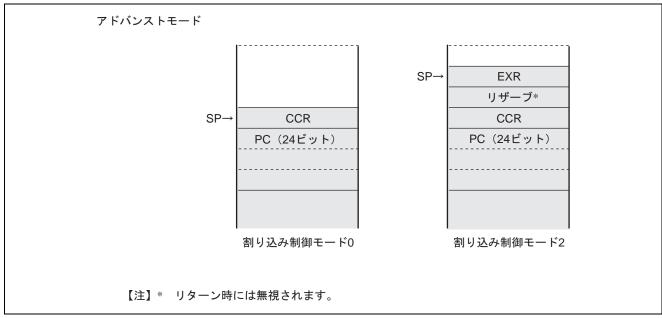

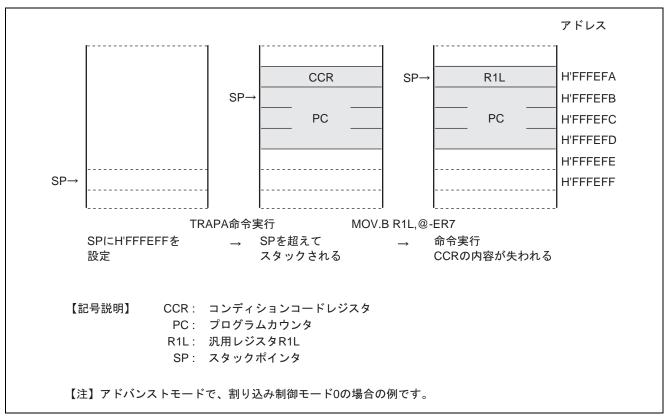

|    | 3.7   | 例外処理後のスタックの状態                         | 3-8  |

|    | 3.8   | 使用上の注意事項                              | 3-9  |

| 4. | 割り    | <u> </u>                              | 4-1  |

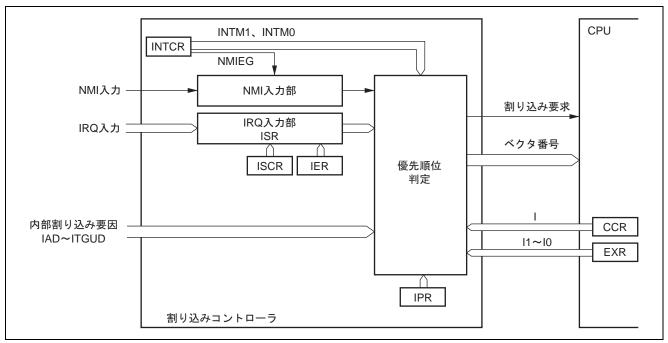

|    | 4.1   | 概要                                    | 4-1  |

|    | 4.2   | レジスタの説明                               | 4-3  |

|    | 4.2.1 | インタラプトコントロールレジスタ(INTCR)               | 4-4  |

|    | 4.2.2 | インタラプトプライオリティレジスタ A~I(IPRA~IPRI)      | 4-5  |

|    | 4.2.3 | IRQ イネーブルレジスタ(IER)                    | 4-7  |

|    | 4.2.4 | IRQ センスコントロールレジスタ H、L(ISCRH、ISCRL)    | 4-8  |

|    | 4.2.5 | IRQ ステータスレジスタ(ISR)                    | 4-10 |

|    | 4.2.6 | IRQ ノイズキャンセラコントロールレジスタ(INCCR)         | 4-11 |

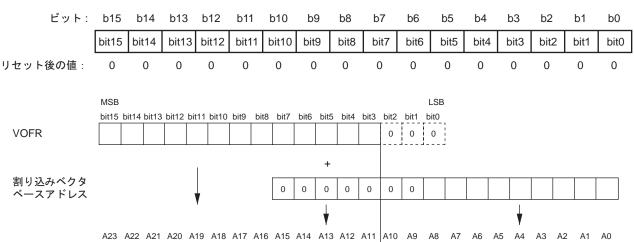

|    | 4.2.7 | 割り込みベクタオフセットレジスタ(VOFR)                | 4-12 |

|    | 4.2.8 | イベントリンク割り込みコントロールステータスレジスタ(ELCSR)     | 4-13 |

|    | 4.3   | 割り込み要因                                | 4-14 |

|    |       |                                       |      |

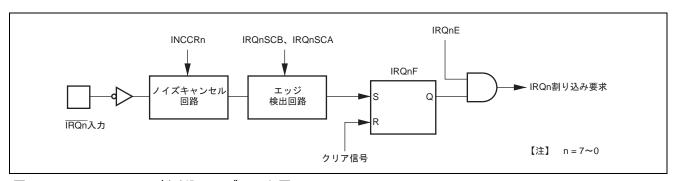

| 4.3.1        | 外部割り込み要因                               | 4-14 |

|--------------|----------------------------------------|------|

| 4.3.2        | 内部割り込み                                 | 4-15 |

| 4.4          | 割り込み例外処理ベクタテーブル                        | 4-15 |

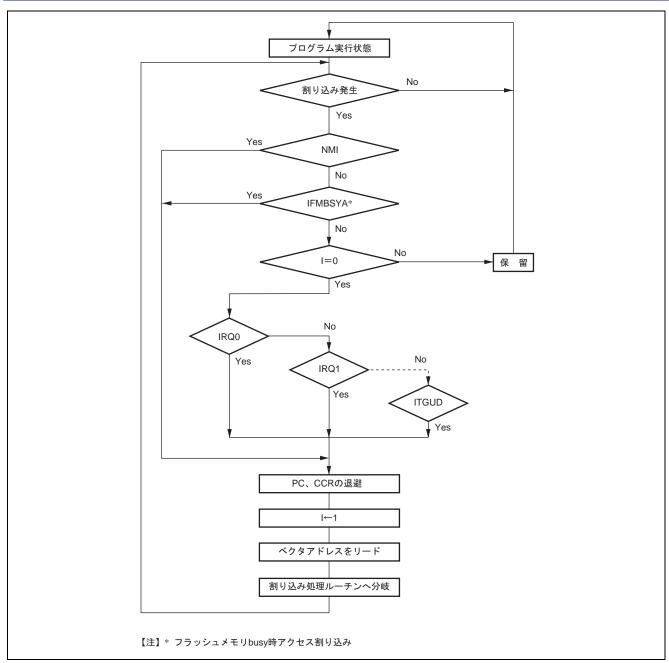

| 4.5          | 割り込み制御モードと割り込み動作                       | 4-21 |

| 4.5.1        | 割り込み制御モード 0                            | 4-21 |

| 4.5.2        | 割り込み制御モード 2                            | 4-23 |

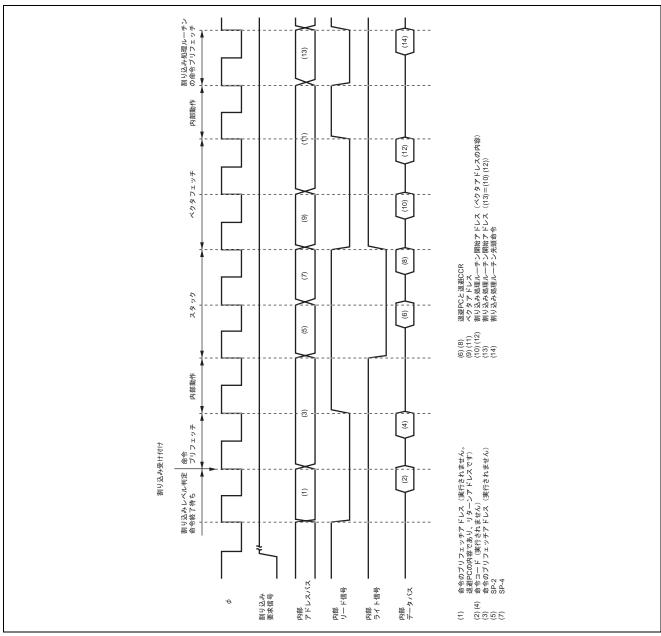

| 4.5.3        | 割り込み例外処理シーケンス                          | 4-25 |

| 4.5.4        | 割り込み応答時間                               | 4-26 |

| 4.5.5        | 割り込みによる DTC の起動                        | 4-26 |

| 4.6          | 使用上の注意事項                               | 4-27 |

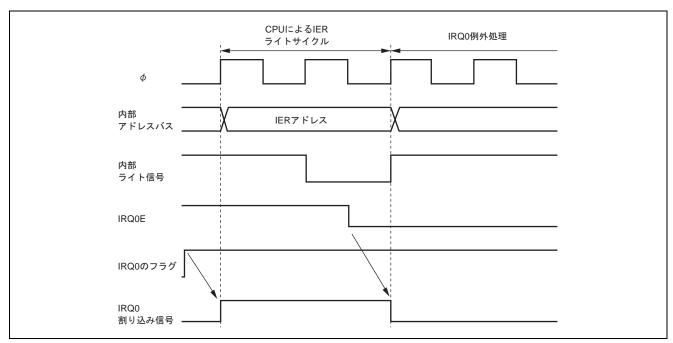

| 4.6.1        | 割り込みの発生とディスエーブルとの競合                    | 4-27 |

| 4.6.2        | 割り込みを禁止している命令                          | 4-28 |

| 4.6.3        | 割り込み禁止期間                               | 4-28 |

| 4.6.4        | EEPMOV 命令実行中の割り込み                      | 4-28 |

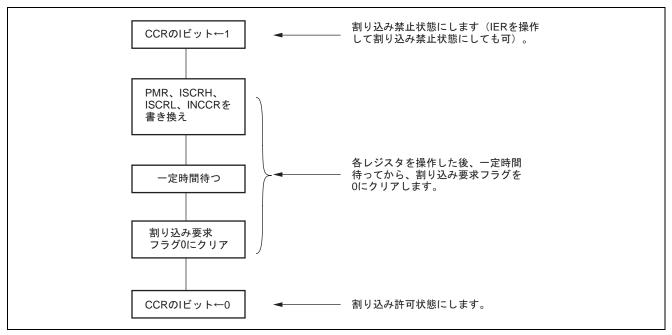

| 4.6.5        | PMR、ISCRH、ISCRL、INCCR レジスタを書き替える際の注意事項 | 4-29 |

| 4.6.6        | IRQ ステータスレジスタ(ISR)について                 | 4-29 |

| 4.6.7        | NMI 端子の注意事項                            | 4-29 |

| 5. クロ        | ック発振器                                  | 5-1  |

| 5.1          | 概要                                     | 5-1  |

| 5.2          | レジスタの説明                                | 5-3  |

| 5.2.1        | バックアップコントロールレジスタ(BAKCR)                | 5-4  |

| 5.2.2        | システムクロックコントロールレジスタ(SYSCCR)             | 5-6  |

| 5.2.3        | 低消費電力制御レジスタ 1(LPCR1)                   | 5-8  |

| 5.2.4        | 低消費電力制御レジスタ 2(LPCR2)                   | 5-10 |

| 5.2.5        | 低消費電力制御レジスタ 3(LPCR3)                   | 5-11 |

| 5.2.6        | OSC 発振安定コントロールステータスレジスタ(OSCCSR)        | 5-13 |

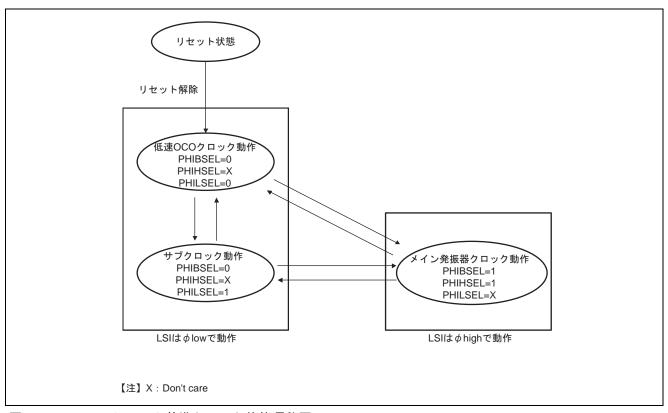

| 5.3          | システム基準クロック選択の動作説明                      | 5-15 |

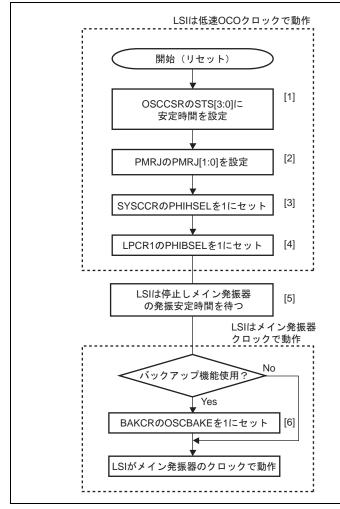

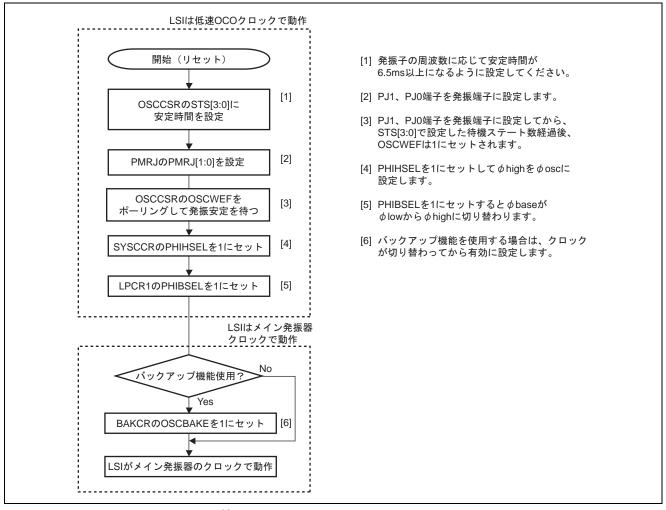

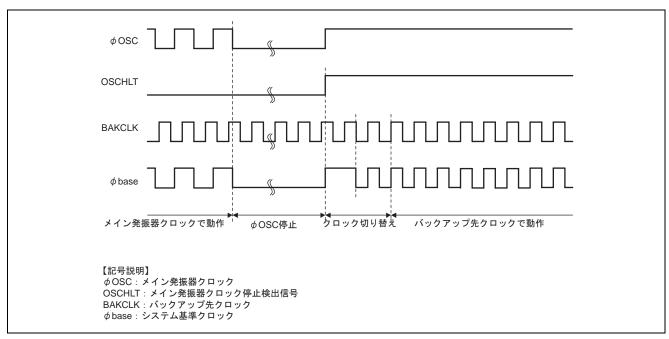

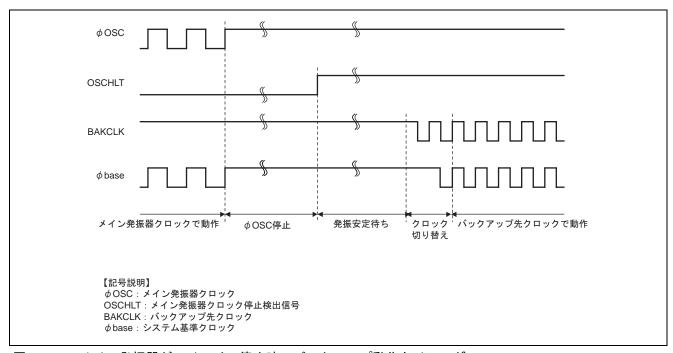

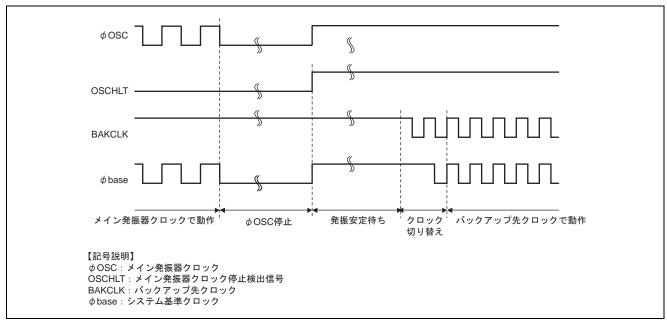

| 5.3.1        | φosc へのシステム基準クロック切り替え動作                | 5-17 |

| 5.3.2        | クロック切り替えタイミング                          | 5-19 |

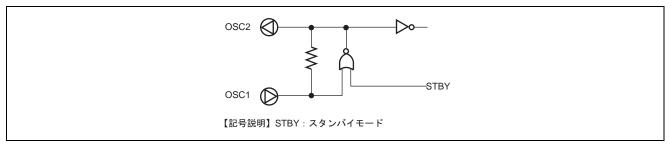

| 5.3.3        | バックアップ動作説明                             | 5-21 |

| 5.4          | メインクロック発振器                             | 5-24 |

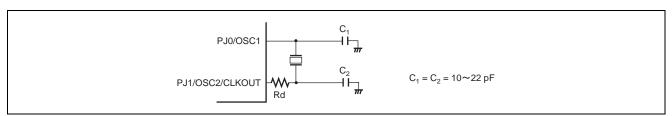

| 5.4.1        | 水晶発振子を接続する方法                           | 5-24 |

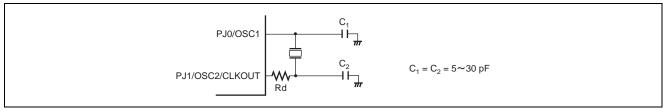

| 5.4.2        | セラミック振子を接続する方法                         | 5-24 |

|              |                                        |      |

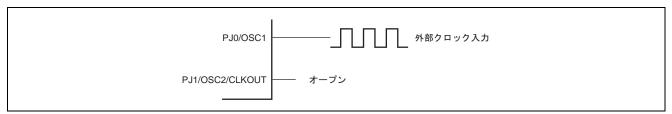

| 5.4.3        | 外部クロックを入力する方法                          | 5-25 |

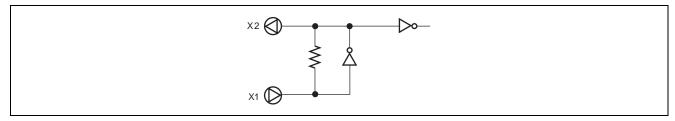

| 5.4.3<br>5.5 | 外部クロックを入力する方法<br>サブクロック発振器             |      |

|              |                                        | 5-26 |

| 5.6    | プリスケーラ (PSC分周器)                      | 5-26 |

|--------|--------------------------------------|------|

| 5.7    | 使用上の注意事項                             | 5-27 |

| 5.7.1  | 発振子に関する注意事項                          | 5-27 |

| 5.7.2  | ボード設計上の注意事項                          | 5-27 |

| 6. 低消  | 費電力状態                                | 6-1  |

| 6.1    | レジスタの説明                              | 6-2  |

| 6.1.1  | 低消費電力制御レジスタ 1、2、3(LPCR1、LPCR2、LPCR3) | 6-3  |

| 6.1.2  | モジュールスタンバイコントロールレジスタ 1(MSTCR1)       | 6-3  |

| 6.1.3  | モジュールスタンバイコントロールレジスタ 2 (MSTCR2)      | 6-4  |

| 6.1.4  | モジュールスタンバイコントロールレジスタ 3 (MSTCR3)      | 6-5  |

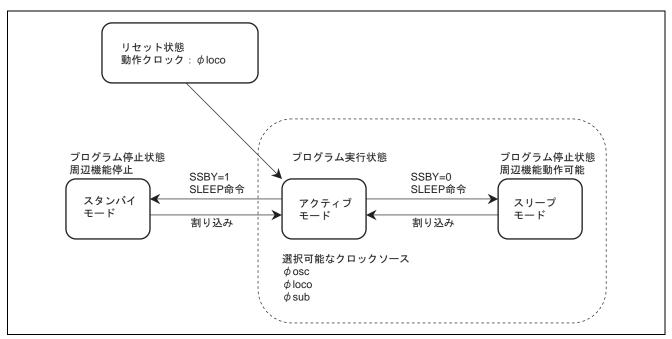

| 6.2    | モード間遷移とLSIの状態                        | 6-7  |

| 6.2.1  | アクティブモード                             | 6-9  |

| 6.2.2  | スリープモード                              | 6-9  |

| 6.2.3  | スタンバイモード                             | 6-9  |

| 6.3    | バスマスタクロック分周機能                        | 6-10 |

| 6.3.1  | リセット状態                               | 6-10 |

| 6.4    | モジュールスタンバイ機能                         | 6-10 |

| 6.5    | PSC分周器停止機能                           | 6-10 |

| 7. ROM | 1                                    | 7-1  |

| 7.1    | 概要                                   | 7-1  |

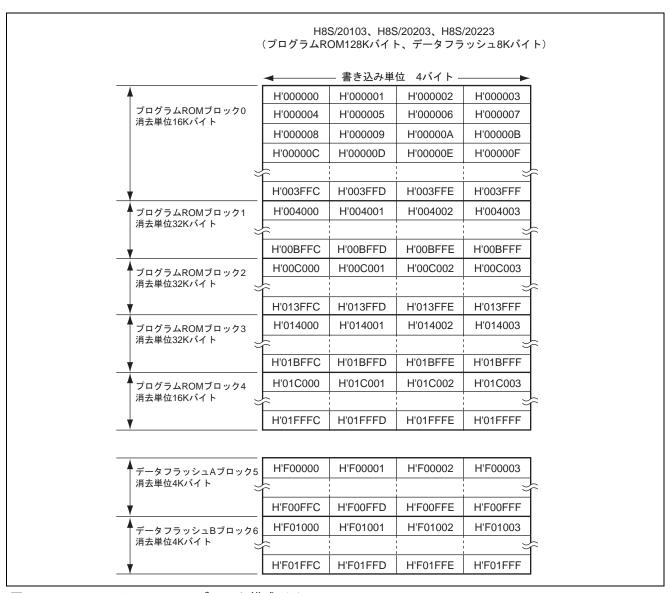

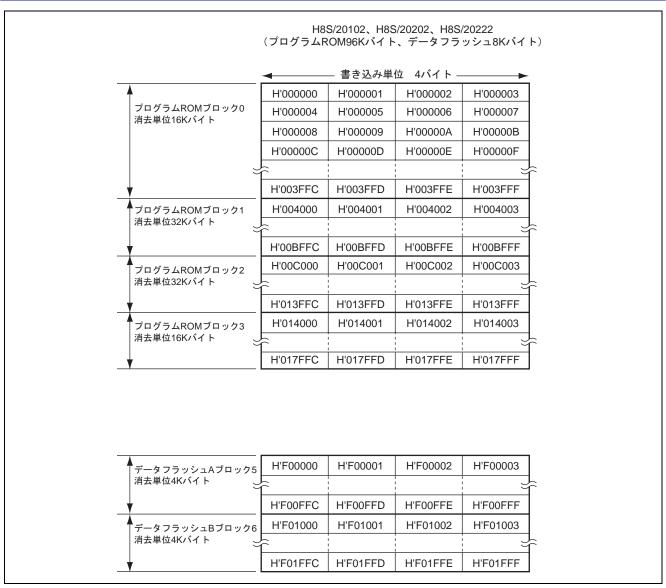

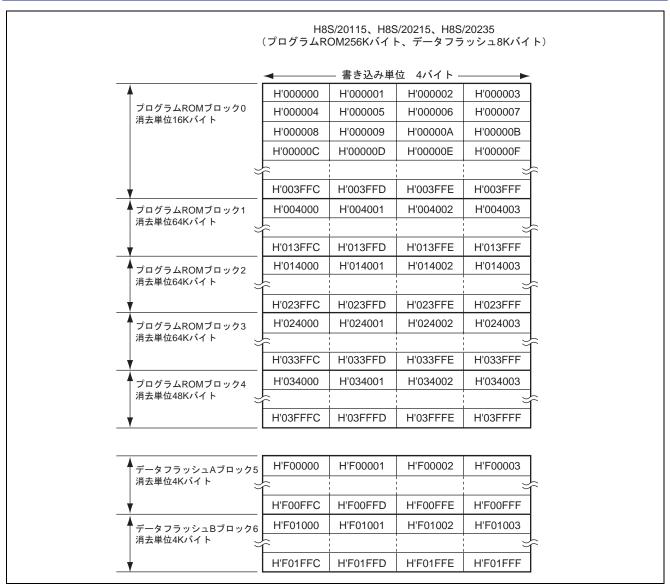

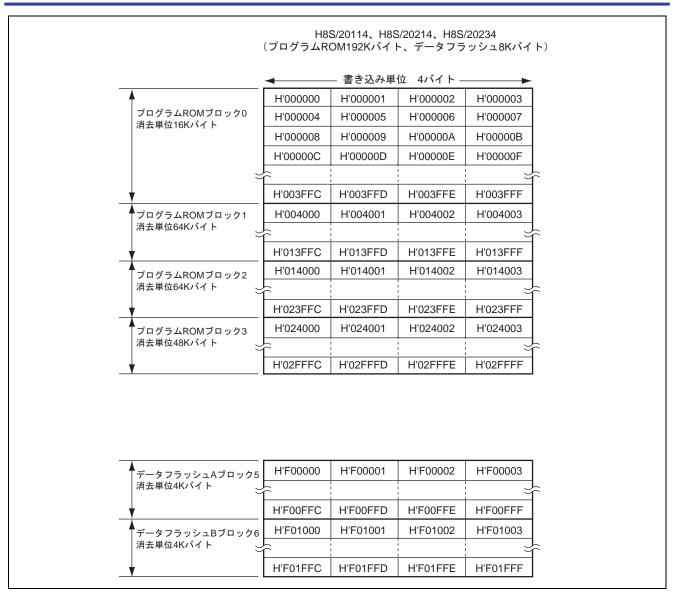

| 7.2    | ブロック構成                               | 7-2  |

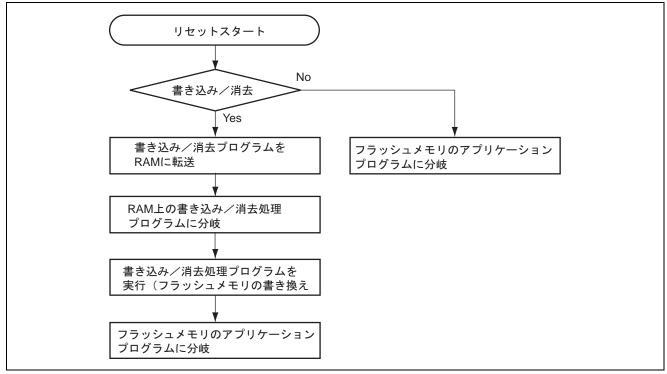

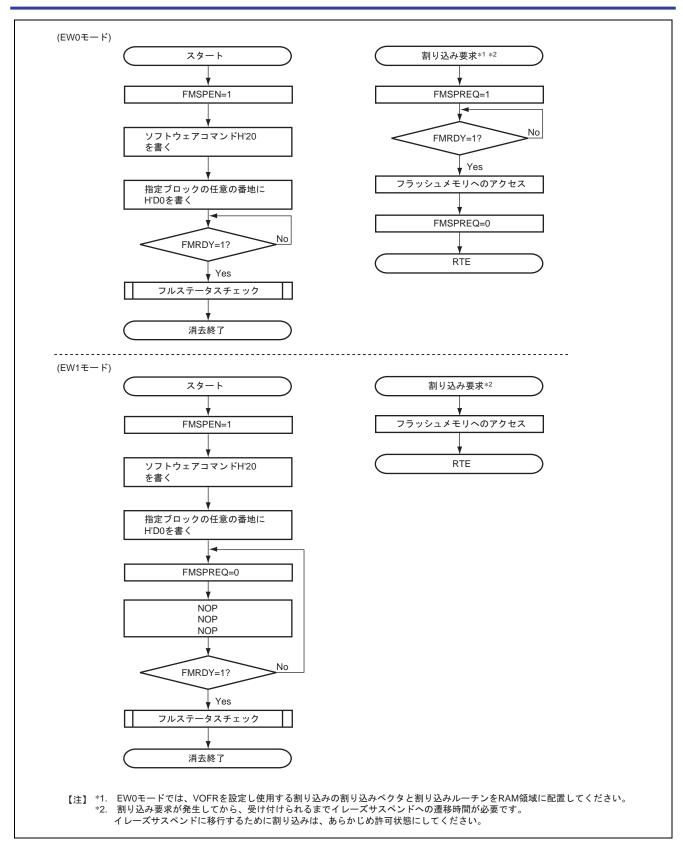

| 7.3    | <b>CPU書き換えモード</b>                    | 7-6  |

| 7.3.1  | EW0 モード                              | 7-7  |

| 7.3.2  | EW1 モード                              | 7-7  |

| 7.4    | レジスタの説明                              | 7-8  |

| 7.4.1  | フラッシュメモリコントロールレジスタ 1(FLMCR1)         | 7-8  |

| 7.4.2  | フラッシュメモリコントロールレジスタ 2(FLMCR2)         | 7-10 |

| 7.4.3  | フラッシュメモリデータフラッシュプロテクトレジスタ(DFPR)      | 7-12 |

| 7.4.4  | フラッシュメモリステータスレジスタ(FLMSTR)            | 7-13 |

| 7.5    | オンボードプログラミング                         | 7-15 |

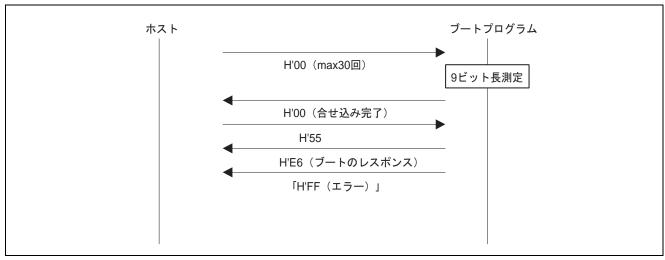

| 7.5.1  | ブートモード                               | 7-15 |

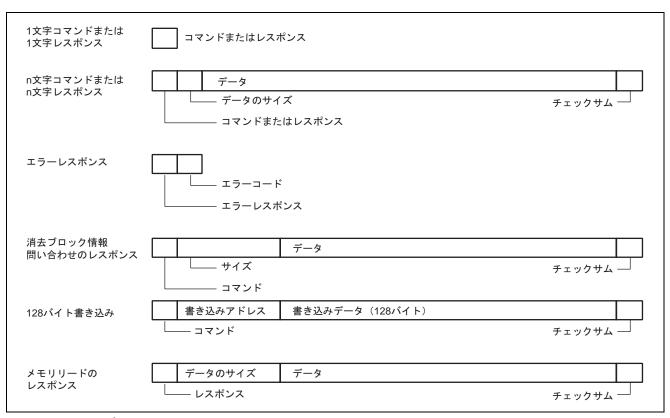

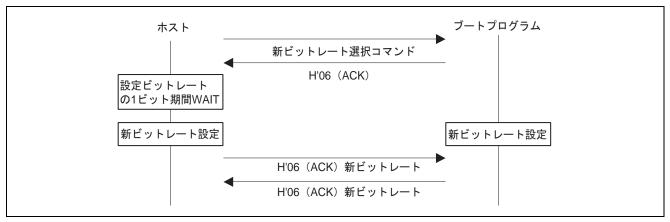

| 7.5.2  | ブートモードの標準シリアル通信インタフェース仕様             | 7-19 |

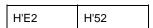

| 7.5.3  | ユーザモードでの書き込み/消去                      | 7-49 |

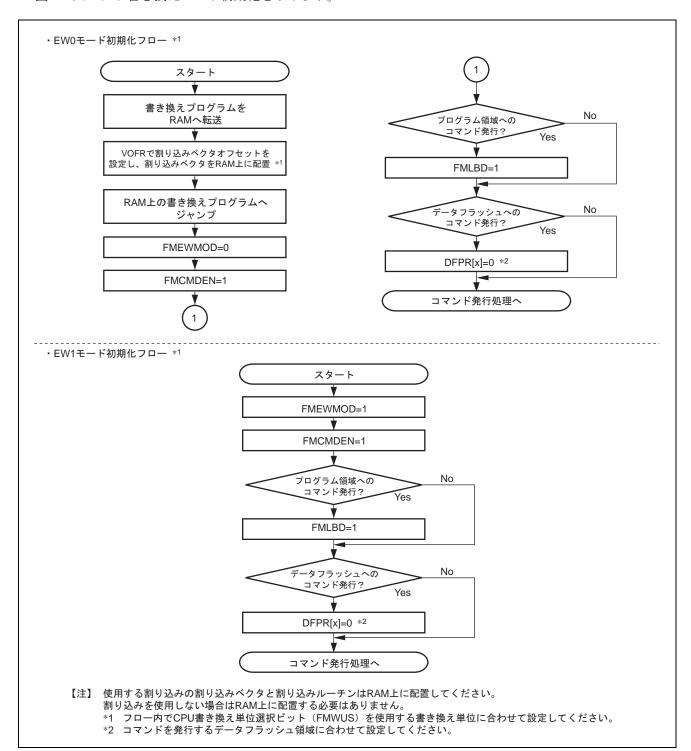

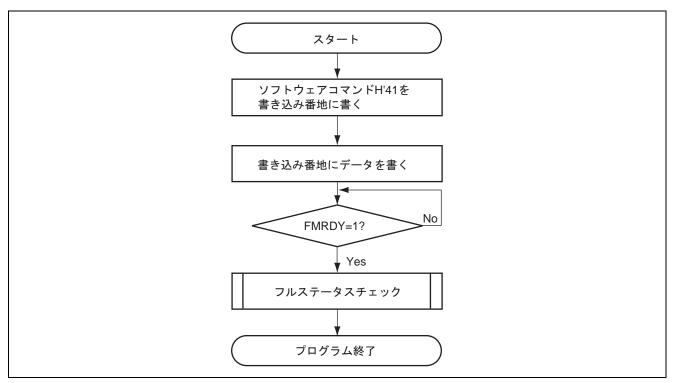

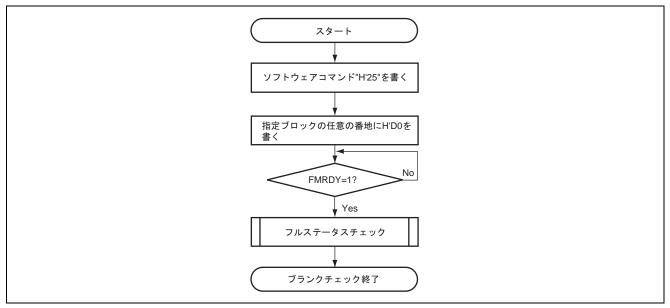

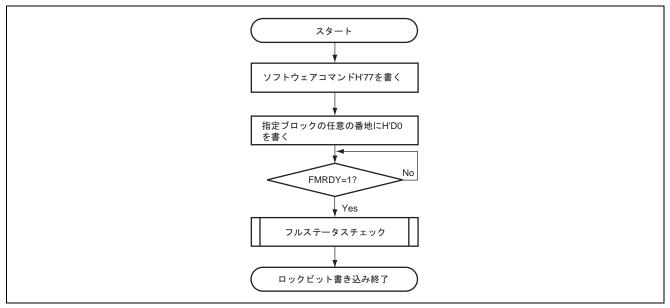

| 7.6    | 書き込み/消去処理                            | 7-50 |

| 7.6.1  | ソフトウェアコマンド                           | 7-50 |

| 7.7    | プロテクト                                | 7-63 |

| 7.7.1      | ソフトウェアプロテクト                                 | 7-63  |

|------------|---------------------------------------------|-------|

| 7.7.2      | ロックビットプロテクト                                 | 7-63  |

| 7.7.3      | PROM ライタプロテクト/ブートモードプロテクト                   | 7-63  |

| 7.8 ラ      | イタモード                                       | 7-64  |

| 7.9 使      | 用上の注意事項                                     | 7-65  |

| 8. RAM     |                                             | 8-1   |

| 9. 周辺機能    | マッピングコントローラ(PMC)                            | 9-1   |

| 9.1 V      | ジスタの説明                                      | 9-3   |

| 9.1.1      | 周辺機能マッピングレジスタ書き込みプロテクトレジスタ (PMCWPR)         | 9-4   |

| 9.1.2      | ポートグループ 1 周辺機能マッピングレジスタ 1~4 (PMCRn1~PMCRn4) |       |

|            | (n=1, 2, 3, 5, 6)                           | 9-5   |

| 9.1.3      | ポートグループ 2 周辺機能マッピングレジスタ 1~4 (PMCRn1~PMCRn4) |       |

|            | (n=8, 9, A)                                 |       |

|            | 用上の注意事項                                     |       |

| 9.2.1      | ポートのマルチプレクス機能設定手順                           |       |

| 9.2.2      | PMC レジスタ設定する場合の注意事項                         | 9-33  |

| 10. 1/0 ポー | F                                           | 10-1  |

| 10.1 ポ     | − <b>⊦</b> 1                                | 10-2  |

| 10.1.1     | ポートモードレジスタ 1 (PMR1)                         | 10-3  |

| 10.1.2     | ポートコントロールレジスタ 1(PCR1)                       | 10-4  |

| 10.1.3     | ポートデータレジスタ 1 (PDR1)                         | 10-5  |

| 10.1.4     | ポートプルアップコントロールレジスタ 1 (PUCR1)                | 10-6  |

| 10.1.5     | ポートドライブコントロールレジスタ 1(PDVR1)                  | 10-7  |

| 10.2 ポ     | <b>一ト2</b>                                  |       |

| 10.2.1     | ポートモードレジスタ 2 (PMR2)                         |       |

| 10.2.2     | ポートコントロールレジスタ 2 (PCR2)                      |       |

| 10.2.3     | ポートデータレジスタ 2(PDR2)                          |       |

| 10.2.4     | ポートプルアップコントロールレジスタ 2 (PUCR2)                | 10-12 |

| 10.2.5     | ポートドライブコントロールレジスタ 2 (PDVR2)                 | 10-13 |

|            | - \hat{3}                                   |       |

| 10.3.1     | ポートモードレジスタ 3 (PMR3)                         |       |

| 10.3.2     | ポートコントロールレジスタ 3 (PCR3)                      |       |

| 10.3.3     | ポートデータレジスタ 3(PDR3)                          |       |

| 10.3.4     | ポートプルアップコントロールレジスタ 3 (PUCR3)                |       |

| 10.3.5     | ポートドライブコントロールレジスタ 3 (PDVR3)                 |       |

| 10.4 ポ     | ート5                                         | 10-20 |

| 10.4.1  | ポートモードレジスタ 5(PMR5)          | 10-21 |

|---------|-----------------------------|-------|

| 10.4.2  | ポートコントロールレジスタ 5(PCR5)       | 10-22 |

| 10.4.3  | ポートデータレジスタ 5(PDR5)          | 10-23 |

| 10.4.4  | ポートプルアップコントロールレジスタ 5(PUCR5) | 10-24 |

| 10.4.5  | ポートドライブコントロールレジスタ 5(PDVR5)  | 10-25 |

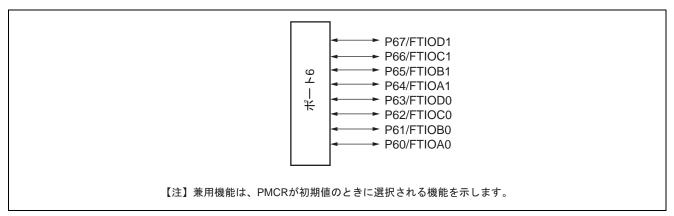

| 10.5 ポ  | °− ⊦6                       | 10-26 |

| 10.5.1  | ポートモードレジスタ 6(PMR6)          |       |

| 10.5.2  | ポートコントロールレジスタ 6(PCR6)       | 10-28 |

| 10.5.3  | ポートデータレジスタ 6(PDR6)          |       |

| 10.5.4  | ポートプルアップコントロールレジスタ 6(PUCR6) | 10-30 |

| 10.5.5  | ポートドライブコントロールレジスタ 6(PDVR6)  | 10-31 |

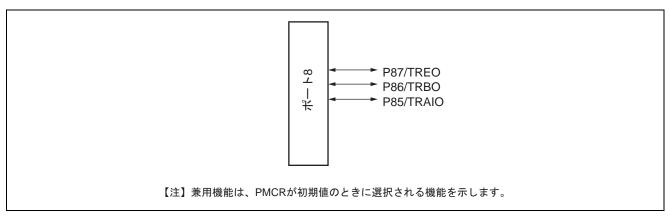

| 10.6 ポ  | °− ⊦8                       | 10-32 |

| 10.6.1  | ポートモードレジスタ 8(PMR8)          | 10-33 |

| 10.6.2  | ポートコントロールレジスタ 8(PCR8)       |       |

| 10.6.3  | ポートデータレジスタ 8(PDR8)          | 10-35 |

| 10.6.4  | ポートプルアップコントロールレジスタ 8(PUCR8) | 10-36 |

| 10.6.5  | ポートドライブコントロールレジスタ 8(PDVR8)  | 10-37 |

| 10.6.6  | ポート8の使用上の注意事項               | 10-37 |

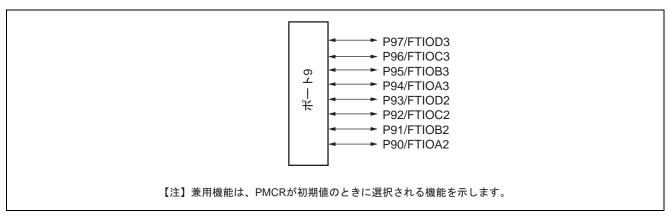

| 10.7 ポ  | °− ⊦9                       | 10-38 |

| 10.7.1  | ポートモードレジスタ 9(PMR9)          | 10-39 |

| 10.7.2  | ポートコントロールレジスタ 9(PCR9)       |       |

| 10.7.3  | ポートデータレジスタ 9(PDR9)          |       |

| 10.7.4  | ポートプルアップコントロールレジスタ 9(PUCR9) |       |

| 10.7.5  | ポートドライブコントロールレジスタ 9(PDVR9)  | 10-43 |

| 10.8 ポ  | <sup>2</sup> −              |       |

| 10.8.1  | ポートモードレジスタ A (PMRA)         |       |

| 10.8.2  | ポートコントロールレジスタ A (PCRA)      | 10-46 |

| 10.8.3  | ポートデータレジスタ A(PDRA)          | 10-47 |

| 10.8.4  | ポートプルアップコントロールレジスタ A(PUCRA) | 10-48 |

| 10.8.5  | ポートモードレジスタ A (PMRA)         |       |

| 10.8.6  | ポートコントロールレジスタ A (PCRA)      |       |

| 10.8.7  | ポートデータレジスタ A(PDRA)          |       |

| 10.8.8  | ポートプルアップコントロールレジスタ A(PUCRA) |       |

| 10.8.9  | ポートモードレジスタ A (PMRA)         |       |

| 10.8.10 | ポートコントロールレジスタ A(PCRA)       | 10-54 |

| 10.8.11 | ポートデータレジスタ A(PDRA)          | 10-55 |

| 10.8.12 | ポートプルアップコントロールレジスタ A(PUCRA) | 10-56 |

| 10.8.13 | ポート A 使用上の注意事項              | 10-57 |

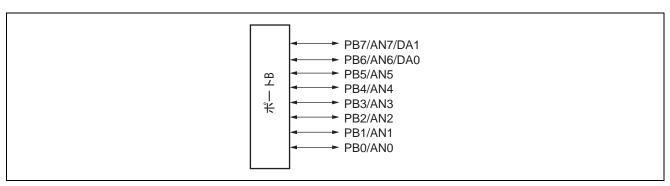

| 10.9 ポ   | <sup>2</sup> − トB                | 10-58 |

|----------|----------------------------------|-------|

| 10.9.1   | ポートコントロールレジスタ B (PCRB)           | 10-59 |

| 10.9.2   | ポートデータレジスタ B(PDRB)               | 10-60 |

| 10.9.3   | ポートプルアップコントロールレジスタ B(PUCRB)      | 10-61 |

| 10.9.4   | ポートB使用上の注意事項                     | 10-62 |

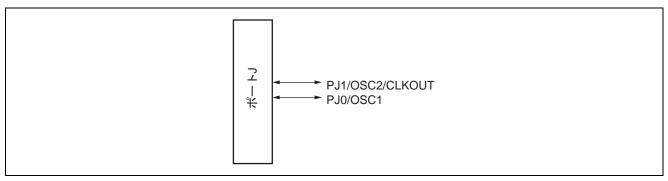

| 10.10 ポ  | <sup>2</sup> —                   | 10-63 |

| 10.10.1  | ポートモードレジスタ J(PMRJ)               | 10-64 |

| 10.10.2  | ポートコントロールレジスタ J(PCRJ)            | 10-65 |

| 10.10.3  | ポートデータレジスタ J(PDRJ)               | 10-66 |

| 10.10.4  | ポートプルアップコントロールレジスタ J(PUCRJ)      | 10-67 |

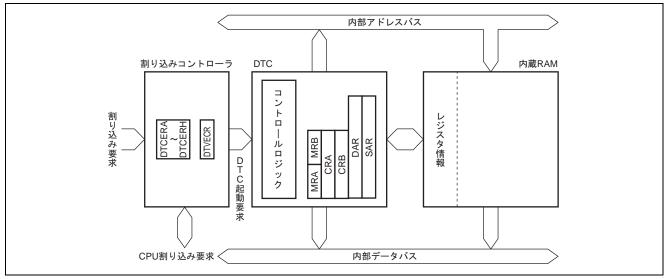

| 11. データト | トランスファコントローラ(DTC)                | 11-1  |

| 11.1 概   | 要                                | 11-1  |

| 11.2 V   | ジスタの説明                           | 11-3  |

| 11.2.1   | DTC モードレジスタ A(MRA)               | 11-4  |

| 11.2.2   | DTC モードレジスタ B(MRB)               | 11-5  |

| 11.2.3   | DTC ソースアドレスレジスタ(SAR)             | 11-6  |

| 11.2.4   | DTC デスティネーションアドレスレジスタ(DAR)       | 11-6  |

| 11.2.5   | DTC 転送カウントレジスタ A(CRA)            | 11-7  |

| 11.2.6   | DTC 転送カウントレジスタ B(CRB)            | 11-7  |

| 11.2.7   | DTC イネーブルレジスタ A~H(DTCERA~DTCERH) | 11-8  |

| 11.2.8   | DTC ベクタレジスタ(DTVECR)              | 11-10 |

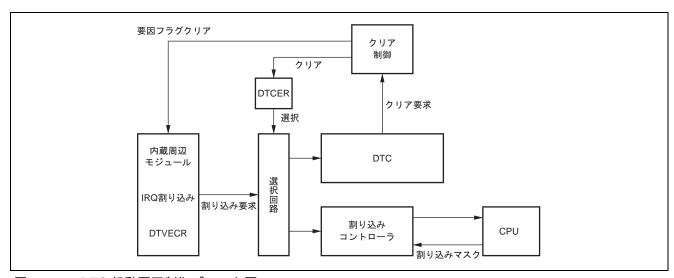

| 11.3 起   | 動要因                              | 11-11 |

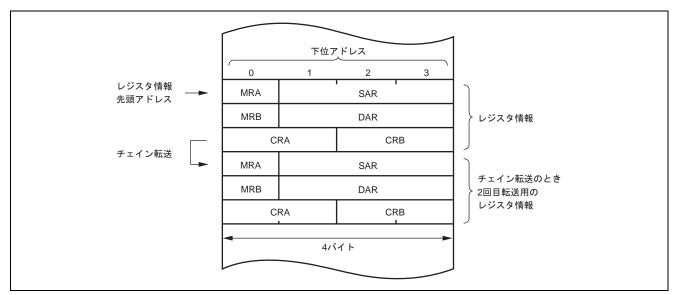

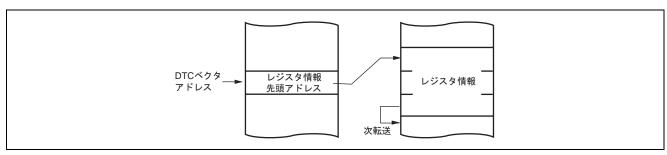

| 11.4 V   | ジスタ情報の配置とDTCベクタテーブル              | 11-12 |

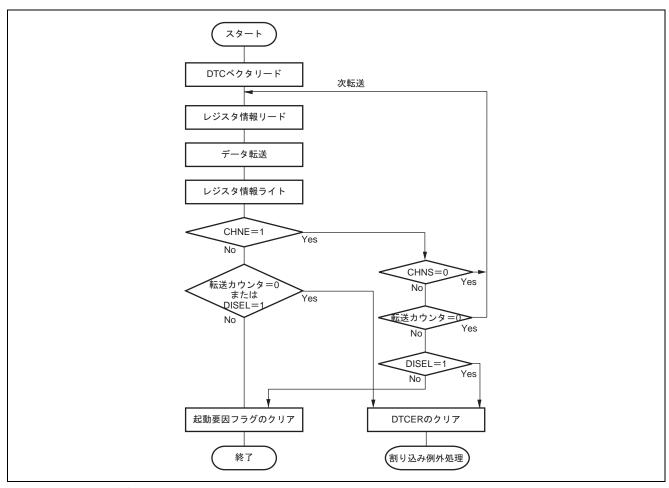

| 11.5 動   | 作説明                              | 11-16 |

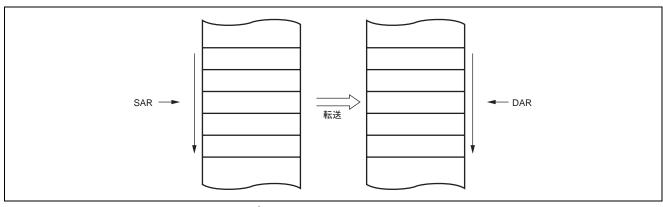

| 11.5.1   | ノーマルモード                          | 11-17 |

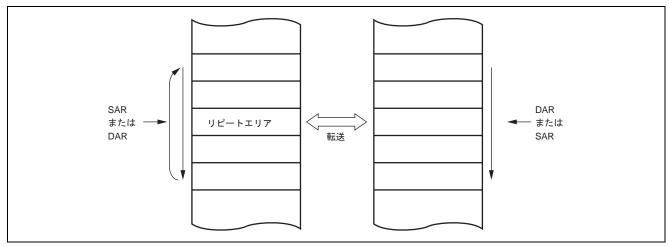

| 11.5.2   | リピートモード                          | 11-18 |

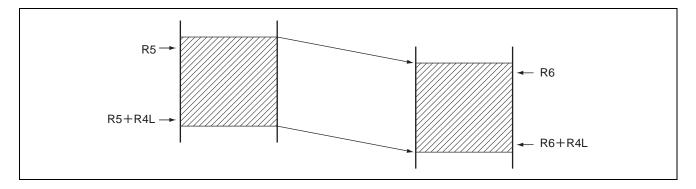

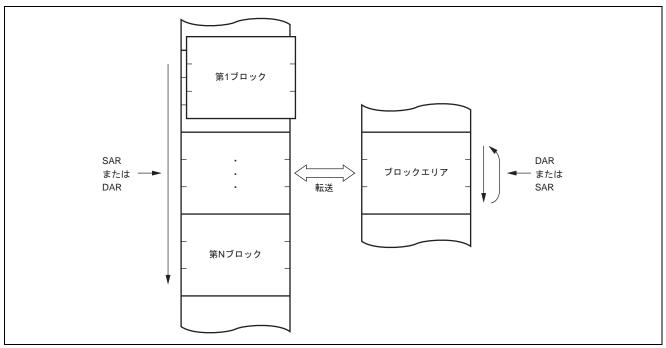

| 11.5.3   | ブロック転送モード                        | 11-19 |

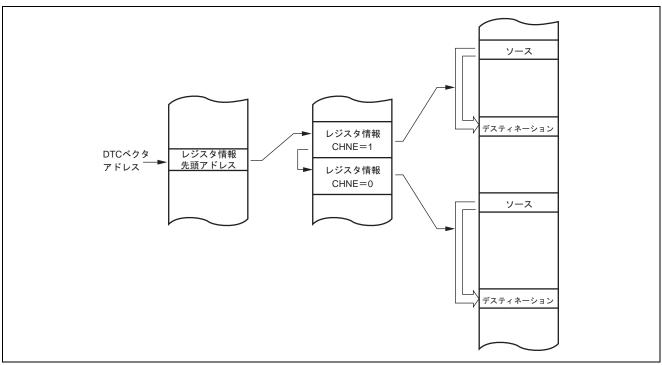

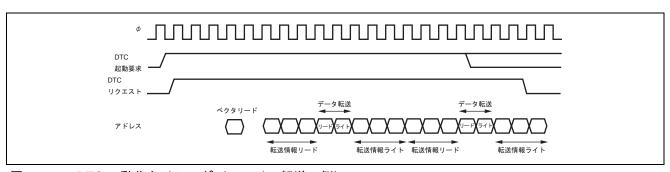

| 11.5.4   | チェイン転送                           | 11-20 |

| 11.5.5   | 割り込み要因                           | 11-21 |

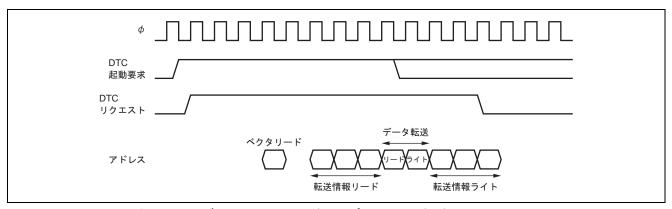

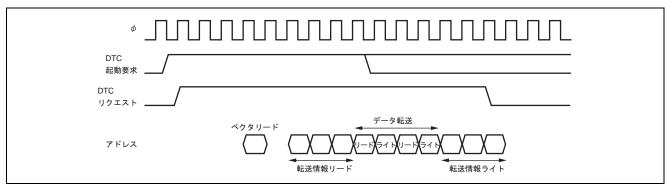

| 11.5.6   | 動作タイミング                          | 11-22 |

| 11.5.7   | DTC 実行ステート数                      | 11-23 |

| 11.6 D   | TC使用手順                           | 11-24 |

| 11.6.1   | 割り込みによる起動                        | 11-24 |

| 11.6.2   | ソフトウェアによる起動                      | 11-24 |

| 11.7 D   | TC使用例                            | 11-25 |

| 11.7.1   | ノーマルモード                          | 11-25 |

| 11.7.2   | 転送カウンタ=0 のときのチェイン転送              | 11-26 |

| 11.7.3   | ソフトウェア起動                                  | 11-27 |

|----------|-------------------------------------------|-------|

| 11.8 使   | 用上の注意事項                                   | 11-28 |

| 11.8.1   | モジュールスタンバイモードの設定                          | 11-28 |

| 11.8.2   | DTCE ビットの設定                               | 11-28 |

| 11.8.3   | SCI、IIC2/SSU および A/D 変換器の割り込み要因による DTC 起動 | 11-28 |

| 11.8.4   | 割り込みベクタオフセットレジスタ(VOFR)使用時の制限事項            | 11-28 |

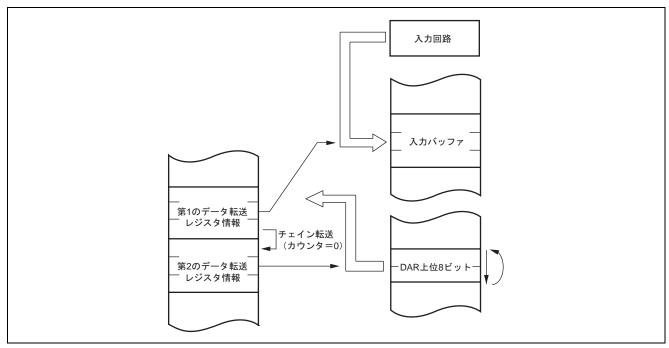

| 12. イベント | ・リンクコントローラ(ELC)                           | 12-1  |

| 12.1 概   | 要                                         | 12-1  |

| 12.2 レ   | ジスタの説明                                    | 12-2  |

| 12.2.1   | イベントリンクコントロールレジスタ(ELCR)                   | 12-3  |

| 12.2.2   | イベントリンク設定レジスタ 0~32 (ELSR0~ELSR32)         | 12-3  |

| 12.2.3   | イベントリンクオプション設定レジスタ A(ELOPA)               | 12-7  |

| 12.2.4   | イベントリンクオプション設定レジスタ B(ELOPB)               | 12-8  |

| 12.2.5   | イベントリンクオプション設定レジスタ C(ELOPC)               | 12-9  |

| 12.2.6   | ポートグループ指定レジスタ 1、2(PGR1、PGR2)              | 12-10 |

| 12.2.7   | ポートグループコントロールレジスタ 1、2(PGC1、PGC2)          | 12-11 |

| 12.2.8   | ポートバッファレジスタ 1、2(PDBF1、PDBF2)              | 12-12 |

| 12.2.9   | イベント接続ポート指定レジスタ 0~3(PEL0~PEL3)            | 12-13 |

| 12.2.10  | イベント発生タイマコントロールレジスタ(ELTMCR)               | 12-14 |

| 12.2.11  | イベント発生タイマ周期設定レジスタ A(ELTMSA)               | 12-15 |

| 12.2.12  | イベント発生タイマ周期設定レジスタ B(ELTMSB)               | 12-16 |

| 12.2.13  | イベント発生タイマ遅延時間選択レジスタ(ELTMDR)               | 12-17 |

| 12.2.14  | ELC タイマカウンタ(ELTMCNT)                      | 12-18 |

| 12.3 動作  | 作説明                                       | 12-19 |

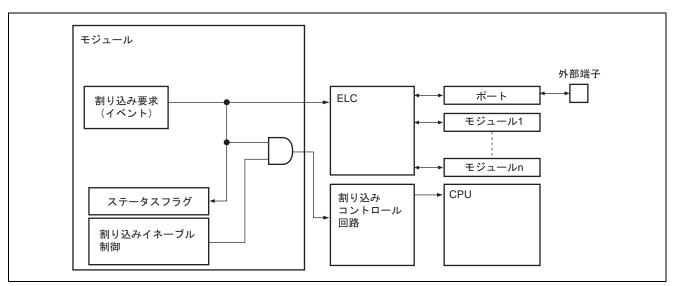

| 12.3.1   | 割り込み処理とイベントリンクの関係                         | 12-19 |

| 12.3.2   | イベントのリンク                                  | 12-20 |

| 12.3.3   | タイマ系周辺機能のイベント入力時の動作                       | 12-21 |

| 12.3.4   | A/D 変換器、D/A 変換器のイベント入力時の動作                | 12-21 |

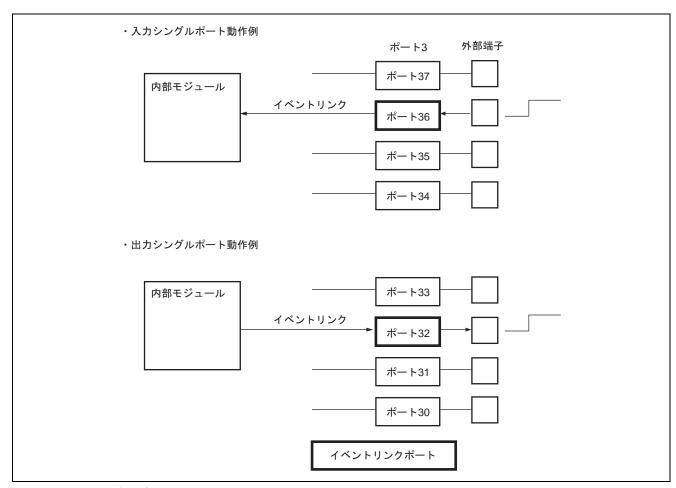

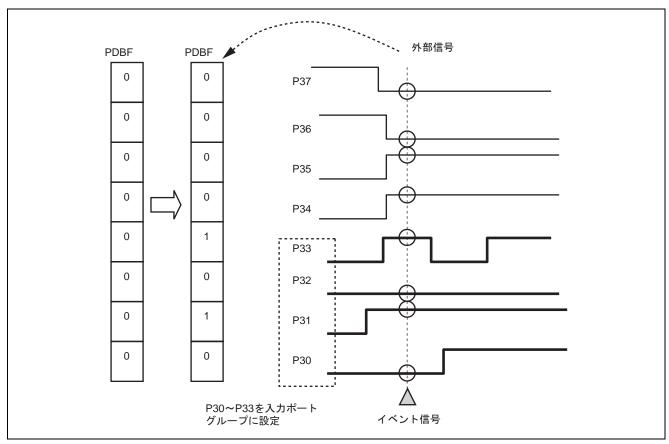

| 12.3.5   | ポートのイベント入力動作とイベント発生動作                     | 12-21 |

| 12.3.6   | イベント発生タイマ                                 | 12-26 |

| 12.3.7   | イベントリンクの動作設定手順                            | 12-28 |

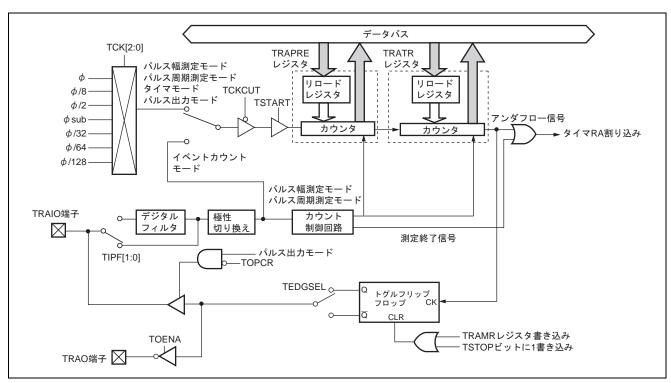

| 13. タイマト | ?A                                        | 13-1  |

| 13.1 概   | 要                                         | 13-1  |

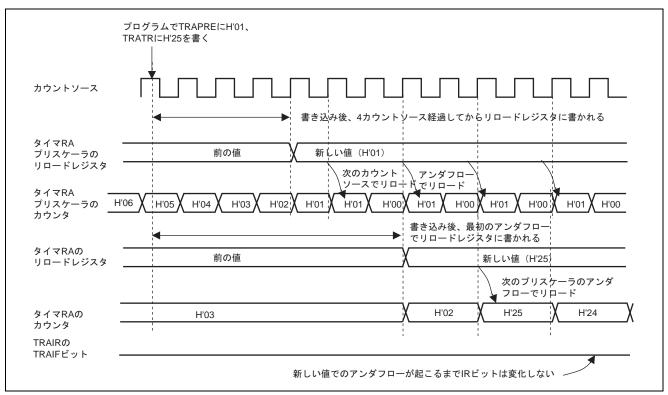

| 13.2 レ   | ジスタの説明                                    | 13-2  |

| 13.2.1   | タイマ RA コントロールレジスタ(TRACR)                  | 13-3  |

| 13.2.2   | タイマ RA I/O コントロールレジスタ(TRAIOC)             | 13-4  |

| 13.2.3    | タイマ RA モードレジスタ(TRAMR)            | 13-6  |

|-----------|----------------------------------|-------|

| 13.2.4    | タイマ RA 割り込みイネーブルステータスレジスタ(TRAIR) | 13-7  |

| 13.2.5    | タイマ RA プリスケーラレジスタ(TRAPRE)        | 13-7  |

| 13.2.6    | タイマ RA タイマレジスタ(TRATR)            | 13-8  |

| 13.3 動    | 作説明                              | 13-9  |

| 13.3.1    | 各モード共通の動作                        | 13-9  |

| 13.3.2    | タイマモード                           | 13-10 |

| 13.3.3    | パルス出力モード                         | 13-10 |

| 13.3.4    | イベントカウンタモード                      | 13-10 |

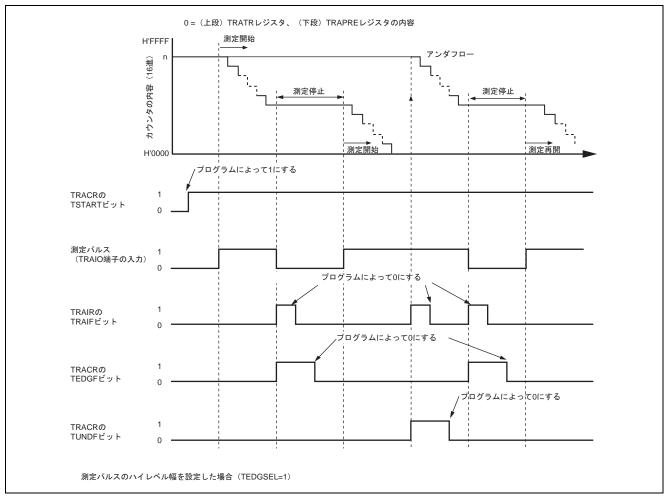

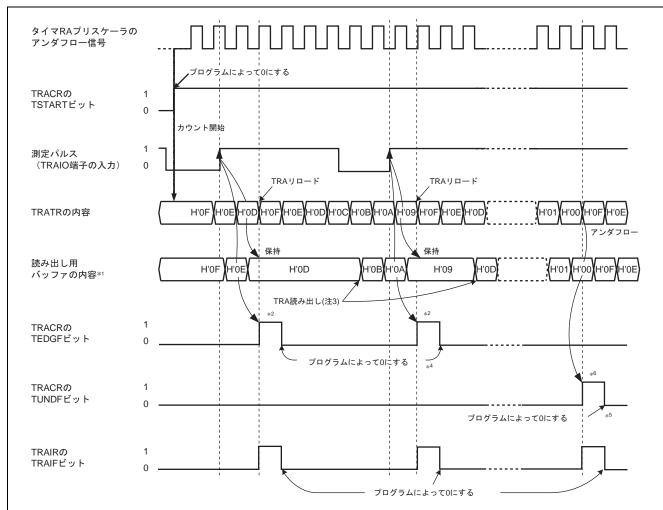

| 13.3.5    | パルス幅測定モード                        | 13-11 |

| 13.3.6    | パルス周期測定モード                       | 13-12 |

| 13.3.7    | イベントリンクによる動作                     | 13-12 |

| 13.4 使    | 用上の注意事項                          | 13-14 |

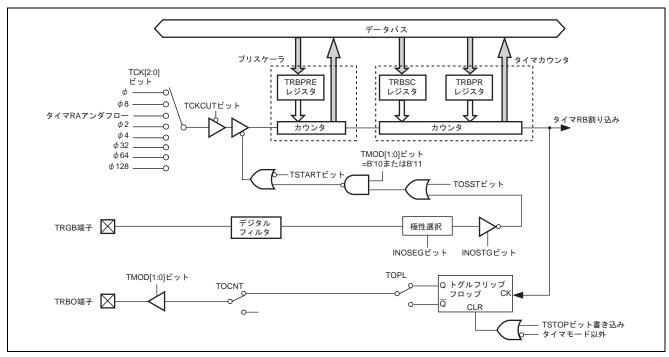

| 14. タイマ F | RB                               | 14-1  |

| 14.1 概    | 要                                | 14-1  |

| 14.2 レ    | ジスタの説明                           | 14-3  |

| 14.2.1    | タイマ RB コントロールレジスタ(TRBCR)         |       |

| 14.2.2    | タイマ RB ワンショットコントロールレジスタ(TRBOCR)  | 14-5  |

| 14.2.3    | タイマ RB I/O コントロールレジスタ(TRBIOC)    | 14-6  |

| 14.2.4    | タイマ RB モードレジスタ(TRBMR)            | 14-8  |

| 14.2.5    | タイマ RB 割り込み要求ステータスレジスタ(TRBIR)    | 14-9  |

| 14.2.6    | タイマ RB プリスケーラレジスタ(TRBPRE)        | 14-10 |

| 14.2.7    | タイマ RB セカンダリレジスタ(TRBSC)          | 14-10 |

| 14.2.8    | タイマ RB プライマリレジスタ(TRBPR)          | 14-11 |

| 14.3 動    | 作説明                              | 14-12 |

| 14.3.1    | タイマモード                           | 14-12 |

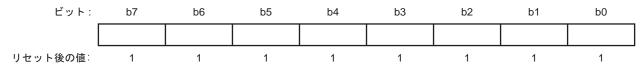

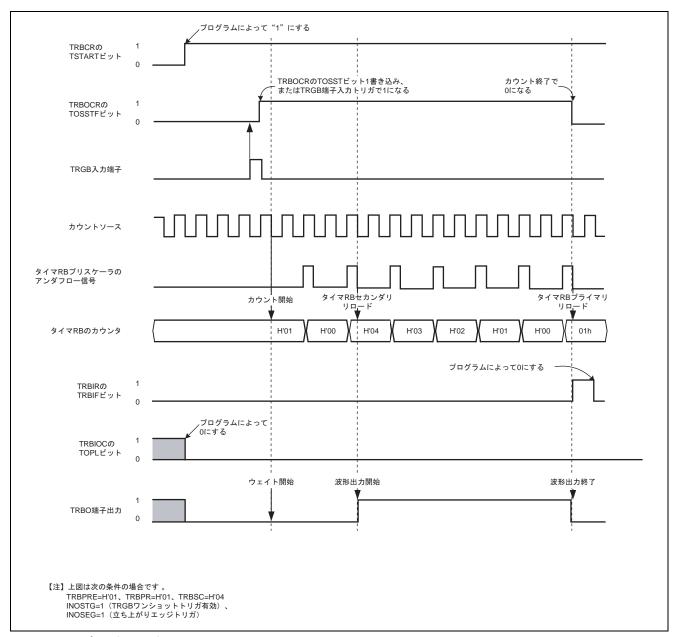

| 14.3.2    | プログラマブル波形発生モード                   | 14-13 |

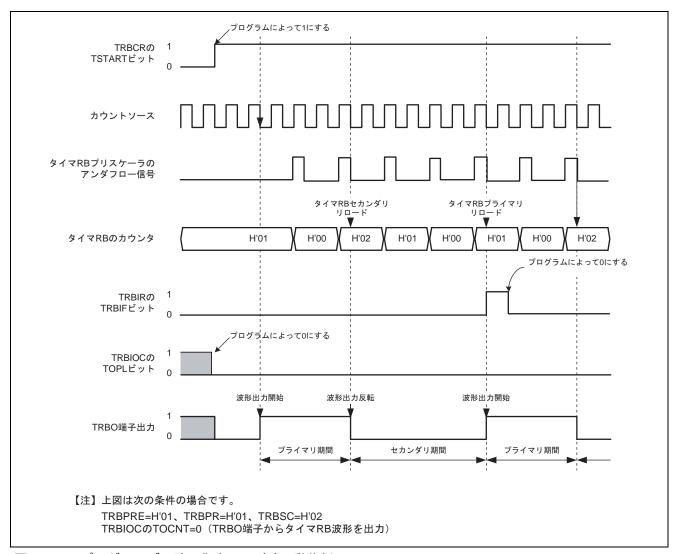

| 14.3.3    | プログラマブルワンショット発生モード               | 14-15 |

| 14.3.4    | プログラマブルウェイトワンショット発生モード           | 14-17 |

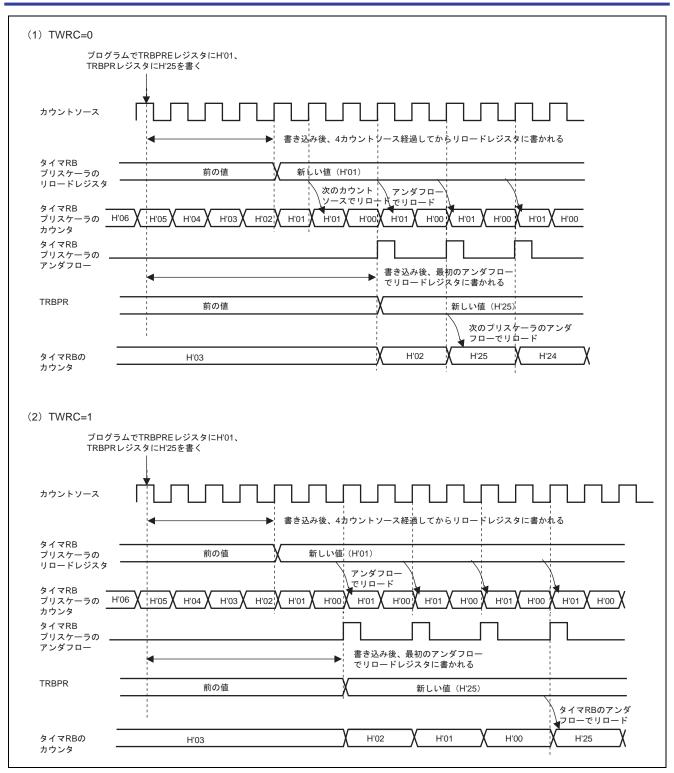

| 14.3.5    | TWRC ビットによるプリスケーラ、カウンタへの反映タイミング  | 14-19 |

| 14.3.6    | TOCNT 設定と端子状態更新条件                | 14-21 |

| 14.3.7    | イベントリンクによる動作                     | 14-21 |

| 14.4 割    | り込み要求                            | 14-22 |

| 14.5 使    | 用上の注意事項                          | 14-22 |

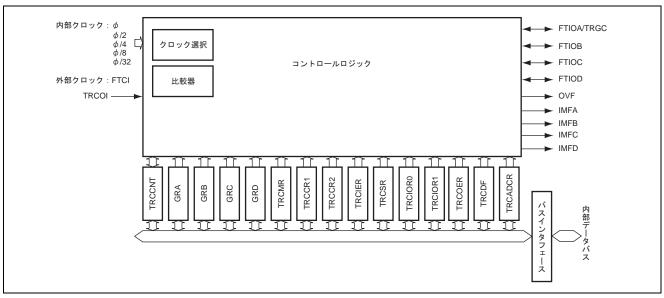

| 15. タイマ F | RC                               | 15-1  |

| 15.1 概    | 要                                | 15-1  |

|           |                                  |       |

| 15.2 V                         | ジスタの説明                                | 15-4  |  |

|--------------------------------|---------------------------------------|-------|--|

| 15.2.1                         | タイマ RC モードレジスタ(TRCMR)                 | 15-5  |  |

| 15.2.2                         | タイマ RC コントロールレジスタ 1(TRCCR1)           | 15-6  |  |

| 15.2.3                         | タイマ RC コントロールレジスタ 2(TRCCR2)           | 15-7  |  |

| 15.2.4                         | タイマ RC インタラプトイネーブルレジスタ(TRCIER)        | 15-8  |  |

| 15.2.5                         | タイマ RC ステータスレジスタ(TRCSR)               | 15-9  |  |

| 15.2.6                         | タイマ RC I/O コントロールレジスタ 0(TRCIOR0)      | 15-11 |  |

| 15.2.7                         | タイマ RC I/O コントロールレジスタ 1(TRCIOR1)      | 15-12 |  |

| 15.2.8                         | タイマ RC アウトプットイネーブルレジスタ(TRCOER)        | 15-14 |  |

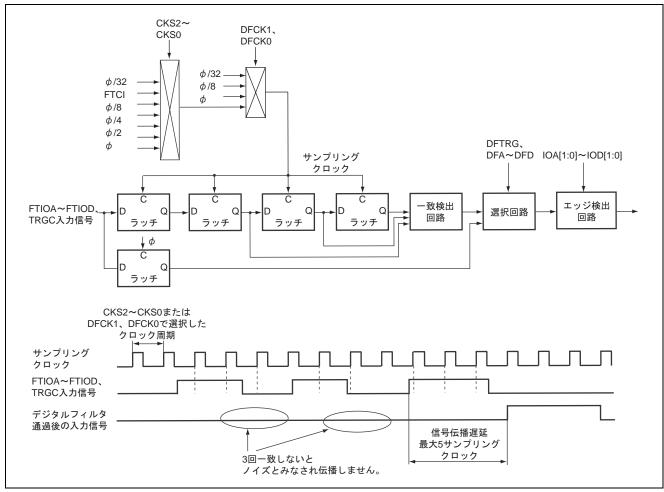

| 15.2.9                         | タイマ RC デジタルフィルタ機能選択レジスタ(TRCDF)        | 15-15 |  |

| 15.2.10                        | タイマ RC A/D 変換開始トリガコントロールレジスタ(TRCADCR) | 15-16 |  |

| 15.2.11                        | タイマ RC カウンタ(TRCCNT)                   | 15-16 |  |

| 15.2.12                        | ジェネラルレジスタ A、B、C、D(GRA、GRB、GRC、GRD)    | 15-17 |  |

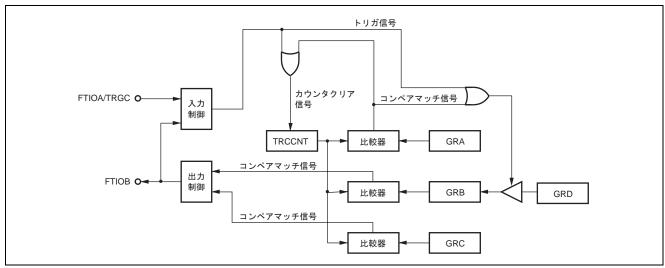

| 15.3 動                         | 作説明                                   | 15-18 |  |

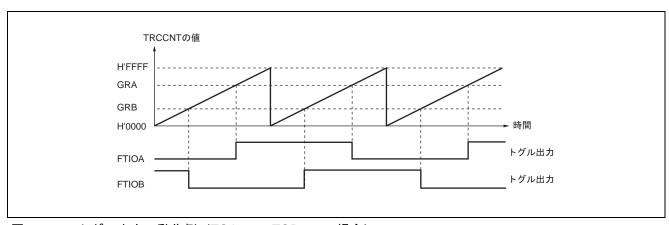

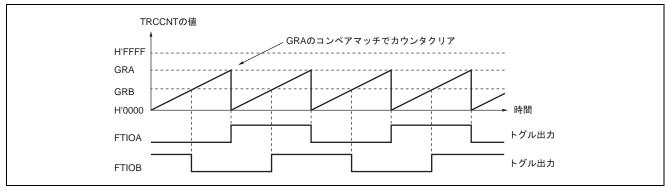

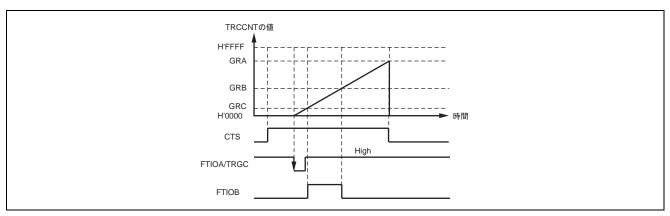

| 15.3.1                         | タイマモード動作                              | 15-20 |  |

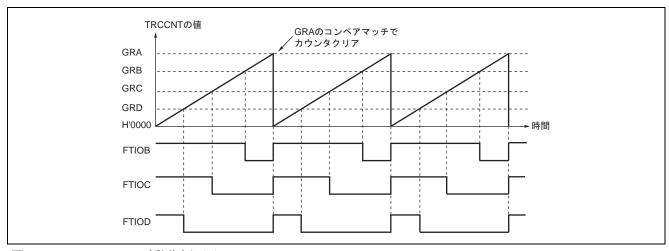

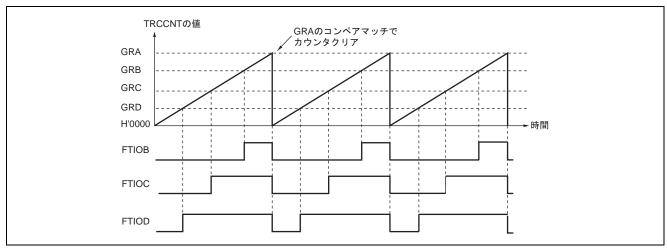

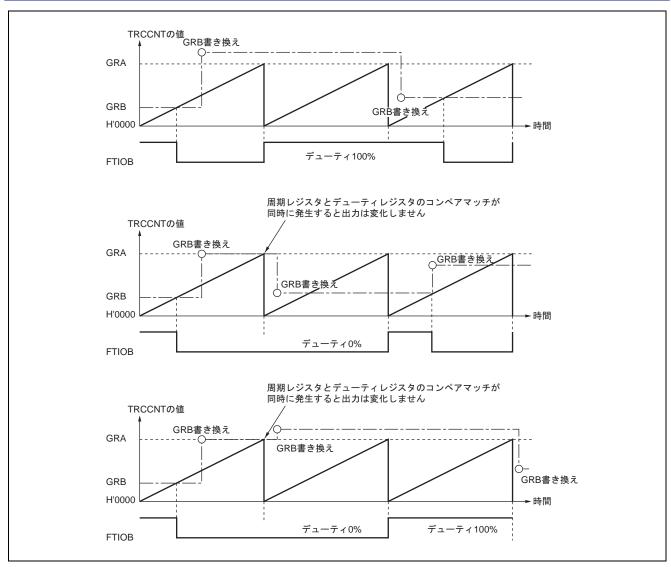

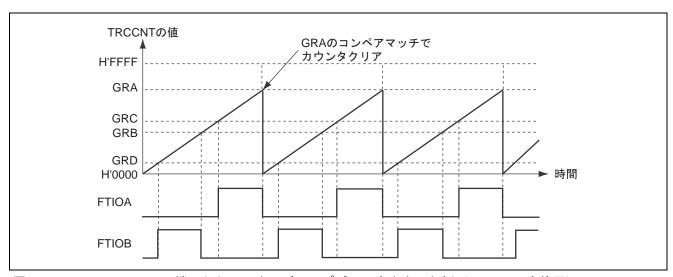

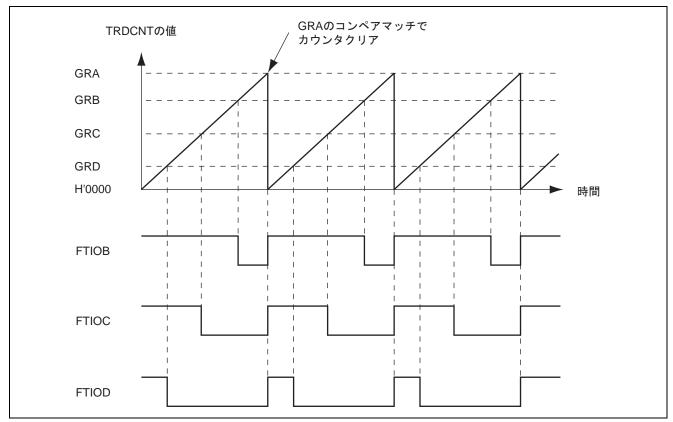

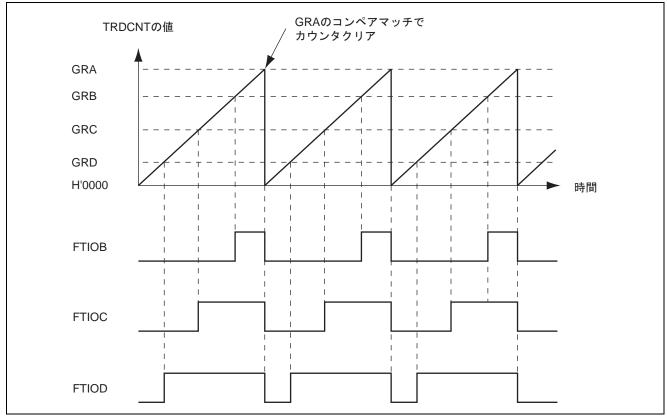

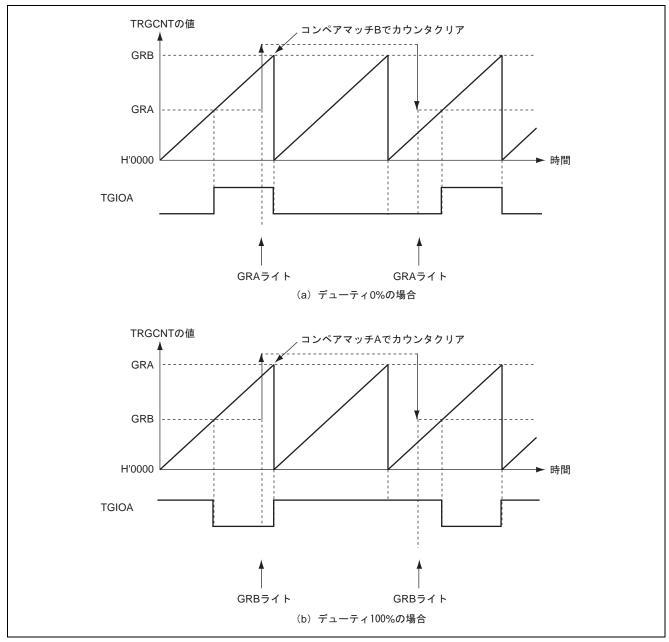

| 15.3.2                         | PWM 動作                                | 15-23 |  |

| 15.3.3                         | PWM2 モード動作                            | 15-28 |  |

| 15.3.4                         | インプットキャプチャ入力デジタルフィルタ機能                | 15-33 |  |

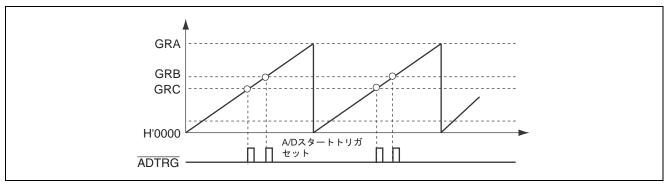

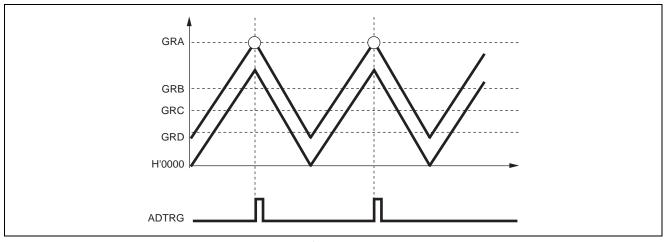

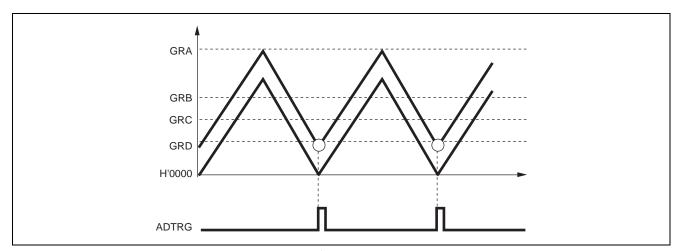

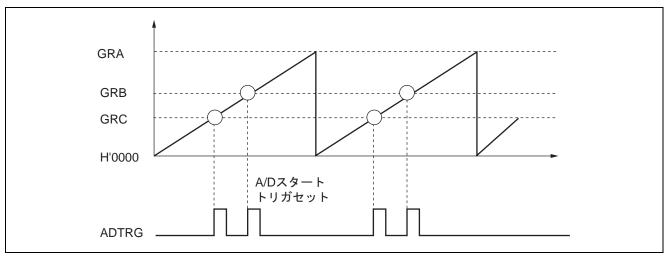

| 15.3.5                         | A/D 変換開始トリガ機能                         | 15-34 |  |

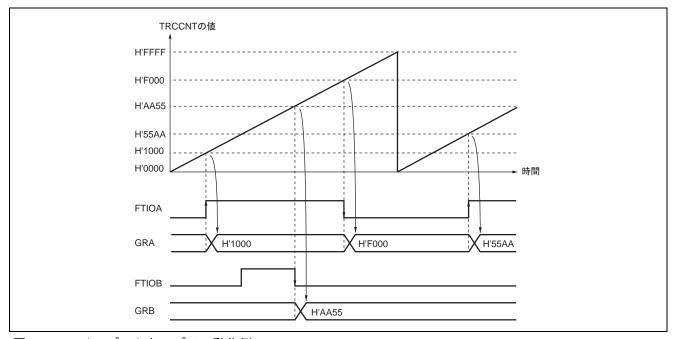

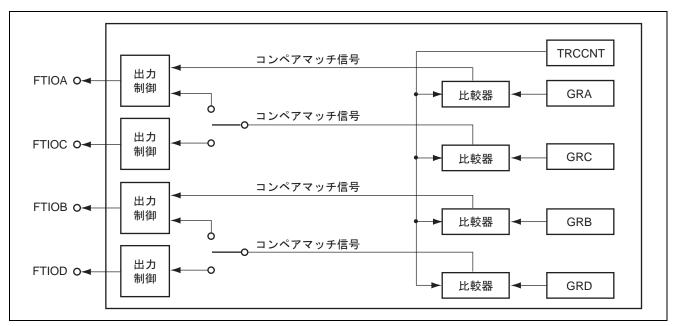

| 15.3.6 GR 対象出力端子可変機能           |                                       |       |  |

| 15.3.7                         | イベントリンクによる動作                          | 15-36 |  |

| 15.4 動                         | 作タイミング                                | 15-37 |  |

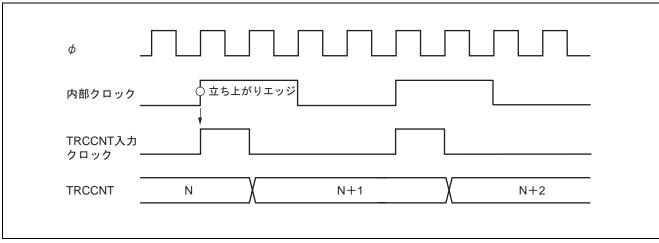

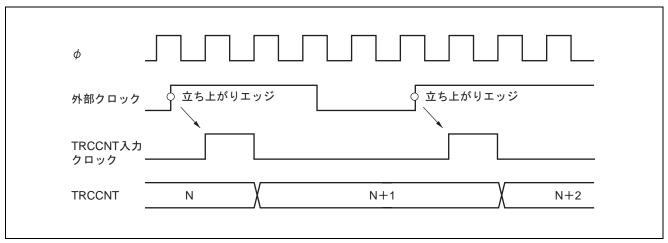

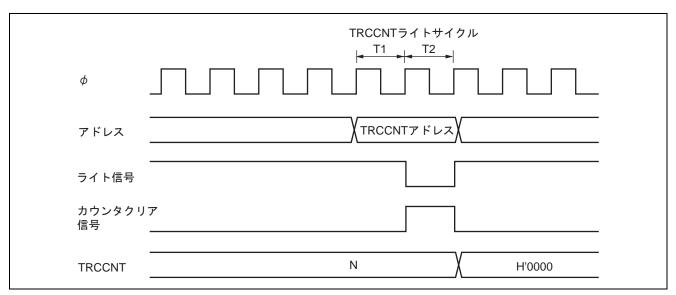

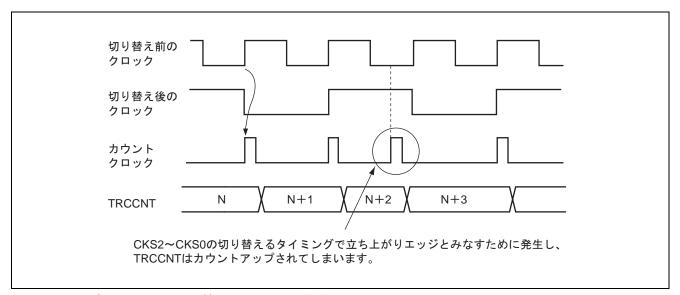

| 15.4.1                         | TRCCNT のカウントタイミング                     | 15-37 |  |

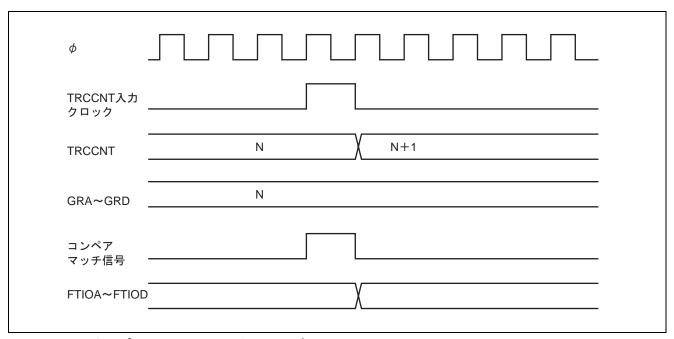

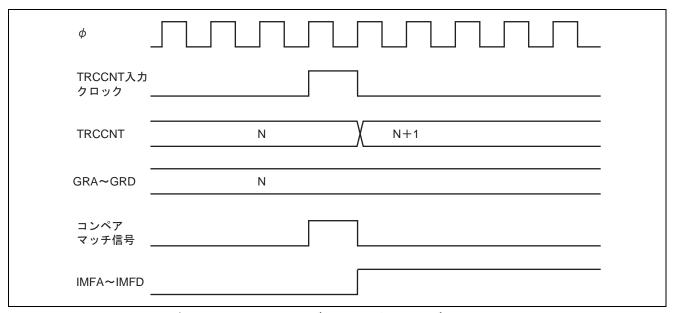

| 15.4.2                         | アウトプットコンペア出力タイミング                     | 15-38 |  |

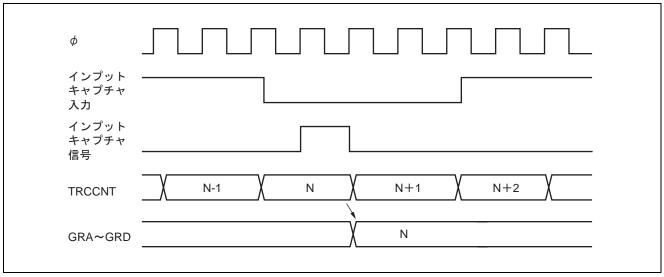

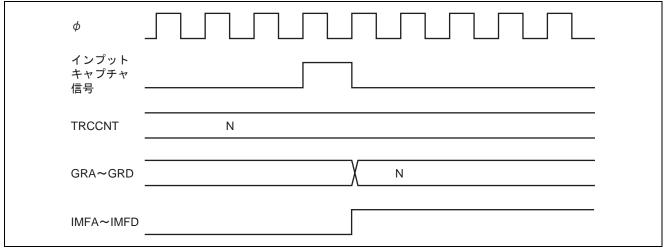

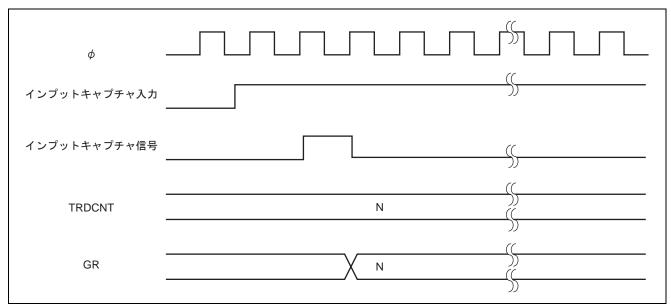

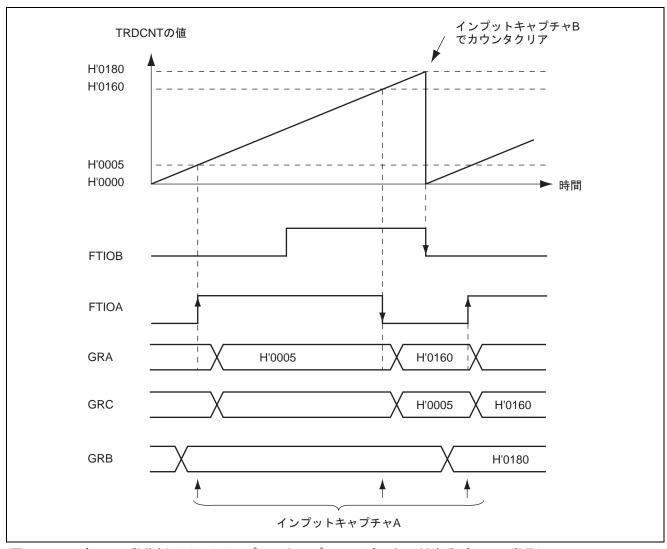

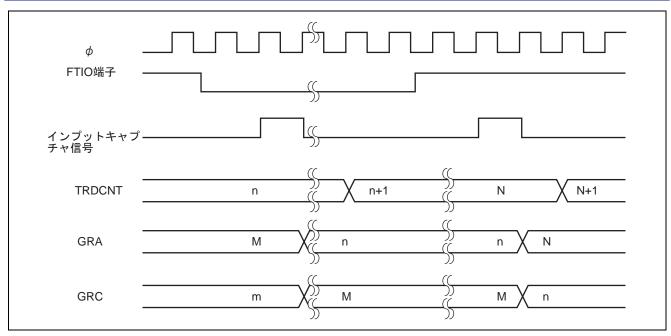

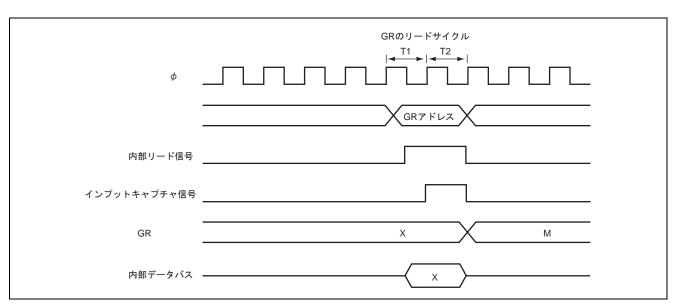

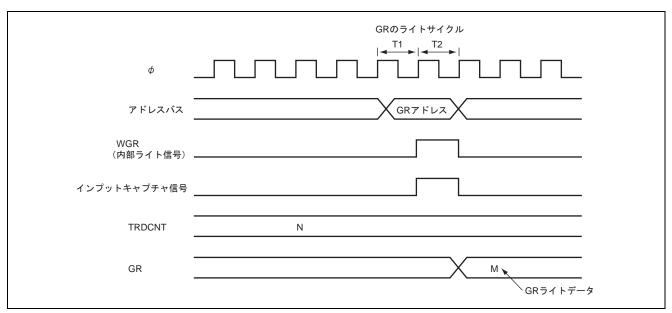

| 15.4.3                         | インプットキャプチャタイミング                       | 15-39 |  |

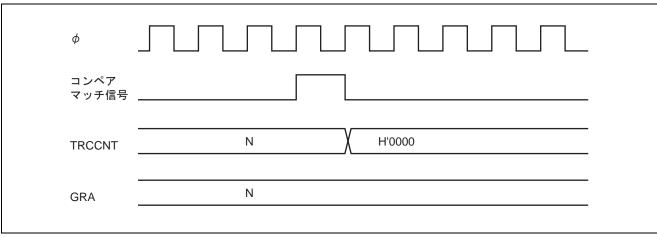

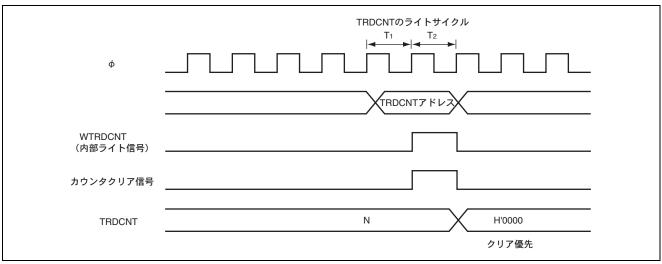

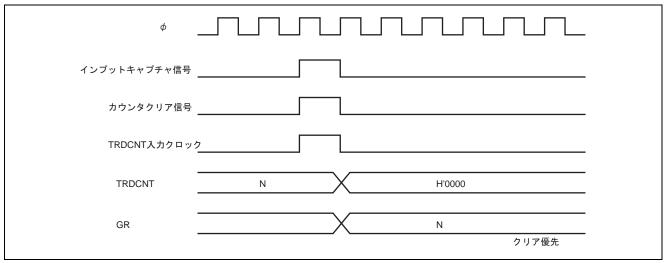

| 15.4.4                         | コンペアマッチによるカウンタクリアタイミング                | 15-39 |  |

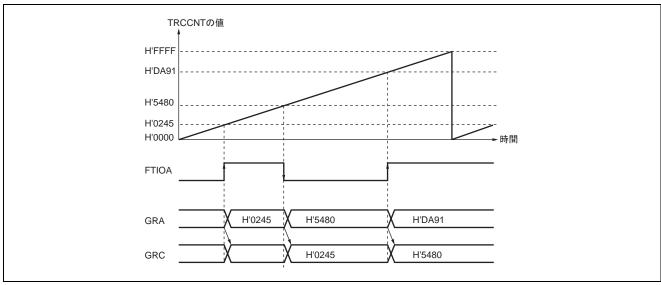

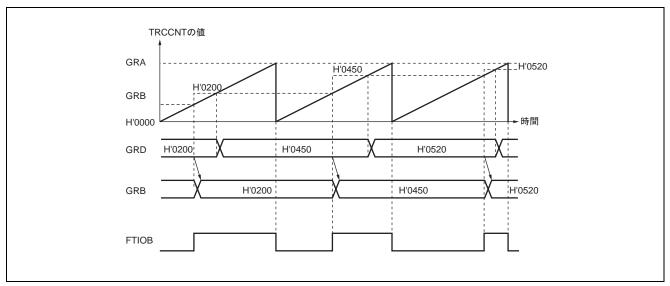

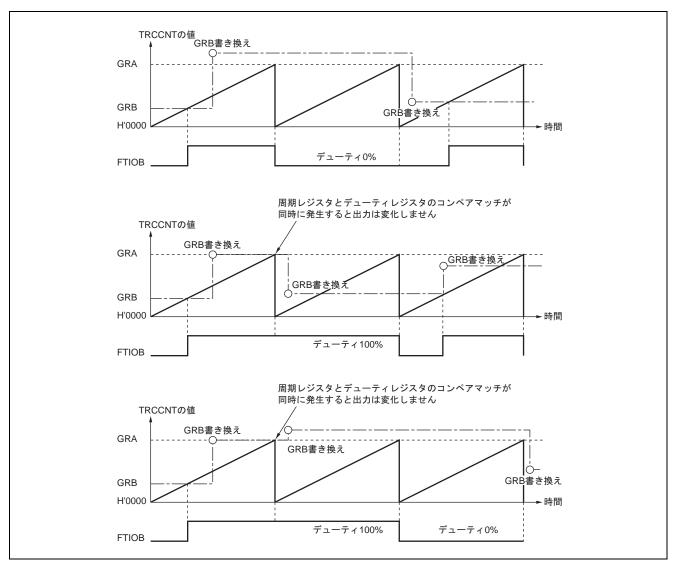

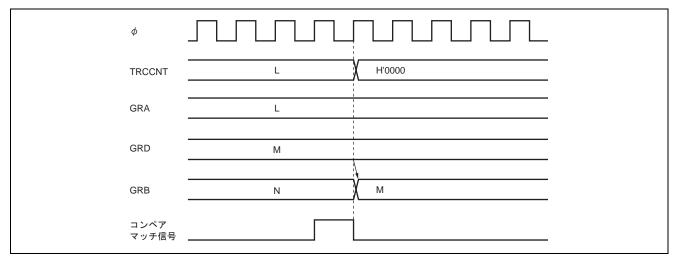

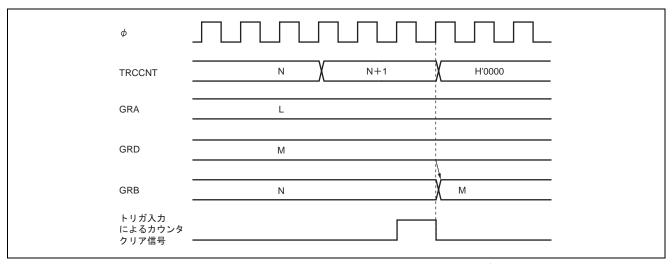

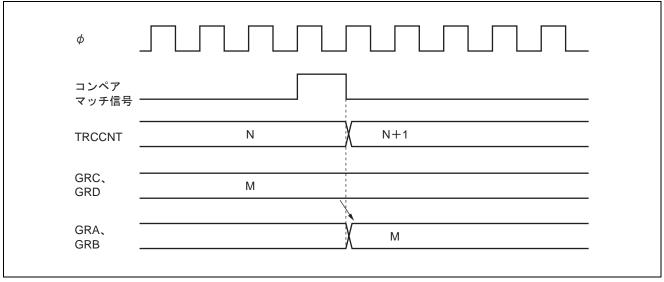

| 15.4.5                         | バッファ動作タイミング                           | 15-40 |  |

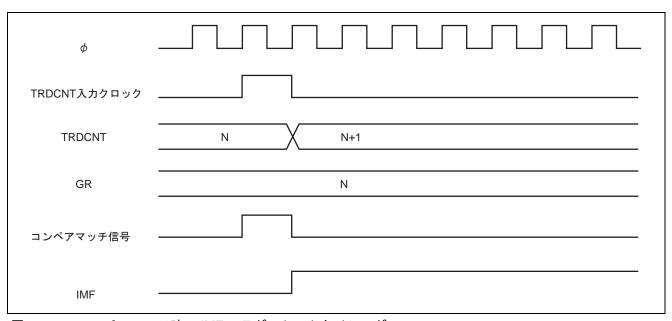

| 15.4.6                         | コンペアマッチ時の IMFA~IMFD フラグのセットタイミング      | 15-41 |  |

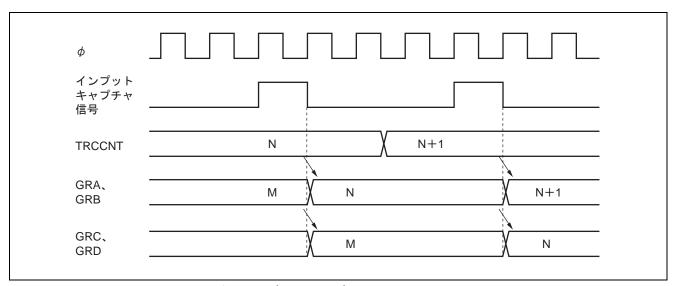

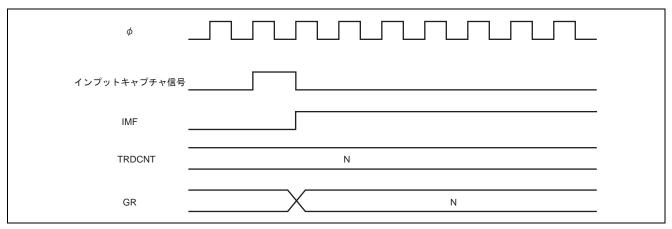

| 15.4.7                         | インプットキャプチャ時のフラグセットタイミング               | 15-42 |  |

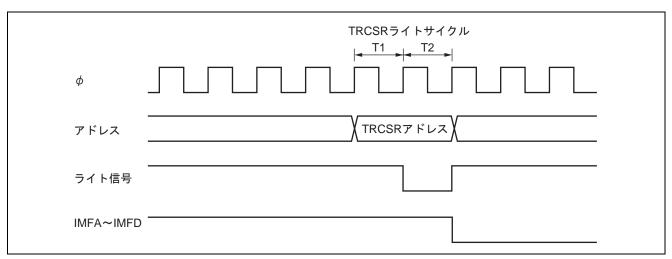

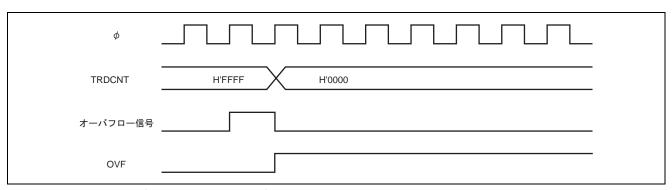

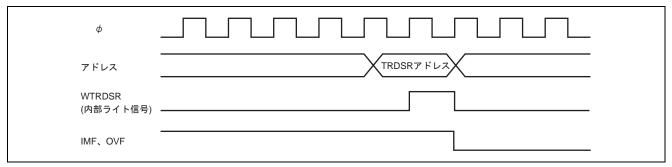

| 15.4.8                         | ステータスフラグのクリアタイミング                     | 15-42 |  |

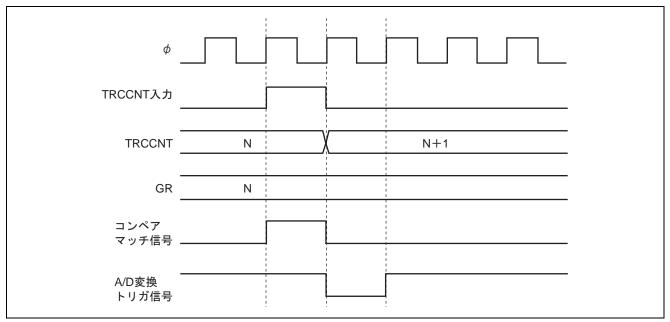

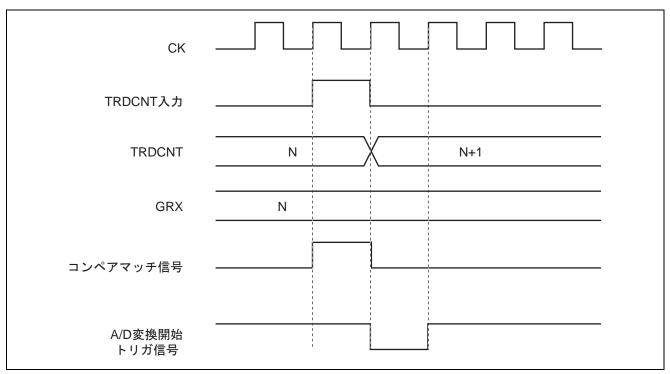

| 15.4.9                         | コンペアマッチで A/D 変換開始トリガのタイミング            | 15-43 |  |

| 15.5 使                         | 用上の注意事項                               | 15-44 |  |

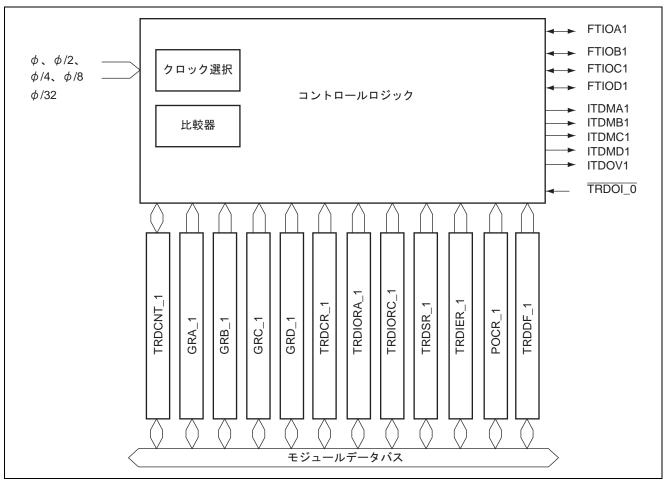

| 16. タイマト                       | RD                                    | 16-1  |  |

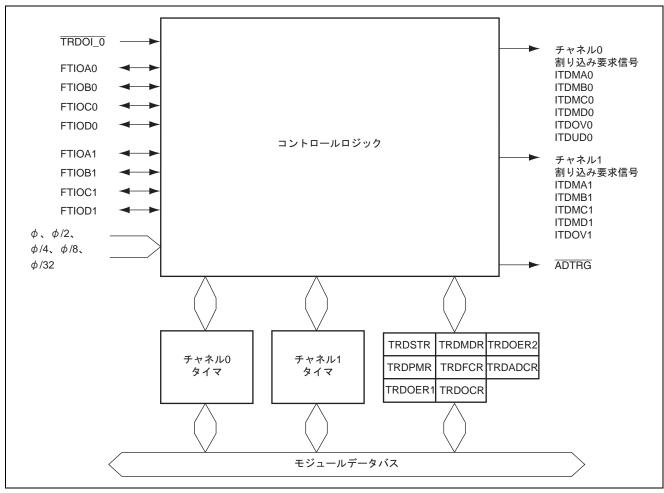

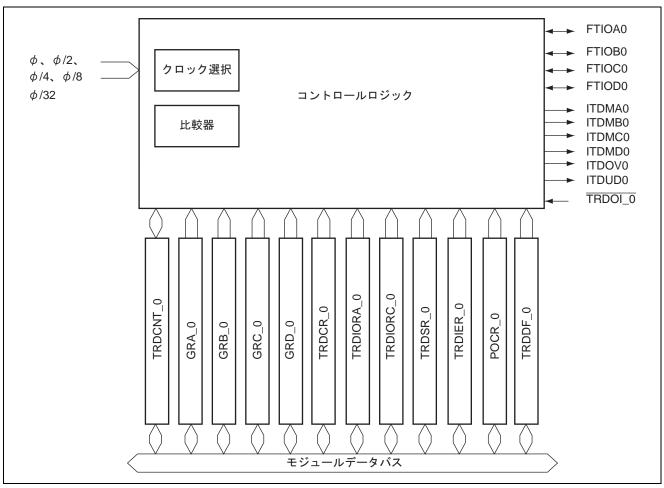

| 16.1 概                         | 要                                     | 16-1  |  |

| 16.2 V                         | ジスタの説明                                | 16-8  |  |

| 16.2.1 タイマ RD スタートレジスタ(TRDSTR) |                                       |       |  |

| 16.2.2                         | 1622 タイマ RD モードレジスタ(TRDMDR)           |       |  |

| 16.2.3              | 16.2.3 タイマ RD PWM モードレジスタ (TRDPMR)      |       |

|---------------------|-----------------------------------------|-------|

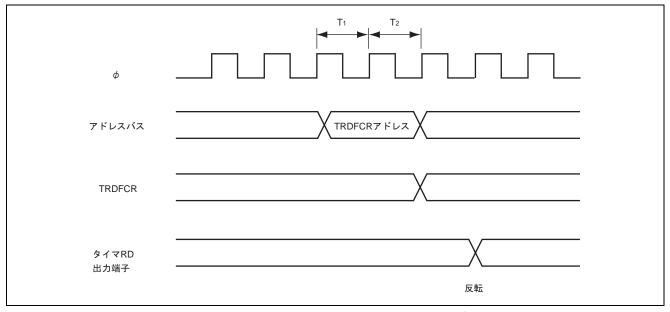

| 16.2.4              | 16.2.4 タイマ RD ファンクションコントロールレジスタ(TRDFCR) |       |

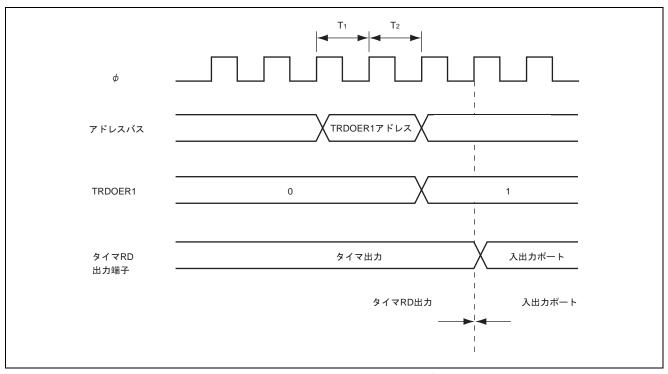

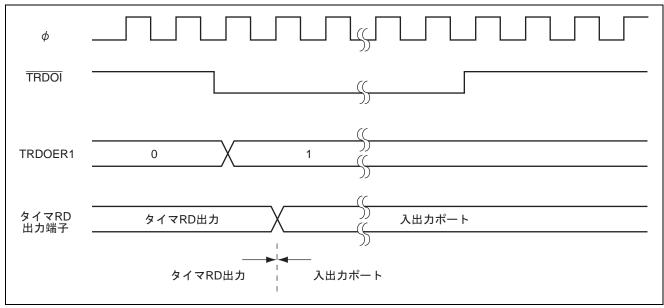

| 16.2.5              | タイマ RD アウトプットマスタイネーブルレジスタ 1(TRDOER1)    | 16-15 |

| 16.2.6              | タイマ RD アウトプットマスタイネーブルレジスタ 2(TRDOER2)    | 16-16 |

| 16.2.7              | 16.2.7 タイマ RD アウトプットコントロールレジスタ(TRDOCR)  |       |

| 16.2.8              | タイマ RD A/D 変換開始トリガコントロールレジスタ(TRDADCR)   | 16-18 |

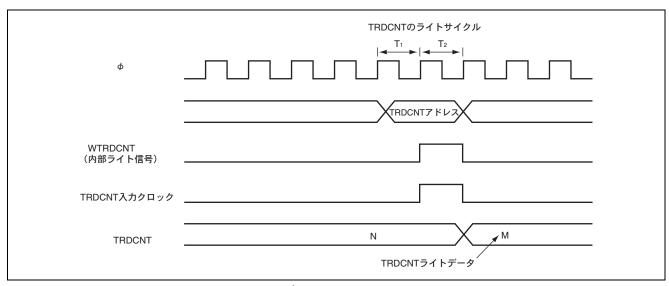

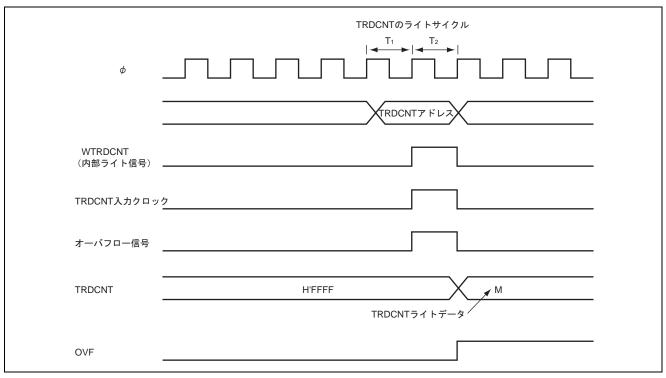

| 16.2.9              | タイマ RD カウンタ(TRDCNT)                     | 16-19 |

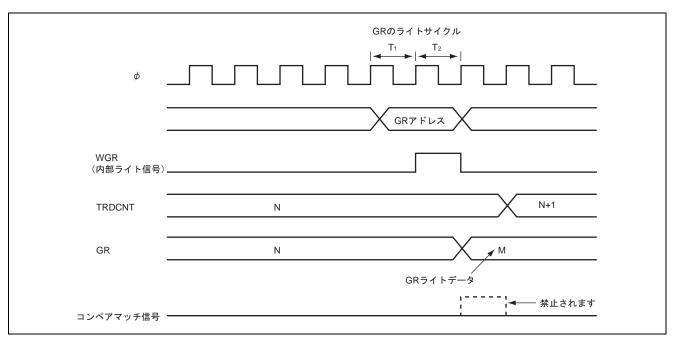

| 16.2.10             | ジェネラルレジスタ A、B、C、D(GRA、GRB、GRC、GRD)      | 16-20 |

| 16.2.11             | タイマ RD コントロールレジスタ(TRDCR)                | 16-21 |

| 16.2.12             | タイマ RD I/O コントロールレジスタ(TRDIORA、TRDIORC)  | 16-22 |

| 16.2.13             | タイマ RD ステータスレジスタ(TRDSR)                 | 16-26 |

| 16.2.14             | タイマ RD インタラプトイネーブルレジスタ(TRDIER)          | 16-29 |

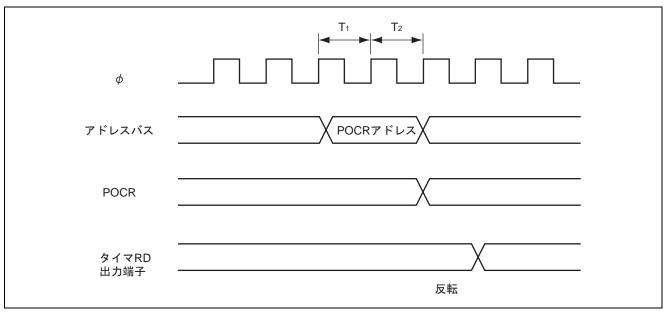

| 16.2.15             | PWM モードアウトプットレベルコントロールレジスタ (POCR)       | 16-30 |

| 16.2.16             | タイマ RD デジタルフィルタ機能選択レジスタ(TRDDF)          | 16-31 |

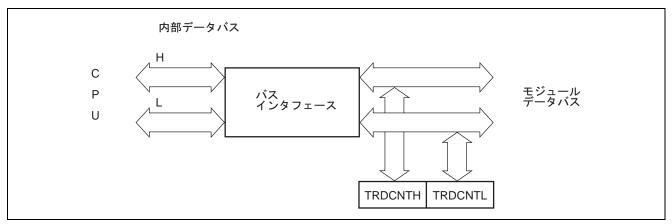

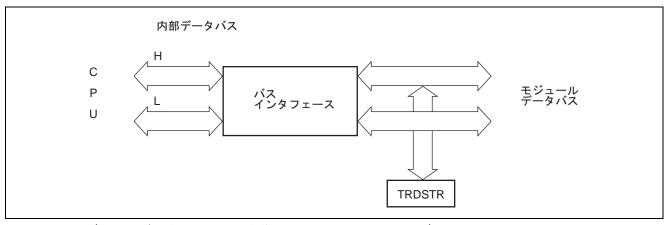

| 16.2.17             | CPU とのインタフェース                           | 16-32 |

| 16.3 動              | 作説明                                     | 16-33 |

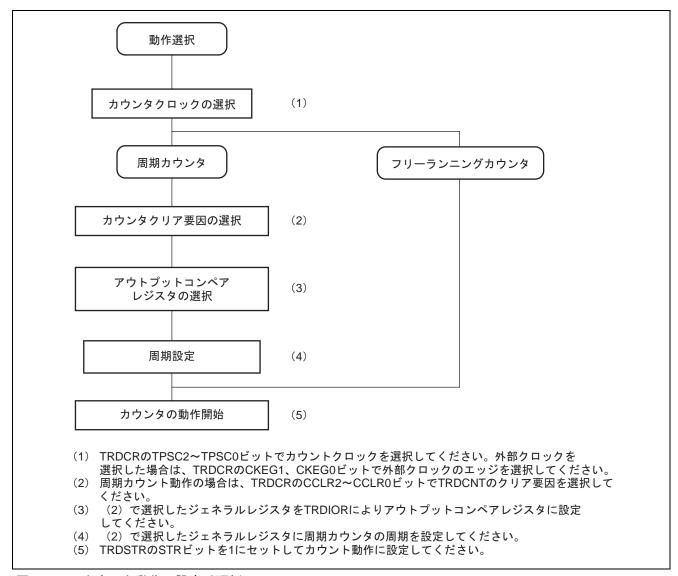

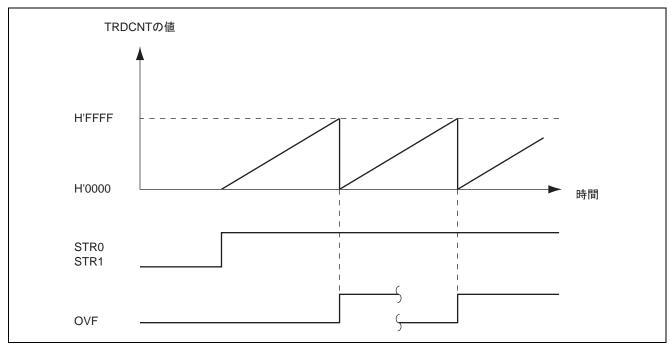

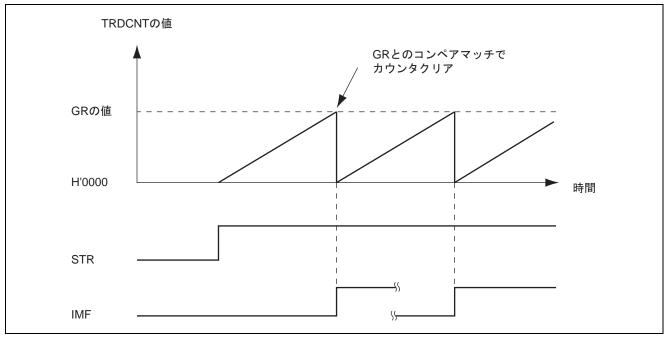

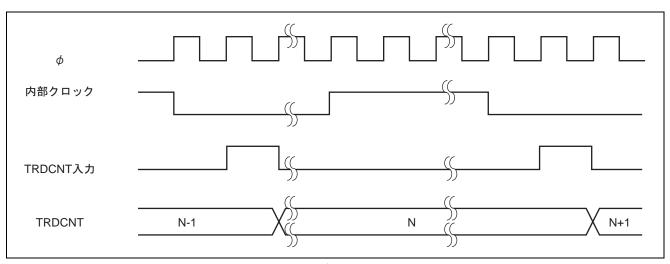

| 16.3.1              | カウンタの動作                                 | 16-36 |

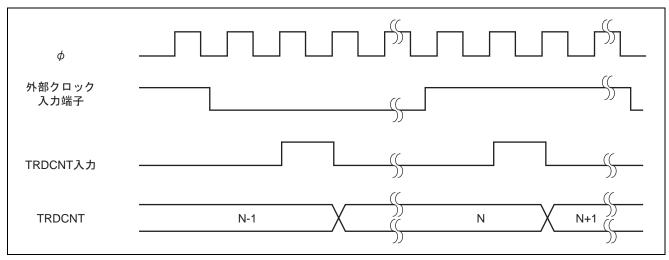

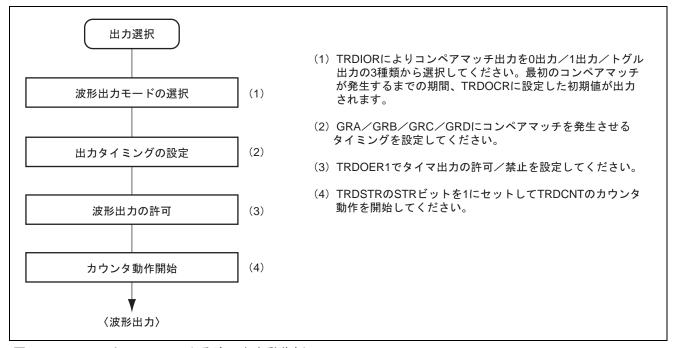

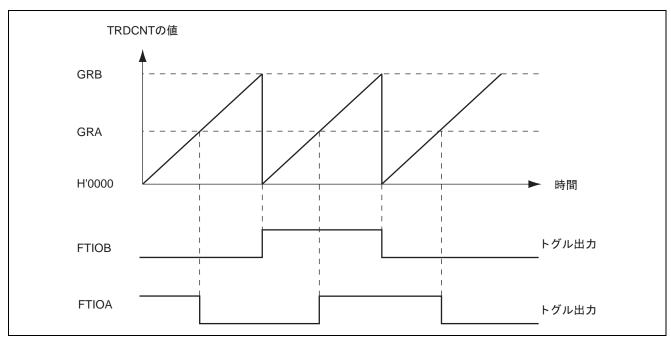

| 16.3.2              | コンペアマッチによる波形出力機能                        | 16-40 |

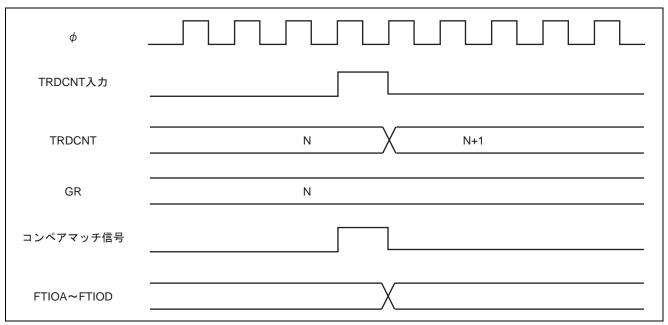

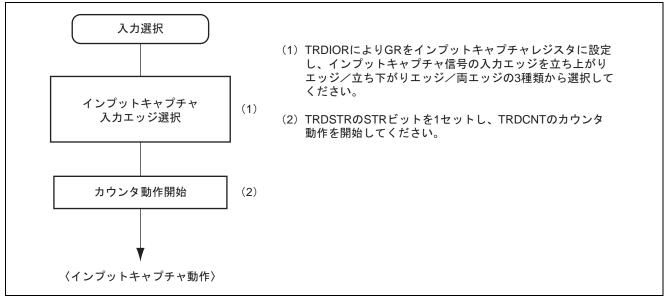

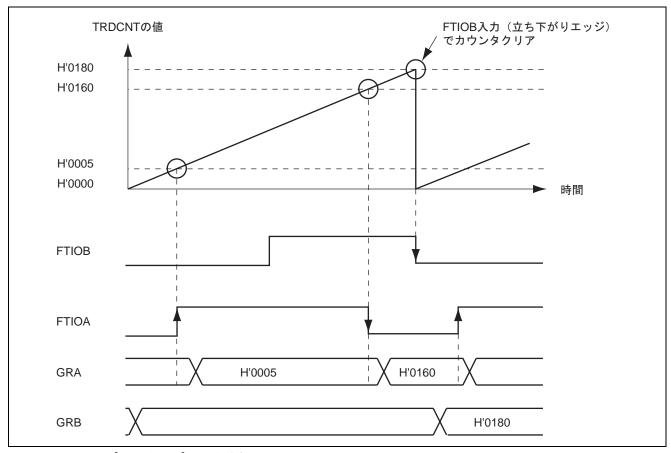

| 16.3.3 インプットキャプチャ機能 |                                         | 16-43 |

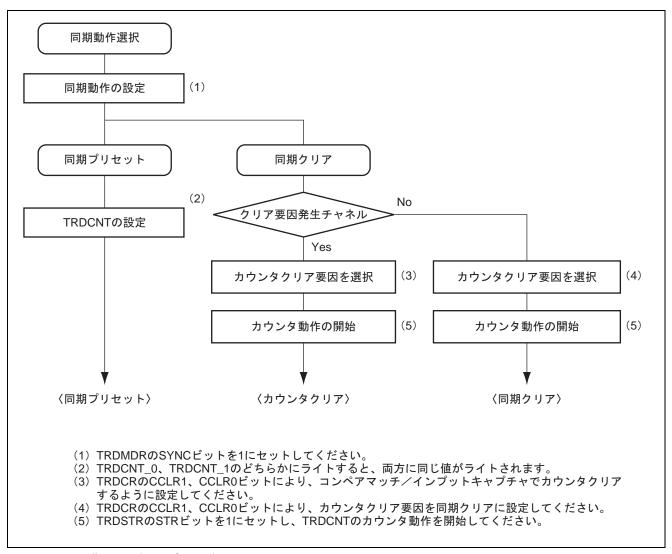

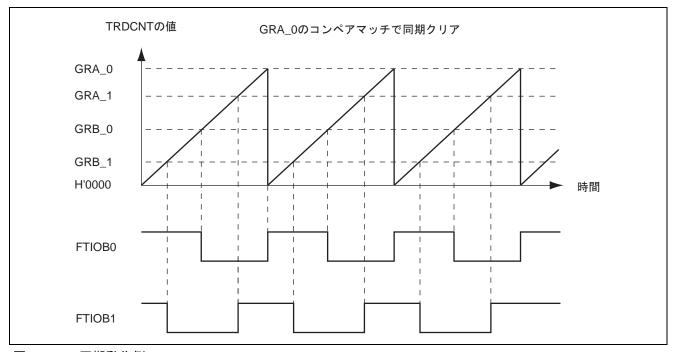

| 16.3.4              | 同期動作                                    | 16-46 |

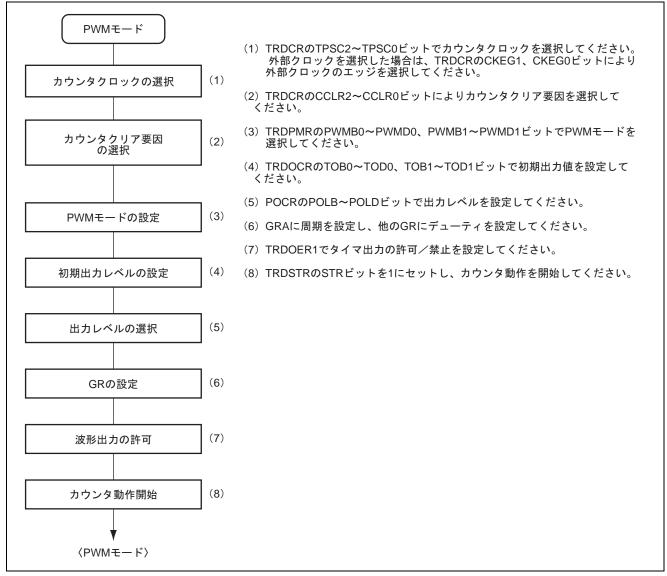

| 16.3.5              | PWM モード                                 | 16-47 |

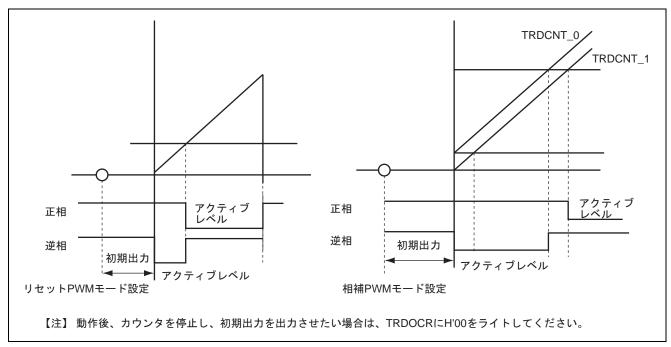

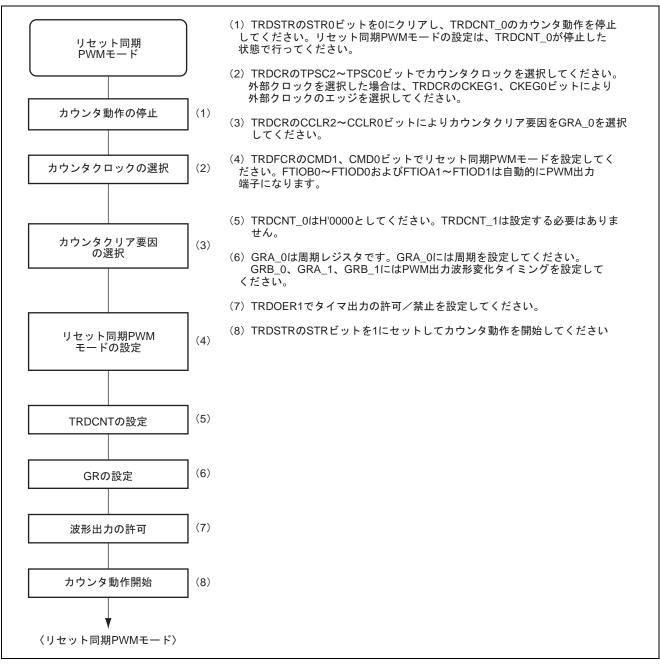

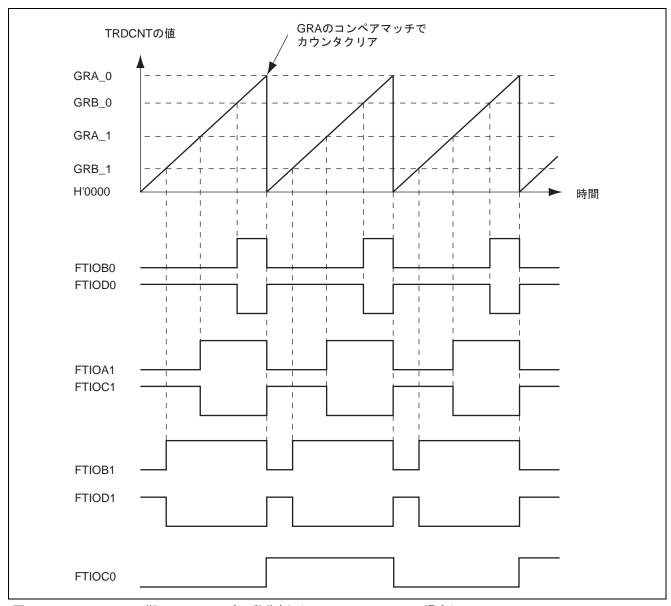

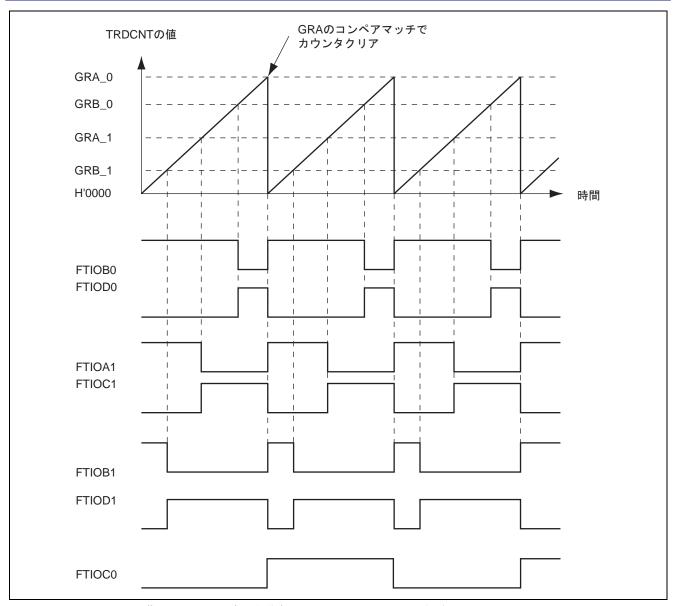

| 16.3.6              | リセット同期 PWM モード                          | 16-53 |

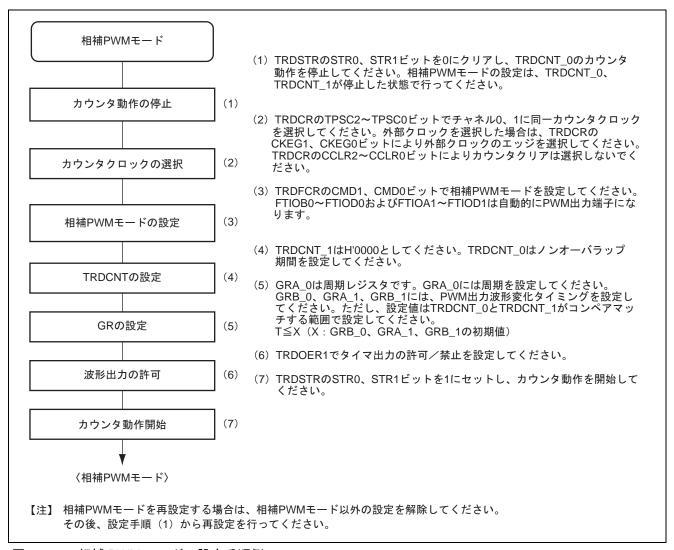

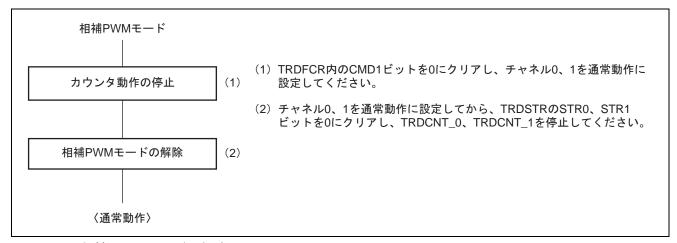

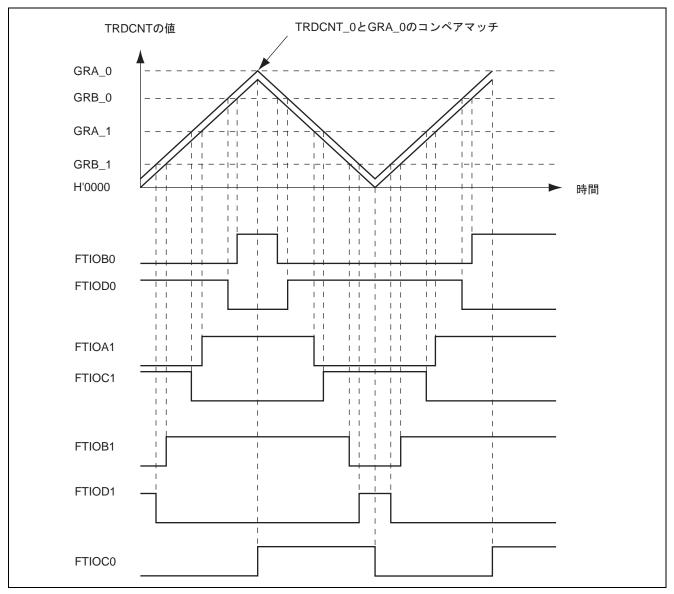

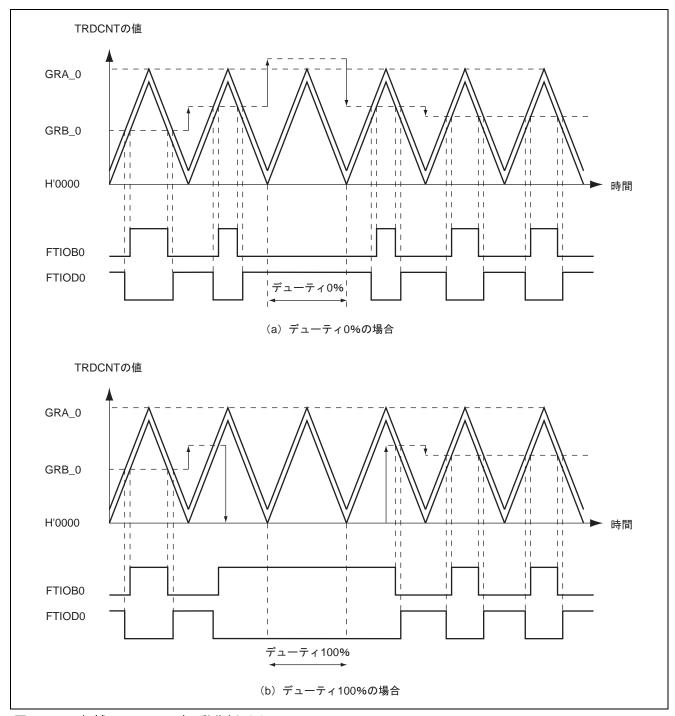

| 16.3.7              | 相補 PWM モード                              | 16-57 |

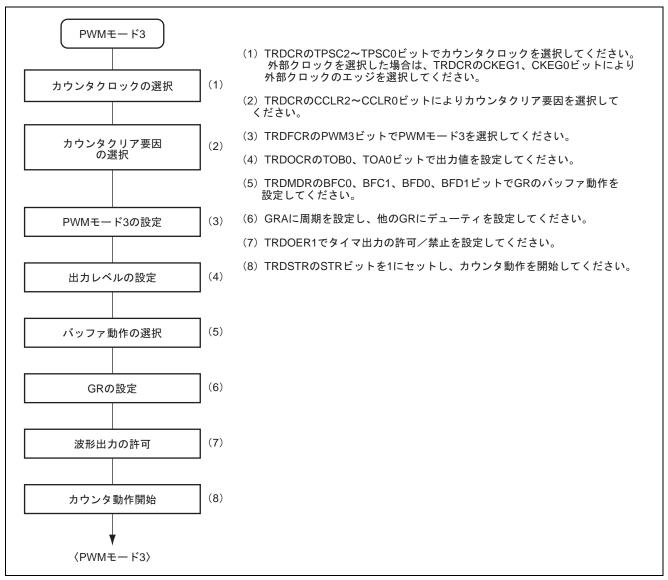

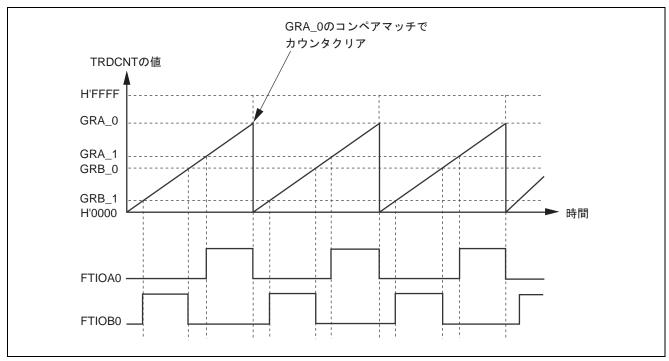

| 16.3.8              | PWM3 モード                                | 16-63 |

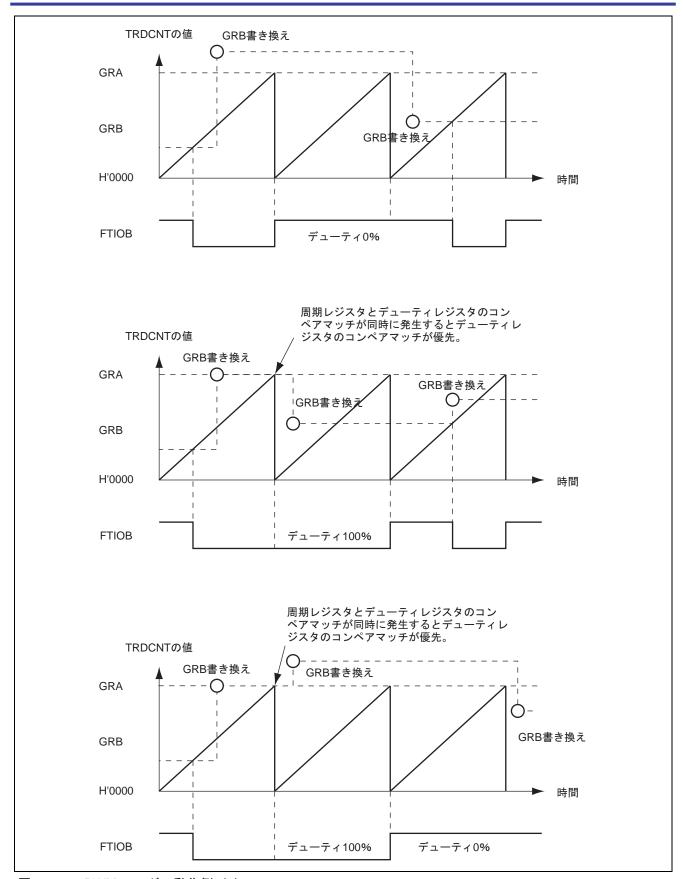

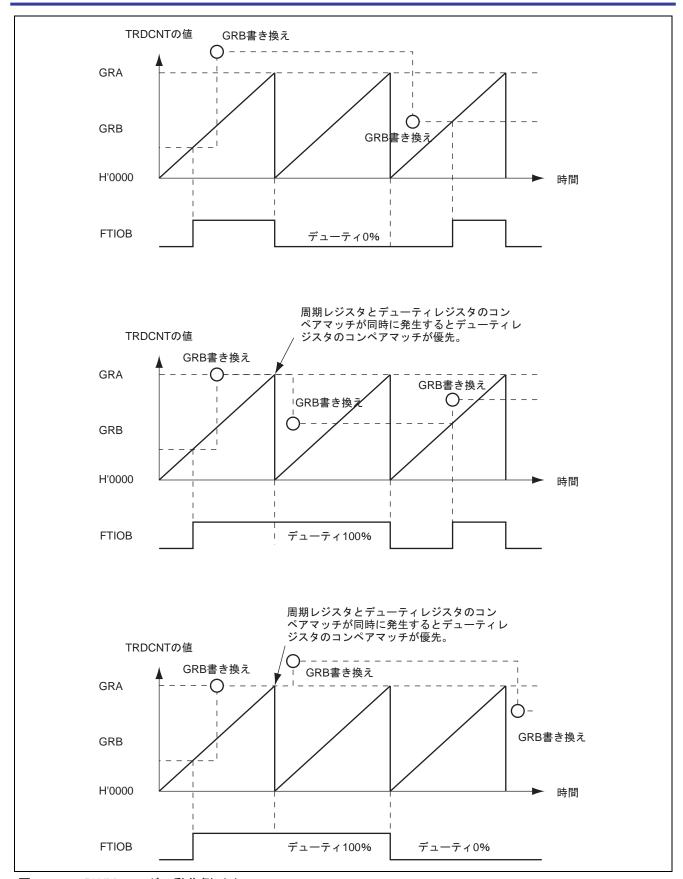

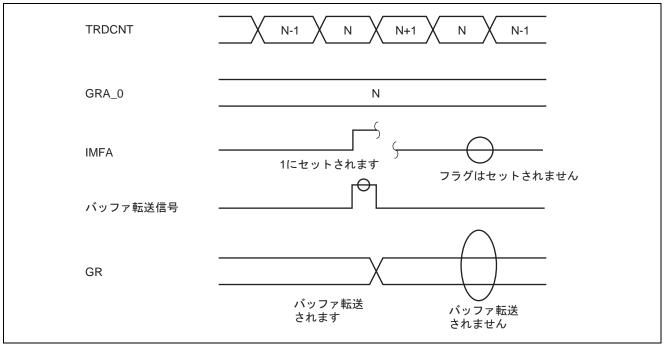

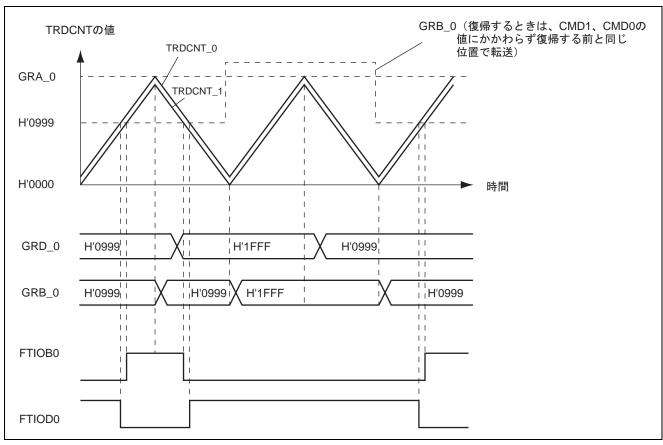

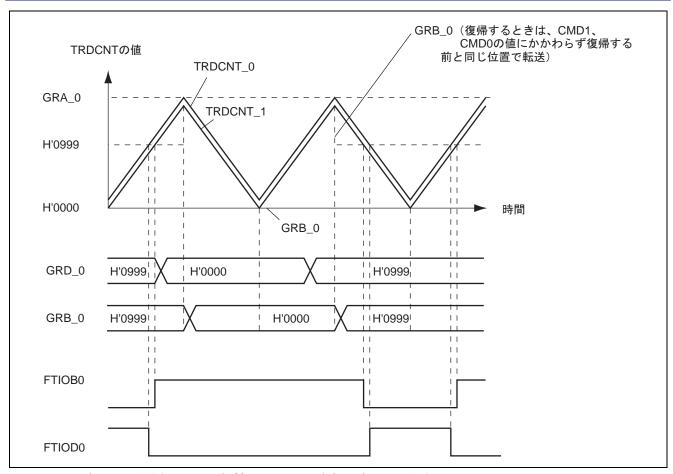

| 16.3.9              | バッファ動作                                  | 16-69 |

| 16.3.10             | タイマ RD 出力タイミング                          | 16-77 |

| 16.3.11             | インプットキャプチャ入力デジタルフィルタ機能                  | 16-80 |

| 16.3.12             | GR 対象出力端子可変機能                           | 16-81 |

| 16.3.13             | A/D 変換開始トリガ設定機能                         | 16-83 |

| 16.3.14             | イベントリンクによる動作                            | 16-85 |

| 16.4 割              | り込み要求                                   | 16-86 |

| 16.4.1              | ステータスフラグのセットタイミング                       | 16-86 |

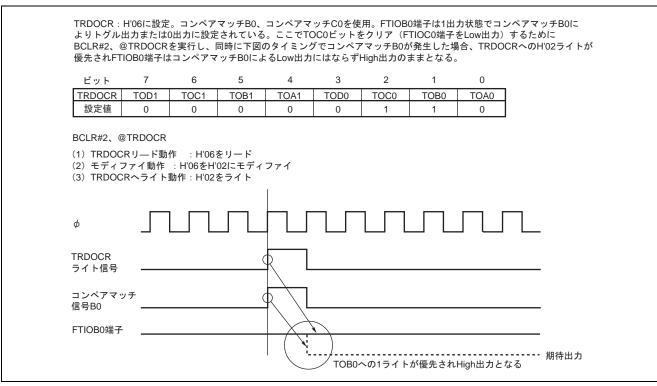

| 16.4.2              | ステータスフラグのクリアタイミング                       | 16-88 |

| 16.5 使              | 用上の注意事項                                 | 16-89 |

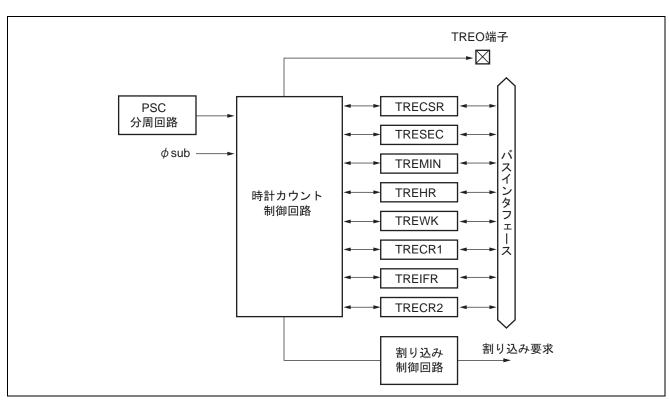

| 17. タイマ F           | RE                                      | 17-1  |

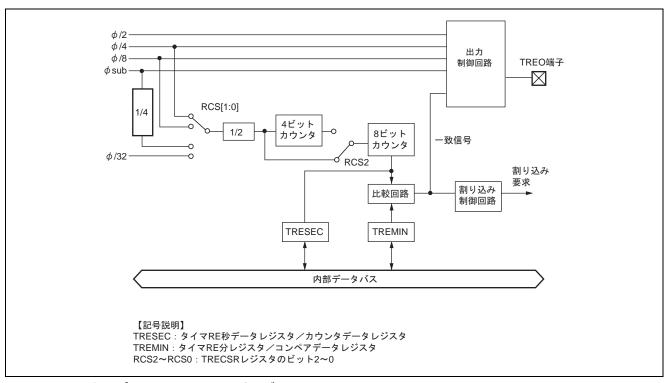

| 17.1 概              | 要                                       | 17-1  |

| 17.2 iz             | ジスタの説明                                  | 17_3  |

| 17.2.1              | タイマ RE 秒データレジスタ/カウンタデータレジスタ(TRESEC) | 17-4  |

|---------------------|-------------------------------------|-------|

| 17.2.2              | タイマ RE 分データレジスタ/コンペアデータレジスタ(TREMIN) | 17-5  |

| 17.2.3              | タイマ RE 時データレジスタ(TREHR)              | 17-6  |

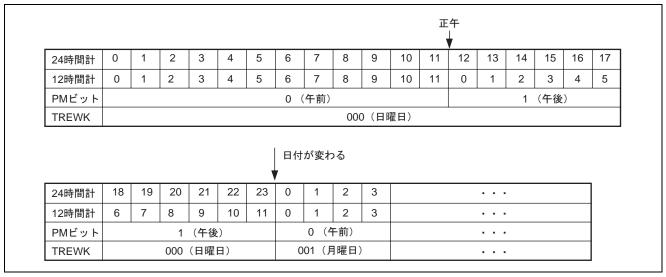

| 17.2.4              | タイマ RE 曜日データレジスタ(TREWK)             | 17-7  |

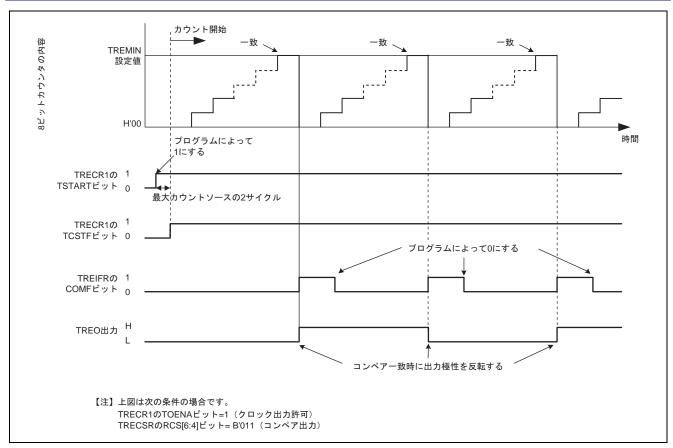

| 17.2.5              | タイマ RE コントロールレジスタ 1(TRECR1)         | 17-8  |

| 17.2.6              | タイマ RE コントロールレジスタ 2(TRECR2)         | 17-10 |

| 17.2.7              | タイマ RE 割り込みフラグレジスタ(TREIFR)          | 17-11 |

| 17.2.8              | タイマ RE クロックソースセレクトレジスタ(TRECSR)      | 17-13 |

| 17.3 リン             | アルタイムクロックモードの動作                     | 17-14 |

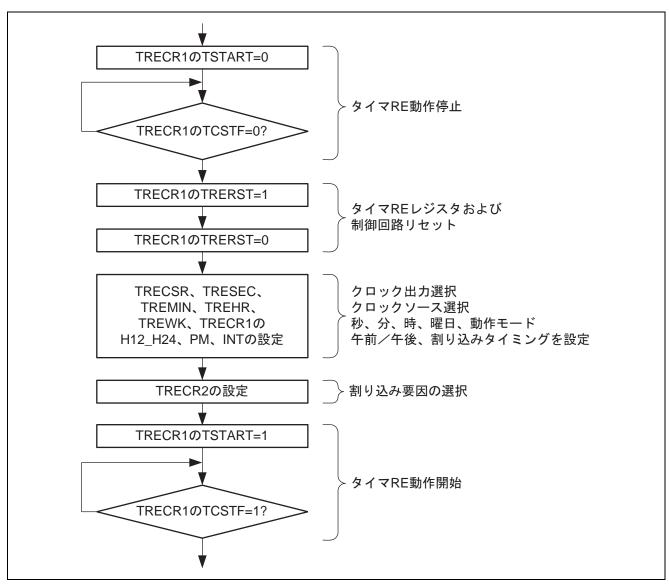

| 17.3.1              | 電源投入後のレジスタの初期設定                     | 17-14 |

| 17.3.2              | 初期設定手順                              | 17-14 |

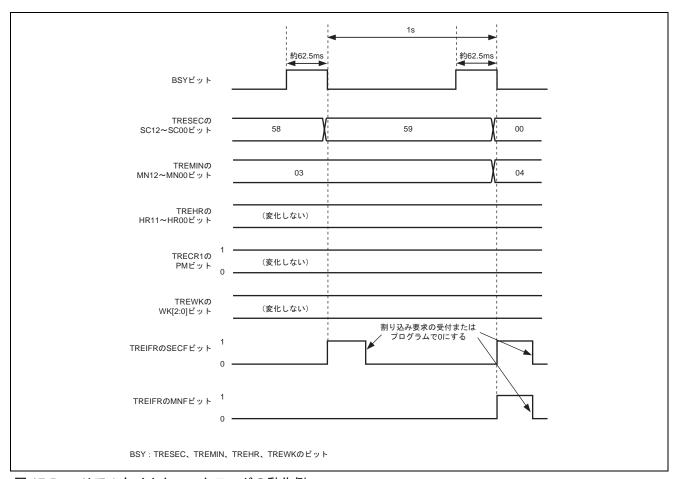

| 17.3.3              | リアルタイムクロックモード時の時刻読み出し手順             | 17-15 |

| 17.3.4              | リアルタイムクロックモードの動作例                   | 17-16 |

| 17.4 ア              | ウトプットコンペアモードの動作                     | 17-17 |

| 17.5 割              | り込み要因                               | 17-19 |

| 17.6 使力             | 用上の注意事項                             | 17-20 |

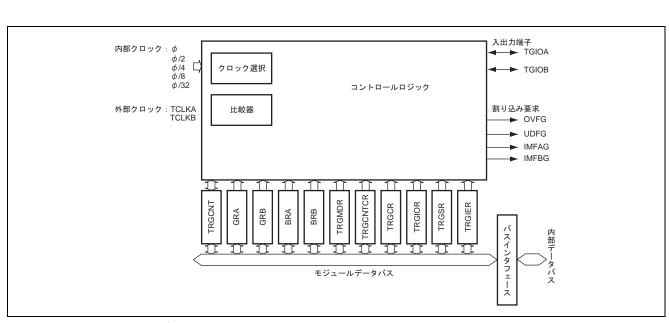

| 18. タイマ R           | ?G                                  | 18-1  |

| 18.1 概              | 要                                   | 18-1  |

| 18.2 V              | ジスタの説明                              | 18-4  |

| 18.2.1              | タイマ RG モードレジスタ(TRGMDR)              | 18-5  |

| 18.2.2              | タイマ RG カウンタコントロールレジスタ(TRGCNTCR)     | 18-6  |

| 18.2.3              | タイマ RG コントロールレジスタ(TRGCR)            | 18-7  |

| 18.2.4              | タイマ RG I/O コントロールレジスタ(TRGIOR)       | 18-8  |

| 18.2.5              | タイマ RG ステータスレジスタ(TRGSR)             | 18-9  |

| 18.2.6              | タイマ RG インタラプトイネーブルレジスタ(TRGIER)      | 18-10 |

| 18.2.7              | タイマ RG カウンタ(TRGCNT)                 | 18-11 |

| 18.2.8              | ジェネラルレジスタ A、B(GRA、GRB)              |       |

|                     | GRA バッファレジスタ、GRB バッファレジスタ(BRA、BRB)  | 18-12 |

| 18.3 動作             | 作説明                                 | 18-13 |

| 18.3.1              | タイマモード                              | 18-14 |

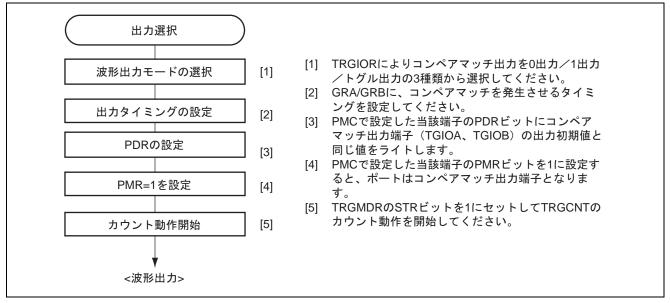

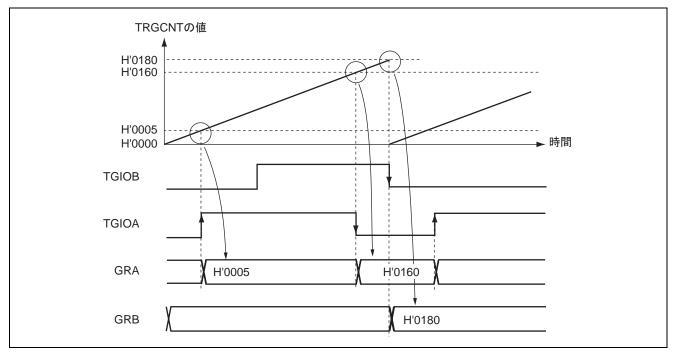

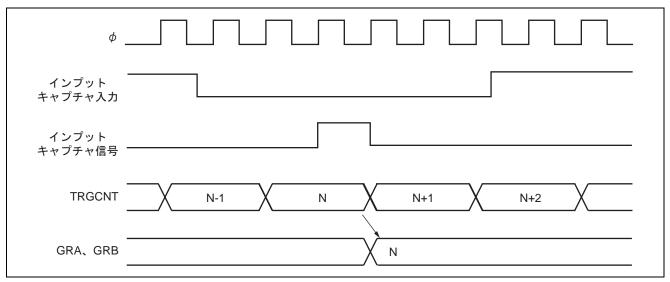

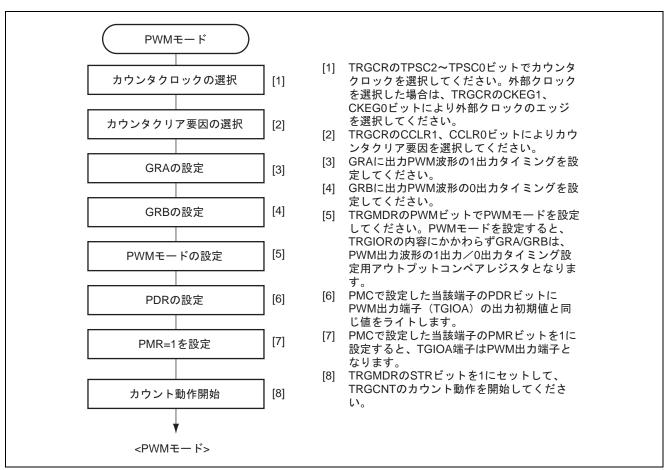

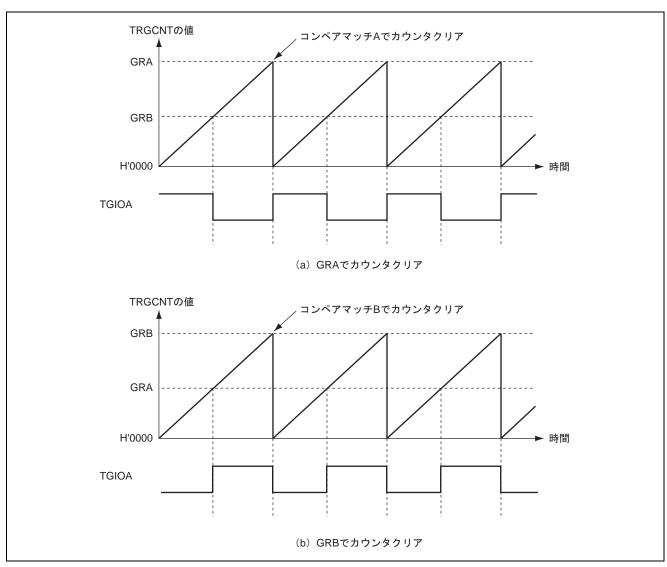

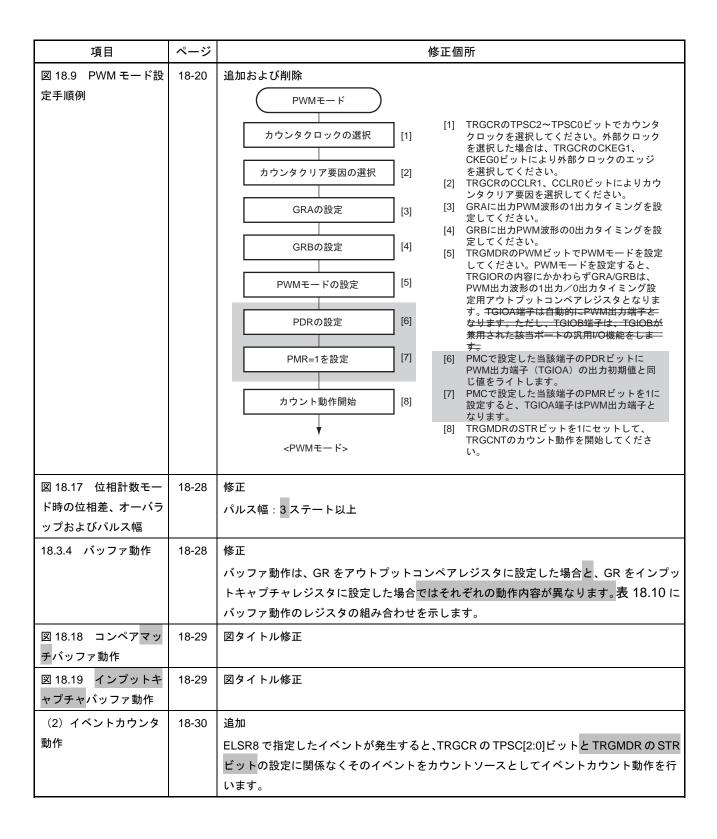

| 18.3.2              | PWM モード                             | 18-20 |

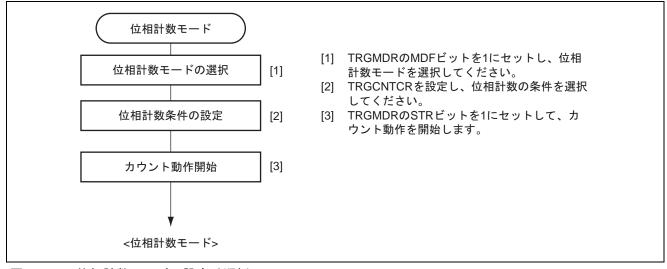

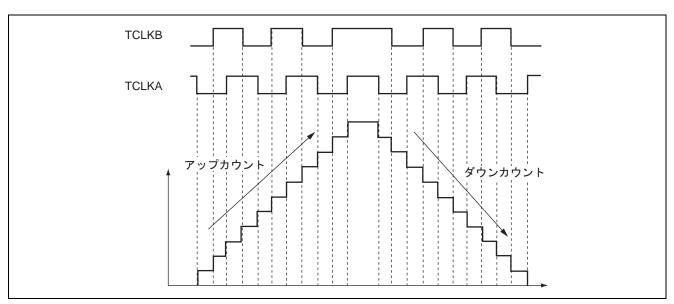

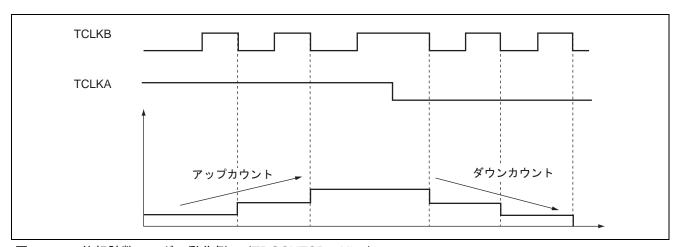

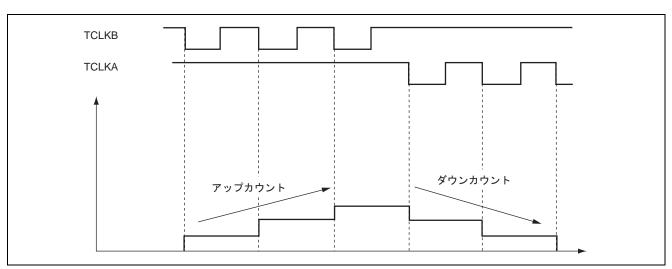

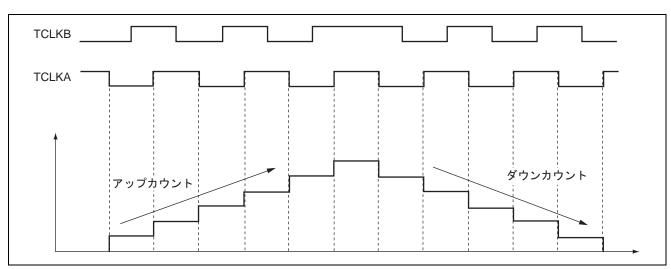

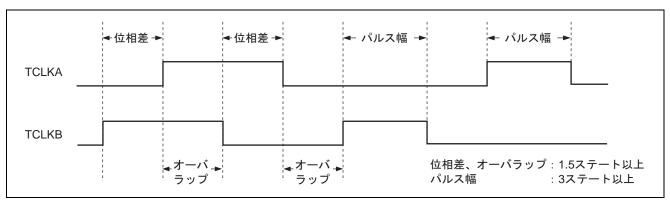

| 18.3.3              | 位相計数モード                             | 18-23 |

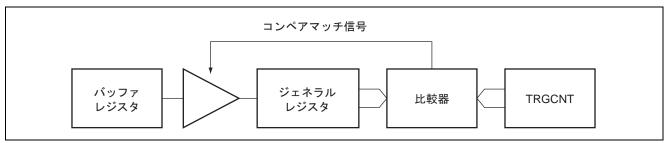

| 18.3.4              | バッファ動作                              | 18-28 |

| 18.3.5 イベントリンクによる動作 |                                     | 18-30 |

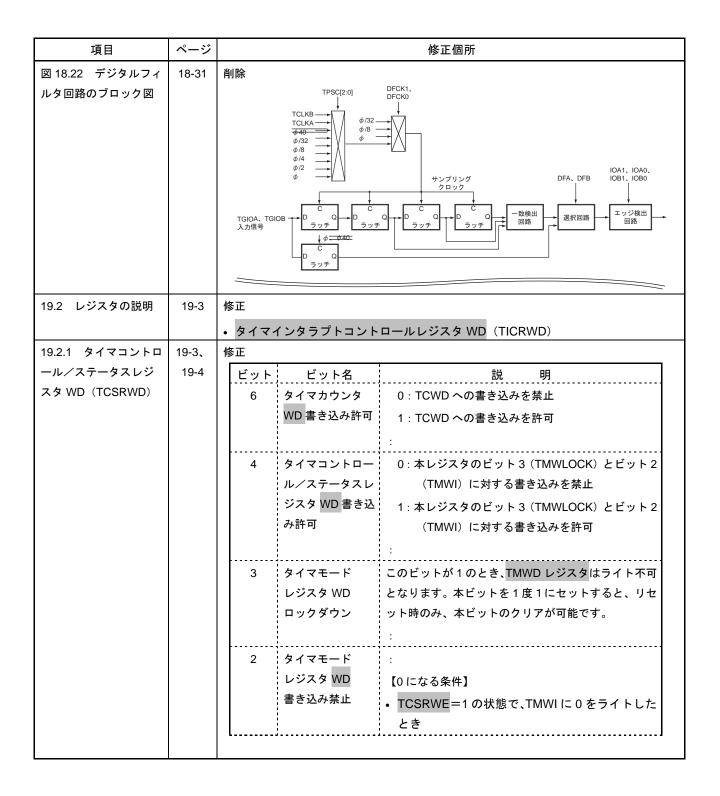

| 18.3.6              | インプットキャプチャ入力デジタルフィルタ機能              | 18-31 |

| 19. ウォ | ッチドッグタイマ(WDT)                        | 19-1  |

|--------|--------------------------------------|-------|

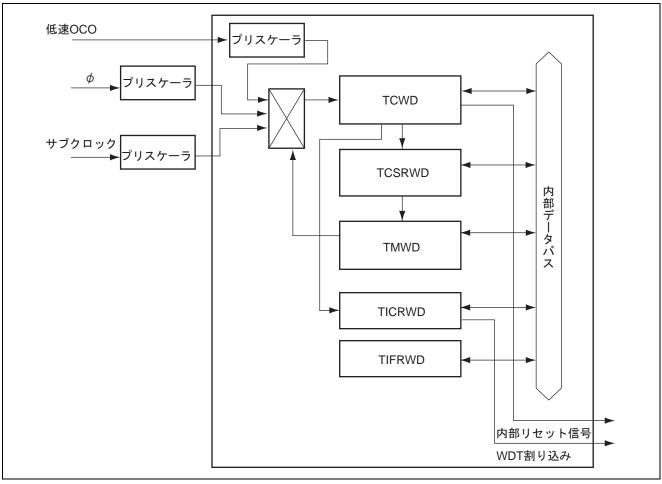

| 19.1   | 概要                                   | 19-2  |

| 19.2   | レジスタの説明                              | 19-3  |

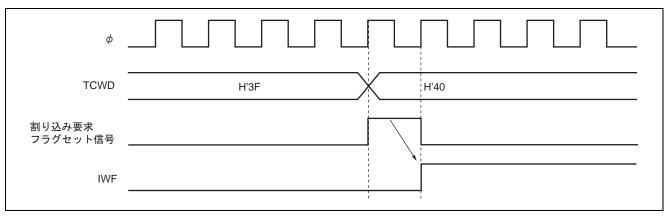

| 19.2.1 | タイマコントロール/ステータスレジスタ WD(TCSRWD)       | 19-3  |

| 19.2.2 | タイマカウンタ WD(TCWD)                     | 19-4  |

| 19.2.3 | タイマモードレジスタ WD(TMWD)                  | 19-5  |

| 19.2.4 | タイマインタラプトコントロールレジスタ WD(TICRWD)       | 19-6  |

| 19.2.5 | タイマインタラプトフラグレジスタ WD(TIFRWD)          | 19-7  |

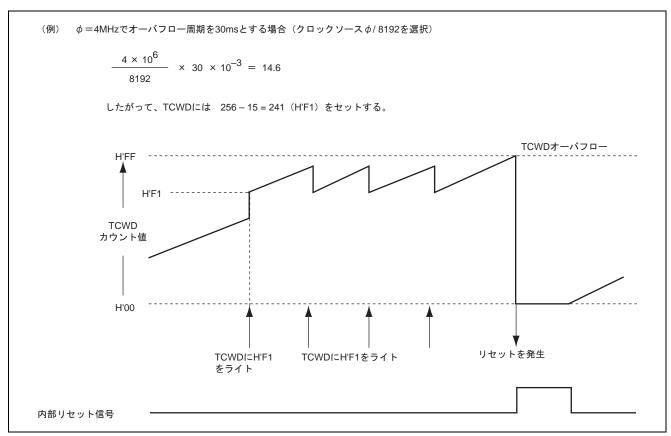

| 19.3   | 動作説明                                 | 19-8  |

| 19.3.1 | ウォッチドッグタイマオーバフローリセット                 | 19-8  |

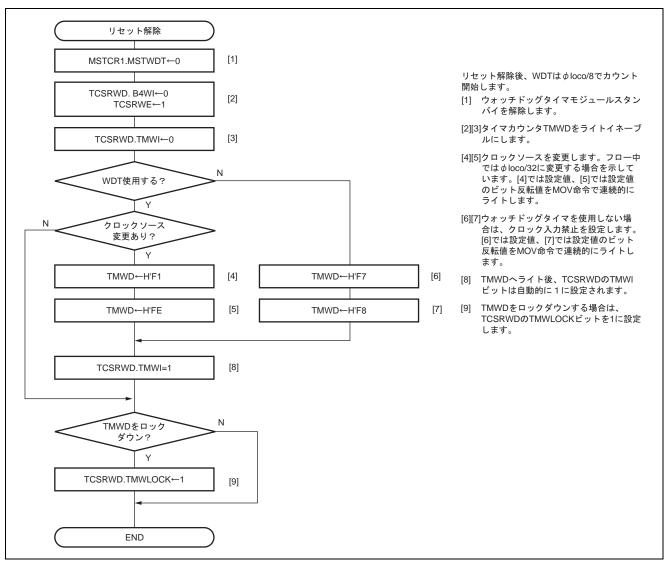

| 19.3.2 | ウォッチドッグタイマ設定フロー                      | 19-9  |

| 19.3.3 | ウォッチドッグタイマ周期割り込み                     | 19-10 |

| 19.4   | 使用上の注意事項                             | 19-11 |

| 19.4.1 | システム設計上での留意点                         | 19-11 |

| 19.4.2 | ウォッチドッグタイマを停止またはカウントクロックを切り替えるときの注意点 | 19-11 |

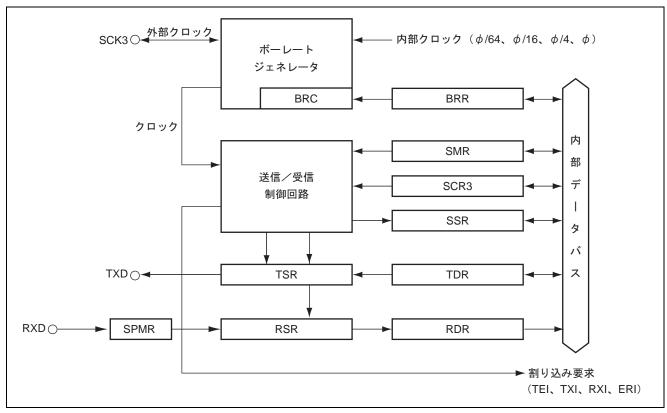

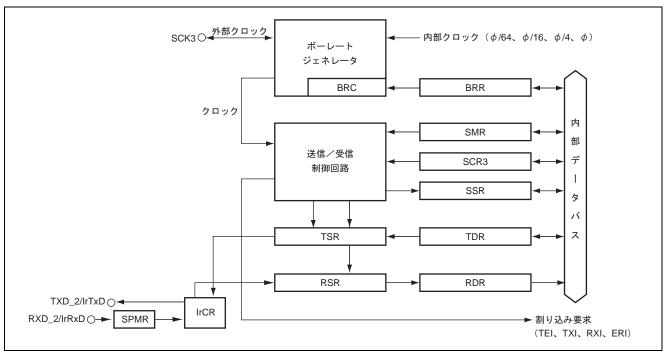

| 20. シリ | アルコミュニケーションインタフェース 3(SCI3、IrDA)      | 20-1  |

| 20.1   | 概要                                   | 20-1  |

| 20.2   | レジスタの説明                              | 20-5  |

| 20.2.1 | レシーブシフトレジスタ(RSR)                     | 20-6  |

| 20.2.2 | レシーブデータレジスタ(RDR)                     | 20-6  |

| 20.2.3 | トランスミットシフトレジスタ(TSR)                  | 20-6  |

| 20.2.4 | トランスミットデータレジスタ(TDR)                  | 20-7  |

| 20.2.5 | シリアルモードレジスタ(SMR)                     | 20-8  |

| 20.2.6 | シリアルコントロールレジスタ 3 (SCR3)              | 20-10 |

| 20.2.7 | ンリアルステータスレジスタ(SSR)                   | 20-11 |

| 20.2.8 | ビットレートレジスタ(BRR)                      | 20-13 |

| 20.2.9 | サンプリングモードレジスタ(SPMR)                  | 20-17 |

| 20.2.1 | 0 IrDA コントロールレジスタ(IrCR)              | 20-18 |

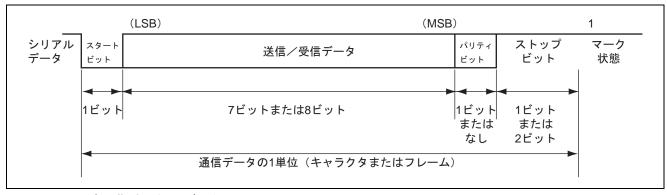

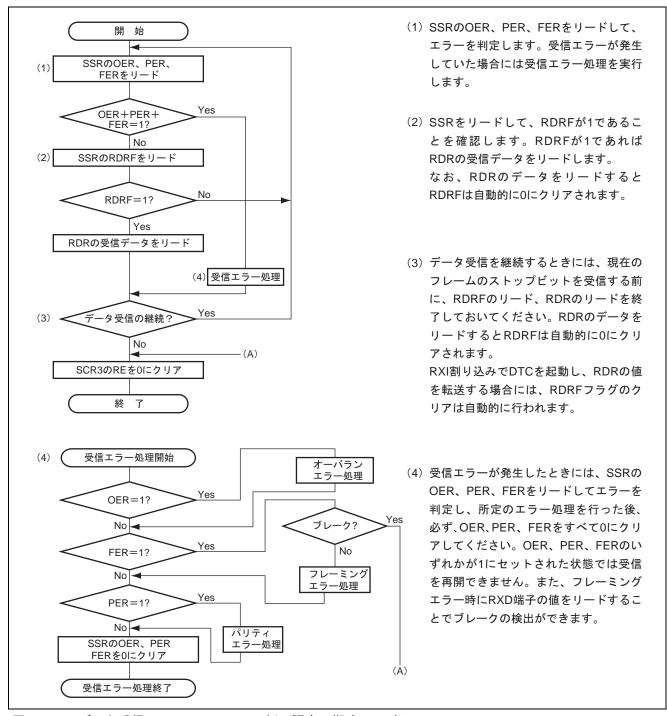

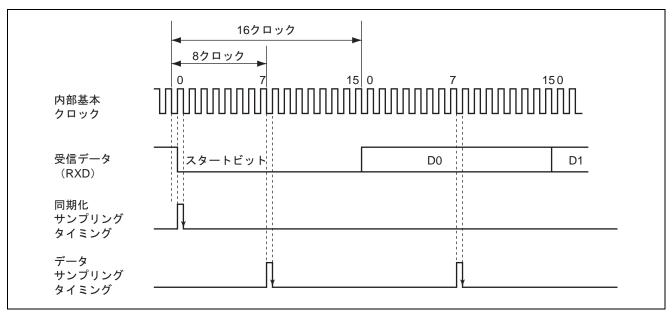

| 20.3   | 調歩同期式モードの動作説明                        | 20-19 |

| 20.3.1 | クロック                                 | 20-19 |

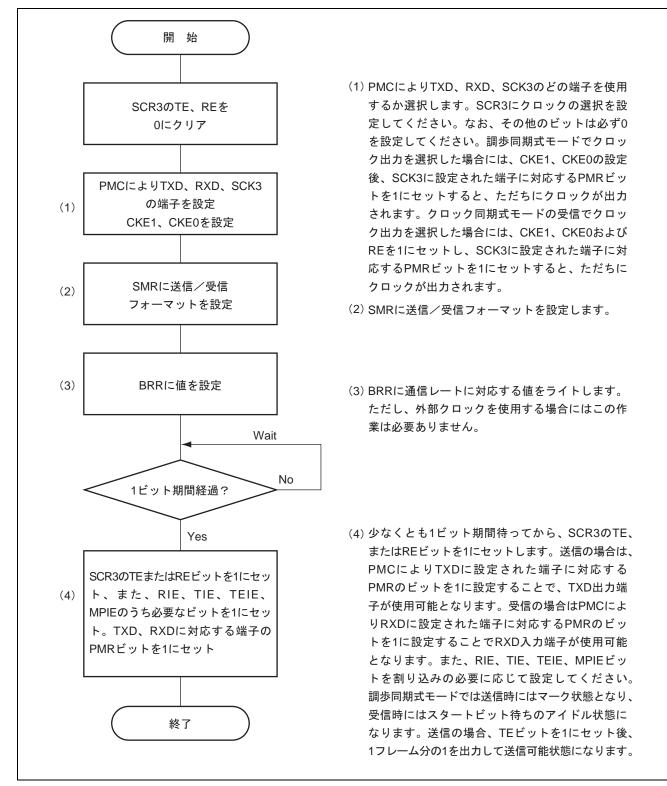

| 20.3.2 | SCI3 の初期化                            | 20-20 |

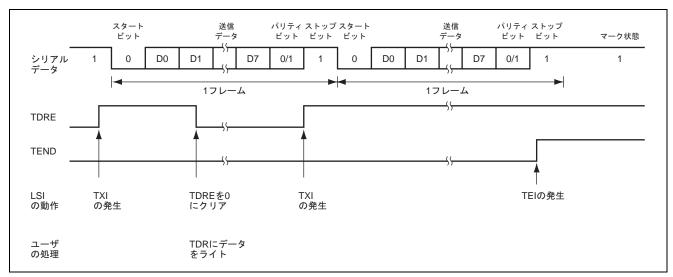

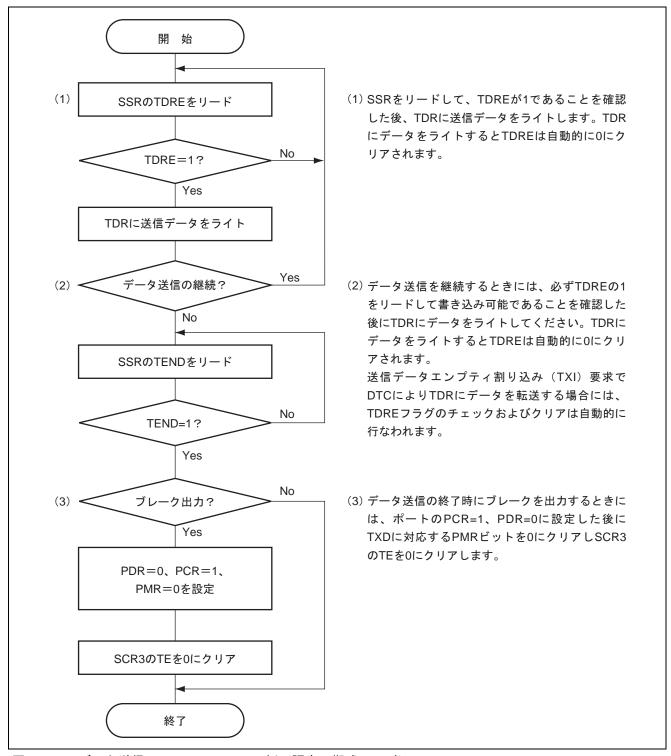

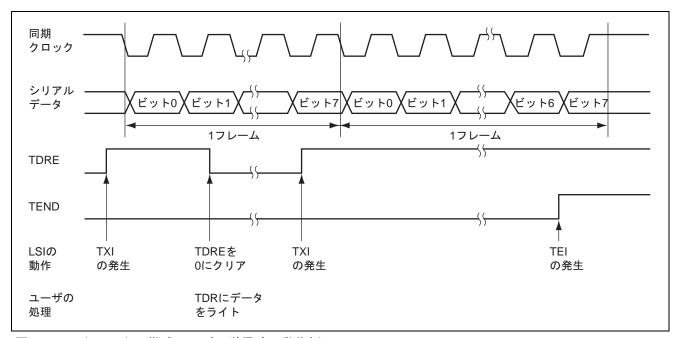

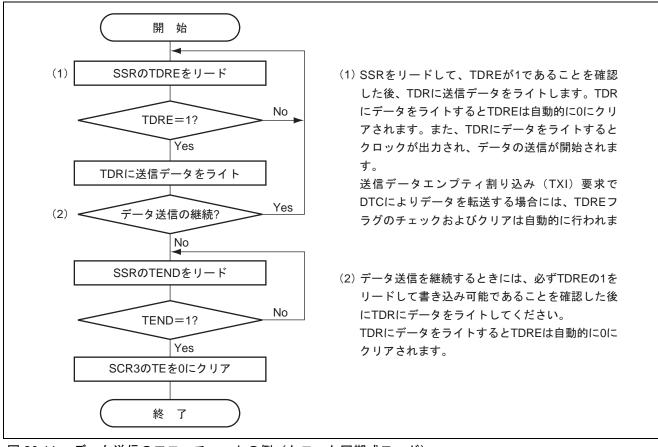

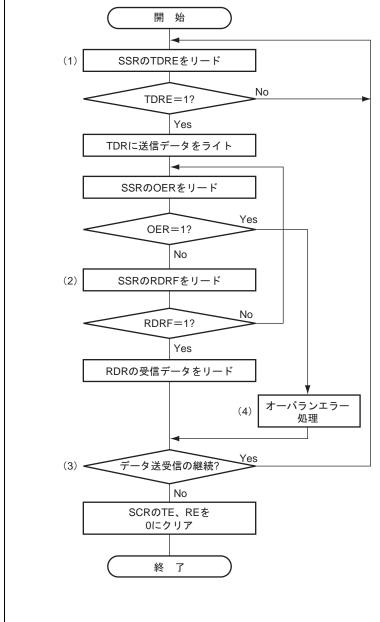

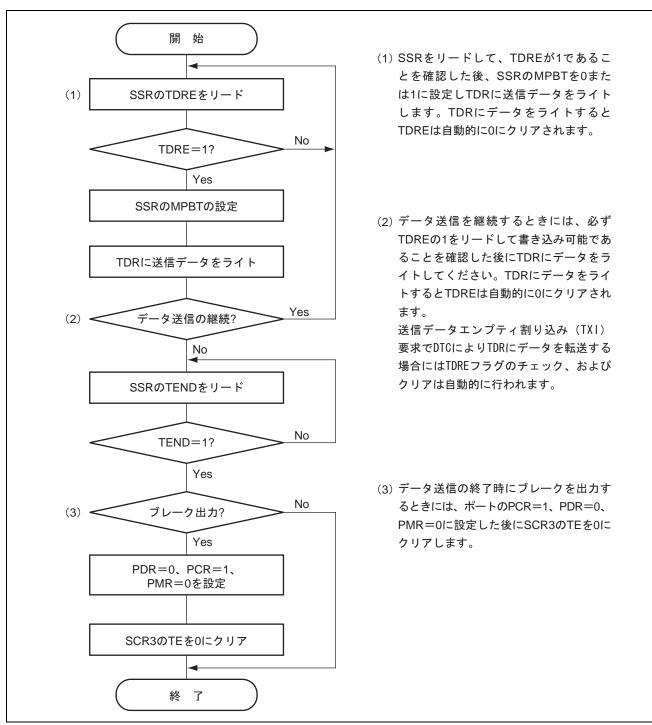

| 20.3.3 | データ送信                                | 20-21 |

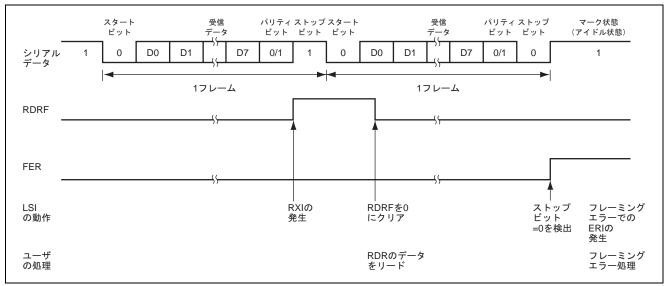

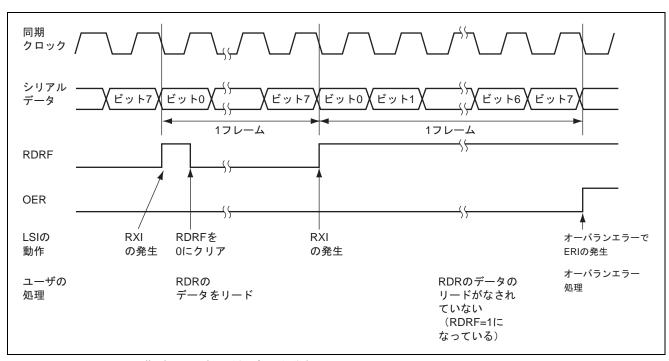

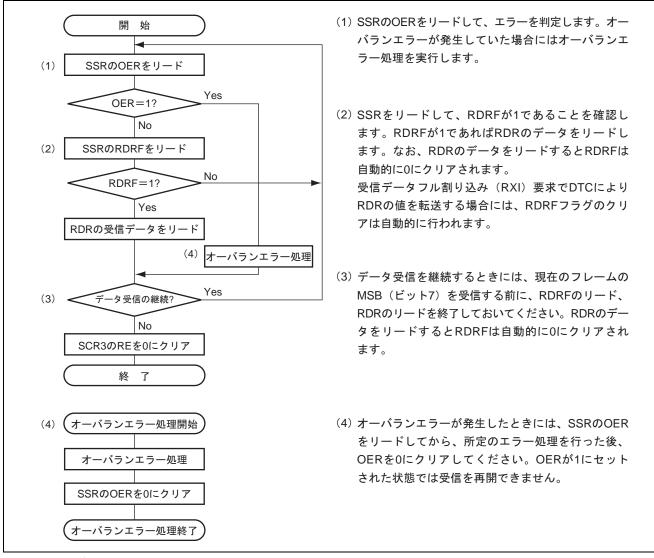

| 20.3.4 | データ受信                                | 20-23 |

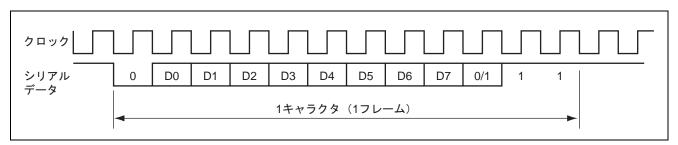

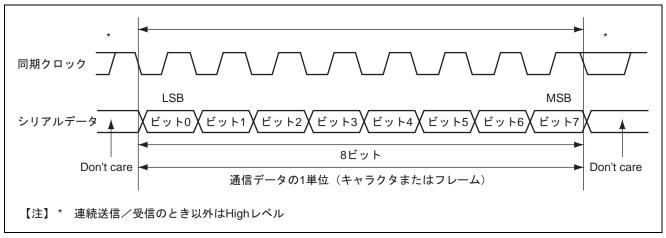

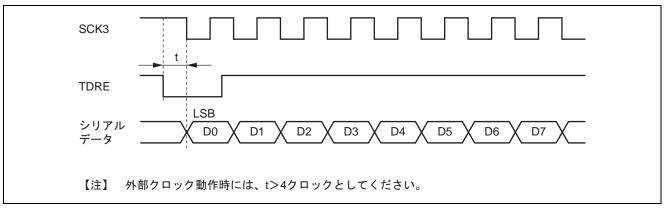

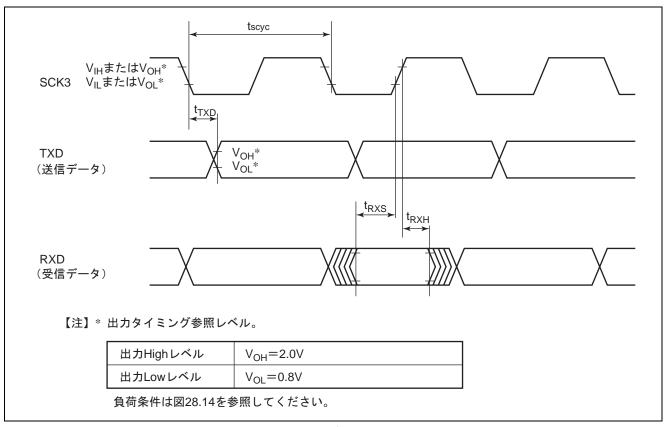

| 20.4   | クロック同期式モードの動作説明                      |       |

| 20.4.1 |                                      |       |

| 20.4.2 | SCI3 の初期化                            | 20-26 |

| 20.4.3 |                                      |       |

| 20.4.4 データ受信 |                                                                                                                      |       |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|-------|--|--|

| 20.4.5       | 20.4.5 データ送受信同時動作                                                                                                    |       |  |  |

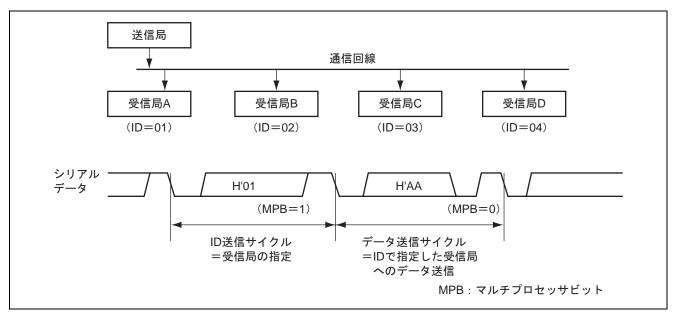

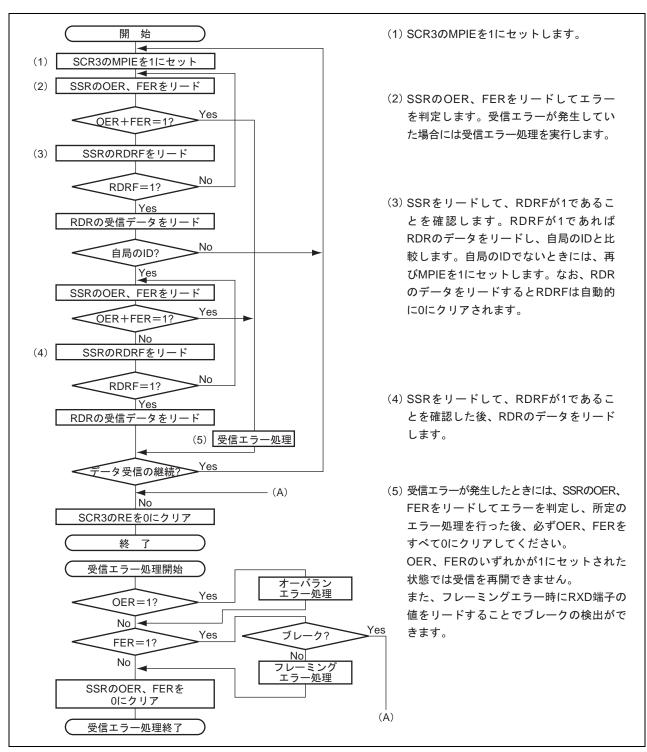

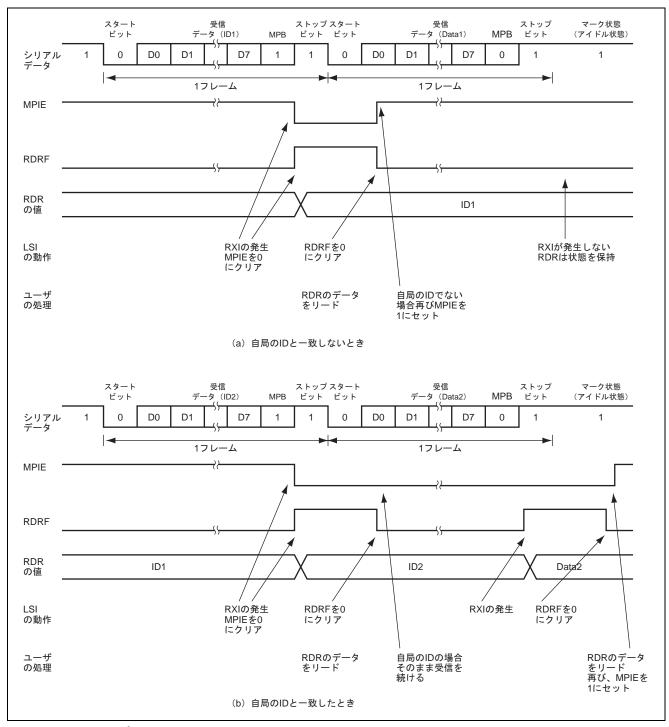

| 20.5 マル      | <b>・チプロセッサ通信機能</b>                                                                                                   | 20-32 |  |  |

| 20.5.1       | 20.5.1 マルチプロセッサデータ送信                                                                                                 |       |  |  |

| 20.5.2       | マルチプロセッサデータ受信                                                                                                        | 20-34 |  |  |

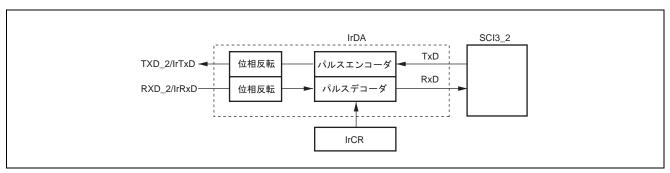

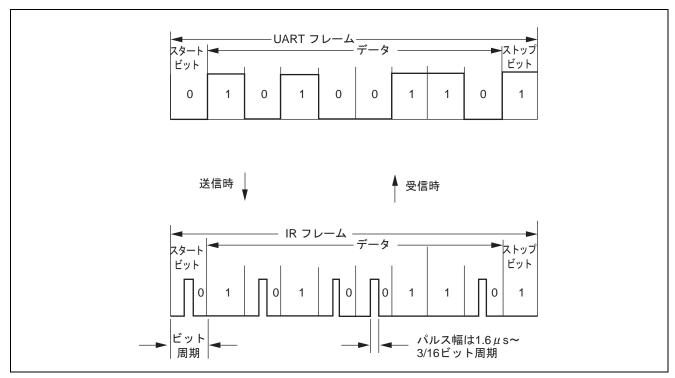

| 20.6 IrDA    | <b>A</b> 動作                                                                                                          | 20-36 |  |  |

| 20.6.1       | 送信                                                                                                                   | 20-37 |  |  |

| 20.6.2       | 受信                                                                                                                   | 20-37 |  |  |

| 20.6.3       | ハイパルス幅の選択                                                                                                            | 20-38 |  |  |

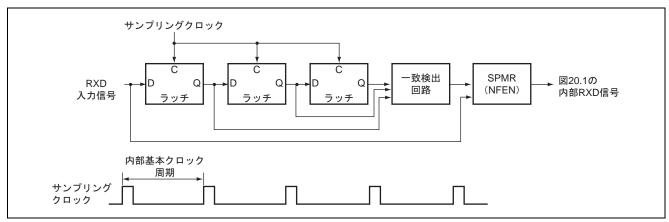

| 20.7 ノイ      | , ズ除去回路                                                                                                              | 20-39 |  |  |

| 20.8 割り      | 込み要求                                                                                                                 | 20-40 |  |  |

| 20.9 使用      | 上の注意事項                                                                                                               | 20-41 |  |  |

| 20.9.1       | ブレークの検出と処理について                                                                                                       | 20-41 |  |  |

| 20.9.2       | マーク状態とブレークの送出                                                                                                        | 20-41 |  |  |

| 20.9.3       | 受信エラーフラグと送信動作について(クロック同期式モードのみ)                                                                                      | 20-41 |  |  |

| 20.9.4       | 調歩同期式モードの受信データサンプリングタイミングと受信マージン                                                                                     | 20-42 |  |  |

| 20.9.5       | TDR へのライトと TDRE フラグの関係                                                                                               | 20-42 |  |  |

| 20.9.6       | DTC 使用上の制約                                                                                                           | 20-43 |  |  |

| 2 .          |                                                                                                                      |       |  |  |

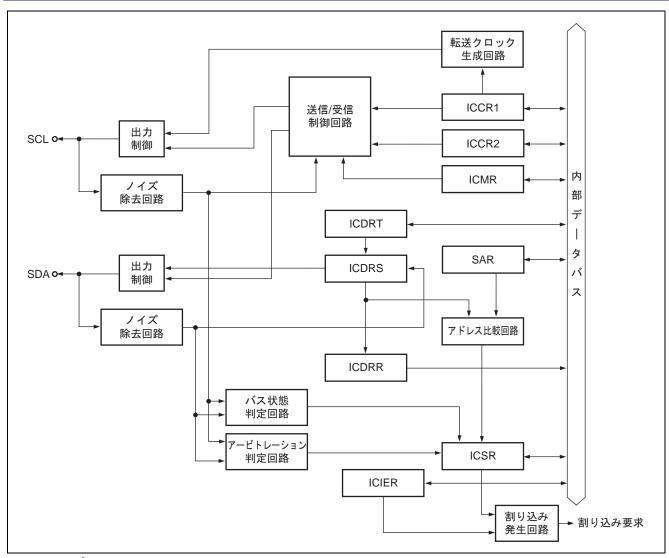

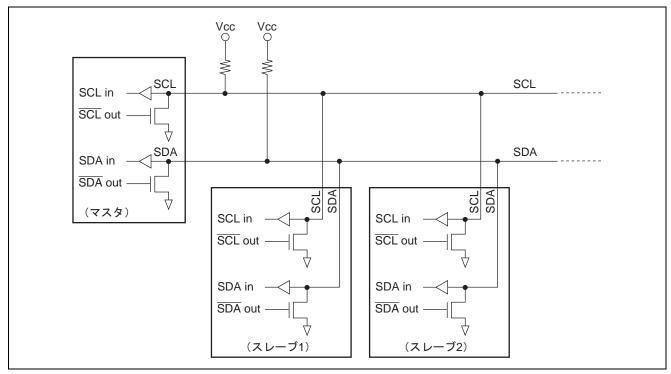

| 21. ピロバスイ    | ′ンタフェース 2(IIC2)                                                                                                      | 21-1  |  |  |

| 21.1 概要      |                                                                                                                      | 21-1  |  |  |

| 21.2 レジ      | ジスタの説明                                                                                                               | 21-4  |  |  |

| 21.2.1       | IIC2/SSU 選択レジスタ(ICSUSR)                                                                                              | 21-4  |  |  |

| 21.2.2       | $I^2C$ $\nearrow$ | 21-5  |  |  |

| 21.2.3       | I <sup>2</sup> C バスコントロールレジスタ 2 (ICCR2)                                                                              | 21-7  |  |  |

| 21.2.4       | I <sup>2</sup> C バスモードレジスタ(ICMR)                                                                                     | 21-9  |  |  |

| 21.2.5       | $I^2C$ バスインタラプトイネーブルレジスタ(ICIER)                                                                                      | 21-11 |  |  |

| 21.2.6       | I <sup>2</sup> C バスステータスレジスタ(ICSR)                                                                                   |       |  |  |

| 21.2.7       | スレーブアドレスレジスタ(SAR)                                                                                                    | 21-16 |  |  |

| 21.2.8       | I <sup>2</sup> C バス送信データレジスタ(ICDRT)                                                                                  | 21-16 |  |  |

| 21.2.9       | I <sup>2</sup> C バス受信データレジスタ(ICDRR)                                                                                  | 21-16 |  |  |

| 21.2.10      | I <sup>2</sup> C バスシフトレジスタ(ICDRS)                                                                                    | 21-17 |  |  |

| 21.3 動作      | =説明                                                                                                                  | 21-18 |  |  |

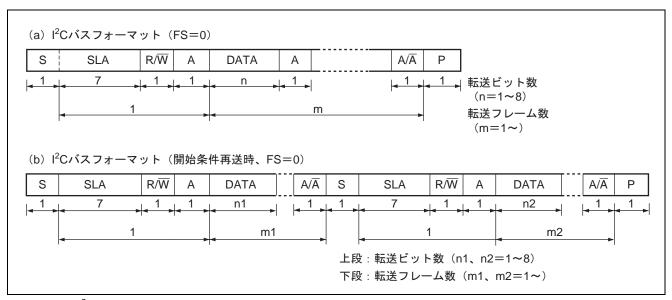

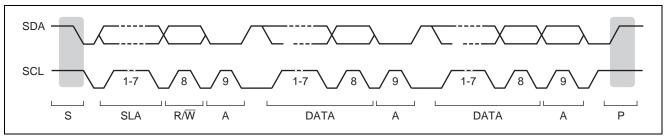

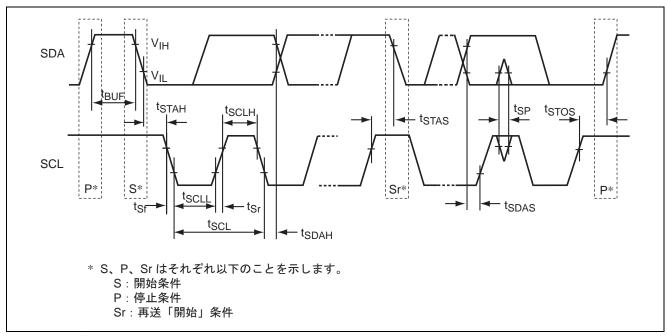

| 21.3.1       | I <sup>2</sup> C バスフォーマット                                                                                            | 21-18 |  |  |

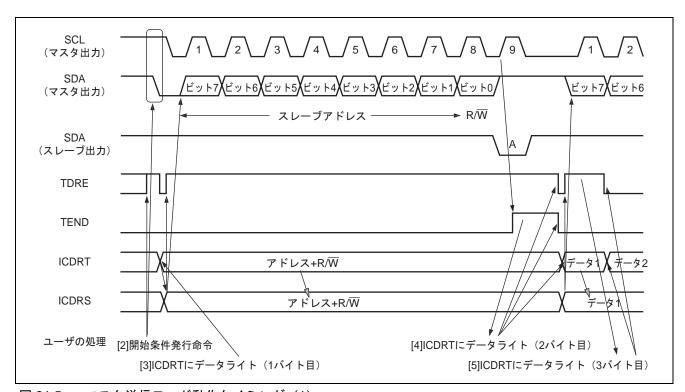

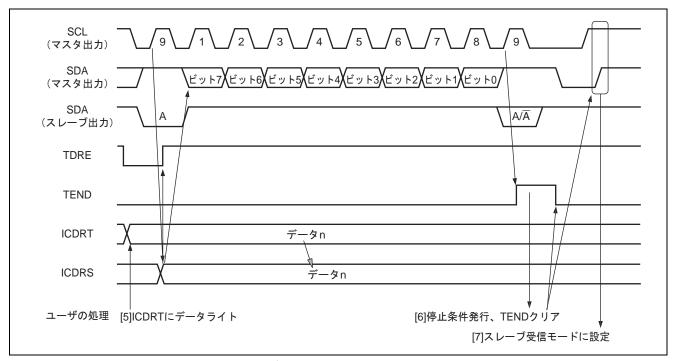

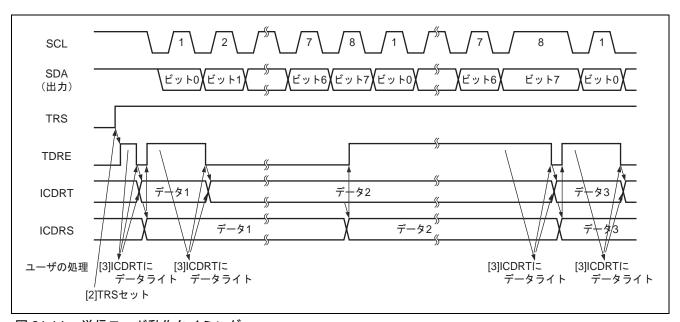

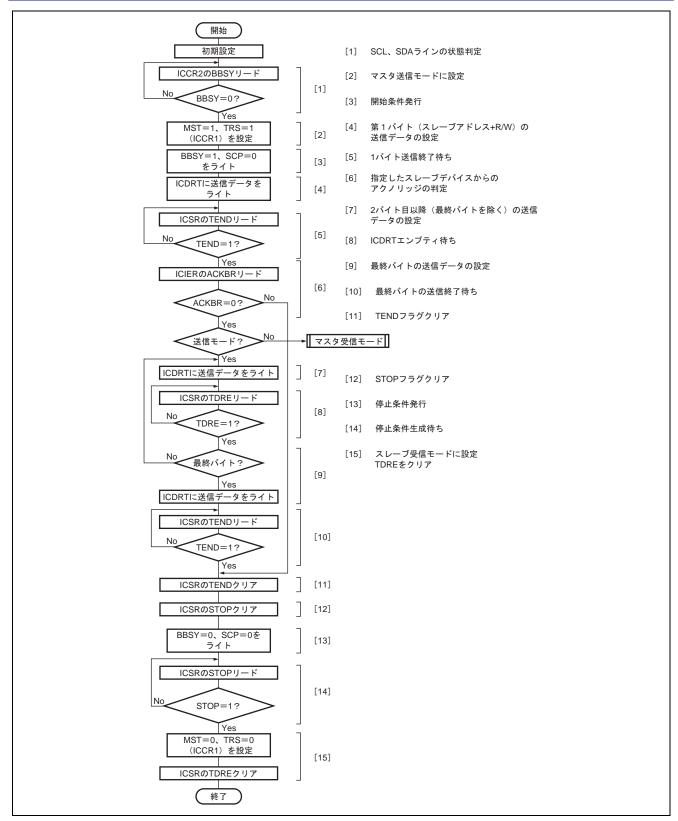

| 21.3.2       | マスタ送信動作                                                                                                              | 21-19 |  |  |

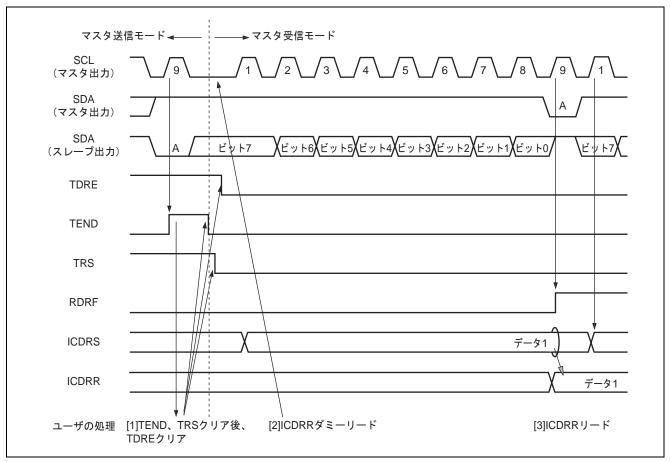

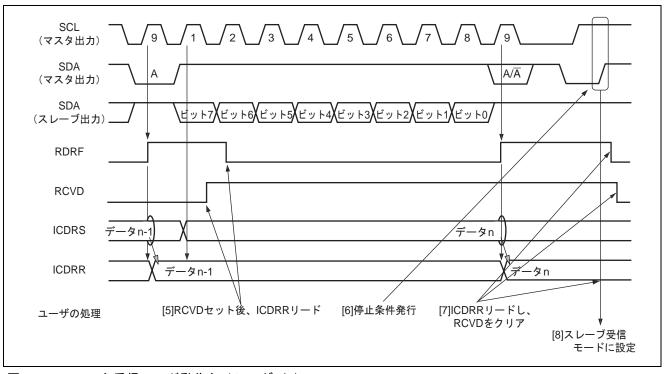

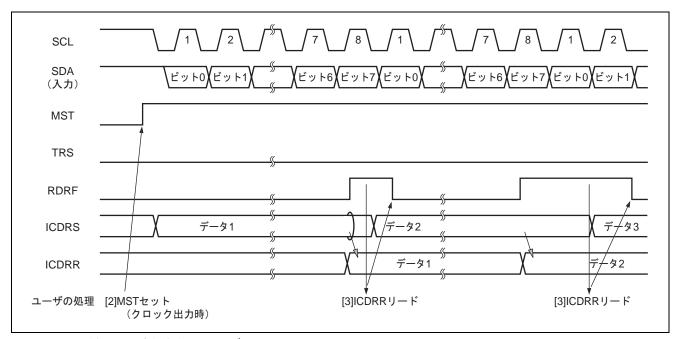

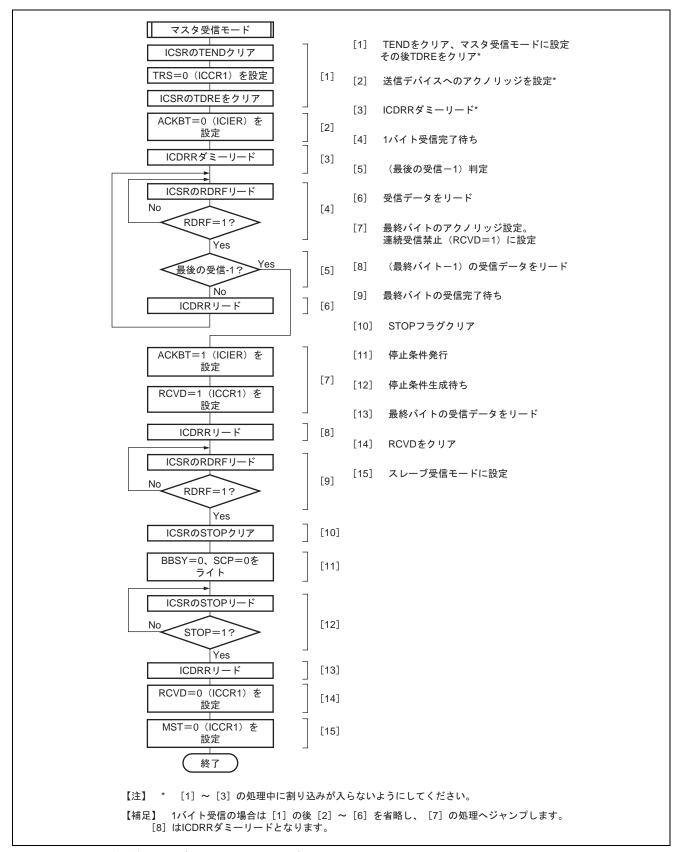

| 21.3.3       | マスタ受信動作                                                                                                              | 21-21 |  |  |

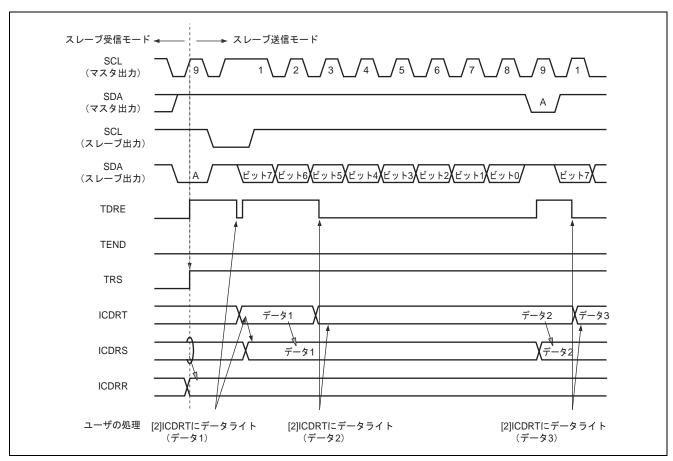

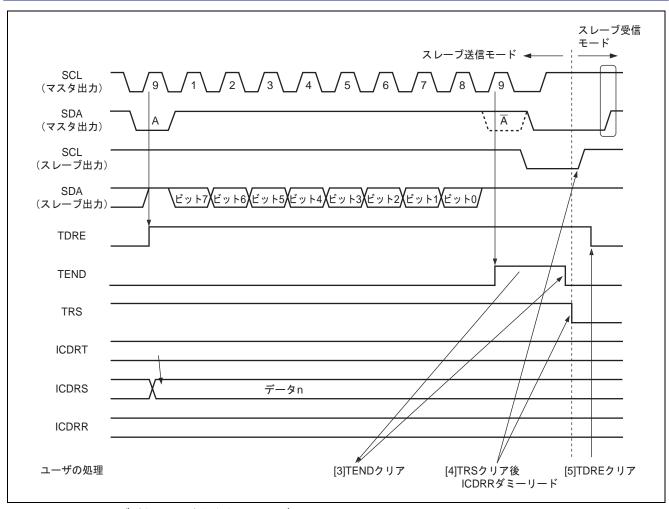

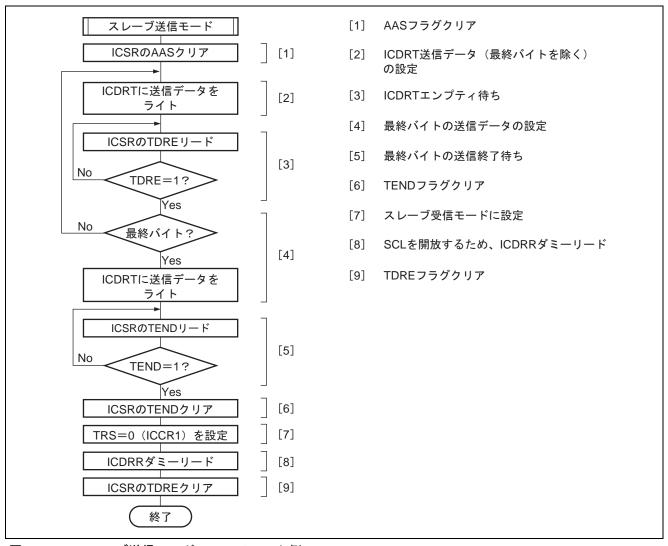

| 21.3.4       | スレーブ送信動作                                                                                                             | 21-23 |  |  |

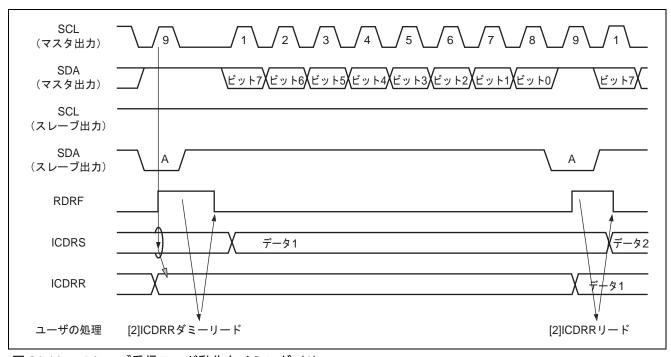

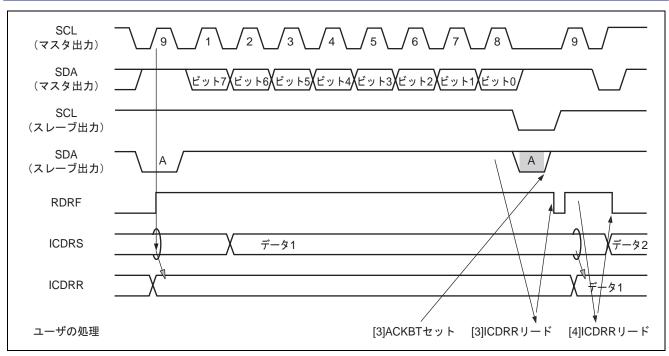

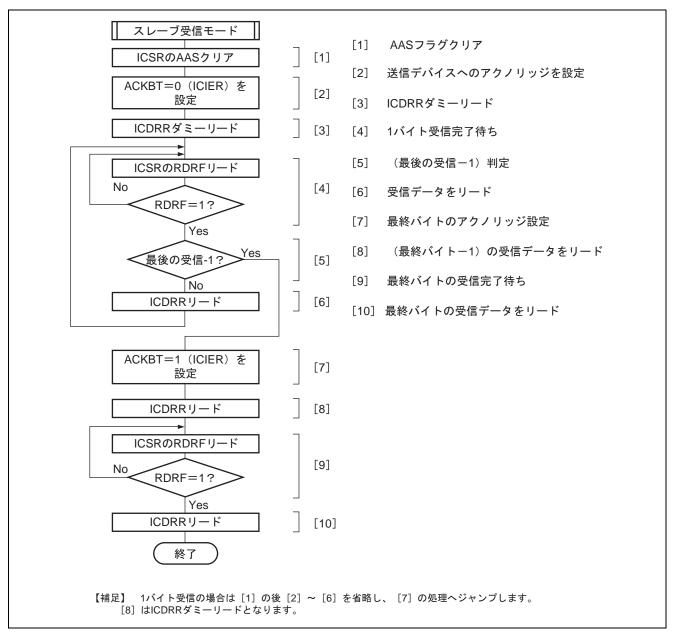

| 21.3.5       | スレーブ受信動作                                                                                                             | 21-25 |  |  |

| 21.3    | 21.3.6 クロック同期式シリアルフォーマット |                                               | 21-27 |

|---------|--------------------------|-----------------------------------------------|-------|

| 21.3    | 3.7                      | ノイズ除去回路                                       | 21-30 |

| 21.3    | 3.8                      | 使用例                                           | 21-30 |

| 21.4    | 割                        | ) 込み要求                                        | 21-35 |

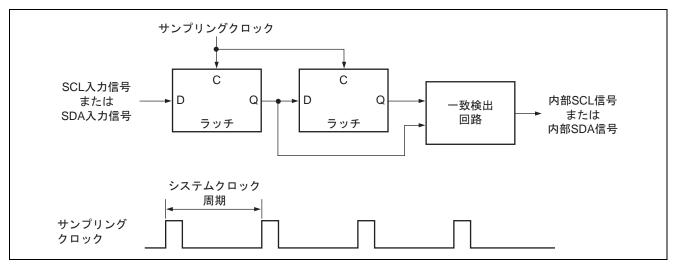

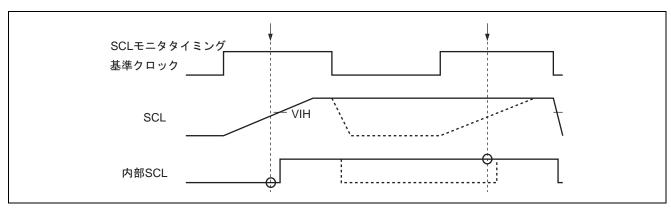

| 21.5    | ピ                        | ット同期回路                                        | 21-36 |

| 21.6    | 使月                       | 用上の注意事項                                       | 21-37 |

| 21.6    | 5.1                      | PMC における SCL、SDA 端子の設定                        | 21-37 |

| 21.6    | 5.2                      | マルチマスタ使用時での MST、TRS 設定時のビット操作命令使用制限           | 21-37 |

| 21.6    | 5.3                      | ${ m I}^2{ m C}$ バスインタフェースモードのマスタ受信モード時の注意事項  | 21-37 |

| 21.6    | 5.4                      | I <sup>2</sup> C バス動作中における ICCR1 の ICE ビットおよび |       |

|         |                          | ICCR2 の IICRST ビットのアクセスに関する注意事項               | 21-38 |

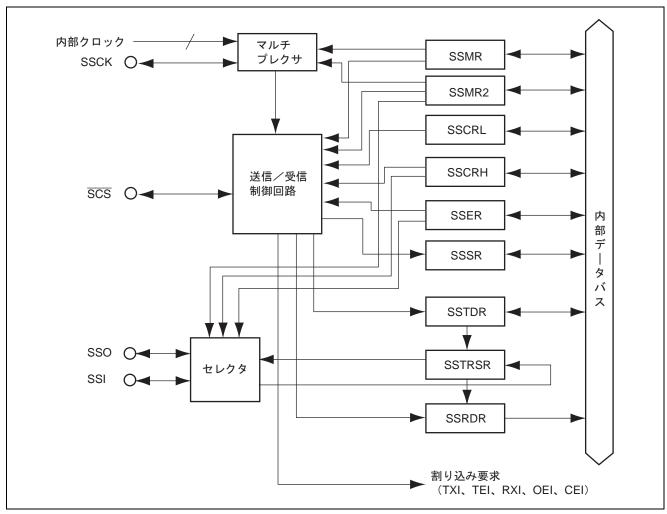

| 22. シン  | ノクロ                      | ナスシリアルコミュニケーションユニット                           | 22-1  |

| 22.1    | 概显                       | <b>要</b>                                      | 22-1  |

| 22.2    | レミ                       | ブスタの説明                                        | 22-3  |

| 22.2    | 2.1                      | IIC2/SSU 選択レジスタ(ICSUSR)                       | 22-3  |

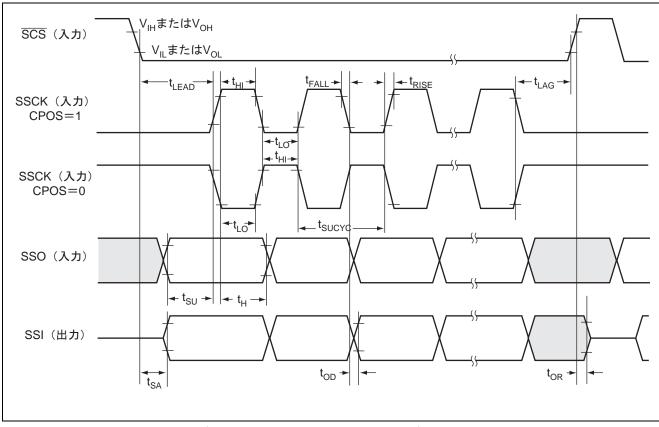

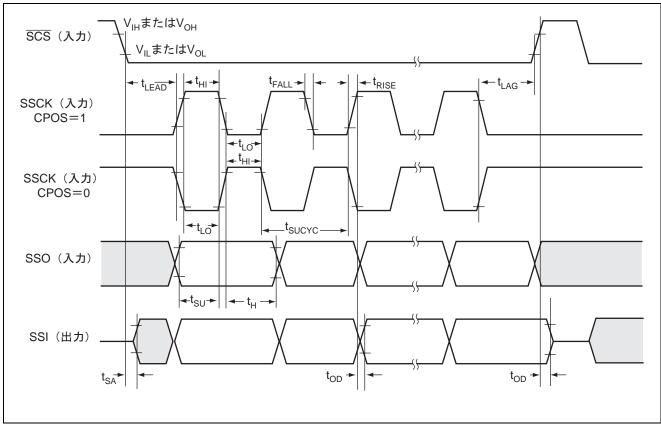

| 22.2    | 2.2                      | SS コントロールレジスタ H(SSCRH)                        | 22-4  |

| 22.2    | 2.3                      | SS コントロールレジスタ L(SSCRL)                        | 22-5  |

| 22.2    | 2.4                      | SS モードレジスタ(SSMR)                              | 22-6  |

| 22.2    | 2.5                      | SS モードレジスタ 2(SSMR2)                           | 22-7  |

| 22.2    | 2.6                      | SS イネーブルレジスタ(SSER)                            | 22-9  |

| 22.2    | 2.7                      | SS ステータスレジスタ(SSSR)                            | 22-10 |

| 22.2    | 2.8                      | SS レシーブデータレジスタ(SSRDR)                         | 22-12 |

| 22.2    | 2.9                      | SS トランスミットデータレジスタ(SSTDR)                      | 22-12 |

| 22.2    | 2.10                     | SS シフトレジスタ(SSTRSR)                            | 22-12 |

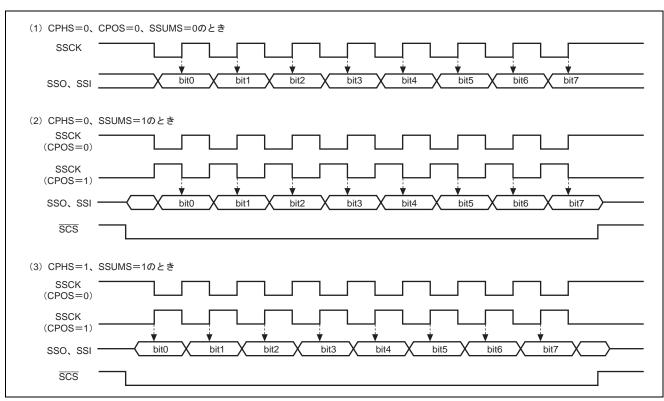

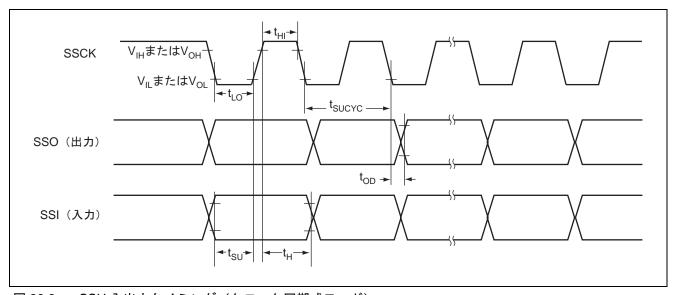

| 22.3    | 動作                       | 乍説明                                           | 22-13 |

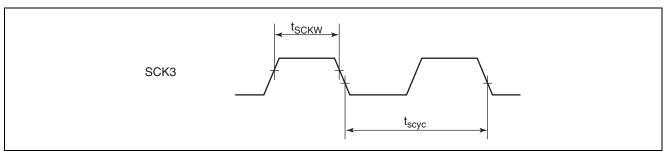

| 22.3    | 3.1                      | 転送クロック                                        | 22-13 |

| 22.3    | 3.2                      | クロックの極性、位相とデータの関係                             | 22-13 |

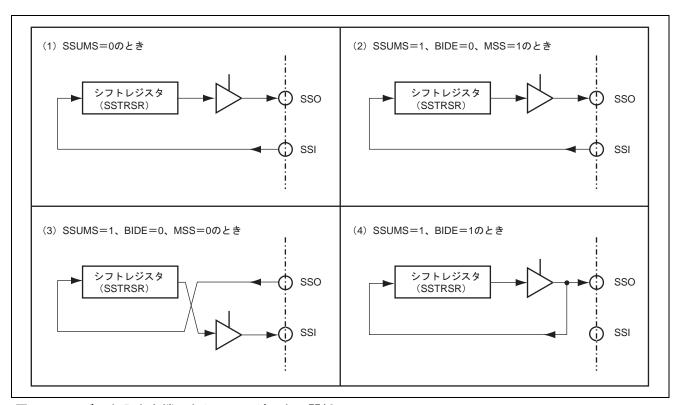

| 22.3    | 3.3                      | データ入出力端子とシフトレジスタの関係                           | 22-14 |

| 22.3    | 3.4                      | 各通信モードと端子機能                                   | 22-15 |

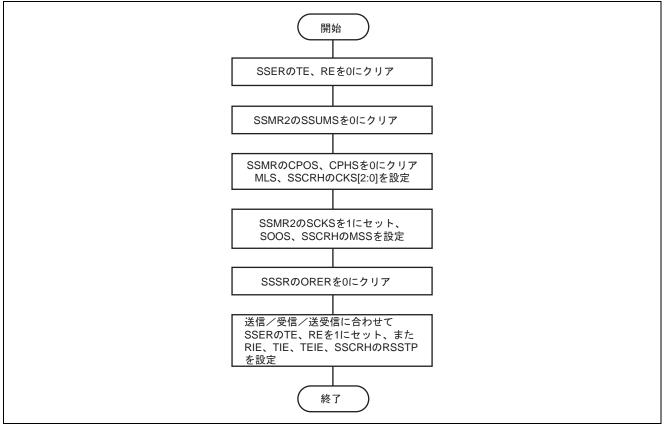

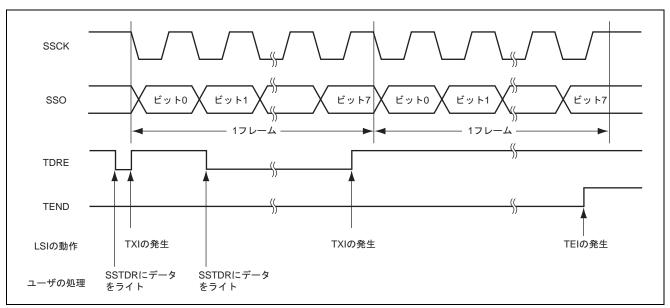

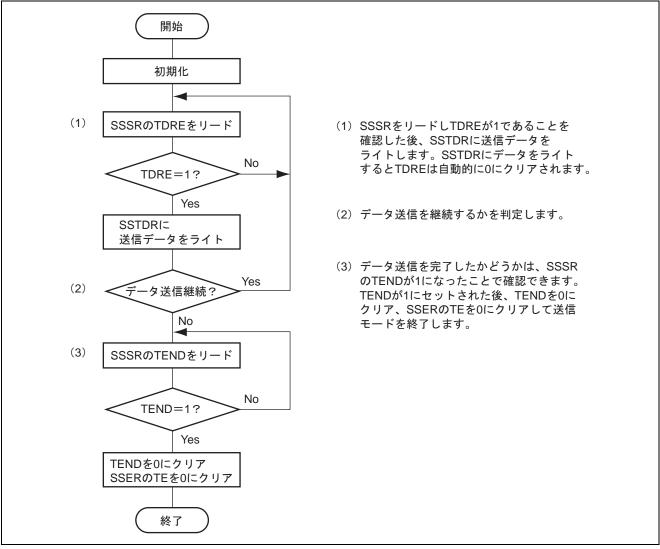

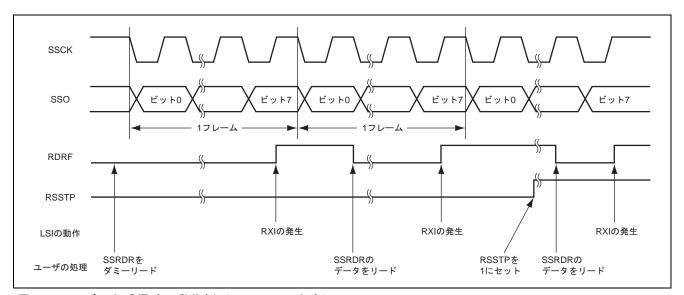

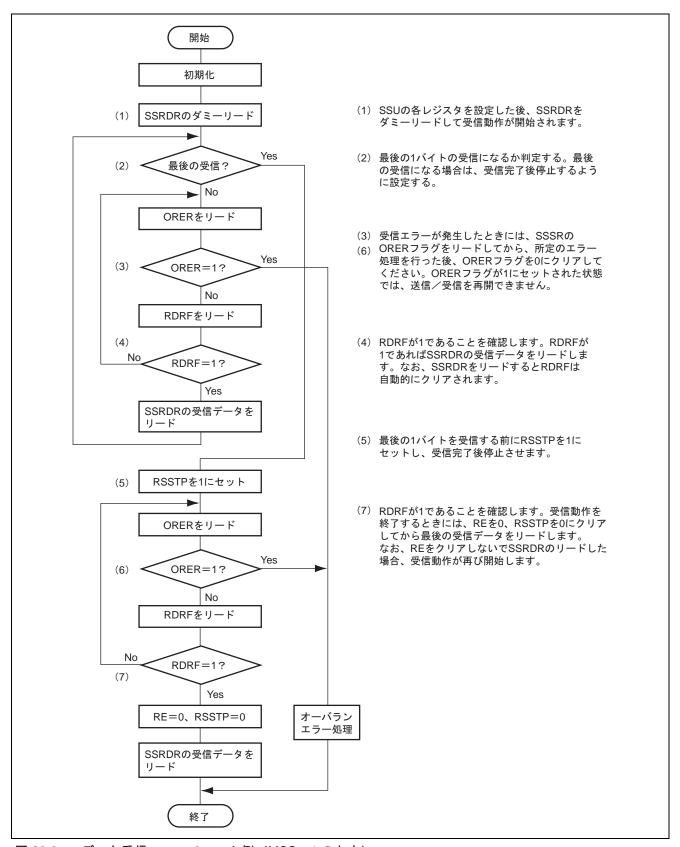

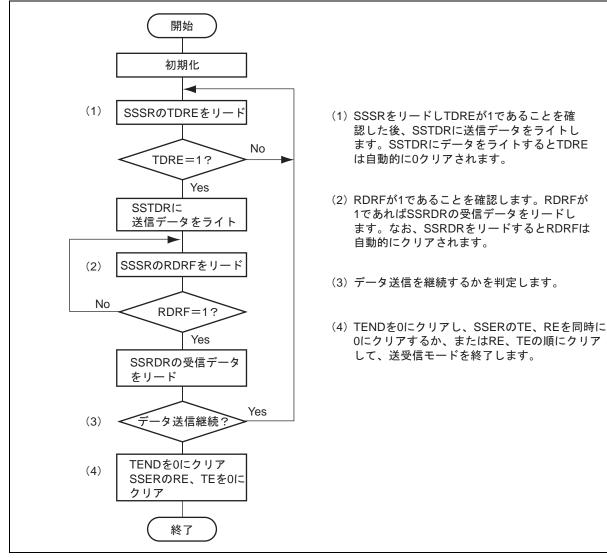

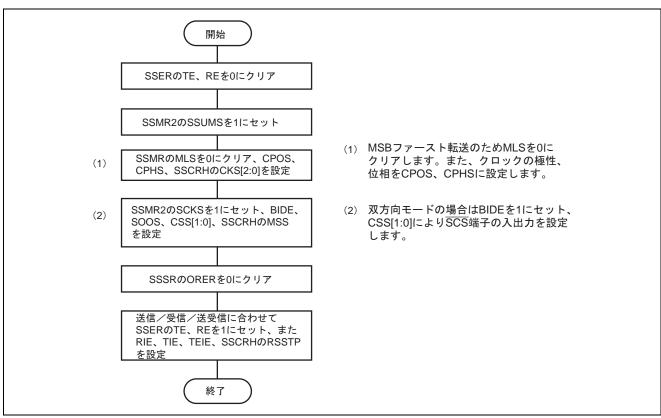

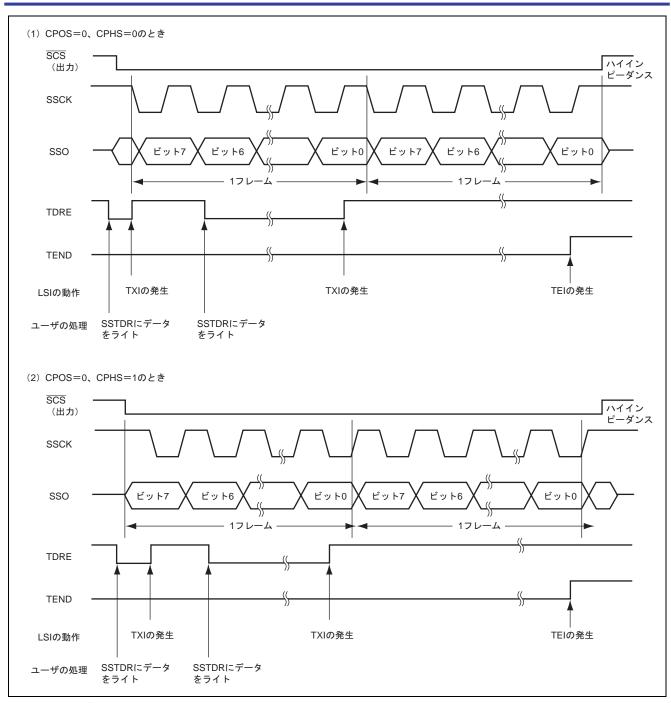

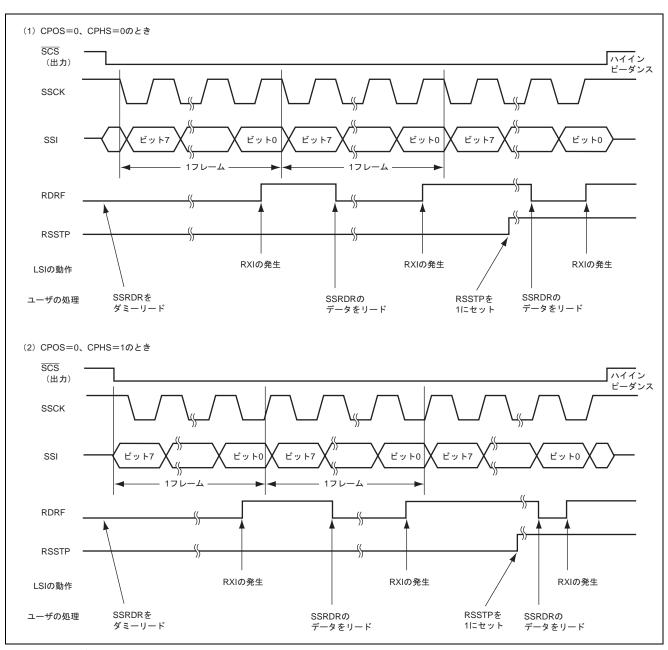

| 22.3    | 3.5                      | クロック同期式通信モードの動作                               | 22-16 |

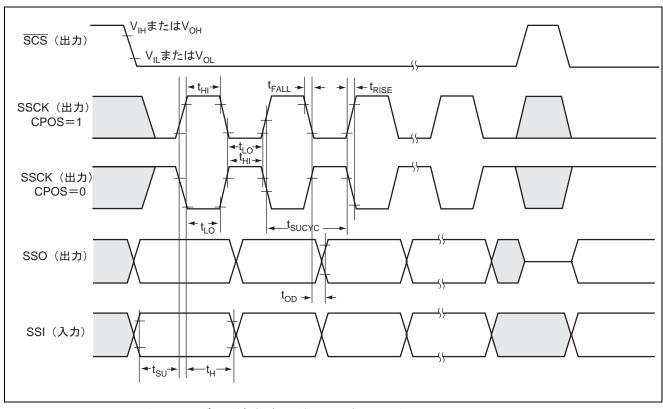

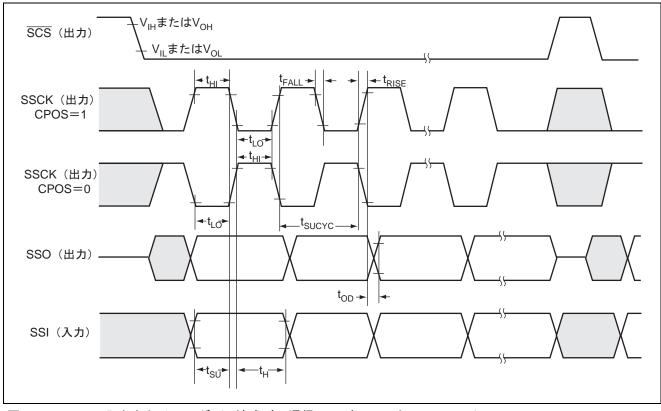

| 22.3    | 3.6                      | 4 線式バス通信モードの動作                                | 22-22 |

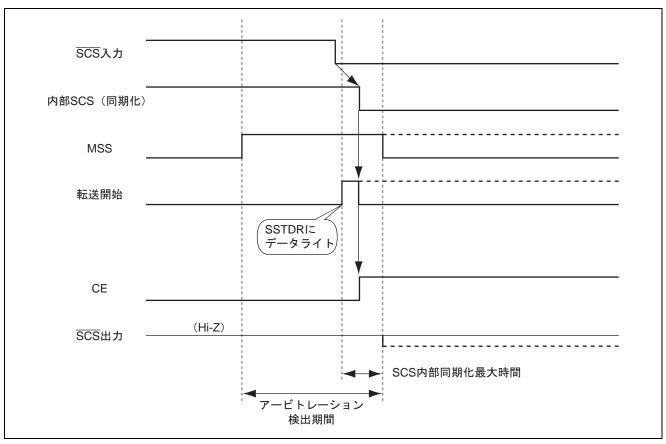

| 22.3    | 3.7                      | SCS 端子制御とアービトレーション                            | 22-27 |

| 22.4    | 割り                       | ) 込み要求                                        | 22-28 |

| 22.5    | 使月                       | 用上の注意事項                                       | 22-28 |

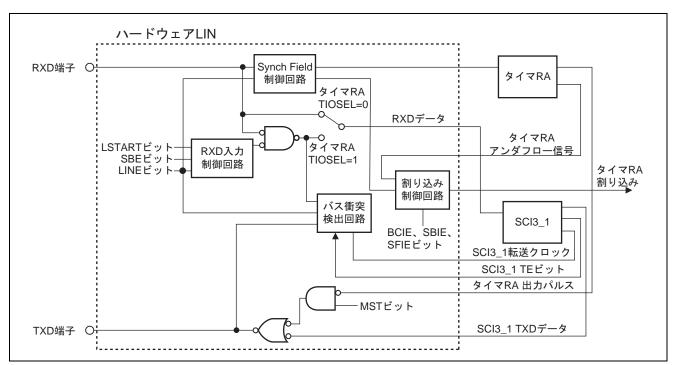

| 23. /\- | -ドウ                      | ェア LIN                                        | 23-1  |

| 23.1    | 概                        | <u> </u>                                      | 23-1  |

| 23.2 レ     | ジスタ構成                           | 23-2  |

|------------|---------------------------------|-------|

| 23.2.1     | LIN コントロールレジスタ(LINCR)           | 23-2  |

| 23.2.2     | LIN ステータスレジスタ(LINST)            | 23-3  |

| 23.3 動     | 作説明                             | 23-4  |

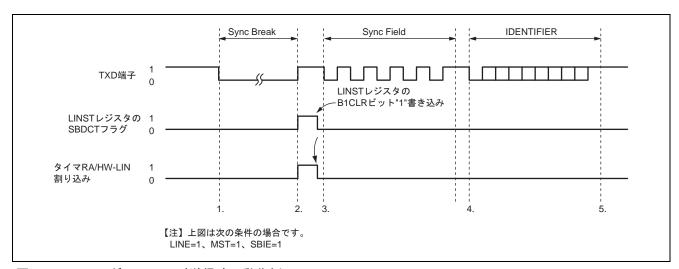

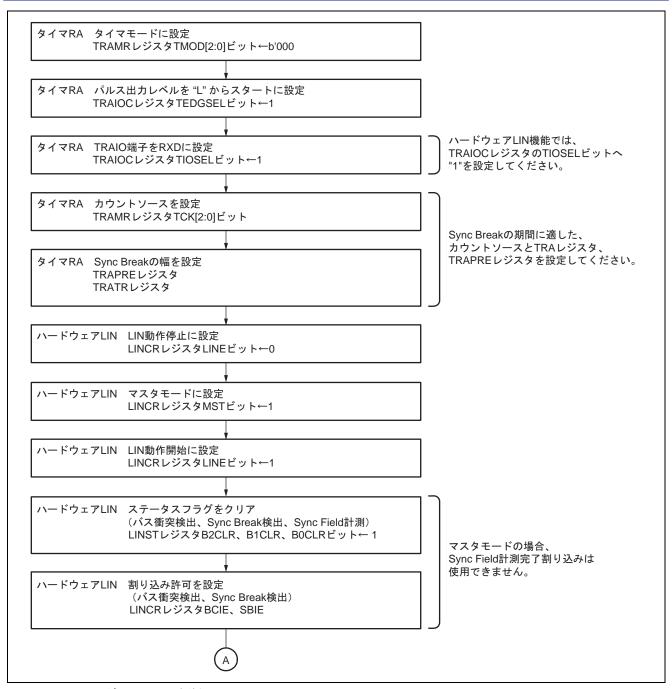

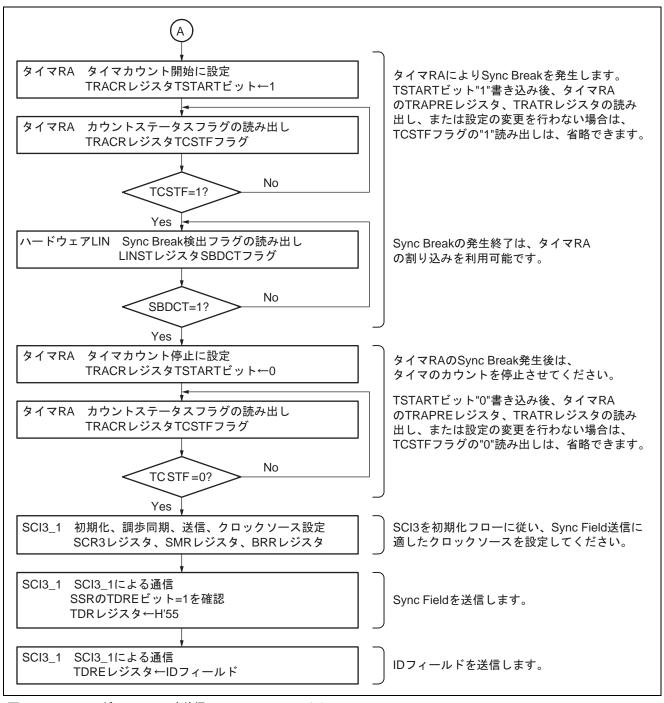

| 23.3.1     | マスタモード                          | 23-4  |

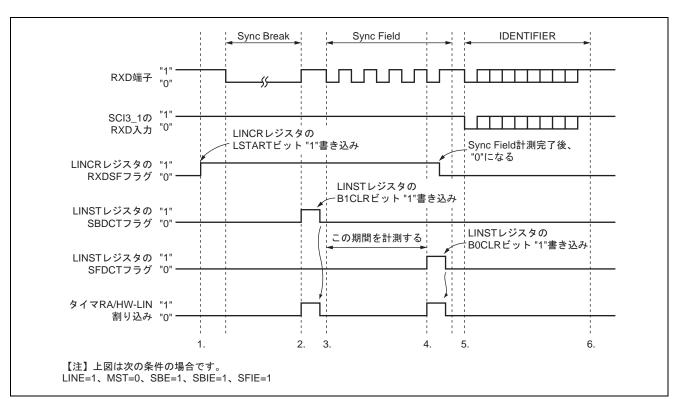

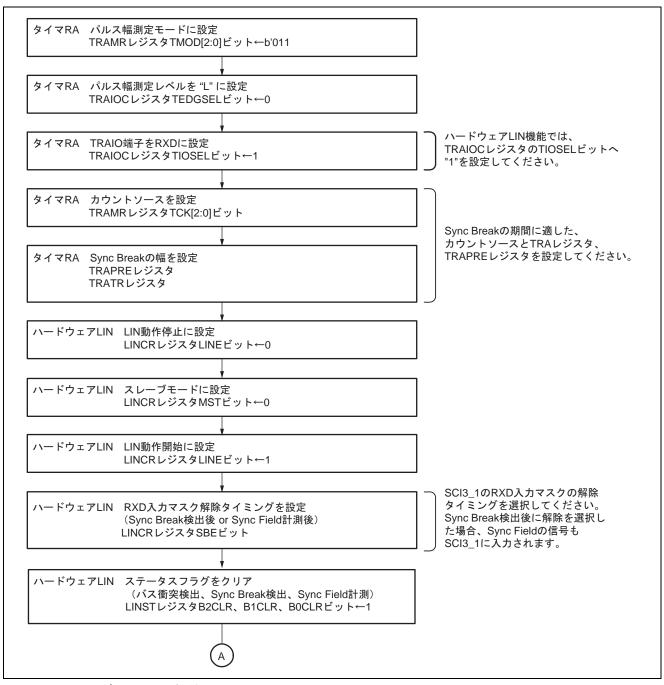

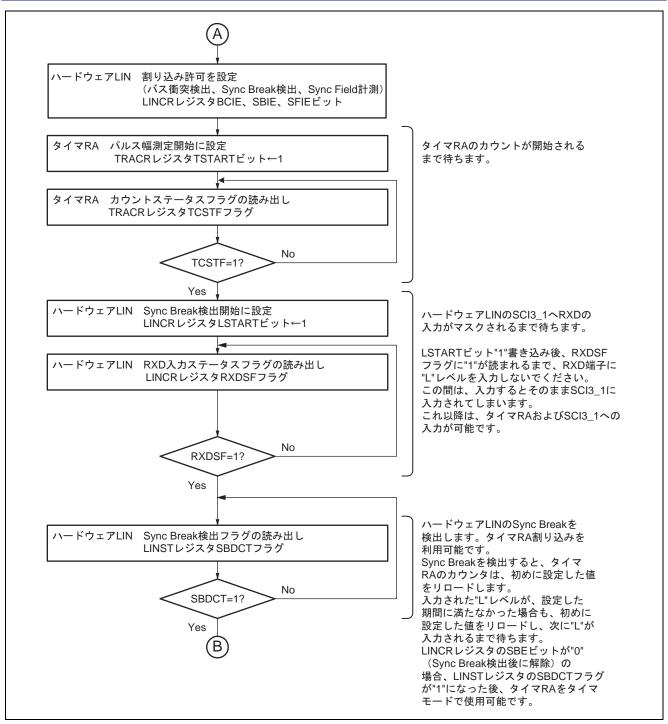

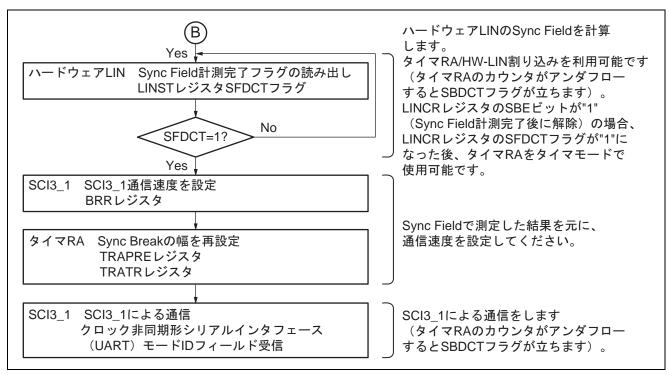

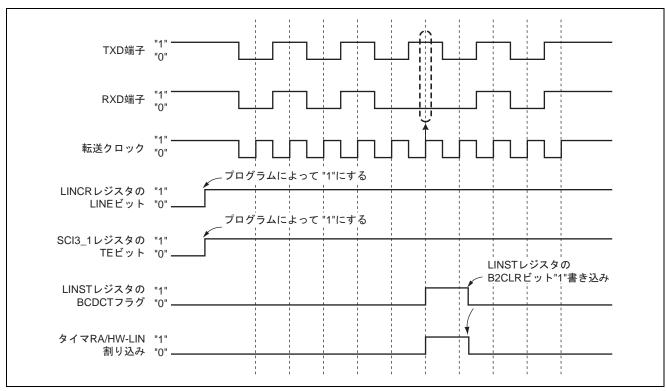

| 23.3.2     | スレーブモード                         | 23-7  |

| 23.3.3     | バス衝突検出機能                        | 23-11 |

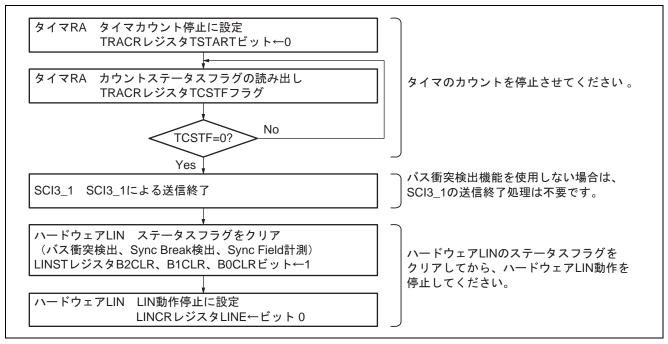

| 23.3.4     | ハードウェア LIN 終了処理                 | 23-12 |

| 23.4 割     | り込み要求                           | 23-13 |

| 23.5 使     | 用上の注意事項                         | 23-13 |

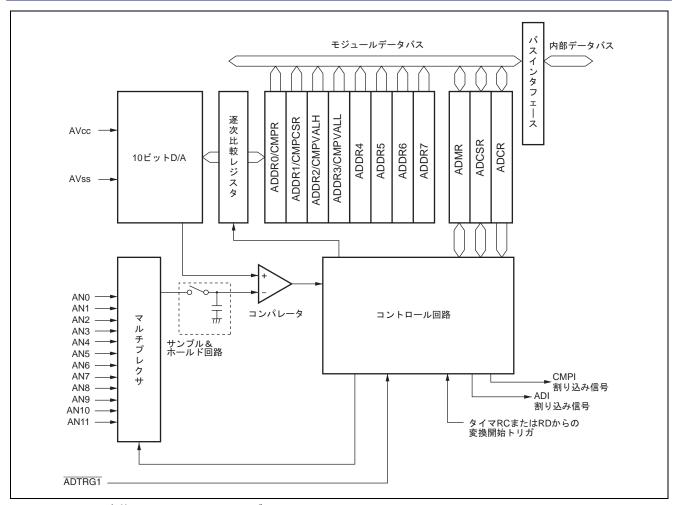

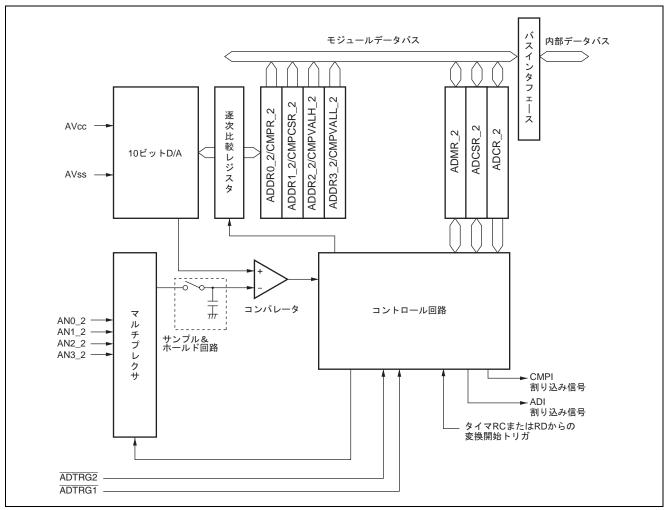

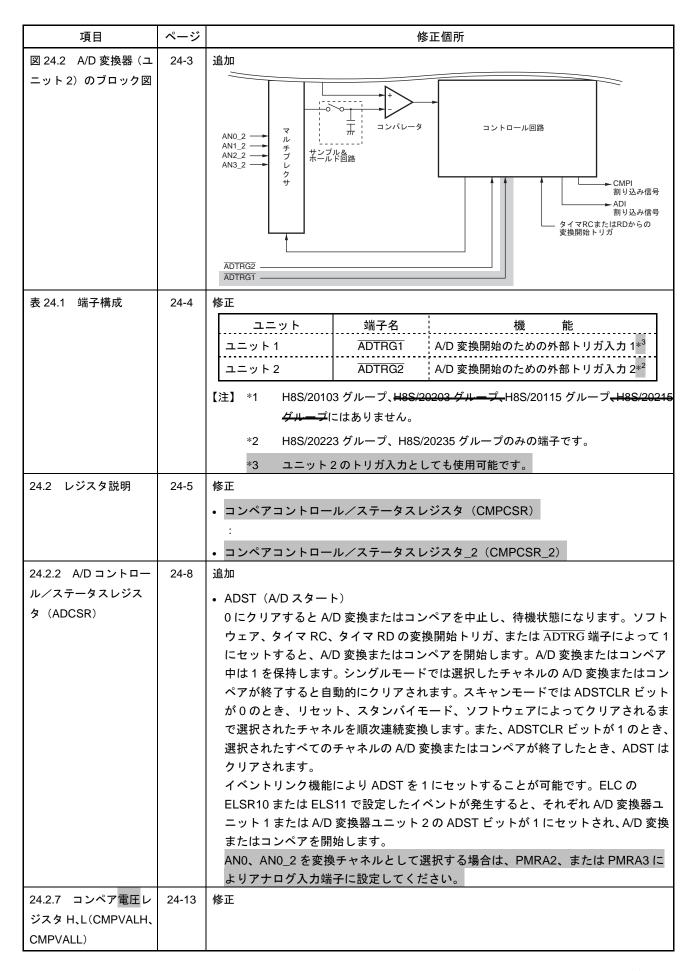

| 24. A/D 変換 | -器                              | 24-1  |

| 24.1 概     | 要                               | 24-1  |

| 24.2 レ     | ジスタの説明                          | 24-5  |

| 24.2.1     | A/D データレジスタ 0~7(ADDR0~ADDR7)    | 24-6  |

| 24.2.2     | A/D コントロール/ステータスレジスタ(ADCSR)     | 24-7  |

| 24.2.3     | A/D コントロールレジスタ(ADCR)            | 24-9  |

| 24.2.4     | A/D モードレジスタ (ADMR)              | 24-10 |

| 24.2.5     | コンペアデータレジスタ (CMPR)              | 24-11 |

| 24.2.6     | コンペアコントロール/ステータスレジスタ (CMPCSR)   | 24-12 |

| 24.2.7     | コンペア電圧レジスタ H、L(CMPVALH、CMPVALL) | 24-13 |

| 24.3 動     | 作説明                             | 24-14 |

| 24.4 A/    | D変換モード                          | 24-15 |

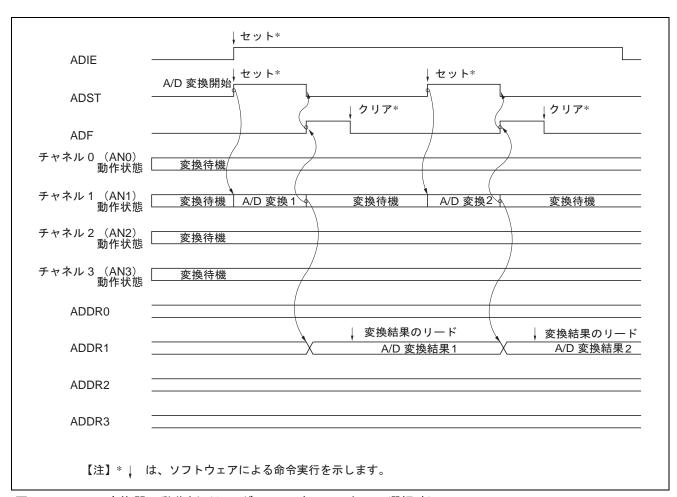

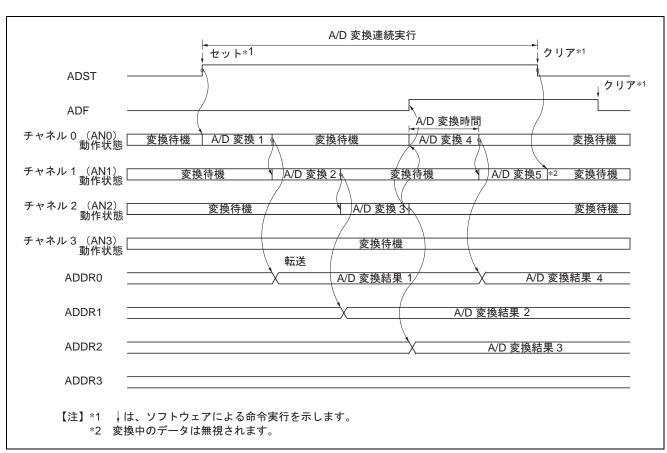

| 24.4.1     | A/D 変換シングルモード                   | 24-15 |

| 24.4.2     | A/D 変換スキャンモード                   | 24-16 |

| 24.5 =     | ンペアモード動作                        | 24-17 |

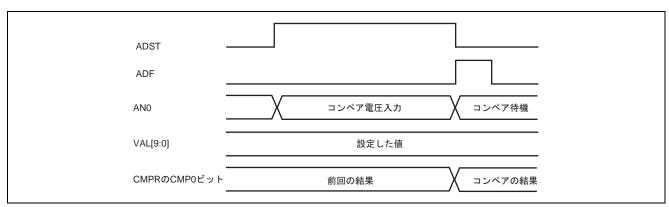

| 24.5.1     | コンペアシングルモード                     | 24-17 |

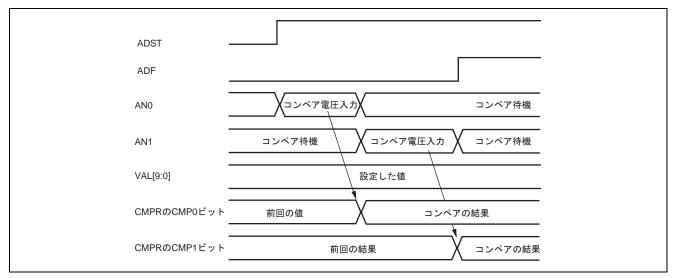

| 24.5.2     | コンペアスキャンモード                     | 24-18 |

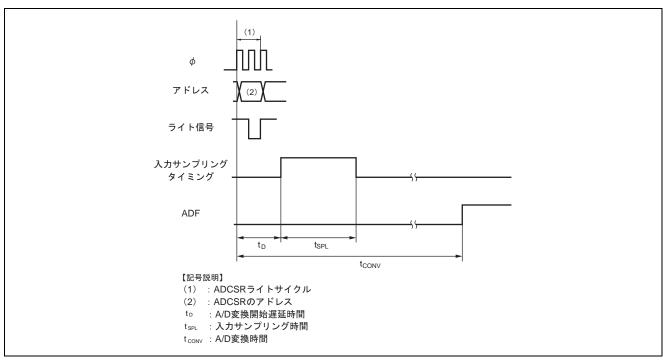

| 24.5.3     | 入力サンプリングと A/D 変換時間              | 24-19 |

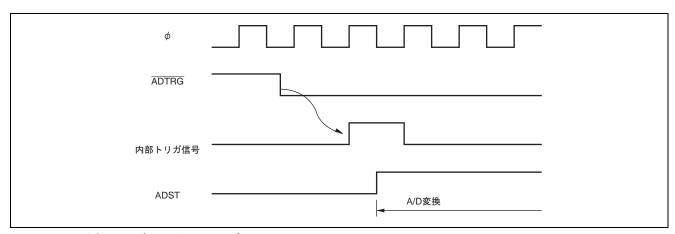

| 24.5.4     | 外部トリガ入力タイミング                    | 24-20 |

| 24.6 割     | り込み要因                           | 24-21 |

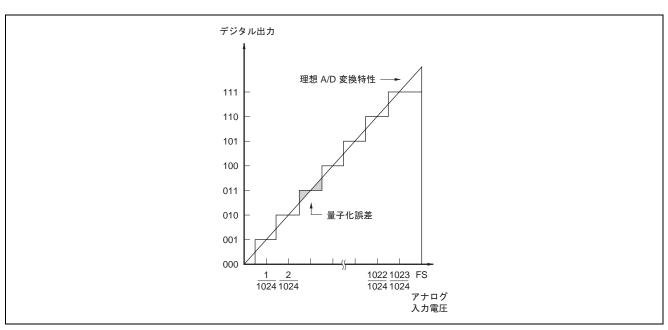

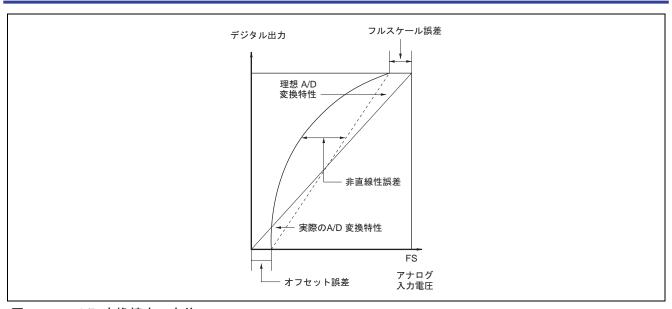

| 24.7 A/    | D変換精度の定義                        | 24-22 |

| 24.8 使     | 用上の注意事項                         | 24-24 |

| 24.8.1     | モジュールスタンバイ機能の設定                 | 24-24 |

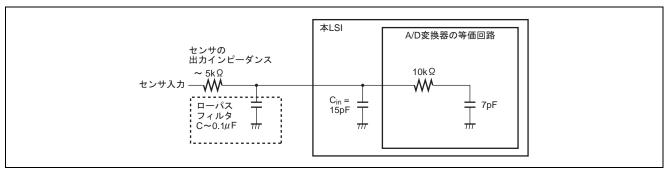

| 24.8.2     | 許容信号源インピーダンスについて                | 24-24 |

| 24.8.3     | 絶対精度への影響                        | 24-25 |

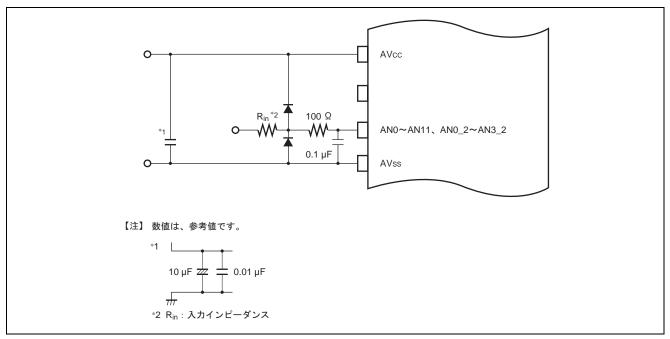

| 24.8.4     | アナログ電源端子他の設定範囲                  | 24-25 |

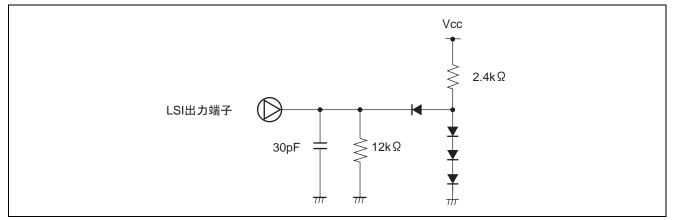

| 24.8.5     | ボード設計上の注意事項                     | 24-25 |

| 24     | .8.6                | ノイズ対策上の注意事項                    | 24-26 |

|--------|---------------------|--------------------------------|-------|

| 24     | 24.8.7 アナログ入力端子について |                                | 24-26 |

| 25. D/ | ′A 変換               | 器                              | 25-1  |

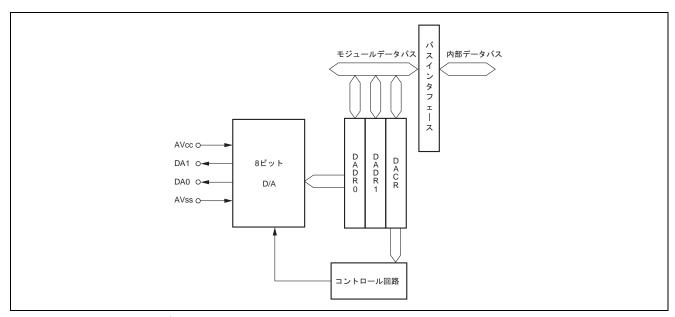

| 25.1   | 概到                  | 要                              | 25-1  |

| 25.2   | レシ                  | ブスタの説明                         | 25-2  |

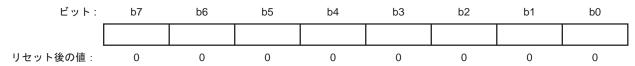

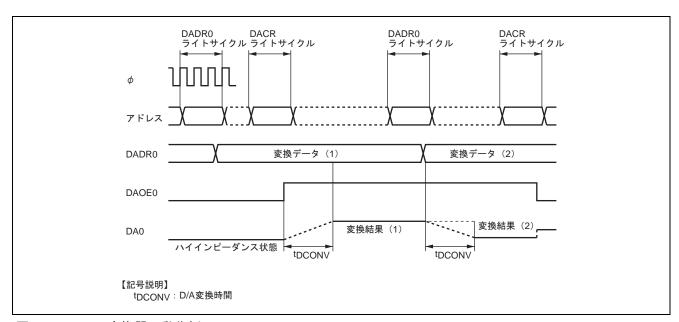

| 25     | .2.1                | D/A データレジスタ 0、1(DADR0、DADR1)   | 25-2  |

| 25     | .2.2                | D/A コントロールレジスタ(DACR)           | 25-3  |

| 25.3   | 動作                  | 乍説明                            | 25-4  |

| 25.4   | 使月                  | 用上の注意事項                        | 25-5  |

| 25     | .4.1                | モジュールスタンバイ機能の設定                | 25-5  |

| 25     | .4.2                | スタンバイモード時の動作                   | 25-5  |

| 26. 低  | 電圧検                 | 出回路                            | 26-1  |

| 26.1   | 特县                  | <u></u>                        | 26-1  |

| 26.2   | レシ                  | ブスタの説明                         | 26-4  |

| 26     | .2.1                | 低電圧検出回路コントロールプロテクトレジスタ (VDCPR) | 26-5  |

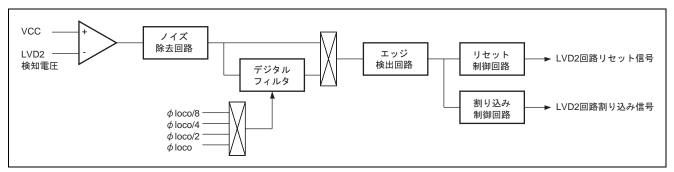

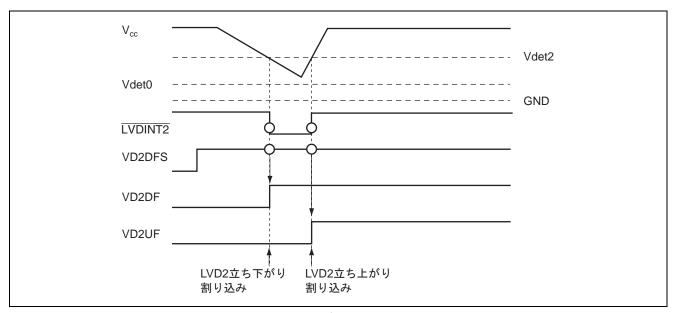

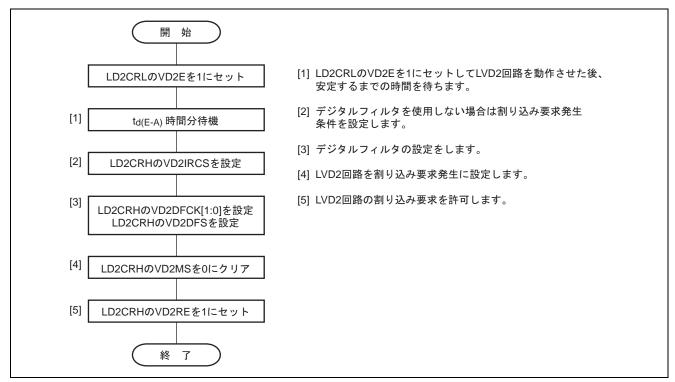

| 26     | .2.2                | 低電圧検出回路 2 コントロールレジスタ H(LD2CRH) | 26-6  |

| 26     | 5.2.3               | 低電圧検出回路 2 コントロールレジスタ L(LD2CRL) | 26-8  |

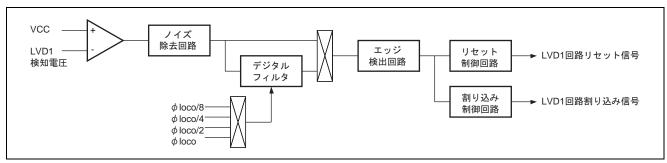

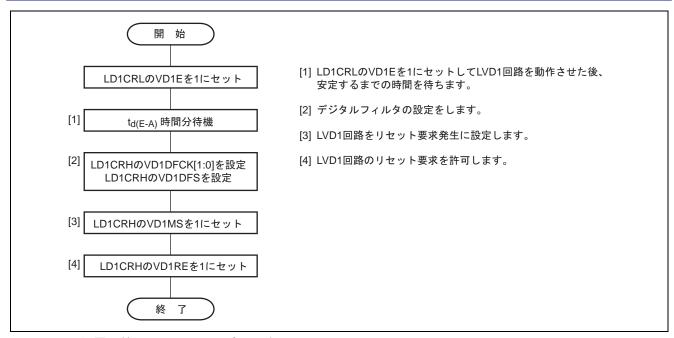

| 26     | .2.4                | 低電圧検出回路 1 コントロールレジスタ H(LD1CRH) | 26-9  |

| 26     | .2.5                | 低電圧検出回路 1 コントロールレジスタ L(LD1CRL) | 26-11 |

| 26     | .2.6                | 低電圧検出回路 0 コントロールレジスタ H(LD0CRH) | 26-12 |

| 26     | 5.2.7               | 低電圧検出回路 0 コントロールレジスタ L(LD0CRL) | 26-13 |

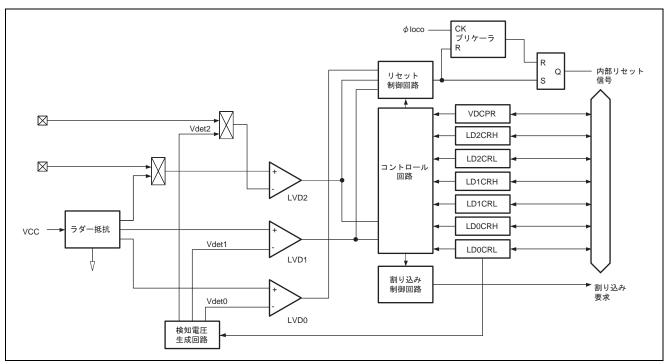

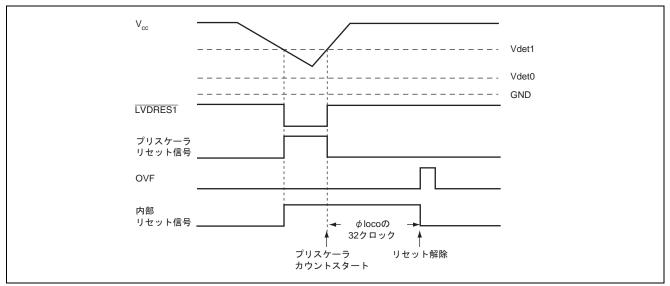

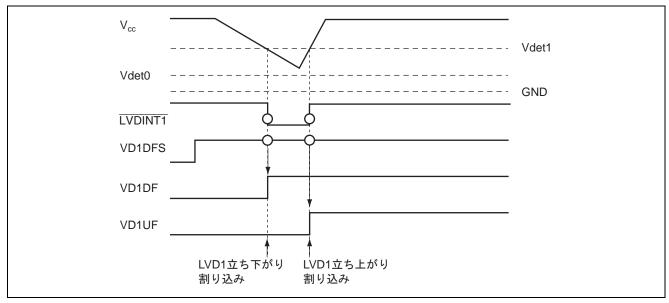

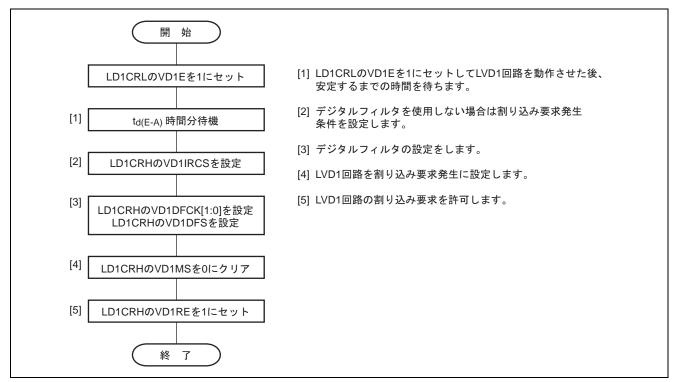

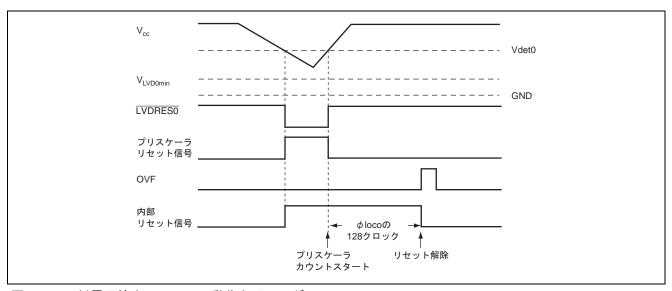

| 26.3   | 動作                  | 乍説明                            | 26-14 |

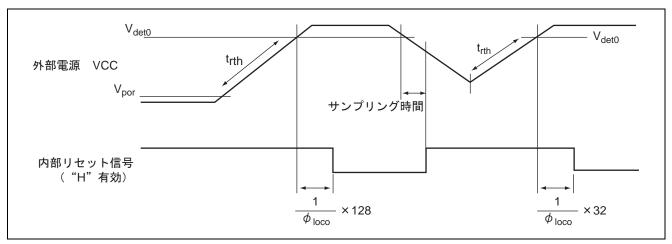

| 26     | 5.3.1               | パワーオンリセット機能                    | 26-14 |

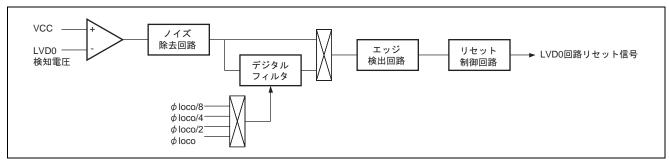

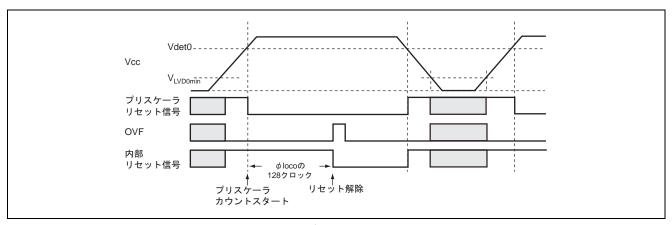

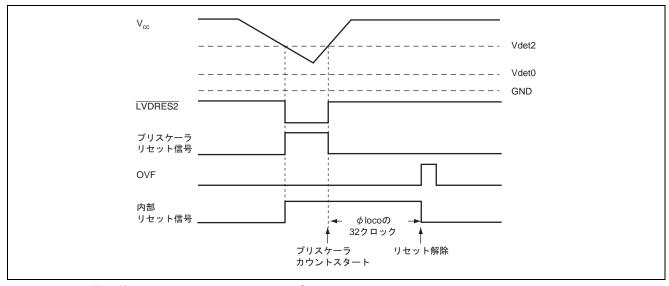

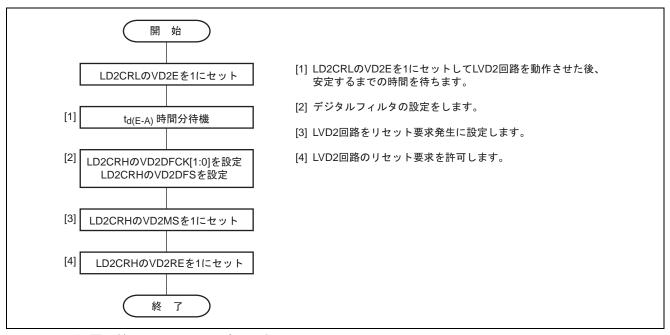

| 26     | 5.3.2               | 低電圧検出回路                        | 26-15 |

| 27. レ  | ジスタ                 | 一覧                             | 27-1  |

| 27.1   | レシ                  | ブスタアドレス一覧(アドレス順)               | 27-2  |

| 27.2   | レミ                  | ブスタビット一覧                       | 27-17 |

| 28. 電  | 気的特                 | 性                              | 28-1  |

| 28.1   | 絶対                  | 付最大定格                          | 28-1  |

| 28.2   | 電気                  | 贰的特性                           | 28-2  |

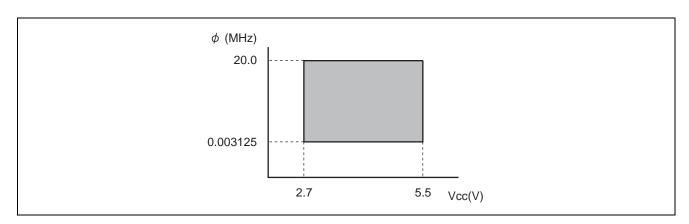

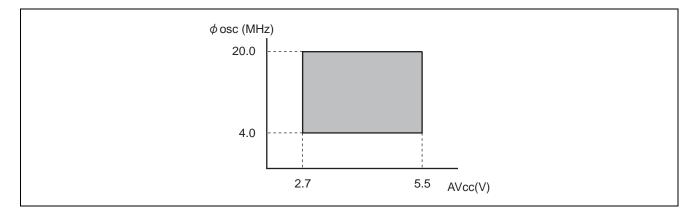

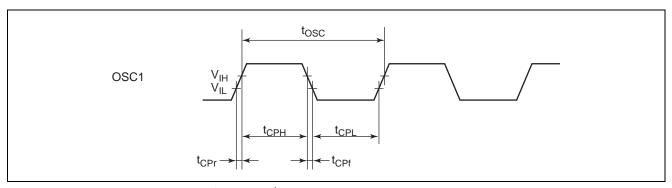

| 28     | .2.1                | 電源電圧と動作範囲                      | 28-2  |

| 28.3   | DC                  | 特性                             | 28-4  |

| 28.4   | AC                  | 特性                             | 28-12 |

| 28.5   | A/L                 | )変換特性                          | 28-17 |

| 28.6   | D/A                 | A変換特性                          | 28-18 |

|        |                     |                                |       |

| 28.7  | フラッシュメモリ特性    |       |

|-------|---------------|-------|

| 28.8  | 低電圧検出回路特性     | 28-20 |

| 28.9  | パワーオンリセット機能特性 | 28-23 |

| 28.10 | タイミング図        | 28-24 |

| 28.11 | 出力負荷条件        | 28-31 |

| 付録    |               | 付録-1  |

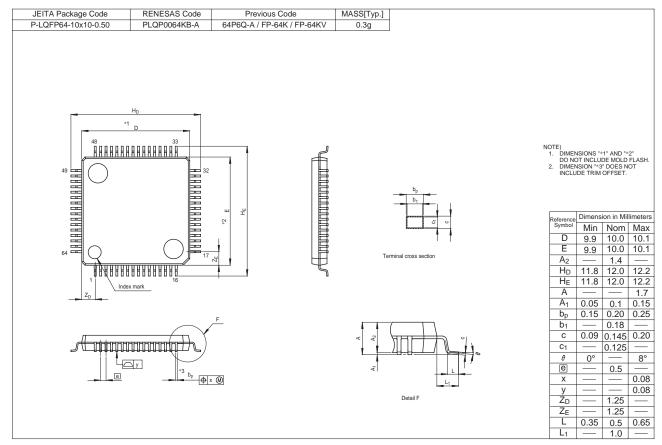

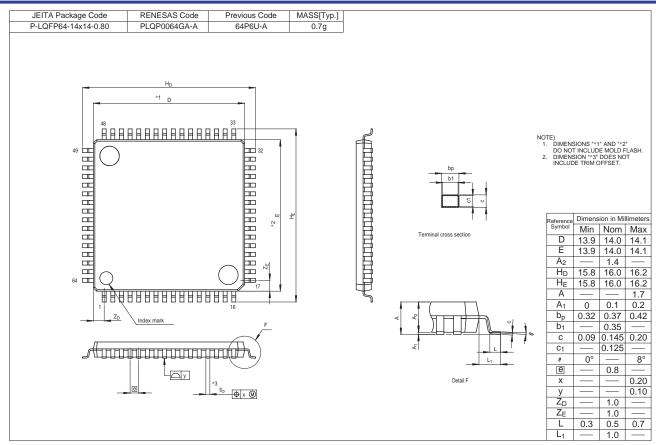

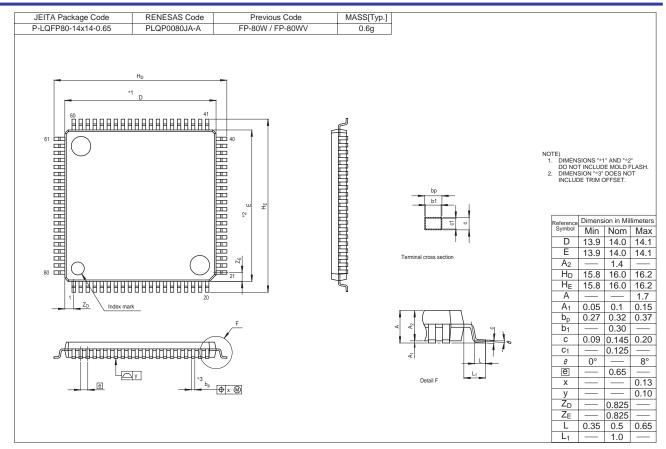

| A.    | 外形寸法図         | 付録-1  |

| B.    | 未使用端子の処理について  | 付録-4  |

| 本版で修  | 多正または追加された箇所  | 改訂-1  |

| 索引    |               | 索引-1  |

|       |               |       |

H8S/20103、H8S/20203、H8S/20223、H8S/20115、H8S/20215、H8S/20235 グループルネサスマイクロコンピュータ

RJJ09B0491-0300 Rev.3.00 2010.09.09

## 1. 概要

#### 1.1 特長

H8S/Tiny シリーズは、ルネサスオリジナルマイコン H8/300、H8/300H の各 CPU に対し上位互換アーキテクチャを持ち、内部 16 ビット構成の H8S/2000 CPU をコアとする CISC(Complex Instruction Set Computer)マイコンです。

周辺機能として、データトランスファコントローラ、イベントリンクコントローラ、シリアルコミュニケーションインタフェース 3、 $I^2C$  バスインタフェース 2、シンクロナスシリアルコミュニケーションユニット、ハードウェア LIN 通信インタフェース、A/D 変換器、D/A 変換器、低電圧検出回路および豊富な各種タイマを内蔵しており、低コストでのシステム構築を可能にします。これらは低消費電力モードにより、ダイナミックな消費電力制御が可能になっています。

## 1.1.1 用途

応用分野例:家電、OA機器、民生機器、産業機器など

## 1.1.2 仕様概要

表 1.1 に、本マイコンの仕様概要を示します。

## 表 1.1 仕様概要

| 分類       | モジュール/機能     | 説明                                           |

|----------|--------------|----------------------------------------------|

| メモリ      | ROM          | • ROM 展開:フラッシュメモリ版                           |

|          |              | プログラムメモリ:256K バイト、192K バイト、128K バイト、         |

|          |              | 96K バイト                                      |

|          |              | プログラム、イレーズ回数:1000 回                          |

|          |              | データフラッシュ:4K バイト×2 ブロック                       |

|          |              | プログラム、イレーズ回数:10000 回                         |

|          | RAM          | • 容量: 12K バイト、8K バイト                         |

| CPU      | CPU          | • 16 ビット高速 H8S/2000 CPU(CISC タイプ)            |

|          |              | H8/300 CPU、H8/300H CPU に対してオブジェクトレベルで上位互換    |

|          |              | • 汎用レジスタ方式 (汎用レジスタ: 16 ビット×16 本)             |

|          |              | • アドレッシングモード:8種類                             |

|          |              | <ul><li>● アドレス空間: 16M バイト</li></ul>          |

|          |              | (プログラム:16M バイト、データ:16M バイト)                  |

|          |              | • 基本命令数                                      |

|          |              | 65 種類(ビット演算、乗除算、ビット操作など)                     |

|          |              | • 最小命令実行時間                                   |

|          |              | 50ns@システムクロックφ=20 MHz、                       |

|          |              | Vcc=2.7~5.5V(ADD 命令)動作時                      |

|          | 動作モード        | アドバンスド・シングルチップモード                            |

| 割り込み(要因) | 割り込みコントローラ   | <ul><li>外部割り込み端子:9本(NMI、IRQ0~IRQ7)</li></ul> |

|          |              | ● 内部割り込み要因数:                                 |

|          |              | 55 本(H8S/20103 グループ、H8S/20115 グループ)          |

|          |              | 61 本(H8S/20203 グループ、H8S/20215 グループ)          |

|          |              | 63 本(H8S/20223 グループ、H8S/20235 グループ)          |

|          |              | • 2種類の割り込み制御モード                              |

|          |              | (割り込みコントロールレジスタで指定)                          |

|          |              | • 4 レベルの割り込み優先順位を設定可能                        |

|          |              | (インタラプトプライオリティレジスタで指定)                       |

|          |              | • 独立したベクタアドレス                                |

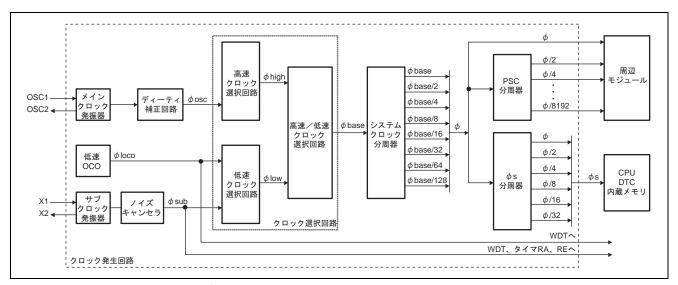

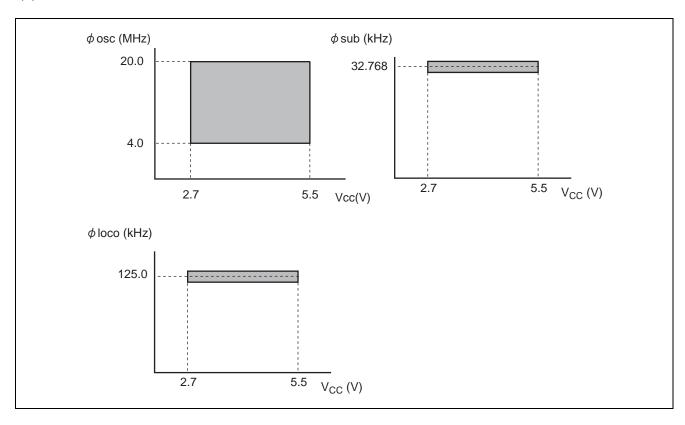

| クロック     | クロック発振器(CPG) | <ul><li>クロック発生回路:2回路</li></ul>               |

|          |              | メイン発振器、サブ発振器                                 |

|          |              | • オンチップオシレータ:1種類                             |

|          |              | 低速 125kHz                                    |

|          |              | • 低消費電力状態:3種類                                |

|          |              | スリープモード、ソフトウェアスタンバイモード、モジュール                 |

|          |              | スタンバイモード                                     |

| 電圧検出     | 低電圧検出回路(LVD) | 電圧低下検出                                       |

| 分類        | モジュール/機能                     | 説明                                                                           |

|-----------|------------------------------|------------------------------------------------------------------------------|

| DMA       | データトランスファ                    | 任意のチャネル数転送可能                                                                 |

|           | コントローラ (DTC)                 | 転送モード:3種類                                                                    |

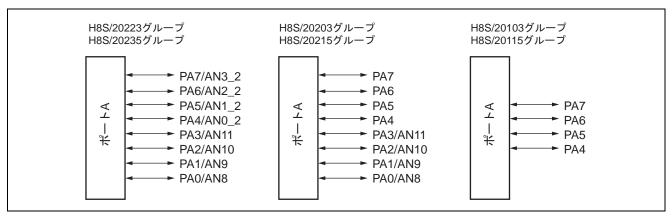

| A/D コンバータ | A/D 変換器(ADC)                 | 分解能(10 ビット)×入力チャネル数(8 チャネル~16 チャネル)                                          |

|           |                              | サンプル&ホールド機能付き                                                                |

|           |                              | 変換時間:1 チャネル当たり 2μs                                                           |

|           |                              | 動作モード:2種類(シングルモード、スキャンモード)                                                   |

|           |                              | A/D 変換開始方法:3 種類                                                              |

|           |                              | (ソフトウェア、タイマのトリガ、外部端子トリガ)                                                     |

| D/A コンバータ | D/A 変換器(DAC)                 | 分解能(8 ビット)×入力チャネル数(2 チャネル)                                                   |

| タイマ       | タイマ RA                       | 8 ビット×1 チャネル(8 ビットプリスケーラ付)                                                   |

|           | タイマ RB                       | 8 ビット×1 チャネル(8 ビットプリスケーラ付)                                                   |

|           | タイマ RC                       | 16 ビット×1 チャネル                                                                |

|           |                              | (H8S/20103 グループ、H8S/20115 グループのみ)                                            |

|           | タイマ RD                       | 16 ビット×2 チャネル                                                                |

|           |                              | (H8S/20203 グループ、H8S/20223 グループ、H8S/20215 グループ、                               |

|           |                              | H8S/20235 グループは 2 ユニット)                                                      |

|           | タイマ RE                       | 8 ビット×1 チャネル                                                                 |

|           |                              | リアルタイムクロック機能                                                                 |

|           | タイマ RG                       | 16 ビット×1 チャネル                                                                |

|           |                              | 位相計数モード付き                                                                    |

|           | ウオッチドッグタイマ<br>(WDT)          | 8 ビット×1 チャネル                                                                 |

| シリアルインタ   | シリアルコミュニケーション                | チャネル数:3チャネル(非同期/クロック同期式兼用)                                                   |

| フェース      | インタフェース 3(SCI3)              | 全二重通信が可能                                                                     |

|           |                              | 任意のビットレートを選択可能                                                               |

|           |                              | IrDA(チャネル 2 のみ IrDA 機能付き)                                                    |

|           | シンクロナスシリアル                   | チャネル数:1 チャネル(IIC2 と選択式)                                                      |

|           | コミュニケーション                    | チップセレクト付クロック同期通信                                                             |

|           | インタフェース (SSU)                |                                                                              |

|           | I <sup>2</sup> C バスインタフェース 2 | チャネル数 : 1 チャネル(SSU と選択式)<br>                                                 |

|           | (IIC2)                       | 連続送信/受信が可能                                                                   |

|           |                              | 送受信フォーマット:2 種類                                                               |

|           |                              | I <sup>2</sup> C バスフォーマット:マスタモードで開始条件、停止条件の自動生成。<br>  アクノリッジビットあり、マスタ、スレーブ動作 |

|           |                              | アクノリッンヒットのり、マスタ、スレーノ剿作<br> <br> <br>  クロック同期シリアルフォーマット: アクノリッジビットなし、マスタ      |

|           |                              | クロック向朔シリアルフォーマット: アクノリッショットなし、マスタ<br>  動作専用                                  |

|           | ハードウェア LIN                   | コチャネル(タイマ RA、SCI3 を使用)                                                       |

|           | インタフェース                      |                                                                              |

| 分類                 | モジュール/機能 | 説明                                        |  |  |

|--------------------|----------|-------------------------------------------|--|--|

| イベントリンクコントローラ(ELC) |          | 各周辺モジュールが出力するイベント(割り込み)をモジュール間で相          |  |  |

|                    |          | 互に接続(リンク)、CPU を介さずにモジュール間で連携動作可能          |  |  |

| 1/0 ポート            |          | • 入出力:55本 (H8S/20103 グループ、H8S/20115 グループ) |  |  |

|                    |          | 69 本(H8S/20203 グループ、H8S/20223 グループ、       |  |  |

|                    |          | H8S/20215 グループ、H8S/20235 グループ)            |  |  |

|                    |          | • プルアップ抵抗:全ポートで設定可能                       |  |  |

|                    |          | • LED 駆動可能                                |  |  |

| パッケージ              |          | • 64 ピン QFP パッケージ (PLQP0064KB-A)          |  |  |

|                    |          | (旧コード:64P6Q-A、ボディサイズ:10×10mm、             |  |  |

|                    |          | ピンピッチ: 0.50mm)                            |  |  |

|                    |          | • 64 ピン QFP パッケージ(PLQP0064GA-A)           |  |  |

|                    |          | (旧コード:64P6U-A、ボディサイズ:14×14mm、             |  |  |

|                    |          | ピンピッチ: 0.80mm)                            |  |  |

|                    |          | • 80 ピン QFP パッケージ(PLQP0080JA-A)           |  |  |

|                    |          | (旧コード:FP-80W、ボディサイズ:14×14mm、              |  |  |

|                    |          | ピンピッチ: 0.65mm)                            |  |  |

|                    |          | • 80 ピン QFP パッケージ(PLQP0080KB-A)(計画中)      |  |  |

|                    |          | (旧コード:80P6Q-A、ボディサイズ:12×12mm、             |  |  |

|                    |          | ピンピッチ: 0.5mm)                             |  |  |

| 動作周波数/電源電圧         |          | 動作周波数:4~20MHz                             |  |  |

|                    |          | 電源電圧:Vcc=2.7~5.5V、AVcc=2.7~5.5V           |  |  |

| 動作周囲温度(℃)          |          | -20°C~+85°C (Nバージョン)                      |  |  |

|                    |          | -40°C~+85°C (Dバージョン)                      |  |  |

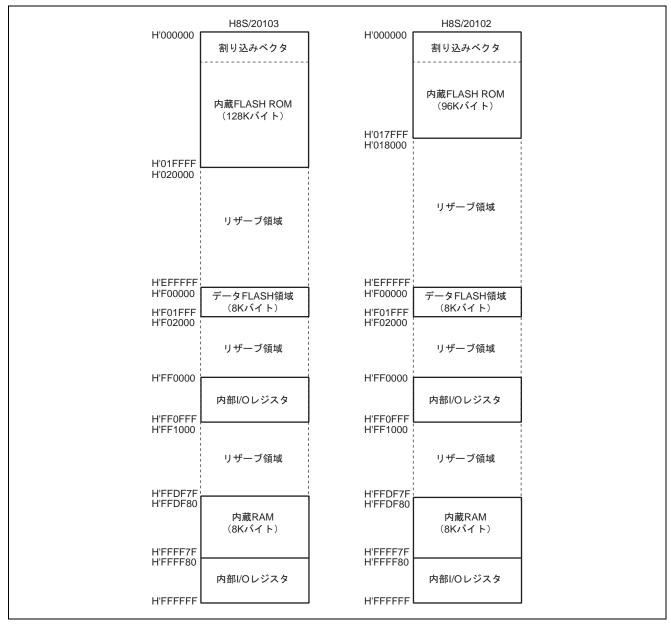

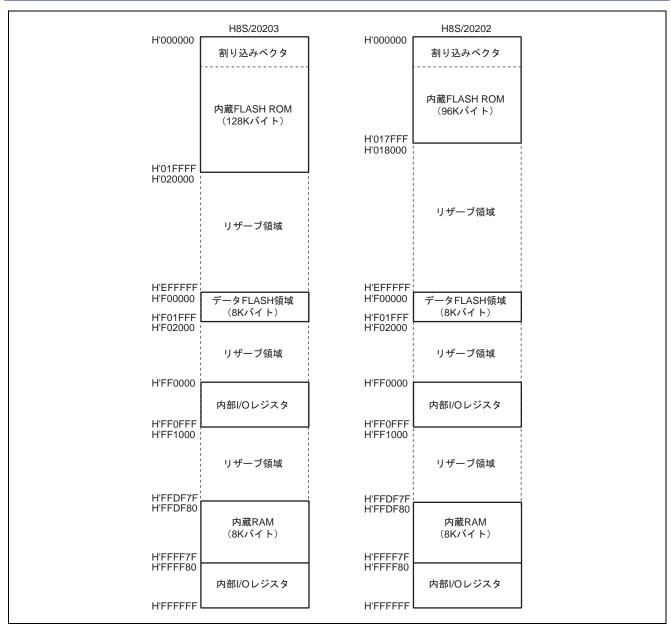

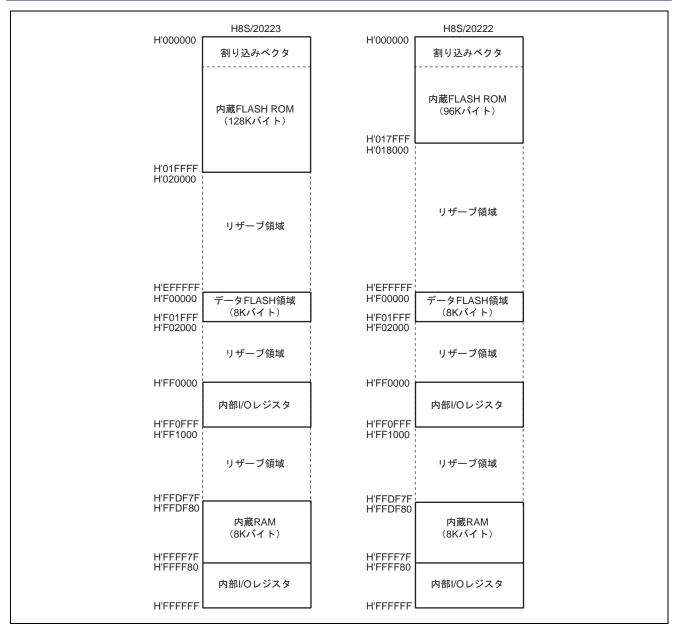

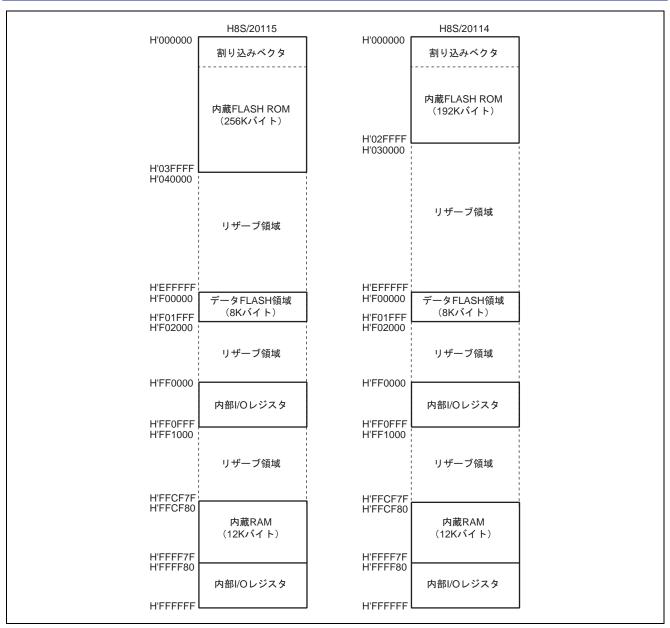

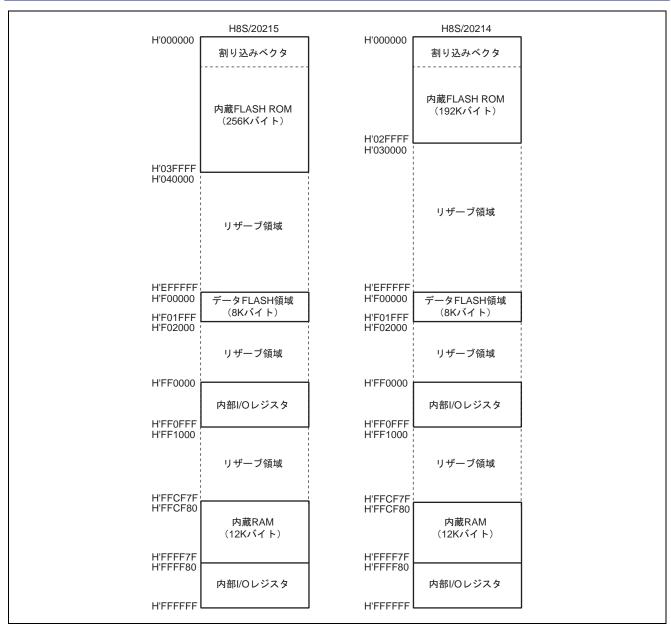

## 1.2 製品一覧

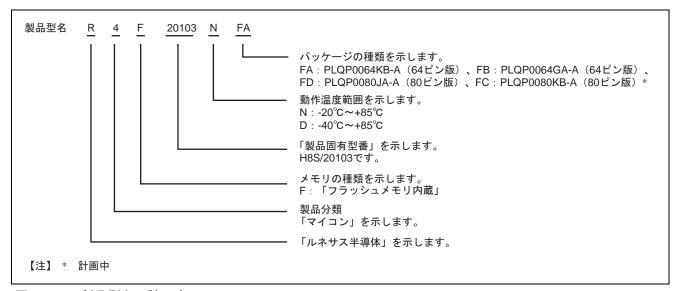

表 1.2 に製品一覧表、図 1.1 に製品型名の読み方を示します。

表 1.2 製品一覧

| グループ      | 製品型名        | ROM 容量   | RAM 容量  | パッケージ                         | 備考             |

|-----------|-------------|----------|---------|-------------------------------|----------------|

| H8S/20103 | R4F20103NFA | 128K バイト | 8K バイト  | PLQP0064KB-A<br>(LQFP1010-64) | N バージョン        |

|           | R4F20102NFA | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20103NFB | 128K バイト | 8K バイト  | PLQP0064GA-A<br>(LQFP1414-64) |                |

|           | R4F20102NFB | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20103DFA | 128K バイト | 8K バイト  | PLQP0064KB-A<br>(LQFP1010-64) | D バージョン<br>—   |

|           | R4F20102DFA | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20103DFB | 128K バイト | 8K バイト  | PLQP0064GA-A<br>(LQFP1414-64) |                |

|           | R4F20102DFB | 96K バイト  | 8K バイト  |                               |                |

| H8S/20203 | R4F20203NFD | 128K バイト | 8K バイト  | PLQP0080JA-A<br>(LQFP1414-80) | Nバージョン         |

|           | R4F20202NFD | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20203DFD | 128K バイト | 8K バイト  |                               | Dバージョン         |

|           | R4F20202DFD | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20203NFC | 128K バイト | 8K バイト  | PLQP0080KB-A<br>(LQFP1212-80) | N バージョン<br>計画中 |

|           | R4F20202NFC | 96K バイト  | 8K バイト  |                               |                |

| H8S/20223 | R4F20223NFD | 128K バイト | 8K バイト  | PLQP0080JA-A<br>(LQFP1414-80) | Nバージョン         |

|           | R4F20222NFD | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20223DFD | 128K バイト | 8K バイト  |                               | Dバージョン         |

|           | R4F20222DFD | 96K バイト  | 8K バイト  |                               |                |

|           | R4F20223NFC | 128K バイト | 8K バイト  | PLQP0080KB-A<br>(LQFP1212-80) | N バージョン<br>計画中 |

|           | R4F20222NFC | 96K バイト  | 8K バイト  |                               |                |

| H8S/20115 | R4F20115NFA | 256K バイト | 12K バイト | PLQP0064KB-A<br>(LQFP1010-64) | N バージョン        |

|           | R4F20114NFA | 192K バイト | 12K バイト |                               |                |

|           | R4F20115NFB | 256K バイト | 12K バイト | PLQP0064GA-A                  |                |

|           | R4F20114NFB | 192K バイト | 12K バイト | (LQFP1414-64)                 |                |

| H8S/20215 | R4F20215NFD | 256K バイト | 12K バイト | PLQP0080JA-A                  |                |

|           | R4F20214NFD | 192K バイト | 12K バイト | (LQFP1414-80)                 |                |

| H8S/20235 | R4F20235NFD | 256K バイト | 12K バイト |                               |                |

|           | R4F20234NFD | 192K バイト | 12K バイト |                               |                |

図 1.1 製品型名の読み方

## 1.3 ブロック図

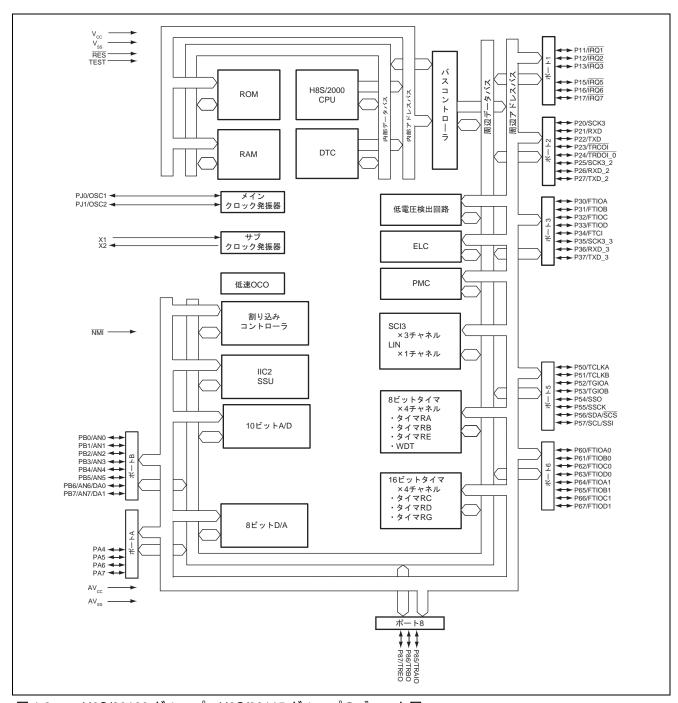

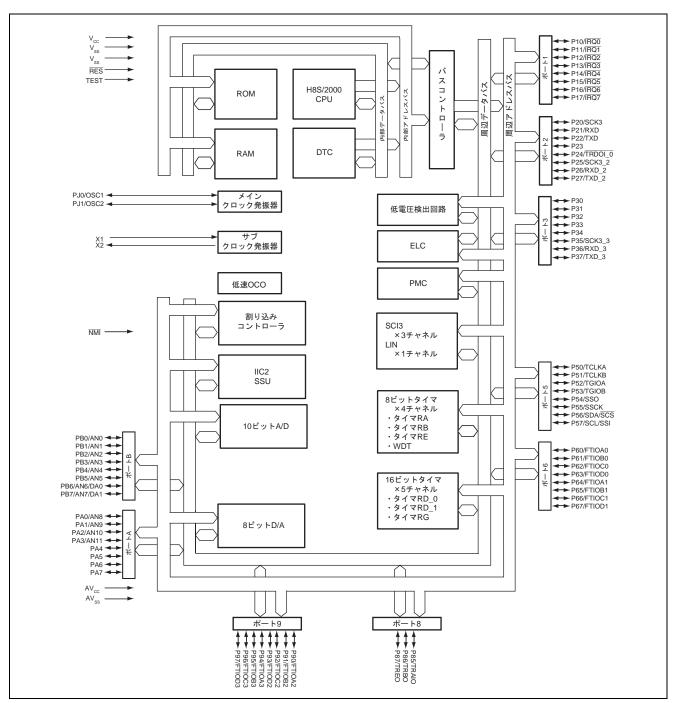

図 1.2 H8S/20103 グループ、H8S/20115 グループのブロック図

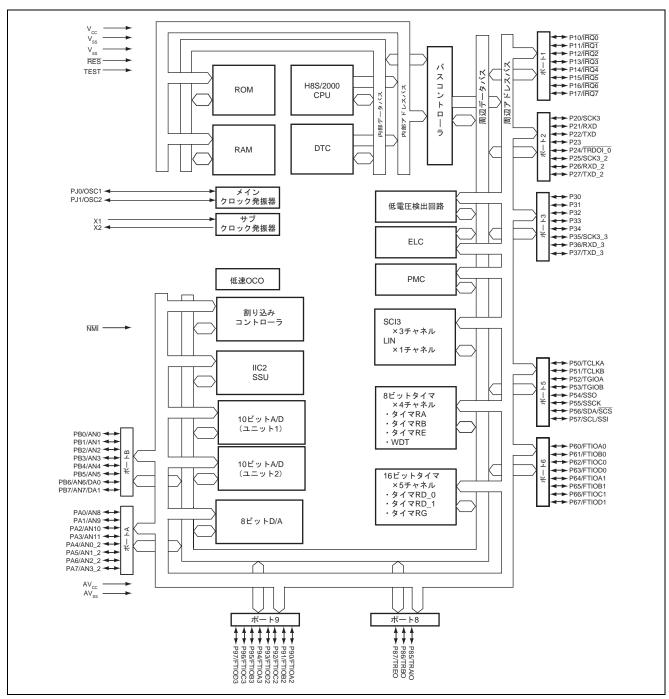

図 1.3 H8S/20203 グループ、H8S/20215 グループのブロック図

図 1.4 H8S/20223 グループ、H8S/20235 グループのブロック図

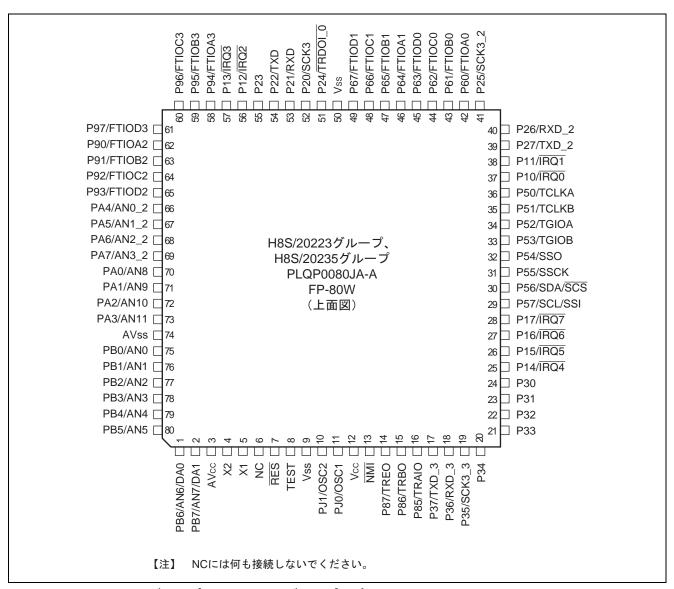

## 1.4 ピン配置図

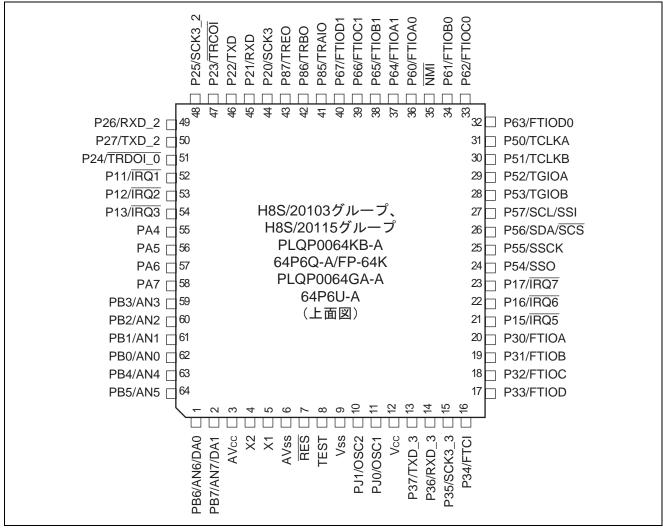

図 1.5 H8S/20103 グループ、H8S/20115 グループのピン配置図

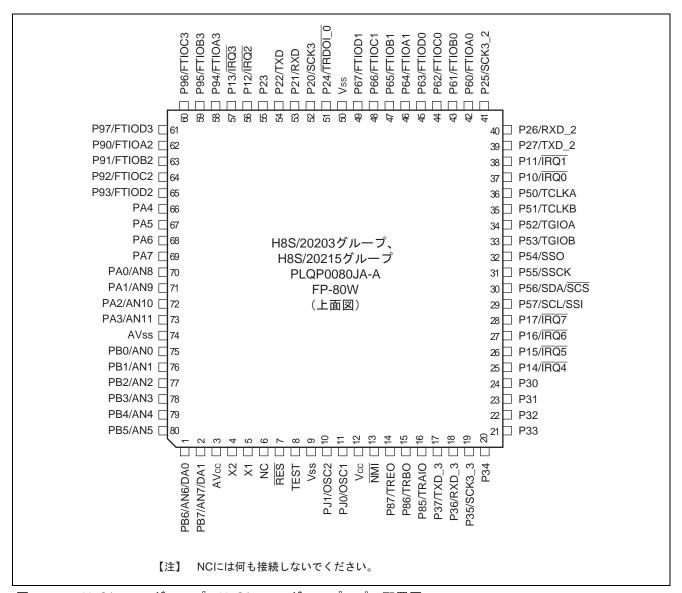

図 1.6 H8S/20203 グループ、H8S/20215 グループのピン配置図

図 1.7 H8S/20223 グループ、H8S/20235 グループのピン配置図

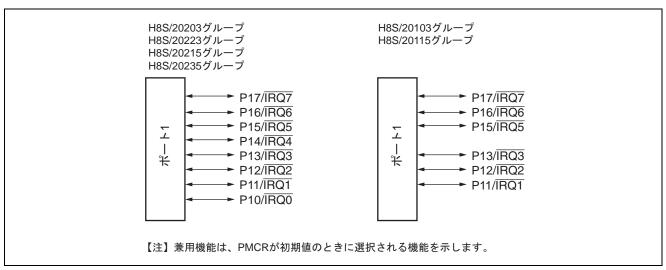

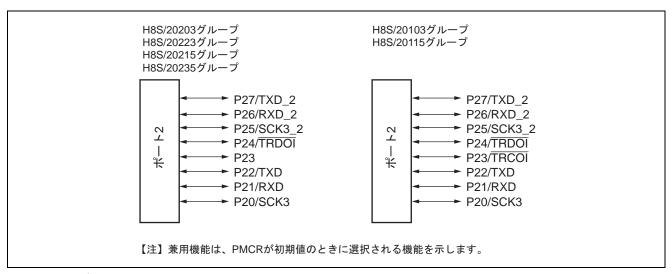

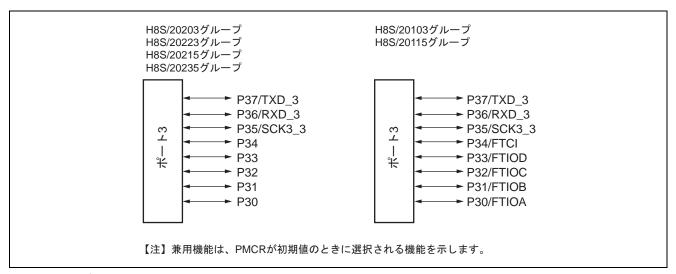

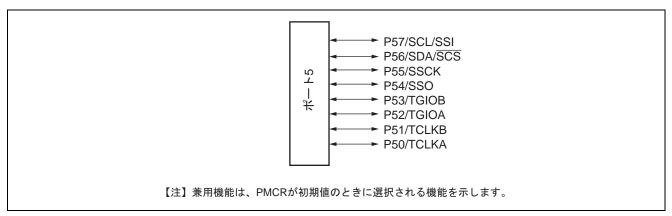

# 1.4.1 端子機能

## 表 1.3 端子機能

| 分類         | 記号              | ピン                               | 番号                                                                   | 入出力 | 機能                                                                                                       |

|------------|-----------------|----------------------------------|----------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------|

|            |                 | H8S/20103 グループ<br>H8S/20115 グループ | H8S/20203 グループ<br>H8S/20223 グループ<br>H8S/20215 グループ<br>H8S/20235 グループ |     |                                                                                                          |

| 電源         | V <sub>cc</sub> | 12                               | 12                                                                   | 入力  | 電源端子です。全端子必ずシステムの電源に接続してください。                                                                            |

|            | $V_{SS}$        | 9                                | 9, 50                                                                | 入力  | グランド端子です。全端子必ずシステム<br>の電源(OV)に接続してください。                                                                  |

|            | AVcc            | 3                                | 3                                                                    | 入力  | A/D 変換、D/A 変換用アナログ電源端子です。A/D 変換器、D/A 変換器を使用しない場合はシステムの電源に接続してください。                                       |

|            | AVss            | 6                                | 74                                                                   | 入力  | A/D 変換、D/A 変換用アナロググランド<br>端子です。システムの電源(0V)に接<br>続してください。                                                 |

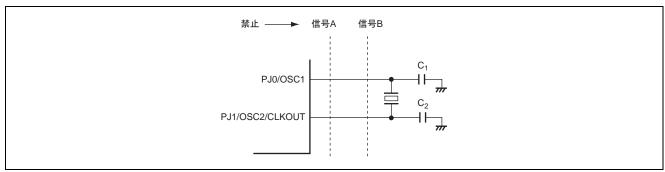

| クロック       | OSC1            | 11                               | 11                                                                   | 入力  | システムクロック用水晶発振子または                                                                                        |

|            | OSC2/<br>CLKOUT | 10                               | 10                                                                   | 出力  | セラミック発振子接続端子です。外部クロックを入力することもできます。オンチップオシレータを使用する場合は、OSC2端子からシステムクロックを出力できます。接続例は「第5章 クロック発振器」を参照してください。 |

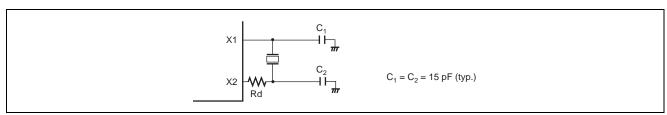

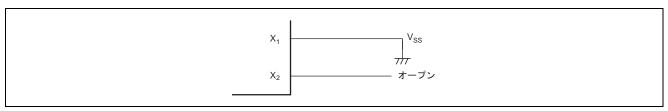

|            | X1              | 5                                | 5                                                                    | 入力  | サブクロック用 32.768kHz 水晶発振子                                                                                  |

|            | X2              | 4                                | 4                                                                    | 出力  | 接続端子です。接続例は「第5章 クロック発振器」を参照してください。                                                                       |

| システム<br>制御 | RES             | 7                                | 7                                                                    | 入力  | リセット端子です。この端子を Low レベルにすると、リセット状態になります。                                                                  |

|            | TEST            | 8                                | 8                                                                    | 入力  | テスト端子です。V <sub>SS</sub> 電位に接地してく<br>ださい。                                                                 |

| 外部割り込み     | NMI             | 35                               | 13                                                                   | 入力  | ノンマスカブル割り込み要求入力端子<br>です。必ず抵抗でプルアップしてくださ<br>い。                                                            |

|            | IRQ0~<br>IRQ7   | 52~54* <sup>1</sup><br>21~23     | 37、38<br>56、57<br>25~28                                              | 入力  | 外部割り込み要求入力端子です。立ち上がりエッジセンス/立ち下がりエッジセンス/両エッジセンスを選択できます。                                                   |

| 分類                   | 記号              | ピン                               | 番号                                                                   | 入出力 | 機能                                                                 |

|----------------------|-----------------|----------------------------------|----------------------------------------------------------------------|-----|--------------------------------------------------------------------|

|                      |                 | H8S/20103 グループ<br>H8S/20115 グループ | H8S/20203 グループ<br>H8S/20223 グループ<br>H8S/20215 グループ<br>H8S/20235 グループ |     |                                                                    |

| タイマ RA               | TRAIO           | 41                               | 16                                                                   | 入出力 | パルス出力/カウントソース入力/測<br>定パルス入力兼用端子です。                                 |

|                      | TRAO            | *2                               | *2                                                                   | 出力  | パルス反転出力端子です。                                                       |

| タイマ RB               | TRGB            | *2                               | *2                                                                   | 入力  | トリガ入力端子です。                                                         |

|                      | TRBO            | 42                               | 15                                                                   | 出力  | パルス出力/PWM 出力兼用端子です。                                                |

| タイマ RC* <sup>3</sup> | FTCI            | 16                               | _                                                                    | 入力  | 外部イベント入力端子です。                                                      |

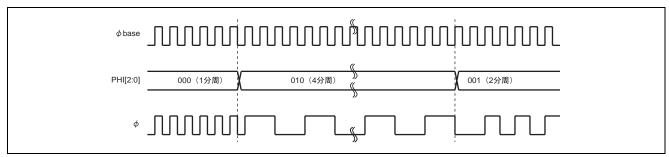

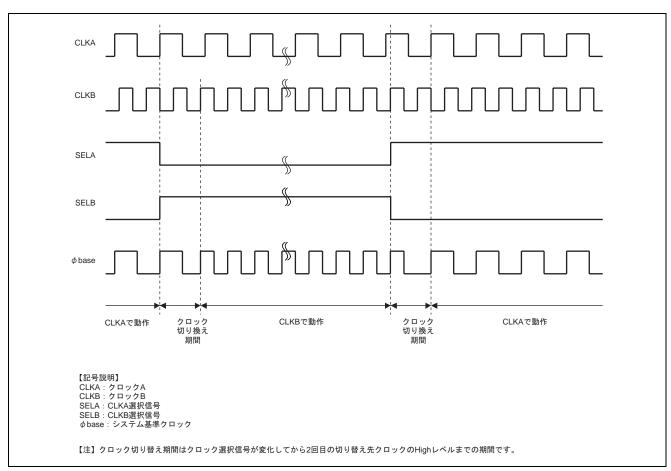

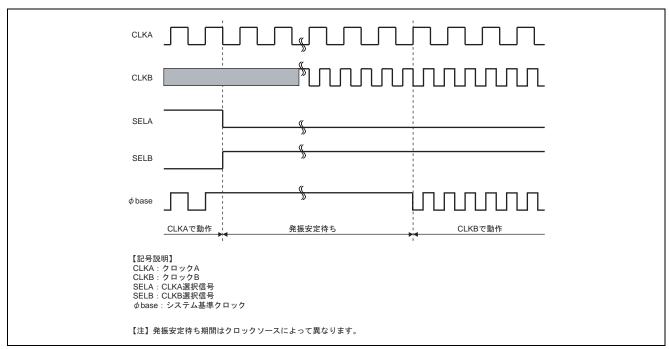

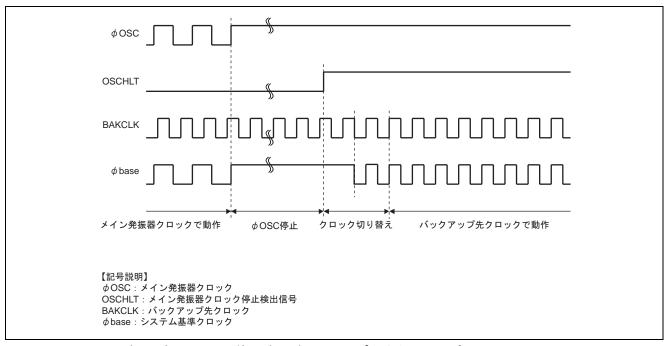

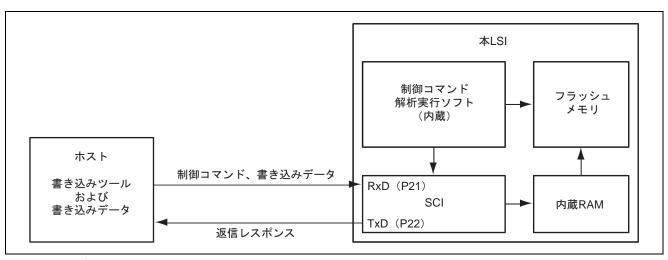

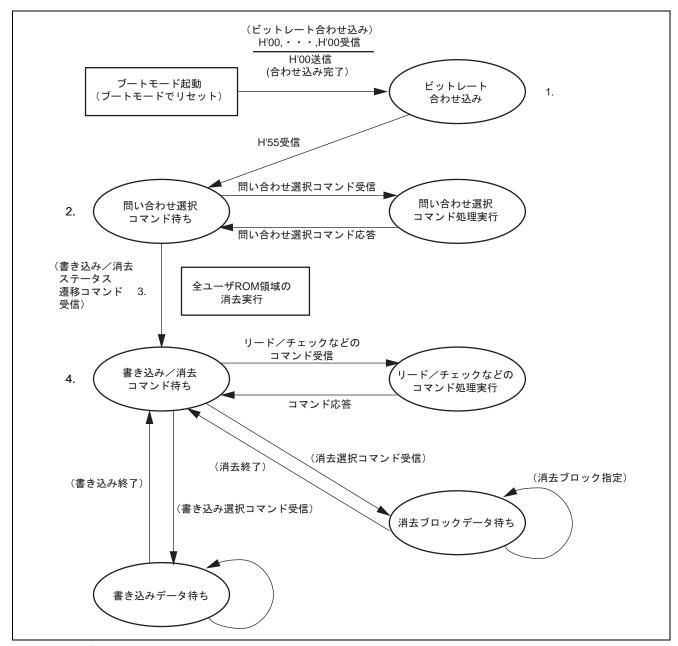

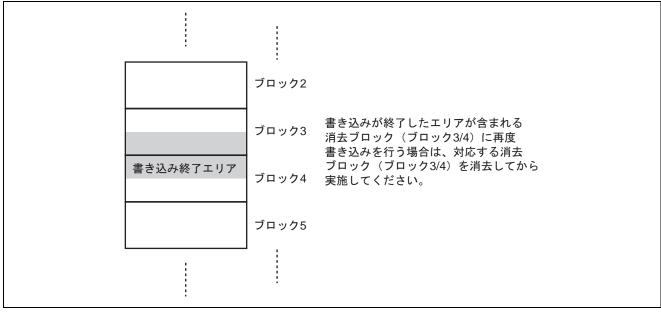

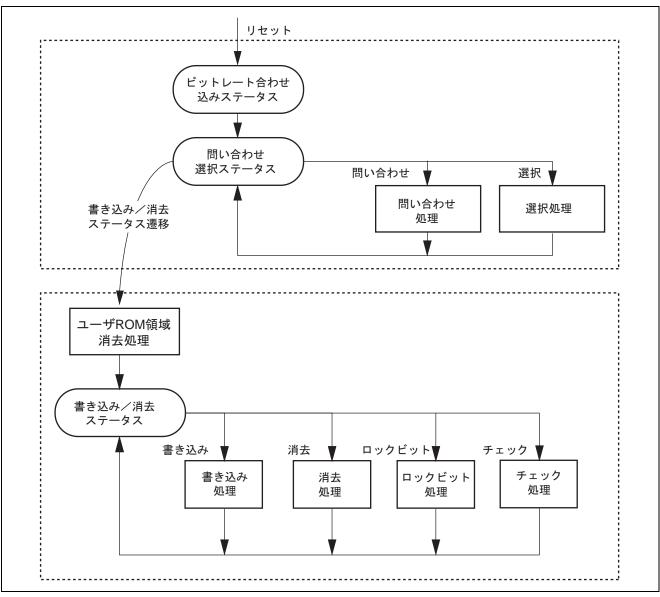

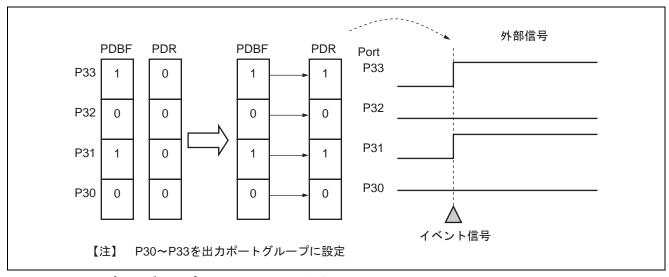

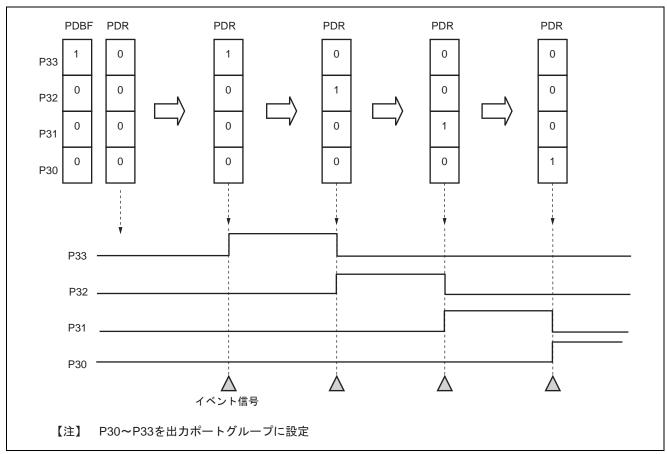

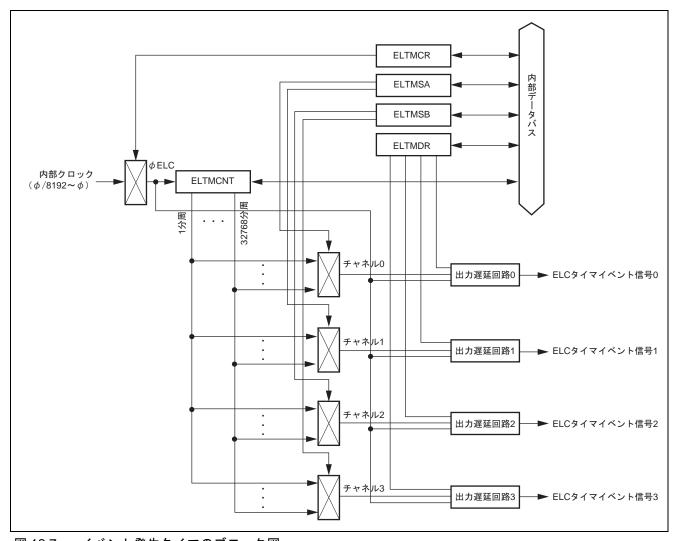

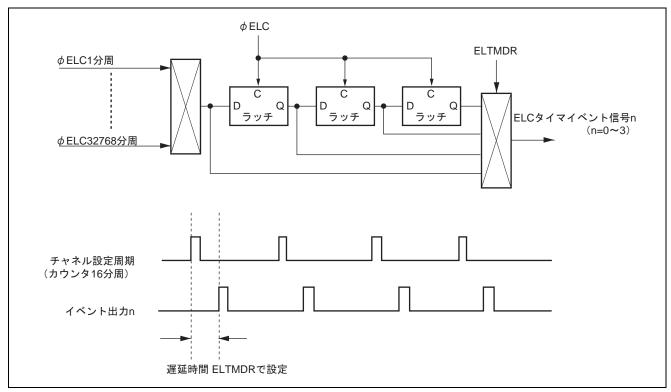

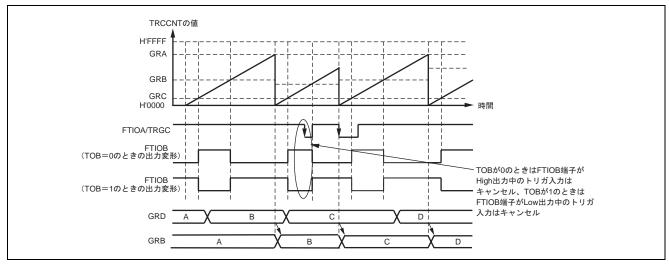

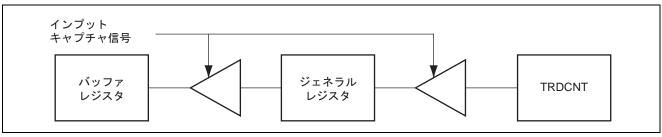

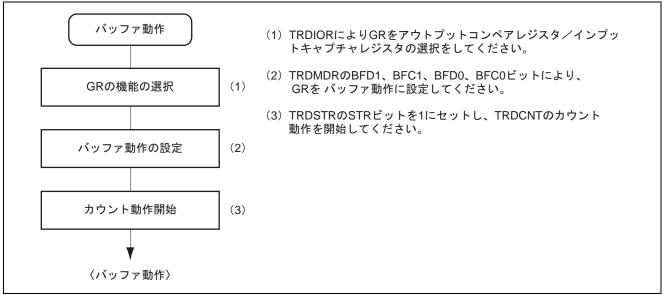

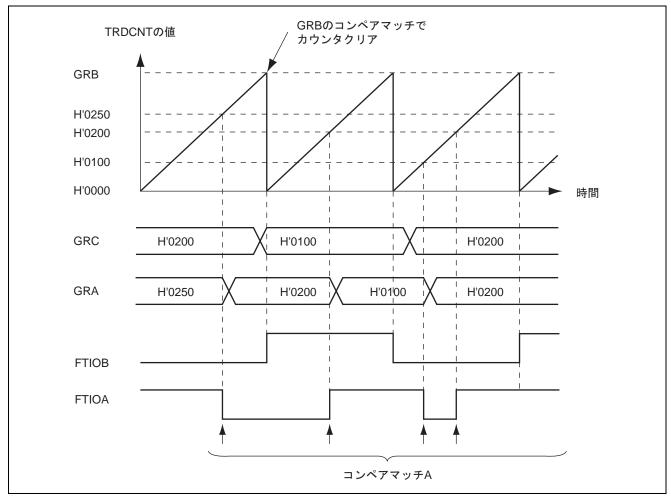

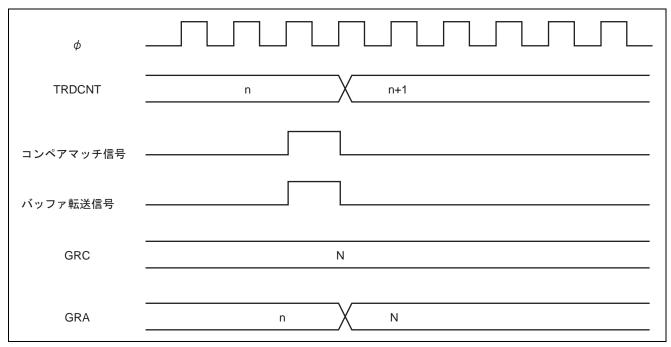

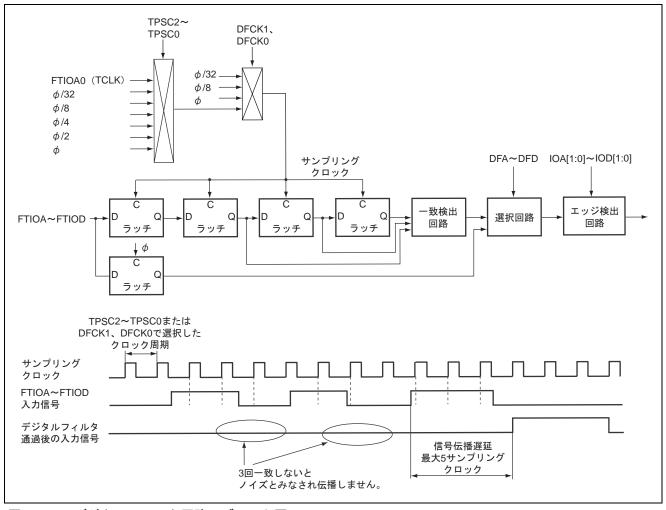

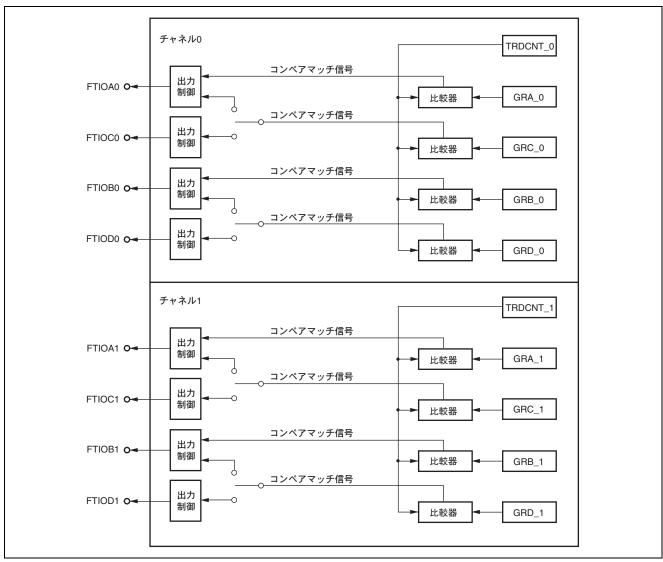

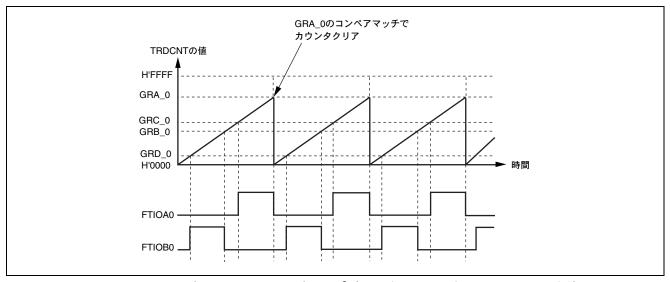

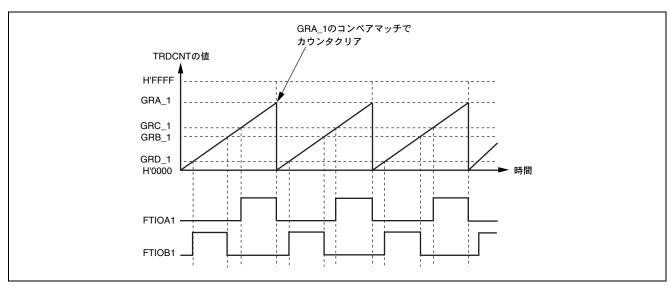

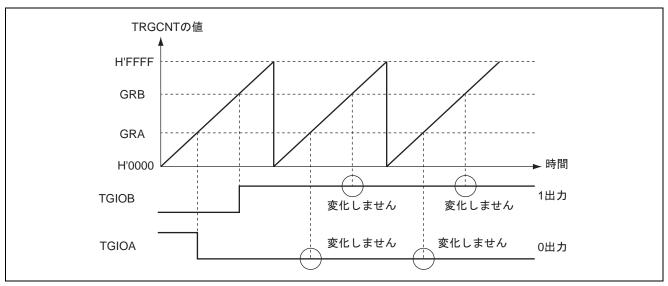

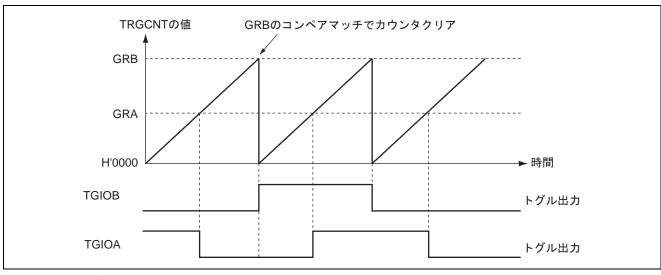

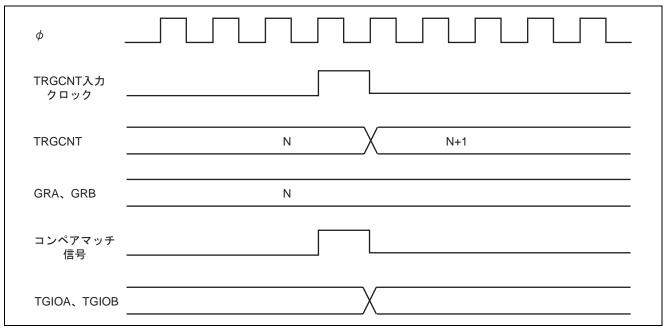

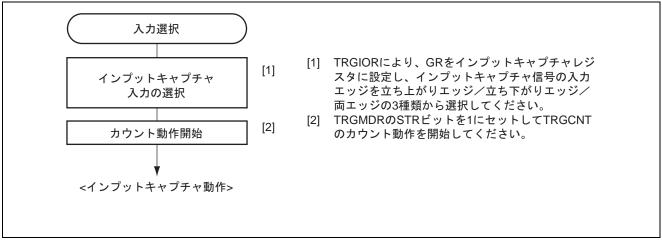

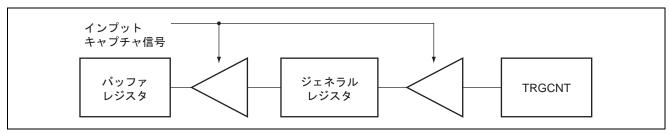

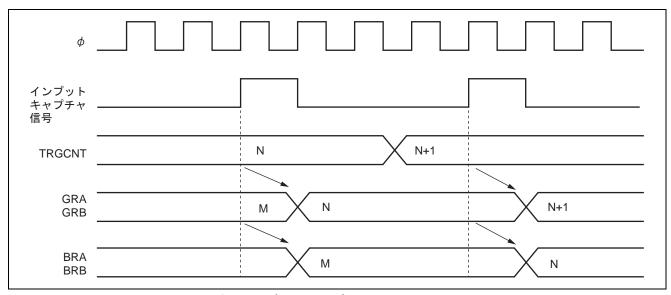

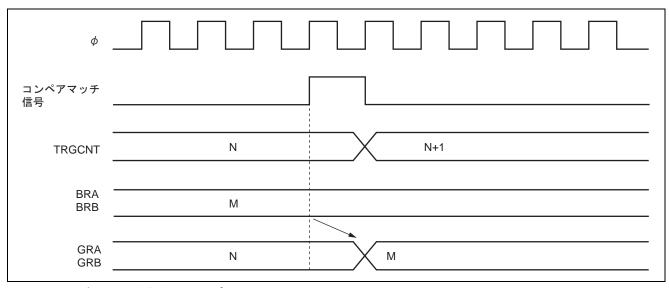

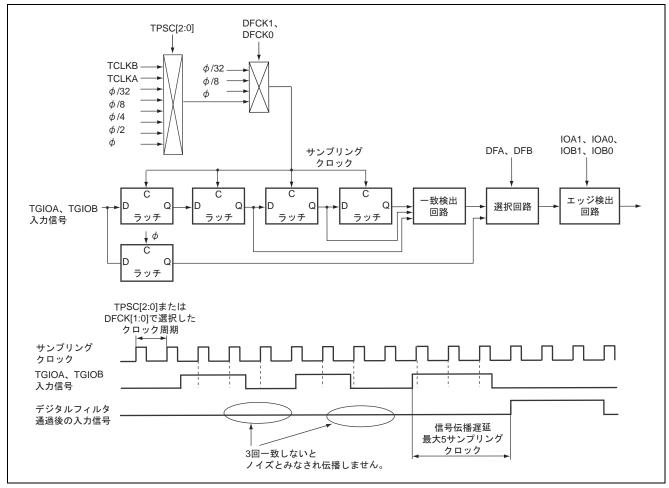

|                      | FTIOA~<br>FTIOD | 20~17                            | _                                                                    | 入出力 | アウトプットコンペア出カ/インプットキャプチャ入力/PWM出力兼用端子です。                             |