## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# 資料中の「日立製作所」、「日立XX」等名称の株式会社ルネサス テクノロジへの変更について

2003年4月1日を以って三菱電機株式会社及び株式会社日立製作所のマイコン、ロジック、アナログ、ディスクリート半導体、及びDRAMを除くメモリ(フラッシュメモリ・SRAM等)を含む半導体事業は株式会社ルネサス テクノロジに承継されました。従いまして、本資料中には「日立製作所」、「株式会社日立製作所」、「日立半導体」、「日立XX」といった表記が残っておりますが、これらの表記は全て「株式会社ルネサス テクノロジ」に変更されておりますのでご理解の程お願い致します。尚、会社商標・ロゴ・コーポレートステートメント以外の内容については一切変更しておりませんので資料としての内容更新ではありません。

ルネサステクノロジ ホームページ (http://www.renesas.com)

2003年4月1日 株式会社ルネサス テクノロジ カスタマサポート部

#### ご注意

#### 安全設計に関するお願い

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサス テクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサス テクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサス テクノロジ半導体製品のご購入に当たりましては、事前にルネサス テクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサス テクノロジホームページ (http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する 損害がお客様に生じた場合には、ルネサス テクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサス テクノロジ、ルネサス販売または特約店までご照会ください。

# H8/3657 シリーズ

ハードウェアマニュアル

# はじめに

H8/300L シリーズは、高速 H8/300L CPU を核にして、システム構成に必要な周辺機能を 集積したシングルチップマイクロコンピュータです。

H8/300L CPUは、H8/300CPUと互換性のある命令体系を備えています。

H8/3657 シリーズは、システム構成に必要な周辺機能として、5 種類のタイマ、14 ビット PWM、2 チャネルのシリアルコミュニケーションインタフェース、A/D 変換器を内蔵しており、高度な制御システムの組込み用マイコンとして活用できます。

本マニュアルは、H8/3657 シリーズのハードウェアについて記載しています。命令の詳細については、「H8/300L シリーズ プログラミングマニュアル」をあわせてご覧ください。

# 目次

| 第 1 | 草 概安      |                  |

|-----|-----------|------------------|

| 1.1 | 概要        | 3                |

| 1.2 | 内部ブロック図   | 6                |

| 1.3 | 端子説明      | 7                |

|     | 1.3.1     | ピン配置7            |

|     | 1.3.2     | 端子機能9            |

| 第2  | 章 CPU     |                  |

| 2.1 | 概要        |                  |

|     | 2.1.1     | 特長15             |

|     | 2.1.2     | アドレス空間15         |

|     | 2.1.3     | レジスタ構成16         |

| 2.2 | 各レジスタの説明  | 17               |

|     | 2.2.1     | 汎用レジスタ17         |

|     | 2.2.2     | コントロールレジスタ17     |

|     | 2.2.3     | CPU 内部レジスタの初期値19 |

| 2.3 | データ構成     | 20               |

|     | 2.3.1     | 汎用レジスタのデータ構成21   |

|     | 2.3.2     | メモリ上でのデータ構成22    |

| 2.4 | アドレッシングモー | F23              |

|     | 2.4.1     | アドレッシングモード23     |

|     | 2.4.2     | 実効アドレスの計算方法25    |

| 2.5 | 命令セット     | 29               |

|     | 2.5.1     | データ転送命令31        |

|     | 2.5.2     | 算術演算命令           |

|     | 2.5.3     | 論理演算命令34         |

|     | 2.5.4     | シフト命令34          |

|     |           |                  |

|                   | 2                                | 2.5.5                                                                         | ビット操作命令                                                                               | 35                                                                          |

|-------------------|----------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|                   | 2                                | 2.5.6                                                                         | 分岐命令                                                                                  | 39                                                                          |

|                   | 2                                | 2.5.7                                                                         | システム制御命令                                                                              | 41                                                                          |

|                   | 2                                | 2.5.8                                                                         | ブロック転送命令                                                                              | 42                                                                          |

| 2.6               | 基本動作タイ                           | イミング                                                                          |                                                                                       | 43                                                                          |

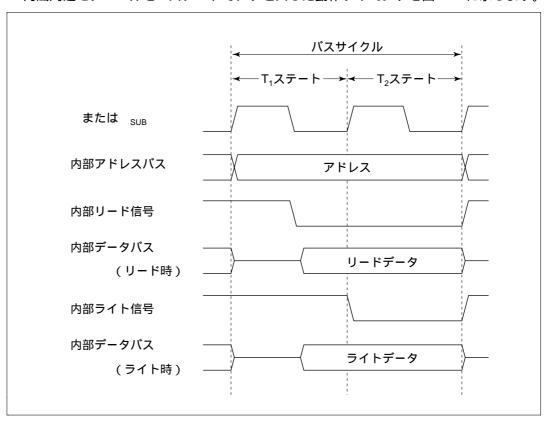

|                   | 2                                | 2.6.1                                                                         | 内蔵メモリ (RAM、ROM )                                                                      | 43                                                                          |

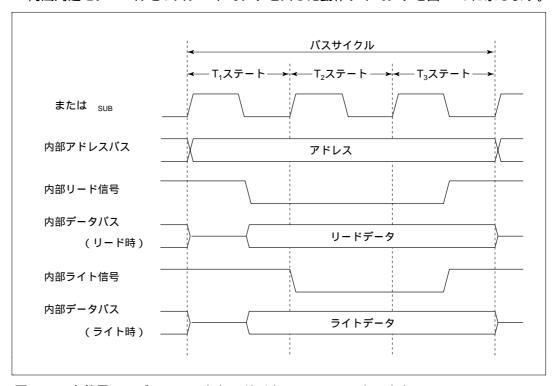

|                   | 2                                | 2.6.2                                                                         | 内蔵周辺モジュール                                                                             | 44                                                                          |

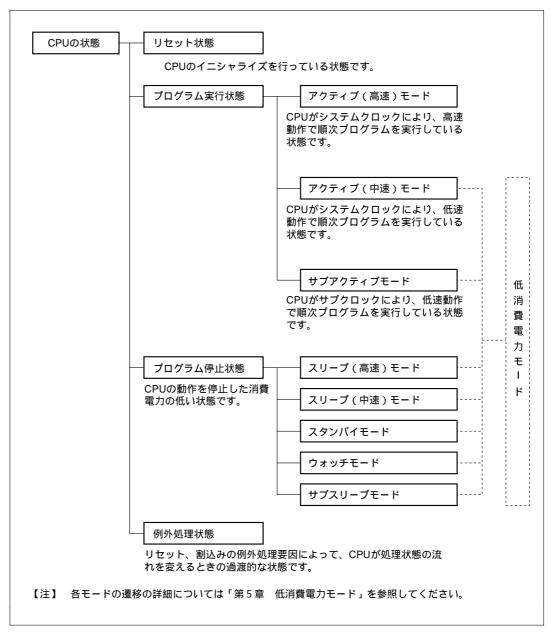

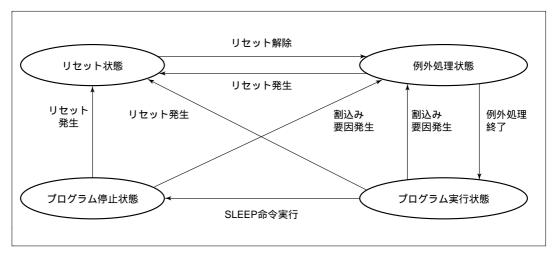

| 2.7               | CPU の状態                          |                                                                               |                                                                                       | 46                                                                          |

|                   | 2                                | 2.7.1                                                                         | 概要                                                                                    | 46                                                                          |

|                   | 2                                | 2.7.2                                                                         | プログラム実行状態                                                                             | 47                                                                          |

|                   | 2                                | 2.7.3                                                                         | プログラム停止状態                                                                             | 47                                                                          |

|                   | 2                                | 2.7.4                                                                         | 例外処理状態                                                                                | 47                                                                          |

| 2.8               | メモリマッ:                           | プ                                                                             |                                                                                       | 48                                                                          |

| 2.9               | 使用上の注意                           | 意事項                                                                           |                                                                                       | 49                                                                          |

|                   | 2                                | 2.9.1                                                                         | データアクセスに関する注意事項                                                                       | 49                                                                          |

|                   | 2                                | 2.9.2                                                                         | ビット操作命令使用上の注意事項                                                                       | 51                                                                          |

|                   | 2                                | 2.9.3                                                                         | EEPMOV 命令使用上の注意事項                                                                     | 57                                                                          |

| <b>∽</b> ∩        | <del>호</del> /티시 /               | л т <b>ш</b>                                                                  |                                                                                       |                                                                             |

| 第3<br>3.1         | 章 例外如                            |                                                                               |                                                                                       | 61                                                                          |

|                   | 概要                               |                                                                               |                                                                                       |                                                                             |

| 3.1               | 概要<br>リセット                       |                                                                               |                                                                                       | 62                                                                          |

| 3.1               | 概要<br>リセット<br>3                  |                                                                               |                                                                                       | 62<br>62                                                                    |

| 3.1               | 概要<br>リセット<br>3                  | 3.2.1                                                                         | 概要                                                                                    | 62<br>62<br>62                                                              |

| 3.1               | 概要<br>リセット<br>3<br>3<br>3        | 3.2.1<br>3.2.2<br>3.2.3                                                       | 概要リセットシーケンス                                                                           | 62<br>62<br>62<br>64                                                        |

| 3.1<br>3.2        | 概要<br>リセット<br>3<br>3<br>3<br>割込み | 3.2.1<br>3.2.2<br>3.2.3                                                       | 概要<br>リセットシーケンス<br>リセット直後の割込み                                                         | <ul><li>62</li><li>62</li><li>62</li><li>62</li><li>64</li><li>65</li></ul> |

| 3.1<br>3.2        | 概要<br>リセット<br>3<br>3<br>3<br>割込み | 3.2.1<br>3.2.2<br>3.2.3                                                       | 概要<br>リセットシーケンス<br>リセット直後の割込み                                                         | 62<br>62<br>62<br>64<br>65<br>65                                            |

| 3.1<br>3.2        | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>                                                   | 概要<br>リセットシーケンス<br>リセット直後の割込み<br>概要                                                   | 62<br>62<br>62<br>64<br>65<br>65<br>67                                      |

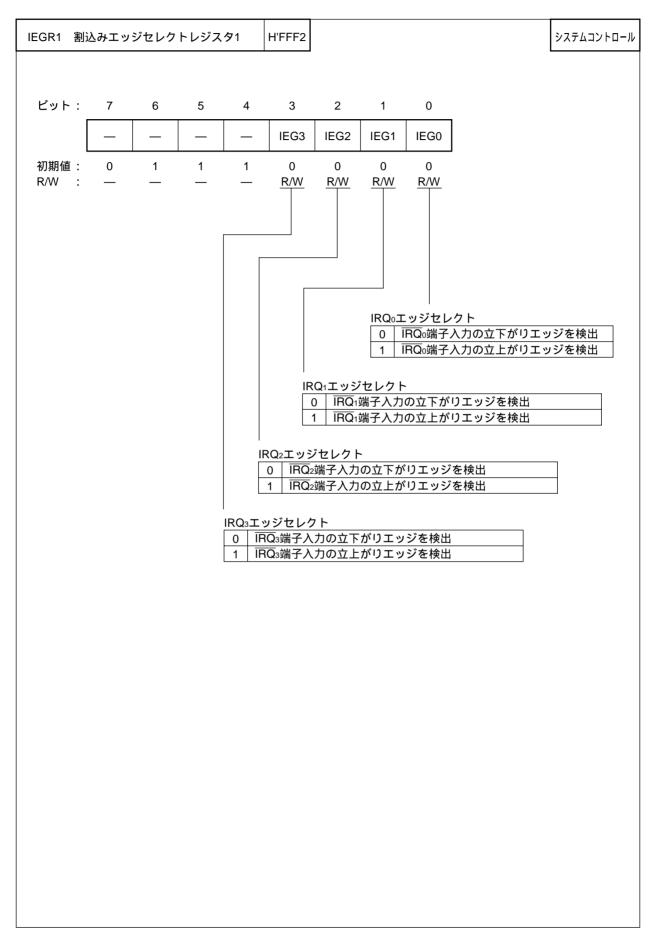

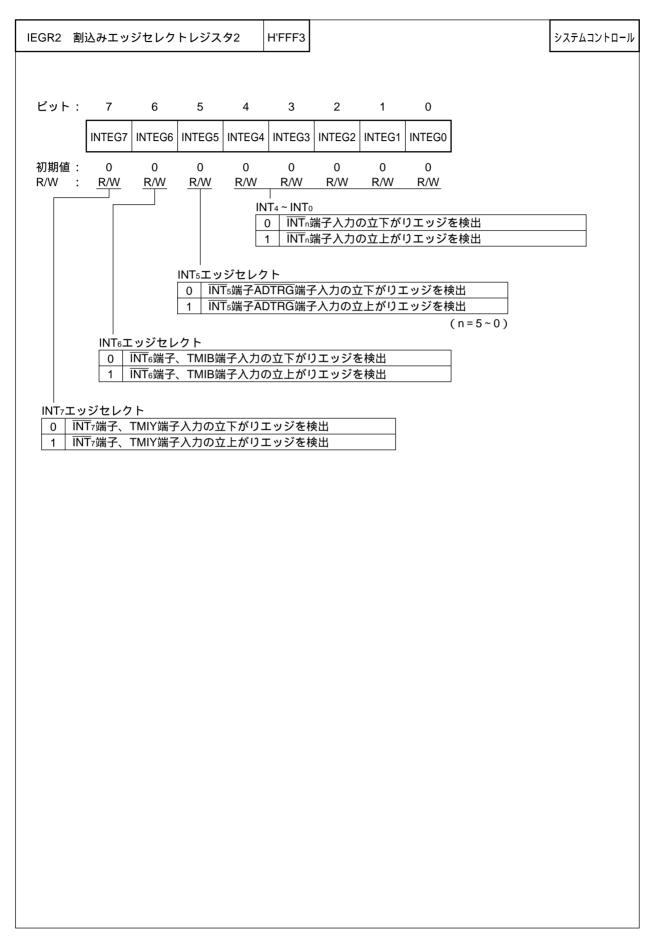

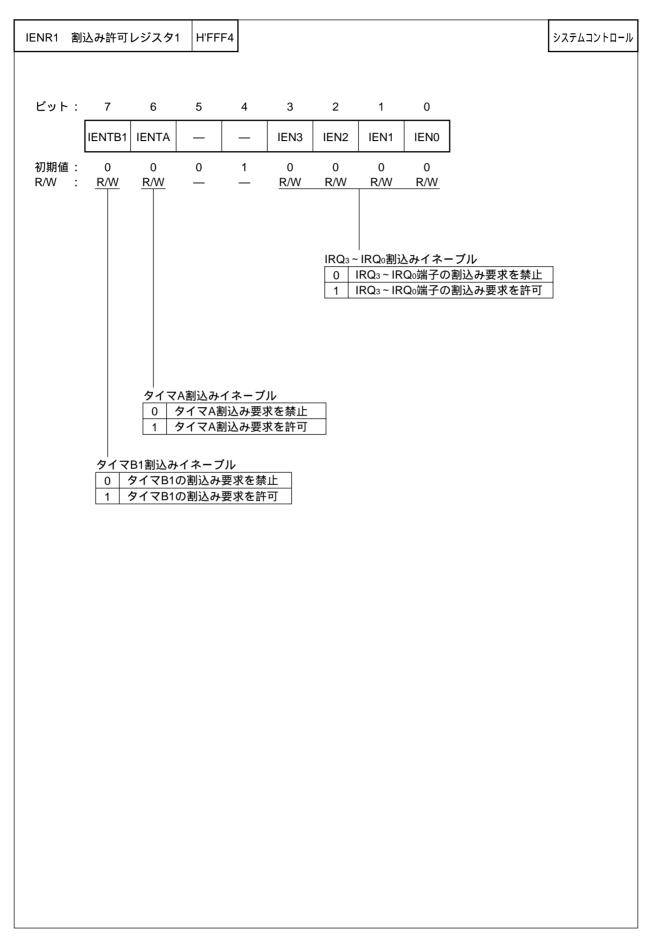

| 3.1<br>3.2        | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>3.3.1<br>3.3.2                                     | 概要<br>リセットシーケンス<br>リセット直後の割込み<br>概要<br>各レジスタの説明                                       | 62<br>62<br>62<br>64<br>65<br>65<br>67<br>76                                |

| 3.1<br>3.2        | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>3.3.1<br>3.3.2<br>3.3.3                            | 概要<br>リセットシーケンス<br>リセット直後の割込み<br>概要<br>各レジスタの説明<br>外部割込み                              | 62<br>62<br>62<br>64<br>65<br>65<br>67<br>76                                |

| 3.1<br>3.2        | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                   | 概要  リセットシーケンス  リセット直後の割込み  概要  各レジスタの説明  外部割込み  内部割込み                                 | 62<br>62<br>62<br>64<br>65<br>65<br>67<br>76<br>76                          |

| 3.1<br>3.2        | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6 | 概要<br>リセットシーケンス<br>リセット直後の割込み<br>概要<br>各レジスタの説明<br>外部割込み<br>内部割込み<br>割込み動作            | 62<br>62<br>62<br>64<br>65<br>65<br>67<br>76<br>77<br>82                    |

| 3.1<br>3.2<br>3.3 | 概要                               | 3.2.1<br>3.2.2<br>3.2.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6 | 概要<br>リセットシーケンス<br>リセット直後の割込み<br>概要<br>各レジスタの説明<br>外部割込み<br>内部割込み<br>割込み動作<br>割込み応答時間 | 62<br>62<br>62<br>64<br>65<br>65<br>67<br>76<br>77<br>82<br>83              |

## 第4章 クロック発振器

| 4.1 | 概要        |                        | 89  |

|-----|-----------|------------------------|-----|

|     | 4.1.1     | ブロック図                  | 89  |

|     | 4.1.2     | システムクロックとサブクロック        | 89  |

| 4.2 | システムクロック  | <b>卷振器</b>             | 90  |

| 4.3 | サブクロック発振器 | 멶                      | 93  |

| 4.4 | プリスケーラ    |                        | 95  |

| 4.5 | 発振子に関する注意 | 意事項                    | 96  |

| 第 5 | 5 章 低消費電力 | Jモ <b>ー</b> ド          |     |

| 5.1 | 概要        |                        | 99  |

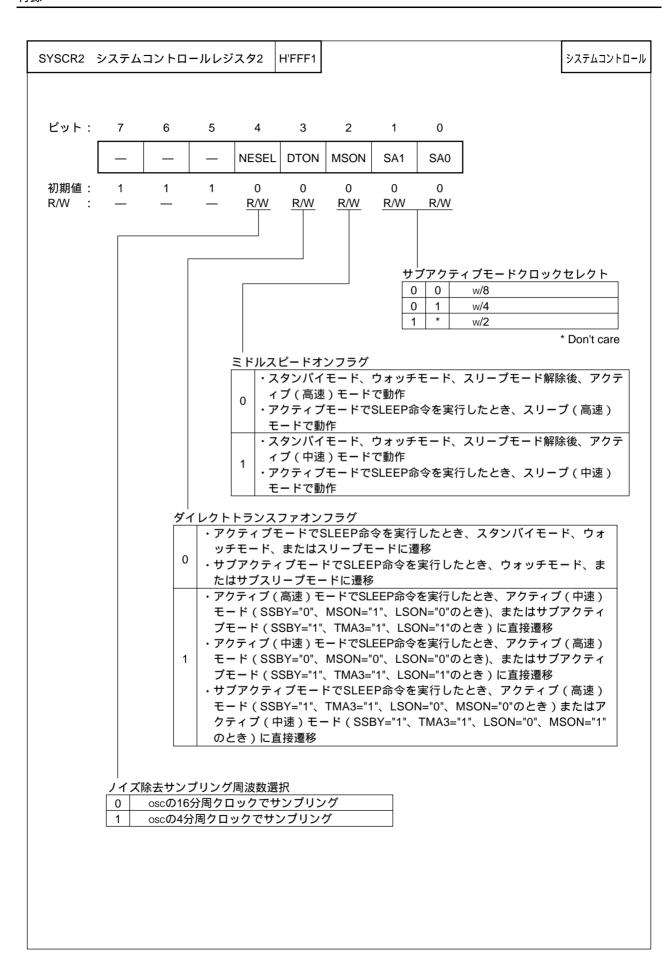

|     | 5.1.1     | システムコントロールレジスタ         | 102 |

| 5.2 | スリープモード   |                        | 107 |

|     | 5.2.1     | スリープモードへの遷移            | 107 |

|     | 5.2.2     | スリープモードの解除             | 107 |

|     | 5.2.3     | スリープ(中速)モードの動作周波数について  | 107 |

| 5.3 | スタンバイモード. |                        | 108 |

|     | 5.3.1     | スタンバイモードへの遷移           | 108 |

|     | 5.3.2     | スタンバイモードの解除            | 108 |

|     | 5.3.3     | スタンバイモード解除後の発振安定時間の設定  | 109 |

| 5.4 | ウォッチモード   |                        | 110 |

|     | 5.4.1     | ウォッチモードへの遷移            | 110 |

|     | 5.4.2     | ウォッチモードの解除             | 110 |

|     | 5.4.3     | ウォッチモード解除後の発振安定時間の設定   | 110 |

| 5.5 | サブスリープモー  | <b>-</b>               | 111 |

|     | 5.5.1     | サブスリープモードへの遷移          | 111 |

|     | 5.5.2     | サブスリープモードの解除           | 111 |

| 5.6 | サブアクティブモ- | - F                    | 112 |

|     | 5.6.1     | サブアクティブモードへの遷移         | 112 |

|     | 5.6.2     | サブアクティブモードの解除          | 112 |

|     | 5.6.3     | サブアクティブモードの動作周波数について   | 112 |

| 5.7 | アクティブ(中速) | ) モード                  | 113 |

|     | 5.7.1     | アクティブ(中速)モードへの遷移       | 113 |

|     | 5.7.2     | アクティブ(中速)モードの解除        | 113 |

|     | 5.7.3     | アクティブ(中速)モードの動作周波数について | 113 |

| 5.8 | 直接遷移      |                        | 114 |

# 第6章 ROM

| 6.1           | 概要          |                      | 119 |

|---------------|-------------|----------------------|-----|

|               | 6.1.1       | ブロック図                | 119 |

| 6.2           | PROM モード    |                      |     |

|               | 6.2.1       | PROM モードの設定          |     |

|               | 6.2.2       | ソケットアダプタの端子対応とメモリマップ |     |

| 6.3           | プログラミング     |                      |     |

|               | 6.3.1       | 書込み / ベリファイ          |     |

|               | 6.3.2       | 書込み時の注意              | 126 |

| 6.4           | 書込み後の信頼性.   |                      |     |

|               |             |                      |     |

| 第7            | '章 RAM      |                      |     |

| 7.1           | 概要          |                      |     |

|               | 7.1.1       | ブロック図                | 131 |

| <i>5</i> /5 0 | ÷ 1/0 -19 1 |                      |     |

|               | 章 I/O ポート   |                      |     |

| 8.1           |             |                      |     |

| 8.2           |             |                      |     |

|               | 8.2.1       | 概要                   |     |

|               | 8.2.2       | レジスタの構成と説明           |     |

|               | 8.2.3       | 端子機能                 |     |

|               | 8.2.4       | 端子状態                 |     |

|               | 8.2.5       | 入力プルアップ MOS          |     |

| 8.3           |             |                      |     |

|               | 8.3.1       | 概要                   |     |

|               | 8.3.2       | レジスタの構成と説明           |     |

|               | 8.3.3       | 端子機能                 |     |

|               | 8.3.4       | 端子状態                 |     |

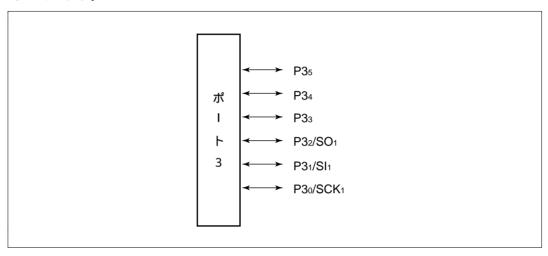

| 8.4           | ポート3        |                      |     |

|               | 8.4.1       | 概要                   |     |

|               | 8.4.2       | レジスタの構成と説明           |     |

|               | 8.4.3       | 端子機能                 |     |

|               | 8.4.4       | 端子状態                 |     |

|               | 8.4.5       | 入力プルアップ MOS          | 151 |

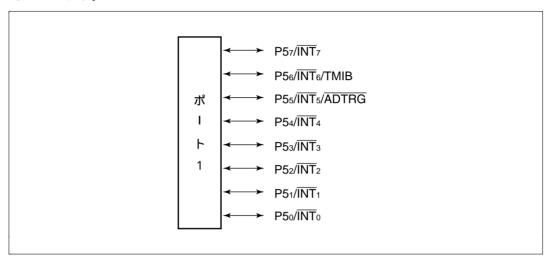

| 8.5           | ポート5        |                      |     |

|               | 8.5.1       | 概要                   | 152 |

|      | 8.5.2      | レジスタの構成と説明                              |     |

|------|------------|-----------------------------------------|-----|

|      | 8.5.3      | 端子機能                                    |     |

|      | 8.5.4      | 端子状態                                    | 154 |

|      | 8.5.5      | 入力プルアップ MOS                             |     |

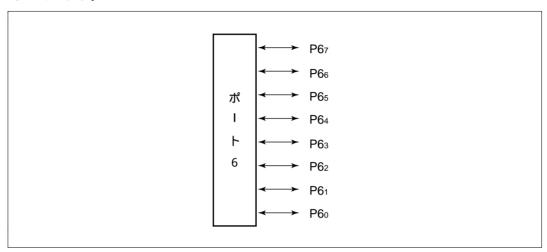

| 8.6  | ポート 6      |                                         |     |

|      | 8.6.1      | 概要                                      | 156 |

|      | 8.6.2      | レジスタの構成と説明                              | 156 |

|      | 8.6.3      | 端子機能                                    |     |

|      | 8.6.4      | 端子状態                                    |     |

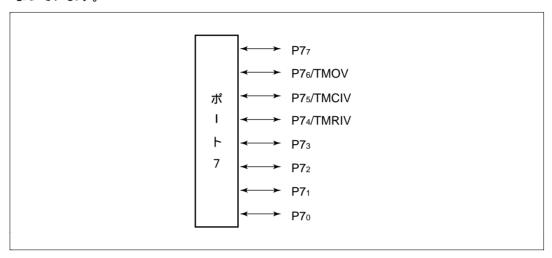

| 8.7  | ポート7       |                                         | 158 |

|      | 8.7.1      | 概要                                      | 158 |

|      | 8.7.2      | レジスタの構成と説明                              | 158 |

|      | 8.7.3      | 端子機能                                    | 160 |

|      | 8.7.4      | 端子状態                                    |     |

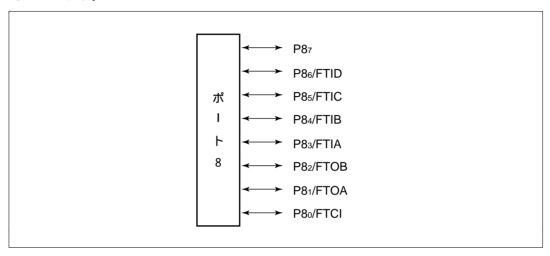

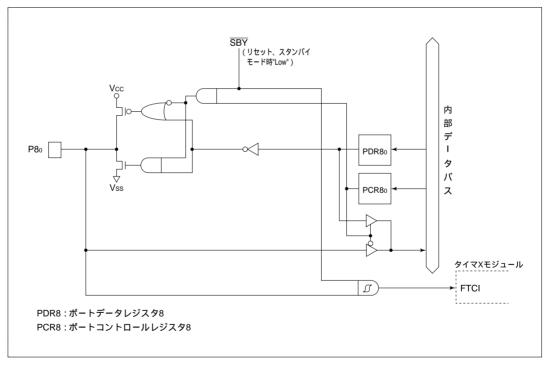

| 8.8  | ポート8       |                                         | 161 |

|      | 8.8.1      | 概要                                      | 161 |

|      | 8.8.2      |                                         |     |

|      | 8.8.3      | 端子機能                                    | 162 |

|      | 8.8.4      | 端子状態                                    | 163 |

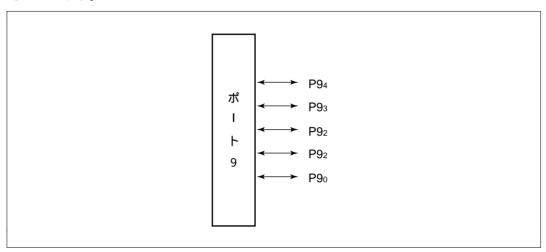

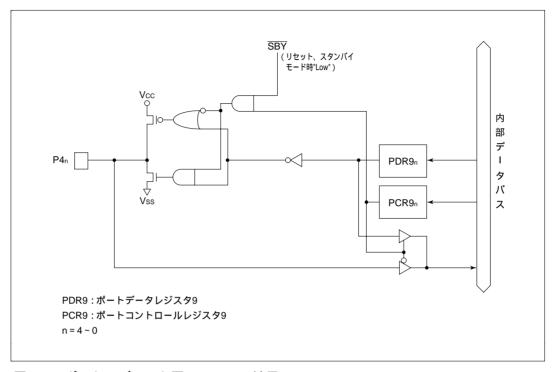

| 8.9  | ポート 9      |                                         | 164 |

|      | 8.9.1      |                                         |     |

|      | 8.9.2      | レジスタの構成と説明                              | 164 |

|      | 8.9.3      | 端子機能                                    | 165 |

|      | 8.9.4      | 端子状態                                    | 166 |

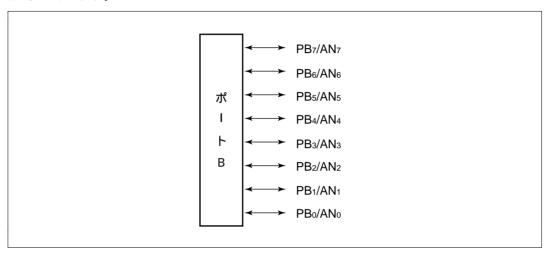

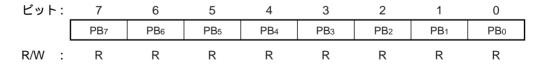

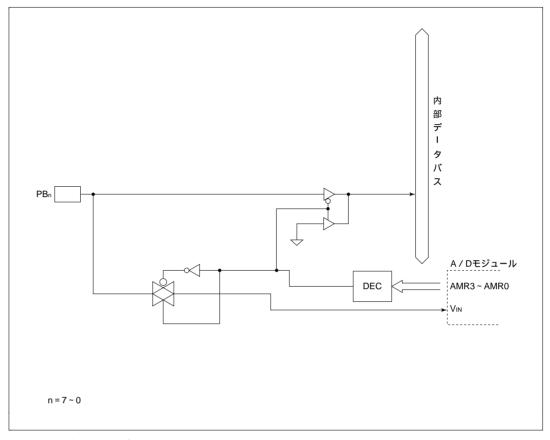

| 8.10 | ポートB       |                                         | 167 |

|      | 8.10.      |                                         |     |

|      | 8.10.      | 2 レジスタの構成と説明                            | 167 |

|      | 8.10.      |                                         |     |

|      | 8.10.      | 4 端子状態                                  | 168 |

| 8.11 | 使用上の注意事    | 項                                       | 168 |

| 0.11 | 文/11工》/工态学 | ~ · · · · · · · · · · · · · · · · · · · | 100 |

|      |            |                                         |     |

| 第9   | 章 タイマ      |                                         |     |

| 9.1  | 概要         |                                         | 171 |

| 9.1  |            |                                         |     |

| 2.4  | 9.2.1      |                                         |     |

|      | 9.2.1      |                                         |     |

|      |            |                                         |     |

|      | 9.2.3      | 動作説明                                    | 1/6 |

|      | 9.2.4             | タイマ A の動作モード       | 177 |

|------|-------------------|--------------------|-----|

| 9.3  | タイマ B1            |                    | 178 |

|      | 9.3.1             | 概要                 | 178 |

|      | 9.3.2             | 各レジスタの説明           | 179 |

|      | 9.3.3             | 動作説明               | 181 |

|      | 9.3.4             | タイマ B1 の動作モード      | 182 |

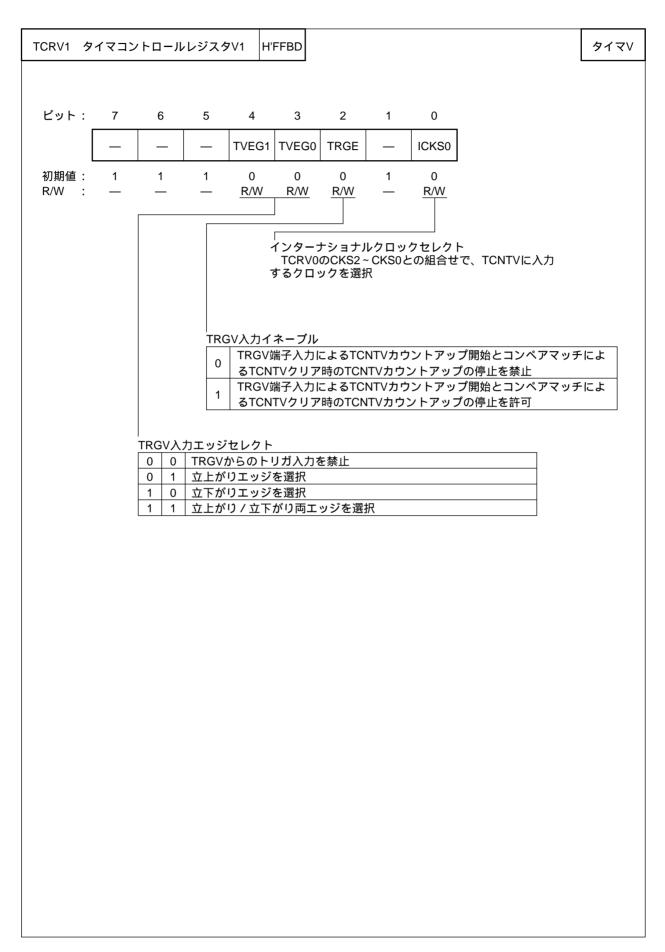

| 9.4  | タイマ V             |                    | 183 |

|      | 9.4.1             | 概要                 |     |

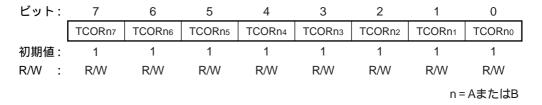

|      | 9.4.2             | 各レジスタの説明           |     |

|      | 9.4.3             | 動作説明               | 193 |

|      | 9.4.4             | タイマ ∨ の動作モード       | 197 |

|      | 9.4.5             | 割込み要因              | 197 |

|      | 9.4.6             | タイマ ∨ の使用例         | 198 |

|      | 9.4.7             | 使用上の注意事項           | 199 |

| 9.5  | タイマ X             |                    | 204 |

|      | 9.5.1             | 概要                 | 204 |

|      | 9.5.2             | 各レジスタの説明           | 207 |

|      | 9.5.3             | CPU とのインタフェース      | 220 |

|      | 9.5.4             | 動作説明               | 222 |

|      | 9.5.5             | タイマ X の動作モード       | 229 |

|      | 9.5.6             | 割込み要因              | 229 |

|      | 9.5.7             | タイマ X の使用例         | 230 |

|      | 9.5.8             | 使用上の注意事項           | 231 |

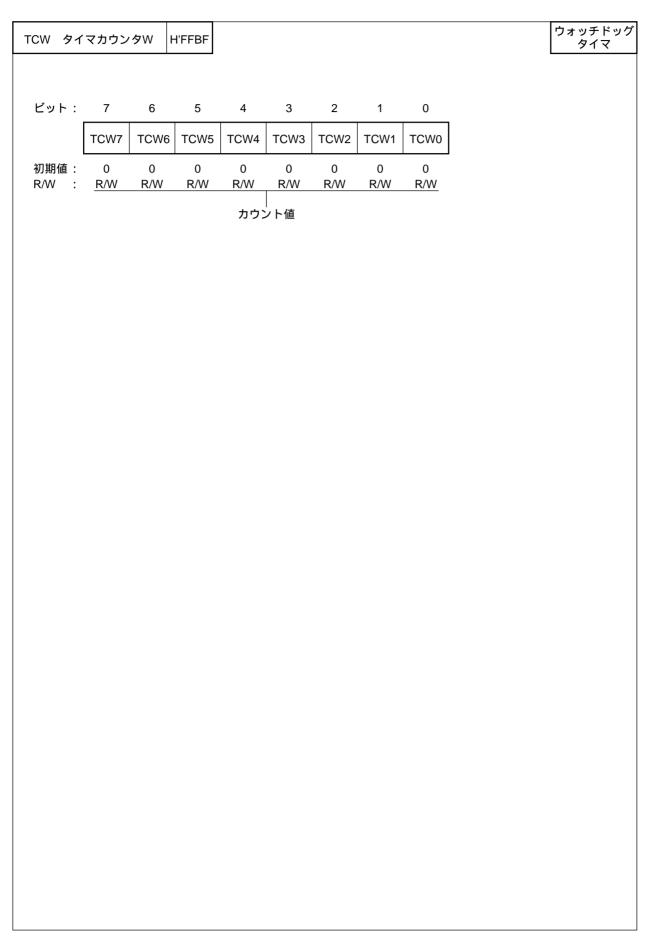

| 9.6  | ウォッチドッグタ <i>~</i> | イマ                 | 236 |

|      | 9.6.1             | 概要                 | 236 |

|      | 9.6.2             | 各レジスタの説明           | 237 |

|      | 9.6.3             | 動作説明               | 241 |

|      | 9.6.4             | ウォッチドッグタイマの動作モード   | 241 |

|      |                   |                    |     |

| 华』   | 0 <del>2</del>    | コニューケ シ.ーン.ノン.クコ コ |     |

| 弗 1  | 0草 ンリアル           | コミュニケーションインタフェース   |     |

| 10.1 | 概要                |                    | 245 |

| 10.2 | SCI1              |                    | 246 |

|      | 10.2.1            | 概要                 | 246 |

|      | 10.2.2            | 各レジスタの説明           | 248 |

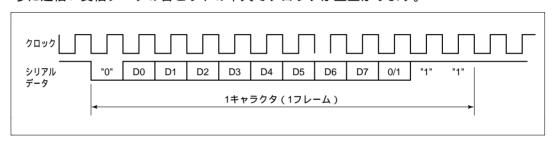

|      | 10.2.3            | クロック同期モード時の動作説明    | 253 |

|      | 10.2.4            | SSB モード時の動作説明      | 255 |

|      | 10.2.5            | 割込み要因              | 257 |

| 10.3 | SCI3               |                              | 258 |

|------|--------------------|------------------------------|-----|

|      | 10.3.1             | 概要                           | 258 |

|      | 10.3.2             | 各レジスタの説明                     | 261 |

|      | 10.3.3             | 動作概要                         | 279 |

|      | 10.3.4             | 調歩同期式モード時の動作説明               | 283 |

|      | 10.3.5             | クロック同期式モード時の動作説明             | 291 |

|      | 10.3.6             | マルチプロセッサ通信機能                 | 298 |

|      | 10.3.7             | 割込み要因                        | 303 |

|      | 10.3.8             | 使用上の注意事項                     | 304 |

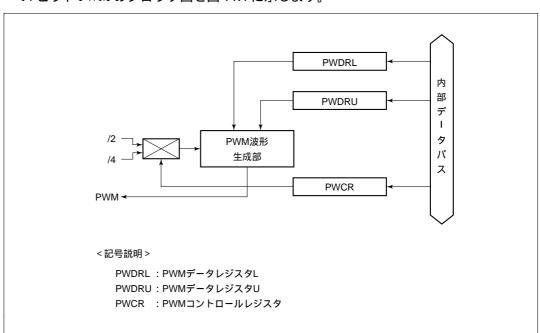

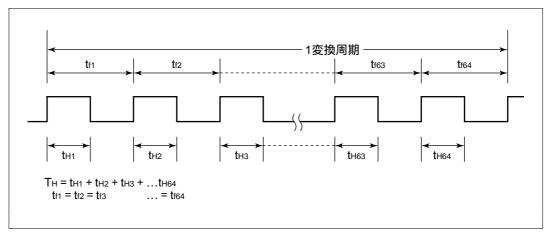

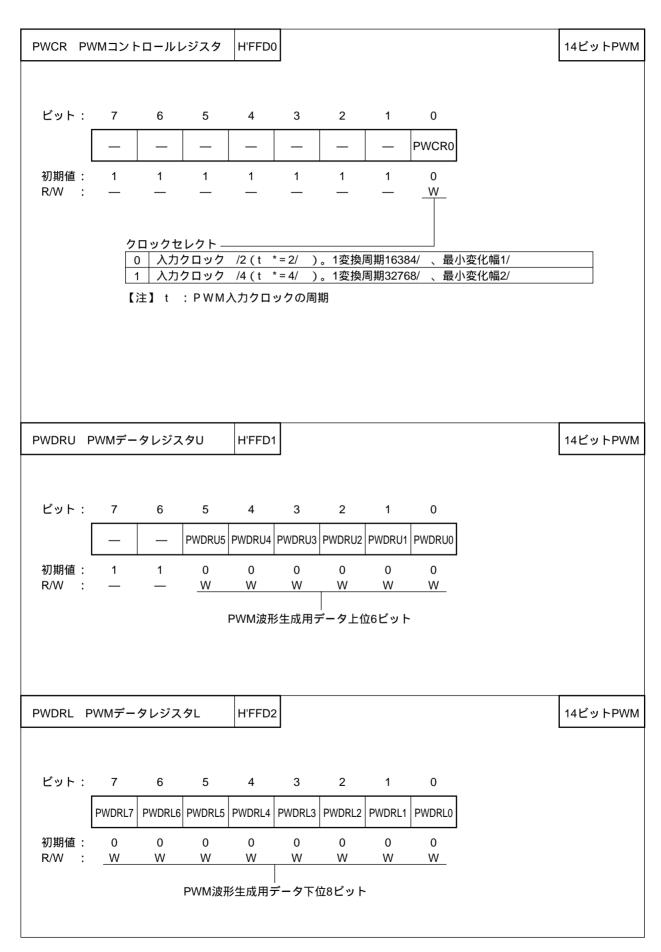

| 第 11 | 章 14 ビット           | PWM                          |     |

| 11.1 | •                  |                              | 211 |

| 11.1 | ている                | 特長                           |     |

|      | 11.1.1             | プロック図                        |     |

|      | 11.1.2             | 端子構成                         |     |

|      | 11.1.3             |                              |     |

| 11.2 |                    | レンスタ博成                       |     |

| 11.2 | 音レクスタの説明<br>11.2.1 | PWM コントロールレジスタ ( PWCR )      |     |

|      | 11.2.1             |                              |     |

| 11.2 |                    | PWM データレジスタ U、L(PWDRU、PWDRL) |     |

| 11.3 | 里川下市北中一            |                              | 313 |

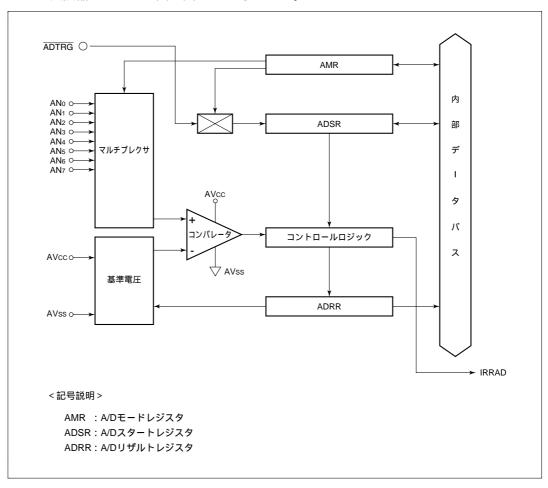

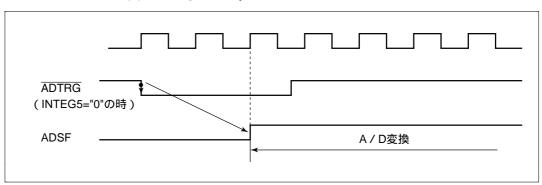

| 第 12 | ? 章 A/D 変換器        | 迟<br>路                       |     |

| 12.1 | 概要                 |                              | 319 |

|      | 12.1.1             | 特長                           |     |

|      | 12.1.2             | ブロック図                        | 319 |

|      | 12.1.3             | 端子構成                         | 320 |

|      | 12.1.4             | レジスタ構成                       | 320 |

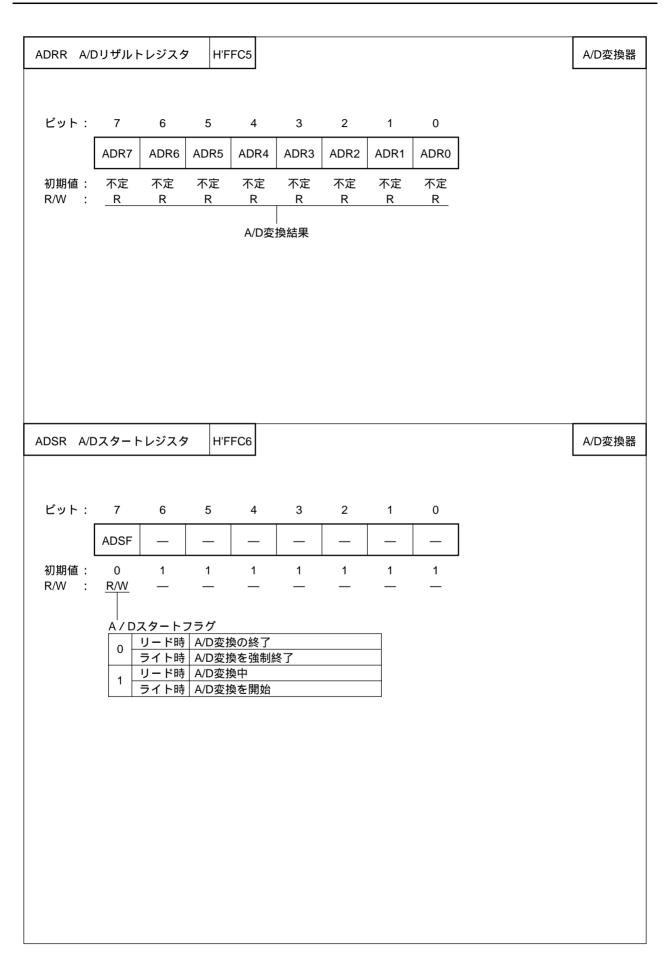

| 12.2 | 各レジスタの説明           |                              | 321 |

|      | 12.2.1             | A/D リザルトレジスタ(ADRR)           | 321 |

|      | 12.2.2             | A/D モードレジスタ ( AMR )          |     |

|      | 12.2.3             | A/D スタートレジスタ ( ADSR )        |     |

| 12.3 |                    |                              |     |

|      | 12.3.1             | A/D 変換動作                     |     |

|      | 12.3.2             |                              |     |

| 12.4 | 割込み要因              |                              |     |

| 12.5 |                    |                              |     |

| 12.6          | 使用」   | 上の注意       |                                                     | 330 |

|---------------|-------|------------|-----------------------------------------------------|-----|

|               |       |            |                                                     |     |

| 第13           | 章     | 電気的特性      |                                                     |     |

| 13.1          | 絶対晶   | 最大定格       |                                                     | 333 |

| 13.2          | 電気的   | 勺特性        |                                                     | 334 |

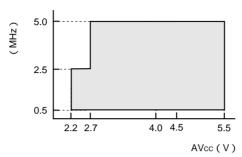

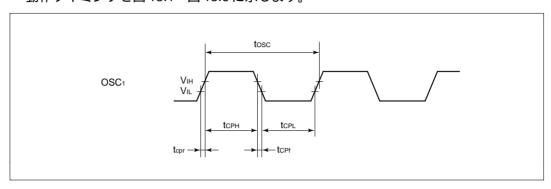

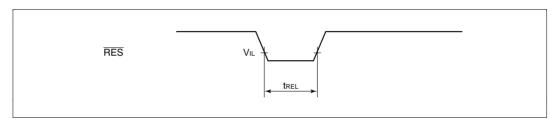

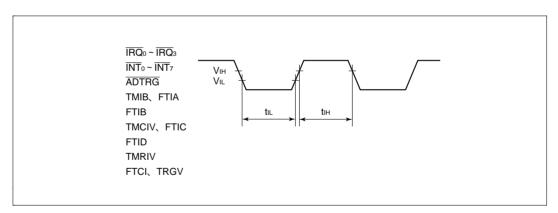

|               |       | 13.2.1     | 電源電圧と動作範囲                                           | 334 |

|               |       | 13.2.2     | DC 特性 ( HD6473657 )                                 | 336 |

|               |       | 13.2.3     | AC 特性 ( HD6473657 )                                 | 340 |

|               |       | 13.2.4     | DC 特性 ( HD6433657、 HD6433656、 HD6433655、 HD6433654  |     |

|               |       |            | HD6433653、HD6433652)                                | 343 |

|               |       | 13.2.5     | AC 特性 ( HD6433657、 HD6433656、 HD6433655、 HD6433654、 |     |

|               |       |            | HD6433653、HD6433652)                                | 347 |

|               |       | 13.2.6     | A/D 变換器特性                                           | 350 |

| 13.3          | 動作為   | タイミング      |                                                     | 351 |

| 13.4          | 出力負   | 負荷回路       |                                                     | 354 |

|               |       |            |                                                     |     |

| <i>/</i> → ¢= |       |            |                                                     |     |

| 付録            |       |            |                                                     |     |

| A.            | 命令.   |            |                                                     |     |

|               |       | A.1        | 命令一覧                                                |     |

|               |       | A.2        | オペレーションコードマップ                                       |     |

|               |       | A.3        | 命令実行ステート数                                           |     |

| B.            | 内部 I  | I/O レジスター覧 |                                                     | 375 |

|               |       | B.1        | アドレス一覧                                              | 375 |

|               |       | B.2        | 機能一覧                                                | 379 |

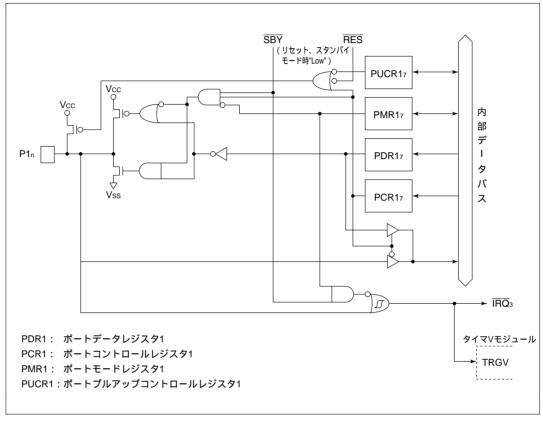

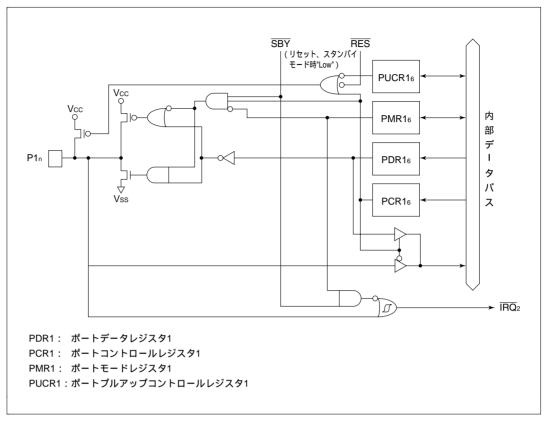

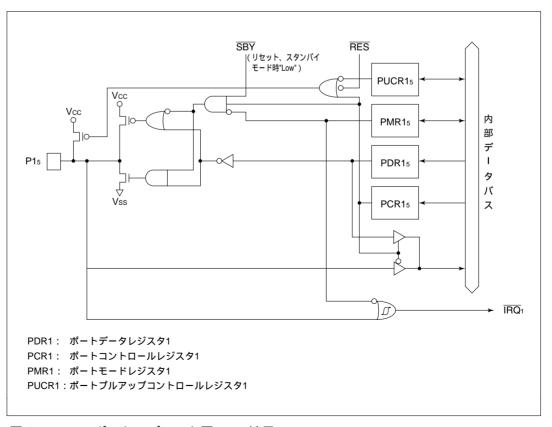

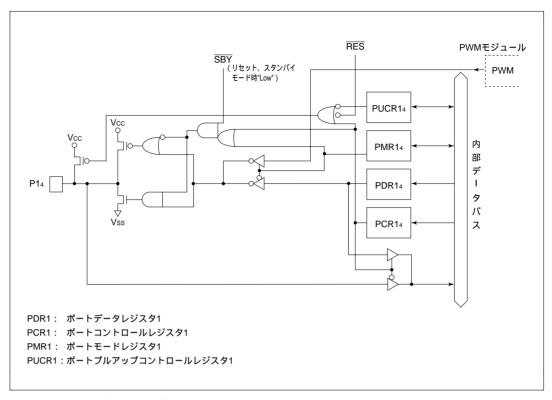

| C.            | I/O ポ | ートブロック図    |                                                     | 426 |

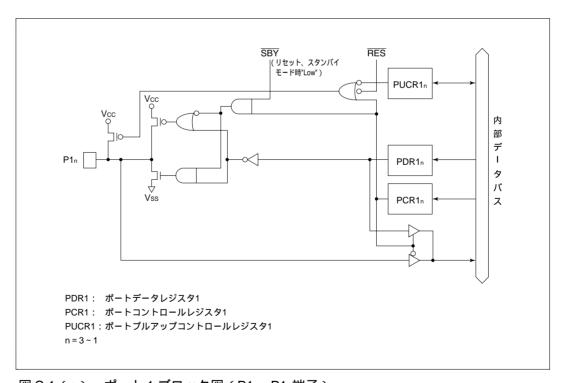

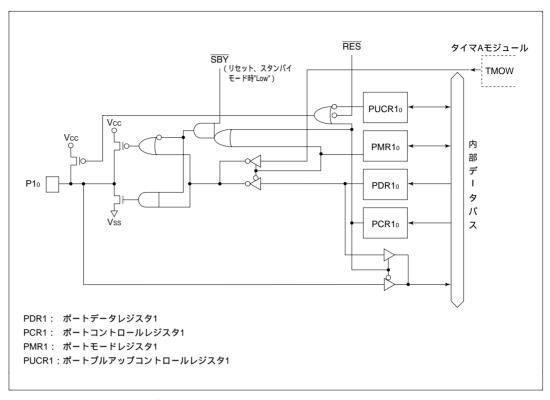

|               |       | C.1        | ポート1ブロック図                                           | 426 |

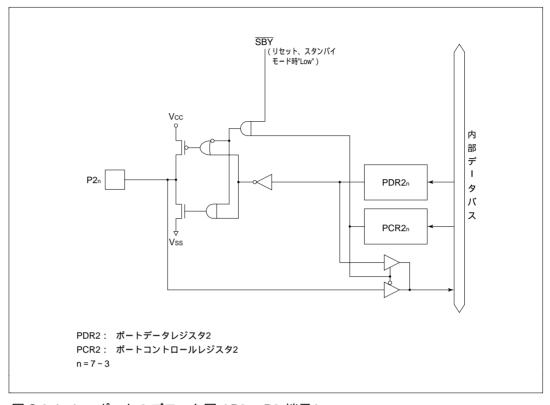

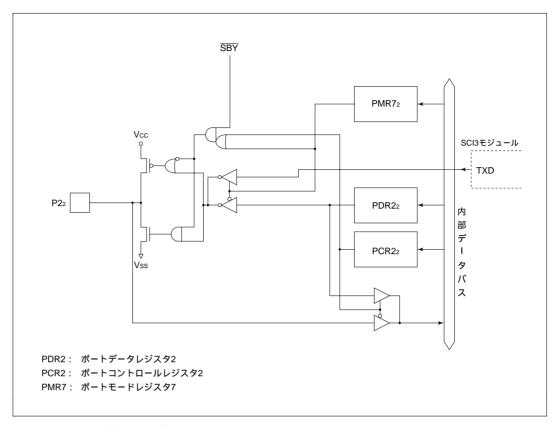

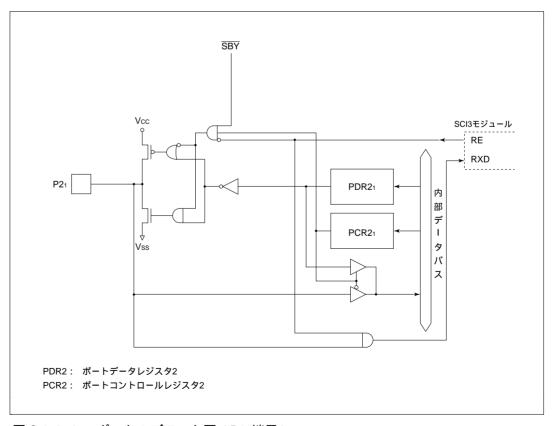

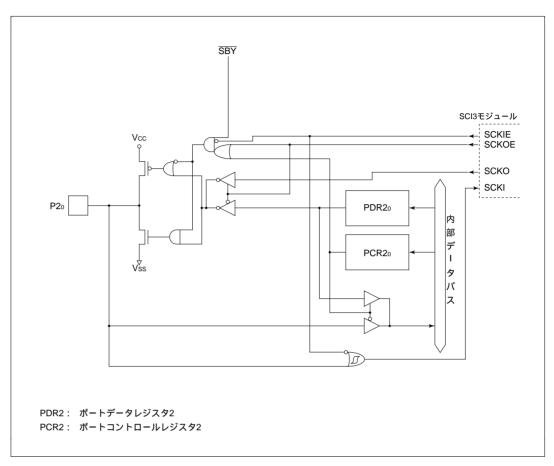

|               |       | C.2        | ポート2ブロック図                                           | 430 |

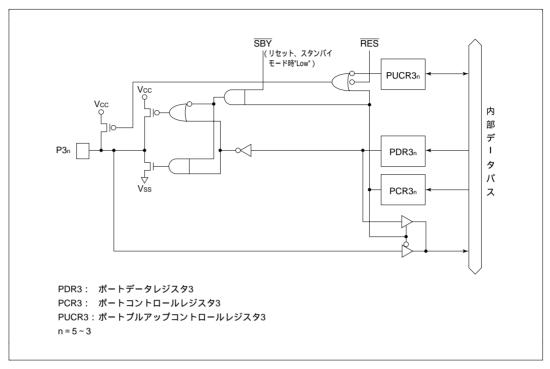

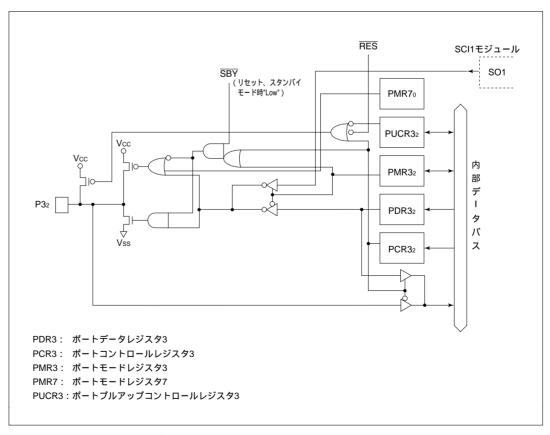

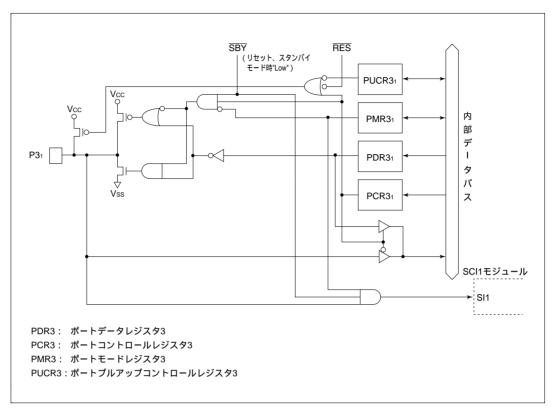

|               |       | C.3        | ポート3ブロック図                                           | 433 |

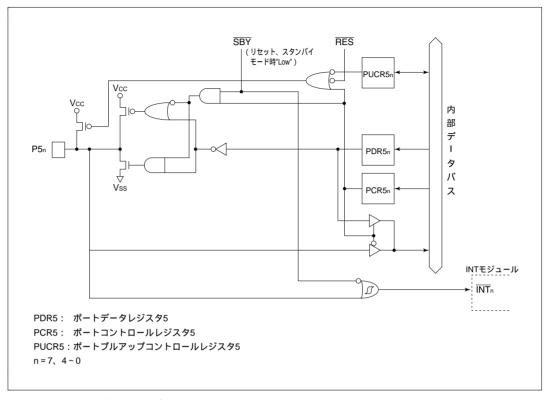

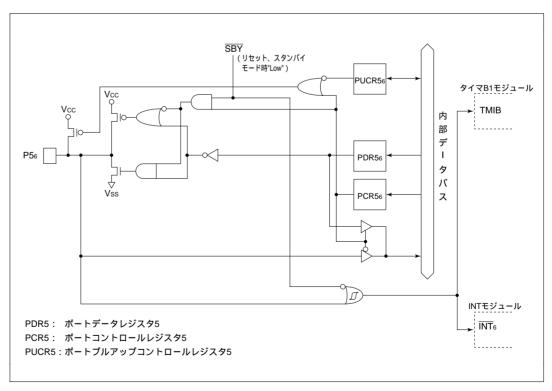

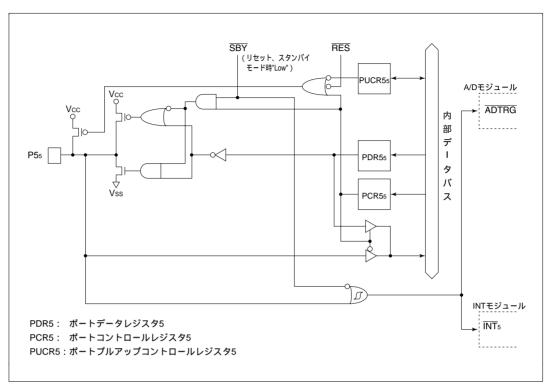

|               |       | C.4        | ポート 5 ブロック図                                         | 435 |

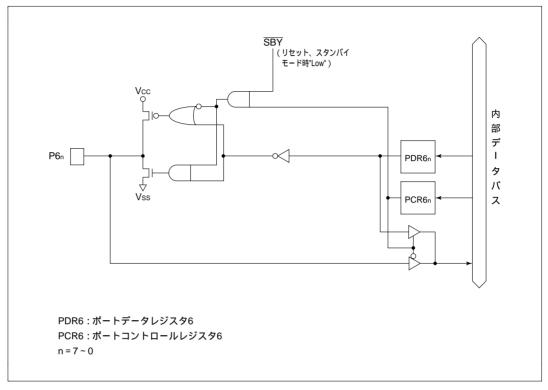

|               |       | C.5        | ポート6ブロック図                                           | 437 |

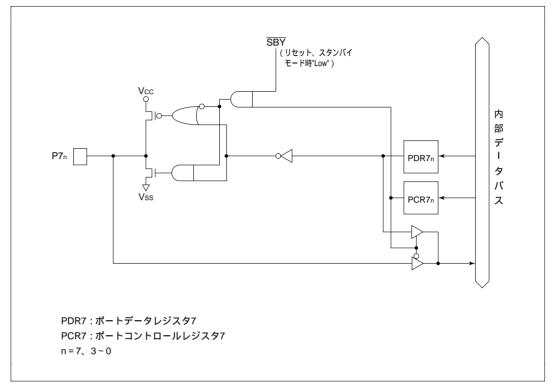

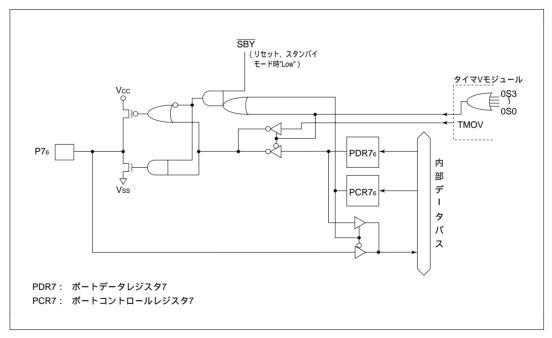

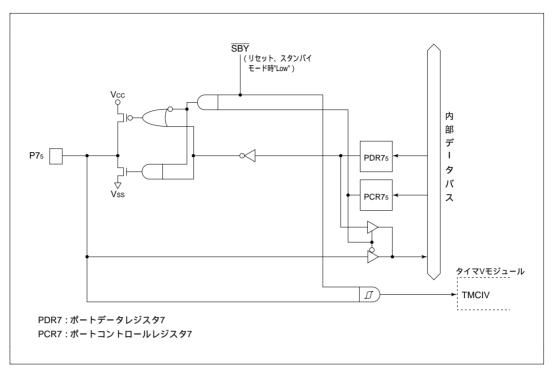

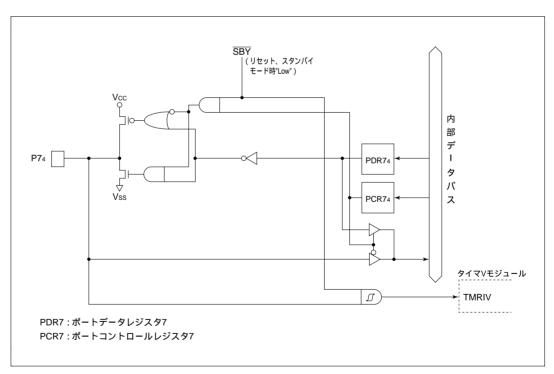

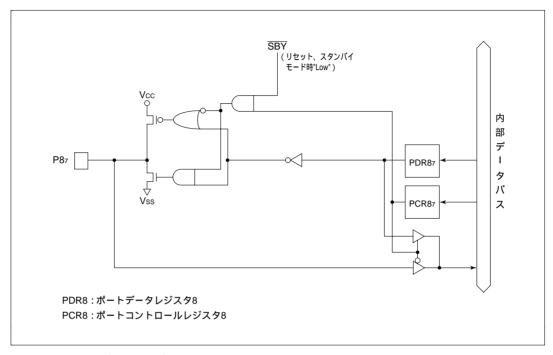

|               |       | C.6        | ポート7ブロック図                                           | 438 |

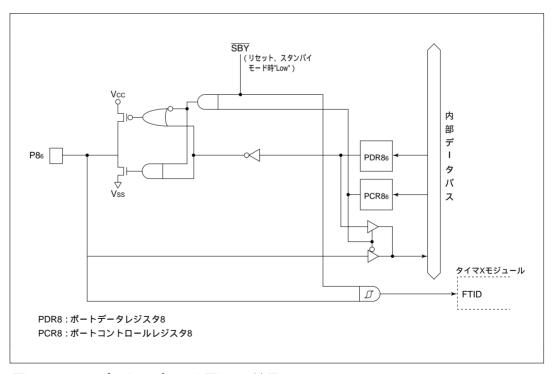

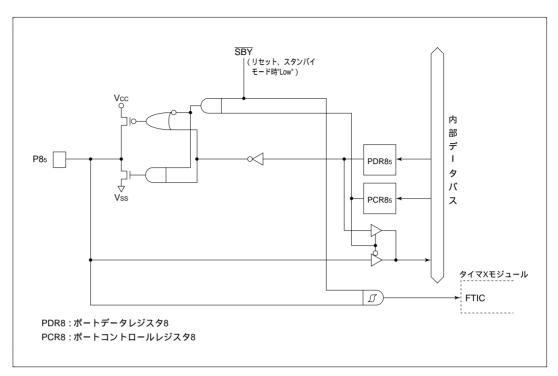

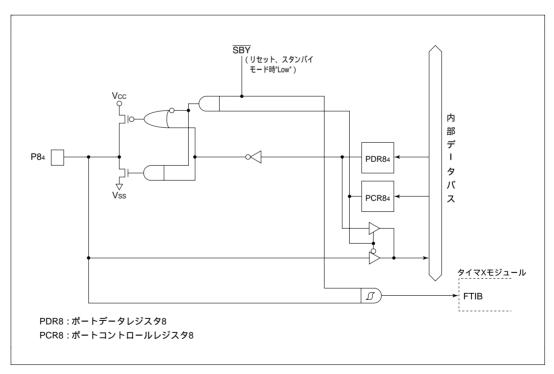

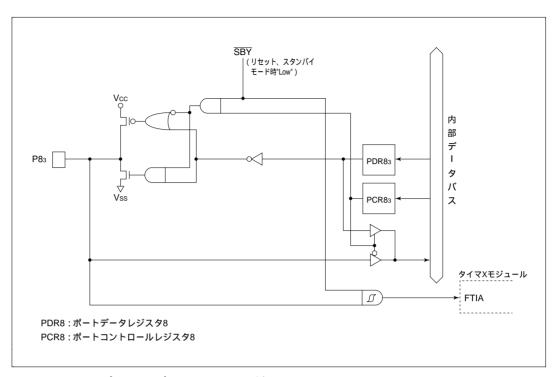

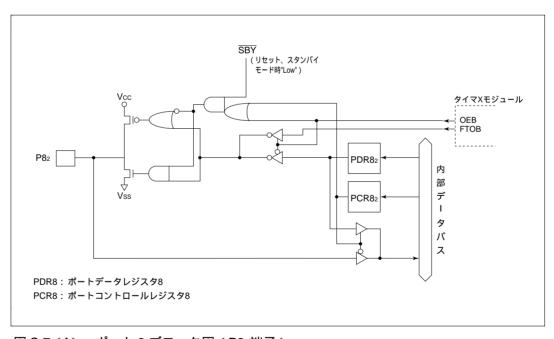

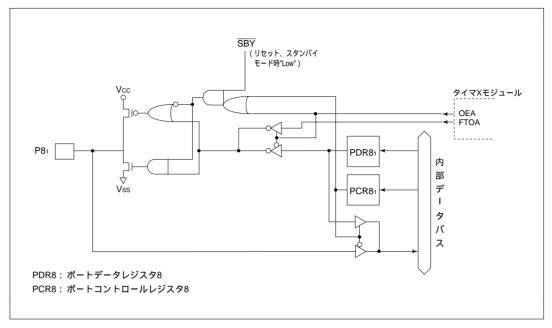

|               |       | C.7        | ポート8ブロック図                                           | 440 |

|               |       | C.8        | ポート9ブロック図                                           | 444 |

|               |       | C.9        | ポート B ブロック図                                         | 445 |

| D.            | 各処理   | 里状態におけるカ   | ペートの状態                                              | 446 |

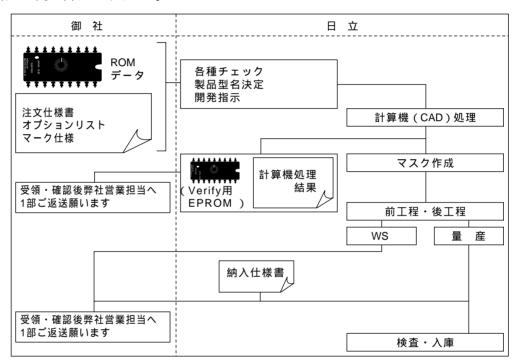

| E.            | ROM   | 発注手順       |                                                     | 447 |

|    | E.1   | ROM 書き換え品開発の流れ(発注手順)447 |

|----|-------|-------------------------|

|    | E.2   | ROM 発注時の注意事項            |

| F. | 型名一覧  |                         |

| G  | 外形寸法図 | 450                     |

# 1. 概要

# 第1章 目次

| 1.1 | 概要      |      | 3 |

|-----|---------|------|---|

| 1.2 | 内部ブロック図 |      | 6 |

|     |         |      |   |

|     |         | ピン配置 |   |

|     | 1.3.2   | 端子機能 | 9 |

## 1.1 概要

H8/300L シリーズは、高速 H8/300L CPU を核にして、システム構成に必要な周辺機能を 集積したシングルチップマイクロコンピュータ (MCU: Microcomputer Unit) です。

H8/3657 シリーズは、UART (Universal Asynchronous Receiver/Transmitter)を内蔵した H8/300L シリーズのシングルチップマイクロコンピュータで、周辺機能として、5 種類の タイマ、14 ビット PWM、2 チャネルのシリアルコミュニケーションインタフェース、A/D 変換器などを内蔵しており、高度な制御システムの組込み用マイコンに最適な構成となっています。

H8/3657 には、ユーザサイドで自由にプログラムの書込みができる PROM を内蔵した  $ZTAT^{**}$  版もあります。

H8/3657 シリーズの特長を表 1.1 に示します。

【注】 \* ZTAT は(株)日立製作所の登録商標です。

表 1.1 特長

| 項目       |                                                                                         |

|----------|-----------------------------------------------------------------------------------------|

| CPU      | 高速 H8/300L CPU                                                                          |

|          | (1)汎用レジスタ方式                                                                             |

|          | ・汎用レジスタ:8 ビット×16 本                                                                      |

|          | (16 ビット×8 本としても使用可能)                                                                    |

|          | (2) 高速演算                                                                                |

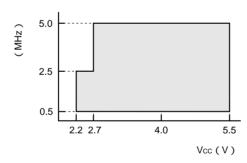

|          | ・最高動作周波数:5MHz                                                                           |

|          | ・加減算:0.4μs( = 5MHz 動作時)                                                                 |

|          | · 乗除算:2.8μs ( = 5MHz 動作時 )                                                              |

|          | ・32.768kHz サブクロックによる動作可能                                                                |

|          | (3) H8/300CPU と互換性のある命令体系                                                               |

|          | ・命令フォーマットは2バイトまたは4バイト長                                                                  |

|          | ・基本演算はレジスタ・レジスタ間で実行                                                                     |

|          | ・MOV 命令によるメモリ・レジスタ間データ転送                                                                |

|          | (4) 特長ある命令                                                                              |

|          | ・乗算命令(8 ビット×8 ビット)                                                                      |

|          | ・除算命令 ( 16 ビット÷8 ビット )                                                                  |

|          | ・ビットアキュムレータ命令                                                                           |

|          | ・レジスタ間接指定によりビット位置の指定が可能                                                                 |

| \$1.7 J. |                                                                                         |

| 割込み      | 33種類の割込み要因                                                                              |

|          | ・外部割込み要因:12 要因(IRQ <sub>3</sub> ~IRQ <sub>0</sub> 、INT <sub>7</sub> ~INT <sub>0</sub> ) |

|          | ・内部割込み要因:21 要因                                                                          |

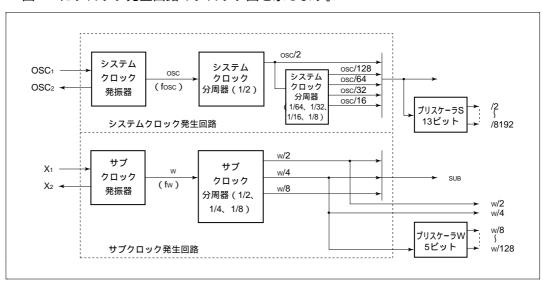

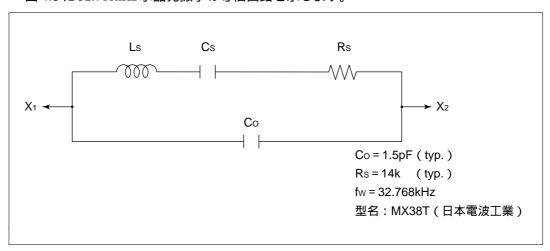

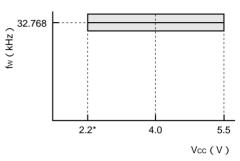

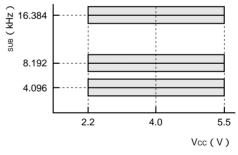

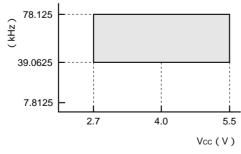

| クロック発振器  | 2種類のクロック発振器内蔵                                                                           |

|          | ・システムクロック発振器:1~10MHz                                                                    |

|          | ・サブクロック発振器 : 32.768kHz                                                                  |

| 項目       | 仕様                                 |

|----------|------------------------------------|

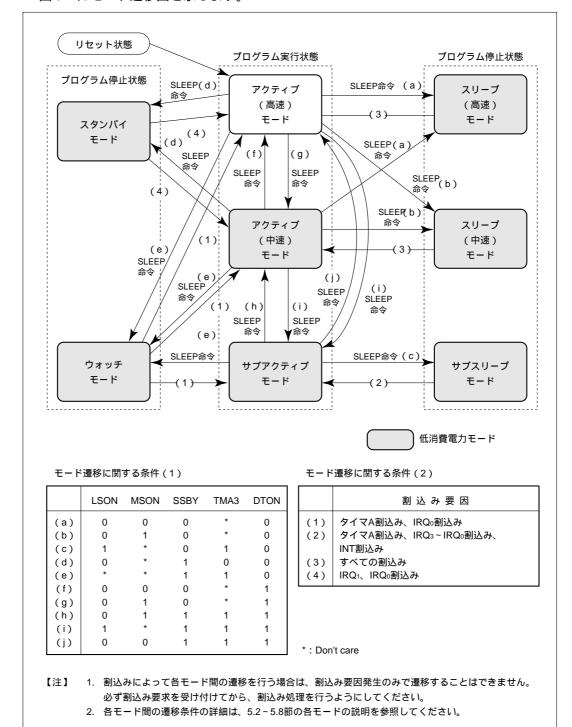

| 低消費電力モード | 7種類の低消費電力モード                       |

|          | ・スリープモード(高速)                       |

|          | ・スリープモード(中速)                       |

|          | ・スタンバイモード                          |

|          | ・ウォッチモード                           |

|          | ・サブスリープモード                         |

|          | ・サブアクティブモード                        |

|          | ・アクティブ(中速)モード                      |

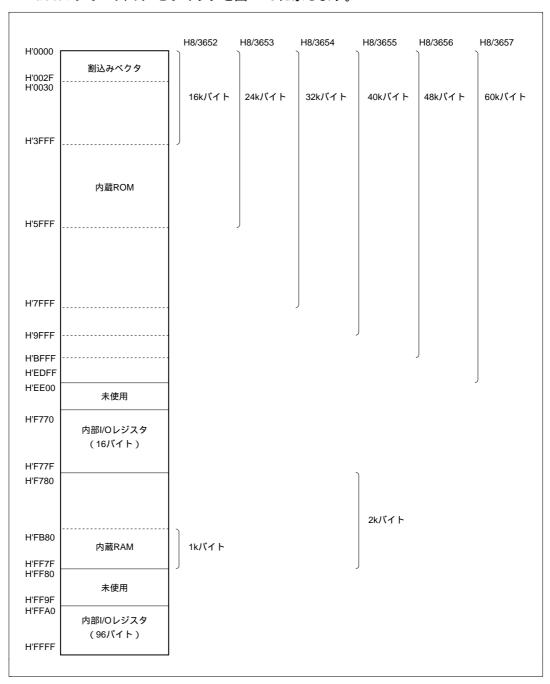

| メモリ      | 大容量メモリ内蔵                           |

|          | H8/3657・ROM:60k バイト・RAM:2k バイト     |

|          | H8/3656・ROM:48k バイト・RAM:2k バイト     |

|          | H8/3655・ROM:40k バイト・RAM:2k バイト     |

|          | H8/3654・ROM:32k バイト・RAM:1k バイト     |

|          | H8/3653・ROM:24k バイト・RAM:1k バイト     |

|          | H8/3652・ROM:16k バイト・RAM:1k バイト     |

| l/O ポート  | I/O ポート 67 本                       |

|          | ・入出力端子:59 本                        |

|          | ・入力端子 :8本                          |

| タイマ      | 5種類のタイマ内蔵                          |

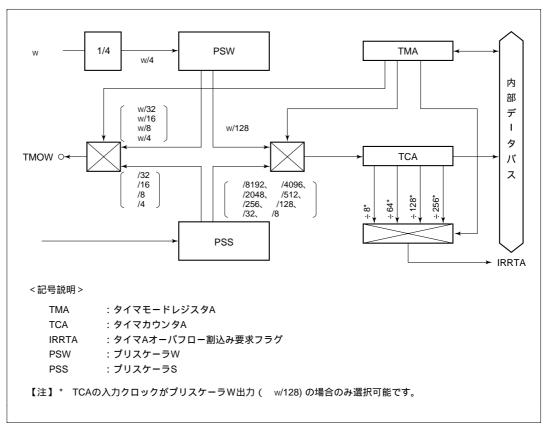

|          | (1)タイマA:8ビットのタイマ                   |

|          | ・システムクロック()*を分周した8種類の内部クロックまたは時計用  |

|          | クロック ( w)*を分周した4種類のクロックによりカウントアップ可 |

|          | 能                                  |

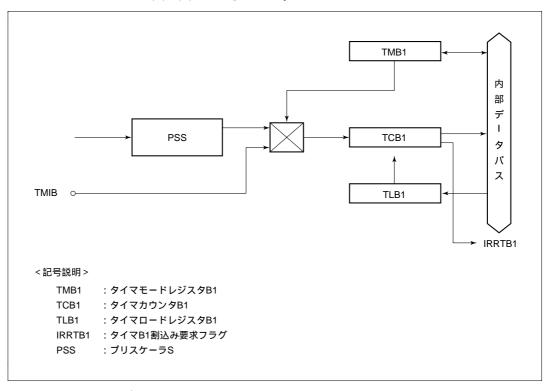

|          | (2) タイマ B1:8 ビットのタイマ               |

|          | ・7 種類の内部クロックまたは外部端子からのイベント入力によりカウン |

|          | トアップ可能                             |

|          | ・オートリロード機能可能                       |

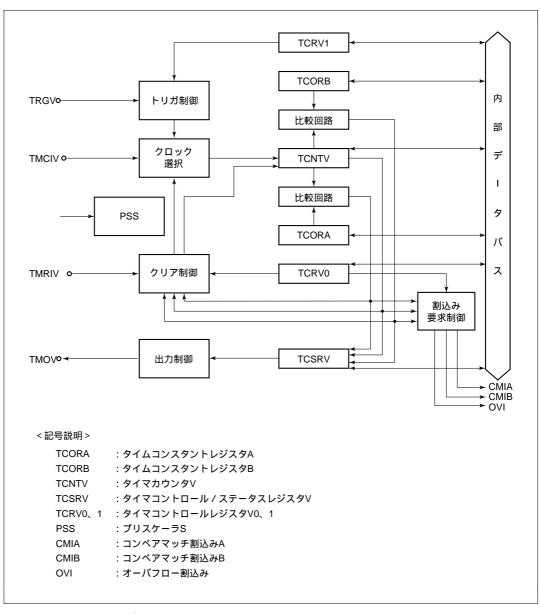

|          | (3) タイマ V:8 ビットのタイマ                |

|          | ・6 種類の内部クロックまたは外部端子からのイベント入力によりカウン |

|          | トアップ可能                             |

|          | ・コンペアマッチ機能による波形出力可能                |

|          | ・外部トリガ入力によりカウントアップ指定可能             |

|          | (4)タイマX:16ビットのタイマ                  |

|          | ・3 種類の内部クロックまたは外部端子からのイベント入力によりカウン |

|          | トアップ可能                             |

|          | ・2 本のアウトプットコンペア出力                  |

|          | ・4 本のインプットキャプチャ入力                  |

|          | (5) ウォッチドッグタイマ                     |

|          | ・8 ビットカウンタのオーバフローによりリセット信号を発生      |

【注】 \* 、 、 。の定義は「第4章 クロック発振器」を参照してください。

| 項目             | 仕様                            |                |                                        |                         |  |  |  |

|----------------|-------------------------------|----------------|----------------------------------------|-------------------------|--|--|--|

| シリアル           | 2 チャネルのシリアルコミュニケーションインタフェース内蔵 |                |                                        |                         |  |  |  |

| コミュニケーション      | (1) SCI1 : クロック同期式            |                |                                        |                         |  |  |  |

| インタフェース        | ・8 ビット / 16 ビットの転送データを選択可能    |                |                                        |                         |  |  |  |

|                | (2) SCI3:8ビットクロック同期式 / 調歩同期式  |                |                                        |                         |  |  |  |

|                |                               |                |                                        |                         |  |  |  |

|                | -                             | セッサ通信機         |                                        |                         |  |  |  |

| 14 ビット PWM     | リップル低減を                       | <b>はかったパルス</b> | .分割方式 PWM                              |                         |  |  |  |

|                | ・外部にロー                        | パスフィルタ         | を接続することで 14 ビッ                         | ト D/A 変換器として            |  |  |  |

|                | 使用可能                          |                |                                        |                         |  |  |  |

| A/D 変換器        | 抵抗ラダー方式し                      | こよる逐次比較        |                                        | 器                       |  |  |  |

|                | ・8 チャネル                       | のアナログ入力        | 力端子                                    |                         |  |  |  |

|                | • 変換時間 ·                      | 1チャネル当         | きり 31/ または 62/                         |                         |  |  |  |

|                |                               |                |                                        |                         |  |  |  |

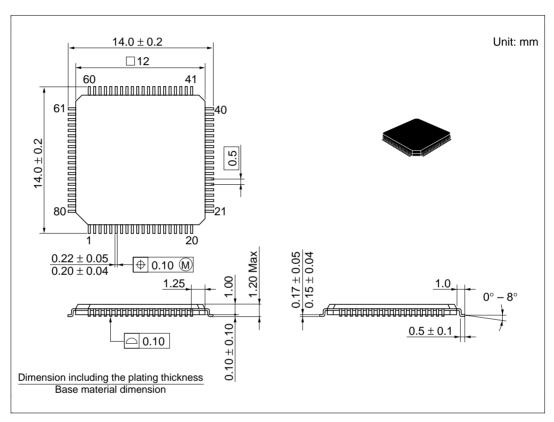

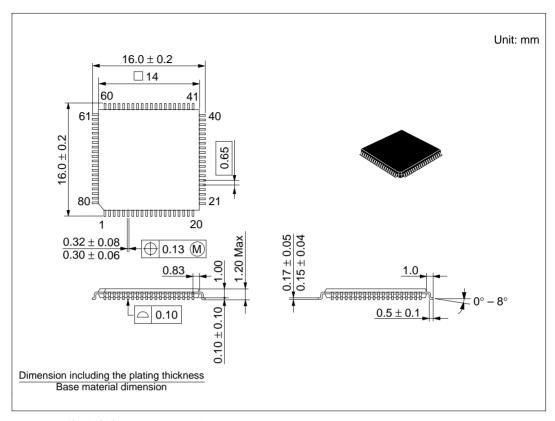

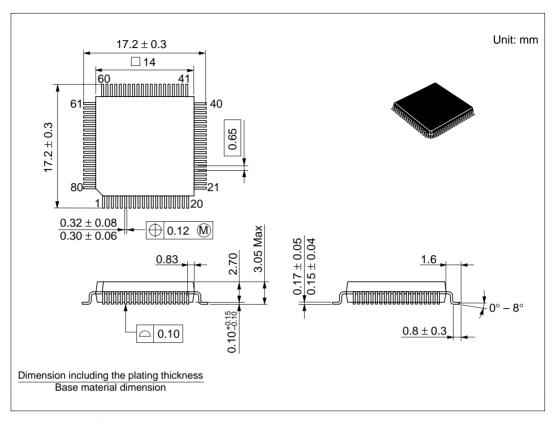

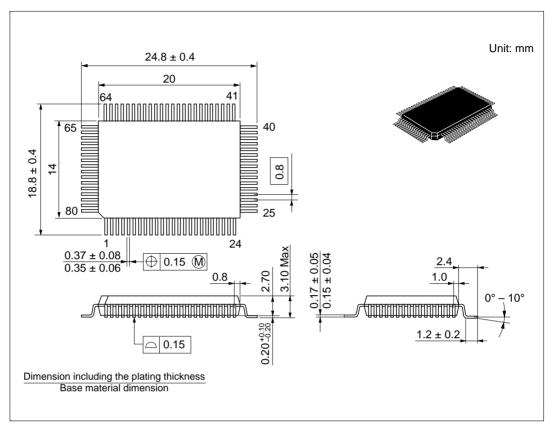

| ACHI D I D D D |                               | 型 名  ZTAT®版    | - パッケ <b>ー</b> ジ                       | ROM / RAM<br>サイズ        |  |  |  |

|                | マスクROM版<br>HD6433657W         | HD6473657W     | 80ピン TQFP ( TFP-80C )                  | 917                     |  |  |  |

|                | HD6433657X                    | HD6473657X     | 80ピン TQFP (TFP-80F)                    | <br>ROM 60kバイト          |  |  |  |

|                | HD6433657H                    | HD6473657H     | 80ピン QFP (FP-80A)                      | RAM 2kバイト               |  |  |  |

|                | HD6433657F                    | HD6473657F     | 80ピン QFP (FP-80B)                      |                         |  |  |  |

|                | HD6433656W                    | _              | 80ピン TQFP (TFP-80C)                    |                         |  |  |  |

|                | HD6433656X                    | _              | 80ピン TQFP (TFP-80F)                    | ─ ROM 48kバイト            |  |  |  |

|                | HD6433656H                    | _              | 80ピン QFP (FP-80A)                      | RAM 2kバイト               |  |  |  |

|                | HD6433656F                    | _              | 80ピン QFP (FP-80B)                      |                         |  |  |  |

|                | HD6433655W                    | _              | 80ピン TQFP (TFP-80C)                    |                         |  |  |  |

|                | HD6433655X                    | _              | 80ピン TQFP (TFP-80F)                    | ROM 40kバイト              |  |  |  |

|                | HD6433655H                    | _              | 80ピン QFP (FP-80A)                      | RAM 2kバイト               |  |  |  |

|                | HD6433655F                    | _              | 80ピン QFP (FP-80B)                      |                         |  |  |  |

|                | HD6433654W                    | _              | 80ピン TQFP ( TFP-80C )                  |                         |  |  |  |

|                | HD6433654X                    | _              | 80ピン TQFP ( TFP-80F )                  | ROM 32kバイト              |  |  |  |

|                | HD6433654H                    | _              | 80ピン QFP (FP-80A)                      | RAM 1kバイト               |  |  |  |

|                | HD6433654F                    | _              | 80ピン QFP (FP-80B)                      |                         |  |  |  |

|                | HD6433653W                    | _              | 80ピン TQFP (TFP-80C)                    |                         |  |  |  |

|                | HD6433653X                    | _              | 80ピン TQFP (TFP-80F)                    | ROM 24kバイト              |  |  |  |

|                | HD6433653H                    | _              | 80ピン QFP (FP-80A)                      | RAM 1kバイト               |  |  |  |

|                | HD6433653F                    | _              | 80ピン QFP (FP-80B)                      |                         |  |  |  |

|                | HD6433652W                    | _              | 80ピン TQFP (TFP-80C)                    | POM 401/11° 4           |  |  |  |

|                | HD6433652X                    | _              | 80ピン TQFP (TFP-80F)                    | ROM 16kバイト<br>RAM 1kバイト |  |  |  |

|                | HD6433652H<br>HD6433652F      |                | 80ピン QFP (FP-80A)<br>80ピン QFP (FP-80B) | - NAIVI IK/\1 F         |  |  |  |

|                | UD0433052F                    |                | 00 L 7 QFF (FF-80B)                    |                         |  |  |  |

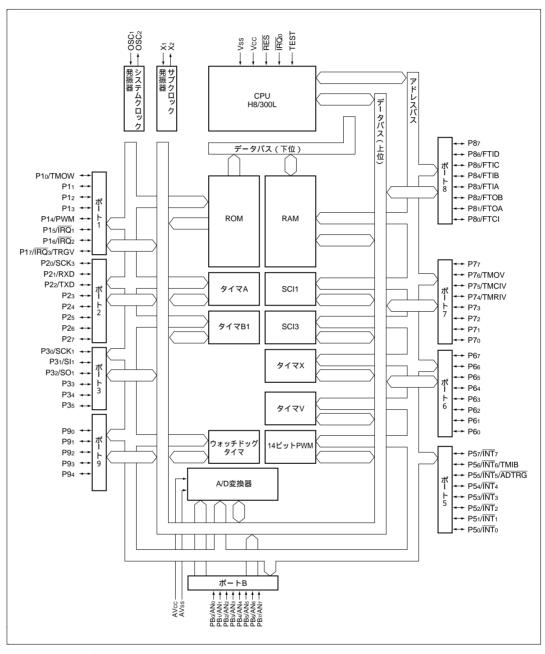

# 1.2 内部ブロック図

H8/3657 シリーズの内部ブロック図を図 1.1 に示します。

図 1.1 内部ブロック図

## 1.3 端子説明

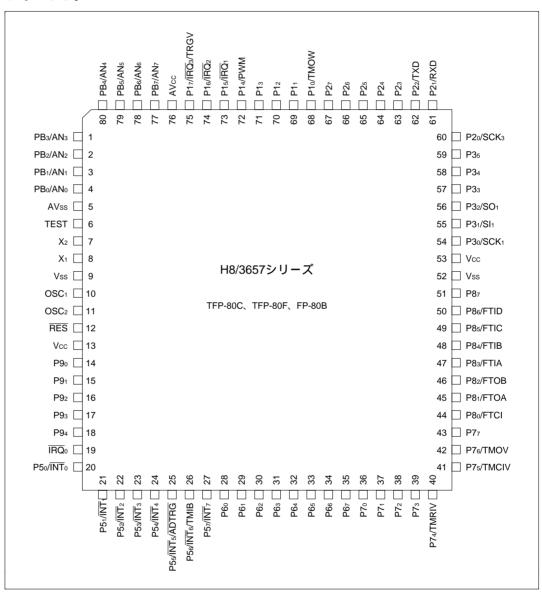

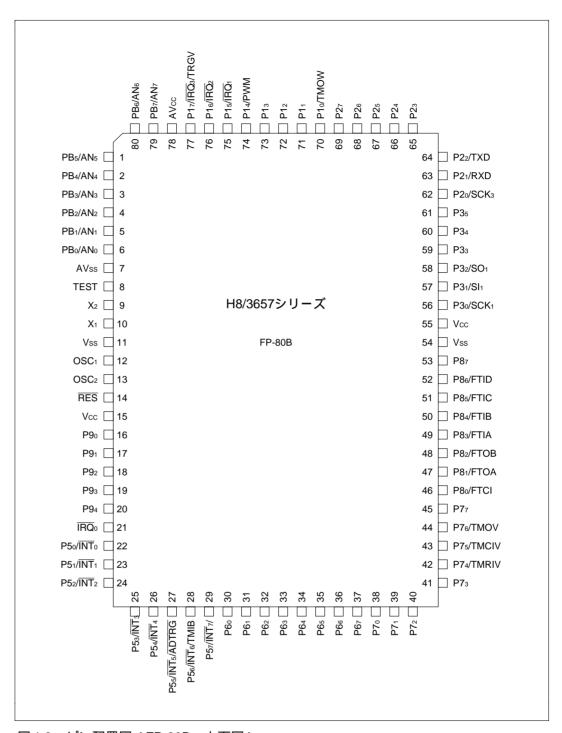

## 1.3.1 ピン配置

H8/3657 シリーズのピン配置図を図 1.2( TFP-80C、TFP-80F、FP-80A )、図 1.3( FP-80B ) に示します。

図 1.2 ピン配置図 (TFP-80C、TFP-80F、FP-80A:上面図)

図 1.3 ピン配置図 (FP-80B:上面図)

## 1.3.2 端子機能

各端子の機能について表 1.2 に示します。

表 1.2 端子機能

|      |                                          | ピン番号    |        |     |                                      |  |

|------|------------------------------------------|---------|--------|-----|--------------------------------------|--|

| 分類   | 記号                                       | TFP-80C | FP-80B | 入出力 | 機能                                   |  |

|      |                                          | TFP-80F |        |     |                                      |  |

|      |                                          | FP-80A  |        |     |                                      |  |

| 電源   | V <sub>cc</sub>                          | 13、53   | 15、55  | 入力  | 電源                                   |  |

|      |                                          |         |        |     | V <sub>○○</sub> 端子は、全端子、システムの電源(+5V) |  |

|      |                                          |         |        |     | に接続してください。                           |  |

|      | V <sub>SS</sub>                          | 9、52    | 11、54  | 入力  | <u>グランド</u>                          |  |

|      |                                          |         |        |     | V <sub>ss</sub> 端子は、全端子、システムの電源(0V)に |  |

|      |                                          |         |        |     | 接続してください。                            |  |

|      | AV <sub>CC</sub>                         | 76      | 78     | 入力  | アナログ電源                               |  |

|      |                                          |         |        |     | A/D 変換器用電源端子です。A/D 変換器を使用<br>        |  |

|      |                                          |         |        |     | しない場合、システムの電源(+5V)に接続                |  |

|      |                                          |         |        |     | してください。                              |  |

|      | AV <sub>ss</sub>                         | 5       | 7      | 入力  | <u>アナロググランド</u>                      |  |

|      |                                          |         |        |     | A/D 変換器用グランド端子です。システムの電              |  |

|      |                                          |         |        |     | 源(OV)に接続してください。                      |  |

| クロック | OSC <sub>1</sub>                         | 10      | 12     | 入力  | 水晶発振子またはセラミック発振子を接続し                 |  |

|      |                                          |         |        |     | ます。また、外部クロックを入力することも                 |  |

|      | OSC <sub>2</sub>                         | 11      | 13     | 出力  | できます。接続例については「第4章 クロ                 |  |

|      |                                          |         |        |     | ック発振器」を参照してください。                     |  |

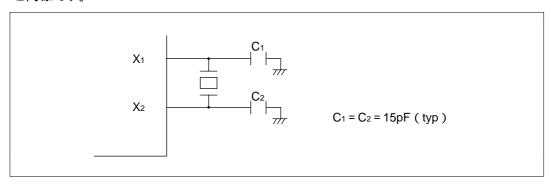

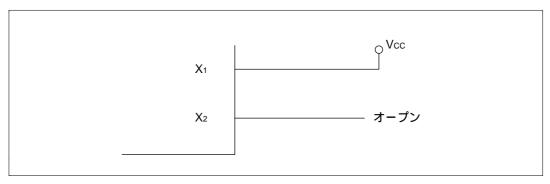

|      | X <sub>1</sub>                           | 8       | 10     | 入力  | 32.768kHz の水晶発振子を接続します。接続            |  |

|      |                                          |         |        |     | 例については「第4章 クロック発振器」を                 |  |

|      | X <sub>2</sub>                           | 7       | 9      | 出力  | 参照してください。                            |  |

| システム | RES                                      | 12      | 14     | 入力  | リセット                                 |  |

| 制御   |                                          |         |        |     | この端子を"Low"レベルにすると、リセット状              |  |

|      |                                          |         |        |     | 態になります。                              |  |

|      | TEST                                     | 6       | 8      | 入力  | テスト端子                                |  |

|      |                                          |         |        |     | ユーザは、使用できません。                        |  |

|      |                                          |         |        |     | V <sub>ss</sub> 電位に接地してください。         |  |

| 割込み  | $\overline{IRQ}_{\scriptscriptstyle{0}}$ | 19      | 21     | 入力  | IRQ 割込み要求 0~3                        |  |

|      | ĪRQ₁                                     | 73      | 75     |     | 立上がりエッジセンス / 立下がりエッジセン               |  |

|      | $\overline{IRQ}_2$                       | 74      | 76     |     | スを選択可能な外部割込み入力端子です。                  |  |

|      | $\overline{IRQ}_3$                       | 75      | 77     |     |                                      |  |

|     |                                     | ピン番号                         |         |     |                                                                        |

|-----|-------------------------------------|------------------------------|---------|-----|------------------------------------------------------------------------|

| 分類  | 記号                                  | TFP-80C<br>TFP-80F<br>FP-80A | FP-80B  | 入出力 | 機能                                                                     |

| 割込み | INT <sub>7</sub> ∼ INT <sub>0</sub> | 27 ~ 20                      | 29 ~ 22 | 入力  | INT割込み要求 0~7<br>立上がりエッジセンス / 立下がりエッジセンスを選択可能な外部割込み入力端子です。              |

| タイマ | TMOW                                | 68                           | 70      | 出力  | <u>クロック出力</u><br>タイマ A 出力回路により生成された波形の出<br>力端子です。                      |

|     | TMIB                                | 26                           | 28      | 入力  | タイマ B1 イベント入力<br>タイマ B1 のカウンタに入力するイベント入力<br>端子です。                      |

|     | TMOV                                | 42                           | 44      | 出力  | <u>タイマ∨出力</u><br>タイマ∨アウトプットコンペア機能により生<br>成された波形の出力端子です。                |

|     | TMCIV                               | 41                           | 43      | 入力  | <u>タイマ∨イベント入力</u><br>タイマ∨のカウンタに入力するイベント入力<br>端子です。                     |

|     | TMRIV                               | 40                           | 42      | 入力  | <u>タイマ∨カウンタリセット</u><br>タイマ∨のカウンタリセットの入力端子で<br>す。                       |

|     | TRGV                                | 75                           | 77      | 入力  | <u>タイマ∨カウンタ開始トリガ入力</u><br>タイマ∨のカウンタ開始トリガ、およびリア<br>ルタイム出力ポートのトリガ入力端子です。 |

|     | FTCI                                | 44                           | 46      | 入力  | タイマ X クロック入力<br>タイマ X のカウンタに入力する外部クロック<br>入力端子です。                      |

|     | FTOA                                | 45                           | 47      | 出力  | タイマ X アウトプットコンペア A 出力<br>タイマ X のアウトプットコンペア A の出力端<br>子です。              |

|     | FTOB                                | 46                           | 48      | 出力  | タイマ X アウトプットコンペア B 出力<br>タイマ X のアウトプットコンペア B の出力端<br>子です。              |

|     | FTIA                                | 47                           | 49      | 入力  | タイマ X インプットキャップチャ A 入力<br>タイマ X のインプットキャップチャ A の入力<br>端子です。            |

|       |                                   | ピン番号    |         |     |                             |  |

|-------|-----------------------------------|---------|---------|-----|-----------------------------|--|

| 分類    | 記号                                | TFP-80C | FP-80B  | 入出力 | 機能                          |  |

|       |                                   | TFP-80F |         |     |                             |  |

|       |                                   | FP-80A  |         |     |                             |  |

| タイマ   | FTIB                              | 48      | 50      | 入力  | <u>タイマXインプットキャップチャB入力</u>   |  |

|       |                                   |         |         |     | タイマXのインプットキャップチャBの入力        |  |

|       |                                   |         |         |     | 端子です。                       |  |

|       | FTIC                              | 49      | 51      | 入力  | <u>タイマXインプットキャップチャC入力</u>   |  |

|       |                                   |         |         |     | タイマ X のインプットキャップチャ C の入力    |  |

|       |                                   |         |         |     | 端子です。                       |  |

|       | FTID                              | 50      | 52      | 入力  | タイマ X インプットキャップチャ D 入力      |  |

|       |                                   |         |         |     | タイマXのインプットキャップチャDの入力        |  |

|       |                                   |         |         |     | 端子です。                       |  |

| 14 ビッ | PWM                               | 72      | 74      | 出力  | <u>14 ビット PWM 出力</u>        |  |

| ⊦ PWM |                                   |         |         |     | 14 ビット PWM により生成された波形の出力    |  |

|       |                                   |         |         |     | 端子です。                       |  |

| I/O   | PB <sub>7</sub> ~ PB <sub>0</sub> | 77 ~ 80 | 79、80   | 入力  | <u>ポートB</u>                 |  |

| ポート   |                                   | 1 ~ 4   | 1~6     |     | 8 ビットの入力端子です。               |  |

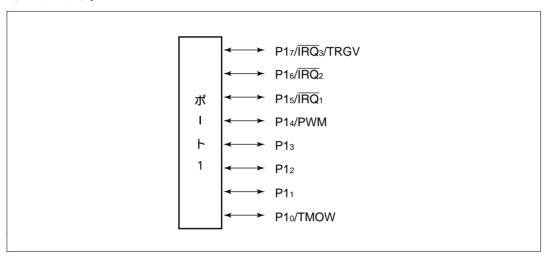

|       | P1 <sub>7</sub> ~ P1 <sub>0</sub> | 75 ~ 68 | 77 ~ 70 | 入出力 | <u>ポート1</u>                 |  |

|       |                                   |         |         |     | 8 ビットの入出力端子です。ポートコントロー      |  |

|       |                                   |         |         |     | ルレジスタ1 ( PCR1 ) によって、1 ビットご |  |

|       |                                   |         |         |     | とに入出力を指定できます。               |  |

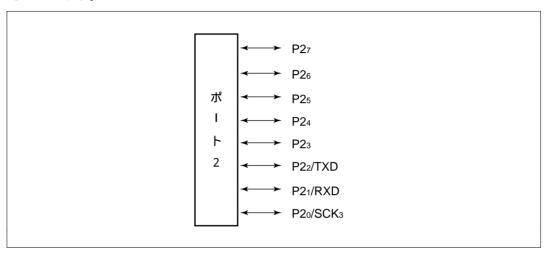

|       | P2 <sub>7</sub> ~ P2 <sub>0</sub> | 67 ~ 60 | 69 ~ 62 | 入出力 | <u>ポート 2</u>                |  |

|       |                                   |         |         |     | 8 ビットの入出力端子です。 ポートコントロー     |  |

|       |                                   |         |         |     | ルレジスタ2( PCR2 ) によって、1 ビットご  |  |

|       |                                   |         |         |     | とに入出力を指定できます。               |  |

|       | P3 <sub>5</sub> ~ P3 <sub>0</sub> | 59 ~ 54 | 61 ~ 56 | 入出力 | <u>ポート3</u>                 |  |

|       |                                   |         |         |     | 6 ビットの入出力端子です。 ポートコントロー     |  |

|       |                                   |         |         |     | ルレジスタ3( PCR3 ) によって、1 ビットご  |  |

|       |                                   |         |         |     | とに入出力を指定できます。               |  |

|       | P5 <sub>7</sub> ~ P5 <sub>0</sub> | 27 ~ 20 | 29 ~ 22 | 入出力 | <u>ポート 5</u>                |  |

|       |                                   |         |         |     | 8 ビットの入出力端子です。 ポートコントロー     |  |

|       |                                   |         |         |     | ルレジスタ 5(PCR5)によって、1 ビットご    |  |

|       |                                   |         |         |     | とに入出力を指定できます。               |  |

|       | P6 <sub>7</sub> ~ P6 <sub>0</sub> | 35 ~ 28 | 37 ~ 30 | 入出力 | <u>ポート 6</u>                |  |

|       |                                   |         |         |     | 8 ビットの入出力端子です。 ポートコントロー     |  |

|       |                                   |         |         |     | ルレジスタ6(PCR6)によって、1 ビットご     |  |

|       |                                   |         |         |     | とに入出力を指定できます。               |  |

|               |                                   | ピン番号                         |              |     |                                                                       |

|---------------|-----------------------------------|------------------------------|--------------|-----|-----------------------------------------------------------------------|

| 分類            | 記号                                | TFP-80C<br>TFP-80F<br>FP-80A | FP-80B       | 入出力 | 機能                                                                    |

| I/O<br>ポート    | P7 <sub>7</sub> ~ P7 <sub>0</sub> | 43 ~ 36                      | 45 ~ 38      | 入出力 | ポート 7<br>8 ビットの入出力端子です。ポートコントロールレジスタ 7(PCR7)によって、1 ビットごとに入出力を指定できます。  |

|               | P8 <sub>7</sub> ~ P8 <sub>0</sub> | 51 ~ 44                      | 53 ~ 46      | 入出力 | ポート8<br>8 ビットの入出力端子です。ポートコントロールレジスタ8 (PCR8)によって、1 ビットごとに入出力を指定できます。   |

|               | P9 <sub>4</sub> ~ P9 <sub>0</sub> | 18 ~ 14                      | 20 ~ 16      | 入出力 | ポート 9<br>5 ビットの入出力端子です。ポートコントロールレジスタ 9 (PCR9)によって、1 ビットごとに入出力を指定できます。 |

| シリアルコミュニ      |                                   | 55                           | 57           | 入力  | <u>SCI1 受信データ入力</u><br>SCI1 のデータ入力端子です。                               |

| ケーションインタ      |                                   | 56                           | 58           | 出力  | SCI1 送信データ出力<br>SCI1 のデータ出力端子です。                                      |

| フェース<br>(SCI) | SCK₁                              | 54                           | 56           | 入出力 | SCI1 クロック入出力<br>SCI1 のクロック入出力端子です。                                    |

|               | RXD                               | 61                           | 63           | 入力  | <u>SCI3 受信データ入力</u><br>SCI3 のデータ入力端子です。                               |

|               | TXD                               | 62                           | 64           | 出力  | SCI3 送信データ出力<br>SCI3 のデータ出力端子です。                                      |

|               | SCK <sub>3</sub>                  | 60                           | 62           | 入出力 | <u>SCI3 クロック入出力</u><br>SCI3 のクロック入出力端子です。                             |

| A/D<br>変換器    | AN <sub>7</sub> ~                 | 77 ~ 80<br>1 ~ 4             | 79、80<br>1~6 | 入力  | アナログ入力 (チャネル 7~チャネル 0)<br>A/D 変換器へのアナログデータ入力端子で<br>す。                 |

|               | ADTRG                             | 25                           | 27           | 入力  | <u>A/D 変換器トリガ入力</u><br>A/D 変換器の外部トリガ入力端子です。                           |

# 2. CPU

# 第2章 目次

| 2.1 | 概要       |                | 15 |

|-----|----------|----------------|----|

|     | 2.1.1    | 特長             | 15 |

|     | 2.1.2    | アドレス空間         | 15 |

|     | 2.1.3    | レジスタ構成         | 16 |

| 2.2 | 各レジスタの説明 |                | 17 |

|     | 2.2.1    | 汎用レジスタ         | 17 |

|     | 2.2.2    | コントロールレジスタ     | 17 |

|     | 2.2.3    | CPU 内部レジスタの初期値 | 19 |

| 2.3 | データ構成    |                | 20 |

|     | 2.3.1    | 汎用レジスタのデータ構成   | 21 |

|     | 2.3.2    | メモリ上でのデータ構成    | 22 |

| 2.4 | アドレッシングモ | ード             | 23 |

|     | 2.4.1    | アドレッシングモード     | 23 |

|     | 2.4.2    | 実効アドレスの計算方法    | 25 |

| 2.5 | 命令セット    |                | 29 |

|     | 2.5.1    | データ転送命令        | 31 |

|     | 2.5.2    | 算析演算命令         | 33 |

|     | 2.5.3    | 論理演算命令         | 34 |

|     | 2.5.4    | シフト命令          | 34 |

|     | 2.5.5    | ビット操作命令        | 35 |

|     | 2.5.6    | 分岐命令           | 39 |

|     | 2.5.7    | システム制御命令       | 41 |

|     | 2.5.8    | ブロック転送命令       | 42 |

| 2.6 | 基本動作タイミン | グ              | 43 |

|     | 2.6.1    | 内蔵メモリ(RAM、ROM) | 43 |

|     | 2.6.2    | 内蔵周辺モジュール      | 44 |

| 2.7 | CPU の状態  |                | 46 |

#### 2. CPU

|     | 2.7.1    | 概要                | 46 |

|-----|----------|-------------------|----|

|     | 2.7.2    | プログラム実行状態         | 47 |

|     | 2.7.3    | プログラム停止状態         | 47 |

|     | 2.7.4    | 例外処理状態            | 47 |

| 2.8 | メモリマップ   |                   | 48 |

|     | 使用上の注意事項 |                   | 49 |

|     | 2.9.1    | データアクセスに関する注意事項   | 49 |

|     | 2.9.2    | ビット操作命令使用上の注意事項   | 51 |

|     | 293      | FEPMOV 命今使田上の注音事項 | 57 |

## 2.1 概要

H8/300L CPU は、8 ビット×16 本(または 16 ビット×8 本)の汎用レジスタ、ならびに高速動作に適した簡潔な命令セットを備えた高速 CPU です。

### 2.1.1 特長

H8/300L CPUには、次の特長があります。

#### 汎用レジスタ方式

- ・8 ビット×16本(16 ビット×8 本としても使用可能)

- 55 種類の基本命令

- ・乗除算命令

- ・強力なビット操作命令

- 8種類のアドレッシングモード

- ・レジスタ直接

- ・レジスタ間接

- ・ディスプレースメント付レジスタ間接

- ・ポストインクリメント / プリデクリメントレジスタ間接

- ・絶対アドレス

- ・イミディエイト

- ・プログラムカウンタ相対

- ・メモリ間接

64k バイトのアドレス空間

#### 高速動作

- ・頻出命令をすべて2~4ステートで実行

- ・高速演算

8/16 ビットレジスタ間加減算 0.4 us\*

8×8ビット乗算 2.8μs\*

16÷8 ビット除算 2.8μs\*

【注】 \* 数値は、 = 5MHz 時のもの

#### 低消費電力動作

・SLEEP命令により低消費電力動作可能

### 2.1.2 アドレス空間

H8/300L CPU がサポートするアドレス空間は、プログラムコードとデータ領域合計で最大 64k バイトです。

メモリマップの詳細は「2.8 メモリマップ」を参照してください。

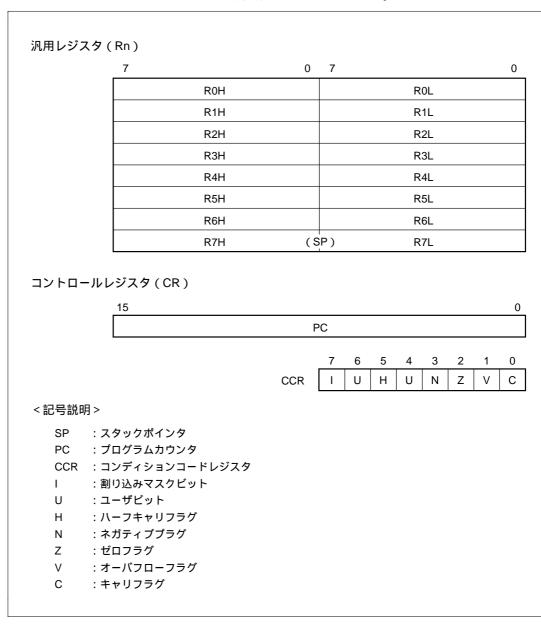

### 2.1.3 レジスタ構成

H8/300L CPU の内部レジスタ構成を図 2.1 に示します。これらのレジスタは、汎用レジスタとコントロールレジスタの 2 つに分類することができます。

図 2.1 CPU 内部レジスタ構成

## 2.2 各レジスタの説明

## 2.2.1 汎用レジスタ

汎用レジスタは、すべて同じ機能をもっており、データレジスタ、アドレスレジスタの 区別なく使用できます。

データレジスタとして使用する場合は、8 ビットレジスタとして上位(R7H~R0H)と下位(R7L~R0L)を別々に使用することも、また 16 ビットレジスタ(R7~R0)として使用することもできます。

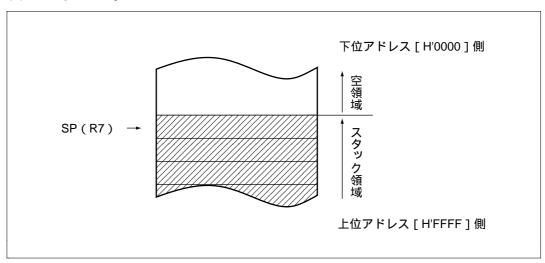

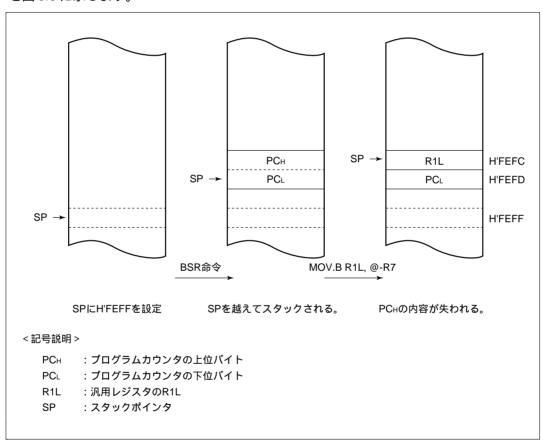

アドレスレジスタとして使用する場合は、16 ビットレジスタ (R7~R0) として使用します。レジスタ R7 には、汎用レジスタとしての機能に加えて、スタックポインタ (SP) としての機能が割り当てられており、例外処理やサブルーチンコールなどで暗黙的に使用されます。このとき、SP は常にスタック領域の先頭を指しています。スタックの状態を図 2.2 に示します。

図 2.2 スタックの状態

### 2.2.2 コントロールレジスタ

コントロールレジスタには、16 ビットのプログラムカウンタ (PC) と 8 ビットのコンディションコードレジスタ (CCR) があります。

#### (1) プログラムカウンタ(PC)

16 ビットのカウンタで、CPU が次に実行する命令のアドレスを示しています。CPU の命令は、すべて 16 ビット (ワード)を単位としているため、最下位ビットは無効です(命令コードのリード時には最下位ビットは"0"とみなされます)。

### (2) コンディションコードレジスタ (CCR)

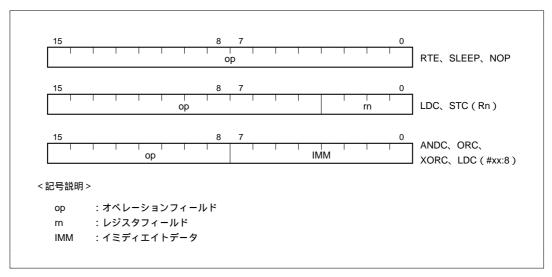

8 ビットのレジスタで、CPUの内部状態を示しています。割込みマスクビット(I)とハーフキャリ(H)、ネガティブ(N)、ゼロ(Z)、オーバフロー(V)、キャリ(C)の各フラグを含む8 ビットで構成されています。これらのビットは、ソフトウェア(LDC、STC、ANDC、ORC、XORC命令)でリード/ライトできます。N、Z、V、C の各フラグは、条件分岐命令(Bcc)で使用されます。

#### ビット7:割込みマスクビット(1)

本ビットが"1"にセットされると、割込みがマスクされます。例外処理の実行が開始されたときに"1"にセットされます。本ビットはソフトウェアによりリード/ライトできます。割込みマスクビットの詳細については「3.3 割込み」を参照してください。

#### ビット6:ユーザビット(U)

ユーザが自由に使用できるビットです。

#### ビット5:ハーフキャリフラグ(H)

ADD.B、ADDX.B、SUB.B、SUBX.B、CMP.B、NEG.B 命令の実行により、ビット 3 にキャリまたはボローが生じたとき"1"にセットされ、生じなかったとき"0"にクリアされます。DAA および DAS 命令実行時に、暗黙的に使用されます。ADD.W、SUB.W、CMP.W 命令ではビット 11 にキャリまたはボローが生じたとき"1"にセットされ、生じなかったとき"0"にクリアされます。

#### ビット4:ユーザビット(U)

ユーザが自由に使用できるビットです。

#### ビット3:ネガティブフラグ(N)

データの最上位ビットを符号ビットとみなし、最上位ビットの値を格納します。

#### ビット2:ゼロフラグ(Z)

データがゼロのとき"1"にセットされ、ゼロ以外のとき"0"にクリアされます。

#### ビット1:オーバフローフラグ(V)

算術演算命令の実行により、オーバフローが生じたとき"1"にセットされます。それ以外のとき"0"にクリアされます。

ビット0:キャリフラグ(C)

演算の実行により、キャリが生じたとき"1"にセットされ、生じなかったとき"0"にクリアされます。キャリには次の種類があります。

- 加算結果のキャリ

- ・減算結果のボロー

- ・シフト/ローテートのキャリ

また、キャリフラグには、ビットアキュムレータ機能があり、ビット操作命令で使用されます。

なお、命令によってはフラグが変化しない場合があります。

各命令ごとのフラグの変化については、「H8/300L シリーズ プログラミングマニュアル」を参照してください。

#### 2.2.3 CPU 内部レジスタの初期値

リセット例外処理によって、CPU内部レジスタのうち、PC はベクタアドレス (H'0000) のロードにより初期化され、CCR の I ビットは"1"にセットされますが、汎用レジスタおよび CCR の他のビットは初期化されません。レジスタ R7 (SP) の初期値も不定です。したがって、リセット直後に、R7 の初期化を行ってください。

## 2.3 データ構成

H8/300L CPU は、1 ビット、4 ビット BCD、8 ビット (バイト)、16 ビット (ワード) のデータを扱うことができます。1 ビットデータはビット操作命令で扱われ、オペランド データ (バイト)の第 n ビット (n = 0、1、2、......7)という形式でアクセスされます。

バイトデータは、ADDS、SUBS 以外の演算命令で扱われます。また、ワードデータは、MOV.W、ADD.W、SUB.W、CMP.W、ADDS、SUBS、MULXU(8 ビット×8 ビット)、DIVXU(16 ビット÷8 ビット)命令で扱われます。

なお、DAA および DAS の 10 進補正命令では、バイトデータは 2 桁の 4 ビット BCD データとなります。

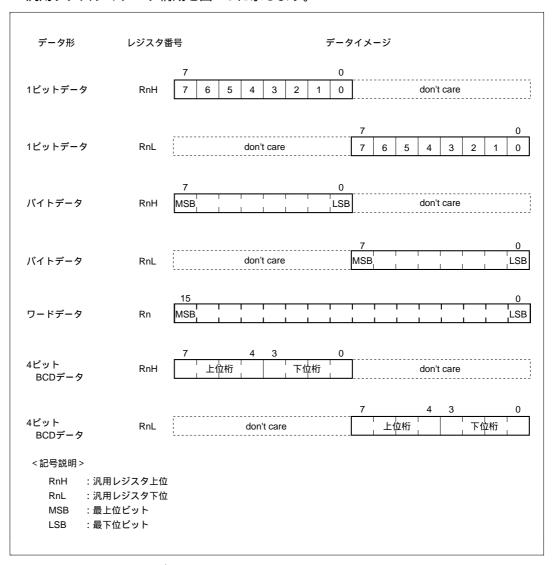

## 2.3.1 汎用レジスタのデータ構成

汎用レジスタのデータ構成を図2.3に示します。

図 2.3 汎用レジスタのデータ構成

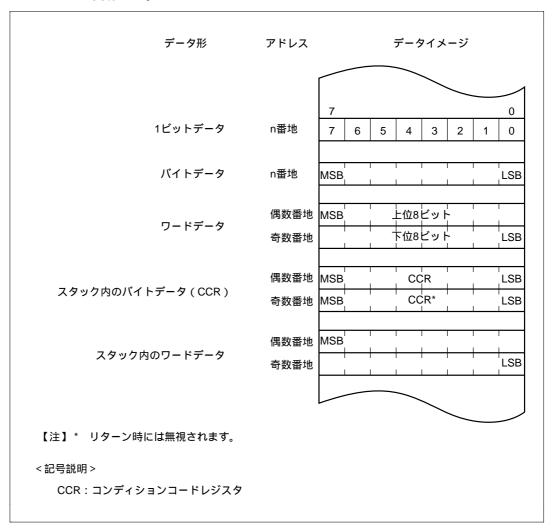

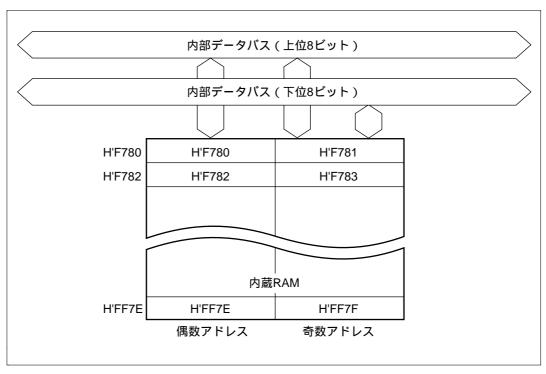

## 2.3.2 メモリ上でのデータ構成

メモリ上でのデータ構成を図 2.4 に示します。H8/300L CPU は、メモリ上のワードデータをアクセスすることができます (MOV.W 命令)が、偶数番地から始まるワードデータに限定されます。奇数番地から始まるワードデータをアクセスした場合、アドレスの最下位ビットは"0"とみなされ、1番地前から始まるワードデータをアクセスします。命令コードについても同様です。

図 2.4 メモリ上でのデータ構成

なお、R7 をアドレスレジスタとして使用し、スタックをアクセスするときは、必ずワードサイズでアクセスしてください。また、CCR は、ワードデータとして上位8ビット、下位8ビットに同じ値が格納され、リターン時には、下位8ビットは無視されます。

# 2.4 アドレッシングモード

# 2.4.1 アドレッシングモード

H8/300L CPU は、表 2.1 に示すように、8 種類のアドレッシングモードをサポートしています。命令ごとに、使用できるアドレッシングモードは異なります。

表 2.1 アドレッシングモード一覧表

| No. | アドレッシングモード        | 記号           |

|-----|-------------------|--------------|

| (1) | レジスタ直接            | Rn           |

| (2) | レジスタ間接            | @Rn          |

| (3) | ディスプレースメント付レジスタ間接 | @(d:16, Rn)  |

| (4) | ポストインクリメントレジスタ間接  | @Rn+         |

|     | プリデクリメントレジスタ間接    | @-Rn         |

| (5) | 絶対アドレス            | @aa:8/@aa:16 |

| (6) | イミディエイト           | #xx:8/#xx:16 |

| (7) | プログラムカウンタ相対       | @(d:8, PC)   |

| (8) | メモリ間接             | @@aa:8       |

#### (1) レジスタ直接 Rn

命令コードのレジスタフィールドで指定されるレジスタ(8ビットまたは16ビット)が オペランドとなります。

16 ビットレジスタを使用する命令は、MOV.W、ADD.W、SUB.W、CMP.W、ADDS、SUBS、MULXU(8ビット×8ビット)、DIVXU(16ビット÷8ビット)の各命令です。

#### (2)レジスタ間接 @Rn

命令コードのレジスタフィールドで指定されるレジスタ(16 ビット) の内容をアドレスとしてメモリ上のオペランドを指定します。

### (3) ディスプレースメント付レジスタ間接 @(d:16, Rn)

命令コードのレジスタフィールドで指定されるレジスタ(16 ビット) の内容に、命令 コードの第2ワード(第3、第4 バイト)の16 ビットディスプレースメントを加算した内 容をアドレスとして、メモリ上のオペランドを指定します。

本アドレッシングモードは、MOV命令のみで使用されます。特に、MOV.W命令では、加算結果が偶数となるようにしてください。

- (4) ポストインクリメントレジスタ間接 @Rn+/プリデクリメントレジスタ間接 @-Rn

- ・ポストインクリメントレジスタ間接 @Rn+

MOV (Load from) 命令で使用されます。

命令コードのレジスタフィールドで指定されるレジスタ(16 ビット)の内容をアドレスとして、メモリ上のオペランドを指定します。その後、レジスタの内容に1または2が加算され、加算結果がレジスタに格納されます。MOV.B命令では1、MOV.W命令では2がそれぞれ加算されます。MOV.W命令では、レジスタの内容が偶数になるようにしてください。

・プリデクリメントレジスタ間接 @-Rn

MOV (Store to) 命令で使用されます。

命令コードのレジスタフィールドで指定されるレジスタ(16 ビット)の内容から1または2を減算した内容をアドレスとして、メモリ上のオペランドを指定します。その後、減算結果がレジスタに格納されます。MOV.B命令では1、MOV.W命令では2がそれぞれ減算されます。MOV.W命令では、レジスタの内容が偶数となるようにしてください。

#### (5)絶対アドレス @aa:8/@aa:16

命令コード中に含まれる絶対アドレスで、メモリ上のオペランドを指定します。

このとき、絶対アドレスは8ビット(@aa:8)または16ビット(@aa:16)で、8ビット 絶対アドレスはMOV.B、ビット操作命令で、16ビット絶対アドレスはMOV.B、MOV.W、 JMP、JSR の各命令で使用されます。

8 ビット絶対アドレスの場合、上位 8 ビットはすべて"1" ( H'FF ) となります。したがって、アクセス範囲は 65280 ~ 65535 ( H'FF00 ~ H'FFFF ) 番地です。

#### (6) イミディエイト #xx:8/#xx:16

命令コードの第2バイト (#xx:8) または第3、第4バイト (#xx:16) を直接オペランド として使用します。#xx:16 は、MOV.W 命令のみで使用されます。

なお、ADDS および SUBS 命令では、イミディエイトデータ (1 または 2) が命令コード中に暗黙的に含まれます。ビット操作命令では、ビット番号を指定するための 3 ビットのイミディエイトデータが、命令コードの第 2 または第 4 バイトに含まれる場合があります。

#### (7) プログラムカウンタ相対 @(d:8, PC)

Bcc、BSR の各命令で使用されます。

PC の内容に、命令コードの第 2 バイトの 8 ビットディスプレースメントを加算して、 分岐アドレスを生成します。加算に際して、ディスプレースメントは 16 ビットに符号拡 張され、また加算される PC の内容は次の命令の先頭アドレスとなっていますので、分岐 可能範囲は分岐命令に対して - 126~ + 128 バイト ( - 63~ + 64 ワード)です。このとき、 加算結果が偶数となるようにしてください。

#### (8) メモリ間接 @@aa:8

JMP および JSR 命令で使用されます。

命令コードの第2バイトに含まれる8ビット絶対アドレスでメモリ上のオペランドを指定し、この内容を分岐アドレスとして分岐します。この場合、8ビット絶対アドレスの上位8ビットはすべて"0"(H'00)とされますので、分岐アドレスを格納できるのは0~255(H'0000~H'00FF)番地です。ただし、H8/300Lシリーズでは、アドレスの下位番地はベクタ領域と共通になっていますから注意してください。ベクタ領域の詳細は「3.3 割込み」を参照してください。

分岐アドレスまたは MOV.W 命令のオペランドアドレスとして奇数アドレスを指定した場合、最下位ビットは"0"とみなされ、1番地前から始まるワードデータをアクセスします (「2.3.2 メモリ上でのデータ構成」を参照してください)。

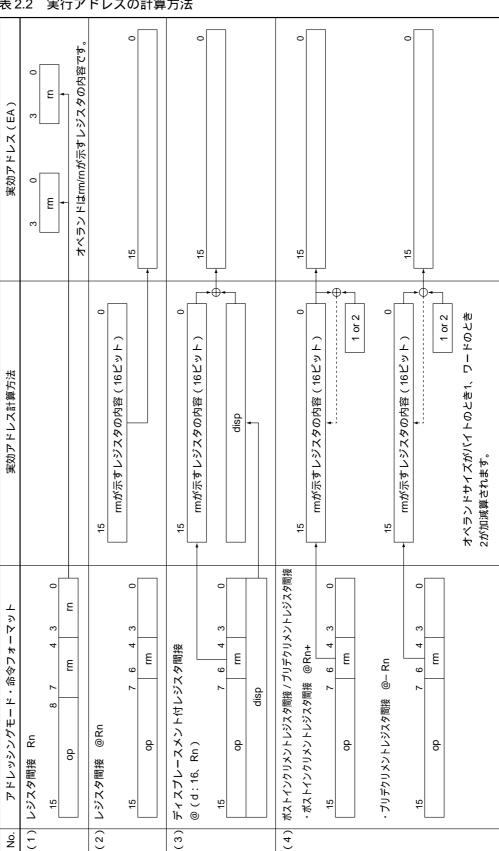

### 2.4.2 実効アドレスの計算方法

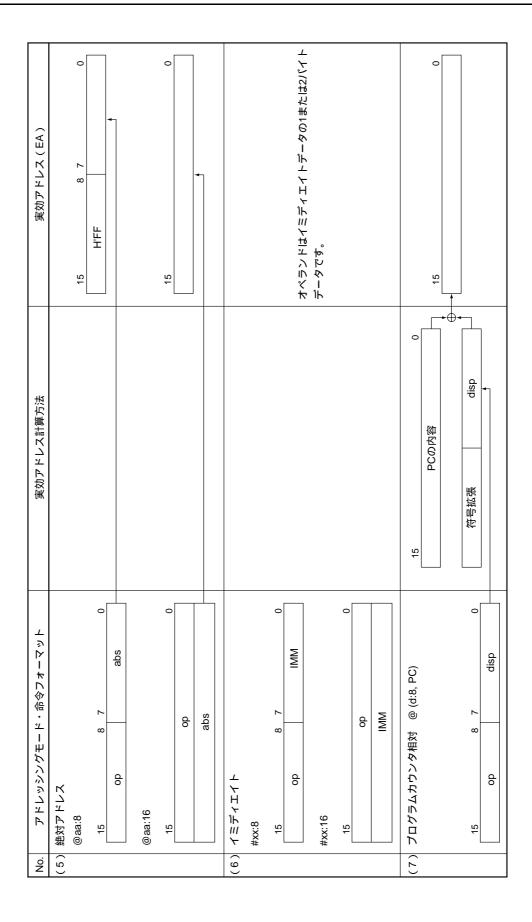

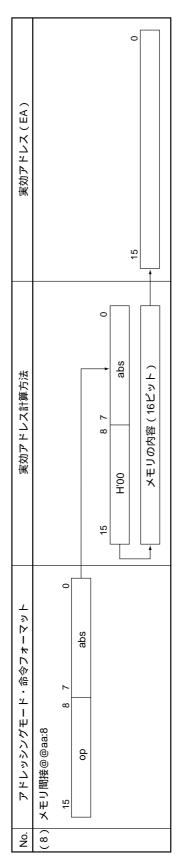

各アドレッシングモードにおける実効アドレス(EA: Effective Address)の計算法を表 2.2 に示します。

演算命令では、(1)レジスタ直接、および(6)イミディエイト(ADD.B、ADDX、SUBX、CMP.B、AND、OR、XORの各命令)が使用されます。

転送命令では、(7)プログラムカウンタ相対と(8)メモリ間接を除くすべてのアドレッシングモードが使用可能です。

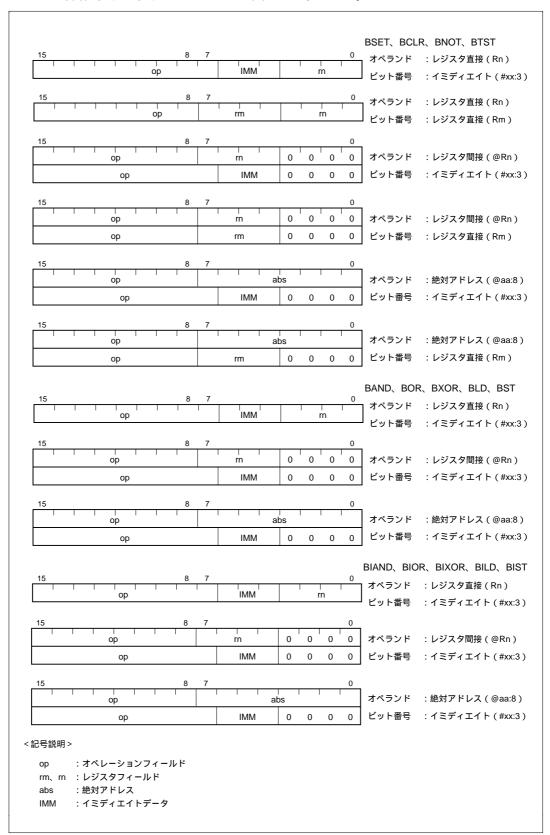

また、ビット操作命令では、オペランドの指定に(1) レジスタ直接、(2) レジスタ間接および(5) 絶対アドレス(8 ビット)が使用可能です。さらに、オペランド中のビット番号を指定するために(1) レジスタ直接(BSET, BCLR, BNOT, BTST の各命令)および(6) イミディエイト(3 ビット)が独立して使用可能です。

表 2.2 実行アドレスの計算方法

< 記号説明 >

rm、rn :レジスタフィールド op :オベレーションフィールド disp :ディスプレースメント IMM :イニディエイドデータ abs :絶対アドレス

# 2.5 命令セット

H8/300L CPU の命令は合計 55 種類あり、各命令のもつ機能によって、表 2.3 に示すように分類されます。

表 2.3 命令の分類

| 機能       | 命令                                               | 種類 |

|----------|--------------------------------------------------|----|

| データ転送命令  | MOV、POP*1、PUSH*1                                 | 1  |

| 算術演算命令   | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS, DAA, |    |

|          | DAS、MULXU、 DIVXU、 CMP、 NEG                       |    |

| 論理演算命令   | AND, OR, XOR, NOT                                | 4  |

| シフト命令    | SHAL、SHAR、SHLL、SHLR、ROTL、ROTR、ROTXL、ROTXR        | 8  |

| ビット操作命令  | BSET、BCLR、BNOT、BTST、BAND、BIAND、BOR、BIOR、         | 14 |

|          | BXOR、BIXOR、BLD、BILD、BST、BIST                     |    |

| 分岐命令     | Bcc*2, JMP, BSR, JSR, RTS                        | 5  |

| システム制御命令 | RTE、SLEEP、LDC、STC、ANDC、ORC、XORC、NOP              | 8  |

| ブロック転送命令 | EEPMOV                                           | 1  |

合計 55 種

- 【注】 \*1 POP Rn、PUSH Rn は、それぞれ MOV.W @SP+, Rn、MOV.W Rn, @-SP と同一です。 機械語についても同一です。

- \*2 Bcc は条件分岐命令の総称です。

各命令の機能について表 2.4 から表 2.11 に示します。各表で使用しているオペレーションの記号の意味は以下のとおりです。

《オペレーションの記号》

| (1) (1) フコンの旧当/    |                     |

|--------------------|---------------------|

| Rd                 | 汎用レジスタ (デスティネーション側) |

| Rs                 | 汎用レジスタ (ソース側)       |

| Rn                 | 汎用レジスタ              |

| (EAd)、 <ead></ead> | デスティネーションオペランド      |

| (EAs)、 <eas></eas> | ソースオペランド            |

| CCR                | コンディションコードレジスタ      |

| N                  | CCRのN(ネガティブ)フラグ     |

| Z                  | CCRのZ(ゼロ)フラグ        |

| V                  | CCRのV(オーバフロー)フラグ    |

| С                  | CCRのC(キャリ)フラグ       |

| PC                 | プログラムカウンタ           |

| SP                 | スタックポインタ            |

| #IMM               | イミディエイトデータ          |

| disp               | ディスプレースメント          |

| +                  | 加算                  |

| _                  | 減算                  |

| ×                  | 乗算                  |

| ÷                  | 除算                  |

|                    | 論理積                 |

|                    | 論理和                 |

| <b>⊕</b>           | 排他的論理和              |

|                    | 転送                  |

| ~                  | 反転論理(論理的補数)         |

| :3                 | 3 ビット長              |

| :8                 | 8 ビット長              |

| :16                | 16 ビット長             |

| ( ), < >           | オペランドの実効アドレスの内容     |

|                    |                     |

# 2.5.1 データ転送命令

データ転送命令の機能を表 2.4 に示します。

表 2.4 データ転送命令

| 命令   | サイズ* | 機能                                                 |

|------|------|----------------------------------------------------|

| MOV  | B/W  | (EAs) Rd、Rs (EAd)                                  |

|      |      | 汎用レジスタと汎用レジスタまたは汎用レジスタとメモリ間でデータ転送                  |

|      |      | します。また、イミディエイトデータを汎用レジスタに転送します。                    |

|      |      | ワードデータは Rn、@Rn、@(d:16, Rn)、@aa:16、#xx:16、@-Rn、@Rn+ |

|      |      | の各アドレッシングモードで扱います。 @aa:8 はバイトデータのみです。              |

|      |      | ただし、@-R7、@R7+を使用する場合は必ずワードサイズを指定してくだ               |

|      |      | ວ່າເ.                                              |

| POP  | W    | @SP+ Rn                                            |

|      |      | スタックから汎用レジスタヘデータを復帰します。                            |

|      |      | 本命令は MOV.W @SP+, Rn と同一です。                         |

| PUSH | W    | Rn @-SP                                            |

|      |      | 汎用レジスタの内容をスタックに退避します。                              |

|      |      | 本命令は MOV.W Rn, @-SP と同一です。                         |

【注】 \* サイズはオペランドサイズを示します。

B:バイト W:ワード

データアクセスに関して使用上の注意事項があります。詳細は「2.9.1 データアクセスに関する注意事項」を参照してください。

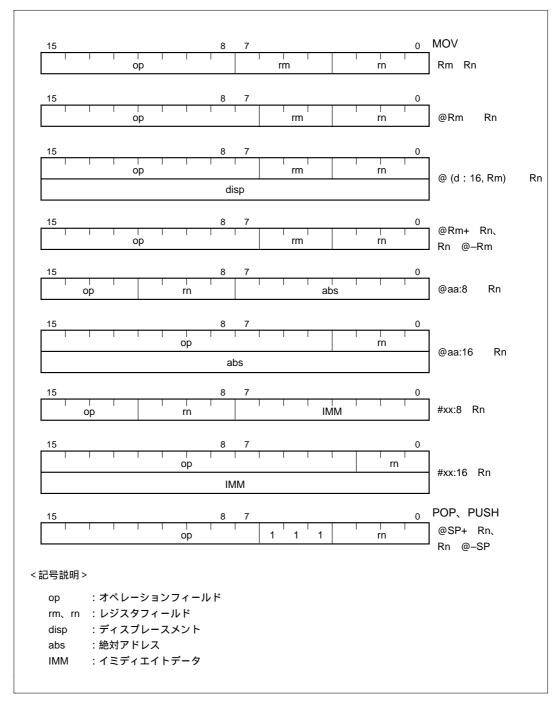

データ転送命令の命令フォーマットを図2.5に示します。

図 2.5 データ転送命令の命令フォーマット

# 2.5.2 算術演算命令

算術演算命令の機能を表 2.5 に示します。

表 2.5 算術演算命令

|       | 四次开口、 |                                                       |

|-------|-------|-------------------------------------------------------|

| 命令    | サイズ*  | 機能                                                    |

| ADD   | B/W   | $Rd \pm Rs$ $Rd$ $Rd+\#IMM$ $Rd$                      |

| SUB   |       | 汎用レジスタ間の加減算、または汎用レジスタとイミディエイトデータの加                    |

|       |       | 算を行います。汎用レジスタとイミディエイトデータの減算はできません。                    |

|       |       | ワードデータは、汎用レジスタ間の加減算のみで扱います。                           |

| ADDX  | В     | $Rd \pm Rs \pm C$ $Rd \times Rd \pm \#IMM \pm C$ $Rd$ |

| SUBX  |       | 汎用レジスタ間のキャリ付の加減算、または汎用レジスタとイミディエイト                    |

|       |       | データのキャリ付の加減算を行います。                                    |

| INC   | В     | Rd ±1 Rd                                              |

| DEC   |       | 汎用レジスタに1を加減算します。                                      |

| ADDS  | W     | Rd ±1 Rd、Rd ±2 Rd                                     |

| SUBS  |       | 汎用レジスタに1または2を加減算します。                                  |

| DAA   | В     | Rd(10 進補正) Rd                                         |

| DAS   |       | 汎用レジスタ上の加減算結果を CCR を参照して 4 ビット BCD データに補              |

|       |       | 正します。                                                 |

| MULXU | В     | Rd×Rs Rd                                              |

|       |       | 汎用レジスタ間の符号なし乗算を行います。8 ビット×8 ビット 16 ビット                |

|       |       | の演算が可能です。                                             |

| DIVXU | В     | Rd ÷ Rs Rd                                            |

|       |       | <br>  汎用レジスタ間の符号なし除算を行います。16 ビット÷8 ビット 商 8 ビ          |

|       |       | ット余り8ビットの演算が可能です。                                     |

| СМР   | B/W   | Rd-Rs、Rd-#IMM                                         |

|       |       | 汎用レジスタ間の比較、または汎用レジスタとイミディエイトデータの比較                    |

|       |       | <br> を行い、その結果を CCR に反映します。ワードデータは、汎用レジスタ間             |

|       |       | の比較のみで扱います。                                           |

| NEG   | В     | 0-Rd Rd                                               |

|       |       | <br> 汎用レジスタの内容の2の補数(算術的補数)をとります。                      |

|       | 1     |                                                       |

【注】 \* サイズはオペランドサイズを示します。

B: バイト W: ワード

# 2.5.3 論理演算命令

論理演算命令の機能を表 2.6 に示します。

表 2.6 論理演算命令

| 命令  | サイズ* | 機能                                 |

|-----|------|------------------------------------|

| AND | В    | Rd Rs Rd、Rd #IMM Rd                |

|     |      | 汎用レジスタ間の論理積、または汎用レジスタとイミディエイトデータの論 |

|     |      | 理積をとります。                           |

| OR  | В    | Rd Rs Rd、Rd #IMM Rd                |

|     |      | 汎用レジスタ間の論理和、または汎用レジスタとイミディエイトデータの論 |

|     |      | 理和をとります。                           |

| XOR | В    | Rd⊕Rs Rd、Rd⊕#IMM Rd                |

|     |      | 汎用レジスタ間の排他的論理和、または汎用レジスタとイミディエイトデー |

|     |      | タの排他的論理和をとります。                     |

| NOT | В    | ~Rd Rd                             |

|     |      | 汎用レジスタの内容の1の補数(論理的補数)をとります。        |

【注】 \* サイズはオペランドサイズを示します。

B : バイト

# 2.5.4 シフト命令

シフト命令の機能を表 2.7 に示します。

表 2.7 シフト命令

| 命令    | サイズ* | 機能                             |

|-------|------|--------------------------------|

| SHAL  | В    | Rd(シフト処理) Rd                   |

| SHAR  |      | 汎用レジスタの内容を算術的にシフトします。          |

| SHLL  | В    | Rd(シフト処理) Rd                   |

| SHLR  |      | 汎用レジスタの内容を論理的にシフトします。          |

| ROTL  | В    | Rd(ローテート処理) Rd                 |

| ROTR  |      | 汎用レジスタの内容をローテートします。            |

| ROTXL | В    | Rd(ローテート処理) Rd                 |

| ROTXR |      | 汎用レジスタの内容を、キャリフラグを含めてローテートします。 |

【注】 \* サイズはオペランドサイズを示します。

B : バイト

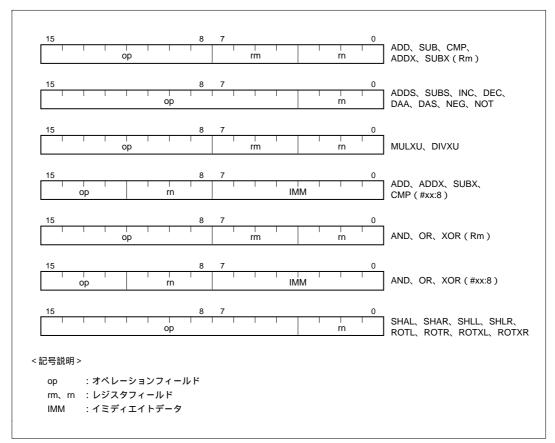

算術演算命令、論理演算命令およびシフト命令の命令フォーマットを図 2.6 に示します。

図 2.6 算術演算命令・論理演算命令・シフト命令の命令フォーマット

# 2.5.5 ビット操作命令

ビット操作命令の機能を表 2.8 に示します。

表 2.8 ビット操作命令

| 命令   | サイズ* | 機能                                    |

|------|------|---------------------------------------|

| BSET | В    | 1 (<ビット番号> of <ead> )</ead>           |

|      |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを"1"にセッ |

|      |      | トします。ビット番号は、3 ビットのイミディエイトデータまたは汎用レジ   |

|      |      | スタの内容下位3ビットで指定されます。                   |

| BCLR | В    | 0 (<ビット番号> of <ead>)</ead>            |

|      |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを"0"にクリ |

|      |      | アします。ビット番号は、3 ビットのイミディエイトデータまたは汎用レジ   |

|      |      | スタの内容下位3ビットで指定されます。                   |

| 命令    | サイズ* | 機能                                                        |

|-------|------|-----------------------------------------------------------|

| BNOT  | В    | ~(<ビット番号> of <ead>)  (&lt;ビット番号&gt; of <ead>)</ead></ead> |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを反転しま                       |

|       |      | す。ビット番号は、3 ビットのイミディエイトデータまたは汎用レジスタの                       |

|       |      | 内容下位3ビットで指定されます。                                          |

| BTST  | В    | ~(<ビット番号> of <ead>)   Z</ead>                             |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットをテスト                        |

|       |      | し、ゼロフラグに反映します。ビット番号は、3 ビットのイミディエイトデ                       |

|       |      | - タまたは汎用レジスタの内容下位3ビットで指定されます。                             |

| BAND  | В    | C (<ビット番号> of <ead>) C</ead>                              |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットとキャリフ                       |

|       |      | ラグとの論理積をとり、キャリフラグに結果を格納します。                               |

| BIAND | В    | C        〔~(<ビット番号> of <ead>)〕</ead>                      |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを反転し、キ                      |

|       |      | ャリフラグとの論理積をとり、キャリフラグに結果を格納します。                            |

|       |      | ビット番号は、3 ビットのイミディエイトデータで指定されます。                           |

| BOR   | В    | C (<ビット番号> of <ead>) C</ead>                              |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットとキャリフ                       |

|       |      | ラグとの論理和をとり、キャリフラグに結果を格納します。                               |

| BIOR  | В    | C        〔~(<ビット番号> of <ead>)〕</ead>                      |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを反転し、キ                      |

|       |      | ャリフラグとの論理和をとり、キャリフラグに結果を格納します。                            |

|       |      | ビット番号は、3 ビットのイミディエイトデータで指定されます。                           |

| BXOR  | В    | C⊕(<ビット番号> of <ead>) C</ead>                              |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットとキャリフ                       |

|       |      | ラグとの排他的論理和をとり、キャリフラグに結果を格納します。                            |

| BIXOR | В    | C⊕〔~(<ビット番号> of <ead>)〕 C</ead>                           |

|       |      | 汎用レジスタまたはメモリのオペランドの指定された 1 ビットを反転し、キ                      |

|       |      | ャリフラグとの排他的論理和をとり、キャリフラグに結果を格納します。                         |

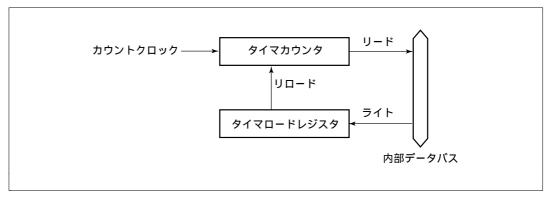

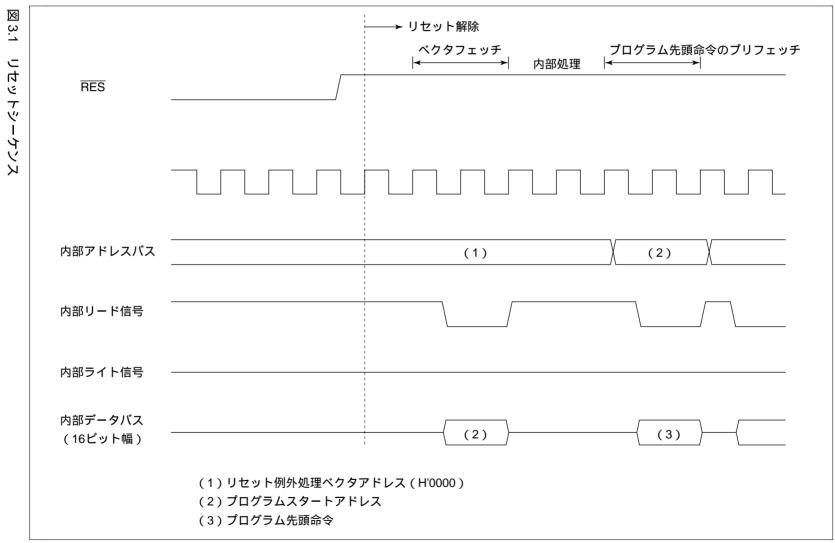

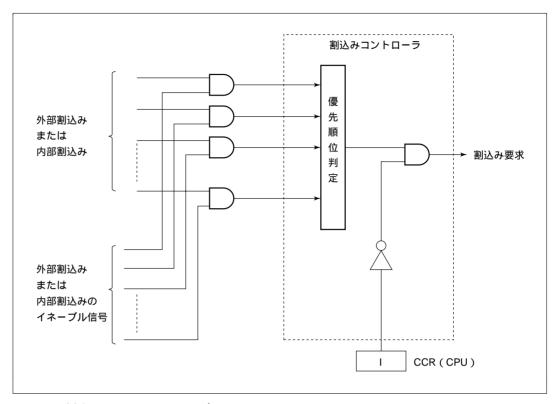

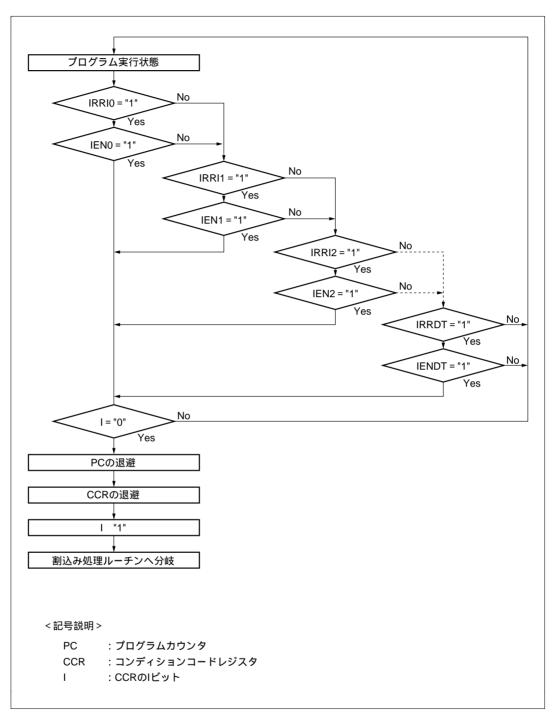

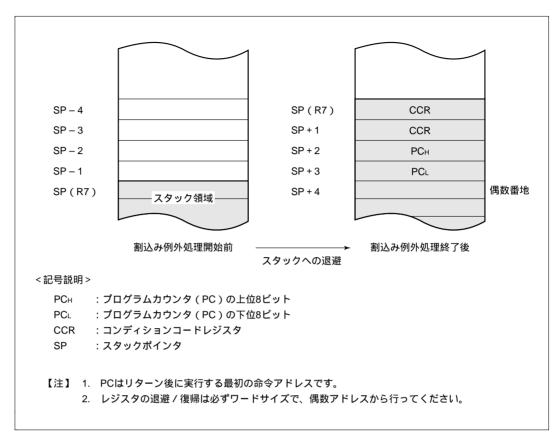

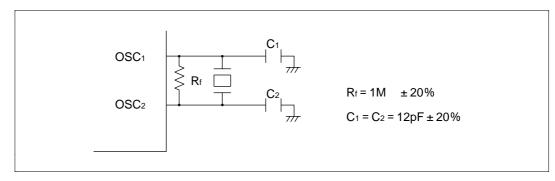

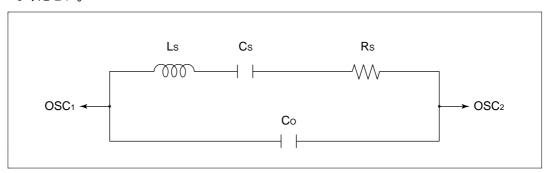

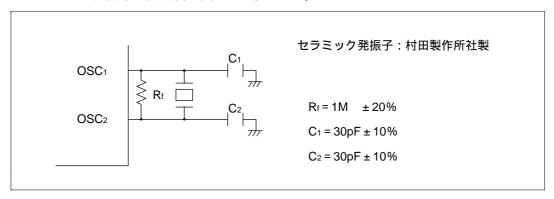

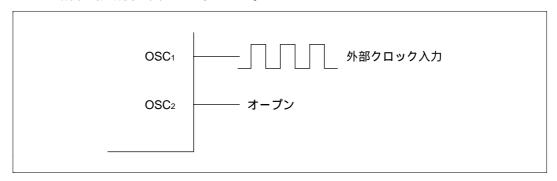

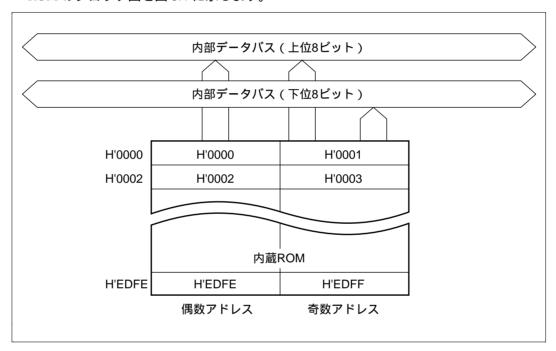

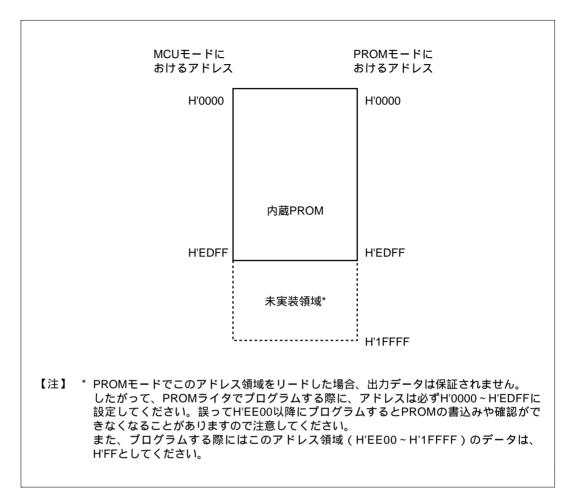

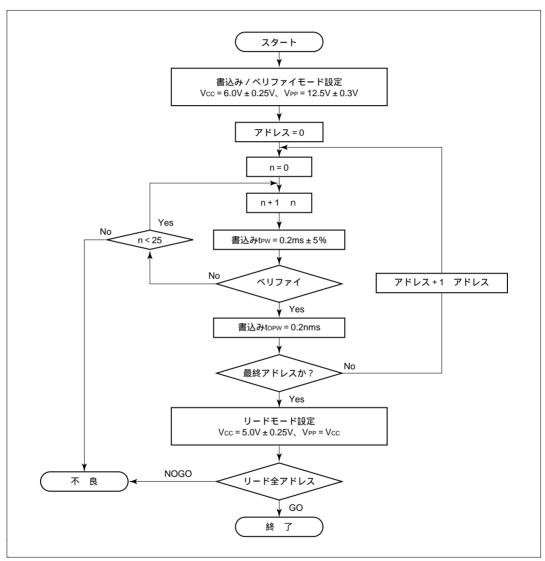

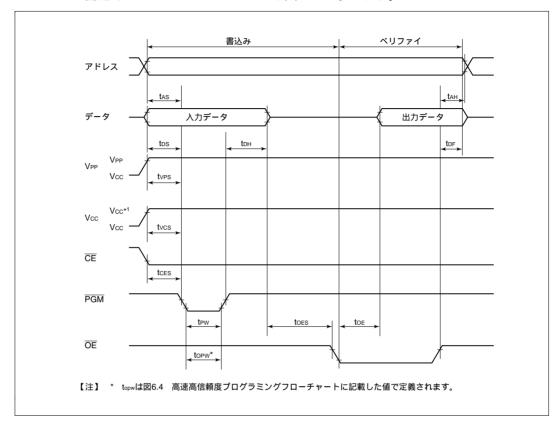

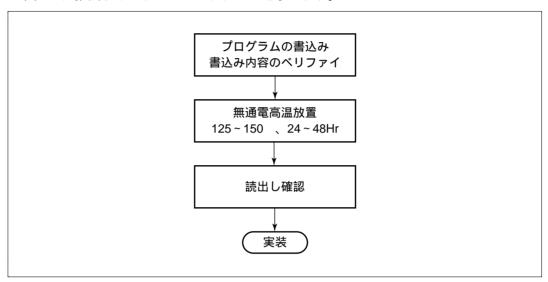

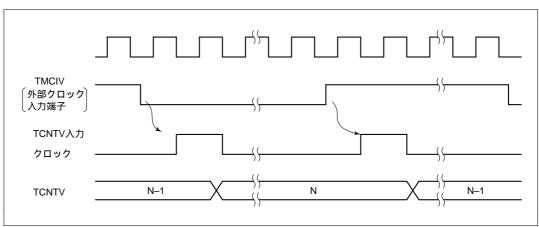

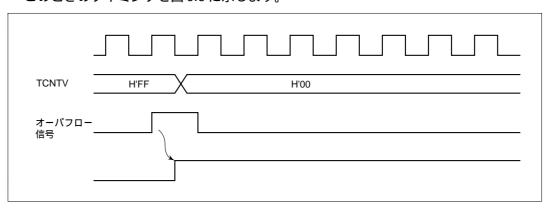

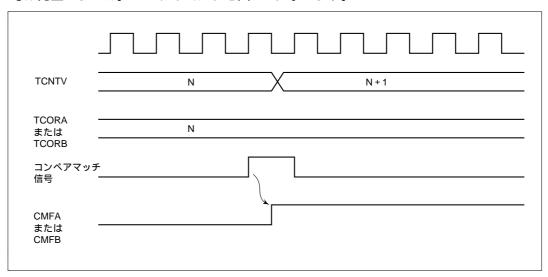

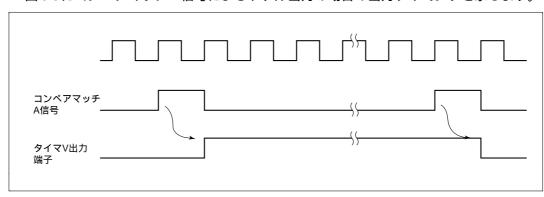

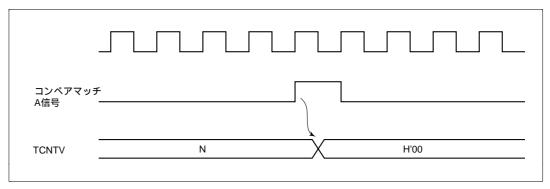

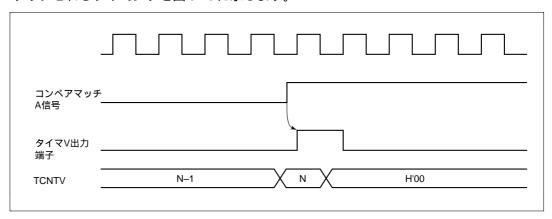

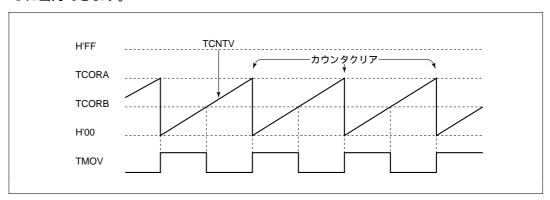

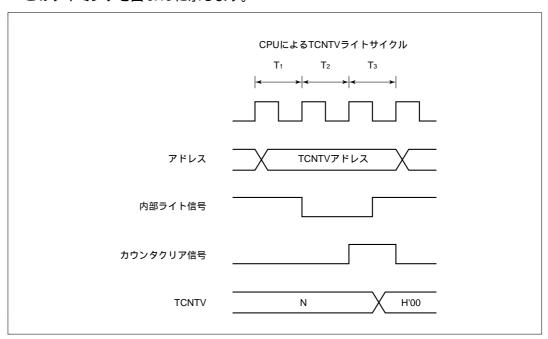

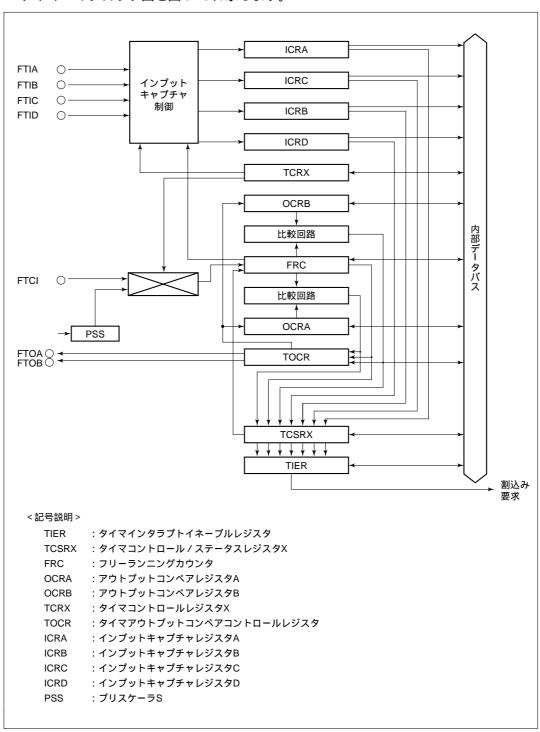

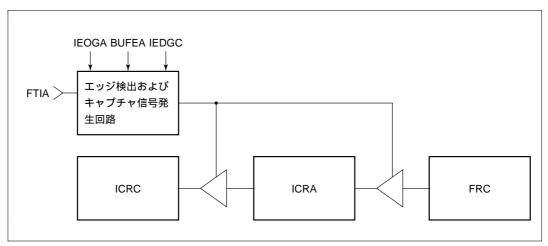

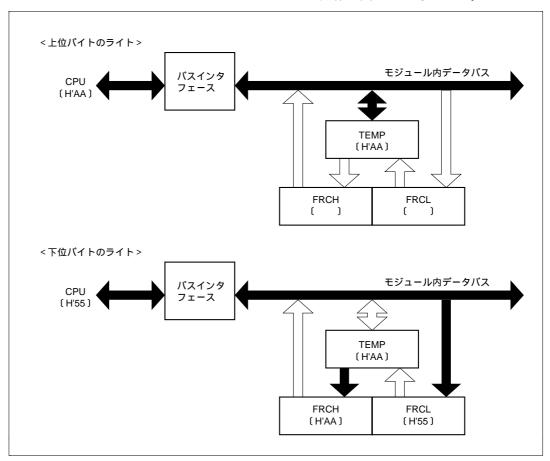

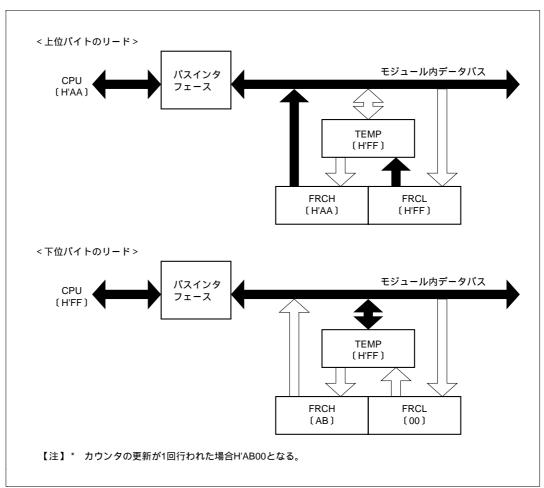

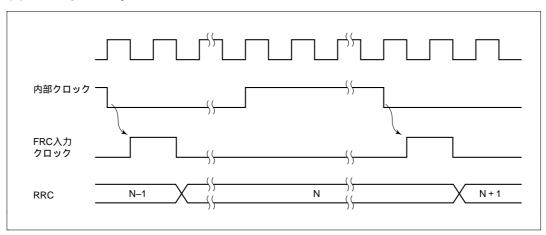

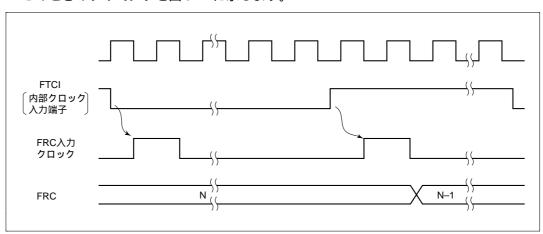

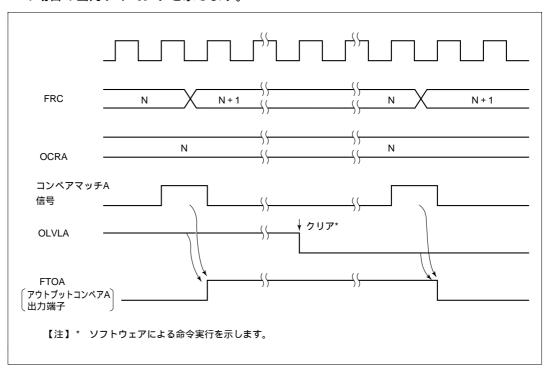

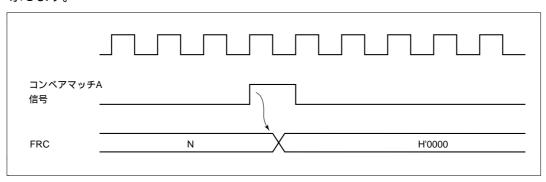

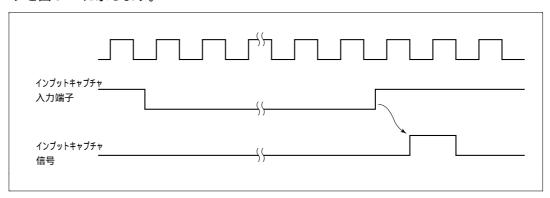

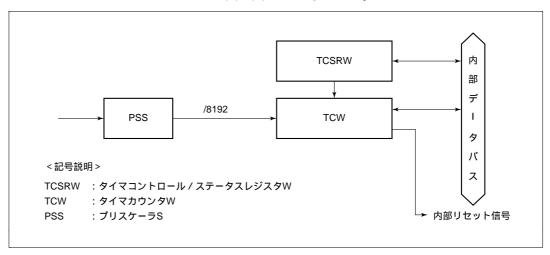

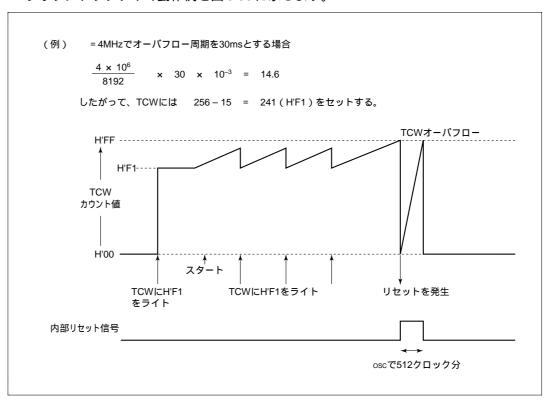

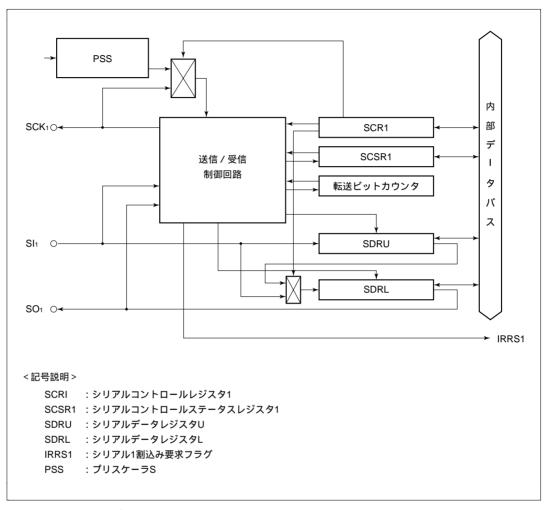

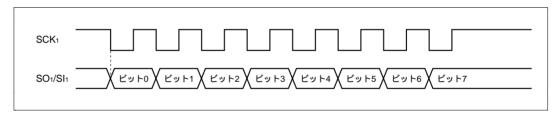

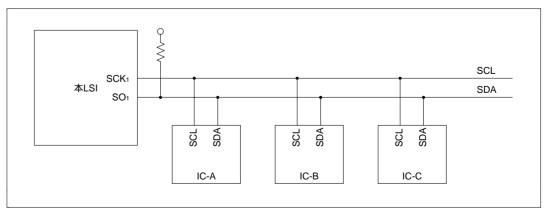

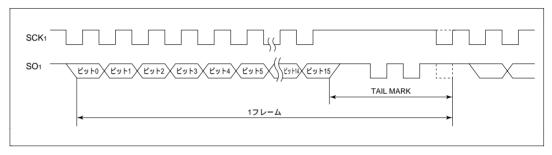

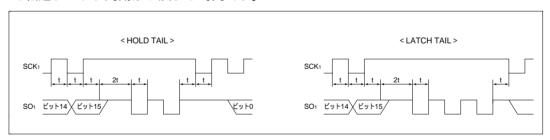

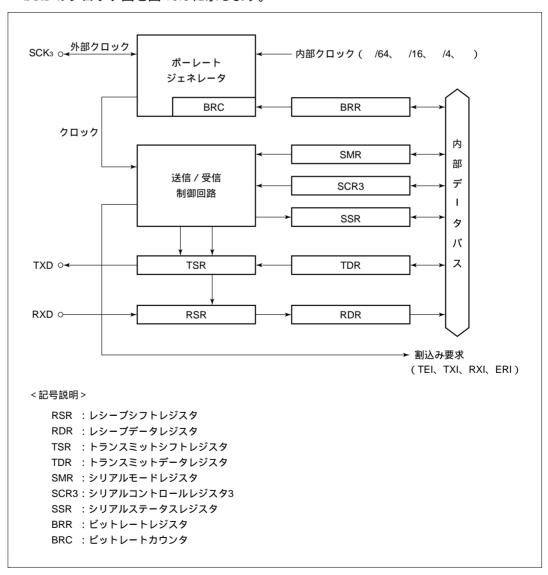

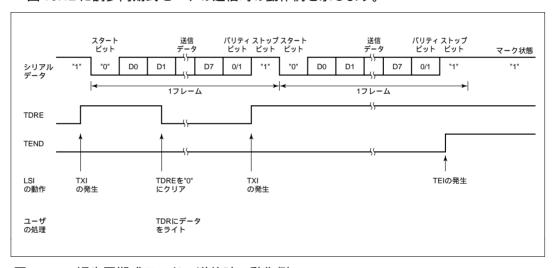

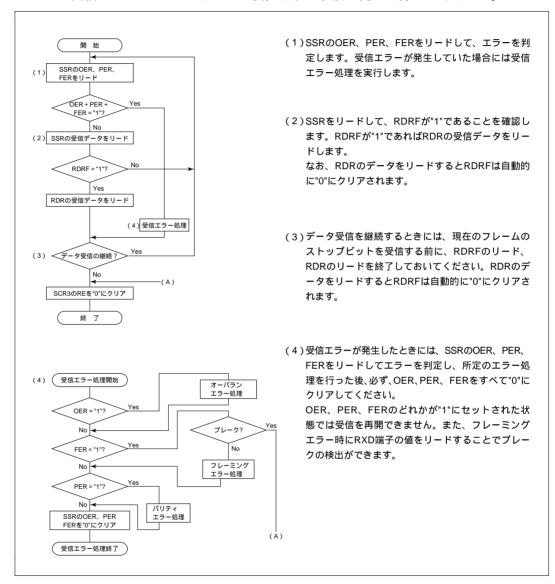

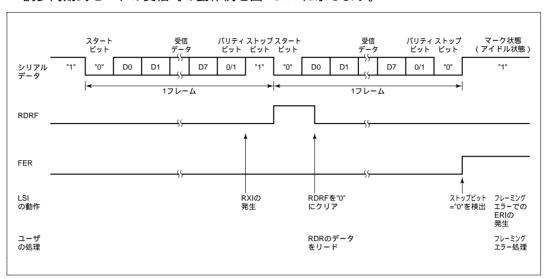

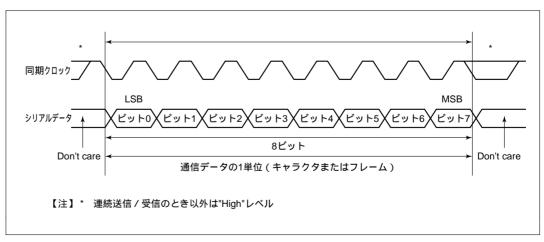

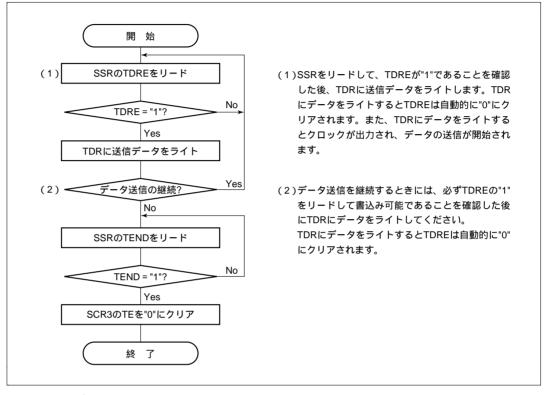

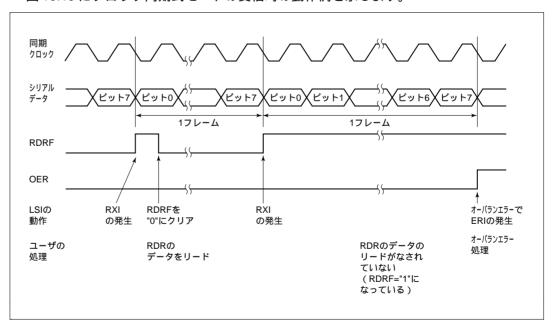

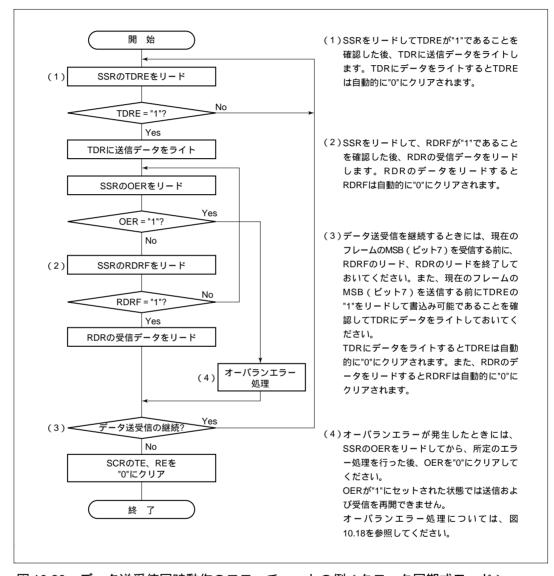

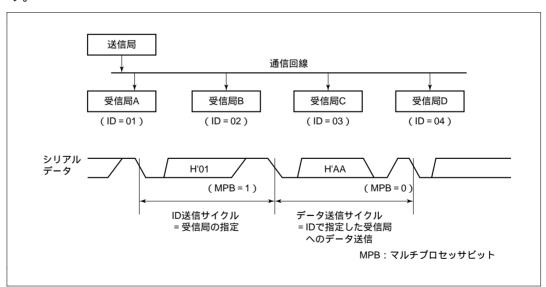

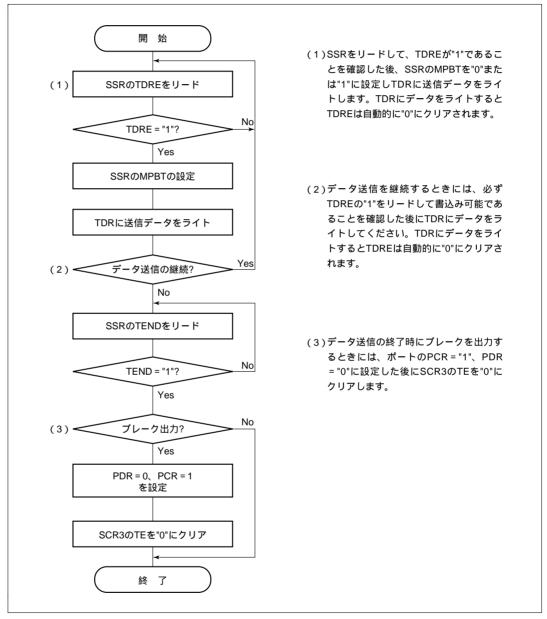

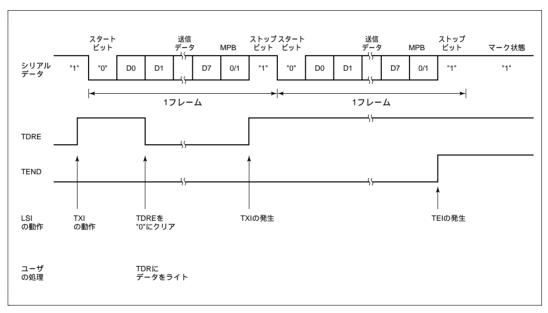

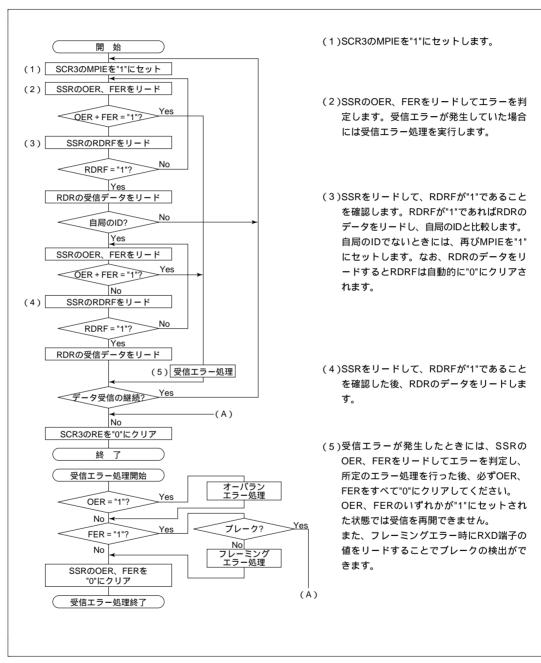

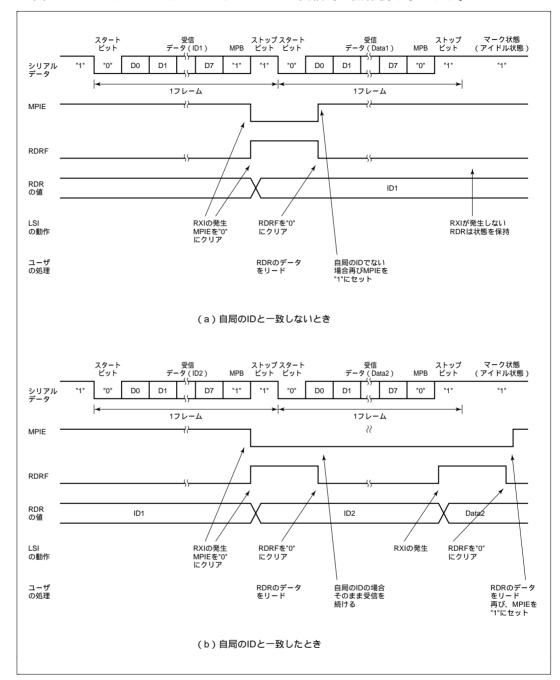

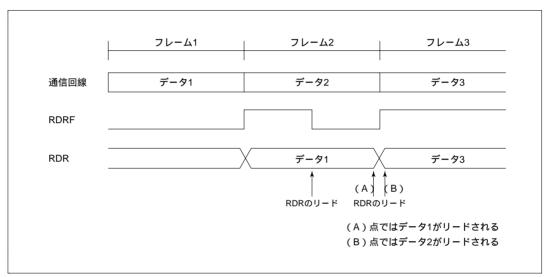

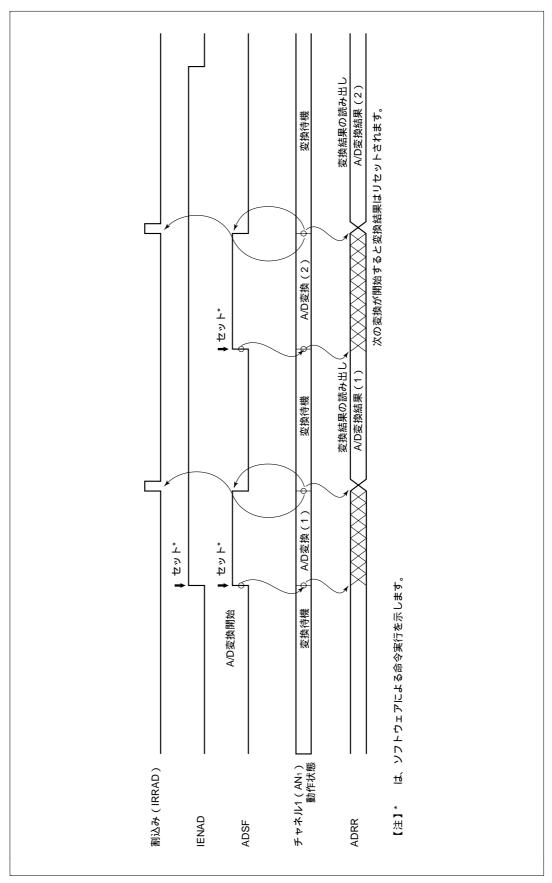

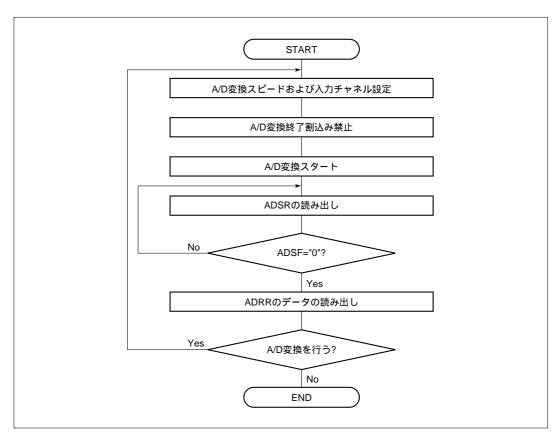

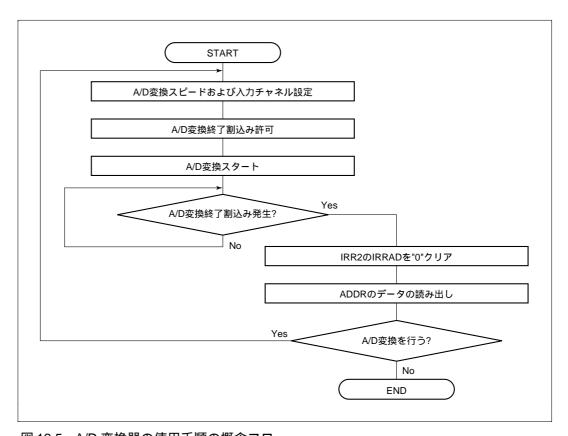

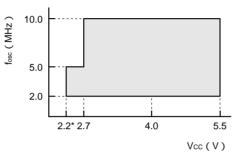

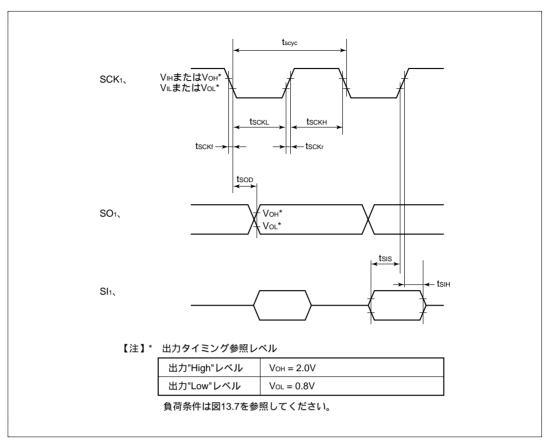

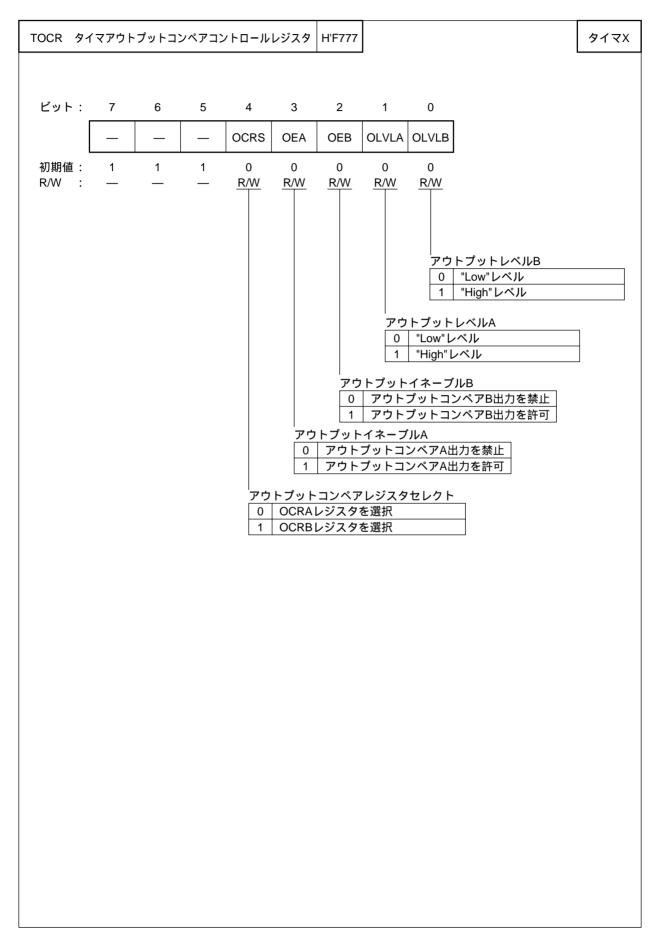

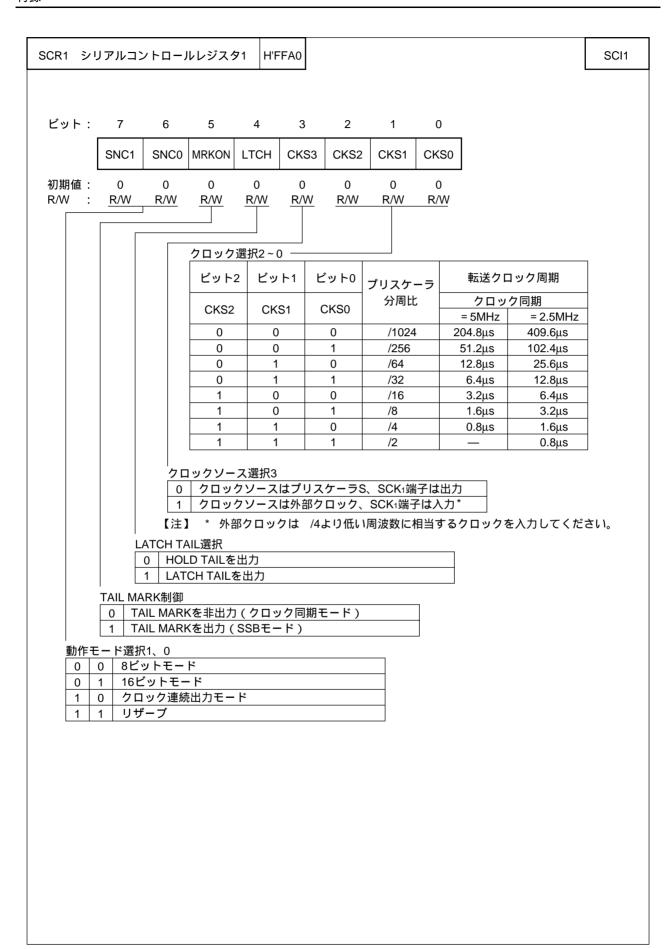

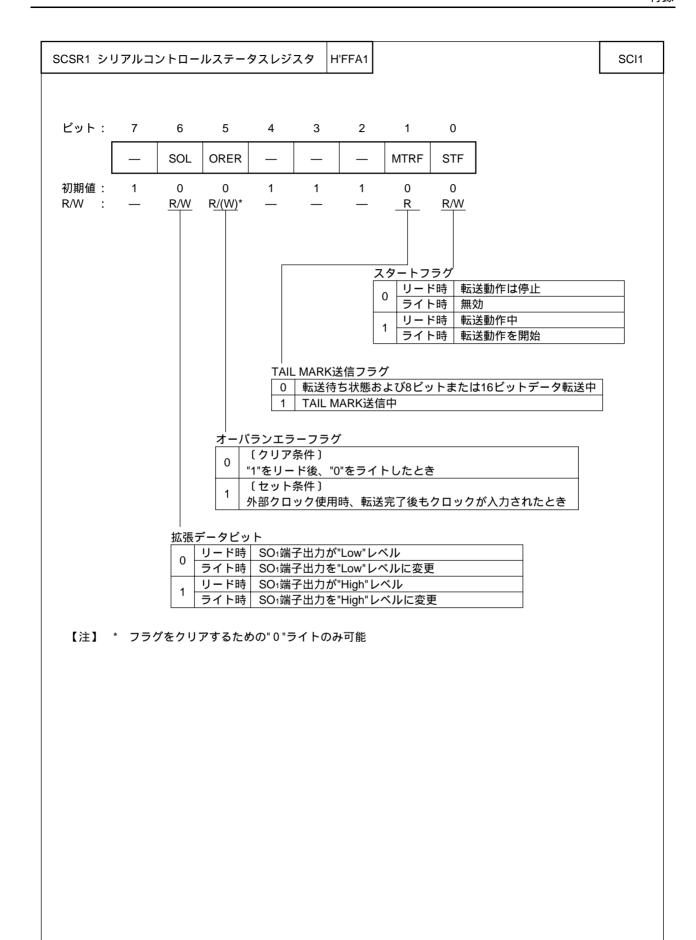

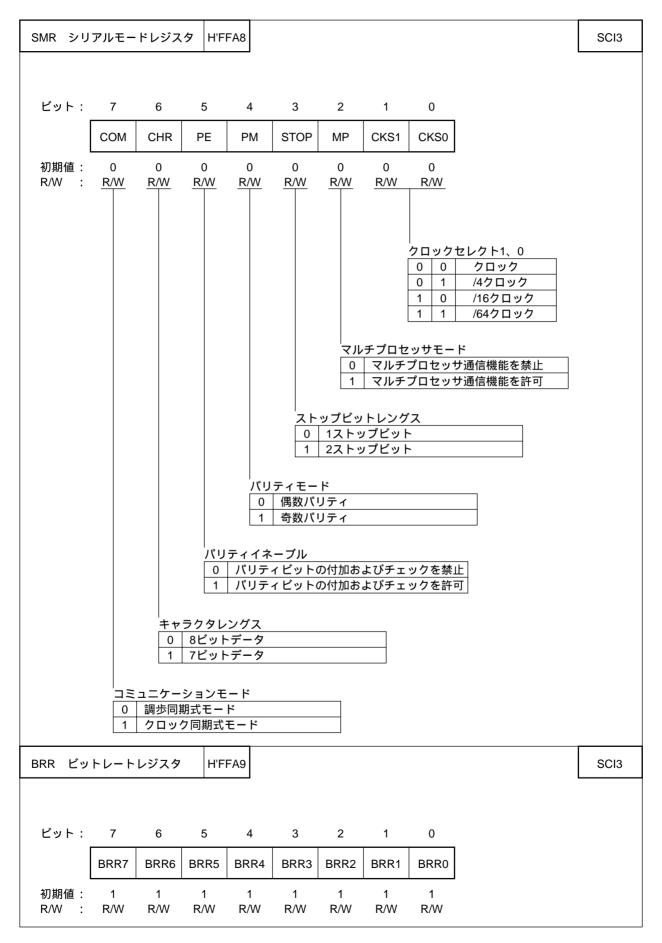

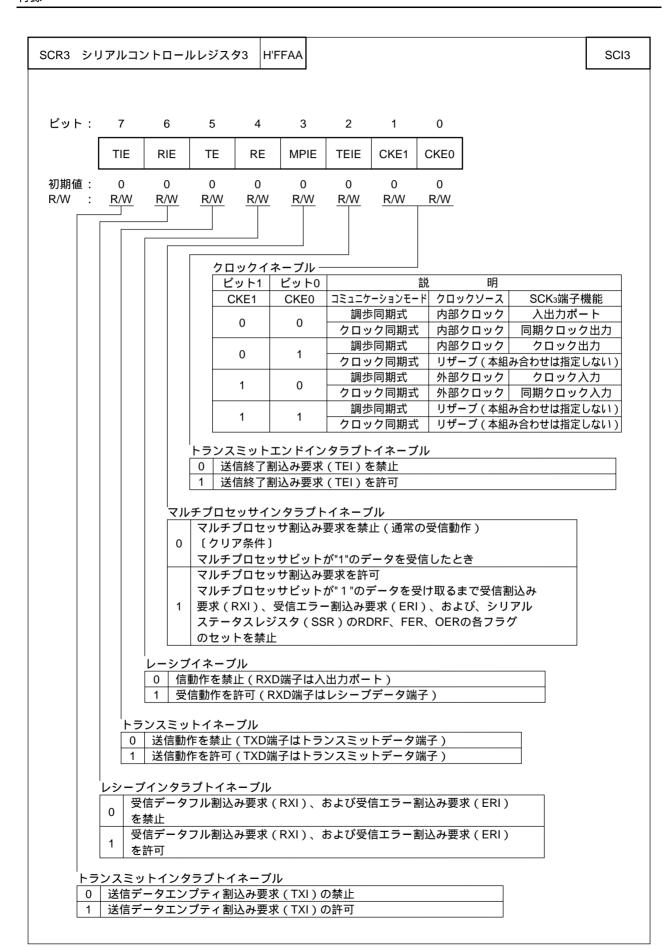

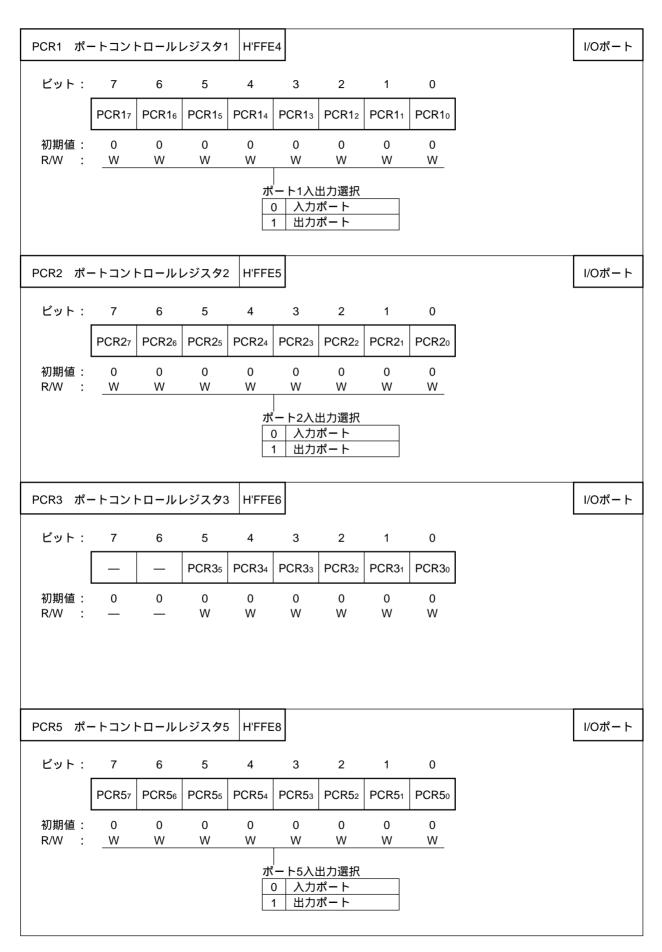

|       |      | ビット番号は、3 ビットのイミディエイトデータで指定されます。                           |