# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# H8/3614グループ

ハードウェアマニュアル ルネサスシングルチップマイクロコンピュータ H8ファミリ/ H8/300Lシリーズ

| H8/3614 | HD6473614 |

|---------|-----------|

|         | HD6433614 |

| H8/3613 | HD6433613 |

| H8/3612 | HD6433612 |

#### 安全設計に関するお願い -

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、 誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した 冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

## 本資料ご利用に際しての留意事項。

- 1. 本資料は、お客様が用途に応じた適切なルネサステクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサステクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報 は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5.本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。

# 製品に関する一般的注意事項

#### 1. NC 端子の処理

【注意】NC 端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC 端子には、何も接続しないようにしてください。接続された場合については保証できません。

2. 未使用入力端子の処理

【注意】未使用の入力端子はハイまたはローレベルに固定してください。

CMOS 製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。未使用の入力端子は、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は、製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシステムが誤動作を起こさないようにシステム設計を行ってください。リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられている場合があります。これらのレジスタをアクセスしたときの動作および継続する動作については、 保証できませんので、アクセスしないようにしてください。

# はじめに

H8/3614 グループは、H8/300L CPU を核にして、システム構成に必要な周辺機能を集積したシングルチップマイクロコンピュータです。

このマニュアルは、H8/3614 グループの CPU アーキテクチャ、周辺機能、電気的特性および外形寸法図について記載しています。

命令の詳細については、「H8/300L シリーズ ソフトウェアマニュアル ( 資料 No.RJJ09B0342 ) 」をご覧ください。

# 本版で改訂された箇所

| 修正項目 | ページ | 修正箇所                                                 |

|------|-----|------------------------------------------------------|

| 全体   | -   | 社名変更による変更<br>(修正前)日立製作所 (修正後)ルネサス テクノロジ<br>呼称変更による変更 |

|      |     | (修正前)H8/3614 シリーズ   (修正後)H8/3614 グループ                |

# 目次

| 1.1 概要 1-1 1.2 内部プロック図 1-4 1.3 端子説明 1-6 1.3.1 ピン配置 1-6 1.3.2 端子機能 1-10 第2章 CPU 2.1 概要 2-1 2.1.2 アドレス空間 2-2 2.1.3 レジスタ構成 2-3 2.2 各レジスタの説明 2-4 2.2.1 加用レジスタ 2-4 2.2.2 コントロールレジスタ 2-4 2.2.1 コーレンジスタ 2-4 2.2.1 加用レジスタの初期値 2-6 2.3 データ構成 2-6 2.3 データ構成 2-6 2.3 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.3 データ構成 2-7 2.3.3 データ構成 2-7 2.3.1 漁用レジスタのデータ構成 2-7 2.3.3 データ構成 2-7 2.3.3 素理リーでのデータ構成 2-7 2.3.3 素理リーでのデータ構成 2-7 2.3.3 素型リーでのデータ構成 2-7 2.3.5 命令セット 2-15 2.5 からやット 2-15 2.5 からやっト 2-20 2.5 グロケラム実行状態 2-20 2.5 グログラム学に状態 2-30 2.6 でPU の状態 2-31 2.7 基本動作タイミング 2-33                                                                                                                                                                                                                                       | 第15 | 章 概要  |                |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------|------|

| 1.2 内部プロック図 1-4 1.3 端子説明 1-6 1.3.1 ピン配置 1-6 1.3.2 端子機能 1-10 第 2章 CPU 2.1 概要 2-1 2.1.1 特長 2-1 2.1.2 アドレス空間 2-2 2.1.3 レジスタ構成 2-3 2.2 各レジスタの説明 2-4 2.2.1 汎用レジスタ 2-4 2.2.2 コントロールレジスタ 2-4 2.2.3 CPU内部レジスタの初期値 2-6 2.3.1 汎用レジスタのデータ構成 2-6 2.3.1 汎用レジスタのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-8 2.4 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.5.1 データ転送命令 2-11 2.5.2 算術演算命令 2-11 2.5.3 論理演算命令 2-11 2.5.3 論理演算命令 2-12 2.5.4 シフト命令 2-20 2.5.5 ヴレル操作命令 2-20 2.5.6 分岐命令 2-20 2.5.7 システム制御命令 2-20 2.5.5 ヴェル解告令 2-20 2.5.6 プログラム実行状態 2-31 2.6.1 概要 2-30 2.6.2 ブログラム実行状態 2-31 2.6.3 プログラム厚上状態 2-31 2.6.4 例外処理状態 2-31 2.6.4 例外処理状態 2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.1 | 概要    |                | 1-1  |

| 1.3. 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.2 |       |                |      |

| 1.3.1 ピン配置 1-6 1.3.2 端子機能 1-10 第2章 CPU  2.1 概要 2-1 2.1.1 特長 2-1 2.1.2 アドレス空間 2-2 2.1.3 レジスタ構成 2-3 2.2 各レジスタの説明 2-4 2.2.1 汎用レジスタ 2-4 2.2.2 コントロールレジスタ 2-4 2.2.3 CPU 内部レジスタの初期値 2-6 2.3 データ構成 2-6 2.3 ボータ構成 2-6 2.3.1 汎用レジスタのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.2 メモリ上でのデータ構成 2-7 2.3.1 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.4.1 アドレッシングモード 2-9 2.4.2 実効アドレスの計算方法 2-11 2.5.1 データ転送命令 2-17 2.5.2 算析演算命令 2-17 2.5.2 算析演算命令 2-17 2.5.3 論理演算命令 2-20 2.5.5 ビット操作命令 2-22 2.5.6 分岐命令 2-26 2.5.7 システム制御命令 2-26 2.5.8 ブロック転送命令 2-27 2.5.8 ブロック転送命令 2-28 2.5.8 ブロック転送命令 2-29 2.5.8 ブロック転送命令 2-22 2.5.8 ブロック転送命令 2-22 2.5.8 ブロック転送命令 2-22 2.5.8 ブロック転送命令 2-22 2.5.9 2.5.9 システム制御命令 2-22 2.5.8 ブロック転送命令 2-22 2.5.9 2.5.9 システム制御命令 2-22 2.5.9 2.5.9 ジステム人制御命令 2-22 2.5.0 2.5.9 ジステム人制御命令 2-22 2.5.9 2.5.9 ジステム人制御命令 2-22 2.5.9 2.5.9 ジステム人制御命令 2-22 2.5.9 2.5.9 ジステム人制御命令 2-22 2.5.9 2.5.9 ジステム人制御命令 2-23 2.6.1 概要 2-30 2.6.2 ブログラム実行状態 2-31 2.6.3 ブログラム実行状態 2-31 2.6.4 例外処理状態 2-31 |     |       |                |      |

| 1.3.2       端子機能       1-10         第 2章 CPU       2.1       概要       2-1         2.1.1       特長       2-1         2.1.2       アドレス空間       2-2         2.1.3       レジスタ構成       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-4         2.2.3       アロールロジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-6         2.3.1       汎用レジスタのデータ構成       2-6         2.3.1       汎用レジスタのデータ構成       2-6         2.3.1       汎用レジスタのデータ構成       2-6         2.4.1       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.5.1       データ転送命令       2-15         2.5.2       算効である。       2-15         2.5.2       算効である。       2-20         2.5.3       プリー・アンター・アンター・アンター・アンター・アンター・アンター・アンター・                                                                                                                                                                                                                                                                                                                                                                                                      | 1.3 |       |                |      |

| 第 2章 CPU  2.1 概要 2.1.1 特長 2.1.2 アドレス空間 2.1.2 アドレス空間 2.2.2 2.1.3 レジスタ構成 2.3  2.2 各レジスタの説明 2.4  2.2.1 汎用レジスタ 2.4  2.2.2 コントロールレジスタ 2.4  2.2.3 CPU 内部レジスタの初期値 2.6  2.3.1 汎用レジスタので・タ構成 2.7  2.3.2 メモリ上でのデータ構成 2.8  2.4 アドレッシングモード 2.9  2.4.1 アドレッシングモード 2.9  2.4.1 アドレッシングモード 2.9  2.5.5 命令セット 2.15  2.5.1 データ転送命令 2.17  2.5.2 算術演算命令 2.21  2.5.3 論理演算命令 2.21  2.5.4 シフト命令 2.22  2.5.5 ピット操作命令 2.22  2.5.5 ピット操作命令 2.22  2.5.6 分岐命令 2.26  2.5.7 システム制御命令 2.26  2.5.7 システム制御命令 2.26  2.5.8 ブロック転送命令 2.26  2.5.1 概要 2.30  2.6.1 概要 2.30  2.6.2 ブログラム実行状態 2.31  2.6.3 ブログラム停止状態 2.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |       |                |      |

| 2.1       概要       2-1         2.1.1       特長       2-1         2.1.2       アドレス空間       2-2         2.1.3       レジスタ構成       2-3         2.2       各レジスタの説明       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-4         2.2.3       CPU 内部レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-22         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.7       システム制御命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命                                                                                                                                                                                                                     |     | 1.3.2 |                | 1-10 |

| 2.1       概要       2-1         2.1.1       特長       2-1         2.1.2       アドレス空間       2-2         2.1.3       レジスタ構成       2-3         2.2       各レジスタの説明       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-4         2.2.3       CPU 内部レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-22         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.7       システム制御命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命                                                                                                                                                                                                                     | 第25 | 章 CPU |                |      |

| 2.1.2       アドレス空間       2-2         2.1.3       レジスタ構成       2-3         2.2       各レジスタの説明       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-6         2.3.1       汎用レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-21         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       今岐命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命令       2-29         2.6.1       概要       2-30         2.6.2       ブログラム集社・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                    | •   | •     |                | 2-1  |

| 2.1.2       アドレス空間       2-2         2.1.3       レジスタ構成       2-3         2.2       各レジスタの説明       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-6         2.3.1       汎用レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-21         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       今岐命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命令       2-29         2.5.8       ブロック転送命令       2-29         2.6.1       概要       2-30         2.6.2       ブログラム集社・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                    |     | 2.1.1 | 特長             | 2-1  |

| 2.1.3       レジスタ構成       2-3         2.2       各レジスタの説明       2-4         2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-4         2.2.3       CPU 内部レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-28         2.5.8       ブロック転送命令       2-28         2.5.8       ブロック転送命令       2-29         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム実行状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                     |     | 2.1.2 |                |      |

| 2.2.1       汎用レジスタ       2-4         2.2.2       コントロールレジスタ       2-4         2.3       CPU内部レジスタの初期値       2-6         2.3       データ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.8       ブロック転送命令       2-26         2.5.1       概要       2-30         2.6.2       プログラム集行状態       2-31         2.6.3       プログラム保上状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                           |     | 2.1.3 |                |      |

| 2.2.2       コントロールレジスタの初期値       2-4         2.3       データ構成       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-28         2.5.8       ブロック転送命令       2-29         2.6       CPU の状態       2-30         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム停止状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                                                                                                                                              | 2.2 | 各レジス  | マタの説明          | 2-4  |

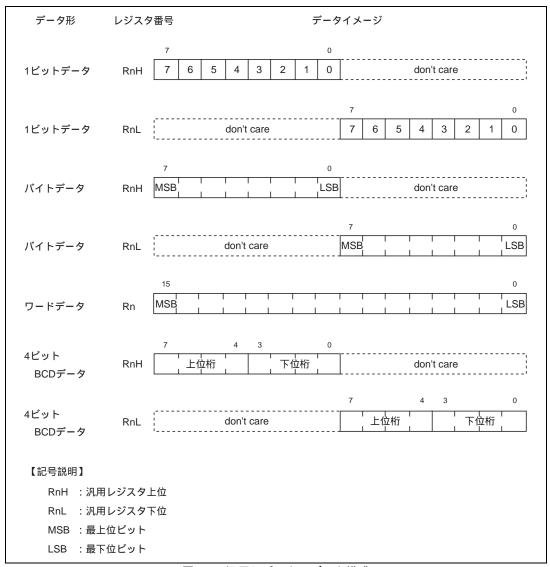

| 2.2.3       CPU 内部レジスタの初期値       2-6         2.3.1       汎用レジスタのデータ構成       2-7         2.3.2       メモリ上でのデータ構成       2-8         2.4       アドレッシングモード       2-9         2.4.1       アドレッシングモード       2-9         2.4.2       実効アドレスの計算方法       2-11         2.5       命令セット       2-15         2.5.1       データ転送命令       2-17         2.5.2       算術演算命令       2-19         2.5.3       論理演算命令       2-20         2.5.4       シフト命令       2-20         2.5.5       ビット操作命令       2-20         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-28         2.5.8       ブロック転送命令       2-28         2.5.8       ブロック転送命令       2-29         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム専止状態       2-31         2.6.4       例外処理状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                                                                                                                                       |     | 2.2.1 | 汎用レジスタ         | 2-4  |

| 2.3データ構成2-62.3.1汎用レジスタのデータ構成2-72.3.2メモリ上でのデータ構成2-82.4アドレッシングモード2-92.4.1アドレッシングモード2-92.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ピット操作命令2-202.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 2.2.2 | コントロールレジスタ     | 2-4  |

| 2.3.1汎用レジスタのデータ構成2-72.3.2メモリ上でのデータ構成2-82.4アドレッシングモード2-92.4.1アドレッシングモード2-92.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ピット操作命令2-202.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-282.5.8ブロック転送命令2-292.6.1概要2-302.6.2ブログラム実行状態2-312.6.3ブログラム停止状態2-312.6.4例外処理状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 2.2.3 | CPU 内部レジスタの初期値 | 2-6  |

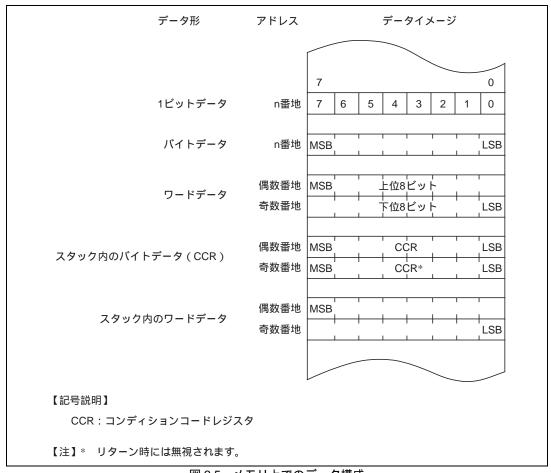

| 2.3.2メモリ上でのデータ構成2-82.4アドレッシングモード2-92.4.1アドレッシングモード2-92.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-202.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-282.5.8ブロック転送命令2-302.6.1概要2-302.6.2ブログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.3 | データ構  | <b>睛成</b>      | 2-6  |

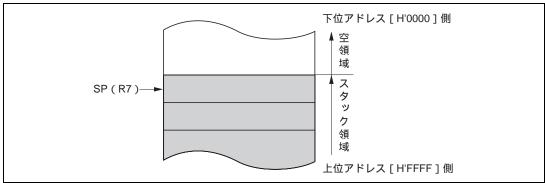

| 2.4アドレッシングモード2-92.4.1アドレッシングモード2-92.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-202.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 2.3.1 | 汎用レジスタのデータ構成   | 2-7  |

| 2.4.1アドレッシングモード2-92.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 2.3.2 | メモリ上でのデータ構成    | 2-8  |

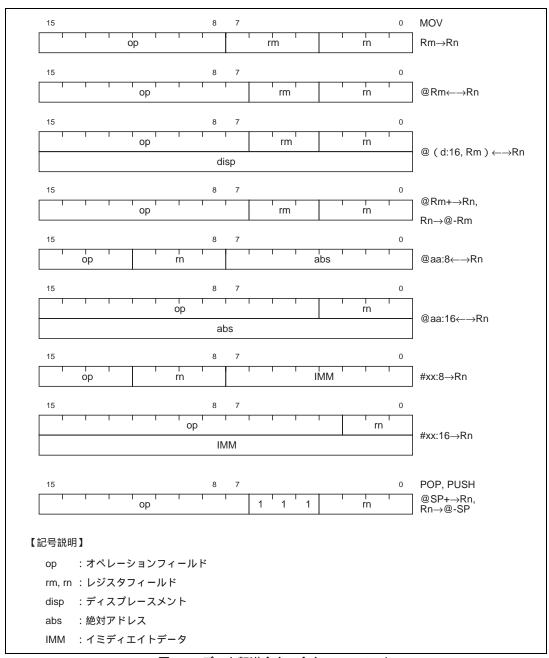

| 2.4.2実効アドレスの計算方法2-112.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.4 | アドレッ  | <b>リシングモード</b> | 2-9  |

| 2.5命令セット2-152.5.1データ転送命令2-172.5.2算術演算命令2-202.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 2.4.1 | アドレッシングモード     | 2-9  |

| 2.5.1データ転送命令2-172.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 2.4.2 | 実効アドレスの計算方法    | 2-11 |

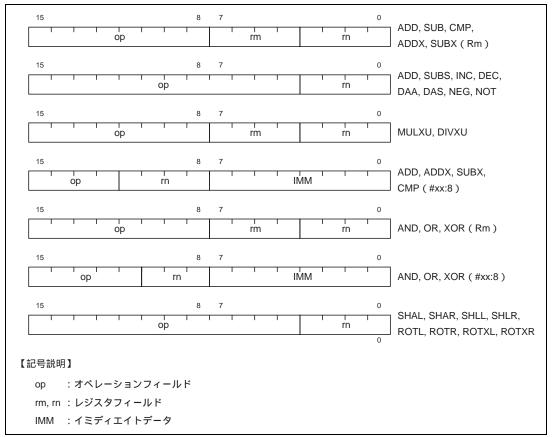

| 2.5.2算術演算命令2-192.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ピット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8プロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.5 | 命令セッ  | <i>y</i>       | 2-15 |

| 2.5.3論理演算命令2-202.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 2.5.1 | データ転送命令        | 2-17 |

| 2.5.4シフト命令2-202.5.5ビット操作命令2-222.5.6分岐命令2-262.5.7システム制御命令2-282.5.8ブロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 2.5.2 | 算術演算命令         | 2-19 |

| 2.5.5       ビット操作命令       2-22         2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-28         2.5.8       ブロック転送命令       2-29         2.6       CPU の状態       2-30         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム停止状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 2.5.3 | 論理演算命令         | 2-20 |

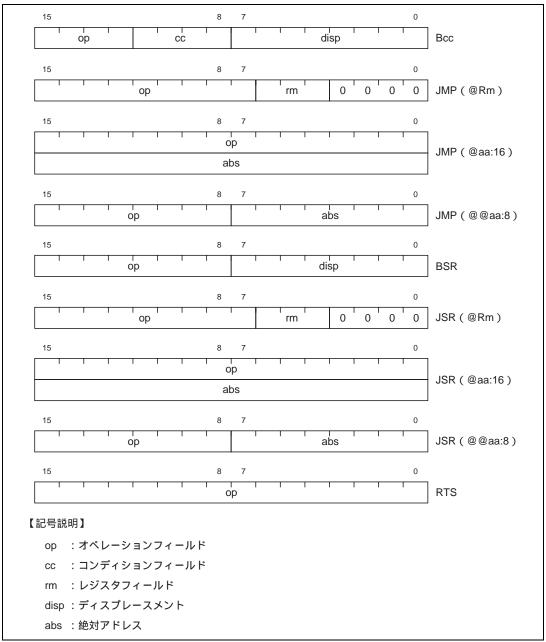

| 2.5.6       分岐命令       2-26         2.5.7       システム制御命令       2-28         2.5.8       ブロック転送命令       2-29         2.6       CPU の状態       2-30         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム停止状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 2.5.4 |                |      |

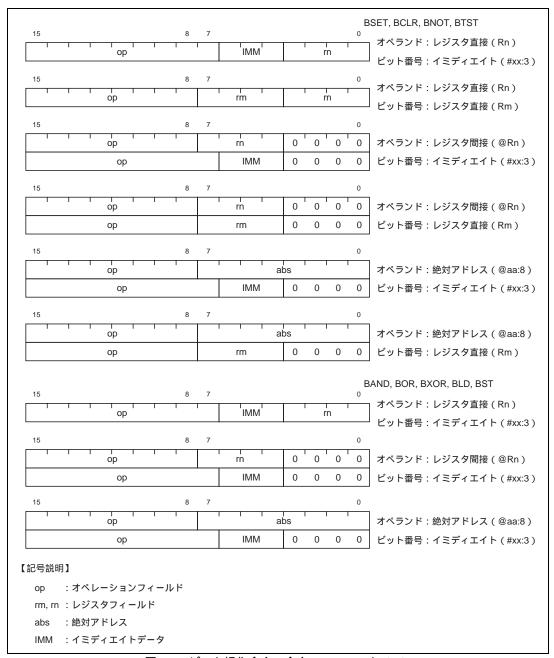

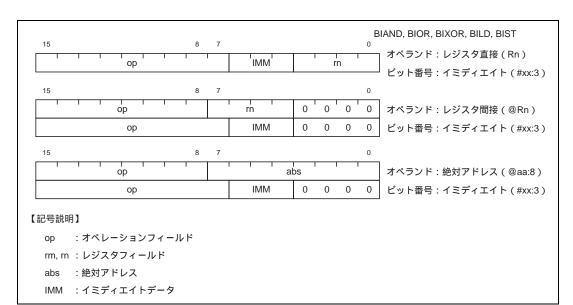

| 2.5.7システム制御命令2-282.5.8プロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |                |      |

| 2.5.8プロック転送命令2-292.6CPU の状態2-302.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       |                |      |

| 2.6       CPU の状態       2-30         2.6.1       概要       2-30         2.6.2       プログラム実行状態       2-31         2.6.3       プログラム停止状態       2-31         2.6.4       例外処理状態       2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |       |                |      |

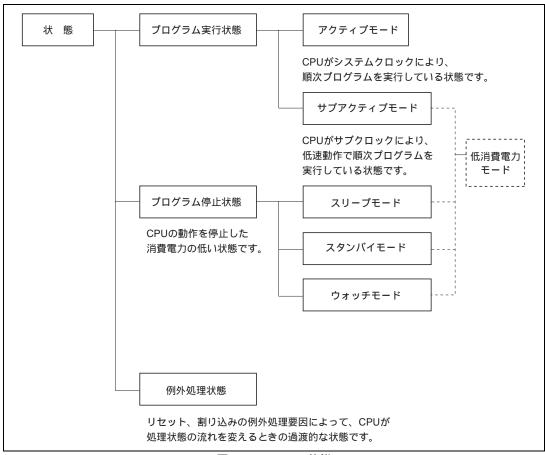

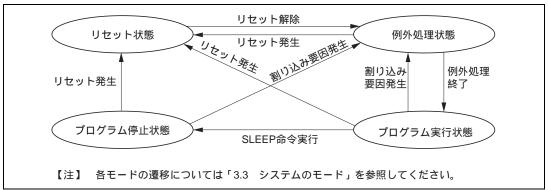

| 2.6.1概要2-302.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.6 |       |                |      |

| 2.6.2プログラム実行状態2-312.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.6 |       |                |      |

| 2.6.3プログラム停止状態2-312.6.4例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |       |                |      |

| 2.6.4 例外処理状態2-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |       |                |      |

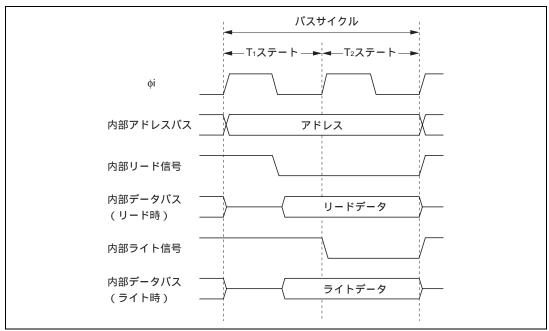

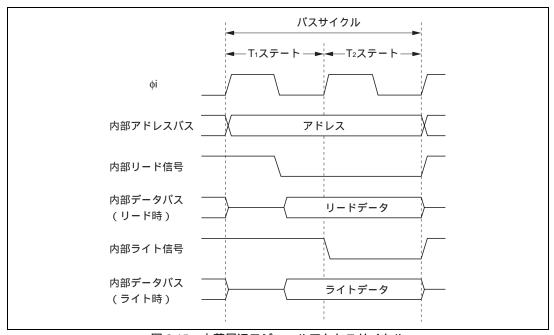

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27  |       |                |      |

|            | 2.7.1      | 内蔵メモリ(RAM、ROM )             | 2-32 |

|------------|------------|-----------------------------|------|

|            | 2.7.2      | 内蔵周辺モジュール                   | 2-33 |

| 2.8        | 使用上        | の注意事項                       | 2-34 |

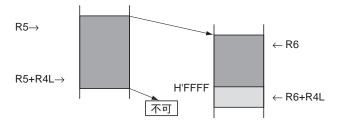

|            | 2.8.1      | データアクセスに関する注意事項             | 2-34 |

|            | 2.8.2      | ビット操作命令使用上の注意事項             | 2-36 |

|            |            |                             |      |

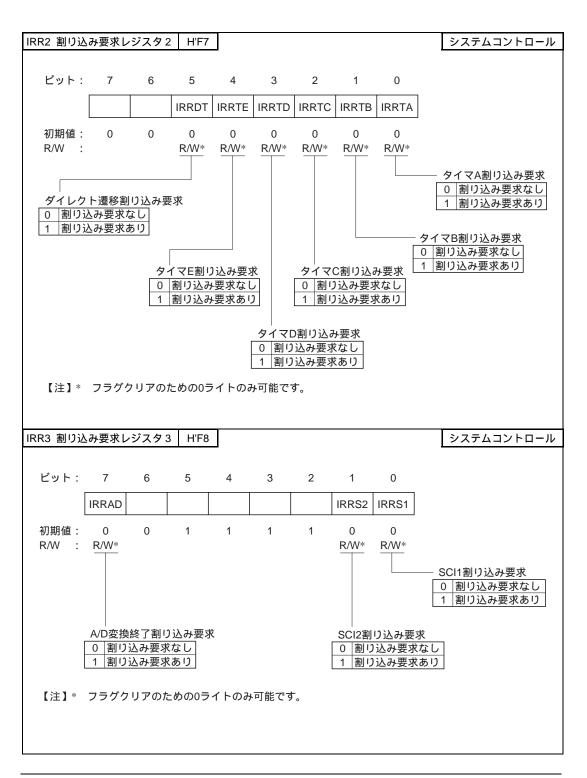

| 笙 3        | 音 シス       | テムコントロール                    |      |

| 3.1        |            | , — — , ,                   | 3-1  |

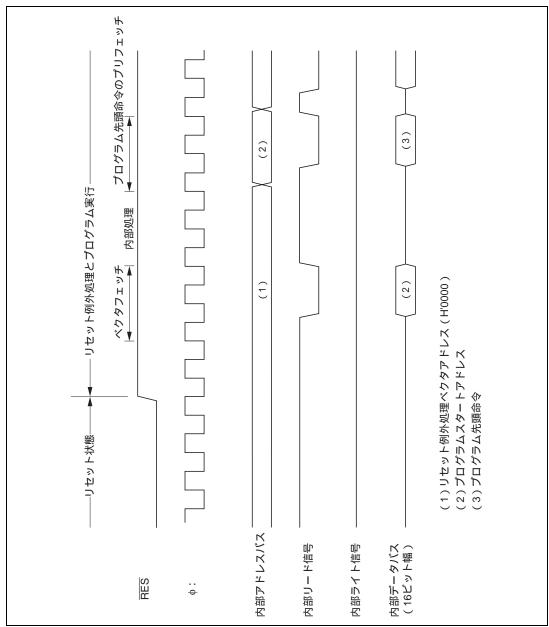

| 3.2        | 例外処        | 理                           | 3-1  |

|            | 3.2.1      | _<br>リセット                   |      |

|            | 3.2.2      | 割り込み                        |      |

|            | 3.2.3      | 割り込み制御レジスタ                  |      |

|            | 3.2.4      | 外部割り込み                      |      |

|            | 3.2.5      | 内部割り込み                      |      |

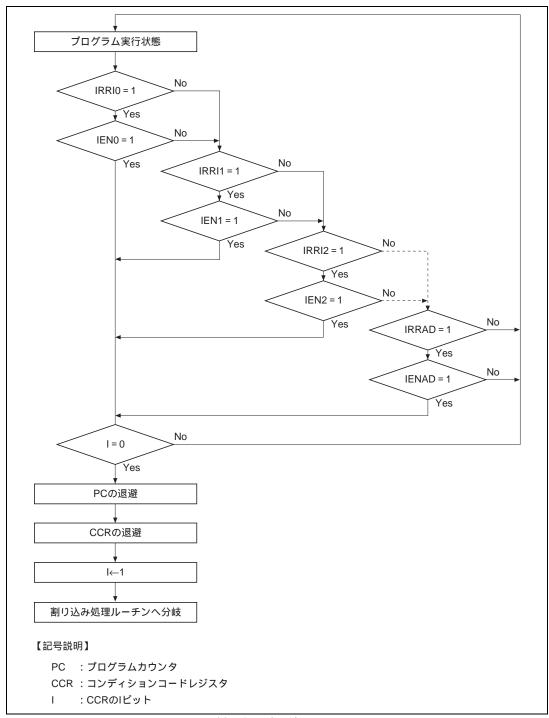

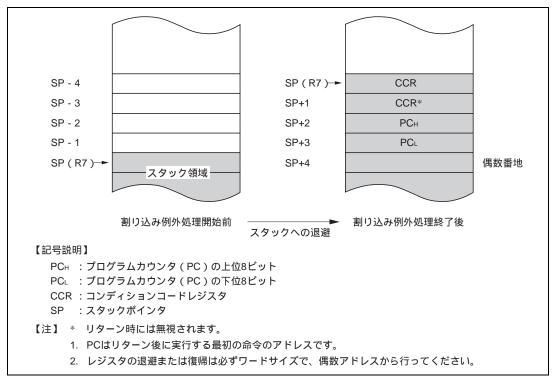

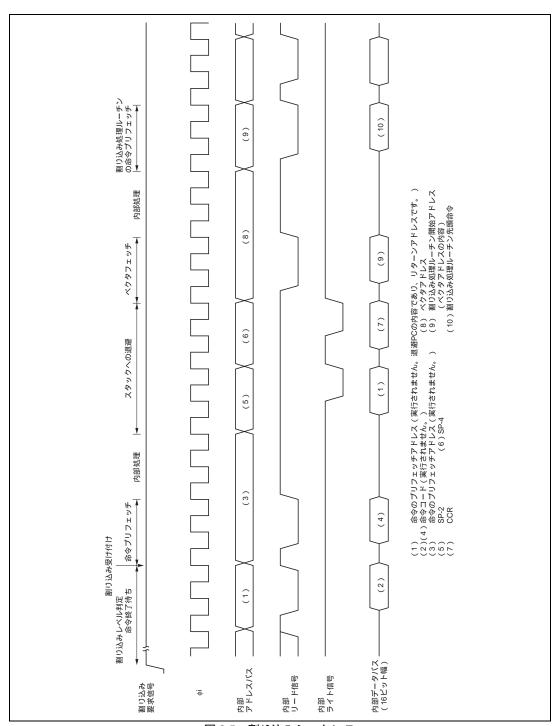

|            | 3.2.6      | 割り込み動作                      | 3-13 |

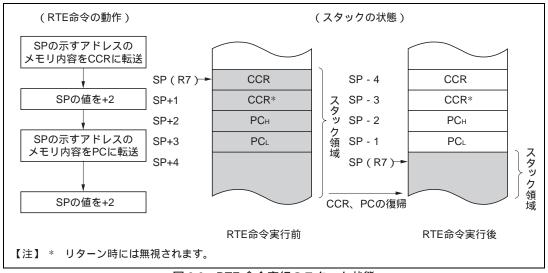

|            | 3.2.7      | 割り込み復帰動作                    | 3-17 |

|            | 3.2.8      | 割り込み応答時間                    | 3-17 |

|            | 3.2.9      | 各モードにおける有効な割り込み要因           | 3-18 |

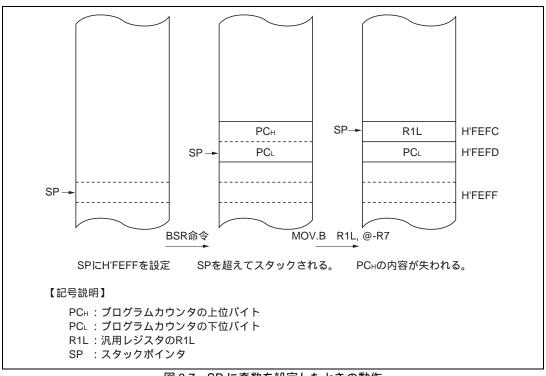

|            | 3.2.10     | スタック領域に関する使用上の注意            | 3-19 |

|            | 3.2.11     | 割り込み要求レジスタのクリアに関する使用上の注意    | 3-19 |

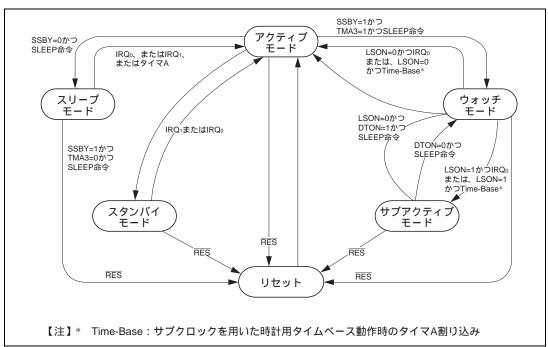

| 3.3        | システ        | ムのモード                       | 3-20 |

|            | 3.3.1      | 概要                          | 3-20 |

|            | 3.3.2      | アクティブモード                    | 3-21 |

|            | 3.3.3      | スリープモード                     |      |

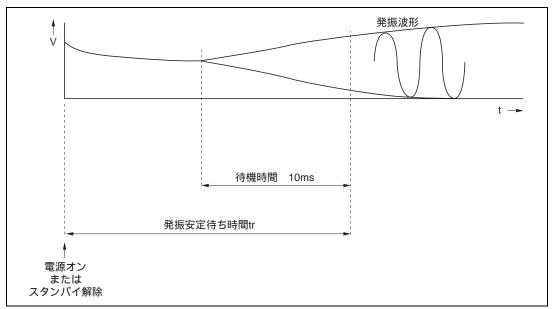

|            | 3.3.4      | スタンバイモード                    | 3-22 |

|            | 3.3.5      | ウォッチモード                     | 3-23 |

|            | 3.3.6      | サブアクティブモード                  | 3-23 |

|            | 3.3.7      | 使用上の注意事項                    | 3-24 |

| 3.4        | システ        | ムコントロールレジスタ                 | 3-25 |

|            | 3.4.1      | システムコントロールレジスタ 1 ( SYSCR1 ) | 3-25 |

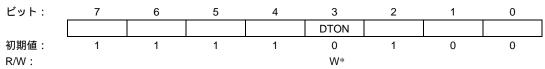

|            | 3.4.2      | システムコントロールレジスタ 2 (SYSCR2)   |      |

|            |            | •                           |      |

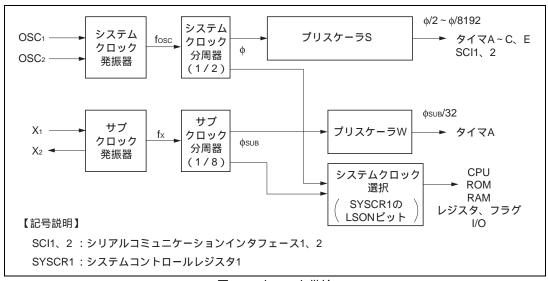

| 第 4        | 章 クロ       | ック発振器                       |      |

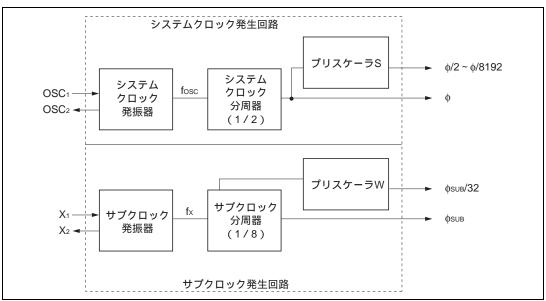

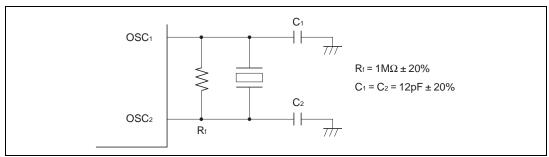

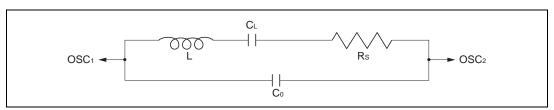

| 4.1        |            |                             | 4-1  |

|            |            | ブロック図                       |      |

| 4.2        |            | - フロファロ                     |      |

|            |            |                             |      |

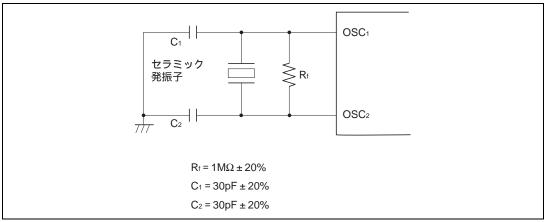

| 4.3        | サノク        | ロック発振器                      | 4-4  |

| <b>学</b> c | 章 I/O 7    | #_ L                        |      |

| •          |            |                             | F 1  |

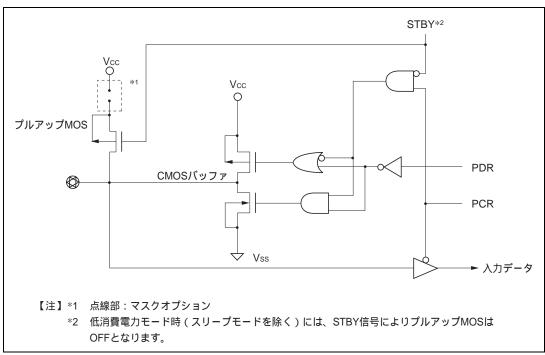

| 5.1        |            | 44フのナープン・ニン・                |      |

|            |            | 端子のオプション                    |      |

| <i>-</i> - |            | プルアップ MOS                   |      |

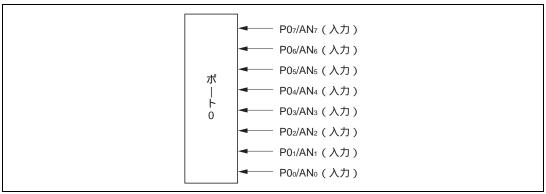

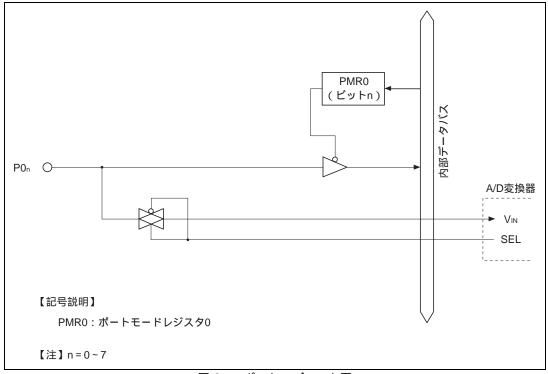

| 5.2        | <b>ツート</b> | 0                           | 5-4  |

|      | 5.2.1       | 概要                                    | 5-4  |

|------|-------------|---------------------------------------|------|

|      | 5.2.2       | レジスタの構成と説明                            | 5-4  |

|      | 5.2.3       | 端子機能                                  | 5-5  |

|      | 5.2.4       | 端子状態                                  | 5-5  |

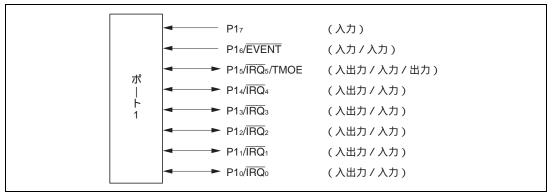

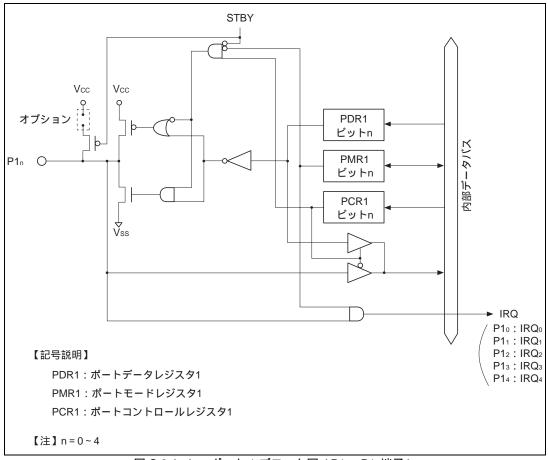

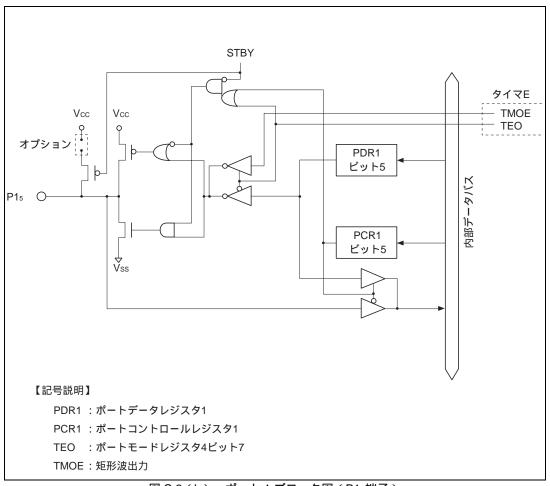

| 5.3  | ポート         | · 1                                   | 5-6  |

|      | 5.3.1       | 概要                                    | 5-6  |

|      | 5.3.2       | <br>レジスタの構成と説明                        |      |

|      | 5.3.3       | 端子機能                                  |      |

|      | 5.3.4       | 端子状態                                  |      |

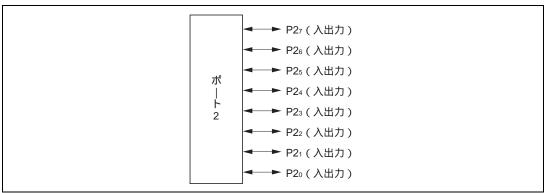

| 5.4  | ポート         | · 2                                   | 5-12 |

|      | 5.4.1       | 概要                                    | 5-12 |

|      | 5.4.2       | レジスタの構成と説明                            |      |

|      | 5.4.3       | ····································· |      |

|      | 5.4.4       | 端子状態                                  |      |

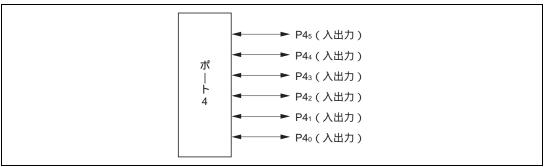

| 5.5  | ポート         | · 4                                   |      |

|      | 5.5.1       | 概要                                    | 5-14 |

|      | 5.5.2       | レジスタの構成と説明                            |      |

|      | 5.5.3       | 端子機能                                  |      |

|      | 5.5.4       | 端子状態                                  |      |

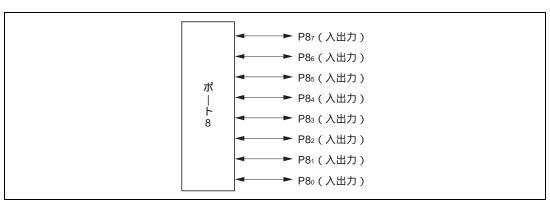

| 5.6  |             | 8                                     |      |

|      | 5.6.1       | 概要                                    | 5-15 |

|      | 5.6.2       | レジスタの構成と説明                            |      |

|      | 5.6.3       | 端子機能                                  |      |

|      | 5.6.4       | 端子状態                                  |      |

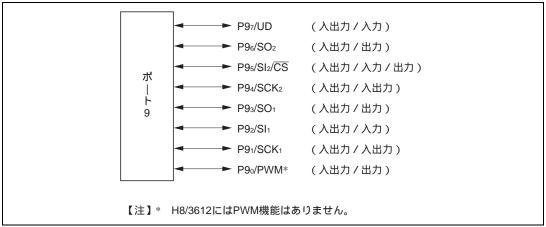

| 5.7  |             | 9                                     |      |

|      | 5.7.1       | 概要                                    | 5-17 |

|      | 5.7.2       | レジスタの構成と説明                            |      |

|      | 5.7.3       | 端子機能                                  |      |

|      | 5.7.4       | 端子状態                                  |      |

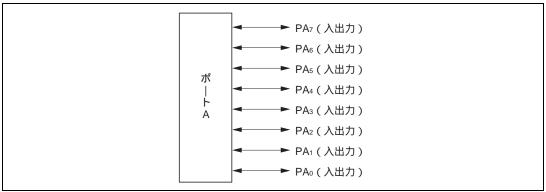

| 5.8  |             | · A                                   |      |

|      | 5.8.1       | 概要                                    |      |

|      | 5.8.2       |                                       |      |

|      | 5.8.3       | 端子機能                                  |      |

|      | 5.8.4       | 端子状態                                  |      |

|      | 5.0.1       | N 1 1 1/104                           |      |

| ~~ ~ | <del></del> | <u>, _</u>                            |      |

| 第6   | 章 タイ        | ₹                                     |      |

| 6.1  | 概要          |                                       | 6-1  |

|      | 6.1.1       | プリスケーラの動作                             | 6-2  |

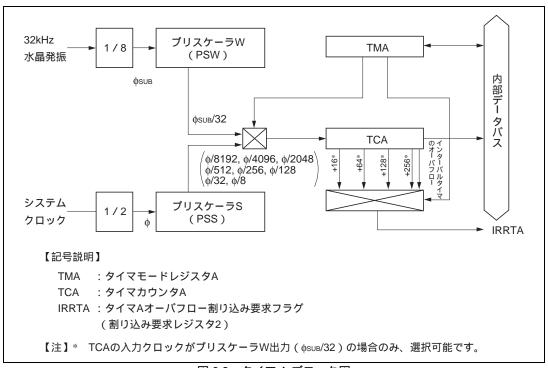

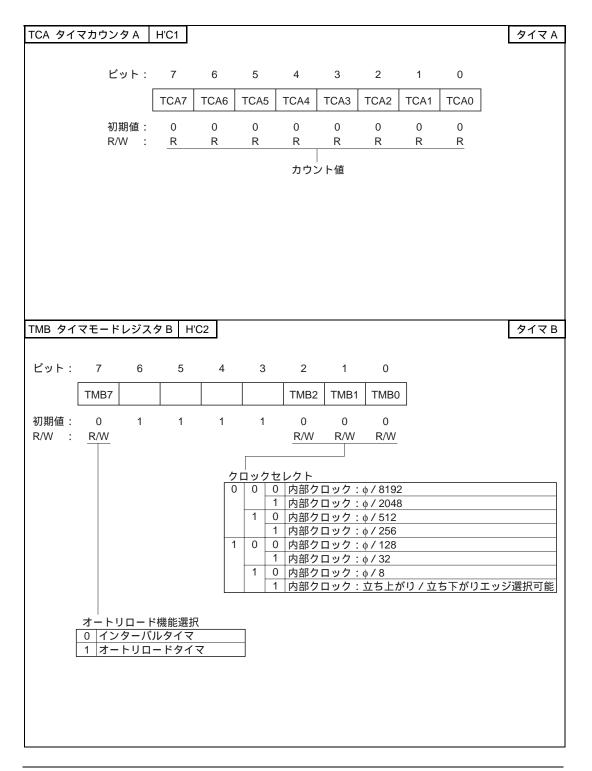

| 6.2  | タイマ         | ' A                                   | 6-3  |

|      | 6.2.1       | 概要                                    | 6-3  |

|      | 6.2.2       | <br>各レジスタの説明                          |      |

|      | 6.2.3       | 動作説明                                  |      |

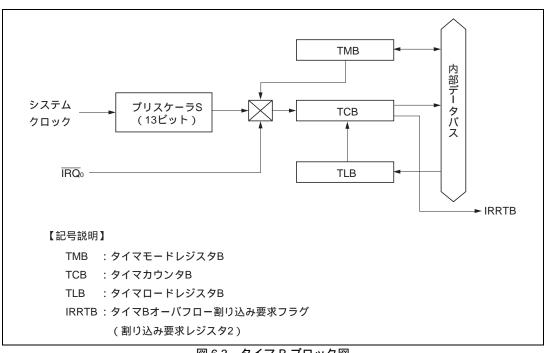

| 6.3  | タイマ         | 'В                                    | 6-6  |

|      | 6.3.1       | 概要                                    | 6-6  |

|      | 0.0.1       | 1-70-                                 | 0 0  |

|      | 6.3.2 各レジスタの説明                      |      |

|------|-------------------------------------|------|

|      | 6.3.3 動作説明                          | 6-9  |

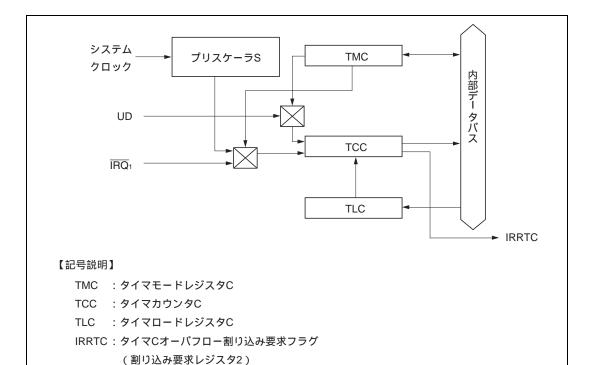

| 6.4  | タイマ C                               | 6-10 |

|      | 6.4.1 概要                            | 6-10 |

|      | 6.4.2 各レジスタの説明                      | 6-12 |

|      | 6.4.3 動作説明                          | 6-14 |

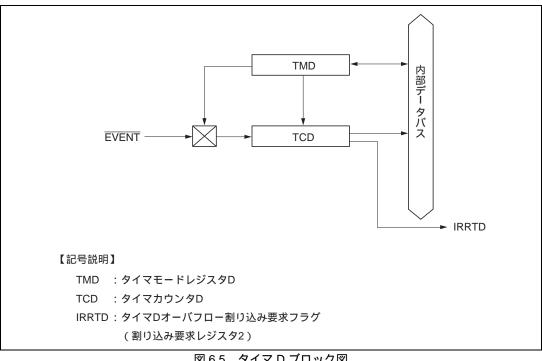

| 6.5  | タイマ D                               | 6-15 |

|      | 6.5.1 概要                            | 6-15 |

|      | 6.5.2 各レジスタの説明                      | 6-17 |

|      | 6.5.3 動作説明                          | 6-18 |

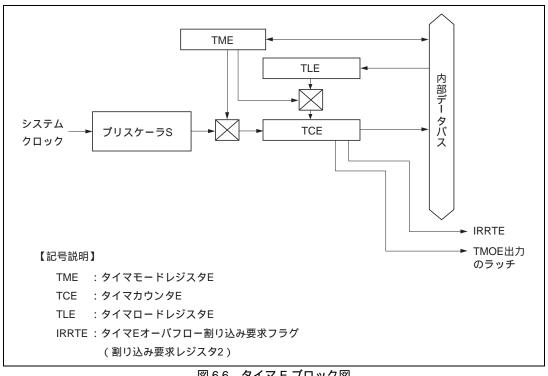

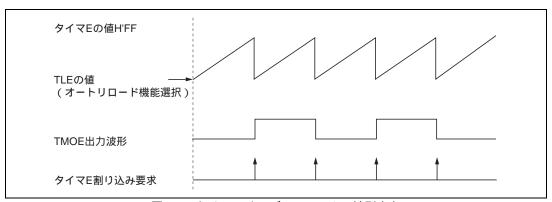

| 6.6  | タイマ E                               | 6-18 |

|      | 6.6.1 概要                            | 6-18 |

|      | 6.6.2 各レジスタの説明                      |      |

|      | 6.6.3 動作説明                          |      |

| 6.7  | 割り込み要因                              |      |

| 6.8  | ー・・ー・ー<br>使用上の注意事項                  |      |

| 0.0  | 区川工V/工态争员                           | 0-24 |

| ~~ _ |                                     |      |

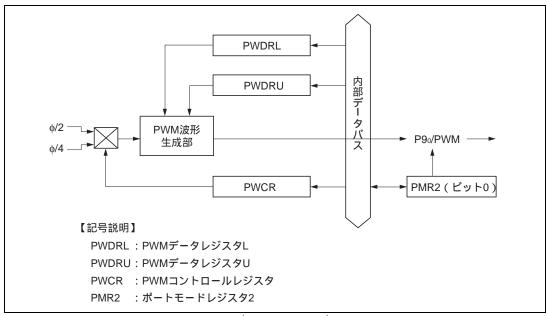

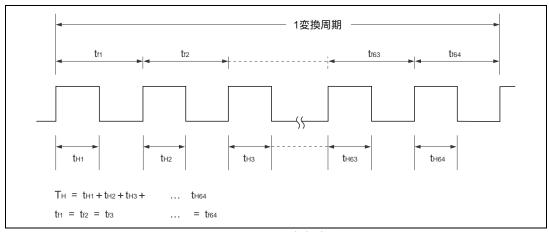

| 第 7  | 7章 14 ビット PWM                       |      |

| 7.1  | 概要                                  |      |

|      | 7.1.1 特長                            | 7-1  |

|      | 7.1.2 ブロック図                         | 7-1  |

|      | 7.1.3 端子構成                          |      |

|      | 7.1.4 レジスタ構成                        | 7-2  |

| 7.2  | 各レジスタの説明                            | 7-2  |

|      | 7.2.1 PWM コントロールレジスタ ( PWCR )       | 7-2  |

|      | 7.2.2 PWM データレジスタ U、L (PWDRU、PWDRL) |      |

| 7.3  | 動作説明                                |      |

|      |                                     |      |

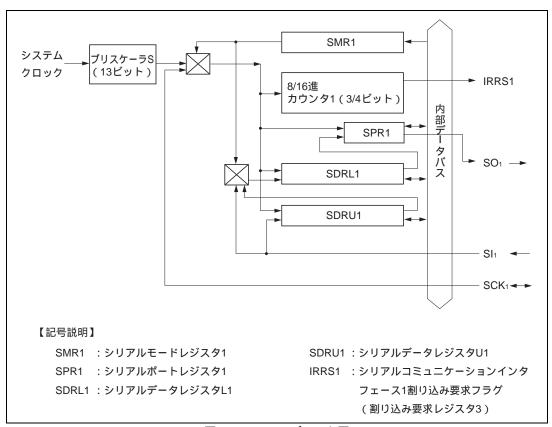

| 筆α   | 3章 シリアルコミュニケーションインタフェース 1(SCI1)     |      |

| 8.1  | / 単                                 | 0.1  |

| 0.1  |                                     |      |

|      | 8.1.1 特長                            |      |

|      | 8.1.2 プロック図                         |      |

|      | 8.1.3 端子構成                          |      |

| 0.2  | 8.1.4 レジスタ構成                        |      |

| 8.2  |                                     |      |

|      | 8.2.1 シリアルモードレジスタ 1 (SMR1)          |      |

|      | 8.2.2 シリアルデータレジスタ U1 (SDRU1)        |      |

|      | 8.2.3 シリアルデータレジスタ L1 ( SDRL1 )      |      |

|      | 8.2.4 シリアルポートレジスタ 1 (SPR1)          |      |

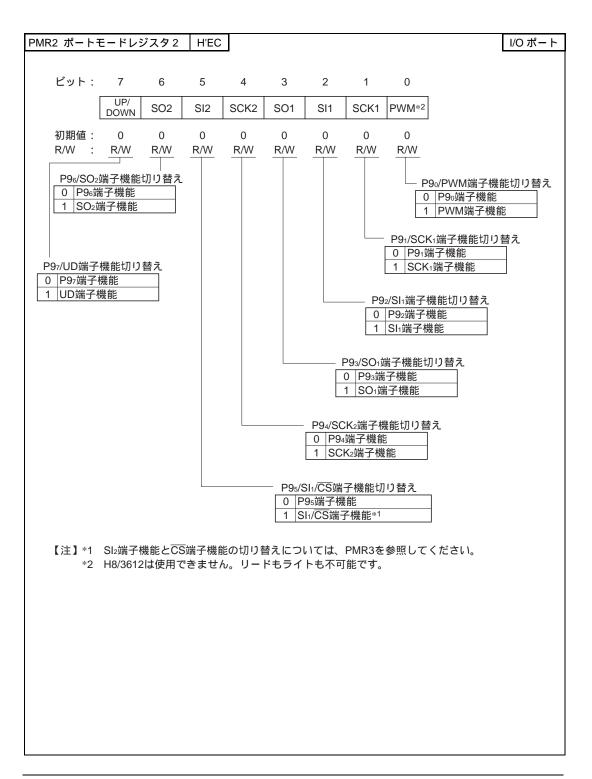

|      | 8.2.5 ポートモードレジスタ 2 (PMR2)           |      |

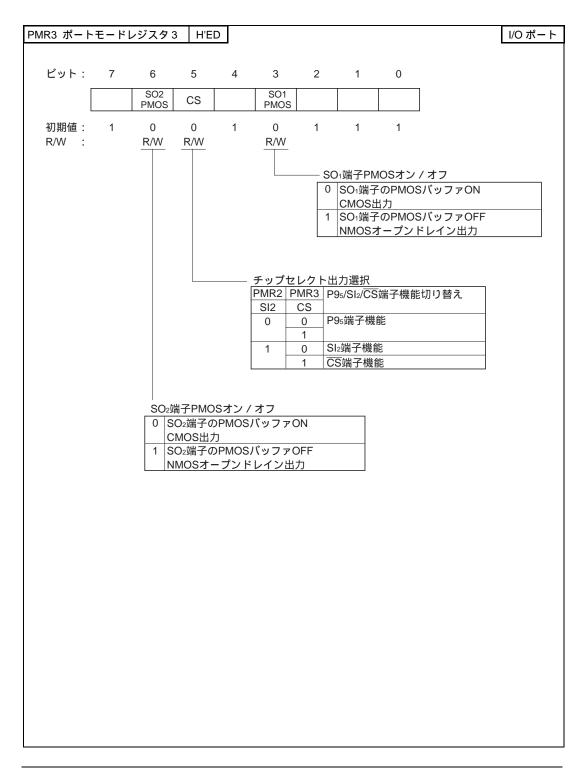

|      | 8.2.6 ポートモードレジスタ 3 (PMR3)           |      |

| 8.3  | 動作説明                                |      |

|      | 8.3.1 概要                            | 8-7  |

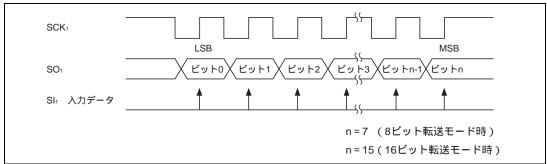

|      | 8.3.2          | データ転送フォーマット                           | 8-8   |

|------|----------------|---------------------------------------|-------|

|      | 8.3.3          | クロック                                  |       |

|      | 8.3.4          | データの送信または受信動作                         |       |

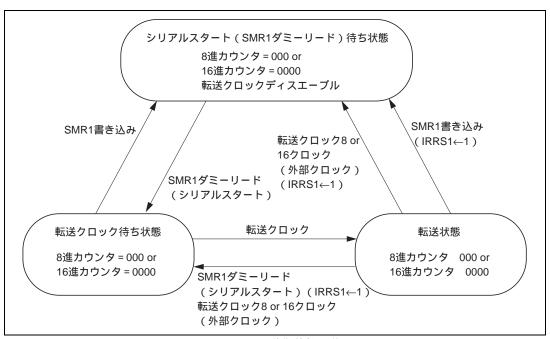

|      | 8.3.5          | SCII の動作状態遷移                          |       |

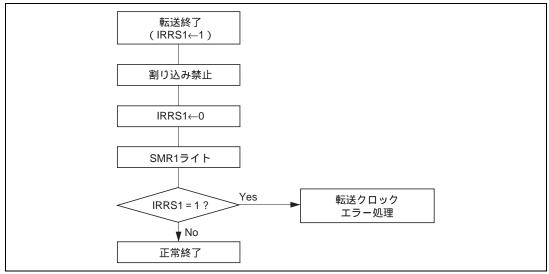

|      | 8.3.6          | 転送クロックエラーの検出例                         |       |

|      | 8.3.7          | 割り込み要因                                | 8-12  |

| 笋a   | 音 シロ           | アルコミュニケーションインタフェース 2 ( SCI2 )         |       |

| 9.1  |                | , , , , , , , , , , , , , , , , , , , | 0.1   |

| 7.1  |                | 特長                                    |       |

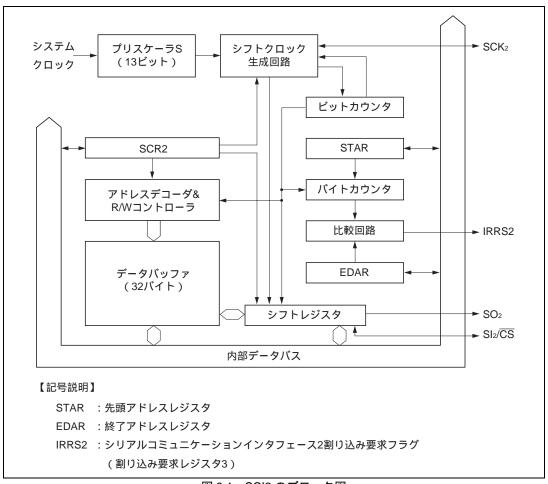

|      | 9.1.1<br>9.1.2 | 特長<br>ブロック図                           |       |

|      | 9.1.2          | ジロック図<br>端子構成                         |       |

|      | 9.1.3<br>9.1.4 | - 場工構成                                |       |

| 9.2  |                | ンスター構成                                |       |

| 9.2  |                |                                       |       |

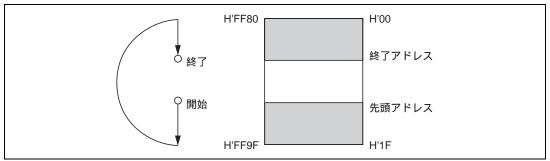

|      | 9.2.1          | 先頭アドレスレジスタ (STAR)                     |       |

|      | 9.2.2          | 終了アドレスレジスタ(EDAR)                      |       |

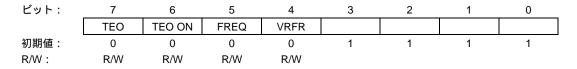

|      | 9.2.3          | シリアルコントロールレジスタ 2 ( SCR2 )             |       |

|      | 9.2.4<br>9.2.5 | ステータスレジスタ(STSR)                       |       |

| 9.3  | ,. <u>_</u>    | ポートモードレジスタ 3(PMR3)                    |       |

| 9.3  |                |                                       |       |

|      | 9.3.1          | 概要                                    |       |

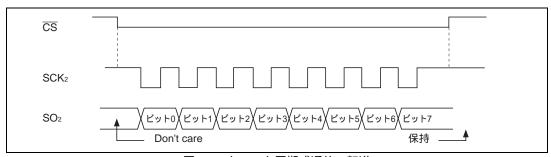

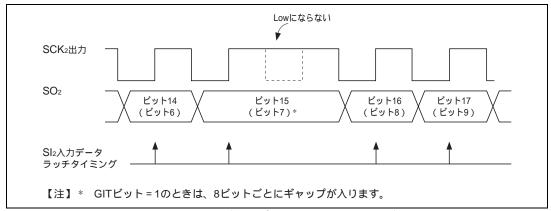

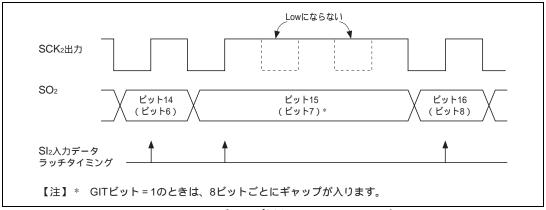

|      | 9.3.2          | クロック                                  |       |

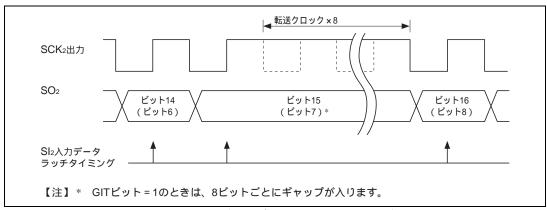

|      | 9.3.3          | データ転送フォーマット                           |       |

| 0.4  | 9.3.4          | データの送信または受信動作                         |       |

| 9.4  |                | .み要因                                  |       |

| 9.5  | 使用上            | の注意事項                                 | 9-12  |

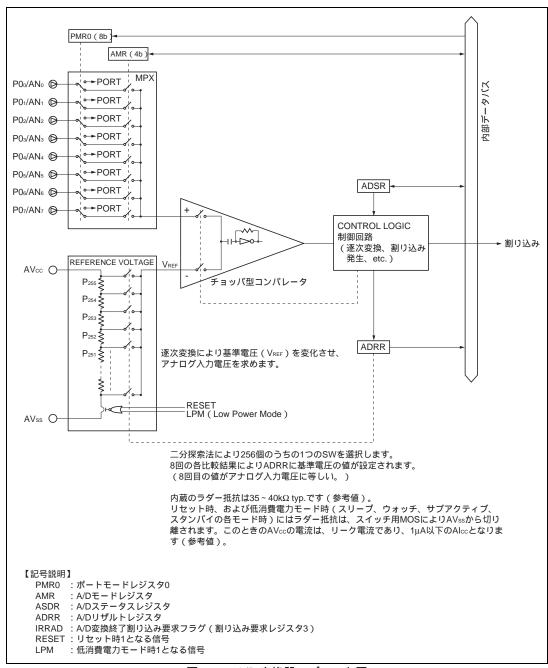

| 第 10 | )章 A/C         | )<br>変換器                              |       |

| 10.1 | 概要             |                                       | 10-1  |

|      | 10.1.1         | 特長                                    | 10-1  |

|      | 10.1.2         | ブロック図                                 |       |

|      | 10.1.3         | 端子構成                                  |       |

|      | 10.1.4         | レジスタ構成                                | 10-3  |

| 10.2 | 各レジ            | `スタの説明                                | 10-3  |

|      | 10.2.1         | A/D リザルトレジスタ(ADRR)                    | 10-3  |

|      | 10.2.2         | A/D モードレジスタ ( AMR )                   |       |

|      | 10.2.3         | A/D スタートレジスタ ( ADSR )                 |       |

|      | 10.2.4         | ポートモードレジスタ 0 ( PMR0 )                 |       |

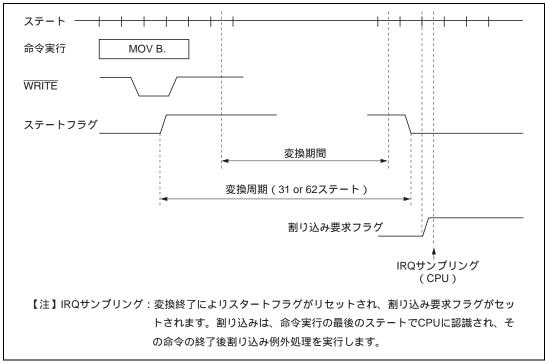

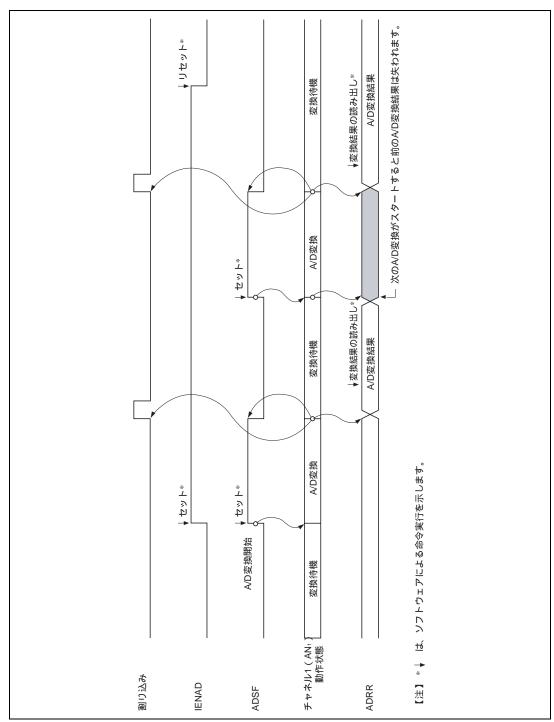

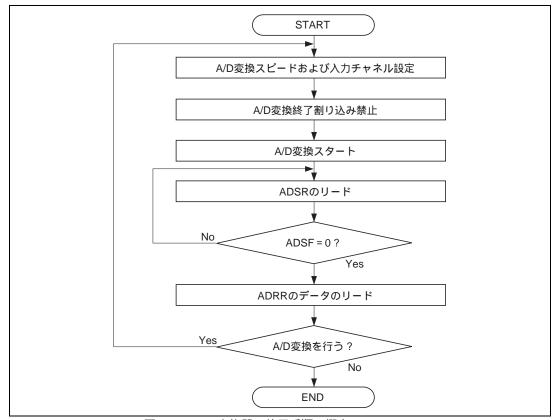

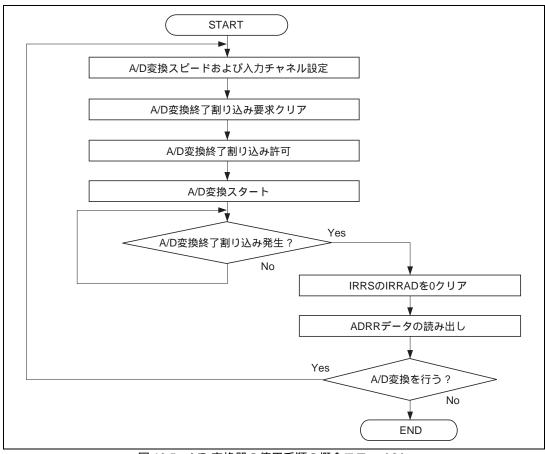

| 10.3 | 動作説            | 明                                     |       |

| 10.4 | 割り込            | み要因                                   | 10-7  |

| 10.5 | 使用例            |                                       | 10-7  |

| 10.6 | 使用上            | の注意                                   | 10-10 |

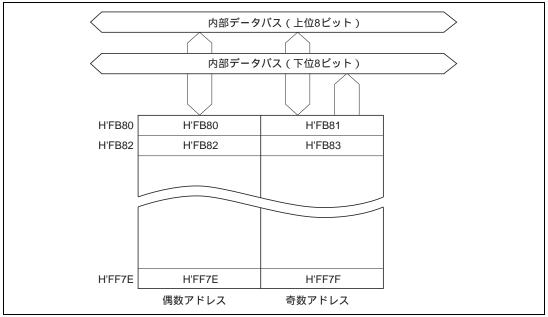

## 第11章 RAM

| 11.1       | 概要               |                                        | 11-1 |

|------------|------------------|----------------------------------------|------|

|            | 11.1.1           | ブロック図                                  | 11-1 |

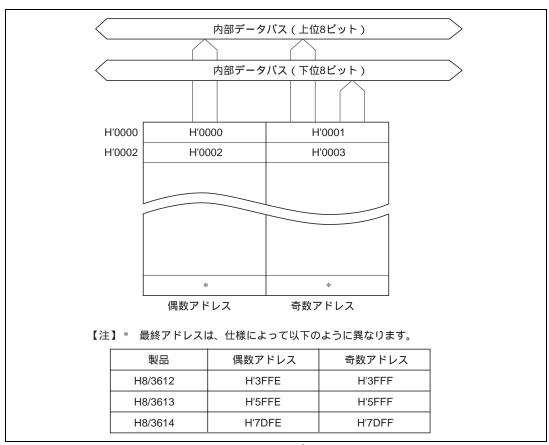

| 笋 12       | 章 RO             | MA                                     |      |

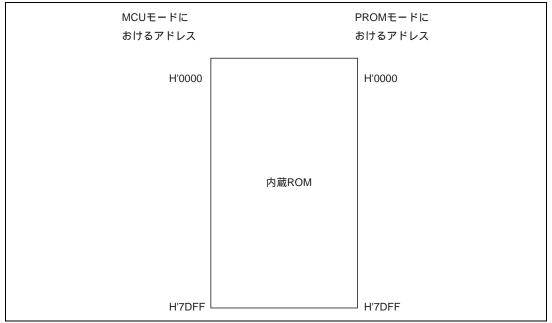

| 12.1       |                  | ····                                   | 12-1 |

| 12.1       |                  | ブロック図                                  |      |

| 12.2       |                  | モード                                    |      |

|            | 12.2.1           | PROM モードの設定                            |      |

|            | 12.2.2           | ソケットアダプタの端子対応とメモリマップ                   |      |

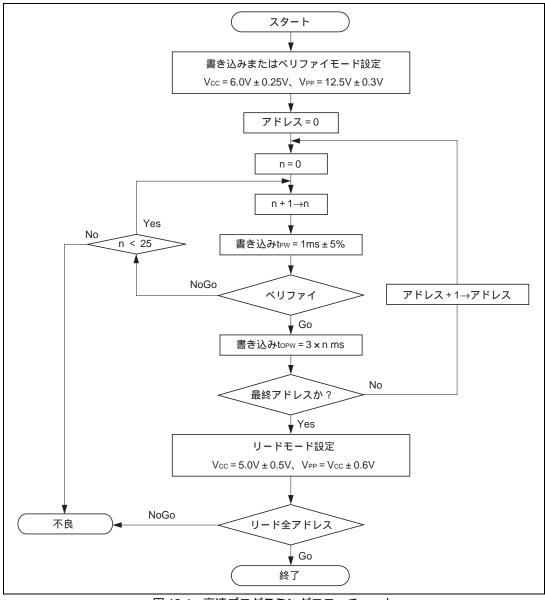

| 12.3       | プログ              | <sup>-</sup> ラミング                      |      |

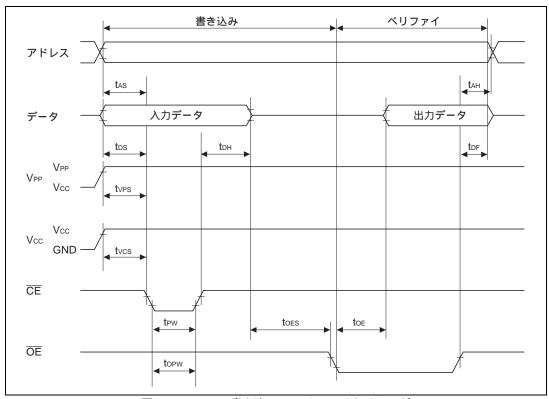

|            | 12.3.1           | 書き込みとベリファイ                             |      |

|            | 12.3.2           | 書き込み時の注意                               |      |

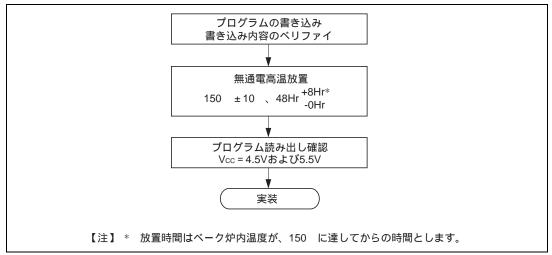

|            | 12.3.3           | 書き込み後の信頼性                              | 12-8 |

| 第 13       | 章 電気             | <b>贰的特性</b>                            |      |

| 13.1       |                  | 大定格                                    | 13-1 |

| 13.2       | HD6473           | 3614 の電気的特性                            |      |

|            | 13.2.1           | HD6473614 の DC 特性                      |      |

|            | 13.2.2           | HD6473614 の AC 特性                      |      |

|            | 13.2.3           | HD6473614 の A/D 変換器特性                  |      |

| 13.3       | HD6433           | 3613、HD6433614 の電気的特性                  |      |

|            | 13.3.1           | HD6433613、HD6433614 の DC 特性            |      |

|            | 13.3.2           | HD6433613、HD6433614 の AC 特性            |      |

| 12.4       | 13.3.3           | HD6433613、HD6433614のA/D変換器特性3612の電気的特性 |      |

| 13.4       |                  |                                        |      |

|            | 13.4.1           | HD6433612 の DC 特性<br>HD6433612 の AC 特性 |      |

|            | 13.4.2<br>13.4.3 | HD6433612 の A/D 変換器特性                  |      |

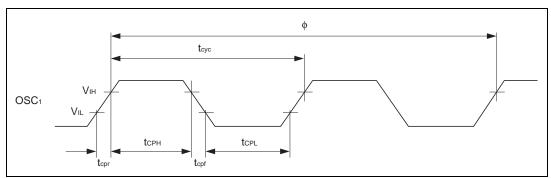

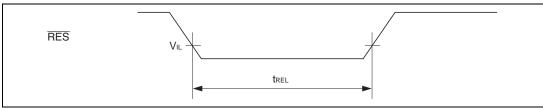

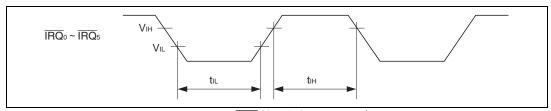

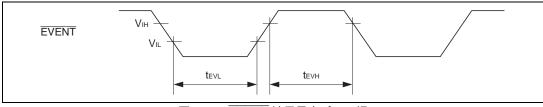

| 13.5       |                  | イミング                                   |      |

| 13.6       |                  | ROM 版と ZTAT 版の電気的特性の相違点                |      |

| / <b>-</b> |                  |                                        |      |

| 付録         |                  |                                        | (145 |

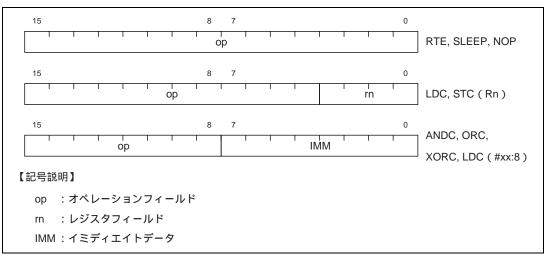

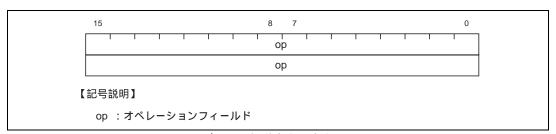

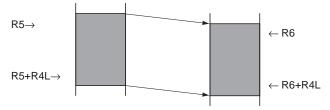

| A.         | 命令               |                                        | 付録-1 |

|            | A.1              | 命令一覧                                   | 付録-1 |

|            | A.2              | オペレーションコードマップ                          |      |

| В.         | A.3              | 命令実行ステート数     ター覧                      |      |

| <b>D</b> . |                  | ッ一見                                    |      |

|            | B.1<br>B.2       | I/O レジスター覧(1)<br>I/O レジスター覧(2)         |      |

| C.         |                  | - I/O レンスター見(2)ートプロック図                 |      |

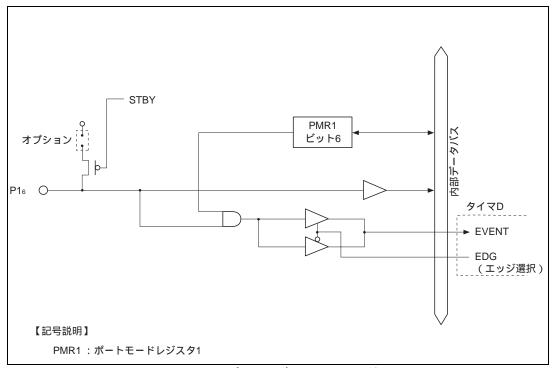

| C.         | C.1              | ポート 0 ブロック図                            |      |

|            | C.1              | <b>小一 [・0 ノロッソ凶</b>                    |      |

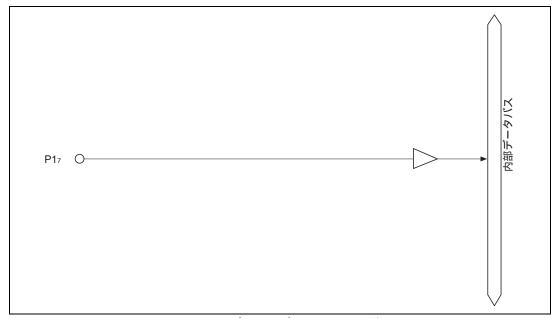

|    | C.2 ポート 1 ブロック図 | 付録-38 |

|----|-----------------|-------|

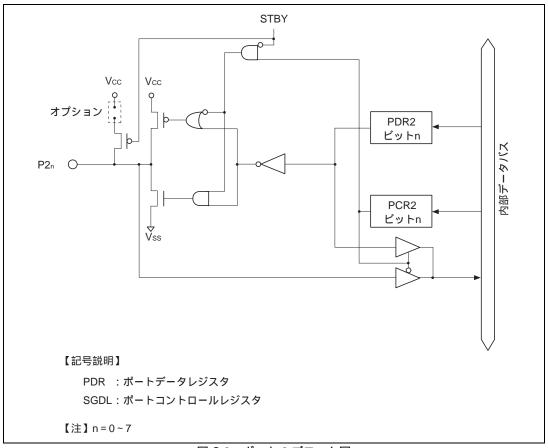

|    | C.3 ポート 2 ブロック図 |       |

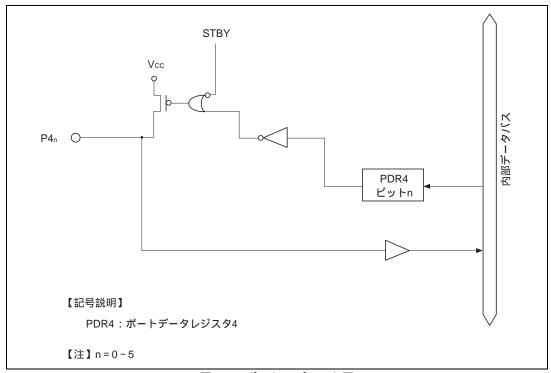

|    | C.4 ポート 4 ブロック図 | 付録-43 |

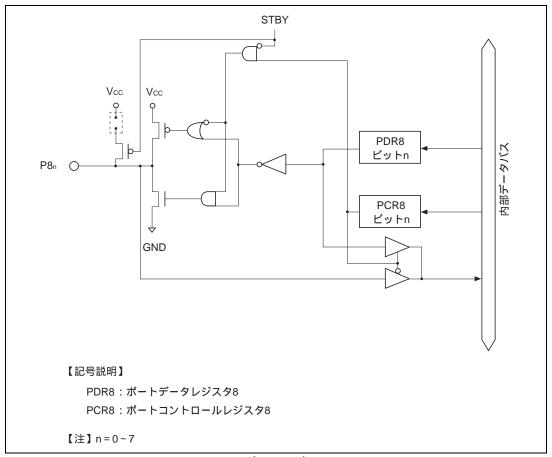

|    | C.5 ポート 8 ブロック図 | 付録-44 |

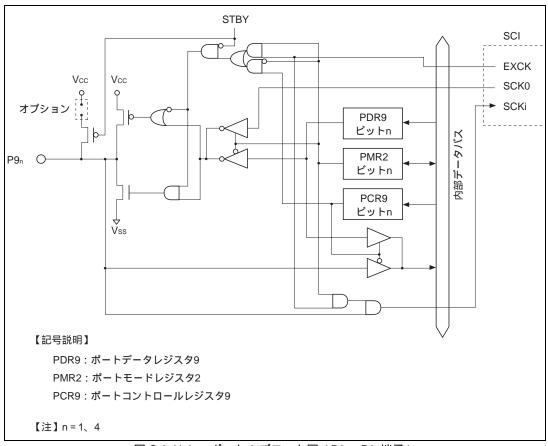

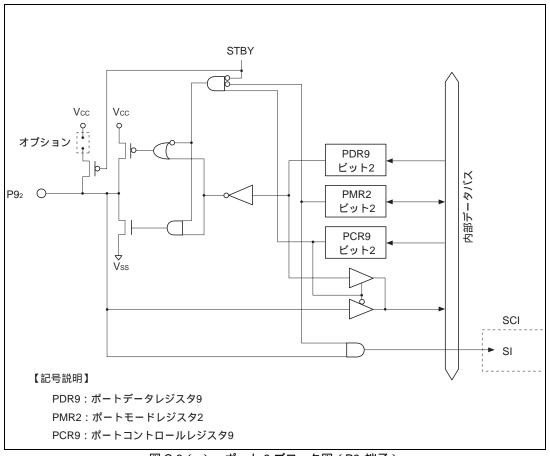

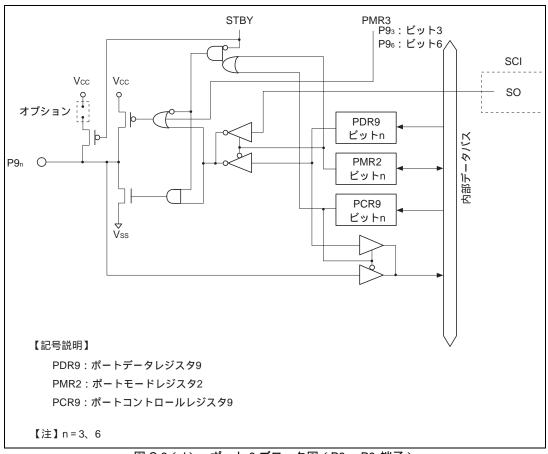

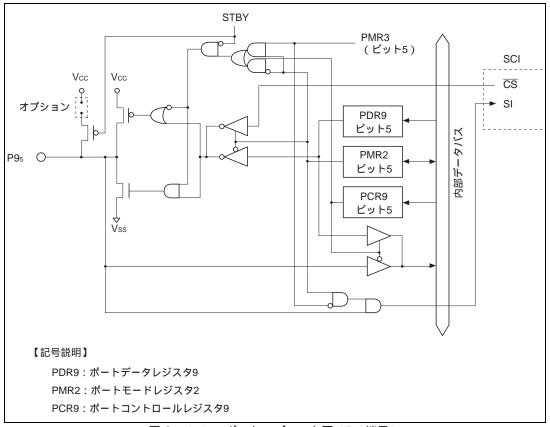

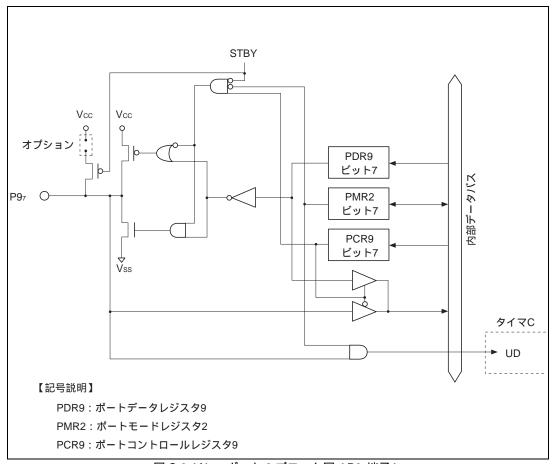

|    | C.6 ポート 9 ブロック図 |       |

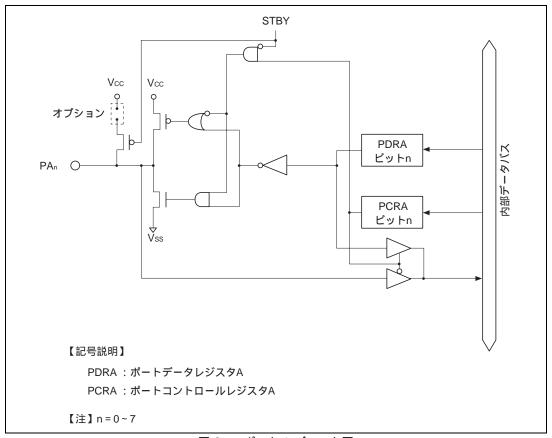

|    | C.7 ポート A ブロック図 |       |

| D. | 各処理状態におけるポートの状態 |       |

| E. | マスクオプションリスト     | 付録-53 |

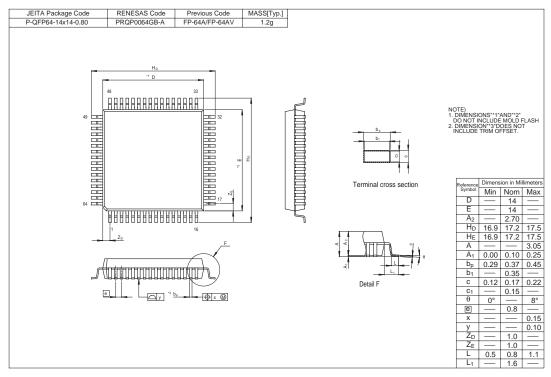

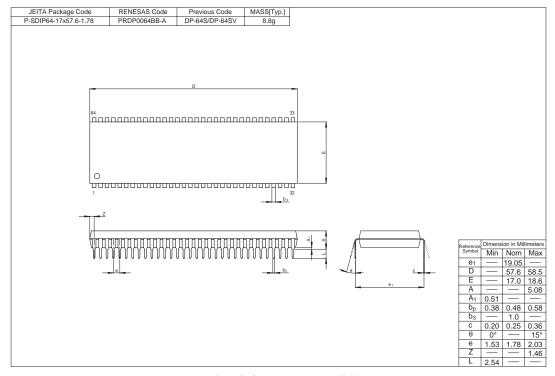

| F. | 外形寸法図           | 付録-54 |

# 1. 概要

# 1.1 概要

H8/300L シリーズは、高速 H8/300L CPU を核にして、システム構成に必要な周辺機能を集積したシングルチップマイクロコンピュータです。

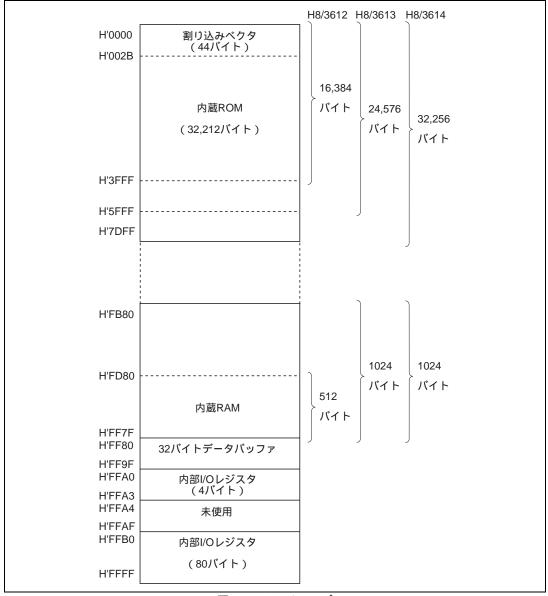

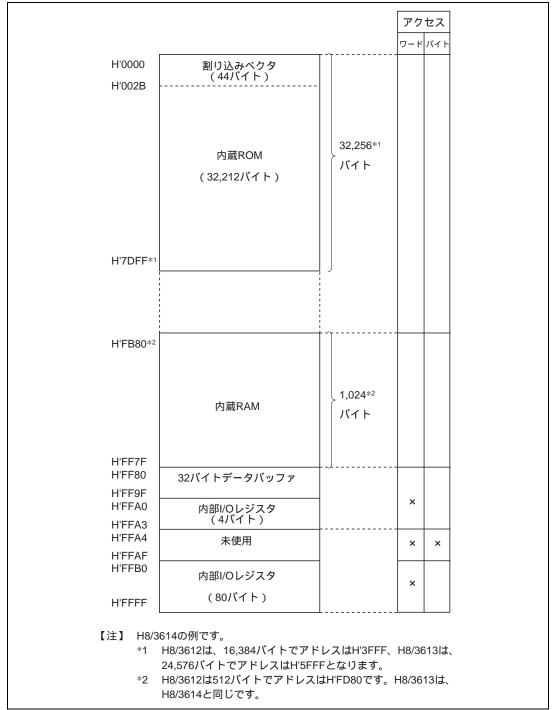

H8/3614 グループは H8/300L シリーズのシングルチップマイクロコンピュータで、周辺機能として 5 種類のタイマ、14 ビット PWM、2 チャネルのシリアルコミュニケーションインタフェース、A/D 変換器などを内蔵しています。ただし、H8/3612 は 14 ビット PWM を内蔵していません。H8/3614 グループには、16K バイトの ROM、512 バイトの RAM を内蔵した H8/3612、24K バイトの ROM、1024 バイトの RAM を内蔵した H8/3613、32K バイトの ROM、1024 バイトの RAM を内蔵した 1024 の RAM を内蔵した 1024 の RAM を内蔵した 10

H8/3614 にはユーザサイドで自由にプログラムの書き込みができる PROM を内蔵した ZTAT 版もあります。

本 LSI の特長を表 1.1 に示します。

【注】\* ZTAT ( Zero Turn Around Time ) は ( 株 ) ルネサス テクノロジの登録商標です。

表 1.1 特長

|      | 表 1.1 特長                                           |

|------|----------------------------------------------------|

| 項目   | 仕 様                                                |

| CPU  | 高速 H8/300L CPU                                     |

|      | (1) 汎用レジスタマシン                                      |

|      | ● 汎用レジスタ : 8 ビット×16 本                              |

|      | (16 ビット×8 本としても使用可能)                               |

|      | (2) 動作速度                                           |

|      | ● 最高動作周波数:4.19MHz                                  |

|      | ● 加減算:0.5μs(φ = 4MHz 動作時)                          |

|      | ● 乗除算:3.5μs(φ = 4MHz 動作時)                          |

|      | ● 32kHz サブクロックによる動作可能                              |

|      | (3) H8/300CPU と互換性のある命令体系                          |

|      | <ul><li>● 2 バイトまたは 4 バイト長の命令</li></ul>             |

|      | ・ レジスタ - レジスタ間の基本演算                                |

|      | ● MOV 命令によるメモリ - レジスタ間データ転送                        |

|      | (4) 特長ある命令                                         |

|      | <ul><li>◆ 乗算命令(8ビット×8ビット)</li></ul>                |

|      | ● 除算命令 (16 ビット÷8 ビット)                              |

|      | • ビットアキュムレータ命令                                     |

|      | • レジスタ間接指定によりビット位置の指定が可能                           |

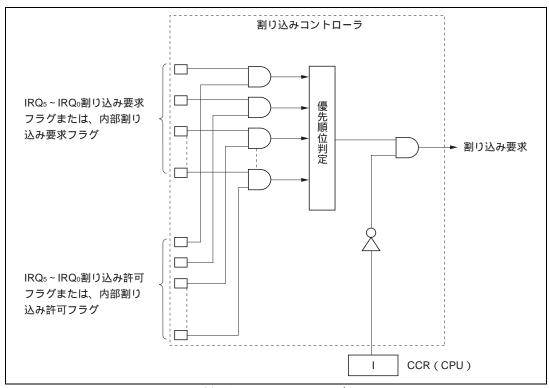

| 割り込み | 15 種類の割り込み要因                                       |

|      | ● 外部割り込み端子 6 本:IRQ <sub>5</sub> ~ IRQ <sub>6</sub> |

|      | ● 内部割り込み要因 9要因                                     |

| 項目                       | 仕 様                                                                         |

|--------------------------|-----------------------------------------------------------------------------|

|                          | 4 種類の低消費電力モード                                                               |

| 18.071332 273 2          | • スリープモード                                                                   |

|                          | • スタンバイモード                                                                  |

|                          | • ウォッチモード                                                                   |

|                          | • サブアクティブモード                                                                |

| クロック発振器                  | 2 種類のクロック発振器内蔵                                                              |

|                          | ● システムクロック発振器 : 1~8.4MHz                                                    |

|                          | ● サブクロック発振器 : 32.768kHz                                                     |

| I/O ポート                  | I/O ポート 54 本                                                                |

|                          | • PMOS オープンドレイン入出力端子 6 本                                                    |

|                          | ● 入出力端子 38 本                                                                |

|                          | ● 入力端子 10 本                                                                 |

| タイマ                      | 5種類のタイマ内蔵                                                                   |

|                          | (1) タイマ A:8 ビットインターバルタイマ                                                    |

|                          | <ul><li>● システムクロック(♠)*¹を分周した8種類の内部クロックまたはサブクロック(♠<sub>SUB</sub>)を</li></ul> |

|                          | 分周した4種類のクロックによりカウントアップ可能                                                    |

|                          | ● サブクロック動作とすることで時計用タイムベースとして使用可能                                            |

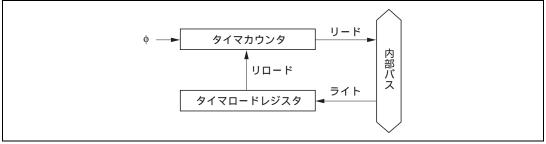

|                          | (2) タイマB:8ビットリロードタイマ                                                        |

|                          | ● 7種類の内部クロックまたはP1。/IRQ。端子からのイベント入力によるカウントアップ可能                              |

|                          | (3) タイマ C: 8 ビットリロードタイマ                                                     |

|                          | ● 7種類の内部クロックまたは P1,/IRQ, 端子からのイベント入力によるカウントアップ / ダウン可能                      |

|                          | (4) タイマ D:8 ビットイベントカウンタ                                                     |

|                          | ● P1 <sub>/</sub> EVENT 端子からのイベント入力によるカウントアップ                               |

|                          | (5) タイマ E: 8 ビットリロードタイマ                                                     |

|                          | • 8種類の内部クロックによるカウントアップ可能                                                    |

|                          | P1。/IRQ。/TMOE 端子より固定周波数出力、またはタイマ E のオーバフローによるデューティ 50%の方形波出力可能              |

| 14 ビット PWM* <sup>2</sup> | リップル低減を図ったパルス分割方式 PWM                                                       |

|                          | • 外部にローパスフィルタを接続することで 14 ビット D/A 交換器として使用可能                                 |

| シリアルコミュニ                 | 2 チャネルのシリアルコミュニケーションインタフェース内蔵                                               |

| ケーションインタ                 | (1) SCI1: クロック同期式                                                           |

| フェース (SCI)               | • 8 ビットまたは 16 ビットの転送データを選択可能                                                |

|                          | (2) SCI2:8ビットクロック同期式                                                        |

|                          | • 32 バイトのデータを自動的に転送可能                                                       |

| A/D 変換器                  | 抵抗ラダー方式による逐次比較方式の 8 ビット A/D 変換器                                             |

|                          | • 8 チャネルのアナログ入力端子                                                           |

|                          | ● 変換時間:1 チャネル当たり31 / ∮または62 / ∮                                             |

| メモリ                      | 大容量メモリ内蔵                                                                    |

|                          | ROM 16K バイト、RAM 512 バイト版(H8/3612)                                           |

|                          | ROM 24K バイト、RAM 1024 バイト版(H8/3613)                                          |

|                          | ROM 32K バイト、RAM 1024 バイト版(H8/3614)                                          |

|                          | PROM 32K バイト、RAM 1024 バイト版(H8/3614ZTAT)                                     |

| 項目       |            |            | 仕 様                 |              |

|----------|------------|------------|---------------------|--------------|

| 製品ラインアップ | 製品         | 型名         | パッケージ               | ROM/RAMサイズ   |

|          | マスクROM版    | ZTAT版      | ハッケーシ               | ROW/RAW 91 A |

|          | HD6433612H | -          | 64ピンQFP (FP-64A)    | ROM 16Kバイト   |

|          | HD6433612P | -          | 64ピンSDIP ( DP-64S ) | RAM 512バイト   |

|          | HD6433613H | -          | 64ピンQFP (FP-64A)    | ROM 24Kバイト   |

|          | HD6433613P | -          | 64ピンSDIP ( DP-64S ) | RAM 1024バイト  |

|          | HD6433614H | HD6473614H | 64ピンQFP (FP-64A)    | ROM 32Kバイト   |

|          | HD6433614P | HD6473614P | 64ピンSDIP ( DP-64S ) | RAM 1024バイト  |

<sup>【</sup>注】 \*1 фは、原発振を 1/2 分周したクロックを示します。

<sup>\*2</sup> H8/3612 には本機能はありません。

# 1.2 内部ブロック図

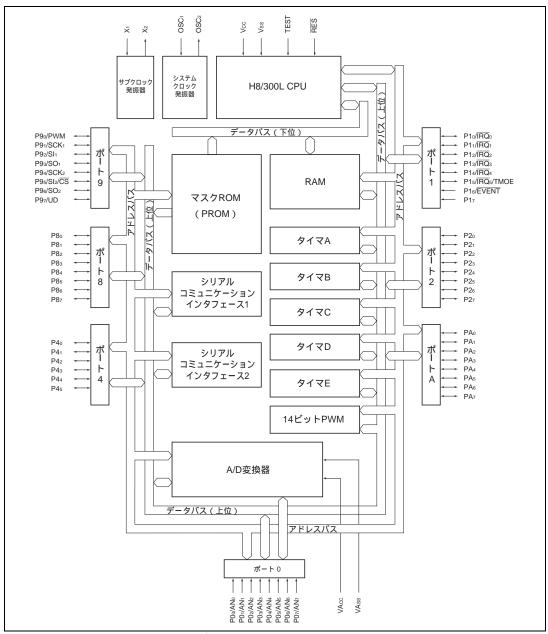

H8/3612 の内部ブロック図を図 1.1 に、H8/3613 および H8/3614 の内部ブロック図を図 1.2 に示します。

図 1.1 内部ブロック図 (H8/3612 の場合)

図 1.2 内部ブロック図 (H8/3613、H8/3614 の場合)

# 1.3 端子説明

# 1.3.1 ピン配置

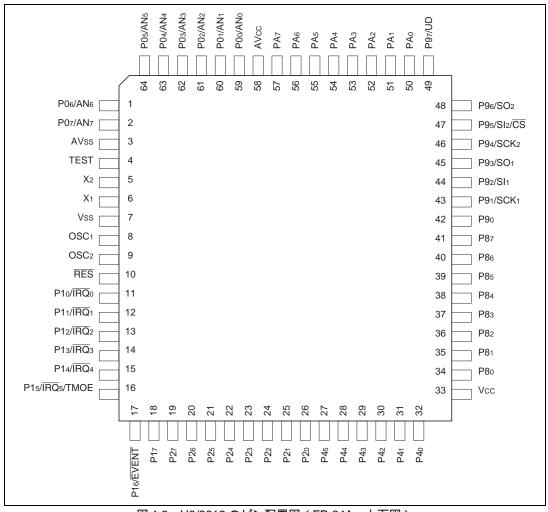

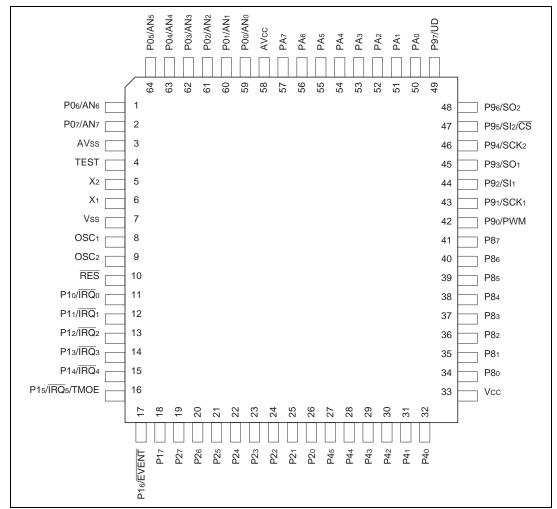

H8/3612 のピン配置図を図 1.3、図 1.4、H8/3613 および H8/3614 のピン配置図を図 1.5、図 1.6 に示します。

図 1.3 H8/3612 のピン配置図 (FP-64A:上面図)

| PA7              | 1 64  | PA6             |

|------------------|-------|-----------------|

| AVcc             | 2 63  | PA5             |

| P0o/ANo          | 3 62  | PA4             |

| P01/AN1          | 4 61  | PA <sub>3</sub> |

| P02/AN2          | 5 60  | PA <sub>2</sub> |

| P03/AN3          | 6 59  | PA1             |

| P04/AN4          | 7 58  | PA <sub>0</sub> |

| P05/AN5          | 8 57  | P97/UD          |

| P06/AN6          | 9 56  | P96/SO2         |

| P07/AN7          | 10 55 | P95/SI2/CS      |

| AVss             | 11 54 | P94/SCK2        |

| TEST             | 12 53 | P93/SO1         |

| X2               | 13 52 | P92/SI1         |

| X1               | 14 51 | P91/SCK1        |

| Vss              | 15 50 | P90             |

| OSC1             | 16 49 | P87             |

| OSC <sub>2</sub> | 17 48 | P86             |

| RES              | 18 47 | P85             |

| P1o/IRQo         | 19 46 | P84             |

| P11/IRQ1         | 20 45 | P83             |

| P12/IRQ2         | 21 44 | P82             |

| P13/IRQ3         | 22 43 | P81             |

| P14/IRQ4         | 23 42 | P80             |

| P1s/IRQs/TMOE    | 24 41 | Vcc             |

| P16/EVENT        | 25 40 | P40             |

| P17              | 26 39 | P41             |

| P27              | 27 38 | P42             |

| P26              | 28 37 | P43             |

| P25              | 29 36 | P44             |

| P24              | 30 35 | P45             |

| P23              | 31 34 | P20             |

| P22              | 32 33 | P21             |

|                  |       |                 |

図 1.4 H8/3612 のピン配置図 (DP-64S:上面図)

図 1.5 H8/3613、H8/3614 のピン配置図 (FP-64A:上面図)

| PA7              | 1 64  | PA6             |

|------------------|-------|-----------------|

| AVcc             | 2 63  | PA <sub>5</sub> |

| P0o/ANo          | 3 62  | PA4             |

| P01/AN1          | 4 61  | PA <sub>3</sub> |

| P02/AN2          | 5 60  | PA <sub>2</sub> |

| P03/AN3          | 6 59  | PA1             |

| P04/AN4          | 7 58  | PA <sub>0</sub> |

| P05/AN5          | 8 57  | P97/UD          |

| P06/AN6          | 9 56  | P96/SO2         |

| P07/AN7          | 10 55 | P95/SI2/CS      |

| AVss             | 11 54 | P94/SCK2        |

| TEST             | 12 53 | P93/SO1         |

| X2               | 13 52 | P92/SI1         |

| X1               | 14 51 | P91/SCK1        |

| Vss              | 15 50 | P90/PWM         |

| OSC1             | 16 49 | P87             |

| OSC <sub>2</sub> | 17 48 | P86             |

| RES              | 18 47 | P85             |

| P10/IRQ0         | 19 46 | P84             |

| P11/IRQ1         | 20 45 | P83             |

| P12/IRQ2         | 21 44 | P82             |

| P13/IRQ3         | 22 43 | P81             |

| P14/IRQ4         | 23 42 | P80             |

| P1s/IRQs/TMOE    | 24 41 | Vcc             |

| P16/EVENT        | 25 40 | P40             |

| P17              | 26 39 | P41             |

| P27              | 27 38 | P42             |

| P26              | 28 37 | P43             |

| P25              | 29 36 | P44             |

| P24              | 30 35 | P45             |

| P23              | 31 34 | P20             |

| P22              | 32 33 | P21             |

|                  |       |                 |

図 1.6 H8/3613、H8/3614 のピン配置図 (DP-64S:上面図)

# 1.3.2 端子機能

各端子の機能について表 1.3 に示します。

表 1.3 端子機能

|                |                  | ا^^،   | <del></del><br>番号 | ر زاالا | , ,,,,,,,                                                                                                                          |

|----------------|------------------|--------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 分類             | 記号               | FP-64A | DP-64S            | 入出力     | 機能                                                                                                                                 |

| 電源             | V <sub>cc</sub>  | 33     | 41                | 入力      | 電源 $V_{cc}$ 端子は、システムの電源(+5V)に接続してください。                                                                                             |

|                | V <sub>ss</sub>  | 7      | 15                | 入力      | グランド<br>V <sub>ss</sub> 端子は、システムの電源(OV)に接続してくださ<br>い。                                                                              |

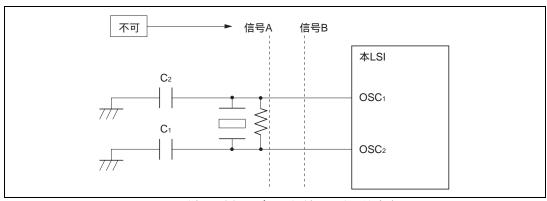

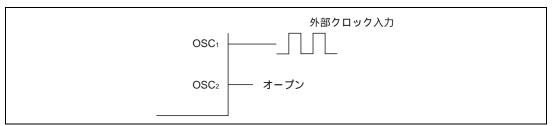

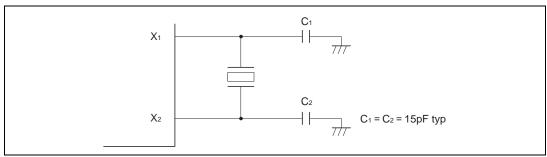

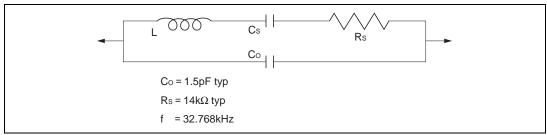

|                | $AV_cc$          | 58     | 2                 | 入力      | アナログ電源<br>A/D 変換器用電源端子です。A/D 変換器を使用しない場合、システムの電源(+5V)に接続してください。                                                                    |