### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **User's Manual**

# **PFESiP<sup>®</sup> EP-1 Evaluation Board**

**FPGA Design Guide**

This document is valid in Japan.

Document No. A19351EJ1V1UM00 (1st Edition) Date published November 2008 NS

2

#### **(1)** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must have hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **(6)** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

PFESiP is a registered trademark of NEC Electronics Corporation in Japan, Germany, and United Kingdom. The Xilinx logo and Virtex are registered trademarks of Xilinx, Inc. in the United States. Visual Elite and Summit Design are trademarks of Summit Design, Inc.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of November, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

To obtain the latest documents when designing, contact an NEC sales office or a distributor.

#### PREFACE

- Readers This manual is intended for users who understand the functions of the microcontroller function chip with an on-chip V850E2 CPU core (PFESiP/V850EP1) and wish to evaluate developing PFESiP EP-1 Series products using the chip. This document is valid in Japan.

- Purpose This manual is intended to help users, who wish to evaluate full-scale prototyping of PFESiP EP-1 Series products using the PFESiP/V850EP1, understand how to use the development evaluation board. Using the PFESiP EP-1 Evaluation Board Lite is recommended for users evaluating the introduction of PFESiP EP-1 Series products.

- How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, microcontrollers, SRAM, page ROM, and SDRAM.

| Conventions | Data significance:<br>Active low representation: | Higher digits on the left and lower digits on the right xxxZ (Add Z after pin or signal name) |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|

|             | Note:                                            | Footnote for item marked with <b>Note</b> in the text                                         |

|             | Caution                                          | Information requiring particular attention                                                    |

|             | Remark:                                          | Supplementary information                                                                     |

|             | Numeric representation:                          | Binary XXXX or XXXXB                                                                          |

|             |                                                  | DecimalXXXX                                                                                   |

|             |                                                  | HexadecimalXXXXH                                                                              |

|             | Prefix indicating power of 2                     |                                                                                               |

|             | (address space, memory capacity):                | K (kilo): 2 <sup>10</sup> = 1,024                                                             |

|             |                                                  | M (mega): 2 <sup>20</sup> = 1,024 <sup>2</sup>                                                |

|             |                                                  | G (giga): 2 <sup>30</sup> = 1,024 <sup>3</sup>                                                |

| Data        | a type:                                          | Word 32 bits                                                                                  |

|             |                                                  | Halfword 16 bits                                                                              |

|             |                                                  | Byte 8 bits                                                                                   |

|             |                                                  |                                                                                               |

# Related Documents The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such. Furthermore, some related documents may be intended for individual customers, because the documents are prepared in the development/planning stage of each core.

#### **Documents related to PFESiP EP-1 Series**

| Document Name                                               | Document No. |

|-------------------------------------------------------------|--------------|

| V850E2 Architecture User's Manual                           | U17135E      |

| PFESiP EP-1 Series Design Manual                            | A19068E      |

| PFESiP/V850EP1 Product Data User's Manual                   | A19069E      |

| PFESiP/V850EP1 Hardware (CPU Function) User's Manual        | A19070E      |

| PFESiP/V850EP1 Hardware (USB Function) User's Manual        | A19071E      |

| PFESiP/V850EP1 USB Function Sample Sofware Application Note | A19349E      |

#### Documents related to PFESiP EP-1 Evaluation Board

| Document Name                                                         | Document No. |

|-----------------------------------------------------------------------|--------------|

| PFESiP EP-1 Evaluation Board Technical Information User's Manual      | A19350E      |

| PFESiP EP-1 Evaluation Board Ordering Information User's Manual       | A19352E      |

| PFESiP EP-1 Evaluation Board FPGA Design Guide User's Manual          | This manual  |

| PFESiP EP-1 Evaluation Board Lite Technical Information User's Manual | A19354E      |

#### Documents related to development tools (User's Manual)

| Document N                                  | lame         |               | Document No. |

|---------------------------------------------|--------------|---------------|--------------|

| RX850 Pro (Real-time OS)                    | Ver.3.21     | Basics        | U18165E      |

|                                             | Ver.3.20     | Installation  | U17421E      |

|                                             | Ver.3.21     | Technical     | U18164E      |

|                                             | Ver.3.20     | Task Debugger | U17422E      |

| PM+ Ver.6.30 Project Manager                |              |               | U18416E      |

| QB-V850MINI On-chip Debug Emulator          |              |               | U17638E      |

| ID850QB Ver.3.20 Integrated Debugger        | Operation    |               | U17964E      |

| RX850V4 Ver.4.22 Real-Time OS               | Fanctionalit | lies          | U16643E      |

|                                             | Task Debug   | gger          | U16811E      |

| AZ850V4 Ver.4.10 System Performance Analyze | r            |               | U17093J      |

#### **Documents related to FPGA (Reference)**

| Document Name                                                                     | Document No.  |

|-----------------------------------------------------------------------------------|---------------|

| Fundamentals of FPGA Design v8 (issued by Technical Support Center, Xilinx, Inc.) | Rev1.1 '06/03 |

This document is a training course textbook for persons starting to design Xilinx FPGAs by using the ISE software tool. This document cannot be downloaded from the Xilinx Web site. Please note that the training course is offered free of charge and attending the course is recommended. See the following URL for details.

http://japan.xilinx.com/support/training/abstracts/fundamentals.htm

A few copies of the document are available and can be lent out if obtaining the document is difficult. Contact pfesip@ml.necel.com if a copy is needed.

#### CONTENTS

| CHAP.             | TER 1   | OVERVIEW                                                          | 10 |

|-------------------|---------|-------------------------------------------------------------------|----|

| 1.1               | Overvi  | ew of Board                                                       | 10 |

| 1.2               | On-Bo   | ard FPGA Use Range                                                | 11 |

| 1.3               | FPGA    | Design Procedure                                                  | 12 |

|                   | 1.3.1   | Design flow                                                       |    |

|                   | 1.3.2   | File flow                                                         | 13 |

| CHAP <sup>.</sup> | TER 2   | ISE 8.2 MANIPULATION PROCEDURE                                    | 14 |

| 2.1               | ISE Op  | otion Setting (Board Restrictions)                                | 14 |

| 2.2               | Source  | e File Preparation                                                | 14 |

|                   | 2.2.1   | HDL source preparation                                            | 14 |

|                   | 2.2.2   | Constraint file (pin layout constraint) preparation               | 14 |

|                   | 2.2.3   | Pin layout constraint check procedure                             |    |

| 2.3               | -       | t Creation                                                        |    |

| 2.4               |         | g Constraint Addition                                             |    |

| 2.5               | Impler  | nentation                                                         | 17 |

|                   | 2.5.1   | Implementation execution                                          |    |

|                   | 2.5.2   | Result check                                                      |    |

| 2.6               | BIT Fil | e Creation                                                        |    |

|                   | 2.6.1   | Unused-pin option setting                                         |    |

|                   | 2.6.2   | Generate execution                                                |    |

| 2.7               | PROM    | File Creation                                                     |    |

|                   | 2.7.1   | Wizard execution (1)                                              |    |

|                   | 2.7.2   | Wizard execution (2)                                              |    |

|                   | 2.7.3   | Generate execution                                                |    |

| 2.8               | Downl   | oad                                                               |    |

|                   | 2.8.1   | Download cable connection                                         |    |

|                   | 2.8.2   | Starting iMPACT                                                   |    |

|                   | 2.8.3   | Downloading to PROM                                               | 22 |

| CHAP              | TER 3   | FPGA UDL DESIGN GUIDE                                             | 23 |

| 3.1               | FPGA    | Pin Design                                                        |    |

|                   | 3.1.1   | Pins requiring processing                                         |    |

|                   | 3.1.2   | Unused pins                                                       | 23 |

|                   | 3.1.3   | FPGA-dedicated external circuit                                   |    |

|                   | 3.1.4   | Connection with PFESiP/V850EP1 system pins                        |    |

|                   | 3.1.5   | Connection with PFESiP/V850EP1 port (shared-function) pins        |    |

|                   | 3.1.6   | Connection with PFESiP/V850EP1 SiP internal memory interface pins |    |

|                   | 3.1.7   | Connection with PFESiP/V850EP1 external memory interface pins     |    |

#### LIST OF FIGURE

| jure No. Title                                          | Page                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                                                                                                                                                                     |

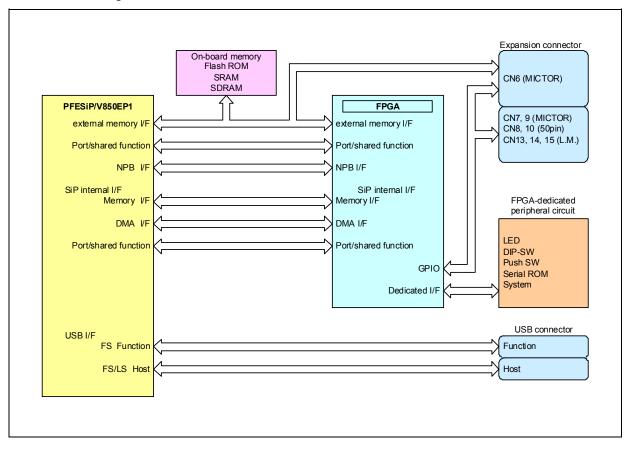

| Overview of Connections Between PFESiP/V850EP1 and FPGA | 11                                                                                                                                                                                                                                                                  |

| FPGA Design Flow                                        |                                                                                                                                                                                                                                                                     |

| File Correlation                                        |                                                                                                                                                                                                                                                                     |

|                                                         |                                                                                                                                                                                                                                                                     |

| PACE Execution Screen                                   |                                                                                                                                                                                                                                                                     |

| New Project Wizard Execution Screen                     |                                                                                                                                                                                                                                                                     |

| Wizard Execution Screen of iMPACT                       |                                                                                                                                                                                                                                                                     |

| Wizard End Screen of iMPACT                             |                                                                                                                                                                                                                                                                     |

| PROM Device Selection Screen                            |                                                                                                                                                                                                                                                                     |

| Programming Properties Setting Screen                   |                                                                                                                                                                                                                                                                     |

|                                                         | Overview of Connections Between PFESiP/V850EP1 and FPGA<br>FPGA Design Flow<br>File Correlation<br>PACE Execution Screen<br>New Project Wizard Execution Screen<br>Wizard Execution Screen of iMPACT<br>Wizard End Screen of iMPACT<br>PROM Device Selection Screen |

#### LIST OF TABLES

| Tal | ble No.                                            | Title       | Page |

|-----|----------------------------------------------------|-------------|------|

| 3-1 | FPGA Pins Requiring Processing                     |             | 23   |

| 3-2 | Unused FPGA Pins                                   |             | 23   |

| 3-3 | FPGA-Dedicated External Circuit Pins               |             | 24   |

| 3-4 | PFESiP/V850EP1 System Pin Connections              |             | 24   |

| 3-5 | PFESiP/V850EP1 Port (Shared) Pin Connections       |             | 25   |

| 3-6 | PFESiP/V850EP1 SiP Internal Memory Interface Pin C | Connections | 25   |

| 3-7 | PFESiP/V850EP1 External Memory Interface Pin Con   | nections    | 26   |

#### CHAPTER 1 OVERVIEW

The PFESiP EP-1 Evaluation Board is a development evaluation board for assisting the development of PFESiP EP-1 Series products.

It can be used for the software development of the PFESiP EP-1 Series-dedicated microcontroller PFESiP/V850EP1 and for user logic development and verification using the on-board FPGA.

The PFESiP/V850EP1 has an on-chip high-performance 32-bit RISC-type CPU core (V850E2 (NBA85E2S) core).

The basic functions of PFESiP EP-1 Series products based on the PFESiP/V850EP1 can be evaluated using this board.

As the on-board FPGA, the Virtex<sup>®</sup>-4 Family LX Series made by Xilinx<sup>®</sup> is employed and the XC4VLX40 is mounted as standard. The FPGA size can be changed.

This chapter describes how to use the FPGA mounted on the PFESiP EP-1 Evaluation Board.

#### 1.1 Overview of Board

The PFESiP EP-1 Evaluation Board is a development evaluation board for assisting the development of PFESiP EP-1 Series products.

The functions of the embedded array (EA-9HD) that is provided with the user logic paired with the PFESiP/V850EP1 within the PFESiP EP-1 Series SiP can be used for developing and verifying the user logic by integrating the functions into the on-board FPGA (Virtex-4 Family LX Series<sup>Note</sup> made by Xilinx).

Furthermore, a more systematic evaluation can be performed by connecting the PFESiP EP-1 Evaluation Board to the user board using system expansion connectors.

On-board memory required for a general system is also provided.

Note that the load capacitance of the PFESiP EP-1 Evaluation Board is not always equivalent, in contrast to the environment of actual SiP products, because the signals originally connected within the SiP are connected to the FPGA on-board.

NoteThe integration degree and the speed grade of the mounted FPGA differ for each board.See the PFESiP EP-1 Evaluation Board Selection Guide for the types of FPGAs that can be mounted.

#### 1.2 On-Board FPGA Use Range

With the SiP internal connection pins of the PFESiP/V850EP1, the peripheral circuits of the PFESiP/V850EP1 can be freely expanded within the FPGA, because almost all external I/Fs are connected to the FPGA. Furthermore, an external expansion board can be connected to the PFESiP/V850EP1 via the FPGA, because all expansion connectors are connected to the FPGA.

Caution Not all signals are connected to each interface. This must be separately checked.

#### 1.3 FPGA Design Procedure

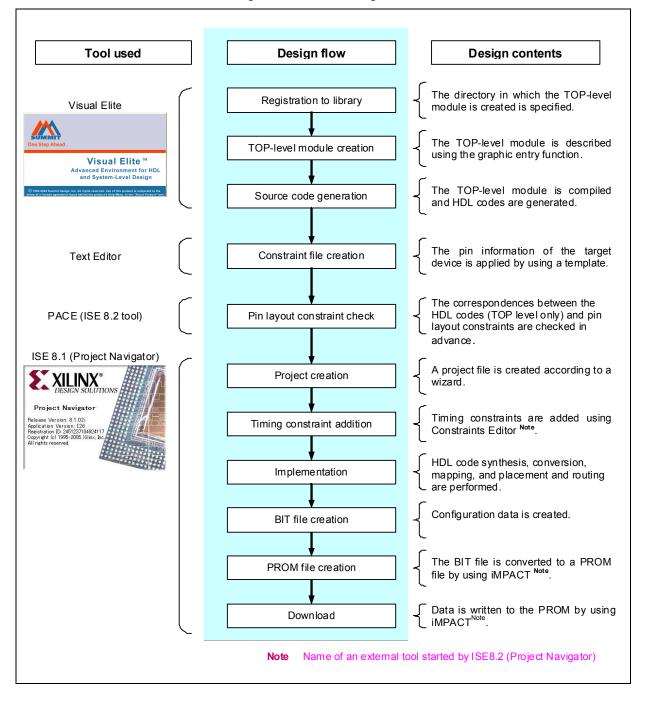

This section explains the procedure of the sequence from creating HDL source codes (mainly TOP level) using the Summit Design<sup>TM</sup> graphic entry tool Visual Elite<sup>TM</sup> 2006.1 and the Xilinx FPGA development tool ISE8.2 to logic synthesis of the HDL source codes, placement and routing, and downloading to the FPGA mounted on the PFESiP EP-1 Evaluation Board.

#### 1.3.1 Design flow

The development flow for FPGAs is shown below.

Figure 1-2. FPGA Design Flow

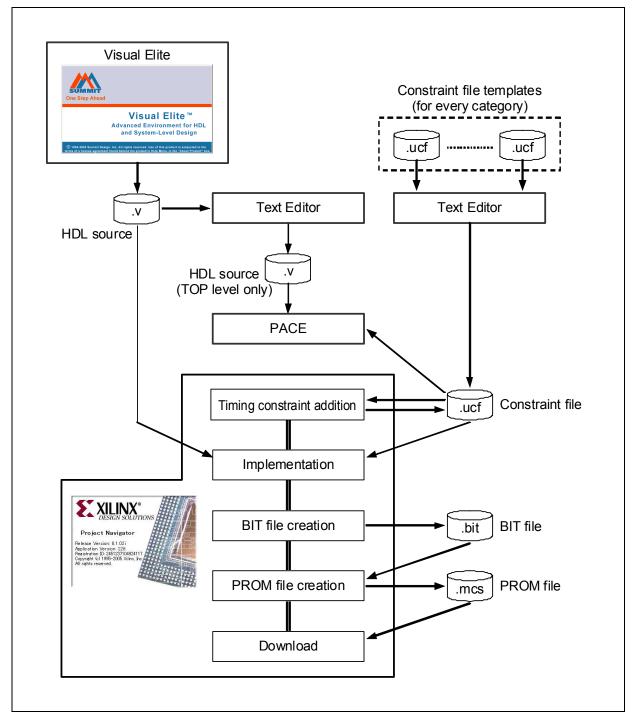

#### 1.3.2 File flow

The correlation of files in the development flow for FPGAs is shown below.

#### CHAPTER 2 ISE 8.2 MANIPULATION PROCEDURE

See the Xilinx seminar document, Fundamentals of FPGA Design v8 (Rev1.1, March 2006) for the ISE 8.2 (Project Navigator) manipulation procedure. (This document is written in Japanese.)

This chapter describes cautions and supplementary information regarding each step.

#### 2.1 ISE Option Setting (Board Restrictions)

#### Caution This option setting is a measure to handle the restrictions of the PFESiP EP-1 Evaluation Board. Cancel this setting for FPGA development other than for this board.

Set the environmental variables via the following procedure so that the clock input pin (N-side) of the FPGA can be used for the global clock.

- <1> Select [System] from the [Control Panel].

- <2> Select the [Detail Setting] tab.

- <3> Click the [Environmental Variables] button.

- <4> Click the [New] button of "System Environmental Variables".

- <5> Enter "XIL\_PLACE\_ALLOW\_LOCAL\_BUFG\_ROUTING" in "Variable Name".

- <6> Enter "1" in "Variable Value".

- <7> Click the [OK] button and end the setting (twice).

#### 2.2 Source File Preparation

#### 2.2.1 HDL source preparation

This section assumes that an HDL source is separately prepared.

#### 2.2.2 Constraint file (pin layout constraint) preparation

The pin names and pin layout of the PFESiP EP-1 Evaluation Board on-board FPGA are predetermined<sup>Note</sup>.

This information is provided as pin layout constraints in the form of template files (text files) (divided into multiple files of different categories). A constraint file can be easily created by extracting only the required pin layout information from these template files and including the information in a single file.

Note the following points when creating a constraint file.

- Comment out the definitions of unused pins, because an error occurs if definitions of unused pins are described (left) in the UCF.

- Change the default IOSTANDARD constraints to "LVCMOS33" n together with LOC, because the constraints are "LVCMOS25".

# This is already reflected in the template file.

- (Example) NET "pin\_name" LOC = "pin\_location" | IOSTANDARD = LVCMOS33 ;

- Pins not defined (omitted to be defined) in the UCF must be checked, because they are automatically assigned.

- **Note** Pin names can be arbitrarily changed, because changing pin names is not prohibited; however, be sure to reflect the changed pin names in the pin layout constraints.

#### 2.2.3 Pin layout constraint check procedure

The validity of the pin definitions and pin layout constraints of the HDL source can be checked in advance via the following procedure.

- <1> Create an HDL source in which only the TOP level is described.

- <2> Start PACE from the [Start] button.

- Click the [Start] button and select [All programs]  $\rightarrow$  [Xilinx ISE8.2]  $\rightarrow$  [Accessories]  $\rightarrow$  [PACE].

- <3> Specify the HDL source created in step <1>, the constraint file, and the target device.

- $\text{Click [File]} \rightarrow [\text{Open...]}.$

- [1] Constraints File: Set the constraint file.

- [2] Design File: Specify the HDL source.

- Click the [Select Parts] button and specify the target device.

- Family: Select "Vertex4".

- [3] Device: Specify the integration degree such as "XC4VLX40" or "XC4VLX80".

- Package: Select "FF1148".

- Speed: Specify a speed grade such as "–11".

Click the [OK] button.

<4> Check the results in the [Design Object List ? I/O Pins] window.

Confirm that the pin constraints are added in the "Loc" column for the listed "I/O Name".

- Cautions 1. Note that an I/O pin for which the "Loc" column is blank will be automatically reallocated. Make sure that the descriptions in the HDL source and pin layout constraints match and that pin layout is reliably performed.

- 2. If a pin to which the pin layout constraints are added is deleted (identified as an unused pin as a result) by HDL code synthesis, an error will occur during implementation.

| Xilinx PACE<br>File Help                |                  |            |     |           |

|-----------------------------------------|------------------|------------|-----|-----------|

| <b>□ ☞ 日</b> 🖶 🗠 🖊 🖊 🖾                  |                  |            |     | Q Q X Q 🖸 |

| New Constraints                         |                  | ×          |     |           |

| Design Flow                             |                  |            |     |           |

| Create new UCF for existing design      |                  |            |     |           |

| C Create new UCF & top-level HDL design |                  |            |     |           |

| L.                                      |                  |            |     |           |

| New Constraints (UCF) File:             |                  |            |     |           |

| C:\FPGA\sample\AuroraDefault.ucf        |                  | vse        |     |           |

| Input Design File:                      |                  |            |     |           |

| C:\FPGA\sample\AuroraDefault.v          | Biov             | vse        |     |           |

| Parttype:                               |                  |            |     |           |

| Select Part.                            | Part Selector    |            |     | ×         |

| J Select Take                           | Eamily: Virtex4  | )          | •   | ОК        |

|                                         | OK Device: XC4VL | ×40        |     | Cancel    |

|                                         | Package: FF114   | <u>,</u> ≻ | 3 - | Help      |

|                                         |                  |            |     |           |

|                                         | Speed Grade: 10  |            | -   |           |

#### Figure 2-1. PACE Execution Screen

#### 2.3 Project Creation

Remark Fundamentals of FPGA Design v8, 3a-13 to 3a-15

O ISE screen explanation, project creation

Create a new project by referring to the document in the remark mentioned above. Supplementary information regarding the setting items in the New Project Wizard is described below.

- <1> Specify the parent directory in which to create a project.

- <2> The project name entered is also reflected to <1> at the same time and becomes the project directory name.

- <3> Specify the target FPGA1 product type.

- Family: Select "Virtex-4".

- Device: Specify the integration degree such as "XC4VLX40" or "XC4VLX80".

- Packagev: Select "FF1148".

- Speed: Specify a speed grade such as "-11".

- <4> Page 3/5 is not required to be set (because a source is not created in ISE).

- <5> Specify the HDL source and constraint file.

<6> If these items are checked, the file specified in <5> will be copied to the project directory. Check these items if the source file is to be managed other than in the project directory.

<7> Execute reading of the specified source after clicking the [Finish] button on page 5/5 and end the setting.

| Project Name:  |                                                | roject Location                                   |                        |

|----------------|------------------------------------------------|---------------------------------------------------|------------------------|

| sample 🖉       |                                                |                                                   |                        |

| 15             | New Project Wizard - Device                    |                                                   |                        |

| Select the Typ | Select the Device and Design Flow              | v for the Project Page 2/5                        |                        |

| Top-Level Sou  | Property Name                                  | Value                                             |                        |

| HDL            | Product Category                               |                                                   |                        |

|                | Family                                         | Virtex4                                           |                        |

|                | Device                                         | XC4VLX40 > (3)                                    |                        |

|                | Package                                        | FF1148                                            |                        |

|                | Speed                                          |                                                   |                        |

|                | T 1 10 T                                       |                                                   |                        |

|                | Top-Level Source Type<br>Synthesis Tool        | HDL<br>XST Kew Project Wizard - Create New Source |                        |

|                | Simulator                                      |                                                   |                        |

|                |                                                | Create a New Source                               | Page 3/5     A         |

|                | Enable Enhanced Design Summa                   |                                                   | New Source             |

| More Info      | Enable Message Filtering                       | Source File Type                                  | Remove                 |

|                | Display Incremental Messages                   |                                                   |                        |

|                | New Design                                     | Wizard - Add Existing Sources                     |                        |

|                |                                                |                                                   |                        |

|                | More Info                                      | 1.480                                             | 4/5                    |

|                | Source                                         |                                                   |                        |

|                |                                                | Defaulty 7 5 Emove                                | 1                      |

|                |                                                |                                                   |                        |

| No.            | Project Wizard – Project Sum                   | mary _ 🛛 🗙                                        |                        |

| New New        | Troject wizaru - Project oum                   |                                                   | created with the New   |

| Proj           | ect Navigator will create a new proj           | ect with the following specifications: Page 5/5   | e "Project->New Source |

|                |                                                |                                                   |                        |

| Pro            | ject:                                          | <u> </u>                                          |                        |

|                | Project Name: sample<br>Project Path: C:\FPGA\ |                                                   |                        |

|                | Project Path: C:(PPGA)                         | sampre                                            | kt > Cancel            |

Figure 2-2. New Project Wizard Execution Screen

#### 2.4 Timing Constraint Addition

RemarkFundamentals of FPGA Design v8, 6-11 to 6-23O Explanation of timing constraints (global constraints)6-24 to 6-31O How to use the Constraints Editor

Add the timing constraints by referring to the document mentioned in the remark above.

#### 2.5 Implementation

#### 2.5.1 Implementation execution

Remark Fundamentals of FPGA Design v8, 3a-17 to 3a-18 O Implementation execution method

Perform the implementation by referring to the document mentioned in the remark above.

#### 2.5.2 Result check

| Remark | Fundamentals of FPGA | Design v8,                                           |

|--------|----------------------|------------------------------------------------------|

|        | 4-1 to 4-8           | O Map report                                         |

|        | 4-9 to 4-14          | O Placement and routing report                       |

|        | 4-15 to 4-21         | O Static timing report (after mapping)               |

|        | 4-22 to 4-24         | O Static timing report (after placement and routing) |

|        | 4-25 to 4-29         | O Pad report                                         |

|        |                      |                                                      |

Check the implementation result by referring to the document mentioned in the remark above. Supplementary information regarding the pad report is described below.

• Check that all I/O pins have been placed according to the pin layout constraints.

<1> Click [Pinout Report] and display the pad report.

<2> Click the row title [Signal Name] and sort the rows by the pin names.

<3> Check that "LOCATED" is added to the row title [Constraint] section.

#### 2.6 BIT File Creation

A BIT file (\*.bit) is created from the implementation results, according to the following procedure. Directly downloading to the FPGA can be performed using this BIT file.

#### 2.6.1 Unused-pin option setting

Set options according to the following procedure so that the unused pins of the FPGA are set to "Float".

- 1. Select the [Generate Programming File] process in the [Processes] window.

- 2. Right-click to select the [Properties...] command and open the [Process Properties] dialog box.

- Select [Configuration Options] from [Category].

Select "Float" from the "Unused IOB Pins" drop-down list in the "Property Name" column.

- Caution Pins pulled up within the PFESiP/V850EP1 exist as the PFESiP/V850EP1 external pins, so be sure to set the unused FPGA pins connected with these pins to "Float". (The default setting in ISE 8.2 is "Pull Down".)

#### 2.6.2 Generate execution

- 1. Display [Generate Programming File] by expanding the directory tree in the [Processes] window.

- 2. Double-click [Programming File Generation Report].

#### Caution Be sure to create a PROM file according to 2.7 PROM File Creation after creating a BIT file.

#### 2.7 PROM File Creation

Create a PROM file (\*.mcs) from the BIT file according to the following procedure. A PROM file is required for downloading to the FPGA configuration PROM.

#### 2.7.1 Wizard execution (1)

- 1. Display [Generate Programming File] by expanding the directory tree in the [Processes] window.

- 2. Double-click [Generate PROM, ACE, or JTAG File] to start iMPACT and a wizard.

Supplementary information regarding the setting items in the wizard is described below.

- <1> Instruct to create a PROM file (\*.mcs). Please select an action from the list below: "Prepare a PROM File"

- <2> Instruct the file format of the PROM file (\*.mcs).

- I want to target: "Xilinx PROM"

- <3> PROM File Format: "MCS"

- <4> Specify the file name and path of the PROM file to be created.

- <5> Select the PROM device and click the [Add] button.

"xcf"

- "xcf32p [4194304]"

- <6> Set the connection status between the PROM and FPGA after clicking the [Finish] button on page 4/4.

| Aut                          | omatically connect to a cable and identify Boundary-Sca | IMPACT - Specify Xilinx PROM Device         |                     |          |

|------------------------------|---------------------------------------------------------|---------------------------------------------|---------------------|----------|

| Prepare a P                  |                                                         | Auto Select PROM                            |                     | Page 3/4 |

| and the second second second | uctam ACE File                                          | Fable Revisioning                           |                     |          |

| C Prepare a                  |                                                         | Number of Rev                               | isions: 1 💌         |          |

|                              | I want to target a                                      | F Enable Compression                        |                     |          |

| C Configure                  | C Generic Parallel PROM                                 | Select a PROM: xcf                          | [4194304] 5         | Add      |

|                              | C 3rd-Party SPI PROM                                    | Position                                    | Part Name           |          |

|                              | C PROM Supporting Multiple Design Versions:             | 0                                           | xcf32p              |          |

|                              |                                                         | Mimpact - File Generation Summa             | TV.                 |          |

|                              |                                                         | You have entered following information:     |                     |          |

|                              | PROM File Format                                        | PROM Type:                                  | Serial              | Page 4/4 |

| 6                            | G MCS C TEK C UFP (C" format)                           | File Format                                 | mcs                 |          |

| <u>(e</u>                    | CEXO CBIN CISC                                          | Fill Value<br>PROM filename                 | FF<br>AuroraDefault |          |

|                              | C HEX F Swap Bits                                       | Number of PROMs                             | nuroraDetault       |          |

|                              |                                                         | Position Part Name                          |                     |          |

| U                            |                                                         | 0 xcf32p                                    |                     |          |

|                              |                                                         |                                             |                     |          |

|                              |                                                         |                                             |                     |          |

|                              | Checksum Fill Value (2 Hex Digits):  FF                 |                                             |                     |          |

|                              | PROM File Name: AuroraDefault                           |                                             |                     |          |

|                              | Location: C:/FPGA/sample                                | Olick "Finish" to start adding device files |                     | ~        |

Figure 2-3. Wizard Execution Screen of iMPACT

#### 2.7.2 Wizard execution (2)

Answer the messages that are displayed and specify the connection between the PROM and FPGA.

- 1. Click the [OK] button in the first message box.

- 2. Specify the BIT file that is the conversion source file.

- 3. Click the [No] button in the second message box.

The PROM and FPGA have a one-to-one correspondence on the PFESiP EP-1 Evaluation Board.

4. Click the [OK] button in the third message box and end the wizard.

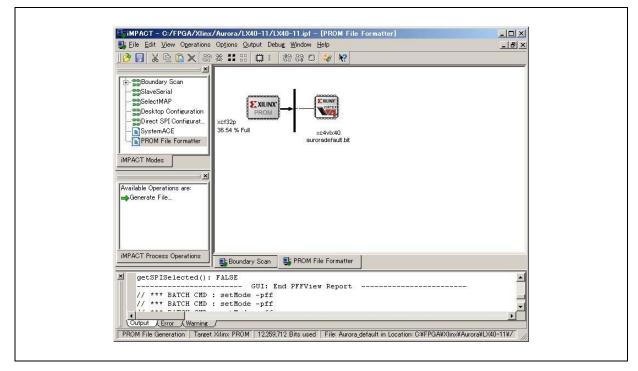

Figure 2-4. Wizard End Screen of iMPACT

#### 2.7.3 Generate execution

A PROM file is created from the BIT file.

1. Double-click [Generate File...] in the [iMPACT Process] window.

#### 2.8 Download

Download the PROM file (\*.mcs) converted from the BIT file (\*.bit) to the on-board PROM, according to the following procedure.

# Caution Check that converting a PROM file from the BIT file via the procedure in 2.7 PROM File Creation has been executed. (Note this, because this is often omitted.)

#### 2.8.1 Download cable connection

Connect CN5 (see the **PFESiP EP-1 Evaluation Board Technical Information User's Manual**) of the PFESiP EP-1 Evaluation Board to a PC using a download cable (parallel cable IV or platform cable USB).

**Remark** When using platform cable USB as the download cable, three types of device drivers must be installed every time it is connected to a PC (tool specifications).

#### 2.8.2 Starting iMPACT

Downloading the PROM file to the PROM is performed by starting iMPACT via ISE 8.2 (Project Navigator).

- 1. Display [Generate Programming File] by expanding the directory tree in the [Processes] window.

- 2. Double-click [Configure Device (iMPACT)] to start iMPACT.

#### 2.8.3 Downloading to PROM

The PROM file is downloaded to the PROM according to the following procedure.

- 1. Double-click [Boundary Scan] in the [Flows] window.

- 2. Click [Initialize Chain] in the [File] menu to display the connection status of the JTAG chain.

- 3. Specifying the BIT file (\*.bit) will be requested. Specify the BIT file. (The specification can also be canceled.)

- 4. Subsequently, specifying the PROM file (\*.mcs) will be requested. Specify the PROM file.

- 5. Click the PROM device in the JTAG chain displayed by performing step 2.

Figure 2-5. PROM Device Selection Screen

|  | ET - C:/FPGA/Xlim:X/Aurora/LX40-11/LX40-11.jpf - [Boundary Scan]         idit View Operations Options Qutput Debug Window Help         Idit View Operations         Idit View Operations |

|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

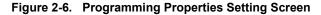

6. Click [Program...] in the [Operations] menu.

7. Specify the following and click the [OK] button in the [Programming Properties] dialog box.

<1> Check "Verify".

<2> Check "Erase Before Programming".

**Remark** The progress state display may not be updated while erasing the PROM.

| ⊇ategory<br>⊟-Programming Properties<br>}Advanced PROM Programming Properties | Programming Properties<br>General Programming Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                                             | Verify General OPLD And PROM Properties FEase Before Programming  Read Protect FROM/CoolBurner-TI Usercode (8 Hex Digits) OPLD Specific Properties White Protect  FEASE Specific Properties Cool Specific Properties Cool Specific Properties Cool Specific Properties Flow Specific Properties Flow Specific Programming Properties Flow Specific Properties Flow Specific Programming Properties Flow Specific Proper |

|                                                                               | OK Garcel Apply Heb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### 3.1 FPGA Pin Design

#### 3.1.1 Pins requiring processing

The FPGA has pins that must be processed (see Table 3-1).

Be sure to process these pins appropriately when implementing the UDL (user designed logic) for the FPGA.

| Туре              | Pin Name                 | I/O                 | Recommended Processing<br>When Unused | Comment                              |

|-------------------|--------------------------|---------------------|---------------------------------------|--------------------------------------|

| System            | FRESET                   | out                 | Fix to "H"                            | Required for starting PFESiP/V850EP1 |

| Serial FROM Note1 | SROM_CLK                 | 3s                  | Pull Up                               | Serial ROM pin protection            |

|                   | SROM_CS                  | 3s                  | Pull Up                               | Serial ROM pin protection            |

|                   | SROM_D                   | 3s                  | Pull Up                               | Serial ROM pin protection            |

| SROM_Q            | Pull Up <sup>Note2</sup> | in                  |                                       | FPGA pin protection                  |

| PAD               | PAD[12:10] Note2         | iO <sup>Note2</sup> | Pull Up                               | FPGA pin protection                  |

| GPIO              | GPIO[287:0]              | iO <sup>Note2</sup> | Pull Up                               | FPGA pin protection                  |

Table 3-1. FPGA Pins Requiring Processing

Notes 1. When using a serial FROM, a dedicated circuit must be built-in as the UDL.

- 2. The io definition is used to enable the pull-up option without a dummy circuit, due to the following reasons.

- The pull-up option is disabled for an output pin.

- An input pin without a drive destination will be deleted during synthesis.

**Remark** The pin names conform to the definitions in the constraint file templates. Pin names can be arbitrarily changed, but the definitions in the pin layout constraints must be changed accordingly.

#### 3.1.2 Unused pins

When pins other than the pins requiring processing (Table 3-1) are unused, no descriptions such as definitions in HDL or pin layout constraints are required. The pin processing state in this case depends on the unused-pin option settings<sup>Note</sup> in ISE8.2.

Set the default statuses of unused pins of the FPGA to "Float", because the PFESiP EP-1 Evaluation Board includes the pull-up/pull-down processing within the PFESiP/V850EP1 pins and on the board.

| Туре       | Pin Name                           | I/O | Recommended Processing<br>When Unused | Comment                                               |

|------------|------------------------------------|-----|---------------------------------------|-------------------------------------------------------|

| Unused pin | All pins except pins in Table 3-1. | -   | 'Float'                               | Depends on unused-pin option settings <sup>Note</sup> |

Table 3-2. Unused FPGA Pins

Note See 2.6.1 Unused-pin option setting for how to set the unused-pin options.

#### 3.1.3 FPGA-dedicated external circuit

The following pins can be used for the FPGA-dedicated external circuit.

These pins are uniquely used with the UDL or can be arbitrarily used, such as connecting them to the external pins of the PFESiP/V850EP1 by using the UDL.

| Туре                     | Pin Name            | I/O    | Recommended Processing<br>When Unused | Comment                       |  |

|--------------------------|---------------------|--------|---------------------------------------|-------------------------------|--|

| LED                      | LED [7:0]           | out    | "L" or "H"                            | LEDs are lit with "L"         |  |

| Switch                   | DIPSW [7:0]         | in     | "float"                               |                               |  |

|                          | SW_NMI              | in     | "float"                               |                               |  |

|                          | SW_INTP7            | in     | "float"                               |                               |  |

| General-purpose clock    | CLK2P               | in     | "float"                               | On-board general-purpose OSC4 |  |

|                          | CN_CLK              | in     | "float"                               | Input from CN6-115 pin        |  |

| CN9 (MICTOR)             | GPIO [110:0] Note   | in/out | Pull Up                               |                               |  |

| CN6 (MICTOR)             | GPIO [239:220] Note | in/out | Pull Up                               |                               |  |

| CN7 (MICTOR)             | GPIO [219:111] Note | in/out | Pull Up                               |                               |  |

| CN10                     | GPIO [162:123] Note | in/out | Pull Up                               |                               |  |

| (general-purpose 50-pin) | GPIO [122:111] Note |        |                                       |                               |  |

| CN8                      | GPIO [259:220] Note | in/out | Pull Up                               |                               |  |

| (general-purpose 50-pin) |                     |        |                                       |                               |  |

| CN13 (MICTOR)            | GPIO [208:128] Note | in/out | Pull Up                               |                               |  |

| CN14 (MICTOR)            | GPIO [318:240] Note | in/out | Pull Up                               |                               |  |

Note GPIO [287:0] is a pin requiring processing.

See 3.1 FPGA Pin Design for the processing when the pin is unused.

Remark The pin names conform to the definitions in the constraint file templates.

Pin names can be arbitrarily changed, but the definitions in the pin layout constraints must be changed accordingly.

#### 3.1.4 Connection with PFESiP/V850EP1 system pins

The following pins of the FPGA are connected to the system pins of the PFESiP/V850EP1.

These pins are used with the UDL or can be arbitrarily used, such as for outputting to the external expansion connectors by using the UDL.

| Туре           | Pin Name | I/O | Recommended Processing<br>When Unused | Comment |

|----------------|----------|-----|---------------------------------------|---------|

| PFESiP/V850EP1 | VBRESTOZ | in  | "Float"                               |         |

| system pin     | VBCLKOUT | in  | "Float"                               |         |

| Table 3-4 | PFESiP/V850EP1 | System Pin  | Connections   |

|-----------|----------------|-------------|---------------|

|           |                | Oystenn i m | 0011100110113 |

**Remark** The pin names conform to the definitions in the constraint file templates.

Pin names can be arbitrarily changed, but the definitions in the pin layout constraints must be changed accordingly.

#### 3.1.5 Connection with PFESiP/V850EP1 port (shared-function) pins

The following pins of the FPGA are connected to the port (shared-function) pins of the PFESiP/V850EP1.

These pins are used with the UDL or can be arbitrarily used, such as for outputting to the external expansion connectors by using the UDL.

| , , , , , , , , , , , , , , , , , , , |                            |                       |              |              |                                       |                         |  |  |

|---------------------------------------|----------------------------|-----------------------|--------------|--------------|---------------------------------------|-------------------------|--|--|

| Port (I/O)                            |                            | Shared Function (I/O) |              | FPGA         | Recommended Processing<br>When Unused | comment                 |  |  |

| P0 [7:0]                              | io                         | INTPZ [7:0]           | out          | $\checkmark$ | "Float"                               |                         |  |  |

| P1 [0]                                | io                         | INTPZ [8]             | out          | $\checkmark$ | "Float"                               | JP2 must be 1-2.        |  |  |

| P1 [7:1]                              |                            | INTPZ [15:9]          |              | $\checkmark$ | "Float"                               |                         |  |  |

| P7 [0]                                | io                         | SELFREFZ              | _            | (JP20)       | "Float"                               | Depends on JP20 setting |  |  |

| Other than abo                        | Other than above (Omitted) |                       | $\checkmark$ | "Float"      |                                       |                         |  |  |

Remark The pin names conform to the definitions in the constraint file templates.

Pin names can be arbitrarily changed, but the definitions in the pin layout constraints must be changed accordingly.

#### 3.1.6 Connection with PFESiP/V850EP1 SiP internal memory interface pins

The following pins of the FPGA are connected to the SiP internal memory interface pins of the PFESiP/V850EP1. These pins are used with the UDL or can be arbitrarily used, such as for outputting to the external expansion connectors by using the UDL. Furthermore, since STBUSCLK is connected to CN7, these pins can be arbitrarily used, such as for inputting to one of the FPGAs when these boards are stacked.

| Pin Name               | I/O | FPGA         | CN7 | Recommended Processing<br>When Unused | Comment                 |

|------------------------|-----|--------------|-----|---------------------------------------|-------------------------|

| SCSZ [3:0]             | in  | $\checkmark$ | ×   | "Float"                               |                         |

| SA [20:0]              | in  | $\checkmark$ | ×   | "Float"                               |                         |

| D [15:0]               | lo  | $\checkmark$ | ×   | "Float"                               |                         |

| SRDZ                   | in  | $\checkmark$ | ×   | "Float"                               |                         |

| SWRZ [1:0]/SBENZ [1:0] | in  | $\checkmark$ | ×   | "Float"                               |                         |

| SIOWRZ                 | in  | $\checkmark$ | ×   | "Float"                               |                         |