## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **User's Manual**

# PFESiP® EP-1 **Evaluation Board Lite**

**Technical Information**

Document No. A19354EJ1V1UM00 (1st edition)

Date published September 2008 NS

#### NOTES FOR CMOS DEVICES —

#### 1 VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### (3) PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **4** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### 5 POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### (6) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

PFESiP is a registered trademark of NEC Electronics Corporation in Japan, Germany, and United Kingdom.

Xilinx, Virtex, and ISE are registered trademarks of Xilinx, Inc. in the United States.

Altera, Stratix, and Quartus are registered trademarks of Altera Corporation in the United States.

ByteBlaster and USB Blaster are trademarks of Altera Corporation.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of September, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this document

or any other liability arising from the use of such products. No license, express, implied or otherwise, is

granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and

"Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

#### **PREFACE**

**Readers** This manual is intended for users who understand the functions of the microcontroller function chip

with an on-chip V850E2 CPU core (PFESiP/V850EP1) and wish to evaluate developing PFESiP EP-1

Series products using the chip.

Purpose This manual is intended to help users, who wish to evaluate introducing PFESiP EP-1 Series products

using the PFESiP/V850EP1, understand how to use the development evaluation board.

How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical

engineering, logic circuits, microcontrollers, SRAM, page ROM, and SDRAM.

**Conventions** Data significance: Higher digits on the left and lower digits on the right

Active low representation: xxxZ (Z after pin or signal name)

**Note**: Footnote for item marked with Note in the text **Caution**: Information requiring particular attention

**Remark**: Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2

(address space, memory capacity): K (kilo):  $2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$

G (giga):  $2^{30} = 1,024^3$

Data type: Word ... 32 bits

Half-word ... 16 bits

Byte ... 8 bits

**Related Documents** The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such. Furthermore, some related documents may be intended for individual customers, because the documents are prepared in the development/planning stage of each core.

#### **Documents Related to PFESiP EP-1 Series**

| Document Name                                                | Document No. |

|--------------------------------------------------------------|--------------|

| V850E2 Architecture User's Manual                            | U17135E      |

| PFESiP EP-1 Series Design Manual                             | A19068E      |

| PFESiP/V850EP1 Product Data User's Manual                    | A19069E      |

| PFESiP/V850EP1 Hardware (CPU Function) User's Manual         | A19070E      |

| PFESiP/V850EP1 Hardware (USB Function) User's Manual         | A19071E      |

| PFESiP/V850EP1 USB Function Sample Software Application Note | A19349E      |

#### **Documents Related to PFESiP EP-1 Evaluation Board**

| Document Name                                                         | Document No. |

|-----------------------------------------------------------------------|--------------|

| PFESiP EP-1 Evaluation Board Technical Information User's Manual      | A19350E      |

| PFESiP EP-1 Evaluation Board Lite Technical Information User's Manual | This manual  |

#### **Documents Related to development tools (User's Manual)**

| Document Name                                 |                 |               | Document No. |

|-----------------------------------------------|-----------------|---------------|--------------|

| RX850 Pro (Real-Time OS)                      | Ver.3.21        | Basics        | U18165E      |

|                                               | Ver.3.20        | Installation  | U17421E      |

|                                               | Ver.3.21        | Technical     | U18164E      |

|                                               | Ver.3.20        | Task Debugger | U17422E      |

| PM+ Ver. 6.30 Project Manager                 |                 |               | U18416E      |

| QB-V850MINI On-Chip Debug Emulator            |                 |               | U17638E      |

| ID850QB Ver. 3.20 Integrated Debugger         | Operation       |               | U17964E      |

| RX850V4 Ver. 4.22 Real-Time OS                | Functionalities |               | U16643E      |

|                                               | Task Debu       | ugger         | U16811E      |

| AZ850V4 Ver. 4.10 System Performance Analyzer |                 |               | U17093J      |

#### **CONTENTS**

| CHAPTER 1 INTRODUCTION                                                | 12 |

|-----------------------------------------------------------------------|----|

| 1.1 Overview of PFESiP EP-1 Evaluation Board Lite                     | 12 |

| 1.1.1 Features                                                        |    |

| 1.1.2 Appearance of PFESiP EP-1 Evaluation Board Lite                 |    |

| 1.1.3 PFESiP EP-1 Evaluation Board Lite (function of each part)       |    |

| ` ,                                                                   |    |

| 1.1.4 Specifications of PFESiP EP-1 Evaluation Board Lite             |    |

| 1.1.5 Summarized block diagram of PFESiP EP-1 Evaluation Board Lite   |    |

| 1.1.6 Detailed block diagram of PFESiP EP-1 Evaluation Board Lite     |    |

| 1.1.7 Caution regarding maximum operating frequency of PFESiP/V850EP1 |    |

| 1.2 Overview of PFESiP/V850EP1                                        |    |

| 1.2.1 Functions of PFESiP/V850EP1                                     |    |

| 1.2.2 Internal block diagram of PFESiP/V850EP1                        |    |

| 1.2.3 PFESiP/V850EP1 pins usable on this board                        | 26 |

| CHAPTER 2 HARDWARE INSTALLATION                                       | 33 |

| 2.1 Preface                                                           | 33 |

| 2.1.1 Operating mode setting                                          | 33 |

| 2.1.2 Mounting oscillation module                                     | 34 |

| 2.2 Connecting Power Supply                                           | 35 |

| 2.2.1 AC adapter (CN13)                                               | 35 |

| 2.2.2 5.0 V power supply terminal (CN12)                              | 35 |

| CHAPTER 3 SWITCH SETTINGS                                             | 36 |

| 3.1 Operating Mode Setting Dip Switches                               | 36 |

| 3.1.1 Setting operating mode using dip switches (SW3-4 to SW3-8)      | 37 |

| 3.1.2 SSCG-PLL operating mode setting dip switches                    |    |

| 3.1.3 Setting operating mode from FPGA                                |    |

| 3.2 Chip Select Signal Setting Dip Switches                           |    |

| 3.3 Jumper Settings                                                   |    |

| 3.3.1 JP1, JP2 (for setting LAN circuit)                              |    |

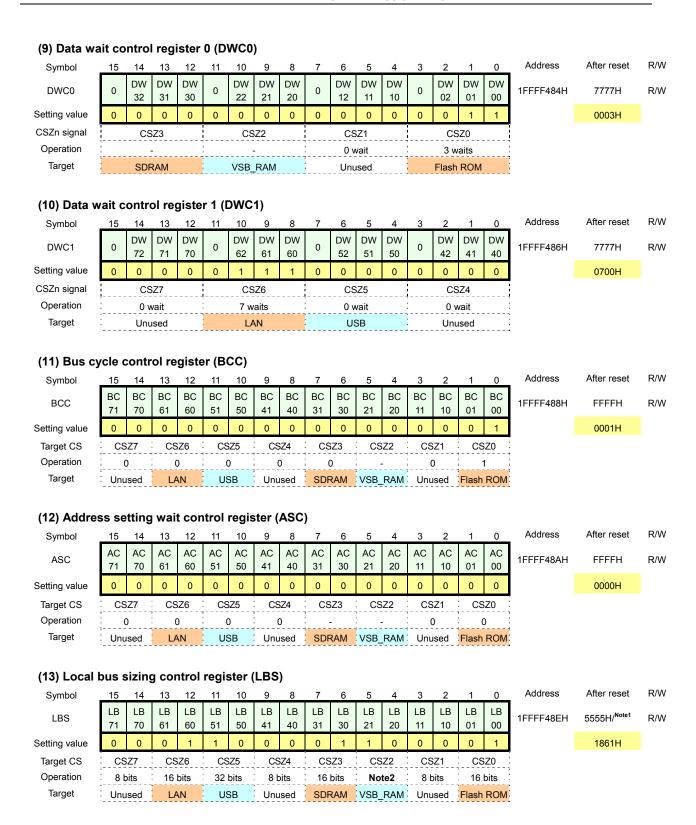

| CHAPTER 4 EXTERNAL MEMORY ACCESS SETTING EXAMPLE                      | 44 |

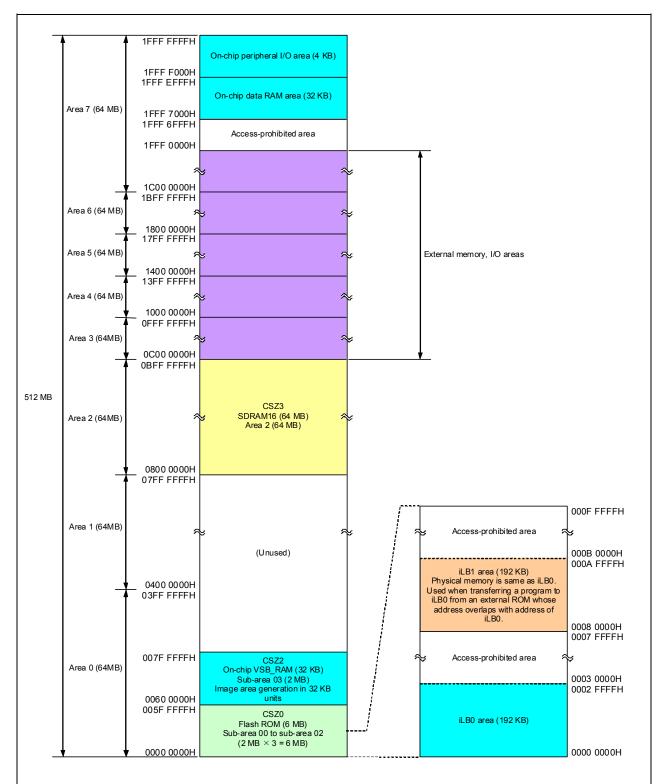

| 4.1 On-Board Memory Specifications                                    | 44 |

| 4.1.1 External memory                                                 |    |

| 4.1.2 Internal memory                                                 |    |

| 4.1.3 Memory map                                                      |    |

| 4.2 Setting External Memory Access Operation                          |    |

| 4.2.2 PFESiP/V850EP1 start procedure                                  |    |

| 4.2.2 PPESIP/V030EPT Start procedure                                  | 52 |

| CHAPTER 5 USING EXPANSION CONNECTORS                                  | 56 |

| 5.1 Connectors (CN3, CN4)                                             |    |

| 5.2 PFESiP/V850EP1 Port Output Connectors (CN1, CN2)                  | 58 |

| CHAPTER 6 EMULATION CONNECTOR                                         | 61 |

| 6.1 N-Wire Interface                                     | 61 |

|----------------------------------------------------------|----|

| CHAPTER 7 ON-BOARD FPGA                                  | 63 |

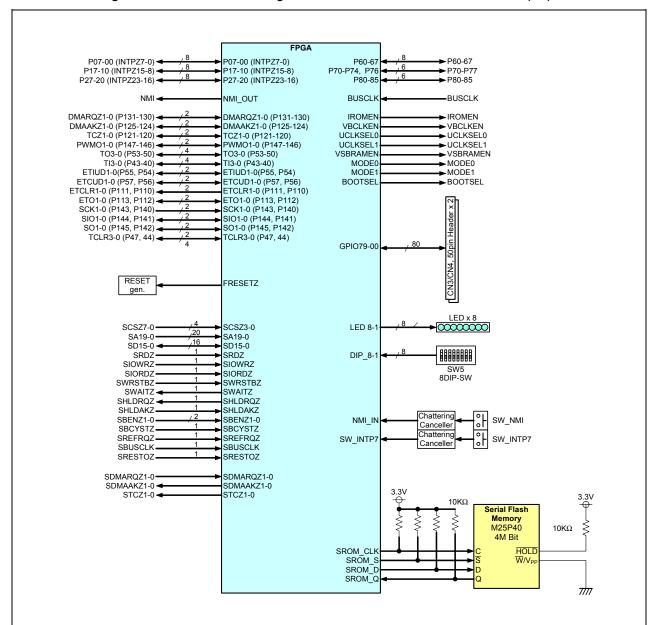

| 7.1 Default FPGA Programming                             | 64 |

| 7.1.1 VerilogHDL source of default PFESiP/V850EP1 data   | 65 |

| 7.2 Default FPGA Data                                    | 67 |

| 7.2.1 FPGA data generation environment                   | 67 |

| 7.2.2 File explanation                                   | 67 |

| 7.3 Push Switches for FPGA                               | 68 |

| 7.4 DIP Switches for FPGA                                | 69 |

| 7.5 LEDs for FPGA                                        | 70 |

| 7.6 Serial ROM for FPGA                                  | 71 |

| 7.7 Connection of FPGA and Expansion Connectors          | 71 |

| 7.8 FPGA Pin Connections                                 | 72 |

| 8.1 Various LEDs                                         |    |

| 8.1.1 USB host port LEDs (LED9, LED10)                   |    |

| 8.1.2 LED for FPGA DONE (LED11)                          |    |

| 8.1.3 Power supply LED (LED15)                           |    |

| 8.2 On-Chip Serial Interface (USB Conversion Circuit)    |    |

| 8.3 External LAN Interface (LAN9115)                     |    |

| 8.4 USB Function                                         |    |

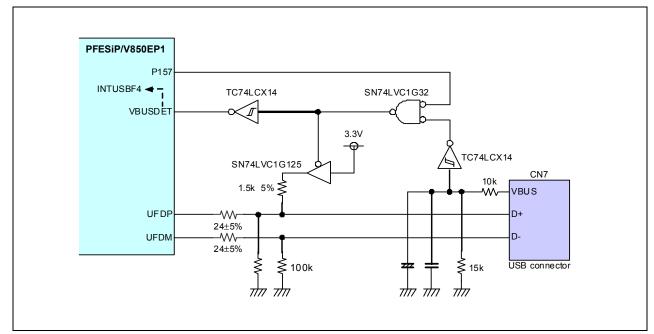

| 8.4.1 Peripheral circuit of USB function controller      | 81 |

| 8.4.2 Peripheral circuit of USB host controller          |    |

| 8.4.3 USB host port LEDs (LED9, LED10)                   | 82 |

| 8.5 Manipulation Switches                                | 83 |

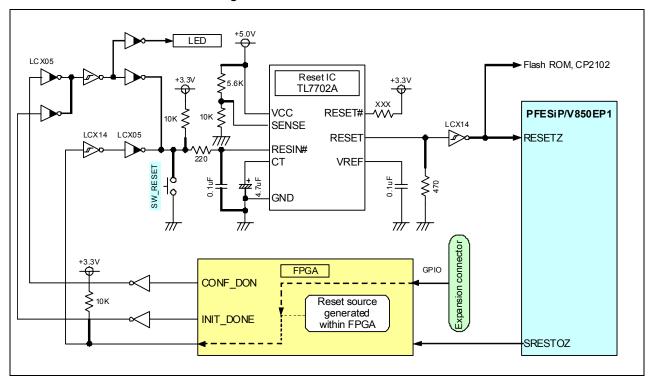

| 8.5.1 Reset switch                                       | 83 |

| 8.5.2 Interrupt switches                                 | 84 |

| ADDENDIX A DIFFERENCES FROM DEESID ED-1 Evaluation Roard | 85 |

#### **LIST OF FIGURE**

| Fig | gure No. Title                                              | Page |

|-----|-------------------------------------------------------------|------|

|     |                                                             |      |

| 1-1 | PFESiP EP-1 Evaluation Board Lite (Appearance)              | 15   |

| 1-2 | PFESiP EP-1 Evaluation Board Lite (Function of Each Part)   | 16   |

| 1-3 | Overall Block Diagram                                       | 18   |

| 1-4 | Detailed Block Diagram of PFESiP EP-1 Evaluation Board Lite | 19   |

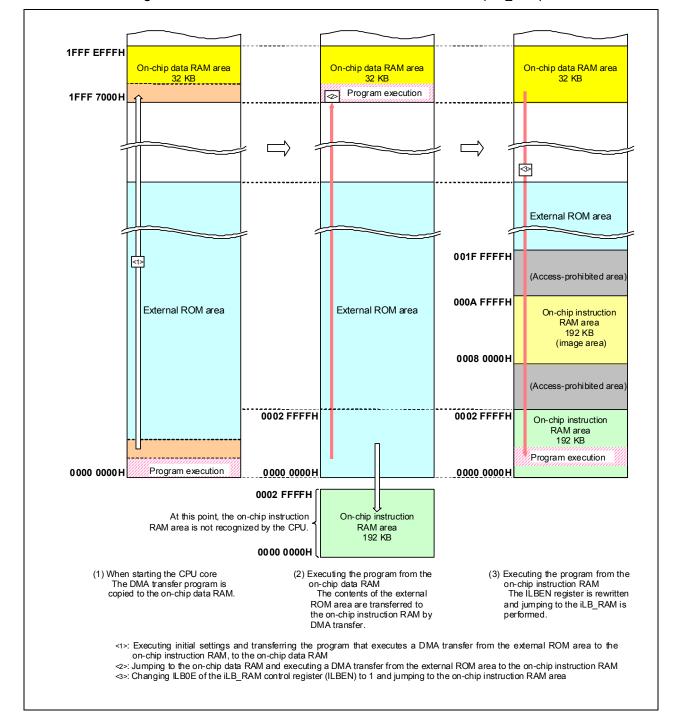

| 4-1 | Transfer from External ROM to Instruction RAM (iLB_RAM)     | 55   |

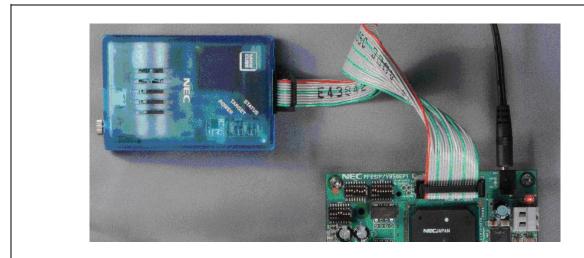

| 6-1 | Connection with MINICUBE (QB-V850MINI)                      | 62   |

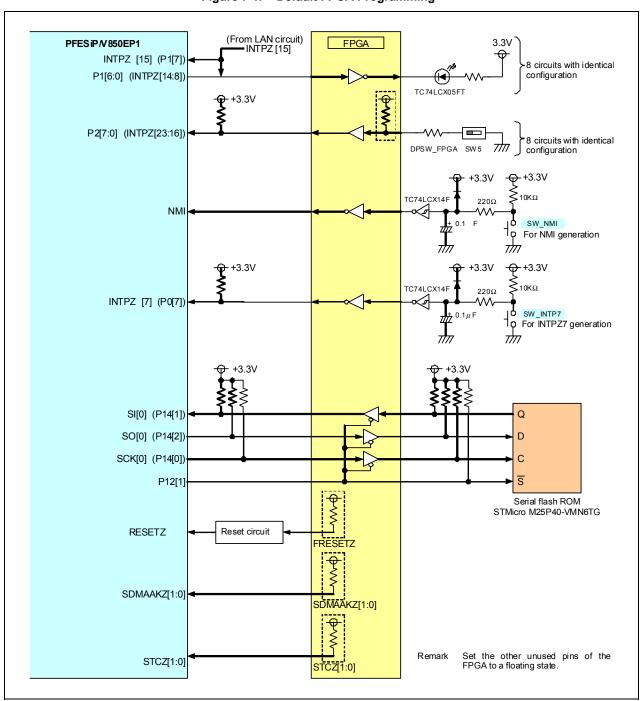

| 7-1 | Default FPGA Programming                                    | 64   |

| 7-2 | Push Switches for FPGA                                      | 68   |

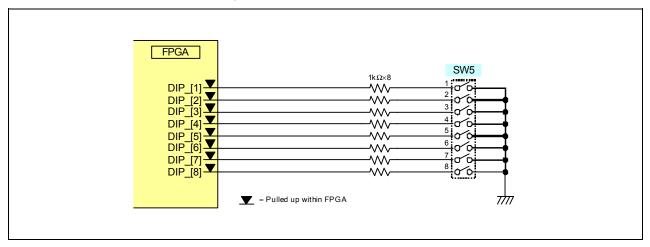

| 7-3 | DIP Switches for FPGA                                       | 69   |

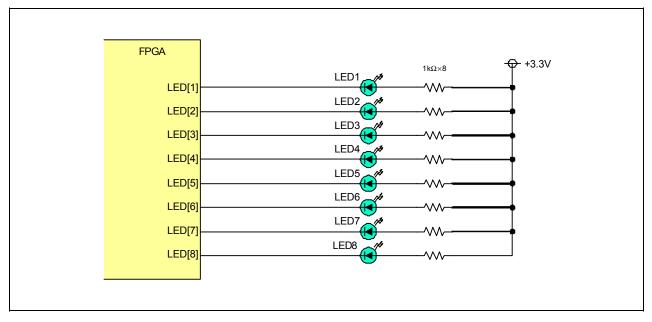

| 7-4 | LED Circuit for FPGA                                        | 70   |

| 7-5 | Serial ROM Connections                                      | 71   |

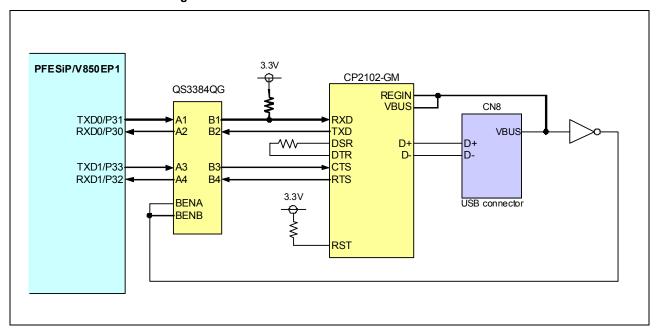

| 8-1 | USB Mini B Connector UART Conversion                        | 78   |

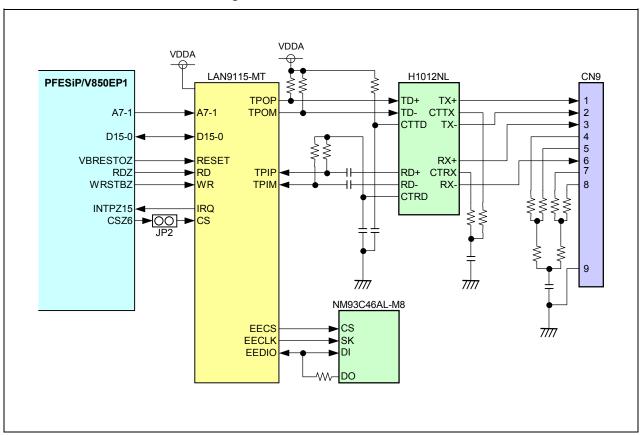

| 8-2 | LAN Interface Circuit                                       | 79   |

| 8-3 | Peripheral Circuit of USB Function Controller               | 81   |

| 8-4 | Peripheral Circuit of USB Host Controller                   | 82   |

| 8-5 | Power-on-Reset Switch                                       | 83   |

#### LIST OF TABLES

| Tal | ole No. Title                                                                   | Page |

|-----|---------------------------------------------------------------------------------|------|

|     |                                                                                 |      |

| 1-1 | Specifications of PFESiP EP-1 Evaluation Board Lite                             | 17   |

| 1-2 | Maximum Operating Frequency of PFESiP/V850EP1 According to Operating Conditions | 21   |

| 2-1 | Operating Mode Setting Pins Set from FPGA                                       | 33   |

| 3-1 | Operating Mode Settings                                                         | 36   |

| 3-2 | On-Chip Work RAM (VSB_RAM) Setting                                              | 41   |

| 4-1 | External Memories                                                               | 44   |

| 4-2 | Mode Setting Using Dip Switches                                                 | 48   |

| 4-3 | Register Setting Values                                                         |      |

| 5-1 | Simplified Connector (General-Purpose 50-Pin) Pin Layout                        | 57   |

| 5-2 | PFESiP/V850EP1 Ports Connected to CN1 and CN2                                   | 58   |

| 5-3 | Simplified Connector (General-Purpose 50-Pin) Pin Layout                        | 59   |

| 5-4 | Analog Pin Jumper Post Setting                                                  | 60   |

| 6-1 | N-Wire Connector (CN5)                                                          | 61   |

| 7-1 | Explanation of Files Directly under TOP Directory                               | 67   |

| 7-2 | SW5 Operation with Default Program                                              | 69   |

| 7-3 | LED Operation with Default Program                                              | 70   |

#### **CHAPTER 1 INTRODUCTION**

The PFESiP EP-1 Evaluation Board Lite is a development evaluation board for assisting the development of PFESiP EP-1 Series products and can be used for the software development of the PFESiP EP-1 Series-dedicated microcontroller PFESiP/V850EP1 and for user logic development and verification using the on-board FPGA.

The PFESiP/V850EP1 has an on-chip high-performance 32-bit RISC-type CPU core (V850E2 core).

The basic functions of PFESiP EP-1 Series products based on the PFESiP/V850EP1 can be evaluated using this board.

The PFESiP EP-1 Evaluation Board Lite is a development evaluation board whose price has been reduced by reducing the functions of the PFESiP EP-1 Evaluation Board and that has been developed for users wishing to evaluate introducing the PFESiP EP-1 Series products.

The Stratix<sup>®</sup> II EP2S15F484C5 made by Altera is used as the on-board FPGA and the Quartus<sup>®</sup> II Web Edition can be used.

Use the PFESiP EP-1 Evaluation Board when adding an external board requiring numerous signals, or when requiring a large-capacity logic cell or on-board RAM, because the size of the on-board FPGA is smaller in contrast to the PFESiP EP-1 Evaluation Board.

#### 1.1 Overview of PFESiP EP-1 Evaluation Board Lite

The PFESiP EP-1 Evaluation Board Lite is a development evaluation board for assisting the development of PFESiP EP-1 Series products.

It can be used for the software development of the PFESiP EP-1 Series-dedicated microcontroller PFESiP/V850EP1 and as a PFESiP EP-1 prototyping environment by using the functions of the embedded array (EA-9HD), which is provided with the user logic paired with the PFESiP/V850EP1, for user logic development and verification by the on-board FPGA within the PFESiP EP-1 Series SiP. A more systematic evaluation can be performed by connecting the PFESiP EP-1 Evaluation Board Lite to the user board using expansion connectors. Furthermore, a flash ROM and an SDRAM are provided as on-board memories.

Note that the load capacitance of the PFESiP EP-1 Evaluation Board Lite is not always equivalent, in contrast to the environment of actual SiP products, because the signals originally connected within the SiP are connected to the FPGA on-board.

Remark See the PFESiP/V850EP1 User's Manual for the functions and specifications of the PFESiP/V850EP1.

#### 1.1.1 Features

#### (1) On-board memory

A flash ROM and SDRAM which can be directly accessed via the external bus interface (MEMC I/F) of the PFESiP/V850EP1 is mounted on-board and a general memory system is provided.

A memory system with a 32-bit width cannot be used.

| On-Board Memory Type | Capacity | Connection Bit Width |

|----------------------|----------|----------------------|

| Flash ROM            | 8 MB     | 16 bits              |

| SDRAM                | 32 MB    | 16 bits              |

#### (2) On-board FPGA (Altera<sup>™</sup> Stratix II)

An FPGA, Stratix II EP2S15F484C5 made by Altera is mounted on-board. The Quartus II Web Edition design software can be downloaded from the Altera Web site free of charge.

The SiP internal connection bus interface of the PFESiP/V850EP1 and almost all signals of the NPB macro I/O pins are connected to this FPGA. The functions of an embedded array to be used in combination with the PFESiP/V850EP1 are performed by this on-board FPGA. In addition, arbitrary signals can be connected via the on-board FPGA, because most expansion connector signals are connected via the FPGA.

External bus interface (MEMC I/F) signals are not connected to the FPGA.

An LED (red) is connected to the DONE signal that indicates that configuring the FPGA has been completed. The LED indicates that the configuration has been started when it is lit and indicates that the configuration has ended when it is turned off.

| Mounted FPGA | Size of Reference<br>Circuit Equivalent to CB-IC | Logic<br>Element | Total Number of Bytes of RAM | Number of I/Os |

|--------------|--------------------------------------------------|------------------|------------------------------|----------------|

| EP2S15F484C5 | 152 K gates                                      | 15,600           | 52 Kb                        | 342 Note       |

**Note** 342 I/Os can be used with the EP2S15F484C5, but only 271 I/Os are used with the PFESiP EP-1 Evaluation Board Lite.

Caution The PFESiP EP-1 Evaluation Board Lite does not support BTO selection of the FPGA.

The FPGA cannot be changed to a higher-grade pin-compatible FPGA.

#### (3) Expansion connectors

General-purpose 50-pin connectors are equipped.

| Connector              | No. of Valid Signals | Purpose                                                                                                                 |

|------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| General-purpose 50-pin | CN1 (40)             | For on-chip peripheral function I/Os of the PFESiP/V850EP1                                                              |

| connectors             | CN2 (27)             | 8 are used as A/D converter inputs. (16 pins, including the GND pins used in combination with the above pins are used.) |

|                        | CN3 (40)             | For on-board FPGA I/Os (GPIO)                                                                                           |

|                        | CN4 (40)             |                                                                                                                         |

#### (4) USB 2.0 FS and UART interface (supported by USB-to-serial signal conversion)

The following general-purpose interfaces are provided by the internal functions of the PFESiP/V850EP1.

| Interface Type                                              | Connector             | Remark                                                                           |

|-------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|

| USB 2.0 FS/LS Host $	imes$ 2                                | USB B type (CN6)      | 2-port host connector × 1                                                        |

| USB 2.0 FS Function × 1                                     | USB mini B type (CN7) |                                                                                  |

| USB 2.0 support (12 Mbps) ↔ On-chip UART5 of PFESiP/V850EP1 | USB mini B type (CN8) | On-chip UART5 of PFESiP/V850EP1 is converted to USB 2.0, using bridge IC CP2102. |

#### (5) On-board power supply circuit

AC adapters (5 V, 2 A, positive center pin, EIJ-2 standard DC jack) are supported.

The AC adapter dedicated to the PFESiP EP-1 Evaluation Board cannot be used.

The required 3.3 V, 1.5 V, and 1.2 V power supplies are supplied by the on-board power supply circuit.

#### (6) Operating mode setting

The various operating modes of the PFESiP/V850EP1 can be set using the output from the FPGA. (A default FPGA data template is attached.)

The multiplication and modulation rates of the on-chip SSCG-PLL of the PFESiP/V850EP1 can be set using the dip switches. (Changing the multiplication or modulation rate during operation is not supported.)

#### (7) On-chip debug function

The on-chip debug function performed by the N-Wire interface is supported by the on-chip DCU (debug control unit) of the PFESiP/V850EP1.

This evaluation board does not support the trace function.

The MINICUBE made by NEC Electronics is the recommended in-circuit emulator.

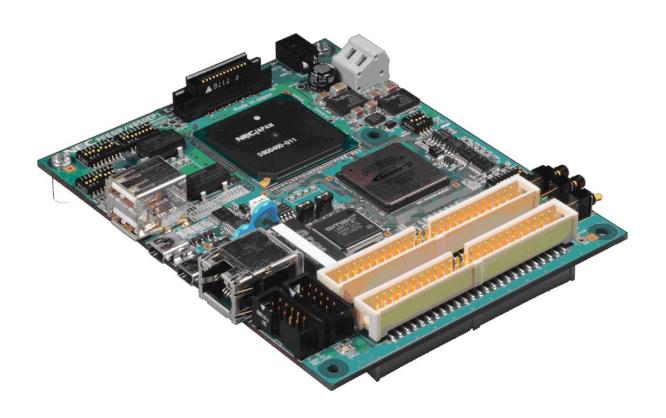

#### 1.1.2 Appearance of PFESiP EP-1 Evaluation Board Lite

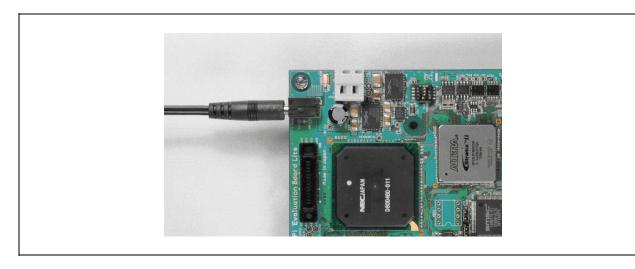

The appearance of the PFESiP EP-1 Evaluation Board Lite is shown below.

Remark Positions specified on-board in the following pages indicate coordinates on the following figure.

Figure 1-1. PFESiP EP-1 Evaluation Board Lite (Appearance)

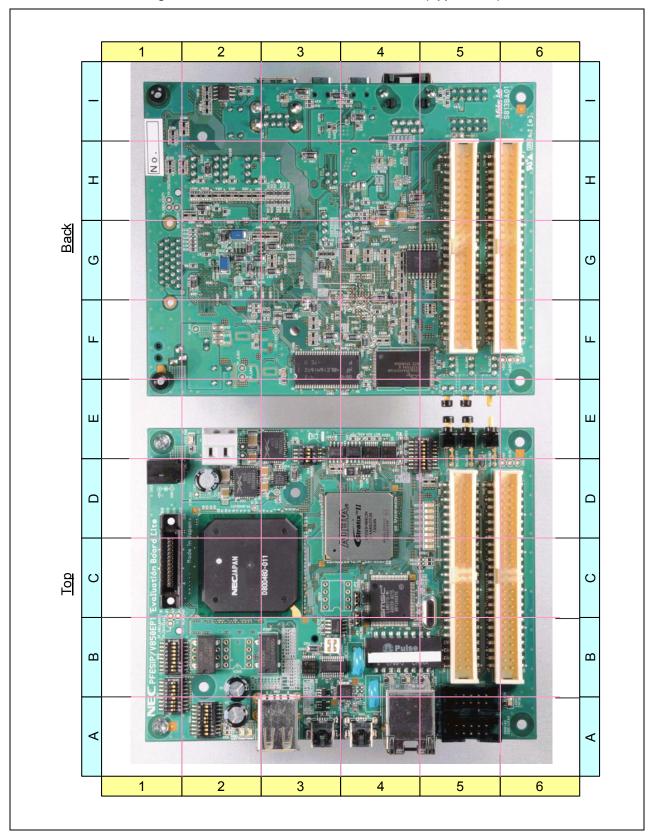

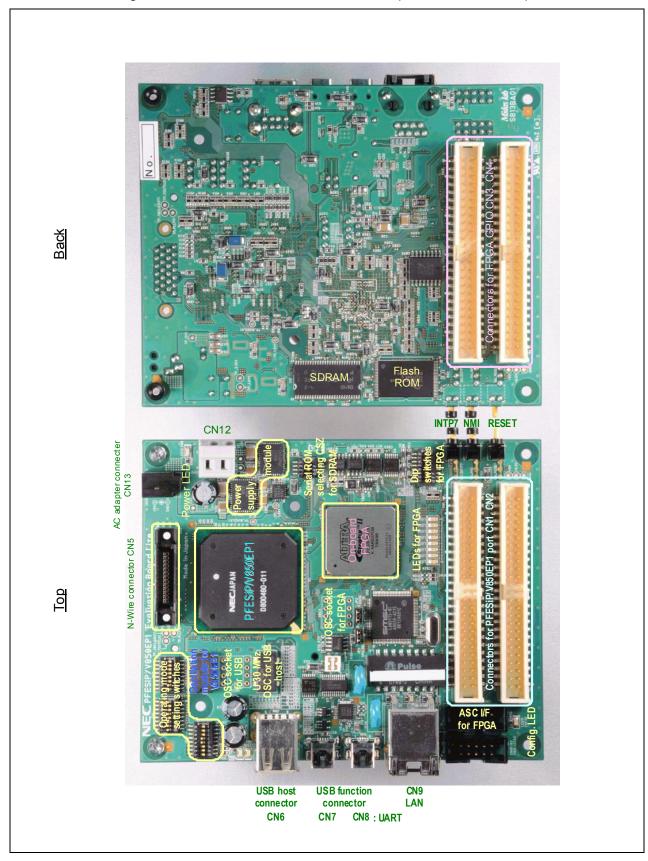

#### 1.1.3 PFESiP EP-1 Evaluation Board Lite (function of each part)

Figure 1-2. PFESiP EP-1 Evaluation Board Lite (Function of Each Part)

### 1.1.4 Specifications of PFESiP EP-1 Evaluation Board Lite

Table 1-1. Specifications of PFESiP EP-1 Evaluation Board Lite

|                             | Item                                                               | Specifications                                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum operating frequency |                                                                    |                                                                                                                                                                   |

|                             | CPU operating frequency                                            | 200 MHz                                                                                                                                                           |

|                             | Internal VSB bus frequency                                         | 100 MHz                                                                                                                                                           |

|                             | External memory bus                                                | 66.7 MHz (C <sub>L</sub> = 30 pF)                                                                                                                                 |

|                             | External memory wait setting                                       | Condition: VBCLK = BUSCLK = 66.7 MHz PFESiP/V850EP1 output delay = 11.0 ns, maximum Wiring delay = 5 ns (to and fro) PFESiP/V850EP1 input delay = 3.8 ns, maximum |

|                             | Flash ROM                                                          | Address setting wait = 0, idle state = 2, data wait = 5                                                                                                           |

|                             | Spansion (S29JL064H70TFI000H)                                      | Access time = 70 ns                                                                                                                                               |

|                             | SDRA                                                               | LTC = 0, C <sub>L</sub> = 2, idle state = 0                                                                                                                       |

|                             | MMT48LC16M16A2TG-7E                                                | ACTIVE Command to R/W Command = 1                                                                                                                                 |

| 0                           | n-board memory and FPGA                                            |                                                                                                                                                                   |

|                             | Flash ROM                                                          | 8 MB (fixed to CSZ0)                                                                                                                                              |

|                             | SDRAM                                                              | 32 MB (selected from CSZ1, CSZ3, CSZ4, or CSZ6 by SW4)                                                                                                            |

|                             | FPGA                                                               | Altera Stratix II EP2S15F484C5N (Any CSZ selected within FPGA)                                                                                                    |

|                             | PFESiP/V850EP1 on-chip memory                                      |                                                                                                                                                                   |

|                             | On-chip instruction RAM (ROM-less setting possible)                | iLB_RAM: 192 KB                                                                                                                                                   |

|                             | On-chip data RAM                                                   | dLB_RAM: 32 KB                                                                                                                                                    |

|                             | On-chip work RAM (disable setting possible)                        | VSB_RAM: 32 KB                                                                                                                                                    |

|                             | FPGA connection memory                                             |                                                                                                                                                                   |

|                             | Serial flash ROM                                                   | 512 KB (4 Mb)                                                                                                                                                     |

| С                           | onnector                                                           |                                                                                                                                                                   |

|                             | Expansion connectors                                               |                                                                                                                                                                   |

|                             | General-purpose 50-pin connectors (CN1, CN2, CN3, CN4)             | General-purpose 2.54 mm pitch (50 pins × 4)                                                                                                                       |

|                             | N-Wire (CN5) tracing impossible                                    | Default MINICUBE connector (26-pin connector made by KEL),<br>RTE-NEC for RTE-2000-TP (Midas lab) supported                                                       |

|                             | USB function connector<br>(PFESiP/V850EP1 on-chip UART connection) | UART ↔ USB conversion performed using CP2102-GM                                                                                                                   |

|                             | Active serial configuration interface for FPGA (CN10)              | 10 pins dedicated to ByteBlaster <sup>™</sup> II/USB Blaster <sup>™</sup> download cable, JTAG not mounted                                                        |

|                             | PFESiP/V850EP1 on-chip USB 2.0 FS function                         | USB2.0 FS/LS Host × 2, USB2.0 FS Function                                                                                                                         |

| 0                           | perating conditions                                                |                                                                                                                                                                   |

|                             | PFESiP/V850EP1 input frequency                                     | Standard 48 MHz (mounted in socket)                                                                                                                               |

|                             | Power supply                                                       | Supplied from CN13 by dedicated AC adapter (UL110-0520 made by UNIFIVE), 5 V supplied from power supply terminal (CN12)                                           |

#### 1.1.5 Summarized block diagram of PFESiP EP-1 Evaluation Board Lite

RESET Control 0000000 PFESiP/V850EP1 **FPGA** 26-pin connector made by KEL Debug N-Wire I/F CN5 V850E2 **ALTERA** O Done LED DCU Stratix II DMAC EP2S15F484C5N Instruction Config ROM EPCS16SI16N PLL multiplication rate

DIP Switch (Operating mode change) Mode Control CSI Serial Flash ROM RAM 512Kbyte Work RAM TMENC× 2 2.54 mm pitch 50-pin connector  $\times$  2 CN3 CN4 UART Ch2,3 INTC For SiP internal conne CN8 UART Ch0,1 CP2102 PORT 2.54 mm pitch 50-pin connector  $\times$  2 CN1 CN2 Oscillator OSC MEMC 16bit Data Bus 님 48 MHz, socket Flash ROM 8Mbyte USB Function Connector A/D Converter CN7 TMC × 4 USB 2.0 FS/LS Host  $\times$  2 USB 2.0 FS Function  $\times$  1 **SDRAM** TMD × 6 32Mbyte 16bit Data Bus CN6  $\text{PWM} \times 2$ LAN9115 Oscillator Test PRS × 1 module, 48 MHz. Control not mounted Oscillator 3.3 V power supply module, 1.5 V power supply (CPU, FPGA) mounted 1.2 V power supply (FPGA)

Figure 1-3. Overall Block Diagram

#### 1.1.6 Detailed block diagram of PFESiP EP-1 Evaluation Board Lite

PFESiP/V850EP1 SELFREFZ CSZ7-0 A25-20 A19-0 D15-0 FPGA, CN1 ◀ Unconnected ← FPGA, CN1 ◀ P27-20 (INTPZ23-16) P17-10 (INTPZ15-8) P157-150 (INTPZ31-24) P07-00 (INTPZ7-0) FPGA FPGA, LAN circuit LAN circuit ►LAN circuit FPGA FPGA DMARQZ3-2 (P133-132) TCZ3-2 (P123-122) DMARZ23-2 (P127-126) DMARQZ1-0 (P131-130) TCZ1-0 (P121-120) DMAKZ1-0 (P125-124) PWMO1-0 (P147-146) TO3-0 (P53-50) TI3-0 (P43-40) ETCUD1-0 (P57, P56) ETCUD1-0 (P57, P56) ETCUB1-0 (P111, P110) ETO1-0 (P111, P110) DMARQZ3-2 (P133-132) RD2 ► FPGA, LAN circuit ► FPGA **^** FPGA IORDZ ► FPGA IORDZ DQM3-0 SDWEZ SDCASZ SDRASZ SDCKE WRSTBZ WAITZ HLDRQZ HLDAKZ BENZ3-0 BCYSTZ CN2 ►FPGA -FPGA -FPGA CN1, CN8: USB function MINI-B FPGA → FPGA → FPGA ETCLR1-U (P111, P110) ETO1-0 (P113, P112) SCK1-0 (P143, P140) SIO1-0 (P144, P141) SO1-0 (P145, P142) TCLR3-0 (P47, P44) TXD3, TXD2 (P37, P35) RXD3, RXD2 (P36, P34) BCYSTZ REFRQZ ► FPGA BUSCLE D31-16 CN2 SCSZ3-0 SA19-0 SD15-0  $22\Omega$ CP2102 RXD/CTS 64M Bit Flash ROM SRDZ SRDZ SIOWRZ SIORDZ SWRSTBZ SWAITZ SHLDRQZ SHLDAKZ SBENZ1-0 SBCYSTZ SREFRQZ SREFRQZ CN2 CE A22-21 A20-0 DQ15-0 WE OE UHD0P UHD0M UHD1P UHD1M CN6: USB circuit ► host × 2 -FPGA PPON0,1 OCI0,1 256M SDRAM CS# BA1-0 A12-0 DQ15-0 DQMH DQML WE# CAS# UFDP USB function MINI-B SBUSCLK UFDM VBUSDET connector SDMARQZ1-0 SDMAAKZ1-0 STCZ1-0 30MHz OSC Module PCI KIN 48MHz OSC Not mounted DCF UCLK DRSTZ nector) -026-170S Module CKE FPGA-NMI DDI DDO CLK FPGA -۸۸۸ RMODEZ TRCCLK TRCEND FPGA RESET RESET Pull-up/pull-down legends TRCDATA7-0 TRCCE EVIN P114 (EVTTRG) P115 (DBINT) gen. SW\_ RESET T° ▽ 3.3V <del>-</del> ₩. Ā LAN UART (USB) VBRESTOZ VBRESTOZ ОТР ►EVTTRG ►DBINT —ADTRG TP VBCLKOUT ADTRG (P116) XT1 XT2 Module ОТР 3.3V <del>-</del> PLLFO AVREFF AIN7-AIN0 QTP -CN2 TESTCLK AVREF 1.2V Regulator 7/1/ TMODE0 TMODE1 TMODE2 TMODE3 TMODE1 resistance not mounted at shipment AVDD\_AD EVDD AGND\_AD EGND 3.3V 3.3V +5V GND SW1-SW3 1kΩ SCKMD1-0 CLKDV1-0 PLL18-0 PLLFOEN IROMEN VBCLKEN AVDD\_PLL IVDD AGND\_PLL IGND 1.5\/ mRegulator BOOTSEL JCLKSEL0 TMS open FPGA open UCLKSEL1 TRS VSBRAMEN TCK MODE1-0 SLBS0 SLBS1 TMC2-7777 7/1/

Figure 1-4. Detailed Block Diagram of PFESiP EP-1 Evaluation Board Lite (1/2)

Figure 1-4. Detailed Block Diagram of PFESiP EP-1 Evaluation Board Lite (2/2)

#### 1.1.7 Caution regarding maximum operating frequency of PFESiP/V850EP1

The maximum operating frequency of the PFESiP/V850EP1 differs depending on the operating conditions. CPCLK is an integer multiple of VBCLK and BUSCLK, and VBCLK is equal to or is an integer multiple of BUSCLK. Conditions half or less of those of CPCLK are applied to VBCLK. Consequently, the combinations of settings are restricted as follows.

Table 1-2. Maximum Operating Frequency of PFESiP/V850EP1 According to Operating Conditions

| SDRAM,             | Prioritized  | Clocks                  |          |                          |  |  |

|--------------------|--------------|-------------------------|----------|--------------------------|--|--|

| Low-Speed Mask ROM | Clocks CPCLK |                         | VBCLK    | BUSCLK                   |  |  |

| None               | CPCLK, VBCLK | 200 MHz <sup>Note</sup> | 100 MHz  | 100 MHz                  |  |  |

| Present            | CPCLK, VBCLK | 200 MHz                 | 100 MHz  | 50 MHz <sup>Note</sup>   |  |  |

|                    | BUSCLK       | 200 MHz                 | 66.6 MHz | 66.6 MHz <sup>Note</sup> |  |  |

Note Clock that is the reference for determining the frequency.

Caution The design-guaranteed value of the maximum operating frequency cannot always be achieved, depending on the load of the FPGA.

#### 1.2 Overview of PFESiP/V850EP1

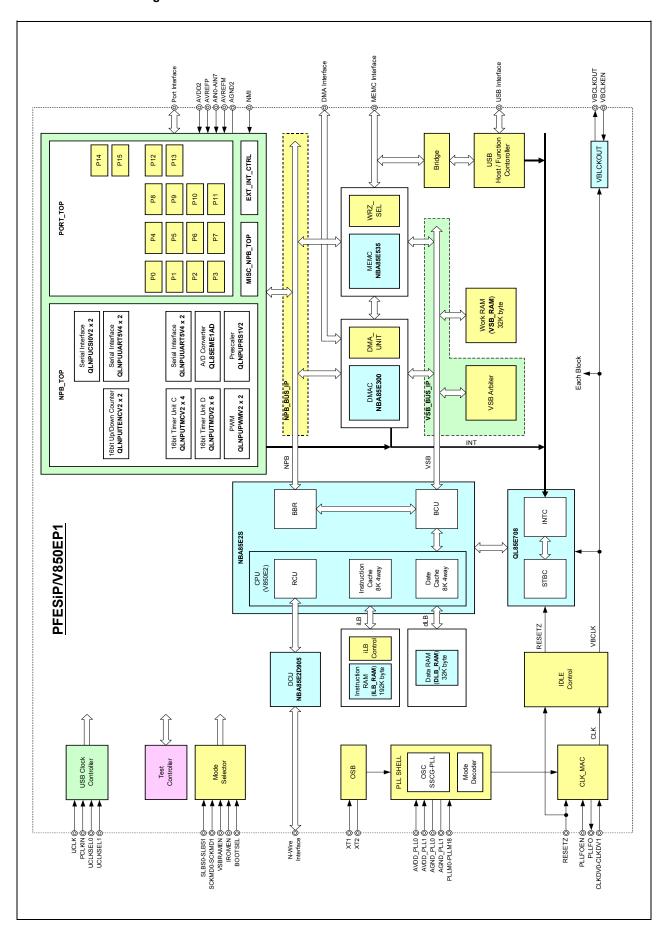

The PFESiP/V850EP1 is a microcontroller function chip developed for the PFESiP EP-1 Series and uses a V850E2 CPU core.

The PFESiP/V850EP1 uses a high-speed process in which the CPU core operates at 200 MHz (maximum) and the internal bus at 100 MHz (maximum). This CPU core has an on-chip instruction cache and data cache. Furthermore, it has a DMA controller, an interrupt controller, general-purpose ports, a timer, a serial interface, an A/D converter, a memory controller, a host controller supporting USB 2.0 FS (full-speed) and LS (low-speed), a function controller supporting USB 2.0 FS (full-speed) as on-chip peripheral functions, and internal functions as a single-chip microcontroller.

A ROM/page ROM/SRAM or SDRAM can be connected as an external memory. Furthermore, the PFESiP/V850EP1 has an on-chip instruction RAM and data RAM, and can perform high-speed processing by executing an external program by transferring it to the instruction RAM.

In software application evaluation, debugging by the N-Wire in-circuit emulator and downloading of programs can be performed using the on-chip debug control unit (DCU).

#### 1.2.1 Functions of PFESiP/V850EP1

(1/2)

| _   | _                                 | Decid (N          | (1/2)                                                                                                                 |  |  |  |  |

|-----|-----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ite | em                                | Product Name      | PFESiP/V850EP1                                                                                                        |  |  |  |  |

| С   | PU core                           |                   | V850E2 CPU core                                                                                                       |  |  |  |  |

|     | Minimum instruction ex            | recution time     | 5.0 ns (during 200 MHz operation)                                                                                     |  |  |  |  |

|     | General-purpose regis             | ters              | 32 bits × 32                                                                                                          |  |  |  |  |

|     | Instruction set                   |                   | V850E2 instruction set                                                                                                |  |  |  |  |

|     | Instruction cache                 |                   | 8 KB 4-way set associative instruction cache                                                                          |  |  |  |  |

|     | Data cache                        |                   | 8 KB 4-way set associative data cache                                                                                 |  |  |  |  |

| ln  | struction RAM                     | Can               | 192 KB RAM structure (128-bit fetch bus)                                                                              |  |  |  |  |

| (il | _B_RAM)                           | independently     |                                                                                                                       |  |  |  |  |

| D   | ata RAM (dLB_RAM)                 | access each other | 32 KB (CPCLK × 1-clock access)                                                                                        |  |  |  |  |

| W   | ork RAM (VSB_RAM)                 | Other             | 32 KB (VBCLK × 2-clock access)                                                                                        |  |  |  |  |

| D   | MA controller                     |                   | 4-channel DMA controller                                                                                              |  |  |  |  |

| М   | emory space,                      |                   | External 66.7 MHz interface                                                                                           |  |  |  |  |

| m   | emory access function             |                   | • 512 MB linear address space                                                                                         |  |  |  |  |

|     |                                   |                   | Memory area division function                                                                                         |  |  |  |  |

|     |                                   |                   | Programmable chip select function: 8                                                                                  |  |  |  |  |

|     |                                   |                   | Programmable wait function                                                                                            |  |  |  |  |

|     |                                   |                   | Idle state insertion function                                                                                         |  |  |  |  |

|     |                                   |                   | Page ROM/ROM/SRAM/SDRAM interface                                                                                     |  |  |  |  |

|     |                                   |                   | SDRAM support area: CSZ1, CSZ3, CSZ4, and CSZ6 areas                                                                  |  |  |  |  |

| In  | terrupts/exceptions               |                   | Non-maskable interrupt (NMI): 1                                                                                       |  |  |  |  |

|     |                                   |                   | Maskable interrupts                                                                                                   |  |  |  |  |

|     |                                   |                   | User interrupts: 32 (external interrupts)                                                                             |  |  |  |  |

|     |                                   |                   | Internal interrupts: 56 (NPB macro: 45, DMA: 4, USB: 7)                                                               |  |  |  |  |

|     |                                   |                   | Priority level specifiable in 8 levels                                                                                |  |  |  |  |

|     |                                   |                   | Software exceptions: 32 sources                                                                                       |  |  |  |  |

|     |                                   |                   | Exception trap: 1 source                                                                                              |  |  |  |  |

|     |                                   |                   | Valid-edge select function                                                                                            |  |  |  |  |

|     |                                   |                   | Variable digital noise filter function                                                                                |  |  |  |  |

| Si  | SiP-dedicated interface functions |                   | SRAM interface     Address space: 2 MB     4 dedicated chip select signals selected from CSZ1 to CSZ7 using registers |  |  |  |  |

|     |                                   |                   | 16-bit data bus Bus hold function supported                                                                           |  |  |  |  |

|     |                                   |                   | DMA interface     Interface with 2 channels selected from 4 channels using registers                                  |  |  |  |  |

|     |                                   |                   | External interrupt function     8 interrupt signals assigned to SiP internal connections first                        |  |  |  |  |

| St  | andby function                    |                   | IDLE/HALT mode (IDLE mode can be released by external interrupt and reset)                                            |  |  |  |  |

(2/2)

| Product Name                                      | PFESiP/V850EP1                                                                     |                                          |  |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|

| Item                                              | 1 1 2611 / 1000021 1                                                               |                                          |  |  |  |  |  |

| On-chip peripheral functions (NPB bus connection) |                                                                                    |                                          |  |  |  |  |  |

| I/O ports                                         | CMOS I/Os: 121                                                                     |                                          |  |  |  |  |  |

| Timers                                            | 16-bit timer/event counter × 4 channels                                            |                                          |  |  |  |  |  |

|                                                   | Interval timer × 6 channels                                                        |                                          |  |  |  |  |  |

|                                                   | Up/down counter/timer for 16-bit 2-phase encoder input $	imes$ 2                   | channels                                 |  |  |  |  |  |

| PWM unit                                          | 8-/9-/10-/12-bit resolution PWM output $	imes$ 2 channels                          |                                          |  |  |  |  |  |

| Serial interfaces                                 | Asynchronous serial interface × 4 channels                                         |                                          |  |  |  |  |  |

|                                                   | Clocked serial interface × 2 channels                                              |                                          |  |  |  |  |  |

| USB host controller                               | USB 2.0 FS (full-speed), LS (low-speed) supported                                  | Both host controller and                 |  |  |  |  |  |

|                                                   | Internal 2-channel root-hub function                                               | function controller are placed at        |  |  |  |  |  |

|                                                   | 2-channel downstream port                                                          | CSZ5.                                    |  |  |  |  |  |

| USB function controller                           | 1 channel supporting USB 2.0 FS (full-speed)                                       | USB host controller uses external SDRAM. |  |  |  |  |  |

|                                                   | Number of end points: 4                                                            | Oxformal OBT V IVI.                      |  |  |  |  |  |

|                                                   | (control, bulk-in, bulk-out, interrupt)                                            |                                          |  |  |  |  |  |

| A/D converter                                     | Internal 8-channel 10-bit 500 kHz A/D converter (NPB bus connection)               |                                          |  |  |  |  |  |

| On-chip debug functions                           | Incorporated in debug controller (DCU)                                             |                                          |  |  |  |  |  |

|                                                   | Run/break function, trace function, event function                                 |                                          |  |  |  |  |  |

| Clock line                                        | External clock input multiplied by PLL and clock supplied (SSCG function provided) |                                          |  |  |  |  |  |

|                                                   | CPU: 200 MHz maximum, bus clock: 100 MHz maximum (CPCLK: VBCLK = 1/2, 1/3, 1/4)    |                                          |  |  |  |  |  |

|                                                   | SDRAM interface: 66.7 MHz maximum (VBCLK: BUSCLK = 1/1, 1/2)                       |                                          |  |  |  |  |  |

|                                                   | Clock source and PLL setting switch pin provided (not switchable during operation) |                                          |  |  |  |  |  |

| Power supply                                      | For pin power supply: EV <sub>DD</sub> = 3.3 ±0.3 V                                |                                          |  |  |  |  |  |

|                                                   | For internal power supply: IV <sub>DD</sub> = 1.5 ±0.15 V                          |                                          |  |  |  |  |  |

| Series                                            | CB-12M type                                                                        |                                          |  |  |  |  |  |

**Remark** The PFESiP EP-1 Evaluation Board Lite does not support the trace function.

#### 1.2.2 Internal block diagram of PFESiP/V850EP1

### 1.2.3 PFESiP/V850EP1 pins usable on this board

(1/7)

| Usable PFESiP/V850EP1 Pins |                |                |                            |     | cted to | Connected to FPGA | (1/7) On-Board Peripheral-Circuit     |

|----------------------------|----------------|----------------|----------------------------|-----|---------|-------------------|---------------------------------------|

| Port                       | Function Pin 1 | Function Pin 2 | SiP Internal<br>Connection | CN1 | CN2     | FPGA Pin Name     | Connection and Pin Processing         |

| P00                        | INTPZ0         | CCC00          | _                          | 2   | _       | INTPZ0/CCC00      | 50 kΩ Pull-up                         |

| P01                        | INTPZ1         | CCC01          | _                          | 3   | _       | INTPZ1/CCC01      | 50 kΩ Pull-up                         |

| P02                        | INTPZ2         | CCC10          | _                          | 4   | _       | INTPZ2/CCC10      | 50 kΩ Pull-up                         |

| P03                        | INTPZ3         | CCC11          | _                          | 5   | _       | INTPZ3/CCC11      | 50 kΩ Pull-up                         |

| P04                        | INTPZ4         | CCC20          | _                          | 7   | _       | INTPZ4/CCC20      | 50 kΩ Pull-up                         |

| P05                        | INTPZ5         | CCC21          | _                          | 8   | _       | INTPZ5/CCC21      | 50 kΩ Pull-up                         |

| P06                        | INTPZ6         | CCC30          | -                          | 9   | -       | INTPZ6/CCC30      | 50 kΩ Pull-up                         |

| P07                        | INTPZ7         | CCC31          | _                          | 10  | _       | INTPZ7/CCC31      | 50 kΩ Pull-up                         |

| P10                        | INTPZ8         | CC00           | -                          | 12  | -       | INTPZ8/CC00       | 50 kΩ Pull-up                         |

| P11                        | INTPZ9         | CC01           | _                          | 13  | _       | INTPZ9/CC01       | 50 kΩ Pull-up                         |

| P12                        | INTPZ10        | CC10           | _                          | 14  | _       | INTPZ10/CC10      | 50 kΩ Pull-up                         |

| P13                        | INTPZ11        | CC11           | _                          | 15  | _       | INTPZ11/CC11      | 50 kΩ Pull-up                         |

| P14                        | INTPZ12        | _              | _                          | 17  | _       | INTPZ12           | 50 kΩ Pull-up                         |

| P15                        | INTPZ13        | _              | _                          | 18  | _       | INTPZ13           | 50 kΩ Pull-up                         |

| P16                        | INTPZ14        | =              | _                          | 19  | _       | INTPZ14           | 50 kΩ Pull-up                         |

| P17                        | INTPZ15        | =              | _                          | 20  | _       | INTPZ15           | LAN circuit, 1 kΩ pull-up             |

| P20                        | INTPZ16        | _              | <b>√</b>                   | _   | _       | P20/INTPZ16       |                                       |

| P21                        | INTPZ17        | _              | V                          | _   | _       | P21/INTPZ17       |                                       |

| P22                        | INTPZ18        | =              | <b>√</b>                   | _   | _       | P22/INTPZ18       |                                       |

| P23                        | INTPZ19        | _              | V                          | _   | _       | P23/INTPZ19       |                                       |

| P24                        | INTPZ20        | _              | V                          | _   | _       | P24/INTPZ20       |                                       |

| P25                        | INTPZ21        | _              | V                          | _   | _       | P25/INTPZ21       |                                       |

| P26                        | INTPZ22        | _              | V                          | _   | _       | P26/INTPZ22       |                                       |

| P27                        | INTPZ23        | =              | <b>√</b>                   | _   | _       | P27/INTPZ23       |                                       |

| P30                        | RXD0           | _              | _                          | 22  | _       | _                 | USB conversion circuit, 50 kΩ pull-up |

| P31                        | TXD0           | _              | _                          | 23  | _       | _                 | USB conversion circuit, 50 kΩ pull-up |

| P32                        | RXD1           | _              | _                          | 24  | _       | _                 | 50 kΩ pull-up, USB circuit            |

| P33                        | TXD1           | _              | _                          | 25  | _       | _                 | 50 kΩ pull-up, USB circuit            |

| P34                        | RXD2           | _              | _                          | 27  | _       | _                 | 50 kΩ Pull-up                         |

| P35                        | TXD2           | _              | _                          | 28  | _       | _                 | 50 kΩ Pull-up                         |

| P36                        | RXD3           | _              | _                          | 29  | _       | _                 | 50 kΩ Pull-up                         |

| P37                        | TXD3           | _              | _                          | 30  | _       | _                 | 50 kΩ Pull-up                         |

| P40                        | TI0            | _              | _                          | 32  | _       | TI0               | 50 kΩ Pull-up                         |

| P41                        | TI1            | =              | _                          | 33  | _       | TI1               | 50 kΩ Pull-up                         |

| P42                        | TI2            | =              | _                          | 34  | _       | TI2               | 50 kΩ Pull-up                         |

| P43                        | TI3            | _              | _                          | 35  | _       | TI3               | 50 kΩ Pull-up                         |

| P44                        | TCLR0          | =              | _                          | 37  | _       | TCLR0             | 50 kΩ Pull-up                         |

| P45                        | TCLR1          | _              | _                          | 38  | _       | TCLR1             | 50 kΩ Pull-up                         |

| P46                        | TCLR2          | =              | -                          | 39  | _       | TCLR2             | 50 kΩ Pull-up                         |

| P47                        | TCLR3          | _              | _                          | 40  | _       | TCLR3             | 50 kΩ Pull-up                         |

(2/7)

|      | Usable PFESiP/V850EP1 Pins |                |                            |     | cted to | Connected to FPGA | (2/7 On-Board Peripheral-Circuit                     |

|------|----------------------------|----------------|----------------------------|-----|---------|-------------------|------------------------------------------------------|

| Port | Function Pin 1             | Function Pin 2 | SiP Internal<br>Connection | CN1 | CN2     | FPGA Pin Name     | Connection and Pin Processing                        |

| P50  | TO0                        | -              |                            | 42  | -       | TO0               | 50 kΩ Pull-up                                        |

| P51  | TO1                        | _              | -                          | 43  | -       | TO1               | 50 kΩ Pull-up                                        |

| P52  | TO2                        | _              | _                          | 44  | _       | TO2               | 50 kΩ Pull-up                                        |

| P53  | TO3                        | _              | _                          | 45  | _       | TO3               | 50 kΩ Pull-up                                        |

| P54  | ETIUD0                     | _              | -                          | 47  | _       | ETIUD0            | 50 kΩ Pull-up                                        |

| P55  | ETIUD1                     | _              | _                          | 48  | _       | ETIUD1            | 50 kΩ Pull-up                                        |

| P56  | ETCUD0                     | _              | _                          | 49  | _       | ETCUD0            | 50 kΩ Pull-up                                        |

| P57  | ETCUD1                     | -              | _                          | 50  | _       | ETCUD1            | 50 kΩ Pull-up                                        |

| P60  | A20                        | _              | _                          | _   | 3       | P60/A20           | Flash ROM                                            |

| P61  | A21                        | _              | _                          | _   | 4       | P61/A21           | Flash ROM                                            |

| P62  | A22                        | _              | =                          | =   | 5       | P62/A22           | Flash ROM                                            |

| P63  | A23                        | _              | -                          | -   | 7       | P63/A23           | SDRAM, flash ROM                                     |

| P64  | A24                        | _              | =                          | _   | 8       | P64/A24           | SDRAM                                                |

| P65  | A25                        | _              | _                          | _   | 9       | P65/A25           |                                                      |

| P66  | A0                         | _              | _                          | _   | 10      | P66/A0            |                                                      |

| P67  | A1                         |                | _                          | _   | 12      | P67/A1            | LAN circuit, SDRAM, flash ROM                        |

| -    | A2                         | _              | _                          | _   | _       | -                 | LAN circuit, SDRAM, flash ROM                        |

|      | A3                         |                |                            |     |         | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A4                         |                |                            | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

|      | A5                         |                |                            |     |         |                   |                                                      |

| _    |                            | _              | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A6                         | -              | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A7                         | =              | =                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A8                         | _              | =                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A9                         | _              | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A10                        | _              | -                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A11                        | _              | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A12                        |                | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A13                        | _              | _                          | _   | _       | _                 | LAN circuit, SDRAM, flash ROM                        |

| _    | A14                        | _              | _                          | _   | _       | _                 | LAN circuit, flash ROM                               |

| _    | A15                        | _              | _                          | _   | _       | _                 | LAN circuit, flash ROM                               |

| _    | A16                        | _              | =                          | -   | -       | _                 | Flash ROM                                            |

| _    | A17                        | _              | _                          | _   | _       | _                 | Flash ROM                                            |