### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# PFESiP/V850EP1

## 32-bit Microcontroller Dedicated to PFESiP<sup>®</sup> EP-1

Hardware (USB Function)

Document No. A19071EJ2V0UM00 (2nd edition) Date Published November 2009 NS

© NEC Electronics Corporation 2008, 2009 Printed in Japan [MEMO]

#### NOTES FOR CMOS DEVICES

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### (3) PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### (6) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

PFESiP is a registered trademark of NEC Electronics Corporation in Japan, Germany, and United Kingdom.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of November, 2009. The information is subject to change without

notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for

the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in

every country. Please check with an NEC Electronics sales representative for availability and additional

information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage

to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must

incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

- (Note 1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

(M8E0909)

#### **Major Revisions in This Edition**

| Location    | Contents                                                                          |

|-------------|-----------------------------------------------------------------------------------|

| p.85        | Modification of 3.4.1 (1) MEMC_INT                                                |

| p.96        | Modification of 3.4.4 (3) UF0 EPNAK register (UF0EN)                              |

| pp.104, 105 | Modification of 3.4.4 (11) UF0 INT status 0 register (UF0IS0)                     |

| p.122       | Modification of 3.4.4 (28) UF0 DMA status 1 register (UF0DMS1)                    |

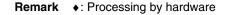

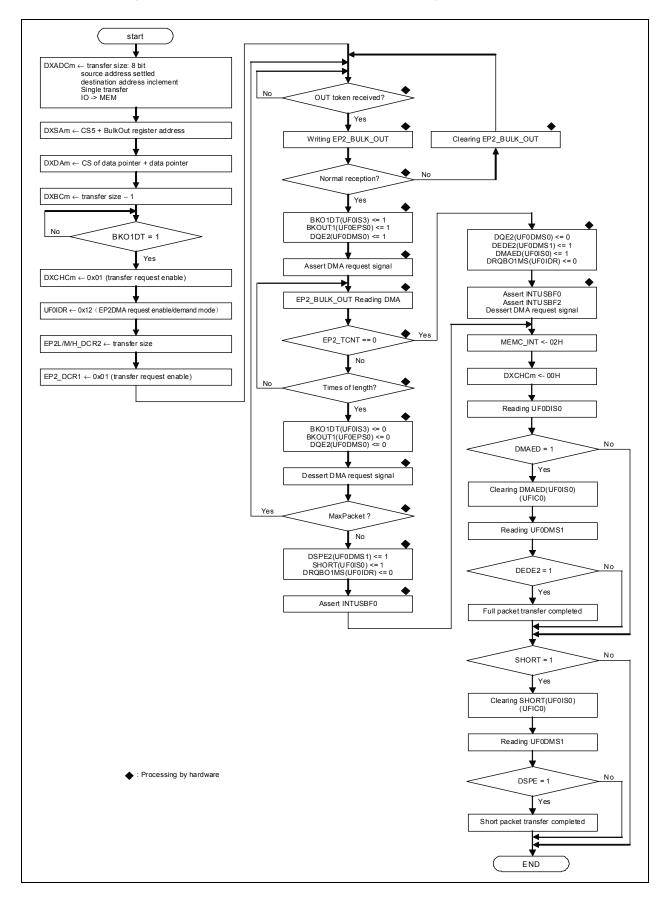

| p.203       | Modification of 3.7.6 Bulk transfer in DMA mode                                   |

| p.203       | Modification of Figure 3-26. DMA Initialization Processing                        |

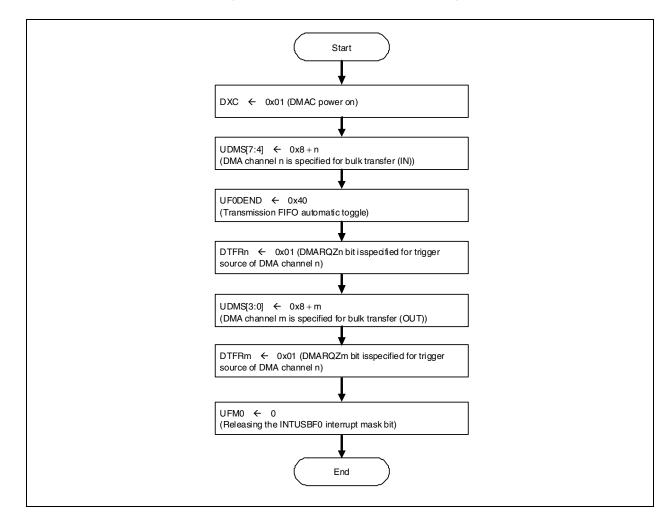

| p.204, 205  | Modification of Figure 3-27. Flow Example of Bulk Transfer Processing in DMA Mode |

| p.212       | Modification of 4.3 Clock and Reset                                               |

| p.212       | Modification of Table 4-2. UCLK Timings                                           |

The mark <R> shows major revised points.

The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

To obtain the latest documents when designing, contact an NEC sales office or a distributor.

#### PREFACE

- Readers

This manual is intended for users who understand the functions of the microcontroller function chip with an on-chip V850E2 CPU core (PFESiP/V850EP1) and wish to evaluate developing PFESiP EP-1 Series products using the chip.

- **Purpose** This manual is intended to give users an understanding of the USB functions among the hardware functions of the PFESiP/V850EP1.

**How to Read This Manual** It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, microcontrollers, SRAM, page ROM, and SDRAM.

| Conventions | Data significance:                | Higher digits on the left and lower digits on the right |

|-------------|-----------------------------------|---------------------------------------------------------|

|             | Active low representation:        | xxxZ (Z after pin or signal name)                       |

|             | Note:                             | Footnote for item marked with Note in the text          |

|             | Caution:                          | Information requiring particular attention              |

|             | Remark:                           | Supplementary information                               |

|             | Numeric representation:           | Binary xxxx or xxxxB                                    |

|             |                                   | Decimal xxxx                                            |

|             |                                   | Hexadecimal xxxxH                                       |

|             | Prefix indicating power of 2 (add | Iress space, memory capacity):                          |

|             |                                   | K (kilo): 2 <sup>10</sup> = 1,024                       |

|             |                                   | M (mega): 2 <sup>20</sup> = 1,024 <sup>2</sup>          |

|             |                                   | G (giga): 2 <sup>30</sup> = 1,024 <sup>3</sup>          |

|             | Data type:                        | Word 32 bits                                            |

|             |                                   | Halfword 16 bits                                        |

|             |                                   | Byte 8 bits                                             |

|             |                                   |                                                         |

## **Related Documents** The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such. Furthermore, some of the related documents may be documents intended for specific customers, because they are prepared when each core is being developed or planned.

#### **Documents related to PFESiP EP-1 Series**

| Document Name                                                | Document No. |

|--------------------------------------------------------------|--------------|

| V850E2 Architecture User's Manual                            | U17135E      |

| PFESiP EP-1 Series Design Manual                             | A19068E      |

| PFESiP/V850EP1 Product Data User's Manual                    | A19069E      |

| PFESiP/V850EP1 Hardware (CPU Function) User's Manual         | A19070E      |

| PFESiP/V850EP1 Hardware (USB Function) User's Manual         | This manual  |

| PFESiP/V850EP1 USB Function Sample Software Application Note | A19349E      |

#### Documents related to PFESiP EP-1 Evaluation Board

| Document Name                                                         | Document No. |  |

|-----------------------------------------------------------------------|--------------|--|

| PFESiP EP-1 Evaluation Board Technical Information User's Manual      | A19350E      |  |

| PFESiP EP-1 Evaluation Board Lite Technical Information User's Manual | A19354E      |  |

#### Documents related to development tools

| Document Name               | Document No. |               |         |

|-----------------------------|--------------|---------------|---------|

| RX850 Pro () (Real-Time OS) | Ver. 3.21    | Basics        | U18165E |

|                             | Ver. 3.20    | Installation  | U17421E |

|                             | Ver. 3.21    | Technical     | U18164E |

|                             | Ver. 3.20    | Task Debugger | U17422E |

#### CONTENTS

| CHAPTE                          | ER 1 USB FUNCTION OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                                                       |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1.1                             | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |

| 1.2                             | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                          |

| 1.3                             | USB Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 1.4                             | USB Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                          |

| 1.5                             | USB-related Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                          |

| 1.6                             | USB-related I/O Register Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| СНАРТЕ                          | ER 2 USB HOST CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                       |

| 2.1                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |

| 2.2                             | PCI Host Bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                          |

|                                 | 2.2.1 PCI host bridge function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                          |

|                                 | 2.2.2 CPU memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                          |

|                                 | 2.2.3 PCI host bridge registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                                                       |

|                                 | 2.2.4 How to initialize PCI host bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35                                                                                                                       |

| 2.3                             | OHCI Host Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                          |

|                                 | 2.3.1 OHCI host controller functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                          |

|                                 | 2.3.2 PCI configuration register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                                       |

|                                 | 2.3.3 OHCI operational register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                       |

|                                 | 2.3.4 Interrupts from USB host controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                                                                                                       |

| СНАРТЕ                          | ER 3 USB FUNCTION CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                          |

| 31                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                                                                                       |

| 3.1<br>3.2                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                          |

| 3.2                             | CPU Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69                                                                                                                       |

|                                 | CPU Memory Space<br>Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69<br>70                                                                                                                 |

| 3.2                             | CPU Memory Space<br>Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

| 3.2<br>3.3                      | CPU Memory Space         Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69<br>                                                                                                                   |

| 3.2                             | CPU Memory Space<br>Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |

| 3.2<br>3.3                      | CPU Memory Space         Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69<br>70<br>70<br>80<br>80<br>81<br>85                                                                                   |

| 3.2<br>3.3                      | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69<br>70<br>                                                                                                             |

| 3.2<br>3.3                      | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69<br>70<br>70<br>80<br>80<br>81<br>85<br>                                                                               |

| 3.2<br>3.3                      | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69<br>70<br>                                                                                                             |

| 3.2<br>3.3                      | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         3.3.4       Function bridge registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69<br>70<br>70<br>80<br>81<br>85<br>85<br>                                                                               |

| 3.2<br>3.3                      | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         3.3.4       Function bridge registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers                                                                                                                                                                                                                                                                                                                                                                              | 69<br>70<br>70<br>80<br>81<br>85<br>85<br>85<br>                                                                         |

| 3.2<br>3.3<br>3.4               | CPU Memory Space         Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69<br>                                                                                                                   |

| 3.2<br>3.3<br>3.4<br>3.5        | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake                                                                                                                                                                                                                                                                                                                    | 69<br>70<br>70<br>80<br>81<br>85<br>85<br>                                                                               |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake       Register Values in Specific Status                                                                                                                                                                                                                                                                           | 69<br>70<br>                                                                                                             |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake       Register Values in Specific Status         Firmware Processing                                                                                                                                                                                                                                               | 69<br>                                                                                                                   |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake         Register Values in Specific Status         Firmware Processing         3.7.1                                                                                                                                                                                                                               | 69<br>70<br>70<br>80<br>81<br>85<br>85<br>91<br>92<br>136<br>151<br>165<br>166<br>168<br>170<br>170                      |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake         Register Values in Specific Status         Firmware Processing         3.7.1       Initialization processing         3.7.2       Interrupt servicing.         3.7.3       USB function main processing         3.7.4       Suspend/Resume processing                                                       | 69<br>70<br>70<br>70<br>80<br>81<br>85<br>87<br>91<br>92<br>136<br>151<br>165<br>166<br>168<br>170<br>173<br>174<br>197  |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake         Register Values in Specific Status         Firmware Processing         3.7.1       Initialization processing         3.7.2       Interrupt servicing         3.7.3       USB function main processing         3.7.4       Suspend/Resume processing         3.7.5       Processing after power application | 69<br>70<br>70<br>80<br>81<br>85<br>87<br>91<br>92<br>136<br>151<br>165<br>166<br>168<br>170<br>173<br>174<br>197<br>200 |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6 | CPU Memory Space         Requests         3.3.1       Automatic requests         3.3.2       Other requests         Registers         3.4.1       Function bridge registers         3.4.2       DMA registers         3.4.3       Bulk in and bulk out registers         3.4.4       EPC Control registers         3.4.5       EPC Data hold registers         3.4.6       EPC Request data register         STALL Handshake or No Handshake         Register Values in Specific Status         Firmware Processing         3.7.1       Initialization processing         3.7.2       Interrupt servicing         3.7.3       USB function main processing         3.7.4       Suspend/Resume processing                                                        | 69<br>70<br>70<br>80<br>81<br>85<br>87<br>91<br>92<br>136<br>151<br>165<br>166<br>168<br>170<br>173<br>174<br>197<br>200 |

| СНАРТЕ | ER 4 EXTERNAL CIRCUIT CONFIGURATION              | 207 |

|--------|--------------------------------------------------|-----|

| 4.1    | USB Host Controller Connection Configuration     |     |

|        | 4.1.1 USB signal connection                      |     |

|        | 4.1.2 USB power supply connection                |     |

| 4.2    | USB Function Controller Connection Configuration | 210 |

|        | 4.2.1 USB signal connection                      | 210 |

| 4.3    | Clock and Reset                                  | 212 |

| СНАРТЕ | ER 5 CAUTIONS                                    | 213 |

| 5.1    | USB Port Status Transition Control               |     |

| 5.2    | Restriction on Number of Hub Stages              |     |

#### LIST OF FIGURES

| Figure | No. Title                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------|------|

|        |                                                                                            |      |

| 1-1    | USB Configuration                                                                          |      |

| 1-2    | USB Memory Map                                                                             | 17   |

| 2-1    | PCI Host Bridge Macro Initialization Procedure                                             |      |

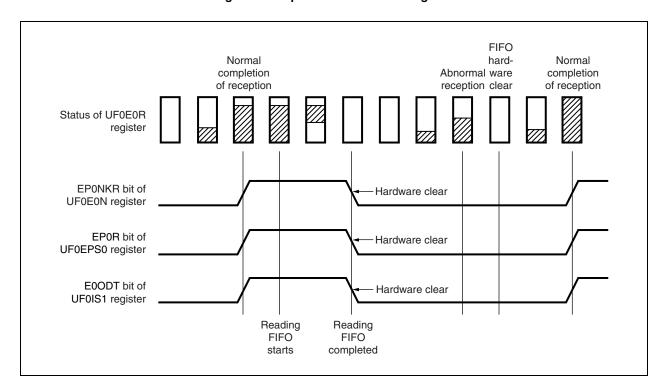

| 3-1    | Operation of UF0E0R Register                                                               | 137  |

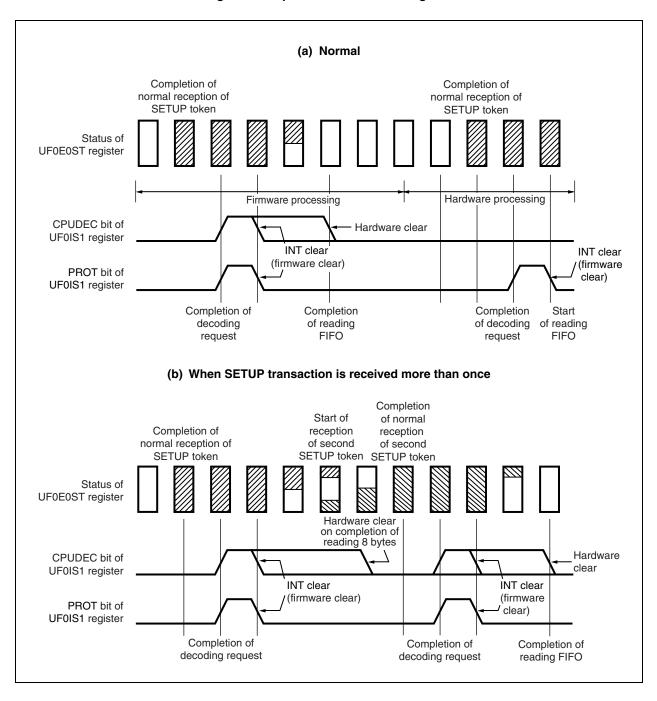

| 3-2    | Operation of UF0E0ST Register                                                              | 139  |

| 3-3    | Operation of UF0E0W Register                                                               | 141  |

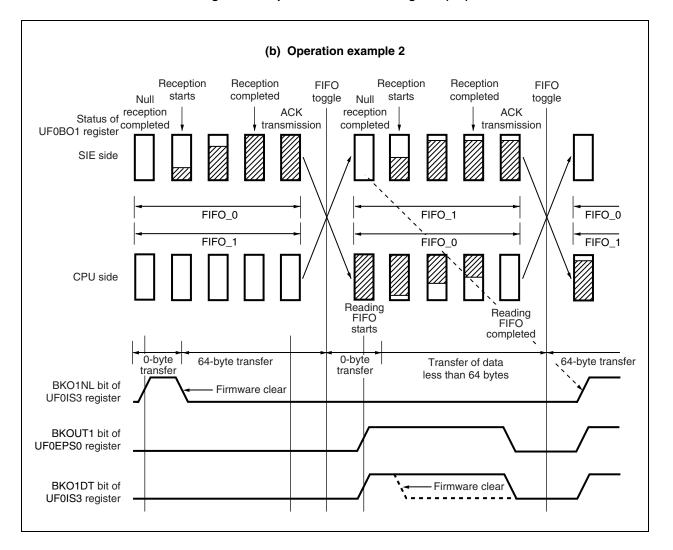

| 3-4    | Operation of UF0BO1 Register                                                               | 143  |

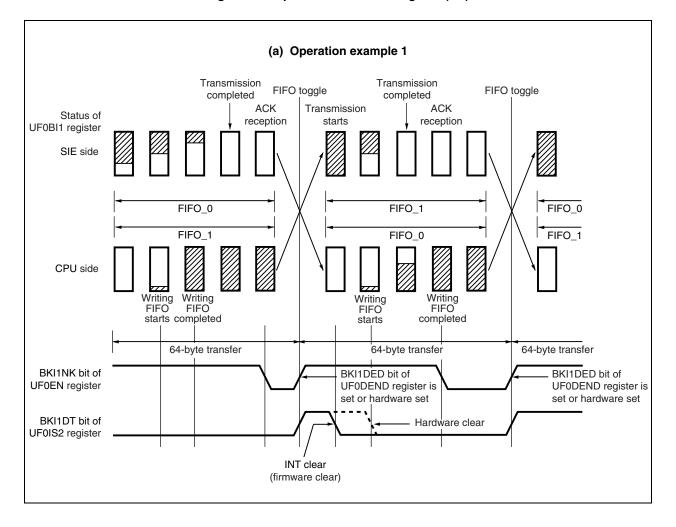

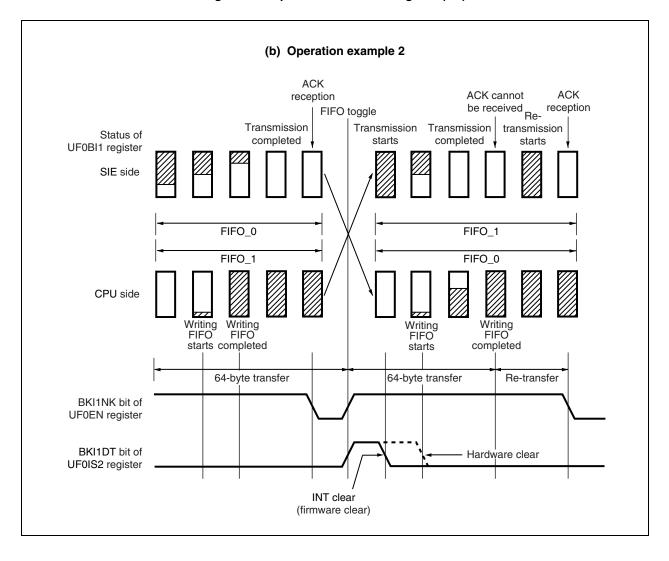

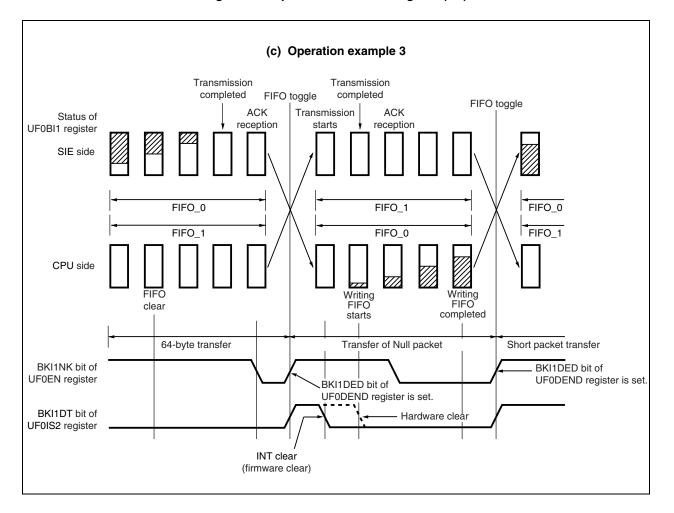

| 3-5    | Operation of UF0BI1 Register                                                               | 146  |

| 3-6    | Operation of UF0INT1 Register                                                              | 150  |

| 3-7    | Flowchart of Program When Host Is Disconnected and Then Reconnected                        | 163  |

| 3-8    | Flowchart of Program When Power Is Supplied                                                | 164  |

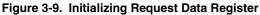

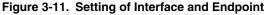

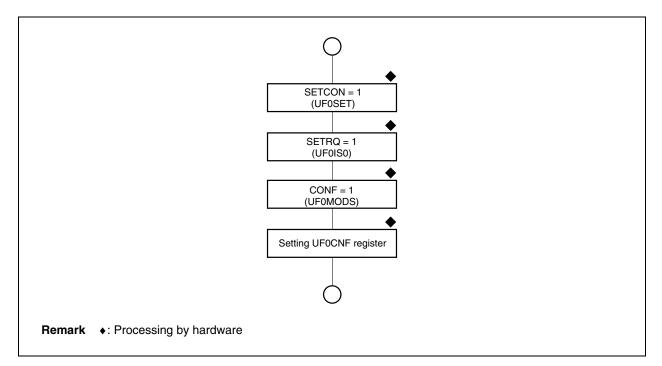

| 3-9    | Initializing Request Data Register                                                         | 170  |

| 3-10   | Initialization of Request Data Register                                                    | 171  |

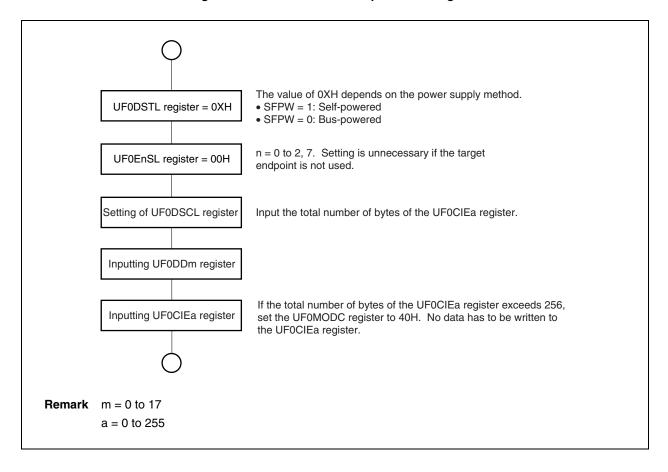

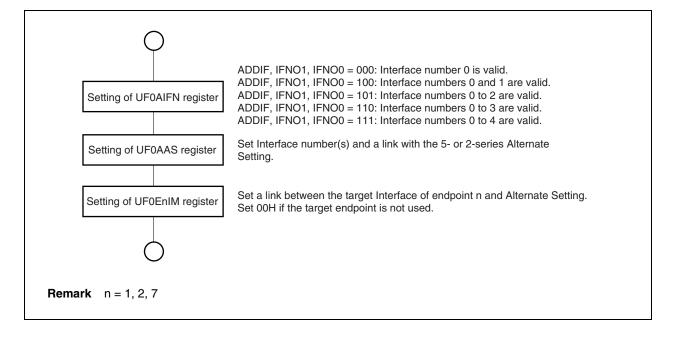

| 3-11   | Setting of Interface and Endpoint                                                          | 171  |

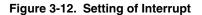

| 3-12   | Setting of Interrupt                                                                       | 172  |

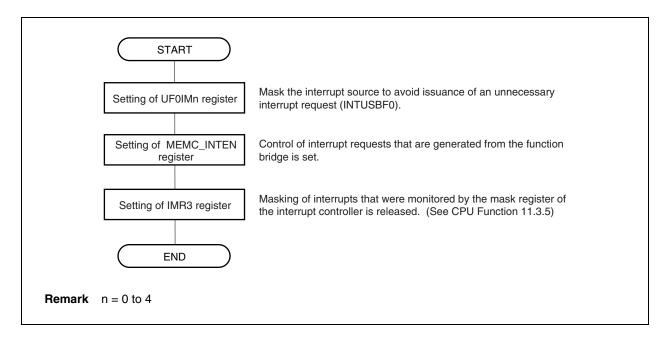

| 3-13   | Interrupt Servicing                                                                        | 173  |

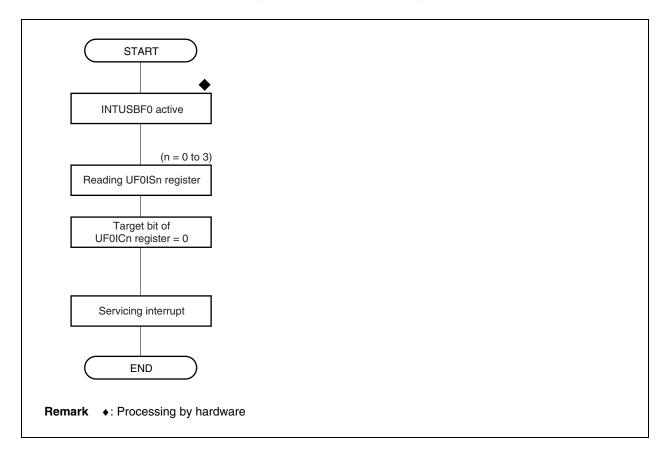

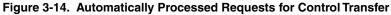

| 3-14   | Automatically Processed Requests for Control Transfer                                      | 175  |

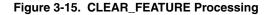

| 3-15   | CLEAR_FEATURE Processing                                                                   | 176  |

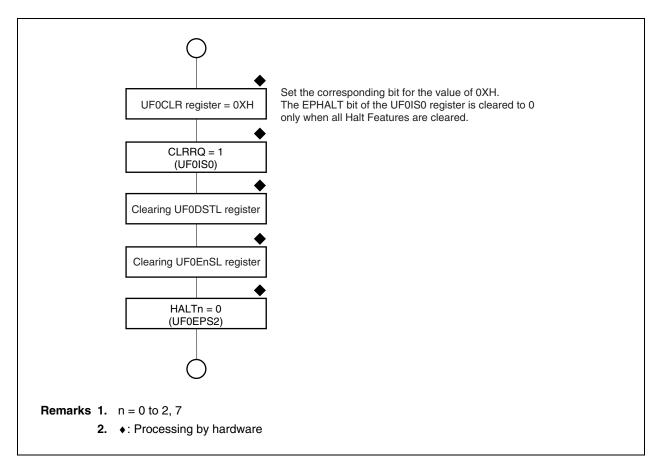

| 3-16   | SET_FEATURE Processing                                                                     | 177  |

| 3-17   | SET_CONFIGURATION Processing                                                               | 177  |

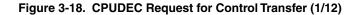

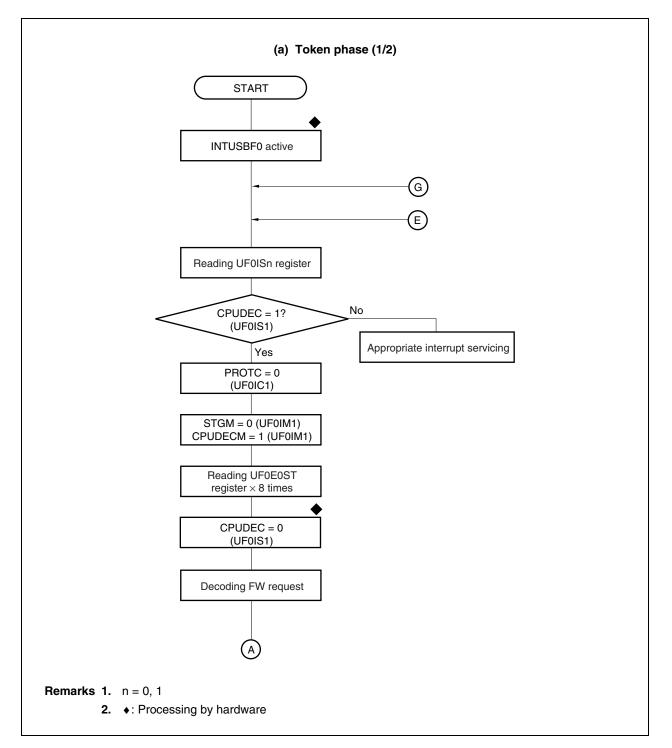

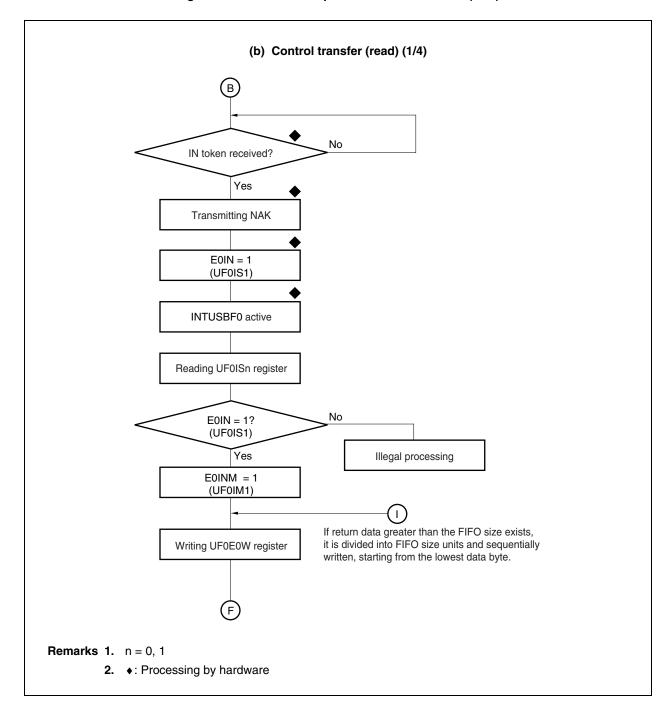

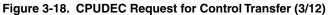

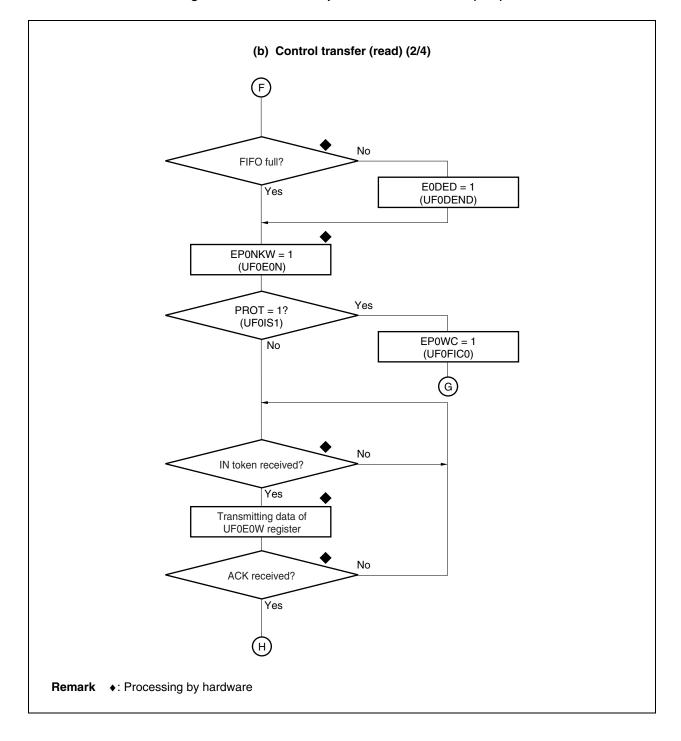

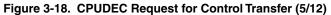

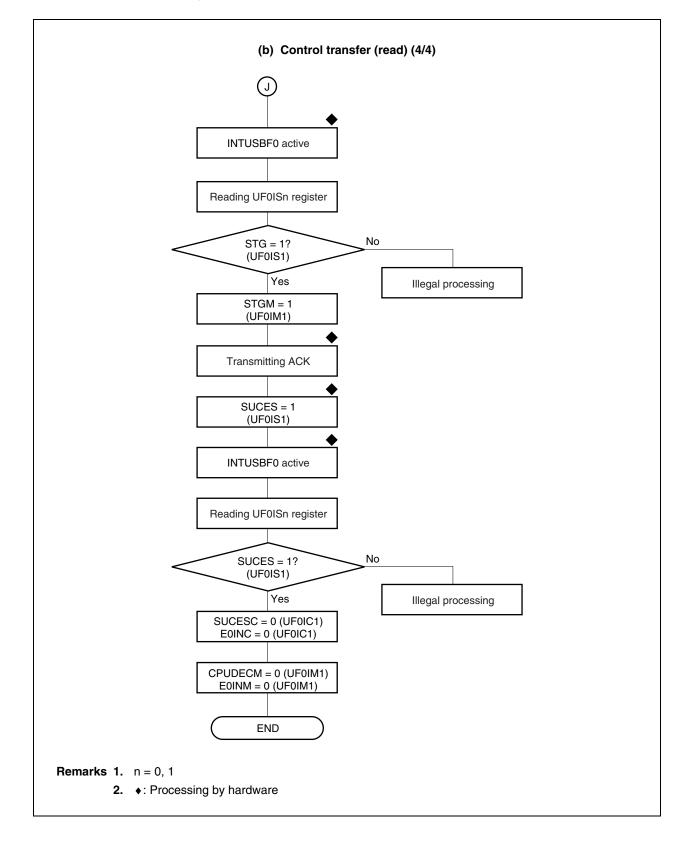

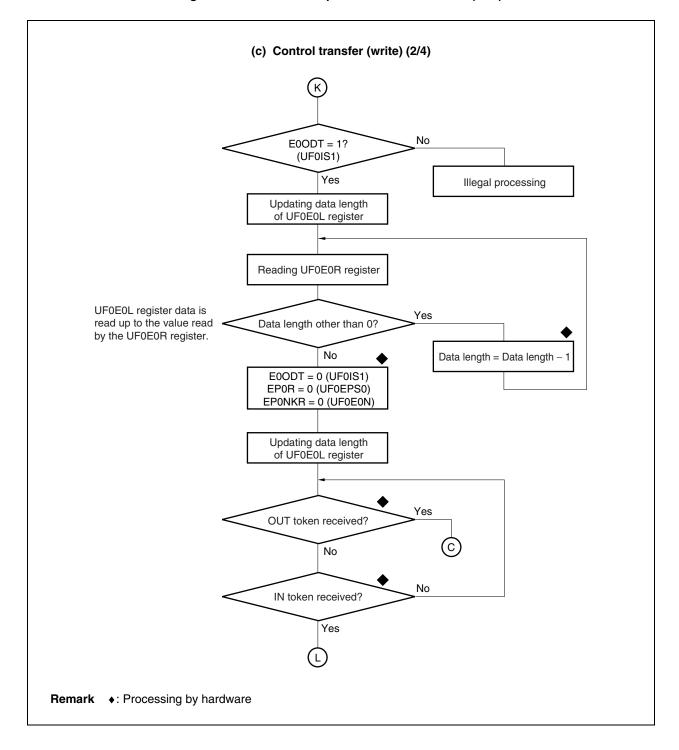

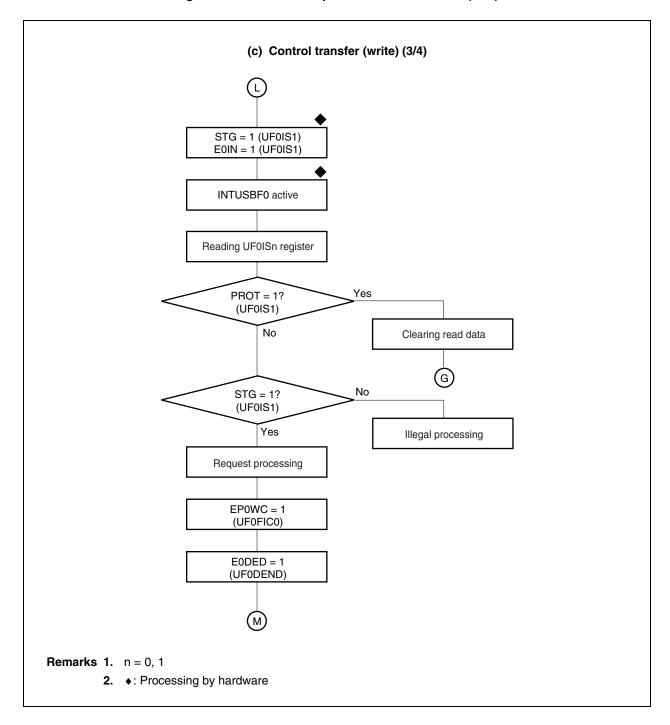

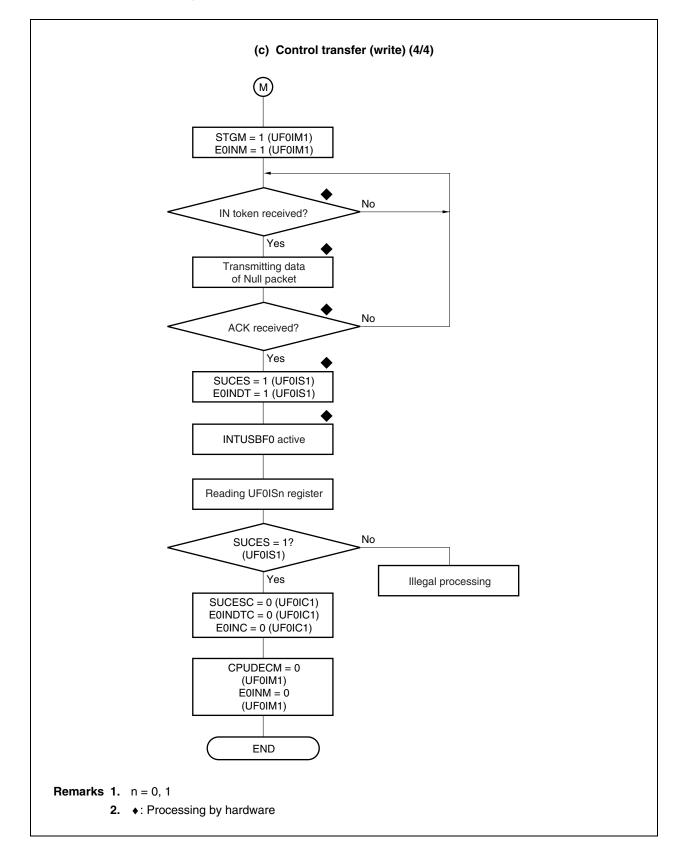

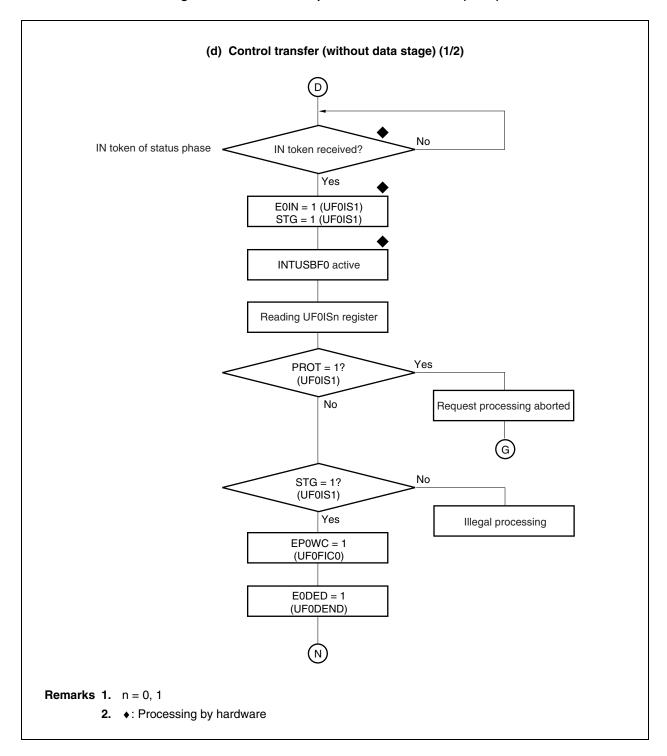

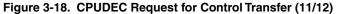

| 3-18   | CPUDEC Request for Control Transfer                                                        | 178  |

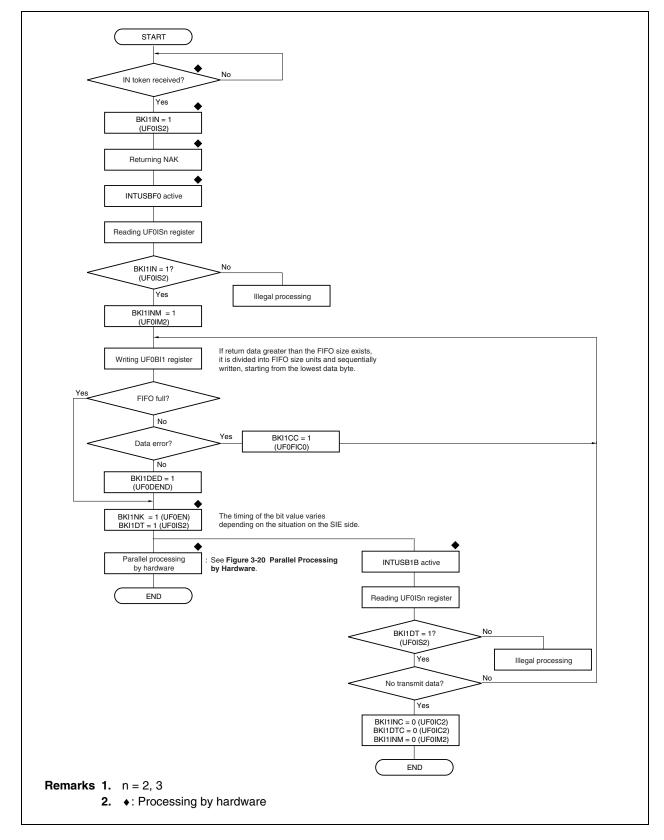

| 3-19   | Processing for Bulk Transfer (IN) (Endpoint1)                                              | 190  |

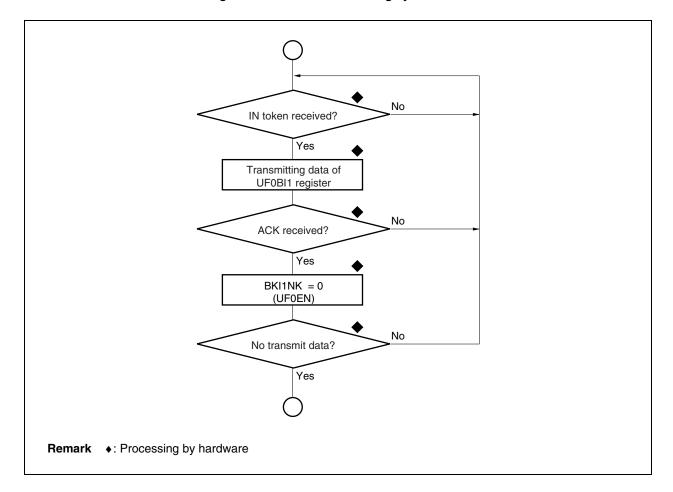

| 3-20   | Parallel Processing by Hardware                                                            | 191  |

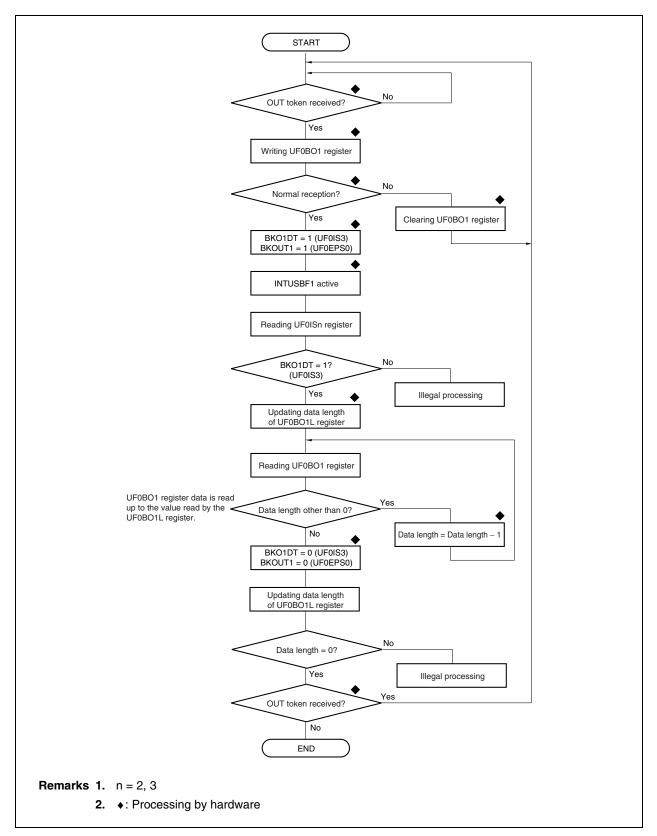

| 3-21   | Normal Processing for Bulk Transfer (OUT) (Endpoint2)                                      | 192  |

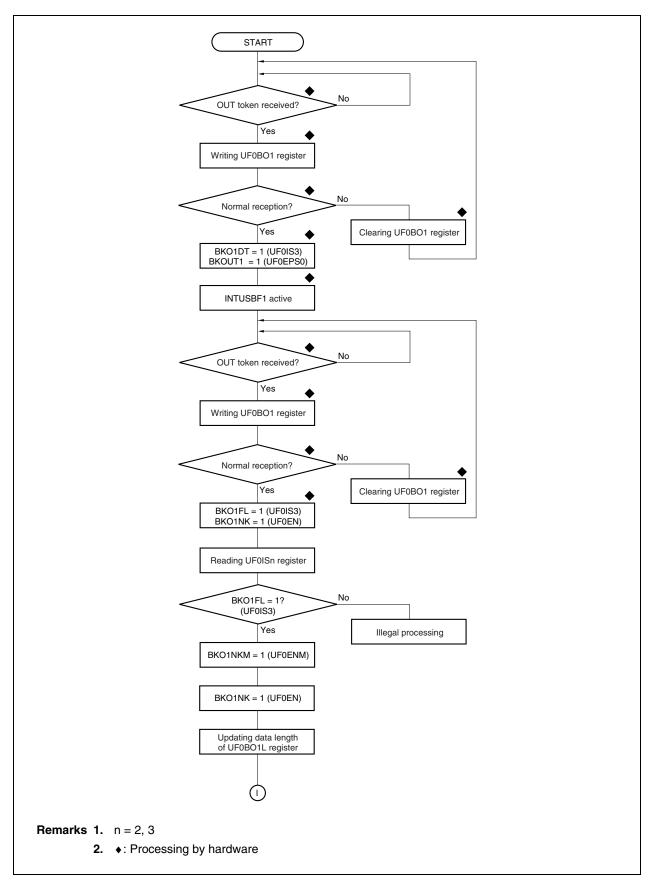

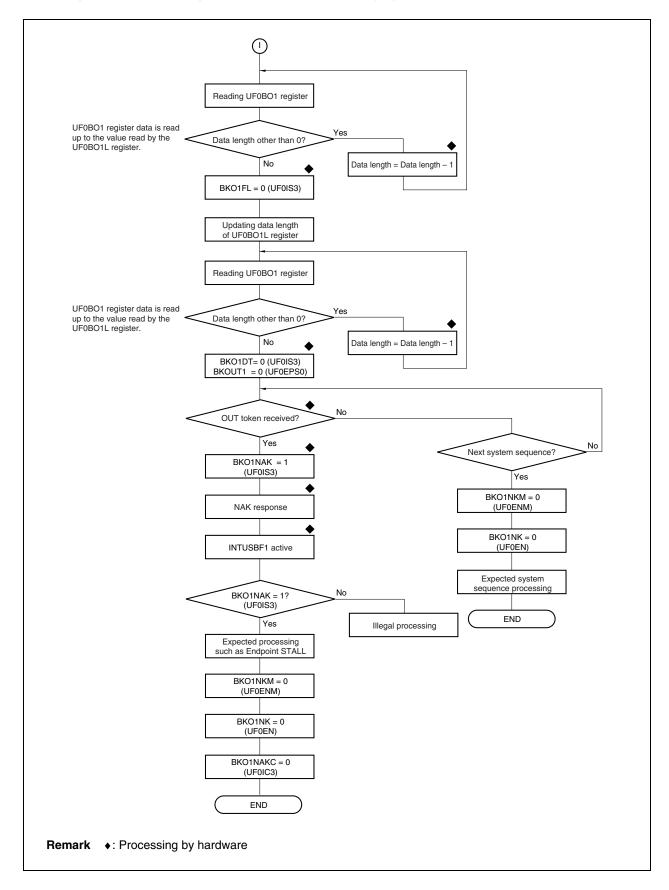

| 3-22   | Processing If More Data Than Expected by System Is Transmitted (Endpoint2)                 | 194  |

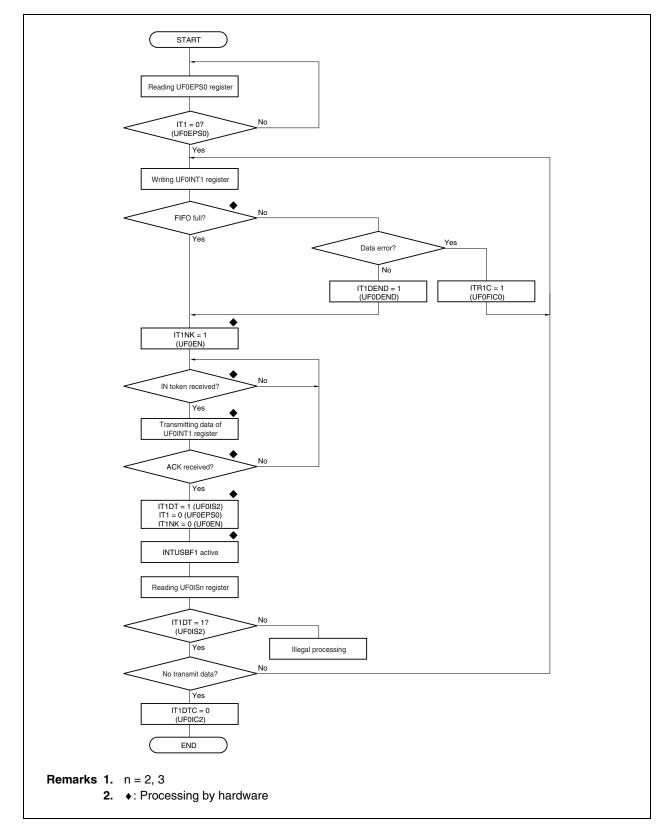

| 3-23   | Processing for Interrupt Transfer (IN) (Endpoint7)                                         | 196  |

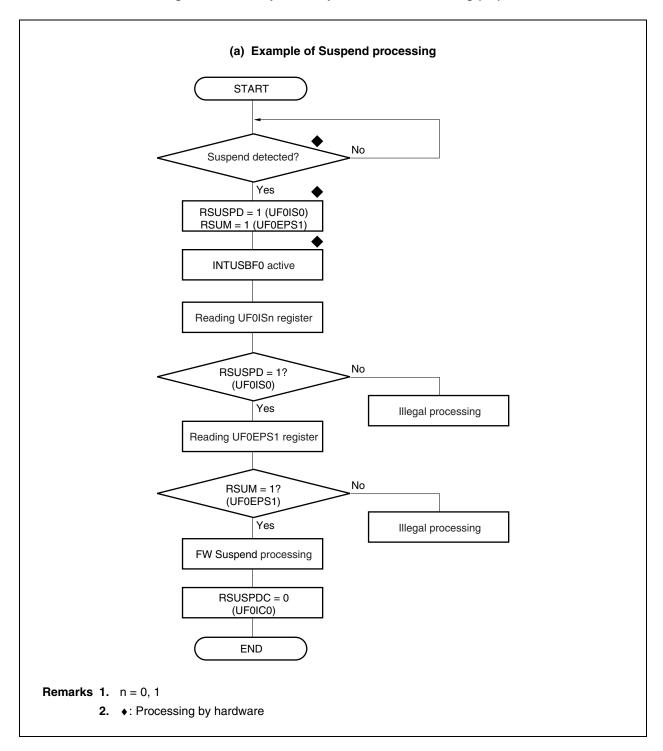

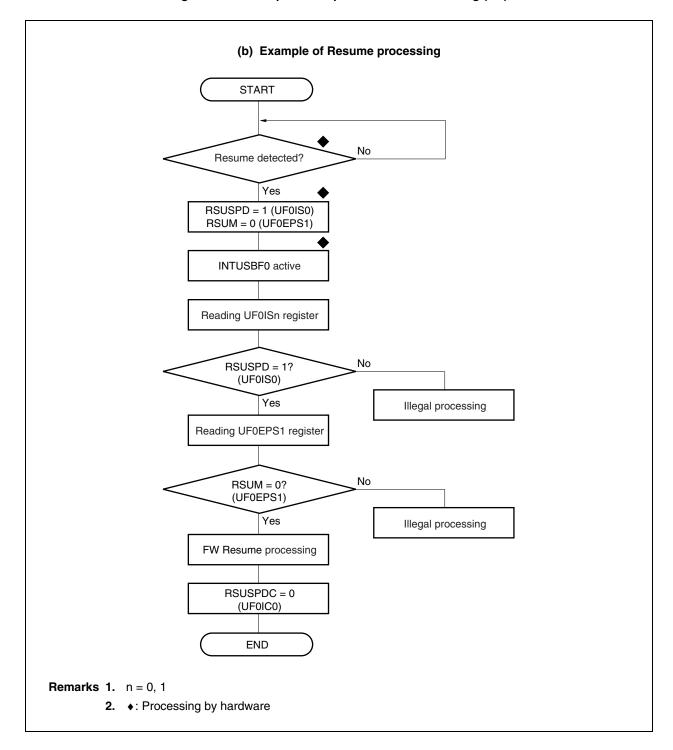

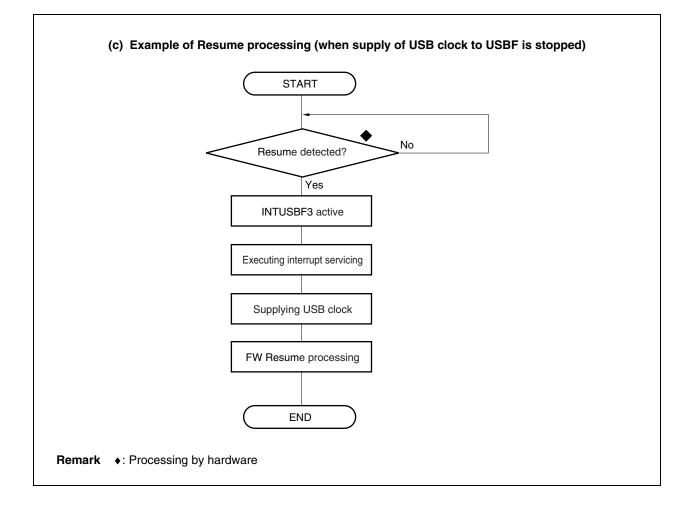

| 3-24   | Example of Suspend/Resume Processing                                                       | 197  |

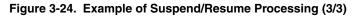

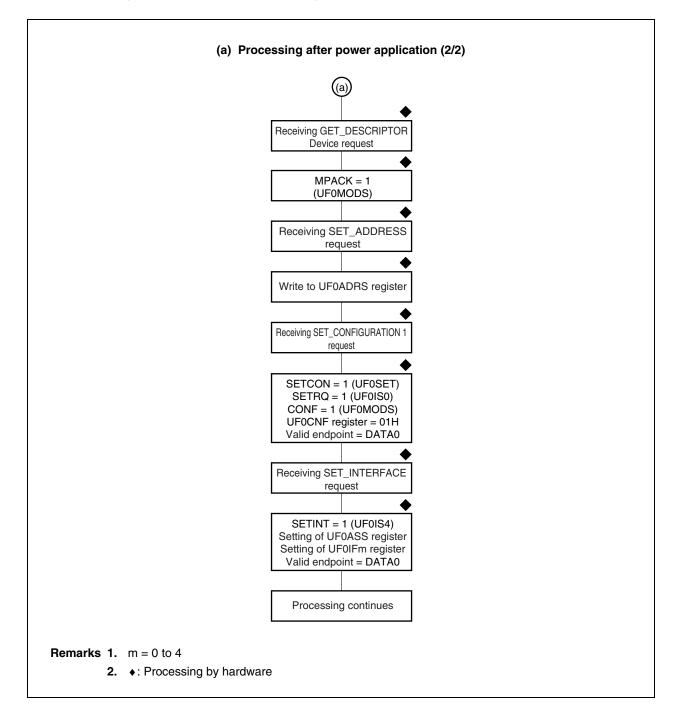

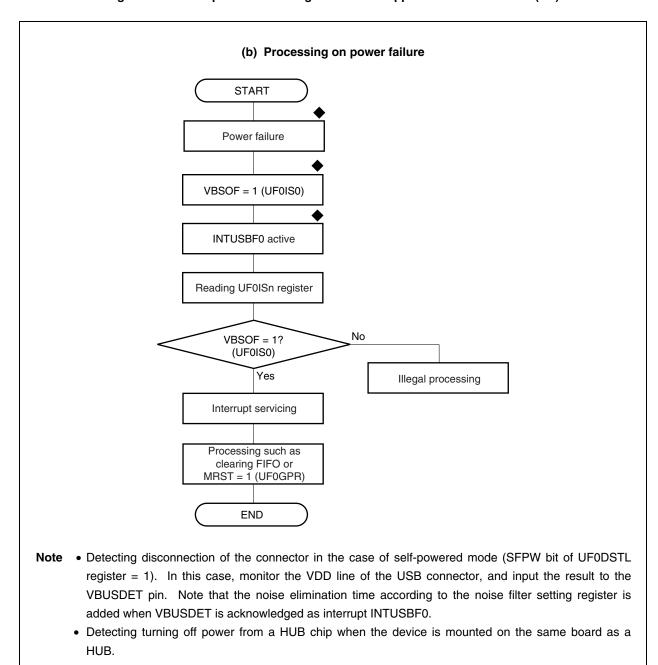

| 3-25   | Example of Processing After Power Application/Power Failure                                | 200  |

| 3-26   | DMA Initialization Processing                                                              | 203  |

| 3-27   | Flow Example of Bulk Transfer Processing in DMA Mode                                       | 204  |

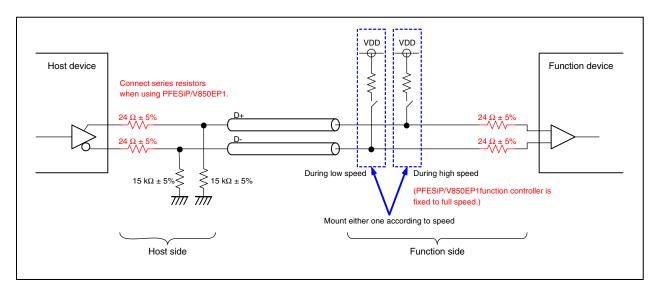

| 4-1    | Configuration Outline of Pull-up, Pull-down, and Series Resistors of USB Transmission Path | 207  |

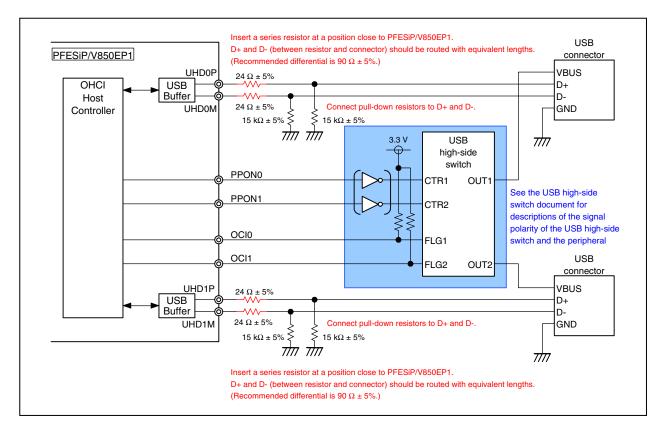

| 4-2    | USB Host Controller Connection Example                                                     | 208  |

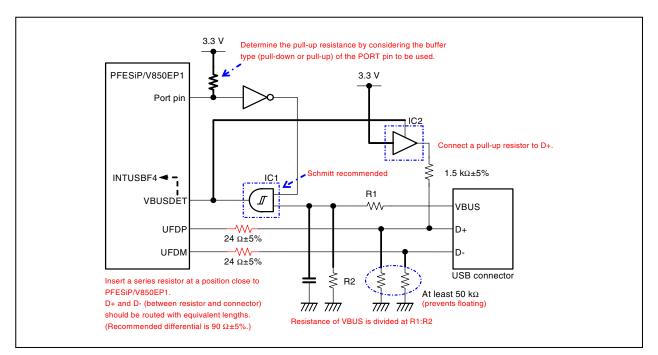

| 4-3    | USB Function Controller Connection Example                                                 | 210  |

#### Table No. Title Page 1-1 1-2 1-3 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9 3-10 3-11 3-12 3-13 3-14 3-15 3-16 3-17 Firmware-Supported Standard Requests ......169 3-18 4-1 4-2 4-3

#### LIST OF TABLES

#### CHAPTER 1 USB FUNCTION OVERVIEW

PFESiP/V850EP1 incorporates a USB function controller and a USB host controller which comply with the Universal Serial Bus Specification.

#### 1.1 Features

- O Complies with the Universal Serial Bus Specification.

- O USB function controller:

Supports 12 Mbps (full-speed) transfer. Equipped with a one-channel upstream port. Incorporates the following transfer endpoints.

| Endpoint | FIFO Size (Bytes) | Transfer Type      | Remark                      |

|----------|-------------------|--------------------|-----------------------------|

| EP0      | 64                | Control Read/Write |                             |

| EP1      | 64 × 2            | Bulk In            | Double buffer configuration |

| EP2      | 64 × 2            | Bulk Out           | Double buffer configuration |

| EP7      | 8                 | Interrupt          |                             |

Can perform DMA transfer (two-clock transfer) of bulk in or bulk out data.

USB host controller: Supports 12 Mbps (full-speed) and 1.5 Mbps (low-speed) transfer.

Supports the OHCI (Open Host Controller Interface) 1.0a standard.

(The control of transitioning the USB port from disable to enable status, however, is restricted.)

Incorporates a two-channel root hub function and is equipped with two downstream ports.

Uses an 8 KB on-chip SRAM and an external SDRAM as shared memories.

- O Memory bus width: CPU interface....32 bits External SDRAM interface of the USB host controller....16 or 32 bits

| MODE1 | MODE0                     | Operation Mode                 |

|-------|---------------------------|--------------------------------|

| 0     | 0                         | USB function invalid           |

| 0     | 1 Only USB function valid |                                |

| 1     | 0                         | Only USB host valid            |

| 1     | 1                         | USB host or USB function valid |

Caution When using the USB function, set the MODE0 and MODE1 pins to the appropriate modes.

When the USB function is disabled, the clock used by the USB function controller or USB host controller is stopped. Do not change these pin settings while PFESiP/V850EP1 is operating.

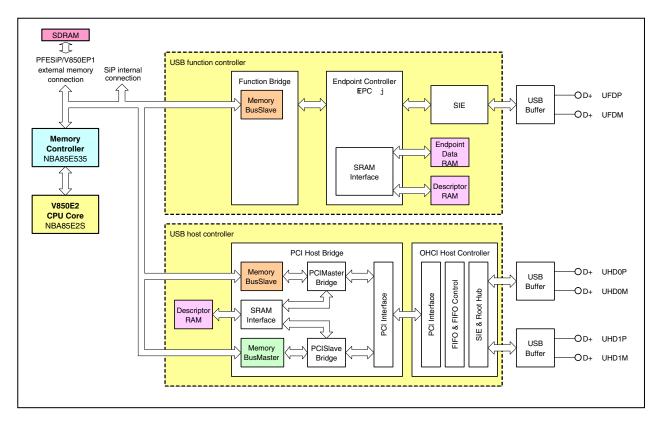

#### 1.2 Configuration

#### 1.3 USB Pin Functions

| Pin          | I/O    | Function                                                                     | Active |  |  |

|--------------|--------|------------------------------------------------------------------------------|--------|--|--|

| UCLK         | Input  | USB clock signal input                                                       |        |  |  |

| UHD0P        | I/O    | USB host channel 0 data I/O (+)                                              | -      |  |  |

| UHD0M        | I/O    | USB host channel 0 data I/O (-)                                              | _      |  |  |

| UHD1P        | I/O    | USB host channel 1 data I/O (+)                                              | _      |  |  |

| UHD1M        | I/O    | USB host channel 1 data I/O (-)                                              | -      |  |  |

| PPON0        | Output | USB host channel 0 power supply control output                               | High   |  |  |

| PPON1        | Output | USB host channel 1 power supply control output                               | High   |  |  |

| OCI0         | Input  | USB host channel 0 overcurrent detection input                               |        |  |  |

| OCI1         | Input  | USB host channel 1 overcurrent detection input                               |        |  |  |

| UFDP         | I/O    | USB function data I/O (+)                                                    |        |  |  |

| UFDM         | I/O    | USB function data I/O (-)                                                    |        |  |  |

| VBUSDET      | Input  | USB function insertion and removal detection input                           |        |  |  |

| PCLKIN       | Input  | USB bus bridge clock                                                         |        |  |  |

| UCLKSEL0     | Input  | USB clock selection input 0: Selects XT1, XT2. 1: Selects UCLK.              |        |  |  |

| UCLKSEL1     | Input  | USB bus bridge clock selection input 0: Selects XT1, XT2. 1: Selects PCLKIN. |        |  |  |

| MODE0, MODE1 | Input  | PFESiP/V850EP1 USB operation mode setting                                    | -      |  |  |

Table 1-1. USB Pins

#### 1.4 USB Memory Map

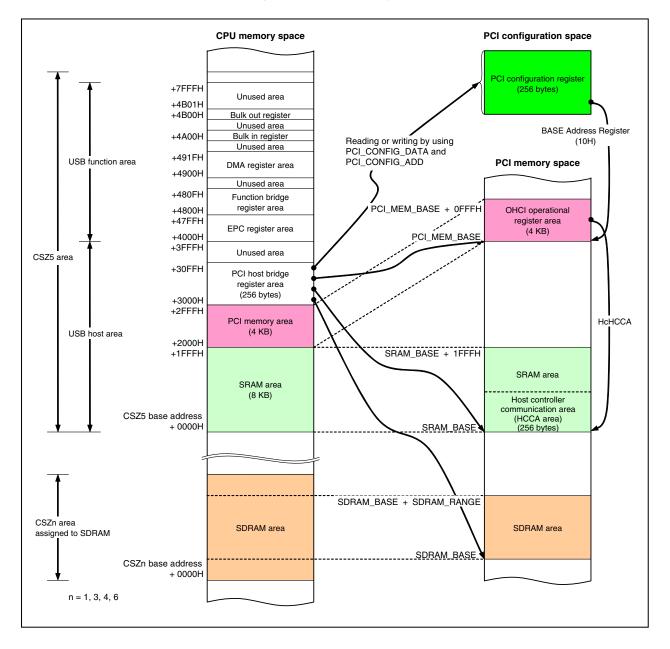

Both the USB host controller and the USB function controller are assigned to the CSZ5 space. Set the CSZ5 address range (subarea) where they are placed via the CSC1 register. Set the CSZ5 area for an SRAM and an I/O via the BCT1 register, and set the bus width as 32 bits via the LBS register.

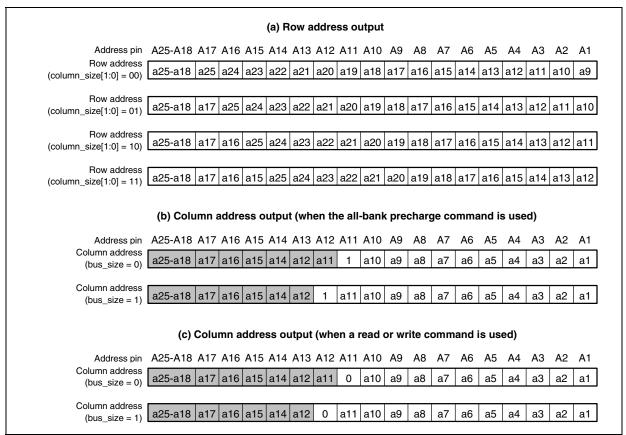

The USB host controller has an external memory bus master function, and can use any SDRAM to which any chip select signal from among CSZ1, CSZ3, CSZ4, and CSZ6 has been assigned for use as the SDRAM interface via the UCSS register. At that time, set the bus width of the SDRAM to be shared to the same bus width (16 or 32 bits) as for SDRAM\_CTL, which is used in the LBS register and USB host controller.

The OHCI host controller, which is the central function of the USB host controller, is connected via the SRAM interface of the CSZ5 space and also via the internal PCI bus bridge. The CPU and the internal PCI bus bridge share the same memory, and the CPU memory space is linked to the PCI memory space. This relationship is defined by the PCI host bridge registers and the PCI configuration register, which is accessed via the PCI host bridge registers.

#### 1.5 USB-related Interrupts

| Maskable Interrupt Source |                      |                                                            |                                                   |          | t Exception | Handler   | Restored | DMA                |

|---------------------------|----------------------|------------------------------------------------------------|---------------------------------------------------|----------|-------------|-----------|----------|--------------------|

| Name                      | Control Register     | Generating Source                                          | Generating Unit                                   | Priority | Code        | Address   | PC       | Transfer<br>Source |

| INTUSBH0                  | UHIC0<br>(1FFFF182H) | USBH interrupt 0<br>(INTA, SMMI, PME)                      | USB host controller<br>(OHCI HC)                  | 57       | 0410H       | 00000410H | Next PC  | 0                  |

| INTUSBH1                  | UHIC1<br>(1FFFF184H) | USBH interrupt 1<br>(PME)                                  | USB host controller<br>(OHCI HC)                  | 58       | 0420H       | 00000420H | Next PC  | 0                  |

| INTUSBF0                  | UFIC0<br>(1FFFF186H) | USBF interrupt 0<br>(endpoint event)                       | USB function controller<br>(EPC, function bridge) | 59       | 0430H       | 00000430H | Next PC  | 0                  |

| INTUSBF1                  | UFIC1<br>(1FFFF188H) | USBF interrupt 1<br>(endpoint1 DMA<br>transfer completion) | USB function controller<br>(function bridge)      | 60       | 0440H       | 00000440H | Next PC  | 0                  |

| INTUSBF2                  | UFIC2<br>(1FFFF18AH) | USBF interrupt 2<br>(endpoint2 DMA<br>transfer completion) | USB function controller<br>(function bridge)      | 61       | 0450H       | 00000450H | Next PC  | 0                  |

| INTUSBF3                  | UFIC3<br>(1FFFF18CH) | USBF interrupt 3<br>(Resume)                               | USB function controller<br>(SIE)                  | 62       | 0460H       | 00000460H | Next PC  | 0                  |

| INTUSBF4                  | UFIC4<br>(1FFFF18EH) | USBF interrupt 4<br>(VBUS detection)                       | USB function controller external pin              | 63       | 0470H       | 00000470H | Next PC  | 0                  |

Table 1-2. USB-related Interrupt Sources

#### 1.6 USB-related I/O Register Settings

To use the USB function, set the peripheral I/O registers as follows.

| Abbreviation | Address    | Setting Value                                                                                          | Remark                                                                                                                                                                                                               |

|--------------|------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSC1         | 1FFF F062H | Assign CSZ5 to any subarea (70, 71, 72, or 73).                                                        | When using CSREMAP, map CSZ5 under the default settings. The chip select signal that is used by the USB function is fixed to CSZ5, so it cannot be changed to another CSZn.                                          |

| BCT1         | 1FFF F482H | xx8xH                                                                                                  | Select an SRAM or I/O for CSZ5.                                                                                                                                                                                      |

| LBS          | 1FFF F48EH | xxxx11xx xxxxxxB                                                                                       | The width of CSZ5 is 32 bits.                                                                                                                                                                                        |

| DWC1         | 1FFF F486H | Any value                                                                                              | Set the CSZ5 data wait to any value (0 to 7).                                                                                                                                                                        |

| BCC          | 1FFF F488H | Any value                                                                                              | Set the CSZ5 idle state to any value (0 to 3).                                                                                                                                                                       |

| ASC          | 1FFF F48AH | Any value                                                                                              | Set the CSZ5 address setting wait to any value (0 to 3).                                                                                                                                                             |

| UCSS         | 1FFF F8B6H | Assign the SDRAM to any chip select<br>signal from among CSZ1, CSZ3,<br>CSZ4, and CSZ6.                | This is used by the USB host controller.<br>Set it to the same CSZ signal as of the SDRAM that is<br>shared with the CPU. When using CSREMAP, it is<br>the remapped chip select signal that is assigned via<br>UCSS. |

| UDMS         | 1FFF F8B8H | Assign two of the four channels used<br>for DMA interface signals as DMA<br>interface signals for USB. | This is used by the USB function controller.<br>Channel 0 corresponds to EP1 (Bulk in) and channel 1<br>corresponds to EP2 (Bulk out).                                                                               |

| Table 1-3. Peri | ipheral I/O Register S   | Settings When Usin | a USB Function |

|-----------------|--------------------------|--------------------|----------------|

|                 | ipiloidi i o ilogiotoi t |                    | 9              |

When using CSREMAP, the USB function uses the address space that has been assigned to the remapped MEM\_CSZn (logically equivalent to CSZn).

#### CHAPTER 2 USB HOST CONTROLLER

#### 2.1 Overview

The USB host controller uses a token based protocol to transfer data to and from external function devices via the polling method.

It complies with the OHCI (Open Host Controller Interface) 1.0a standard, and is equipped with a two-channel root hub function and two downstream ports. For data transfers with external function devices, all transfer types (control, bulk, isochronous, interrupt) can be used (however, for transfers such as isochronous transfers that involve a heavy system load, a performance evaluation is needed beforehand).

#### 2.2 PCI Host Bridge

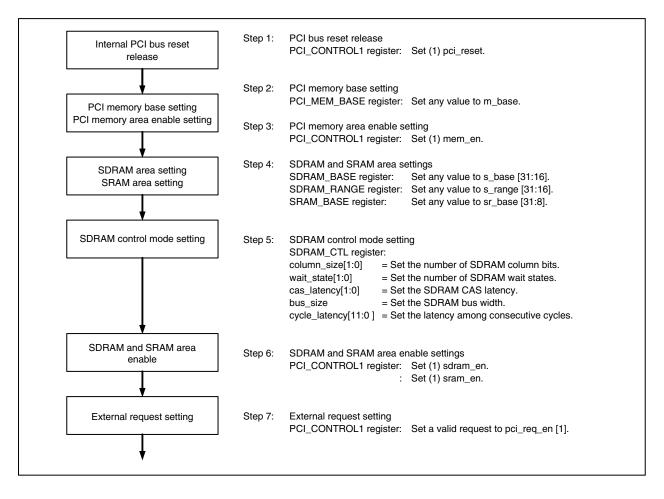

#### 2.2.1 PCI host bridge function

The PCI host bridge is a bridge circuit that is connected from the CPU system to the OHCI host controller, via the PCI bus, and it includes the following functions.

#### O PCI master cycle control

The following are issued in response to a PCI bus access request from the CPU (MEMC):

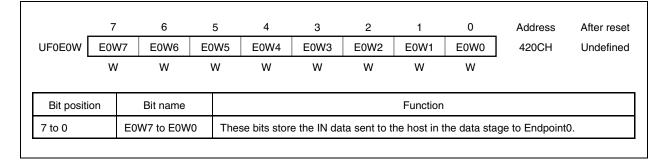

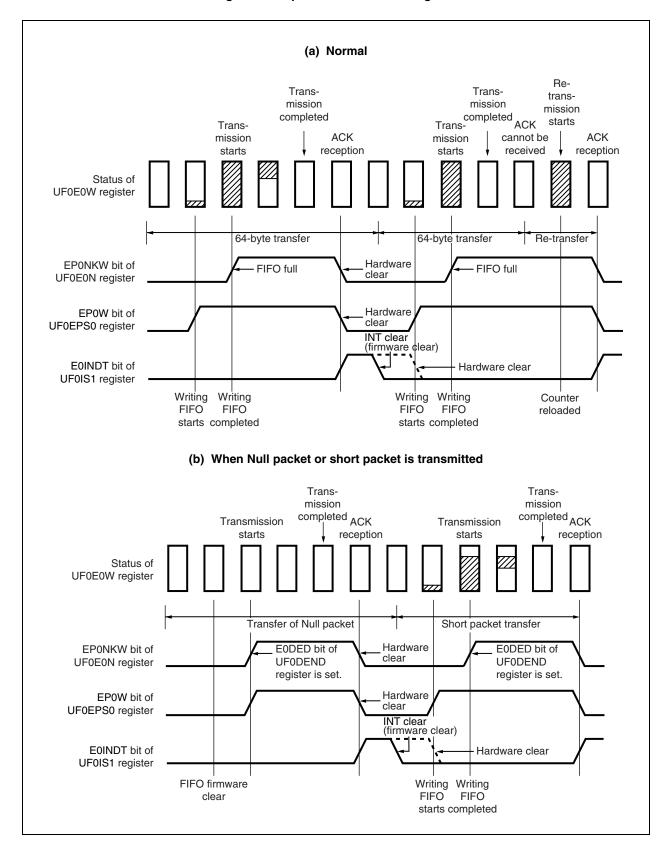

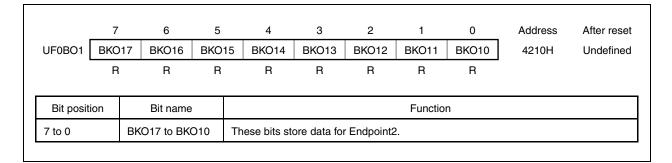

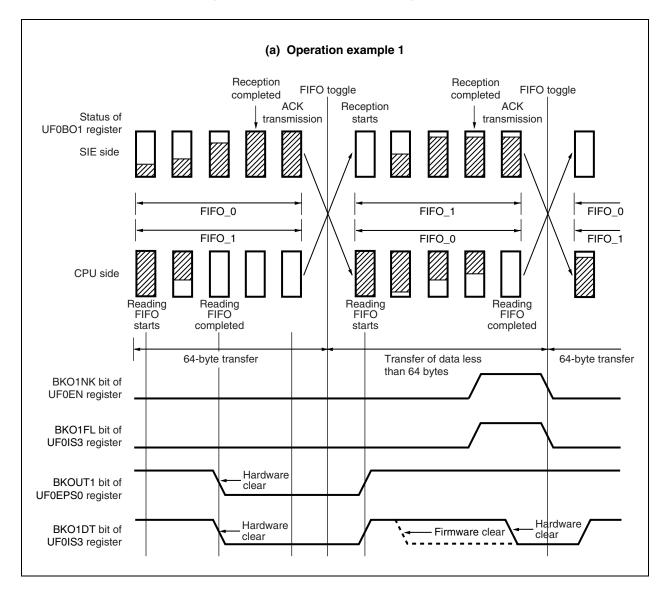

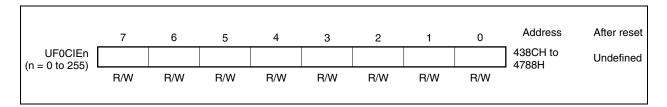

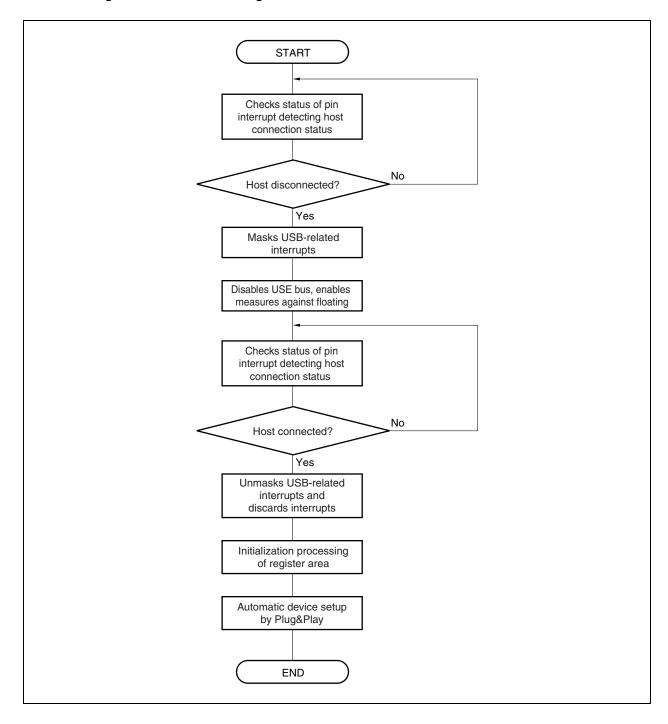

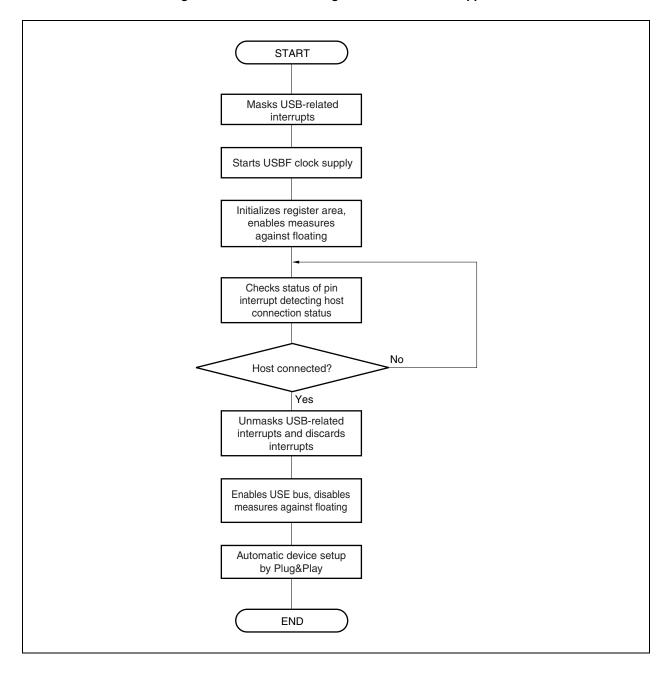

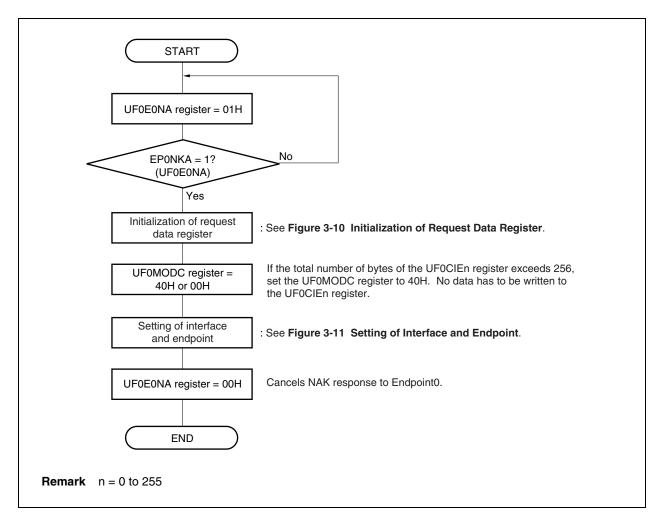

PCI Configuration Register Read/Write Single Cycle