# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# MOS 集積回路 MOS Integrated Circuit **PD9971**

# 3D ポジショニング・サラウンド機能内蔵携帯電話着信メロディ音源 LSI

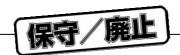

μPD9971 は,3D ポジショニング・サラウンド機能を内蔵した携帯電話の着信メロディ用音源 LSI です。

#### 特徵

最大 128 音同時発音可能な PCM 音源コアを搭載し,リアルな音色を再現します。

128GM 音色 + 47 ドラム・セット + 効果音 32 音色, 32 kHz サンプリング Wavetable 搭載。

1音色あたり2 Wave を使用し,より豊かな音色を実現可能。

GM 音色以外の音色ダウンロードおよびパラメータのダウンロードが可能で,固定音色に限定されない音づくりが可能。

4ポートの MIDI®ポートを搭載しているため,同時に4曲を再生することが可能。

カラオケ, JAVA®アプリケーションを想定した MIDI のリアルタイム制御用ポートを搭載。

スピーカのイコライジング用として、ディジタル・パラメトリック・イコライザを内蔵。

低音量の出力に対しても常に最大音量レベルでの再生を可能にする AGC (Auto Gain Control)機能を内蔵。

各種音響エフェクト(ピッチベンド,ビブラート,ディレイ,リバーブ,コーラス,ドップラ,コンプレッサ) を実現可能。

MOBILE-XMF に対応

リアルタイム処理の 3D ポジショニング・サラウンド用音響コアを内蔵しています。

ディジタル信号処理により、音源が立体的に移動しているような音響効果を得ることが可能。

ディジタル信号処理により、広がりのある立体音響効果を得ることが可能。

プログラマブルな立体音響パラメータを搭載し、携帯電話の筐体、スピーカ配置などに最適な設定が可能。

ヘッドフォン使用時も立体音響効果を得ることが可能。

オーディオ用高性能ステレオ 16 ビット DA コンバータを内蔵しています。

オーディオ DAC サンプリング周波数 (fs) は 8 kHz/16 kHz/32 kHz/44.1 kHz/ 48kHz の 5 種類に対応。

オーディオ・シリアル入出力インタフェース (16 ビット) を装備しています。

シリアル・データの入力周波数は 32fs~64fs まで可変可能(スレーブ・モード時)。

フォーマットは右詰め, 左詰め, IIS に対応。

オーディオ用ステレオ・ライン出力を装備しています。

3D-Audio 等を想定した,外部接続用シリアル入出力インタフェースを装備しています。

CPU インタフェースとして 8 ビット・パラレル・インタフェースとシリアル・インタフェースを装備しています。

バイブレーション, LED の制御出力機能を内蔵しています。

内部マスタ・クロック生成用 PLL を内蔵しているため, さまざまな入力クロックに対応可能です。

本資料の内容は、予告なく変更することがありますので、最新のものであることをご確認の上ご使用ください。

ディジタル電源(DVDD)用レギュレータを内蔵しています。

#### 電源電圧

I/O 電源(EVDD)

: 1.7~3.3 V

PLL 用電源(PLLVDD)

: 2.7~3.3 V

アナログ電源(AVDD)

: 2.7~3.3 V

レギュレータ電源(REGVDD)

: 2.7~3.3 V

ディジタル電源(DVDD):内蔵レギュレータから供給(外部電圧印可も可能)

動作周囲温度: - 20~ + 85°C

85 ピン・テープ FBGA パッケージ (6 mm × 6 mm, 0.5 mm ボール・ピッチ)

#### オーダ情報

オーダ名称 パッケージ μ PD9971F9-BA3-A 85 ピン・テープ FBGA (6 × 6 mm)

備考 鉛フリー製品です。

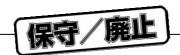

#### ブロック図

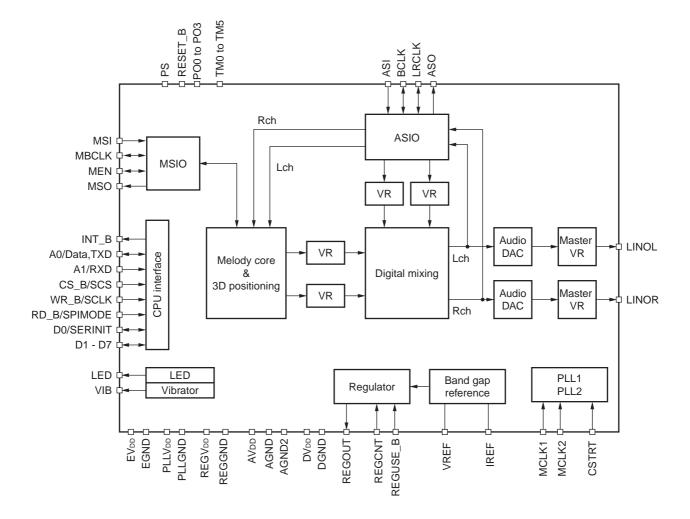

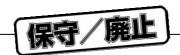

## 端子接続図

・85 ピン・テープ FPBGA (6 × 6 mm)

$\mu$  PD9971F9-BA3-A

| 端子 | 端子名                | 端子 | 端子名                | 端子 | 端子名              | 端子  | 端子名              |

|----|--------------------|----|--------------------|----|------------------|-----|------------------|

| 番号 |                    | 番号 |                    | 番号 |                  | 番号  |                  |

| 1A | 1K とショート           | 3C | MSO                | 6B | PS               | 9B  | N.C              |

| 1B | N.C                | 3D | N.C                | 6C | TM5              | 9C  | EV <sub>DD</sub> |

| 1C | LINOL              | 3E | N.C                | 6H | PO1              | 9D  | VIB              |

| 1D | AGND               | 3F | MCLK2              | 6J | CS_B/SCS         | 9E  | RESET_B          |

| 1E | AV <sub>DD</sub>   | 3G | REGGND             | 6K | A0/Data, TXD     | 9F  | D7               |

| 1F | LINOR              | 3H | REGV <sub>DD</sub> | 7A | ASI              | 9G  | D5               |

| 1G | AGND2              | 3J | REGOUT             | 7B | ASO              | 9H  | D3               |

| 1H | PLLGND             | 3K | REGCNT             | 7C | DV <sub>DD</sub> | 9J  | N.C              |

| 1J | REGV <sub>DD</sub> | 4A | MSI                | 7H | DV <sub>DD</sub> | 9K  | N.C              |

| 1K | 1A とショート           | 4B | TM4                | 7J | RD_B/SPIMODE     | 10A | 10K とショート        |

| 2A | N.C                | 4C | DV <sub>DD</sub>   | 7K | WR_B/SCLK        | 10B | N.C              |

| 2B | N.C                | 4D | N.C (index)        | 8A | LRCLK            | 10C | LED              |

| 2C | TM0                | 4H | REGUSE_B           | 8B | BCLK             | 10D | DV <sub>DD</sub> |

| 2D | IREF               | 4J | PO3                | 8C | CSTRT            | 10E | INT_B            |

| 2E | VREF               | 4K | PO2                | 8D | N.C              | 10F | D6               |

| 2F | TM1                | 5A | MEN                | 8E | N.C              | 10G | D4               |

| 2G | PLLV <sub>DD</sub> | 5B | MBCLK              | 8F | DV <sub>DD</sub> | 10H | D2               |

| 2H | MCLK1              | 5C | DGND               | 8G | EGND             | 10J | N.C              |

| 2J | N.C                | 5H | P00                | 8H | EV <sub>DD</sub> | 10K | 10A とショート        |

| 2K | REGOUT             | 5J | A1/RXD             | 8J | D1               |     |                  |

| 3A | TM3                | 5K | DGND               | 8K | D0/SERINIT       |     |                  |

| 3B | TM2                | 6A | EGND               | 9A | N.C              |     |                  |

#### 端子名称

| A0, A1: | Address                 | MSO:  | Data Output for Melody Core |

|---------|-------------------------|-------|-----------------------------|

| AGND:   | Ground for Analog Block | N.C.: | No Connection               |

N.C. ( index ) : No Connection AGND2: Ground for Analog Block ASI: Audio Serial Data Input PLLGND: Ground for PLL

ASO: Audio Serial Data Output PLLV<sub>DD</sub>: Power Supply for PLL AV<sub>DD</sub>: Power Supply for Analog Block PO0-PO3: Peripheral Output

BCLK: Bit Clock Input/Output PS: Parallel/Serial Interface Select

CS B: Chip Select Read RD B:

CSTRT: Clock Select Signal Input from External REGCNT: Regulator Control

Data Bus D0-D7: REGGND: Ground for Regulator Data: Data REGOUT: Regulator Output

DGND: Ground for Digital Block **REGUSE B:** Regulator Block Enable Signal Input

DV<sub>DD</sub>: Power Supply for Digital Block Power Supply for Regulator REGV<sub>DD</sub>:

EGND: Ground for I/O Pins RESET B: Reset

EV<sub>DD</sub>: Power Supply for I/O Pins RXD: Serial Data Input Clock for Serial I/F

INT\_B: Interruption SCLK: IREF: Current Reference for Analog Block SCS: Chip Select Input for Serial I/F

LED: **LED Control Output** SERINIT: Initialization Signal for Serial I/F

Line Out (Lch) LINOL: SPIMODE: SPI Mode Select Line Out (Rch) LINOR: TM0-TM2: Test Mode Input

LRCLK: Left Right Clock Input/Output TM3, TM4: Test Mode I/O MBCLK: Bit Clock for Melody Core TM5: Test Mode Input

MCLK1: Clock Input VIB: Vibration Control Output

MCLK2: Clock Input VREF: Voltage Reference for Analog Block

MEN: Frame Clock for Melody Core WR B: Write

Data Input for Melody Core

**備考** N.C.は将来製品との互換性のために備えています。オープンで使用してください。

MSI:

# 目 次

| 1. | 機           | 能 10                                      |

|----|-------------|-------------------------------------------|

|    | 1. 1        | 機能概要説明 10                                 |

|    | 1. 2        | 回路概略説明 10                                 |

|    |             |                                           |

| 2. | 端           | 子 11                                      |

|    | 2. 1        | 端子構成 11                                   |

|    | 2. 2        | 推奨外付け回路 12                                |

|    | 2. 3        | 端子機能説明 13                                 |

|    | 2. 4        | 未使用端子の処理 18                               |

|    | 2. 5        | 端子状態 19                                   |

|    |             |                                           |

| 3. |             | インタフェース 22                                |

|    | 3. 1        | パラレル・ホスト CPU インタフェース 22                   |

|    |             | 3. 1. 1 ライト・アクセス 22                       |

|    |             | 3.1.2 リード・アクセス 23                         |

|    | 3. 2        | シリアル・ホスト・インタフェース 24                       |

|    |             | 3. 2. 1 端子機能 24                           |

|    |             | 3.2.2 シリアル・フォーマット 25                      |

|    |             | 3. 2. 3 アクセス・フォーマット (3線 SPI モード) 26       |

|    |             | 3. 2. 4 アクセス・フォーマット(4 線 SPI モード) 28       |

|    |             | 3.2.5 シリアル・インタフェースの初期化について 30             |

|    |             | N. 17   1   1   1   1   1   1   1   1   1 |

| 4. |             | シリアル・インタフェース 31                           |

|    |             | オーディオ・シリアル・インタフェース(ASIO) 31               |

|    | 4. 2        | 音源コア外部接続専用シリアル・インタフェース(MSIO) 33           |

| 5  | <b>プ</b> ロ、 | ック機能 34                                   |

| ٥. |             | - 基準電圧/電流源部 35                            |

|    |             | レギュレータ部 36                                |

|    |             | PLL 部 37                                  |

|    |             | ・ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・         |

|    |             | オーディオ・シリアル・インタフェース部(ASIO) 39              |

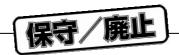

|    |             | オーディオ再生ディジタル・ゲイン調整プロック 41                 |

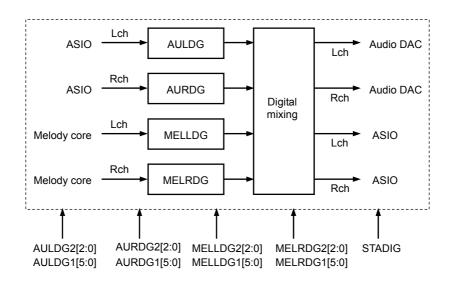

|    |             | オーディオ再生アナログ・プロック 42                       |

|    |             | ディジタル・ミキシング部 43                           |

|    |             | 音源コア外部接続専用シリアル・インタフェース (MSIO) 45          |

|    |             | 5. 9. 1 MSIO 使用時の注意事項 46                  |

|    |             |                                           |

| 6. | レジ          | スタ(音源以外のレジスタ) 47                          |

|    | 6. 1        | スタンパイ設定 (STNBY) 48                        |

6. 1. 1 STADIG ... 48

|       | 6. 1. 2  | STPLL2 48                                     |

|-------|----------|-----------------------------------------------|

|       | 6. 1. 3  | STPLL1 48                                     |

|       | 6. 1. 4  | STASI 48                                      |

|       | 6. 1. 5  | STASO 48                                      |

|       | 6. 1. 6  | STSYNTH 49                                    |

|       | 6. 1. 7  | STADAC 49                                     |

|       | 6. 1. 8  | STREF 49                                      |

| 6. 2  | マスタ      | ・クロックの切り替え(MCLK1A, MCLK1B, MCLK2A, MCLK2B) 49 |

|       | 6. 2. 1  | MCLK1A[6:0] 50                                |

|       | 6. 2. 2  | MCLK1B[7:0] 50                                |

|       | 6. 2. 3  | MCLK2A[4:0] 50                                |

|       | 6. 2. 4  | MCLK2B[7:0] 50                                |

| 6. 3  | 入力ク      | ロック選択(MCLKSEL) 50                             |

|       | 6. 3. 1  | MCLKSEL 50                                    |

|       | 6. 3. 2  | CSTRTEN 50                                    |

| 6. 4  | オーデ      | ィオ・シリアル・インタフェース FS 切り替え,BCLK 切り替え(SEL_FS) 52  |

|       | 6. 4. 1  | FS[2:0] 52                                    |

|       | 6. 4. 2  | BFS[4:0] 52                                   |

| 6. 5  | ASIO =   | Eード設定(SEL_ASI) 53                             |

|       | 6. 5. 1  | EX3DAEN 53                                    |

|       | 6. 5. 2  | AULOOPSW 53                                   |

|       | 6. 5. 3  | SLR 53                                        |

|       | 6. 5. 4  | AMS 53                                        |

|       | 6. 5. 5  | ASIM 53                                       |

|       | 6. 5. 6  | LRCLK 53                                      |

| 6. 6  | ディジ      | タル・ミキシング・パス(ASI 入力データ)選択(MIXING1) … 54        |

|       | 6. 6. 1  | DACLMIX[1:0] 54                               |

|       | 6. 6. 2  | DACRMIX[1:0] 54                               |

|       | 6. 6. 3  | DACLSW[1:0] 54                                |

|       | 6. 6. 4  | DACRSW[1:0] 54                                |

| 6. 7  | ディジ      | タル・ミキシング・パス(音源出力データ)選択(MIXING2) 55            |

|       | 6. 7. 1  | MELLMIX[1:0] 55                               |

|       | 6. 7. 2  | MELRMIX[1:0] 55                               |

|       | 6. 7. 3  | MELLSW[1:0] 55                                |

|       | 6. 7. 4  | MELRSW[1:0] 55                                |

| 6. 8  | ディジ      | タル・ミキシング・パス(ASI - 音源)選択(MIXING3) 56           |

|       | 6. 8. 1  | PCMLSW 56                                     |

|       | 6. 8. 2  | PCMRSW 56                                     |

| 6. 9  | VIB, LI  | ED 設定(LEDVIB) 56                              |

|       | 6. 9. 1  | VIB 56                                        |

|       | 6. 9. 2  | LED 56                                        |

| 6. 10 | 汎用出      | 出力端子の設定(POUT) 57                              |

|       | 6. 10. 1 | POUT0-POUT3 57                                |

|    | 6. 11 オーティオ・ソフト・ミュート制御(SMUTE) 57                        |

|----|---------------------------------------------------------|

|    | 6. 11. 1 SLOPE[1:0] 57                                  |

|    | 6. 11. 2 AUSMUTE 57                                     |

|    | 6. 11. 3 MELSMUTE 57                                    |

|    | 6. 12 オーディオ DAC 用ディジタル・ボリューム(音源出力 L ch)設定(MELLDG) 58    |

|    | 6. 12. 1 MELLDG2[1:0] 58                                |

|    | 6. 12. 2 MELLDG1[5:0] 58                                |

|    | 6. 13 オーディオ DAC 用ディジタル・ポリューム(音源出力 R ch)設定(MELRDG) 59    |

|    | 6. 13. 1 MELRDG2[1:0] 59                                |

|    | 6. 13. 2 MELRDG1[5:0] 59                                |

|    | 6. 14 オーディオ DAC 用ディジタル・ボリューム(ASI 入力 L ch)設定(AULDG) … 59 |

|    | 6. 14. 1 AULDG2[1:0] 59                                 |

|    | 6. 14. 2 AULDG1[5:0] 59                                 |

|    | 6. 15 オーディオ DAC 用ディジタル・ボリューム(ASI 入力 R ch)設定(AURDG) … 60 |

|    | 6. 15. 1 AURDG2[1:0] 60                                 |

|    | 6. 15. 2 AURDG1[5:0] 60                                 |

|    | 6. 16 オーディオ DAC 用アナログ・マスタ・ポリューム(L ch)設定(ADACLVR) 62     |

|    | 6. 16. 1 ADACLVRGA[4:0] 62                              |

|    | 6. 17 オーディオ DAC 用アナログ・マスタ・ボリューム(R ch)設定(ADACRVR) 62     |

|    | 6. 17. 1 ADACRVRGA[4:0] 62                              |

|    | 6. 18 LSI スタンパイ(MSIO)の設定(STNBY2) 63                     |

|    | 6. 18. 1 STMSO 63                                       |

|    | 6. 18. 2 STMSI 63                                       |

|    | 6. 19 MSIO モード設定(SEL_MSIO1) 64                          |

|    | 6. 19. 1 SMBCLK 64                                      |

|    | 6. 19. 2 SMEN 64                                        |

|    | 6. 19. 3 MMS 64                                         |

|    | 6. 19. 4 MLOOPSW 64                                     |

|    | 6. 19. 5 MBFS[2:0] 65                                   |

|    | 6. 20 オーディオ・シリアル・インタフェース FS 切り替え,BCLK 切り替え(SEL_FS) 66   |

|    | 6. 20. 1 MCHI[3:0] 66                                   |

|    | 6. 20. 2 MCHO[3:0] 66                                   |

|    | 6. 21 LSI パージョン設定(LSIVER) 67                            |

|    | 6. 21. 1 VER[3:0] 67                                    |

|    | 6. 22 シリアル・インタフェース・モード時パンク設定(BANK) 67                   |

|    | 6. 22. 1 BANK[1:0] 67                                   |

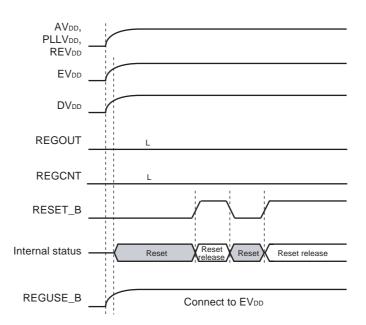

| 7. | 電源立ち上げ手順 68                                             |

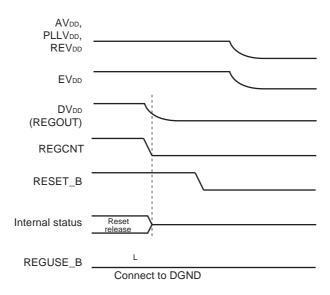

|    | 7.1 電源立ち上げ順序 68                                         |

|    | 7. 1. 1 レギュレータ未使用時 68                                   |

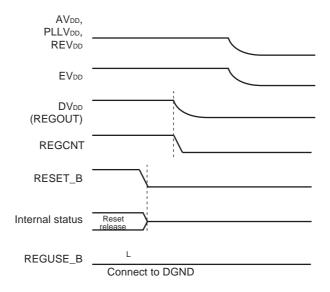

|    | 7. 1. 2 レギュレータ使用時 69                                    |

7.2 電源立ち下げ順序 ... 70

7. 2. 1 レギュレータ未使用時 ... 70

- 7.2.2 レギュレータ使用時 ... 71

- 7.3 パワー・セービング機能 ... 72

- 7.3.1 ハードウエア・パワー・セービング ... 72

- 7.3.2 ソフトウエア・パワー・セービング ... 72

- 8. 設定シーケンス ... 73

- 8.1 パワーアップ・シーケンス ... 73

- 8.2 各種動作モード切り替えの基本シーケンス ... 74

- 8.2.1 ミュート設定 ... 75

- 8.2.2 スタンバイ設定/解除 ... 75

- 8.2.3 FS 切り替え ... 75

- 8.2.4 パス切り替え ... 76

- 8.2.5 3DA/サラウンド切り替え ... 76

- 8.2.6 ASIO モード設定 ... 77

- 8.3 設定シーケンス例 ... 78

- 8.3.1 音源 DAC ライン出力 (クロック: MCLK2 = 12 MHz) ... 79

- 8.3.2 音源 ASO 出力(クロック: MCLK2 = 12 MHz, マスタ・モード時) ... 80

- 8.3.3 音源 ASO 出力(クロック: MCLK2 = 12 MHz, スレーブ・モード時) ... 81

- 8.3.4 ASI DAC ライン出力(クロック: MCLK2 = 12 MHz) ... 82

- 8.3.5 ASI ASO 出力 (クロック: MCLK2 = 12 MHz) ... 83

- 8. 3. 6 ASI サラウンド DAC ライン出力(クロック: MCLK2 = 12 MHz, fs = 32 kHz) ... 84

- 8.3.7 ASI サラウンド DAC ライン出力 ( クロック: MCLK2 = 12 MHz , fs = 44.1 kHz ) ... 85

- 8. 3. 8 ASI サラウンド ASO 出力 ( クロック: MCLK2 = 12 MHz , fs = 32 kHz ) ... 86

- 8. 3. 9 ASI サラウンド ASO 出力(クロック:MCLK2 = 12 MHz, fs = 44.1 kHz) ... 87

- 9. 電気的特性 ... 88

- 9.1 絶対最大定格 ... 88

- 9.2 推奨動作条件 ... 88

- 9.3 容 量 ... 88

- 9.4 DC 特性 ... 89

- 9.5 AC 特性 ... 90

- 9.5.1 クロック ... 90

- 9.5.2 リセット ... 90

- 9.5.3 パラレル CPU I/F モード ... 91

- 9. 5. 4 シリアル CPU インタフェース・モード (3 線 SPI モード, 4 線 SPI モード共通 ) ... 93

- 9.5.5 オーディオ・シリアル・インタフェース(ASIO) ... 96

- 9.5.6 音源コア外部接続専用シリアル・インタフェース (MSIO) ... 98

- 9.6 アナログ特性 ... 100

- 9.6.1 アナログ・ブロック特性(参考値) ... 101

- 10. 消費電流特性 ... 102

- 11. 外形図 ... 103

- 12. 半田付け推奨条件 ... 104

#### 1. 機 能

#### 1.1 機能概要説明

#### (1) 電源電圧

ディジタル IO 電源 : 1.7 V~3.3 V (1.8 V TYP)

アナログ電源 : 2.7 V~3.3 V (3.0 V TYP)

PLL 電源 : 2.7 V~3.3 V (3.0 V TYP)

レギュレータ電源 : 2.7 V~3.3 V (3.0 V TYP)

(ディジタル電源 : 1.45 V~1.65 V (1.54 V TYP))

#### (2)動作温度範囲

- 20 ~ +85°C

#### (3)機能プロック

Melody Core : 128 和音 PCM 音源コア

3D Positioning : 3D ポジショニング・サラウンド機能

Digital Mixing : ディジタル・ミキシング回路

Regulator : ディジタル電源供給用レギュレータ

PLL1/PLL2 : 音源用 PLL , オーディオ用 PLL

Audio DAC: ステレオ 16 ビット・オーディオ DACBand gap: アナログ回路用基準電圧 / 電流発生回路

VIB/LED : バイブレーション LED の制御信号発生回路

Master VR/Digital VR : ボリューム回路

#### 1.2 回路概略説明

| ブロック                 | 機能                                                                |

|----------------------|-------------------------------------------------------------------|

| Melody Core          | 最大 128 音の同時発音可能                                                   |

|                      | PCM 音源,シーケンサ内蔵,サンプリング周波数 32 kHz                                   |

| 3D Positioning       | 3D ポジショニング・サラウンド機能                                                |

| Digital Mixing       | 音源出力,オーディオ・シリアル入力の切り替えまたは加算                                       |

| PLL                  | 内部信号処理用マスタ・クロック生成                                                 |

|                      | 入力クロック:3.84~15.36 MHz                                             |

|                      | 逓倍数はレジスタにより設定可能                                                   |

| Audio DAC            | 16 ビット×2 ch ( L ch, R ch )                                        |

|                      | サンプリング周波数:48 kHz, 44.1 kHz, 32 kHz, 16 kHz, 8 kHz(ディフォールト 32 kHz) |

|                      | インタフェース:マスタ/スレーブ対応                                                |

|                      | ダイナミック・レンジ:90 dBr TYP.(プロック単体)                                    |

| Regulator            | ディジタル電源供給用 1.54 V 出力レギュレータ                                        |

| VIB/LED              | VIB/LED 制御信号出力                                                    |

| Master VR/Digital VR | マスタ・ボリューム:0~ - 45 dB / 1.5 dB step                                |

|                      | ディジタル・ボリューム: + 12~ - 63 dB / 1 dB step                            |

#### 2. 端 子

#### 2.1 端子構成

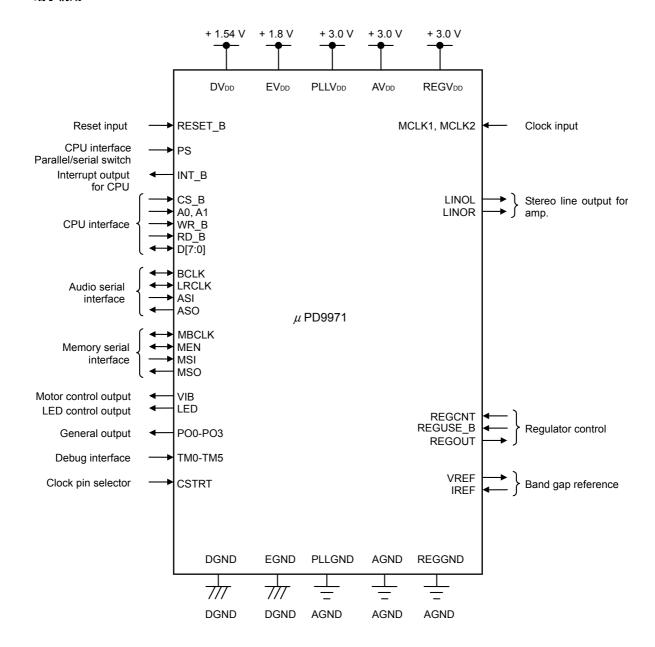

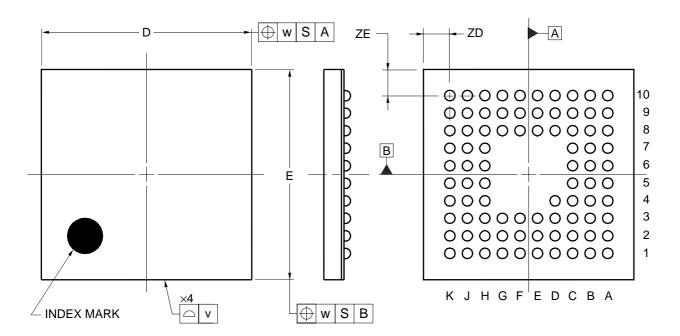

## 2.2 推奨外付け回路

# 2.3 端子機能説明

# (1) 電源 , GND

| 端子名称               | 端子番号        | 入出力 | 機能                                        |

|--------------------|-------------|-----|-------------------------------------------|

| DV <sub>DD</sub>   | 4C, 7C, 7H, | -   | ディジタル・ブロック用電源                             |

|                    | 8F, 10D     |     | 内蔵レギュレータを使用する場合は本端子と REGOUT 端子を LSI 外部で接続 |

|                    |             |     | してください。                                   |

|                    |             |     | 0.1 μF のコンデンサを本端子と DGND の間に接続してください。      |

| DGND               | 5C, 5K      | -   | ディジタル・ブロック用グランド                           |

| EV <sub>DD</sub>   | 8H, 9C      | -   | ディジタル I/O 用電源                             |

|                    |             |     | 0.1 μF のコンデンサを本端子と EGND の間に接続してください。      |

| EGND               | 6A, 8G      | -   | ディジタル I/O 用グランド                           |

| PLLV <sub>DD</sub> | 2G          | -   | PLL 用電源                                   |

|                    |             |     | 0.1 μF のコンデンサを本端子と PLLGND の間に接続してください。    |

| PLLGND             | 1H          | -   | PLL 用グランド                                 |

| AV <sub>DD</sub>   | 1E          | -   | アナログ・ブロック用電源                              |

|                    |             |     | 0.1μF のコンデンサを本端子と AGND の間に接続してください。       |

| AGND               | 1D          | -   | アナログ・ブロック用グランド                            |

| AGND2              | 1G          | -   | アナログ・ブロック用グランド                            |

| REGV <sub>DD</sub> | 1J, 3H      | -   | レギュレータ・バンド・ギャップ・リファレンス用電源                 |

|                    |             |     | 0.1 μF のコンデンサを本端子と REGGND の間に接続してください。    |

| REGGND             | 3G          | -   | レギュレータ用グランド                               |

# (2) クロック,システム・コントロール

| 端子名称    | 端子番号 | 入出力 | 機能                                          |

|---------|------|-----|---------------------------------------------|

| MCLK1   | 2H   | 入力  | クロック入力(3.84~15.36 MHz)                      |

|         |      |     | 内部マスタ・クロック生成用基準クロック入力です。                    |

|         |      |     | 容量結合(1000 pF)での入力を推奨します。                    |

|         |      |     | 使用しない場合は GND に接地してください。                     |

| MCLK2   | 3F   | 入力  | クロック入力 (3.84~15.36 MHz)                     |

|         |      |     | 内部マスタ・クロック生成用基準クロック入力です。                    |

|         |      |     | 入力レベル EVDD の矩形波入力用です。                       |

|         |      |     | 使用しない場合は GND に接地してください。                     |

| CSTRT   | 8C   | 入力  | クロック入力外部切り替え信号入力                            |

|         |      |     | 注意 レジスタ CSTRTEN = ハイ・レベルのとき ,本端子は有効となりますが , |

|         |      |     | CSTRT 端子での切り替えを使用する場合は入力可能な周波数が限定さ          |

|         |      |     | れてしまいます。本端子使用時は別途お問い合わせください。                |

|         |      |     | 0: MCLK2 入力選択                               |

|         |      |     | 1: MCLK1 入力選択                               |

|         |      |     | 本端子は LSI 内部でプルダウンされています。                    |

| RESET_B | 9E   | 入力  | ハードウエア・リセット信号入力                             |

|         |      |     | 本 LSI をリセットします。リセット後レジスタは初期値となります。          |

|         |      |     | 0: リセット                                     |

|         |      |     | 1: リセット解除                                   |

# (3) ホスト CPU インタフェース

(1/2)

| 端子名称         | 端子番号 | 入出力 | 機能                                     |

|--------------|------|-----|----------------------------------------|

| A0/DaTa, TXD | 6K   | 入出力 | パラレル・モード時 ( PS = 0 )                   |

|              |      |     | ホスト・インタフェース・アドレス A0 信号入力               |

|              |      |     | ホスト CPU がアクセスするときのアドレスまたはデータを指定する入力    |

|              |      |     | 端子です。                                  |

|              |      |     | 1:データを転送するとき                           |

|              |      |     | 0:アクセスするレジスタのアドレスを設定するとき               |

|              |      |     | シリアル・モード時 ( PS = 1 )                   |

|              |      |     | 3 線 SPI モード時(RD_B = 0): 送受信データ入出力      |

|              |      |     | 4 線 SPI モード時(RD_B = 1): 送信データ出力        |

| A1/RXD       | 5J   | 入力  | パラレル・モード時 ( PS = 0 )                   |

|              |      |     | ホスト・インタフェース・アドレス A1 信号入力               |

|              |      |     | ホスト CPU がアクセスするときのアクセス先レジスタを選択する入力端    |

|              |      |     | 子です。                                   |

|              |      |     | 1:音源ブロック・レジスタ                          |

|              |      |     | 0:音源以外プロック・レジスタ                        |

|              |      |     | シリアル・モード時 ( PS = 1 )                   |

|              |      |     | 3 線 SPI モード時(RD_B = 0): 使用せず           |

|              |      |     | 4 線 SPI モード時(RD_B = 1): 受信データ入力        |

| CS_B/SCS     | 6J   | 入力  | パラレル・モード時 ( PS = 0 )                   |

|              |      |     | チップ・セレクト入力                             |

|              |      |     | ホスト・インタフェース・セレクト信号の入力端子です。             |

|              |      |     | ホスト CPU がホスト・インタフェースのレジスタをアクセスする間 , この |

|              |      |     | 端子をアクティブ(ロウ・レベル)にします。                  |

|              |      |     | シリアル・モード時 ( PS = 1 )                   |

|              |      |     | チップ・セレクト入力                             |

| RD_B/SPIMODE | 7J   | 入力  | パラレル・モード時 ( PS = 0 )                   |

|              |      |     | ホスト・リード入力                              |

|              |      |     | ホスト CPU がホスト・インタフェースのレジスタを読み出す場合に , この |

|              |      |     | 端子をアクティブ(ロウ・レベル)にします。                  |

|              |      |     | WR_B 端子と同時にアクティブにしないでください。             |

|              |      |     | シリアル・モード時 ( PS = 1 )                   |

|              |      |     | SPI モード選択入力                            |

|              |      |     | 0:3線 SPI モード選択                         |

|              |      |     | 1:4 線 SPI モード選択                        |

| WR_B/SCLK    | 7K   | 入力  | パラレル・モード時 ( PS = 0 )                   |

|              |      |     | ホスト・ライト入力                              |

|              |      |     | ホスト CPU がホスト・インタフェースのレジスタに書き込む場合に , この |

|              |      |     | 端子をアクティブ(ロウ・レベル)にします。                  |

|              |      |     | RD_B 端子と同時にアクティブにしないでください。             |

|              |      |     | シリアル・モード時 ( PS = 1 )                   |

|              |      |     | シリアル・クロック入力                            |

|              |      |     | 13 MHz まで動作可能です。                       |

(2/2)

| 端子名称       | 端子番号        | 入出力 | 機能                                       |

|------------|-------------|-----|------------------------------------------|

| D0/SERINIT | 8K          | 入出力 | パラレル・モード時 ( PS = 0 )                     |

|            |             |     | 8 ビット・ホスト・データ・バス                         |

|            |             |     | ホスト CPU が本 LSI をアクセスするとき ,アドレスおよびデータの入出力 |

|            |             |     | を行います。                                   |

|            |             |     | CS_B がインアクティブ(ハイ・レベル)の場合,ハイ・インピーダンス      |

|            |             |     | になります。                                   |

|            |             |     | シリアル・モード時 ( PS=1 )                       |

|            |             |     | シリアル・インタフェース・リセット入力                      |

| D1 - D7    | 8J, 10H,    | 入出力 | パラレル・モード時 ( PS = 0 )                     |

|            | 9H, 10G,    |     | 8 ビット・ホスト・データ・バス                         |

|            | 9G, 10F, 9F |     | ホスト CPU が本 LSI をアクセスするとき ,アドレスおよびデータの入出力 |

|            |             |     | を行います。                                   |

|            |             |     | CS_B がインアクティブ(ハイ・レベル)の場合,ハイ・インピーダンス      |

|            |             |     | になります。                                   |

|            |             |     | シリアル・モード時 ( PS=1 )                       |

|            |             |     | 未使用につき GND に接地してください。                    |

| INT_B      | 10E         | 出力  | ホスト割り込み出力                                |

|            |             |     | 本 LSI からホスト CPU への割り込み信号です。              |

|            |             |     | データ転送時のデータ送受信要求,内部状態を通知するときの要求などに使用      |

|            |             |     | します。                                     |

|            |             |     | <b>備考</b> 音源ブロックの制御にのみ使用可能です。            |

| PS         | 6B          | 入力  | パラレル / シリアル設定入力                          |

|            |             |     | ホスト CPU インタフェースの , パラレル・モードとシリアル・モードの設定を |

|            |             |     | 行います。                                    |

|            |             |     | 1:シリアル・インタフェース・モード                       |

|            |             |     | 0:パラレル・インタフェース・モード                       |

|            |             |     | LSI 内部でプルダウンされているため,パラレル・モード時はオープンで構い    |

|            |             |     | ません。                                     |

# (4) オーディオ・シリアル・インタフェース (ASIO)

| 端子名称  | 端子番号 | 入出力 | 機能                                   |

|-------|------|-----|--------------------------------------|

| BCLK  | 8B   | 入出力 | オーディオ・シリアル用ビット同期クロック入出力              |

|       |      |     | 未使用時は GND へ接地してください。                 |

| LRCLK | 8A   | 入出力 | オーディオ・シリアル用フレーム同期クロック入出力             |

|       |      |     | 未使用時は GND へ接地してください。                 |

| ASO   | 7B   | 出力  | オーディオ・シリアル用データ出力                     |

|       |      |     | オーディオ・シリアル・データのフレーム・サイズはレジスタで設定します。  |

|       |      |     | マスタ・モード時:64 ビット,32 ビットの選択            |

|       |      |     | スレーブ・モード時:32~64 ビット,2 ビット・ステップからの選択  |

|       |      |     | 未使用時はオープンにしてください。                    |

| ASI   | 7A   | 入力  | オーディオ・シリアル用データ入力                     |

|       |      |     | オーディオ・シリアル・データのフレーム・サイズはレジスタで設定します。  |

|       |      |     | マスタ・モード時:64 ビット,32 ビットの選択            |

|       |      |     | スレーブ・モード時:32~64 ビット,2 ビット・ステップからの選択  |

|       |      |     | LSI内部でプルダウンされているため,未使用時はオープンにしてください。 |

## (5) 音源コア外部接続専用シリアル・インタフェース (MSIO)

| 端子名称  | 端子番号 | 入出力 | 機能                                                  |

|-------|------|-----|-----------------------------------------------------|

| MBCLK | 5B   | 入出力 | 音源コア外部接続専用ビット同期クロック入出力                              |

|       |      |     | 未使用時は GND へ接地してください。                                |

| MEN   | 5A   | 入出力 | 音源コア外部接続専用フレーム同期クロック入出力                             |

|       |      |     | 未使用時は GND へ接地してください。                                |

| MSO   | 3C   | 出力  | 音源コア外部接続専用データ出力                                     |

|       |      |     | シリアル・データのフレーム・サイズはレジスタで設定します。                       |

|       |      |     | マスタ・モード時 : 32, 64, 128, 256 ビットからの選択 ( MSIO 単独使用時 ) |

|       |      |     | スレープ・モード時 : 32~256 ビット / 32 ビット・ステップで選択 ( MSIO      |

|       |      |     | 単独使用時 )                                             |

|       |      |     | 未使用時はオープンにしてください。                                   |

| MSI   | 4A   | 入力  | 音源コア外部接続専用データ入力                                     |

|       |      |     | シリアル・データのフレーム・サイズはレジスタで設定します。                       |

|       |      |     | マスタ・モード時 : 32, 64, 128, 256 ビットからの選択 ( MSIO 単独使用時 ) |

|       |      |     | スレープ・モード時 : 32~256 ビット / 32 ビット・ステップで選択 ( MSIO      |

|       |      |     | 単独使用時 )                                             |

|       |      |     | 未使用時はオープンにしてください ( プルダウン抵抗内蔵 )。                     |

注意 1. マスタ・モード,スレーブ・モードによって設定可能なデータ・サイズが変わります。

マスタ・モード時 MBFS = 32, 64, 128, 256 fs のみ

スレープ・モード時 MBFS = 32~256 fs/32 fs step

2. MSIO と ASIO を同時使用する場合は, ASIO はマスタ・モードのみ (BFS = 32, 64 fs) となります。

## (6)外部 LED, モータ制御出力

| 端子名称 | 端子番号 | 入出力 | 機能                                            |

|------|------|-----|-----------------------------------------------|

| LED  | 10C  | 出力  | 外部 LED 制御出力(ドライブ能力:1 mA ただし EV₪ = 1.8 V)      |

|      |      |     | ポート出力です。設定はホスト CPU からポート設定レジスタに値を書き込むことで行います。 |

|      |      |     | 未使用時はオープンにしてください。                             |

| VIB  | 9D   | 出力  | 外部モータ制御出力(ドライブ能力:1mA ただし EVpp = 1.8 V)        |

|      |      |     | ポート出力です。設定はホスト CPU からポート設定レジスタに値を書き込むこ        |

|      |      |     | とで行います。                                       |

|      |      |     | 未使用時はオープンにしてください。                             |

#### (7)アナログ回路用基準電圧/基準電流

| 端子名称 | 端子番号 | 入出力 | 機能                                    |  |  |  |  |

|------|------|-----|---------------------------------------|--|--|--|--|

| VREF | 2E   | 出力  | アナログ・ブロック用基準電圧                        |  |  |  |  |

|      |      |     | 0.22 μF のコンデンサを本端子と AGND の間に接続してください。 |  |  |  |  |

| IREF | 2D   | 入力  | 56 kΩの抵抗を本端子と AGND の間に接続してください。       |  |  |  |  |

#### (8) オーディオ DAC 出力

| 端子名称  | 端子番号 | 入出力 | 機能                 |

|-------|------|-----|--------------------|

| LINOL | 1C   | 出力  | 外部スピーカ用ライン(L ch)出力 |

| LINOR | 1F   | 出力  | 外部スピーカ用ライン(R ch)出力 |

# (9) レギュレータ

| 端子名称     | 端子番号   | 入出力 | 機能                                     |  |  |  |  |

|----------|--------|-----|----------------------------------------|--|--|--|--|

| REGOUT   | 2K, 3J | 出力  | レギュレータ出力                               |  |  |  |  |

|          |        |     | ディジタル電源にレギュレータ出力を使用する場合は,本端子と DVoo 端子を |  |  |  |  |

|          |        |     | LSI 外部で接続してください。                       |  |  |  |  |

|          |        |     | 2.2 μF のコンデンサを本端子と REGGND の間に接続してください。 |  |  |  |  |

| REGUSE_B | 4H     | 入力  | レギュレータ・ブロック・イネーブル信号入力端子                |  |  |  |  |

|          |        |     | 0: レギュレータ使用時                           |  |  |  |  |

|          |        |     | 1:レギュレータ未使用時                           |  |  |  |  |

| REGCNT   | 3K     | 入力  | レギュレータ・コントロール用入力端子                     |  |  |  |  |

|          |        |     | 0:出力停止                                 |  |  |  |  |

|          |        |     | 1:出力開始                                 |  |  |  |  |

# (10)汎用外部出力

| 端子名称      | 端子番号        | 入出力 | 機能                           |  |  |  |

|-----------|-------------|-----|------------------------------|--|--|--|

| PO0 - PO3 | 5H, 6H, 4K, | 出力  | 汎用外部出力                       |  |  |  |

|           | 4J          |     | 周辺デバイスのコントロール信号を出力することができます。 |  |  |  |

|           |             |     | 未使用時はオープンにしてください。            |  |  |  |

# (11) テスト用端子

| 端子名称      | 端子番号       | 入出力 | 機能                 |

|-----------|------------|-----|--------------------|

| TM0 - TM2 | 2C, 2F, 3B | 入力  | テスト用入力             |

|           |            |     | 通常使用時はオープンにしてください。 |

| TM3, TM4  | 3A, 4B     | 入出力 | テスト用入出力            |

|           |            |     | 通常使用時はオープンにしてください。 |

| TM5       | 6C         | 入力  | テスト用入力             |

|           |            |     | 通常使用時はオープンにしてください。 |

# (12) その他

| 端子名称        | 端子番号        | 入出力 | 機能                                 |

|-------------|-------------|-----|------------------------------------|

| N.C         | 1B, 2A, 2B, | -   | 従来製品との互換性のために備えています。オープンで使用してください。 |

|             | 2J, 3D, 3E, |     |                                    |

|             | 8D, 8E, 9A, |     |                                    |

|             | 9B, 9J, 9K, |     |                                    |

|             | 10B, 10J    |     |                                    |

| N.C (index) | 4D          | -   | 従来製品との互換性のために備えています。オープンで使用してください。 |

# 2.4 未使用端子の処理

表 2-1 未使用端子の処理

| 端子名                | 入出力   | 推奨接続方法                                        |

|--------------------|-------|-----------------------------------------------|

| MCLK1              | I     | PLLGND へ接地してください。                             |

| MCLK2              | I     | EGND へ接地してください。                               |

| CSTRT              | I     | オープンにしてください(Pull-Down 内蔵 )。                   |

| A1/RXD             | I     | DGND へ接地してください。                               |

| D0/SERINIT         | I     | DGND へ接地してください。                               |

| D1 - D7            | I     | DGND へ接地してください。                               |

| INT_B              | 0     | オープンにしてください。                                  |

| LRCLK              | I/O   | DGND へ接地してください。                               |

| BCLK               | I/O   | DGND へ接地してください                                |

| ASI                | I     | オープンにしてください(Pull-Down 内蔵 )。                   |

| ASO                | 0     | オープンにしてください。                                  |

| MEN                | I/O   | DGND へ接地してください。                               |

| MBCLK              | I/O   | DGND へ接地してください                                |

| MSI                | I     | オープンにしてください(Pull-Down 内蔵 )。                   |

| MSO                | 0     | オープンにしてください。                                  |

| LED                | 0     | オープンにしてください。                                  |

| VIB                | 0     | オープンにしてください。                                  |

| LINOL              | 0     | オープンにしてください。                                  |

| LINOR              | 0     | オープンにしてください。                                  |

| REGUSE_B           | 1     | EV <sub>DD</sub> へ接続してください(Regulator 未使用時)。   |

| REGCNT             | I     | EGND へ接続してください(Regulator 未使用時)。               |

| REGV <sub>DD</sub> | Power | 3.0 V 電源へ接続してください ( Regulator 使用時 , 未使用時とも )。 |

| REGOUT             | 0     | オープンにしてください(Regulator 未使用時)。                  |

| PO0 - PO3          | 0     | オープンにしてください。                                  |

| TM0 - TM2          | I     | オープンにしてください(Pull-Down 内蔵 )。                   |

| TM3, TM4           | I/O   | オープンにしてください。                                  |

| TM5                | I     | オープンにしてください(Pull-Down 内蔵)。                    |

# 2.5 端子状態

(1/2)

| 端子  | I/O    | A/D     | 端子名                | スタンバ           | イ時<br>   | RESET_B =        | 0 のとき | リセット後 |

|-----|--------|---------|--------------------|----------------|----------|------------------|-------|-------|

| 番号  |        |         |                    | 制御信号           | 端子状態     | 制御信号             | 端子状態  |       |

| 2F  | Input  | Digital | TM1                |                | Input    |                  | Input | Input |

| 1C  | Output | Analog  | LINOL              | STDAC          | Hi-Z     | STDAC            | Hi-Z  | Hi-Z  |

| 1D  | -      | Analog  | AGND               |                |          |                  |       |       |

| 2D  | Output | Analog  | IREF               | STREF          | Hi-Z     | STREF            | Hi-Z  | Hi-Z  |

| 2E  | Output | Analog  | VREF               | STREF          | Hi-Z     | STREF            | Hi-Z  | Hi-Z  |

| 1E  | -      | Analog  | AV <sub>DD</sub>   |                |          |                  |       |       |

| 1F  | Output | Analog  | LINOR              | STDAC          | Hi-Z     | STDAC            | Hi-Z  | Hi-Z  |

| 1G  | -      | Analog  | AGND2              |                |          |                  |       |       |

| 2G  | -      | Analog  | PLLV <sub>DD</sub> |                |          |                  |       |       |

| 2H  | Input  | Analog  | MCLK1              | STPLL1, STPLL2 | Input    | STPLL1, STPLL2   | Input | Input |

| 1H  | -      | Analog  | PLLGND             |                |          |                  |       |       |

| 3G  | -      | Analog  | REGGND             |                |          |                  |       |       |

| 3H  | -      | Analog  | REGV <sub>DD</sub> |                |          |                  |       |       |

| 1J  | -      | Analog  | REGV <sub>DD</sub> |                |          |                  |       |       |

| 2K  | Output | Analog  | REGOUT             | REGCNT         | Low      | REGCNT           | Low   | Low   |

| 3J  | Output | Analog  | REGOUT             | REGCNT         | Low      | REGCNT           | Low   | Low   |

| 3F  | input  | Analog  | MCLK2              | STPLL1, STPLL2 | Input    | t STPLL1, STPLL2 |       | Input |

| 3K  | Input  | Digital | REGCNT             |                | Input    |                  | Input | Input |

| 4H  | Input  | Digital | REGUSE_B           |                | Input    |                  | Input | Input |

| 5H  | Output | Digital | P00                |                | Register | RESET_B          | Low   | Low   |

| 4K  | Output | Digital | PO2                |                | Register | RESET_B          | Low   | Low   |

| 4J  | Output | Digital | PO3                |                | Register | RESET_B          | Low   | Low   |

| 6H  | Output | Digital | PO1                |                | Register | RESET_B          | Low   | Low   |

| 5K  | -      | Digital | DGND               |                |          |                  |       |       |

| 5J  | input  | Digital | A1/RXD             |                | Input    |                  | input | Input |

| 7H  | -      | Digital | DV <sub>DD</sub>   |                |          |                  |       |       |

| 6K  | I/O    | Digital | A0/Data, TXD       |                | Input    |                  | Input | Input |

| 6J  | Input  | Digital | CS_B/SCS           |                | Input    |                  | Input | input |

| 7J  | Input  | Digital | RD_B/SPIMO         |                | Input    |                  | Input | Input |

|     |        |         | DE                 |                |          |                  |       |       |

| 7K  | Input  | Digital | WR_B/SCLK          |                | Input    |                  | input | Input |

| 8H  | -      | Digital | EV <sub>DD</sub>   |                |          |                  |       |       |

| 8K  | I/O    | Digital | D0/SERINIT         |                | Input    | RESET_B          | Hi-Z  | Input |

| 8J  | I/O    | Digital | D1                 |                | Input    | RESET_B          | Hi-Z  | Input |

| 8G  | -      | Digital | EGND               |                |          |                  |       |       |

| 10H | I/O    | Digital | D2                 |                | Input    | RESET_B          | Hi-Z  | Input |

| 9H  | I/O    | Digital | D3                 |                | Input    | RESET_B          | Hi-Z  | Input |

| 8F  | -      | Digital | DV <sub>DD</sub>   |                |          |                  |       |       |

| 10G | I/O    | Digital | D4                 |                | Input    | RESET_B          | Hi-Z  | Input |

| 9G  | I/O    | Digital | D5                 |                | Input    | RESET_B          | Hi-Z  | Input |

| 10F | I/O    | Digital | D6                 |                | Input    | RESET_B          | Hi-Z  | Input |

(2/2)

|     |        |         |                  |              |          |           |       | ( 2/2 ) |

|-----|--------|---------|------------------|--------------|----------|-----------|-------|---------|

| 端子  | I/O    | A/D     | 端子名              | スタンハ         | イ時       | RESET_B = | 0 のとき | リセット後   |

| 番号  |        |         |                  | 制御信号         | 端子状態     | 制御信号      | 端子状態  |         |

| 9F  | I/O    | Digital | D7               |              | Input    | RESET_B   | Hi-Z  | Input   |

| 10E | Output | Digital | INT_B            |              | Output   | RESET_B   | High  | High    |

| 9E  | Input  | Digital | RESET_B          |              | Input    |           | Input | input   |

| 10D | -      | Digital | DV <sub>DD</sub> |              |          |           |       |         |

| 9D  | Output | Digital | VIB              |              | Register | RESET_B   | Low   | Low     |

| 10C | Output | Digital | LED              |              | Register | RESET_B   | Low   | Low     |

| 9C  | -      | Digital | EV <sub>DD</sub> |              |          |           |       |         |

| 8C  | Input  | Digital | CSTRT            |              | Input    |           | Input | input   |

| 8B  | I/O    | Digital | BCLK             | STASI, STASO |          | RESET_B   | Hi-Z  | input   |

| 8A  | I/O    | Digital | LRCLK            | STASI, STASO |          | RESET_B   | Hi-Z  | input   |

| 7C  | ı      | Digital | DV <sub>DD</sub> |              |          |           |       |         |

| 7A  | Input  | Digital | ASI              | STASI, STASO |          |           | input | input   |

| 7B  | Output | Digital | ASO              | STASI, STASO |          | RESET_B   | Hi-Z  | Hi-Z    |

| 6B  | input  | Digital | PS               |              | Input    |           | Input | Input   |

| 6A  | ı      | Digital | EGND             |              |          |           |       |         |

| 6C  | input  | Digital | TM5              |              | Input    |           | input | Input   |

| 5B  | I/O    | Digital | MBCLK            | STMSI, STMSO |          | RESET_B   | Hi-Z  | input   |

| 5A  | I/O    | Digital | MEN              | STMSI, STMSO |          | RESET_B   | Hi-Z  | input   |

| 5C  | ı      | Digital | DGND             |              |          |           |       |         |

| 4C  | -      | Digital | DV <sub>DD</sub> |              |          |           |       |         |

| 4A  | Input  | Digital | MSI              | STMSI, STMSO |          |           | input | input   |

| 4B  | I/O    | Digital | TM4              |              | Low      | RESET_B   | Hi-Z  | Low     |

| 3C  | Output | Digital | MSO              | STMSI, STMSO |          | RESET_B   | Hi-Z  | Hi-Z    |

| 3A  | I/O    | Digital | TM3              |              | Low      | RESET_B   | Hi-Z  | Low     |

| 3B  | Input  | Digital | TM2              |              | Input    |           | Input | Input   |

| 2C  | Input  | Digital | ТМО              |              | Input    |           | input | Input   |

**備考** ASIO モード, MSIO モード時の状態は,表 2-2,表 2-3を参照してください。

# 表 2 - 2 ASIO 状態表

| 端子名   | 機能                           | AMS=0 (スレーブ・モード)     |           |        |        | AMS = 1(マスタ・モード) |        |        |        |

|-------|------------------------------|----------------------|-----------|--------|--------|------------------|--------|--------|--------|

|       |                              | (                    | STASI, ST | ASO)   |        | (STASI, STASO)   |        |        |        |

|       |                              | (0, 0)               | (1, 1)    | (1, 0) | (0, 1) | (0, 0)           | (1, 1) | (1, 0) | (0, 1) |

| BCLK  | オーディオ・シリアル用ビッ<br>ト同期クロック入出力  | IN<br>(internal:Low) | IN        | IN     | IN     | Low              | OUT    | OUT    | OUT    |

| LRCLK | オーディオ・シリアル用フ<br>レーム同期クロック入出力 | IN<br>(internal:Low) | IN        | IN     | IN     | Low              | OUT    | OUT    | OUT    |

| ASI   | オーディオ・シリアル用デー<br>タ入力         | -                    | IN        | IN     | -      | -                | IN     | IN     | -      |

| ASO   | オーディオ・シリアル用デー<br>タ出力         | Hi-Z                 | OUT       | Hi-Z   | OUT    | Hi-Z             | OUT    | Hi-Z   | OUT    |

# 表 2 - 3 MSIO 状態表

| 端子名   | 機能                          | MMS = 0              | MMS=0(スレーブ・モード) |        |        |                | MMS = 1(マスタ・モード) |        |        |  |

|-------|-----------------------------|----------------------|-----------------|--------|--------|----------------|------------------|--------|--------|--|

|       |                             | ()                   | STMSI, ST       | MSO)   |        | (STMSI, STMSO) |                  |        |        |  |

|       |                             | (0, 0)               | (1, 1)          | (1, 0) | (0, 1) | (0, 0)         | (1, 1)           | (1, 0) | (0, 1) |  |

| MBCLK | 音源コア外部接続専用ビット<br>同期クロック入出力  | IN<br>(internal:Low) | IN              | IN     | IN     | Lo             | OUT              | OUT    | OUT    |  |

| MEN   | 音源コア外部接続専用フレー<br>ム同期クロック入出力 | IN<br>(internal:Low) | IN              | IN     | IN     | Lo             | OUT              | OUT    | OUT    |  |

| MSI   | 音源コア外部接続専用データ<br>入力         | -                    | IN              | IN     | -      | -              | IN               | IN     | -      |  |

| MSO   | 音源コア外部接続専用データ<br>出力         | Hi-Z                 | OUT             | Hi-Z   | OUT    | Hi-Z           | OUT              | Hi-Z   | OUT    |  |

#### 3. CPU インタフェース

#### 3.1 パラレル・ホスト CPU インタフェース

ホスト CPU インタフェースからのパラレル・アクセスの方法を説明します。

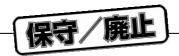

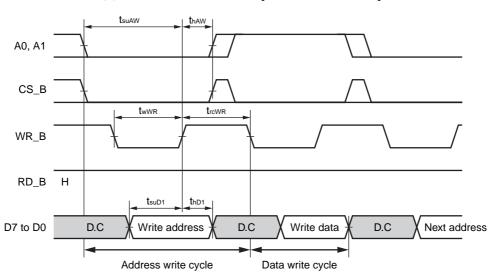

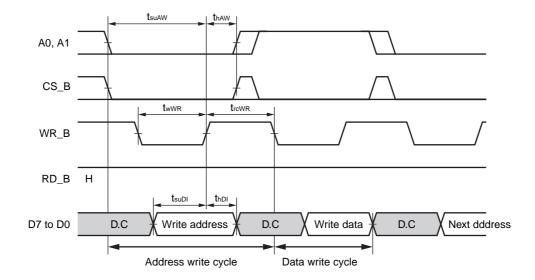

#### 3.1.1 ライト・アクセス

ライト・アクセスではシステム側から本 LSI に対してデータ書き込みを行います。

- ・AO 端子によりアドレス・ライト・サイクルとデータ・ライト・サイクルを区別します。

- ・A1 端子により音源用レジスタ・アクセスと音源以外用レジスタ・アクセスを区別します(0:音源以外,1:音源)

- ・アドレス・ライト・サイクルに書き込むデータは, D7 D0 にアドレスを割り当てます。

# 注意 アドレス・ライト・サイクルおよびデータ・ライト・サイクル中は RD\_B 端子を常にハイ・レベル固定にしてください。

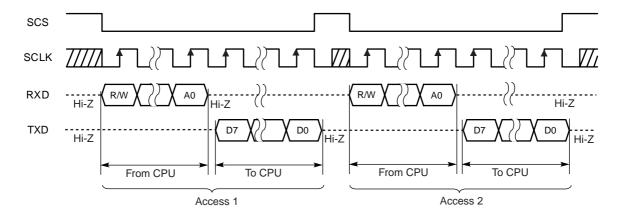

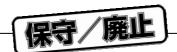

図 3-1 ライト・アクセス (シングル・アクセス)

**備考** CS\_B 端子は,ライト期間はロウ・レベル固定にしてください。連続ライト・アクセス中は CS\_B 端子を常にロウ・レベルにする必要はありません。

D.C.: Don't Care

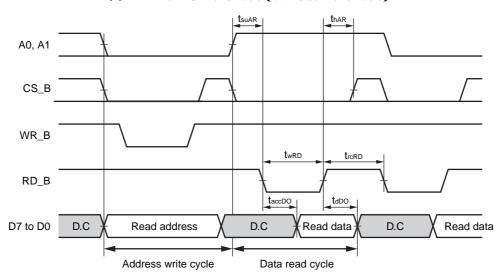

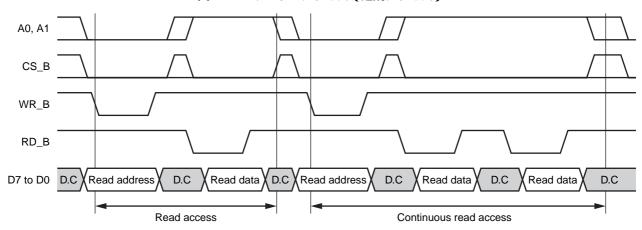

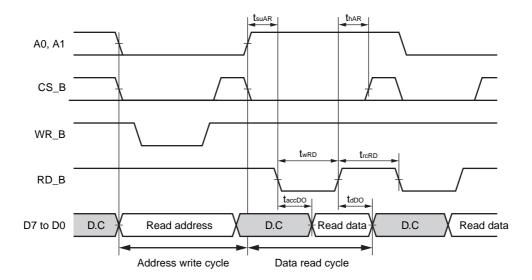

#### 3.1.2 リード・アクセス

リード・アクセスではシステム側から本 LSI に対してデータ読み出しを行います。

- ・AO によりアドレス・ライト・サイクルとデータ・リード・サイクルを区別します。

- ・A1により音源用レジスタ・アクセスと音源以外用レジスタ・アクセスを区別します(0:音源以外,1:音源)。

- ・システム・クロックによる WR\_B および RD\_B の立ち上がりエッジ検出を基準に動作します。

- ・アドレス・ライト・サイクルに書き込むデータは, D7-D0 にアドレスを割り当てます。

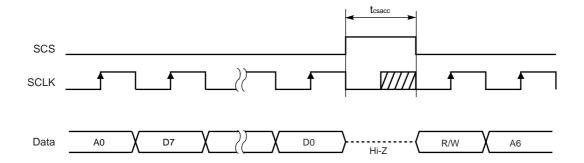

図 3-3 リード・アクセス (シングル・アクセス)

図 3-4 リード・アクセス (連続アクセス)

**備考** CS\_B 端子は , リード期間はロウ・レベル固定にしてください。連続リード・アクセス中は CS\_B 端子を常に ロウ・レベルにする必要はありません。

D.C.: Don't Care

#### 3.2 シリアル・ホスト・インタフェース

ホスト CPU インタフェースからのシリアル・アクセスの方法を説明いたします。

#### 3.2.1 端子機能

- ・シリアル・モードで使用するピンは、パラレル・モードで使用するピンと共用になります

- ・PS ピンを設定することにより,シリアル・モードを有効にします。

- 1:シリアル・モード

- 0:パラレル・モード(ディフォールト)

- ・RD\_B ( SPIMODE ) 端子を切り替えることで , 3 線 SPI モードと 4 線 SPI モードの 2 通りの転送方式を実現可能です。

1:4線SPIモード 0:3線SPIモード

| 端子名     |      | I/O | 機能                                              |

|---------|------|-----|-------------------------------------------------|

| シリアル    | パラレル |     |                                                 |

| PS      | PS   | 1   | ホスト CPU インタフェース・モード選択信号入力                       |

|         |      |     | 0:パラレル・モード有効                                    |

|         |      |     | 1:シリアル・モード有効                                    |

| SPIMODE | RD_B | 1   | SPI モード選択信号入力                                   |

|         |      |     | 0:3 線 SPI モード                                   |

|         |      |     | 1:4 線 SPI モード                                   |

| SCLK    | WR_B | 1   | シリアル・クロック入力                                     |

| SCS     | CS_B | 1   | チップ・セレクト信号入力                                    |

| Data,   | A0   | I/O | 3 線 SPI モード時:送受信データ入出力                          |

| TXD     |      |     | 4 線 SPI モード時:送信データ出力                            |

| RXD     | A1   | - 1 | 3 線 SPI モード時:使用しません                             |

|         |      |     | 4 線 SPI モード時:受信データ入力                            |

| SERINT  | D0   | ı   | シリアル・リセット信号入力                                   |

|         |      |     | SERINT = 1 のときに,SCS = 1 になるとシリアル・インタフェース回路に非同期リ |

|         |      |     | セットがかかります。                                      |

#### 3.2.2 シリアル・フォーマット

トータル ; 16 ビット

リード/ライト制御 :1ビット(ハイ・レベル:ライト,ロウ・レベル:リード)

アドレス : 7 ビットデータ : 8 ビット

#### (1) レジスタ領域

本 LSI は 2 つのバンクを持っています。ひとつは音源コア設定用(音源バンク)で,もうひとつはチップ制御用(NEC バンク)です。バンク切り替えは,バンク設定用レジスタ(アドレス:7CH)で設定します。

#### (2) アクセス・フォーマット

次のフォーマットを持ちます。

ノーマル・ライト・アクセス

ノーマル・リード・アクセス

連続ライト・アクセス (1)

連続ライト・アクセス (2) for FIFO

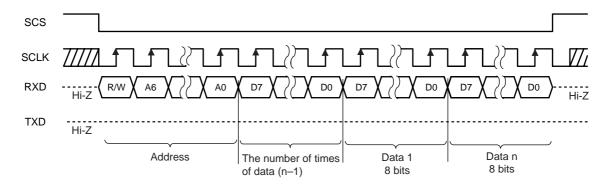

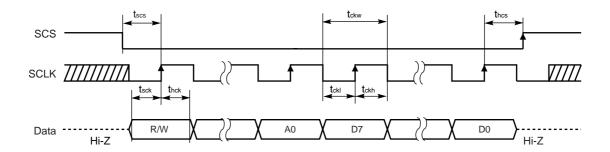

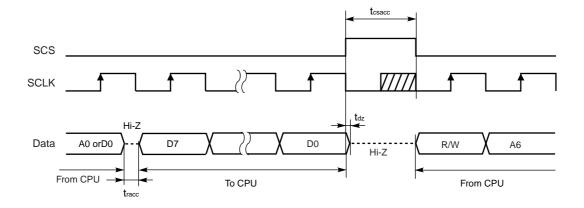

# 3.2.3 アクセス・フォーマット (3線 SPI モード)

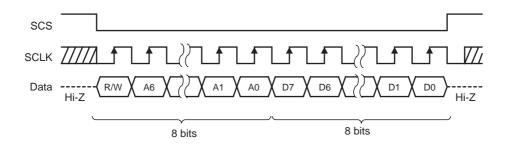

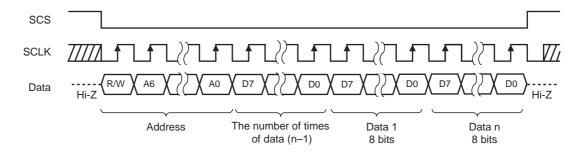

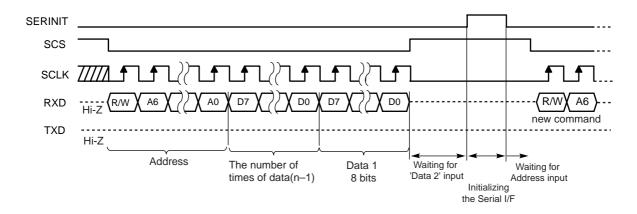

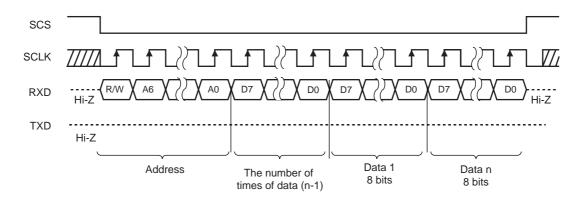

#### 図 3-5 ホスト CPU アクセス (ライト/リード・アクセス期間)

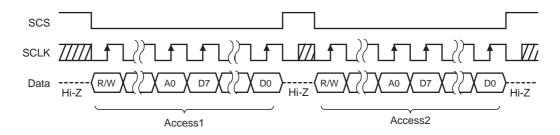

図 3-6 ホスト CPU アクセス・フォーマット (連続アクセス 1)

#### (a) ライト・アクセス

#### (b) リード・アクセス

備考 このフォーマットは,音源コアの FIFO 以外へのアクセスの場合です。

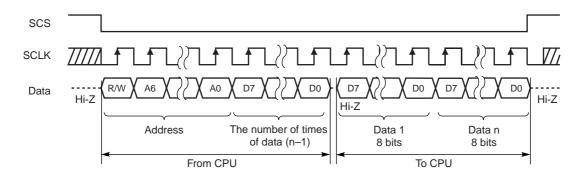

# 図 3-7 ホスト CPU アクセス・フォーマット (連続アクセス 2)

(a) ライト・アクセス

(b) リード・アクセス

備考 このフォーマットは,音源コアの FIFO ヘアクセスする場合だけに使用できます。

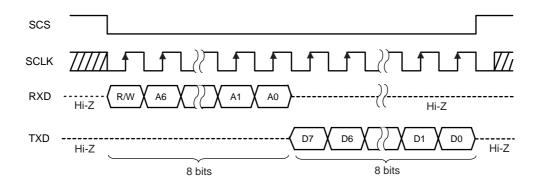

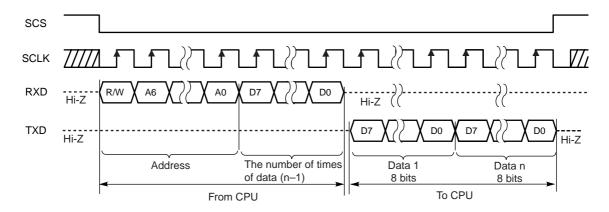

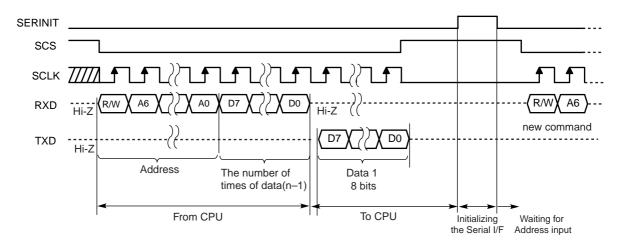

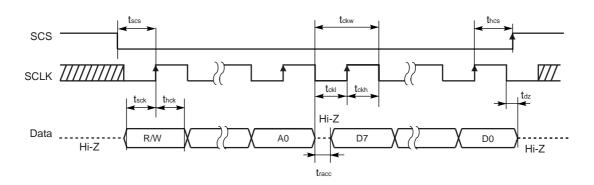

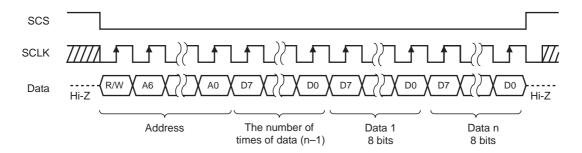

# 3.2.4 アクセス・フォーマット (4線 SPI モード)

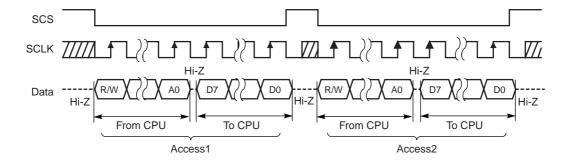

#### 図 3-8 ホスト CPU アクセス・フォーマット (リード/ライト・アクセス)

図 3-9 ホスト CPU アクセス・フォーマット (連続アクセス)

#### (a) ライト・アクセス

#### (b) リード・アクセス

備考 このフォーマットは音源コアの FIFO 以外へアクセスする場合だけに使用できます。

28

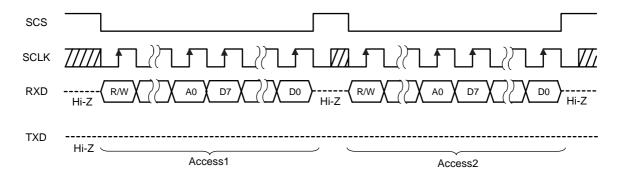

# 図 3 - 10 ホスト CPU アクセス・フォーマット (連続アクセス 2)

(a) ライト・アクセス

(b) リード・アクセス

注意 このフォーマットは音源コアの FIFO ヘアクセスする場合だけに使用できます。

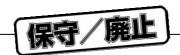

#### 3.2.5 シリアル・インタフェースの初期化について

SERINIT/D0 端子は,シリアル・インタフェースの連続リード/ライト・アクセスを強制的に初期化するための端子です。ただし初期化が必要なければ,SERINIT/D0 端子はロウ・レベルに固定してください。

この初期化は,シリアル・インタフェースのみにかかり,SCS = 1 かつ SERINIT = 0 のときに,非同期で実行されます。音源コア・ブロックや,NEC ブロックのレジスタは初期化されません。

したがって,シリアル・インタフェースは初期化後,次のアドレスが設定されるのを待ちます。 この初期化信号の例を次に示します。

#### 図 3 - 11 SERINIT/D0 端子を使用した連続アクセスの取り消し

#### (a) ライト・アクセス

#### (b) リード・アクセス

備考 3線 SPI モード, 4線 SPI モードでの初期化条件は同じです。

#### 4. 音楽シリアル・インタフェース

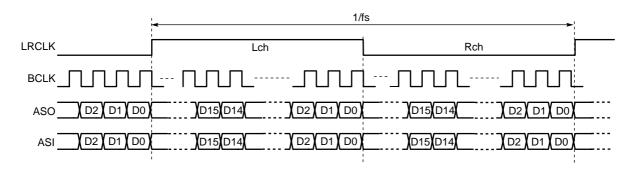

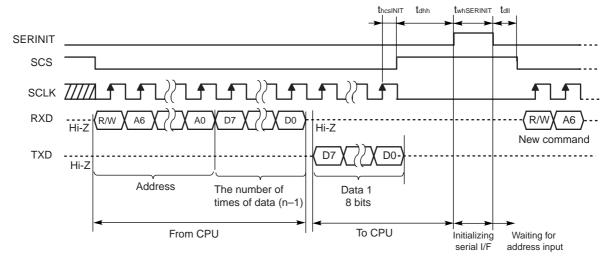

#### 4.1 オーディオ・シリアル・インタフェース (ASIO)

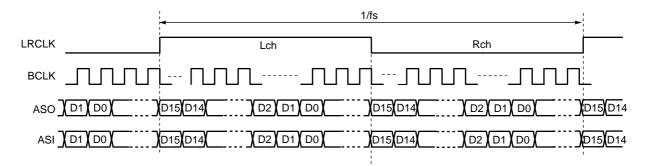

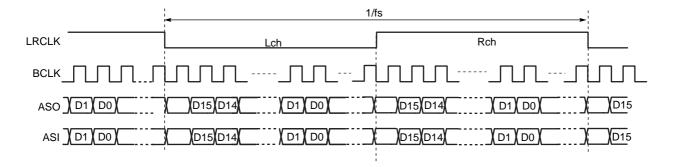

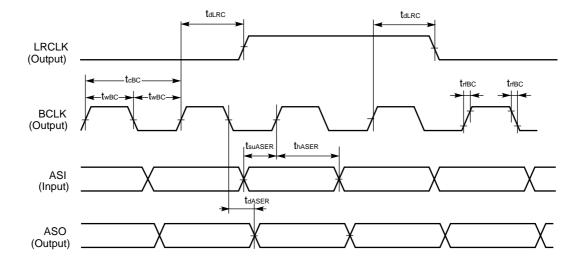

LRCLK 立ち上がり区間内に L ch データ, LRCLK 立ち下がり区間内に R ch データが配置されます。IIS フォーマットはその逆です。それぞれの区間内に, 右詰めや左詰め, IIS フォーマットといったフォーマットの切り替えができます。シリアル入出力のタイミングは図 4 - 1のとおりです。またマスタ・モード/スレーブ・モードの選択が可能です。フレーム内のデータ・ビット数はレジスタ設定で可変可能です。

#### 図 4-1 オーディオ・シリアル・インタフェース・タイミング

#### (a) 右詰めフォーマット

#### (b) 左詰めフォーマット

#### (c) IIS フォーマット

- 注意 1. IIS フォーマットは , 1 ビット空け左詰め , L ch : ロウ・レベル , R ch : ハイ・レベルです。そのほかは左右 詰めの組み合わせに対応します。

- 2. リセット解除後の初期設定では L ch 32 ビット, R ch 32 ビット, 計 64 ビットで 1 フレーム構成となっています。

- 3. 1フレームのビット数はレジスタ設定により可変できます。

マスタ・モード時:64 ピット,32 ピット

スレーブ・モード時:32 ビット~64 ビット,2 ビット・ステップ

(マスタ,スレープ共に,初期値は64 ピットです)

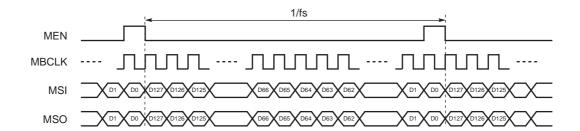

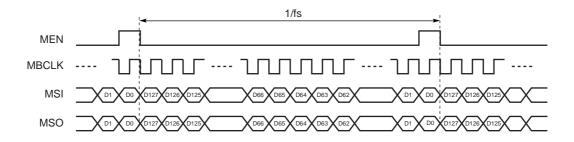

#### 4.2 音源コア外部接続専用シリアル・インタフェース (MSIO)

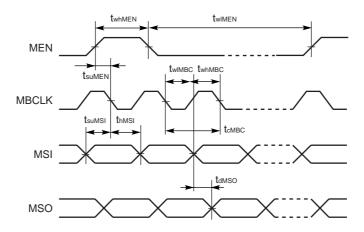

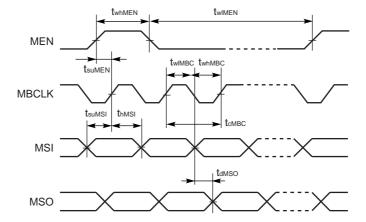

本インタフェースは,本 LSI 内蔵の音源コアと外部アプリケーション・チップとを接続する,専用のシリアル・インタフェースです。従来は音源コア内部で処理をしていたエフェクト効果が,本インタフェースを使用することで,外部アプリケーション・チップで制御可能となります。データ・フォーマットは IIS フォーマットのみ対応します。シリアル入出力のタイミングは次のとおりです。モード設定,ビット・クロック反転使用,およびビット幅設定が,レジスタの変更により可能です。

図 4 - 2 フレーム同期モード 1 (SMEN = 0)

MBCLK 正転 (SMBCLK = 0), ピット幅 128 (MBFS = 128), 8 チャネル (MCH = 8)

図 4-3 フレーム同期モード2(SMEN=0)

MBCLK 反転 (SMBCLK = 1), ビット幅 128 (MBFS = 128), 8 チャネル (MCH = 8)

図 4-4 LR ステレオ・モード (SMEN =1)

MBCLK 反転 (SMBCLK = 1), ピット幅 32 (MBFS = 32), 2 チャネル (MCH = 2)

注意 1. マスタ・モード/スレーブ・モードによって設定可能なデータ・サイズが変わります。

マスタ・モード時:MBFS = 32, 64, 128, 256 fs のみ

スレープ・モード時: MBFS = 32~256fs/32 fs step

2. MSIO と ASIO を同時使用する場合は, ASIO はマスタ・モードのみ (BFS = 32, 64 fs) となります。

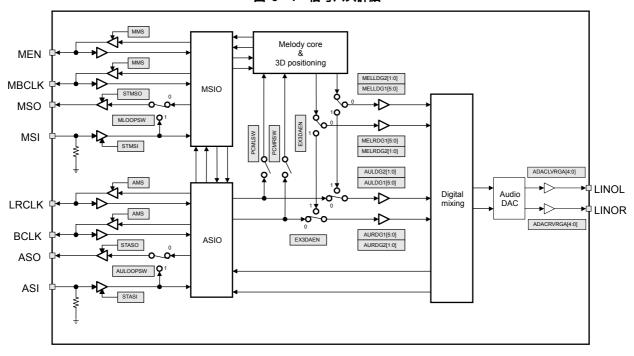

# 5. ブロック機能

図 5-1 信号パス詳細

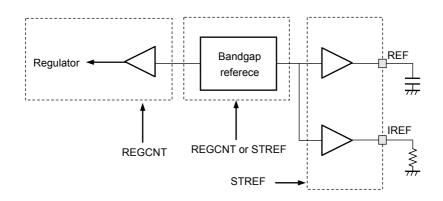

### 5.1 基準電圧/電流源部

図 5-2 基準電圧,電流部プロック

本ブロックは次の機能を持っています。

- ・バンド・ギャップによる基準電圧を発生し,アナログ回路およびPLL,レギュレータに供給します。

- ・上記基準電圧と外付け抵抗から基準電流を発生させ,全アナログ回路およびPLL,レギュレータに供給します。

- ・本ブロックは AVDD から電源供給されます。

本ブロックのスタンバイ制御は,STREF レジスタにより制御を行います。

内蔵レギュレータを動作させるためには,本ブロックの一部から供給される基準電圧が必要となります。基準電圧供給の制御はREGCNT端子により行われます。このためレギュレータ使用時は,REGVddとAVddの両方に必ず3.0V電源を供給してください。

本ブロック立ち上げ後(スタンバイ解除後),最大5 ms で定常状態となります。

本ブロック使用時の注意事項は次のとおりです。

- ・VREF 端子には ,  $0.22~\mu\text{F} \pm 20~\%$ の容量を AGND との間に接続してください。なお全体のアナログ特性に影響があるため , できる限り VREF 端子の近傍に配置してください。また本端子には本容量以外は接続しないでください。

- ・IREF 端子には , 56 k $\Omega$  ± 5 %の抵抗を AGND との間に接続してください。また , 本端子には本抵抗以外は接続しないでください。

- ・本ブロックが定常状態になる前にほかのアナログ・ブロックを立ち上げると,出力が不安定になることがあります。

μ PD9971

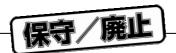

### 5.2 レギュレータ部

# 図 5-3 レギュレータ

本ブロックは次の機能を持っています。

- ・レギュレータにより定電圧を発生し、ディジタル回路用電源 DVpp に電流を供給します。

- ・レギュレータ使用時は、レギュレータ出力 REGOUT 端子と DVpp 端子は LSI 外部でショートしてください。

- ・レギュレータ未使用時は、レギュレータ出力がロウ・レベルになります。

- ・本ブロックは REGVDD から電源供給されます。

- ・レギュレータ未使用時も,レギュレータが未使用であることを認識するために,REGVdd に 3.0 V 電源を供給してください。

本ブロックは , REGUSE\_B 端子 = ロウ・レベル ( DGND ) とすることで使用可能となります。本ブロックを使用しない場合は REGUSE\_B 端子 = ハイ・レベル ( EVDD ) としてください。

また REGUSE\_B 端子 = ロウ・レベルの状態で, REGCNT 端子 = ハイ・レベルとすることで電流供給を開始し, REGCNT 端子 = ロウ・レベルとすることで電流供給を停止します。

| 端子                 | 端子状態            |                       |  |  |  |  |  |

|--------------------|-----------------|-----------------------|--|--|--|--|--|

|                    | レギュレータ未使用時      | レギュレータ使用時             |  |  |  |  |  |

| REGV <sub>DD</sub> | 外部電源 3.0 V      | 外部電源 3.0 V            |  |  |  |  |  |

| REGOUT             | オープン(ロウ・レベル出力)  | DVDDとショート             |  |  |  |  |  |

| DV <sub>DD</sub>   | 外部電源 1.54 V を接続 | REGOUT とショート          |  |  |  |  |  |

| REGCNT             | DGND とショート      | ハイ・レベル:レギュレータ・スタンバイ解除 |  |  |  |  |  |

|                    |                 | ロウ・レベル:レギュレータ・スタンバイ   |  |  |  |  |  |

| REGUSE_B           | EVDD とショート      | DGND とショート            |  |  |  |  |  |

表 5-1 レギュレータ使用時 / 未使用時の端子設定方法

本ブロック使用時の注意事項は次のとおりです。

- ・REGOUT 端子には , 2.2  $\mu$ F  $\pm 20$  %の容量を AGND との間に接続してください。本容量はレギュレータのノイズ特性に影響を与えるため , できる限り REGOUT 端子の近傍に配置してください。また本端子には本容量以外は接続しないでください。

- ・REGV<sub>DD</sub> 端子には, 0.1 μF±20 %の容量を AGND との間に接続してください。

- ・本ブロックが定常状態になる前にディジタル・ブロックを立ち上げると,出力が不安定になることがあるので ご注意ください。

- ・REGOUT 端子に接続される容量に充電を行うため,レギュレータ起動時に約 350 mA の貫通電流が約 50  $\mu$ sec の間流れます。問題のある場合は当社販売員に相談してください。

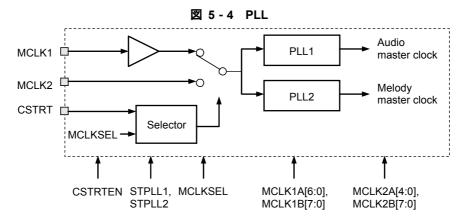

#### 5.3 PLL 部

本ブロックは次の機能を持っています。

- ・外部から入力されたクロックを,レジスタ設定により分周,逓倍し,音源用マスタ・クロック,オーディオ用マスタ・クロックを生成します。

- ・クロック入力端子は, MCLK1 と MCLK2 のどちらかを, 内部レジスタ MCLKSEL および外部端子 CSTRT で選択できます(CSTRT 端子による切り替えは特殊モードです。通常は MCLKSEL レジスタでの切り替えを使用してください)。

- ・CSTRT 端子による切り替えを有効にするためには, CSTRTEN レジスタ = ハイ・レベルとしてください。

- ・MCLK2 端子は、外部ディジタル信号をクロックとして用いるため、EVDD レベルの入力になります。

- ・本ブロックは PLLVDD から電源供給されます。

本プロックは,レジスタ STPLL1 = ハイ・レベルとすることでオーディオ用マスタ・クロックの生成を,STPLL2 = ハイ・レベルとすることで音源プロック用マスタ・クロックの生成を行います。各マスタ・クロックは,入力周波数,サンプリング周波数にあわせて,MCLK1A, MCLK1B, MCLK2A, MCLK2B レジスタによって分周比を設定する必要があります。

CSTRTEN レジスタ = ロウ・レベルのとき, MCLKSEL レジスタを切り替えることで, クロック入力端子としてMCLK1 端子(MCLKSEL レジスタ=ロウ・レベル), MCLK2 端子(MCLKSEL レジスタ=ハイ・レベル)を選択します。

また, CSTRTEN レジスタ=ハイ・レベル, かつあらかじめ特定の分周比を設定することで, 外部端子 CSTRT によってクロック入力端子の切り替えを可能とする特殊モードに入ります。特殊モードの詳細については, 別途お問い合わせください。通常は MCLKSEL レジスタでの切り替えを使用してください。

| CSTRTEN | MCLKSEL    | CSTRT      | クロック選択                            |

|---------|------------|------------|-----------------------------------|

| Low     | Low        | Don't care | クロック入力端子に MCLK2 を選択               |

| Low     | Low        | Don't care | クロック入力端子に MCLK1 を選択               |

| High    | Don't care | High       | クロック入力端子に MCLK1 を選択(15.36 MHz 固定) |

| High    | Don't care | Low        | クロック入力端子に MCLK2 を選択(12.00 MHz 固定) |

表 5-2 レジスタによるクロック切り替え

ブロック使用時の注意事項は次のとおりです。

- ・本ブロックが動作するには,基準電圧源/電流源ブロックが,定常状態にある必要があります。

- ・基準電圧源/電流源ブロックは,スタンバイ解除後5msで定常状態になります。

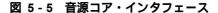

# 5.4 音源コア (音源/3D ポジショニング/イコライザ)インタフェース部

本ブロックは次の機能を持っています。

- ・サンプリング周波数 32 kHz 時は, ASI から入力された PCM データをサラウンド処理可能です。

- ・サンプリング周波数 44.1 kHz 時に,ASI から入力された PCM データをサラウンド処理する場合は,拡張 3DA モード(レジスタ EX3DAEN = ハイ・レベル)に設定する必要があります。

- ・拡張 3DA モード時は, サラウンド処理されたデータの出力先が, MELLDG/MELRDG ブロックから AULDG/AURDG ブロックとなります。

- ・本ブロックの電源は DVDD です。

本ブロックは, STADIG = ハイ・レベルでオーディオ・シリアル・インタフェースが動作します。 本ブロックは, STSYNTH = ハイ・レベルで音源コア部が動作します。

サラウンド処理するオーディオ・データの選択 / 加算は,表5-3のとおりです。

表 5-3 サラウンド処理データ選択

| ブロック   | 設定アドレス | 調整範囲        |  |  |

|--------|--------|-------------|--|--|

| PCMLSW | 0BH    | ミュート,ASI 入力 |  |  |

| PCMRSW | 0BH    | ミュート,ASI 入力 |  |  |

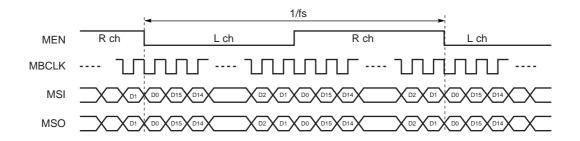

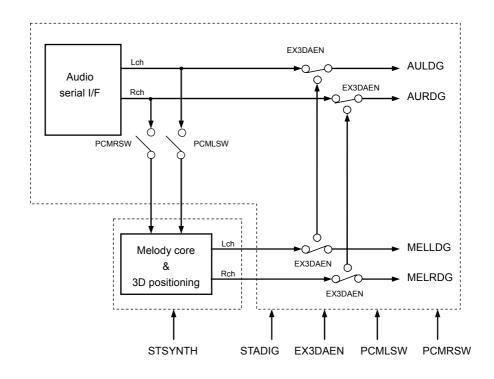

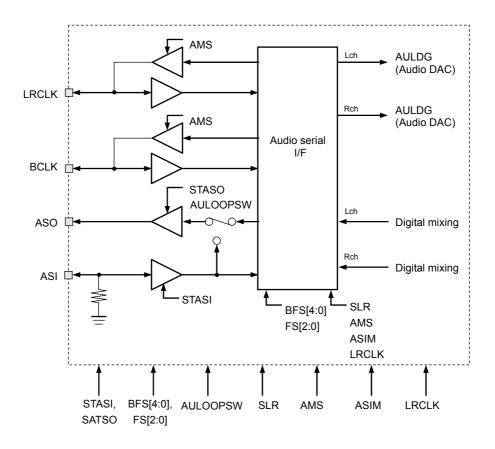

# 5.5 オーディオ・シリアル・インタフェース部 (ASIO)

### 図 5-6 オーディオ・シリアル・インタフェース

本ブロックは次の機能を持っています。

- ・ASI より入力されたシリアル・データをパラレル・データに変換し, Audio DAC 部へ出力します。

- ・Digital mixing 部より入力されたパラレル・データをシリアル・データに変換し, ASO から出力します。

- ・レジスタ設定により,サンプリング周波数を8/16/32(ディフォールト)/44.1/48 kHzから選択します。

- ・レジスタ設定により, BCLK の周波数を変更可能(ディフォールト:64 fs)です。

- ・レジスタ設定により, ASI-ASO のループ・バックをすることができます。

- ・レジスタ設定により,データ・フォーマットの右詰め(ディフォールト)/左詰めを選択できます。

- ・レジスタ設定により,スレーブ・モード(ディフォールト)/マスタ・モードを選択できます。

- ・レジスタ設定により,LRモード(ディフォールト)/IISモードを選択できます。

- ・レジスタ設定により,LRCLKを反転できます。

- ・本ブロックの電源は DVDD です。

本ブロックはレジスタ STASI, STASO により動作します。詳細は表 5-4を参照してください。

# 表 5-4 ASIO 状態表

| 端子名   | 機能                           | AMS = 0              | (スレー      | ブ・モート  | <sup>2</sup> ) | AMS            | ら=1(マス | (マスタ・モード) |        |

|-------|------------------------------|----------------------|-----------|--------|----------------|----------------|--------|-----------|--------|

|       |                              | (                    | STASI, ST | ASO)   |                | (STASI, STASO) |        |           |        |

|       |                              | (0, 0)               | (1, 1)    | (1, 0) | (0, 1)         | (0, 0)         | (1, 1) | (1, 0)    | (0, 1) |

| BCLK  | オーディオ・シリアル用ビッ<br>ト同期クロック入出力  | IN<br>(internal:Low) | IN        | IN     | IN             | Low            | OUT    | OUT       | OUT    |

| LRCLK | オーディオ・シリアル用フ<br>レーム同期クロック入出力 | IN<br>(internal:Low) | IN        | IN     | IN             | Low            | OUT    | OUT       | OUT    |

| ASI   | オーディオ・シリアル用デー<br>タ入力         | -                    | IN        | IN     | -              | -              | IN     | IN        | -      |

| ASO   | オーディオ・シリアル用デー<br>タ出力         | Hi-Z                 | OUT       | Hi-Z   | OUT            | Hi-Z           | OUT    | Hi-Z      | OUT    |

本ブロック使用時の注意事項は次のとおりです。

- ・本ブロックが動作するためには PLL が動作している必要があります。

- ・IIS モード選択時は, LRCLK レジスタ=ハイ・レベル, SLR レジスタ=ハイ・レベルを選択してください。

- ・ASI から入力されたデータをサラウンド処理する場合 , サンプリング周波数を 32/44.1 kHz にする必要があります。

# 5.6 オーディオ再生ディジタル・ゲイン調整プロック

図 5-7 オーディオ再生ディジタル・ゲイン・ブロック

本ブロックは,次の機能を持っています。

- ・オーディオ・シリアル・インタフェースからの 8/16/32/44.1/48 kHz サンプリング・ステレオ・リニア PCM フォーマットのディジタル入力に対して,ディジタル・ゲイン調整を行います。

- ・音源からの 32 kHz サンプリング・ステレオ・リニア PCM フォーマットのディジタル入力に対して,ディジタル・ゲイン調整を行います。

- ・上記ディジタル・ゲイン調整後の信号について、ディジタル・ミキシングを行います。

- ・ディジタル・ミキシング後の信号を, Audio DAC およびオーディオ・シリアル・インタフェースへ出力します。

- ・本ブロックの電源は DVDD です。

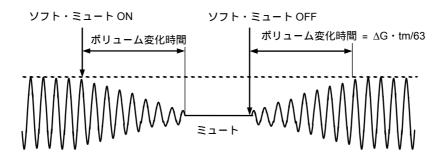

本ブロックは,STADIG レジスタ=ハイ・レベルで動作します。ゲイン調整部では,各ディジタル信号入力に対して,係数を乗算することで,ゲイン調整を行います。また,ゲインを徐々に変化させることで,異音を目立たなくするソフト・ミュート機能があります。

表 5-5 ディジタル・ゲイン調整

| ブロック   | 設定アドレス | 調整範囲                                |

|--------|--------|-------------------------------------|

| AULDG  | 13H    | ミュート,+12 dB~0 dB~ - 63 dB/1 dB ステップ |

| AURDG  | 14H    | ミュート,+12 dB~0 dB~ - 63 dB/1 dB ステップ |

| MELLDG | 11H    | ミュート,+12 dB~0 dB~ - 63 dB/1 dB ステップ |

| MELRDG | 12H    | ミュート,+12 dB~0 dB~ - 63 dB/1 dB ステップ |

本ブロック使用時の注意事項は次のとおりです。

・本ブロックが動作するには,PLLが安定して動作している必要があります。

# 5.7 オーディオ再生アナログ・ブロック

# 図 5-8 オーディオ再生アナログ・ブロック

本ブロックは次の機能を持っています。

- ・Digital mixing から出力されたディジタル信号を Audio DAC にて D/A 変換を行い, 出力されたアナログ信号を アナログ・ゲイン調整します。

- ・ゲイン調整した信号を LINEOL 端子, LINEOR 端子からライン出力します。

- ・本ブロックの電源は AVDD です。

本プロックは, STADAC レジスタ=ハイ・レベルで動作します。ゲイン調整部では, Audio DAC 出力に対し, アナログ回路でゲイン調整を行います。L ch, R ch のゲインは個別に設定可能です。

表 5-6 アナログ・ゲイン調整

| ブロック      | 設定アドレス | 調整範囲                      |

|-----------|--------|---------------------------|

| ADACLVRGA | 17H    | ミュート,0~-45 dB/1.5 dB ステップ |

| ADACRVRGA | 18H    | ミュート,0~-45 dB/1.5 dB ステップ |

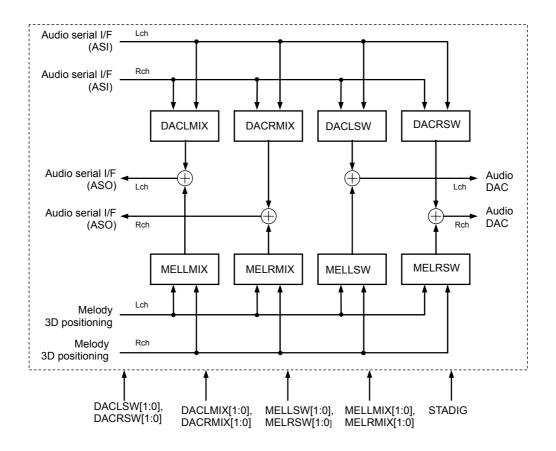

# 5.8 ディジタル・ミキシング部

### 図 5-9 ディジタル・ミキシング・ブロック

本ブロックは次の機能を持っています。

- ・オーディオ・シリアル・インタフェースからのディジタル入力信号,音源からのディジタル出力信号をミキシングします(ミキシングは fs = 32 kHz 時のみ可能)。

- ・ミキシングされたディジタル・データを, ASIO ブロック, Audio DAC ブロックへ出力します。

- ・各セレクタは,スルー(Lch Lch,Rch Rch),チャネル反転(Lch Rch,Rch Lch),モノラル 化(Lch Lch + Rch,Rch Lch + Rch),ミュート(Lch ×,Rch ×)の選択が可能です。 なおモノラル化の場合は,Lch.Rchのゲインを 1/2 にした後加算となります。

- ・本ブロックの電源は DVDD です。

本ブロックは, STADIG レジスタ=ハイ・レベルで動作します。

# 表 5-7 セレクタ設定

| ブロック    | 初期設定 | 設定パス                  |

|---------|------|-----------------------|

| DACLSW  | スルー  | ASI - Audio DAC 間パス設定 |

| DACRSW  | スルー  | ASI - Audio DAC 間パス設定 |

| MELLSW  | スルー  | 音源 - Audio DAC 間パス設定  |

| MELRSW  | スルー  | 音源 - Audio DAC 間パス設定  |

| DACLMIX | ミュート | ASI - ASO 間パス設定       |

| DACRMIX | ミュート | ASI - ASO 間パス設定       |

| MELLMIX | ミュート | 音源 - ASO 間パス設定        |

| MELRMIX | ミュート | 音源 - ASO 間パス設定        |

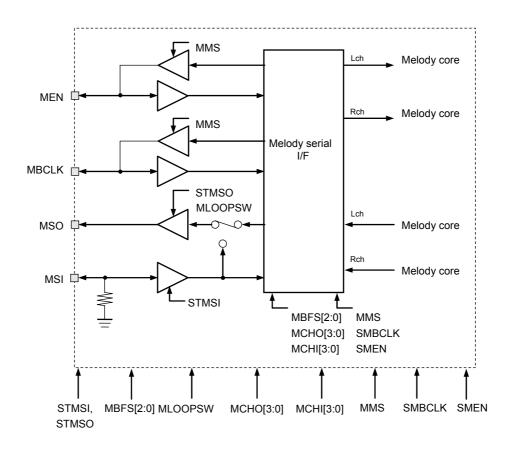

# 5.9 音源コア外部接続専用シリアル・インタフェース (MSIO)

本ブロックは次の機能を持っています。

- ・MSIより入力されたシリアル・データをパラレル・データに変換し,音源コア部へ出力します。

- ・音源コア部より入力されたパラレル・データをシリアル・データに変換し, MSO から出力します。

- ・サンプリング周波数は32 kHz 固定です。

- ・レジスタ設定により、MBCLKの周波数を変更可能(ディフォールト:64 fs)です。

- ・レジスタ設定により, MSI 入力データ, MSO 出力データの有効データ数を個別に設定可能です。

- ・レジスタ設定により, MSI MSO 間でデータのループバックが可能です。

- ・レジスタ設定により,スレーブ・モード(ディフォールト),マスタ・モードの設定が可能です。

- ・レジスタ設定により,フレーム同期モード(ディフォールト),LRステレオ・モードの設定が可能です。

- ・レジスタ設定により、ビット・クロック MBCLK を反転可能です。

- ・本ブロックの電源は DVDD です。

本ブロックはレジスタ STMSI, STMSO により動作します。詳細は表 5-8をご覧ください。

### 表 5-8 MSIO 状態表

| 端子名   | 機能                          | MMS = 0              | MMS = 1(マスタ・モード) |              |        |        |                |        |        |  |

|-------|-----------------------------|----------------------|------------------|--------------|--------|--------|----------------|--------|--------|--|

|       |                             | (5                   | STMSI, ST        | TMSI, STMSO) |        |        | (STMSI, STMSO) |        |        |  |

|       |                             | (0, 0)               | (1, 1)           | (1, 0)       | (0, 1) | (0, 0) | (1, 1)         | (1, 0) | (0, 1) |  |

| MBCLK | 音源コア外部接続専用ビット<br>同期クロック入出力  | IN<br>(internal:Low) | IN               | IN           | IN     | Low    | OUT            | OUT    | OUT    |  |

| MEN   | 音源コア外部接続専用フレー<br>ム同期クロック入出力 | IN<br>(internal:Low) | IN               | IN           | IN     | Low    | OUT            | OUT    | OUT    |  |

| MSI   | 音源コア外部接続専用データ<br>入力         | -                    | IN               | IN           | -      | -      | IN             | IN     | -      |  |

| MSO   | 音源コア外部接続専用データ<br>出力         | Hi-Z                 | OUT              | Hi-Z         | OUT    | Hi-Z   | OUT            | Hi-Z   | OUT    |  |

本ブロック使用時の注意事項については次に示します。

### 5.9.1 MSIO 使用時の注意事項

MSIO は, ASIO と同じくスレーブ・モード, マスタ・モードでの動作が可能です。

ASIO と MSIO を同時に使用する場合には,本 LSI 内部のフレーム信号を統一する必要があるため,ASIO はマスタ・モードのみ使用可能となります。

また, それぞれの使用状態において, 次の記制限事項が加わります。

- (1) ASIO を単独, かつマスタ・モードで使用する場合は, BFS の設定値は 64 fs, 32 fs のみです。

- (2) MSIO を単独, かつマスタ・モードで使用する場合は, MBFS の設定値は32 fs, 64 fs, 128 fs, 256 fs のみです

- (3) ASIO, MSIO の両方を使用する場合は, ASIO はマスタ・モードのみ使用可能となります。

- (4) 上記 (1),(2),(3) のいずれの場合も, BFS, MBFS に無効な値が設定された場合, それぞれディフォールト値が設定されます。

# 6. レジスタ (音源以外のレジスタ)

音源部を除くレジスタの説明を表 6-1に示します。ここに設定されていないレジスタに書き込むことはできません。

表 6-1 コントロール・レジスタ

|     |     |        |          |                  |                   |              |              | l            |              |     |                        |           |

|-----|-----|--------|----------|------------------|-------------------|--------------|--------------|--------------|--------------|-----|------------------------|-----------|

| アド  | R/W | D7     | D6       | D5               | D4                | D3           | D2           | D1           | D0           | 初期値 | 機能                     | レジスタ名     |

| レス  |     |        |          |                  |                   |              |              |              |              |     |                        |           |

| 00H | R/W | STADIG | STPLL2   | STPLL1           | STASI             | STASO        | STSYNTH      | STADAC       | STREF        | 00H | LSI スタンバイ設定            | STNBY     |

| 01H | R/W | 0      |          |                  |                   | MCLK1A[6:0]  | ]            |              |              | 1CH | マスタ・クロック設定 1           | MCLK1A    |

| 02H | R/W |        |          | 1                | MCLK <sup>-</sup> | 1B[7:0]      |              |              |              | 80H | マスタ・クロック設定 1           | MCLK1B    |

| 03H | R/W | 0      | 0        | 0                |                   |              | MCLK2A[4:0   | ]            |              | 02H | マスタ・クロック設定 2           | MCLK2A    |

| 04H | R/W |        |          | 1                | MCLK              | 2B[7:0]      | i            | i            | i            | 2AH | マスタ・クロック設定 2           | MCLK2B    |

| 05H | R/W | 0      | 0        | 0                | 0                 | 0            | 0            | CSTRTEN      | MCLKSEL      | 00H | クロック切り替え               | MCLKSEL   |

| 06H | R/W |        |          |                  |                   |              |              |              |              | 不定  | Reserved               | Reserved  |

| 07H | R/W |        |          | BFS[4:0]         |                   |              |              | FS[2:0]      |              | 00H | FS, BCLK セレクト          | SEL_FS    |

| 08H | R/W | 0      | 0        | EX3DAEN          | AULOOPSW          | SLR          | AMS          | ASIM         | LRCLK        | 00H | ASI                    | SEL_ASI   |

| 09H | R/W | DACLN  | 1IX[1:0] | DACR             | MIX[1:0]          | DACLS        | SW[1:0]      | DACRS        | SW[1:0]      | F0H | ミキシング・パス 1             | MIXING1   |

| 0AH | R/W | MELLM  | 1IX[1:0] | MELRA            | ИIX[1:0]          | MELLS        | SW[1:0]      | MELRS        | SW[1:0]      | F0H | ミキシング・パス 2             | MIXING2   |

| 0BH | R/W | 0      | 0        | 0                | 0                 | 0            | PCMLSW       | 0            | PCMRSW       | 00H | ミキシング・パス 3             | MIXING3   |

| 0CH | R/W |        |          |                  |                   |              |              |              |              | 不定  | Reserved               | Reserved  |

| 0DH | R/W | 0      | 0        | 0                | 0                 | 0            | 0            | VIB          | LED          | 00H | LED, VIB 出力の設定         | LEDVIB    |

| 0EH | R/W | 0      | 0        | 0                | 0                 | POUT3        | POUT2        | POUT1        | POUT0        | 00H | 汎用ポート外部出力設定            | POUT      |

| 0FH | R/W |        |          |                  |                   |              |              |              |              |     | Reserved               | Reserved  |

| 10H | R/W | 0      | 0        | 0                | 0                 | SLOP         | E[1:0]       | AUSMUTE      | MELSMUTE     | 00H | ソフト・ミュート               | SMUTE     |

| 11H | R/W | MELLD  | G2[1:0]  |                  |                   | ı            | G1[5:0]      |              |              | FFH | ADAC ディジタル・ゲイン/        | MELLDG    |

|     |     |        |          |                  |                   |              |              |              |              |     | パス                     |           |

| 12H | R/W | MELRD  | G2[1:0]  |                  |                   | MELRD        | G1[5:0]      |              |              | FFH | ADAC ディジタル・ゲイン/        | MELRDG    |

|     |     |        |          |                  |                   |              |              |              |              |     | パス                     |           |

| 13H | R/W | AULDO  | G2[1:0]  |                  |                   | AULDO        | G1[5:0]      |              |              | FFH | ADAC ディジタル・ゲイン/        | AULDG     |

|     |     |        |          |                  |                   |              |              |              |              |     | パス                     |           |

| 14H | R/W | AURDO  | G2[1:0]  |                  |                   | AURD         | G1[5:0]      |              |              | FFH | ADAC ディジタル・ゲイン/        | AURDG     |

|     |     |        |          |                  | <del>i</del>      | <del>i</del> | <del>i</del> | <del>i</del> | <del>i</del> |     | パス                     |           |

| 15H | R/W |        |          |                  |                   |              |              |              |              |     | Reserved               | Reserved  |

| 16H | R/W |        |          |                  |                   |              |              |              |              |     | Reserved               | Reserved  |

| 17H | R/W | 0      | 0        | 0                |                   | AE           | ACLVRGA[4    | 1:0]         |              | 1FH | ADAC アナログ・ゲイン          | ADACLVR   |

| 18H | R/W | 0      | 0        | 0                |                   | AD           | ACRVRGA[4    | 4:0]         |              | 1FH | ADAC アナログ・ゲイン          | ADACRVR   |

| 20H | R/W | 0      | 0        | 0                | 0                 | 0            | 0            | STMSI        | STMSO        | 00H | LSI スタンバイ設定(MSIO       | STNBY2    |

|     |     |        |          |                  |                   |              |              |              |              |     | 時)                     |           |

| 21H | R/W | 0      |          | MBFS[2:0] MLOOPS |                   |              | MMS          | SMEN         | SMBCLK       | 10H | MSIO                   | SEI_MSIO1 |

| 22H | R/W |        | MCH      | II[3:0]          |                   |              | MCHO[3:0]    |              |              | 33H | MSIO                   | SEL_MSIO2 |

| 3FH | R   | 1      | 0        | 1                | 1                 |              | VER          | R[3:0]       |              | 不定  | LSIバージョン               | LSIVER    |

| 7CH | R/W | 0      | 0        | 0                | 0                 | 0            | 0            | BANK1        | BANK0        | 00H | BANK 切り替え <sup>注</sup> | BANK      |

注 シリアル・モード時のみです。

# 6.1 スタンパイ設定 (STNBY)

スタンバイ・モードの設定を行います。

アドレス: 00H, レジスタ名: STNBY, ブロック:全体, アクセス: R/W, 初期値: 00H

| D7     | D6     | D5     | D4    | D3    | D2      | D1     | D0    |

|--------|--------|--------|-------|-------|---------|--------|-------|

| STADIG | STPLL2 | STPLL1 | STASI | STASO | STSYNTH | STADAC | STREF |

### 6. 1. 1 STADIG

| データ | モード      | 初期値 | 説明                      |

|-----|----------|-----|-------------------------|

| 0   | Stand-by | 0   | オーディオ・ディジタル・プロック部のスタンバイ |

| 1   | ON       |     | 通常動作                    |

### 6. 1. 2 STPLL2

スタンバイ・モード中, PLL2出力はクロック供給を停止します。

| データ | モード      | 初期値 | 説明          |

|-----|----------|-----|-------------|

| 0   | Stand-by | 0   | PLL2 のスタンバイ |

| 1   | ON       |     | 通常動作        |

### 6. 1. 3 STPLL1

スタンバイ・モード中, PLL1 出力はクロック供給を停止します。

| データ | モード      | 初期値 | 説明          |

|-----|----------|-----|-------------|

| 0   | Stand-by | 0   | PLL1 のスタンバイ |

| 1   | ON       |     | 通常動作        |

# 6. 1. 4 STASI

| データ | モード      | 初期値 | 説明                                  |

|-----|----------|-----|-------------------------------------|

| 0   | Stand-by | 0   | ASI ( オーディオ・シリアル・インタフェース入力 ) のスタンバイ |

| 1   | ON       |     | 通常動作                                |

### 6. 1. 5 STASO

LRCLKおよびBCLKの動作は、STASIとSTASO両方のビットをスタンバイにしたときのみスタンバイとなります。 詳しくは表 5 - 4 ASIO 状態表を参照してください。

| データ | モード      | 初期値 | 説明                              |

|-----|----------|-----|---------------------------------|

| 0   | Stand-by | 0   | ASO(オーディオ・シリアル・インタフェース出力)のスタンバイ |

| 1   | ON       |     | 通常動作                            |

# 6. 1. 6 STSYNTH

| データ | モード      | 初期値 | 説明                        |

|-----|----------|-----|---------------------------|

| 0   | Stand-by | 0   | 音源プロック(Synthesizer)のスタンバイ |

| 1   | ON       |     | 通常動作                      |

# 6. 1. 7 STADAC

| データ | モード      | 初期値 | 説明                    |

|-----|----------|-----|-----------------------|

| 0   | Stand-by | 0   | オーディオ DAC ブロック部のスタンバイ |

| 1   | ON       |     | 通常動作                  |

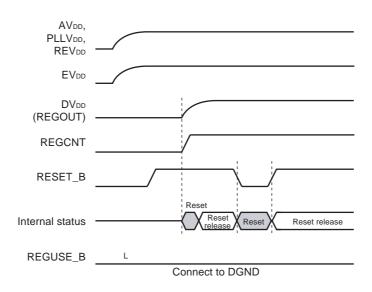

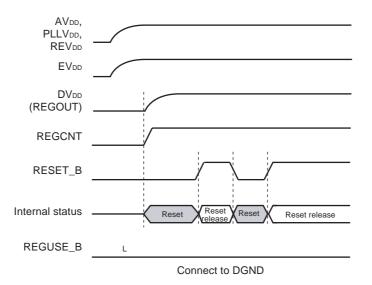

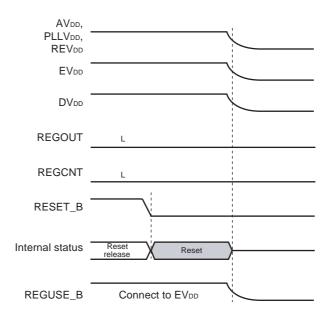

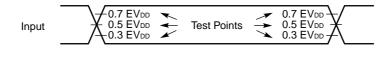

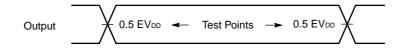

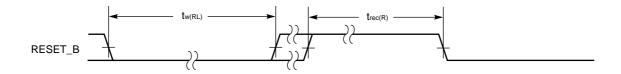

# 6. 1. 8 STREF