# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

MOS**集積回路** MOS Integrated Circuit

# $\mu$ PD78F0988

# 8 ビット・シングルチップ・マイクロコンピュータ

$\mu$  PD78F0988は,78K/0シリーズの中の  $\mu$  PD780988サブシリーズの製品で, $\mu$  PD780988の内部ROMを,フラッシュ・メモリに置き換えたものです。基板に実装した状態で電気的に書き込み,消去が可能なため,システム開発時の評価用,少量生産用,また,頻繁なバージョン・アップが予想されるシステムに最適です。

詳しい機能説明などは次のユーザーズ・マニュアルに記載しております。設計の際には必ずお読みください。

μPD780988サプシリーズ ユーザーズ・マニュアル: U13029J 78K/0シリーズ ユーザーズ・マニュアル 命令編 : U12326J

#### 特徵

マスクROM製品とピン・コンパチブル(Vpp端子を除く)

フラッシュ・メモリ:60 Kバイト<sup>注1</sup>

内部高速RAM : 1024バイト 内部拡張RAM : 1024バイト<sup>注2</sup>

マスクROM製品と同じ電源電圧で動作可能(VDD=4.0~5.5 V)

注1.メモリ・サイズ切り替えレジスタ(IMS)により,フラッシュ・メモリ容量の変更可能

2.内部拡張RAMサイズ切り替えレジスタ(IXS)により,内部拡張RAM容量の変更可能

**備考** フラッシュ・メモリ製品とマスクROM製品の違いについては , **1** . μ PD78F0988**とマスク**ROM**製品の違い**を 参照してください。

#### オーダ情報

オーダ名称 パッケージ μ PD78F0988CW 64ピン・プラスチック・シュリンクDIP ( 750 mil ) μ PD78F0988GC-AB8 64ピン・プラスチックQFP ( 14 mm )

本資料は,この製品の企画段階で作成していますので,予告なしに内容を変更することがあります。 また本資料で扱う製品の製品化を中止することがあります。

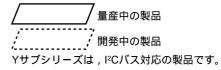

#### ★ 78K/0シリーズの展開

78K/0シリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

各サブシリーズ間の主な機能の違いを次に示します。

|         | 機能          | ROM容量     |       | タイ     | イマ  |     | 8-bit | 10-bit | 8-bit | シリアル・             | I/O | VDD   | 外部       |

|---------|-------------|-----------|-------|--------|-----|-----|-------|--------|-------|-------------------|-----|-------|----------|

| サブシリー   | -ズ名         |           | 8-bit | 16-bit | 時計  | WDT | A/D   | A/D    | D/A   | インタフェース           |     | MIN.值 | 拡張       |

| 制御用     | μ PD78075B  | 32 K-40 K | 4ch   | 1ch    | 1ch | 1ch | 8ch   | -      | 2ch   | 3ch( UART:1ch )   | 88本 | 1.8 V |          |

|         | μ PD78078   | 48 K-60 K |       |        |     |     |       |        |       |                   |     |       |          |

|         | μ PD78070A  | -         |       |        |     |     |       |        |       |                   | 61本 | 2.7 V |          |

|         | μ PD780058  | 24 K-60 K | 2ch   |        |     |     |       |        |       | 3ch( 時分割UART:1ch) | 68本 | 1.8 V |          |

|         | μ PD78058F  | 48 K-60 K |       |        |     |     |       |        |       | 3ch( UART:1ch )   | 69本 | 2.7 V |          |

|         | μ PD78054   | 16 K-60 K |       |        |     |     |       |        |       |                   |     | 2.0 V |          |

|         | μ PD780065  | 40 K-48 K |       |        |     |     |       |        | -     | 4ch( UART:1ch )   | 60本 | 2.7 V |          |

|         | μ PD780078  | 48 K-60K  |       | 2ch    |     |     | _     | 8ch    |       | 3ch( UART:2ch )   | 52本 | 1.8 V |          |

|         | μ PD780034A | 8 K-32 K  |       | 1ch    |     |     |       |        |       | 3ch( UART:1ch )   | 51本 |       |          |

|         | μ PD780024A |           |       |        |     |     | 8ch   | -      |       |                   |     |       |          |

|         | μ PD78014H  |           |       |        |     |     |       |        |       | 2ch               | 53本 |       |          |

|         | μ PD78018F  | 8 K-60 K  |       |        |     |     |       |        |       |                   |     |       |          |

|         | μ PD78083   | 8 K-16 K  |       | -      | _   |     |       |        |       | 1ch( UART:1ch )   | 33本 |       | -        |

| インバータ   | μ PD780988  | 16 K-60 K | 3ch   | 注      | _   | 1ch | _     | 8ch    | -     | 3ch( UART:2ch )   | 47本 | 4.0 V |          |

| 制御用     |             |           |       |        |     |     |       |        |       |                   |     |       |          |

| FIP     | μ PD780208  | 32 K-60 K | 2ch   | 1ch    | 1ch | 1ch | 8ch   | -      | -     | 2ch               | 74本 | 2.7 V | -        |

| 駆動用     | μ PD780228  | 48 K-60 K | 3ch   | _      | _   |     |       |        |       | 1ch               | 72本 | 4.5 V |          |

|         | μ PD780232  | 16 K-24 K |       |        |     |     | 4ch   |        |       | 2ch               | 40本 |       |          |

|         | μ PD78044H  | 32 K-48 K | 2ch   | 1ch    | 1ch |     | 8ch   |        |       | 1ch               | 68本 | 2.7 V |          |

|         | μ PD78044F  | 16 K-40 K |       |        |     |     |       |        |       | 2ch               |     |       |          |

| LCD     | μ PD780308  | 48 K-60 K | 2ch   | 1ch    | 1ch | 1ch | 8ch   | -      | -     | 3ch( 時分割UART:1ch) | 57本 | 2.0 V | -        |

| 駆動用     | μ PD78064B  | 32 K      |       |        |     |     |       |        |       | 2ch( UART:1ch )   |     |       |          |

|         | μ PD78064   | 16 K-32 K |       |        |     |     |       |        |       |                   |     |       |          |

| Call ID | μ PD780841  | 24 K-32 K | 2ch   | _      | 1ch | 1ch | 2ch   | -      | -     | 2ch( UART:1ch )   | 61本 | 2.7 V | -        |

| 対応      |             |           |       |        |     |     |       |        |       |                   |     |       |          |

| バス・イン   | μ PD780948  | 60 K      | 2ch   | 2ch    | 1ch | 1ch | 8ch   | -      | -     | 3ch( UART:1ch )   | 79本 | 4.0 V |          |

| タフェース   | μ PD78098B  | 40 K-60 K |       | 1ch    |     |     |       |        | 2ch   |                   | 69本 | 2.7 V | -        |

| 対応      | μ PD780814  | 32 K-60 K |       | 2ch    |     |     | 12ch  |        | -     | 2ch( UART:1ch )   | 46本 | 4.0 V |          |

| メータ     | μ PD780958  | 48 K-60 K | 4ch   | 2ch    | -   | 1ch | -     | -      | -     | 2ch( UART:1ch )   | 69本 | 2.2 V | -        |

| 制御用     | μ PD780973  | 24 K-32 K | 3ch   | 1ch    | 1ch |     | 5ch   |        |       |                   | 56本 | 4.5 V | 1        |

|         | μ PD780824  | 32 K-60 K |       |        |     |     |       |        |       |                   | 59本 | 4.0 V | <u> </u> |

|         | μ PD780955  | 40 K      | 6ch   | 1      | -   | 1   | 1ch   | 1      |       | 2ch( UART:2ch )   | 50本 | 2.2 V | 1        |

注 16ビット・タイマ: 2チャネル 10ビット・タイマ: 1チャネル

## 機能概要

| I              | 頁 目       | 機能                                                       |  |  |  |

|----------------|-----------|----------------------------------------------------------|--|--|--|

| 内部メモリ          | フラッシュ・メモリ | 60 Kバイト <sup>注 1</sup>                                   |  |  |  |

|                | 高速RAM     | 1024バイト                                                  |  |  |  |

|                | 拡張RAM     | 1024バイト <sup>注2</sup>                                    |  |  |  |

| メモリ空間          |           | 64 Kバイト                                                  |  |  |  |

| 汎用レジスタ         |           | 8 ビット×32レジスタ(8 ビット×8 レジスタ×4 バンク)                         |  |  |  |

| インストラクション・サイクル |           | 命令実行時間の可変機能内蔵                                            |  |  |  |

|                |           | 0.24 μs/0.48μs/0.96μs/1.9μs/3.8μs(システム・クロック:8.38 MHz動作時) |  |  |  |

| 命令セット          |           | ・16ビット演算                                                 |  |  |  |

|                |           | ・乗除算(8ビット×8ビット,16ビット÷8ビット)                               |  |  |  |

|                |           | ・ビット操作(セット,リセット,テスト,プール演算)                               |  |  |  |

|                |           | ・BCD補正など                                                 |  |  |  |

| I/Oポート         |           | 合計 : 47本                                                 |  |  |  |

|                |           | · CMOS入力 : 8本                                            |  |  |  |

|                |           | ・CMOS入出力:39本                                             |  |  |  |

| リアルタイム出力       | ]ポート      | ・8 ビット× 1 または 4 ビット× 2                                   |  |  |  |

|                |           | ・6 ビット× 1 または 4 ビット× 1                                   |  |  |  |

| A/Dコンバータ       |           | ・10ビット分解能×8チャネル                                          |  |  |  |

|                |           | ・電源電圧:AVDD = 4.0~5.5 V                                   |  |  |  |

| シリアル・インタ       | 7フェース     | ・UARTモード:2チャネル                                           |  |  |  |

|                |           | ・ 3 線式シリアルI/Oモード: 1 チャネル                                 |  |  |  |

| タイマ            |           | ・16ビット・タイマ / イベント・カウンタ: 2 チャネル                           |  |  |  |

|                |           | ・8 ビット・タイマ / イベント・カウンタ :3 チャネル                           |  |  |  |

|                |           | ・10ビット・インバータ制御用タイマ : 1 チャネル                              |  |  |  |

|                |           | ・ウォッチドッグ・タイマ : 1 チャネル                                    |  |  |  |

| タイマ出力          |           | 11本(汎用出力:5本,インバータ制御用出力:6本)                               |  |  |  |

| ベクタ割り込み        | マスカブル     | 内部:16,外部:8                                               |  |  |  |

| 要因             | ノンマスカブル   | 内部: 1                                                    |  |  |  |

|                | ソフトウエア    | 1                                                        |  |  |  |

| 電源電圧           |           | V <sub>DD</sub> = 4.0 ~ 5.5 V                            |  |  |  |

| 動作周囲温度         |           | T <sub>A</sub> = -40 ~ +85                               |  |  |  |

| パッケージ          |           | ・64ピン・プラスチック・シュリンクDIP(750 mil)                           |  |  |  |

|                |           | ・64ピン・プラスチックQFP( 14 mm)                                  |  |  |  |

- 注1.メモリ・サイズ切り替えレジスタ (IMS)により, フラッシュ・メモリ容量の変更可能。

- 2.内部拡張RAMサイズ切り替えレジスタ(IXS)により,内部拡張RAM容量の変更可能。

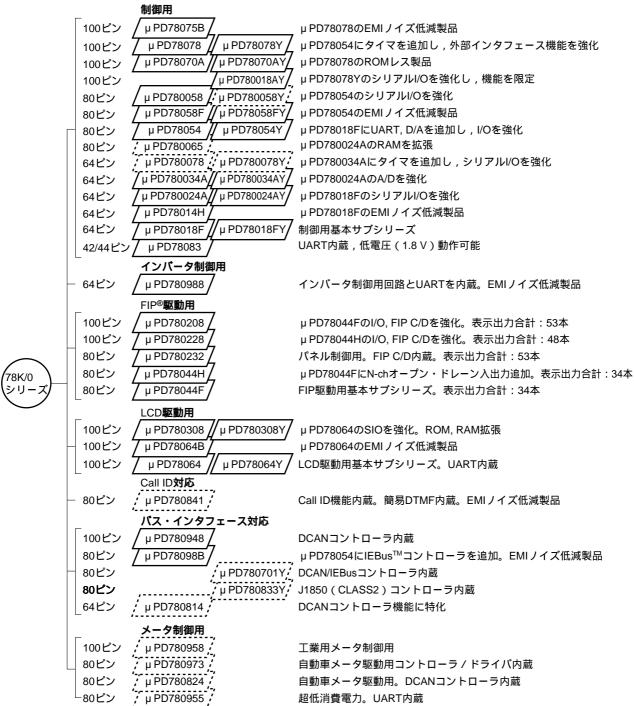

#### 端子接続図 (Top View)

・64ピン・プラスチック・シュリンクDIP (750 mil)

μ PD78F0988CW

★ 注意 通常動作モード時は , Vpp端子はVssoに直接接続してください。

**備考** マイコン内部から発生するノイズを低減する必要がある応用分野で使用する場合, VDDOとVDD1に個別の電源を供給し, VSSOとVSS1を別々のグランド・ラインに接続するなどのノイズ対策を行うことを推奨します。

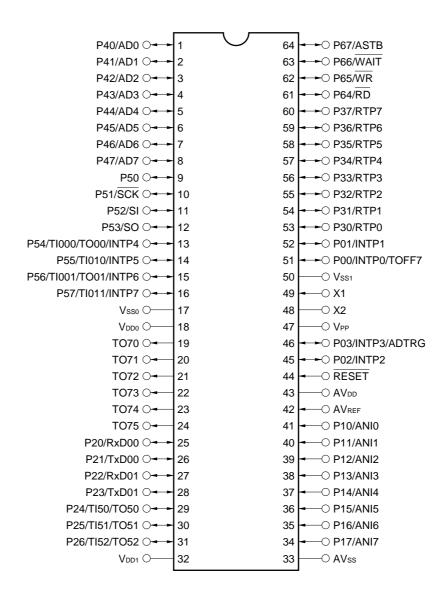

## ・64ピン・プラスチックQFP ( 14 mm)

µ PD78F0988GC-AB8

- ★ 注意 通常動作モード時は , Vpp端子はVssoに直接接続してください。

- **備考** マイコン内部から発生するノイズを低減する必要がある応用分野で使用する場合, VDDOとVDD1に個別の電源を供給し, VSSOとVSS1を別々のグランド・ラインに接続するなどのノイズ対策を行うことを推奨します。

6

AD0-AD7 : Address/Data Bus RxD00, RxD01 : Receive Data

ADTRG : AD Trigger Input SCK : Serial Clock

ANI0-ANI7 : Analog Input SI : Serial Input

ASTB : Address Strobe SO : Serial Output

AVDD : Analog Power Supply TI000, TI001,

AVREF : Analog Reference Voltage TI010, TI011,

AVss : Analog Ground TI50-TI52 : Timer Input

INTP0-INTP7 : External Interrupt Input TO00, TO01, P00-P03 : Port0 TO50-TO52,

P10-P17

: Port1

TO70-TO75

: Timer Output

P20-P26

: Port2

TOFF7

: Timer Output Off

P30-P37

: Port3

TxD00, TxD01

: Transmit Data

P40-P47

: Port4

VDD0, VDD1

: Power Supply

P50-P57 : Port5 VPP : Programming Power Supply

P64-P67 : Port6  $V_{SS0}$ ,  $V_{SS1}$  : Ground  $\overline{RD}$  : Read Strobe  $\overline{WAIT}$  : Wait

RESET : Reset WR : Write Strobe

RTP0-RTP7 : Real-time Port X1, X2 : Crystal

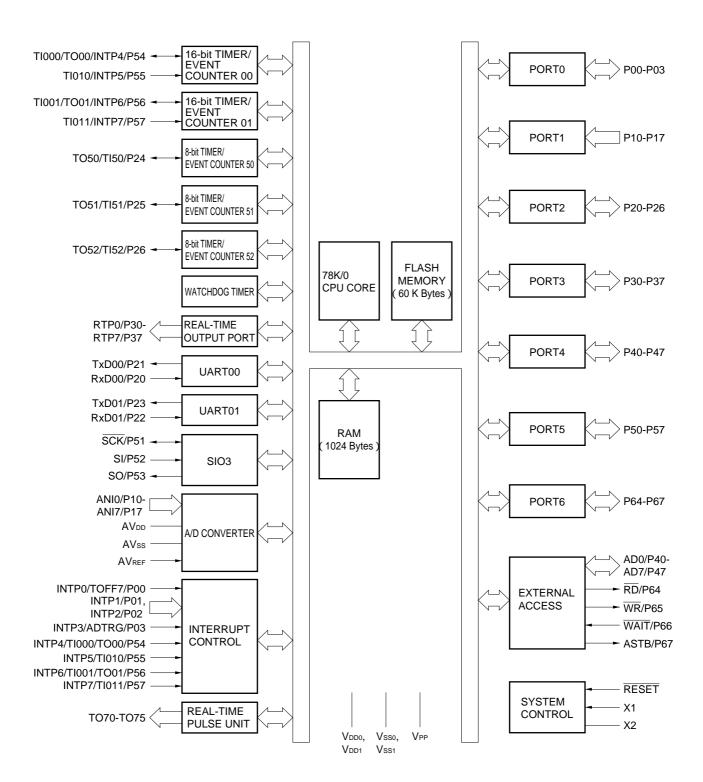

#### ブロック図

# 目 次

- 1. μPD78F0988とマスクROM製品の違い ... 10

- 2. 端子機能一覧 ... 11

- 2.1 ポート端子 ... 11

- 2.2 ポート以外の端子 ... 12

- 2.3 端子の入出力回路と未使用端子の処理 ... 14

- 3.メモリ・サイズ切り替えレジスタ (IMS) ... 16

- **4.内部拡張**RAM**サイズ切り替えレジスタ (**IXS ) ... 17

- 5.フラッシュ・メモリ・プログラミング ... 18

- 5.1 通信方式の選択 ... 18

- 5.2 フラッシュ・メモリ・プログラミングの機能 ... 19

- 5.3 Flashpro , の接続 ... 19

- ★ **6.電気的特性** ... 21

- 7.外形図 ... 36

- 付録A.開発ツール ... 38

- **付録 B . 関連資料** ... 41

#### 1. μ PD78F0988とマスクROM製品の違い

μPD78F0988は,基板に実装した状態でプログラムの書き込み,消去,再書き込み可能なフラッシュ・メモリを内蔵した製品です。

メモリ・サイズ切り替えレジスタ(IMS),内部拡張RAMサイズ切り替えレジスタ(IXS)の設定により,フラッシュ・メモリ仕様以外の機能をマスクROM製品と同一にできます。

★ 表 1 - 1 にフラッシュ・メモリ製品(μ PD78F0988)とマスクROM製品(μ PD780982, 780983, 780984, 780986, 780988) の違いを示します。

▶ 表 1 - 1 μPD78F0988とマスクROM製品の違い

| 項目                   | μ PD78F0988 | マスクROM製品            |

|----------------------|-------------|---------------------|

| 内部ROM構造              | フラッシュ・メモリ   | マスクROM              |

| 内部ROM容量              | 60 Kバイト     | μPD780982:16 Κバイト   |

|                      |             | μ PD780983:24 Kバイト  |

|                      |             | μPD780984:32 Kバイト   |

|                      |             | μPD780986 : 48 Kバイト |

|                      |             | μPD780988:60 Kバイト   |

| 内部拡張RAM容量            | 1024バイト     | μPD780982:なし        |

|                      |             | μPD780983:なし        |

|                      |             | μPD780984:なし        |

|                      |             | μPD780986 : 1024バイト |

|                      |             | μPD780988:1024バイト   |

| メモリ・サイズ切り替えレジスタ(IMS) | 可注1         | 不可                  |

| による内部ROM容量の変更        |             |                     |

| 内部拡張RAMサイズ切り替えレジスタ   | 可注2         | 不可                  |

| (IXS)による内部拡張RAM容量の変更 |             |                     |

| TEST端子               | なし          | あり                  |

| Vpp端子                | あり          | なし                  |

注1. RESET入力により, フラッシュ・メモリ容量は60 Kバイトとなります。

注意 フラッシュ・メモリ製品とマスクROM製品では,ノイズ耐量やノイズ輻射が異なります。試作から量産の過程でフラッシュ・メモリ製品からマスクROM製品への置き換えを検討される場合は,マスクROM製品のCS製品(ES製品でなく)で十分に評価してください。

<sup>2.</sup> RESET 入力により,内部拡張RAM容量は0バイトとなります。

# 2.端子機能一覧

# 2.1 ポート端子

| 端子名称    | 入出力 | 機能                             | リセット時 | 兼用端子            |

|---------|-----|--------------------------------|-------|-----------------|

| P00     | 入出力 | ポート0。                          | 入力    | INTP0/TOFF7     |

| P01     |     | 4 ビット入出力ポート。                   |       | INTP1           |

| P02     |     | 1 ビット単位で入力 / 出力の指定可能。          |       | INTP2           |

| P03     |     | ソフトウエアにより,内蔵プルアップ抵抗を使用可能。      |       | INTP3/ADTRG     |

| P10-P17 | 入力  | ポート1。                          | 入力    | ANI0-ANI7       |

|         |     | 8 ビット入力専用ポート。                  |       |                 |

| P20     | 入出力 | ポート2。                          | 入力    | RxD00           |

| P21     |     | 7 ビット入出力ポート。                   |       | TxD00           |

| P22     |     | 1 ビット単位で入力 / 出力の指定可能。          |       | RxD01           |

| P23     |     | ソフトウエアにより,内蔵プルアップ抵抗を使用可能。      |       | TxD01           |

| P24     |     |                                |       | TI50/TO50       |

| P25     |     |                                |       | TI51/TO51       |

| P26     |     |                                |       | TI52/TO52       |

| P30-P37 | 入出力 | ポート3。                          | 入力    | RTP0-RTP7       |

|         |     | 8 ビット入出力ポート。                   |       |                 |

|         |     | 1 ビット単位で入力 / 出力の指定可能。          |       |                 |

|         |     | ソフトウエアにより,内蔵プルアップ抵抗を使用可能。      |       |                 |

| P40-P47 | 入出力 | ポート4。                          | 入力    | AD0-AD7         |

|         |     | 8 ビット入出力ポート。                   |       |                 |

|         |     | 1 ビット単位で入力 / 出力の指定可能。          |       |                 |

|         |     | ソフトウエアにより,内蔵プルアップ抵抗を使用可能。      |       |                 |

| P50     | 入出力 | ポート5。                          | 入力    | -               |

| P51     |     | 8 ビット入出力ポート。                   |       | SCK             |

| P52     |     | 1 ビット単位で入力 / 出力の指定可能。          |       | SI              |

| P53     |     | LEDを直接駆動可能。                    |       | so              |

| P54     |     | ソフトウエアにより,内蔵プルアップ抵抗を使用可能。      |       | INTP4/TI000/TO0 |

| P55     |     |                                |       | INTP5/TI010     |

| P56     |     |                                |       | INTP6/TI001/TO0 |

| P57     |     |                                |       | INTP7/TI011     |

| P64     | 入出力 | ポート6。                          | 入力    | RD              |

| P65     |     | 4 ビット入出力ポート。                   |       | WR              |

| P66     |     | 1 ビット単位で入力 / 出力の指定可能。          |       | WAIT            |

| P67     |     | <br> ソフトウエアにより,内蔵プルアップ抵抗を使用可能。 |       | ASTB            |

11

# 2.2 ポート以外の端子(1/2)

| 端子名称      | 入出力 | 機能                                    | リセット時 | 兼用端子            |

|-----------|-----|---------------------------------------|-------|-----------------|

| INTP0     | 入力  | 有効エッジ(立ち上がりエッジ,立ち下がりエッジ,立ち上がりおよ       | 入力    | P00/TOFF7       |

| INTP1     |     | び立ち下がりの両エッジ)指定可能な外部割り込み要求入力。          | 入力    | P01             |

| INTP2     |     |                                       | 入力    | P02             |

| INTP3     |     |                                       | 入力    | P03/ADTRG       |

| INTP4     |     |                                       | 入力    | P54/TI000/TO00  |

| INTP5     |     |                                       | 入力    | P55/TI010       |

| INTP6     |     |                                       | 入力    | P56/TI001/TO01  |

| INTP7     |     |                                       | 入力    | P57/TI011       |

| TI50      | 入力  | 8 ビット・タイマ ( TM50 ) への外部カウント・クロック入力。   | 入力    | P24/TO50        |

| TI51      |     | 8 ビット・タイマ ( TM51 ) への外部カウント・クロック入力。   | 入力    | P25/TO51        |

| TI52      |     | 8 ビット・タイマ (TM52) への外部カウント・クロック入力。     | 入力    | P26/TO52        |

| TI000     |     | 16ビット・タイマ ( TM00 ) への外部カウント・クロック入力。   | 入力    | P54/INTP4/TO00  |

|           |     | 16ビット・タイマ (TM00) のキャプチャ・レジスタ (CR000,  |       |                 |

|           |     | CR010)へのキャプチャ・トリガ入力。                  |       |                 |

| TI010     |     | 16ビット・タイマ (TM00)のキャプチャ・レジスタ (CR000)への | 入力    | P55/INTP5       |

|           |     | キャプチャ・トリガ入力。                          |       |                 |

| TI001     |     | 16ビット・タイマ ( TM01 ) への外部カウント・クロック入力。   | 入力    | P56/INTP6/TO01  |

|           |     | 16ビット・タイマ (TM01) のキャプチャ・レジスタ (CR001,  |       |                 |

|           |     | CR011)へのキャプチャ・トリガ入力。                  |       |                 |

| TI011     |     | 16ビット・タイマ (TM01)のキャプチャ・レジスタ (CR001)への | 入力    | P57/INTP7       |

|           |     | キャプチャ・トリガ入力。                          |       |                 |

| TO50      | 出力  | 8 ビット・タイマ ( TM50 ) 出力。                | 入力    | P24/TI50        |

| TO51      |     | 8 ビット・タイマ ( TM51 ) 出力。                | 入力    | P25/TI51        |

| TO52      |     | 8 ビット・タイマ (TM52) 出力。                  | 入力    | P26/TI52        |

| TO00      |     | 16ビット・タイマ ( TM00 ) 出力。                | 入力    | P54/INTP4/TI000 |

| TO01      |     | 16ビット・タイマ (TM01) 出力。                  | 入力    | P56/INTP6/TI001 |

| RTP0-RTP7 | 出力  | リアルタイム・パルス・ユニットからのトリガ信号に同期して、パル       | 入力    | P30-P37         |

|           |     | ス出力を行うリアルタイム出力ポート。                    |       |                 |

| TxD00     | 出力  | アシンクロナス・シリアル・インタフェースのシリアル・データ出        | 入力    | P21             |

| TxD01     |     | 力。                                    | 入力    | P23             |

| RxD00     | 入力  | アシンクロナス・シリアル・インタフェースのシリアル・データ人        | 入力    | P20             |

| RxD01     |     | 力。                                    | 入力    | P22             |

| SCK       | 入出力 | シリアル・インタフェースのシリアル・クロック入力/出力。          | 入力    | P51             |

| SI        | 入力  | シリアル・インタフェースのシリアル・データ入力。              | 入力    | P52             |

| SO        | 出力  | シリアル・インタフェースのシリアル・データ出力。              | 入力    | P53             |

| ANI0-ANI7 | 入力  | A/Dコンバータのアナログ入力。                      | 入力    | P10-P17         |

| ADTRG     | 入力  | A/Dコンバータへの外部トリガ信号入力。                  | 入力    | P03/INTP3       |

| TO70-TO75 | 出力  | 3 相PWMインバータ制御用タイマ出力。                  | Hi-Z  | -               |

| TOFF7     | 入力  | タイマ出力(TO70-TO75)停止外部入力。               | 入力    | P00/INTP0       |

| AD0-AD7   | 入出力 | 外部にメモリを拡張する場合の,アドレス/データ・バス。           | 入力    | P40-P47         |

# 2.2 ポート以外の端子(2/2)

|   | 端子名称             | 入出力 | 機能                              | リセット時 | 兼用端子 |

|---|------------------|-----|---------------------------------|-------|------|

|   | RD               | 出力  | 外部メモリのリード動作用ストローブ信号出力。          | 入力    | P64  |

|   | WR               |     | 外部メモリのライト動作用ストローブ信号出力。          | 入力    | P65  |

|   | WAIT             | 入力  | 外部メモリ・アクセス時のウエイト挿入。             | 入力    | P66  |

|   | ASTB             | 出力  | 外部メモリをアクセスするために,ポート4,5に出力されるアドレ | 入力    | P67  |

|   |                  |     | ス情報を外部でラッチするストローブ出力。            |       |      |

|   | AVREF            | 入力  | A/Dコンバータの基準電圧入力。                | -     | -    |

| * | AVDD             | -   | A/Dコンバータのアナログ電源。                | -     | -    |

| * | AVss             | -   | A/Dコンバータのグランド電位。                | 1     | -    |

|   | RESET            | 入力  | システム・リセット入力。                    | -     | -    |

|   | X1               | 入力  | システム・クロック発振用クリスタル接続。            | -     | -    |

|   | X2               | -   |                                 | 1     | -    |

|   | V <sub>DD0</sub> | -   | ポート部の正電源。                       | -     | -    |

|   | Vsso             | -   | ポート部のグランド電位。                    | 1     | -    |

|   | V <sub>DD1</sub> | -   | 正電源(ポート部を除く)。                   | 1     | -    |

|   | Vss1             | -   | グランド電位(ポート部を除く)。                | -     | -    |

|   | V <sub>PP</sub>  | -   | プログラム書き込み/ベリファイ時の高電圧印加。通常動作モード時 | -     | -    |

|   |                  |     | は,Vssoに直接接続してください。              |       |      |

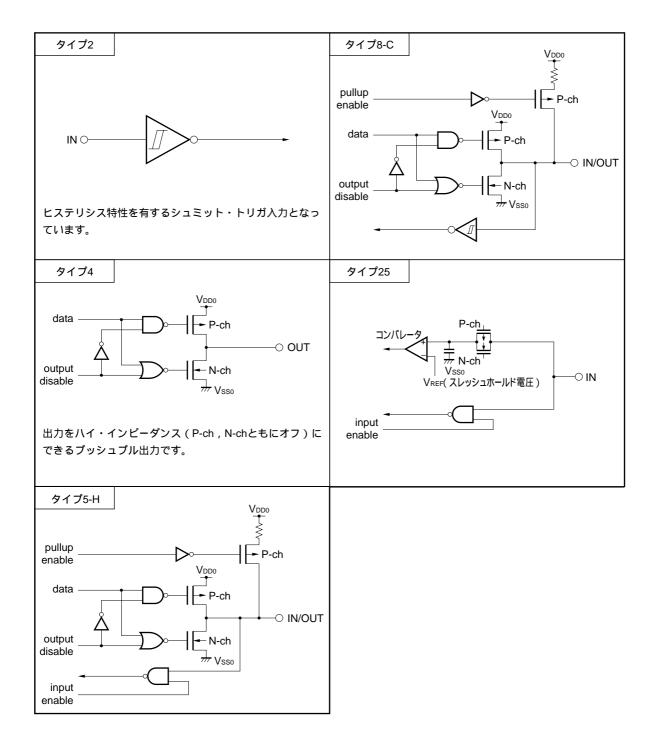

#### ★ 2.3 端子の入出力回路と未使用端子の処理

各端子の入出力回路タイプと,未使用端子の処理を表2-1に示します。 また,各タイプの入出力回路の構成は,図2-1を参照してください。

表2-1 各端子の入出力回路タイプ

| 端子                   | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法                     |

|----------------------|----------|-----|---------------------------------|

| P00/INTP0/TOFF7      | 8-C      | 入出力 | 個別に抵抗を介して,Vssoに接続してください。        |

| P01/INTP1            |          |     |                                 |

| P02/INTP2            |          |     |                                 |

| P03/INTP3/ADTRG      |          |     |                                 |

| P10/ANI0-P17/ANI7    | 25       | 入力  | 個別に抵抗を介して,VppoまたはVssoに接続してください。 |

| P20/RxD00            | 8-C      | 入出力 |                                 |

| P21/TxD00            | 5-H      |     |                                 |

| P22/RxD01            | 8-C      |     |                                 |

| P23/TxD01            | 5-H      |     |                                 |

| P24/TI50/TO50        | 8-C      |     |                                 |

| P25/TI51/TO51        |          |     |                                 |

| P26/TI52/TO52        |          |     |                                 |

| P30/RTP0-P37/RTP7    | 5-H      |     |                                 |

| P40/AD0-P47/AD7      |          |     |                                 |

| P50                  |          |     |                                 |

| P51/SCK              | 8-C      |     |                                 |

| P52/SI               | 5-H      |     |                                 |

| P53/SO               |          |     |                                 |

| P54/INTP4/TI000/TO00 |          |     |                                 |

| P55/INTP5/TI010      |          |     |                                 |

| P56/INTP6/TI001/TO01 |          |     |                                 |

| P57/INTP7/TI011      |          |     |                                 |

| P64/RD               |          |     |                                 |

| P65/WR               |          |     |                                 |

| P66/WAIT             |          |     |                                 |

| P67/ASTB             |          |     |                                 |

| TO70-TO75            | 4        | 出力  | オープンにしてください。                    |

| RESET                | 2        | 入力  | -                               |

| AVDD                 | -        | -   | Vppoに接続してください。                  |

| AVREF                |          |     | Vssoに接続してください。                  |

| AVss                 |          |     |                                 |

| Vpp                  |          |     | Vssoに直接接続してください。                |

図2-1 端子の入出力回路一覧

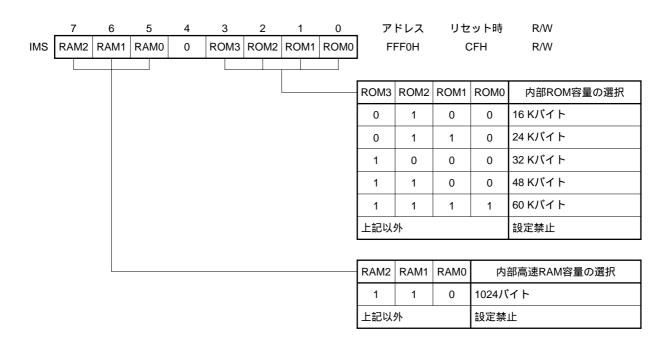

#### 3 . メモリ・サイズ切り替えレジスタ (IMS)

ソフトウエアにより内部メモリの一部を使用しないようにするためのレジスタです。IMSを設定することにより,内部メモリ容量の異なるマスクROM製品と同一のメモリ・マップにできます。

IMSは,8ビット・メモリ操作命令で設定します。

RESET入力により, CFHになります。

#### 図3-1 メモリ・サイズ切り替えレジスタのフォーマット

マスクROM製品と同一のメモリ・マップにするIMSの設定値を表3 - 1に示します。

表3-1 メモリ・サイズ切り替えレジスタの設定値

| 対象のマスクROM製品 | IMSの設定値 |

|-------------|---------|

| μ PD780982  | C4H     |

| μ PD780983  | C6H     |

| μ PD780984  | C8H     |

| μ PD780986  | ССН     |

| μ PD780988  | CFH     |

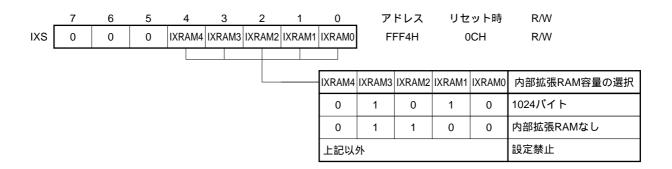

#### 4.内部拡張RAMサイズ切り替えレジスタ(IXS)

ソフトウエアにより内部拡張RAM容量の設定をするためのレジスタです。IXSを設定することにより,内部拡張RAM容量の異なるマスクROM製品と同一のメモリ・マップにできます。

IXSは,8ビット・メモリ操作命令で設定します。

RESET入力により, 0CHになります。

図4-1 内部拡張RAMサイズ切り替えレジスタのフォーマット

マスクROM製品と同一のメモリ・マップにするIXSの設定値を表4-1に示します。

表4-1 内部拡張RAMサイズ切り替えレジスタの設定値

| 対象のマスクROM製品 | IXSの設定値 |

|-------------|---------|

| μ PD780982  | 0CH     |

| μ PD780983  |         |

| μ PD780984  |         |

| μ PD780986  | 0AH     |

| μ PD780988  |         |

#### 5.フラッシュ・メモリ・プログラミング

フラッシュ・メモリへの書き込みは,ターゲット・システムに実装した状態(オンボード)で行えます。専用フラ

★ ッシュ・ライタ(Flashpro II(型番 FL-PR2),Flashpro (型番 FL-PR3,PG-FP3))をホスト・マシンおよびターゲット・システムに接続して書き込みます。また,Flashpro II, に接続されたフラッシュ・メモリ書き込み用アダプタ上でも書き込み可能です。

★ 備考 FL-PR2, FL-PR3は,株式会社内藤電誠町田製作所の製品です。

#### 5.1 通信方式の選択

フラッシュ・メモリへの書き込みは, Flashpro II, を使用し,シリアル通信で行います。表5 - 1に示す通信方式から選択して書き込みます。この通信方式の選択は,図5 - 1に示すようなフォーマットを用います。表5 - 1に示すVPPパルス数で,それぞれの通信方式が選択されます。

| 通信方式                        | チャネル数 | 使用端子                        | Vppパルス数 |

|-----------------------------|-------|-----------------------------|---------|

| 3 線式シリアルI/O                 | 1     | SCK/P51                     | 0       |

|                             |       | SI/P52                      |         |

|                             |       | SO/P53                      |         |

| UART                        | 1     | RxD00/P20                   | 8       |

|                             |       | TxD00/P21                   |         |

| 疑似 3 線式シリアルI/O <sup>注</sup> | 1     | P24/TI50/TO50 (シリアル・データ入力)  | 12      |

|                             |       | P25/TI51/TO51 (シリアル・データ出力)  |         |

|                             |       | P26/Tl52/TO52 (シリアル・クロック入力) |         |

表 5 - 1 通信方式一覧

注意 通信方式は,必ず表5-1に示すVppパルス数で選択してください。

10 V V<sub>PP</sub> V<sub>DD</sub> V<sub>SS</sub> 1 2 n RESET V<sub>DD</sub> V<sub>SS</sub> フラッシュ・メモリ書き込みモード

図5-1 通信方式選択フォーマット

注 ポートをソフトウエアで制御してシリアル転送を行います。

#### 5.2 フラッシュ・メモリ・プログラミングの機能

選択された通信方式による各種コマンド / データ送受信により , フラッシュ・メモリの書き込みなどの動作を行います。主な機能を表 5 - 2 に示します。

機能

説明

一括消去

全メモリの内容を消去します。

一括ブランク・チェック

全メモリの消去状態を確認します。

データ・ライト

書き込み開始アドレスおよび書き込みデータ数 (バイト数)をもとに,フラッシュ・メモリに書き

表5-2 フラッシュ・メモリ・プログラミングの主な機能

#### 5.3 Flashpro , の接続

一括ベリファイ

Flashpro , と  $\mu$  PD78F0988との接続は,通信方式によって異なります。それぞれの場合の接続図を図 5 - 2 から図 5 - 4 に示します。

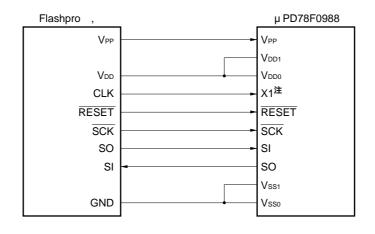

## 図5-2 3線式シリアルI/O方式でのFlashpro , の接続

全メモリの内容と入力したデータを比較します。

注 X1への入力は, CLKではなく通常の発振回路を使用することも可能です。

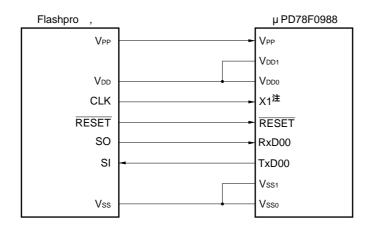

図5-3 UART**方式での**Flashpro **, の接続**

注 X1への入力は, CLKではなく通常の発振回路を使用することも可能です。

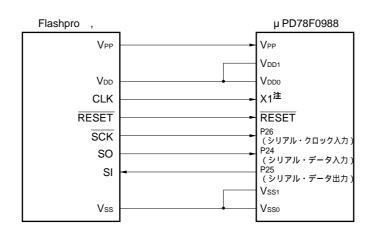

▼ 図5-4 疑似3線式シリアルI/O方式でのFlashpro , の接続

注 X1への入力は, CLKではなく通常の発振回路を使用することも可能です。

#### ★ 6.電気的特性

#### **絶対最大定格 (**TA = 25 )

| 項 目      | 略号                 | 条                             | 件                             |         | 定格                               | 単位 |

|----------|--------------------|-------------------------------|-------------------------------|---------|----------------------------------|----|

| 電源電圧     | V <sub>DD</sub>    |                               |                               |         | - 0.3 ~ + 6.5                    | V  |

|          | Vpp                | - 0.3 ~ + 10.5                | V                             |         |                                  |    |

|          | AV <sub>DD</sub>   |                               |                               |         | - 0.3 ~ V <sub>DD</sub> + 0.3    | V  |

|          | AVREF              |                               |                               |         | - 0.3 ~ V <sub>DD</sub> + 0.3    | V  |

|          | AVss               |                               |                               |         | - 0.3 ~ + 0.3                    | V  |

| 入力電圧     | Vı                 | P00-P03, P10-P17, P20-P26, P  | - 0.3 ~ V <sub>DD</sub> + 0.3 | V       |                                  |    |

|          |                    | P64-P67, TO70-TO75, X1, X2, i | RESET                         |         |                                  |    |

| 出力電圧     | Vo                 |                               |                               |         | - 0.3 ~ V <sub>DD</sub> + 0.3    | V  |

| アナログ入力電圧 | Van P10-P17 アナログ入力 |                               |                               | <br>力端子 | AVss - 0.3 ~ AVREF + 0.3         | V  |

|          |                    |                               |                               |         | かつ - 0.3 ~ V <sub>DD</sub> + 0.3 |    |

| ハイ・レベル   | Іон                | 1端子                           | - 10                          | mA      |                                  |    |

| 出力電流     |                    | P00, P01, P30-P37, P40-P47, P | - 15                          | mA      |                                  |    |

|          |                    | P02, P03, P20-P26, TO70-TO75  |                               | - 15    | mA                               |    |

| ロウ・レベル   | lou <sup>注</sup>   | P00-P03, P10-P17, P20-P26,    |                               | ピーク値    | 20                               | mA |

| 出力電流     |                    | P30-P37, P40-P47, P64-P67 1   | 端子                            | 実効値     | 10                               | mA |

|          |                    | P50-P57, TO70-TO75 1 端子       |                               | ピーク値    | 30                               | mA |

|          |                    |                               |                               | 実効値     | 15                               | mA |

|          |                    | P00, P01, P30-P37, P40-P47, P | 64-P67                        | ピーク値    | 50                               | mA |

|          |                    | 合計                            |                               | 実効値     | 20                               | mA |

|          |                    | P02, P03, P20-P26             |                               | ピーク値    | 30                               | mA |

|          |                    | 合計                            |                               | 実効値     | 15                               | mA |

|          |                    | TO70-TO75                     |                               | ピーク値    | 100                              | mA |

|          |                    | 合計                            |                               | 実効値     | 70                               | mA |

|          |                    | P50-P57                       |                               | ピーク値    | 100                              | mA |

|          |                    | 合計                            |                               | 実効値     | 70                               | mA |

| 動作周囲温度   | Та                 |                               |                               |         | - 40 ~ +85                       |    |

| <br>保存温度 | T <sub>stg</sub>   |                               |                               |         | - 40 ~ + 125                     |    |

注 実効値は〔実効値〕=[ピーク値]×√デューティで計算してください。

注意 各項目のうち1項目でも,また一瞬でも絶対最大定格を越えると,製品の品質を損なう恐れがあります。つまり絶対最大定格とは,製品に物理的な損傷を与えかねない定格値です。必ずこの定格値を越えない状態で,製品をご使用ください。

容量 (TA = 25 , VDD = VSS = 0 V)

| 項 目   | 略号  | 条                    | 件                          | MIN. | TYP. | MAX. | 単位 |

|-------|-----|----------------------|----------------------------|------|------|------|----|

| 入力容量  | CIN | f=1 MHz 被測定端子以外は 0 V |                            |      |      | 15   | pF |

| 入出力容量 | Сю  | f = 1 MHz            | P00-P03, P20-P26, P30-P37, |      |      | 15   | pF |

|       |     | 被測定端子以外は0V           | P40-P47, P50-P57, P64-P67, |      |      |      |    |

|       |     |                      | TO70-TO75                  |      |      |      |    |

備考 特に指定のないかぎり,兼用端子の特性はポート端子の特性と同じです。

#### **システム・クロック発振回路特性 (TA=-40~+85**, VDD=4.0~5.5 V)

| 発振子       | 推奨回路                  | 項目                                | 条              | 件        | MIN. | TYP. | MAX. | 単位  |

|-----------|-----------------------|-----------------------------------|----------------|----------|------|------|------|-----|

| セラミック 発振子 | V <sub>PP</sub> X2 X1 | 発振周波数(fx) <sup>注1</sup>           |                |          | 1.0  |      | 8.38 | MHz |

|           | C1 <del>+</del> C2+   | 発振安定時間 <sup>注2</sup>              | Vppが発振電圧に達したあと | E範囲のMIN. |      |      | 4    | ms  |

| 水晶振動子     | V <sub>PP</sub> X2 X1 | 発振周波数 (fx) <sup>注1</sup>          |                |          | 1.0  |      | 8.38 | MHz |

|           | C1= C2=               | 発振安定時間 <sup>注 2</sup>             | Vppが発振電圧に達したあと | E範囲のMIN. |      |      | 10   | ms  |

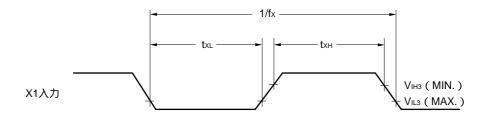

| 外部クロック    | X2 X1                 | X1入力周波数(fx) <sup>注</sup>          |                |          | 1.0  |      | 8.38 | MHz |

|           | μ PD74HCU04 Δ         | X1入力ハイ , ロウ・レ<br>ベル幅 ( txH, txL ) | ,              |          | 50   |      | 500  | ns  |

- 注1.発振回路の特性だけを示すものです。命令実行時間は,AC特性を参照してください。

- 2.リセットまたはSTOPモード解除後,発振が安定するのに必要な時間です。

注意 システム・クロック発振回路を使用する場合は,配線容量などの影響を避けるために,図中の破線の部分を次のように配線してください。

配線は極力短くする。

他の信号線と交差させない。

変化する大電流が流れる線に接近させない。

発振回路のコンデンサの接地点は、常にVssiと同電位になるようにする。

大電流が流れるグランド・パターンに接地しない。

発振回路から信号を取り出さない。

#### 推奨発振回路定数

システム・クロック:セラミック発振子(TA = -40~+85)

| メーカ          | 品 名          | 周波数   | 推奨回     | 路定数     | 発振電      | 圧範囲      |

|--------------|--------------|-------|---------|---------|----------|----------|

|              |              | (MHz) | C1 (pF) | C2 (pF) | MIN. (V) | MAX. (V) |

| 村田製作所        | CSA2.00MG040 | 2.00  | 100     | 100     | 4.0      | 5.5      |

|              | CST2.00MG040 | 2.00  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA3.58MG    | 3.58  | 30      | 30      | 4.0      | 5.5      |

|              | CST3.58MGW   | 3.58  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA4.00MG    | 4.00  | 30      | 30      | 4.0      | 5.5      |

|              | CST4.00MGW   | 4.00  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA4.19MG    | 4.19  | 30      | 30      | 4.0      | 5.5      |

|              | CST4.19MGW   | 4.19  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA4.91MG    | 4.91  | 30      | 30      | 4.0      | 5.5      |

|              | CST4.91MGW   | 4.91  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA5.00MG    | 5.00  | 30      | 30      | 4.0      | 5.5      |

|              | CST5.00MGW   | 5.00  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA7.37MTZ   | 7.37  | 30      | 30      | 4.0      | 5.5      |

|              | CST7.37MTW   | 7.37  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA8.00MTZ   | 8.00  | 30      | 30      | 4.0      | 5.5      |

|              | CST8.00MTW   | 8.00  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA8.38MTZ   | 8.38  | 30      | 30      | 4.0      | 5.5      |

|              | CST8.38MTW   | 8.38  | 内蔵      | 内蔵      | 4.0      | 5.5      |

|              | CSA10.0MTZ   | 10.0  | 30      | 30      | 4.0      | 5.5      |

|              | CST10.0MTW   | 10.0  | 内蔵      | 内蔵      | 4.0      | 5.5      |

| ÷ 2645 - 104 |              |       |         |         | 26.1E E  | *        |

注意 発振回路定数および発振電圧範囲は,安定して発振する条件を示しています。発振周波数精度は保証していません。アプリケーションで発振周波数精度が必要な場合,実装回路で発振周波数を調整する必要があります。 詳細については,ご使用になる発振子のメーカに直接お問い合わせください。

DC特性(TA=-40~+85 , VDD=4.0~5.5V)

| 項目                  | 略号               | 条                                 | 件                                   | MIN.                  | TYP. | MAX.                | 単位 |

|---------------------|------------------|-----------------------------------|-------------------------------------|-----------------------|------|---------------------|----|

| ハイ・レベル              | V <sub>IH1</sub> | P10-P17, P21, P23, P30-P37        | 7, P40-P47, P50, P53, P64-P67       | 0.7 Vdd               |      | V <sub>DD</sub>     | V  |

| 入力電圧                | V <sub>IH2</sub> | RESET, P00-P03, P20, P22,         | P24-P26, P51, P52, P54-P57          | 0.8 V <sub>DD</sub>   |      | V <sub>DD</sub>     | V  |

|                     | V <sub>IH3</sub> | X1, X2                            |                                     | V <sub>DD</sub> - 0.5 |      | V <sub>DD</sub>     | V  |

| ロウ・レベル              | V <sub>IL1</sub> | P10-P17, P21, P23, P30-P37        | 7, P40-P47, P50, P53, P64-P67       | 0                     |      | 0.3 V <sub>DD</sub> | V  |

| 入力電圧                | V <sub>IL2</sub> | RESET, P00-P03, P20, P22,         | P24-P26, P51, P52, P54-P57          | 0                     |      | 0.2 V <sub>DD</sub> | V  |

|                     | V <sub>IL3</sub> | X1, X2                            |                                     | 0                     |      | 0.4                 | V  |

| ハイ・レベル              | Vон1             | 4.5 V VDD 5.5 V, IOH = - 1        | mA                                  | V <sub>DD</sub> - 1.0 |      | V <sub>DD</sub>     | V  |

| 出力電圧                |                  | Іон = - 100 µ А                   |                                     | V <sub>DD</sub> - 0.5 |      | V <sub>DD</sub>     | V  |

| ロウ・レベル              | V <sub>OL1</sub> | P50-P57, TO70-TO75 5.0            | ) V VDD 5.5 V,                      |                       | 0.4  | 2.0                 | V  |

| 出力電圧                |                  | lou                               | = 15 mA                             |                       |      |                     |    |

|                     |                  | P00-P03, P20-P26, 5.0             | ) V VDD 5.5 V,                      |                       |      | 0.4                 | V  |

|                     |                  | P30-P37, P40-P47, loL             | = 1.6 mA                            |                       |      |                     |    |

|                     |                  | P64-P67                           |                                     |                       |      |                     |    |

|                     | V <sub>OL2</sub> | Ιοι = 400 μΑ                      |                                     |                       |      | 0.5                 | V  |

| ハイ・レベル              | Ішн1             | V <sub>IN</sub> = V <sub>DD</sub> | 0-P03, P10-P17, P20-P26,            |                       |      | 3                   | μΑ |

| 入力リーク電流             |                  | P3                                | 0-P37, P40-P47, P50-P57,            |                       |      |                     |    |

|                     |                  | P6                                | 4-P67, TO70-TO75, RESET             |                       |      |                     |    |

|                     | ILIH2            | X1                                | , X2                                |                       |      | 20                  | μΑ |

| ロウ・レベル              | ILIL1            | V <sub>IN</sub> = 0 V P0          | 0-P03, P10-P17, P20-P26,            |                       |      | - 3                 | μΑ |

| 入力リーク電流             |                  | P3                                | 0-P37, P40-P47, P50-P57,            |                       |      |                     |    |

|                     |                  | P6                                | 4-P67, TO70-TO75, RESET             |                       |      |                     |    |

|                     | ILIL2            | X1                                | , X2                                |                       |      | - 20                | μΑ |

| ハイ・レベル              | Ісон             | Vout = Vdd                        |                                     |                       |      | 3                   | μΑ |

| 出力リーク電流             |                  |                                   |                                     |                       |      |                     |    |

| ロウ・レベル              | ILOL             | Vout = 0 V                        |                                     |                       |      | - 3                 | μΑ |

| 出力リーク電流             |                  |                                   |                                     |                       |      |                     |    |

| ソフトウエア・プ            | R <sub>2</sub>   | VIN = 0 V                         |                                     | 15                    | 30   | 90                  | k  |

| ルアップ抵抗              |                  | P00-P03, P20-P26, P30-P37,        | , P40-P47, P50-P57, P64-P67         |                       |      |                     |    |

| 電源電流 <sup>注 1</sup> | I <sub>DD1</sub> | 8.38 MHz水晶発振 VDD = 5.0            | V ± 10 % <sup>注 2</sup> A/Dコンバータ停止時 |                       | 15   | 30                  | mA |

|                     |                  | 動作モード                             | A/Dコンバータ動作時                         |                       | 16   | 32                  | mA |

|                     | I <sub>DD2</sub> | 8.38 MHz水晶発振 VDD = 5.0            | V±10 % <sup>注2</sup> 周辺機能停止時        |                       | 1.3  | 2.6                 | mA |

|                     |                  | HALTモード                           | 周辺機能動作時                             |                       |      | 7.3                 | mA |

|                     | I <sub>DD3</sub> | STOPモード VDD = 5.0                 | 0 V ± 10 %                          |                       | 0.1  | 30                  | μА |

**注1**. 内部電源 (VDDO, VDD1) に流れるトータル電流です。周辺動作電流を含みます (ただし,ポートのプルアップ抵抗, AVREF端子に流れる電流は含みません)。

**備考** 特に指定のないかぎり,兼用端子の特性はポート端子の特性と同じです。

<sup>2.</sup> 高速動作モード時 (プロセッサ・クロック・コントロール・レジスタ (PCC)を00Hに設定したとき)。

#### AC特性

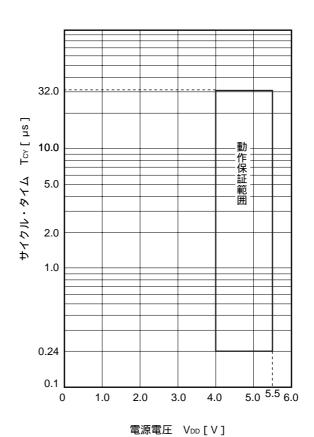

# (1)基本動作(TA = -40~+85 , VDD = 4.0~5.5 V)

| 項目               | 略号               | 条件           | MIN.                 | TYP. | MAX.  | 単位  |

|------------------|------------------|--------------|----------------------|------|-------|-----|

| サイクル・タイム         | Тсч              | システム・クロックで動作 | 0.24                 |      | 32    | μs  |

| (最小命令実行時間)       |                  |              |                      |      |       |     |

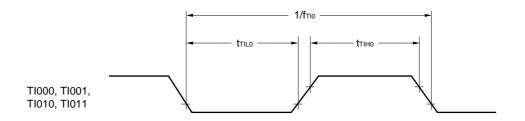

| TI000, TI001,    | fтıo             |              | 0                    |      | fx/64 | MHz |

| TI010, TI011     |                  |              |                      |      |       |     |

| 入力周波数            |                  |              |                      |      |       |     |

| TI000, TI001,    | <b>t</b> тіно    |              | 2/f <sub>sam</sub> + |      |       | μs  |

| TI010, TI011     | <b>t</b> TILO    |              | 0.1 <sup>注</sup>     |      |       |     |

| 入力ハイ ,口ウ・        |                  |              |                      |      |       |     |

| レベル幅             |                  |              |                      |      |       |     |

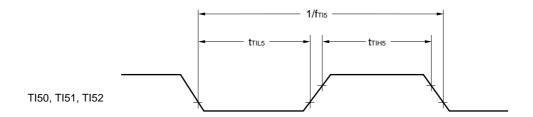

| TI50, TI51, TI52 | f <sub>T15</sub> | 8/16ビット精度時   | 0                    |      | 4     | MHz |

| 入力周波数            |                  |              |                      |      |       |     |

| TI50, TI51, TI52 | <b>t</b> тін5    | 8/16ビット精度時   | 100                  |      |       | ns  |

| 入力ハイ ,ロウ・        | <b>t</b> TIL5    |              |                      |      |       |     |

| レベル幅             |                  |              |                      |      |       |     |

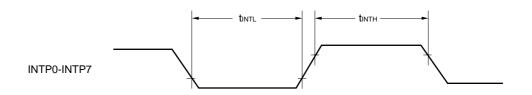

| 割り込み要求入力         | tinth            | INTP0-INTP7  | 1                    |      |       | μs  |

| ハイ ,ロウ・レベル幅      | tintl            |              |                      |      |       |     |

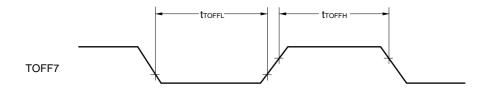

| TOFF入力八イ,        | tтоғғн           |              | 2                    |      |       | μs  |

| ロウ・レベル幅          | <b>t</b> TOFFL   |              |                      |      |       |     |

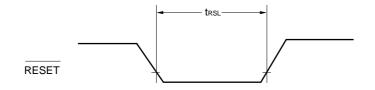

| RESET入力ロウ・       | trsL             |              | 10                   |      |       | μs  |

| レベル幅             |                  |              |                      |      |       |     |

注 プリスケーラ・モード・レジスタ00 (PRM00) のビット 0 , 1 (PRM000, PRM001) またはプリスケーラ・モード・レジスタ01 (PRM01) のビット 0 , 1 (PRM010, PRM011) により , fsam = fx, fx/4, fx/32の選択が可能です。ただし , カウント・クロックとしてTI000 (TM00) またはTI001 (TM01) 有効エッジを選択した場合は , fsam = fx/16となります。

25

# Tcy vs Vdd (システム・クロック動作時)

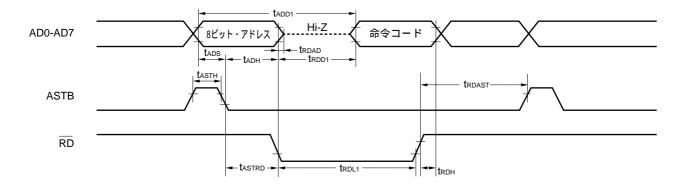

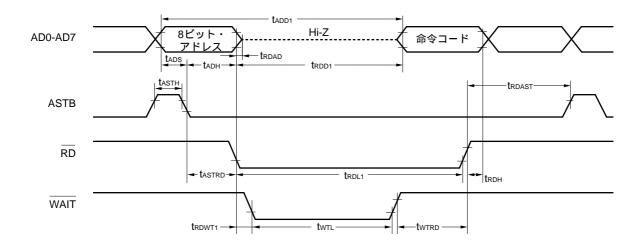

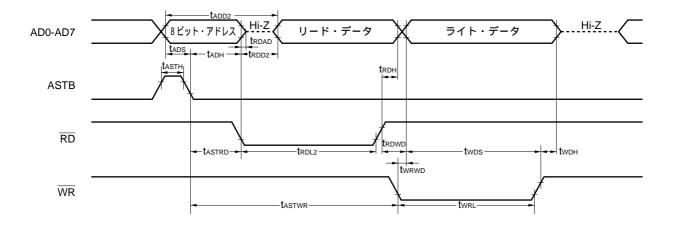

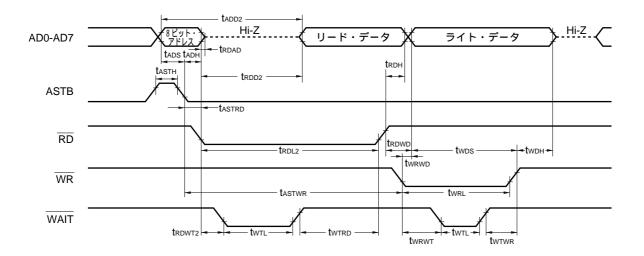

## (2) y-F/ = -40 - +85, VDD = 4.0 - 5.5 V

| 項目                  | 略号                | 条 件 | MIN.                | MAX.            | 単位 |

|---------------------|-------------------|-----|---------------------|-----------------|----|

| ASTBハイ・レベル幅         | tasth             |     | 0.3 tcy             |                 | ns |

| アドレス・セットアップ時間       | tads              |     | 20                  |                 | ns |

| アドレス・ホールド時間         | tadh              |     | 6                   |                 | ns |

| アドレス データ入力時間        | t <sub>ADD1</sub> |     |                     | (2+2n) tcy - 54 | ns |

|                     | tADD2             |     |                     | (3+2n) tcy - 60 | ns |

| RD アドレス出力時間         | trdad             |     | 0                   | 100             | ns |

| RD データ入力時間          | tRDD1             |     |                     | (2+2n) tcy - 87 | ns |

|                     | tRDD2             |     |                     | (3+2n) tcy - 93 | ns |

| リード・データ・ホールド時間      | <b>t</b> RDH      |     | 0                   |                 | ns |

| RDロウ・レベル幅           | tRDL1             |     | (1.5 + 2n) tcy - 33 |                 | ns |

|                     | tRDL2             |     | (2.5 + 2n) tcy - 33 |                 | ns |

| RD WAIT 入力時間        | tRDWT1            |     |                     | tcy - 43        | ns |

|                     | trdwt2            |     |                     | tcy - 43        | ns |

| WR WAIT 入力時間        | twrwt             |     |                     | 0.5 tcy - 25    | ns |

| WAIT ロウ・レベル幅        | twtL              |     | (0.5 + 2n) tcy + 10 | (2+2n) tcy      | ns |

| ライト・データ・セットアップ時間    | twos              |     | 60                  |                 | ns |

| ライト・データ・ホールド時間      | twoн              |     | 6                   |                 | ns |

| WRロウ・レベル幅           | twrL              |     | (1.5 + 2n) tcy - 15 |                 | ns |

| ASTB RD 遅延時間        | tastrd            |     | 6                   |                 | ns |

| ASTB WR 遅延時間        | tastwr            |     | 2 tcy - 15          |                 | ns |

| 外部フェッチ時RD ASTB 遅延時間 | <b>t</b> RDAST    |     | 0.8 tcy - 15        | 1.2 tcy         | ns |

| RD ライト・データ出力時間      | trowd             |     | 40                  |                 | ns |

| WR ライト・データ出力時間      | twrwd             |     | 10                  | 60              | ns |

| WAIT RD 遅延時間        | twtrd             |     | 0.8 tcy             | 2.5 tcy + 25    | ns |

| WAIT WR 遅延時間        | twtwr             |     | 0.8 tcy             | 2.5 tcy + 25    | ns |

**備考1**.tcy = Tcy/4

- 2.nはウエイト数を示します。

- 3.CL = 100 pF (CLはAD0-AD7, RD, WR, WAIT, ASTB端子の負荷容量です)

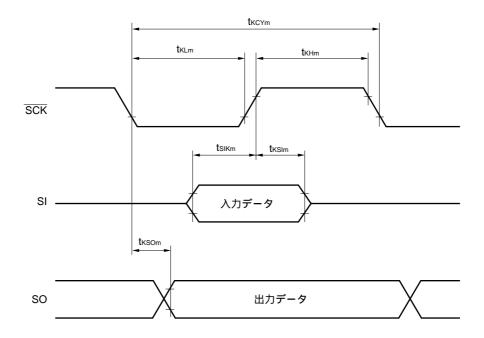

# (3)シリアル・インタフェース(TA = -40~+85 , VDD = 4.0~5.5 V)

## (a) 3線式シリアルI/Oモード(SCK...内部クロック出力)

| 項                 | 目     | 略                 | 号 | 条                       | 件 | MIN.         | TYP. | MAX. | 単位 |

|-------------------|-------|-------------------|---|-------------------------|---|--------------|------|------|----|

| SCKサイク            | ル・タイム | tkcy1             |   |                         |   | 954          |      |      | ns |

| SCKハイ,            | ロウ・レベ | t <sub>KH1</sub>  |   |                         |   | tксү1/2 - 50 |      |      | ns |

| ル幅                |       | t <sub>KL1</sub>  |   |                         |   |              |      |      |    |

| SIセットア            | 'ップ時間 | tsik1             |   |                         |   | 100          |      |      | ns |

| (対SCK             | )     |                   |   |                         |   |              |      |      |    |

| SIホールド            | 時間    | t <sub>KSI1</sub> |   |                         |   | 400          |      |      | ns |

| (対 <del>SCK</del> | )     |                   |   |                         |   |              |      |      |    |

| SCK S             | O出力遅延 | tkso1             |   | C = 100 pF <sup>注</sup> |   |              |      | 300  | ns |

| 時間                |       |                   |   |                         |   |              |      |      |    |

注 Cは, SCK, SO出力ラインの負荷容量です。

## (b) 3線式シリアルI/Oモード(SCK...外部クロック入力)

| 項 目       | 略                 | 号 | 条                       | 件 | MIN. | TYP. | MAX. | 単位 |

|-----------|-------------------|---|-------------------------|---|------|------|------|----|

| SCKサイクル・タ | イム tĸcy:          | 2 |                         |   | 800  |      |      | ns |

| SCKハイ,ロウ・ | レベ tĸн2           |   |                         |   | 400  |      |      | ns |

| ル幅        | t <sub>KL2</sub>  |   |                         |   |      |      |      |    |

| SIセットアップ時 | 間 tsik2           |   |                         |   | 100  |      |      | ns |

| (対SCK )   |                   |   |                         |   |      |      |      |    |

| SIホールド時間  | t <sub>KSI2</sub> |   |                         |   | 400  |      |      | ns |

| (対SCK )   |                   |   |                         |   |      |      |      |    |

| SCK SO出力i | 遅延 tkso           | 2 | C = 100 pF <sup>注</sup> |   |      |      | 300  | ns |

| 時間        |                   |   |                         |   |      |      |      |    |

注 Cは, SCK, SO出力ラインの負荷容量です。

## (c) UARTモード (UART00) (専用ボー・レート・ジェネレータ出力)

| 項     | 目 | 略号 | 条 | 件 | MIN. | TYP. | MAX.   | 単位  |

|-------|---|----|---|---|------|------|--------|-----|

| 転送レート |   |    |   |   |      |      | 125000 | bps |

#### (d) UARTモード (UARTOO) (赤外線データ転送モード)

| 項      | 目       | 略 | 号 | 条 | 件 | MIN. | TYP. | MAX.                  | 単位  |

|--------|---------|---|---|---|---|------|------|-----------------------|-----|

| 転送レート  |         |   |   |   |   |      |      | 115200                | bps |

| ビット・レ- | - 卜許容誤差 |   |   |   |   |      |      | ± 0.87                | %   |

| 出力パルス  | 幅       |   |   |   |   | 1.2  |      | 0.24/fbr <sup>注</sup> | μs  |

| 入力パルス  | 幅       |   |   |   |   | 4/fx |      |                       | μs  |

## **注** fbr:設定ボー・レート

#### **(e)** UARTモード (UART01) (専用ボー・レート・ジェネレータ出力)

| 項     | 目 | 略号 | 条 | 件 | MIN. | TYP. | MAX.  | 単位  |

|-------|---|----|---|---|------|------|-------|-----|

| 転送レート |   |    |   |   |      |      | 38400 | bps |

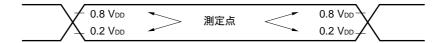

## ACタイミング測定点(X1入力を除く)

#### クロック・タイミング

## TIタイミング

#### TOFFタイミング

#### リード/ライト・オペレーション

## 外部フェッチ (ノー・ウエイト時):

#### 外部フェッチ (ウエイト挿入時):

## 外部データ・アクセス (ノー・ウエイト時):

#### 外部データ・アクセス (ウエイト挿入時):

## シリアル転送タイミング

## 3線式シリアル/○モード:

m = 1, 2

A/Dコンパータ特性 (Ta = -40~+85 , VDD = AVDD = 4.0~5.5 V, AVSS = VSS = 0 V)

| 項目                | 略     | 号 | 条                               | 件 | MIN. | TYP.  | MAX.  | 単位   |

|-------------------|-------|---|---------------------------------|---|------|-------|-------|------|

| 分解能               |       |   |                                 |   | 10   | 10    | 10    | bit  |

| 総合誤差 <sup>注</sup> |       |   | 4.0 V AVREF 5.5 V               |   |      | ± 0.2 | ± 0.4 | %FSR |

|                   |       |   | 2.7 V AVREF < 4.0 V             |   |      | ± 0.3 | ± 0.6 | %FSR |

| 変換時間              | tconv |   | 4.0 V AVREF 5.5 V               |   | 14   |       | 96    | μs   |

|                   |       |   | 2.7 V AV <sub>REF</sub> < 4.0 V |   | 19   |       | 96    | μs   |

| ゼロスケール・オフセ        |       |   | 4.0 V AVREF 5.5 V               |   |      |       | ± 0.4 | %FSR |

| ット <sup>注</sup>   |       |   | 2.7 V AV <sub>REF</sub> < 4.0 V |   |      |       | ± 0.6 | %FSR |

| フルスケール・オフセ        |       |   | 4.0 V AVREF 5.5 V               |   |      |       | ± 0.4 | %FSR |

| ット <sup>注</sup>   |       |   | 2.7 V AV <sub>REF</sub> < 4.0 V |   |      |       | ± 0.6 | %FSR |

| 非直線性誤差            |       |   | 4.0 V AVREF 5.5 V               |   |      |       | ± 2.5 | LSB  |

|                   |       |   | 2.7 V AV <sub>REF</sub> < 4.0 V |   |      |       | ± 4.5 | LSB  |

| 微分非直線性誤差          |       |   | 4.0 V AVREF 5.5 V               |   |      |       | ± 1.5 | LSB  |

|                   |       |   | 2.7 V AV <sub>REF</sub> < 4.0 V |   |      |       | ± 2.0 | LSB  |

| アナログ入力電圧          | VIAN  |   |                                 |   | 0    |       | AVREF | V    |

| 基準電圧              | AVRE  | F |                                 |   | 2.7  |       | AVDD  | V    |

| AVREF-AVss間抵抗     | RREF  |   | A/D変換非動作時                       |   | 20   | 40    |       | k    |

注 量子化誤差 (± 1/2 LSB)を含みません。フルスケール値に対する比率で表します。

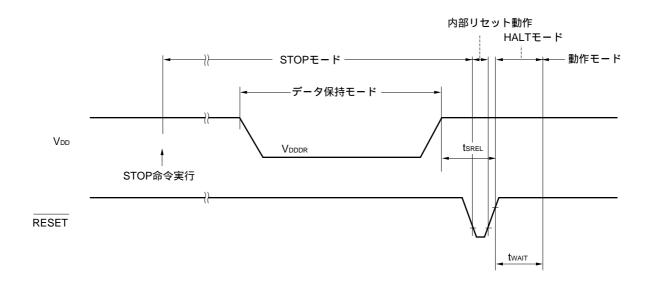

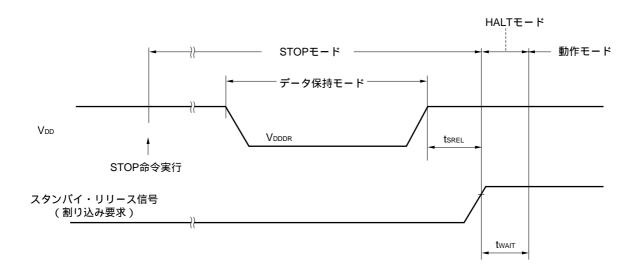

**データ・メモリSTOPモード低電源電圧データ保持特性 (TA = -40~+85 )**

| 項目          | 略号    | 条件            | MIN. | TYP.   | MAX. | 単位 |

|-------------|-------|---------------|------|--------|------|----|

| データ保持電源電圧   | VDDDR |               | 2.0  |        | 5.5  | V  |

| データ保持電源電流   | IDDDR | VDDDR = 2.0 V |      | 0.1    | 10   | μА |

| リリース信号セット時間 | tsrel |               | 0    |        |      | μs |

| 発振安定ウエイト時間  | twait | RESETによる解除    |      | 217/fx |      | ms |

|             |       | 割り込み要求による解除   |      | 注      |      | ms |

**注** 発振安定時間選択レジスタ (OSTS)のビット0-2 (OSTS0-OSTS2)により, 2<sup>12</sup>/fx, 2<sup>14</sup>/fx-2<sup>17</sup>/fxの選択が可能です。

#### データ保持タイミング(RESET によるSTOPモード解除)

# データ保持タイミング (スタンパイ・リリース信号:割り込み要求信号によるSTOPモード解除)

#### 割り込み要求入力タイミング

## RESET 入力タイミング

# フラッシュ・メモリ・プログラミング特性 (VDD = 4.0 ~ 5.5 V, Vss = 0 V, VPP = 9.7 ~ 10.3 V)

## (1)基本特性

| 項目              | 略号               | 条件           | MIN.                | TYP.            | MAX.                | 単 位 |

|-----------------|------------------|--------------|---------------------|-----------------|---------------------|-----|

| 動作周波数           | fx               |              | 1.0                 |                 | 8.38                | MHz |

| 電源電圧            | V <sub>DD</sub>  |              | 4.0                 |                 | 5.5                 | V   |

|                 | VPPL             | Vppロウ・レベル検出時 | 0                   |                 | 0.2 V <sub>DD</sub> | V   |

|                 | VPP              | Vpp八イ・レベル検出時 | 0.8 V <sub>DD</sub> | V <sub>DD</sub> | 1.2 V <sub>DD</sub> | V   |

|                 | V <sub>PPH</sub> | Vpp高電圧検出時    | 9.0                 | 10.0            | 10.5                | V   |

|                 |                  | プログラミング時     | 9.7                 | 10.0            | 10.3                | V   |

| Vpp電源電流         | <b>I</b> PP      | VPP = 10.0 V |                     | 50              | 100                 | mA  |

| 書き込み時間(1バイトあたり) | Twrt             |              | 50                  |                 | 500                 | μs  |

| 書き換え回数          | CWRT             |              |                     |                 | 20                  | 回   |

| 消去時間            | TERASE           |              | 1                   |                 | 20                  | S   |

| プログラミング温度       | T <sub>PRG</sub> |              | 10                  |                 | 40                  |     |

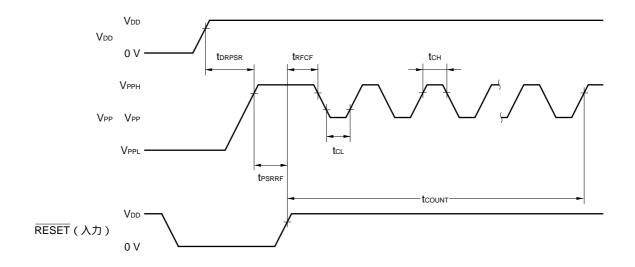

#### (2)シリアル書き込みオペレーション特性

| 項目                                    | 略号             | 条件     | MIN. | TYP. | MAX. | 単 位 |

|---------------------------------------|----------------|--------|------|------|------|-----|

| V <sub>DD</sub> V <sub>PP</sub> セット時間 | <b>t</b> DRPSR | Vpp高電圧 | 0    |      |      | μs  |

| V <sub>PP</sub> RESET セット時間           | <b>t</b> PSRRF | Vpp高電圧 | 1.0  |      |      | μs  |

| RESET V <sub>PP</sub> カウント開始時間        | <b>t</b> rfcf  | Vpp高電圧 | 1.0  |      |      | μs  |

| カウント実行時間                              | tcount         |        |      |      | 20   | ms  |

| Vppカウンタ・ハイ・レベル幅                       | tсн            |        | 8.0  |      |      | μs  |

| Vppカウンタ・ロウ・レベル幅                       | tcL            |        | 8.0  |      |      | μs  |

| Vppカウンタ・ノイズ除去幅                        | tnfw           |        |      | 40   |      | ns  |

## フラッシュ書き込みモード設定タイミング

## ★ 7.外形図

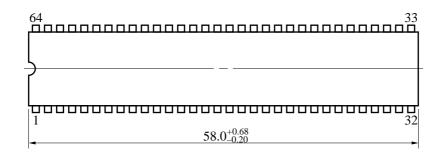

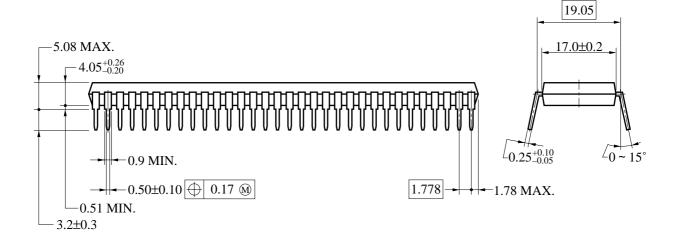

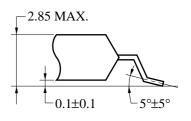

# 64ピン・プラスチック・シュリンク DIP (750 mil) 外形図 (単位:mm)

P64C-70-750A,C-3

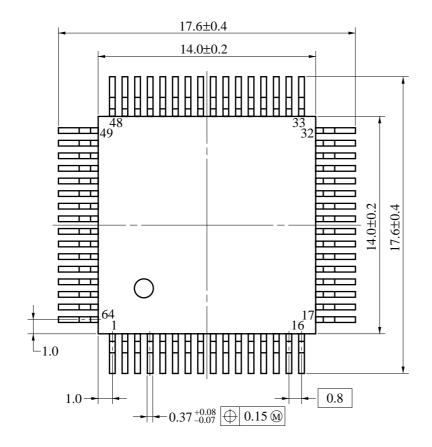

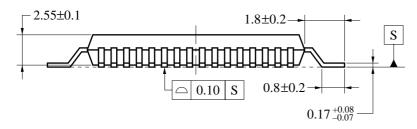

# 64ピン・プラスチック QFP ( 14) 外形図 (単位:mm)

端子先端形状詳細図

P64GC-80-AB8-4

## ★ 付録A.開発ツール

μPD780988サブシリーズを使用するシステム開発のために次のような開発ツールを用意しています。

(5)開発ツールを使用する際の注意も参照してください。

#### (1)言語処理用ソフトウエア

| RA78K/0   | 78K/0シリーズ共通のアセンブラ・パッケージ           |

|-----------|-----------------------------------|

| CC78K/0   | 78K/0シリーズ共通のCコンパイラ・パッケージ          |

| DF780988  | μ PD780988サブシリーズ用デバイス・ファイル        |

| CC78K/0-L | 78K/0シリーズ共通のCコンパイラ・ライブラリ・ソース・ファイル |

# (2)フラッシュ・メモリ書き込み用ツール

| Flashpro (型番FL-PR2) | フラッシュ・メモリ内蔵マイコン専用のフラッシュ・ライタ |

|---------------------|-----------------------------|

| Flashpro            |                             |

| (型番FL-PR3, PG-FP3)  |                             |

| FA-64CW             | フラッシュ・メモリ書き込み用アダプタ          |

| FA-64GC             |                             |

## (3)ディバグ用ツール

## ・インサーキット・エミュレータ IE-78K0-NSを使用する場合

| IE-78K0-NS                 | 78K/0シリーズ共通のインサーキット・エミュレータ                           |  |  |

|----------------------------|------------------------------------------------------|--|--|

| IE-70000-MC-PS-B           | IE-78K0-NS用電源ユニット                                    |  |  |

| IE-78K0-NS-PA <sup>注</sup> | IE-78K0-NSの機能を強化 / 拡張するためのパフォーマンス・ボード                |  |  |

| IE-70000-98-IF-C           | ホスト・マシンとしてPC-9800シリーズ(ノート型パソコンを除く)を使用するときのインタフェー     |  |  |

|                            | ス・アダプタ (Cバス対応)                                       |  |  |

| IE-70000-CD-IF-A           | ホスト・マシンとしてノート型パソコンを使用するときのPCカードとインタフェース・ケーブル         |  |  |

|                            | (PCMCIAソケット対応)                                       |  |  |

| IE-70000-PC-IF-C           | ホスト・マシンとしてIBM PC/AT™互換機を使用するときのインタフェース・アダプタ(ISAバス対応) |  |  |

| IE-70000-PCI-IF            | ホスト・マシンとしてPCIバスを内蔵したパソコンを使用するときに必要なアダプタ              |  |  |

| IE-780988-NS-EM4           | μPD780988サブシリーズをエミュレーションするためのエミュレーション・ボード            |  |  |

| IE-78K0-NS-P01             | μ PD780988サブシリーズをエミュレーションするときに必要なI/Oボード              |  |  |

| NP-64CW                    | 64ピン・プラスチック・シュリンクDIP(CWタイプ)用エミュレーション・プローブ            |  |  |

| NP-64GC                    | 64ピン・プラスチックQFP(GC-AB8タイプ)用エミュレーション・プローブ              |  |  |

| NP-64GC-TQ                 |                                                      |  |  |

| EV-9200GC-64               | 64ピン・プラスチックQFP (GC-AB8タイプ)を実装できるように作られたターゲット・システムの基  |  |  |

|                            | 板と,NP-64GCを接続するための変換ソケット                             |  |  |

| TGC-064SAP                 | 64ピン・プラスチックQFP (GC-AB8タイプ)を実装できるように作られたターゲット・システムの基  |  |  |

|                            | 板と,NP-64GC-TQを接続するための変換アダプタ                          |  |  |

| ID78K0-NS                  | IE-78K0-NS用統合ディバッガ                                   |  |  |

| SM78K0                     | 78K/0シリーズ共通のシステム・シミュレータ                              |  |  |

| DF780988                   | μ PD780988サブシリーズ用デバイス・ファイル                           |  |  |

#### 注 開発中

# ・インサーキット・エミュレータ IE-78001-R-Aを使用する場合

| IE-78001-R-A     | 78K/0シリーズ共通のインサーキット・エミュレータ                                          |

|------------------|---------------------------------------------------------------------|

| IE-70000-98-IF-C | ホスト・マシンとしてPC-9800シリーズ(ノート型パソコンを除く)を使用するときのインタフェー                    |

|                  | ス・アダプタ(Cバス対応)                                                       |

| IE-70000-PC-IF-C | ホスト・マシンとしてIBM PC/AT互換機を使用するときのインタフェース・アダプタ(ISAバス対応)                 |

| IE-70000-PCI-IF  | ホスト・マシンとしてPCIバスを内蔵したパソコンを使用するときに必要なアダプタ                             |

| IE-78000-R-SV3   | ホスト・マシンとしてEWSを使用するときのインタフェース・アダプタとケーブル                              |

| IE-780988-NS-EM4 | μPD780988サブシリーズをエミュレーションするためのエミュレーション・ボード                           |

| IE-78K0-NS-P01   | μPD780988サブシリーズをエミュレーションするときに必要なI/Oボード                              |

| IE-78K0-R-EX1    | IE-780988-NS-EM4 + IE-78K0-NS-P01をIE-78001-R-A上で使用するときに必要なエミュレーション・ |

|                  | プローブ変換ボード                                                           |

| EP-78240CW-R     | 64ピン・プラスチック・シュリンクDIP(CWタイプ)用エミュレーション・プローブ                           |

| EP-78240GC-R     | 64ピン・プラスチックQFP(GC-AB8タイプ)用エミュレーション・プローブ                             |

| EV-9200GC-64     | 64ピン・プラスチックQFP(GC-AB8タイプ)用に作られたターゲット・システムの基板上に実装する                  |

|                  | ソケット                                                                |

| ID78K0           | IE-78001-R-A用統合ディバッガ                                                |

| SM78K0           | 78K/0シリーズ共通のシステム・シミュレータ                                             |

| DF780988         | μ PD780988サプシリーズ用デバイス・ファイル                                          |

|                  |                                                                     |

## **(4) リアルタイム**OS

| RX78K/0 | 78K/0シリーズ用リアルタイムOS |

|---------|--------------------|

| MX78K0  | 78K/0シリーズ用OS       |

#### (5) 開発ツールを使用する際の注意

- ・ID78K0-NS, ID78K0, SM78K0は, DF780988と組み合わせて使用します。

- ・CC78K/0, RX78K/0は, RA78K/0およびDF780988と組み合わせて使用します。

- ・FL-PR2, FL-PR3, FA-64CW, FA-64GC, NP-64CW, NP-64GC, NP-64GC-TQは,株式会社内藤電誠町田製作 所(TEL(044)822-3813)の製品です。ご購入の際はNEC特約店にご相談ください。

- ・TGC-064SAPは,東京エレテック株式会社の製品です。

問い合わせ先: 大丸興業株式会社 東京電子部 (TEL (03) 3820-7112)

大阪電子部 (TEL(06)6244-6672)

- ・3rdパーティ製開発ツールについては,78K/0**シリーズ セレクション・ガイド (**U11126J**)** を参照してください。

- ・各ソフトウエアに対応するホスト・マシンとOSは次のとおりです。

| ホスト・マシン   | PC                             | EWS                                |

|-----------|--------------------------------|------------------------------------|

| [08]      | PC-9800シリーズ [ Windows™ ]       | HP9000シリーズ700™ [ HP-UX™ ]          |

|           | IBM PC/AT互換機 日本語 / 英語Windows ] | SPARCstation™ [ SunOS™, Solaris™ ] |

| ソフトウエア    |                                | NEWS™ (RISC) [NEWS-OS™]            |

| RA78K/0   | 注                              |                                    |

| CC78K/0   | 注                              |                                    |

| ID78K0-NS |                                | -                                  |

| ID78K0    |                                |                                    |

| SM78K0    |                                | -                                  |

| RX78K/0   | 注                              |                                    |

| MX78K0    | 注                              |                                    |

注 DOSベースのソフトウエアです。

# ★ 付録 B. 関連資料

#### デバイスの関連資料

| 資 料 名                                             | 資料番号    |         |  |  |

|---------------------------------------------------|---------|---------|--|--|

|                                                   | 和文      | 英 文     |  |  |

| μPD780988サブシリーズ ユーザーズ・マニュアル                       | U13029J | U13029E |  |  |

| µРD780982, 780983, 780984, 780986, 780988 データ・シート | U12804J | U12804E |  |  |

| μPD78F0988 データ・シート                                | この資料    | U12805E |  |  |

| μPD780988サブシリーズ アプリケーション・ノート インバータ制御編             | U13119J | U13119E |  |  |

| μ PD780988サブシリーズ 特殊機能レジスタ活用表                      | U12806J | -       |  |  |

| 78K/0シリーズ ユーザーズ・マニュアル 命令編                         | U12326J | U12326E |  |  |

| 78K/0シリーズ インストラクション活用表                            | U10903J | -       |  |  |

| 78K/0シリーズ インストラクション・セット                           | U10904J | -       |  |  |

# 開発ツールの資料 (ユーザーズ・マニュアル)

| 資料名                           | 資料番号          |         |          |  |

|-------------------------------|---------------|---------|----------|--|

|                               |               | 和文      | 英 文      |  |

| RA78KO アセンブラ・パッケージ            | 操作編           | U11802J | U11802E  |  |

|                               | アセンブリ言語編      | U11801J | U11801E  |  |

|                               | 構造化アセンブリ言語編   | U11789J | U11789E  |  |

| RA78Kシリーズ 構造化アセンブラ・プリプロセッサ    |               | U12323J | EEU-1402 |  |

| CC78K0 Cコンパイラ                 | 操作編           | U11517J | U11517E  |  |

|                               | 言語編           | U11518J | U11518E  |  |

| CC78KO Cコンパイラ アプリケーション・ノート    | プログラミング・ノウハウ編 | U13034J | U13034E  |  |

| IE-78K0-NS                    |               | 作成予定    | 作成予定     |  |

| IE-78001-R-A                  |               | 作成予定    | 作成予定     |  |

| IE-780988-NS-EM4              |               | 作成予定    | 作成予定     |  |

| EP-78240                      |               | EEU-986 | U10332E  |  |

| SM78K0 システム・シミュレータ Windowsベース | レファレンス編       | U10181J | U10181E  |  |

| SM78Kシリーズ システム・シミュレータ         | 外部部品ユーザオープン   | U10092J | U10092E  |  |

|                               | インタフェース仕様編    |         |          |  |

| ID78K0-NS 統合ディバッガ Windowsベース  | レファレンス編       | U12900J | U12900E  |  |

| ID78K0 統合ディバッガ EWSベース         | レファレンス編       | U11151J | -        |  |

| ID78K0 統合ディバッガ PCベース          | レファレンス編       | U11539J | U11539E  |  |

| ID78K0 統合ディバッガ Windowsベース     | ガイド編          | U11649J | U11649E  |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 組み込み用ソフトウエアの資料 (ユーザーズ・マニュアル)

| 資 料 名               |         | 資料番号    |   |         |  |

|---------------------|---------|---------|---|---------|--|

|                     |         | 和       | 文 | 英 文     |  |

| 78K/0シリーズ リアルタイムOS  | 基礎編     | U11537J |   | U11537E |  |

|                     | インストール編 | U11536J |   | U11536E |  |

| 78K/0シリーズ用OS MX78K0 | 基礎編     | U12257J |   | U12257E |  |

## その他の資料

| 資 料 名                                                         | 資料番号    |         |  |  |

|---------------------------------------------------------------|---------|---------|--|--|

|                                                               | 和文      | 英文      |  |  |

| SEMICONDUCTORS SELECTION GUIDE Products & Packages ( CD-ROM ) | X13769X |         |  |  |

| 半導体デバイス 実装マニュアル                                               | C10535J | C10535E |  |  |

| NEC半導体デバイスの品質水準                                               | C11531J | C11531E |  |  |

| NEC半導体デバイスの信頼性品質管理                                            | C10983J | C10983E |  |  |

| 静電気放電(ESD)破壊対策ガイド                                             | C11892J | C11892E |  |  |

| 半導体 品質 / 信頼性ハンドブック                                            | C12769J | -       |  |  |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                                      | U11416J | -       |  |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

## CMOSデバイスの一般的注意事項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース,または導電性の緩衝材,金属ケースなどを利用し,組み立て工程にはアースを施してください。プラスチック板上に放置したり,端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

FIPは,日本電気株式会社の登録商標です。

IEBusは,日本電気株式会社の商標です。

Windowsは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

NEWS, NEWS-OSは, ソニー株式会社の商標です。

関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

- 本資料は、この製品の企画段階で作成していますので、予告なしに内容を変更することがあります。また本資料で扱う製品の製品化を中止することがあります。

- ◆ 文書による当社の承諾なしに本資料の転載複製を禁じます。

- 本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に 起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんの でご了承ください。

- ◆本資料に記載された回路,ソフトウエア,及びこれらに付随する情報は,半導体製品の動作例,応用例を説明するためのものです。従って,これら回路・ソフトウエア・情報をお客様の機器に使用される場合には,お客様の責任において機器設計をしてください。これらの使用に起因するお客様もしくは第三者の損害に対して,当社は一切その責を負いません。

- 当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート/データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

M5 98.8

#### --- お問い合わせ先-

#### 【技術的なお問い合わせ先】

NEC半導体テクニカルホットライン(インフォメーションセンター) 電話: 044-548-8899 FAX: 044-548-7900

(電話:午前9:00~12:00,午後1:00~5:00) F-mail: s-info@saed.tmg.nec.co.jp

#### 【営業関係お問い合わせ先】

| 半導体第                                              | 一 販 売 事 業 部<br>二 販 売 事 業 部<br>三 販 売 事 業 部                                                     | 〒108-8001                                                                                                                    | 東京都港区芝5 - 7                                                                                          | - 1 (E              | 日本電気本社ビル)                                                                                                                                                                   | (03)3                                           | 454–111            | 1                                                                                                                                    |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 中部支社                                              | 半導体第一販売部<br>半導体第二販売部                                                                          | 〒460-8525                                                                                                                    | 愛知県名古屋市中区                                                                                            | 錦1-17-              | - 1 (日本電気中部ビル)                                                                                                                                                              |                                                 | 222-217<br>222-219 |                                                                                                                                      |

| 関西支社                                              | 半導体第一販売部<br>半導体第二販売部<br>半導体第三販売部                                                              |                                                                                                                              | 大阪府大阪市中央区城見1 - 4 - 24 (日本電気関西ビル)                                                                     |                     |                                                                                                                                                                             | (06)6945-3178<br>(06)6945-3200<br>(06)6945-3208 |                    |                                                                                                                                      |

| 北東岩郡い長水土群太海北支支支支支支支支支支支支支支支支支支支支支支支支支支支支支支支支支支方方。 | 仙台 (022)<br>盛岡 (019)<br>郡山 (024)<br>いわき (024)<br>長岡 (025)<br>水戸 (029)<br>土浦 (029)<br>高崎 (027) | 251-5599<br>267-8740<br>2651-4344<br>1923-5511<br>6)21-5511<br>8)36-2155<br>1226-1717<br>8)23-6161<br>1326-1255<br>6)46-4011 | 字小甲唇<br>即位<br>事实<br>事实<br>事实<br>事实<br>事实<br>等<br>等<br>等<br>等<br>等<br>等<br>等<br>等<br>等<br>等<br>等<br>等 | 宇小甲松静立大千横津宮山府本岡川宮葉浜 | (028)621-2281<br>(0285)24-5011<br>(055)224-4141<br>(0263)35-1662<br>(054)254-4794<br>(042)526-5981,6167<br>(048)649-1415<br>(043)238-8116<br>(045)682-4524<br>(059)225-7341 | 北京神中国政立支社社社社社社社社社社社社社社社社立支支支支支支支支支支支支支支支支支      | 金京神広鳥岡松福沢都戸島取山山岡   | (076)232-7303<br>(075)344-7824<br>(078)333-3854<br>(082)242-5504<br>(0857)27-5311<br>(086)225-4455<br>(089)945-4149<br>(092)261-2806 |

C99 1