この資料は暫定版であり、今後変更することがあります。

μ PD70F4017, 70F4018

- V850E2/SK4-H-

# ルネサスマイクロコンピュータ

R01DS0108JJ0002 Rev.0.02 2012.01.31

$\mu$ PD70F4017, 70F4018 は、リアルタイム制御向け 32 ビット・シングルチップ・マイクロコントローラ「V850 マイコン」の一製品です。32 ビット CPU, ROM, RAM, 割り込みコントローラ、シリアル・インタフェース、タイマ/カウンタ、様々なバス・ネットワーク(CAN, MOST®(MediaLB®)、イーサネット)などを 1 チップに集積しています。

詳しい機能説明などは下記ユーザーズ・マニュアルに記載しております。設計の際には必ずお読みください。

V850E2/Sx4-H ハードウエア編: R01UH0107J

V850E2M アーキテクチャ編: R01US0001J

#### 用 途

〇カー・オーディオをはじめとするカー・マルチメディア機器

# 目 次

| 1. | 概要.        |       |                                                  | 16 |

|----|------------|-------|--------------------------------------------------|----|

|    | 1.1        | 端子名和  | <b>陈について</b>                                     | 16 |

|    |            | 1.1.1 | 兼用機能端子                                           | 16 |

|    |            | 1.1.2 | 電源端子                                             | 16 |

|    | 1.2        |       | ループ                                              |    |

|    | 1.3        |       | 定条件                                              |    |

|    |            | 1.3.1 | - AC 特性の測定条件                                     |    |

| 2. | 絶対晶        |       | 恪                                                |    |

|    | 2.1        |       | 王<br>-                                           |    |

|    | 2.2        | •     | <b>電圧</b>                                        |    |

|    | 2.3        |       | <b>電流</b>                                        |    |

| _  |            | 2.3.1 | 温度特性                                             |    |

| 3. |            |       | ク                                                |    |

|    | 3.1        |       | 読の要件                                             |    |

|    |            | 3.1.1 | グランド端子の定義                                        |    |

|    |            | 3.1.2 | 電源端子の定義・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |    |

|    | 3.2<br>3.3 |       | 給領域の定義                                           |    |

|    | 3.3        | 电源电源  | ェ                                                |    |

|    |            | 3.3.2 | AWO 电源内蔵レイュレータ行性                                 |    |

|    |            | 3.3.2 | 電圧の傾き                                            |    |

|    |            | 3.3.4 | 電圧の傾さ                                            |    |

|    | 3.4        |       | 王の電源立ち上げ/電源立ち下げ順序(使用条件)                          |    |

|    | 0.4        | 3.4.1 | 条件 1                                             |    |

|    |            | 3.4.2 | 条件 2                                             |    |

|    |            | 3.4.3 | 条件 3                                             |    |

|    |            | 3.4.4 | 条件 4                                             |    |

|    |            | 3.4.5 | 条件 5                                             |    |

|    |            | 3.4.6 | 条件 6                                             | 31 |

| 4. | クロ・        | ック発   | 生回路                                              | 32 |

| •• | 4.1        |       | <b>ユーニャー</b> ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |    |

|    | 4.2        |       | ロック周波数                                           |    |

|    | 4.3        | 発振回記  | 格特性                                              | 32 |

|    |            | 4.3.1 | メイン発振回路(MainOsc)特性                               | 32 |

|    |            | 4.3.2 | サブ発振回路(SubOsc)特性                                 | 34 |

|    |            | 4.3.3 | 内蔵発振器特性                                          | 34 |

|    | 4.4        | PLL 特 | 性                                                | 34 |

| 5. | 入出         | カスペ   | ック                                               | 35 |

|    | 5.1        |       | 特 <b>性</b>                                       |    |

|    |            | 5.1.1 | PgE0                                             |    |

|    |            | 5.1.2 | PgE1                                             |    |

|    |            | 5.1.3 | PgB0                                             |    |

|    |            | 5.1.4 | PgA0                                             | 38 |

|    | 5.2            | 入出力容量                                        | 38 |

|----|----------------|----------------------------------------------|----|

| 6. | 電源電            | 電流スペック                                       | 39 |

|    | 6.1            | 1.2 V 電源電流スペック (A) グレード品                     |    |

|    | 6.2            | 3.3 V 電源電流スペック (A) グレード品                     | 41 |

|    | 6.3            | 1.2 V 電源電流スペック (A9) グレード品                    | 43 |

|    | 6.4            | 3.3 V 電源電流スペック (A9) グレード品                    | 45 |

| 7. | 入出             | カ VDD の AC タイミング制限事項                         | 47 |

| 8. |                | <b>幾能スペック</b>                                |    |

| Ο. | /미, 221<br>8.1 | 成fit ハ・ソフ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |    |

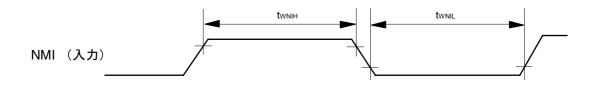

|    | 8.2            | NMI タイミング                                    |    |

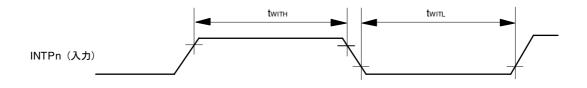

|    | 8.3            | 外部割り込みタイミング                                  |    |

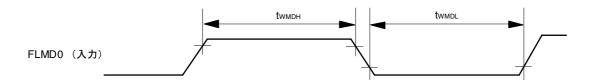

|    | 8.4            | FLMD0 タイミング                                  |    |

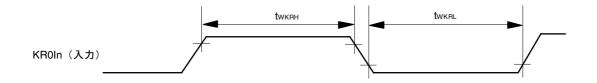

|    | 8.5            | キー・リターン・タイミング                                |    |

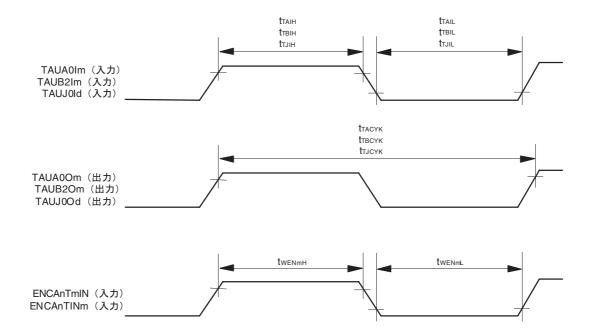

|    | 8.6            | タイマ・タイミング                                    |    |

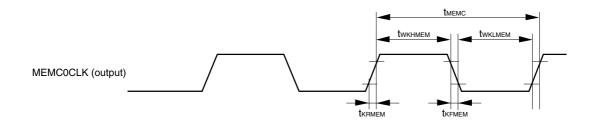

|    | 8.7            | MEMC クロック・タイミング                              |    |

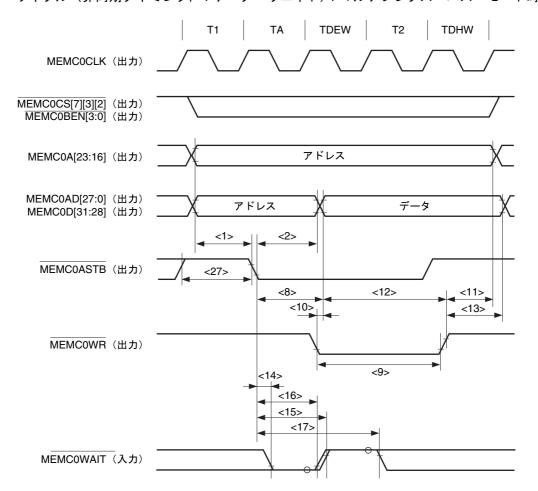

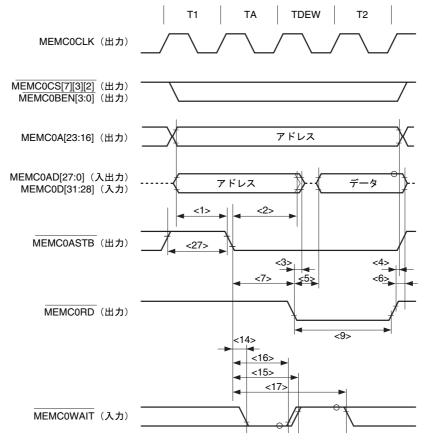

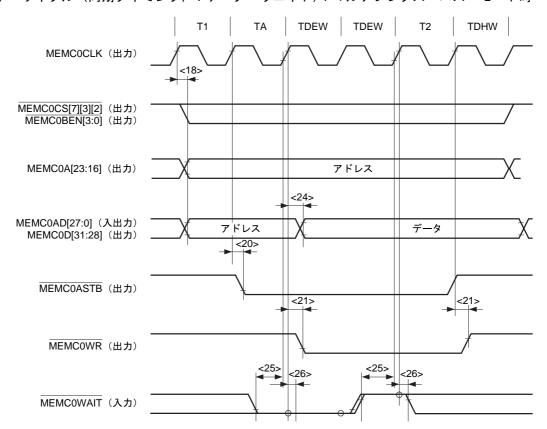

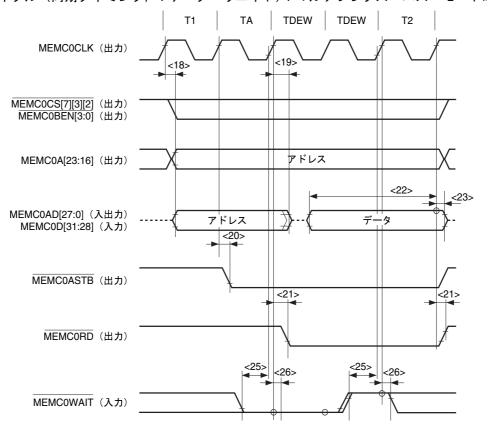

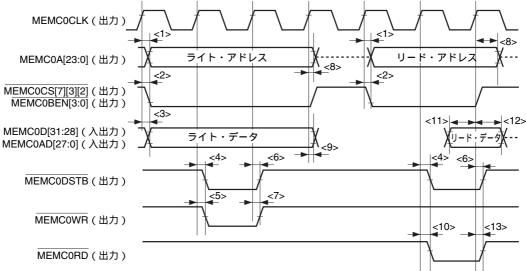

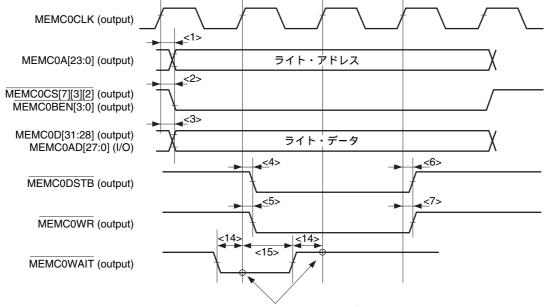

|    | 8.8            | マルチプレクス・バス・モード時の SRAM バス・タイミング               |    |

|    |                | 8.8.1 MEMCOCLK 非同期タイミング (リード/ライト・サイクル)       | 53 |

|    |                | 8.8.2 MEMCOCLK 同期タイミング (リード/ライト・サイクル)        | 54 |

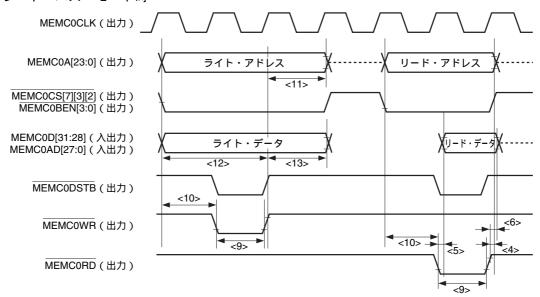

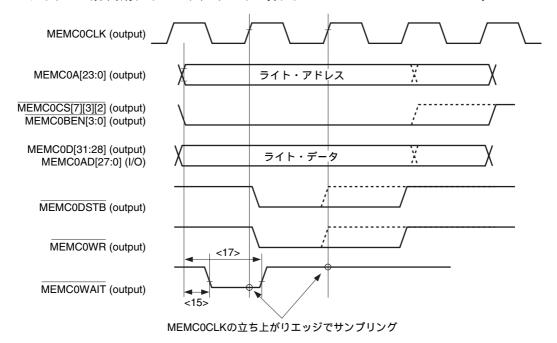

|    | 8.9            | セパレート・バス・モード時の SRAM バス・タイミング                 | 59 |

|    |                | 8.9.1 MEMCOCLK 非同期タイミング(リード/ライト・サイクル)        | 59 |

|    |                | 8.9.2 MEMCOCLK 同期タイミング(リード/ライト・サイクル)         | 60 |

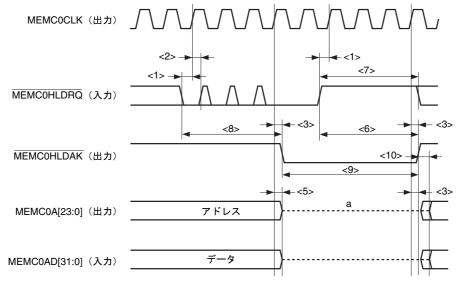

|    | 8.10           | MEMC ホールド・タイミング(非同期/同期タイミング)                 | 63 |

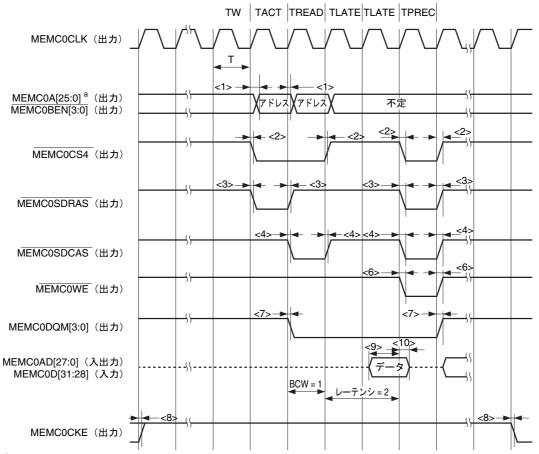

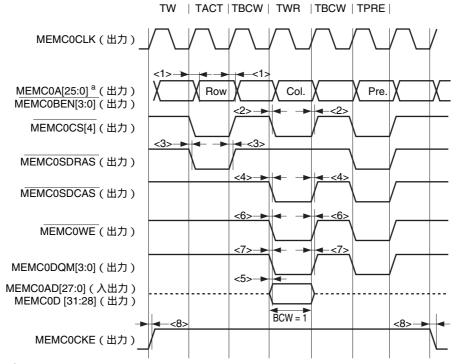

|    | 8.11           | SDRAM バス・タイミング                               | 64 |

|    | 8.12           | CSI タイミング                                    | 67 |

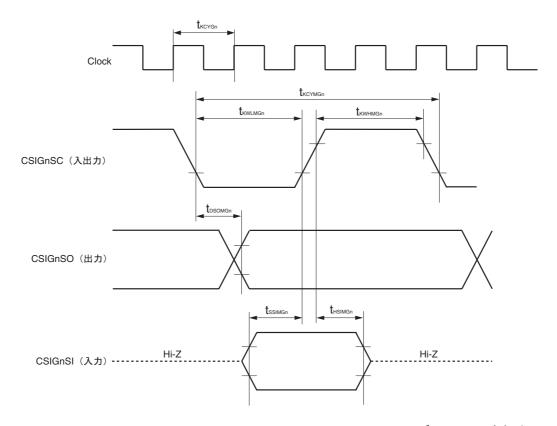

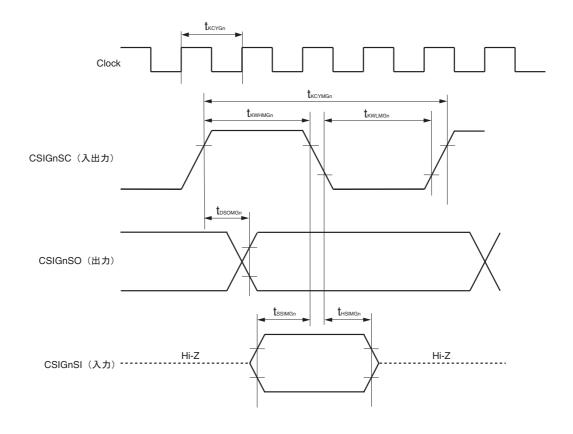

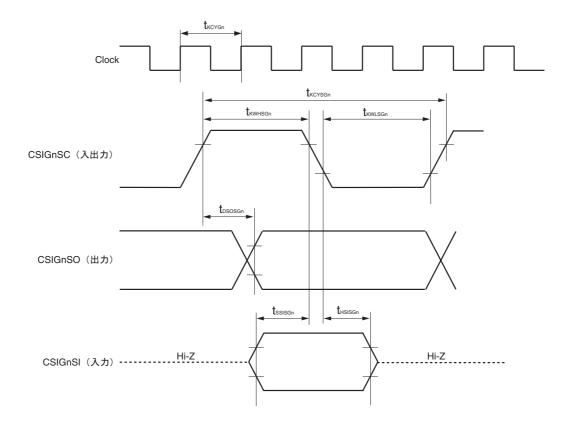

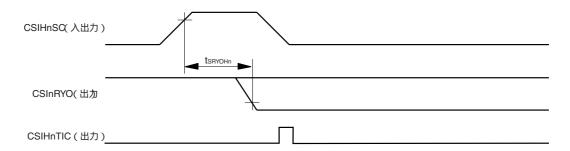

|    |                | 8.12.1 CSIG タイミング(マスタ・モード)                   | 67 |

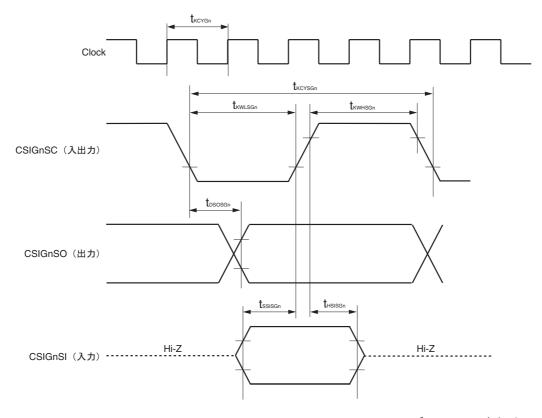

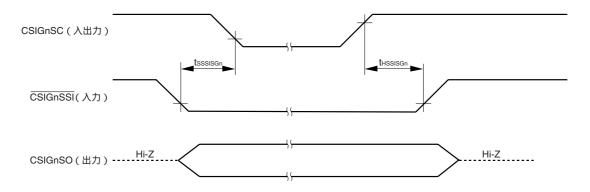

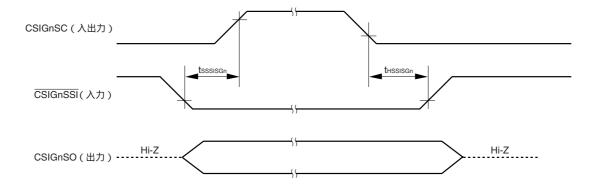

|    |                | 8.12.2 CSIG タイミング(スレーブ・モード)                  | 69 |

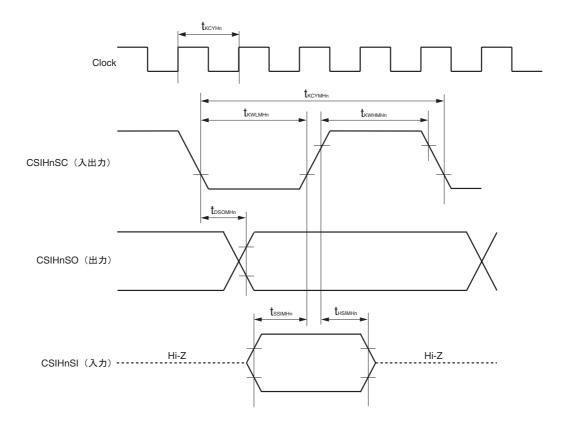

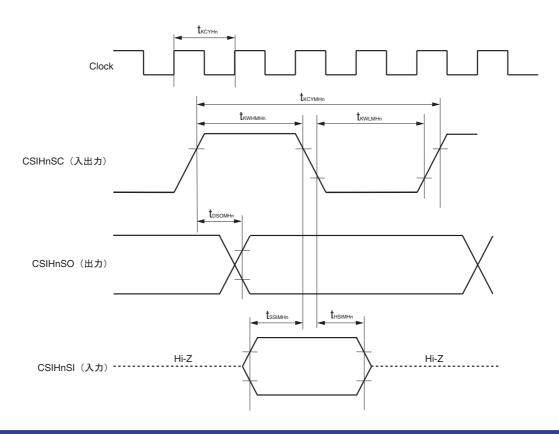

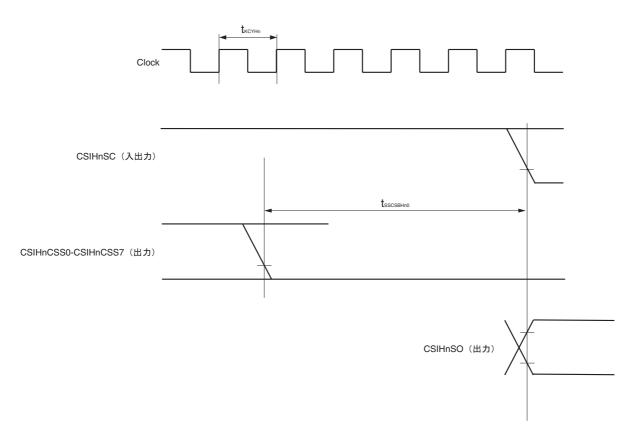

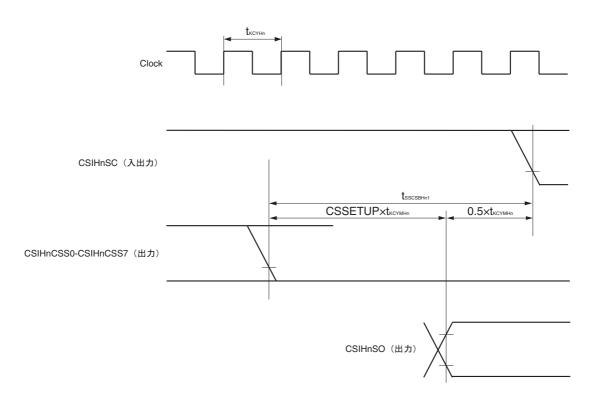

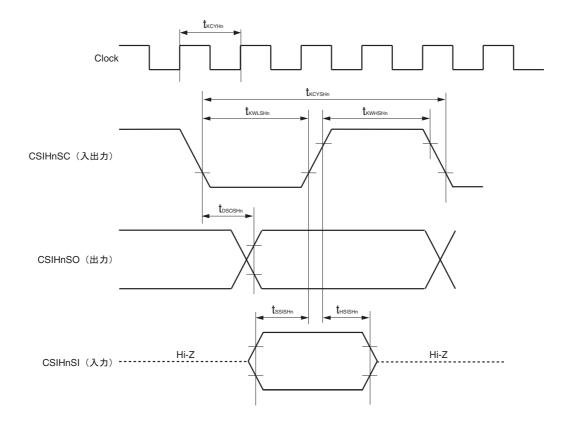

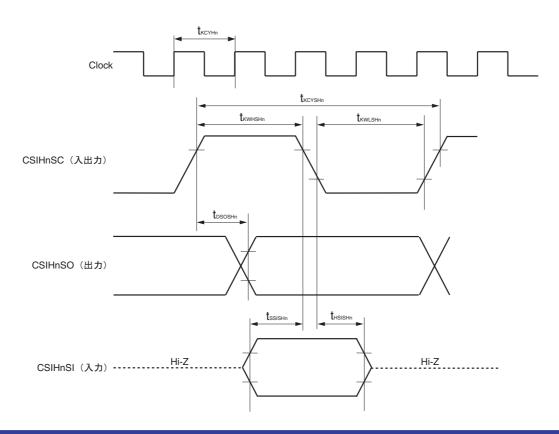

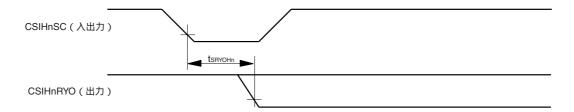

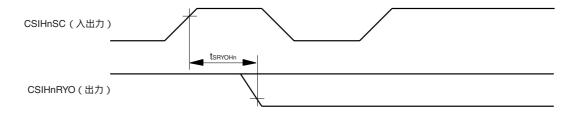

|    |                | 8.12.3 CSIH タイミング(マスタ・モード)                   | 72 |

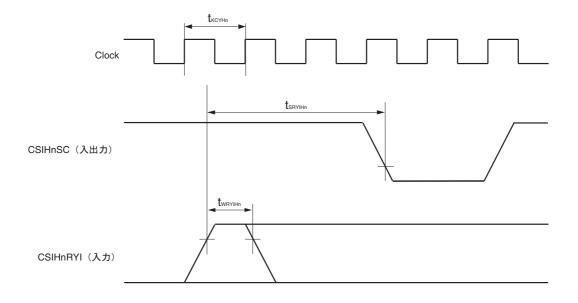

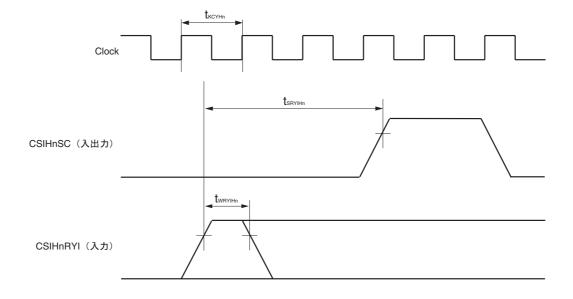

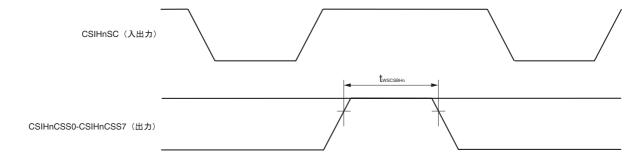

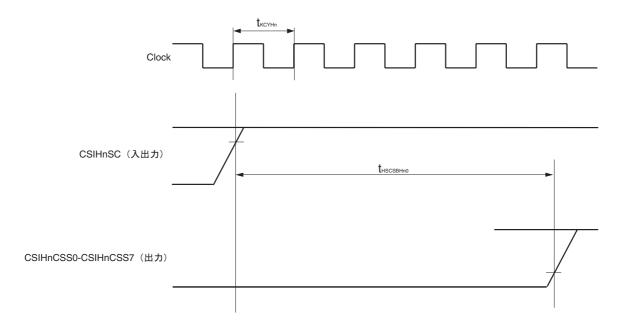

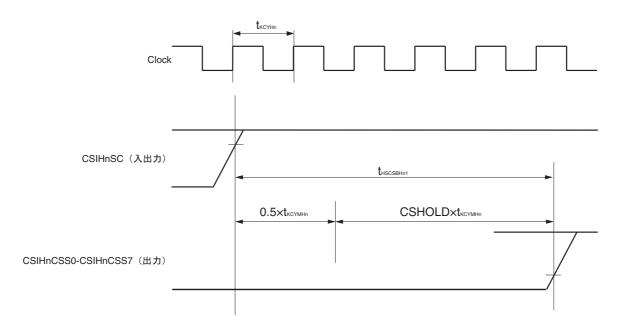

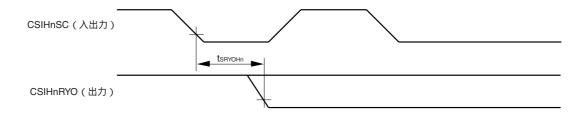

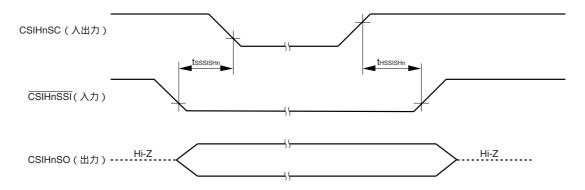

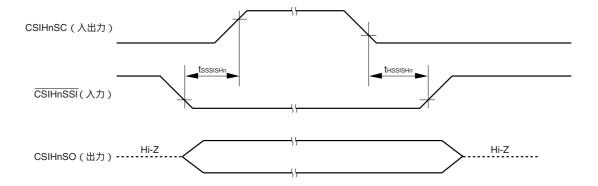

|    |                | 8.12.4 CSIH タイミング (スレーブ・モード)                 | 78 |

|    | 8.13           | UARTE タイミング                                  | 82 |

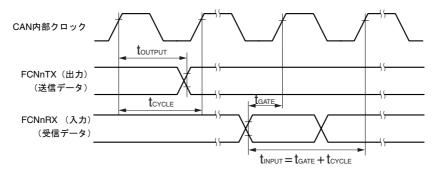

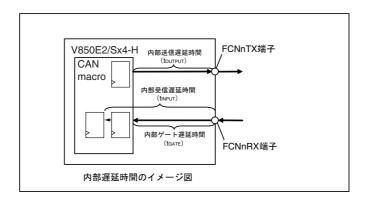

|    | 8.14           | CAN (FCN) タイミング                              |    |

|    | 8.15           | IEBus(IEBB)タイミング                             | 82 |

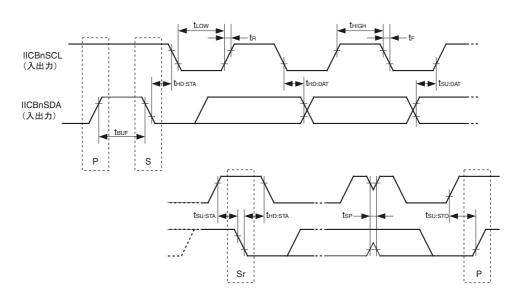

|    | 8.16           | I <sup>2</sup> C タイミング                       |    |

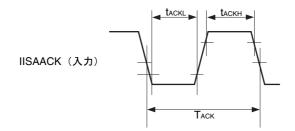

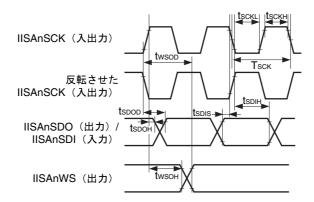

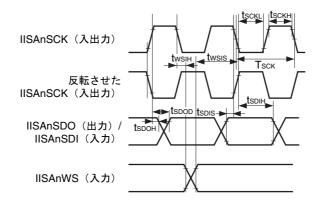

|    | 8.17           | IISA タイミング                                   |    |

|    |                | 8.17.1 IISA オーディオ・クロック・タイミング                 |    |

|    |                | 8.17.2 IISA マスタ・モード・タイミング                    | 86 |

|    |                | 8.17.3 IISA スレーブ・モード・タイミング                   | 87 |

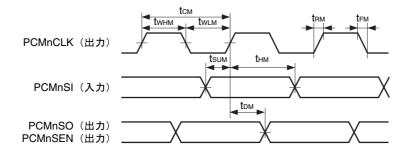

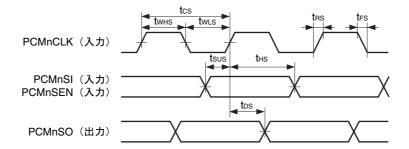

|    | 8.18           | PCM タイミング                                    |    |

|    |                | 8.18.1 PCM マスタ・モード・タイミング                     |    |

|    |                | 8.18.2 PCM スレーブ・モード・タイミング                    | 89 |

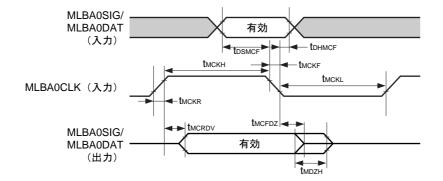

|    | 8.19           | MediaLB タイミング                                |    |

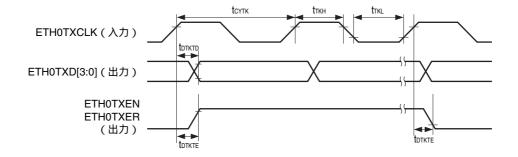

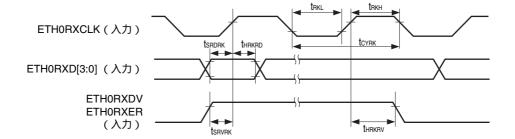

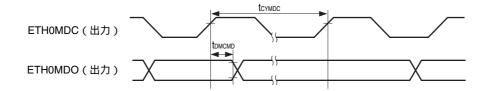

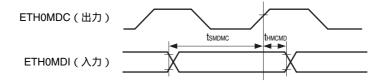

|    | 8.20           | イーサネット・タイミング                                 | 92 |

|    |                | 8.20.1 MII インタフェース                           |    |

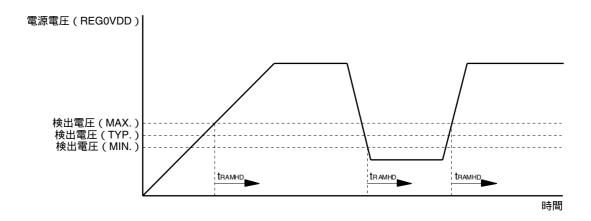

|    | 8.21           | RAM 保持フラグ特性                                  |    |

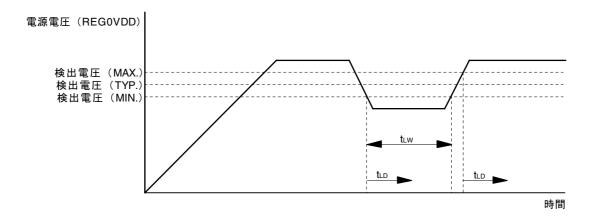

|    | 8.22           | LVI 回路特性                                     |    |

|    | 8.23           | A/D コンバータ特性                                  |    |

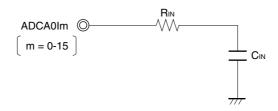

|    |                | 8.23.1 10 ビット分解能 A/D:ADCA0Im                 |    |

|    |                | 8.23.2 アナログ入力部の等価回路(参考値)                     | 98 |

## $\mu$ PD70F4017, 70F4018

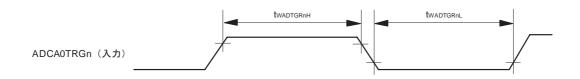

|     | 8.23.3  | A/D トリガタイミング98        |

|-----|---------|-----------------------|

| 9.  | フラッシュ   | ・メモリ・プログラミング特性99      |

|     | 9.1 基本特 | <b>±</b> 99           |

|     | 9.2 シリア | <b>レ書き込みオペレーション特性</b> |

| 10. | 外形図     |                       |

# 仕様概要

(1/3)

| 愛 称       |                                                   |     | SK4-H-1.5M         | SK4-H-2M                             |

|-----------|---------------------------------------------------|-----|--------------------|--------------------------------------|

|           | 品 名                                               |     | μ <b>PD70F4017</b> | μ <b>PD70F4018</b>                   |

| 内蔵メモリ     | 命令フラッシュ                                           |     | 1.5 MB             | 2 MB                                 |

|           | データ・フラッシュ                                         |     | 32 KB              |                                      |

|           | CPU RAM                                           |     | 128 KB             | 192 KB                               |

|           | HBUS-RAM                                          |     | 32 KB              |                                      |

|           | バックアップ RAM                                        |     | 32 KB              |                                      |

| 外部メモリ・イ   | ンタフェース(MEM(                                       | C)  | マルチプレクス/セパレー       | ノタフェース<br>- ト SRAM インタフェース<br>! ビット) |

| CPU       | CPU システム                                          |     | V850               | DE2M                                 |

|           | FPU                                               |     | あ                  | IJ                                   |

|           | CPU 周波数                                           |     | 160 MHz            | (MAX.)                               |

|           | システム保護機能                                          | MPU | あ                  | IJ                                   |

|           | (SPF)                                             | SRP | あり                 |                                      |

|           |                                                   | TSU | あり                 |                                      |

|           |                                                   | PPU | あり                 |                                      |

|           | 命令キャッシュ                                           |     |                    | アソシエイティブ<br>ウエイ)                     |

| DMA       |                                                   |     | 16 <del>チ</del>    | ヤネル                                  |

| 動作クロック    | メイン・クロック発<br>(MainOsc)                            | 振回路 | 4 MHz ~            | 20 MHz                               |

|           | 低速内蔵発振回路<br>(LS IntOsc)                           |     | 240 kHz            | (TYP.)                               |

|           | 高速内蔵発振回路<br>(HS IntOsc)<br>サブクロック発振回路<br>(SubOsc) |     | 8 MHz              | (TYP.)                               |

|           |                                                   |     | 32768 H.           | z (TYP.)                             |

|           | PLL0 (SSCG0)                                      |     | 160 MHz (MAX.)     |                                      |

|           | PLL1                                              |     | 120 MHz (MAX.)     |                                      |

|           | PLL2 (SSCG2)                                      |     | 120 MHz (MAX.)     |                                      |

| 1/0 ポート   |                                                   |     | 12                 | 27                                   |

| A/D コンバータ | A (ADCA)                                          |     | 16 チャネル , 10 ビット   |                                      |

(2/3)

|                 | 愛称                                  |        | SK4-H-1.5M             | SK4-H-2M           |

|-----------------|-------------------------------------|--------|------------------------|--------------------|

|                 | 品名                                  |        | μ <b>PD70F4017</b>     | μ <b>PD70F4018</b> |

| タイマ             | タイマ・アレイ・ユニット<br>A(TAUA), 16 ビット     |        | 1 ユニット × 16 チャネル       |                    |

|                 | タイマ・アレイ・3<br>B (TAUB) , 16 ビ        |        | 1ユニット×                 | 16 チャネル            |

|                 | タイマ・アレイ・ <i>二</i><br>(TAUJ), 32 ビット |        | 1 ユニット×                | 4 チャネル             |

|                 | リアルタイム・クロ<br>(RTCA) キャリブレン          |        | 1 ユ=                   | ニット                |

|                 | ウインドウ・ウォッ<br>グ・タイマ (WDT             |        | 2 チャ                   | ネル                 |

|                 | OS タイマ(OSTM                         | 1)     | 1 チャ                   | ·ネル                |

|                 | エンコーダ・タイ <sup>-</sup><br>(ENCA)     | ₹      | 2 チャ                   | ・ネル                |

| シリアル・           | CAN (FCN)                           |        | 2 チャネル (64 メッ          | ,セージ・バッファ)         |

| インタフェー<br>  ス   | LIN マスタ・コン<br>付き(LMA)UAR<br>(URTE)  |        | 5 チャネル                 |                    |

|                 | CSI (CSIG)                          |        | 2 チャネル                 |                    |

|                 | FIFO 付き CSI(CS                      | SIH)   | 3 チャネル                 |                    |

|                 | I <sup>2</sup> C (IICB)             |        | 4 チャネル                 |                    |

|                 | I <sup>2</sup> S (IISA)             |        | 6 チャネル                 |                    |

|                 | PCM インタフェース<br>(PCM)                |        | 2 チャネル                 |                    |

|                 | メディア・ローカル・バス<br>(MLB)               |        | 1チャ                    | ネル                 |

|                 | IEBus コントローラ                        | (IEBB) | 1 チャ                   | ネル                 |

| その他のイン<br>タフェース | イーサネット・コンラ(ETHA)                    | ントロー   | 1 ユニット(MII インタ         | <b>フェースをサポート</b> ) |

| 割り込み            | マスカブル                               | 外部     | 16                     |                    |

|                 |                                     | 内部     | 20                     | 8                  |

|                 | ノンマスカブル                             | 外部     | 1                      |                    |

|                 | (NMI)                               | 内部     | 2 (WDTA)               |                    |

| その他の機能          | パワーオン・クリア(POC)                      |        | M1 品<br>M2 品           |                    |

|                 | クロック・モニタ (CLMA)                     |        | 3 チャ<br>(メイン・クロック,高速内蔵 | • • •              |

|                 | データ CRC(DCR                         | RA)    | 1 チャネル                 |                    |

|                 | キー割り込み(KR                           | )      | 8 チャ                   | ネル                 |

|                 | オンチップ・デバッグ<br>(OCD)                 |        | b                      | ี                  |

| 電源監視            | 低電圧検出回路(L                           | VI)    | あり                     |                    |

|                 | DEEPSTOP モード<br>カ(WAKE)             | の表示出   | あ                      | ų                  |

(3/3)

|       | 愛 称    | SK4-H-1.5M         | SK4-H-2M                                                 |  |

|-------|--------|--------------------|----------------------------------------------------------|--|

| 品 名   |        | μ <b>PD70F4017</b> | μ <b>PD70F4018</b>                                       |  |

| 電源    | 内部供給   | 1.2                | 1.2 V <sup>a</sup>                                       |  |

|       | I/O 供給 | 3.3                | Va                                                       |  |

| 動作温度  |        |                    | (A) グレード品:-40° C ~ +85° C<br>(A9) グレード品:-40° C ~ +105° C |  |

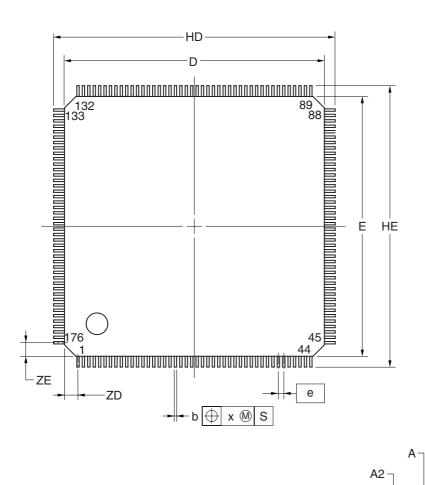

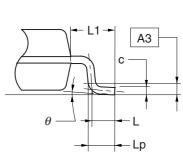

| パッケージ |        | 176 ピ              | 176 ピン QFP                                               |  |

a) 詳細については、3. 電源スペックを参照してください。

# オーダ名称

| オーダ名称                   | パッケージ         | 内蔵コード・<br>フラッシュ | 品質水準 | 備考       |

|-------------------------|---------------|-----------------|------|----------|

| μ PD70F4017M1GMA-GAR-G  | 176 ピン・プラスチック | 1.5 M バイト       | (A)  | POC 機能あり |

| μ PD70F4017M1GMA9-GAR-G | LQFP(ファインピッチ) |                 | (A9) |          |

| μ PD70F4017M2GMA-GAR-G  | (24×24)       |                 | (A)  | POC 機能なし |

| μ PD70F4017M2GMA9-GAR-G |               |                 | (A9) |          |

| μ PD70F4018M1GMA-GAR-G  |               | 2 M バイト         | (A)  | POC 機能あり |

| μ PD70F4018M1GMA9-GAR-G |               |                 | (A9) |          |

| μ PD70F4018M2GMA-GAR-G  |               |                 | (A)  | POC 機能なし |

| μ PD70F4018M2GMA9-GAR-G |               |                 | (A9) |          |

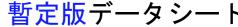

#### 端子接続図(Top View)

• 176 ピン・プラスチック LQFP (ファインピッチ) (24×24)

#### (1) 端子接続図

<sup>a)</sup> IC端子には,ロウ・レベルを入力してください。

備考 電源供給元の電源端子は、次のようになります。

- : E0VDD (JP0 / P0グループ、 Always-Onエリアの電カドメイン)

- : OSCVDD (X1/X2/XT1/XT2, Always-Onエリアの電カドメイン)

- : E1VDD (P1/P3グループ, Isolatedエリア0の電力ドメイン)

- : A0VDD (P10グループ、 Isolatedエリア0の電カドメイン)

- : B0VDD(P21/P24-P28グループ,Isolated エリア1の電カドメイン)

- : MLB0VDD(Isolated エリア1の電力ドメイン)

# (2) ピン配置

(1/5)

| ピン番号 | 名 称                                                                    |

|------|------------------------------------------------------------------------|

| 1    | P25_3/MEMC0AD3/TAUA0I3/TAUA0O3/IISA0SDI/IISA0SDO/CSIH0RYI/CSIH0RYO     |

| 2    | P25 4/MEMC0AD4/TAUA014/TAUA0O4/IISA1SDO/CSIH0SC                        |

| 3    | P25_5/MEMC0AD5/TAUA0I5/TAUA0O5/IISA1SCK                                |

| 4    | P25_6/MEMC0AD6/TAUA016/TAUA006/IISA1WS                                 |

| 5    | P25_7/MEMC0AD7/TAUA017/TAUA007/IISA1SDI/IISA1SDO                       |

| 6    | B0VSS                                                                  |

| 7    | BOVDD                                                                  |

| 8    | P25_8/MEMC0AD8/TAUA018/TAUA008/IISA2SDO/CSIH1SSI                       |

| 9    | P25_9/MEMC0AD9/TAUA019/TAUA0O9/IISA2SCK/CSIH1SI                        |

| 10   | P25_10/MEMC0AD10/TAUA0I10/TAUA0O10/IISA2WS/CSIH1SO                     |

| 11   | P25_11/MEMC0AD11/TAUA0I11/TAUA0O11/IISA2SDI/IISA2SDO/CSIH1RYI/CSIH1RYO |

| 12   | P25 12/MEMC0AD12/TAUA0I12/TAUA0O12/IISA3SDO/CSIH1SC                    |

| 13   | P25_13/MEMC0AD13/TAUA0I13/TAUA0O13/IISA3SCK                            |

| 14   | P25_14/MEMC0AD14/TAUA0I14/TAUA0O14/IISA3WS                             |

| 15   | P25_15/MEMC0AD15/TAUA0I15/TAUA0O15/IISA3SDI/IISA3SDO                   |

| 16   | REG0VDD                                                                |

| 17   | REG0C                                                                  |

| 18   | REG0VSS                                                                |

| 19   | RESET                                                                  |

| 20   | JP0_4/DCUTRST                                                          |

| 21   | IC                                                                     |

| 22   | JP0_0/INTP0/TAUJ0I0/TAUJ0O0/DCUTDI                                     |

| 23   | JP0_1/INTP1/TAUJ011/TAUJ0O1/DCUTDO                                     |

| 24   | JP0_2/INTP2/TAUJ0I2/TAUJ0O2/DCUTCK                                     |

| 25   | JP0_3/INTP3/TAUJ0I3/TAUJ0O3/DCUTMS                                     |

| 26   | JP0_5/NMI/RTCA0OUT/DCURDY                                              |

| 27   | X2                                                                     |

| 28   | X1                                                                     |

| 29   | OSCVSS                                                                 |

| 30   | OSCVDD                                                                 |

| 31   | XT1                                                                    |

| 32   | XT2                                                                    |

| 33   | FVDD                                                                   |

| 34   | E0VDD                                                                  |

| 35   | E0VSS                                                                  |

| 36   | FLMD0                                                                  |

| 37   | P0_0/TAUJ0I0/TAUJ0O0/INTP4/CSIG0SSI/IICB0SDA/RESETOUT                  |

| 38   | P0_1/TAUJ0I1/TAUJ0O1/INTP5/CSIG0SO/IICB0SCL/FLMD1                      |

(2/5)

| ピン番号 | 名 称                                                                            |  |  |  |

|------|--------------------------------------------------------------------------------|--|--|--|

| 39   | P0_2/TAUJ0I2/TAUJ0O2/INTP6/CSIG0SI/IICB1SDA                                    |  |  |  |

| 40   | P0_3/TAUJ0I3/TAUJ0O3/INTP7/CSIG0SC/IICB1SCL                                    |  |  |  |

| 41   | P0_4/IEBB0RX/FCN0TX/INTP8/CSIH1SI/URTE0TX/IICB2SDA                             |  |  |  |

| 42   | P0_5/FCN0RX/IEBB0TX/INTP9/URTE0RX/CSIH1SO/IICB2SCL                             |  |  |  |

| 43   | P0_6/FCN1TX/INTP10/CSIH1RYI/CSIH1RYO/CSIH1SSI/URTE10TX                         |  |  |  |

| 44   | P0_7/FCN1RX/INTP11/CSIH1SC/URTE10RX                                            |  |  |  |

| 45   | P0_8                                                                           |  |  |  |

| 46   | WAKE                                                                           |  |  |  |

| 47   | CVDD                                                                           |  |  |  |

| 48   | CVSS                                                                           |  |  |  |

| 49   | P1_0/TAUA010/TAUA000/IISAACK/URTE1RX/ETH0RXER/CSIH0CSS0                        |  |  |  |

| 50   | P1_1/TAUA011/TAUA001/IISA0SCK/CSIG4SSI/URTE1TX/ETH0RXD0/CSIH0CSS1              |  |  |  |

| 51   | P1_2/TAUA0I2/TAUA0O2/IISA0WS/CSIG4SO/ETH0RXD1/CSIH0CSS2                        |  |  |  |

| 52   | P1_3/TAUA013/TAUA003/IISA0SDI/IISA0SDO/CSIG4SI/ETH0RXD2/CSIH0CSS3              |  |  |  |

| 53   | P1_4/TAUA0I4/TAUA0O4/INTP12/IISA1SDO/CSIG4SC/ETH0RXD3/CSIH0CSS4                |  |  |  |

| 54   | P1_5/TAUA015/TAUA0O5/IISA1SCK/ENCA0AIN/ETH0TXD0/CSIH0SSI                       |  |  |  |

| 55   | P1_6/TAUA016/TAUA006/IISA1WS/ENCA0BIN/ETH0TXD1/CSIH0SI                         |  |  |  |

| 56   | E1VDD                                                                          |  |  |  |

| 57   | E1VSS                                                                          |  |  |  |

| 58   | P1_7/TAUA017/TAUA007/IISA1SDI/IISA1SDO/ENCA0ZIN/ETH0TXD2/CSIH0SO               |  |  |  |

| 59   | P1_8/TAUA018/TAUA008/INTP13/IISA2SDO/ENCA0TIN0/ETH0TXD3/CSIH0RYI/CSIH0RYO      |  |  |  |

| 60   | P1_9/TAUA019/TAUA009/IISA2SCK/ENCA0TIN1/ETH0TXEN/CSIH0SC                       |  |  |  |

| 61   | P1_10/TAUA0I10/TAUA0O10/IISA2WS/ENCA1AIN/CSIH0CSS5/URTE2RX/ETH0MDC             |  |  |  |

| 62   | P1_11/TAUA0I11/TAUA0O11/IISA2SDI/IISA2SDO/ENCA1BIN/CSIH0CSS6/ETH0CRSDV/URTE2TX |  |  |  |

| 63   | P1_12/TAUA0I12/TAUA0O12/INTP14/IISA3SDO/ENCA1ZIN/CSIH0CSS7/ETH0MDI/ETH0MDO     |  |  |  |

| 64   | P1_13/TAUA0I13/TAUA0O13/PCM0CLK/ENCA1TIN0/IICB1SCL                             |  |  |  |

| 65   | P1_14/TAUA0I14/TAUA0O14/PCM0SEN/ENCA1TIN1/URTE3TX/IICB3SDA                     |  |  |  |

| 66   | P1_15/TAUA0I15/TAUA0O15/PCM0SI/PCM0SO/URTE3RX/IICB3SCL                         |  |  |  |

| 67   | P3_0/TAUB2I1/TAUB2O1/PCM1CLK/KR0I0/CSIH1CSS0/IICB0SDA                          |  |  |  |

| 68   | P3_1/TAUB2I2/TAUB2O2/PCM1SEN/KR0I1/CSIH1CSS1/IICB0SCL                          |  |  |  |

| 69   | P3_2/TAUB2I3/TAUB2O3/PCM1SI/PCM1SO/KR0I2/CSIH1CSS2/IICB1SDA                    |  |  |  |

| 70   | E1VDD                                                                          |  |  |  |

| 71   | E1VSS                                                                          |  |  |  |

| 72   | P3_3/TAUB2I5/TAUB2O5/IISAACK/KR0I3/CSIH1CSS3/ETH0REFCLK/ETH0TXER               |  |  |  |

| 73   | P3_4/TAUB2I6/TAUB2O6/INTP15/IISA3SDO/KR0I4/CSIH1CSS4/ETH0COL                   |  |  |  |

| 74   | P3_5/TAUB2I7/TAUB2O7/IISA3SCK/KR0I5/CSIH1CSS5/ETH0TXCLK                        |  |  |  |

| 75   | P3_6/TAUB2I9/TAUB2O9/IISA3WS/KR0I6/CSIH1CSS6/ETH0RXDV                          |  |  |  |

| 76   | P3_7/TAUB2I10/TAUB2O10/IISA3SDI/IISA3SDO/KR0I7/CSIH1CSS7/ETH0RXCLK             |  |  |  |

| 77   | REG1VDD                                                                        |  |  |  |

(3/5)

| ピン番号 | 名 称                                                                     |

|------|-------------------------------------------------------------------------|

| 78   | CVDD                                                                    |

| 79   | REG1VSS                                                                 |

| 80   | PTCTL1                                                                  |

| 81   | P10_0/ADCA0I0                                                           |

| 82   | P10 1/ADCA0I1                                                           |

| 83   | P10 2/ADCA0I2                                                           |

| 84   | P10_3/ADCA0I3                                                           |

| 85   | P10_4/ADCA0I4                                                           |

| 86   | P10_5/ADCA0I5                                                           |

| 87   | P10_6/ADCA0I6                                                           |

| 88   | P10_7/ADCA0I7                                                           |

| 89   | A0VDD                                                                   |

| 90   | A0VSS                                                                   |

| 91   | AVREFP0                                                                 |

| 92   | AVREFM0                                                                 |

| 93   | P10_8/ADCA0I8                                                           |

| 94   | P10_9/ADCA0TRG0/ADCA0I9                                                 |

| 95   | P10_10/ADCA0TRG1/ADCA0I10                                               |

| 96   | P10_11/ADCA0TRG2/ADCA0I11                                               |

| 97   | P10_12/ADCA0I12                                                         |

| 98   | P10_13/ADCA0I13                                                         |

| 99   | P10_14/ADCA0I14                                                         |

| 100  | P10_15/ADCA0I15                                                         |

| 101  | CVDD                                                                    |

| 102  | CVSS                                                                    |

| 103  | P26_0/KR0I0/MEMC0A0/TAUB2I0/TAUB2O0/IISA4SDO/CSIH2SSI                   |

| 104  | P26_1/KR0I1/MEMC0A1/TAUB2I1/TAUB2O1/IISA4SCK/CSIH2SI                    |

| 105  | P26_2/KR0I2/MEMC0A2/TAUB2I2/TAUB2O2/IISA4WS/CSIH2SO                     |

| 106  | P26_3/KR0I3/MEMC0A3/TAUB2I3/TAUB2O3/IISA4SDI/IISA4SDO/CSIH2RYI/CSIH2RYO |

| 107  | P26_4/KR0I4/MEMC0A4/TAUB2I4/TAUB2O4/IISA5SDO/CSIH2SC                    |

| 108  | P26_5/KR0I5/MEMC0A5/TAUB2I5/TAUB2O5/IISA5SCK/CSIH2CSS0                  |

| 109  | P26_6/KR0I6/MEMC0A6/TAUB2I6/TAUB2O6/IISA5WS/CSIH2CSS1                   |

| 110  | P26_7/KR0I7/MEMC0A7/TAUB2I7/TAUB2O7/IISA5SDI/IISA5SDO/CSIH2CSS2         |

| 111  | P26_8/INTP8/MEMC0A8/TAUB2I8/TAUB2O8/IISA3SCK/CSIH2CSS3                  |

| 112  | BOVSS                                                                   |

| 113  | BOVDD                                                                   |

| 114  | P26_9/INTP9/MEMC0A9/TAUB2I9/TAUB2O9/IISA3WS/CSIH2CSS4                   |

| 115  | P26_10/INTP10/MEMC0A10/TAUB2I10/TAUB2O10/IISA2SCK/CSIH2CSS5             |

| 116  | P26_11/INTP11/MEMC0A11/TAUB2I11/TAUB2O11/IISA2WS/CSIH2CSS6              |

(4/5)

| ピン番号 | 名 称                                                          |

|------|--------------------------------------------------------------|

| 117  | P26_12/INTP12/MEMC0A12/TAUB2I12/TAUB2O12/IISA0SCK/CSIH2CSS7  |

| 118  | P26_13/INTP13/MEMC0A13/TAUB2I13/TAUB2O13/IISA0WS             |

| 119  | P26_14/INTP14/MEMC0A14/TAUB2I14/TAUB2O14/IISA5SDI/IISA5SDO   |

| 120  | P26_15/INTP15/MEMC0A15/TAUB2I15/TAUB2O15/IISA4SDI/IISA4SDO   |

| 121  | P27_0/INTP0/MEMC0A16/IISA3SDI/IISA3SDO/CSIH1CSS0             |

| 122  | P27_1/INTP1/MEMC0A17/IISA2SDI/IISA2SDO/CSIH1CSS1             |

| 123  | P27_2/INTP2/MEMC0A18/IISA1SDI/IISA1SDO/CSIH1CSS2             |

| 124  | CVDD                                                         |

| 125  | cvss                                                         |

| 126  | P27_3/INTP3/MEMC0A19/IISA0SDI/IISA0SDO/CSIH1CSS3             |

| 127  | P27_4/INTP4/MEMC0A20/IISA0SCK/URTE10TX                       |

| 128  | P27_5/INTP5/MEMC0A21/IISA0WS/URTE10RX                        |

| 129  | P21_0/MEMC0BEN3/MEMC0DQM3/ETH0COL                            |

| 130  | P21_1/MEMC0BEN2/MEMC0DQM2/ETH0CRSDV                          |

| 131  | P21_2/MEMC0BEN1/MEMC0DQM1                                    |

| 132  | P21_3/MEMC0BEN0/MEMC0DQM0                                    |

| 133  | P21_4/MEMC0WR/IEBB0RX/URTE2TX/CSIG0SSI/MEMC0WE/IICB0SDA      |

| 134  | P21_5/MEMC0RD/URTE2RX/IEBB0TX/CSIG0SO/IICB0SCL               |

| 135  | BOVSS                                                        |

| 136  | B0VDD                                                        |

| 137  | P21_6/MEMC0CLK/URTE1TX/CSIG0SI/IICB1SDA                      |

| 138  | P21_7/MEMC0WAIT/URTE1RX/CSIG0SC/IICB1SCL                     |

| 139  | P21_8/MEMC0SDRAS/IICB3SDA                                    |

| 140  | P21_9/MEMC0CS2/MEMC0SDCAS/IICB3SCL                           |

| 141  | P21_10/MEMC0CS3/FCN1RX                                       |

| 142  | P21_11/MEMC0CS4/FCN1TX                                       |

| 143  | P21_12/MEMC0CS7/CSIG4SSI                                     |

| 144  | P21_13/MEMC0HLDRQ/MEMC0DSTB/FCN0RX/MEMC0CKE/CSIG4SO/IICB2SDA |

| 145  | P21_14/MEMC0HLDAK/URTE0RX/FCN0TX/CSIG4SI/IICB2SCL            |

| 146  | P21_15/MEMC0ASTB/URTE0TX/CSIG4SC                             |

| 147  | MLB0VSS                                                      |

| 148  | MLBA0SIG                                                     |

| 149  | MLBA0DAT                                                     |

| 150  | MLBA0CLK                                                     |

| 151  | MLB0VDD                                                      |

| 152  | P28_0/INTP6/MEMC0A22/MEMC0A24/IISA1SCK                       |

| 153  | P28_1/INTP7/MEMC0A23/MEMC0A25/IISA1WS                        |

| 154  | P24_0/MEMC0AD16/INTP0/CSIH0CSS0/ENCA0AIN/ETH0RXER            |

| 155  | P24_1/MEMC0AD17/INTP1/CSIH0CSS1/ENCA0BIN/ETH0RXD0            |

(5/5)

| ピン番号 | 名 称                                                             |  |  |

|------|-----------------------------------------------------------------|--|--|

| 156  | CVDD                                                            |  |  |

| 157  | CVSS                                                            |  |  |

| 158  | P24_2/MEMC0AD18/INTP2/CSIH0CSS2/ENCA0ZIN/ETH0RXD1               |  |  |

| 159  | P24_3/MEMC0AD19/INTP3/CSIH0CSS3/ENCA0TIN0/ETH0RXD2              |  |  |

| 160  | P24_4/MEMC0AD20/INTP4/CSIH0CSS4/ENCA0TIN1/ETH0RXD3              |  |  |

| 161  | P24_5/MEMC0AD21/INTP5/CSIH0CSS5/ETH0TXD0                        |  |  |

| 162  | P24_6/MEMC0AD22/INTP6/CSIH0CSS6/ETH0TXD1                        |  |  |

| 163  | BOVSS                                                           |  |  |

| 164  | BOVDD                                                           |  |  |

| 165  | P24_7/MEMC0AD23/INTP7/CSIH0CSS7/ETH0TXD2                        |  |  |

| 166  | P24_8/MEMC0AD24/INTP8/CSIH1CSS0/ENCA1AIN/ETH0TXD3               |  |  |

| 167  | P24_9/MEMC0AD25/INTP9/CSIH1CSS1/ENCA1BIN/ETH0TXEN               |  |  |

| 168  | P24_10/MEMC0AD26/INTP10/CSIH1CSS2/ENCA1ZIN/ETH0MDC              |  |  |

| 169  | P24_11/MEMC0AD27/INTP11/CSIH1CSS3/ENCA1TIN0/ETH0REFCLK/ETH0TXER |  |  |

| 170  | P24_12/MEMC0D28/INTP12/CSIH1CSS4/ENCA1TIN1/ETH0MDI/ETH0MDO      |  |  |

| 171  | P24_13/MEMC0D29/INTP13/CSIH1CSS5/ETH0TXCLK                      |  |  |

| 172  | P24_14/MEMC0D30/INTP14/CSIH1CSS6/ETH0RXDV                       |  |  |

| 173  | P24_15/MEMC0D31/INTP15/CSIH1CSS7/ETH0RXCLK                      |  |  |

| 174  | P25_0/MEMC0AD0/TAUA010/TAUA000/IISAACK/IISA0SDO/CSIH0SSI        |  |  |

| 175  | P25_1/MEMC0AD1/TAUA0I1/TAUA0O1/IISA0SCK/CSIH0SI                 |  |  |

| 176  | P25_2/MEMC0AD2/TAUA0I2/TAUA0O2/IISA0WS/CSIH0SO                  |  |  |

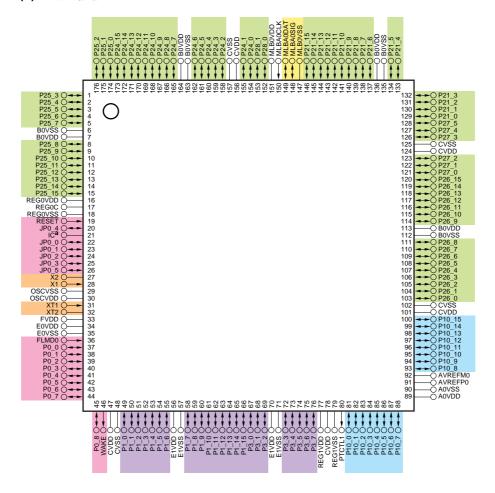

# 内部ブロック図

<sup>&</sup>lt;sup>a)</sup> M1品はPOC機能あり。M2品はPOC機能なし。

μ PD70F4017, 70F4018 1. 概要

## 1. 概要

#### 1.1 端子名称について

#### 1.1.1 兼用機能端子

| 周辺機能        | マクロ名に続く数字                     | 機能名             | 末尾の数字                 |

|-------------|-------------------------------|-----------------|-----------------------|

| マクロ名の<br>略称 | 同一周辺モジュールの<br>連番 <sup>a</sup> | 周辺マクロ端<br>子の機能名 | 同一端子名の連番 <sup>a</sup> |

a) 1つしかない場合は省略

- TAUA010, TAUA115

- URTE0TX, URTE0RX, URTE1TX, URTE1RX

- CSIH0SO, CSIH0SI, CSIH0SC,  $\overline{\text{CSIH0SSI}}$ , CSIH0RYI, CSIH0CSSO, CSIH1SO, CSIH1SI, CSIH1SC, CSIH1SSI, CSIH1RYI, CSIH1CSSO

#### 1.1.2 電源端子

| 機能 | 端子名に続く数字            | 電源の種類       |

|----|---------------------|-------------|

| 略称 | 各機能の連番 <sup>a</sup> | VDD または VSS |

a) 1つしかない場合は省略

- CVDD, E0VDD, REG0VSS

| 略称  | 機能                         |

|-----|----------------------------|

| С   | 内部用電源                      |

| REG | 内部レギュレータ用電源                |

| OSC | 発振回路用電源                    |

| F   | フラッシュ・モジュール用電源             |

| E   | ポート用電源                     |

| В   | ポート用電源                     |

| Α   | アナログ・モジュール用電源(A/D コンバータなど) |

| MLB | MediaLB 用電源                |

μ PD70F4017, 70F4018 1. 概要

## 1.2 端子グループ

| 略号    | ポート・グループの電源      | 関連ポート/関連端子                                          |

|-------|------------------|-----------------------------------------------------|

| PgE0  | E0VDD, E0VSS     | 関連ポート <u>: JP0,</u> P0<br>関連端子 : RESET, FLMD0, WAKE |

| PgE1  | E1VDD, E1VSS     | 関連ポート: P1, P3                                       |

| PgB0  | B0VDD, B0VSS     | 関連ポート : P21, P24 to P28                             |

| PgMLB | MLB0VDD, MLB0VSS | 関連端子 : MLBA0SIG, MLBA0DAT,<br>MLBA0CLK              |

| PgOSC | OSCVDD, OSCVSS   | 関連端子: X1, X2, XT1, XT2                              |

| PgA0  | A0VDD, A0VSS     | 関連ポート : P10                                         |

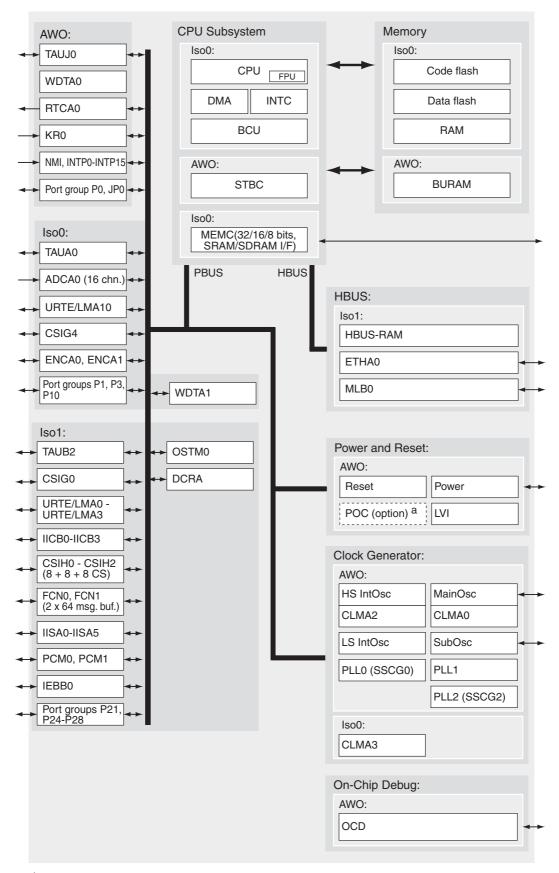

## 1.3 通常測定条件

#### 1.3.1 AC特性の測定条件

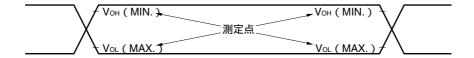

#### (1) AC テスト入力測定点

#### (2) AC テスト出力測定点

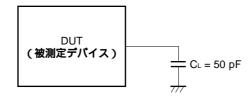

#### (3) 負荷条件

注意 回路構成により負荷容量が 50 pF を越える場合は、バッファを入れるなどして、このデバイスの負荷容量を 50 pF 以下にしてください。

μ PD70F4017, 70F4018 2. 絶対最大定格

# 2. 絶対最大定格

# 注意 1. IC 製品の出力(または入出力)端子同士を直結したり、VDD または VCC やGND に直結したりしないでください。

- 2. 各項目のうち1項目でも、また一瞬でも絶対最大定格を越えると、製品の品質を 損なう恐れがあります。つまり絶対最大定格とは、製品に物理的な損傷を与えか ねない定格値です。必ずこの定格値を越えない状態で、製品をご使用ください。 DC 特性と AC 特性に示す規格や条件が、製品の正常動作、品質保証の範囲です。

- 3. ハイ・インピーダンスとなる端子で出力の衝突を避けるタイミング設計をした外部回路では直結可能です。

#### 2.1 電源電圧

表 2-1 VDD

| 項目            | 略号      | 条件               | 定格                      | 単位 |

|---------------|---------|------------------|-------------------------|----|

| システム用電源電圧     | CVDD    |                  | - 0.5 <b>~</b> + 1.6    | V  |

|               | FVDD    |                  | - 0.5 <b>~</b> + 4.6    | V  |

|               | OSCVDD  |                  | - 0.5 <b>~</b> + 4.6    | V  |

|               | REG0VDD |                  | - 0.5 <b>~</b> + 4.6    | V  |

|               | REG1VDD |                  | - 0.5 <b>~</b> + 4.6    | V  |

| ポート用電源電圧      | E0VDD   |                  | - 0.5 <b>~</b> + 4.6    | V  |

|               | E1VDD   |                  | - 0.5 <b>~</b> + 4.6    | V  |

|               | B0VDD   |                  | - 0.5 <b>~</b> + 4.6    | V  |

| MediaLB 用電源電圧 | MLB0VDD |                  | - 0.5 <b>~</b> + 4.6    | V  |

| A/D コンバータ用    | A0VDD   |                  | - 0.5 <b>~</b> + 4.6    | V  |

| 電源電圧          | AVREFP0 | AVREFP0 ≦+ 4.6 V | $-0.3 \sim A0VDD + 0.3$ | V  |

表 2-2 VSS

| 項目            | 略号      | 条件 | 定格                      | 単位 |

|---------------|---------|----|-------------------------|----|

| システム用電源電圧     | CVSS    |    | - 0.5 <b>~</b> + 0.5    | V  |

|               | OSCVSS  |    | - 0.5 <b>~</b> + 0.5    | V  |

|               | REG0VSS |    | - 0.5 <b>~</b> + 0.5    | V  |

|               | REG1VSS |    | - 0.5 <b>~</b> + 0.5    | V  |

| ポート用電源電圧      | E0VSS   |    | - 0.5 <b>~</b> + 0.5    | V  |

|               | E1VSS   |    | - 0.5 <b>~</b> + 0.5    | V  |

|               | B0VSS   |    | - 0.5 <b>~</b> + 0.5    | V  |

| MediaLB 用電源電圧 | MLB0VSS |    | - 0.5 <b>~</b> + 0.5    | V  |

| A/D コンバータ用    | A0VSS   |    | - 0.5 <b>~</b> + 0.5    | V  |

| 電源電圧          | AVREFM0 |    | $-0.3 \sim A0VSS + 0.3$ | V  |

# 2.2 ポート電圧

表 2-3 ポート入力電圧

| 項目                | 端子グループ | 略号 | 条件              | 定格                         | 単位 |

|-------------------|--------|----|-----------------|----------------------------|----|

| 入力電圧 <sup>a</sup> | PgE0   | Vı | E0VDD ≦ 3.6 V   | $-0.5 \sim E0VDD + 0.5$    | V  |

|                   | PgE1   |    | E1VDD ≦ 3.6 V   | − 0.5 <b>~</b> E1VDD + 0.5 | V  |

|                   | PgB0   |    | B0VDD ≦ 3.6 V   | − 0.5 ~ B0VDD + 0.5        | V  |

|                   | PgMLB  |    | MLB0VDD ≦ 3.6 V | $-0.5 \sim MLB0VDD + 0.5$  | V  |

|                   | PgOSC  |    | OSCVDD ≦ 3.6 V  | $-0.5 \sim OSCVDD + 0.5$   | V  |

|                   | PgA0   |    | A0VDD ≤ 3.6V    | $-0.3 \sim A0VDD + 0.3$    | V  |

<sup>&</sup>lt;sup>3)</sup> 特に指定がないかぎり,兼用端子の特性はポート端子の特性と同じです 。

## 2.3 ポート電流

表 2-4 ハイ・レベル・ポート出力電流

| 項目     | 端子グループ | 略号  | 条件    | 定 格 (MAX.)   | 単位 |

|--------|--------|-----|-------|--------------|----|

| ハイ・レベル | PgE0   | Іон | 1 端子  | <b>- 10</b>  | mA |

| 出力電流   |        |     | 全端子合計 | <b>— 150</b> | mA |

|        | PgE1   |     | 1 端子  | <b>- 10</b>  | mA |

|        |        |     | 全端子合計 | <b>–</b> 120 | mA |

|        | PgB0   |     | 1 端子  | <b>– 10</b>  | mA |

|        |        |     | 全端子合計 | <b>–</b> 180 | mA |

|        | PgMLB  |     | 1 端子  | <b>- 10</b>  | mA |

|        |        |     | 全端子合計 | <b>- 30</b>  | mA |

|        | PgA0   |     | 1 端子  | <b>– 10</b>  | mA |

|        |        |     | 全端子合計 | <b>– 25</b>  | mA |

表 2-5 ロウ・レベル・ポート出力電流

| 項目     | 端子グループ | 略号  | 条件    | 定 格 (MAX.) | 単位 |

|--------|--------|-----|-------|------------|----|

| ロウ・レベル | PgE0   | lol | 1 端子  | 10         | mA |

| 出力電流   |        |     | 全端子合計 | 150        | mA |

|        | PgE1   |     | 1 端子  | 10         | mA |

|        |        |     | 全端子合計 | 120        | mA |

|        | PgB0   |     | 1 端子  | 10         | mA |

|        |        |     | 全端子合計 | 180        | mA |

|        | PgMLB  |     | 1 端子  | 10         | mA |

|        |        |     | 全端子合計 | 30         | mA |

|        | PgA0   |     | 1 端子  | 10         | mA |

|        |        |     | 全端子合計 | 25         | mA |

#### 温度特性 2.3.1

表 2-6 温度特性

| 項目     | 略号   | 条件         | 定 格                 | 単位 |

|--------|------|------------|---------------------|----|

| 保存温度   | Tstg |            | − 65 <b>~</b> + 150 | °C |

| 動作周囲温度 | TA   | (A) グレード品  | <b>− 40 ~ + 85</b>  | °C |

|        |      | (A9) グレード品 | - 40 <b>~</b> + 105 | °C |

#### 3. 電源スペック

#### 3.1 電源接続の要件

#### 3.1.1 グランド端子の定義

このデータ・シートでは、グランド端子を次のように定義します。 VSS = OSCVSS = REGnVSS = EnVSS = B0VSS = MLB0VSS = A0VSS = AVREFM0 = CVSS = FVSS = 0 V

詳細な端子名は次のようになります。

• REGnVSS: REG0VSS, REG1VSS

• EnVSS: E0VSS, E1VSS

#### 3.1.2 電源端子の定義

このデータ・シートでは、電源端子を次のように定義します。

EnVDD, B0VDD, FVDD, REGnVDD, OSCVDD, CVDD, A0VDD, AVREFP0, MLB0VDD

詳細な端子名は次のようになります。

• EnVDD: E0VDD, E1VDD

• REGnVDD: REG0VDD, REG1VDD

#### 3.2 電源供給領域の定義

V850E2/SK4-Hは、次に示す電源供給領域で構成されています。

- AWO (Always-Onエリア)

- Iso0 (Isolated エリア0)

- Iso1 (Isolated エリア1)

#### 3.3 電源電圧

表 3-1 電源電圧 (動作条件)

| 項目            | 略号      | 条件                          | MIN.  | TYP. | MAX.  | 単位 |

|---------------|---------|-----------------------------|-------|------|-------|----|

| システム用電源電圧     | CVDD    |                             | 1.1   |      | 1.3   | V  |

|               | FVDD    | b                           | а     |      | 3.6   | V  |

|               | OSCVDD  | b                           | а     |      | 3.6   | V  |

|               | REG0VDD | b                           | а     |      | 3.6   | V  |

|               | REG1VDD | b                           | а     |      | 3.6   | V  |

| ポート用電源電圧      | E0VDD   | b                           | а     |      | 3.6   | V  |

|               | E1VDD   | b                           | а     |      | 3.6   | V  |

|               | B0VDD   | b                           | а     |      | 3.6   | V  |

| MediaLB 用電源電圧 | MLB0VDD |                             | 3.135 | 3.3  | 3.6   | V  |

| A/D コンバータ用    | A0VDD   | 10 ビット分解能                   | 3     |      | 3.6   | V  |

| 電源電圧          | AVREFP0 | AVREFP0 - AVREFM0 > A0VDD/2 |       |      | A0VDD | V  |

a) M1 品: Vpoc M2 品: 2.7 V

V<sub>POC</sub>: POC 検出電圧

VPoc の詳細については、3.3.4 パワーオン・クリア回路 (POC) 特性を参照してください。

b) FVDD=OSCVDD=REG0VDD=REG1VDD=E0VDD=E1VDD=B0VDD

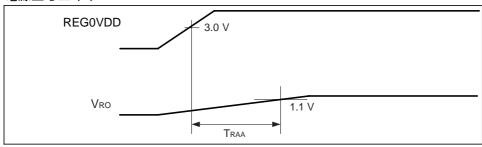

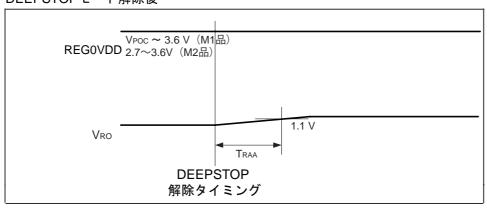

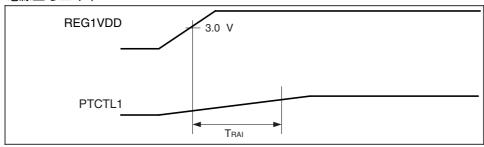

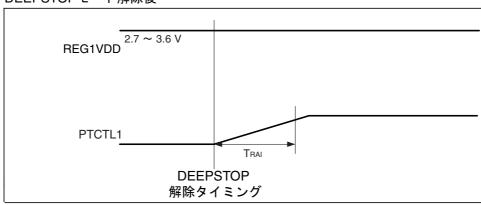

#### 3.3.1 AWO電源内蔵レギュレータ特性

表 3-2 AWO 電源内蔵レギュレータ特性

| 項目                   | 略号              | 条件                     | MIN. | TYP. | MAX. | 単位 |

|----------------------|-----------------|------------------------|------|------|------|----|

| 入力電圧                 | REG0VDD         |                        | а    |      | 3.6  | V  |

| 出力電圧                 | V <sub>RO</sub> |                        | 1.1  | 1.2  | 1.3  | V  |

| REGOC 端子の<br>キャパシタンス | REG0C           |                        | 3.29 | 4.7  | 6.11 | μF |

| 出力電圧安定時間             | Traa            | REG0VDD が 3.0 V に達したあと |      |      | 1    | ms |

|                      |                 | DEEPSTOP モード解除後        |      |      | 0.5  | ms |

M1 品:Vpoc M2 品:2.7 V Vpoc:POC 検出電圧

VPOC の詳細については、3.3.4 パワーオン・クリア回路(POC)特性を参照してください。

電源立ち上げ中

#### DEEPSTOPモード解除後

#### 3.3.2 Iso0/Iso1 電源制御特性

注意 PTCTL1 信号での外部パワートランジスタ制御は, M2 品(POC 機能なし)のみサポートします。

表 3-3 Iso0/Iso1 電源制御特性

| 項目                  | 略号      | 条件                     | MIN. | TYP. | MAX. | 単位 |

|---------------------|---------|------------------------|------|------|------|----|

| 入力電圧                | REG1VDD |                        | 2.7  |      | 3.6  | V  |

| CVDD 端子の<br>キャパシタンス | CVDD    |                        | 3.29 | 4.7  | 6.11 | μF |

| PTCTL1 安定時間         | Trai    | REG1VDD が 3.0 V に達したあと |      |      | 1    | ms |

|                     |         | DEEPSTOP モード解除後        |      |      | 0.5  | ms |

#### 電源立ち上げ中

#### DEEPSTOPモード解除後

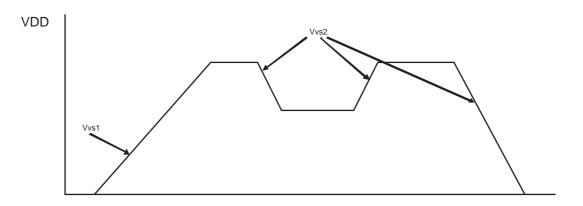

# 3.3.3 電圧の傾き

表 3-4 電圧の傾き

| 項目      | 略号                            | 条件        | MIN.   | TYP. | MAX.   | 単位   |

|---------|-------------------------------|-----------|--------|------|--------|------|

| 電圧の傾き1  | Vvs1                          | 0V ~ 3.6V | 0.18   |      | 1800.0 | V/ms |

| 電圧の傾き 2 | V <sub>VS2</sub> <sup>a</sup> |           | 0.0018 |      | 10.0   | V/ms |

<sup>a)</sup> 100μF 以上の外部容量を 3.3V 電源に接続してください。

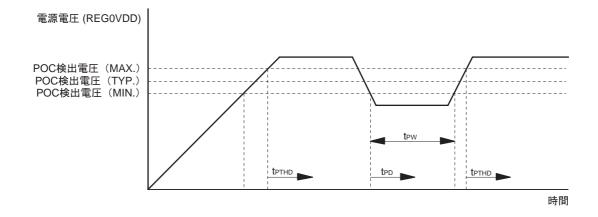

#### 3.3.4 パワーオン・クリア回路(POC)特性

注意 M1 品にはパワーオン・クリア回路(POC)があります。 M2 品にはパワーオン・クリア回路(POC)がありません。

表 3-5 パワーオン・クリア回路 (POC) 特性

| 項目                  | 略号            | 条件 | MIN. | TYP. | MAX. | 単位 |

|---------------------|---------------|----|------|------|------|----|

| POC 検出電圧            | VPOC          |    | 2.8  | 2.9  | 3.0  | V  |

| 応答時間 1 <sup>a</sup> | <b>t</b> ртно |    |      |      | 2    | ms |

| 応答時間 2 <sup>b</sup> | <b>t</b> PD   |    |      |      | 2    | ms |

| REG0VDD 最小幅         | tpw           |    | 0.2  |      |      | ms |

- <sup>a)</sup> POC 検出電圧を検出してからリセット信号(POCRES)を解除するまでの時間です。

- b) POC 検出電圧を検出してからリセット信号(POCRES)を発生するまでの時間です。

## 3.4 電源電圧の電源立ち上げ/電源立ち下げ順序(使用条件)

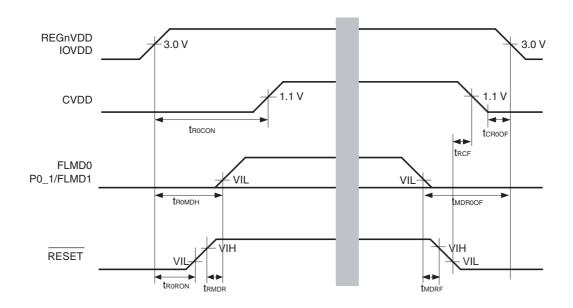

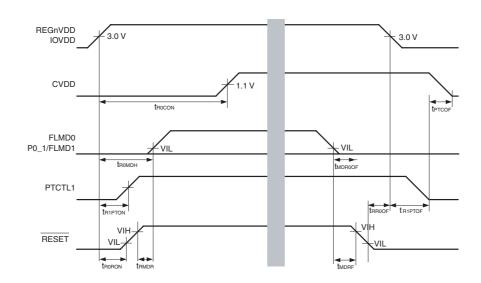

#### 3.4.1 条件1

WAKE, PTCTL1端子未使用 通常動作モード

表 3-6 条件 1

| 項目                                                                                 | 略号                          | 条件 | MIN. | TYP. | MAX. | 単位 |

|------------------------------------------------------------------------------------|-----------------------------|----|------|------|------|----|

| REGnVDD, IOVDD ↑ → CVDD ↑                                                          | <b>t</b> R0CON              |    | 1    |      | 10   | ms |

| REGnVDD, IOVDD ↑ →<br>FLMD0, FLMD1 (≦ VIL)<br>ホールド時間                               | trомдн                      |    | 3    |      |      | ms |

| REGnVDD, IOVDD ↑ → RESET ↑                                                         | <b>t</b> R0RON <sup>b</sup> |    | 2    |      |      | ms |

| RESET ↑ → FLMD0,<br>FLMD1 ↑                                                        | <b>t</b> RMDR <sup>b</sup>  |    | 1    |      |      | ms |

| FLMD0, FLMD1 ( $\leq$ VIL)<br>$\downarrow \rightarrow$ REG0VDD, IOVDD $\downarrow$ | tmdroof                     |    | 1    |      |      | ms |

| CVDD (0 V) ↓ → REG0VDD, IOVDD ↓                                                    | tcroof                      |    | 0    |      |      | ms |

| RESET ↓ → CVDD ↓                                                                   | <b>t</b> RCF <sup>b</sup>   |    | 0    |      |      | ms |

| FLMD0, FLMD1 ↓ →<br>RESET ↓                                                        | <b>t</b> MDRF <sup>b</sup>  |    | 1    |      |      | ms |

- a) IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

- b) M2 品の特性値です。

備考 n=0,1

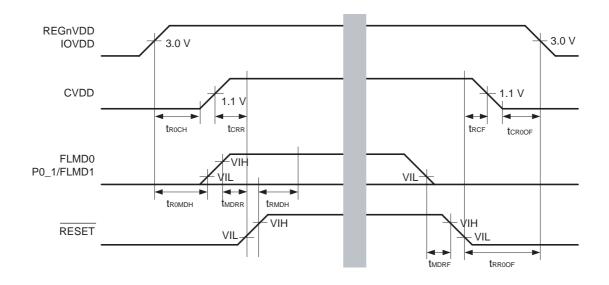

#### 3.4.2 条件 2

WAKE, PTCTL1端子未使用 シリアル・プログラミング・モード

表 3-7 条件 2

| 項目                                                                        | 略号            | 条件 | MIN. | TYP. | MAX. | 単位 |

|---------------------------------------------------------------------------|---------------|----|------|------|------|----|

| REGnVDD, IOVDD ↑ →<br>CVDD(0V)ホールド時間                                      | trосн         |    | 1    |      |      | ms |

| REGnVDD, IOVDD ↑→<br>FLMD0, FLMD1(≦ VIL)<br>ホールド時間                        | trомдн        |    | 1    |      |      | ms |

| CVDD $\uparrow \rightarrow \overline{RESET} \uparrow$                     | tcrr          |    | 0    |      |      | ms |

| FLMD0, F <u>LMD1</u> (VIH or VIL) $\downarrow \rightarrow RESET \uparrow$ | tmdrr         |    | 1    |      |      | ms |

| RESET ↑→ FLMD0,<br>FLMD1(VIH or VIL)ホー<br>ルド時間                            | trмdн         |    | 1    |      |      | ms |

|                                                                           | <b>t</b> MDRF |    | 0    |      |      | ms |

| RESET ↓ → CVDD ↓                                                          | <b>t</b> RCF  |    | 0    |      |      | ms |

| RESET ↓ → REGnVDD, IOVDD ↓                                                | trroof        |    | 0    |      |      | ms |

| CVDD (0V) ↓ → REGnVDD, IOVDD ↓                                            | tcroof        |    | 0    |      |      | ms |

備考 n=0,1

例 IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

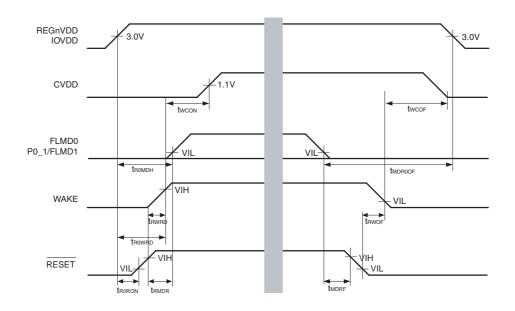

## 3.4.3 条件3

WAKE端子使用 通常動作モード

表 3-8 条件 3

| 項目                                                                                 | 略号                          | 条件 | MIN. | TYP. | MAX. | 単位 |

|------------------------------------------------------------------------------------|-----------------------------|----|------|------|------|----|

| REGnVDD, IOVDD ↑ →<br>WAKE ↑<br>出力遅延時間                                             | trowrd                      |    |      |      | 2    | ms |

| WAKE ↑ → CVDD ↑                                                                    | twcon                       |    | 0    |      | 8    | ms |

| REGnVDD, IOVDD ↑ →<br>FLMD0, FLMD1<br>(≦ VIL) ホールド時間                               | trомдн                      |    | 3    |      |      | ms |

| REGnVDD, IOVDD ↑ → RESET ↑                                                         | <b>t</b> R0RON <sup>b</sup> |    | 2    |      |      | ms |

| RESET ↑ →<br>FLMD0, FLMD1 ↑                                                        | <b>t</b> rmdr <sup>b</sup>  |    | 1    |      |      | ms |

| RESET ↑ → WAKE ↑<br>出力遅延時間                                                         | <b>t</b> rwrd <sup>b</sup>  |    |      |      | 1    | μs |

| FLMD0, FLMD1 ( $\leq$ VIL)<br>$\downarrow \rightarrow$ REG0VDD, IOVDD $\downarrow$ | tmdroof                     |    | 1    |      |      | ms |

| WAKE ↓ → CVDD (0V)                                                                 | twcof                       |    | 0    |      |      | ms |

| FLMD0, FLMD1 ↓ → RESET ↓                                                           | <b>t</b> MDRF <sup>b</sup>  |    | 1    |      |      | ms |

| RESET ↓ → WAKE ↓<br>出力遅延時間                                                         | trwor⁵                      |    |      |      | 1    | μs |

- a) IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

- b) M2 品の特性値です。

備考 n=0, 1

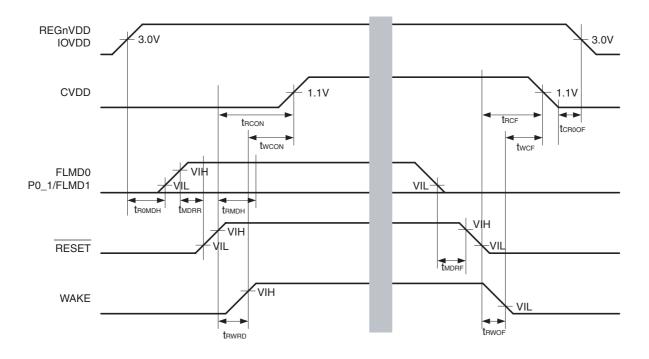

#### 3.4.4 条件 4

WAKE端子使用 シリアル・プログラミング・モード

表 3-9 条件 4

| 項目                                                              | 略号            | 条件 | MIN. | TYP. | MAX. | 単位 |

|-----------------------------------------------------------------|---------------|----|------|------|------|----|

| REGnVDD, IOVDD ↑→<br>FLMD0, FLMD1<br>(≦ VIL) ホールド時間             | trомдн        |    | 1    |      |      | ms |

| FLMD0, FLMD1 (VIH or VIL) $\uparrow \rightarrow RESET \uparrow$ | tmdrr         |    | 1    |      |      | ms |

| RESET ↑ → CVDD ↑                                                | <b>t</b> RCON |    | 0    |      | 10   | ms |

| RESET ↑→ WAKE ↑出力<br>遅延時間                                       | trwrd         |    |      |      | 1    | μs |

| WAKE ↑ → CVDD ↑                                                 | twcon         |    | 0    |      |      | ms |

| RESET ↑→ FLMD0,<br>FLMD1(VIH or VIL)<br>ホールド時間                  | trмdн         |    | 1    |      |      | ms |

| FLM <u>D0, FLM</u> D1 ( $\leq$ VIL)<br>↓ → RESET ↓              | <b>t</b> MDRF |    | 0    |      |      | ms |

| RESET ↓ → CVDD ↓                                                | <b>t</b> RCF  |    | 0    |      | 10   | ms |

| RESET ↓ → WAKE ↓出力<br>遅延時間                                      | trwof         |    |      |      | 1    | μs |

| WAKE $\downarrow \rightarrow \text{CVDD} \downarrow$            | twcf          |    | 0    |      |      | ms |

| CVDD (0V) → REG0VDD,<br>IOVDD ↓                                 | tcroof        |    | 0    |      |      | ms |

備考 n=0, 1

例 IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

#### 3.4.5 条件 5

PTCTL1端子使用 通常動作モード

表 3-10 条件 5

| 項目                                                                                 | 略号                           | 条件 | MIN. | TYP. | MAX. | 単位 |

|------------------------------------------------------------------------------------|------------------------------|----|------|------|------|----|

| REG1VDD IOVDD ↑→<br>PTCTL1 ↑<br>セットアップ時間                                           | tr1pton                      |    |      |      | 1    | ms |

| REGnVDD, IOVDD ↑ → CVDD ↑ by PTCTL1 ↑                                              | <b>t</b> R0CON               |    | 1    |      | 10   | ms |

| REGnVDD, IOVDD ↑ →<br>FLMD0, FLMD1(≦ VIL)<br>ホールド時間                                | trомдн                       |    | 3    |      |      | ms |

| REGnVDD, IOVDD ↑ → RESET ↑                                                         | <b>t</b> roron <sup>b</sup>  |    | 2    |      |      | ms |

| RESET ↑ → FLMD0,<br>FLMD1 ↑                                                        | <b>t</b> RMDR <sup>b</sup>   |    | 1    |      |      | ms |

| FLMD0, FLMD1 ( $\leq$ VIL)<br>$\downarrow \rightarrow$ REG0VDD, IOVDD $\downarrow$ | tmdroof                      |    | 1    |      |      | ms |

| REG1VDD, IOVDD ↓→<br>PTCTL1 ↓                                                      | <b>t</b> R1PTOF <sup>b</sup> |    |      |      | 1    | ms |

| PTCTL1 ↓ → CVDD ↓                                                                  | <b>t</b> PTCOF <sup>b</sup>  |    | 0    |      |      | ms |

| FLMD0, FLMD1 ↓ →<br>RESET ↓                                                        | <b>t</b> MDRF <sup>b</sup>   |    | 1    |      |      | ms |

| RESET ↓ → REG0VDD,<br>IOVDD ↓                                                      | <b>t</b> RR0OF⁵              |    | 0    |      |      | ms |

- a) IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

- b) M2 品の特性値です。

備考 n=0, 1

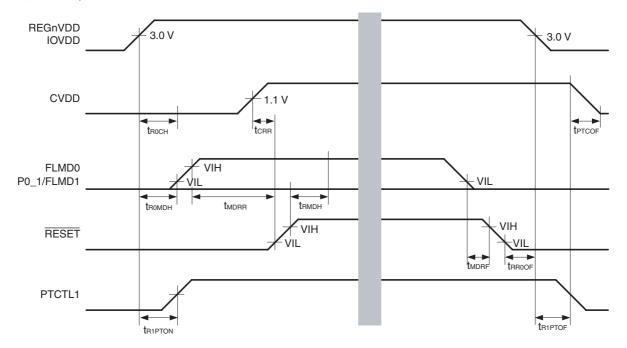

## 3.4.6 条件6

PTCTL1端子使用 シリアル・プログラミング・モード

表 3-11 条件 6

| 項目                                                  | 略号              | 条件 | MIN. | TYP. | MAX. | 単位 |

|-----------------------------------------------------|-----------------|----|------|------|------|----|

| REGnVDD, IOVDD ↑ →<br>CVDD (0 V)<br>ホールド時間          | trосн           |    |      |      | 1    | ms |

| REG1VDD ↑→ PTCTL1 ↑<br>セットアップ時間                     | <b>t</b> R1PTON |    |      |      | 1    | ms |

| CVDD ↑ → RESET ↑                                    | <b>t</b> CRR    |    | 0    |      |      | ms |

| REG0VDD, IOVDD ↑ →<br>FLMD0, FLMD1(≦ VIL)<br>ホールド時間 | trомдн          |    | 1    |      |      | ms |

| FLMD0, FL <u>MD1 (V</u> IH or VIL1) ↑ → RESET ↑     | <b>t</b> MDRR   |    | 1    |      |      | ms |

| RESET ↑→ FLMD0,<br>FLMD1(VIH or VIL)<br>ホールド時間      | trmdh           |    | 1    |      |      | ms |

| FLM <u>D0, FLM</u> D1 ( $\leq$ VIL)<br>↓ → RESET ↓  | <b>t</b> MDRF   |    | 0    |      |      | ms |

| RESET ↓ → REG0VDD,<br>IOVDD ↓                       | trroof          |    | 0    |      |      | ms |

| REG1VDD ↓ → PTCTL1 ↓                                | <b>t</b> R1PTOF |    |      |      | 1    | ms |

| PTCTL1 $\downarrow$ → CVDD $\downarrow$             | <b>t</b> PTCOF  |    | 0    |      |      | ms |

#### 備考 n=0,1

例 IOVDD: A0VDD, B0VDD, E0VDD, E1VDD, FVDD, OSCVDD, MLB0VDD

# 4. クロック発生回路

#### 4.1 CPU クロック 周波数

表 4-1 CPU クロック周波数

| 項       | 目    | 略号           | 条件                          | MIN. | TYP. | MAX.             | 単位  |

|---------|------|--------------|-----------------------------|------|------|------------------|-----|

| CPU クロッ | ク周波数 | <b>f</b> cpu | PLLC0.PC1, PC0 = 00 (固定周波数) |      |      | 160 <sup>a</sup> | MHz |

|         |      |              | PLLC0.PC1, PC0 = 10         |      |      | 160 <sup>a</sup> | MHz |

|         |      |              | (ダウン・スプレッド変調)               |      |      |                  |     |

|         |      |              | PLLC0.PC1, PC0 = 11         |      |      | 144 <sup>a</sup> | MHz |

|         |      |              | (センター・スプレッド変調)              |      |      |                  |     |

a) CPU クロックに SSCG を使用した場合,最大周波数は,PLLCn レジスタ(n = 0-2)で設定した変調モードに依存します。最大周波数は,ダウン・スプレッド変調に設定した場合は 160 MHz,センター・スプレッド変調に設定した場合は 144 MHz となります。

#### 4.2 周辺クロック周波数

表 4-2 周辺クロック周波数

| 項目        | 略号            | 条件 | MIN. | TYP. | MAX.            | 単位  |

|-----------|---------------|----|------|------|-----------------|-----|

| 周辺クロック周波数 | <b>f</b> PERI |    |      |      | 80 <sup>a</sup> | MHz |

a) 周辺クロック周波数の MAX. 値は 80MHz です。ただし, MLB/ システムクロックまたは IISABRG クロックとして PLL クロックを使う場合は, PLL1/PLL2 は 120MHz, PLL0 は 160MHz が MAX. 値となります。

#### 4.3 発振回路特性

#### 4.3.1 メイン発振回路 (MainOsc) 特性

表 4-3 メイン発振回路(MainOsc)特性

| 項目                              | 略号            | 条件               | MIN. | TYP. | MAX. | 単位  |

|---------------------------------|---------------|------------------|------|------|------|-----|

| メイン発振回路<br>(MainOsc)クロック<br>周波数 | fmosc         | セラミック発振子または水晶振動子 | 4    |      | 20   | MHz |

| MainOsc 安定時間                    | <b>f</b> мsтв |                  |      | а    |      | μs  |

a) この値は、MOSCST レジスタ設定値に依存します。

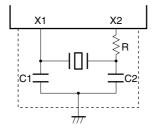

図 4-1 推奨メイン発振回路 (MainOsc)

#### 注意 1. 外部クロック入力は禁止です。

- 2. プリント基板上にレイアウトする際には、図中の破線の部分を次のように配線してください。

- ・配線は極力短くする。

- ・他の信号線と交差させない。

- •変化する大電流が流れる信号線に接近させない。

- 発振回路のコンデンサの接地点は、常に REGOVSS および OSCVSS と同電位になるようにする。

- ・大電流が流れるグランド・パターンに接地しない。

- •発振回路から信号を取り出さない。

- 3. C1, C2, Rの値は、ご使用のセラミック発振子または水晶振動子によるため、 発振子/振動子メーカとご相談の上、決定してください。

#### 4.3.2 サブ発振回路(SubOsc)特性

表 4-4 サブ発振回路 (SubOsc) 特性

| 項目                             | 略号            | 条件    | MIN. | TYP.   | MAX. | 単位  |

|--------------------------------|---------------|-------|------|--------|------|-----|

| サブ発振回路<br>(SubOsc) クロック<br>周波数 | fsosc         | 水晶振動子 |      | 32.768 |      | kHz |

| SubOsc 安定時間                    | <b>f</b> sstb |       |      | а      |      | S   |

この値は、SOSCST レジスタ設定値に依存します。

#### 内蔵発振器特性 4.3.3

表 4-5 内蔵発振器特性

| 項目                                 | 略号     | 条件                                                                                | MIN.  | TYP. | MAX.  | 単位  |

|------------------------------------|--------|-----------------------------------------------------------------------------------|-------|------|-------|-----|

| 低速内蔵発振回路<br>(低速 IntOsc)<br>クロック周波数 | frL    | - DEEPSTOP モード以外<br>- DEEPSTOP モードかつ<br>PSCn.PSCnREGSTP ビット = 0 の<br>とき(n = 0, 1) | 220.8 | 240  | 259.2 | kHz |

|                                    | frllp  | - DEEPSTOP モードかつ<br>PSCn.PSCnREGSTP ビット = 1 の<br>とき(n = 0, 1)                     | 216   | 240  | 264   | kHz |

| 高速内蔵発振回路<br>(高速 IntOsc)<br>クロック周波数 | fкн    | - DEEPSTOP モード以外<br>- DEEPSTOP モードかつ<br>PSCn.PSCnREGSTP ビット = 0 の<br>とき(n = 0, 1) | 7.2   | œ    | 8.8   | MHz |

|                                    | frhlp  | - DEEPSTOP モードかつ<br>PSCn.PSCnREGSTP ビット = 1 の<br>とき(n = 0, 1)                     | 6.64  | 8    | 8.8   | MHz |

| 高速内蔵発振回路<br>(高速 IntOsc)<br>安定時間    | tкнѕтв |                                                                                   |       |      | 19    | μs  |

## 4.4 PLL特性

表 4-6 PLL 特性

| 項目          | 略号             | 条件                      | MIN.  | TYP. | MAX. | 単位  |

|-------------|----------------|-------------------------|-------|------|------|-----|

| 入力周波数       | fxn            |                         | 4     |      | 20   | MHz |

| PLL0 用出力周波数 | fxx0           | PLL モード                 | 25    |      | 160  | MHz |

|             |                | SSCG モード , センター・スプレッド変調 | 22.40 |      | 144  | MHz |

|             |                | SSCG モード , ダウン・スプレッド変調  | 22.40 |      | 160  | MHz |

| PLL1 用出力周波数 | fxx1           | PLL モード                 | 25    |      | 120  | MHz |

| PLL2 用出力周波数 | fxx2           | PLL モード                 | 25    |      | 120  | MHz |

|             |                | SSCG モード , センター・スプレッド変調 | 22.40 |      | 120  | MHz |

|             |                | SSCG モード , ダウン・スプレッド変調  | 22.40 |      | 120  | MHz |

| ロック時間       | <b>t</b> LCKPn | PLL モード                 |       |      | 650  | μs  |

|             | tLCKSn         | SSCG モード                |       |      | 1300 | μs  |

備考 n = 0-2

# 5. 入出力スペック

$\mu$  PD70F4017, 70F4018

# 5.1 ポート特性

# 5.1.1 PgE0

表 5-1 PgE0

| 項目            | 略号           | 条件                         | MIN.        | TYP. | MAX.         | 単位 |

|---------------|--------------|----------------------------|-------------|------|--------------|----|

| ハイ・レベル入力電圧    | ViH          | CMOS                       | 0.7 E0VDD   |      | E0VDD + 0.3  | V  |

|               |              | シュミット1(SHMT1)              | 0.7 E0VDD   |      | E0VDD + 0.3  | V  |

|               |              | シュミット2(SHMT2)              | 0.8 E0VDD   |      | E0VDD + 0.3  | V  |

|               |              | シュミット4(SHMT4)              | 0.84 E0VDD  |      | E0VDD + 0.3  | V  |

| ロウ・レベル入力電圧    | VIL          | CMOS                       | - 0.5       |      | 0.3 E0VDD    | V  |

|               |              | シュミット1(SHMT1)              | - 0.5       |      | 0.3 E0VDD    | V  |

|               |              | シュミット2(SHMT2)              | - 0.5       |      | 0.2 E0VDD    | V  |

|               |              | シュミット4(SHMT4)              | - 0.5       |      | 0.4 E0VDD    | V  |

| ハイ・レベル出力電圧    | Vон          | $I$ он = $-5 \text{ mA}^a$ | E0VDD - 1.0 |      |              | V  |

|               |              | Іон = — 100 μ А            | E0VDD - 0.5 |      |              | V  |

| ロウ・レベル出力電圧    | Vol          | IoL = 5 mA <sup>a</sup>    |             |      | 0.4          | V  |

|               |              | IoL = 100 μ A              |             |      | 0.4          | V  |

| シュミットの        | Vн           | シュミット1(SHMT1)              | 0.3         |      |              | V  |

| 入力ヒステリシス      |              | シュミット2(SHMT2)              | 0.3         |      |              | V  |

|               |              | シュミット4(SHMT4)              | 0.1         |      |              | V  |

| プルアップ抵抗       | R∪           |                            | 20          | 40   | 100          | kΩ |

| プルダウン抵抗       | R□           |                            | 20          | 40   | 100          | kΩ |

| ハイ・レベル入力リーク電流 | Ішн          | Vi = E0VDD                 |             |      | 0.5          | μΑ |

| ロウ・レベル入力リーク電流 | ILIL         | V <sub>I</sub> = 0 V       |             |      | <b>-</b> 0.5 | μΑ |

| ハイ・レベル出力リーク電流 | Ісон         | Vo = E0VDD                 |             |      | 0.5          | μΑ |

| ロウ・レベル出カリーク電流 | ILOL         | Vo = 0 V                   |             |      | - 0.5        | μΑ |

| 立ち上がり時間(出力)   | <b>t</b> krp | 低速モード                      |             |      | 15           | ns |

|               |              | 高速モード                      |             |      | 8            | ns |

| 立ち下がり時間(出力)   | <b>t</b> KFP | 低速モード                      |             |      | 15           | ns |

|               |              | 高速モード                      |             |      | 8            | ns |

a) PgEO の合計電流値として、IoH は-5 mA、IoL は 5 mA を越えないでください。

# 5.1.2 PgE1

表 5-2 PgE1

| 項目            | 略号           | 条件                         | MIN.        | TYP. | MAX.         | 単位 |

|---------------|--------------|----------------------------|-------------|------|--------------|----|

| ハイ・レベル入力電圧    | Vін          | CMOS                       | 0.7 E1VDD   |      | E1VDD + 0.3  | V  |

|               |              | シュミット1(SHMT1)              | 0.7 E1VDD   |      | E1VDD + 0.3  | V  |

|               |              | シュミット2(SHMT2)              | 0.8 E1VDD   |      | E1VDD + 0.3  | V  |

|               |              | シュミット4(SHMT4)              | 0.84 E1VDD  |      | E1VDD + 0.3  | V  |

| ロウ・レベル入力電圧    | VIL          | CMOS                       | - 0.5       |      | 0.3 E1VDD    | V  |

|               |              | シュミット1(SHMT1)              | - 0.5       |      | 0.3 E1VDD    | V  |

|               |              | シュミット2(SHMT2)              | - 0.5       |      | 0.2 E1VDD    | V  |

|               |              | シュミット4(SHMT4)              | - 0.5       |      | 0.4 E1VDD    | V  |

| ハイ・レベル出力電圧    | Vон          | $I$ он = $-5 \text{ mA}^a$ | E1VDD — 1.0 |      |              | V  |

|               |              | Іон = — 100 μ А            | E1VDD — 0.5 |      |              | V  |

| ロウ・レベル出力電圧    | Vol          | IoL = 5 mA <sup>a</sup>    |             |      | 0.4          | V  |

|               |              | Ιοι = 100 μ Α              |             |      | 0.4          | V  |

| シュミットの        | Vн           | シュミット1(SHMT1)              | 0.3         |      |              | V  |

| 入力ヒステリシス      |              | シュミット2(SHMT2)              | 0.3         |      |              | V  |

|               |              | シュミット4(SHMT4)              | 0.1         |      |              | V  |

| プルアップ抵抗       | Rυ           |                            | 20          | 40   | 100          | kΩ |

| プルダウン抵抗       | R□           |                            | 20          | 40   | 100          | kΩ |

| ハイ・レベル入力リーク電流 | Ін           | Vı = E1VDD                 |             |      | 0.5          | μΑ |

| ロウ・レベル入力リーク電流 | ILIL         | V <sub>I</sub> = 0 V       |             |      | <b>-</b> 0.5 | μΑ |

| ハイ・レベル出力リーク電流 | Ісон         | Vo = E1VDD                 |             |      | 0.5          | μΑ |

| ロウ・レベル出力リーク電流 | ILOL         | Vo = 0 V                   |             |      | - 0.5        | μΑ |

| 立ち上がり時間(出力)   | <b>t</b> krp | 低速モード                      |             |      | 15           | ns |

|               |              | 高速モード                      |             |      | 8            | ns |

| 立ち下がり時間(出力)   | <b>t</b> KFP | 低速モード                      |             |      | 15           | ns |

|               |              | 高速モード                      |             |      | 8            | ns |

a) PgE1 の合計電流値として、IoH は- 15 mA、IoL は 15 mA を越えないでください。

### 5.1.3 PgB0

表 5-3 PgB0

| 項目            | 略号           | 条件                        | MIN.         | TYP. | MAX.         | 単位 |

|---------------|--------------|---------------------------|--------------|------|--------------|----|

| ハイ・レベル入力電圧    | VIH          | CMOS                      | 0.7 B0VDD    |      | B0VDD + 0.3  | V  |

|               |              | シュミット1(SHMT1)             | 0.7 B0VDD    |      | B0VDD + 0.3  | V  |

|               |              | シュミット2(SHMT2)             | 0.8 B0VDD    |      | B0VDD + 0.3  | V  |

|               |              | シュミット4(SHMT4)             | 0.84 B0VDD   |      | B0VDD + 0.3  | V  |

| ロウ・レベル入力電圧    | VIL          | CMOS                      | <b>-</b> 0.5 |      | 0.3 B0VDD    | V  |

|               |              | シュミット1(SHMT1)             | <b>-</b> 0.5 |      | 0.3 B0VDD    | V  |

|               |              | シュミット2(SHMT2)             | <b>-</b> 0.5 |      | 0.2 B0VDD    | V  |

|               |              | シュミット4(SHMT4)             | <b>-</b> 0.5 |      | 0.4 B0VDD    | V  |

| ハイ・レベル出力電圧    | Vон          | Іон = — 5 mA <sup>a</sup> | B0VDD - 1.0  |      |              | V  |

|               |              | Іон = — 100 μ А           | B0VDD — 0.5  |      |              | V  |

| ロウ・レベル出力電圧    | Vol          | IoL = 5 mA <sup>a</sup>   |              |      | 0.4          | V  |

|               |              | Ιοι = 100 μ Α             |              |      | 0.4          | V  |

| シュミットの        | Vн           | シュミット1(SHMT1)             | 0.3          |      |              | V  |

| 入力ヒステリシス      |              | シュミット2(SHMT2)             | 0.3          |      |              | V  |

|               |              | シュミット4(SHMT4)             | 0.1          |      |              | V  |

| プルアップ抵抗       | Rυ           |                           | 20           | 40   | 100          | kΩ |

| プルダウン抵抗       | R□           |                           | 20           | 40   | 100          | kΩ |

| ハイ・レベル入力リーク電流 | Ішн          | Vı = B0VDD                |              |      | 0.5          | μΑ |

| ロウ・レベル入力リーク電流 | ILIL         | V <sub>I</sub> = 0 V      |              |      | <b>-</b> 0.5 | μΑ |

| ハイ・レベル出力リーク電流 | Ісон         | Vo = B0VDD                |              |      | 0.5          | μΑ |

| ロウ・レベル出力リーク電流 | ILOL         | Vo = 0 V                  |              |      | - 0.5        | μΑ |

| 立ち上がり時間(出力)   | <b>t</b> krp | 低速モード                     |              |      | 8            | ns |

|               |              | 高速モード(CL = 30 pF)         |              |      | 5            | ns |

| 立ち下がり時間(出力)   | <b>t</b> KFP | 低速モード                     |              |      | 8            | ns |

|               |              | 高速モード(CL = 30 pF)         |              |      | 5            | ns |

a) PgB0 の合計電流値として、IoH は - 35 mA, IoL は 35 mA を越えないでください。 PgB0 で出力バッファのポート・ドライブ強度を高速モード(ハイ・ドライブ強度)に設定した場合、使用可能な PgB0 は 8 本です(外部メモリ・インタフェースとして使用するとき以外)。また、PgB0 で出力バッファのポート・ドライブ強度を低速モード(ロウ・ドライブ強度)に設定した場合、使用可能な PgB0 は 5 本です。

5. 入出力スペック

## 5.1.4 PgA0

表 5-4 PgA0

| 項目            | 略号           | 条件                         | MIN.         | TYP. | MAX.        | 単位 |

|---------------|--------------|----------------------------|--------------|------|-------------|----|

| ハイ・レベル入力電圧    | Vih          | CMOS                       | 0.7 A0VDD    |      | A0VDD + 0.3 | V  |

| ロウ・レベル入力電圧    | VIL          | CMOS                       | <b>-</b> 0.5 |      | 0.3 A0VDD   | V  |

| ハイ・レベル出力電圧    | Vон          | $I$ он = $-1 \text{ mA}^a$ | A0VDD - 1.0  |      |             | V  |

|               |              | $I$ он = $-$ 100 $\mu$ A   | A0VDD - 0.5  |      |             | V  |

| ロウ・レベル出力電圧    | Vol          | IoL = 1 mA <sup>a</sup>    |              |      | 0.4         | V  |

|               |              | IoL = 100 μ A              |              |      | 0.4         | V  |

| ハイ・レベル入力リーク電流 | Ішн          | Vı = A0VDD                 |              |      | 0.2         | μΑ |

| ロウ・レベル入力リーク電流 | ILIL         | V1 = 0 V                   |              |      | - 0.2       | μΑ |

| ハイ・レベル出力リーク電流 | Ісон         | Vo = A0VDD                 |              |      | 0.2         | μΑ |

| ロウ・レベル出力リーク電流 | ILOL         | Vo = 0 V                   |              |      | - 0.2       | μΑ |

| 立ち上がり時間(出力)   | <b>t</b> krp |                            |              |      | 15          | ns |

| 立ち下がり時間(出力)   | <b>t</b> KFP |                            |              |      | 15          | ns |

a) PgA0 の合計電流値として、Ioн はー 20 mA、IoL は 20 mA を越えないでください。

### 5.2 入出力容量

表 5-5 入出力容量

| 項     | 目 | 略号 | 条件         | MIN. | TYP. | MAX. | 単位 |

|-------|---|----|------------|------|------|------|----|

| 入力容量  |   | _  | fx = 1 MHz |      |      | 10   | pF |

| 入出力容量 |   | Сю | 被測定ピン以外は0V |      |      | 10   | pF |

| 出力容量  |   | Со |            |      |      | 10   | pF |

### 6. 電源電流スペック

#### 6.1 1.2 V電源電流スペック (A) グレード品

表 6-1 CVDD (Iso0 and Iso1) の消費電流

|                  |     | 電源   |      | 条   | 件          | EP '771  | 1            | フロック         | ・ソース        | ζ.         |      | 規格値  | İ    |    |

|------------------|-----|------|------|-----|------------|----------|--------------|--------------|-------------|------------|------|------|------|----|

| 項目               | AWO | Iso0 | Iso1 | PLL | CPU<br>周波数 | 問辺<br>機能 | 低速<br>IntOsc | 高速<br>IntOsc | Main<br>OSC | Sub<br>OSC | MIN. | TYP. | MAX. | 単位 |

| RUN モード          | ON  | ON   | ON   | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 210  | 308  | mA |

|                  | ON  | ON   | ON   | OFF | 8          | 動作       | ON           | ON           | ON          | ON         | -    | 17   | 105  | mA |

|                  | ON  | ON   | STP  | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 160  | 294  | mA |

|                  | ON  | ON   | STP  | OFF | 8          | 動作       | ON           | ON           | ON          | ON         | -    | 13   | 99   | mA |

|                  | ON  | ON   | OFF  | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 135  | 188  | mA |

|                  | ON  | ON   | OFF  | OFF | 8          | 動作       | ON           | ON           | ON          | ON         | 1    | 11   | 69   | mA |

| フラッシュ書き込<br>みモード | ON  | ON   | ON   | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 210  | 308  | mA |

| STOP モード         | ON  | ON   | ON   | OFF | -          | 停止       | ON           | OFF          | OFF         | OFF        | -    | 1.4  | 60   | mA |

|                  | ON  | ON   | OFF  | OFF | -          | 停止       | ON           | OFF          | OFF         | OFF        | 1    | 1.2  | 44   | mA |

| DEEPSTOP         | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | OFF         | OFF        | -    | 0.01 | 0.4  | mA |

| モード              | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | ON           | OFF         | OFF        | -    | 0.01 | 0.4  | mA |

|                  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | ON           | ON          | ON         | -    | 0.01 | 0.4  | mA |

|                  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | ON          | OFF        | -    | 0.01 | 0.4  | mA |

|                  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | OFF         | ON         | -    | 0.01 | 0.4  | mA |

| 25 °C MAX. の     | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | OFF         | OFF        | -    | -    | 0.04 | mA |

| DEEPSTOP<br>モード  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | ON           | OFF         | OFF        | -    | -    | 0.04 | mA |

| r                | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | ON           | ON          | ON         | -    | -    | 0.04 | mA |

|                  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | ON          | OFF        | -    | -    | 0.04 | mA |

|                  | ON  | OFF  | OFF  | OFF | -          | 停止       | ON           | OFF          | OFF         | ON         | -    | -    | 0.04 | mA |

備考 1. ON : 電源供給許可状態

STP:電源供給許可状態。ただし、クロック停止。

OFF : 電源供給停止状態

2. SSCG の場合,動作周波数 = 160 MHz は平均周波数です。

3. 上記は、ポート・バッファ、A/D コンバータの電流は含みません。

4. RUN モード時の電流には、セルフ・プログラミング時および EEPROM® エミュレーション実行時の電流を含みます。

- 5. 動作周波数が 8 MHz の場合, Ethernet と MediaLB の電流は含みません。

- 6. TYP. 値は参考値です。

TYP. 値の条件を次に示します。

- •T<sub>A</sub> = 25 °C

- •REGNVDD = FVDD = OSCVDD = EnVDD = B0VDD = A0VDD = AVREFP0 = 3.3 V

- •CVDD = 1.2 V

- •MLB0VDD = 3.3 V

- •REGnVSS = OSCVSS = EnVSS = B0VSS = CVSS = MLB0VSS = A0VSS = AVREFM0 = 0V

- 25 °C MAX. の DEEPSTOP モードの MAX. 値は参考値です。

25 °C MAX. の DEEPSTOP モードの MAX. 値の条件を次に示します。

- •T<sub>A</sub> = 25 °C

- •REGnVDD = FVDD = OSCVDD = EnVDD = B0VDD = A0VDD = AVREFP0 = 3.6 V

- •CVDD = 1.3 V

- •MLB0VDD = 3.6 V

- •REGnVSS = OSCVSS = EnVSS = B0VSS = CVSS = MLB0VSS = A0VSS = AVREFM0 = 0V

#### 6.2 3.3 V電源電流スペック (A) グレード品

#### 表 6-2 OSCVDD, REGnVDD, FVDD の消費電流

|                       |     | 電源   |      | 条   | 件          | EE YT    |              | クロック         | ・ソース        |            |      | 規格値  | i    |    |

|-----------------------|-----|------|------|-----|------------|----------|--------------|--------------|-------------|------------|------|------|------|----|

| 項目                    | AWO | Iso0 | Iso1 | PLL | CPU<br>周波数 | 周辺<br>機能 | 低速<br>IntOsc | 高速<br>IntOsc | Main<br>OSC | Sub<br>OSC | MIN. | TYP. | MAX. | 単位 |

| RUN モード               | ON  | ON   | ON   | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 29   | 34   | mA |

|                       | ON  | ON   | ON   | OFF | 8          | 動作       | ON           | ON           | ON          | ON         | -    | 13   | 19   | mA |

|                       | ON  | ON   | STP  | ON  | 160        | 動作       | ON           | ON           | ON          | ON         | -    | 29   | 34   | mA |