## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

## MOS 集積回路 MOS Integrated Circuit

# $\mu$ PD64031A

## ゴースト・リデューサ LSI

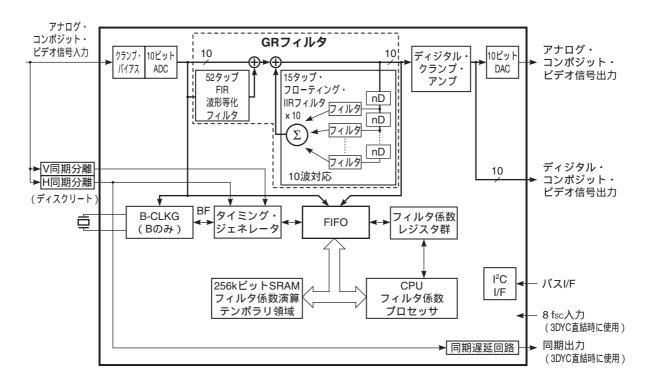

$\mu$ PD64031A は , 日本国内の GCR 方式に対応した , ゴースト・リデューサ LSI です。日本方式の GCR 信号を含ん だ映像信号の波形等化とゴースト低減を行います。

GR システムに必要な機能をすべて(A/D コンバータ ,D/A コンバータ ,マイコン ,クロック・ジェネレータ ,SRAM )を 1 チップに内蔵しています。

### 特徵

ゴースト低減フィルタ(GR フィルタ), コントローラ , A/D コンバータ , D/A コンバータ , クロック・ジェネレータをすべて 1 チップ化

- 2.6~ + 1.0 μs , - 6 dB の波形等化および 1.0~40 μs , - 6 dB のゴースト低減機能

チャネル変更またはリセットから約1.2秒でゴースト低減動作開始

当社製の 3 次元 Y/C 分離 IC  $\mu$  PD64083, 64084 やビデオ・デコーダ IC  $\mu$  PD64011B とディジタル直結が可能 I<sup>2</sup>C バスによる各種コントロールが可能

## オーダ情報

| オーダ名称                             | パッケージ                              |

|-----------------------------------|------------------------------------|

| μ PD64031AGJ-8EN-A 注1             | 144 ピン・プラスチック LQFP(ファインピッチ)(20×20) |

| $\mu$ PD64031AGJ-8EN-Y $^{\rm 2}$ | 144 ピン・プラスチック LQFP(ファインピッチ)(20×20) |

注 1. 鉛フリー製品

2. 耐熱性向上品

本資料の内容は予告なく変更することがありますので、最新のものであることをご確認の上ご使用ください。

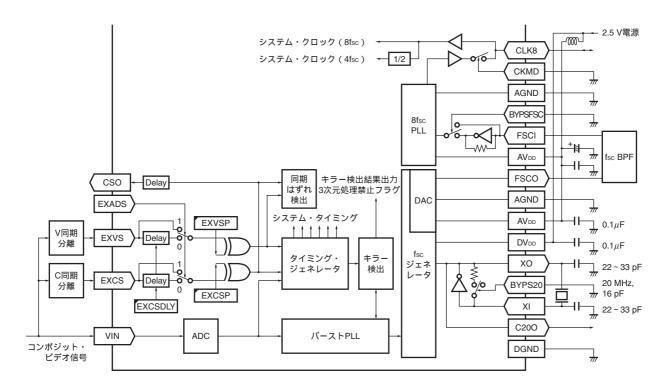

## プロック図

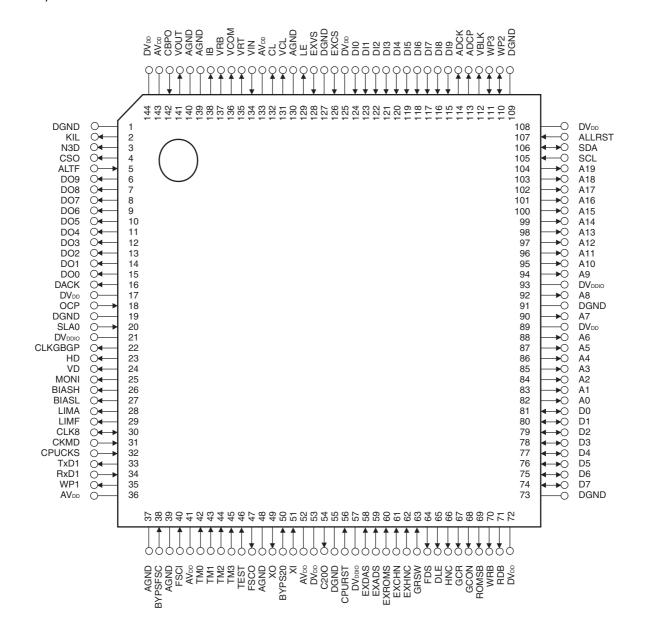

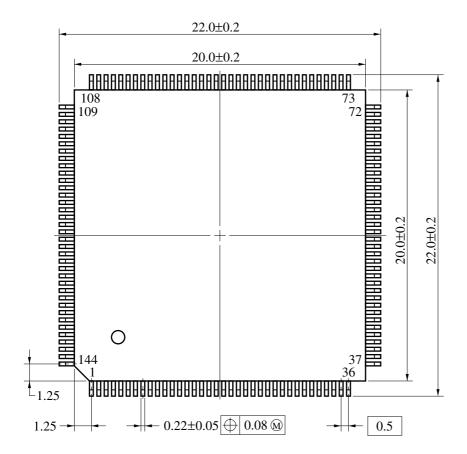

## 端子接続図 (Top View)

144 ピン・プラスチック LQFP (ファインピッチ)(20×20)

- μPD64031AGJ-8EN-A

- μPD64031AGJ-8EN-Y

## 目 次

| 1. | 端子   | 幾能 6                                     |

|----|------|------------------------------------------|

| 2. | シス   | テム概要 11                                  |

|    | 2. 1 | 動作モード 11                                 |

|    | 2. 2 | 動作概要 12                                  |

|    | 2. 3 | ゴースト低減範囲について 13                          |

|    | 2. 4 | 電源起動とリセット 13                             |

|    |      | 2.4.1 電源投入時と切断時の注意事項 14                  |

|    |      | 2.4.2 CPU リセットについて 14                    |

|    | 2. 5 | ポート制御と I <sup>2</sup> C レジスタ制御の関係について 14 |

|    |      | 2. 5. 1 ゴースト低減動作 ON/OFF 制御 14            |

|    |      | 2. 5. 2 チャネル変更制御 15                      |

|    |      | 2. 5. 3 強制ハンチング制御 16                     |

|    |      | 2. 5. 4 ディジタル・データ出力制御 17                 |

| 3. | コンフ  | ポジット・ビデオ信号入力プロック 18                      |

|    |      | コンポジット・ビデオ信号入力 18                        |

|    | 3. 2 | クランプ回路およびバイアス回路 19                       |

|    | 3. 3 | コンポジット・ビデオ信号入力レベル 19                     |

|    | 3. 4 | 端子処理など 20                                |

| 1  | ДΠ,  | ック生成/タイミング生成プロック 21                      |

| 7. |      | - コンポジット同期信号入力 21                        |

|    |      | 垂直同期信号入力 21                              |

|    |      | タイミング・ジェネレータ 21                          |

|    |      | バースト PLL 回路 22                           |

|    | 4. 5 | キラー検出回路 22                               |

|    | 4. 6 | fsc ジェネレータ 22                            |

|    | 4. 7 | 8fsc PLL 回路 22                           |

|    | 4. 8 | 端子処理など 22                                |

|    | 4. 9 | 外部同期分離回路設計時の注意点 23                       |

| 5. | 同期に  | まずれ検出プロック 24                             |

|    |      | - 水平同期はずれ判定 24                           |

|    |      | 垂直同期はずれ判定 24                             |

|    | 5. 3 | ハンチング検出 24                               |

- 6. コンポジット・ビデオ信号出力プロック ... 25

- 6.1 ディジタル・コンポジット・ビデオ信号出力処理 ... 25

- 6.2 コンポジット・ビデオ信号出力レベル ... 25

- 6.3 ディジタル・クランプ・アンプ機能 ... 26

- 6.4 端子処理など ... 27

- 7. I<sup>2</sup>C パス・インタフェース ... 28

- 7.1 基本仕様 ... 28

- 7.2 データ送受信フォーマット ... 29

- 7.3 I<sup>2</sup>C バスの初期化 ... 30

- 8. シリアル・パス・レジスタ一覧 ... 31

- 9. 電気的特性 ... 44

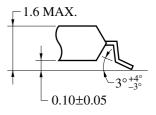

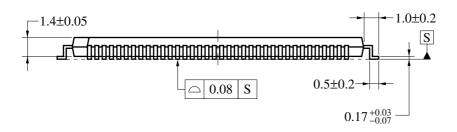

- 10. 外形図 ... 47

- 11. 半田付け推奨条件 ... 48

## 1. 端子機能

表1-1 端子機能一覧 (1/5)

| 端子番号                                | 端子略号             | I/O | レベル  | バッファ・                | 機能                                                                                               |

|-------------------------------------|------------------|-----|------|----------------------|--------------------------------------------------------------------------------------------------|

|                                     |                  |     |      | タイプ                  |                                                                                                  |

|                                     |                  |     |      | PU/PD [kΩ]           |                                                                                                  |

| 1, 19, 55,<br>73, 91, 109,<br>127   | DGND             | -   | •    |                      | ディジタル部接地                                                                                         |

| 17, 53, 72,<br>89, 108,<br>125, 144 | DV <sub>DD</sub> | -   | -    |                      | ディジタル部 2.5 V 電源                                                                                  |

| 2                                   | KIL              | 0   | CMOS | 3 mA<br>3.3 V 振幅     | キラー出力<br>キラーを検出すると Low が出力されます                                                                   |

| 3                                   | N3D              | 0   | CMOS | 3 mA<br>3.3 V 振幅     | 3 次元処理禁止フラグ出力<br>(3 次元 Y/C 分離 IC とのディジタル直結時に,3 次元処理<br>禁止フラグとして使用)                               |

| 4                                   | CSO              | 0   | CMOS | 3 mA<br>3.3 V 振幅     | コンポジット同期信号出力<br>EXCS 端子(126ピン)に入力されたコンポジット同期信号<br>をシステム・ディレイ分遅延して出力します(3次元 Y/C分離ICとのディジタル直結時に使用) |

| 5                                   | ALTF             | I   | CMOS | 50 kΩ PD<br>3.3 V 耐圧 | 外部 4fsc 位相入力<br>外部から 4fsc クロックを入力します(3 次元 Y/C 分離 IC と<br>のディジタル直結時に使用)                           |

| 6-15                                | DO9-DO0          | 0   | CMOS | 3 mA<br>3.3 V 振幅     | ディジタル信号出力<br>初期値 Hi-Z, I <sup>2</sup> C によりプルダウン可能                                               |

| 16                                  | DACK             | 0   | CMOS | 3 mA<br>3.3 V 振幅     | テスト端子                                                                                            |

| 18                                  | ОСР              | I   | CMOS | 50kΩ PD<br>3.3 V 耐圧  | 外部バースト・ゲート・パルス入力<br>外部で生成したバースト・ゲート・パルスを入力します<br>(3次元 Y/C 分離 IC とのディジタル直結時に使用)                   |

| 20                                  | SLA0             | I   | CMOS | 50 kΩ PD<br>3.3 V 耐圧 | I <sup>2</sup> C バス・スレーブ・アドレス選択<br>High: 26h/27h<br>Low: 24h/25h                                 |

| 22                                  | CLKGBGP          | 0   | CMOS | 3 mA<br>3.3 V 振幅     | CLKG 用 BGP モニタ出力<br>(アクティブ・ハイ)                                                                   |

| 23                                  | HD               | 0   | CMOS | 3 mA<br>3.3 V 振幅     | 水平同期信号モニタ出力<br>(アクティブ・ロウ)                                                                        |

| 24                                  | VD               | 0   | CMOS | 3 mA<br>3.3 V 振幅     | 垂直同期信号モニタ出力<br>(アクティブ・ロウ)                                                                        |

| 25                                  | MONI             | 0   | CMOS | 3 mA<br>3.3 V 振幅     | テスト端子                                                                                            |

| 26                                  | BIASH            | 0   | CMOS | 3 mA<br>3.3 V 振幅     | テスト用出力                                                                                           |

| 27                                  | BIASL            | 0   | CMOS | 3 mA<br>3.3 V 振幅     | テスト用出力                                                                                           |

表1-1 端子機能一覧(2/5)

| 端子番号  | 端子略号    | I/O | レベル     | バッファ・                                                                                                                                | 機能                                                                                                                                                                                |

|-------|---------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |         |     |         | タイプ<br>PU/PD [kΩ]                                                                                                                    |                                                                                                                                                                                   |

| 28    | LIMA    | 0   | CMOS    | 3 mA テスト端子<br>3.3 V 振幅                                                                                                               |                                                                                                                                                                                   |

| 29    | LIMF    | 0   | CMOS    | 3 mA<br>3.3 V 振幅                                                                                                                     | テスト端子                                                                                                                                                                             |

| 30    | CLK8    | I/O | CMOS    | 6 mA 3.3 V 振幅 外部で生成された 8fsc クロックを入力または出力し 入出力の切り替えは CKMD (31 ピン) で行います CKMD が Low : 出力モード (標準) CKMD が High : 入力モード (3 次元 Y/C 分離 IC と |                                                                                                                                                                                   |

| 31    | CKMD    | I   | CMOS    | 50 kΩ PD<br>3.3 V 耐圧                                                                                                                 | クロック生成モード制御<br>8fsc クロックの生成方法を切り替えます<br>Low:内部で生成された 8fsc を使用(通常時)<br>High:外部から CLK8 端子(30 ピン)へ入力(3 次元 Y/C<br>分離 IC とのディジタル直結時に使用)                                                |

| 32    | CPUCKS  | I   | CMOS    | 50 kΩ PD<br>3.3V 耐圧                                                                                                                  | テスト端子<br>(GND に接続)                                                                                                                                                                |

| 33    | TxD1    | 0   | CMOS    | 3 mA<br>3.3 V 振幅                                                                                                                     | テスト端子                                                                                                                                                                             |

| 34    | RxD1    | I   | Schmitt | 50 kΩ PU<br>3.3 V 耐圧                                                                                                                 | テスト端子<br>(Vodio にプルアップ)                                                                                                                                                           |

| 35    | WP1     | 0   | CMOS    | 3 mA<br>3.3V 振幅                                                                                                                      | 3 次元 Y/C 分離ディジタル接続モード・コントロール出力  μPD64031A (ゴースト・リデューサ: GR) と当社製 3 次 元 Y/C 分離 IC (3DYC) をディジタル接続時,入力信号などに応じて,GR+3DYC,または3DYC 単体での動作に切り替えるための信号が出力されます  Low: GR+3DYC  High: 3DYC 単体 |

| 38    | BYPSFSC | I   | CMOS    | 2.5 V 耐圧                                                                                                                             | FSCI 端子(40 ピン)入力アンプ選択<br>Low:アンプ受け(通常設定)<br>High: CMOS 受け                                                                                                                         |

| 40    | FSCI    | I   | Analog  | 2.5 V 耐圧                                                                                                                             | 8fsc PLL fsc 入力<br>fsc BPF より DC カットした fsc を入力<br>(3 次元 Y/C 分離 IC とのディジタル直結時は GND に接続)                                                                                            |

| 42-45 | TM0-TM3 | I   | CMOS    | 50 kΩ PD<br>2.5 V 耐圧                                                                                                                 | テスト端子(GND に接続)                                                                                                                                                                    |

| 46    | TEST    | I   | CMOS    | 50 kΩ PD<br>2.5V 耐圧                                                                                                                  | テスト端子(GND に接続)                                                                                                                                                                    |

| 47    | FSCO    | 0   | Analog  | 2.5 V 振幅                                                                                                                             | fsc ジェネレータ fsc クロック出力<br>内部クロック・ジェネレータで生成された fsc クロックが出<br>力されます。バッファを介して BPF に接続します                                                                                              |

表1-1 端子機能一覧(3/5)

| 端子番号     | 端子略号    | I/O      | レベル     | バッファ・                | 機能                                                                          |

|----------|---------|----------|---------|----------------------|-----------------------------------------------------------------------------|

| NU 1 E 1 | NIII J  |          | "       | タイプ                  | IN BU                                                                       |

|          |         |          |         | PU/PD [kΩ]           |                                                                             |

| 49       | XO      | 0        | Analog  | 2.5 V 振幅             | fsc ジェネレータ基準クロック反転出力                                                        |

|          |         |          |         |                      | 20 MHz 水晶発振回路を接続。                                                           |

| 50       | BYPS20  | 1        | CMOS    | 2.5 V 耐圧             | XI 端子(51 ピン)入力アンプ選択                                                         |

|          |         |          |         |                      | Low:アンプ受け(通常設定)                                                             |

|          |         |          |         |                      | High: CMOS 受け                                                               |

| 51       | ΧI      | - 1      | Analog  | 2.5 V 耐圧             | fsc ジェネレータ基準クロック入力                                                          |

|          |         |          |         |                      | 20 MHz 水晶発振回路を接続                                                            |

| 54       | C20O    | 0        | CMOS    | 6 mA                 | fsc ジェネレータ 20 MHz クロック出力                                                    |

|          |         |          |         | 3.3 V 振幅             | fsc ジェネレータに接続する 20 MHz クロックが出力されま                                           |

|          |         |          |         |                      | す( 3 次元 Y/C 分離 IC とのディジタル直結時に使用します )                                        |

| 56       | CPURST  | I        | Schmitt | 50 kΩ PU             | テスト端子                                                                       |

|          |         |          |         | 3.3 V 耐圧             | (Vodio にプルアップ)                                                              |

| 58       | EXDAS   | I        | CMOS    | 50 kΩ PD             | データ出力選択                                                                     |

|          |         |          |         | 3.3 V 耐圧             | High:ディジタル出力(DO9-DO0 端子: 6-15 ピン)有効,                                        |

|          |         |          |         |                      | Low:ディジタル出力無効(DO9-DO0端子はHi-Z)                                               |

|          |         |          |         |                      | l <sup>2</sup> C バス・レジスタ EXDAS ( SA01h: D7 ) と同時設定が必要<br>です                 |

|          | EVADO   |          | 01400   | FA LO DD             |                                                                             |

| 59       | EXADS   | I        | CMOS    | 50 kΩ PD<br>3.3 V 耐圧 | テスト端子                                                                       |

|          | 5/50140 | <u> </u> | 01100   |                      | (GND に接続)                                                                   |

| 60       | EXROMS  | I        | CMOS    | 50 kΩ PD<br>3.3 V 耐圧 | テスト端子                                                                       |

|          | 5×0+11+ |          | 0 1 111 |                      | (GND に接続)                                                                   |

| 61       | EXCHN   | I        | Schmitt | 50 kΩ PD             | チャネル変更制御入力                                                                  |

|          |         |          |         | 3.3 V 耐圧             | チャネル変更信号を入力します(アクティブ・ハイ)<br>I <sup>2</sup> C バス・レジスタ CH(SA00h: D4)で制御する場合はこ |

|          |         |          |         |                      | の端子を Low に固定してください                                                          |

| 62       | EXHNC   | ı        | Schmitt | 50 kΩ PD             | 強制同期はずれ制御入力                                                                 |

|          |         |          |         | 3.3 V 耐圧             | この端子を High にすると強制的にハンチング状態となりま                                              |

|          |         |          |         |                      | す。l <sup>2</sup> C バス・レジスタ HNCS(SA06h: D7, D6)で制御す                          |

|          |         |          |         |                      | る場合はこの端子を Low に固定してください ( OR 論理 )                                           |

| 63       | GRSW    | ı        | Schmitt | 50 kΩ PD             | ゴースト低減動作 ON/OFF                                                             |

|          |         |          |         | 3.3 V 耐圧             | High:ゴースト低減動作 OFF                                                           |

|          |         |          |         |                      | Low:ゴースト低減動作 ON                                                             |

|          |         |          |         |                      | I <sup>2</sup> C バス・レジスタ GRMD [0] (SA00h: D6) で制御する場                        |

|          |         |          |         |                      | 合はこの端子を Low に固定してください                                                       |

| 64       | FDS     | 0        | CMOS    | 3 mA                 | テスト端子                                                                       |

|          |         |          |         | 3.3 V 耐圧             |                                                                             |

| 65       | DLE     | 0        | CMOS    | 3 mA                 | テスト端子                                                                       |

|          |         |          |         | 3.3 V 耐圧             |                                                                             |

表1-1 端子機能一覧(4/5)

| 端子番号       | 端子略号   | I/O | レベル        | バッファ・          | 機能                                                                    |

|------------|--------|-----|------------|----------------|-----------------------------------------------------------------------|

|            |        |     |            | タイプ            |                                                                       |

|            |        |     |            | PU/PD [kΩ]     |                                                                       |

| 66         | HNC    | 0   | CMOS       | 3 mA           | 同期はずれ検出出力                                                             |

|            |        |     |            | 3.3 V 耐圧       | 同期はずれを検出したときに High が出力されます<br>I <sup>2</sup> C バスにも出力されます             |

| 07         | GCR    |     | CMOS       | 3 mA           |                                                                       |

| 67         | GCR    | 0   | CMOS       | _              | GCR 信号検出出力                                                            |

|            |        |     |            | 3.3 V 耐圧       | 入力されたビデオ信号から GCR 信号を検出すると High<br>が出力されます。I <sup>2</sup> C バスにも出力されます |

| 68         | GCON   | 0   | CMOS       | 3 mA           | ゴースト低減動作状態出力                                                          |

|            |        |     |            | 3.3 V 耐圧       | ゴースト低減動作を開始すると High が出力されます I <sup>2</sup> C バスにも出力されます               |

| 69         | ROMSB  | 0   | CMOS       | 3 mA           | テスト端子                                                                 |

|            |        |     |            | 3.3 V 耐圧       |                                                                       |

| 70         | WRB    | 0   | CMOS       | 3 mA           | テスト端子                                                                 |

|            |        |     |            | 3.3 V 耐圧       |                                                                       |

| 71         | RDB    | 0   | CMOS       | 3 mA           | テスト端子                                                                 |

|            |        |     |            | 3.3 V 耐圧       |                                                                       |

| 74-81      | D7-D0  | I/O | CMOS       | 50 kΩ PU       | テスト端子                                                                 |

|            |        |     |            | 3 mA           |                                                                       |

|            |        |     |            | 3.3 V 耐圧       |                                                                       |

| 82-88, 90, | A0-A19 | 0   | CMOS       | 3 mA           | テスト端子                                                                 |

| 92, 94-104 |        |     |            | 3.3 V 耐圧       |                                                                       |

| 105        | SCL    | -1  | Schmitt/FS | 5 V 耐圧         | I <sup>2</sup> C バス・クロック入力                                            |

|            |        |     |            |                | システムの I <sup>2</sup> C バス・クロック・ラインに接続                                 |

| 106        | SDA    | I/O | Schmitt/FS | 6 mA           | I <sup>2</sup> C バス・データ入出力                                            |

|            |        |     | /Nch OD    | 5 V 耐圧         | システムの I <sup>2</sup> C バス・データ・ラインに接続                                  |

| 107        | ALLRST | -1  | Schmitt/FS | 5 V 耐圧         | リセット入力                                                                |

|            |        |     |            |                | μ PD64031A 全体のリセットを行います                                               |

|            |        |     |            |                | (アクティブ・ロウ)                                                            |

| 110        | WP2    | I/O | CMOS       | 50 kΩ PD       | I <sup>2</sup> C 汎用入出力                                                |

|            |        |     |            | 3 mA           | 8 ビットの PWM 入出力( リセット直後は入力モードです )                                      |

|            |        |     |            | 5 V 耐圧         |                                                                       |

| 111        | WP3    | I/O | CMOS       | 50 kΩ PD       | I <sup>2</sup> C 汎用入出力                                                |

|            |        |     |            | 3 mA<br>5 V 耐圧 | 8 ビットの PWM 入出力( リセット直後は入力モードです )                                      |

| 112        | VBLK   | 0   | CMOS       | 3 mA           | 垂直プランキング信号出力                                                          |

|            |        |     |            | 5 V 耐圧         | 各フィールドの先頭 9H 期間 Low を出力します                                            |

| 113        | ADCP   | 0   | CMOS       | 3 mA           | テスト端子                                                                 |

|            |        |     |            | 5 V 耐圧         |                                                                       |

表1-1 端子機能一覧(5/5)

| 端子番号                            | 端子略号             | I/O | レベル     | バッファ・<br>タイプ<br>PU/PD [kΩ] | 機能                                                  |

|---------------------------------|------------------|-----|---------|----------------------------|-----------------------------------------------------|

| 114                             | ADCK             | 0   | CMOS    | 3 mA<br>5 V 耐圧             | テスト端子                                               |

| 115-124                         | DI9-DI0          | I   | CMOS    | 50 kΩ PD<br>5 V 耐圧         | テスト端子                                               |

| 126                             | EXCS             | ı   | Schmitt | 5 V 耐圧                     | コンポジット同期分離入力<br>外部同期分離回路より分離されたコンポジット同期信号を<br>入力します |

| 128                             | EXVS             | I   | Schmitt | 5 V 耐圧                     | 垂直同期分離入力<br>外部同期分離回路より分離された垂直同期信号を入力しま<br>す         |

| 129                             | LE               | 0   | CMOS    | 3 mA<br>3.3 V 耐圧           | 直流誤差レベル出力                                           |

| 131                             | VCL              | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ・クランプ基準電位                                  |

| 132                             | CL               | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ・クランプ出力                                    |

| 134                             | VIN              | I   | Analog  | 2.5 V 耐圧                   | 映像信号入力                                              |

| 135                             | VRT              | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ・トップ基準電圧                                   |

| 136                             | VCOM             | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ同相基準電圧                                     |

| 137                             | VRB              | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ・ボトム基準電圧                                   |

| 138                             | IB               | 0   | Analog  | 2.5 V 耐圧                   | A/D コンバータ基準電圧                                       |

| 141                             | VOUT             | 0   | Analog  | 2.5 V 耐圧                   | 映像信号出力                                              |

| 142                             | СВРО             | I   | Analog  | 2.5 V 耐圧                   | D/A コンバータ位相補償                                       |

| 21, 57, 93                      | DVDDIO           | -   | -       |                            | IO 部電源 ( 3.3 V )                                    |

| 36, 41, 52,<br>133, 143         | AV <sub>DD</sub> | -   | -       |                            | アナログ部 2.5 V 電源                                      |

| 37, 39, 48,<br>130, 139,<br>140 | AGND             | -   | -       |                            | アナログ部接地                                             |

#### 2. システム概要

#### 2.1 動作モード

$\mu$  PD64031A には,主にゴースト低減動作 ON または OFF の 2 つのモードがあります。設定方法は,シリアル・バス・レジスタ GRMD (SA00h: D7, D6)か, GRSW 端子 (63 ピン)で行います。シリアル・バス・レジスタ GRMD およびレジスタ SWSEL (SA00h: D5)ではゴースト低減動作 ON/OFF の制御方法の設定も行います。

なお , ゴースト低減動作の ON/OFF を行う際のシリアル・バスと端子の優先順位関係については , **2**. **5** ポート制 御と  $I^2$ C レジスタ制御の関係についてを参照してください。

シリアル・バス設定, 機 長, 端子設定 モデル図 レジスタ GRMD = 00 ・入力信号から GCR 信号を検出し,ゴースト低減動作可能な場合,CPU ゴースト低減動作 でフィルタ係数の演算を行い、その結果を GR フィルタに適用すること かつ でゴーストの低減を行います。 GRSW 端子 = Low ADC GRフィルタ 映像信号入力 -- DAC ► 映像信号出力 "ON" CPU "ON" ・入力信号の状態にかかわらず,ゴースト低減動作を停止します。 レジスタ SWSEL = 0 ゴースト低減動作停止 かつ (アパーチャ補正あり) ・レジスタ SWSEL = 0 のとき,内蔵 CPU により停止制御が行われます。 ・このとき, GR フィルタは動作しますが, CPU が演算を停止しフィルタ レジスタ GRMD = 01 係数が GR フィルタに設定されないため,ゴースト低減動作は行われま または GRSW 端子 = High ・出力信号にはアパーチャ補正のみがかかります(レジスタ RFS = 1xxx 選 択時》。 GRフィルター ADC DAC 映像信号入力 ▶ 映像信号出力 "ON" CPU "OFF"

表2-1 動作モード一覧表 (1/2)

| シリアル・バス設定,     | 機能          | 特 長,                                        |  |  |  |  |  |

|----------------|-------------|---------------------------------------------|--|--|--|--|--|

| 端子設定           |             | モデル図                                        |  |  |  |  |  |

| レジスタ SWSEL = 1 | ゴースト低減動作停止  | ・入力信号の状態にかかわらず,ゴースト低減動作を停止します。              |  |  |  |  |  |

| かつ             | (アパーチャ補正なし) | ・レジスタ SWSEL = 1 のとき ,GR フィルタにより停止制御が行われます。  |  |  |  |  |  |

| レジスタ GRMD = 01 |             | ・このとき , CPU は動作しますが , GR フィルタが動作していないため ,   |  |  |  |  |  |

| または            |             | ゴースト低減動作は行われません。                            |  |  |  |  |  |

| GRSW 端子 = High |             | ・出力には入力信号がそのままスルーされます(アパーチャ補正もかかり           |  |  |  |  |  |

|                |             | ません )。                                      |  |  |  |  |  |

|                |             | 映像信号入力 → ADC GR7ィルタ → DAC → 映像信号出力 CPU "ON" |  |  |  |  |  |

| レジスタ GRMD = 1x | スルー         | ・入力された信号を GR フィルタを通さずそのまま出力します。             |  |  |  |  |  |

|                | (遅延最短)      | ・このとき , 信号は GR フィルタを通らないため遅延時間が最短となりま       |  |  |  |  |  |

|                |             | <b>ब</b> ं.                                 |  |  |  |  |  |

|                |             | 映像信号入力 ———————————————————————————————————— |  |  |  |  |  |

表 2-1 動作モード一覧表 (2/2)

#### 2.2 動作概要

$\mu$  PD64031A のゴースト低減動作は次の手順で行われます。

- (1) リセット, またはチャネル変更信号が入力された時点から動作を開始します。

- (2) 入力されたコンポジット・ビデオ信号から GCR 信号を取り出します。

- (3) 取り出された GCR 信号は CPU に送られ, CPU でゴーストの位置や強さ,周波数特性を解析します。

- (4)解析結果から,波形等化およびゴースト低減動作を行うためのフィルタ係数を演算します。

- (5) CPU で得られたフィルタ係数が GR フィルタにセットされ,ゴースト低減動作を開始します。

この(2)-(4)の動作を1回のサイクルとして,以降,次にチャネル変更が行われるまで繰り返します。このとき1サイクル内でのGCR信号の解析回数は,サイクルが進むにつれて増加していきます。取り込まれたGCR信号は積分されるので,トータルの解析回数が増えるに従い,フィルタ係数の精度が向上します。

表 2 - 2に GCR 信号の解析回数とその処理時間を示します。

| フィルタ係数設定                  | 1 回目 | 2 回目 | 3 回目 | 4 回目 | 5 回目 | 6 回目 | 7 回目 | 8 回目 | 9 回目 | 10 回目以降 |

|---------------------------|------|------|------|------|------|------|------|------|------|---------|

| GCR 解析回数 注1               | 1    | 2    | 4    | 8    | 16   | 32   | 64   | 128  | 256  | 256     |

| 処理時間 ( 秒 ) <sup>注 2</sup> | 1.2  | 2.4  | 4.2  | 7.0  | 12   | 22   | 39   | 74   | 142  | 278     |

表2-2 フィルタ係数処理時間

- **注 1.** 1回目の解析回数と最終的な解析回数はシリアル・バス・レジスタ INTS( SA03h: D5-D3 )および INTE( SA03h: D2-D0 ) で設定可能です。表 2 2 は初期値(初回:1回,最大:256回)の場合のものです。

- 2. 表内の数値は計算値です。実際にはゴーストの状況などによって多少変動する場合があります。

#### 2.3 ゴースト低減範囲について

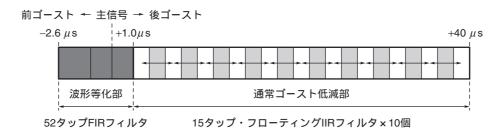

$\mu$  PD64031A は 52 タップの FIR フィルタによる波形等化部(近接ゴースト低減)と 15 タップの IIR フィルタ x 10 個からなる通常ゴースト低減部から構成されています。これにより入力信号の - 2.6 ~ + 1.0  $\mu$  s の範囲の近接ゴーストと 1.0 ~ 40  $\mu$  s の範囲の通常ゴーストを低減することができます。

図2 - 1 GR フィルタ概要図

波形等化部における周波数特性補正時のレファレンス波形はシリアル・バス・レジスタ RFS ( SA02h: D3-D0 ) により 12 種類 ( 6 波形×アパーチャ補正あり / なし ) の中から選択することができます。また,前ゴーストの低減範囲はシリアル・バス・レジスタ PREGHSTS ( SA02h: D4 ) により, - 1.0  $\mu$ s まで,または - 2.6  $\mu$ s までの 2 種類を設定できます。

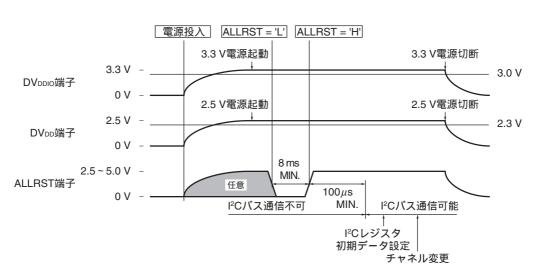

#### 2.4 電源起動とリセット

$\mu$  PD64031A は , 内周部用電源 2.5 V (ディジタル , アナログ ) と外周部用電源 3.3 V の 2 電源を必要とします。電源起動のシーケンスとシステムのリセットの方法を次に示します。

図2-2 電源投入とリセットのシーケンス

起動とリセットの手順は次のようになります。

- ・内周部用 2.5 V 電源 ( DVpp および AVpp ) と外周部用 3.3 V 電源 ( DVppo ) を同時に投入します。

- ・リセット信号は ALLRST 端子 (107 ピン) に入力します。各電源が起動後に 8 ms 以上のパルス幅で行ってください。なお, CPURST 端子 (56 ピン) は特にリセットをかける必要はありません (DVppio にプルアップ)。

- ・ $\rm I^2C$  通信はリセット完了後 100  $\mu$  s 以上経過後に可能となります。レジスタ設定はこのあとで開始してください。

- ・I<sup>2</sup>C レジスタ設定後,チャネル変更信号を入力することでゴースト低減動作を開始します。

#### 2.4.1 電源投入時と切断時の注意事項

- ・電源投入時,内周部用 2.5 V 電源 (DVpp および AVpp ) は外周部用 3.3 V 電源 (DVpp pp ) 投入後,10 ms 以内に起動するようにしてください。

- ・電源切断時, 内周部用 2.5 V 電源(DVDD および AVDD)と外周部用 3.3 V 電源(DVDDIO)の切断は同時に行ってください。

- ・内周部用 2.5 V 電源 ( DVpp および AVpp ) 切断時に , 外周部用 3.3 V 電源 ( DVppio ) だけを印加しないでください。

#### 2.4.2 CPU リセットについて

CPURST 端子により $\mu$  PD64031A 内蔵の CPU のみリセットをかけることができます。このとき ,  $I^2$ C レジスタ設定値は保持されます (初期化されません)。

## 2.5 ポート制御と I<sup>2</sup>C レジスタ制御の関係について

$\mu$  PD64031A には一部ポートとシリアル・バスの両方に割り振られている制御機能があります。2. 5. 1 から 2. 5. 4 に , ポートと  $I^2$ C レジスタの優先順位について説明します。

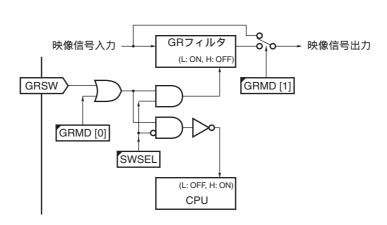

## 2. 5. 1 ゴースト低減動作 ON/OFF 制御

ゴースト低減動作の ON/OFF は GRSW 端子かもしくはレジスタ GRMD [0]で行います。両信号は次の図のような論理で制御されています。したがって,端子と  $I^2C$  の両方がアクティブ (Low) のときゴースト低減動作を行い,どちらか一方でも OFF 設定になると動作を停止します。

図2 - 3 ゴースト低減動作 ON/OFF 制御

| ゴースト低減    | 動作状態 | GRSW 端子 |          |  |  |  |

|-----------|------|---------|----------|--|--|--|

|           |      | High    | Low      |  |  |  |

| レジスタ GRMD | 00   | 停止      | ゴースト低減動作 |  |  |  |

| [1: 0]    | 01   | 停止      | 停止       |  |  |  |

|           | 1x   | スルー     | スルー      |  |  |  |

表2-3 ゴースト低減動作状態

注意 1. ポート制御を行う場合,シリアル・バス・レジスタ GRMD は 00 に設定してください。

2. I<sup>2</sup>C による制御を行う場合, GRSW 端子は Low に固定してください。

シリアル・バス・レジスタ SWSEL (SA00h: D5) は GRSW 端子またはシリアル・バス・レジスタ GRMD [0]によるゴースト低減動作の ON/OFF を , GR フィルタで行うか CPU で行うかを決定します (2.1 動作モード参照)。

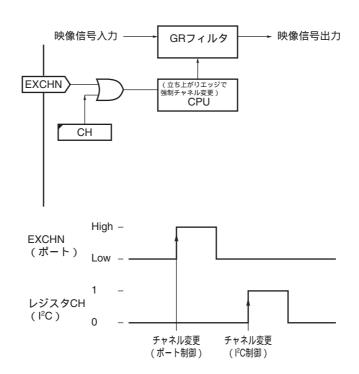

#### 2.5.2 チャネル変更制御

チャネル変更入力は EXCHN 端子(61 ピン)かもしくはシリアル・バス・レジスタ CH(SA00h: D4)で行います。 両信号は OR 論理で制御されていますので, どちらかをアクティブ(High)にすればチャネル変更が行われます。

図2-4 チャネル変更制御

- 注意 1. ポート制御を行う場合,シリアル・バス・レジスタ CH は 0 に設定してください。

- 2. I<sup>2</sup>C による制御を行う場合, EXCHN 端子は Low に固定してください。

#### 2.5.3 強制ハンチング制御

強制ハンチング入力は EXHNC 端子 (62 ピン) かもしくはシリアル・バス・レジスタ HNCS (SA06h: D7, D6) で行います。両信号は OR 論理で制御されていますので, どちらかをアクティブ (High) にすれば強制ハンチング状態となります。

図2-5 強制ハンチング制御

表2-4 ハンチング状態

| ハンチング     | ブ状態 | EXHNC 端子 |                |  |  |  |

|-----------|-----|----------|----------------|--|--|--|

|           |     | High     | Low            |  |  |  |

| レジスタ HNCS | 00  | 強制ハンチング  | GR フィルタ判定結果による |  |  |  |

| [1: 0]    | 01  | 強制ハンチング  | 強制非ハンチング       |  |  |  |

|           | 10  | 強制ハンチング  | 強制ハンチング        |  |  |  |

- 注意 1. 特に強制ハンチング設定を使用する必要がない場合は, EXHNC 端子は Low に固定, シリアル・バス・レジスタ HNCS は 00 に設定してください。

- 2. ポート制御により強制ハンチング設定を行う場合,シリアル・パス・レジスタ HNCS は 00 に設定してください。

- 3. I<sup>2</sup>C 制御による強制ハンチング設定を行う場合, EXHNC 端子は Low に固定してください。

- 4. 強制非ハンチング設定を行うには , EXHNC 端子は Low に , シリアル・バス・レジスタ HNCS を 01 に設定してください。

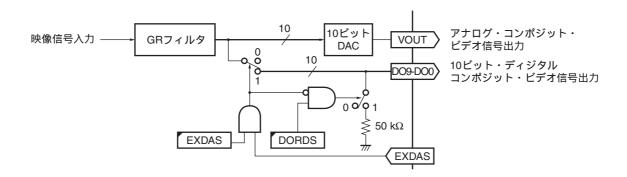

## 2.5.4 ディジタル・データ出力制御

ディジタル出力端子の設定は EXDAS 端子 (58 ピン) とシリアル・バス・レジスタ EXDAS (SA01: D7) で行います。両信号は AND 論理で制御されていますので,同時にアクティブに設定することでディジタル出力が有効となります。

図2-6 ディジタル・データ出力制御

表2-5 ディジタル出力端子の状態

| ディジタル出力端   | 岩子の状態 | EXDAS 端子   |            |  |  |  |

|------------|-------|------------|------------|--|--|--|

|            |       | High       | Low        |  |  |  |

| レジスタ EXDAS | 0     | ハイ・インピーダンス | ハイ・インピーダンス |  |  |  |

|            | 1     | ディジタル出力    | ハイ・インピーダンス |  |  |  |

注意 特にディジタル出力を使用する必要がない場合は, EXDAS 端子は Low に固定してください。

## 3. コンポジット・ビデオ信号入力ブロック

このブロックでは,コンポジット・ビデオ信号の A/D 変換を行います。

ADCPSEL クランプ・パルス **AGND** 発生回路 10ビットADC -₩-VCL  $33 \mu F$ クランプ CL  $47 \mu F$ コンポジット・ビデオ信号入力 #+ (内部ADC使用時)  $AV_{DD}$ 0.1 μF  $\dashv \vdash$ +# 10 VIN 140IRE = 0.5 V<sub>P-P</sub> -内部へ A/Dコア 2.2 *μ* F **}**  $\dashv$ VRT 0.22 *μ* F  $\dashv\vdash$ VCOM バイアス 0.22*μ* F 0 ~ 3/4CLK  $\dashv\vdash$ **VRB** delay 0.22 μ F \_-/\/. 4.7 kΩ ΙB CLK < 4fsc -\\\ **EXADS** ADCPMD ADCLKS FBIASEN

図3-1 コンポジット・ビデオ信号入力プロック概要図

#### 3.1 コンポジット・ビデオ信号入力

コンポジット・ビデオ信号を VIN 端子 (134 ピン) に入力します。入力されたコンポジット・ビデオ信号は内部の 10 ビット A/D コンバータでディジタル・コンポジット・ビデオ信号に変換します (EXADS 端子 (59 ピン) が Low のとき )。

#### 3.2 クランプ回路およびバイアス回路

内蔵 A/D コンバータ入力部にはペデスタル・クランプ回路とバイアス回路が内蔵されています。クランプ回路使用時は入力信号のペデスタル位置を VCL (131 ピン)端子電圧 (0.9 V TYP.)でクランプを行います。バイアス回路は入力信号の DC レベルが内蔵 A/D コンバータ入力間口の中心 (1.0 V TYP.)に一致するようバイアスをかけます。これらのどちらを使用するかはシリアル・バス・レジスタ ADCPMD (SA04h: D5, D4)で選択することができます。

| ADCPMD ( SA04h: D5, D4 ) | 機能      | 動作                                                                |

|--------------------------|---------|-------------------------------------------------------------------|

| 00                       | 両方とも使用  | 通常はクランプ回路を使用しますが、映像の乱れが大きくなり同期検出できないような場合(ハンチング時)はバイアス回路に切り替わります。 |

| 01                       | クランプ    | 常にクランプ回路を使用します(標準設定)。                                             |

| 10                       | バイアス    | 常にバイアス回路を使用します。                                                   |

| 11                       | 両方とも不使用 | どちらも使用しません。                                                       |

表3-1 クランプ回路およびバイアス回路

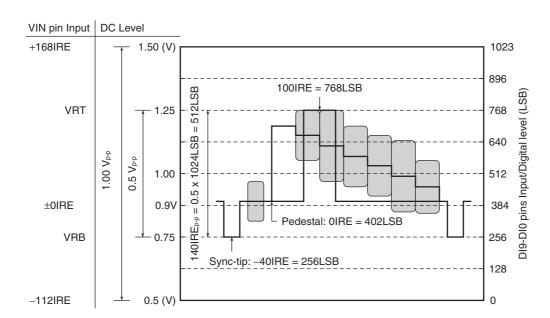

#### 3.3 コンポジット・ビデオ信号入力レベル

入力されるコンポジット・ビデオ信号は、ゴーストが重畳した影響で振幅が膨らみ過大なレベル(オーバシュート、アンダシュート)が含まれることが考えられます。正確なゴースト低減動作を行うには、これらのゴースト成分による過大なレベルの信号も取り込む必要があります。したがって $\mu$  PD64031A へのコンポジット・ビデオ信号の入力レベルは入力レンジに対して十分に余裕をとる必要があります。コンポジット・ビデオ信号入力振幅を 140IRE = 0.5 V<sub>P-P</sub> (最大入力レンジ 1 V<sub>P-P</sub> の半分 512LSB)としてください。

図3-2 コンポジット・ビデオ信号入力波形例 (クランプ使用,標準カラー・パー入力時)

#### 3.4 端子処理など

- ・AV<sub>DD</sub> 端子には, 2.5 V 電源を投入します。ディジタル部電源とは十分なアイソレーションを行ってください。

- ・AGND 端子, 各バイパス・コンデンサの接地は, 配線パターンを極力太く広くしてください。

- ・VIN 端子には,コンポジット・ビデオ信号を容量結合で入力します。コンポジット・ビデオ信号は,極力低インピーダンスで入力してください。電解コンデンサと VIN 端子間の配線は,極力太く短くしてください。

- ・基準電圧端子 VRT ( 135 ピン ), VCOM ( 136 ピン ), VRB ( 137 ピン ) には , 0.22  $\mu$  F 程度のバイパス・コンデンサを接続してください。

- ・クランプ電圧端子 VCL には , 33  $\mu$  F 程度の電解コンデンサを接続してください。

## 4. クロック生成/タイミング生成プロック

このブロックでは、コンポジット・ビデオ信号からシステム・クロックやタイミング信号を生成します。

図4-1 クロック生成/タイミング生成プロック概要図

#### 4.1 コンポジット同期信号入力

EXCS 端子(126 ピン)には, VIN 端子(134 ピン)に入力するコンポジット・ビデオ信号から分離された, コンポジット同期信号を入力します。入力論理はシリアル・バス・レジスタ EXCSP(SA05h: D6)で, アクティブ・ロウ(初期値)かアクティブ・ハイかを選択することができます。

この入力は,タイミング・ジェネレータの基準信号として使用するほか,同期はずれ検出にも使用されます。また,システム・ディレイ分遅延されて CSO 端子(4 ピン)より,アクティブ・ロウで出力されます(この出力は3次元 Y/C 分離IC とのディジタル接続時に使用します)。

#### 4.2 垂直同期信号入力

EXVS 端子(128 ピン)には, VIN 端子に入力するコンポジット・ビデオ信号から分離された, 垂直同期信号を入力します。入力論理はシリアル・バス・レジスタ EXVSP(SA05h: D4)で, アクティブ・ロウ(初期値)かアクティブ・ハイかを選択することができます。

この入力は、タイミング・ジェネレータの基準信号として使用するほか、同期はずれ検出にも使用されます。

## 4.3 タイミング・ジェネレータ

タイミング・ジェネレータでは 4fsc でサンプリングされたコンポジット・ビデオ信号と外部より入力される水平同期信号と垂直同期信号を基準信号として,各種のシステム・タイミングを生成します。

#### 4.4 パースト PLL 回路

4fsc でサンプリングされたコンポジット・ビデオ信号からバースト信号の位相誤差を検出し,後段の fsc ジェネレータの発振周波数を決定します。

#### 4.5 キラー検出回路

バースト信号の振幅を、シリアル・バス・レジスタ KILS (SA0Eh: D3-D0)設定値と比較し、カラー・キラー判定を行います。バースト振幅が KILS 設定値以下となった場合、fsc ジェネレータの発振周波数をフリーランとします。

#### 4.6 fsc ジェネレータ

PLL フィルタで決定された発振周波数をもとに fsc を生成します。fsc を内部 D/A コンバータでアナログのサイン波形に変換し,FSCO 端子(47 ピン)に出力します。この出力には,D/A 変換時の高調波成分が含まれているため,バッファを介して外部の BPF(バンド・パス・フィルタ)で高調波成分を除去してから,容量結合で FSCI 端子(40 ピン)に入力します。fsc ジェネレータでは,基準クロックとして 20 MHz のフリーラン・クロックを使用しています。

#### 4.7 8fsc PLL 回路

FSCI 端子から入力された fsc から ,8 逓倍の 8fsc を生成します。この 8fsc を CLK8 端子 (30 ピン)に出力し同時に内部のシステム・クロックとして使用します。また , CKMD 端子 (31 ピン)を High (3.3V 電源ヘプルアップ)とした場合 , システム・クロックは , 内部発生したものでなく , CLK8 端子に入力される外部クロックを使用します (3 次元 Y/C 分離 IC とのディジタル直結時に使用します )。

#### 4.8 端子処理など

- ・AVpp 端子には , 2.5 V 電源を投入します。ディジタル部の電源とは十分なアイソレーションを行ってください。

- ・DGND, AGND 端子, 各バイパス・コンデンサの接地は, 配線パターンを極力太く広くとってください。

- ・XI 端子 (51 ピン), XO 端子 (49 ピン)には, 20 MHz の水晶発振子を接続します。ほかのブロックと干渉しないよう, GND パターンによるガード領域を設けてください。表 4 1 に, 水晶発振子の仕様例を示します。

- ・FSCO 端子は,エミッタ・フォロワを介して BPF に接続してください。FSCI 端子には,容量結合で fsc 信号を入力します。

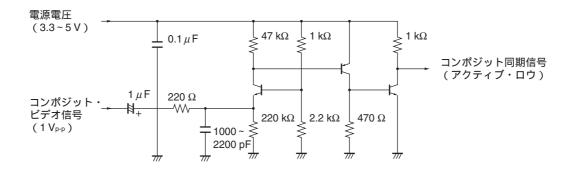

- ・EXCS 端子にはアクティブ・ロウ(またはアクティブ・ハイ)のコンポジット同期信号を入力します。図 4 2 にコンポジット同期分離回路例を示します。

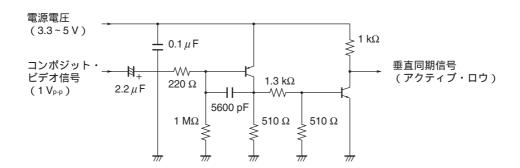

- ・EXVS 端子にはアクティブ・ロウ(またはアクティブ・ハイ)の垂直同期信号を入力します。図4-3に垂直同期分離回路例を示します。

| 項目      | 規 格                 |

|---------|---------------------|

| 公称発振周波数 | 20.000000 MHz (基本波) |

| 負荷容量    | 16 pF               |

| 直列抵抗成分  | 40 Ω以下              |

| 周波数偏差   | 50 ppm 以下           |

| 温度偏差    | 50 ppm 以下           |

表4-1 水晶発振子仕樣例

#### 図4-2 コンポジット同期分離回路例

図4-3 垂直同期分離回路例

## 4.9 外部同期分離回路設計時の注意点

コンポジット同期信号と垂直同期信号のタイミングは以下の条件を満たしてください。

コンポジット同期信号入力に対する垂直同期信号入力の許容遅延範囲:4~30 µs(約1/2H以下)

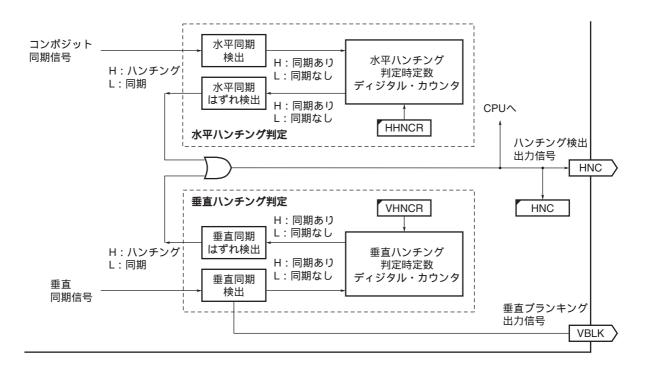

#### 5. 同期はずれ検出ブロック

このブロックでは,非常に強いゴーストが重畳されるなどの精度の悪い信号を検出します。ここでの検出結果は, ゴースト低減処理の停止に利用します。

図5-1 同期はずれ検出ブロック概要図

#### 5.1 水平同期はずれ判定

水平同期検出回路において,入力されたコンポジット同期信号より同期信号期間を検出し,それが一定間隔であるとき,水平同期がとれていると判定します。この判定結果を時定数回路で積分します。この時定数はシリアル・バス・レジスタ HHNCR (SA06h: D5-D0) で設定できます。この積分結果より水平同期はずれ検出回路で水平同期はずれかどうか検出します。

#### 5.2 垂直同期はずれ判定

入力された垂直同期信号と水平同期信号より、奇数フィールドを検出します。この奇数フィールドの開始点が一定間隔であるとき垂直同期がとれていると判定します。この判定結果を時定数回路で積分します。この時定数はシリアル・バス・レジスタ VHNCR (SA07h: D5-D0)で設定できます。この積分結果より垂直同期はずれ検出回路で垂直同期はずれかどうか検出します。

#### 5.3 ハンチング検出

水平あるいは垂直のいずれか同期はずれを検出すると,次に同期が検出されるまでハンチング信号を CPU に与えます。またこの信号は HNC 端子(66 ピン)とシリアル・バス・レジスタにも出力されます。

## 6. コンポジット・ビデオ信号出力ブロック

このブロックでは,ディジタル・コンポジット・ビデオ信号の D/A 変換,およびディジタル出力を行います。

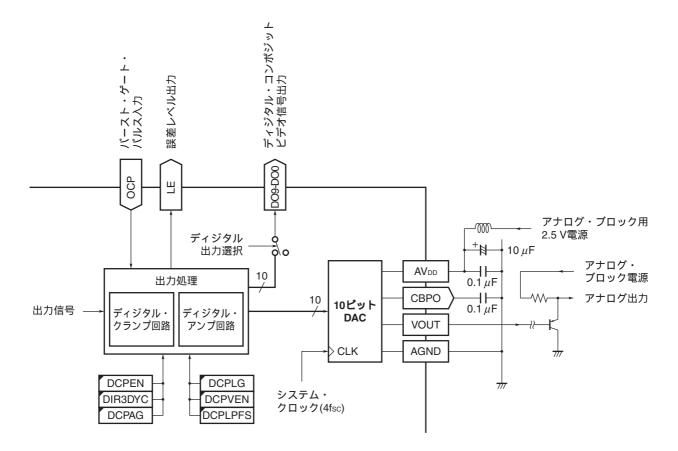

図6-1 コンポジット・ビデオ信号出力ブロック

## 6.1 ディジタル・コンポジット・ビデオ信号出力処理

10 ビット・ストレート・バイナリのコンポジット・ビデオ信号が, DO9-DO0 端子 (6-15 ピン) から 4fsc のクロック・レートで出力されます。

EXDAS 端子 (58 ピン) およびシリアル・バス・レジスタ EXDAS で , ディジタル出力の有効 / 無効を切り替えることができます。無効に設定したとき , DO9-DO0 端子はハイ・インピーダンスとなります。詳しくは **2.5 ポート制御と I^2C レジスタ制御の関係について**を参照してください。

#### 6.2 コンポジット・ビデオ信号出力レベル

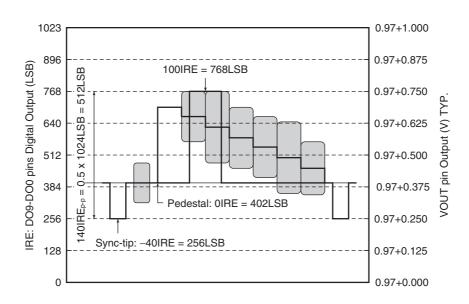

図 6 - 2 に , 標準的なコンポジット・ビデオ信号入力 (3. コンポジット・ビデオ信号入力ブロック参照 ) を行った場合の DO9-DO0 端子および VOUT 端子 (141 ピン ) の出力波形を示します。

25

#### 6.3 ディジタル・クランプ・アンプ機能

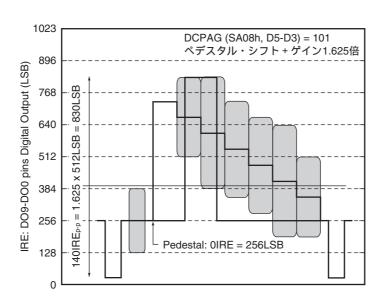

$\mu$  PD64031A の後段に 3 次元 Y/C 分離 IC などをディジタル直結する場合,ディジタル・クランプ・アンプ回路で出力信号のペデスタル・レベルの調整と振幅の制御(ペデスタル位置が中心)を行うことができます。この機能を使用するには,ディジタル出力を有効としたうえで,シリアル・バス・レジスタ DCPEN(SA09h: D6)と DIR3DYC(SA08h: D7, D6)を設定する必要があります。また,ペデスタル位置の調整とゲインの設定はシリアル・バス・レジスタ DCPAG (SA08h: D5-D3)で設定します。ディジタル・クランプ時のクランプ・パルスは OCP 端子(18 ピン)より入力する必要があります。図 6-3 にディジタル・クランプ時(ペデスタル・シフト+ゲイン 1.625 倍に設定)のディジタル・コンポジット・ビデオ信号出力波形を示します。

図6-2 コンポジット・ビデオ信号出力波形例(標準カラー・バー入力時)

図6 - 3 ディジタル・コンポジット・ビデオ信号出力波形例 (0.5 Vp-p 標準カラー・バー入力,ディジタル・クランプ・アンプ使用時)

## 6.4 端子処理など

- ・AV<sub>DD</sub> 端子には, 2.5 V 電源を投入します。ディジタル部電源とは十分なアイソレーションを行ってください。

- ・AGND 端子,バイパス・コンデンサの接地は,配線パターンを極力太く広くしてください。

- ・CBPO 端子 ( 142 ピン ) には ,  $0.1 \mu$  F 程度のコンデンサを接続してください。

## 7. I<sup>2</sup>C バス・インタフェース

#### 7.1 基本仕様

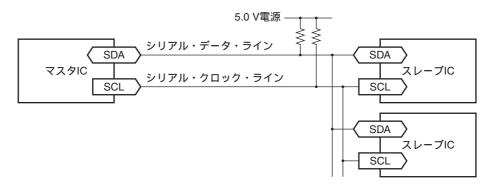

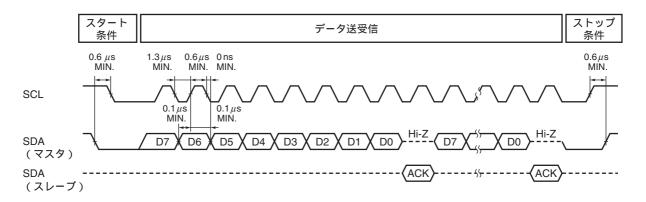

I<sup>2</sup>C バスはフィリップス社が開発した 2 線式双方向シリアル・バスです。IC 間で通信を行うシリアル・データ・ライン (SDA)と,通信の同期をとるためのシリアル・クロック・ライン (SCL)の 2 線で構成されています。

図7 - 1 I<sup>2</sup>C パス・インタフェース

マスタ IC からスレーブ IC へ送信を行う場合の手順を,次に示します。

スタート条件:SCLを'H'に保持したまま,SDAを'H'から'L'に立ち下げ,通信を開始します。

データ送受信: SDA を保持したまま, SCL を 'L'から'H'に立ち上げ, データ送信を行います。各アドレスやデータの送受信は, データ・ビット (D7-D0: MSB first) とアクノリッジ・ビット (ACK) の 9 ビット単位で行います。選択されたスレーブ IC は, 9 ビット目で SDA を 'L'とし, アクノリッジを送信します。

ストップ条件: アクノリッジ通信後, SCL を 'H'に保持したまま, SDA を 'L'から 'H'に立ち上げ, 通信を終了します。

図7-2 スタート条件,データ送受信,ストップ条件フォーマット

#### 7.2 データ送受信フォーマット

マスタ側のスタート条件発行直後に , スレーブ・アドレスの受信を行います。 $\mu$  PD64031A のスレーブ・アドレス と ,受信したスレーブ・アドレスが一致した場合 ,通信を開始し ,不一致の場合 ,SDA ラインを解放します。 $\mu$  PD64031A のスレーブ・アドレスは , SLA0 端子 (20 ピン) 設定で 2 組の指定が行えます。

| SLA0 端子設定    | スレーブ・           | ・アドレス           |

|--------------|-----------------|-----------------|

| (電源投入後は変更不可) | ライト・モード         | リード・モード         |

| L            | 24h (00100100b) | 25h (00100101b) |

| Н            | 26h (00100110b) | 27h (00100111b) |

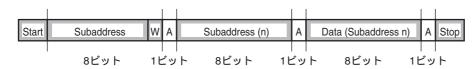

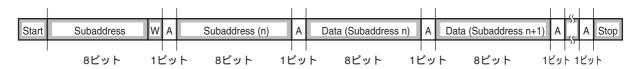

## (1) ライト・モード・フォーマット (スレープ受信)

1 バイト目に自己のライト・モードのスレーブ・アドレスを受信すると, 2 バイト目にサブ・アドレス, 3 バイト目以降にデータを受信します。サブ・アドレスのオート・インクリメント機能により, データの連続受信が可能です。

## 1 バイト・ライト・フォーマット

#### 複数パイト・ライト・フォーマット

**備考** Start : スタート条件 Stop : ストップ条件

W :ライト・モード指定(=0) A :アクノリッジ

| XXX|| : マスタ・デバイス発行 | XXX|| : スレーブ・デバイス ( μPD64031A ) 発行

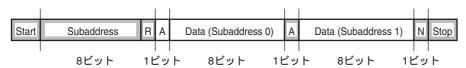

#### (2) リード・モード・フォーマット (スレーブ送信)

1 バイト目に自己のリード・モードのスレーブ・アドレスを受信すると,2 バイト目以降はデータを送信します。このモードにはサブ・アドレス指定はなく,常にアドレス0から送信開始されます。ストップ条件発行前には,マスタ側からノー・アクノリッジを送信し,SDAラインを解放する必要があります。

#### リード・フォーマット

**備考** Start : スタート条件 Stop : ストップ条件

R : リード・モード指定(=1) A : アクノリッジ

N : ノー・アクノリッジ

<u>||xxx||</u>:アクノリッジ | xxx|:スレーブ・デバイス(μPD64031A)発行

データ・シート S14778JJ4V0DS

## 7.3 I<sup>2</sup>C パスの初期化

NEC

$I^2C$  バス・レジスタは ,  $\mu$  PD64031A リセット (ALLRST) と同時に初期化されます。リセット後 100  $\mu$ s 以上経過したあとに通信可能となります。またこのとき , ライト・レジスタは初期値にプリセットされます。リセットの方法は , **2.4 電源起動とリセット**を参照してください。

なお,一部のライト・レジスタは値をセット後,チャネル変更または CPU リセットを行ってはじめて変更が有効となるものがあります。詳細は 8. シリアル・バス・レジスター覧を参照してください。これらのレジスタを変更したあとは,変更を有効にするために必ずチャネル変更信号(または CPU リセット信号)を入力してゴースト低減動作を再スタートさせてください。

30

## 8. シリアル・パス・レジスタ一覧

$\mu$  PD64031A には , ライト・モード (スレーブ受信 ) で書き込み可能な , 24 個の 8 ビット・ライト・レジスタ , リード・モード (スレーブ送信 ) で読み出し可能な , 2 個の 8 ビット・リード・レジスタが内蔵されています。次に , 各 シリアル・バス・レジスタ・マップを示します。

ライト・レジスタ・マップ スレープ・アドレス:00100100b = 24h (SLA0 = L), 00100110b = 26h (SLA0 = H)

|    |               |         |          | Data Map (SA0 | 0-SA17)                       |        |      |         |

|----|---------------|---------|----------|---------------|-------------------------------|--------|------|---------|

| SA | D7            | D6      | D5       | D4            | D3 D2 D1 D0                   |        |      |         |

| 00 | GR            | MD      | SWSEL    | СН            |                               | 0000b  |      |         |

| 01 | EXDAS         | DORDS   | N3D1STEN | LELOW         | CLK8LOW CLK20LOW WP2OEN WP3OE |        |      |         |

| 02 | 0             | 1       | 0        | PREGHSTS      |                               | RE     | ES   |         |

| 03 | CC            | OR      |          | INTS          |                               |        | INTE |         |

| 04 | ADC           | LKS     | ADC      | PMD           | ADCI                          | PSEL   | FCLP | FBIASEN |

| 05 | EXCSS         | EXCSP   | EXVSS    | EXVSP         |                               | EXC    | SDLY |         |

| 06 | HN            | CS      |          |               | НН                            | NCR    |      |         |

| 07 | 0             | 0       |          |               | VHN                           | ICR    |      |         |

| 08 | DIR3          | DYC     |          | DCPAG DCPLG   |                               |        |      |         |

| 09 | 0             | DCPEN   | DCPLPFS  | DCPVEN 0000b  |                               |        |      |         |

| 0A |               |         |          | WP            | 20                            |        |      |         |

| 0B |               |         |          | WP            | 30                            |        |      |         |

| 0C | 0             | PLLFS   | PLLSP    | PLLFG         |                               | 110    | )1b  |         |

| 0D |               |         |          | 5E            | h                             |        |      |         |

| 0E | KILM          | UNLOCKS | KI       | LS            |                               | KII    | LR   |         |

| 0F |               | HS      | SR       |               | VS                            | SR     | 0    | 0       |

| 10 | 0             | 0       |          |               | 0000                          | 000b   |      |         |

| 11 | 0             | 0       | 0        |               |                               | 00000b |      |         |

| 12 | 0             | 0       |          | 000b          |                               |        | 000b |         |

| 13 | 00b 000b 000b |         |          |               |                               |        |      |         |

| 14 |               |         |          | 00            | )h                            |        |      |         |

| 15 | 00h           |         |          |               |                               |        |      |         |

| 16 | 00h           |         |          |               |                               |        |      |         |

| 17 |               |         |          | 00            | )h                            |        |      |         |

注意 当社の性能評価により,シリアル・バス上の固定設定値を変更する場合があります。また,標準値は当社での評価値であり,最適値とはかぎりません。

リード・レジスタ・マップ スレーブ・アドレス: 00100101b = 25h (SLA0 = L), 00100111 = 27h (SLA0 = H)

|    | Data Map (SA00, SA01)                                                                      |     |      |      |     |      |  |  |  |

|----|--------------------------------------------------------------------------------------------|-----|------|------|-----|------|--|--|--|

| SA | SA         D7         D6         D5         D4         D3         D2         D1         D0 |     |      |      |     |      |  |  |  |

| 00 | KILF                                                                                       | HNC | GCON | GCR  | DVG | INTM |  |  |  |

| 01 |                                                                                            |     | WP2I | WP3I | VER |      |  |  |  |

各ライト・レジスタ機能について,表8-1に示します。各レジスタの初期値,標準値は,当社の評価により決定したものであり,最適値とはかぎりません。また,当社の性能評価により,標準値を変更する場合があります。

表8-1 ライト・レジスタ機能一覧 (SA00)

| SA | ビット    | 名称,機能                  | 設定内容                                                                                                                                                  | 標準値  | 初期値  |

|----|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| 00 | D7, D6 | <b>GRMD</b><br>動作モード設定 | ゴースト低減動作の ON/OFF およびスルーの設定をします。<br>ON/OFF 時の制御方法は SWSEL( SA00h: D5 )により変わります。                                                                         | -    | 00   |

|    |        |                        | 00:ゴースト低減動作:ゴースト低減動作を行います。                                                                                                                            |      |      |

|    |        |                        | 01: ゴースト低減動作停止: ゴースト低減動作を停止します。OFF時の制御内容は SWSEL で決まりま                                                                                                 |      |      |

|    |        |                        | す。<br>1x:フィルタ・スルー:入力された信号は GR フィルタをバイパス<br>し最短の遅延でそのまま出力されます。                                                                                         |      |      |

|    | D5     | SWSEL<br>ON/OFF 制御動作設定 | GRMD によりゴースト低減動作を ON/OFF する場合の制御方法を<br>設定します。                                                                                                         | 0    | 0    |

|    |        |                        | 0:内部 CPU による ON/OFF 制御<br>ゴースト低減動作 OFF 時(GRMD = 01),選択したレファレン<br>ス波形がアパーチャ補正ありの場合(レジスタ RFS = 1xxx)は<br>出力にはアパーチャ補正のみがかかります。<br>1:GR フィルタによる ON/OFF 制御 |      |      |

|    |        |                        | ゴースト低減動作 OFF 時 ( GRMD = 01 ) , 出力にはいっさい補<br>正がかからず , スルーします。                                                                                          |      |      |

|    | D4     | CH<br>チャネル変更制御         | このビット・データの立ち上がりエッジで,チャネル変更制御を行います。EXCHN端子(61ピン)で制御する場合は,このビットは0固定としてください。 チャネル変更時は0 1 0としてください。0 1ヘデータを変更したときにチャネル変更が行われます。                           | -    | 0    |

|    | D3-D0  |                        | テスト・ビット                                                                                                                                               | 0000 | 0000 |

表8-1 ライト・レジスタ機能一覧 (SA01)

| SA | ビット | 名称,機能                         | 設定内容                                                                                           | 標準値            | 初期値 |

|----|-----|-------------------------------|------------------------------------------------------------------------------------------------|----------------|-----|

| 01 | D7  | EXDAS<br>ディジタル出力設定            | ディジタル出力端子 DO9-DO0(6-15 ピン)の状態を設定します。<br>この設定は EXDAS 端子(58 ピン)と同時設定ではじめて有効と<br>なります(AND 論理で制御)。 | 1              | 1   |

|    |     |                               | 0:ハイ・インピーダンス                                                                                   |                |     |

|    |     |                               | このとき DORDS ( SA00h: D6 ) によりプルダウン抵抗あり/な<br>しを設定できます。                                           |                |     |

|    |     |                               | 」 して収定してより。<br>1:EXDAS 端子が High のとき,ディジタル・データ出力                                                |                |     |

|    |     |                               | 10 ビットのディジタル・データ出力                                                                             |                |     |

|    | D6  | DORDS<br>ディジタル出力端子設定          | ディジタル出力端子 DO9-DO0 をハイ・インピーダンスに設定したとき(EXDAS = 0)プルダウン抵抗のあり / なしを設定します。                          | 0              | 0   |

|    |     |                               | 0: プルダウンなし<br>1:50 kΩでプルダウン                                                                    |                |     |

|    | D5  | N3D1STEN<br>3 次元処理禁止フラグ制<br>御 | 初回ゴースト低減動作開始時に3次元処理禁止制御信号をN3D端子(3ピン)より出力するかどうかを設定します。この機能は当社製3次元Y/C分離ICと組み合わせて使うときに有効です。       | 0 <sup>注</sup> | 0   |

|    |     |                               | 0:3次元処理禁止信号を出力しない<br>1:3次元処理禁止信号を出力する                                                          |                |     |

|    | D4  | <b>LELOW</b><br>PWM 出力マスク設定   | 直流誤差レベル出力端子(LE 端子:129 ピン)の出力状態を設定<br>します。                                                      | 1              | 1   |

|    |     |                               | 0:PWM 出力<br>1:Low 固定                                                                           |                |     |

|    | D3  | CLK8LOW<br>CLK8 出力マスク設定       | 8fsc クロック出力( CLK8 端子: 30 ピン )の出力状態を設定します。                                                      | 1              | 1   |

|    |     |                               | 0:8fsc クロック出力<br>1:Low 固定                                                                      |                |     |

|    | D2  | CLK20LOW<br>C20O 出力マスク設定      | 20 MHz クロック出力(C20O 端子:54 ピン)の出力状態を設定します。                                                       | 1 <sup>注</sup> | 0   |

|    |     |                               | 0 : 20 MHz クロック出力<br>1 : Low 固定                                                                |                |     |

|    | D1  | WP2OEN<br>WP2 端子出力設定          | 汎用 I <sup>2</sup> C ポート WP2 端子(110 ピン)の出力状態を設定します。                                             | 0              | 0   |

|    |     |                               | 0 : ハイ・インピーダンス<br>1 : PWM 出力                                                                   |                |     |

|    | D0  | WP3OEN<br>WP3 端子出力設定          | 汎用 I <sup>2</sup> C ポート WP3 端子(111 ピン)の出力状態を設定します。                                             | 0              | 0   |

|    |     |                               | 0 : ハイ・インピーダンス<br>1 : PWM 出力                                                                   |                |     |

|    |     |                               | · · · · · · · · · · · · · · · · · · ·                                                          |                |     |

注 当社製 3 次元 Y/C 分離 IC とのディジタル直結時は変更が必要です。

## 表8-1 ライト・レジスタ機能一覧 (SA02)

| SA | ビット   | 名称,機能                   | 設定内容                                                                                                                                                                                                                                                                                          | 標準値 | 初期値  |

|----|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| 02 | D7    |                         | テスト・ビット                                                                                                                                                                                                                                                                                       | 0   | 0    |

|    | D6    |                         | テスト・ビット                                                                                                                                                                                                                                                                                       | 1   | 1    |

|    | D5    |                         | テスト・ビット                                                                                                                                                                                                                                                                                       | 0   | 0    |

|    | D4    | PREGHSTS<br>前ゴースト処理範囲選択 | 前ゴーストに対する GR フィルタ適用範囲の選択を行います。適用<br>範囲を広く設定すると ,孫ゴーストが取りきれずに残る場合があり<br>ます。<br>0:-1μsまで                                                                                                                                                                                                        | 1   | 0    |

|    |       |                         | 1: - 2.6 μs まで PREGHSTS = 1 に設定すると,処理範囲は広がりますが,孫ゴーストが発生する場合があります。 この設定はデータ変更後,チャネル変更または CPU リセットを行ってはじめて有効となります。                                                                                                                                                                              |     |      |

|    | D3-D0 | RFS<br>レファレンス・データ選<br>択 | GCR 信号のレファレンス・データを選択します。8 種類の基本波形とそれぞれの D/A コンバータのアパーチャ補正あり / なしが選べます。チューナの特性などにあわせて選択してください。  D/A アパーチャ補正なし 0000:周波数特性低(リンギング小) ~0101:周波数特性高(リンギング大) 0110,0111:テスト設定  D/A アパーチャ補正あり 1000:周波数特性低(リンギング小) ~1101:周波数特性高(リンギング大) 1110,1111:テスト設定  この設定はデータ変更後,チャネル変更または CPU リセットを行ってはじめて有効となります。 | -   | 1000 |

# 表8-1 ライト・レジスタ機能一覧 (SA03)

| SA | ビット    | 名称,機能              | 設定内容                                                                                                                          | 標準値 | 初期値 |

|----|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 03 | D7, D6 | COR<br>コアリング・レベル設定 | GCR 信号取り込み時のコアリング・レベルを設定します。コアリングの設定を大きくすると ,ノイズによる疑似ゴースト発生を低減することができます。                                                      | 10  | 10  |

|    |        |                    | 00:コアリング小~11:コアリング大                                                                                                           |     |     |

|    |        |                    | この設定はデータ変更後,チャネル変更または CPU リセットを<br>行ってはじめて有効となります。                                                                            |     |     |

|    | D5-D3  | INTS<br>初回積分回数設定   | リセット後またはチャネル変更直後の初回ゴースト低減動作時,<br>GCR 信号取り込み積分回数を設定します。32 フィールド(8 フィールド・シーケンス×4)が1回の処理単位となります。                                 | 000 | 000 |

|    |        |                    | 000:1回       100:16回         001:2回       101:32回         010:4回       110:64回         011:8回       111:128回                  |     |     |

|    |        |                    | この設定はデータ変更後,チャネル変更または CPU リセットを<br>行ってはじめて有効となります。                                                                            |     |     |

|    | D2-D0  | INTE<br>最大積分回数設定   | ゴースト低減動作時の最終的な積分回数を設定します。リセット後またはチャネル変更から十分時間がたったあとは、ここで設定した積分回数ごとにフィルタ係数更新が行われるようになります。32フィールド(8フィールド・シーケンス×4)が1回の処理単位となります。 | 111 | 111 |

|    |        |                    | 000:2回       100:32回         001:4回       101:64回         010:8回       110:128回         011:16回       111:256回                |     |     |

|    |        |                    | この設定はデータ変更後,チャネル変更または CPU リセットを<br>行ってはじめて有効となります。                                                                            |     |     |

# 表8 - 1 ライト・レジスタ機能一覧 (SA04)

| SA                                     | ビット    | 名称,機能                             | 設定内容                                                                                                                    | 標準値 | 初期値 |

|----------------------------------------|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 04                                     | D7, D6 | ADCLKS<br>A/D コンバータ動作ク<br>ロック遅延設定 | μ PD64031A 内部のシステム・クロック(4fsc)に対する A/D コン<br>バータ動作クロックのタイミング(位相)を設定します。<br>00:0delay<br>01:1/4CLKdelay<br>10:1/2CLKdelay | 11  | 11  |

|                                        | D5, D4 | ADCPMD<br>クランプ・バイアス・モー<br>ド設定     | 内蔵 A/D コンバータのクランプおよびバイアスの切り替えを行います。  00:通常時はクランプ動作,ハンチング時はバイアス 01:常にクランプ動作 10:常にバイアス動作 11:クランプ,バイアスともに使用せず              | 01  | 01  |

| D3, D2 ADCPSEL<br>A/D コンバータ・クラン<br>プ設定 |        | A/D コンバータ・クラン                     | A/D コンバータ・クランプ・パルスの動作を設定します。 00:ハンチング時出力なし 01:常に出力あり 1x:テスト設定                                                           | 01  | 01  |

|                                        | D1     | FCLP<br>クランプ能力切り替え                | クランプの強さを設定します。<br>0:ソフト・クランプ<br>1:通常                                                                                    | 1   | 1   |

|                                        | D0     | FBIASEN<br>強制バイアス許可設定             | 入力信号が A/D コンバータの入力間口からはずれた場合などの対策として強制的バイアスをかけることができます。 0:無効 1:有効                                                       | 0   | 0   |

# 表8 - 1 ライト・レジスタ機能一覧 (SA05, SA06)

| SA | ビット    | 名称,機能                       | 設定内容                                                                                                                                                                        | 標準値    | 初期値    |

|----|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 05 | D7     | EXCSS<br>コンポジット同期分離回<br>路選択 | コンポジット同期分離回路について内蔵 / 外部を切り替えます。極性は EXCSP (SA05h: D6) で設定します。                                                                                                                | 1      | 1      |

|    |        | PHACIN                      | 0:内部ディジタル同期分離回路を使用<br>1:外部入力(EXCS 端子:126 ピンに入力)                                                                                                                             |        |        |

|    |        |                             | 注意 内部同期分離回路使用時には , SA04h: D5,D4 (ADCPMD)<br>は必ず " 01 " (常にクランプ動作 ) に設定してください。                                                                                               |        |        |

|    | D6     | EXCSP<br>コンポジット同期分離極<br>性選択 | 外部よりコンポジット同期分離入力する場合の極性を設定します。<br>0:アクティブ・ロウ<br>1:アクティブ・ハイ                                                                                                                  | -      | 0      |

|    | D5     | EXVSS<br>垂直同期分離回路選択         | 垂直同期分離回路について内蔵 / 外部を切り替えます。極性は<br>EXVSP(SA05h: D4)で設定します。                                                                                                                   | 1      | 1      |

|    |        |                             | 0:内部ディジタル同期分離回路を使用 1:外部入力(EXVS端子:128ピンに入力) 注意 内部同期分離回路使用時には,SA04h:D5,D4(ADCPMD)                                                                                             |        |        |

|    | D4     | EXVSP<br>垂直同期分離極性選択         | は必ず"01"(常にクランプ動作)に設定してください。<br>外部より垂直同期分離入力する場合の極性を設定します。                                                                                                                   | -      | 0      |

|    |        |                             | 0 : アクティブ・ロウ<br>1 : アクティブ・ハイ                                                                                                                                                |        |        |

|    | D3-D0  | EXCSDLY<br>外部同期分離遅延設定       | 外部同期分離回路(アナログ・ディジタル)の遅延量を設定します。                                                                                                                                             | 0011   | 0011   |

|    |        |                             | 0000 : 0delay<br>0001 : 1delay<br>1111 : 15delay                                                                                                                            |        |        |

| 06 | D7, D6 | <b>HNCS</b><br>強制ハンチング設定    | 強制的に同期はずれ(ハンチング)状態を設定します。強制ハンチングに設定すると,強制ハンチング端子(EXHNC端子:62ピン)による制御は無効となります。                                                                                                | 00     | 00     |

|    |        |                             | 00:通常(µPD64031A内部の検出結果に従います)<br>01:強制非ハンチング状態<br>10:強制ハンチング状態<br>11:テスト設定(設定禁止)                                                                                             |        |        |

|    | D5-D0  | HHNCR<br>水平ハンチング判定時定<br>数設定 | 水平同期はずれ検出の時定数を設定します。  上位 3 ピット: 上り側時定数 同期はずれ状態から同期検出するときの時定数 x00xxx: 5 ms x01xxx: 12 ms x10xxx: 24 ms x11xxx: 48 ms                                                         | 010100 | 010100 |

|    |        |                             | 下位 3 ピット: 下り側時定数<br>同期状態から同期はずれを検出するときの時定数<br>xxx000: 2.75 ms xxx100: 44 ms<br>xxx001: 5.5 ms xxx101: 88 ms<br>xxx010: 11 ms xxx110: 176 ms<br>xxx011: 22 ms xxx111: 440 ms |        |        |

# 表8 - 1 ライト・レジスタ機能一覧 (SA07)

| SA | ビット   | 名称,機能       | 設定内容                   | 標準値    | 初期値    |

|----|-------|-------------|------------------------|--------|--------|

| 07 | D7    |             | テスト・ビット                | 0      | 0      |

|    |       |             |                        |        |        |

|    | D6    |             | テスト・ビット                | 0      | 0      |

|    |       |             |                        |        |        |

|    | D5-D0 | VHNCR       | 垂直同期はずれ検出の時定数を設定します。   | 001011 | 001011 |

|    |       | 垂直ハンチング判定時定 |                        |        |        |

|    |       | 数設定         | 上位 3 ビット:上り側時定数        |        |        |

|    |       |             | 同期はずれ状態から同期検出するときの時定数  |        |        |

|    |       |             | x00xxx: 66 ms          |        |        |

|    |       |             | x01xxx: 100 ms         |        |        |

|    |       |             | x10xxx : 133 ms        |        |        |

|    |       |             | x11xxx : 166 ms        |        |        |

|    |       |             |                        |        |        |

|    |       |             | 下位 3 ビット:下り側時定数        |        |        |

|    |       |             | 同期状態から同期はずれを検出するときの時定数 |        |        |

|    |       |             | xxx000 : 135 ms        |        |        |

|    |       |             | xxx001 : 200 ms        |        |        |

|    |       |             | xxx010 : 270 ms        |        |        |

|    |       |             | xxx011 : 400 ms        |        |        |

表8-1 ライト・レジスタ機能一覧 (SA08)

| SA | ビット    | 名称,機能                                  | 設定内容                                                                                                                                                                                           | 標準値             | 初期値 |

|----|--------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| 08 | D7, D6 | DIR3DYC<br>3 次元 Y/C 分離ディジタ<br>ル直結モード設定 | 当社製3次元Y/C分離ICとディジタル直結で用いる場合の動作設定を行います。                                                                                                                                                         | 00 <sup>注</sup> | 00  |

|    |        |                                        | 0x: $\mu$ PD64031A のみ動作                                                                                                                                                                        |                 |     |

|    |        |                                        | このとき,ディジタル・クランプ機能はオフします。                                                                                                                                                                       |                 |     |

|    |        |                                        | 10:当社製 3 次元 Y/C 分離 IC ディジタル直結(チューナ入力) WP1 端子(35 ピン)に Low が出力されます。チューナ入力などのコンポジット・ビデオ信号に対し,μPD64031A でゴースト低減を行ったあと,後段に接続された当社製 IC で 3 次元 Y/C 分離を行うためのコントロール信号として使用します。                          |                 |     |

|    |        |                                        | 11:当社製 3 次元 Y/C 分離 IC ディジタル直結(S 入力など)                                                                                                                                                          |                 |     |

|    |        |                                        | WP1 端子に High が出力されます。S 入力などの信号に対し,μPD64031A によるゴースト低減は行わず,3 次元 Y/C 分離 IC による Y/C 分離やノイズ低減のみ行う場合のコントロール信号として使用します。                                                                              |                 |     |

|    | D5-D3  | DCPAG<br>ディジタル・クランプ・<br>アンプ・ゲイン設定      | ゴースト低減後の信号に対し、ディジタル・クランプをかけると同時に、出力振幅の拡大を行うアンプ・ゲインを設定します。出力されるディジタル・ビデオ信号のペデスタル・レベルをシフトしたのち、コンポジット・ビデオ信号の振幅を拡大します。<br>この設定は DIR3DYC (SA08h: D7, D6) = 1x および DCPEN (SA09h: D6) = 1 のとき有効となります。 | 101             | 111 |

|    |        |                                        | 000:ペデスタル・シフト + 1.0 倍 001:ペデスタル・シフト + 1.125 倍 010:ペデスタル・シフト + 1.250 倍 011:ペデスタル・シフト + 1.375 倍 100:ペデスタル・シフト + 1.500 倍 101:ペデスタル・シフト + 1.625 倍 110:ペデスタル・シフト + 1.750 倍 (同期信号が欠ける場合があります)        |                 |     |

|    | D2-D0  | DCPLG<br>ディジタル・クランプ・<br>ループ・ゲイン設定      | 出力部のディジタル・クランプのループ・ゲインを設定します。<br>000:クランプ速い~111:クランプ遅い                                                                                                                                         | 111             | 101 |

注 当社製 3 次元 Y/C 分離 IC とのディジタル直結時には変更が必要です。

表8 - 1 ライト・レジスタ機能一覧 (SA09-SA0C)

| SA | ビット   | 名称,機能                                | 設定内容                                                                                         | 標準値            | 初期値  |

|----|-------|--------------------------------------|----------------------------------------------------------------------------------------------|----------------|------|

| 09 | D7    |                                      |                                                                                              | 0              | 0    |

|    | D6    | DCPEN<br>ディジタル・クランプ選<br>択            | ディジタル・クランプの有効 / 無効を選択します。 0:ディジタル・クランプ無効 1:ディジタル・クランプ有効                                      | 0 <sup>注</sup> | 0    |

|    | D5    | DCPLPFS<br>誤差演算部 LPF 選択              | ディジタル・クランプ部においてペデスタル位置の誤差演算時に<br>LPF 処理を行うかどうか選択します。<br>0:LPF なし<br>1:LPF あり                 | 1              | 1    |

|    | D4    | DCPVEN<br>クランプ・タイミング選<br>択           | ディジタル・クランプを行うタイミングを設定します。<br>0:ラインごと<br>1:垂直同期期間                                             | 1              | 0    |

|    | D3-D0 |                                      | テスト・ビット                                                                                      | 1111           | 0000 |

| 0A | D7-D0 | <b>WP2O</b><br>WP2ポートPWMデータ<br>出力    | 汎用 I <sup>2</sup> C ポート WP2 端子に出力するデータを設定します。<br>ここで設定した 8 ビットのデータが WP2 端子より PWM 出力され<br>ます。 | 00h            | 00h  |

| 0B | D7-D0 | <b>WP3O</b><br>WP3 ポート PWM デー<br>夕出力 | 汎用 I <sup>2</sup> C ポート WP3 端子に出力するデータを設定します。<br>ここで設定した 8 ビットのデータが WP3 端子より PWM 出力され<br>ます。 | 00h            | 00h  |

| 0C | D7    |                                      | テスト・ビット                                                                                      | 0              | 0    |

|    | D6    | PLLFS<br>PLL フィルタ特性切り替<br>え          | PLL フィルタ特性切り替えを設定します。 0: 収束速い 1: 収束遅い                                                        | 0              | 0    |

|    | D5    | PLLSP<br>PLL 誤差検出サンプリン<br>グ量         | PLL 誤差検出サンプリング量を設定します。<br>0:4 サンプリング<br>1:9 サンプリング                                           | 0              | 0    |

|    | D4    | PLLFG<br>PLL 位相誤差ゲイン調整               | PLL 位相誤差ゲインを調整します。 0: ×1 1: ×2                                                               | 1              | 1    |

|    | D3-D0 |                                      | テスト・ビット                                                                                      | 1101           | 1101 |

注 当社製 3 次元 Y/C 分離 IC とのディジタル直結時には変更が必要です。

# 表8 - 1 ライト・レジスタ機能一覧 (SA0D-SA10)

| SA | ビット    | 名称,機能                             | 設定内容                                                                                                                | 標準値    | 初期値    |

|----|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|--------|

| 0D | D7-D0  |                                   | テスト・ビット                                                                                                             | 5Eh    | 5Eh    |

| 0E | D7     | KILM<br>キラー検出モード設定                | キラー検出の動作を設定します。 0:バースト振幅検出 1:バースト振幅検出 + 引き込み検出                                                                      | 0      | 0      |

|    | D6     | UNLOCKS<br>クロックはずれ時処理設<br>定       | クロック・ジェネレータにおいてクロックはずれを検出したときに,3次元処理禁止フラグ端子(N3D端子)から3次元処理禁止フラグを出力するかどうかを設定します。 0:3次元処理禁止フラグを出力しない 1:3次元処理禁止フラグを出力する | 0      | 0      |

|    | D5, D4 | KILS<br>キラー出力制御                   | キラー出力端子(KIL 端子:2 ピン)の出力状態を設定します。  0x:キラー判定結果を出力  10:強制 Low 固定  11:強制 High 固定                                        | 00     | 00     |

|    | D3-D0  | KILR<br>キラー検出レベル設定                | キラー検出の感度を設定します。<br>0001:検出感度小~1111:検出感度大<br>0000:検出 OFF                                                             | 0000   | 1010   |

| 0F | D7-D4  | <b>HSSR</b><br>水平同期スライス・レベ<br>ル設定 | 水平同期検出の水平同期信号に対するスライス・レベルを設定します。<br>11111:深い~0000:中点~0111:浅い                                                        | 1101   | 1101   |

|    | D3, D2 | VSSR<br>垂直同期スライス・レベ<br>ル設定        | 垂直同期検出のスライス・レベルを設定します。水平同期スライス・レベルに対する相対位置で設定します。  00: +1/16 01: +1/8 1x: +1/4                                      | 00     | 00     |

|    | D1     |                                   | テスト・ビット                                                                                                             | 0      | 0      |

|    | D0     |                                   |                                                                                                                     | 0      | 0      |

| 10 | D7     |                                   | テスト・ビット                                                                                                             | 0      | 0      |

|    | D6     |                                   | テスト・ビット                                                                                                             | 0      | 0      |

|    | D5-D0  |                                   |                                                                                                                     | 000000 | 000000 |

# 表8 - 1 ライト・レジスタ機能一覧 (SA11-SA17)

| SA | ビット    | 名称,機能 | 設定内容    | 標準値   | 初期値   |

|----|--------|-------|---------|-------|-------|

| 11 | D7     |       | テスト・ビット | 0     | 0     |

|    | D6     |       | テスト・ビット | 0     | 0     |

|    | D5     |       | テスト・ビット | 0     | 0     |

|    | D4-D0  |       |         | 00000 | 00000 |

| 12 | D7     |       | テスト・ビット | 0     | 0     |

|    | D6     |       | テスト・ビット | 0     | 0     |

|    | D5-D3  |       | テスト・ビット | 000   | 000   |

|    | D2-D0  |       |         | 000   | 000   |

| 13 | D7, D6 |       | テスト・ビット | 00    | 00    |