# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

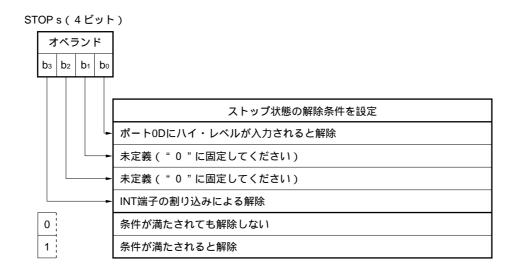

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

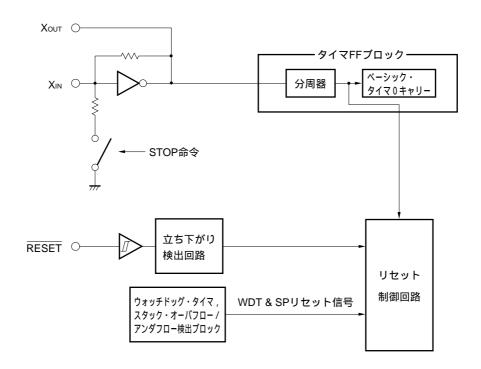

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

MOS**集積回路** MOS Integrated Circuit

# μPD17934A

# ディジタル・チューニング・システム用専用ハードウエア内蔵 4 ピット・シングルチップ・マイクロコントローラ

- ★ µPD17934Aは,ディジタル・チューニング・システム用ハードウエアを内蔵した4ビット・シングルチップCMOSマイクロコントローラです。

- μ PD17934Aは、電源電圧0.9 Vの超低電圧で230 MHzまで動作するプリスケーラ、PLL周波数シンセサイザ、中間周波数 (IF) カウンタおよびLCDコントローラ / ドライバを 1 チップに納めたディジタル・チューニング・システム (DTS) 用低電圧 4 ビットCMOSマイクロコントローラです。

したがって,1チップで高性能なポータブル・セット用ディジタル・チューニング・システムを構成することができます。

#### 特徵

★ プログラム・メモリ(ROM)

16 Kバイト (8192×16ビット)

汎用データ・メモリ (RAM)

448×4ビット

命令実行時間

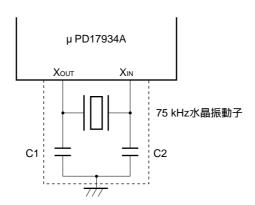

53.3 μ sec (75 kHz水晶振動子使用)

PLL周波数シンセサイザ内蔵

デュアル・モジュラス・プリスケーラ(230 MHz MAX.),

プログラマブル・ディバイダ,位相比較器,チャー

ジ・ポンプ

周辺ハードウエア

汎用入出力ポート,LCDコントローラ/ドライバ,

シリアル・インタフェース, A/Dコンバータ,

BEEP出力, 周波数カウンタ

割り込み

外部:1本

内部:3本

RESET端子によるリセット

低消費電力

電源電圧: VDD = 0.9~1.8 V

#### ★ オーダ情報

オーダ名称

パッケージ

μ PD17934AGK- × × × -BE9

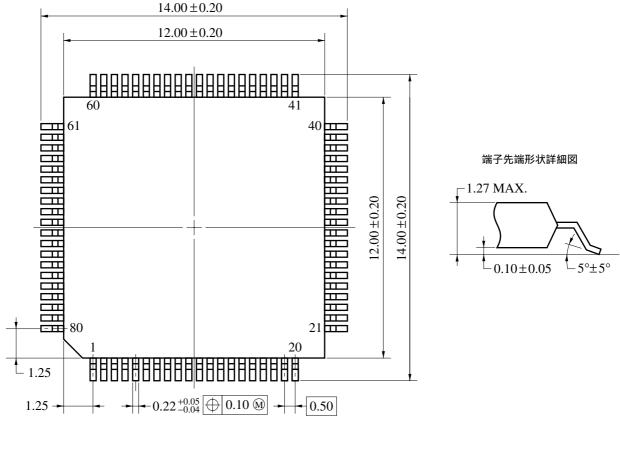

80ピン・プラスチックTQFP (ファインピッチ) (12x12)

備考 ×××はROMコード番号です。

本資料の内容は、予告なく変更することがありますので、最新のものであることをご確認の上ご使用ください。

# 機能概要

| 項        | 目         | 機能                                                        |  |  |  |  |  |

|----------|-----------|-----------------------------------------------------------|--|--|--|--|--|

| プログラム・メ  | ベモリ(ROM)  | 16 Kバイト (8192×16ビット)                                      |  |  |  |  |  |

| 汎用データ・メ  | Kモリ(RAM)  | 448×4ビット                                                  |  |  |  |  |  |

| 命令実行時間   |           | 53.3 µ s(75 kHz水晶振動子使用)                                   |  |  |  |  |  |

| 汎用ポート    |           | ・入出力ポート:20本                                               |  |  |  |  |  |

|          |           | 37本<br>・入力ポート : 11本(内 3 本はLCDセグメント端子と兼用)                  |  |  |  |  |  |

|          |           | ・出力ポート : 6本                                               |  |  |  |  |  |

| スタック・レベ  | ベル        | ・アドレス・スタック : 15レベル(スタック操作可)                               |  |  |  |  |  |

|          |           | ・割り込みスタック : 4 レベル ( スタック操作可 )                             |  |  |  |  |  |

| ベクタ割り込み  | <i></i>   | ・外部:1本(INT)                                               |  |  |  |  |  |

| (マスカブル害  | 刊り込み)     | ・内部:3本(ベーシック・タイマ0,8ビット・タイマ,シリアル・インタフェース)                  |  |  |  |  |  |

| タイマ      |           | 3チャネル                                                     |  |  |  |  |  |

|          |           | ・ベーシック・タイマ 0 (125 ms)                                     |  |  |  |  |  |

|          |           | ・ベーシック・タイマ 1 (8 ms, 32 ms)                                |  |  |  |  |  |

|          |           | ・8 ビット・タイマ(イベント・カウンタ付き)                                   |  |  |  |  |  |

| A/Dコンバータ |           | 8 ビット分解能×3チャネル                                            |  |  |  |  |  |

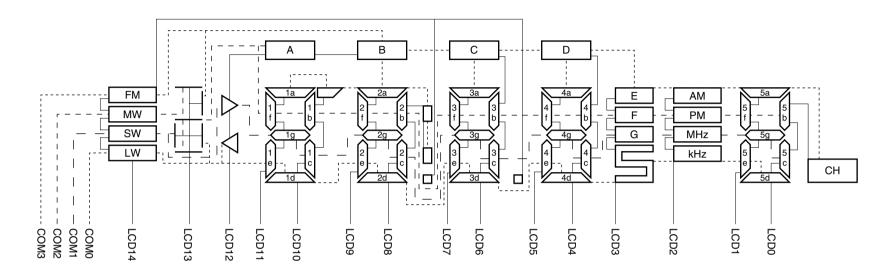

| LCDコントロ- | -ラ / ドライバ | ・20セグメント , 4 コモン                                          |  |  |  |  |  |

|          |           | ・1/4デューティ,1/2バイアス,フレーム周波数 62.5 Hz,駆動電圧 VLCD1 = 3.0 V TYP. |  |  |  |  |  |

|          |           | ・兼用セグメント端子:3本(1本ごとに汎用入力ポートとして使用可能)                        |  |  |  |  |  |

| シリアル・イン  | /タフェース    | 1 チャネル (3 線式 / 2 線式モード選択可能)                               |  |  |  |  |  |

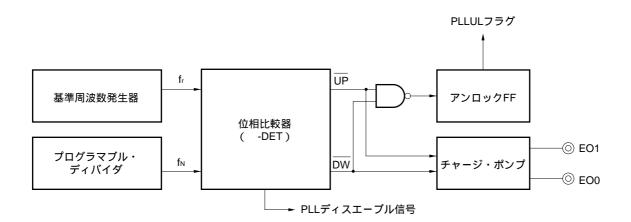

| PLL周波数   | 分周方式      | ・直線分周方式 (VCOL端子)                                          |  |  |  |  |  |

| シンセサイザ   |           | 2 種類                                                      |  |  |  |  |  |

|          | 基準周波数     | 6 種類選択可能(1, 3, 5, 6.25, 12.5, 25 kHz)                     |  |  |  |  |  |

|          | チャージ・ポンプ  | エラー・アウト出力: 2 本 ( EO0, EO1端子 )                             |  |  |  |  |  |

|          | 位相比較器     | プログラムによりアンロック検出可能                                         |  |  |  |  |  |

| 中間周波数(IF | ・) カウンタ   | 周波数測定 J ・AMIFC端子 400 kHz~2 MHz                            |  |  |  |  |  |

|          |           | ・FMIFC端子 10~11 MHz                                        |  |  |  |  |  |

|          |           | 外部ゲート幅測定(FCG端子)                                           |  |  |  |  |  |

| BEEP出力   |           | 1 本(1.5 kHz, 3 kHz)                                       |  |  |  |  |  |

| リセット     |           | ・RESET端子によるリセット                                           |  |  |  |  |  |

|          |           | ・ウォッチドッグ・タイマ・リセット                                         |  |  |  |  |  |

|          |           | 電源投入時1回のみ設定可能:4096命令,8192命令,未使用を選択                        |  |  |  |  |  |

|          |           | ・スタック・ポインタ・オーバフロー / アンダフロー・リセット                           |  |  |  |  |  |

|          |           | 電源投入時1回のみ設定可能:割り込みスタック,アドレス・スタックを選択                       |  |  |  |  |  |

| 電源電圧     |           | V <sub>DD</sub> = 0.9 ~ 1.8 V                             |  |  |  |  |  |

| パッケージ    |           | 80ピン・プラスチックTQFP(ファインピッチ)(12x12)                           |  |  |  |  |  |

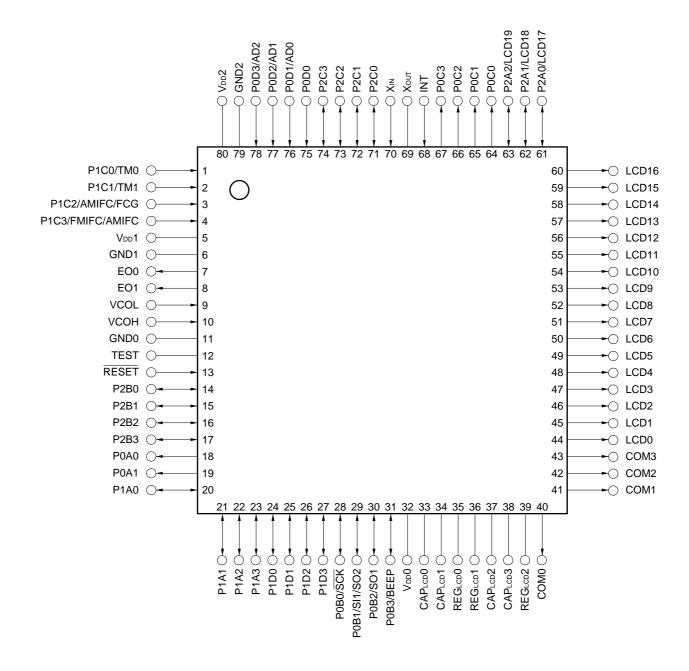

#### 端子接続図 (Top View)

#### ★ 80ピン・プラスチックTQFP (ファインピッチ) (12x12)

$\mu$  PD17934AGK-  $\times$   $\times$  -BE9

#### 端子名称

P1A0-P1A3

: ポート1A

AD0-AD2

: A/Dコンバータ入力

P1C0-P1C3

: ポート1C

AMIFC

: AM中間周波数カウンタ入力

P1D0-P1D3

: ポート1D

BEEP : BEEP出力 P2A0-P2A2 : ポート2A

CAPLCD0-CAPLCD3: LCD駆動電圧用コンデンサ接続P2B0-P2B3: ポート2BCOM0-COM3: LCDコモン出力P2C0-P2C3: ポート2C

EO0, EO1 : エラー・アウト出力 REGLCD0-REGLCD2: LCD駆動用レギュレータ出力

FCG : 外部ゲート・カウンタ入力 RESET : リセット入力

FMIFC : FM中間周波数カウンタ入力 SCK : 3 線式シリアル・クロック入出力

GND0-GND2

: グランド

SI1

: 3線式シリアル・データ入力

INT

: 外部割り込み入力

SO1, SO2

: 3 線式シリアル・データ出力

LCD0-LCD19 : LCDセグメント出力 TEST : テスト用入力

P0A0, P0A1

: ポート0A

TM0, TM1

: タイマ・イベント入力

P0B0-P0B3

: ポート0B

VCOH, VCOL

: PLL用局部発振入力

POC0-POC3 : ポートOC V<sub>DD</sub>0-V<sub>DD</sub>2 : 電源

P0D0-P0D3 : ポート0D XIN, Xout : 水晶振動子接続

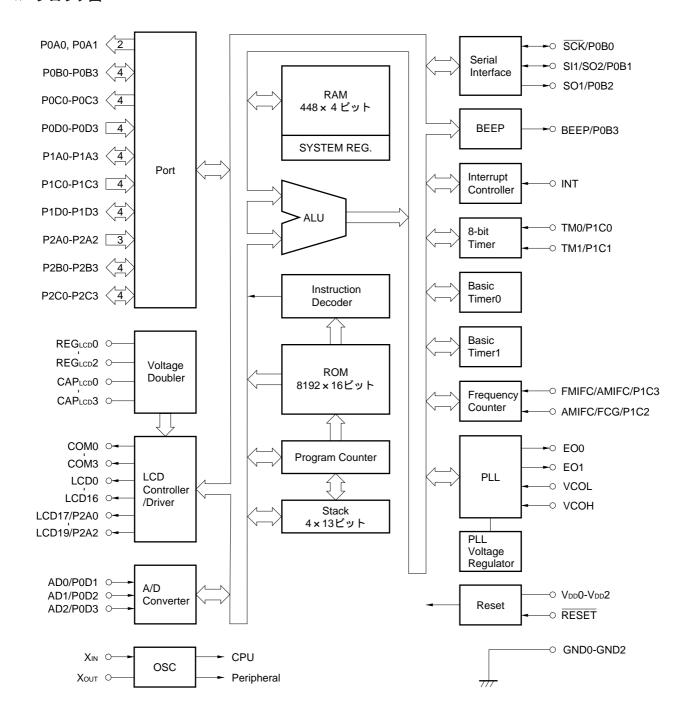

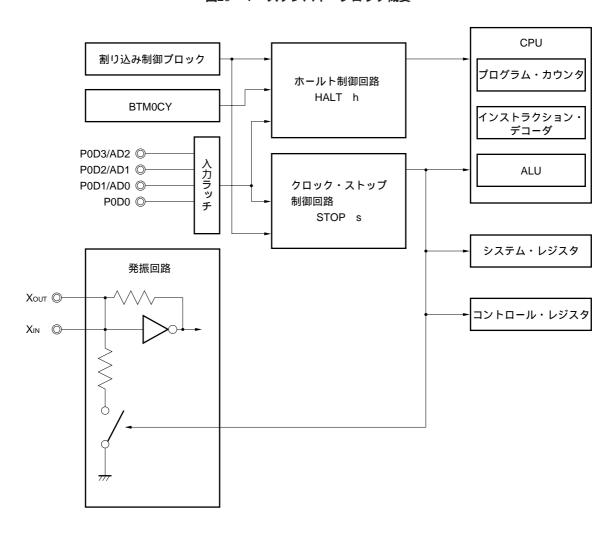

#### ★ プロック図

# 目 次

| 1.端 | 子機       | <b>能</b> 11                                      |

|-----|----------|--------------------------------------------------|

| 1   | . 1      | 端子機能一覧 11                                        |

| 1   | . 2      | 端子の等価回路 14                                       |

| 1   | . 3      | 未使用端子の処理 18                                      |

| 1   | . 4      | TEST端子の使用上の注意 19                                 |

| 2.ブ | ゚゚ログ     | プム・メモリ (ROM) 20                                  |

| 2   | . 1      | プログラム・メモリ概要 20                                   |

| 2   | . 2      | プログラム・メモリ 21                                     |

| 2   | . 3      | プログラム・カウンタ 22                                    |

| 2   | . 4      | プログラムの流れ 22                                      |

| 2   | . 5      | プログラム・メモリ使用時の注意 25                               |

| 3.ア | 'ドレ      | ·ス・スタック (ASK) 26                                 |

| 3   | . 1      | アドレス・スタック概要 26                                   |

| 3   | . 2      | アドレス・スタック・レジスタ(ASR) 26                           |

| 3   | . 3      | スタック・ポインタ (SP) 28                                |

| 3   | . 4      | アドレス・スタックの動作 29                                  |

| 3   | . 5      | アドレス・スタック使用時の注意 30                               |

| 4.デ | ータ       | ・メモリ (RAM) 31                                    |

| 4   | . 1      | データ・メモリ概要 31                                     |

| 4   | . 2      | データ・メモリの構成と機能 33                                 |

| 4   | . 3      | データ・メモリのアドレシング 35                                |

| 4   | . 4      | データ・メモリ使用時の注意 36                                 |

| 5.シ | ゚ステ      | ム・レジスタ (SYSREG) 37                               |

| 5   | . 1      | システム・レジスタ概要 37                                   |

| 5   | . 2      | システム・レジスター覧 38                                   |

| 5   | . 3      | アドレス・レジスタ(AR) 39                                 |

| 5   | . 4      | ウインドウ・レジスタ(WR) 41                                |

| 5   | . 5      | バンク・レジスタ (BANK) 42                               |

| 5   | . 6      | インデクス・レジスタ(IX)とデータ・メモリ・ロウ・アドレス・ポインタ(MP:メモリ・ポインタ) |

|     |          | 43                                               |

| 5   | . 7      | ジェネラル・レジスタ・ポインタ(RP) 45                           |

| 5   | . 8      | プログラム・ステータス・ワード(PSWORD) 47                       |

| 6.ジ | ゙゙゙゙゙゙ェネ | ラル・レジスタ (GR) 49                                  |

|     |          | ジェネラル・レジスタ概要 49                                  |

|     |          | ジェネラル・レジスタ 49                                    |

| 6   | 3        | 各命今におけるジェネラル・レジスタのアドレス生成 50                      |

#### 50

| 6.4       | ジェネラル・レジスタ使用時の注意                |

|-----------|---------------------------------|

|           |                                 |

| 7 . ALU ( | Arithmetic Logic Unit ) プロック 51 |

| 7.1       | ALUブロック概要 51                    |

| 7.2       | 各ブロックの構成と機能 52                  |

| 7.3       | ALU処理命令一覧 52                    |

| 7.4       | ALU使用時の注意 56                    |

|           |                                 |

| 8.レジス     | タ・ファイル (RF) とコントロール・レシ          |

| 8.1       | レジスタ・ファイル概要 57                  |

| 0 2       | しぶフタ・ファイルの構成と機能 50              |

# ·ジスタ ... 57

- 8.2 レジスタ・ファイルの構成と機能 ... 58

- 8.3 コントロール・レジスタと入力/出力選択レジスタ ... 59

- 8.4 LCDセグメント・レジスタ ... 69

- 8.5 コントロール・レジスタ使用時の注意 ... 69

#### 9. データ・バッファ (DBF) ... 70

- 9.1 データ・バッファ概要 ... 70

- 9.2 データ・バッファ ... 71

- 9.3 周辺ハードウエアとデータ・バッファー覧 ... 72

- 9.4 データ・バッファ使用時の注意 ... 74

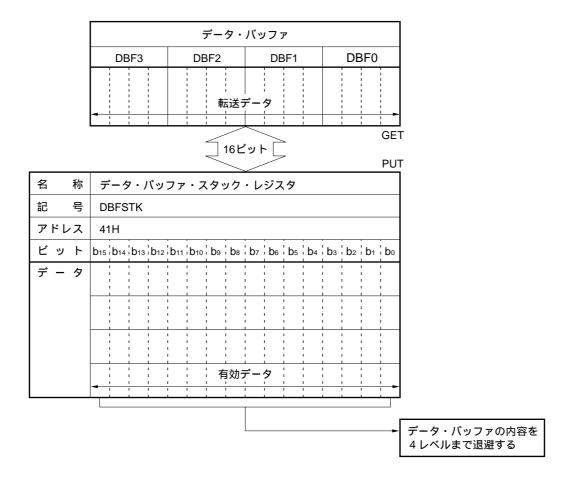

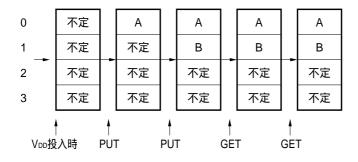

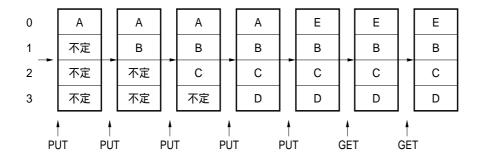

#### 10. データ・バッファ・スタック ... 75

- 10.1 データ・バッファ・スタック概要 ... 75

- 10.2 データ・バッファ・スタック・レジスタ ... 75

- 10.3 データ・バッファ・スタック・ポインタ ... 77

- 10.4 データ・バッファ・スタックの動作 ... 78

- 10.5 データ・バッファ・スタックの使用方法 ... 79

- 10.6 データ・バッファ・スタック使用時の注意 ... 79

#### 11.汎用ポート ... 80

- 11.1 汎用ポート概要 ... 80

- 11.2 汎用入出力ポート (P0B, P1A, P1D, P2B, P2C) ... 82

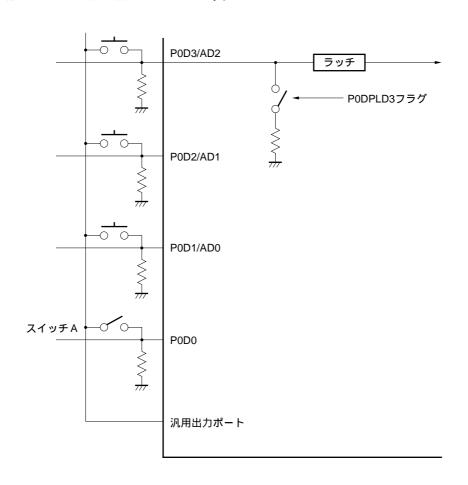

- 11.3 汎用入力ポート (POD, P1C, P2A) ... 91

- 11.4 汎用出力ポート(POA, POC) ... 94

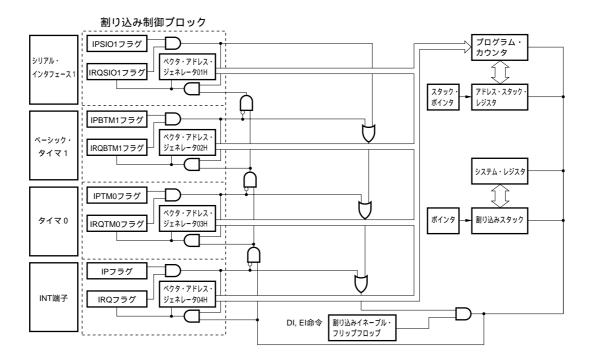

#### 12.割り込み ... 96

- 12.1 割り込みブロック概要 ... 96

- 12.2 割り込み制御ブロック ... 98

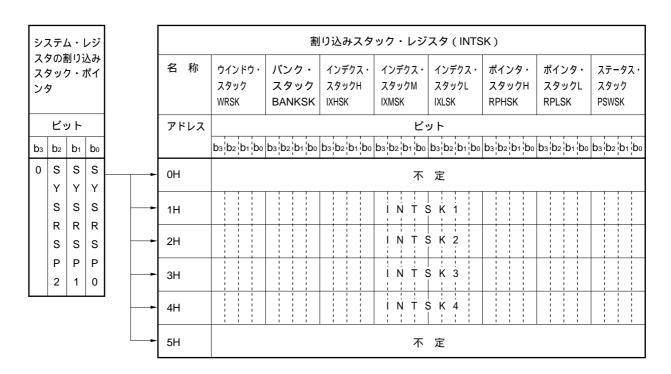

- 12.3 割り込みスタック・レジスタ ... 104

- 12.4 スタック・ポインタ,アドレス・スタック・レジスタとプログラム・カウンタ ... 108

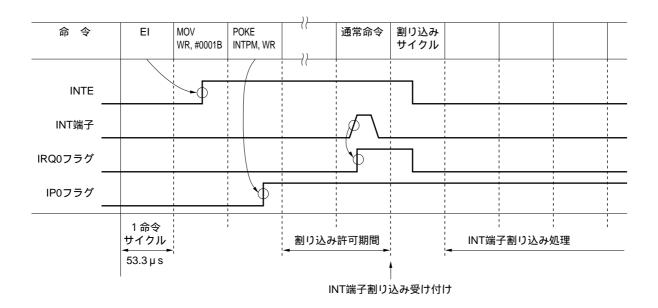

- 12.5 割り込みイネーブル・フリップフロップ (INTE) ... 108

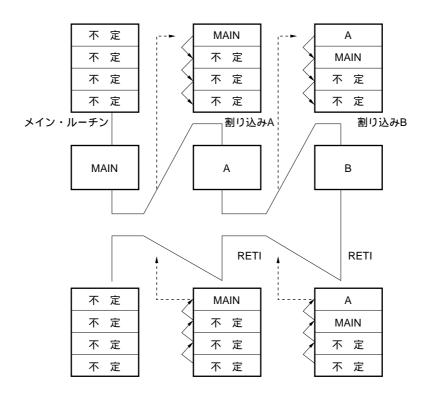

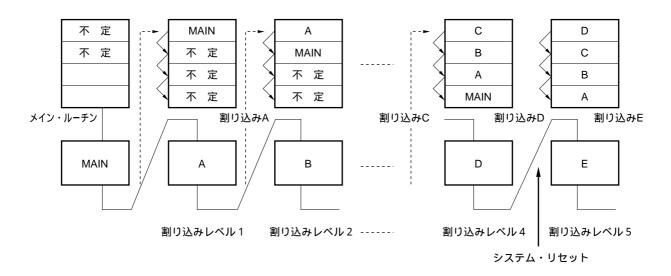

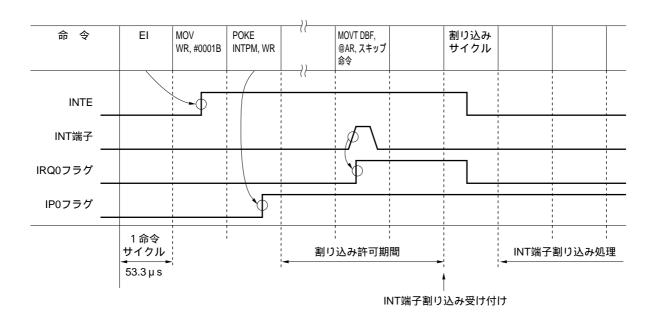

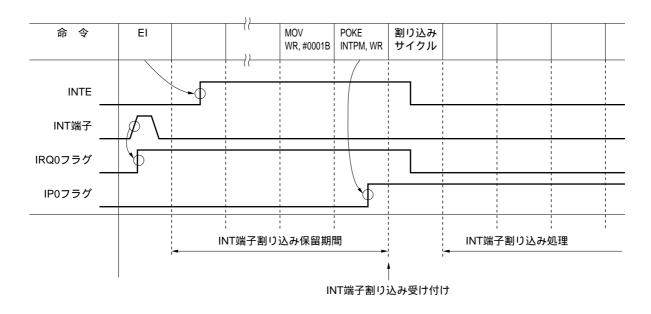

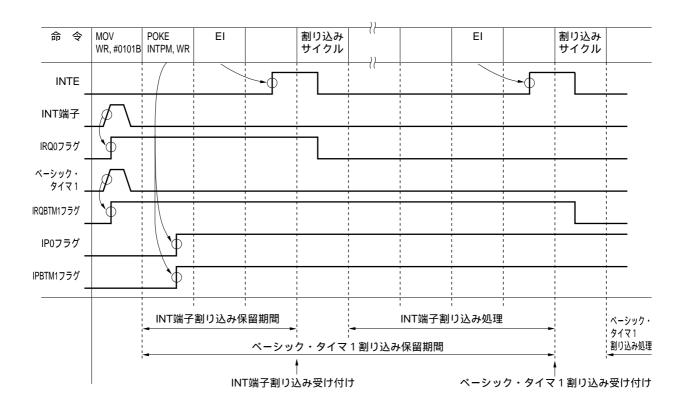

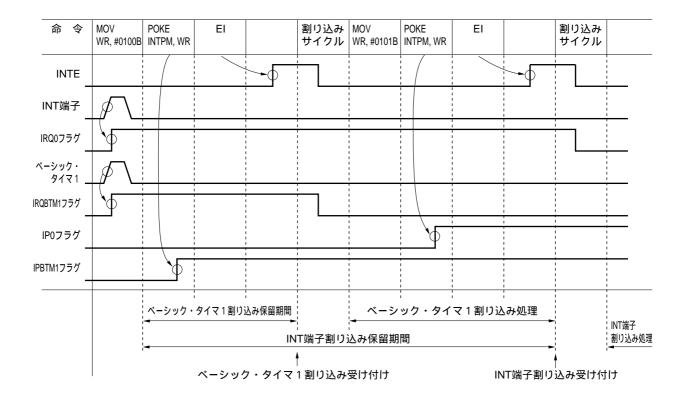

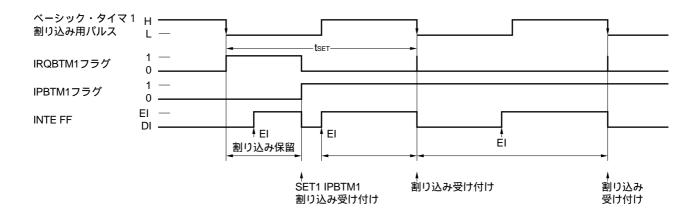

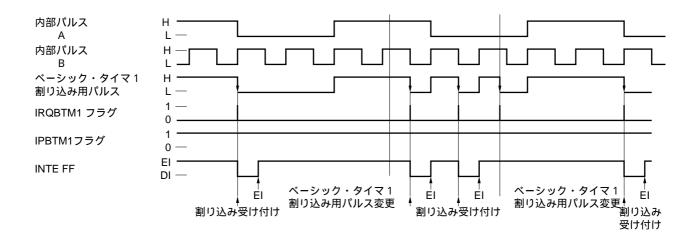

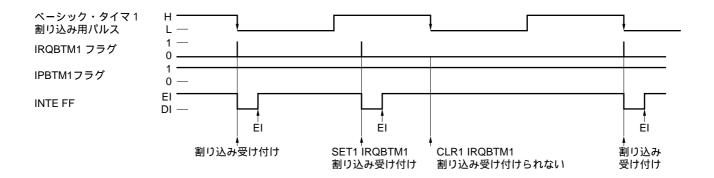

- 12.6 割り込み受け付け動作 ... 109

- 12.7 割り込み受け付け後の動作 ... 114

|      | 12.10  | 内部割り込み 117                                    |

|------|--------|-----------------------------------------------|

| 13 . | タイ     | マ 118                                         |

|      |        | タイマ概要 118                                     |

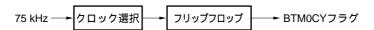

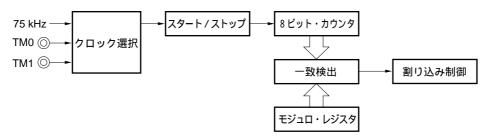

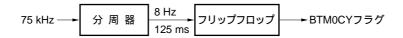

|      |        | ベーシック・タイマ 0 119                               |

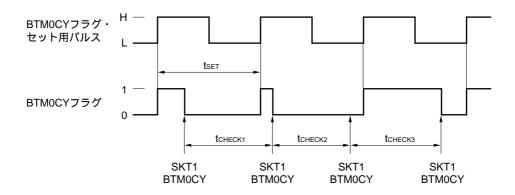

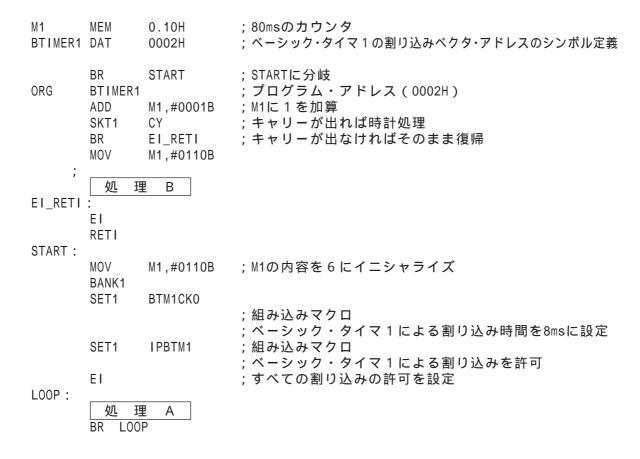

|      |        | ベーシック・タイマ 1 123                               |

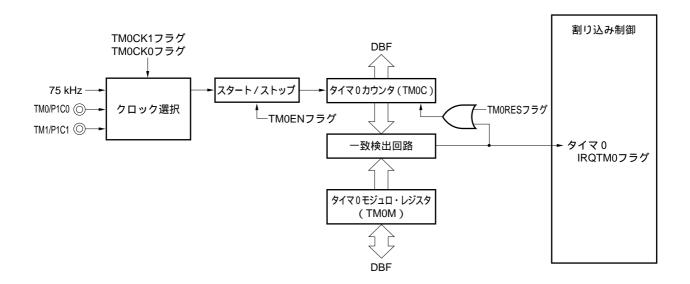

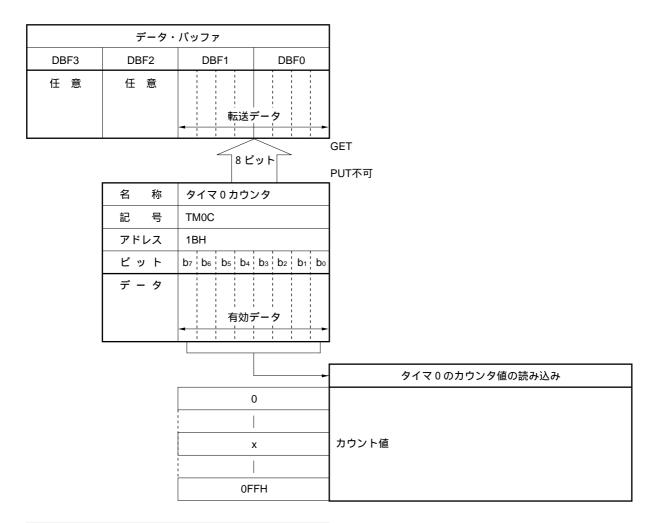

|      |        | タイマ 0 129                                     |

|      | . /5 = | Aville de 100                                 |

| 14   |        | ンパータ 136                                      |

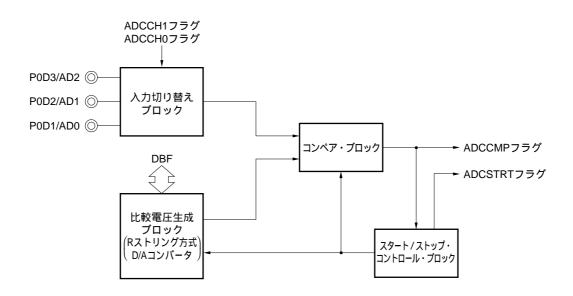

|      |        | A/Dコンバータ概要 136                                |

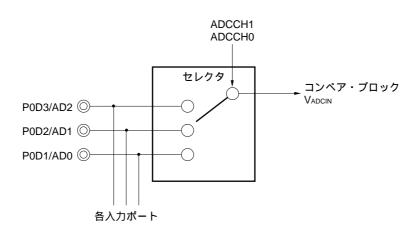

|      |        | 入力切り替えブロック 137                                |

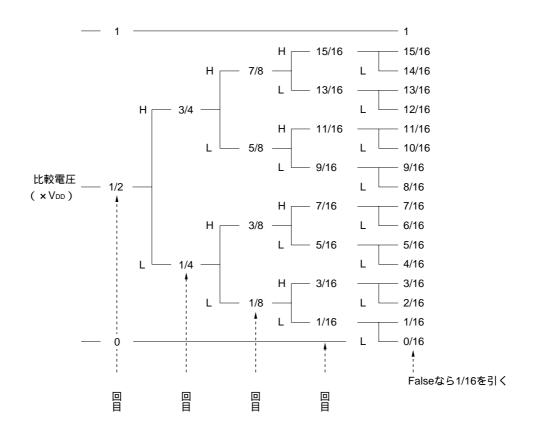

|      |        | 比較電圧生成およびコンペア・ブロック 139                        |

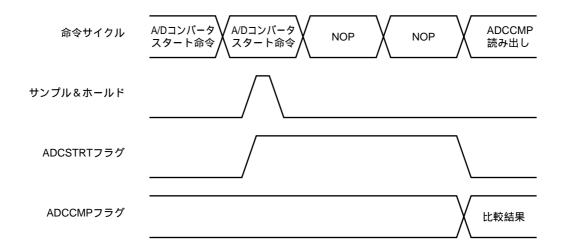

|      |        | 比較タイミング・チャート 141                              |

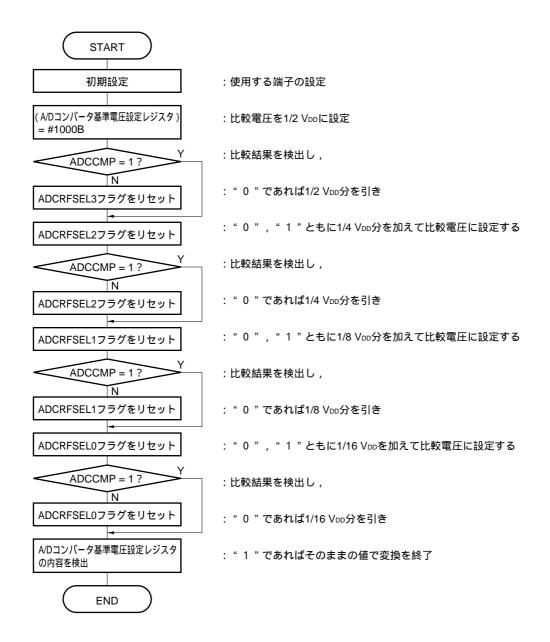

|      | 14. 5  | A/Dコンバータの使用方法 142                             |

|      | 14. 6  | A/Dコンバータ使用時の注意 146                            |

|      | 14. 7  | リセット時の状態 146                                  |

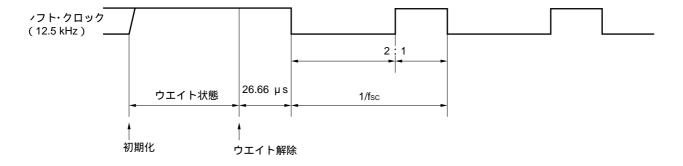

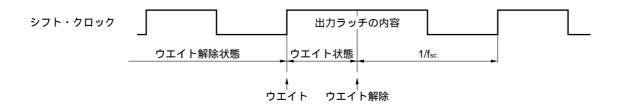

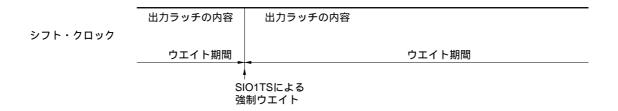

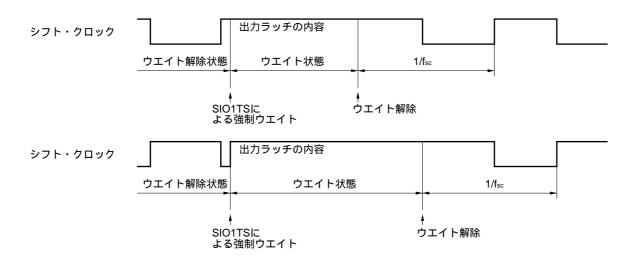

| 15 . | . シリア  | プル・インタフェース 147                                |

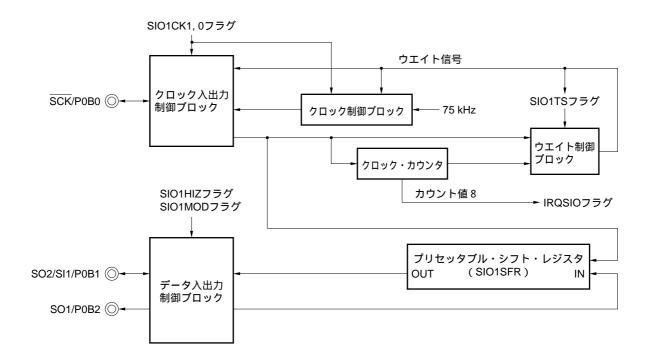

|      | 15. 1  | シリアル・インタフェース概要 147                            |

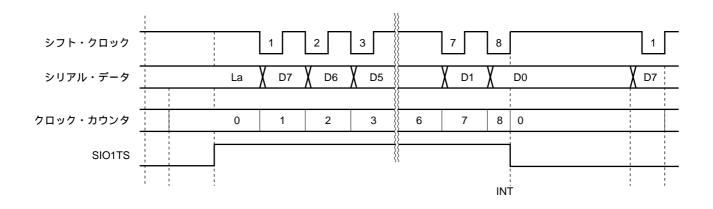

|      | 15. 2  | クロック入出力制御ブロックおよびデータ入出力制御ブロック 148              |

|      | 15.3   | クロック制御ブロック 151                                |

|      | 15.4   | クロック・カウンタ 151                                 |

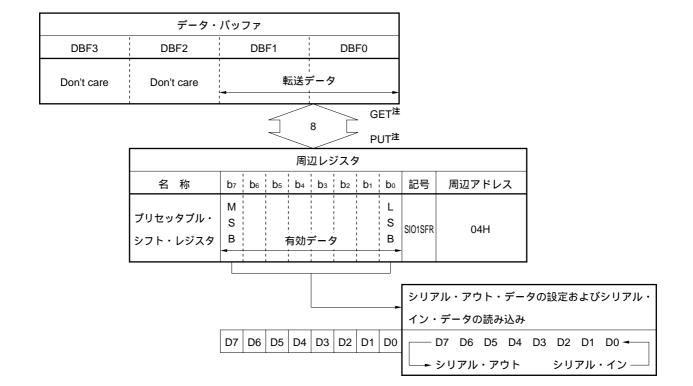

|      | 15. 5  | プリセッタブル・シフト・レジスタ 152                          |

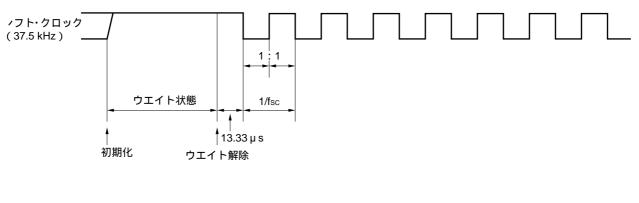

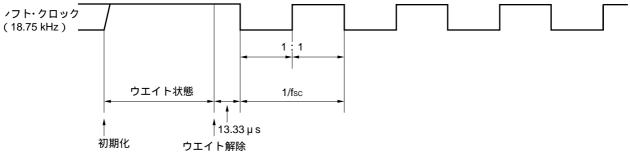

|      | 15. 6  | ウエイト制御ブロック 152                                |

|      | 15. 7  | シリアル・インタフェースの動作 153                           |

|      | 15.8   | データ設定時およびデータ読み込み時の注意 157                      |

|      | 15. 9  | 動作モードと各部の動作概要 158                             |

|      | 15.10  | リセット時の状態 160                                  |

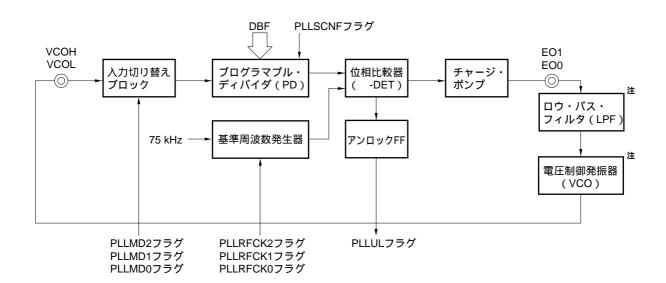

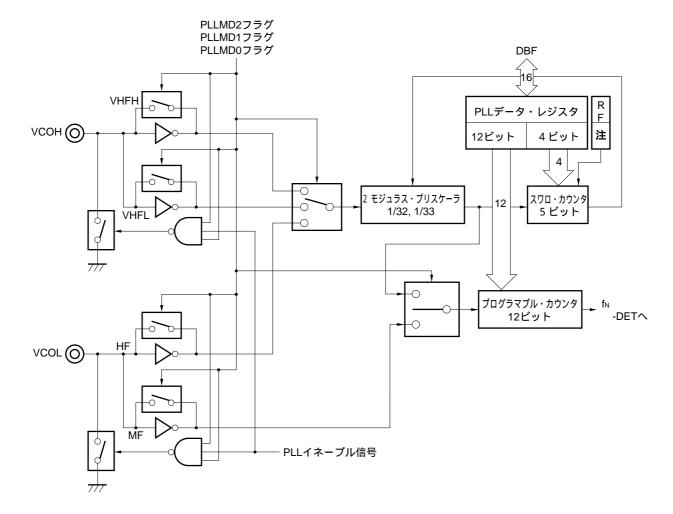

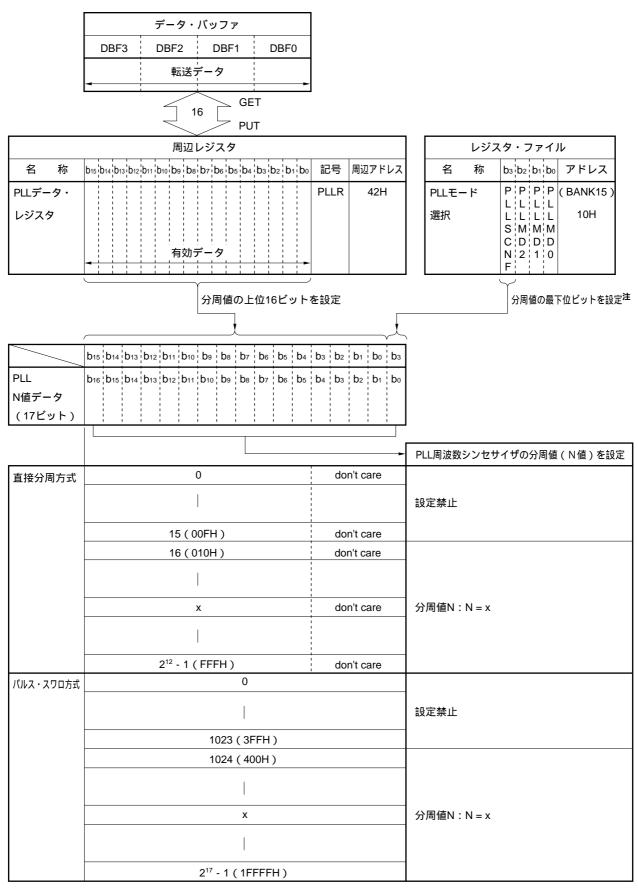

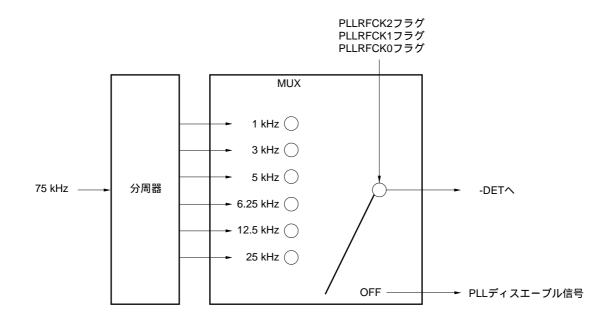

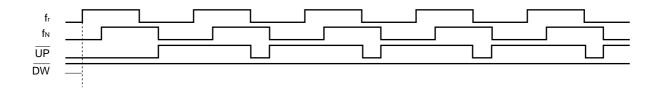

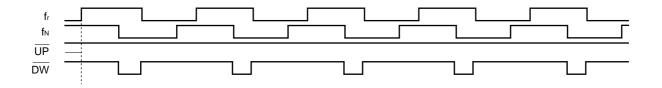

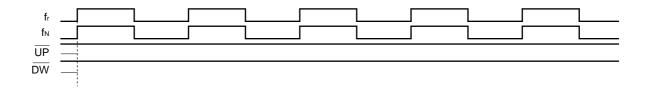

| 16   | PII周   | <b>波数シンセサイザ</b> 161                           |

|      |        | <b>ルー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</b> |

|      |        | 入力切り替えブロックおよびプログラマブル・ディバイダ 162                |

|      |        | 基準周波数発生器 166                                  |

|      |        | <u> </u>                                      |

|      |        | PLLディスエーブル状態 172                              |

|      |        |                                               |

|      |        | PLL周波数シンセサイザの使用方法 173                         |

|      | 16. /  | リセット時の状態 177                                  |

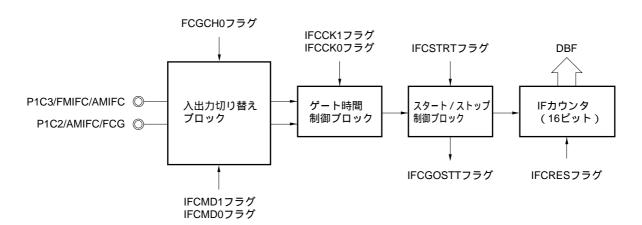

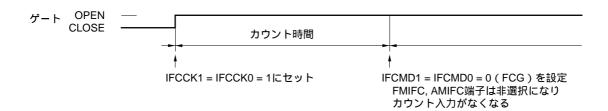

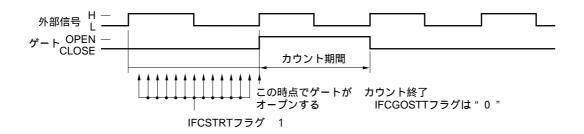

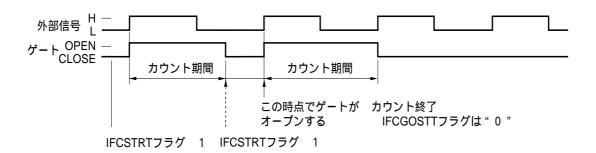

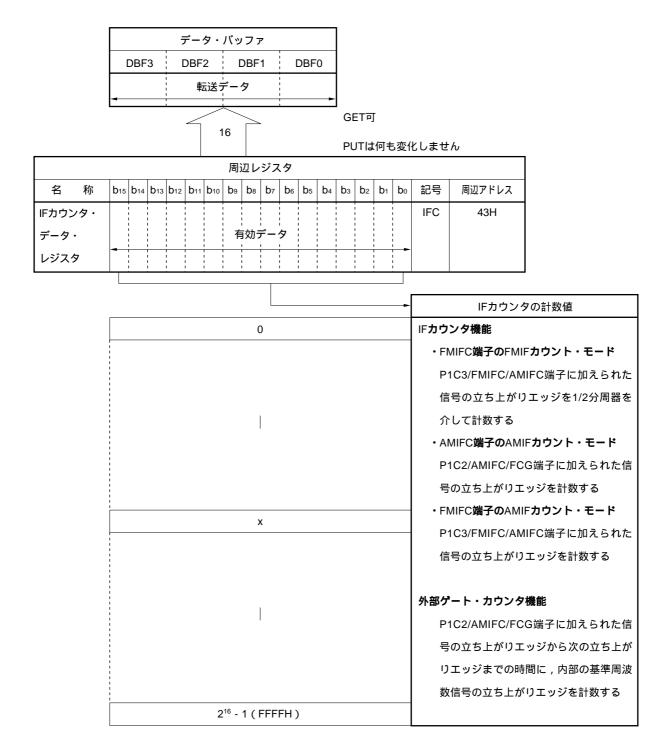

| 17   | . 中間周  | <b>波数(IF)カウンタ</b> 178                         |

|      | 17. 1  | 中間周波数 (IF) カウンタ概要 178                         |

|      | 17. 2  | 入力切り替えブロックおよびゲート時間制御ブロック 179                  |

| 8    |        | データ・シート U13778JJ2V0DS                         |

12.8 割り込み処理ルーチンからの復帰処理 ... 114

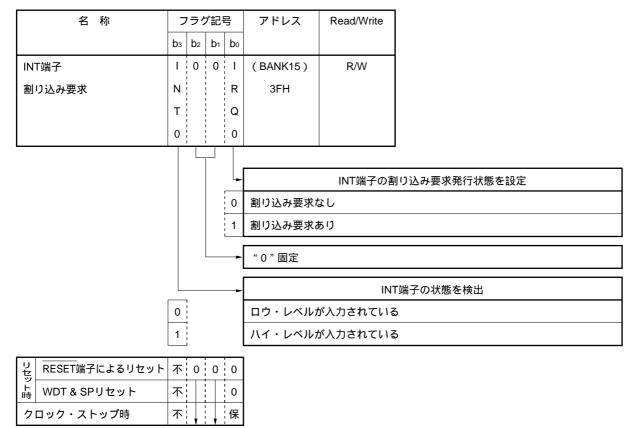

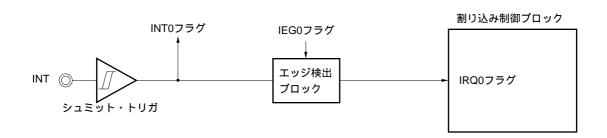

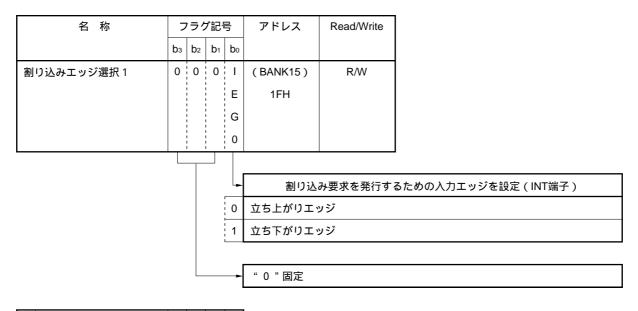

12.9 外部 (INT端子)割り込み ... 115

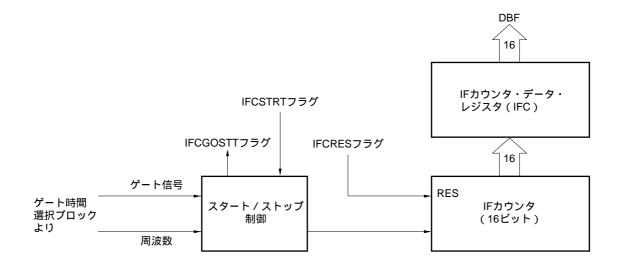

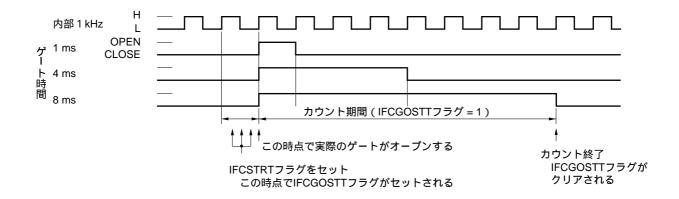

|     | 17.3  | スタート / ストップ制御ブロックおよびIFカウンタ 182       |

|-----|-------|--------------------------------------|

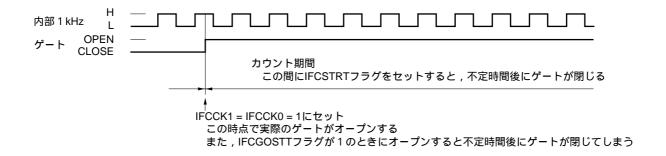

|     | 17.4  | IFカウンタの使用方法 189                      |

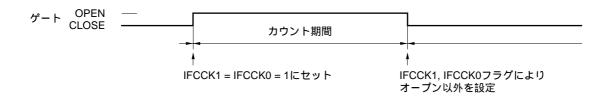

|     | 17.5  | 外部ゲート・カウンタの使用方法 191                  |

|     | 17. 6 | リセット時の状態 192                         |

|     |       |                                      |

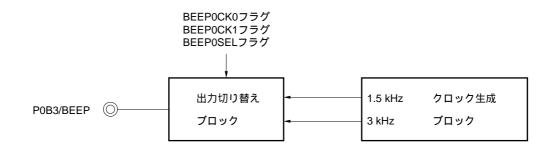

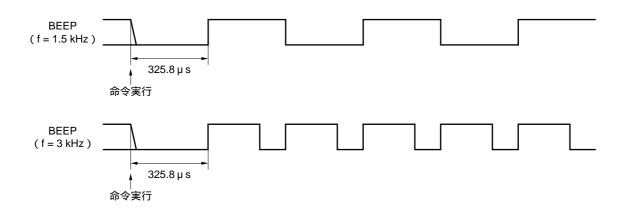

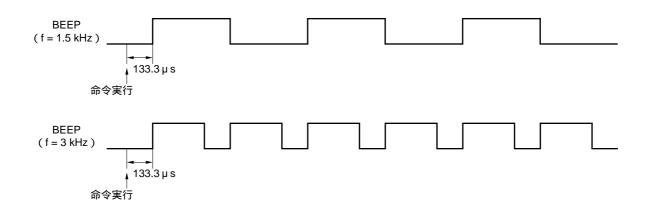

| 18. | BEEP  | 193                                  |

|     | 18. 1 | BEEP概要 193                           |

|     | 18. 2 | BEEPの出力波形 195                        |

|     | 18.3  | リセット時の状態 196                         |

|     |       |                                      |

| 19. | LCD 🗖 | ント <b>ローラ/ドライバ</b> 197               |

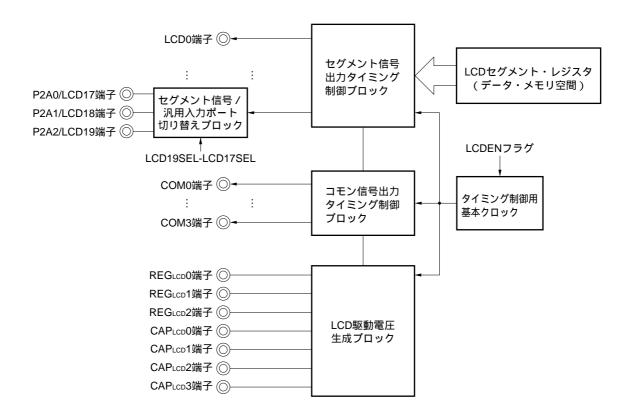

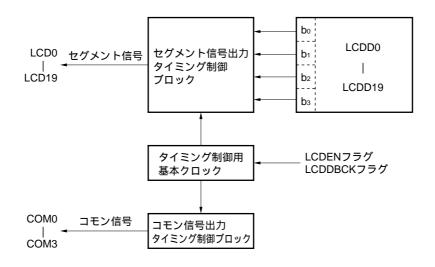

|     | 19. 1 | LCDコントローラ / ドライバ概要 197               |

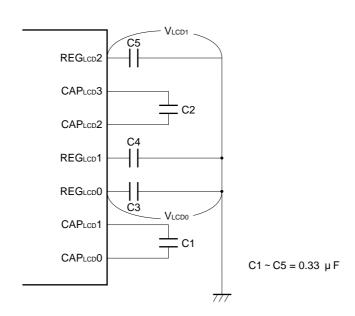

|     | 19. 2 | LCD駆動電圧生成プロック 198                    |

|     | 19.3  | LCDセグメント・レジスタ 199                    |

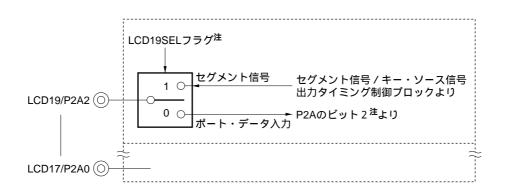

|     | 19.4  | セグメント信号 / 汎用入力ポート切り替えブロック 201        |

|     | 19.5  | コモン信号出力,セグメント信号出力タイミング制御ブロック 203     |

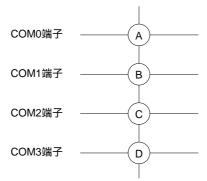

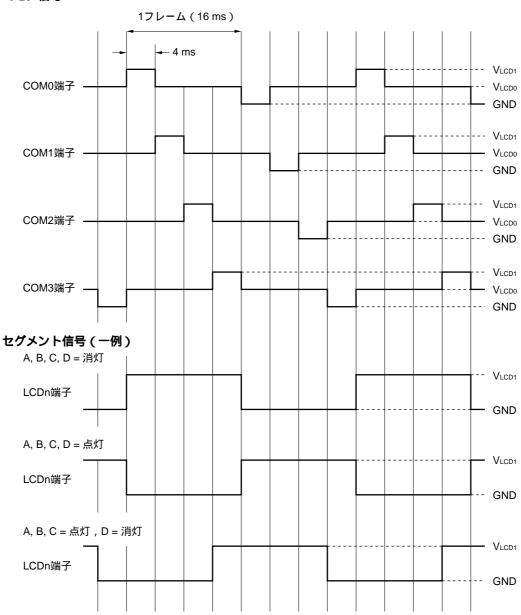

|     | 19.6  | コモン信号およびセグメント信号出力波形 204              |

|     | 19.7  | LCDコントローラ / ドライバの使用方法 206            |

|     | 19.8  | リセット時の状態 208                         |

|     |       |                                      |

| 20. | スタン   | パイ 209                               |

|     | 20. 1 | スタンバイ機能概要 209                        |

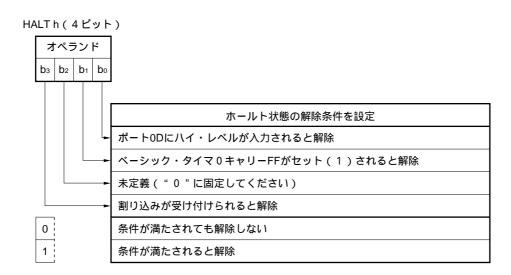

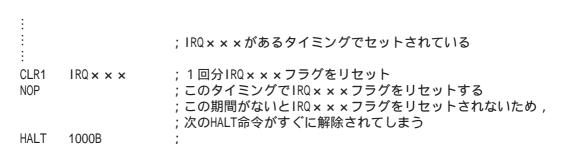

|     | 20. 2 | ホールト機能 210                           |

|     | 20.3  | クロック・ストップ機能 216                      |

|     | 20.4  | ホールトおよびクロック・ストップ時のデバイス動作 218         |

|     | 20.5  | ホールト状態およびクロック・ストップ状態中の各端子の処理上の注意 218 |

|     |       |                                      |

| 21. | リセッ   | <b>h</b> 221                         |

|     | 21.1  | リセットの概要 221                          |

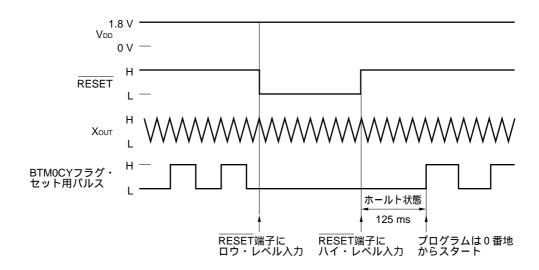

|     | 21. 2 | RESET端子によるリセット 222                   |

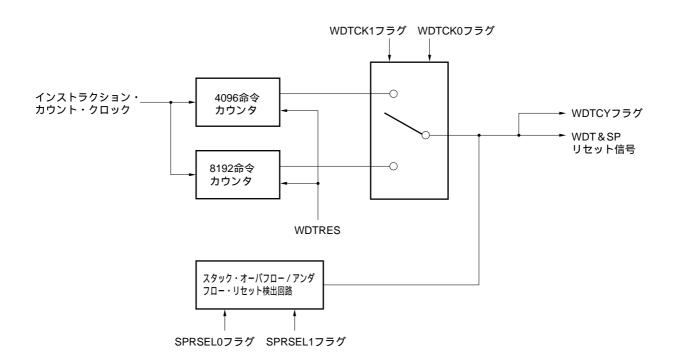

|     | 21.3  | WDT & SPリセット 223                     |

|     |       |                                      |

| 22. | 命令セ   | ット 229                               |

|     | 22. 1 | 命令セット概要 229                          |

|     | 22. 2 | 凡 例 230                              |

|     | 22. 3 | 命令一覧表 231                            |

|     | 22.4  | アセンブラ(RA17K)組み込みマクロ命令 233            |

|     |       |                                      |

| 23. | 予約シ   | ンポル 234                              |

|     | 23. 1 | データ・バッファ (DBF) 234                   |

|     | 23. 2 | システム・レジスタ (SYSREG) 234               |

|     | 23. 3 | LCDセグメント・レジスタ 235                    |

|     | 23.4  | ポート・レジスタ 236                         |

- 23.5 レジスタ・ファイル (コントロール・レジスタ) ... 237

- 23.6 周辺ハードウエア・レジスタ ... 239

- 23.7 その他 ... 239

- 24. 電気的特性 ... 240

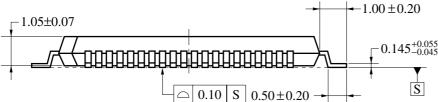

- 25.外形図 ... 244

- 26. 半田付け推奨条件 ... 245

- 付録A.水晶振動子を接続するときの注意 ... 246

- 付録B. 開発ツール ... 247

# 1.端子機能

#### 1.1 端子機能一覧

| 端子番号 | 記号                                   |                      | 機能                    |                | 出力形式  |  |  |  |

|------|--------------------------------------|----------------------|-----------------------|----------------|-------|--|--|--|

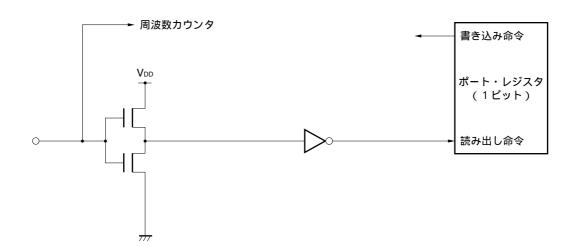

| 1    | P1C0/TM0                             | ポート1C , タイマ・イベント     | 入力,AM/FMのIFカウンタ(周     | 波数カウント用)入      | -     |  |  |  |

| 2    | P1C1/TM1                             | カです。                 |                       |                |       |  |  |  |

| 3    | P1C2/AMIFC/                          | P1C0-P1C3            |                       |                |       |  |  |  |

|      | FCG                                  | 4 ビットの入力ポート          |                       |                |       |  |  |  |

| 4    | P1C3/FMIFC/                          | TM0, TM1             |                       |                |       |  |  |  |

|      | AMIFC                                | タイマ・イベント入力           |                       |                |       |  |  |  |

|      |                                      | AMIFC                |                       |                |       |  |  |  |

|      |                                      | AM用のIFカウンタ入力端子       |                       |                |       |  |  |  |

|      |                                      | FMIFC                |                       |                |       |  |  |  |

|      |                                      | FM用のIFカウンタ入力端子       |                       |                |       |  |  |  |

|      |                                      | FCG                  |                       |                |       |  |  |  |

|      |                                      | <br>  IFカウンタのゲート・カウン | ント入力端子                |                |       |  |  |  |

|      |                                      | リセッ                  | ット時                   | クロック・ストップ時     |       |  |  |  |

|      |                                      | RESET端子によるリセット       | WDT&SPリセット            |                |       |  |  |  |

|      |                                      | 入力 (P1C0-P1C3)       | 入力 (P1C0-P1C3)        | 入力 (P1C0-P1C3) |       |  |  |  |

| 80   | V <sub>DD</sub> 2                    | 電源です。同電位を供給してください。   |                       |                |       |  |  |  |

| 5    | V <sub>DD</sub> 1                    | VDD2:A/Dコンバータのコン     |                       |                |       |  |  |  |

| 32   | V <sub>DD</sub> 0                    | Vpp1:PLLの電源です。       |                       |                |       |  |  |  |

|      |                                      | Vpp0:上記を除くすべての       |                       |                |       |  |  |  |

| 79   | GND2                                 | グランドです。              |                       |                | -     |  |  |  |

| 6    | GND1                                 |                      |                       |                |       |  |  |  |

| 11   | GND0                                 |                      |                       |                |       |  |  |  |

| 7    | EO0                                  | PLL周波数シンセサイザのチャ      | ァージ・ポンプからの出力です。       | ,              | CMOS  |  |  |  |

| 8    | EO1                                  | 局部発振の分周周波数と基準原       | <b>司波数の位相差比較結果を出力</b> | します。           | 3ステート |  |  |  |

|      |                                      | リセッ                  | ソト時                   | クロック・ストップ時     |       |  |  |  |

|      |                                      | RESET端子によるリセット       | WDT&SPリセット            |                |       |  |  |  |

|      |                                      | ハイ・インピーダンス出力         | ハイ・インピーダンス出力          | ハイ・インピーダンス出力   |       |  |  |  |

| 9    | VCOL                                 | PLLの局部発振(VCO)周波数     | 数の入力です。               |                | -     |  |  |  |

| 10   | VCOH                                 | VCOL                 |                       |                |       |  |  |  |

|      |                                      | ・プログラムでHF, MFモー      | ド選択時,アクティブ。それ以        | 外のときはプルダウ      |       |  |  |  |

|      |                                      | ン。                   |                       |                |       |  |  |  |

|      |                                      | VCOH                 |                       |                |       |  |  |  |

|      |                                      | ・プログラムでVHFL, VHFI    | Hモード選択時,アクティブ。        | それ以外のときはプ      |       |  |  |  |

|      |                                      | ルダウン。                |                       |                |       |  |  |  |

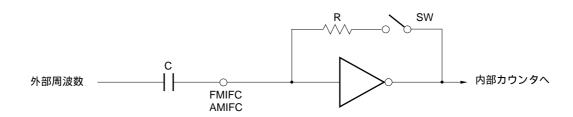

|      | これらの端子の入力は交流アンプとなっているため,入力信号の直流分はコンラ |                      |                       |                |       |  |  |  |

|      |                                      | ンサでカットしてください。        |                       |                |       |  |  |  |

| 12   | TEST                                 | テスト用入力端子です。必ず(       | GNDに直接接続してください。       |                | -     |  |  |  |

| 13   | RESET                                | リセット入力です。            |                       |                | -     |  |  |  |

| 端子番号 | 記号           |                          | 出力形式                             |              |           |  |  |  |

|------|--------------|--------------------------|----------------------------------|--------------|-----------|--|--|--|

| 14   | P2B0         | 4 ビットの入出力ポートです。          |                                  | CMOS         |           |  |  |  |

|      |              | 1 ビット単位で入力 / 出力設況        | プッシュプル                           |              |           |  |  |  |

| 17   | P2B3         | リセッ                      |                                  |              |           |  |  |  |

|      |              | RESET端子によるリセット           | WDT&SPリセット                       |              |           |  |  |  |

|      |              | 入力                       | 入力                               | 保持           |           |  |  |  |

| 18   | P0A0         | 2 ビットの出力ポートです。           |                                  |              | N-chオープン・ |  |  |  |

| 19   | P0A1         | リセッ                      | ット時                              | クロック・ストップ時   | ドレーン      |  |  |  |

|      |              | RESET端子によるリセット           | WDT&SPリセット                       |              |           |  |  |  |

|      |              | ロウ・レベルを出力                | ロウ・レベルを出力                        | 保持           |           |  |  |  |

| 20   | P1A0         | 4 ビットの入出力ポートです。          |                                  |              | N-chオープン・ |  |  |  |

|      |              | 1 ビット単位で入力 / 出力設         | 定が可能です。                          |              | ドレーン      |  |  |  |

| 23   | P1A3         | リセッ                      | ソト時                              | クロック・ストップ時   |           |  |  |  |

|      |              | RESET端子によるリセット           | WDT&SPリセット                       |              |           |  |  |  |

|      |              | 入力                       | 入力                               | 保持           |           |  |  |  |

| 24   | P1D0         | 4 ビットの入出力ポートです。          |                                  |              | N-chオープン・ |  |  |  |

|      |              | 1 ビット単位で入力 / 出力設況        | 定が可能です。                          |              | ドレーン      |  |  |  |

| 27   | P1D3         | リセッ                      | クロック・ストップ時                       |              |           |  |  |  |

|      |              | RESET端子によるリセット           | WDT&SPリセット                       |              |           |  |  |  |

|      |              | 入力                       | 保持                               |              |           |  |  |  |

| 28   | P0B0/SCK     | P0Bおよびシリアル・インタフ          | POBおよびシリアル・インタフェースの入出力とBEEP出力です。 |              |           |  |  |  |

|      | P0B1/SI1/SO2 | P0B3-P0B0                |                                  |              | プッシュプル    |  |  |  |

| 31   | P0B2/SO1     | ・4 ビットの入出力ポート            |                                  |              |           |  |  |  |

|      | P0B3/BEEP    | ・ 1 ビット単位で入力 / 出力の       | の設定可能                            |              |           |  |  |  |

|      |              | BEEP                     |                                  |              |           |  |  |  |

|      |              | ・BEEP出力                  |                                  |              |           |  |  |  |

|      |              | SO1, SO2, SI1            |                                  |              |           |  |  |  |

|      |              | シリアル・インタフェース 1 0         | D 3 線式または 2 線式シリアルI              | /O選択時の , シリア |           |  |  |  |

|      |              | ル・データ出力 , シリアル・:         | データ入力                            |              |           |  |  |  |

|      |              | SCK                      |                                  |              |           |  |  |  |

|      |              | ・シリアル・クロック入出力            |                                  |              |           |  |  |  |

|      |              | リセッ                      | ット時                              | クロック・ストップ時   |           |  |  |  |

|      |              | RESET端子によるリセット           | WDT&SPリセット                       |              |           |  |  |  |

|      |              | 入力 (P0B3-P0B0)           | 入力 (P0B3-P0B0)                   | 保持           |           |  |  |  |

| 33   | CAPLCD0      | LCD駆動用電源を作るための           | , ダブラ回路用のコンデンサを                  | 接続する端子です。    | -         |  |  |  |

| 34   | CAPLCD1      | CAPLCD0-CAPLCD1間, CAPLCD |                                  |              |           |  |  |  |

| 37   | CAPLCD2      | 続してください。                 |                                  |              |           |  |  |  |

| 38   | CAPLCD3      |                          |                                  |              |           |  |  |  |

| 35   | REGLCD0      | LCD駆動用電源のレギュレー           | タ出力端子です。                         |              | -         |  |  |  |

| 36   | REGLCD1      | 0.1 μ FのコンデンサでGNDに       | 接続してください。                        |              |           |  |  |  |

| 39   | REGLCD2      |                          |                                  |              |           |  |  |  |

| 端子番号 | 記号         |                        | 出力形式                                  |            |        |  |  |  |

|------|------------|------------------------|---------------------------------------|------------|--------|--|--|--|

| 40   | СОМО       | LCDコントローラ / ドライバの      | カコモン信号を出力します。<br>カコモン信号を出力します。        |            | CMOS   |  |  |  |

|      |            | リセッ                    | ノト時                                   | クロック・ストップ時 | 3ステート  |  |  |  |

| 43   | СОМЗ       | RESET端子によるリセット         | WDT&SPリセット                            |            |        |  |  |  |

|      |            | ロウ・レベルを出力              | ロウ・レベルを出力                             | ロウ・レベルを出力  |        |  |  |  |

| 44   | LCD0       | LCDコントローラ / ドライバの      | Dセグメント信号出力です。                         |            | CMOS   |  |  |  |

|      |            |                        |                                       |            | プッシュプル |  |  |  |

| 60   | LCD16      |                        |                                       |            |        |  |  |  |

| 61   | P2A0/LCD17 | ポート2A入力,およびLCDコ        | ぱート2A入力,およびLCDコントローラ/ドライバのセグメント信号の出力で |            |        |  |  |  |

|      | P2A1/LCD18 | す。                     |                                       |            |        |  |  |  |

| 63   | P2A2/LCD19 | P2A0-P2A2              |                                       |            |        |  |  |  |

|      |            | 3 ビットの入力ポート            |                                       |            |        |  |  |  |

|      |            | LCD17-LCD19            |                                       |            |        |  |  |  |

|      |            | LCDセグメント出力             |                                       |            |        |  |  |  |

|      |            | リセッ                    | ット時                                   | クロック・ストップ時 |        |  |  |  |

|      |            | RESET端子によるリセット         | WDT&SPリセット                            |            |        |  |  |  |

|      |            | 入力 ( P2A2-P2A0 )       | 入力 ( P2A2-P2A0 )                      | 保持         |        |  |  |  |

| 64   | P0C0       | 4 ビットの出力です。            | 4 ビットの出力です。                           |            |        |  |  |  |

|      |            | リセッ                    | プッシュプル                                |            |        |  |  |  |

| 67   | P0C3       | <br>RESET端子によるリセット     | WDT&SPリセット                            |            |        |  |  |  |

|      |            | ロウ・レベルを出力              |                                       |            |        |  |  |  |

| 68   | INT        | エッジ検出のベクタ割り込み。         | 入力です。                                 |            | -      |  |  |  |

|      |            | エッジは立ち上がり、立ち下が         | がりの選択が可能です。                           |            |        |  |  |  |

| 69   | Хоит       | 水晶振動子の接続用端子です。         |                                       |            | -      |  |  |  |

| 70   | Xin        |                        |                                       |            |        |  |  |  |

| 71   | P2C0       | 4 ビットの入出力ポートです。        |                                       |            | CMOS   |  |  |  |

|      |            | 1 ビット単位で入力 / 出力設定      | 定が可能です。                               |            | プッシュプル |  |  |  |

| 74   | P2C3       | リセッ                    | ット時                                   | クロック・ストップ時 |        |  |  |  |

|      |            | <br>RESET端子によるリセット     | WDT&SPリセット                            |            |        |  |  |  |

|      |            | 入力                     | 入力                                    | 保持         |        |  |  |  |

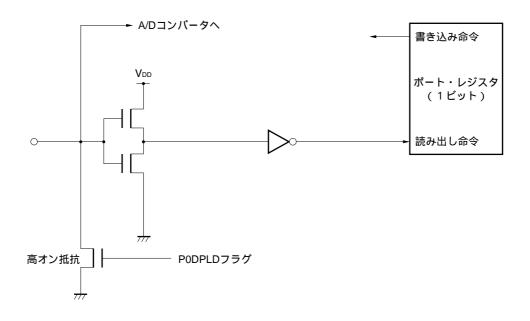

| 75   | P0D0       | ポート0D入力,A/Dコンバーク       | タ入力 , HALT, STOP解除信号.                 | <br>入力です。  | -      |  |  |  |

|      | P0D1/AD0   | P0D0-P0D3              |                                       |            |        |  |  |  |

| 78   | P0D2/AD1   | 4 ビットの入力ポート            |                                       |            |        |  |  |  |

|      | P0D3/AD2   | AD0-AD2                |                                       |            |        |  |  |  |

|      |            | A/Dコンバータのアナログ <i>入</i> | カ                                     |            |        |  |  |  |

|      |            | HALT, STOP解除           |                                       |            |        |  |  |  |

|      |            | ハイ・レベル入力によりモ・          | ードを解除                                 |            |        |  |  |  |

|      |            | リセッ                    | ソト時                                   | クロック・ストップ時 |        |  |  |  |

|      |            | RESET端子によるリセット         | WDT&SPリセット                            |            |        |  |  |  |

|      |            | プルダウン抵抗付き入力            | プルダウン抵抗付き入力                           | 保持         |        |  |  |  |

|      |            | (P0D3-P0D0)            | (P0D3-P0D0)                           |            |        |  |  |  |

# 1.2 端子の等価回路

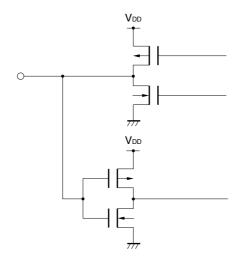

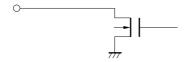

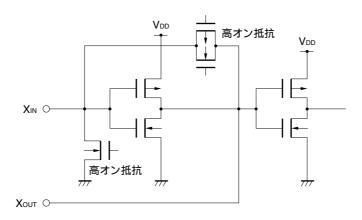

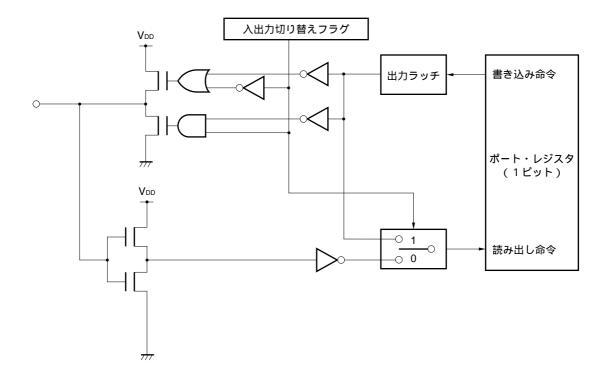

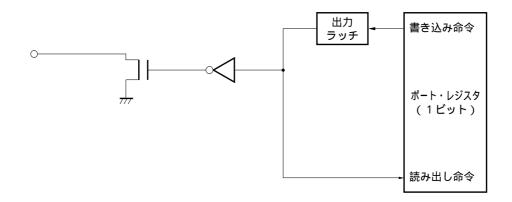

(1) P0B (P0B3/BEEP, P0B2/SO1, P0B1/SI1/SO2, P0B0/SCK)

P2B (P2B3, P2B2, P2B1, P2B0)

P2C (P2C3, P2C2, P2C1, P2C0)

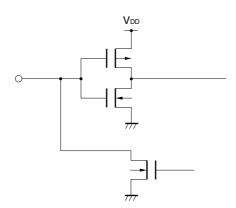

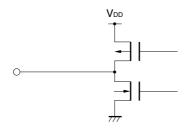

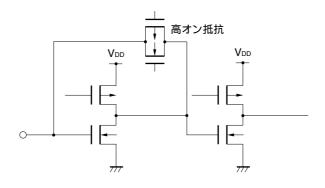

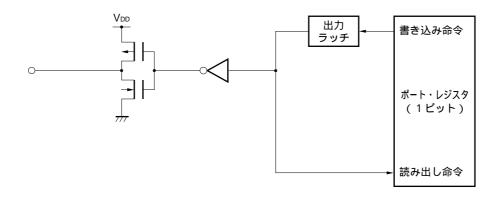

(2) P1A (P1A3, P1A2, P1A1, P1A0) P1D (P1D3, P1D2, P1D1, P1D0)

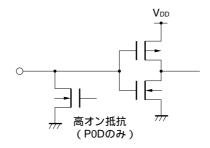

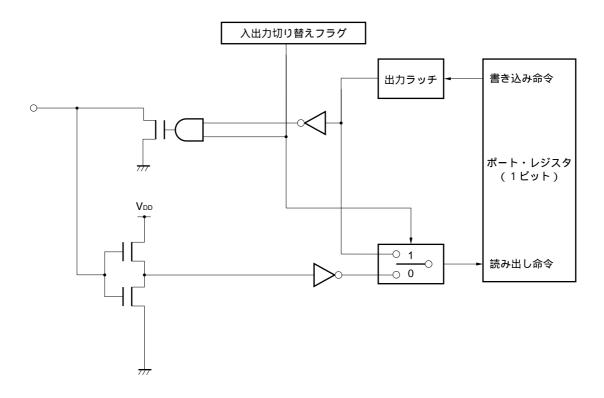

(3) POA (POA1, POA0) (出力)

(4) POC (POC3, POC2, POC1, POC0) (出力)

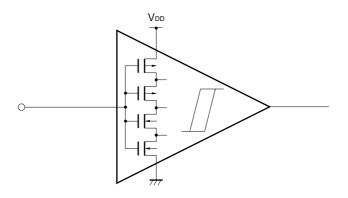

(5) P0D (P0D3/AD2, P0D2/AD1, P0D1/AD0, P0D0)

P1C (P1C3/FMIFC/AMIFC, P1C2/AMIFC/FCG, P1C1/TM1, P1C0/TM0) (入力)

P2A (P2A2/LCD19, P2A1/LCD18, P2A0/LCD17)

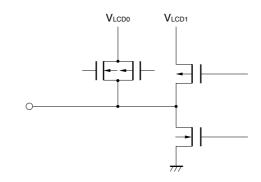

(7) XOUT(出力), XIN(入力)

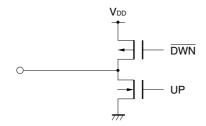

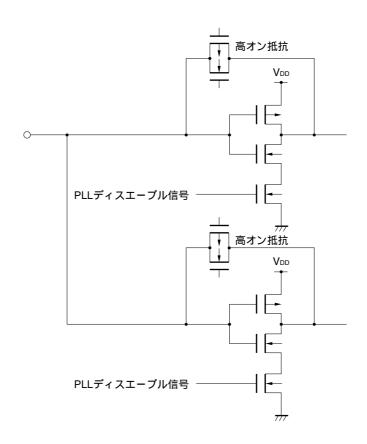

# (8) EO1, EO0 (出力)

# (9) COM3-COM0(出力)

# (10) VCOH(入力)

(11) VCOL(入力)

#### 1.3 未使用端子の処理

未使用端子には,次に示すような処置を推奨します。

表1-1 未使用端子の処理

|                  | 端子名                            | 入出力方式              | 未使用時の推奨処理                                |

|------------------|--------------------------------|--------------------|------------------------------------------|

| ポー               | P0D3/AD2-P0D1/AD0, P0D0        | 入力                 | 各端子ごとに抵抗を介して,GNDに接続してください。 <sup>注1</sup> |

| ·<br>ト<br>端<br>子 | P1C3/FMIFC/AMIFC <sup>注2</sup> |                    |                                          |

| 学                | P1C2/AMIFC/FCG <sup>注2</sup>   |                    |                                          |

|                  | P1C1/TM1                       |                    | ポートに設定して,各端子ごとに抵抗を介して,VooまたはGNDに         |

|                  | P1C0/TM0                       |                    | 接続してください。                                |

|                  | P0A1, P0A0                     | 出力                 | ソフトウエアでロウ・レベル出力に設定して,オープンにしてくだ           |

|                  | P0C3-P0C0                      |                    | さい。                                      |

|                  | P0B3/BEEP                      | 入出力 <sup>注 3</sup> | ソフトウエアで汎用入力ポートに設定して,各端子ごとに抵抗を介           |

|                  | P0B2/SO1                       |                    | して,VppまたはGNDに接続してください。                   |

|                  | P0B1/SI1/SO2                   |                    |                                          |

|                  | P0B0/SCK                       |                    |                                          |

|                  | P1A3-P1A0                      |                    |                                          |

|                  | P1D3-P1D0                      |                    |                                          |

|                  | P2A2/LCD19                     |                    |                                          |

|                  | P2A1/LCD18                     |                    |                                          |

|                  | P2A0/LCD17                     |                    |                                          |

|                  | P2B3-P2B0                      |                    |                                          |

|                  | P2C3-P2C0                      |                    |                                          |

| ポー               | EO1                            | 出力                 | オープンにしてください。                             |

| 1 .              | EO0                            |                    |                                          |

| ト以外の端子           |                                |                    |                                          |

| 端子               | INT                            | 入力                 | 抵抗を介して,GNDに接続してください。 <sup>注1</sup>       |

|                  | TEST                           | -                  | GNDに直接接続してください。                          |

|                  | VCOH                           | 入力                 | ソフトウエアでPLLディスエーブルに設定して,オープンにしてく          |

|                  | VCOL                           |                    | ださい。                                     |

- 注1.外部でプルアップ(抵抗を介してVooに接続)またはプルダウン(抵抗を介してGNDに接続)する場合,高い抵抗値でプルアップまたはプルダウンすると,その端子はハイ・インピーダンスに近くなるためポートの消費(貫通)電流が増えますので注意してください。応用回路にもよりますが,プルアップまたはプルダウン抵抗値は,数十k 程度が一般的です。

- 2. 汎用入力ポートではハイ・インピーダンス状態でも消費電流は増加しない回路になっています。 AMIFC, FMIFC, FCGには設定しないでください。設定すると消費電流が増えます。

- 3.入出力ポートは, RESET端子によるリセット時, ウォッチドッグ・タイマまたはスタック・オーバフロー/アンダ・フロー・リセット時, クロック・ストップ時, 汎用入力ポートとなります。

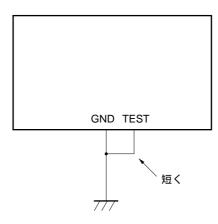

#### 1.4 TEST 端子の使用上の注意

TEST端子にVddを印加すると,テスト・モードに設定されてしまいます。このため,必ず配線長を極力短くしてGND端子に直接接続してください。

TEST端子とGND端子間の配線の引き回しが長い場合や,TEST端子に外来ノイズが加わった場合などで,TEST端子とGND端子間に電位差が生じたときには,お客様のプログラムが正常に動作しないことがあります。

# 2 . プログラム・メモリ (ROM)

#### 2.1 プログラム・メモリ概要

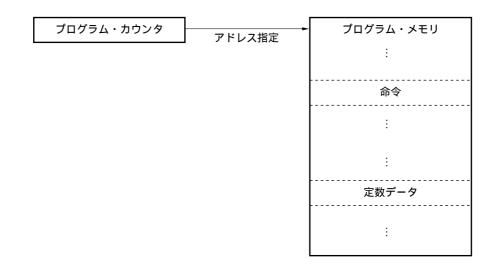

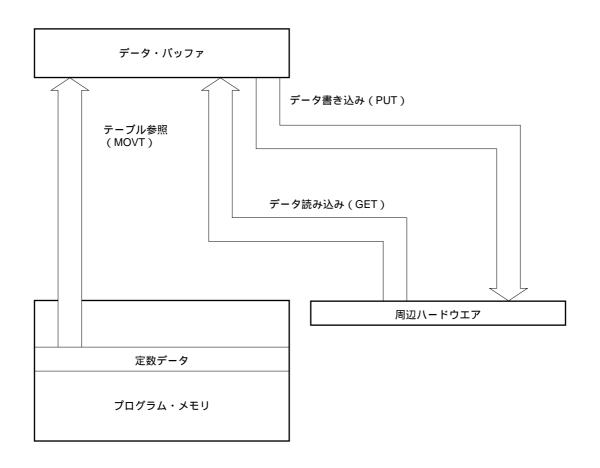

図2-1に,プログラム・メモリの概要を示します。

図2 - 1 に示すように,プログラム・メモリのアドレスは,プログラム・カウンタにより指定します。 プログラム・メモリは,大別して次の2つの機能があります。

- ・プログラムを格納しておく

- ・定数データを格納しておく

図2-1 プログラム・メモリの概略

#### ★ 2.2 プログラム・メモリ

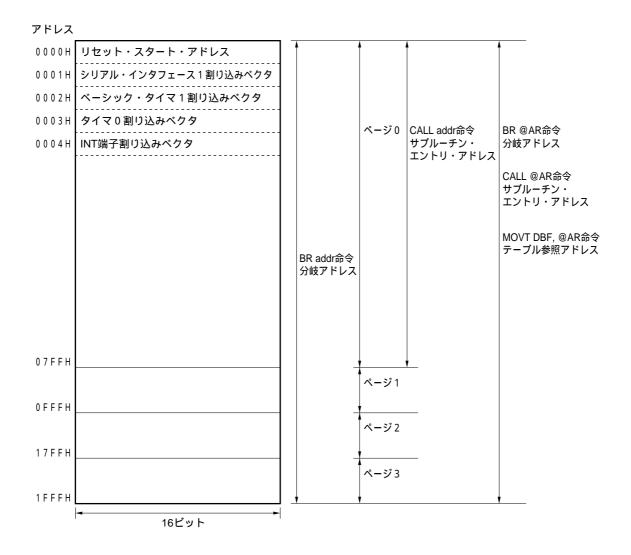

図2-2に,プログラム・メモリの構成を示します。

図2-2に示すように,プログラム・メモリは,次のように構成されています。

μPD17934A:8192×16ビット(0000H-1FFFH番地)

"命令"はすべて16ビット長の"1語命令"であるため、プログラム・メモリの1つの番地に1つの命令を格納することができます。

定数データは、テーブル参照命令を使用して、データ・バッファにプログラム・メモリの内容を読み込みます。

図2-2 プログラム・メモリの構成

#### 2.3 プログラム・カウンタ

#### 2.3.1 プログラム・カウンタの構成

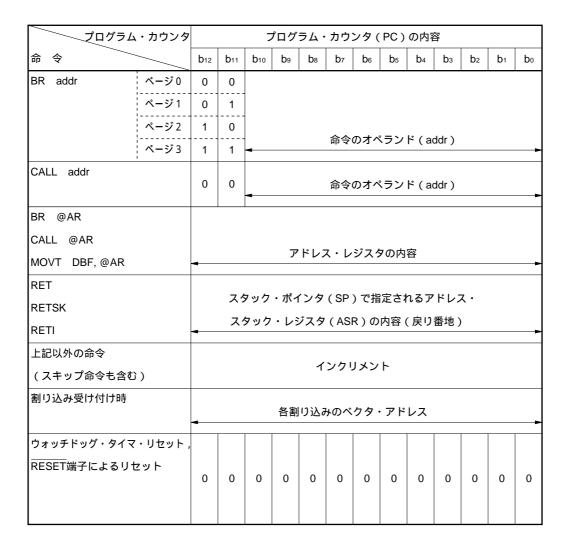

図2-3にプログラム・カウンタの構成を示します。

図2 - 3に示すように,プログラム・カウンタは,13ビットのバイナリ・カウンタで構成されています。さらに,ビット11およびビット12は,ページを示します。

プログラム・カウンタは,プログラム・メモリのアドレスを指定します。

図2-3 プログラム・カウンタの構成

| PC <sub>12</sub> | PC <sub>11</sub> | PC <sub>10</sub> | PC <sub>9</sub> | PC8 | PC <sub>7</sub> | PC <sub>6</sub> | PC₅ | PC <sub>4</sub> | РС₃ | PC <sub>2</sub> | PC <sub>1</sub> | PC <sub>0</sub> |

|------------------|------------------|------------------|-----------------|-----|-----------------|-----------------|-----|-----------------|-----|-----------------|-----------------|-----------------|

| ~-               | -ジ               |                  |                 |     |                 |                 |     |                 |     |                 |                 |                 |

| 4                | PC               |                  |                 |     |                 |                 |     |                 |     |                 |                 |                 |

#### 2.4 プログラムの流れ

プログラムの流れは,プログラム・メモリのアドレスを指定するプログラム・カウンタによって制御されます。 次に,各命令実行時の動作を示します。

図2-4に,各命令実行時にプログラム・カウンタに設定される値を示します。

また,表2-1に,割り込み受け付け時のベクタ・アドレスを示します。

#### 2.4.1 分岐命令

# (1)直接分岐("BR addr")

直接分岐命令の分岐先アドレスは、プログラム・メモリの全アドレスです。

#### (2)間接分岐("BR@AR")

★ 間接分岐命令の分岐先アドレスは,プログラム・メモリの全アドレス(0000H-1FFFH番地)です。

"5.3 アドレス・レジスタ(AR)"も参照してください。

#### 2.4.2 サブルーチン

#### **(1)直接サブルーチン・コール (** "CALL addr ")

直接サブルーチン・コール命令で呼び出せるサブルーチンの先頭アドレスは,ページ 0 内(0000H-07FFH番地)です。

#### **(2)間接サブルーチン・コール (CALL @AR)**

間接サブルーチン・コール命令で呼び出せるサブルーチンの先頭アドレスは,プログラム・メモリの全アドレ

- ★ ス (0000H-1FFFH番地)です。

- "5.3 アドレス・レジスタ (AR)"も参照してください。

#### 2.4.3 テーブル参照

- ★ テーブル参照命令("MOVT DBF, @AR")で参照できるアドレスは,プログラム・メモリの全アドレス(0000H-1FFFH番地)です。

- " **5.3 アドレス・レジスタ (**AR **)** " および " **9.2.2 テーブル参照命令 (** " MOVT DBF, **@**AR " **)** " も参照してください。

図2-4 各命令におけるプログラム・カウンタの値

表2-1 割り込みベクタ・アドレス

| 順位 | 内部 / 外部 | 割り込み要因         | ベクタ・アドレス |

|----|---------|----------------|----------|

| 1  | 外部      | INT端子          | 0004H    |

| 2  | 内部      | タイマ 0          | 0003H    |

| 3  | "       | ベーシック・タイマ 1    | 0002H    |

| 4  | "       | シリアル・インタフェース 1 | 0001H    |

#### ★ 2.5 プログラム・メモリ使用時の注意

プログラム・メモリ・アドレスは0000H-1FFFH番地です。次のことに注意してください。

・1FFFH番地に命令を書き込むときは,必ず分岐命令を書き込んでください。

#### 3. アドレス・スタック (ASK)

#### 3.1 アドレス・スタック概要

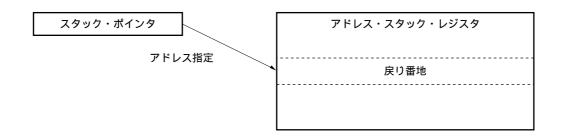

図3-1に,アドレス・スタックの概要を示します。

アドレス・スタックは,スタック・ポインタおよびアドレス・スタック・レジスタで構成されています。

アドレス・スタック・レジスタのアドレスは,スタック・ポインタにより指定します。

アドレス・スタックは,サブルーチン・コール命令実行時,割り込み受け付け時などに戻り番地を退避します。

また、テーブル参照命令実行時も、アドレス・スタックを使用します。

図3-1 アドレス・スタック概要

#### 3.2 アドレス・スタック・レジスタ (ASR)

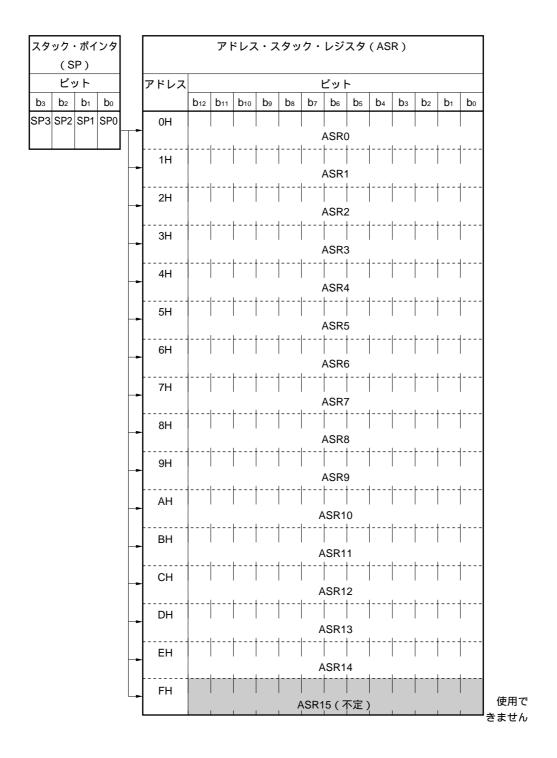

図3-2に,アドレス・スタック・レジスタの構成を示します。

アドレス・スタック・レジスタは,13ビット×16個のレジスタASR0-ASR15で構成されています。ただし,ASR15にはレジスタがなく,実際には13ビット×15個のレジスタ(ASR0-ASR14)で構成されています。

アドレス・スタックは,サブルーチン・コール時,割り込み受け付け時およびテーブル参照命令実行時に,戻り番地を格納します。

図3-2 アドレス・スタック・レジスタの構成

#### 3.3 スタック・ポインタ(SP)

#### 3.3.1 スタック・ポインタの構成と機能

図3-3に,スタック・ポインタの構成と機能を示します。

スタック・ポインタは,4ビットのバイナリ・カウンタで構成されています。

スタック・ポインタは,アドレス・スタック・レジスタのアドレスを指定します。

スタック・ポインタは,レジスタ操作命令により,直接,値を読み込んだり書き込んだりすることもできます。

図3-3 スタック・ポインタの構成と機能

| 名 称       | -             | フラグ記号          |                |                | アドレス | Read/Write |

|-----------|---------------|----------------|----------------|----------------|------|------------|

|           | рз            | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |      |            |

| スタック・ポインタ | $\overline{}$ |                |                |                | 01H  | R/W        |

| (SP)      | S             | S              | S              | S              |      |            |

|           | Р             | Р              | Р              | Р              |      |            |

|           | 3             | 2              | 1              | 0              |      |            |

|           | $\overline{}$ |                |                |                |      |            |

|   |   | ١, |   |                             |

|---|---|----|---|-----------------------------|

|   |   |    | - | アドレス・スタック・レジスタ(ASR)のアドレスを指定 |

| 0 | 0 | 0  | 0 | アドレス 0 (ASR0)               |

| 0 | 0 | 0  | 1 | アドレス 1 (ASR1)               |

| 0 | 0 | 1  | 0 | アドレス 2 ( ASR2 )             |

| 0 | 0 | 1  | 1 | アドレス3(ASR3)                 |

| 0 | 1 | 0  | 0 | アドレス4 (ASR4)                |

| 0 | 1 | 0  | 1 | アドレス 5 (ASR5)               |

| 0 | 1 | 1  | 0 | アドレス 6 (ASR6)               |

| 0 | 1 | 1  | 1 | アドレス7(ASR7)                 |

| 1 | 0 | 0  | 0 | アドレス 8 ( ASR8 )             |

| 1 | 0 | 0  | 1 | アドレス 9 ( ASR9 )             |

| 1 | 0 | 1  | 0 | アドレス10 ( ASR10 )            |

| 1 | 0 | 1  | 1 | アドレス11 ( ASR11 )            |

| 1 | 1 | 0  | 0 | アドレス12 ( ASR12 )            |

| 1 | 1 | 0  | 1 | アドレス13 ( ASR13 )            |

| 1 | 1 | 1  | 0 | アドレス14 ( ASR14 )            |

| 1 | 1 | 1  | 1 | 設定禁止                        |

| リセッ        | RESET端子によるリセット | 1 | 1   | 1 | 1 |  |

|------------|----------------|---|-----|---|---|--|

| ト時         | WDT & SPリセット   | 1 | 1   | 1 | 1 |  |

| クロック・ストップ時 |                |   | 保 持 |   |   |  |

RESET端子によるリセット: RESET端子によるリセット時

WDT&SPリセット : ウォッチドッグ・タイマおよびスタック・ポインタ・リセット時

クロック・ストップ : クロック・ストップ命令実行時

#### 3.4 アドレス・スタックの動作

3.4.1 サブルーチン・コール命令 ( " CALL addr ", " CALL @AR " ) およびリターン命令 ( " RET ", " RETSK " )

サブルーチン・コール命令が実行されると,スタック・ポインタの値を - 1 し,スタック・ポインタで指定されるアドレス・スタック・レジスタに戻り番地を格納します。

リターン命令が実行されると,スタック・ポインタで指定されるアドレス・スタック・レジスタの内容(戻り番地) をプログラム・カウンタに復帰し,スタック・ポインタの値を+1します。

#### 3.4.2 テーブル参照命令 ( " MOVT DBF, @AR " )

テーブル参照命令が実行されると,スタック・ポインタの値を - 1 し,スタック・ポインタで指定されるアドレス・スタック・レジスタに戻り番地を格納します。

次に,アドレス・レジスタで指定されるプログラム・メモリの内容をデータ・バッファに読み出し,スタック・ポインタで指定されるアドレス・スタック・レジスタの内容(戻り番地)をプログラム・カウンタに復帰したあと,スタック・ポインタの値を+1します。

#### 3.4.3 **割り込み受け付け時とリターン命令(** "RETI")

割り込みが受け付けられると,スタック・ポインタの値を - 1 し,スタック・ポインタで指定されるアドレス・スタック・レジスタに戻り番地を格納します。

リターン命令が実行されると,スタック・ポインタで指定されるアドレス・スタック・レジスタの内容(戻り番地) をプログラム・カウンタに復帰し,スタック・ポインタの値を+1します。

#### 3.4.4 アドレス・スタック操作命令 ("PUSH AR", "POP AR")

"PUSH"命令が実行されると,スタック・ポインタの値を - 1 し,スタック・ポインタで指定されるアドレス・スタック・レジスタにアドレス・レジスタの内容を転送します。

"POP"命令が実行されると,スタック・ポインタで指定されるアドレス・スタック・レジスタの内容をアドレス・レジスタに転送し,スタック・ポインタの値を+1します。

**NEC**

#### 3.5 アドレス・スタック使用時の注意

#### 3.5.1 ネスティング・レベルとオーバフロー時の動作

スタック・ポインタがOFHのときのアドレス・スタック・レジスタ (ASR15)の値は"不定"です。

したがって,スタック操作を行わない状態で15レベルを越えるサブルーチン・コールや割り込みを使用すると, "不定"な番地へ復帰するため使用しないでください。

# 3.5.2 アドレス・スタックのオーパフローまたはアンダフロー検出によるリセット

アドレス・スタックのオーバフローまたはアンダフローの検出によりリセットを発生させることを,プログラムにより選択できます。リセットが発生するとプログラムは0番地からスタートし,コントロール・レジスタの一部を初期化します。

また, RESET端子によるリセット時は, このリセット機能が有効になっています。詳しくは "21 . **リセット**"を参照してください。

# 4 . データ・メモリ (RAM)

# 4.1 データ・メモリ概要

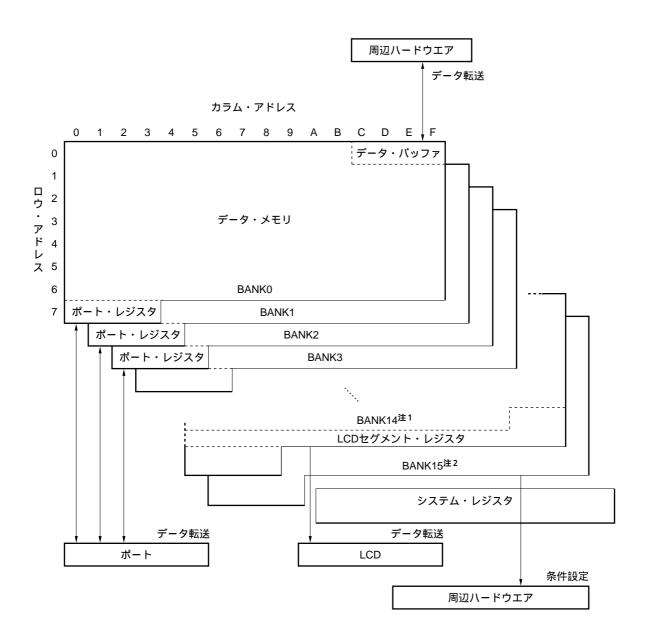

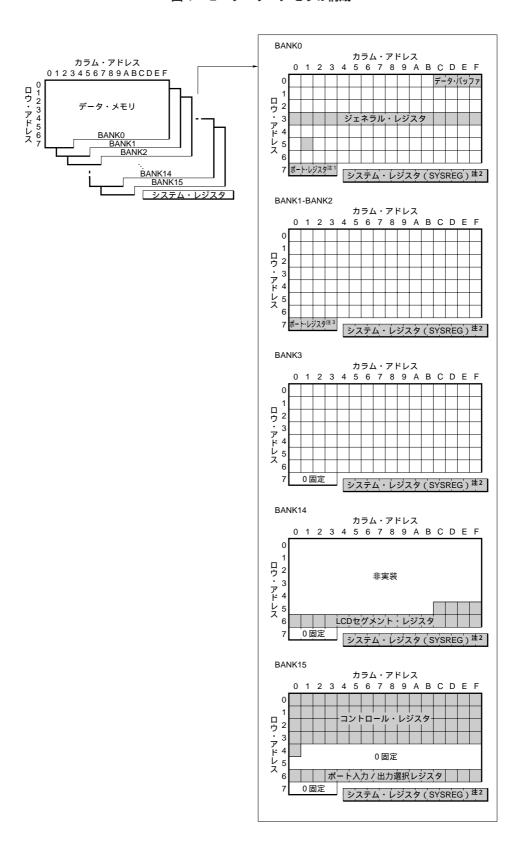

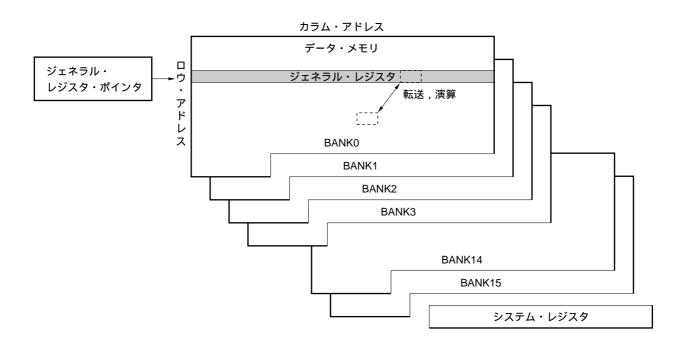

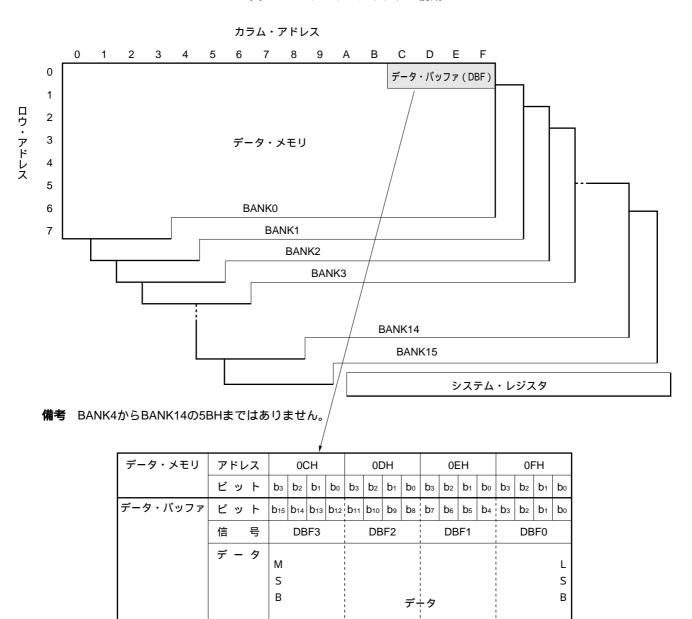

図4-1に,データ・メモリの概要を示します。

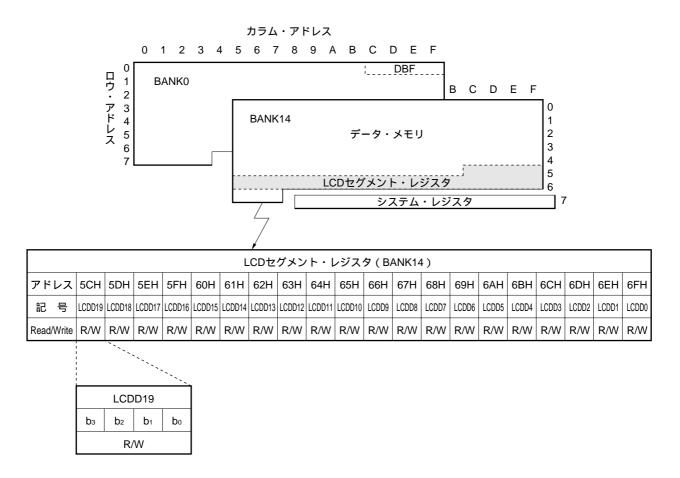

図4 - 1に示すように,データ・メモリ上には,システム・レジスタ,データ・バッファ,ポート・レジスタ,LCD セグメント・レジスタおよびコントロール・レジスタが配置されています。

データ・メモリは,データの格納,周辺ハードウエアとのデータ転送,ポートとのデータ転送およびCPUの制御を行います。

#### 図4-1 データ・メモリの概要

- 注1.BANK14の5CH-6FHには,LCDセグメント・レジスタが割り当てられています。

- **2** . BANK15の00H-6FHには,コントロール・レジスタが割り当てられています。なお,60H-6FHにはポート入力 / 出力選択レジスタが割り当てられています。

- 注意1.BANK15の31H番地はテスト・モード用領域になっていますので,絶対に何も書き込まないでください。

- 2.BANK4からBANK14の5BHまではありません。

#### 4.2 データ・メモリの構成と機能

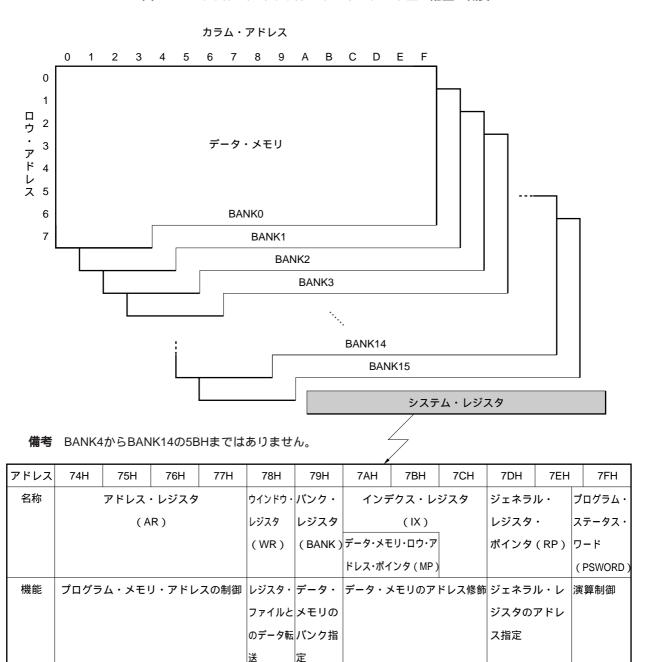

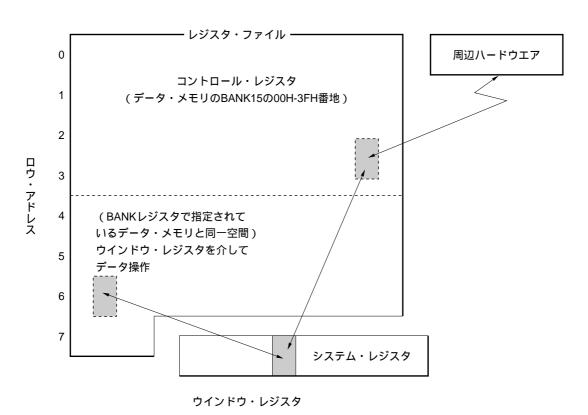

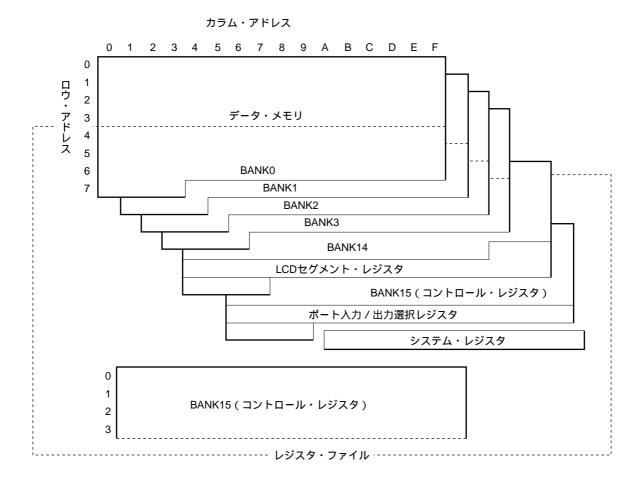

図4-2に,データ・メモリの構成を示します。

図4 - 2 に示すように,データ・メモリは,複数のバンクに分割されており,各バンクは,ロウ・アドレス7H,カラム・アドレス0FHの計128ニブルで構成されています。

データ・メモリは,機能別に次の4.2.1-4.2.6に示すブロックに分けられます。

データ・メモリの内容は,データ・メモリ操作命令を実行することにより,4ビットの演算,比較,判断および転送が1命令で行えます。

表4-1に,データ・メモリ操作命令を示します。

#### 4.2.1 システム・レジスタ (SYSREG)

システム・レジスタは,アドレス74H-7FH番地に割り当てられています。

システム・レジスタは,バンクに無関係に割り当てられているため,どのバンクであってもアドレス74H-7FH番地には,同一のシステム・レジスタが存在します。

詳細は, "5.システム・レジスタ(SYSREG)"を参照してください。

#### 4.2.2 データ・バッファ (DBF)

データ・バッファは,BANKOのアドレスOCH-OFH番地に割り当てられています。

詳細は, "9.データ・バッファ(DBF)"を参照してください。

#### 4.2.3 ポート・レジスタ

ポート・レジスタは, BANKO-BANK2のアドレス70H-73H番地に割り当てられています。

詳細は, "11. 汎用ポート"を参照してください。

#### 4.2.4 コントロール・レジスタ,ポート入力/出力選択レジスタ

コントロール・レジスタはBANK15のアドレス00H-6FH番地に割り当てられています。そのうち,ポート入力/出力 選択レジスタはBANK15のアドレス60H-6FH番地に割り当てられています。また,コントロール・レジスタのBANK15 のアドレス00H-3FH番地は,レジスタ・ファイルのアドレス00H-3FH番地と重なっています。

詳細は , " 8 . レジスタ・ファイル (RF) とコントロール・レジスタ " を参照してください。

#### 4.2.5 LCDセグメント・レジスタ

LCDセグメント・レジスタはデータ・メモリのBANK14のアドレス5CH-6FH番地の計20二ブルで構成されています。 詳細は"8.4 LCD**セグメント・レジスタ**"および"19.LCD**コントローラ/ドライバ**"を参照してください。

#### 4.2.6 汎用データ・メモリ

汎用データ・メモリは,データ・メモリからシステム・レジスタ,ポート・レジスタ,コントロール・レジスタ,ポート入力/出力選択レジスタ,LCDセグメント・レジスタを除いた部分に割り当てられています。

BANKO-BANK3の各112ニブルの計448ニブルから構成されます。

#### 図4-2 データ・メモリの構成

- 注1.70Hの上位2ビットは0固定です。

- 2.同一のシステム・レジスタが存在しています。

- 3.BANK1の71Hと, BANK2の70Hの上位1ビット, 73Hはすべて0固定です。

- 注意 1 . BANK15の31H番地はテスト・モード用領域になっていますので , 絶対に何も書き込まないでください。

- 2 . BANK4からBANK14の5BHまではありません。

機 令 能 演算 加算 ADD ADDC 減算 SUB SUBC 論理 AND OR XOR 比較 SKE SKGE SKLT **SKNE** 転送 MOV LD ST 判断 SKT SKF

表4-1 データ・メモリ操作命令一覧

## 4.3 データ・メモリのアドレシング

図4-3に,データ・メモリのアドレス指定を示します。

データ・メモリのアドレスは,バンク,ロウ・アドレスおよびカラム・アドレスで指定します。

ロウ・アドレスおよびカラム・アドレスはデータ・メモリ操作命令で直接指定しますが,バンクは,バンク・レジスタの内容で指定します。

バンク・レジスタについては, "5.システム・レジスタ(SYSREG)"を参照してください。

バンク

ロウ・アドレス

カラム・アドレス

$b_3$   $b_2$   $b_1$   $b_0$   $b_2$   $b_1$   $b_0$   $b_3$   $b_2$   $b_1$   $b_0$

データ・メモリ・アドレス

バンク・レジスタ

命令のオペランド

図4-3 データ・メモリのアドレス指定

# 4.4 データ・メモリ使用時の注意

# 4.4.1 RESET端子によるリセット時

RESET端子によるリセット時は,汎用データ・メモリの内容は"不定"です。 必要に応じて,イニシャライズしてください。

# 4.4.2 実装されていないデータ・メモリに対する注意

実装されていないデータ・メモリのアドレスに対してデータ・メモリ操作命令の読み込み命令を実行すると,不定なデータが読み込まれます。

なお,書き込み命令を行っても何も変化しません。

# 5.システム・レジスタ(SYSREG)

#### 5.1 システム・レジスタ概要

図5-1に,システム・レジスタのデータ・メモリ上の配置と概要を示します。

図5 - 1に示すように,システム・レジスタは,データ・メモリ・アドレスの74H-7FH番地にバンクとは無関係に配置されています。つまり,どのバンクであっても,74H-7FH番地には同一のシステム・レジスタが存在しています。システム・レジスタは,データ・メモリ上に配置されているため,すべてのデータ・メモリ操作命令で操作することができます。

システム・レジスタは,機能別に7種類のレジスタで構成されています。

図5-1 システム・レジスタのデータ・メモリ上の配置と概要

37

# 5.2 システム・レジスタ一覧

図5-2に,システム・レジスタの構成を示します。

図5-2 システム・レジスタの構成

| アドレス | 74H                                                         | 75H                                                         | 76H         | 77H         | 78H                           | 79H                                                         | 7AH                                                         | 7BH           | 7CH         | 7DH                         | 7EH      | 7FH                                                                        |

|------|-------------------------------------------------------------|-------------------------------------------------------------|-------------|-------------|-------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|---------------|-------------|-----------------------------|----------|----------------------------------------------------------------------------|

| 名称   |                                                             |                                                             |             |             |                               | システム                                                        | ・レジスタ                                                       |               |             |                             |          |                                                                            |

|      |                                                             | アドレス・                                                       | ・レジスタ       |             | ウインドウ・                        | バンク・                                                        | インテ                                                         | <b>デ</b> クス・レ | ジスタ         | ジェネラ                        | ル・       | プログラム・                                                                     |

|      |                                                             | ( A                                                         | R)          |             | レジスタ                          | レジスタ                                                        |                                                             | (IX)          | _           | レジスタ                        | •        | ステータス・                                                                     |

|      |                                                             |                                                             |             |             | (WR)                          | (BANK)                                                      | データ・メモ                                                      | リ・ロウ・ア        |             | ポインタ                        | (RP)     | ワード                                                                        |

|      |                                                             |                                                             |             |             |                               |                                                             | ドレス・ポイ                                                      | ′ンタ(MP)       |             |                             |          | ( PSWORD )                                                                 |

| 記号   | AR3                                                         | AR2                                                         | AR1         | AR0         | WR                            | BANK                                                        | IXH                                                         | IXM           | IXL         | RPH                         | RPL      | PSW                                                                        |

|      |                                                             |                                                             |             |             |                               |                                                             | MPH                                                         | MPL           |             |                             |          |                                                                            |

| ビット  | b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> | b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> | b3 b2 b1 b0 | b3 b2 b1 b0 | b3 b2 b1 b0                   | b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> | b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> | b3 b2 b1 b0   | b3 b2 b1 b0 | b3 b2 b1 b0                 | b3 b2 b1 | b <sub>0</sub> b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> |

| データ  |                                                             |                                                             |             |             |                               |                                                             | М                                                           | (IX           |             |                             |          | BCCZI                                                                      |

|      |                                                             |                                                             |             | -           | -                             | -                                                           | Р                                                           | (MD)          |             | (RP                         |          | СМҮХ                                                                       |

|      |                                                             |                                                             | 1 1 1       | 1 1 1       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                               | E                                                           | (MP)          |             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1      | D P E                                                                      |

## 5.3 アドレス・レジスタ (AR)

## 5.3.1 アドレス・レジスタの構成

図5-3に,アドレス・レジスタの構成を示します。

図 5 - 3 に示すように , アドレス・レジスタは , システム・レジスタの74H-77H番地 (AR3-AR0) の16ビットで構成されています。

図5-3 アドレス・レジスタの構成

|        | アドレス           |             | 74             | 4H             |                |     | 75             | 5H             |                |     | 76             | 6H             |                |    | 7              | 7H             |                |

|--------|----------------|-------------|----------------|----------------|----------------|-----|----------------|----------------|----------------|-----|----------------|----------------|----------------|----|----------------|----------------|----------------|

|        | 名称             |             |                |                |                |     | アト             | ・レス            | ・レ             | ジスク | 7 (Al          | ۲)             |                |    |                |                |                |

|        | 記号             |             | AR3            |                |                | AR2 |                |                |                |     | Al             | R1             |                |    | Al             | R0             |                |

|        | ビット            | bз          | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

|        | データ            | M<br>S<br>B | S              |                |                |     |                |                |                |     |                |                |                |    |                |                | L<br>S<br>B    |

| リセッ    | RESET端子によるリセット |             | 0              |                |                | 0   |                |                | 0              |     |                |                | 0              |    |                |                |                |

| ト<br>時 | WDT&SPリセット     |             | 0              |                |                | 0   |                |                | 0              |     |                |                |                | (  | 0              |                |                |

| ク      | ロック・ストップ時      |             | 保持             |                |                | 保持  |                |                | 保持             |     |                |                | 保持             |    |                |                |                |

RESET端子によるリセット: RESET端子によるリセット時

WD&SPリセット : ウォッチドッグ・タイマおよびスタック・ポインタ・リセット時

クロック・ストップ : クロック・ストップ命令実行時

#### 5.3.2 アドレス・レジスタの機能

アドレス・レジスタは , テーブル参照命令 ( " MOVT DBF, @AR " ) ,スタック操作命令 ( " PUSH AR " , " POP AR " ) ,間接分岐命令 ( " BR @AR " ) および間接サブルーチン・コール命令 ( " CALL @AR " ) 実行時に , プログラム・メモリ・アドレスの指定を行います。

アドレス・レジスタには, " 1 " ずつインクリメントできる専用命令("INC AR") が用意されています。 次の(1)-(5)に,各命令を実行したときの動作を説明します。

#### (1) テーブル参照命令("MOVT DBF, @AR")

アドレス・レジスタの内容で指定されるプログラム・メモリ・アドレスの定数データ (16ビット) を , データ・ バッファに読み出します。

★ アドレス・レジスタで指定できる定数データの格納番地は,0000H-1FFFH番地です。

#### (2) スタック操作命令("PUSH AR", "POP AR")

"PUSH AR"命令を実行したときは,スタック・ポインタを - 1 し, - 1 されたスタック・ポインタで指定されるアドレス・スタック・レジスタに,アドレス・レジスタ(AR)の内容を転送します。

"POP AR"命令を実行したときは、スタック・ポインタで指定されるアドレス・スタック・レジスタの内容をアドレス・レジスタに転送して、スタック・ポインタを + 1 します。

#### (3)間接分岐命令("BR@AR")

アドレス・レジスタの内容で指定されるプログラム・メモリ・アドレスへ分岐します。

★ アドレス・レジスタで指定できる分岐アドレスは,0000H-1FFFH番地です。

#### (4)間接サブルーチン・コール命令("CALL@AR")

アドレス・レジスタの内容で指定されるプログラム・メモリ・アドレスのサブルーチンを,コールできます。

★ アドレス・レジスタで指定できるサブルーチンの先頭アドレスは,0000H-1FFFH番地です。

## (5) アドレス・レジスタ・インクリメント命令("INC AR")

アドレス・レジスタの内容を,"1"ずつインクリメントします。

#### 5.3.3 アドレス・レジスタとデータ・パッファ

アドレス・レジスタは,周辺ハードウエアの一部として,データ・バッファを介してのデータ転送ができます。 詳細は, "9.データ・バッファ(DBF)"を参照してください。

#### 5.3.4 アドレス・レジスタ使用時の注意

アドレス・レジスタは、16ビットで構成されていますので、最大FFFFH番地まで指定できます。

- ★ しかし,プログラム・メモリが存在するのは0000H-1FFFH番地です。

- ★ したがって,アドレス・レジスタに設定する最大値は1FFFH番地までとしてください。

#### 5.4 ウインドウ・レジスタ (WR)

#### 5.4.1 ウインドウ・レジスタの構成

図5-4にウインドウ・レジスタの構成を示します。

図5 - 4に示すように, ウインドウ・レジスタはシステム・レジスタの78H番地(WR)の4ビットで構成されています。

アドレス 78H 名称 ウインドウ・レジスタ (WR) WR 記号 ビット рз  $b_2$  $b_0$ データ Μ S S В В 不定 保持 クロック・ストップ時

図5-4 ウインドウ・レジスタの構成

# 5.4.2 ウインドウ・レジスタの機能

ウインドウ・レジスタは後述するレジスタ・ファイル(RF)とのデータ転送に使用します。

レジスタ・ファイルとのデータ転送は専用命令である "PEEK WR, rf" および "POKE rf, WR" 命令により操作します (rf: レジスタ・ファイルのアドレス)。

次の(1)および(2)に,各命令を実行したときの動作を説明します。

"8. レジスタ・ファイル (RF) とコントロール・レジスタ"も参照してください。

# (1) "PEEK WR, rf"命令

"f"でアドレス指定されるレジスタ・ファイルの内容を, ウインドウ・レジスタに転送します。

#### (2) "POKE rf, WR "命令

ウインドウ・レジスタの内容を , " ff " でアドレス指定されるレジスタ・ファイルに転送します。

# 5.5 バンク・レジスタ (BANK)

## 5.5.1 パンク・レジスタの構成

図5-5に,バンク・レジスタの構成を示します。

図 5 - 5 に示すように , バンク・レジスタはシステム・レジスタの79H番地 (BANK) の 4 ビットで構成されています。

アドレス 79H バンク・レジスタ 名称 (BANK) BANK 記号 ビット Ьз b<sub>2</sub> **b**<sub>1</sub> **b**<sub>0</sub> データ L М S S В В リー セ RESET端子によるリセット 0 WDT&SPリセット 0 クロック・ストップ時 保持

図5-5 パンク・レジスタの構成

## 5.5.2 パンク・レジスタの機能

バンク・レジスタは,データ・メモリのバンクを指定します。

表5-1に,バンク・レジスタの値とデータ・メモリのバンク指定を示します。

バンク・レジスタはシステム・レジスタ上に存在しているため,現在指定されているバンクに関係なく書き換えることができます。

つまり、バンク・レジスタを操作する場合は、そのときのバンクの状態は関係ありません。

表5-1 データ・メモリのバンク指定

| バン | /ク・            | レジ             | スタ | データ・メモリの |

|----|----------------|----------------|----|----------|

|    | (BA            | NK)            |    | バンク      |

| bз | b <sub>2</sub> | b <sub>1</sub> | bo |          |

| 0  | 0              | 0              | 0  | BANK0    |

| 0  | 0              | 0              | 1  | BANK1    |

| 0  | 0              | 1              | 0  | BANK2    |

| 0  | 0              | 1              | 1  | BANK3    |

| 1  | 1              | 1              | 0  | BANK14   |

| 1  | 1              | 1              | 1  | BANK15   |

備考 BANK4からBANK14の00H-5BHまではありません。

注意 データ・メモリの実装領域は製品によって異なります。詳しくは"図4-2 データ・メモリの構成"を参照してください。

## 5.6 インデクス・レジスタ(IX)とデータ・メモリ・ロウ・アドレス・ポインタ(MP:メモリ・ポインタ)

#### 5.6.1 インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタの構成

図5-6に,インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタの構成を示します。

図 5 - 6 に示すように , インデクス・レジスタは , システム・レジスタの7AHの下位 3 ビット (IXH) と7BH, 7CH (IXM, IXL) の計11ビットからなるインデクス・レジスタ (IX) と , 7FH (PSW) の最下位ビットにあるインデクス・イネーブル・フラグ (IXE) から構成されています。

データ・メモリ・ロウ・アドレス・ポインタ (メモリ・ポインタ) は7AH (MPH) の下位 3 ビットと7BH (MPL) の計 7 ビットからなるデータ・メモリ・ロウ・アドレス・ポインタ (MP) と,7AH (MPH) の最上位ビットにあるデータ・メモリ・ロウ・アドレス・ポインタ・イネーブル・フラグ (メモリ・ポインタ・イネーブル・フラグ:MPE) から構成されています。

すなわちインデクス・レジスタの上位 7 ビットとデータ・メモリ・ロウ・アドレス・ポインタは共用していること になります。

図5-6 インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタの構成

アドレス 7AH 7BH 7CH 7EH

| アドレス               |             | 7                          | ΑН             |                |     | 71             | вн             |                |     | 70             | СН             |                |    | 71             | ΞH             |                |     | 71             | -H             |                |

|--------------------|-------------|----------------------------|----------------|----------------|-----|----------------|----------------|----------------|-----|----------------|----------------|----------------|----|----------------|----------------|----------------|-----|----------------|----------------|----------------|

| 名称                 |             |                            |                | イン             | /デク | ス・             | レジフ            | <b>スタ</b> (    | IX) |                |                |                |    |                |                | プロ・            | グラム | ゝ・ス            | テーク            | タス・            |

|                    |             | メ                          | モリ             | ・ポイ            | ンタ  | (MP            | ')             |                |     |                |                |                |    |                |                | ワー             | ド(P | SWC            | RD)            |                |

| 記号                 |             | ۱X                         | ΚH             |                |     | ۱>             | ΚM             |                |     | D              | ΚL             |                |    |                |                |                |     | PS             | SW             |                |

|                    |             | M                          | PH             |                |     | М              | PL             |                |     |                |                |                |    |                |                |                |     |                |                |                |

| ビット                | bз          | b <sub>2</sub>             | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| データ                | M<br>P<br>E | M<br>S<br>B<br>M<br>S<br>B |                | M              | Р   | Ľ              | X              | L<br>S<br>B    |     |                |                | L<br>S<br>B    |    |                |                |                |     |                |                | I<br>X<br>E    |

| リセ RESET端子によるリセット  |             | (                          | 0              |                |     |                | 0              |                |     |                | 0              |                |    |                |                |                |     |                |                | 0              |

| ット<br>時 WDT&SPリセット |             | (                          | 0              |                |     |                | 0              |                |     |                | 0              |                |    |                |                |                |     |                |                | 0              |

| クロック・ストップ時         |             | 保                          | 持              |                |     | 保              | 持              |                |     | 保              | 持              |                |    |                |                |                |     |                |                | 保              |

保:保持

43

#### 5.6.2 インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタの機能

インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタは , データ・メモリのアドレスを修飾します。 次の (1) および (2) に , それぞれの機能を示します。

また,インデクス・レジスタには," 1 " ずつインクリメントする専用命令("INC IX ")が用意されています。 アドレス修飾の詳細については," 7.ALU (Arithmetic Logic Unit) プロック " を参照してください。

# (1) インデクス・レジスタ(IX)

データ・メモリ操作命令を実行したときに,データ・メモリ・アドレスを,インデクス・レジスタの内容により修飾します。

ただし,IXEフラグが"1"にセットされているときのみ有効になります。

アドレス修飾の方法は,データ・メモリのバンクとロウ・アドレスおよびカラム・アドレスをインデクス・レジスタの内容とOR演算し,その演算結果(実アドレスと呼ぶ)で指定されるデータ・メモリに対して命令を実行します。

インデクス・レジスタによるアドレス修飾は,すべてのデータ・メモリ操作命令が対象になります。 また,次の命令は,インデクス・レジスタの修飾対象となりません。

| INC  | AR       | RORC  | r    |

|------|----------|-------|------|

| INC  | IX       | CALL  | addr |

| MOVT | DBF, @AR | CALL  | @AR  |

| PUSH | AR       | RET   |      |

| POP  | AR       | RETSK |      |

| PEEK | WR, rf   | RETI  |      |

| POKE | rf, WR   | El    |      |

| GET  | DBF, p   | DI    |      |

| PUT  | p, DBF   | STOP  | S    |

| BR   | addr     | HALT  | h    |

| BR   | @AR      | NOP   |      |

#### (2) データ・メモリ・ロウ・アドレス・ポインタ (MP)

ジェネラル・レジスタ間接転送命令( " MOV @r, m ", " MOV m, @r " ) を実行したときに , 間接転送先のアドレスを修飾します。

ただし, MPEフラグが"1"にセットされているときのみ有効になります。

アドレス修飾の方法は,間接転送先のバンクとロウ・アドレスを,データ・メモリ・ロウ・アドレス・ポインタの内容で置き換えます。

ジェネラル・レジスタ間接転送命令以外は、アドレス修飾の対象になりません。

# (3) インデクス・レジスタ・インクリメント命令("INCIX")

インデクス・レジスタの内容を"1"ずつインクリメントします。

インデクス・レジスタは,10ビットで構成されていますので,インデクス・レジスタの内容が"3FFH"のときに"INC IX"命令を実行すると, "000H"になります。

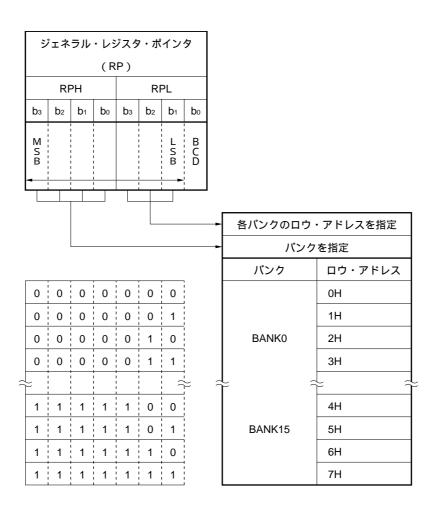

## 5.7 ジェネラル・レジスタ・ポインタ (RP)

# 5.7.1 ジェネラル・レジスタ・ポインタの構成

図5-7に,ジェネラル・レジスタ・ポインタの構成を示します。

図 5 - 7 に示すように , ジェネラル・レジスタ・ポインタはシステム・レジスタの7DH番地 (RPH) の 4 ビットと 7EH番地 (RPL) の上位 3 ビットの計 7 ビットで構成されています。

図5-7 ジェネラル・レジスタ・ポインタの構成

| _   |                |     |                |                |     |     |                |                |                |  |

|-----|----------------|-----|----------------|----------------|-----|-----|----------------|----------------|----------------|--|

|     | アドレス           |     | 7[             | DΗ             |     |     | 78             | ΞH             |                |  |

|     | 名称             | ジェ  | ネラノ            | レ・レ            | ジスケ | タ・オ | ペイン            | タ              |                |  |

|     |                | (RF | )              |                |     |     |                |                |                |  |

|     | 記号             |     | RI             | PH             |     |     | R              | PL             |                |  |

|     | ビット            | bз  | b <sub>2</sub> | b <sub>1</sub> | bo  | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |  |

|     | データ            | М   |                |                |     |     |                | L              | В              |  |

|     |                | S   |                |                |     |     |                | S              | С              |  |

|     |                | В   |                |                |     |     |                | В              | D              |  |

|     |                | -   |                |                |     |     |                | _              | i              |  |

| リセッ | RESET端子によるリセット |     | (              | 0              |     |     | (              | 0              |                |  |

| ット時 | WDT&SPリセット     |     | (              | 0              |     |     |                | 0              |                |  |

| ク   | ロック・ストップ時      |     | 保              | 持              |     | 保持  |                |                |                |  |

#### 5.7.2 ジェネラル・レジスタ・ポインタの機能

ジェネラル・レジスタ・ポインタは、データ・メモリ上のジェネラル・レジスタを指定します。

図5 - 8 に,ジェネラル・レジスタ・ポインタで指定されるジェネラル・レジスタのアドレスを示します。

図 5 - 8 に示すように,ジェネラル・レジスタ・ポインタの上位 4 ビット(RPH:7DH番地)でバンクを指定し, 下位 3 ビット(RPL:7EH番地)でロウ・アドレスを指定します。

ジェネラル・レジスタ・ポインタの有効ビットは 7 ビットであるため, すべてのバンクのすべてのロウ・アドレス (0H-7H番地)をジェネラル・レジスタに指定できます。

ジェネラル・レジスタの動作の詳細は, "6.ジェネラル・レジスタ(GR)"を参照してください。

図5-8 ジェネラル・レジスタ・ポインタで指定されるジェネラル・レジスタのアドレス

備考 BANK4からBANK14の5BHまではありません。

#### 5.7.3 ジェネラル・レジスタ・ポインタ使用時の注意

ジェネラル・レジスタ・ポインタであるアドレス7EH番地 (RPL)の最下位ビットは,プログラム・ステータス・ワードのBCDフラグに割り当てられています。

したがって, RPLを書き換える場合は, BCDフラグの値に注意してください。

и PD17934A

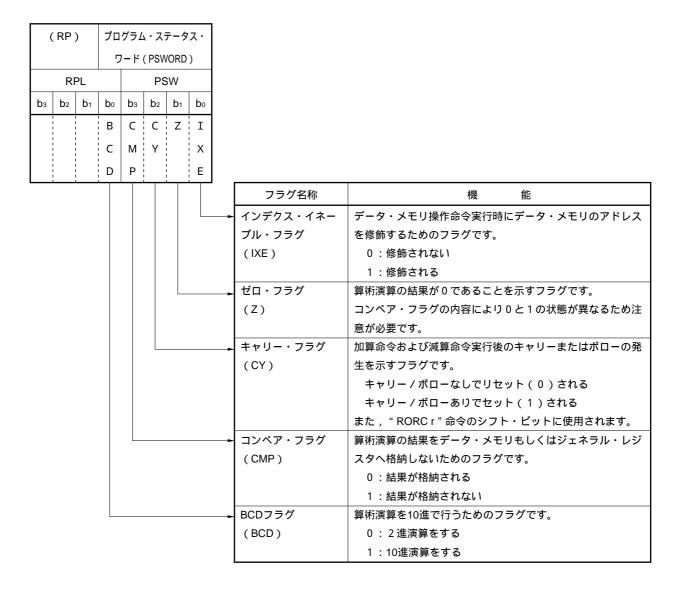

# 5.8 プログラム・ステータス・ワード (PSWORD)

# 5.8.1 プログラム・ステータス・ワードの構成

図5-9にプログラム・ステータス・ワードの構成を示します。

図5 - 9に示すように,プログラム・ステータス・ワードはシステム・レジスタの7EH番地(RPL)の最下位ビットと7FH番地(PSW)の4ビットの計5ビットで構成されています。

プログラム・ステータス・ワードはさらに 1 ビットずつ機能が分かれており,それぞれBCDフラグ(BCD),コンペア・フラグ(CMP),キャリー・フラグ(CY),ゼロ・フラグ(Z)およびインデクス・イネーブル・フラグ (IXE) から構成されています。

図5-9 プログラム・ステータス・ワードの構成

|       | アドレス           |    | 71             | <u></u>        |                |     | 71             | -H             |                |  |

|-------|----------------|----|----------------|----------------|----------------|-----|----------------|----------------|----------------|--|

|       | 名称             |    |                |                | プロ・            | グラム | ٠٨             | テーク            | タス・            |  |

|       |                |    |                |                | ワー             | ド(P | swc            | RD)            |                |  |

|       | 記号             |    | R              | PL             |                |     | PS             | SW             |                |  |

|       | ビット            | bз | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |  |

|       | データ            |    |                |                | В              | С   | С              | Z              | I              |  |

|       |                |    |                |                | С              | М   | Υ              |                | Х              |  |

|       |                |    |                |                | D              | Р   |                |                | Ε              |  |

|       |                |    |                |                | !<br>!<br>!    |     |                |                |                |  |

| リセ    | RESET端子によるリセット |    | (              | 0              |                |     | (              | 0              |                |  |

| リセット時 | WDT&SPリセット     |    |                | 0              |                |     |                | 0              |                |  |

| ク     | ロック・ストップ時      |    | 保              | 持              | 保持             |     |                |                |                |  |

#### 5.8.2 プログラム・ステータス・ワードの機能

プログラム・ステータス・ワードはALU(Arithmetic Logic Unit)での演算および転送命令の条件を設定したり演算 結果の状態を示すためのレジスタです。

表5-2に,プログラム・ステータス・ワードの各フラグの機能概要を示します。

詳しい動作については"7.ALU (Arithmetic Logic Unit)プロック"を参照してください。

表5-2 プログラム・ステータス・ワードの各フラグの機能概要

#### 5.8.3 プログラム・ステータス・ワード使用時の注意

プログラム・ステータス・ワードに対して算術演算(加算および減算)命令を行うと,算術演算の "結果"が格納されます。

たとえば,キャリーが発生するような演算を実行しても,算術演算の結果が0000BであればPSWには0000Bが格納されます。

#### 6.ジェネラル・レジスタ (GR)

#### 6.1 ジェネラル・レジスタ概要

図6-1に,ジェネラル・レジスタの概要を示します。

図6 - 1 に示すように,ジェネラル・レジスタはジェネラル・レジスタ・ポインタによって,データ・メモリ上に指定されます。

ジェネラル・レジスタを指定するバンクおよびロウ・アドレスは,ジェネラル・レジスタ・ポインタで設定します。 ジェネラル・レジスタは,データ・メモリ間で,データ転送や演算に使用します。

図6-1 ジェネラル・レジスタの概要

備考 BANK4からBANK14の5BHまではありません。

## 6.2 ジェネラル・レジスタ

ジェネラル・レジスタは,データ・メモリ上の同一ロウ・アドレスである16ニブル (16×4ビット)で構成されます。

ジェネラル・レジスタ・ポインタ,およびジェネラル・レジスタに指定できるバンクとロウ・アドレスの範囲については,"5.7 ジェネラル・レジスタ・ポインタ(RP)"を参照してください。

ジェネラル・レジスタに指定されている同一ロウ・アドレスの16二ブルは,データ・メモリとの間で演算や転送を1命令で行います。

つまり, 1命令でデータ・メモリ同士の演算や転送が可能になります。

ジェネラル・レジスタは,ほかのデータ・メモリと同様に,データ・メモリ操作命令で制御することができます。

#### 6.3 各命令におけるジェネラル・レジスタのアドレス生成

6.3.1 および 6.3.2 に各命令実行時のジェネラル・レジスタのアドレス生成を示します。

各命令の動作についての詳細は, "7.ALU (Arithmetic Logic Unit) プロック"を参照してください。

6.3.1 加算("ADD r, m", "ADDC r, m"), 減算("SUB r, m", "SUBC r, m"),

**論理演算 (** "AND r, m ", "OR r, m ", "XOR r, m "),

直接転送 ( "LD r, m ", "ST m, r " ) ,

回転処理 ( " RORC r " ) 命令

表 6-1 に , 命令のオペランド " r " で指定されるジェネラル・レジスタのアドレスを示します。命令のオペランド " r " は , カラム・アドレスのみを指定します。

|                 |                                 | バン             | ノク             |                | ロウ             | ・アド            | レス                    | カラ | 5Δ·            | アドレ            | ノス             |

|-----------------|---------------------------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----|----------------|----------------|----------------|

|                 | <b>b</b> 3                      | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | b <sub>2</sub> | b <sub>1</sub> | <b>b</b> <sub>0</sub> | bз | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| ジェネラル・レジスタ・アドレス | ジェ <sup>;</sup><br><del>-</del> | ネラル            | ・・レシ           | <b>ブ</b> スタ    | ・ポイ            | ンタの            | )内容                   | •  | !              | •              |                |

表 6 - 1 ジェネラル・レジスタのアドレス生成

## 6.3.2 間接転送 ( " MOV @r, m ", " MOV m, @r " ) 命令

表 6 - 2 に , 命令のオペランド " r " で指定されるジェネラル・レジスタのアドレスおよび " @ r " で指定される間接転送アドレスを示します。

|                 |     | バン             | ノク             |                | ロウ             | ・アド            | レス                  | カラ | ラム・            | アドレ            | ノス             |

|-----------------|-----|----------------|----------------|----------------|----------------|----------------|---------------------|----|----------------|----------------|----------------|

|                 | bз  | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | b <sub>2</sub> | b <sub>1</sub> | bo                  | bз | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| ジェネラル・レジスタ・アドレス | ジェニ | ネラル            | ・・レシ           | <b>ジスタ</b>     | ・ポイ            | ンタの            | )内容<br><del>-</del> | •  |                | r              | •              |

| 間接転送アドレス        | 4   | デ              | ータ・            | メモ             | リと同            | ]—             | _                   | 4  | rのI            | 内容             | •              |

表 6 - 2 ジェネラル・レジスタのアドレス生成

# 6.4 ジェネラル・レジスタ使用時の注意

#### 6.4.1 ジェネラル・レジスタのロウ・アドレス

ジェネラル・レジスタのロウ・アドレスは,ジェネラル・レジスタ・ポインタで指定されるため,現在指定されているバンクとジェネラル・レジスタのバンクが異なる場合があるので注意してください。

## 6.4.2 ジェネラル・レジスタとイミーディエト・データとの演算

ジェネラル・レジスタとイミーディエト・データとの演算命令はありません。

ジェネラル・レジスタとイミーディエト・データとの演算命令を行うためには,ジェネラル・レジスタではなく, データ・メモリとして扱う必要があります。

# 7 . ALU (Arithmetic Logic Unit) プロック

## 7.1 ALU**ブロック概要**

図7-1に,ALUブロックの概要を示します。

図 7 - 1 に示すように , ALUブロックは , ALU , 一時記憶レジスタ A , B , プログラム・ステータス・ワード , 10進補正回路およびデータ・メモリ・アドレス制御回路から構成されています。

ALUは,データ・メモリ上の4ビット・データの演算,判断,比較,回転および転送を行います。

データ・バス アドレス 一時記憶 一時記憶 プログラム・ 制御 レジスタA レジスタB ステータス・ワード キャリー / ボロー / ゼロ検出 インデクス修飾 10進 / 格納指定 メモリ・ポインタ ALU ・算術演算 ・論理演算 ・ビット判断 ・比較判断 ・回転処理 ・転送 データ・メモリ

10進補正

図7-1 ALU プロック概要

#### 7.2 各プロックの構成と機能

#### 7.2.1 ALU

ALUは,プログラムにより指定された命令により,4ビットの算術演算,論理演算,ビット判断,比較判断,回転処理および転送を行います。

#### 7.2.2 一時記憶レジスタAおよびB

一時記憶レジスタAおよびBは,A ビットのデータを一時的に蓄わえておくレジスタです。

このレジスタは、命令実行時に自動的に使用され、プログラムで制御することはできません。

#### 7.2.3 プログラム・ステータス・ワード

プログラム・ステータス・ワードは, ALUの動作制御, および状態を格納します。

プログラム・ステータス・ワードについては, " 5.8 プログラム・ステータス・ワード (PSWORD) "を参照してください。

# 7.2.4 10進補正回路

算術演算時に,プログラム・ステータス・ワードのBCDフラグが"1"にセットされていると,10進補正回路により算術演算結果を10進数に変換します。

#### 7.2.5 アドレス制御回路

アドレス制御回路は,データ・メモリのアドレスを指定します。

このとき,インデクス・レジスタやデータ・メモリ・ロウ・アドレス・ポインタによるアドレスの修飾も制御します。

# 7.3 ALU 処理命令一覧

表7-1に,各命令実行時のALU動作一覧を示します。

表7-2に,インデクス・レジスタとデータ・メモリ・ロウ・アドレス・ポインタによる,データ・メモリ・アドレスの修飾を示します。

表 7 - 3 に , 10進演算時の10進補正データを示します。

表7-1 ALU 処理命令動作一覧

| A    | 命    | 令      |      | プログラ       | ラム・ステータス・ワ | ード(PSWORD)に | こよる動作の違い        | アドレ   | ス修飾  |

|------|------|--------|------|------------|------------|-------------|-----------------|-------|------|

| lυ   |      |        | BCDフ | CMPフ       | 演算動作       | CYフラグの動作    | Zフラグの動作         | インデクス | メモリ・ |

| 機能   |      |        | ラグの値 | ラグの値       |            |             |                 |       | ポインタ |

| 加算   | ADD  | r, m   | 0    | 0          | 2 進演算      | キャリーまたはボ    | 演算の結果0000Bでセット  | あり    | なし   |

| **   |      | m, #n4 |      | <br>       | 結果を格納する    | ローでセット      | 0000B以外はリセット    |       |      |