## USB Charging Port Power Switch and Controller

## General Description

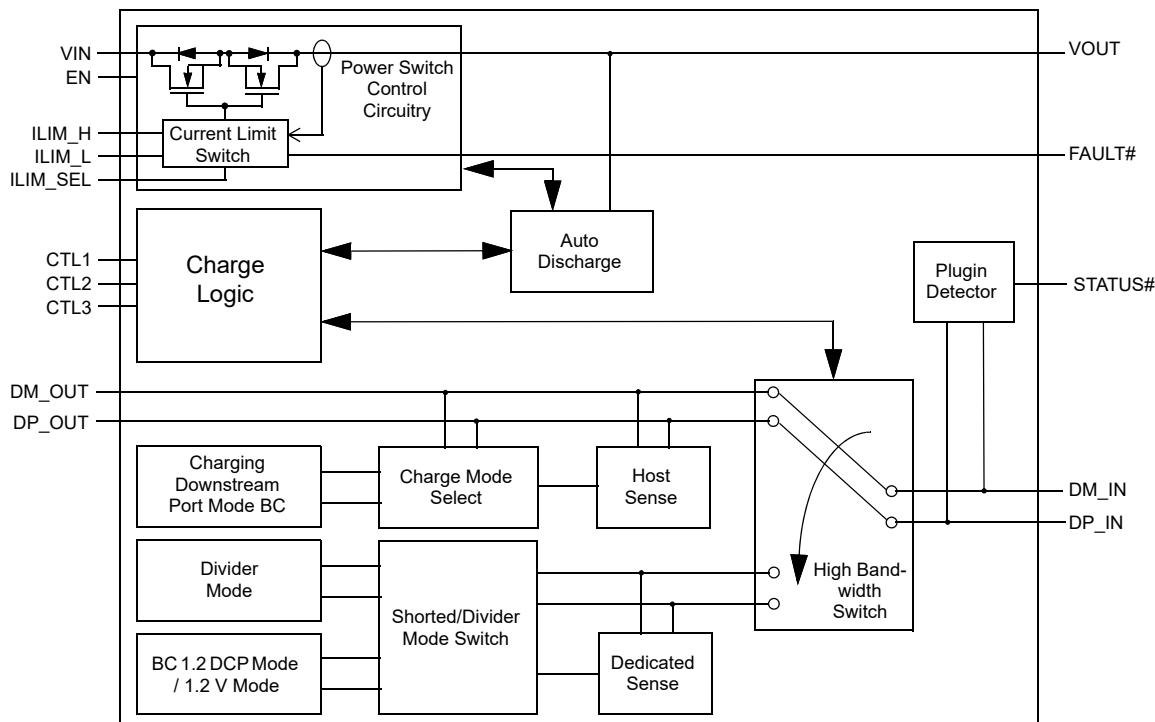

Renesas SLGC55546CV is a combination of current-limited USB port power switch with a USB 2.0 high-speed data line (D+/D-) switch and USB charging port identification circuit. Applications include notebook PCs and other intelligent USB host devices. The wide bandwidth (2.6 GHz) data-line switch also features low capacitance and low on resistance, allowing signals to pass with minimum edge and phase distortion. The SLGC55546CV monitors D+ and D-, providing the correct hand-shaking protocol with compliant client devices.

## Features

- Meets Battery Charging Specification BC1.2 for DCP and CDP

- Meets Chinese Telecommunications Industry Standard YD/T 1591-2009

- Supports Non-BC 1.2 charging modes via Automatic selection

- DM/DP Divider Modes 2.7 V/2.0 V (1A) & 2.0V/2.7V (2A)

- DM/DP 1.2 V Mode

- Support Smart-CDP function - Automatic CDP/SDP mode support for Always data Communication

- Compatible with USB 2.0/3.0 power switch requirements

- 73 mΩ (typ) high side MOSFET

- Adjustable Current Limit up to 3.0 A (typ)

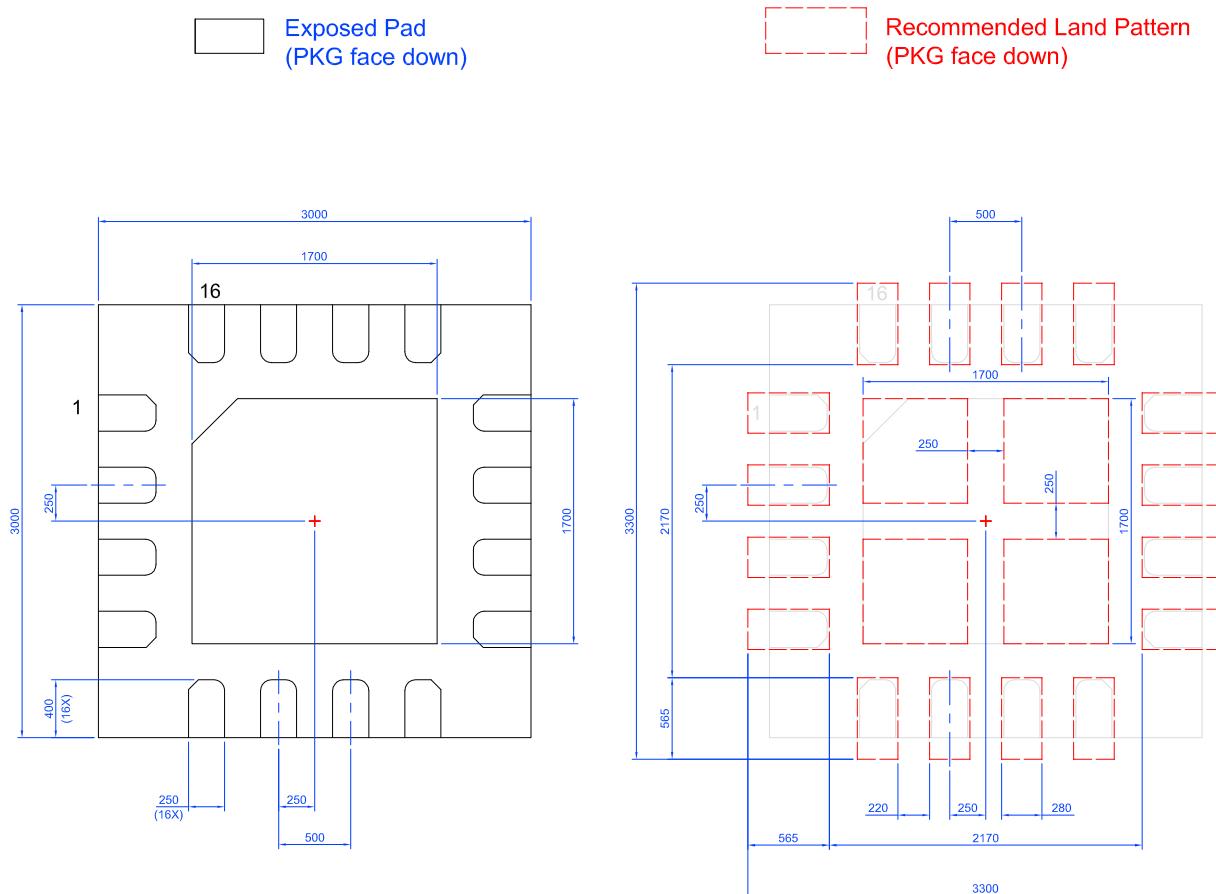

- Pb-Free / RoHS Compliant

- Halogen-Free

- TQFN-16 Package

- UL Listed and CB File No. E468659

## Block Diagram

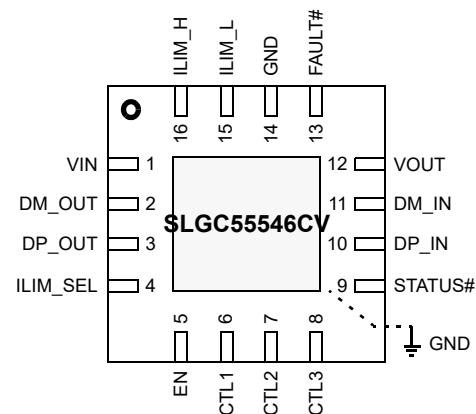

## Pin Configuration

16-pin TQFN

(Top View)

## Applications

- USB Ports/Hubs

- Notebook PCs

- Universal Wall Charging Adapter

**Pin Description**

| Pin # | Pin Name    | Type         | Pin Description                                                                                                                                                              |

|-------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN         | PWR          | Input voltage, connect a 0.1 $\mu$ F or greater ceramic capacitor from IN to GND as close to the device as possible                                                          |

| 2     | DM_OUT      | Input/Output | D- data line to USB host controller                                                                                                                                          |

| 3     | DP_OUT      | Input/Output | D+ data line to USB host controller                                                                                                                                          |

| 4     | ILIM_SEL    | Input        | Logic level input signal used to dynamically change power switch current-limit threshold; logic LOW selects ILIM_L, logic HIGH selects ILIM_H                                |

| 5     | EN          | Input        | Logic level control input for turning the power switch and the signal switches on/off. When EN is LOW, the device is disabled, the signal and power switches are OFF.        |

| 6     | CTL1        | Input        | Logic level control inputs for controlling the charging mode and the signal switches. The "000" configuration is used to force and discharge of the output (VOUT) capacitor. |

| 7     | CTL2        | Input        |                                                                                                                                                                              |

| 8     | CTL3        | Input        |                                                                                                                                                                              |

| 9     | STATUS#     | Output       | Active Low open drain output, asserted while charge limit occur by Power Wake or Port Power Management functions.                                                            |

| 10    | DP_IN       | Input/Output | D+ data line to connector, input/output used for hand-shaking with portable equipment                                                                                        |

| 11    | DM_IN       | Input/Output | D- data line to connector, input/output used for hand-shaking with portable equipment                                                                                        |

| 12    | VOUT        | PWR          | Power switch output                                                                                                                                                          |

| 13    | FAULT#      | Output       | Active low open drain output, asserted during over-temperature or current-limit conditions                                                                                   |

| 14    | GND         | GND          | Ground                                                                                                                                                                       |

| 15    | ILIM_L      | Input        | External resistor used to set current-limit threshold when ILIM_SEL is LOW. See current limit setting in detailed description.                                               |

| 16    | ILIM_H      | Input        | External resistor used to set current-limit threshold when ILIM_SEL is HIGH. See current limit setting in detailed description.                                              |

| --    | Thermal Pad | GND          | Ground                                                                                                                                                                       |

**Ordering Information**

| Part Number   | Type                    | Production Flow             |

|---------------|-------------------------|-----------------------------|

| SLGC55546CV   | TQFN-16                 | Industrial, -40 °C to 85 °C |

| SLGC55546CVTR | TQFN-16 - Tape and Reel | Industrial, -40 °C to 85 °C |

## Absolute Maximum Ratings

| Parameter                             | Description                                                       | Min.               | Max.           | Unit |

|---------------------------------------|-------------------------------------------------------------------|--------------------|----------------|------|

| Supply Voltage range                  | VIN                                                               | -0.3               | 7              | V    |

| Input Voltage range                   | EN, ILIM_L, ILIM_H, ILIM_SEL, CTL1, CTL2, CTL3                    | -0.3               | 7              | V    |

| Output Voltage range                  | VOUT, FAULT#, STATUS# <sup>2</sup>                                | -0.3               | 7              | V    |

| Output Voltage range                  | VIN to VOUT                                                       | -7                 | 7              | V    |

| Voltage range                         | DP_IN, DM_IN, DP_OUT, DM_OUT                                      | -0.3               | VIN+0.3 or 5.7 | V    |

| Input Clamp current                   | DP_IN, DM_IN, DP_OUT, DM_OUT                                      | --                 | ±20            | mA   |

| Continuous current in SDP or CDP mode | DP_IN to DP_OUT or DM_IN to DM_OUT                                | --                 | ±100           | mA   |

| Continuous current in BC1.2 DCP mode  | DP_IN to DM_IN                                                    | --                 | ±35            | mA   |

| Continuous output current             |                                                                   | Internally limited |                |      |

| Continuous output sink current        | FAULT#, STATUS#                                                   | --                 | 25             | mA   |

| Continuous output source current      | ILIM_L, ILIM_H                                                    | --                 | 1              | mA   |

| Continuous total power dissipation    |                                                                   | Internally limited |                |      |

| ESD Rating, Human Body Model (HBM)    | VIN, EN, ILIM_L, ILIM_H, ILIM_SEL, CTL1, CTL2, CTL3, VOUT, FAULT# | 2                  | --             | kV   |

| ESD Rating, Human Body Model (HBM)    | DP_IN, DM_IN, DP_OUT, DM_OUT                                      | 8                  | --             | kV   |

| ESD Rating, Charged Device Model      |                                                                   | 500                | --             | V    |

| Operating Temperature Range           |                                                                   | -40                | 85             | °C   |

| Storage Temperature Range             |                                                                   | -65                | 165            | °C   |

## Note:

1. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. Do not apply external voltage sources directly

Thermal Information <sup>1</sup>

| Parameter        |                                                           | Typ. | Unit |

|------------------|-----------------------------------------------------------|------|------|

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>2</sup>       | 53.4 | °C/W |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>3</sup>    | 51.4 | °C/W |

| $\theta_{JB}$    | Junction-to-board thermal resistance <sup>4</sup>         | 17.2 | °C/W |

| $\psi_{JT}$      | Junction-to-top characterization parameter <sup>5</sup>   | 3.7  | °C/W |

| $\psi_{JB}$      | Junction-to-board characterization parameter <sup>6</sup> | 20.7 | °C/W |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>7</sup> | 3.9  | °C/W |

## Note:

1. For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

2. The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

3. The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

4. The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

5. The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

6. The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

7. The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## Electrical Characteristics

Conditions are  $-40 \leq T_J \leq 125$  °C unless otherwise noted.  $V_{EN} = V_{IN} = 5$  V,  $R_{FAULT\#} = R_{STATUS\#} = 10$  kΩ,  $R_{ILIM\_L} = 80$  kΩ,  $R_{ILIM\_H} = 20$  kΩ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $CTL1 = CTL2 = CTL3 = V_{IN}$ , unless otherwise noted. Positive currents are into pins. Typical values are at 25 °C. All voltages are with respect to GND unless otherwise noted.

## Electrical Characteristics - Power Switch

| Symbol                 | Parameter                                            | Condition/Note                                                                              | Min. | Typ. | Max. | Unit |

|------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

| R <sub>DS ON</sub>     | Static drain-source on-state resistance <sup>1</sup> | $I_{OUT} = 100$ mA, $V_{ILIM\_SEL} = \text{Logic Low}$                                      | --   | 73   | --   | mΩ   |

|                        |                                                      | $T_A = T_J = 25$ °C, $I_{OUT} = 2$ A, $V_{ILIM\_SEL} = \text{Logic High}$                   | --   | 73   | 84   | mΩ   |

|                        |                                                      | $-40$ °C $\leq T_A = T_J \leq 85$ °C, $I_{OUT} = 2$ A, $V_{ILIM\_SEL} = \text{Logic High}$  | --   | 73   | 105  | mΩ   |

|                        |                                                      | $-40$ °C $\leq T_A = T_J \leq 125$ °C, $I_{OUT} = 2$ A, $V_{ILIM\_SEL} = \text{Logic High}$ | --   | 73   | 120  | mΩ   |

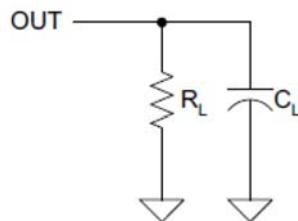

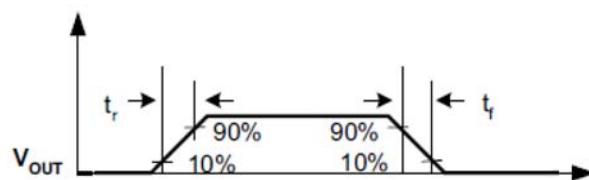

| T <sub>R</sub>         | Rise Time, Output                                    | $C_{LOAD} = 1$ μF, $R_{LOAD} = 100$ Ω                                                       | 0.7  | 1.50 | 1.6  | ms   |

| T <sub>F</sub>         | Fall Time, Output                                    | $C_{LOAD} = 1$ μF, $R_{LOAD} = 100$ Ω                                                       | 0.2  | 0.35 | 0.5  | ms   |

| R <sub>DIS</sub>       | V <sub>OUT</sub> Discharge Resistance                |                                                                                             | 337  | 498  | 681  | Ω    |

| T <sub>DIS</sub>       | Out Discharge Hold Time                              |                                                                                             | --   | 2    | --   | s    |

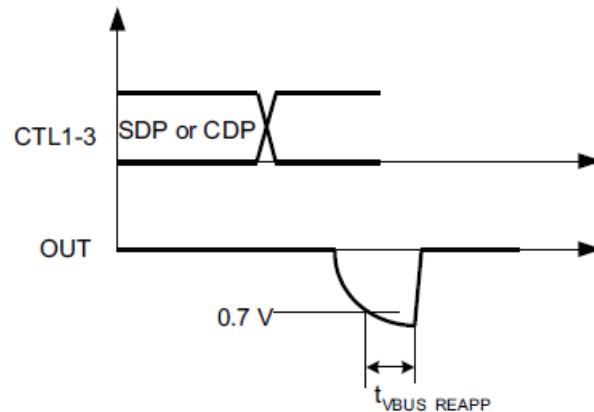

| T <sub>DIS_LONG</sub>  | Long Out Discharge Hold Time <sup>2</sup>            | Time $V_{OUT} < 0.7$ V                                                                      | 1    | 2    | 3    | s    |

| T <sub>DIS_SHORT</sub> | Short Out Discharge Hold Time <sup>2</sup>           | Time $V_{OUT} < 0.7$ V                                                                      | 150  | 250  | 400  | ms   |

| I <sub>REV</sub>       | Reverse Leakage Current                              | $V_{OUT} = 5.5$ V, $V_{IN} = V_{EN} = 0$ V, $T_J = 25$ °C                                   | --   | --   | 2    | μA   |

## Electrical Characteristics - Input EN

| Symbol        | Parameter                                 | Condition/Note                                    | Min. | Typ.             | Max. | Unit          |

|---------------|-------------------------------------------|---------------------------------------------------|------|------------------|------|---------------|

| $V_{EN}$      | Enable pin Turn on/off Threshold, falling |                                                   | --   | 1.08             | --   | V             |

| $V_{EN\_HYS}$ | EN Hysteresis                             |                                                   | --   | 230 <sup>1</sup> | --   | mV            |

|               | Input Current                             | $V_{EN} = 0 \text{ V or } 5.5 \text{ V}$          | -0.5 | --               | 0.5  | $\mu\text{A}$ |

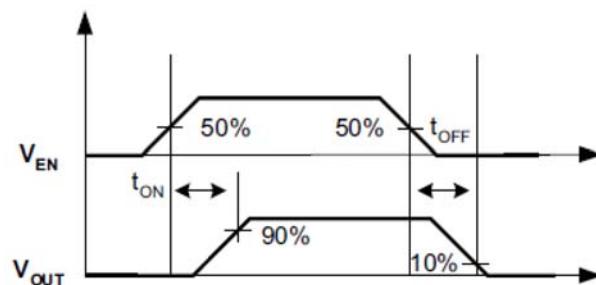

| $T_{ON}$      | Turn On Time                              | $C_{LOAD} = 1 \mu\text{F}, R_{LOAD} = 100 \Omega$ | --   | 2.7              | 4.0  | ms            |

| $T_{OFF}$     | Turn Off Time                             | $C_{LOAD} = 1 \mu\text{F}, R_{LOAD} = 100 \Omega$ | --   | 1.7              | 3.0  | ms            |

Note: 1. Typical value for reference only, not 100% tested.

## Electrical Characteristics - Current Limit

| Symbol          | Parameter                                  | Condition/Note                                                                                                               | Min.  | Typ.              | Max.  | Unit          |

|-----------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|-------|---------------|

| $V_{ILIM\_SEL}$ | ILIM_SEL turn on/off threshold, falling    |                                                                                                                              | --    | 1.08              | --    | V             |

| $V_{ILIM\_HYS}$ | ILIM_SEL Hysteresis                        |                                                                                                                              | --    | 230 <sup>1</sup>  | --    | mV            |

| $I_{EN}$        | ILIM_SEL Input Current                     | $V_{ILIM\_HYS} = 0 \text{ V or } 5.5 \text{ V}$                                                                              | -0.5  | --                | 0.5   | $\mu\text{A}$ |

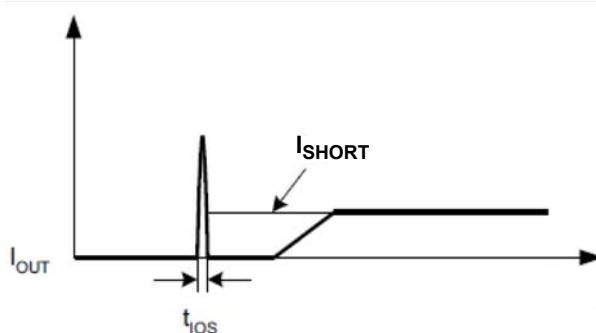

| $I_{SHORT}$     | Maximum DC Output Current from VIN to VOUT | $V_{ILIM\_SEL} = \text{Logic Low}$<br>$R_{ILIM\_L} = 210 \text{ k}\Omega$                                                    | 0.22  | 0.26              | 0.30  | A             |

|                 |                                            | $V_{ILIM\_SEL} = \text{Logic Low}$<br>$R_{ILIM\_L} = 80.6 \text{ k}\Omega, -40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ | 0.60  | 0.66              | 0.72  | A             |

|                 |                                            | $V_{ILIM\_SEL} = \text{Logic Low}$<br>$R_{ILIM\_L} = 22.1 \text{ k}\Omega$                                                   | 2.120 | 2.275             | 2.430 | A             |

|                 |                                            | $V_{ILIM\_SEL} = \text{Logic High}$<br>$R_{ILIM\_H} = 20 \text{ k}\Omega$                                                    | 2.340 | 2.510             | 2.685 | A             |

|                 |                                            | $V_{ILIM\_SEL} = \text{Logic High}$<br>$R_{ILIM\_H} = 16.9 \text{ k}\Omega$                                                  | 2.77  | 2.97              | 3.17  | A             |

| $T_{Ios}$       | Response Time to Short Circuit             | $V_{IN} = 5 \text{ V}$                                                                                                       | --    | 6.65 <sup>1</sup> | --    | $\mu\text{s}$ |

Note: 1. Typical value for reference only, not 100% tested.

## Electrical Characteristics - Supply Current

| Symbol    | Parameter                       | Condition/Note                                                                                     | Min. | Typ. | Max. | Unit          |

|-----------|---------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $I_{CCL}$ | Supply Current, switch disabled | $V_{EN} = 0 \text{ V}, V_{OUT} \text{ grounded}, -40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ | --   | 0.1  | 2    | $\mu\text{A}$ |

| $I_{CCH}$ | Supply Current, operating       | $V_{EN} = V_{IN}$                                                                                  | --   | 215  | 270  | $\mu\text{A}$ |

## Electrical Characteristics - Undervoltage Lockout

| Symbol        | Parameter                   | Condition/Note  | Min. | Typ.             | Max. | Unit |

|---------------|-----------------------------|-----------------|------|------------------|------|------|

| $V_{UVLO}$    | Low level input voltage, IN | $V_{IN}$ rising | 3.9  | 4.1              | 4.3  | V    |

| $V_{IN\_HYS}$ | Hysteresis, IN              |                 |      | 100 <sup>1</sup> |      | mV   |

Note: 1. Typical value for reference only, not 100% tested.

## Electrical Characteristics - FAULT#

| Symbol     | Parameter                  | Condition/Note                                                 | Min. | Typ. | Max. | Unit          |

|------------|----------------------------|----------------------------------------------------------------|------|------|------|---------------|

| $V_{OL}$   | Output Low voltage, FAULT# | $I_{FAULT\#} = 1 \text{ mA}$                                   | --   | --   | 100  | mV            |

| $I_{LEAK}$ | Off-state Leakage          | $V_{FAULT\#} = 5.5 \text{ V}$                                  | --   | --   | 1    | $\mu\text{A}$ |

|            | FAULT# Deglitch            | FAULT# assertion or de-assertion due to over-current condition | --   | 8.6  | --   | ms            |

## Electrical Characteristics - CTL Inputs

| Symbol         | Parameter                               | Condition/Note                            | Min. | Typ.             | Max. | Unit          |

|----------------|-----------------------------------------|-------------------------------------------|------|------------------|------|---------------|

| $V_{CTL}$      | CTL pins turn on/off threshold, falling |                                           | --   | 1.08             | --   | V             |

| $V_{CTL\_HYS}$ | Hysteresis, CTL                         |                                           | --   | 230 <sup>1</sup> | --   | mV            |

|                | Input Current                           | $V_{CTL} = 0 \text{ V or } 5.5 \text{ V}$ | -0.5 | --               | 0.5  | $\mu\text{A}$ |

Note: 1. Typical value for reference only, not 100% tested.

## Electrical Characteristics - Thermal Shutdown

| Symbol | Parameter                                   | Condition/Note | Min. | Typ.            | Max. | Unit |

|--------|---------------------------------------------|----------------|------|-----------------|------|------|

|        | Thermal shutdown threshold                  |                | 155  | --              | --   | °C   |

|        | Thermal shutdown threshold in current-limit |                | 135  | --              | --   | °C   |

|        | Hysteresis                                  |                |      | 20 <sup>1</sup> |      | °C   |

Note: 1. Typical value for reference only, not 100% tested.

## Electrical Characteristics - Analog Switch

$V_{IN} = 5.0 \text{ V}$ ,  $T_A = 25 \text{ }^\circ\text{C}$  (unless specified otherwise)

| Symbol                             | Parameter                                                    | Condition/Note                                                                                                                                                                 | Min. | Typ. | Max.     | Unit     |

|------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|----------|

| $V_{DP\_IN}, V_{DM\_IN}$           | Analog signal Range                                          |                                                                                                                                                                                | 0    | --   | $V_{DD}$ | V        |

| $R_{ON}$                           | On Resistance DP_OUT/DM_OUT Switch                           | $V_{DP/DM\_OUT} = 0 \text{ V}$ ,<br>$I_{DP/DM\_IN} = 30 \text{ mA}$                                                                                                            | --   | 2    | 4        | $\Omega$ |

|                                    |                                                              | $V_{DP/DM\_OUT} = 2.4 \text{ V}$ ,<br>$I_{DP/DM\_IN} = -15 \text{ mA}$                                                                                                         | --   | 3    | 6        | $\Omega$ |

| $\Delta R_{ON}$                    | On Resistance Mismatch between channels DP_OUT/DM_OUT Switch | $V_{IN} = 5 \text{ V}$<br>$V_{DP\_IN} = V_{DM\_IN} = 400 \text{ mV}$<br>$I_{DP\_IN} = I_{DM\_IN} = 10 \text{ mA}$                                                              | --   | 0.1  | --       | $\Omega$ |

| $R_{FLAT}$                         | On Resistance flatness DP_OUT/DM_OUT Switch                  | $V_{IN} = 5.0 \text{ V}$<br>$V_{DP\_IN} = V_{DM\_IN} = 0 \text{ V to } V_{IN}$<br>$I_{DP\_IN} = I_{DM\_IN} = 10 \text{ mA}$                                                    | --   | 0.5  | --       | $\Omega$ |

| $R_{SHORT}$                        | On Resistance of DP_OUT/DM_OUT Short                         | $V_{CB} = 0 \text{ V}$<br>$V_{DP\_IN} = 1 \text{ V}$<br>$I_{DP\_IN} = I_{DM\_IN} = 10 \text{ mA}$                                                                              | --   | 100  | 150      | $\Omega$ |

| $I_{DP\_OUT\_OFF}, I_{DM\_OUTOFF}$ | Off-Leakage Current                                          | $V_{IN} = 3.6 \text{ V}$<br>$V_{DP\_IN} = V_{DM\_IN} = 0.3 \text{ V to } 3.3 \text{ V}$<br>$V_{DP\_OUT} = V_{DM\_OUT} = 3.3 \text{ V to } 0.3 \text{ V}, V_{EN} = 0 \text{ V}$ | -250 | --   | 250      | nA       |

## Electrical Characteristics - Analog Switch

$V_{IN} = 5.0 \text{ V}$ ,  $T_A = 25 \text{ }^\circ\text{C}$  (unless specified otherwise)

| Symbol                                   | Parameter           | Condition/Note                                                                                                | Min. | Typ. | Max. | Unit |

|------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $I_{DP\_IN\_OFF}$ ,<br>$I_{DM\_IN\_OFF}$ | Off-Leakage Current | $V_{IN} = 3.6 \text{ V}$<br>$V_{DP\_IN} = V_{DM\_IN} = 3.3 \text{ V}$ to $0.3 \text{ V}$<br>$V_{EN} = V_{IN}$ | -250 | --   | 250  | nA   |

## Electrical Characteristics - Dynamic Performance

$V_{DD} = 5.0 \text{ V}$ ,  $T_A = 25 \text{ }^\circ\text{C}$  (unless specified otherwise)

| Symbol             | Parameter                              | Condition/Note                                                                                                 | Min. | Typ. | Max. | Unit          |

|--------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $T_{ON}$           | Turn On Time                           | $V_{DP\_OUT} \text{ or } V_{DM\_OUT} = 1.5 \text{ V}$<br>$R_{LOAD} = 300 \Omega$<br>$C_{LOAD} = 35 \text{ pF}$ | --   | 20   | 100  | $\mu\text{s}$ |

| $T_{OFF}$          | Turn Off Time                          | $V_{DP\_OUT} \text{ or } V_{DM\_OUT} = 1.5 \text{ V}$<br>$R_{LOAD} = 300 \Omega$<br>$C_{LOAD} = 35 \text{ pF}$ | --   | 1    | 5    | $\mu\text{s}$ |

| $T_{PLH}, T_{PHL}$ | DP_OUT/DM_OUT Switch Propagation Delay | $R_{LOAD} = R_S = 50 \Omega$                                                                                   | --   | 60   | --   | $\mu\text{s}$ |

| $T_{SKEW}$         | Output Skew                            | Skew between DP_IN and DM_IN when connected to DP_OUT and DM_OUT<br>$R_{LOAD} = R_S = 50 \Omega$               | --   | 40   | --   | $\text{ps}$   |

| $C_{OFF}$          | DP_OUT/DM_OUT Off-Capacitance          | $f = 1 \text{ MHz}$                                                                                            | --   | 2.0  | --   | $\text{pF}$   |

| $C_{ON}$           | DP_IN/DM_IN On-Capacitance             | $f = 240 \text{ MHz}$                                                                                          | --   | 4.0  | 5.5  | $\text{pF}$   |

| BW                 | -3dB Bandwidth                         | $R_{LOAD} = R_S = 50 \Omega$                                                                                   | --   | 1000 | --   | $\text{MHz}$  |

| $V_{ISO}$          | Off-Isolation                          | $V_{DP\_OUT}, V_{DP\_IN} = 0 \text{ dBm}$<br>$R_{LOAD} = R_S = 50 \Omega$<br>$f = 250 \text{ MHz}$             | --   | -20  | --   | $\text{dB}$   |

| $V_{CT}$           | Crosstalk                              | $V_{DP\_OUT}, V_{DP\_IN} = 0 \text{ dBm}$<br>$R_{LOAD} = R_S = 50 \Omega$<br>$f = 250 \text{ MHz}$             | --   | -25  | --   | $\text{dB}$   |

## Parameter Measurement Information

## Test Circuit

## Voltage Waveform

## Voltage Waveforms

## Response Time to Short-Circuit Waveforms

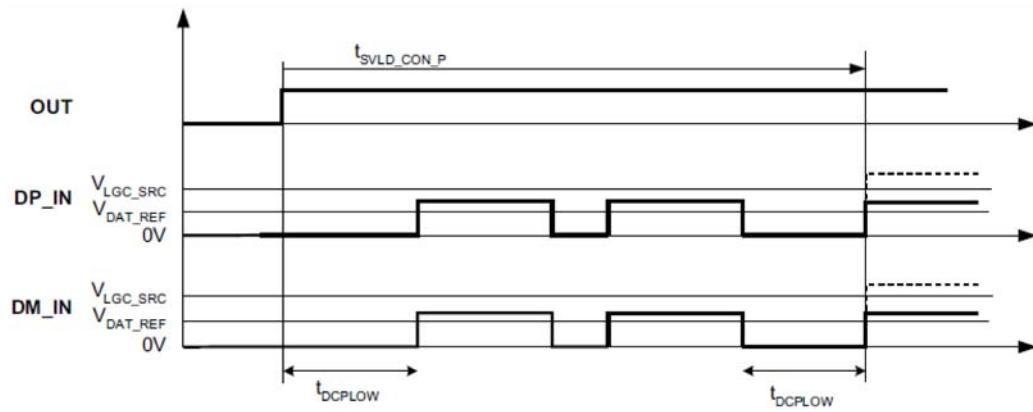

## DCP BC1.2 Operation

## VOUT Discharge During CTL Lines Change

## Overview

The following overview references various industry standards. It is always recommended to consult the most up-to-date standard to ensure the most recent and accurate information. Rechargeable portable equipment requires an external power source to charge its batteries. USB ports are a convenient location for charging because of an available 5 V power source. Universally accepted standards are required to make sure host and client-side devices operate together in a system to ensure power management requirements are met. Traditionally, USB host ports following the USB 2.0 specification must provide at least 500 mA to downstream client-side devices. Because multiple USB devices can be attached to a single USB port through a bus-powered hub, it is the responsibility of the client-side device to negotiate its power allotment from the host to ensure the total current draw does not exceed 500 mA. In general, each USB device is granted 100 mA and may request more current in 100 mA unit steps up to 500 mA. The host may grant or deny based on the available current.

Additionally, the success of USB has made the mini-USB connector a popular choice for wall adapter cables. This allows a portable device to charge from both a wall adapter and USB port with only one connector. One common difficulty has resulted from this. As USB charging has gained popularity, the 500 mA minimum defined by USB 2.0 has become insufficient for many handset and personal media players which need a higher charging rate. On the other hand, wall adapters can provide much more current than 500 mA. Several new standards have been introduced defining protocol handshaking methods that allow host and client devices to acknowledge and draw additional current beyond the 500 mA minimum defined by USB 2.0 while still using a single micro-USB input connector.

The SLGC55546CV supports three of the most common protocols:

- USB 2.0 Battery Charging Specification BC1.2

- Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider Mode

All three methods have similarities and differences, but the biggest commonality is that all three define three types of charging ports that provide charging current to client-side devices. These charging ports are defined as:

- Standard Downstream Port (SDP)

- Charging Downstream Port (CDP)

- Dedicated Charging Port (DCP)

BC1.2 defines a Charging Port as a downstream facing USB port that provides power for charging portable equipment.

The table below shows the differences between these ports according to BC1.2 (draft).

## Operating Modes

| Port Type     | Supports USB 2.0 Communication | Maximum Allowable Current Draw By Portable Equipment (A) |

|---------------|--------------------------------|----------------------------------------------------------|

| SDP (USB 2.0) | Yes                            | 0.5                                                      |

| SDP (USB 3.0) | Yes                            | 0.9                                                      |

| CDP           | Yes                            | 1.5                                                      |

| DCP           | No                             | 1.5                                                      |

BC1.2 (draft) defines the protocol necessary to allow portable equipment to determine what type of port it is connected to so that it can allot its maximum allowable current draw. The hand-shaking process has two steps. During step one, the primary detection, the portable equipment outputs a nominal 0.6-V output on its D+ line and reads the voltage input on its D- line. The portable device concludes it is connected to an SDP if the voltage is less than the nominal data detect voltage of 0.3 V. The portable device concludes that it is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3 V and less than 0.8 V. The second step, the secondary detection, is necessary for portable equipment to determine between a CDP and a DCP. The portable device outputs a nominal 0.6 V output on its D- line and reads the voltage input on its D+ line. The portable device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect voltage of 0.3 V. The portable device concludes it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3 V and less than 0.8 V.

### Standard Downstream Port (SDP)

An SDP is a traditional USB port that follows USB 2.0/3.0 and supplies a maximum of 500 mA per port for USB 2.0 and 900 mA per port for USB 3.0. USB 2.0 communications is supported, and the host controller must be active to allow charging.

### Charging Downstream Port (CDP)

A CDP is a USB port that follows USB 2.0/3.0 BC1.2 (draft) and supplies a minimum of 1.5 A per port. It provides power and meets USB 2.0/3.0 requirements for device enumeration. USB 2.0/3.0 communications is supported, and the host controller must be active to allow charging. What separates a CDP from an SDP is the host-charge handshaking logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 (draft) client device and allows for additional current draw by the client device.

The CDP hand-shaking process is two steps. During step one the portable equipment outputs a nominal 0.6 V output on its D+ line and reads the voltage input on its D- line. The portable device concludes it is connected to an SDP if the voltage is less than the nominal data detect voltage of 0.3 V. The portable device concludes that it is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3V and less than 0.8 V.

The second step is necessary for portable equipment to determine between a CDP and a DCP. The portable device outputs a nominal 0.6 V output on its D- line and reads the voltage input on its D+ line. The portable device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect voltage of 0.3 V. The portable device concludes it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3 V and less than 0.8 V.

### Dedicated Charging Port (DCP)

A DCP is a special type of wall-adapter used in charging applications that uses a micro-B connector to connect to portable devices. A DCP only provides power and does not support data connection to an upstream port. As shown in following sections, a DCP is identified by the electrical characteristics of its data lines. The SLGC55546CV emulates DCP in two charging states, namely DCP Forced and DCP Auto. In DCP Forced state the device will support one of the following two DCP charging schemes: Divider1 or Shorted. In DCP Auto state, the SLGC55546CV charge detection state machine is enabled which will selectively implement charging schemes involved with the Shorted, Divider1, Divider2, and 1.2 V modes.

Shorted DCP mode complies with BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, Divider and 1.2V modes are used to charge devices that do not comply with BC1.2 DCP standard.

### High-Bandwidth Data Line Switch

The SLGC55546CV passes the D+ and D- data lines through the device to enable monitoring and handshaking while supporting charging operation. A wide bandwidth signal switch is used, allowing data to pass through the device without corrupting signal integrity. The data line switches are turned on in any of CDP or SDP operating modes. The EN input also needs to be at logic High for the data line switches to be enabled.

Note:

1. While in CDP mode, the data switches are ON even while CDP handshaking is occurring.

2. The data line switches are OFF if EN is low, or if in DCP mode (BC1.2 (draft), Divider mode or Auto-detect). They are not automatically turned off if the power switch (VIN to VOUT) is doing current limiting. With SLGC55546CV, the data line switches are also off when in "000" mode.

3. The data switches are for USB 2.0 differential pair only. In the case of a USB 3.0 host, the super speed differential pairs must be routed directly to the USB connector without passing through the SLGC55546CV.

### Logic Control Modes

The SLGC55546CV supports the listed standards above for the SDP, CDP and DCP modes using the CTL1, CTL2, and CTL3 logic I/O control pins, although their truth tables are different as shown below. The different CTLx settings correspond to the different types of charge modes. Also, using the Auto-Detect Mode, the Divider Mode or BC1.2 (draft) / YD/T 1591-2009 can be automatically selected without external user interaction

Note:

With the SLGC55546CV, if the "000" mode is selected, the power switch will be turned off and an output discharge resistor will be connected, while the data line switches will be turned off.

## SLGC55546CV Control Truth Table

| CTL1 | CTL2 | CTL3 | ILIM_SEL | MODE              | Current Limit Settings             | Status Output                 | Note                                                            |

|------|------|------|----------|-------------------|------------------------------------|-------------------------------|-----------------------------------------------------------------|

| 0    | 0    | 0    | 0        | Discharge         | N/A                                | OFF                           | Output held LOW                                                 |

| 0    | 0    | 0    | 1        | Discharge         | N/A                                | OFF                           | Output held LOW                                                 |

| 0    | 0    | 1    | 0        | DCP Auto          | ILIM_H                             | OFF                           | Data Lines Disconnected                                         |

| 0    | 0    | 1    | 1        | DCP Auto          | $I_{OS\_PW}$ & ILIM_H <sup>1</sup> | DCP Load Present <sup>2</sup> | Data Lines Disconnected & Power Wake Function Active            |

| 0    | 1    | 0    | 0        | SDP1              | ILIM_L                             | OFF                           | Data Lines Connected                                            |

| 0    | 1    | 0    | 1        | SDP1              | ILIM_H                             | OFF                           | Data Lines Connected                                            |

| 0    | 1    | 1    | 0        | DCP Auto          | ILIM_H                             | OFF                           | Data Lines Disconnected                                         |

| 0    | 1    | 1    | 1        | DCP Auto          | ILIM_H                             | DCP Load Present <sup>3</sup> | Data Lines Disconnected & Port Power Management Function Active |

| 1    | 0    | 0    | 0        | DCP Shorted       | ILIM_L                             | OFF                           | Device forced to stay in DCP BC 1.2 charging mode               |

| 1    | 0    | 0    | 1        | DCP Shorted       | ILIM_H                             | OFF                           | Device forced to stay in DCP BC 1.2 charging mode               |

| 1    | 0    | 1    | 0        | DCP / Divider1    | ILIM_L                             | OFF                           | Device forced to stay in DCP Divider1 charging mode             |

| 1    | 0    | 1    | 1        | DCP / Divider1    | ILIM_H                             | OFF                           | Device forced to stay in DCP Divider1 charging mode             |

| 1    | 1    | 0    | 0        | SDP1              | ILIM_L                             | OFF                           | Data Lines Connected                                            |

| 1    | 1    | 0    | 1        | SDP1              | ILIM_H                             | OFF                           | Data Lines Connected                                            |

| 1    | 1    | 1    | 0        | SDP2 <sup>4</sup> | ILIM_L                             | OFF                           | Data Lines Connected                                            |

| 1    | 1    | 1    | 1        | CDP <sup>4</sup>  | ILIM_H                             | CDP Load Present <sup>5</sup> | Data Lines Connected & Port Power Management Active             |

## Notes:

1. Current Limit ( $I_{OS}$ ) is automatically switched between  $I_{OS\_PW}$  and the value set by ILIM\_H according to the Power Wake Functionality.

2. DCP Load present governed by the “Power Wake” limits.

3. DCP Load present governed by the “Non-Power Wake” limits.

4. No VOUT discharge when charging between 1111 and 1110.

5. CDP Load present governed by the “Non-Power Wake” limits and SMART-CDP function.

### Trans-State Time

| Transition From | Transition To | Discharge Time (Typ.) |

|-----------------|---------------|-----------------------|

| SDP1            | CDP           | 2 s                   |

| SDP1            | DCP           | 2 s                   |

| CDP             | SDP1          | 2 s                   |

| CDP             | DCP           | 2 s                   |

| CDP             | SDP2          | No Discharge          |

| SDP2            | CDP           | No Discharge          |

| DCP             | SDP1,2        | 250 ms                |

| DCP             | CDP           | 250 ms                |

### Wake On USB

The SLGC55546CV supports low and full speed HID (human interface device like mouse/keyboard) wake function. There are two scenarios under which wake on mouse are supported by the SLGC55546CV. The specific CTL pin changes that the SLGC55546CV will override are shown below. The information is presented as CTL1, CTL2, CTL3. The ILIM\_SEL pin plays no role.

1. 111 (CDP/SDP2) to 011 (DCP-Auto)

2. 010 (SDP1) to 011 (DCP-Auto)

Note that the 110 (SDP1) to 011 (DCP-Auto) transition is not supported. This is done for practical reasons since the transition involves changes to two CTL pins. Depending on which CTL pin changes first, the device will see either a temporary 111 or 010 command. The 010 command is safe but the 111 command will cause an OUT discharge as the SLGC55546CV will instead proceed to the 111 state.

### Output Discharge

To allow a charging port to renegotiate current with a portable device, SLGC55546CV uses the VBUS discharge function. It proceeds by turning off the power switch while discharging VOUT, then turning back ON the power switch to reassert the VOUT voltage. This discharge function is automatically applied when a change at the CTLx lines results in any of the following mode transitions.

- Any transition to and from CDP

- Any transition to and from SDP

In addition to this, can be achieved using the mode "000".

### Overcurrent Protection

When an over-current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before VIN has been applied.

The SLGC55546CV senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for nominally one to two microseconds before the current-limit circuit can react. The device operates in constant-current mode after the current-limit circuit has responded. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting. The device will remain off until the junction temperature cools approximately 10°C and will then re-start. The device will continue to cycle on/off until the over-current condition is removed.

### FAULT# Response

The FAULT# open-drain output is asserted (active low) during an over-temperature or current limit condition. The output remains asserted until the fault condition is removed. The SLGC55546CV is designed to eliminate false FAULT# reporting by using an internal deglitch circuit for current limit conditions without the need for external circuitry. This ensures that FAULT# is not accidentally asserted.

tally asserted due to normal operation such as starting into a heavy capacitive load. Over-temperature conditions are not deg-latched and assert the FAULT# signal immediately.

### Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turn-on threshold. Built-in hysteresis prevents unwanted oscillations on the output due to input voltage drop from large current surges.

### Thermal Sense

The SLGC55546CV protects itself with two independent thermal sensing circuits that monitor the operating temperature of the power distribution switch and disables operation if the temperature exceeds recommended operating conditions. The device operates in constant-current mode during an over-current condition, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, so the junction temperature rises during an over-current condition. The first thermal sensor turns off the power switch when the die temperature exceeds 135 °C and the part is in current limit. The second thermal sensor turns off the power switch when the die temperature exceeds 155 °C regardless of whether the power switch is in current limit. Hysteresis is built into both thermal sensors, and the switch turns on after the device has cooled by approximately 10 °C. The switch continues to cycle off and on until the fault is removed. The open-drain false reporting output FAULT# is asserted (active low) during an over-temperature shutdown condition.

### Power Wake

The SLGC55546CV monitors charging current at the VOUT pin and provide a mechanism via the STATUS# pin to switch out the high power DC-DC and switch to a low power LDO when charging current requirement is < 45 mA (typ). This saves system power in S4/S5 state while the port has no peripheral device connected. The function is specified in the truth table setting "0011"

### Power Management

When a connected peripheral device request high current charge for their battery, the system may not be able to support to enough current for every USB port. In this situation, the SLGC55546CV supports a port power management function to help the system designer to control their USB port power. STATUS# trip point is based on ILIM\_L current limit value to set the point. When a connected peripheral device requires port power charge current higher than ILIM\_L+60 mA 200 ms then the STATUS# pin will automatically output LOW to let system know. When the charge current is below ILIM\_L + 60 mA, 3 s then STATUS# return back to HIGH. This function works via truth table setting "0111" DCP\_Auto mode and "1111" CDP mode.

### Application and Layout Guidelines

- The designed power supply range is from 4.5 V to 5.5 V. If the input supply is located more than a few inches from the device, an input bypass capacitor larger than 0.1  $\mu$ F is recommended.

- The trace routing from the upstream regulator to the VIN pin must be as short as possible to reduce the voltage drop and parasitic inductance.

- The trace routing from the Current-Limit Set Resistors to the device must be as short as possible to reduce parasitic effects on Current-Limit accuracy.

## Package Top Marking System Definition

|           |        |          |

|-----------|--------|----------|

| Part Code | XXXXX  |          |

| Datecode  | DD LLL | Lot      |

| COO       | CRR    | Revision |

|           | o      |          |

XXXXX – Part ID Field: identifies the specific device configuration

DD – Date Code Field: Coded date of manufacture

LLL – Lot Code: Designates Lot #

C – Assembly Site/COO: Specifies Assembly Site/Country of Origin

RR – Revision Code: Device Revision

**SLGC55546CV**

## USB Charging Port Power Switch and Controller

## PCB Landing Pattern

## Marking View

UNIT: um

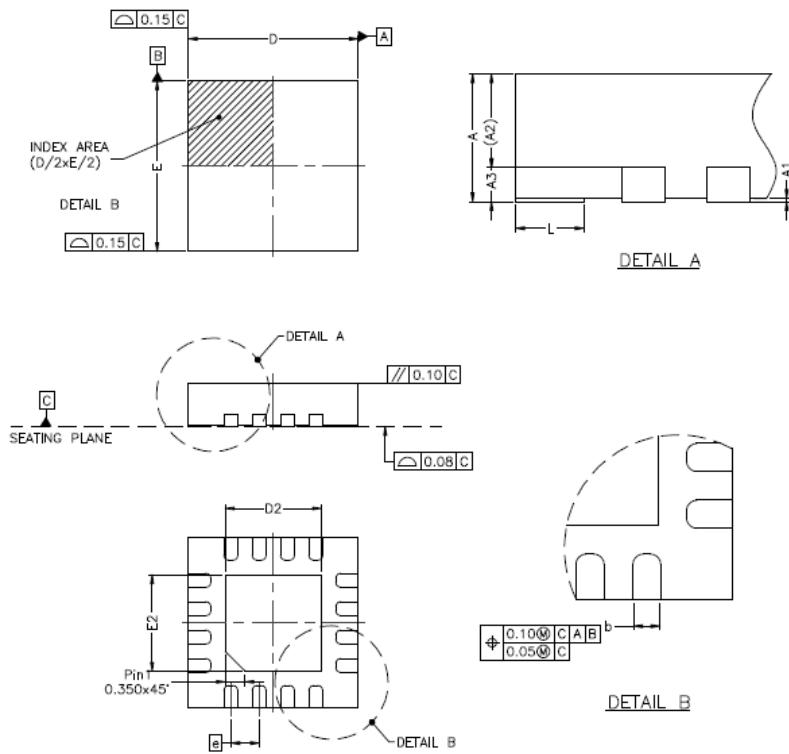

## Package Drawing and Dimensions

## 16 Lead TQFN Package

| SYMBOL | DIMENSION (MM) |      |      | DIMENSION (MIL) |      |      |

|--------|----------------|------|------|-----------------|------|------|

|        | MIN.           | NOM. | MAX. | MIN.            | NOM. | MAX. |

| A      | 0.70           | 0.75 | 0.80 | 28              | 30   | 31   |

| A1     | 0.00           | 0.02 | 0.05 | 0               | 1    | 2    |

| A2     | 0              | 0.55 | 0.80 | 0               | 22   | 31   |

| A3     | —              | 0.20 | —    | —               | 8    | —    |

| b      | 0.18           | 0.25 | 0.30 | 7               | 10   | 12   |

| D      | 2.90           | 3.00 | 3.10 | 114             | 118  | 122  |

| D1     | —              |      |      | —               |      |      |

| D2     | 1.60           | 1.70 | 1.80 | 63              | 67   | 71   |

| E      | 2.90           | 3.00 | 3.10 | 114             | 118  | 122  |

| E1     | —              |      |      | —               |      |      |

| E2     | 1.60           | 1.70 | 1.80 | 63              | 67   | 71   |

| e      | 0.50 BSC       |      |      | 20 BSC          |      |      |

| L      | 0.35           | 0.40 | 0.45 | 14              | 16   | 18   |

## NOTE

1. REFER TO JEDEC STD: MO-220.

2. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

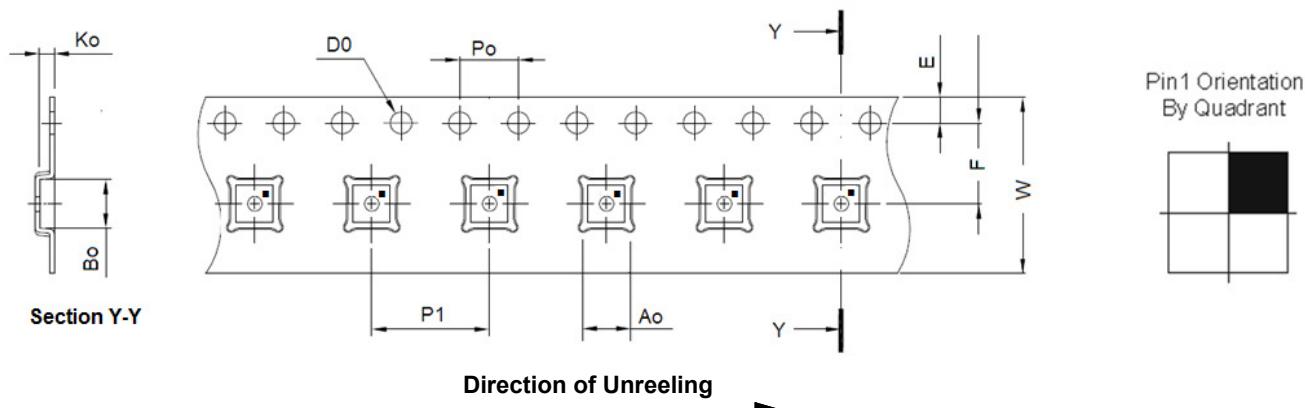

## Tape and Reel Specifications

| Package Type                  | # of Pins | Nominal Package Size [mm] | Max Units |         | Reel & Hub Size [mm] | Leader (min) |             | Trailer (min) |             | Tape Width [mm] | Part Pitch [mm] |

|-------------------------------|-----------|---------------------------|-----------|---------|----------------------|--------------|-------------|---------------|-------------|-----------------|-----------------|

|                               |           |                           | per Reel  | per Box |                      | Pockets      | Length [mm] | Pockets       | Length [mm] |                 |                 |

| TQFN 16L<br>3 x 3 mm<br>Green | 16        | 3 x 3 x 0.75              | 5,000     | 10,000  | 330 / 100            | 42           | 336         | 42            | 336         | 12              | 8               |

## Carrier Tape Drawing and Dimensions

| Package Type                  | Pocket BTM Length | Pocket BTM Width | Pocket Depth | Index Hole Pitch | Pocket Pitch | Index Hole Diameter | Index Hole to Tape Edge | Index Hole to Pocket Center | Tape Width |

|-------------------------------|-------------------|------------------|--------------|------------------|--------------|---------------------|-------------------------|-----------------------------|------------|

|                               | A0                | B0               | K0           | P0               | P1           | D0                  | E                       | F                           | W          |

| TQFN 16L<br>3 x 3 mm<br>Green | 3.3               | 3.3              | 1.0          | 4.0              | 8.0          | 1.55                | 1.75                    | 5.5                         | 12.0       |

## Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 6.75 mm<sup>3</sup> (nominal). More information can be found at [www.jedec.org](http://www.jedec.org).

## Revision History

| Date       | Version | Change                                                                                                                                                                       |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/21/2022 | 1.04    | Updated company name and logo                                                                                                                                                |

| 3/5/2020   | 1.03    | Updated Style and formatting                                                                                                                                                 |

| 10/6/2017  | 1.02    | Added additional conditions for RDS <sub>ON</sub><br>Added T <sub>DIS_LONG</sub> and T <sub>DIS_SHORT</sub><br>Added Trans-State Time Table<br>Added Wake On USB description |

| 7/11/2017  | 1.01    | Added Application and Layout Guidelines                                                                                                                                      |

| 6/5/2015   | 1.00    | Production Release                                                                                                                                                           |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).