RZ/T2L グループ

RZ Arm ベースハイエンド 32 ビット/64 ビット MPU

R01DS0409JJ0120 Rev.1.20 Dec 8, 2023

200/400/800 MHz シングル Arm<sup>®</sup> Cortex<sup>®</sup>-R52 で、FPU および NEON<sup>™</sup>を内蔵し、1.0 MB 内蔵 SRAM、イーサネット MAC、 EtherCAT、USB 2.0 ハイスピード、CAN/CANFD、xSPI や ΔΣ インタフェースなどの多種多様な通信機能、エンコーダイン タフェース、およびセキュリティ機能を搭載

- 内蔵 32 ビット Arm Cortex-R52 プロセッサ

- 動作周波数 200/400/800 MHz の高速リアルタイムコントロー

- シングル 32 ビット Arm Cortex-R52 (revision rlp2) を内蔵 ECC 付き密接合メモリ (TCM)

- 512 KB/64 KB

- ECC 付き命令キャッシュ /データキャッシュ - キャッシュあたり、16 KB • 高速割り込み

- FPU は単精度及び倍精度の加算、減算、乗算、除算、積和演算、平方根演算をサポート

- NEON および Advanced SIMD は、整数及び単精度の演算結果

- 8段パイプラインのハーバードアーキテクチャ

- メモリプロテクションユニット (MPU) 対応

Arm CoreSight アーキテクチャで JTAG および SWD インタフェースによるデバッグをサポート

#### ■ 低消費電力

スタンバイモード、モジュールストップ機能

#### ■ 内蔵 SRAM

- 1.0 MB の ECC 付き内蔵 SRAM

- 150/200 MHz

#### ■ データ転送

● DMAC: 16 チャネル×2 ユニット

#### ■ イベントリンクコントローラ

- 割り込みを介さず、イベント信号でモジュール動作が可能

- CPU がスタンバイ状態でも、モジュール間のリンク動作が可

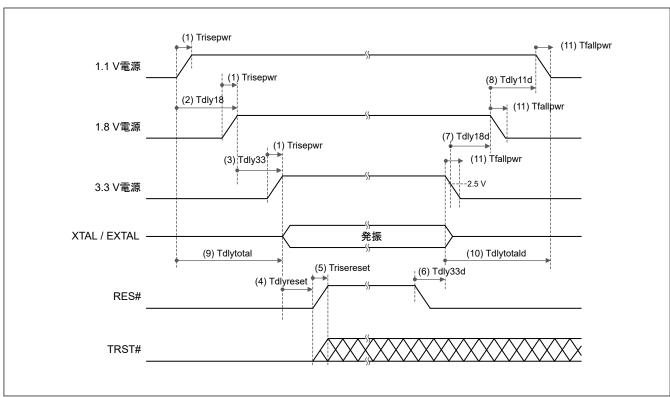

#### ■ リセットと電源電圧制御

• 端子リセットを含む4つのリセット要因

### ■ クロック機能

- ◆ 外部クロック/発振器入力周波数:25 MHz◆ CPU クロック周波数:200/400/800 MHz または150/300/600

- システムクロック周波数: 200 MHz または 150 MHz

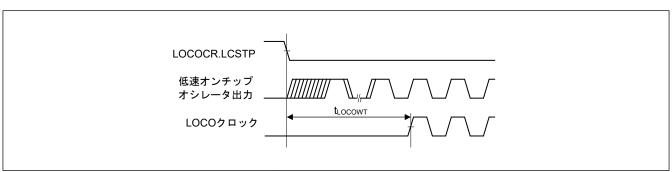

- 低速オンチップオシレータ (LOCO): 240 kHz

### ■ セーフティ機能

- レジスタライトプロテクション、入力クロック発振停止の検 出および CRC

- マスタメモリプロテクションユニット (MPU)

### ■ セキュリティ機能(オプション)

- 暗号化によるセキュリティを備えたブートモード

- JTAG 認証

- 暗号化アクセラレータ

- TRNG

#### ■ エンコーダインタフェース

- 最大2チャネル

- EnDat 2.2、BiSS-C、A-format、および HIPERFACE DSL 準拠のインタフェース

エンコーダからの周波数分周出力

### ■ 多種多様な通信機能を内蔵

- イーサネット

- EtherCAT スレーブコントローラ:3ポート - イーサネット MAC : 1 ポート

- USB2.0 ハイスピードホスト/ファンクション:1 チャネル

- ISO11898-1 準拠の CAN/CANFD: 2 チャネル

- 16 バイトの送受信 FIFO 搭載 SCI: 6 チャネル● 12C バスインタフェース: 3 チャネル (最大転送速度 400 kbps)

- SPI: 4 チャネル

● xSPI: 2 チャネル

### ■ 外部ホストインタフェース

● シリアルホストインタフェース (SHOSTIF)

#### ■ 外部アドレス空間

- 高速データ転送バス (最大 100 MHz)

- 最大4つの CS 領域をサポート

- エリアごとに8ビットまたは16ビットバス空間を選択可能

#### ■ 最大 35 本の拡張タイマ機能

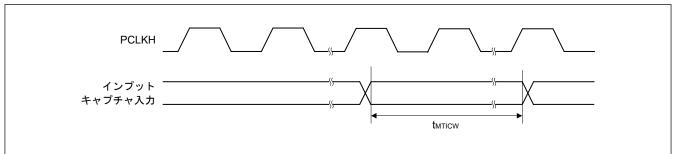

- 16 ビット×8+32 ビット MTU3 (9 チャネル)、32 ビット GPT (18 チャネル): インプットキャプチャ、アウトプットコン 、PWM 波形出力

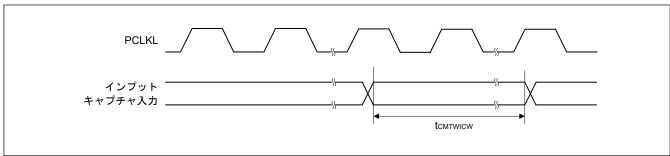

- 16 ビット CMT (6 チャネル)、32 ビット CMTW (2 チャネ

### ■ ΔΣ インタフェース

• 外部に最大 6 チャネルの ΔΣ モジュレータを接続可能

#### ■ 三角関数ユニット

- sin と cos を同時に計算

- arctan と hypot\_k を同時に計算

#### ■ 12 ビット A/D コンバータ

- 12 ビット×2 ユニット (ユニット 0 とユニット 1 に対し 4 チ

- チップ内部の温度を計測可能な温度センサを内蔵

#### ■ 汎用入出力ポート

- 入力プルアップ/プルダウン

- 周辺機能の入出力端子を複数個所から選択可能

#### ■ 動作温度範囲

• Tj = -40 $\sim$ +125 $^{\circ}$ C

# 1. 概要

# 1.1 仕様概要

この MPU は、浮動小数点ユニット (FPU) および NEON $^{\text{TM}}$ を備える Arm Cortex $^{\text{®}}$ -R52 プロセッサによる高性能 ASSP です。システム構成に必要な統合された周辺機能を内蔵しています。

### 表 1.1 CPU

| 機能              | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm®Cortex®-R52 | <ul> <li>シングルプロセッサ</li> <li>動作周波数         <ul> <li>200 MHz/400 MHz/800 MHz (200 MHz システムクロック時)</li> <li>150 MHz/300 MHz/600 MHz (150 MHz システムクロック時)</li> </ul> </li> <li>Arm の設計による 32 ビット CPU Cortex-R52 (Core revision r1p2)</li> <li>アドレス空間: 4 GB</li> <li>命令キャッシュ         <ul> <li>16 KB (ECC あり)</li> </ul> </li> <li>データキャッシュ         <ul> <li>16 KB (ECC あり)</li> </ul> </li> <li>密接合メモリ (TCM)         <ul> <li>ATCM: 512 KB (ECC あり) 1 ウェイト (400 MHz 未満の場合、0 ウェイト選択可能)</li> <li>BTCM: 64 KB (ECC あり) 0 ウェイト</li> <li>CTCM: 0 KB (ECC あり)</li> </ul> </li> <li>命令セット: Arm v8-R アーキテクチャ、Thumb<sup>®</sup>および Thumb-2 を含めてサポート</li> <li>データ配置         <ul> <li>命令: リトルエンディアン</li> <li>データ: リトルエンディアン</li> <li>2 ステージメモリプロテクションユニット (MPU)</li> </ul> </li> </ul> |

| FPU             | <ul> <li>単精度と倍精度の加算、減算、乗算、除算、積和演算、および平方根演算をサポートします。</li> <li>レジスタ 64 ビットシングルワードレジスタ: 64 ビット×32 (16 個のダブルワードレジスタとして使用可能: 128 ビット×16)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NEON            | 整数および単精度の演算結果をサポートする Advanced SIMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### 表 1.2 メモリ

| 機能                | 機能説明                                                                                                                                                                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECC 付き内蔵システム SRAM | <ul> <li>容量:最大 1.0 MB (512 KB × 2 ユニット) (ECC 付き)</li> <li>動作周波数: 150 MHz/200 MHz</li> <li>SEC-DED (シングルエラー訂正/ダブルエラー検出)<br/>エラーインジェクションをサポート</li> </ul>                            |

| ワンタイムプログラマブルメモリ   | <ul> <li>上書き保護</li> <li>冗長機能対応</li> <li>ECC 対応</li> <li>使用可能な情報         <ul> <li>ユニーク ID</li> <li>認証設定</li> <li>トリミングデータ</li> <li>ブートモード設定</li> <li>ユーザー領域</li> </ul> </li> </ul> |

# 表 1.3 システム

| 機能                 | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 動作モード              | 動作モードは、以下の 7 つのブートモードから選択できます。  • xSPI0 ブートモード (CS0 × 1 ブートシリアルフラッシュ)  • xSPI0 ブートモード (CS0 × 8 ブートシリアルフラッシュ)  • 16 ビットバスブートモード (CS0 NOR フラッシュ)  • xSPI1 ブートモード (CS0 × 1 ブートシリアルフラッシュ)  • SHOSTIF ブートモード  • SCI ブートモード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| クロック発生回路           | <ul> <li>入カクロックは、外部クロックまたは外部発振子から選択できます。</li> <li>入カクロック発振停止の検出</li> <li>以下のクロックを発生します。         <ul> <li>CPU0 クロック:システムクロック×1、×2、または×4</li> <li>システムクロック: 150 MHz または 200 MHz</li> <li>高速周辺モジュールクロック: 150 MHz または 200 MHz</li> <li>中速周辺モジュールクロック: 75 MHz または 100 MHz</li> <li>低速周辺モジュールクロック: 37.5 MHz または 50 MHz</li> <li>12 ビット A/D コンバータの ADC クロック: 18.75 MHz または 25 MHz</li> <li>外部バスクロック: 最高 100 MHz</li> <li>低速オンチップオシレータ: 240 kHz (固定)</li> </ul> </li> </ul>                                                                                                                                                                                                                                        |

| リセット               | RES#端子リセット、ソフトウェアリセット、エラーリセット、CPU0 ソフトウェアリセット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 低消費電力機能            | <ul><li> スタンバイモード (Cortex-R52)</li><li> モジュールストップ機能</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 割り込みコントローラ (ICU)   | <ul> <li>Cortex-R52 CPU0 の GIC (ジェネリック割り込みコントローラ) に割り込みを接続します</li> <li>起動トリガを DMAC と ELC に接続します</li> <li>周辺機能割り込み: 448 要因</li> <li>外部割り込み: 16 要因 (IRQ0~IRQ15 端子)</li> <li>ソフトウェア割り込み: 8 要因</li> <li>ノンマスカブル割り込み: 1 要因</li> <li>16 レベルの優先順位を GIC に設定可能</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

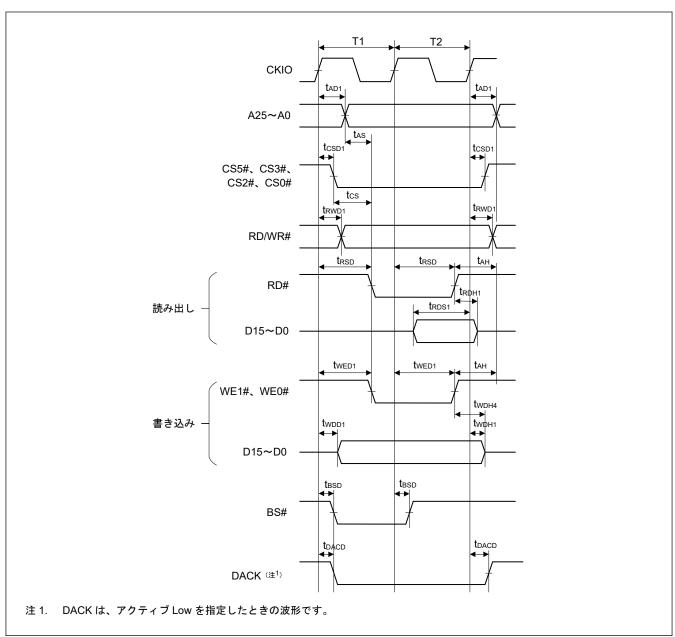

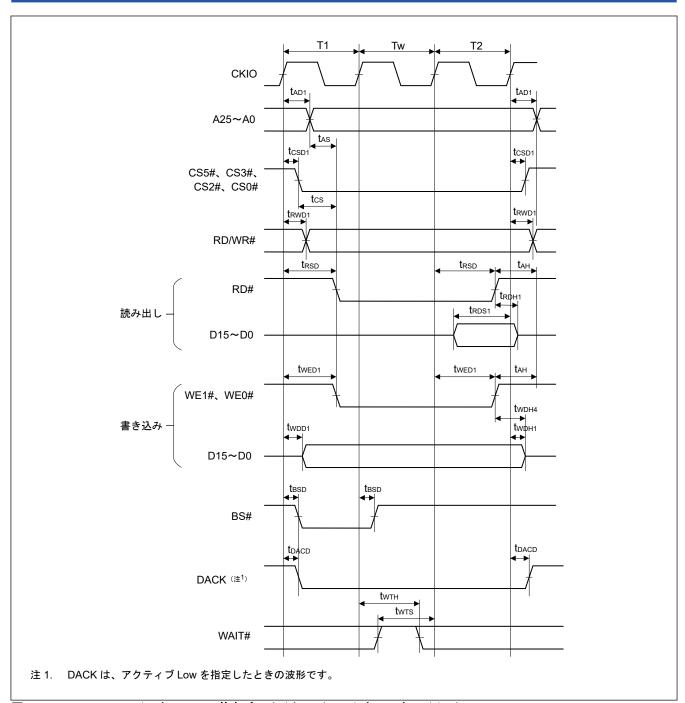

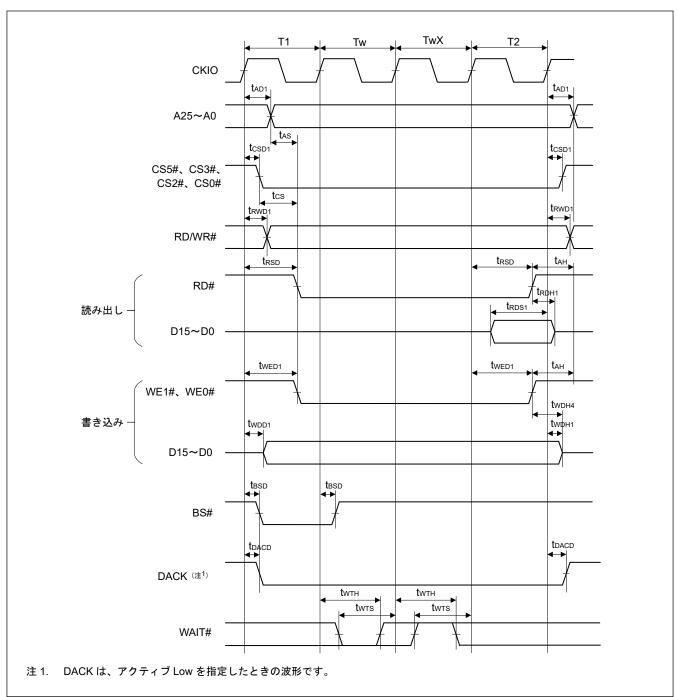

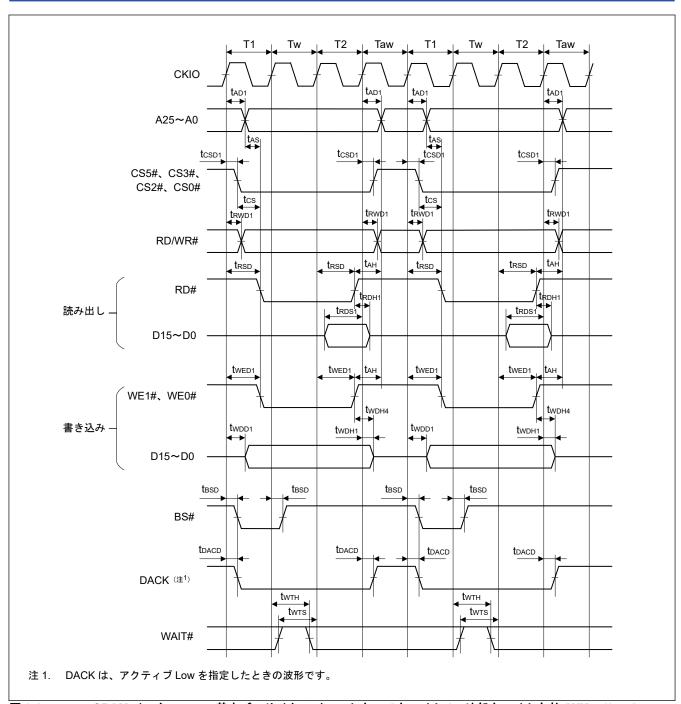

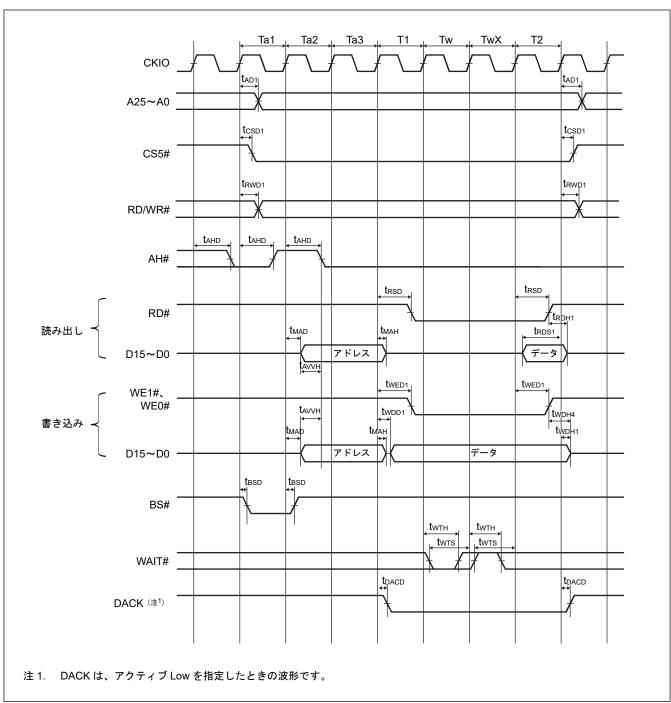

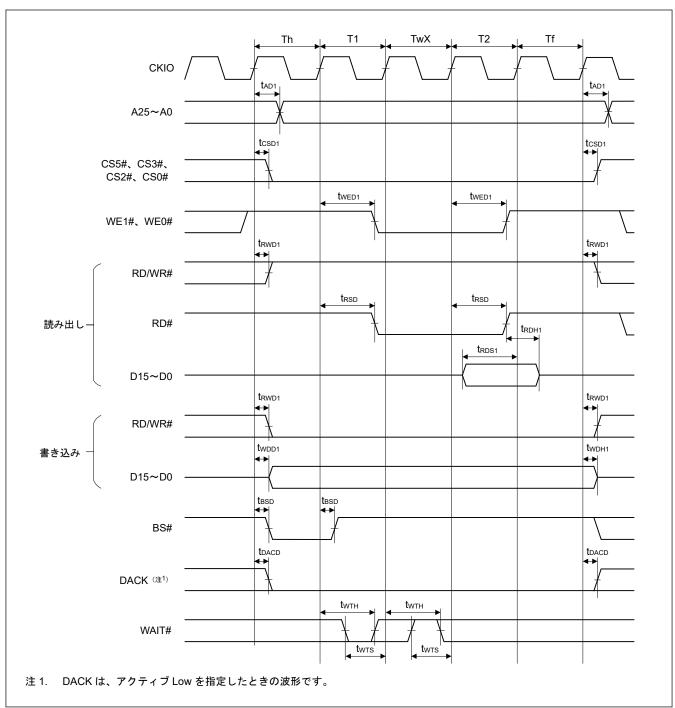

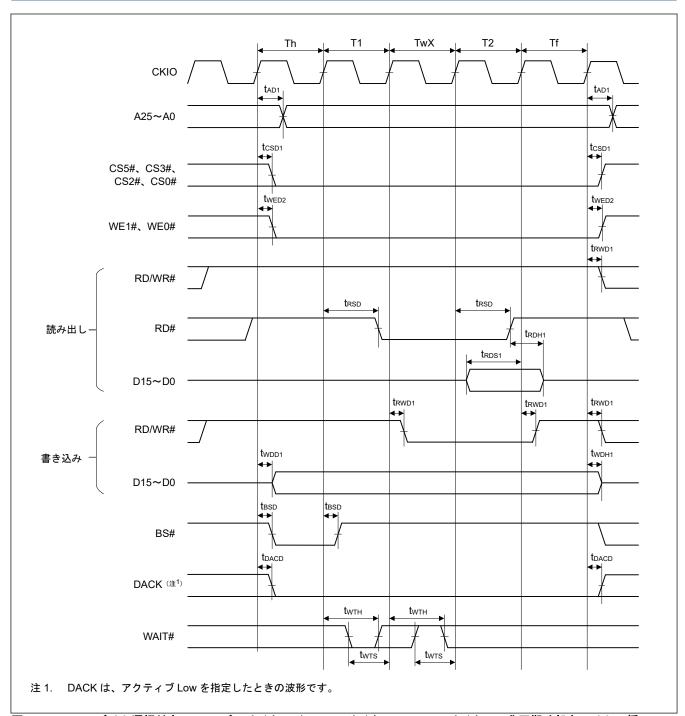

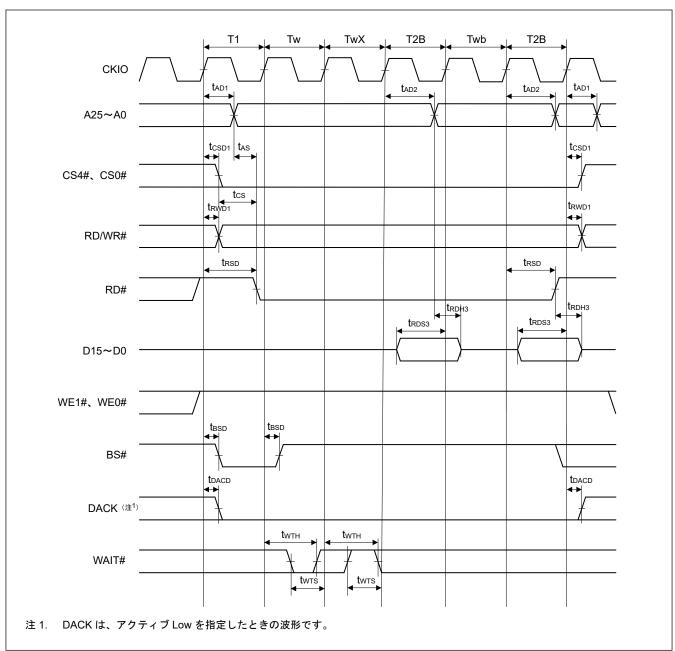

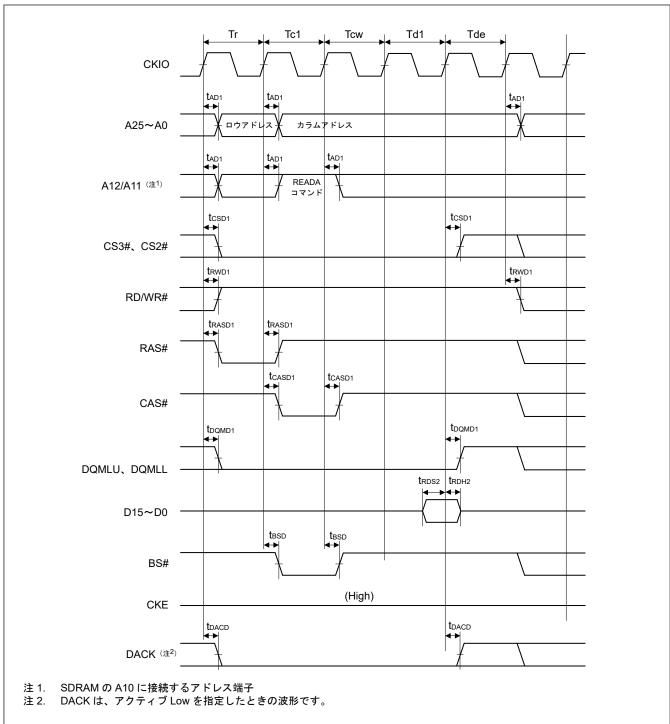

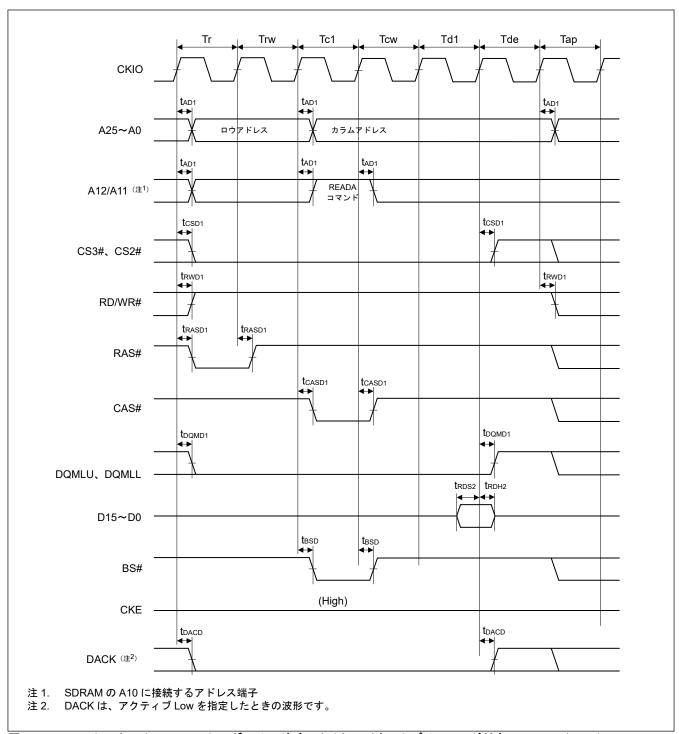

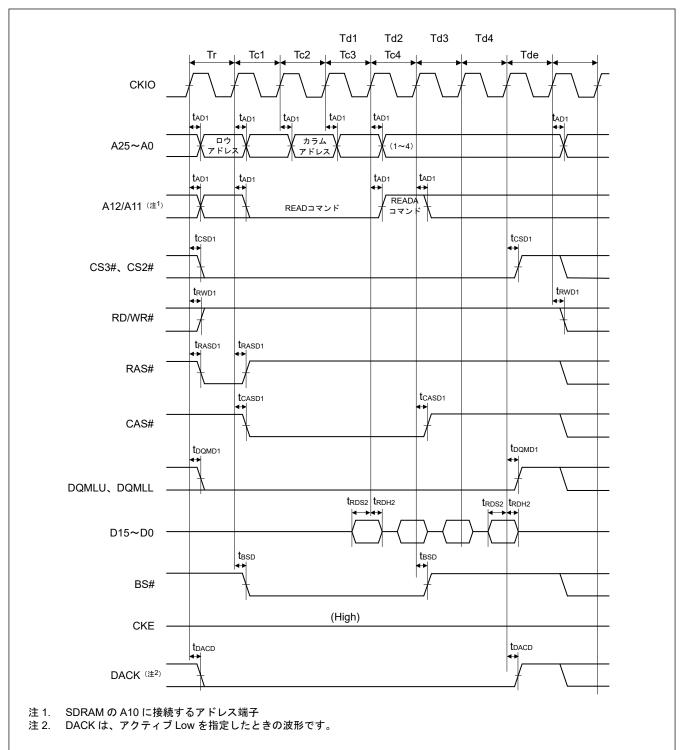

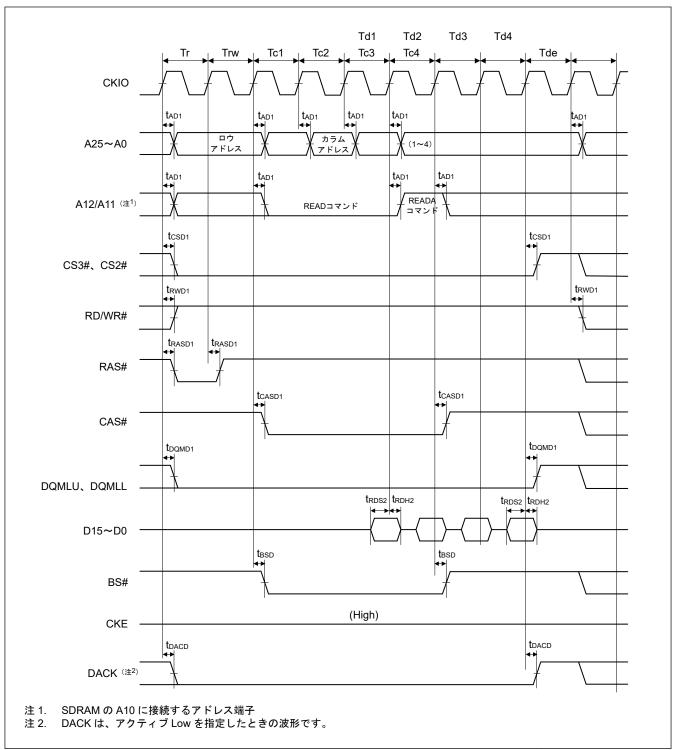

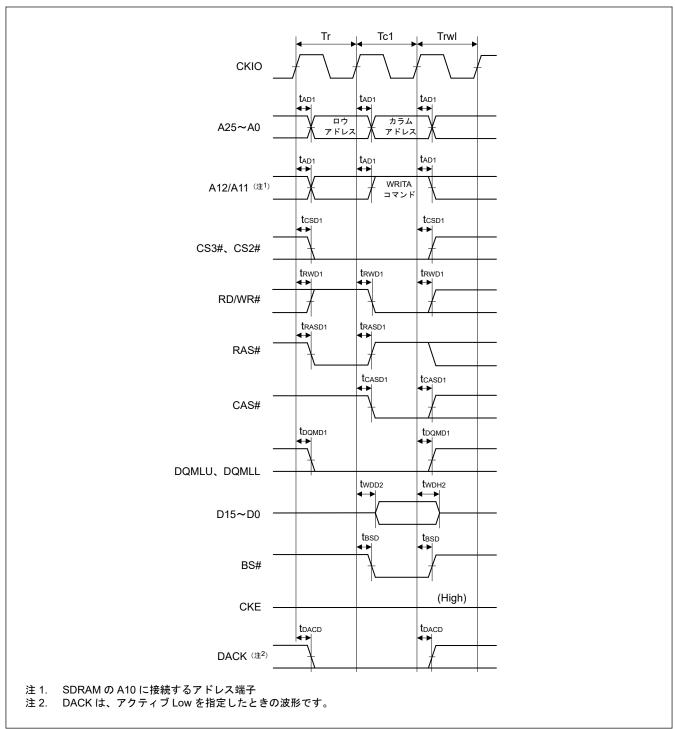

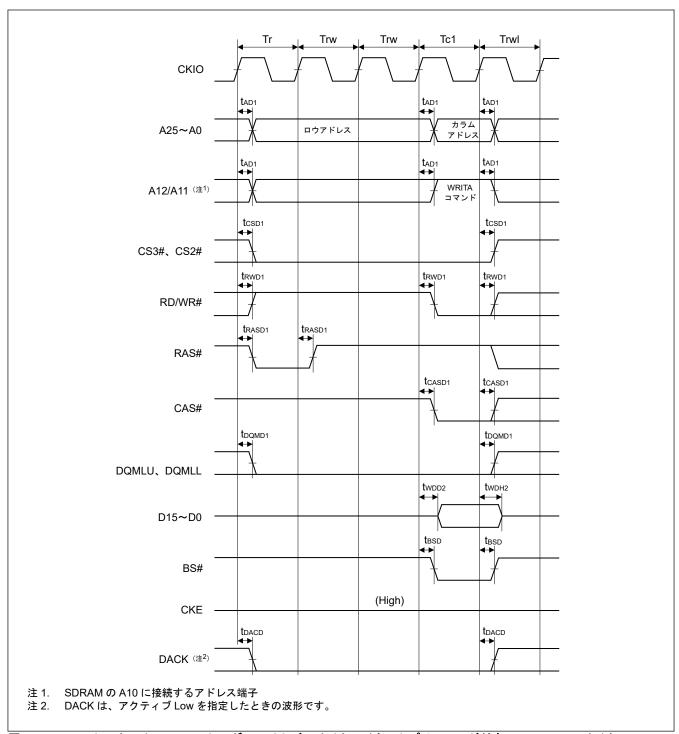

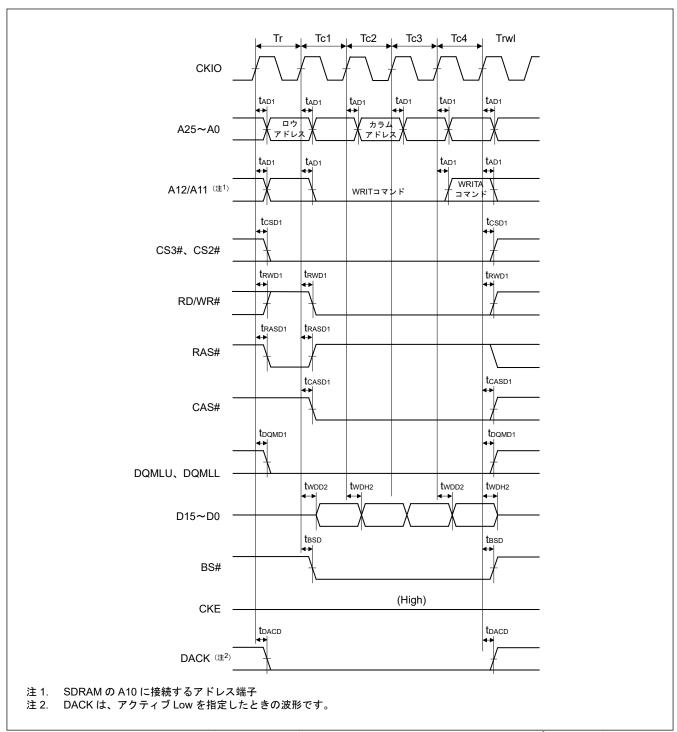

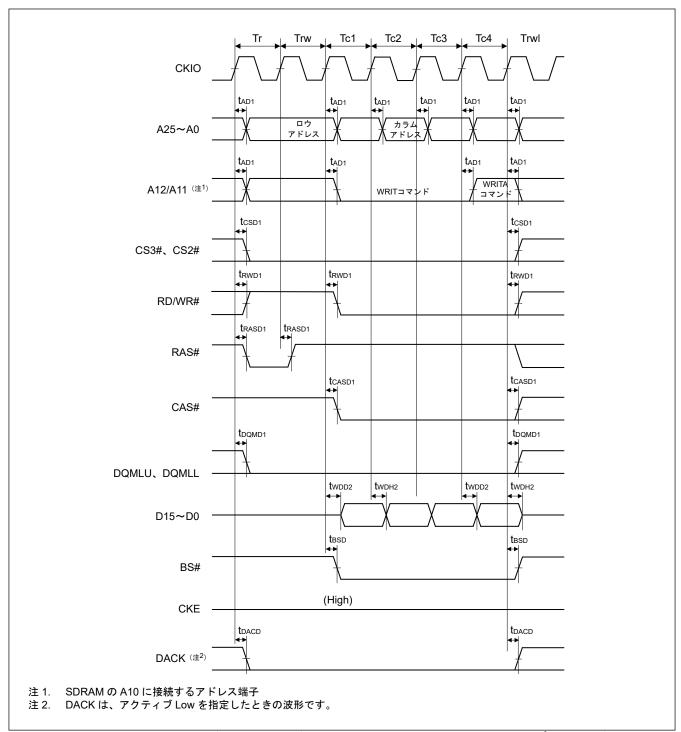

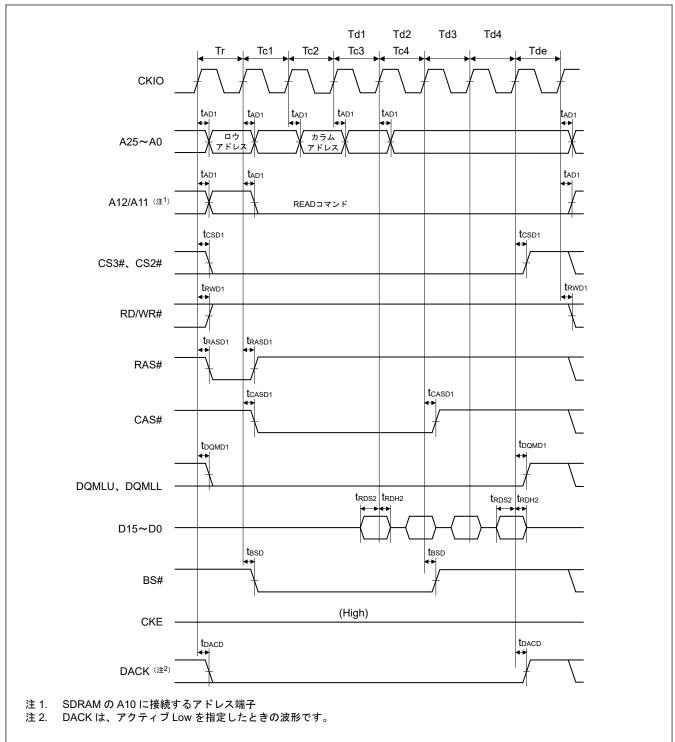

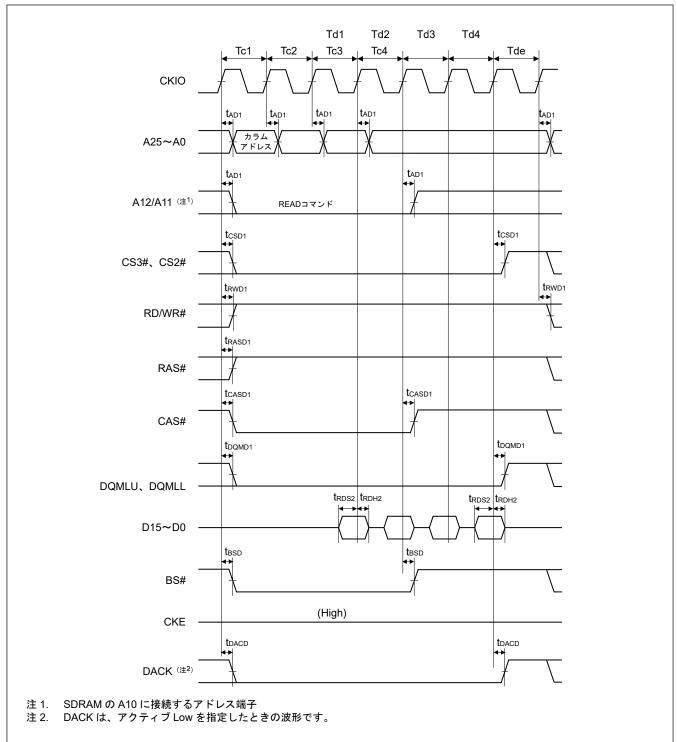

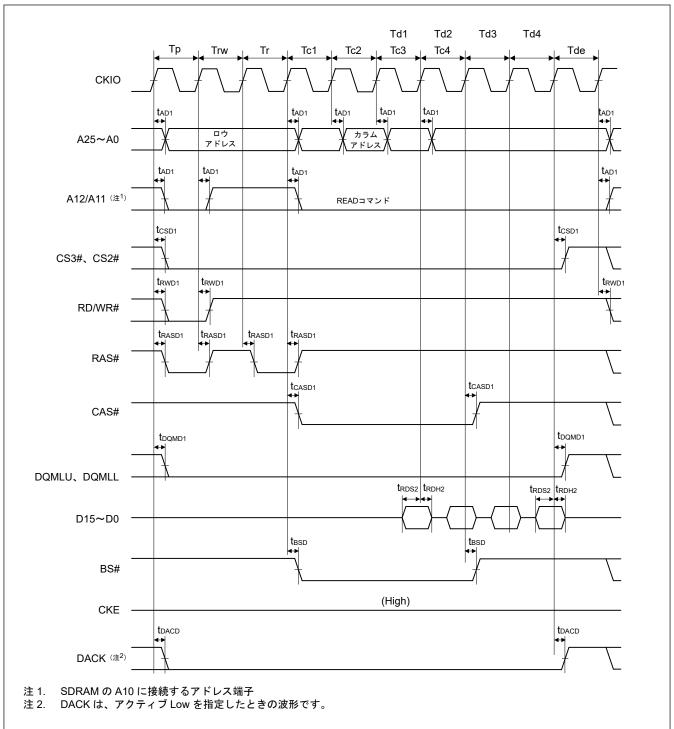

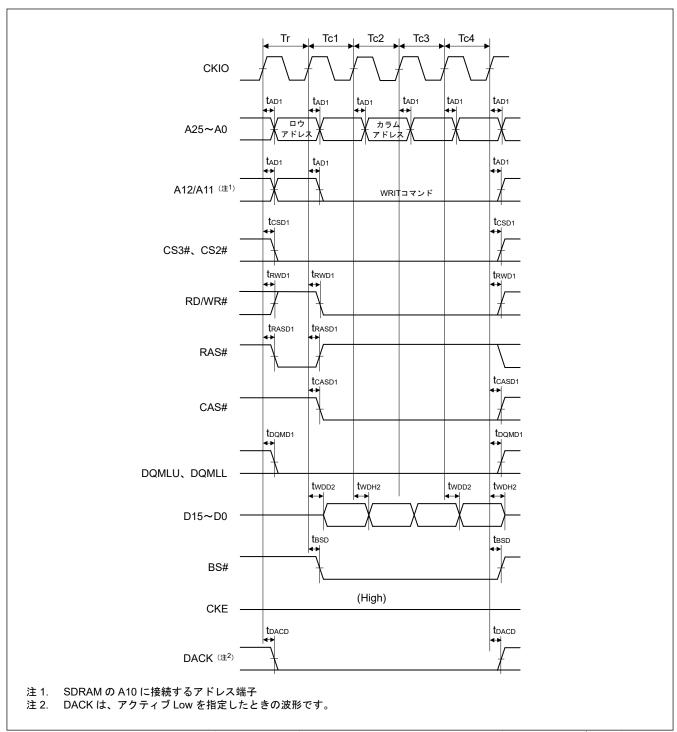

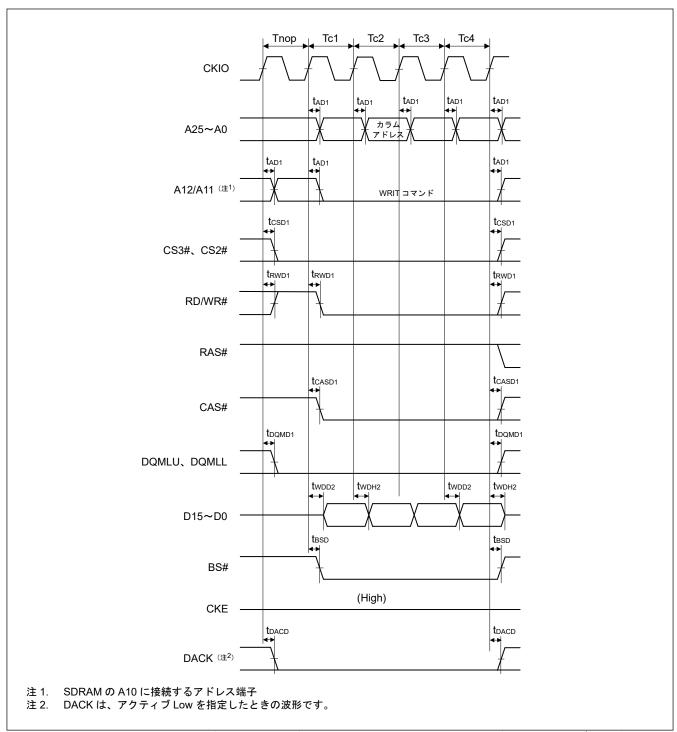

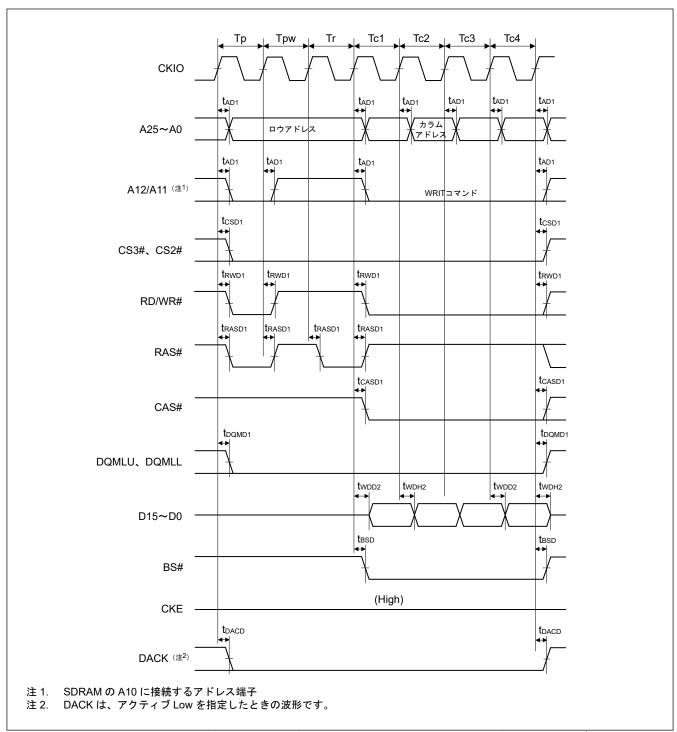

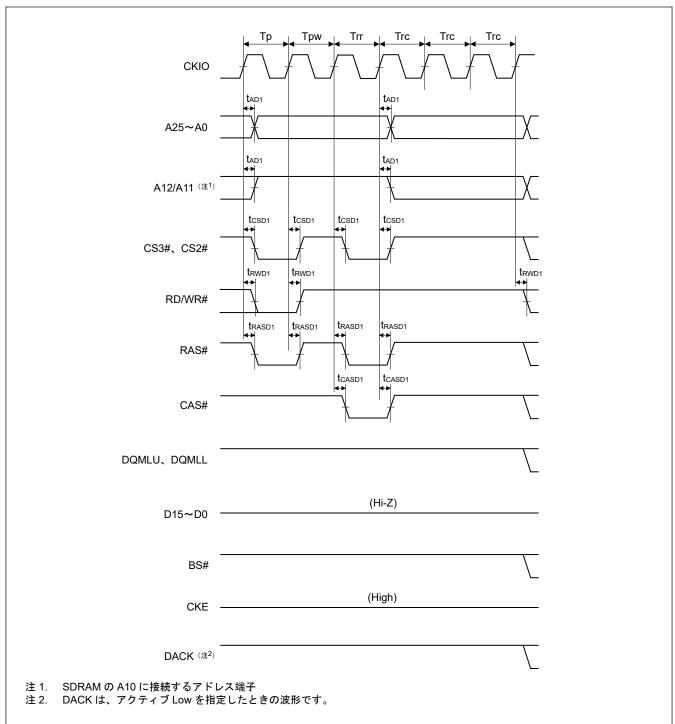

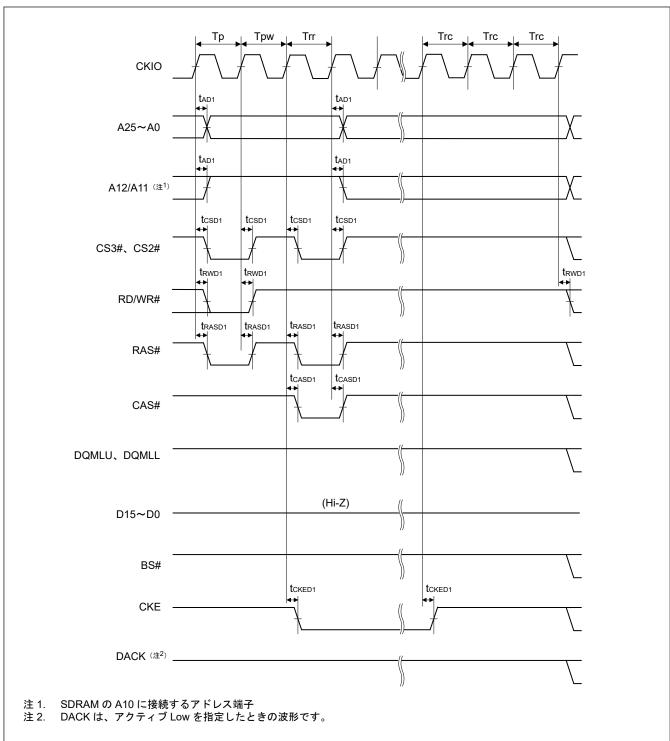

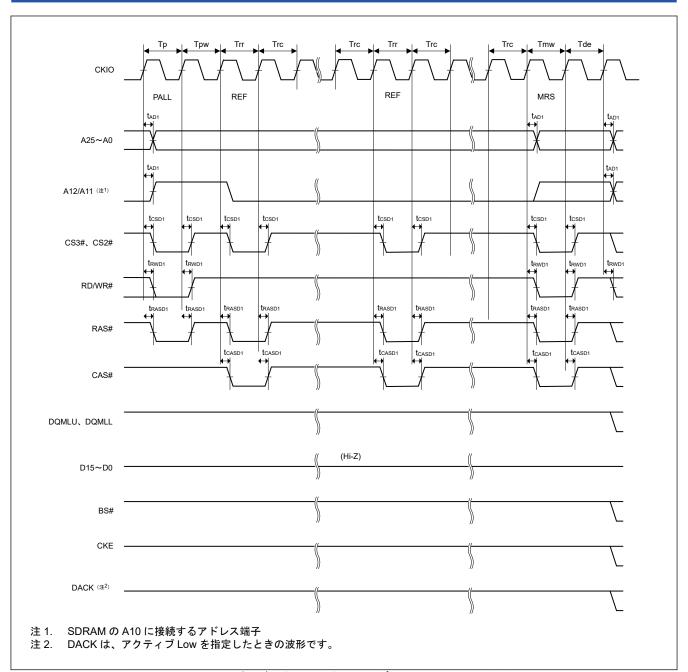

| バスステートコントローラ (BSC) | <ul> <li>外部アドレス空間は、管理のために 4 領域(CS0、CS2、CS3、CS5)に分割されています。</li> <li>以下の機能を各領域に対して独立して設定可能です。 バスサイズ (8 ビットまたは 16 ビット):使用可能なサイズは領域に依存します。アクセスウェイトサイクル数 (領域によって、読み出しアクセスサイクルと書き込みアクセスサイクルに異なるウェイトサイクルを指定可能です)。アイドルウェイトサイクル挿入 (同じ領域のアクセスサイクル間、または異なる領域のアクセスサイクル間)。各領域に接続されるメモリを指定することで、SRAM、バイト選択付き SRAM、SDRAM、およびバーストROM (クロック同期または調歩同期)への直接接続が可能です。アドレス/データマルチプレクス入出力 (MPX) インタフェースも利用可能です。</li> <li>対象の領域に従って、チップセレクト信号 (CS0#~CS5#)を出力します。(CS アサートまたはネゲートのタイミングはソフトウェアで選択可能です。)</li> <li>各領域に接続可能なメモリタイプ CS0: SRAM、バースト ROM CS2: SRAM CS2: SRAM SDRAM (CS2 のみの SDRAM はサポートされていません。) CS3: SRAM、SDRAM CS5: SRAM、MPX-IO</li> <li>SDRAM リフレッシュ オートリフレッシュモード/セルフリフレッシュモードを選択可能</li> <li>SDRAM バーストアクセス</li> </ul> |

# 表 1.4 ダイレクトメモリアクセス

| 機能                        | 機能説明                                                                                                                                                                                                                                                 |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

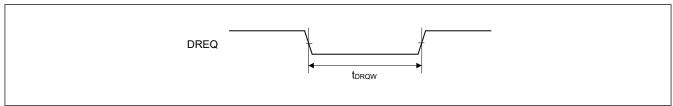

| ダイレクトメモリアクセスコントローラ (DMAC) | <ul> <li>2ユニット(各ユニットあたり16チャネル)</li> <li>転送モード:シングル転送モードおよびブロック転送モード</li> <li>転送サイズ         <ul> <li>ユニット0:1/2/4/8/16/32/64 バイト</li> <li>ユニット1:1/2/4/8/16/32 バイト</li> </ul> </li> <li>起動要因:ソフトウェアトリガ、外部 DMA 要求 (DREQ)、外部割り込み、および周辺機能割り込み要求</li> </ul> |

# 表 1.5 I/O ポート

| 機能       | 機能説明                                                                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 汎用入出力ポート | <ul> <li>196 ピン FBGA</li> <li>- 入出力端子: 110</li> <li>- 入力端子: 1</li> <li>- プルアップ/プルダウン抵抗: 111</li> <li>◆ 入出力機能の場所は、複数の端子から選択可能です。</li> </ul> |

# 表 1.6 イベントリンク

| 機能                  | 機能説明                                                                                                                                           |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| イベントリンクコントローラ (ELC) | <ul> <li>最大 213 イベント信号をモジュールの動作に連動可能です。</li> <li>特にタイマ系のモジュールの動作はイベント信号の入力で起動できます。</li> <li>ポート 16 およびポート 18 の信号のイベントリンク動作が可能になります。</li> </ul> |

# 表 1.7 タイマ (1/2)

| 機能機能                                                | <b></b><br>能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

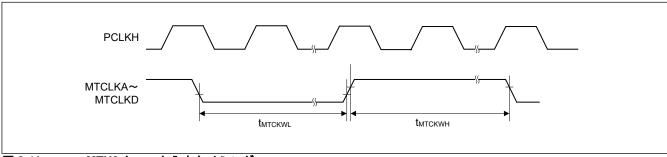

| = y + 3 (MTU3)  • • • • • • • • • • • • • • • • • • | 9 チャネル (16 ビット×8 チャネル、32 ビット×1 チャネル) 最大 28 本のパルス入出力および 3 本のパルス入力が可能 チャネルごとに 10、11、12、または 14 種類のカウンタ入カクロック信号から選択可能 (最高動作周波数 200 MHz) インブットキャブチャ機能 39 本のアウトプットコンペアレジスタ兼インプットキャプチャによる同期クリア) 複数のタイマカウンタ (TCNT) への同時書き込み カウンタの同期動作による各レジスタの同時入出力 バッファ動作 カスケード接続動作をサポートレジスタデータの自動転送 パルス出力モードトグル/PWM/相補 PWM/リセット同期 PWM 相補 PWM 出力モード - 3 相のインバータ制御用ノンオーバーラップ波形を出力 - デッドタイム自動設定 - PWM デューティーサイクル: PWM のデューティー比を 0~100%の任意の値に選択可能 - A/D 変換要求ディレイド機能 - 山/谷割り込み間引き機能 - ダブルバッファ機能 リセット同期 PWM モード任意のデューティー比の正相ノ逆相 PWM 波形を 6 相出力位相計数モード: 16 ビットモード (チャネル 1 および 2) / 32 ビットモード (チャネル 1 と 2 のカスケード接続) デッドタイム補償用カウンタ機能 A/D コンバータの変換開始トリガの間引きが可能 インプットキャプチャ端子および外部カウントクロック端子の信号に対するデジタルノイズフィルタ機能 |

# 表 1.7 タイマ (2/2)

| 機能                          | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

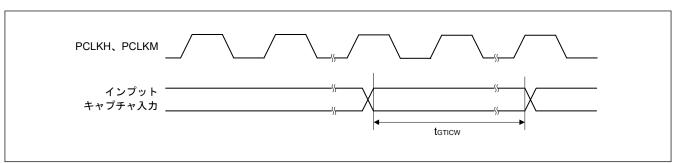

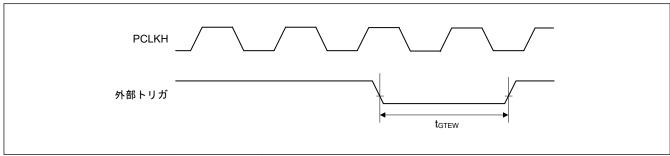

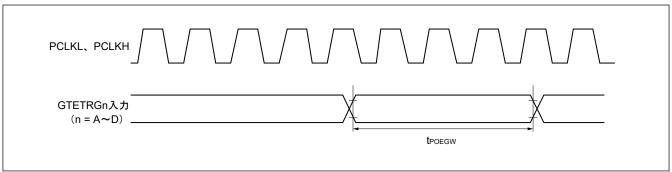

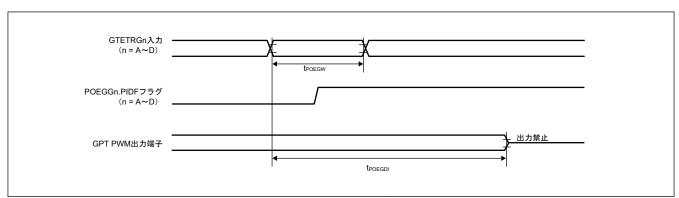

| 汎用 PWM タイマ (GPT)            | <ul> <li>32 ビット×18 チャネル</li> <li>全チャネルで、アップカウントもしくはダウンカウント(のこぎり波)、アップダウンカウント(三角波)が選択可能</li> <li>チャネルごとに4種類のカウンタ入カクロック信号から選択可能(LLPPでの最高動作周波数 400 MHz)</li> <li>チャネルごとに2本の入出力端子</li> <li>チャネルごとに2本の入出力端子</li> <li>チャネルごとに7ウトブットコンペア/インプットキャプチャ用レジスタが2本</li> <li>各チャネル2本のアウトブットコンペア/インブットキャプチャレジスタに対し、バッファレジスタとして4本のレジスタがあり、バッファ動作しないときにはコンペアレジスタとしても動作可能</li> <li>アウトプットコンペア動作時に山/谷それぞれバッファ動作可能で左右非対称なPWM波形を生成可能</li> <li>チャネルごとにフレーム周期用レジスタを搭載(オーバーフロー/アンダーフローで割り込み可能)</li> <li>複数のカウンタを同期動作可能</li> <li>同期動作の際にデッドタイム生成が可能</li> <li>3つのカウンタを組み合わせ、デットタイム付きの3相PWM波形を生成可能</li> <li>外部/内部トリガによるアップカウンタ/ダウンカウンタのスタート/クリア/ストップ/切り替え、およびインプットキャプチャスカレベル比較によるアップカウンタ/ダウンカウンタのスタート/クリア/ストップ/切り替え、およびインブットキャプチャ</li> <li>入カレベル比較によるアップカウンタ/ダウンカウンタのスタート/クリア/ストップ/切り替え、およびインブットキャプチャ</li> <li>入カレベル比較によるアップカウンタ/ダウンカウンタのスタート/クリア/ストップ/切り替え、およびインブットキャプチャ</li> <li>内部トリガ生成機能</li> <li>インプットキャプチャ端子および外部トリガ端子の信号に対するデジタルノイズフィルタ機能</li> <li>ELCによるイベントリンク機能をサポート</li> <li>谷、または山/谷から出カデューティー0%および出力デューティー100%機能を選択可能(全ユニット)</li> </ul> |

| コンペアマッチタイマ (CMT)            | <ul><li>◆ (16 ビット×2 チャネル)×3 ユニット</li><li>◆ チャネルごとに 4 種類のカウンタ入力クロック信号から選択</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| コンペアマッチタイマ W (CMTW)         | <ul> <li>(32 ビット×1 チャネル)×2 ユニット</li> <li>コンペアマッチ、インプットキャプチャ入力、およびアウトプットコンペア出力が可能</li> <li>チャネルごとに4種類のカウンタ入力クロック信号から選択</li> <li>コンペアマッチ、インプットキャプチャ、およびアウトプットコンペアのイベントに応答して、割り込み要求の出力が可能</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ウォッチドッグタイマ (WDT)            | <ul><li>14 ビット×1 チャネル</li><li>チャネルごとに 6 種類のカウンタ入力クロック信号から選択</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

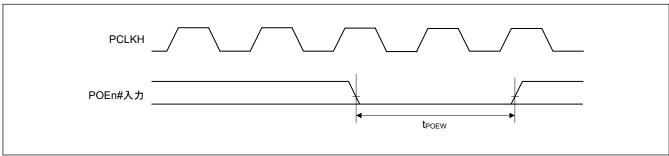

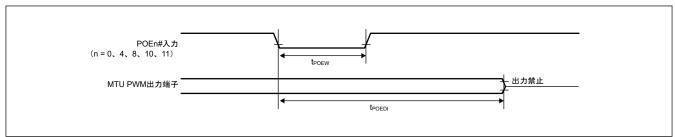

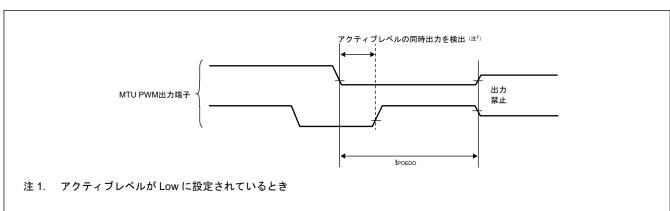

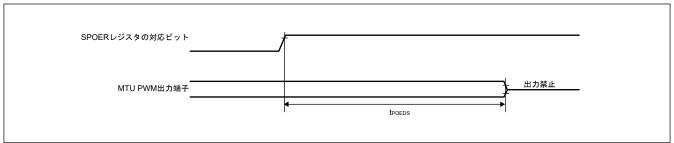

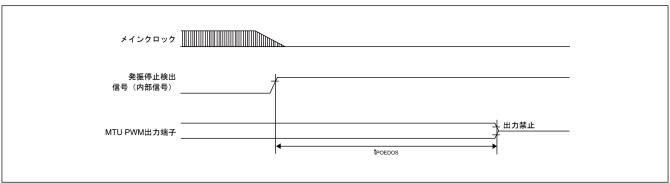

| ポートアウトプットイネーブル 3<br>(POE3)  | <ul> <li>MTU3 波形出力端子のハイインピーダンス制御</li> <li>以下の5つの入力端子からの入力: POE0#、POE4#、POE8#、POE10#、POE11#</li> <li>出力短絡検出(PWM 出力が同時にアクティブレベルになったことを検出)による起動</li> <li>入力クロック発振停止検出、PLL 発振異常検出、2 種類の DSMIF エラー検出、またはソフトウェアによる起動</li> <li>出力制御対象端子をプログラマブルに追加制御可能</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

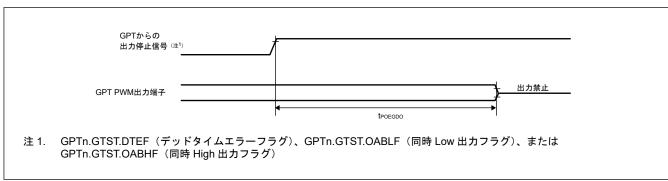

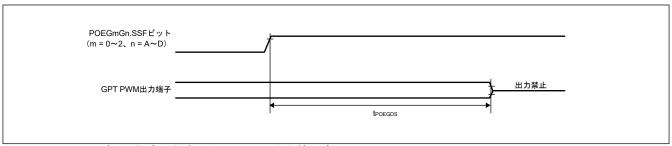

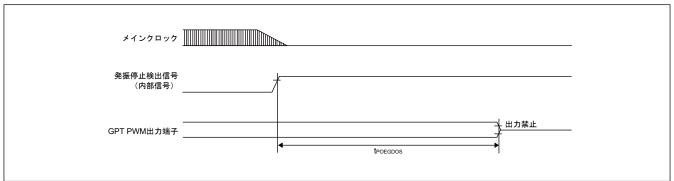

| GPT 用のポートアウトプットイネーブル (POEG) | <ul> <li>GPT 波形出力の出力禁止を制御</li> <li>GTETRG 端子の入力レベル検出による起動</li> <li>GPT からの出力禁止要求による起動</li> <li>発振停止検出、2 種類の DSMIF エラー検出(LLPP のユニットのみ)、またはソフトウェアによる起動</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| リアルタイムクロック (RTC)            | <ul> <li>2000 年から 2099 年までの 100 年カレンダー</li> <li>BCD コード表示</li> <li>クロック源は、メイン発振器を分周</li> <li>うるう年自動補正機能</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 表 1.8 通信インタフェース (1/2)

| 表 1.8 通信インダフェース (1/2)<br>機能            | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

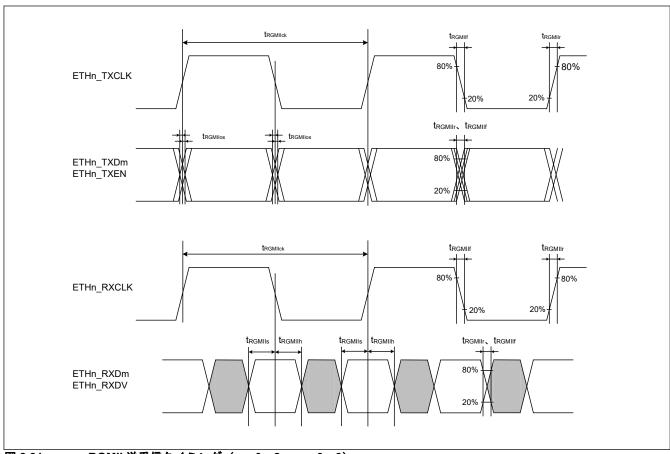

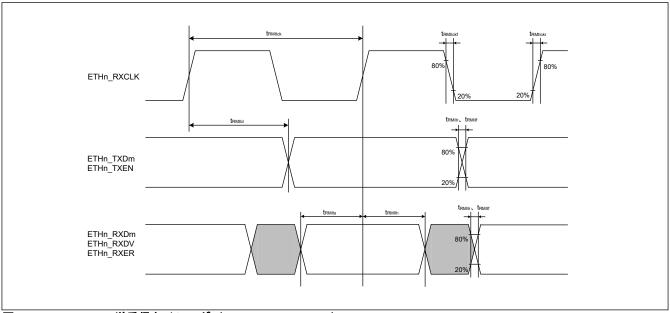

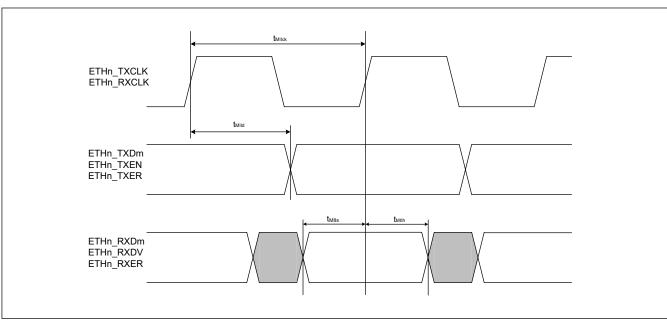

| イーサネット MAC (GMAC) <sup>(注2)</sup>      | <ul> <li>1ポート</li> <li>IEEE802.3</li> <li>IEEE1588-2008</li> <li>EEE 用の IEEE802.3-az-2010</li> <li>10/100/1000 Mbps データ転送をサポート</li> <li>全二重モードおよび半二重モードに対応</li> <li>16 KB までの標準フレームとジャンボフレームの両方をサポートするプログラマブルなフレーム長</li> <li>17 本のアドレスフィルタブロック用 MAC アドレスレジスタ</li> <li>多様なフレキシブルアドレスフィルタモードをサポート</li> <li>先進の IEEE 1588-2002 および 2008 イーサネットフレームタイムスタンプをサポート</li> <li>RMII/RGMII コンバータが MII/RMII/RGMII インタフェースをサポート</li> <li>タイマモジュール</li> </ul>                                              |

| EtherCAT スレーブコントローラ (ESC)<br>(注1) (注2) | <ul> <li>1 チャネル(3 ポート)</li> <li>EtherCAT スレーブコントローラ IP コア(Beckhoff Automation GmbH 製)を搭載</li> <li>MII インタフェースをサポート。イーサネットサブシステムの RGMII コンバータが MII/<br/>RMII インタフェースをサポート。</li> </ul>                                                                                                                                                                                                                                                                                                         |

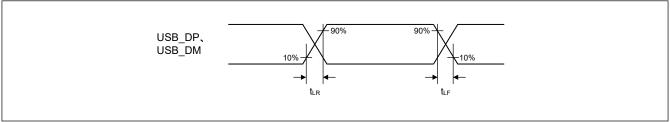

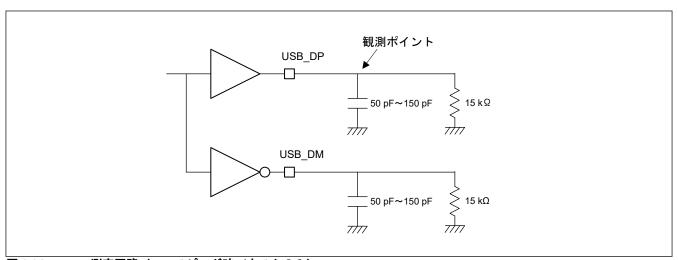

| USB2.0 HS ホスト/ファンクションモ<br>ジュール         | <ul> <li>1ポート</li> <li>USB 2.0 仕様に準拠</li> <li>OTG 対応</li> <li>転送速度         ハイスピード (480 Mbps)、フルスピード (12 Mbps)、およびロースピード (1.5 Mbps、ホストのみ)</li> <li>通信バッファ         <ul> <li>ホストモード用に 1 KB の RAM を内蔵</li> <li>ファンクションモード用に 8 KB の RAM を内蔵</li> </ul> </li> <li>DMAC (2 チャネル)を内蔵</li> </ul>                                                                                                                                                                                                      |

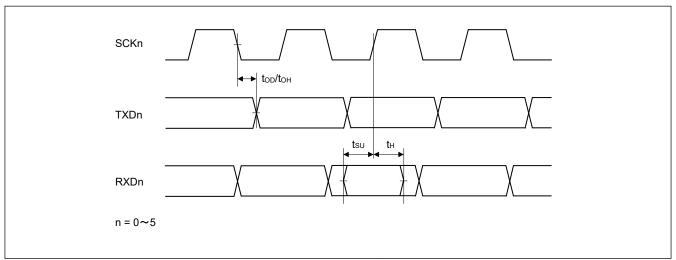

| シリアルコミュニケーションインタフェース (SCI)             | <ul> <li>6 チャネル</li> <li>5 種類の通信モード         <ul> <li>調歩同期式インタフェース</li> <li>8 ビットクロック同期式インタフェース</li> <li>簡易 I2C (マスタのみ)</li> <li>簡易 SPI</li> <li>スマートカードインタフェース</li> </ul> </li> <li>クロック源は、4 つの内部クロック信号から選択</li> <li>内蔵のボーレートジェネレータにより任意のビットレートを設定可能</li> <li>全二重モードおよび半二重モード通信</li> <li>データ長:7~9 ビット (調歩同期式モード)</li> <li>ビットレート変調</li> <li>倍速モード (調歩同期式モード、クロック同期式モード、および簡易 SPI モード)</li> <li>RS-485 ドライバコントロール機能 (調歩同期式モード)</li> <li>自己診断機能を有効にするループバック機能 (調歩同期式モード、クロック同期式モード)</li> </ul> |

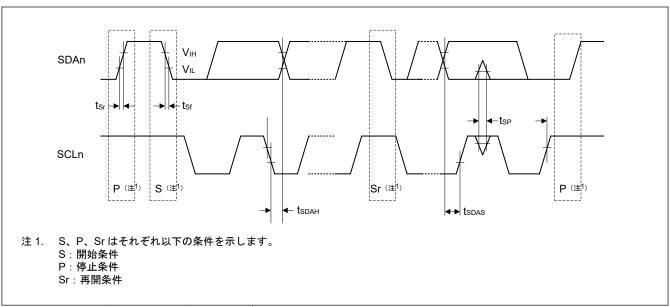

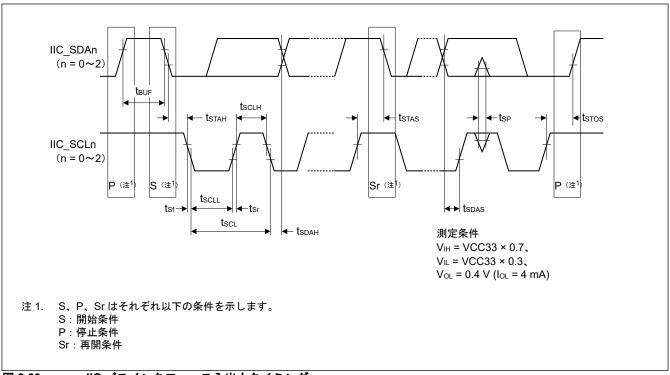

| I <sup>2</sup> C バスインタフェース (IIC)       | <ul> <li>3 チャネル</li> <li>通信フォーマット: I2C バスフォーマットまたは SMBus フォーマット</li> <li>マスタ/スレーブモードを選択可能</li> <li>マルチマスタ対応</li> <li>最大転送速度: 400 kbps (スタンダードモードおよびファストモード)</li> </ul>                                                                                                                                                                                                                                                                                                                       |

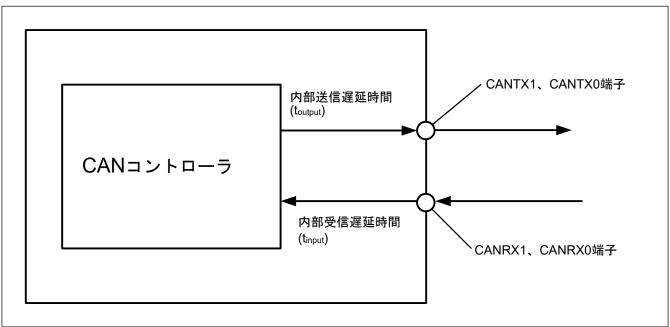

| CAN-FD モジュール (CANFD) <sup>(注3)</sup>   | <ul> <li>● 2 チャネル</li> <li>● CAN-FD ISO 11898-1 (2015) 準拠</li> <li>● 通信速度         <ul> <li>● クラシカル CAN モード: 1 Mbps</li> <li>■ CAN FD モード: 公称ビットレート:最大 1 Mbps データビットレート:最大 8 Mbps</li> </ul> </li> <li>● 合計 192 メッセージバッファ (フレームサイズが 76 バイトの場合)</li> <li>■ 個別バッファ: TX 用 64 個</li> <li>■ 共用バッファ: TX と RX 共用 128 個 (FIFO を含む)</li> <li>● 11 ビットの標準 ID および 18 ビットの拡張 ID の選択可能な ID タイプ</li> <li>● 選択可能なフレームタイプ: データフレームとリモートフレーム</li> <li>● 最大 256 の受信ルール</li> </ul>                               |

#### 表 1.8 通信インタフェース (2/2)

| 機能                             | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

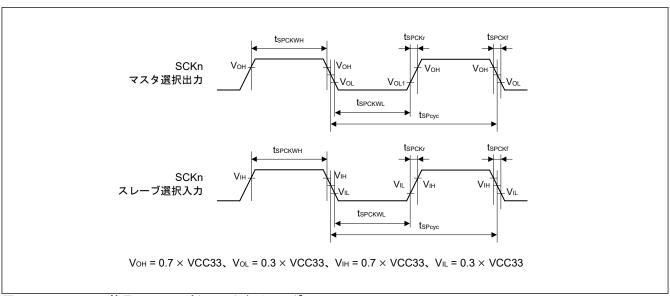

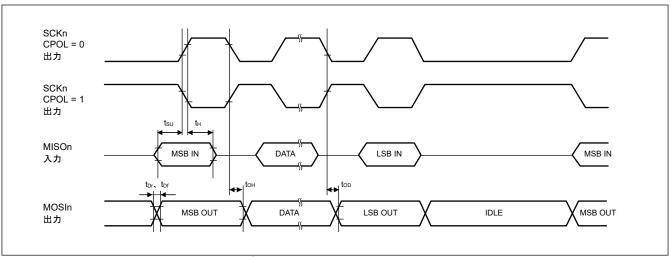

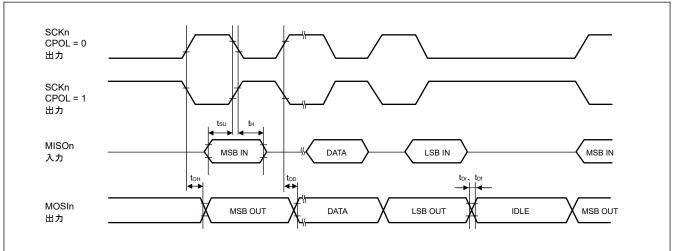

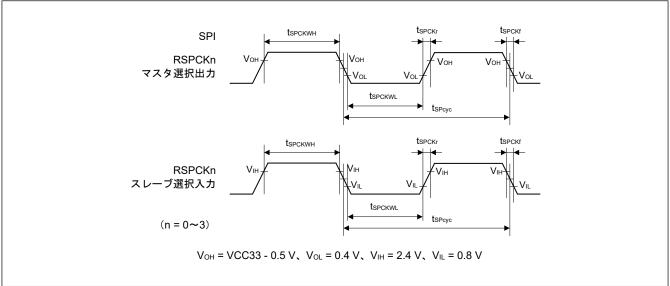

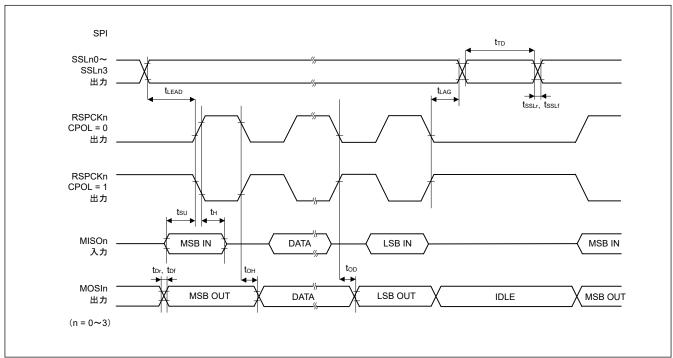

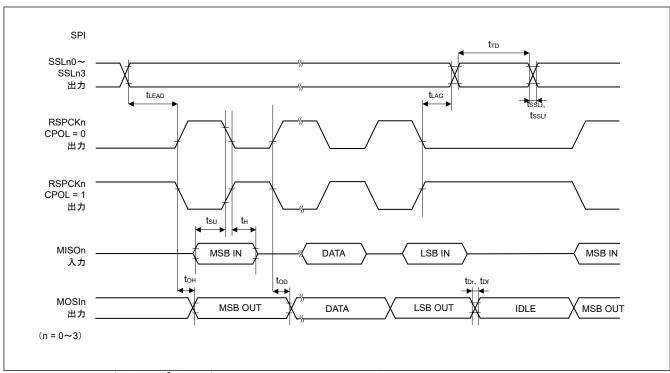

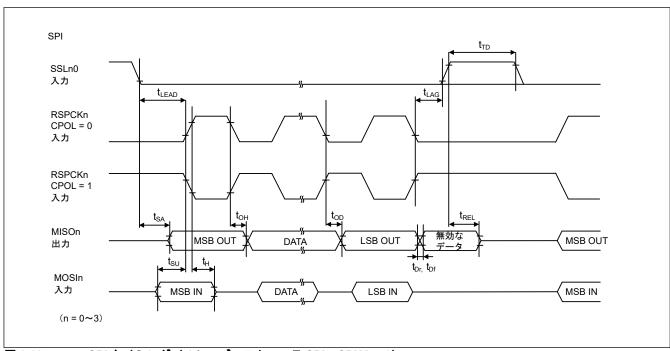

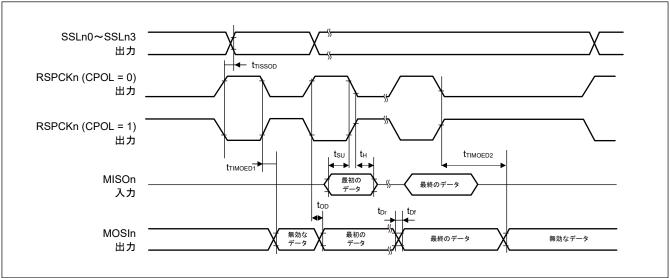

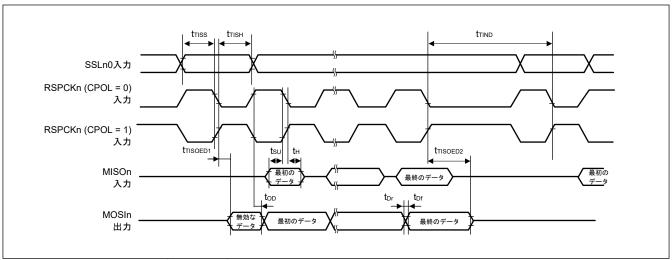

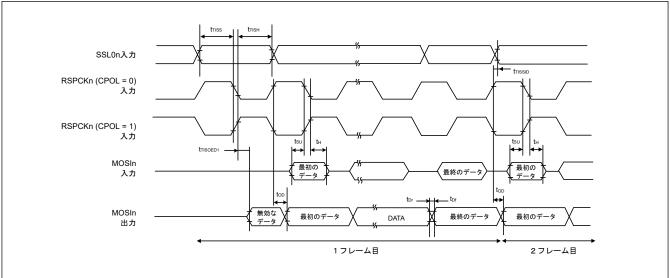

| シリアルペリフェラルインタフェース<br>(SPI)     | <ul> <li>◆ 4 チャネル</li> <li>◆ SPI 転送機能         MOSI (マスタ出力、スレーブ入力)、MISO (マスタ入力、スレーブ出力)、SSL (スレーブ選択)、および RSPCK (SPI クロック) 信号を使用して、マスタまたはスレーブとしてシリアル転送が可能な SPI 動作 (4 線式) またはクロック同期式動作 (3 線式) でシリアル通信が可能</li> <li>◆ データフォーマット         <ul> <li>MSB ファースト/LSB ファーストの切り替え可能</li> <li>転送ビット長を 4 ビット〜32 ビットから選択可能</li> <li>32 ビット×4 ステージ FIFO の送信用パッファと受信用パッファー 1回の転送動作で最大 4 フレームの送受信が可能 (1 フレームは最大 32 ビット)</li> </ul> </li> <li>マスタ受信時、RSPCK は受信パッファフルで自動停止可能</li> </ul>                                                                                                                                                                                    |

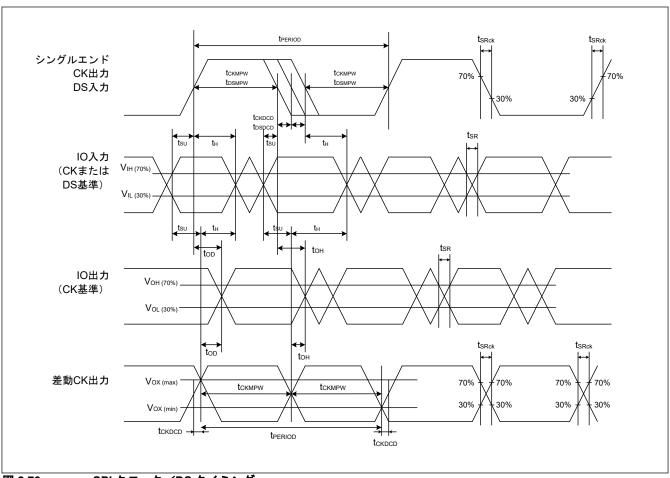

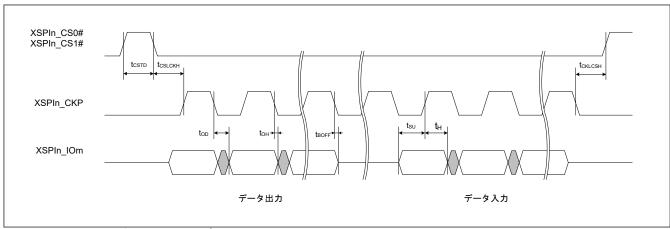

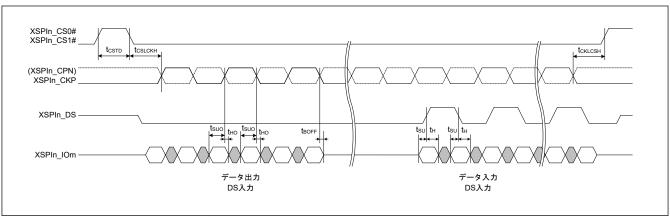

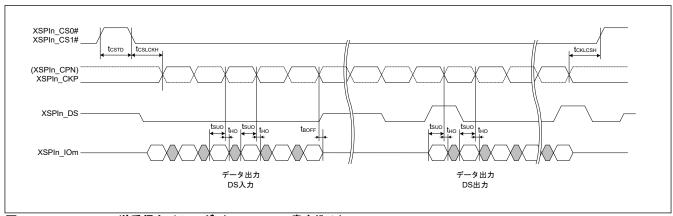

| 拡張シリアルペリフェラルインタフェ<br>ース (xSPI) | <ul> <li>● 2 チャネル</li> <li>● JESD251 準拠</li> <li>● マルチスレーブは最大 2 スレーブ</li> <li>● プロトコルモード: 1/4/8 ピン SDR/DDR 1S-1S-1S、4S-4D-4D、8D-8D-8D</li> <li>● OctaFlash、OctaRAM、HyperFlash、および HyperRAM をサポート</li> <li>● プロトコルモード: QSPI 互換の 2/4 ピン SDR 1S-2S-2S、2S-2S-2S 1S-4S-4S、4S-4S-4S</li> <li>● 設定可能なアドレス長</li> <li>● 設定可能な初期アクセスレイテンシサイクル</li> <li>● XiP モードをサポート</li> <li>● 最大 256 MB アドレス空間をサポート</li> <li>● 低レイテンシのバーストリードプリフェッチ機能</li> <li>● 高スループットのバーストライト高性能バッファ</li> <li>● 最大 4 コマンドまで設定可能なマニュアルコマンド</li> <li>● 出カクロック/入カストローブのポートタイミングシフト</li> <li>● リセット解除後の自動コマンド設定:最大 4 コマンド</li> <li>● xSPI0 には 1.8 V/3.3 V が選択可能、xSPI1 には 3.3 V 固定</li> </ul> |

- 注 1. EtherCAT は、Beckhoff Automation GmbH, Germany の登録商標です。

- 製品には、GMAC および ESC をサポートしない製品があります。 製品には、クラシカル CAN モードのみのものがあります。 注 2.

- 注 3.

#### 表 1.9 アナログ

| 機能                       | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

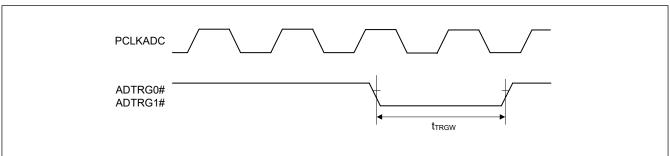

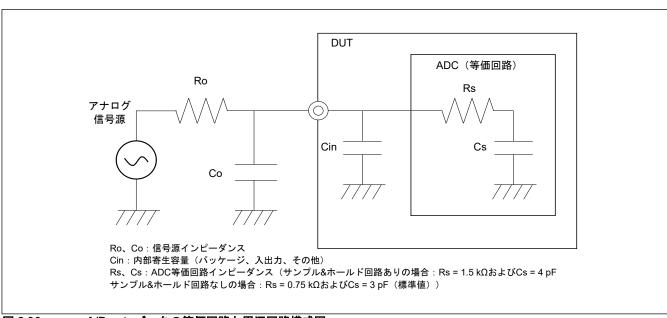

| 12 ビット A/D コンバータ (ADC12) | <ul> <li>12 ビット×2ユニット (ユニット0:4 チャネル、ユニット1:4 チャネル)</li> <li>分解能:12 ビット</li> <li>変換時間         <ul> <li>0.84 μs/チャネル</li> </ul> </li> <li>動作モード             スキャンモード(シングルスキャンモード/連続スキャンモード/3 グループスキャンモード)             グループ優先制御</li> <li>サンプル&amp;ホールド機能             共用のサンプル&amp;ホールド機能             上記に加え、チャネル専用サンプル&amp;ホールド機能を搭載             上記に加え、チャネル専用サンプル&amp;ホールド機能を搭載             (ユニット0、ユニット1ともに3 チャネル)</li> <li>サンプリング可変機能             チャネルごとにサンプリング時間が設定可能</li> <li>ダブルトリガモード(A/D変換データ2重化機能)</li> <li>3 種類のA/D変換開始方法             ソフトウェアトリガ、タイマ(MTU3、ELC)のトリガ、外部トリガ</li> </ul> <li>ELCによるイベントリンク機能をサポート</li> |

| 温度センサユニット (TSU)          | ● 1 チャネル<br>● 相対精度:±1°C (Typ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 表 1.10 産業用インタフェース用ハードウェアアクセラレータ

| 機能                 | 機能説明                                                                                                                                                                                                    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

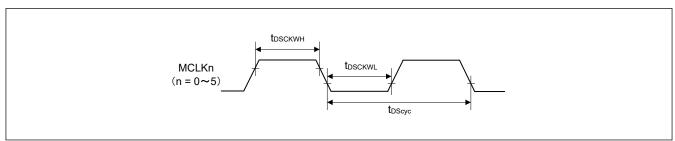

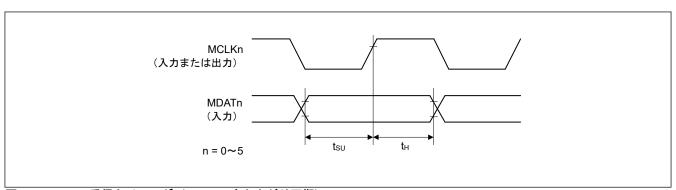

| ΔΣ インタフェース (DSMIF) | <ul> <li>3 チャネル×2ユニット</li> <li>2 入力 (U/V) または3 入力 (U/V/W) 選択可能</li> <li>最大6本の ΔΣ モジュレータを外部から接続可能</li> <li>Sinc フィルタは、1 次、2 次、または3 次を選択可能</li> <li>POE3 と POEG に直接エラー接続</li> <li>電流エラー検出の機能強化</li> </ul> |

| 三角関数ユニット (TFU)     | sin、cos、arctan、hypot_k ( $\sqrt{x^2+y^2}/k$ )の計算     sin と cos の同時計算     arctan と hypot_k の同時計算                                                                                                         |

| エンコーダインタフェース       | <ul> <li>EnDat 2.2 (2ユニット)</li> <li>BiSS-C (2ユニット)</li> <li>A-format (2ユニット)</li> <li>HIPERFACE DSL (2ユニット)</li> <li>ENCOUT (1ユニット)</li> </ul>                                                          |

### 表 1.11 セーフティ

| 機能                   | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| メモリプロテクションユニット (MPU) | <ul> <li>Cortex-R52 MPU         <ul> <li>2 ステージ MPU (EL2 および EL1)</li> <li>各 MPU あたり 24 領域</li> </ul> </li> <li>マスタ MPU         <ul> <li>Cortex-R52 以外のマスタ (DMAC、USB、イーサネット MAC、CoreSight、SHOSTIF) に対するメモリプロテクション</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| レジスタライトプロテクション機能     | プログラムが暴走したときに備え、重要なレジスタの書き換えを防止                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CRC 演算器 (CRC)        | <ul> <li>2 チャネル</li> <li>8、16、または32 ビット単位の任意のデータ長に対して CRC コードを生成</li> <li>以下の4つの多項式から選択可能:         <ul> <li>X<sup>32</sup>+ X<sup>26</sup>+ X<sup>23</sup>+ X<sup>22</sup>+ X<sup>16</sup>+ X<sup>12</sup>+ X<sup>11</sup>+ X<sup>10</sup>+ X<sup>8</sup>+ X<sup>7</sup>+ X<sup>5</sup>+ X<sup>4</sup>+ X<sup>2</sup>+ X + 1 (32-Ethernet)</li> <li>X<sup>32</sup>+ X<sup>28</sup>+ X<sup>27</sup>+ X<sup>26</sup>+ X<sup>25</sup>+ X<sup>23</sup>+ X<sup>22</sup>+ X<sup>20</sup>+ X<sup>19</sup>+ X<sup>18</sup>+ X<sup>14</sup>+ X<sup>13</sup>+ X<sup>11</sup>+ X<sup>10</sup>+ X<sup>9</sup>+ X<sup>8</sup>+ X<sup>6</sup>+ 1 (CRC-32C)</li> <li>X<sup>16</sup>+ X<sup>15</sup>+ X<sup>2</sup>+ 1 (CRC-16)</li> <li>X<sup>16</sup>+ X<sup>12</sup>+ X<sup>5</sup>+ 1 (CRC-CCITT)</li> <li>X<sup>8</sup>+ X<sup>2</sup>+ X + 1 (CRC-8)</li> </ul> </li> </ul> |

| クロックモニタ回路 (CLMA)     | <ul> <li>入力クロック(メインクロック発振器)、PLL 回路、または低速オンチップオシレータからの異常な出力クロック周波数を監視</li> <li>入力クロック発振停止の検出:使用可能</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| データ演算回路 (DOC)        | 16 ビットのデータを比較、加算、または減算する機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 独立周辺モジュール            | <ul> <li>以下のセーフティ機能専用周辺モジュールが利用可能です:</li> <li>GPT: 4 チャネル</li> <li>SCI: 1 チャネル</li> <li>IIC: 1 チャネル</li> <li>SPI: 1 チャネル</li> <li>CRC: 1 ユニット</li> <li>RTC: 1 ユニット</li> <li>GPIO: 通常 GPIO と兼用可能</li> <li>ECC 付き内蔵システム SRAM</li> <li>これらの周辺モジュールは通常の周辺モジュールから独立してマッピングされているため、EL2 MPU によりアクセス保護が可能です。</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### 表 1.12 セキュリティ

| 機能                     | 機能説明                                                                                                                                                                                                                                                                                                                                         |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| セキュリティ <sup>(注1)</sup> | <ul> <li>セキュアブート</li> <li>JTAG 認証</li> <li>暗号化アクセラレータ <ul> <li>対称暗号: CBC/ECB/CTR/GCM/XTS の AES128/192/256 ビット</li> <li>非対称暗号: ECC 256 ビット、RSA 1024/2048/3072 ビット、RSAES-OAEP</li> <li>ハッシュ: SHA-1、SHA-2</li> <li>メッセージ認証: HMAC、CMAC、GMAC</li> <li>署名アルゴリズム: NIST P-256 による ECDSA、RSASSA-PSS、RSASSA-PKCS1</li> </ul> </li> <li>TRNG</li> </ul> |

注 1. 詳しくは、弊社営業担当までお問い合わせください。

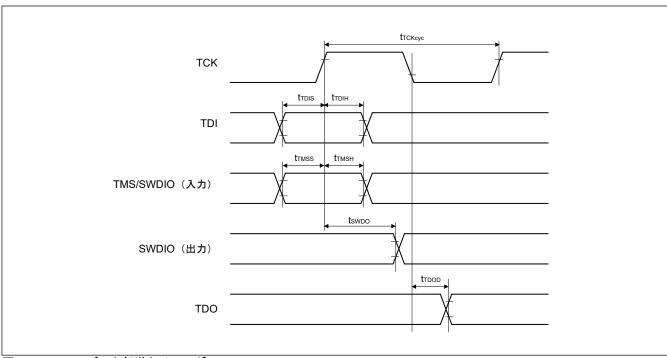

### 表 1.13 デバッグ

| 機能          | 機能説明                                                                                                        |

|-------------|-------------------------------------------------------------------------------------------------------------|

| デバッグインタフェース | <ul> <li>Arm の設計による CoreSight アーキテクチャ</li> <li>JTAG/SWD インタフェースによるデバッグ機能、トレースポートインタフェースによるトレース機能</li> </ul> |

### 表 1.14 外部ホストインタフェース

| 機能                          | 機能説明                                                                                                                                                                                                                                                   |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

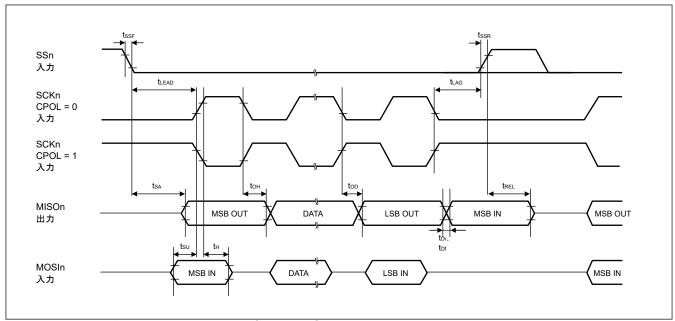

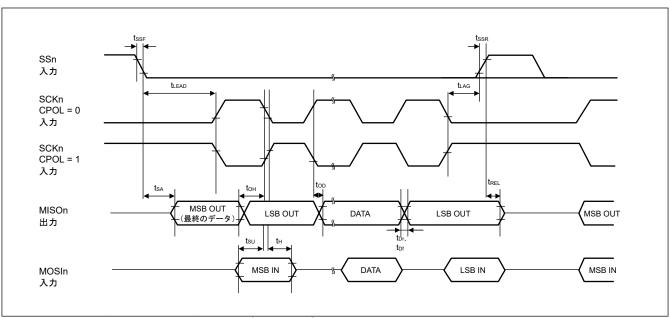

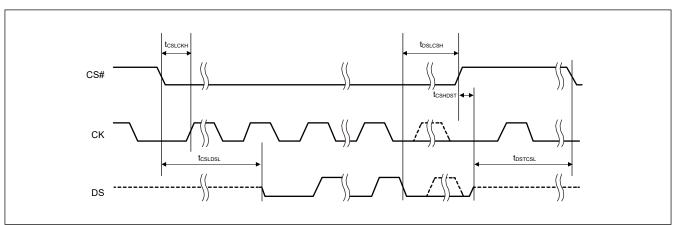

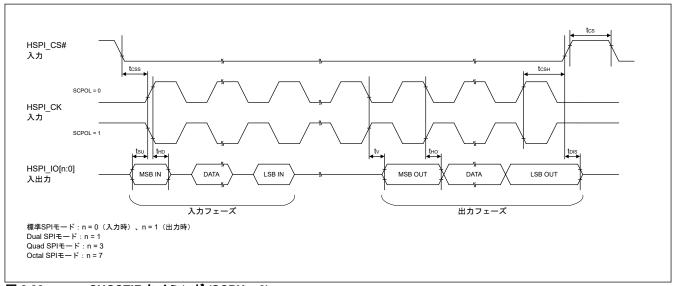

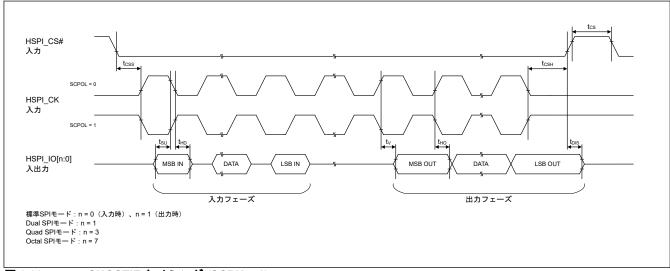

| シリアルホストインタフェース<br>(SHOSTIF) | <ul> <li>スレーブモードでのシリアル通信が可能です。</li> <li>対応インタフェース</li> <li>モトローラシリアルペリフェラルインタフェース(4線式 SPI)</li> <li>デュアル、クワッド、またはオクタル SPI による拡張 SPI モード</li> <li>シリアルクロック極性切り替え</li> <li>シリアルクロック位相切り替え</li> <li>シングルデータ転送</li> <li>データサイズは最大32 ビット×64 バースト</li> </ul> |

| メールボックスおよびセマフォ<br>(MBXSEM)  | <ul> <li>8 つのセマフォ</li> <li>外部ホスト CPU から Cortex-R52 へと Cortex-R52 から外部ホスト CPU への両方向に用いる 4 つの 32 ビットメールボックス</li> <li>外部ホスト CPU と Cortex-R52 の両方から、割り込みの発生とクリアが可能</li> </ul>                                                                              |

### 表 1.15 その他

| 機能    | 機能説明                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 電源電圧  | VDD = 1.1 V (Core)<br>VCC18 = 1.8 V (PLL, USB, ADC, TSU)<br>VCC33 = 3.3 V (I/O, USB)<br>VCC1833 = 1.8 V (RGMII, xSPI) または 3.3 V (RMII/MII, xSPI <sup>(注1)</sup> ) |

| 動作温度  | Tj = -40~+125°C                                                                                                                                                   |

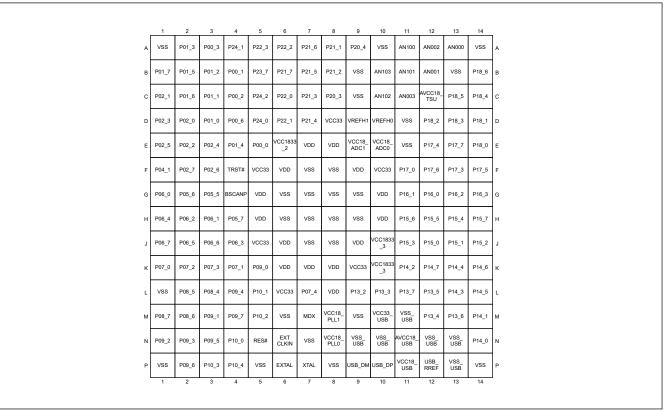

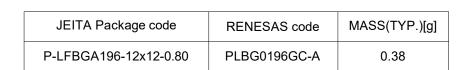

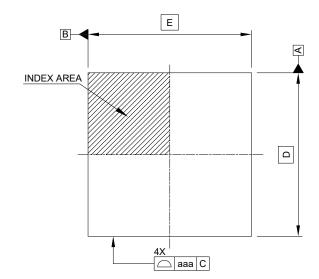

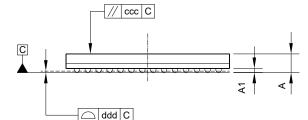

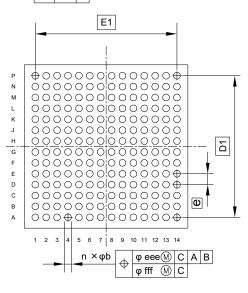

| パッケージ | 196 ピン FBGA(12 mm×12 mm、0.8mm ピッチ)                                                                                                                                |

注 1. 最高 xSPI クロック周波数は 3.3 V 時に 75 MHz です。

# 1.2 製品ラインナップ

表 1.16 に製品ラインナップを示します。

# 表 1.16 製品ラインナップ

| 型名              | パッケージ        | СРИ                 | システム<br>SRAM 容量 | CAN       | EtherCAT | セキュリティ |

|-----------------|--------------|---------------------|-----------------|-----------|----------|--------|

| R9A07G074M08GBG | PLBG0196GC-A | シングル Cortex-<br>R52 | 1.0 MB          | CAN-FD    | 使用可能     | 使用可能   |

| R9A07G074M05GBG | PLBG0196GC-A | シングル Cortex-<br>R52 | 1.0 MB          | クラシカル CAN | 使用不可     | 使用可能   |

| R9A07G074M04GBG | PLBG0196GC-A | シングル Cortex-<br>R52 | 1.0 MB          | CAN-FD    | 使用可能     | 使用不可   |

| R9A07G074M01GBG | PLBG0196GC-A | シングル Cortex-<br>R52 | 1.0 MB          | クラシカル CAN | 使用不可     | 使用不可   |

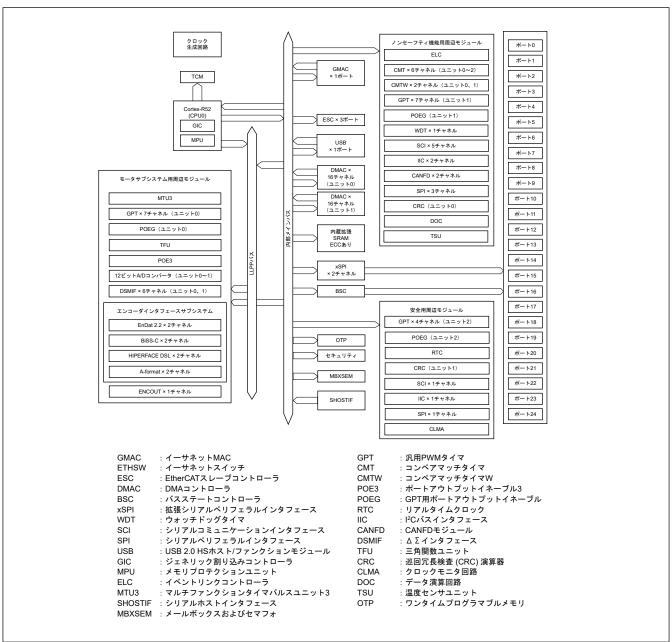

### 1.3 ブロック図

図 1.1 にブロック図を示します。

図 1.1 ブロック図

# 1.4 端子機能

表 1.17 に端子機能を示します。

# 表 1.17 端子機能 (1/7)

| 分類          | 端子名                    | 入出力 | 機能                                                                                                                    |

|-------------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 電源          | VDD                    | 入力  | 電源端子。システムの電源に接続してください。                                                                                                |

|             | VSS                    | 入力  | グランド端子。システムの電源 (0 V) に接続してください。                                                                                       |

|             | VCC1833_2<br>VCC1833_3 | 入力  | 各 I/O ドメインの電源端子。(1.8 V または 3.3 V)                                                                                     |

|             | VCC33                  | 入力  | 入出力端子の電源端子                                                                                                            |

|             | VCC18_PLL0、VCC18_PLL1  | 入力  | 内蔵 PLL 発振器の電源端子                                                                                                       |

|             | AVCC18_TSU             | 入力  | 温度センサユニットの電源端子                                                                                                        |

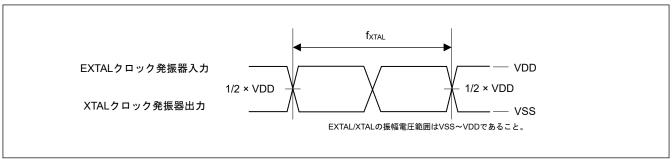

| クロック        | XTAL                   | 出力  | 水晶振動子の接続端子。外部クロック信号を使用する                                                                                              |

|             | EXTAL                  | 入力  | ── 場合、EXTAL 端子は Low にしてください。XTAL 端子は、水晶振動子以外のもので駆動したり、負荷をかけたりしないでください。EXTAL の電圧レベルがコア VDD (1.16 V) を絶対に超えないようにしてください。 |

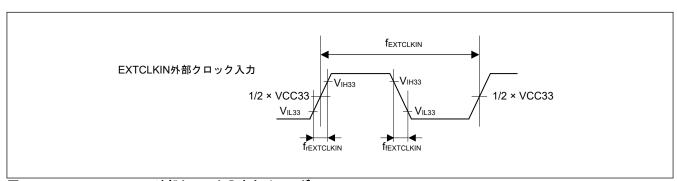

|             | EXTCLKIN               | 入力  | 外部クロック入力端子。水晶振動子を接続する場合は、<br>Low にしてください。                                                                             |

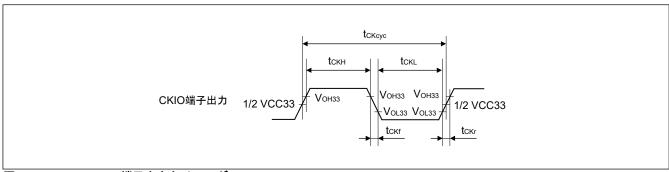

|             | CKIO                   | 出力  | 外部デバイス用の外部バスクロック出力端子                                                                                                  |

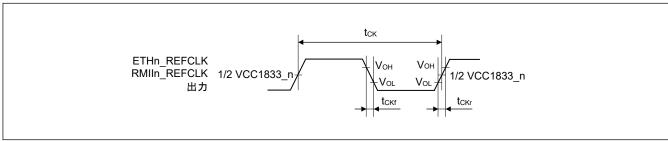

|             | ETH0_REFCLK            | 出力  | EtherPHY 0 用 25 MHz クロック出力端子                                                                                          |

|             | ETH1_REFCLK            | 出力  | EtherPHY 1 用 25 MHz クロック出力端子                                                                                          |

|             | ETH2_REFCLK            | 出力  | EtherPHY 2 用 25 MHz クロック出力端子                                                                                          |

|             | RMII0_REFCLK           | 出力  | RMII0 用 50 MHz クロック出力端子                                                                                               |

|             | RMII1_REFCLK           | 出力  | RMII1 用 50 MHz クロック出力端子                                                                                               |

|             | RMII2_REFCLK           | 出力  | RMII2 用 50 MHz クロック出力端子                                                                                               |

| 動作モードコントロール | MDX                    | 入力  | Lowにしてください。                                                                                                           |

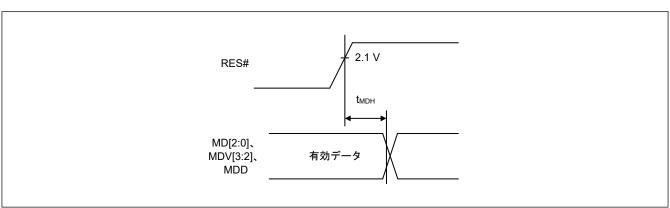

|             | MD0~MD2                | 入力  | 動作モード選択信号の入力端子。この端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                                                              |

|             | MDV2、MDV3              | 入力  | 動作電圧選択信号の入力端子。この端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                                                               |

|             | MDW                    | 入力  | ATCM ウェイトサイクル選択信号の入力端子。この端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                                                      |

|             | MDD                    | 入力  | ハッシュ信号による JTAG 認証有効入力端子。この端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                                                     |

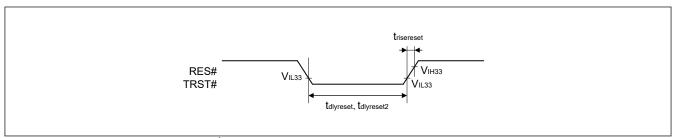

| システムコントロール  | RES#                   | 入力  | リセット信号の入力端子。この端子が Low になると、<br>本 MPU はリセット状態となります。                                                                    |

|             | BSCANP                 | 入力  | バウンダリスキャンイネーブル信号の入力端子。この端子が High になると、バウンダリスキャンが有効となります。バウンダリスキャンを使用しない場合、この端子は Low にしてください。                          |

|             | RSTOUT#                | 出力  | 外部リセット信号の出力端子                                                                                                         |

# 表 1.17 端子機能 (2/7)

| 分類                            |       | 端子名                   | 入出力                                                                     | 機能                                                                    |

|-------------------------------|-------|-----------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------|

| デバッグインタ                       | フェース  | TRST#                 | 入力                                                                      | オンチップエミュレータ用テストリセット端子                                                 |

|                               | TMS   | 入出力                   | オンチップエミュレータ用テストモード選択端子<br>シリアルワイヤデバッグ (SWD) モードでは SWDIO 端<br>子として機能します。 |                                                                       |

|                               |       | TDI                   | 入力                                                                      | オンチップエミュレータ用テストデータ入力端子                                                |

|                               |       | TDO                   | 出力                                                                      | オンチップエミュレータ用テストデータ出力端子                                                |

|                               |       | ТСК                   | 入力                                                                      | オンチップエミュレータ用テストクロック端子<br>シリアルワイヤデバッグ (SWD) モードでは SWCLK<br>端子として機能します。 |

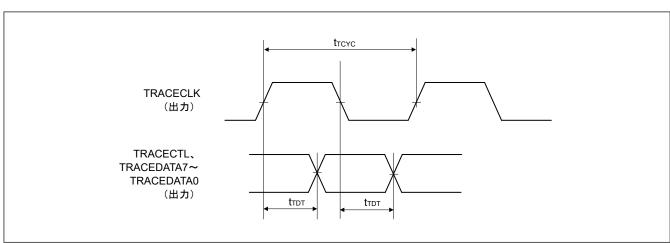

|                               |       | TRACECLK              | 出力                                                                      | トレースデータとの同期用クロック出力端子                                                  |

|                               |       | TRACECTL              | 出力                                                                      | トレースコントロール用イネーブル信号の出力端子                                               |

|                               |       | TRACEDATA0~TRACEDATA7 | 出力                                                                      | トレースデータ出力端子                                                           |

| バスステートコ                       | ントローラ | A25~A0                | 出力                                                                      | アドレス出力端子                                                              |

| (BSC)                         |       | D15~D0                | 入出力                                                                     | データ入出力端子                                                              |

|                               |       | CS0#、CS2#、CS3#、CS5#   | 出力                                                                      | 外部メモリおよびデバイス用のチップセレクト信号の<br>出力端子                                      |

|                               |       | RD#                   | 出力                                                                      | 読み出し進行中を示すストローブ信号の出力端子                                                |

|                               |       | RD/WR#                | 出力                                                                      | 読み出しまたは書き込みアクセスを示すストローブ信<br>号の出力端子                                    |

|                               |       | BS#                   | 出力                                                                      | バスサイクルの開始を示すステータス信号の出力端子                                              |

|                               |       | AH#                   | 出力                                                                      | マルチプレクス I/O インタフェースを使用するデバイ<br>ス用のアドレスホールド信号の出力端子                     |

|                               | WAIT# | 入力                    | バスサイクルにウェイトサイクルを挿入する外部ウェ<br>イトコントロール信号の入力端子                             |                                                                       |

|                               |       | WE0#                  | 出力                                                                      | D7~D0 へのライトストローブ信号の出力端子                                               |

|                               |       | WE1#                  | 出力                                                                      | D15~D8 へのライトストローブ信号の出力端子                                              |

|                               |       | DQMLL                 | 出力                                                                      | D7~D0 へのデータマスクイネーブル信号の出力端子<br>(SDRAM 接続時)                             |

|                               |       | DQMLU                 | 出力                                                                      | D15~D8 へのデータマスクイネーブル信号の出力端子<br>(SDRAM 接続時)                            |

|                               |       | RAS#                  | 出力                                                                      | SDRAM ロウアドレスストローブ信号の出力端子。この端子は SDRAM の RAS#端子に接続してください。               |

|                               | CAS#  | 出力                    | SDRAM カラムアドレスストローブ信号の出力端子。<br>この端子は SDRAM の CAS#端子に接続してください。            |                                                                       |

|                               | CKE   | 出力                    | SDRAM クロックイネーブル信号の出力端子。この端子は SDRAM の CKE 端子に接続してください。                   |                                                                       |

| ダイレクトメモリアクセス<br>コントローラ (DMAC) | DREQ  | 入力                    | 外部デバイス DMA 転送要求信号の入力端子                                                  |                                                                       |

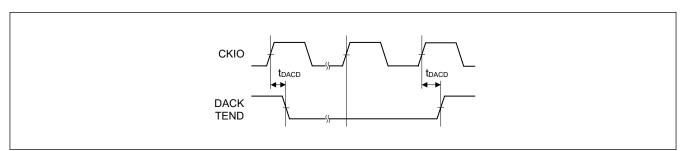

|                               | DACK  | 出力                    | 外部デバイスからの DMA 転送要求を受け付けたこと<br>を示すアクノリッジ信号の出力端子                          |                                                                       |

|                               | TEND  | 出力                    | DMA 転送終了信号の出力端子                                                         |                                                                       |

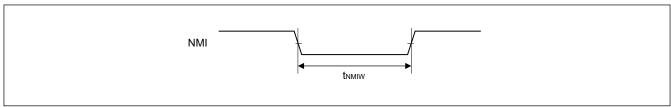

| 割り込み                          |       | NMI                   | 入力                                                                      | ノンマスカブル割り込み要求信号の入力端子                                                  |

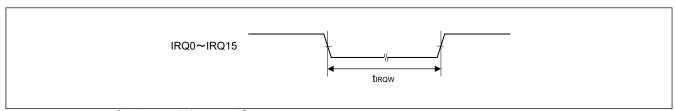

|                               |       | IRQ0~IRQ15            | 入力                                                                      | 外部割り込み要求信号の入力端子                                                       |

# 表 1.17 端子機能 (3/7)

| 分類                                  | 端子名                                         | 入出力 | 機能                                                    |

|-------------------------------------|---------------------------------------------|-----|-------------------------------------------------------|

|                                     | MTIOCOA, MTIOCOB, MTIOCOC, MTIOCOD          | 入出力 | TGRA0~TGRD0 インプットキャプチャ入力、アウトプットコンペア出力、および PWM 出力端子    |

|                                     | MTIOC1A、MTIOC1B                             | 入出力 | TGRA1、TGRB1 インプットキャプチャ入力、アウトプットコンペア出力、および PWM 出力端子    |

|                                     | MTIOC2A、MTIOC2B                             | 入出力 | TGRA2、TGRB2 インプットキャプチャ入力、アウトプットコンペア出力、および PWM 出力端子    |

|                                     | MTIOC3A、MTIOC3B、MTIOC3C、MTIOC3D             | 入出力 | TGRA3~TGRD3 インプットキャプチャ入力、アウトプットコンペア出力、および PWM 出力端子    |

|                                     | MTIOC4A、MTIOC4B、MTIOC4C、<br>MTIOC4D         | 入出力 | TGRA4~TGRD4 インプットキャプチャ入力、アウトプットコンペア出力、および PWM 出力端子    |

|                                     | MTIC5U、MTIC5V、MTIC5W                        | 入力  | TGRU5、TGRV5、TGRW5 インプットキャプチャ入<br>カ、およびデッドタイム補償機能の入力端子 |

|                                     | MTIOC6A、MTIOC6B、MTIOC6C、MTIOC6D             | 入出力 | TGRA6~TGRD6 インプットキャプチャ入力/アウト<br>プットコンペア出力/PWM 出力端子    |

|                                     | MTIOC7A、MTIOC7B、MTIOC7C、MTIOC7D             | 入出力 | TGRA7~TGRD7 インプットキャプチャ入力/アウト<br>プットコンペア出力/PWM 出力端子    |

|                                     | MTIOC8A、MTIOC8B、MTIOC8C、MTIOC8D             | 入出力 | TGRA8~TGRD8 インプットキャプチャ入力/アウト<br>プットコンペア出力/PWM 出力端子    |

|                                     | MTCLKA、MTCLKB、MTCLKC、MTCLKD                 | 入力  | MTU3 用外部クロック入力端子                                      |

| ポートアウトプットイネー<br>ブル 3 (POE3)         | POE0#、POE4#、POE8#、POE10#、<br>POE11#         | 入力  | MTU3 をハイインピーダンス状態にする要求信号の入力端子                         |

| 汎用 PWM タイマ (GPT)/<br>GPT 用のポートアウトプッ | GTETRGA、GTETRGB、GTETRGC、GTETRGD             | 入力  | 外部トリガ入力端子および出力禁止要求の入力端子                               |

| トイネーブル (POEG)                       | GTETRGSA、GTETRGSB                           | 入力  | 外部トリガ入力端子および出力禁止要求の入力端子<br>(SAFETY)                   |

|                                     | GTIOC0A~GTIOC17A、GTIOC0B~<br>GTIOC17B       | 入出力 | インプットキャプチャ入力/アウトプットコンペア出力/PWM 出力端子                    |

|                                     | GTADSML0、GTADSML1、<br>GTADSMP0、GTADSMP1     | 出力  | A/D 変換開始要求監視用の出力端子                                    |

| コンペアマッチタイマ W<br>(CMTW)              | CMTW0_TIC0、CMTW0_TIC1、CMTW1_TIC0、CMTW1_TIC1 | 入力  | CMTW インプットキャプチャ入力端子                                   |

|                                     | CMTW0_TOC0、CMTW0_TOC1、CMTW1_TOC0、CMTW1_TOC1 | 出力  | CMTW アウトプットコンペア出力端子                                   |

| リアルタイムクロック<br>(RTC)                 | RTCAT1HZ                                    | 出力  | RTC 1 Hz 出力端子                                         |

# 表 1.17 端子機能 (4/7)

| 分類                             | 端子名                   | 入出力 | 機能                                                                                                                   |

|--------------------------------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| シリアルコミュニケーショ<br>ンインタフェース (SCI) | SCK0~SCK5             | 入出力 | クロック入出力端子 (クロック同期式モード/簡易 SPI<br>モード/スマートカードモード)                                                                      |

|                                | RXD0~RXD5             | 入力  | 受信データ入力端子(調歩同期式モード/クロック同期<br>式モード/スマートカードモード)                                                                        |

|                                | TXD0~TXD5             | 出力  | 送信データ出力端子(調歩同期式モード/クロック同期<br>式モード/スマートカードモード)                                                                        |

|                                | CTS0#~CTS5#           | 入力  | 送信開始信号の入力端子(調歩同期式モード/クロック同期式モード)、アクティブ Low                                                                           |

|                                | RTS0#~RTS5#           | 出力  | 受信出力端子(調歩同期式モード/クロック同期式モード)、アクティブ Low                                                                                |

|                                | SCL0~SCL5             | 入出力 | I2C クロック入出力端子(簡易 I2C モード)                                                                                            |

|                                | SDA0~SDA5             | 入出力 | I2C データ入出力端子 (簡易 I2C モード)                                                                                            |

|                                | MISO0~MISO5           | 入出力 | スレーブ送信データ入出力端子(簡易 SPI モード)                                                                                           |

|                                | MOSI0~MOSI5           | 入出力 | マスタ送信データ入出力端子(簡易 SPI モード)                                                                                            |

|                                | SS0#~SS5#             | 入力  | チップセレクト入力端子(簡易 SPI モード)、アクティブ Low                                                                                    |

|                                | DE0~DE5               | 出力  | ドライバイネーブル出力端子 (調歩同期式モード)                                                                                             |

| I2C バスインタフェース                  | IIC_SCL0~IIC_SCL2     | 入出力 | クロック入出力端子                                                                                                            |

| (IIC)                          | IIC_SDA0~IIC_SDA2     | 入出力 | データ入出力端子                                                                                                             |

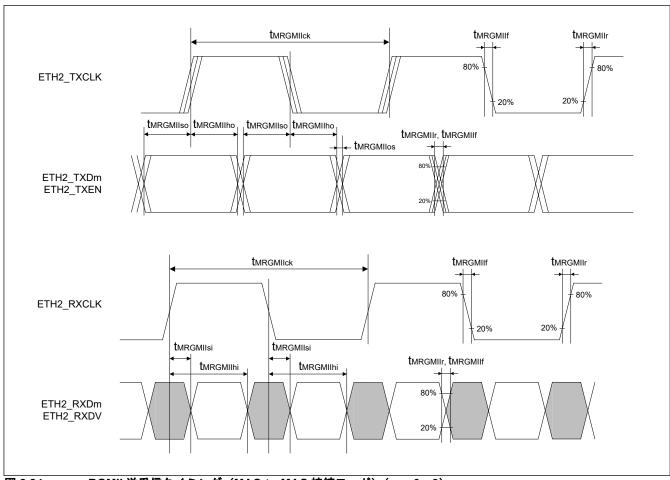

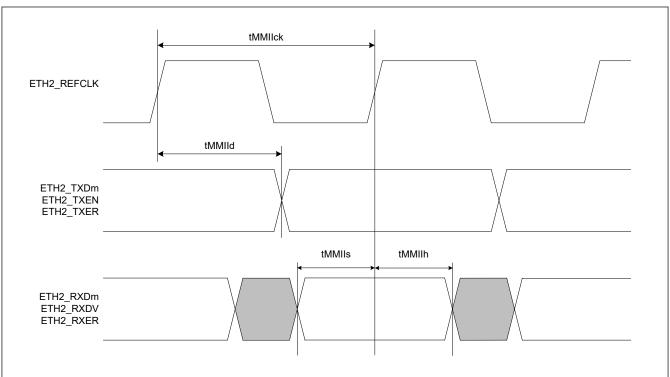

| イーサネット<br>(RGMII はポート 2 でのみち   | ETH0_TXCLK~ETH2_TXCLK | 入出力 | TX クロック入力端子(MII モード)<br>TX クロック出力端子(RGMII モード)                                                                       |

| ポートされます。)<br>                  | ETH0_TXD0~ETH2_TXD0   | 出力  | TX データ 0 出力端子(RGMII、RMII、MII モード)                                                                                    |

|                                | ETH0_TXD1~ETH2_TXD1   | 出力  | TX データ 1 出力端子(RGMII、RMII、MII モード)                                                                                    |

|                                | ETH0_TXD2~ETH2_TXD2   | 出力  | TX データ 2 出力端子(RGMII、MII モード)                                                                                         |

|                                | ETH0_TXD3~ETH2_TXD3   | 出力  | TX データ 3 出力端子(RGMII、MII モード)                                                                                         |

|                                | ETH0_TXEN~ETH2_TXEN   | 出力  | TX データイネーブル出力端子(RMII、MII モード)<br>TX データイネーブル/TX データエラー (TX_CTL) 端<br>子(RGMII モード)                                    |

|                                | ETH2_TXER             | 出力  | TX データエラー出力端子(MII モード)                                                                                               |

|                                | ETH0_RXCLK~ETH2_RXCLK | 入力  | RX クロック入力端子(RGMII、RMII、MII モード)                                                                                      |

|                                | ETH0_RXD0~ETH2_RXD0   | 入力  | RX データ 0 入力端子(RGMII、RMII、MII モード)                                                                                    |

|                                | ETH0_RXD1~ETH2_RXD1   | 入力  | RX データ 1 入力端子(RGMII、RMII、MII モード)                                                                                    |

|                                | ETH0_RXD2~ETH2_RXD2   | 入力  | RX データ 2 入力端子(RGMII、MII モード)                                                                                         |

|                                | ETH0_RXD3~ETH2_RXD3   | 入力  | RX データ 3 入力端子(RGMII、MII モード)                                                                                         |

|                                | ETH0_RXDV~ETH2_RXDV   | 入力  | RX データ有効入力端子(MII モード)<br>キャリア検知/RX データ有効 (CRS_DV) 入力端子<br>(RMII モード)<br>RX データ有効/RX エラー (RX_CTL) 入力端子<br>(RGMII モード) |

|                                | ETH0_RXER~ETH2_RXER   | 入力  | RX データエラー端子(RMII、MII モード)                                                                                            |

|                                | ETH2_CRS              | 入力  | キャリア検知入力端子(MII モード)                                                                                                  |

|                                | ETH2_COL              | 入力  | 衝突検出の入力端子(MII モード)                                                                                                   |

# 表 1.17 端子機能 (5/7)

| 分類                | 端子名                           | 入出力 | 機能                                                         |

|-------------------|-------------------------------|-----|------------------------------------------------------------|

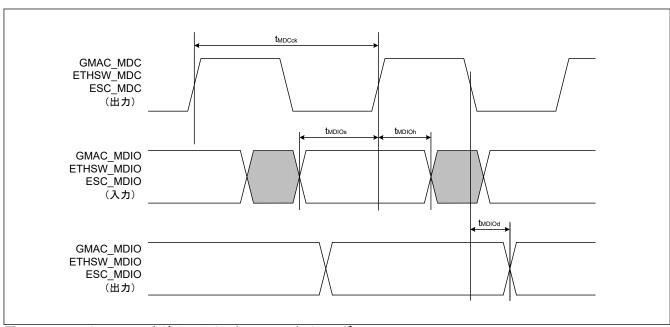

| イーサネット MAC (GMAC) | GMAC_PTPTRG0                  | 入力  | PTP タイマトリガ外部入力端子 0                                         |

|                   | GMAC_PTPTRG1                  | 入力  | PTP タイマトリガ外部入力端子 1                                         |

|                   | GMAC_PTPOUT0~<br>GMAC_PTPOUT3 | 出力  | PTP タイマパルス出力                                               |

|                   | GMAC_MDC                      | 出力  | マネジメントデータクロック出力端子                                          |

|                   | GMAC_MDIO                     | 入出力 | マネジメントデータ入出力端子                                             |

| EtherCAT スレーブコントロ | ESC_LEDRUN                    | 出力  | EtherCAT RUN LED 信号の出力端子                                   |

| ーラ (ESC)          | ESC_IRQ                       | 出力  | EtherCAT IRQ 信号の出力端子                                       |

|                   | ESC_LEDSTER                   | 出力  | EtherCAT デュアルカラーステート LED 信号の出力端<br>子                       |

|                   | ESC_LEDERR                    | 出力  | EtherCAT エラー LED 信号の出力端子                                   |

|                   | ESC_LINKACT0~ESC_LINKACT2     | 出力  | EtherCAT リンク/アクティビティ LED 信号の出力端<br>子                       |

|                   | ESC_SYNC0、ESC_SYNC1           | 出力  | EtherCAT SYNC 信号の出力端子                                      |

|                   | ESC_LATCH0、ESC_LATCH1         | 入力  | EtherCAT LATCH 信号の入力端子                                     |

|                   | ESC_RESETOUT#                 | 出力  | EtherCAT リセット信号の出力端子                                       |

|                   | ESC_I2CCLK                    | 出力  | EtherCAT EEPROM I2C クロック信号の出力端子                            |

|                   | ESC_I2CDATA                   | 入出力 | EtherCAT EEPROM I2C データ信号の入出力端子                            |

|                   | ESC_PHYLINK0~ESC_PHYLINK2     | 入力  | EtherCAT PHY リンクステータス信号の入力端子                               |

|                   | ESC_MDC                       | 出力  | マネジメントデータクロック出力端子                                          |

|                   | ESC_MDIO                      | 入出力 | マネジメントデータ入出力端子                                             |

| USB2.0 ホスト/ファンクシ  | VCC33_USB                     | 入力  | USB 用電源入力端子                                                |

| ョンモジュール<br>       | VCC18_USB                     | 入力  | USB 用電源入力端子                                                |

|                   | VSS_USB                       | 入力  | USB 用グランド入力端子                                              |

|                   | AVCC18_USB                    | 入力  | USB 用アナログ電源入力端子                                            |

|                   | USB_RREF                      | 入力  | USB 用基準電流入力端子。この端子は VSS_USB 端子に 1.8 kΩ (±1%) の抵抗で接続してください。 |

|                   | USB_DP                        | 入出力 | USB バス D+データ入出力端子                                          |

|                   | USB_DM                        | 入出力 | USB バス D-データ入出力端子                                          |

|                   | USB_VBUSEN                    | 出力  | USB 用 VBUS パワーイネーブル信号の出力端子                                 |

|                   | USB_OVRCUR                    | 入力  | USB 用過電流信号の入力端子                                            |

|                   | USB_VBUSIN                    | 入力  | USB ケーブル接続/切断検出の入力端子                                       |

|                   | USB_EXICEN                    | 出力  | OTG 電源 IC 制御出力端子                                           |

|                   | USB_OTGID                     | 入力  | OTG ID 入力端子                                                |

| CANFD モジュール       | CANRX0、CANRX1                 | 入力  | 受信データ入力端子                                                  |

| (CANFD)           | CANTX0、CANTX1                 | 出力  | 送信データ出力端子                                                  |

|                   | CANRXDP0、CANRXDP1             | 出力  | 受信データフェーズ出力端子                                              |

|                   | CANTXDP0、CANTXDP1             | 出力  | 送信データフェーズ出力端子                                              |

# 表 1.17 端子機能 (6/7)

| 分類                             | 端子名                                                                 | 入出力 | 機能                                                                                     |

|--------------------------------|---------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------|

| シリアルペリフェラルイン                   | SPI_RSPCK0~SPI_RSPCK3                                               | 入出力 | クロック入出力端子                                                                              |

| タフェース (SPI)                    | SPI_MOSI0~SPI_MOSI3                                                 | 入出力 | マスタ送信データ入出力端子                                                                          |

|                                | SPI_MISO0~SPI_MISO3                                                 | 入出力 | スレーブ送信データ入出力端子                                                                         |

|                                | SPI_SSL00~SPI_SSL30                                                 | 入出力 | スレーブセレクト信号の入出力端子                                                                       |

|                                | SPI_SSL01~SPI_SSL31,<br>SPI_SSL02~SPI_SSL32,<br>SPI_SSL03~SPI_SSL33 | 出力  | スレーブセレクト信号の出力端子                                                                        |

| 拡張シリアルペリフェラル<br>インタフェース (xSPI) | XSPI0_CKP、XSPI1_CKP、<br>XSPI0_CKN                                   | 出力  | クロック出力端子                                                                               |

|                                | XSPI0_CS0#、XSPI0_CS1#、<br>XSPI1_CS0#                                | 出力  | チップセレクト出力端子                                                                            |

|                                | XSPI0_DS、XSPI1_DS                                                   | 入出力 | リードデータストローブ/ライトデータマスク入出力<br>端子                                                         |

|                                | XSPI0_IO0~XSPI0_IO7、XSPI1_IO0<br>~XSPI1_IO7                         | 入出力 | Data0~Data7 入出力端子                                                                      |

|                                | XSPI0_RESET0#、XSPI0_RESET1#                                         | 出力  | マスタリセットステータス出力端子                                                                       |

|                                | XSPI0_RSTO0#、XSPI0_RSTO1#                                           | 入力  | スレーブリセットステータス入力端子                                                                      |

|                                | XSPI0_INT0#、XSPI0_INT1#                                             | 入力  | 割り込み入力端子                                                                               |

|                                | XSPI0_ECS0#、XSPI0_ECS1#                                             | 入力  | 誤り訂正ステータス入力端子                                                                          |

|                                | XSPI0_WP0#、XSPI0_WP1#                                               | 出力  | 書き込み保護出力端子                                                                             |

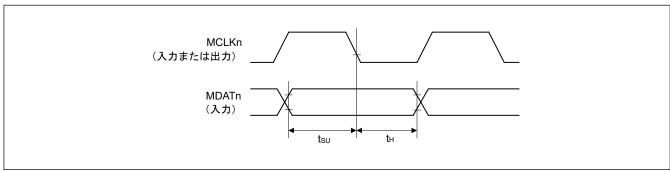

| ΔΣインタフェース (DSMIF)              | MCLK0~MCLK5                                                         | 入出力 | クロック入出力端子                                                                              |

|                                | MDAT0~MDAT5                                                         | 入力  | データ入力端子                                                                                |

| 12 ビット A/D コンバータ<br>(ADC12)    | AN000~AN003、<br>AN100~AN103                                         | 入力  | A/D コンバータ用アナログ入力端子                                                                     |

|                                | ADTRG0#、ADTRG1#                                                     | 入力  | A/D 変換開始のための外部トリガ入力端子                                                                  |

| アナログ電源                         | VCC18_ADC0、VCC18_ADC1                                               | 入力  | 12 ビット A/D コンバータのアナログ電源入力端子。<br>12 ビット A/D コンバータを使用しない場合は、この端<br>子を 1.8 V 電源に接続してください。 |

|                                | VREFH0、VREFH1                                                       | 入力  | 12 ビット A/D コンバータの基準電圧入力端子。12 ビット A/D コンバータを使用しない場合は、この端子を1.8 V 電源に接続してください。            |

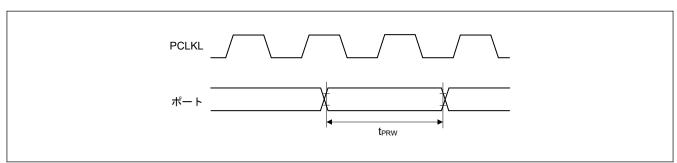

| I/O ポート                        | P00_0~P24_2                                                         | 入出力 | 汎用入出力端子                                                                                |

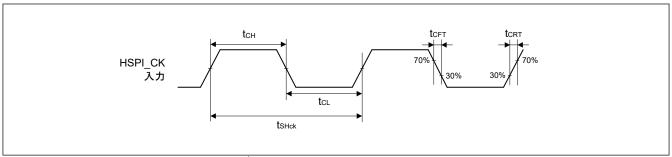

| シリアルホストインタフェ                   | HSPI_CK                                                             | 入力  | クロック入力端子                                                                               |

| ース (SHOSTIF)                   | HSPI_CS#                                                            | 入力  | チップセレクト入力端子                                                                            |

|                                | HSPI_IO0~HSPI_IO7                                                   | 入出力 | Data0~Data7 入出力端子                                                                      |

|                                | HSPI_INT#                                                           | 出力  | 割り込み出力端子                                                                               |

| メールボックス                        | MBX_HINT#                                                           | 出力  | Cortex-R52 からホストへのメールボックスの割り込み<br>出力端子                                                 |

| エンコーダインタフェース                   | ENCIFCK0、ENCIFCK1                                                   | 出力  | エンコーダインタフェースクロック出力端子                                                                   |

| 共通                             | ENCIFOE0、ENCIFOE1                                                   | 出力  | エンコーダインタフェースデータ出力イネーブル端子                                                               |