RA8M2 グループ

ルネサスマイクロコントローラ

R01DS0438JJ0120 Rev.1.20 Aug 27, 2025

高性能な 1 GHz Arm® Cortex®-M85 コア、250 MHz Arm® Cortex®-M33 コア、最大 1 MB のコード MRAM、および ECC を備 えた 2 MB の SRAM。高集積度のレイヤ 3 イーサネットスイッチモジュール、USB 2.0 ハイスピード、CANFD、SDHI、I3C、 オクタ SPI、オンザフライ復号、高度なアナログ機能。Arm® TrustZone と協調して動作する暗号化アクセラレータ、鍵管理 サポート、改ざん検出、および電源分析耐性を備え、セキュア要素機能を有機的に結ぶ統合ルネサスセキュリティ IP。

# 特長

- Arm® Cortex®-M85 コア

- Armv8.1-M アーキテクチャプロファイル

- Armv8-M セキュリティ拡張

- 最高動作周波数:1 GHz

- メモリプロテクションユニット (Arm MPU)− 保護メモリシステムアーキテクチャ (PMSAv8)

- セキュア MPU (MPU S): 8 領域

- 非セキュア MPÙ (MPU NS): 8 領域

- SysTick タイマ

- 2 つの SysTick タイマを搭載: セキュアおよび非セキュアイ

- CPUCLK0 または MOCO 駆動 (8 分周)

- CoreSight<sup>™</sup> ETM-M85

### ■ Arm® Cortex®-M33 コア

- Armv8-M アーキテクチャプロファイル Armv8-M セキュリティ拡張

- Affilyo-M とイュリティが無

最高動作周波数: 250 MHz

メモリプロテクションユニット (Arm MPU)

保護メモリシステムアーキテクチャ (PMSAv8)

セキュア MPU (MPU\_S): 8 領域

非セキュア MPU (MPU\_NS): 8 領域

- SysTick タイマ

- 2つの SysTick タイマを搭載: セキュアおよび非セキュアインスタンス

- CPUCLK1 または MOCO 駆動 (8 分周)

- CoreSight<sup>TM</sup> ETM-M33

### ■メモリ

- 最大 1 MB の MRAM

- 2 MB の SRAM(256 KB の CM85 TCM および 128 KB の CM33 TCM を含む)

• 最大 8 MB のフラッシュメモリ (SiP 製品)

### ■ 接続性

- シリアルコミュニケーションインタフェース (SCI)×10、最大 60 Mbps

- I<sup>2</sup>C バスインタフェース (IIC) × 3

- I<sup>3</sup>C バスインタフェース (I3C)

- シリアルペリフェラルインタフェース (SPI)×2、最大

- 166 Mbps オクタシリアルペリフェラルインタフェース (OSPI) × 2、最大 333 MB/s

• USB 2.0 フルスピードモジュール (USBFS)

- USB 2.0 ハイスピードモジュール (USBHS)

- USB 2.0 ハイスピートモシュール (USBHS)

CAN フレキシブルデータレート (CANFD)×2

レイヤ3 イーサネットスイッチモジュール (ESWM)

SD/MMC ホストインタフェース (SDHI)×2

拡張シリアルサウンドインタフェース (SSIE)×2

パルス密度変調インタフェース (PDMIF)

### ■ アナログ

- 16 ビット A/D コンバータ (ADC16H) × 2、最大 23 チャネル

12 ビット D/A コンバータ (DAC12) × 2

高速アナログコンパレータ (ACMPHS) × 4

- 温度センサ (TSN)

#### ■タイマ

- 高分解能の 32 ビット汎用 PWM タイマ (GPT32)×4 300 MHz での分解能 52 ps

32 ビット汎用 PWM タイマ (GPT32)×10

低消費電力非同期汎用タイマ (AGT)×2

超低消費電力タイマ (ULPT)×2

### ■ セキュリティおよび暗号化

- ルネサスセキュリティ IP (RSIP-E50D)

- Arm<sup>®</sup> TrustZone<sup>®</sup>

- プリビレッジ制御デバイスライフサイクルの管理セキュアブート

- OTP 内の不変ファーストステージブートローダー

- オンザフライ復号 (DOTF)

- 端子機能

- 最大3つの耐タンパー端子

- セキュア端子マルチプレキシング

- HUK のゼロ化

#### ■ システムおよび電源管理

- 低消費電力モード

- バッテリバックアップ機能 (VBATT)

- リアルタイムクロック (RTC) (カレンダー、VBATT 対応)

イベントリンクコントローラ (ELC)

データトランスファコントローラ (DTC) × 2

- DMA コントローラ (DMAC) × 16

- パワーオンリセットプログラマブル電圧検出機能 (PVD) の設定可能

- ・ ウォッチドッグタイマ (WDT) × 2・ 独立ウォッチドッグタイマ (IWDT)

### ■ ヒューマンマシンインタフェース (HMI)

● キャプチャエンジンユニット(CEU)

#### ■ マルチクロックソース

- メインクロック発振器 (MOSC) (8~48 MHz)

- ・ メインクロック発振器 (MOSC) (6 46 MHz)

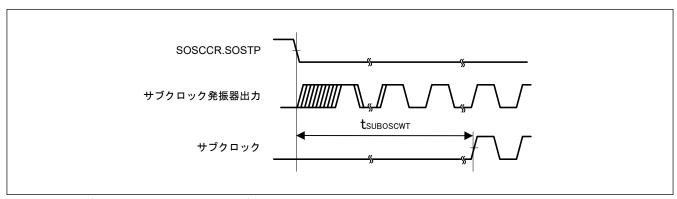

・ サブクロック発振器 (SOSC) (32.768 kHz)

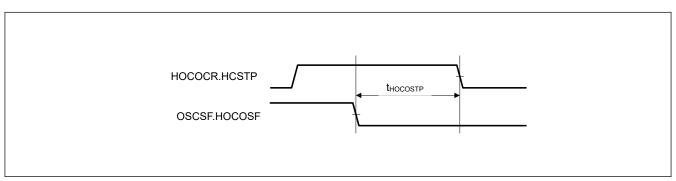

・ 高速オンチップオシレータ (HOCO) (16/18/20/32/48 MHz)

・ ජ・ボインチップオシレータ (MOCO) (8 MHz)

・ ජ・ボインチップオシレータ (LOCO) (32.768 kHz)

- HOCO/MOCO/LOCO に対するクロックトリム機能

- PLL1/PLL2

- クロックアウトのサポート

#### ■ 汎用入出力ポート

● 5 V トレランス、オープンドレイン、入力プルアップ、切り替え可能駆動能力

### ■ 動作電圧

- 標準製品

- VCC/VCC2: 1.62∼3.63 V

- SiP 製品

- VCC: 1.62~3.63 V

- VCC2: 1.70~2.00 V

#### ■ 動作ジャンクション温度およびパッケージ

- Tj =  $0 \, ^{\circ}\text{C} \sim +95 \, ^{\circ}\text{C}$

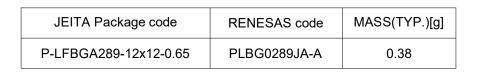

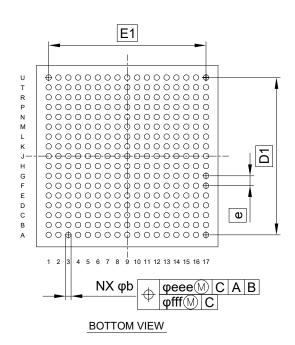

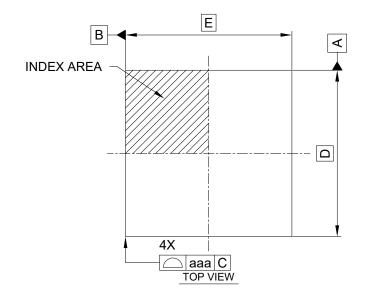

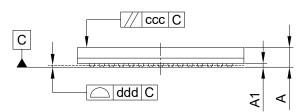

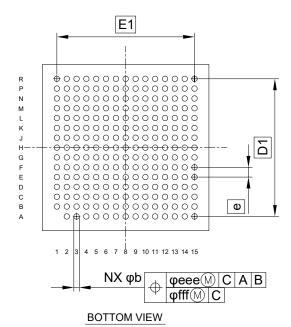

- 1J-V と BGA (12 mm×12 mm、0.65 mm ピッチ) 289 ピン BGA (11 mm×11 mm、0.65 mm ピッチ) 303 ピン BGA (15 mm×15 mm、0.8 mm ピッチ)

- Tj = -40 °C $\sim$ +105 °C

- 289 ピン BGA(12 mm×12 mm、0.65 mm ピッチ) 224 ピン BGA(11 mm×11 mm、0.65 mm ピッチ) 303 ピン BGA(15 mm×15 mm、0.8 mm ピッチ)

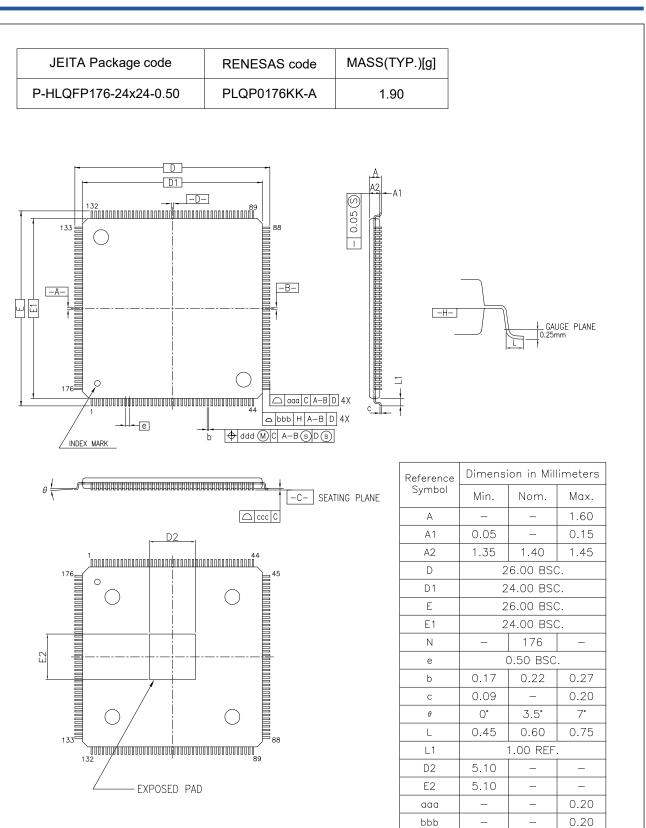

- 305 ピン BOA(13 mm ^ 13 mm, 0.6 mm ピッテ) Tj = -40 °C~+125 °C 289 ピン BGA(12 mm × 12 mm、0.65 mm ピッチ) 224 ピン BGA(11 mm × 11 mm、0.65 mm ピッチ) 176 ピン HLQFP(24 mm × 24 mm、0.5 mm ピッチ)

### 1. 概要

本 MCU は、さまざまなシリーズのソフトウェアと互換性のある Arm®ベースの 32 ビットコアで構成されています。同じ一連のルネサス周辺デバイスを共有することで、設計の拡張性やプラットフォームベースの製品開発の効率が高まります。

本シリーズの MCU は、高性能な Arm<sup>®</sup> Cortex<sup>®</sup>-M85 コア (最高 1 GHz で動作) および Arm<sup>®</sup> Cortex<sup>®</sup>-M33 コア (最高 250 MHz で動作) を内蔵しており、以下の特長があります。

- 最大 1 MB の MRAM

- 2 MB の SRAM(256 KB の CM85 TCM RAM、128 KB の CM33 TCM RAM、1664 KB のユーザー SRAM)

- オクタシリアルペリフェラルインタフェース (OSPI)

- レイヤ3イーサネットスイッチモジュール (ESWM)、USBFS、USBHS、SD/MMC ホストインタフェース

- アナログ周辺機能

- セキュリティ&セーフティ機能

### 1.1 機能の概要

#### 表 1.1 Arm コア

| 機能                                           | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm <sup>®</sup> Cortex <sup>®</sup> -M85 コア | <ul> <li>最高動作周波数: 1 GHz</li> <li>Arm® Cortex®-M85 コア         <ul> <li>リビジョン: (r1p1-00rel0)</li> <li>ARMv8.1-M アーキテクチャプロファイル</li> <li>Armv8-M セキュリティ拡張</li> <li>ANSI/IEEE 規格 754-2008 準拠浮動小数点ユニット (FPU) スカラーの半精度、単精度、および倍精度浮動小数点演算</li> <li>M プロファイルベクタ拡張 (MVE) 整数、半精度、および単精度浮動小数点 MVE (MVE-F)</li> </ul> </li> <li>Arm®メモリプロテクションユニット (Arm MPU)         <ul> <li>保護メモリシステムアーキテクチャ (PMSAv8)</li> <li>セキュア MPU (MPU_S): 8 領域</li> <li>まセキュア MPU (MPU_NS): 8 領域</li> </ul> </li> <li>SysTick タイマ         <ul> <li>2 つの SysTick タイマを搭載: セキュアインスタンス (SysTick_S) と非セキュアインスタンス (SysTick_NS)</li> <li>CPUCLK0 または MOCO 駆動 (8 分周)</li> </ul> </li> <li>CoreSight™ ETM-M85</li> </ul> |

| Arm <sup>®</sup> Cortex <sup>®</sup> -M33 コア | <ul> <li>最高動作周波数: 250 MHz</li> <li>Arm® Cortex®-M33 コア         <ul> <li>リビジョン: (r0p4-00rel2)</li> <li>ARMv8-M アーキテクチャプロファイル</li> <li>Armv8-DSP セキュリティ拡張</li> <li>ANSI/IEEE 規格 754-2008 の単精度浮動小数点数演算に準拠した浮動小数点ユニット (FPU)</li> </ul> </li> <li>Arm®メモリプロテクションユニット (Arm MPU)         <ul> <li>保護メモリシステムアーキテクチャ (PMSAv8)</li> <li>セキュア MPU (MPU_S): 8 領域</li> </ul> </li> <li>SysTick タイマ</li> <li>2 つの SysTick タイマを搭載: セキュアインスタンス (SysTick_S) と非セキュアインスタンス (SysTick_NS)</li> <li>CPUCLK1 または MOCO 駆動 (8 分周)</li> </ul> <li>CoreSight™ ETM-M33</li>                                                                                                                             |

#### 表 1.2 メモリ (1/2)

| 機能       | 機能の説明              |

|----------|--------------------|

| コード MRAM | 最大 1 MB のコード MRAM。 |

# 表 1.2 メモリ (2/2)

| 機能         | 機能の説明                                                   |

|------------|---------------------------------------------------------|

| フラッシュメモリ   | システムインパッケージ (SiP) 最大 8 MB のシリアルフラッシュメモリ。                |

| オプション設定メモリ | オプション設定メモリは、MCU のリセット後の状態を決定します。                        |

| SRAM       | 誤り訂正コード (ECC) を備えた高速 SRAM を内蔵しています。                     |

| ОТР        | 内蔵 OTP はファーストステージブートローダー (FSBL) を含みます。<br>汎用 96 バイト OTP |

### 表 1.3 システム

| 機能                   | 機能の説明                                                                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 動作モード                | <ul> <li>3 種類の動作モード:</li> <li>シングルチップモード</li> <li>JTAG ブートモード</li> <li>SCI/USB ブートモード</li> </ul>                                                                                                                                          |

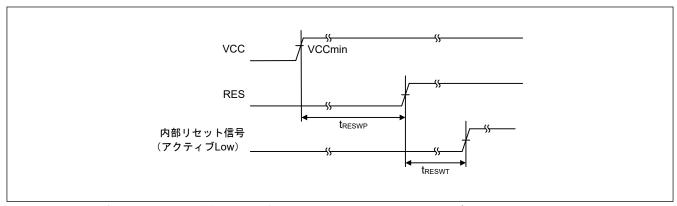

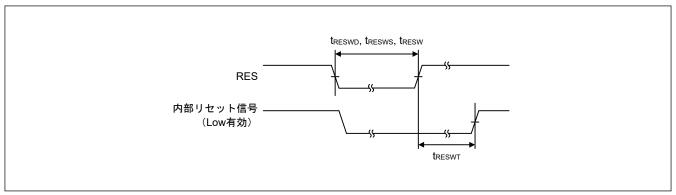

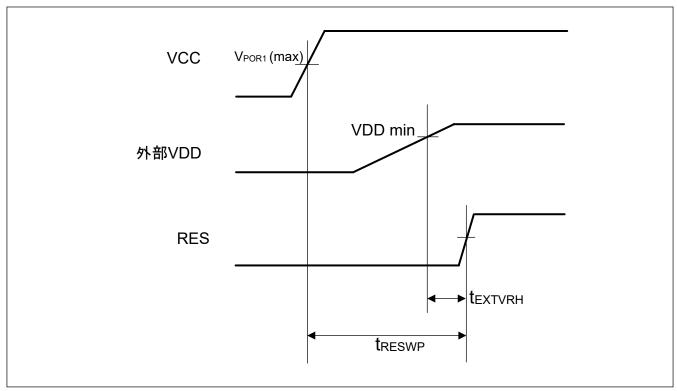

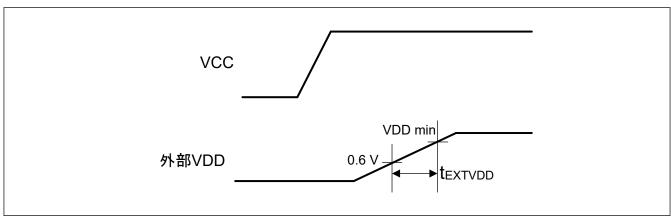

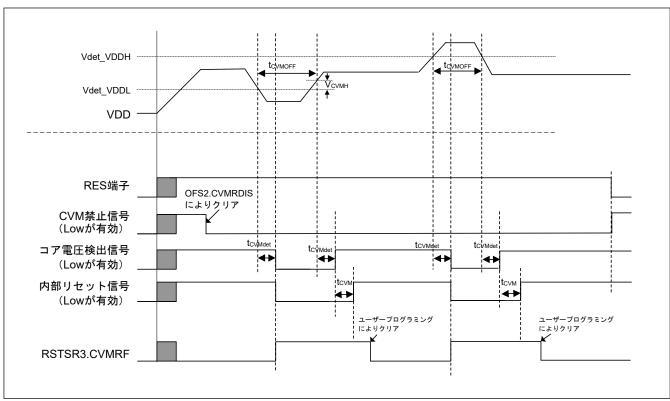

| リセット                 | 本 MCU は以下の 21 種類のリセットをサポートしています。                                                                                                                                                                                                          |

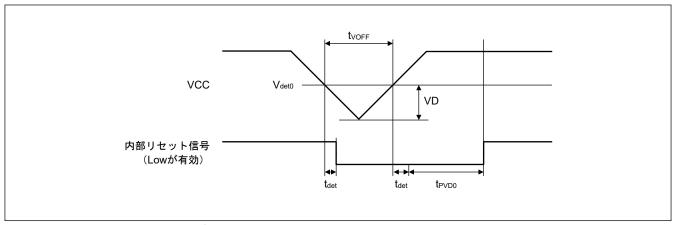

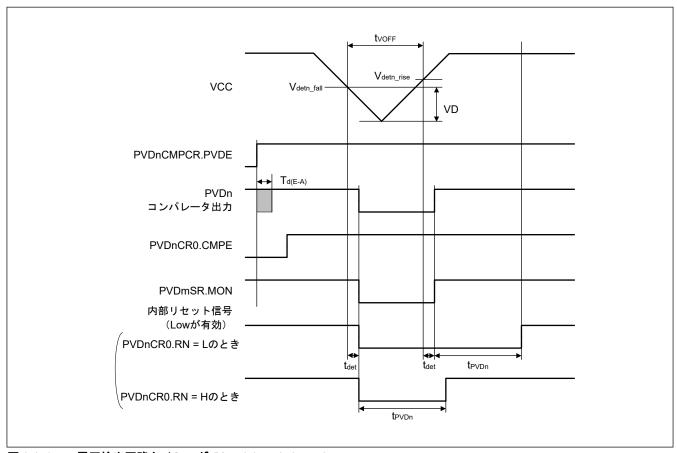

| プログラマブル電圧検出 (PVD)    | プログラマブル電圧検出 (PVD) モジュールは、VCC 端子への入力電圧レベルを監視します。検出レベルはレジスタ設定で選択できます。PVD モジュールは、5 つの独立した電圧監視回路 (PVD0, PVD1, PVD2, PVD4, PVD5) から構成されています。これらの PVD は VCC 端子への入力電圧レベルを測定します。PVD のレジスタは、アプリケーションの設定により、さまざまな電圧しきい値で VCC 端子への入力電圧の変動の検出を設定できます。 |

| クロック                 | <ul> <li>メインクロック発振器 (MOSC)</li> <li>サブクロック発振器 (SOSC)</li> <li>高速オンチップオシレータ (HOCO)</li> <li>中速オンチップオシレータ (MOCO)</li> <li>低速オンチップオシレータ (LOCO)</li> <li>PLL1/PLL2</li> <li>クロックアウトのサポート</li> </ul>                                           |

| クロック周波数精度測定回路 (CAC)  | クロック周波数精度測定回路 (CAC) は、測定の対象となるクロック (測定対象クロック) に対して、測定の基準となるクロック (測定基準クロック) で生成した時間内のクロックのパルスを数え、そのパルス数が許容範囲内にあるか否かで精度を判定します。測定終了時、または測定基準クロックで生成した時間内のパルスの数が許容範囲内にないとき、割り込み要求が発生します。                                                      |

| 割り込みコントローラユニット (ICU) | 割り込みコントローラユニット (ICU) は、ネスト型ベクタ割り込みコントローラ (NVIC)、DMA<br>コントローラ (DMAC) モジュール、およびデータトランスファコントローラ (DTC) モジュール<br>にリンクされるイベント信号を制御します。ICU はノンマスカブル割り込みも制御します。                                                                                  |

| 低消費電力モード             | 消費電力は、以下に示す複数の方法で低減できます。その方法には、クロック分周器の設定、<br>EBCLK 出力制御、SDCLK 出力制御、モジュール停止、パワーゲート制御、通常動作時の動作電力制御モードの選択、低消費電力モードやプロセッサ低消費電力モードへの遷移があります。                                                                                                  |

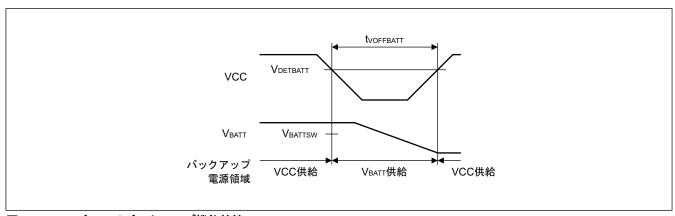

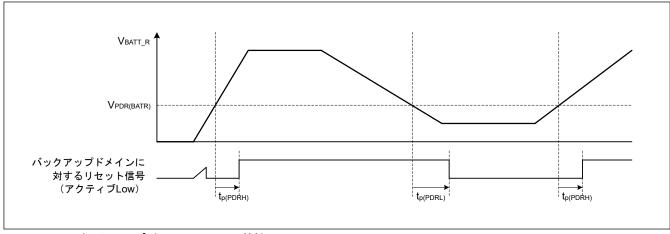

| バッテリバックアップ機能         | バッテリバックアップ機能により、バッテリによる部分電力供給が可能です。バッテリ電源領域に含まれるものには、RTC、SOSC、バックアップレジスタ、改ざん検出、VBATT_R電圧降下検出、および VCC/VBATT 切り替えがあります。                                                                                                                     |

| レジスタライトプロテクション       | レジスタライトプロテクション機能は、ソフトウェアエラーによって重要なレジスタが書き換えられないように保護します。保護対象のレジスタは、プロテクトレジスタ(PRCR_SとPRCR_NS)で設定します。                                                                                                                                       |

| メモリプロテクションユニット (MPU) | すべてのバスマスタには、メモリプロテクションユニット (MPU) があります。                                                                                                                                                                                                   |

# 表 1.4 イベントリンク

| 機能                  | 機能の説明                                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------|

| イベントリンクコントローラ (ELC) | イベントリンクコントローラ (ELC) は、さまざまな周辺モジュールで発生するイベント要求をソース信号として使用し、それらのモジュールを別のモジュールと接続することによって、CPUを介さずにモジュール間の直接リンクを実現します。 |

# 表 1.5 ダイレクトメモリアクセス (1/2)

| 機能 | 機能の説明                                                       |

|----|-------------------------------------------------------------|

|    | データトランスファコントローラ (DTC) モジュールは、割り込み要求によって起動するとデータ<br>転送を行います。 |

# 表 1.5 ダイレクトメモリアクセス (2/2)

| 機能                | 機能の説明                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------|

| DMA コントローラ (DMAC) | 8 チャネルのダイレクトメモリアクセスコントローラ (DMAC) は CPU を介さずにデータ転送が可能です。DMA 転送要求が発生すると、DMAC は転送元アドレスに格納されているデータを転送先アドレスへ転送します。 |

# 表 1.6 外部パスインタフェース

| 機能   | 機能の説明                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部バス | <ul> <li>CS 領域 (ECBI): 外部デバイス(外部メモリインタフェース)を接続</li> <li>SDRAM 領域 (ECBI): SDRAM(外部メモリインタフェース)を接続</li> <li>OSPI0 領域 (OSPI0BI): OSPI0(外部デバイスインタフェース)を接続</li> <li>OSPI1 領域 (OSPI1BI): OSPI1(外部デバイスインタフェース)を接続</li> </ul> |

### 表 1.7 タイマ

| 機能                          | 機能の説明                                                                                                                                                                                                                                                                                  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

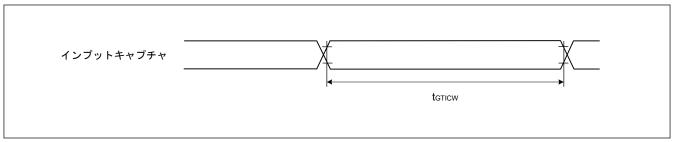

| 汎用 PWM タイマ (GPT)            | 汎用 PWM タイマ (GPT) は、GPT32 × 14 チャネルの 32 ビットタイマです。PWM 波形はアップカウンタ、ダウンカウンタ、またはその両方を制御することにより生成が可能です。さらに、ブラシレス DC モーターを制御するために、PWM 波形の生成が可能です。GPT は、汎用タイマとしても使用できます。                                                                                                                        |

| PWM 遅延生成回路 (PDG)            | PWM 遅延生成回路 (PDG) は、GPT に接続できる 4 チャネルの遅延回路を備えています。PDG は、GPT323 を介した GPT320 に対する PWM 出力の立ち上がり/立ち下がりエッジタイミングを制御できます。                                                                                                                                                                      |

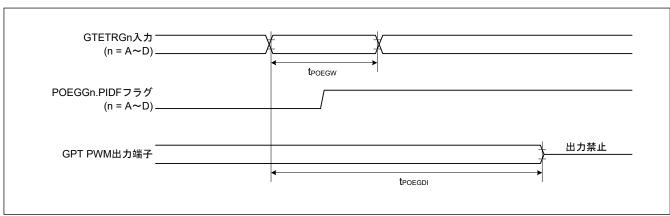

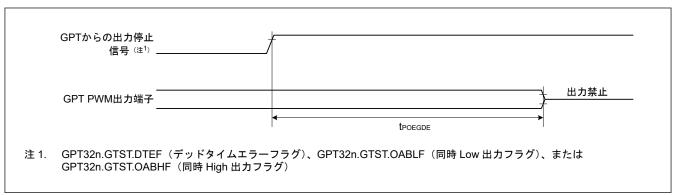

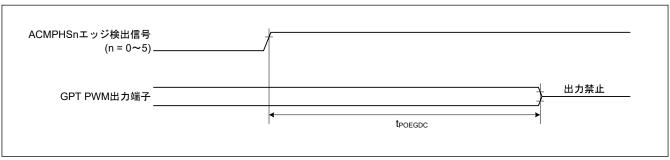

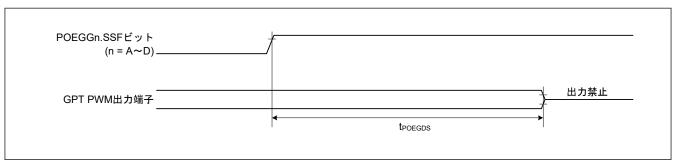

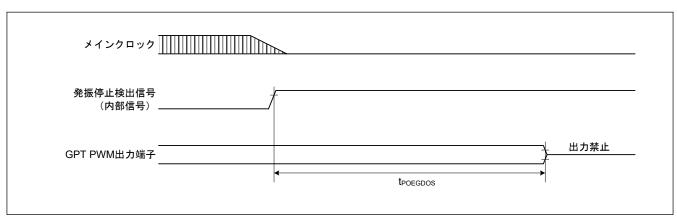

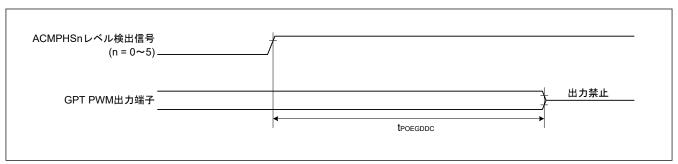

| GPT 用のポートアウトプットイネーブル (POEG) | ポートアウトプットイネーブル (POEG) は、汎用 PWM タイマ (GPT) の出力端子を出力禁止状態にすることができます。                                                                                                                                                                                                                       |

| 低消費電力非同期汎用タイマ (AGT)         | 低消費電力非同期汎用タイマ (AGT) は、パルス出力、外部パルスの幅または周期の測定、および外部イベントのカウントに利用可能な 16 ビットのタイマです。このタイマは、リロードレジスタとダウンカウンタで構成されています。これらのリロードレジスタとダウンカウンタは、同一アドレスに配置され、AGT レジスタでアクセス可能です。                                                                                                                    |

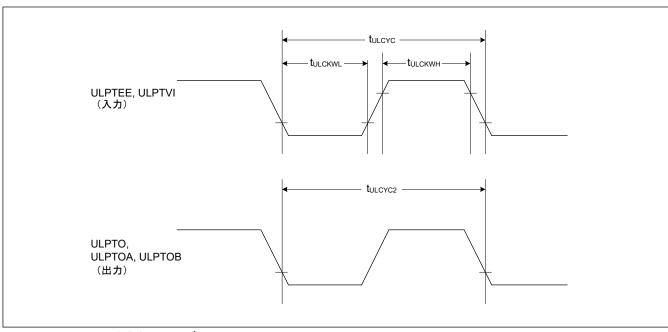

| 超低消費電力タイマ (ULPT)            | 超低消費電力タイマ (ULPT) は、パルス出力または外部イベントのカウントに使用可能な 32 ビットタイマです。この 32 ビットタイマは、リロードレジスタとダウンカウンタで構成されています。これらのリロードレジスタとダウンカウンタは、同一アドレスに配置され、ULPTCNT レジスタでアクセス可能です。                                                                                                                              |

| リアルタイムクロック (RTC)            | リアルタイムクロック (RTC) には、カレンダーカウントモードとバイナリカウントモードの 2 種類のカウントモードがあり、レジスタの設定を切り替えることにより使用します。カレンダーカウントモードでは、RTC は 2000 年から 2099 年の 100 年間のカレンダーを保持し、うるう年の日付を自動補正します。バイナリカウントモードでは、RTC は秒をカウントし、その情報をシリアル値として保持します。バイナリカウントモードは、西暦以外のカレンダーに使用可能です。                                             |

| ウォッチドッグタイマ (WDT)            | ウォッチドッグタイマ (WDT) は 14 ビットのダウンカウンタです。システムが暴走すると WDT をリフレッシュできなくなるため、カウンタがアンダーフローした際に MCU をリセットするのに使用できます。さらに、WDT はノンマスカブル割り込みまたはアンダーフロー割り込みを発生させるのに使用できます。                                                                                                                              |

| 独立ウォッチドッグタイマ (IWDT)         | 独立ウォッチドッグタイマ (IWDT) には、14 ビットのダウンカウンタがあり、ダウンカウンタのアンダーフロー時のリセット出力によって、MCU をリセットします。代替的には、カウンタのアンダーフロー時の割り込み要求の発生を選択できます。これにより、リフレッシュインターバルを考慮して、プログラムの暴走を検出できます。IWDT には、次の2種類のスタートモードがあります。オートスタートモードでは、リセット状態の解除後にカウントを自動的に開始します。また、レジスタスタートモードでは、リフレッシュ(特定のレジスタへの書き込み)により、カウントを開始します。 |

# 表 1.8 通信インタフェース (1/2)

| 機能                                                            | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| シリアルコミュニケーションインタフェース (SCI)                                    | <ul> <li>シリアルコミュニケーションインタフェース (SCI) × 10 チャネルには、調歩同期式および同期式のシリアルインタフェースがあります。</li> <li>■ 調歩同期式インタフェース (UART および調歩同期式通信インタフェースアダプタ (ACIA))</li> <li>● 8 ビットクロック同期式インタフェース</li> <li>● 簡易 IIC (マスタのみ)</li> <li>● 簡易 SPI</li> <li>● スマートカードインタフェース</li> <li>● でンチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェース</li> <li>● でリチェスタインタフェースは、電子信号と伝送プロトコルに関して ISO/IEC 7816-3 規格に準拠しています。すべてのチャネルは FIFO バッファを内蔵しており、連続した全二重通信が可能です。また、内蔵のボーレートジェネレータを用いて、データ転送速度の個別設定が可能です。また、内蔵のボーレートジェネレータを用いて、データ転送速度の個別設定が可能です。</li> <li>本 MCU では、最大レートがサポートされています。実際のレートについては、電気的特性を参照してください。</li> </ul> |

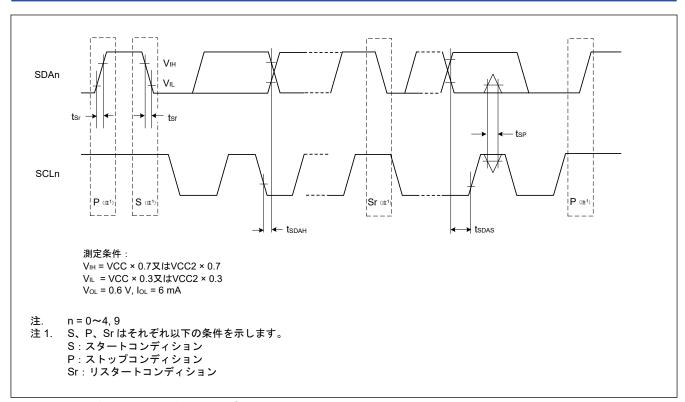

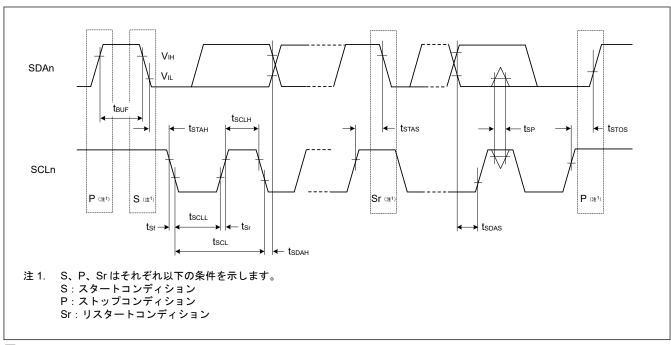

| I <sup>2</sup> C バスインタフェース (IIC)                              | $I^2$ C バスインタフェース (IIC) には $3$ チャネルあります。IIC モジュールは、NXP 社の $I^2$ C (InterIntegrated Circuit) バスインタフェース方式に準拠しており、そのサブセット機能を備えています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

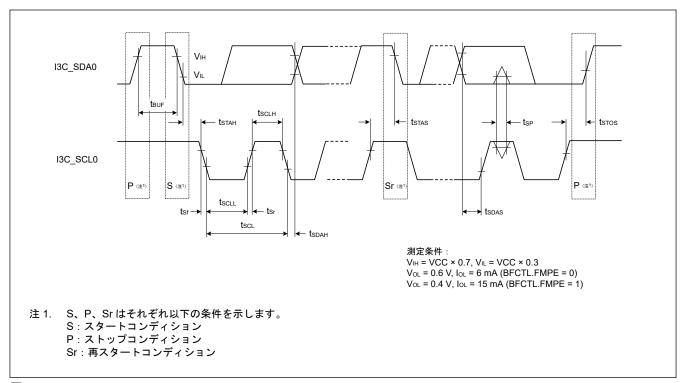

| I3C バスインタフェース (I3C)                                           | I3C バスインタフェース (I3C) には 1 チャネルあります。I3C モジュールは、NXP 社の I <sup>2</sup> C (Inter-Integrated Circuit) および MIPI 社の I3C バスインタフェース方式に準拠しており、それらのサブセット機能を備えています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

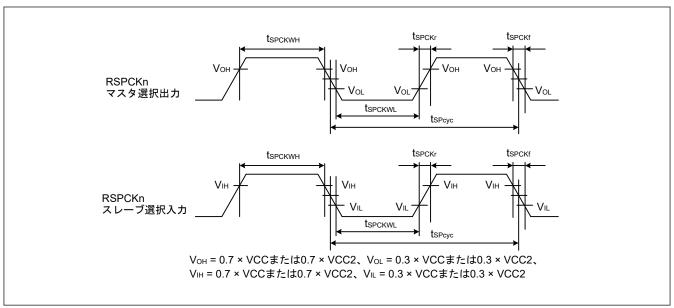

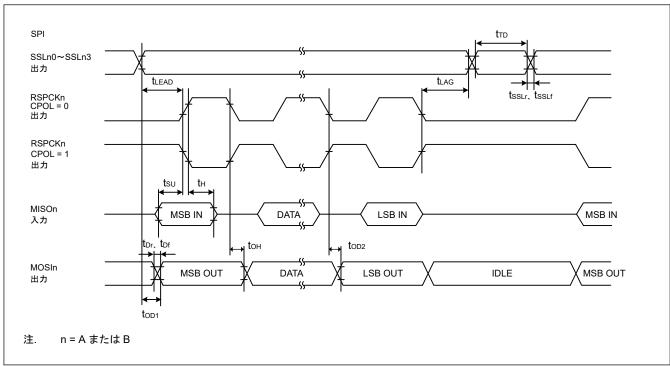

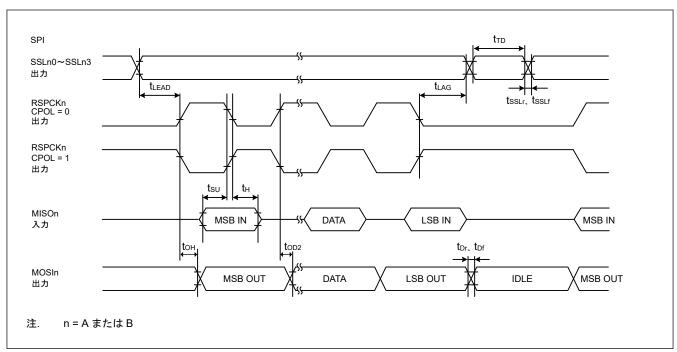

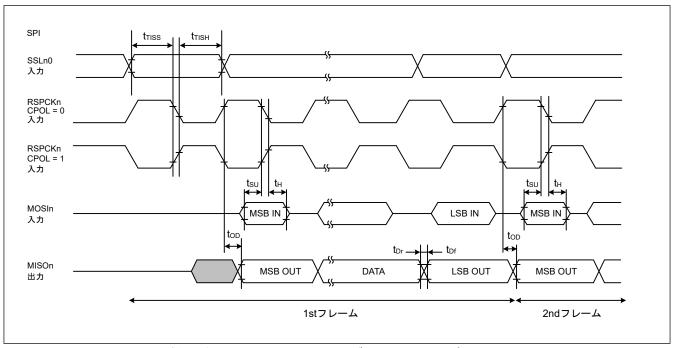

| シリアルペリフェラルインタフェース<br>(SPI)                                    | シリアルペリフェラルインタフェース (SPI) によって、複数のプロセッサおよび周辺デバイスとの高速な全二重同期式シリアル通信が可能です。<br>本 MCU では、最大レートがサポートされています。実際のレートについては、電気的特性を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

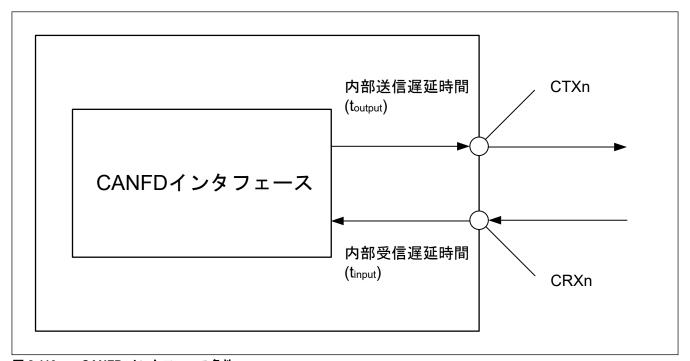

| Control Area Network with Flexible<br>Data-Rate モジュール (CANFD) | CAN with Flexible Data-Rate (CANFD) モジュールは、クラシカル CAN フレームと ISO 11898-1<br>規格に準拠する CANFD フレームの両方を取り扱うことができます。<br>本モジュールはチャネルごとに 4 個の送信バッファと 16 個の受信バッファをサポートしています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| USB 2.0 フルスピードモジュール<br>(USBFS)                                | ホストコントローラまたはデバイスコントローラとして動作可能な USB2.0 フルスピードモジュール (USBFS) です。このモジュールは、ユニバーサルシリアルバス規格 2.0 のフルスピード およびロースピード転送 (ホストコントローラのみ) をサポートしています。また USB トランシーバを内蔵しており、ユニバーサルシリアルバス規格 2.0 で定義されている全転送タイプに対応しています。USB はデータ転送用にバッファメモリを内蔵し、最大 10 本のパイプを使用できます。パイプ 1~9 に対しては、通信を行う周辺デバイスやユーザーシステムに合わせた任意のエンドポイント番号の割り付けが可能です。                                                                                                                                                                                                                                                                                                                                                                                          |

| USB 2.0 ハイスピードモジュール<br>(USBHS)                                | USB (Universal Serial Bus) 規格 2.0 に準拠するホストコントローラまたはデバイスコントローラとして動作する USB2.0 ハイスピードモジュール (USBHS) です。ホストコントローラは、USB2.0 ハイスピード、フルスピード、ロースピード転送に対応しています。デバイスコントローラは、USB2.0 ハイスピード転送とフルスピード転送に対応しています。また、USBHS は USB トランシーバを内蔵し、USB 2.0 規格で定義されている全転送タイプに対応しています。                                                                                                                                                                                                                                                                                                                                                                                                                                            |

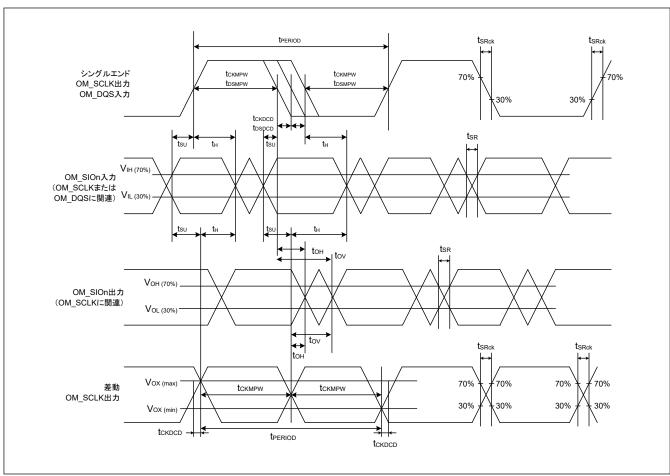

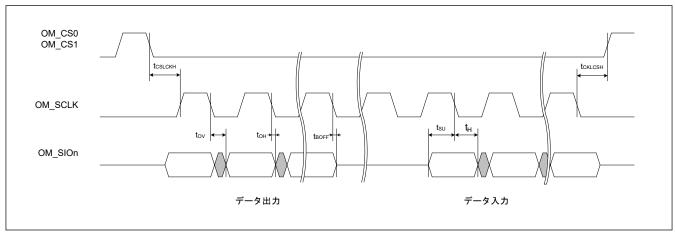

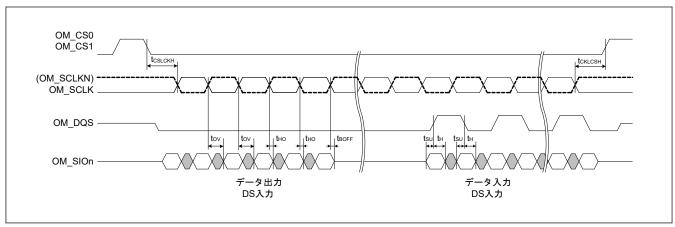

| オクタシリアルペリフェラルインタフェース (OSPI)                                   | オクタシリアルペリフェラルインタフェース (OSPI) は、拡張シリアルペリフェラルインタフェース (xSPI) (JEDEC 規格の JESD251、JESD251-1、および JESD252)をサポートするメモリコントローラです。OSPI は 1 ビット、2 ビット、4 ビット、および 8 ビットのプロトコルをサポートします。 JESD251 では 2 つのインタフェースプロファイルを指定します。 プロファイル 1.0 はオクタル SPI、プロファイル 2.0 は HyperBus $^{\text{TM}}$ (HyperRAM $^{\text{TM}}$ および HyperFlash $^{\text{TM}}$ ) です。OSPI はQSPI プロトコルをサポートします。                                                                                                                                                                                                                                                                                                                                              |

| 拡張シリアルサウンドインタフェース<br>(SSIE)                                   | 拡張シリアルサウンドインタフェース (SSIE) 周辺機能は、I <sup>2</sup> S/モノラル/TDM オーディオデータを送信するため、デジタルオーディオデバイスをシリアルバス経由で接続する機能を提供しています。 SSIE は最高 50 MHz のオーディオクロック周波数をサポートしており、各種アプリケーションに適合するスレーブまたはマスタレシーバ/トランスミッタ/トランシーバとして動作します。 SSIE はレシーバとトランスミッタに 32 段 FIFO バッファを内蔵し、割り込みおよび DMA 駆動によるデータ送受信をサポートしています。                                                                                                                                                                                                                                                                                                                                                                                                                  |

# 表 1.8 通信インタフェース (2/2)

| 機能                             | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD/MMC ホストインタフェース (SDHI)       | セキュアデジタル (SD) カードホストインタフェースおよびマルチメディアカード (MMC) ホストインタフェースは、各種の外付けメモリカードと MCU との接続に必要な機能を提供します。 SDHI は、SD、SDHC、および SDXC フォーマットに対応するメモリカードを接続するために 1 ビットと 4 ビットのバスをサポートしています。 SD 規格に対応したホスト機器を開発するには、SD Host/Ancillary Product License Agreement (SD HALA) に準拠する必要があります。 MMC インタフェースは、eMMC 4.51 (JEDEC Standard JESD 84-B451) デバイスアクセスを可能にする 1 ビット、4 ビット、および 8 ビットの MMC バスをサポートしています。このインタフェースには下位互換性があり、高速 SDR 転送モードもサポートしています。 |

| レイヤ3イーサネットスイッチモジュ<br>ール (ESWM) | レイヤ3イーサネットスイッチモジュール (ESWM) は、2 チャネルのギガビットイーサネットコントローラ、高レベルのルーティング機能を持つイーサネットスイッチ、およびマルチプロトコルインタフェースサポートで構成されています。ギガビットイーサネットコントローラは、IEEE 802.3 規格のイーサネット MAC (Media Access Control) 層の定義に準拠します。この規格に準拠する外部物理層 LSI チップ (PHY-LSI) に接続することにより、イーサネット (IEEE 802.3) フレームの送信と受信が可能です。本イーサネットスイッチは、同一のネットワークインタフェースプロトコル内および異なるネットワークインタフェースプロトコル間、または最適化されたゲートウェイアプリケーションとの間での自立的なフレームルーティングが可能です。                                   |

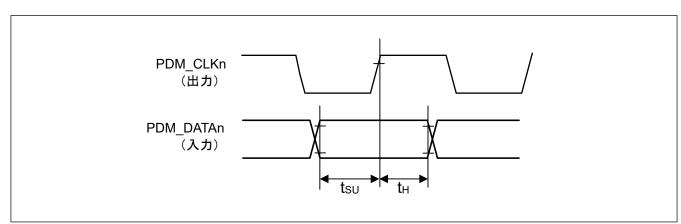

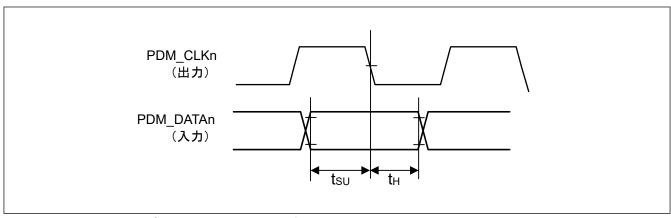

| パルス密度変調インタフェース<br>(PDMIF)      | PDM-IF には、パルス密度変調 (PDM) 信号を出力する外部マイクロホンに接続可能なチャネルが最大3つあります。PDM-IF は最大3つの外部マイクロホンと接続可能です。PDM-IF は、高いサンプリングレートでパルス密度変調された1 ビットのデジタルデータストリームをフィルタリングして、より低いサンプリングレートの20 ビットまたは16 ビットのデジタルデータに変換できます。                                                                                                                                                                                                                              |

# 表 1.9 アナログ

| 機能                        | 機能の説明                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 ビット A/D コンバータ (ADC16H) | 16 ビット A/D コンバータを内蔵しています。最大 23 チャネルのアナログ入力を選択可能です。<br>変換には温度センサ出力、内部基準電圧、および VBATT 1/6 電圧監視を選択可能です。                                                                                                      |

| 12 ビット D/A コンバータ (DAC12)  | 12 ビットの D/A コンバータ (DAC12) を内蔵しています。                                                                                                                                                                      |

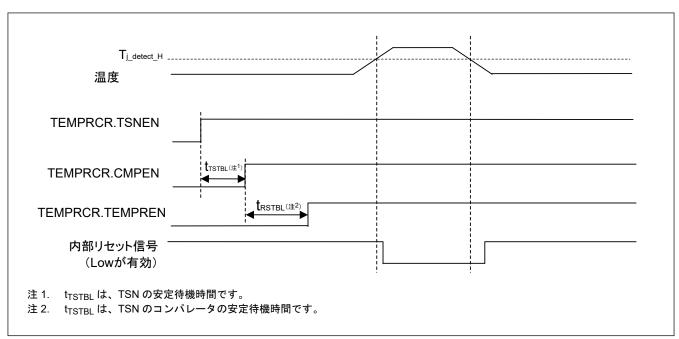

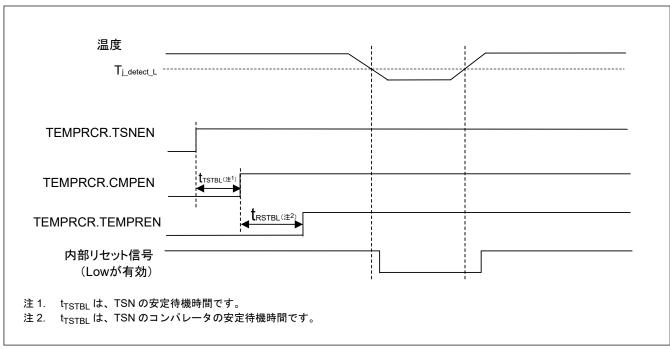

| 温度センサ (TSN)               | デバイス動作の信頼性確保のため、内蔵されている温度センサ (TSN) でチップの温度を測定し、監視します。センサはチップの温度と正比例する電圧を出力します。チップ温度と出力電圧はほとんどリニアの関係にあります。出力電圧は ADC16H で変換されてから、末端の応用機器で使用できます。センサは異常温度検出信号をリセット制御回路に出力し、これを使用して異常温度による不具合を防止できます。        |

| 高速アナログコンパレータ (ACMPHS)     | 高速アナログコンパレータ (ACMPHS) は、アナログ入力電圧と基準電圧の比較、および変換結果に基づいたデジタル出力に使用できます。アナログ入力電圧と基準電圧は、どちらも内部ソース (D/A コンバータ出力または内部基準電圧) および外部ソースから ACMPHS に供給できます。このような柔軟性は、A/D 変換を行うことなくアナログ信号間の合否判定を実施する必要があるアプリケーションで有用です。 |

### 表 1.10 ヒューマンマシンインタフェース

| 機能                  | 機能の説明                                                           |

|---------------------|-----------------------------------------------------------------|

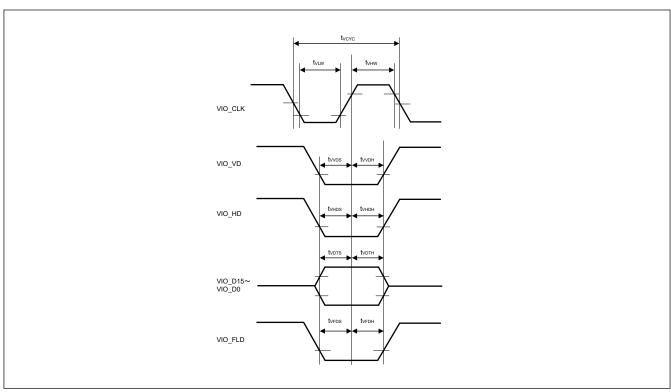

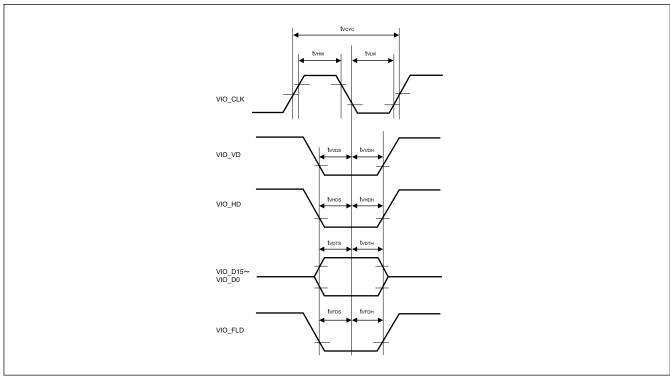

| キャプチャエンジンユニット (CEU) | キャプチャエンジンユニット (CEU) は、外部から入力される画像データを取り込み、メモリに転送するキャプチャモジュールです。 |

# 表 1.11 データ処理

| 機能               | 機能の説明                                                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 巡回冗長検査 (CRC) 演算器 | 巡回冗長検査 (CRC: Cyclic Redundancy Check) 演算器は、CRC コードを生成してデータエラーを検出します。LSB ファーストまたは MSB ファーストでの通信用に、CRC 演算結果のビットオーダーを切り替えることができます。さらに、さまざまな CRC 生成多項式を使用できます。スヌーブ機能は、特定のアドレスに対する読み出しと書き込みをモニタするのを許可します。この機能は、シリアル送信バッファへの書き込みとシリアル受信バッファからの読み出しを監視する場合など、特定のイベントで CRC コードの自動生成が必要となるアプリケーションで役立ちます。 |

| データ演算回路 (DOC)    | データ演算回路 (DOC) は、32 ビットのデータを比較、加算、および減算します。選択した条件が適用される場合、32 ビットのデータが比較され、割り込みを生成可能です。                                                                                                                                                                                                            |

# 表 1.12 セキュリティ

| 機能                          | 機能の説明                                                                                                                                                                                                                                                                                 |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| セキュリティ機能                    | <ul> <li>ARMv8-M TrustZone セキュリティ</li> <li>プリビレッジ制御</li> <li>デバイスライフサイクル管理</li> <li>認証レベル (AL)</li> <li>キーインジェクション</li> <li>セキュア端子マルチプレキシング</li> <li>HUK のゼロ化</li> <li>VBATT バックアップレジスタのゼロ化</li> <li>セキュアブート</li> <li>セキュアファクトリプログラミング</li> </ul>                                     |

| Renesas セキュア IP (RSIP-E50D) | <ul> <li>対称暗号: AES および ChaCha20-Poly1305</li> <li>非対称暗号: RSA および ECC</li> <li>メッセージダイジェスト計算: HASH、HMAC</li> <li>128 ビット真性乱数生成回路</li> <li>256 ビットハードウェアユニークキー (HUK)</li> <li>128 ビットのユニーク ID</li> <li>OEM ブートローダーバージョン</li> <li>オンザフライ復号 (DOTF) 用のキーデータ</li> <li>SPA/DPA 保護</li> </ul> |

| オンザフライ復号 (DOTF)             | オンザフライ復号 (DOTF) は、外部メモリに格納されている暗号化されたコンテンツをリアルタイムで復号します。                                                                                                                                                                                                                              |

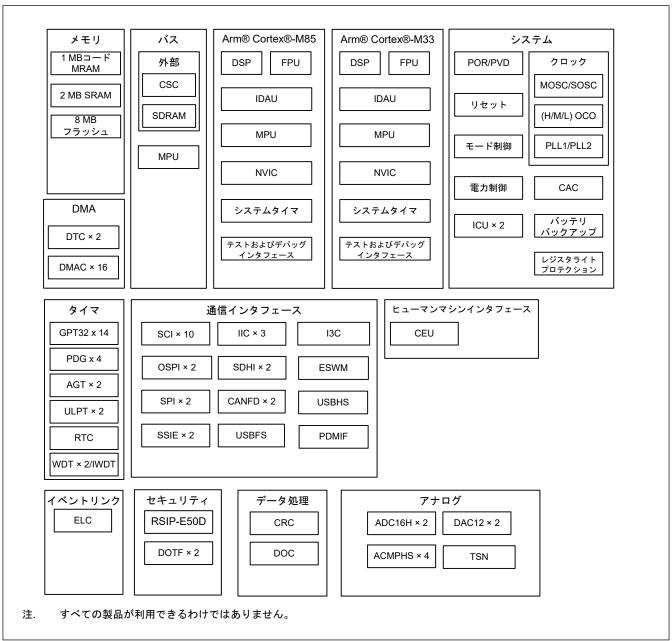

### 1.2 ブロック図

図 1.1 に、本 MCU のスーパーセットのブロック図を示します。グループ内の個々のデバイスは、その機能のサブセットを持つ場合があります。

図 1.1 ブロック図

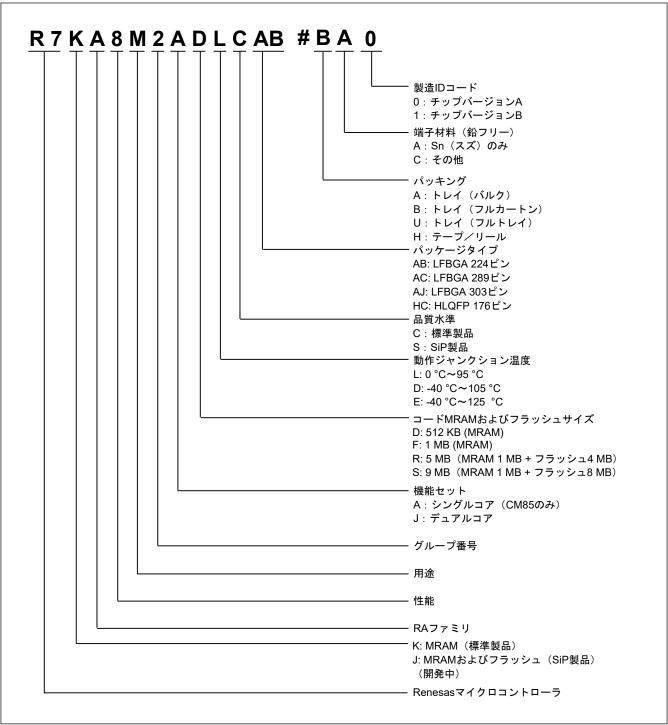

### 1.3 型名

図 1.2 に、メモリ容量およびパッケージタイプを含む製品の型名情報を示します。表 1.13 に、製品一覧表を示します。

図 1.2 型名の読み方

# 表 1.13 製品一覧

| 製品型名          | 製品グループ | CPU  | パッケージコード     | コード MRAM | SRAM | フラッシュ | 動作ジャンクション温度 |

|---------------|--------|------|--------------|----------|------|-------|-------------|

| R7KA8M2ADLCAB | Α      | シングル | PLBG0224JA-A | 512 KB   | 2 MB | _     | 0~95 °C     |

| R7KA8M2ADLCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2ADDCAB | В      |      | PLBG0224JA-A |          |      |       | -40~105 °C  |

| R7KA8M2ADDCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2ADECAB | С      |      | PLBG0224JA-A |          |      |       | -40~125 °C  |

| R7KA8M2ADECAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2ADECHC |        |      | PLQP0176KK-A |          |      |       |             |

| R7KA8M2AFLCAB | Α      |      | PLBG0224JA-A | 1 MB     |      |       | 0~95 °C     |

| R7KA8M2AFLCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2AFDCAB | В      |      | PLBG0224JA-A |          |      |       | -40~105 °C  |

| R7KA8M2AFDCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2AFECAB | С      |      | PLBG0224JA-A |          |      |       | -40~125 °C  |

| R7KA8M2AFECAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2AFECHC |        |      | PLQP0176KK-A |          |      |       |             |

| R7KA8M2JFLCAB | Α      | デュアル | PLBG0224JA-A | 1 MB     |      |       | 0~95 °C     |

| R7KA8M2JFLCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2JFDCAB | В      |      | PLBG0224JA-A |          |      |       | -40~105 °C  |

| R7KA8M2JFDCAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2JFECAB | С      |      | PLBG0224JA-A |          |      |       | -40~125 °C  |

| R7KA8M2JFECAC |        |      | PLBG0289JA-A |          |      |       |             |

| R7KA8M2JFECHC |        |      | PLQP0176KK-A |          |      |       |             |

| R7JA8M2JRLSAJ | Α      | デュアル | PLBG0303xx-x | 1 MB     |      | 4 MB  | 0~95 °C     |

| R7JA8M2JSLSAJ |        |      |              |          |      | 8 MB  |             |

| R7JA8M2JRDSAJ | В      |      |              |          |      | 4 MB  | -40~105 °C  |

| R7JA8M2JSDSAJ |        |      |              |          |      | 8 MB  |             |

# 1.4 機能の比較

# 表 1.14 機能の比較 (1/2)

| 型名       |                 | R7KA8M2Ax<br>xCAC                   | R7KA8M2Jx<br>xCAC | R7KA8M2Ax<br>xCAB | R7KA8M2Jx<br>xCAB | R7KA8M2Ax<br>xCHC | R7KA8M2Jx<br>xCHC | R7JA8M2Jx<br>xSAJ         |  |  |  |

|----------|-----------------|-------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|--|--|--|

| 端子総数     |                 | 289                                 | •                 | 224               |                   | 176               |                   | 303                       |  |  |  |

| パッケーシ    | ;               | BGA                                 |                   | 1                 |                   | HLQFP             |                   | BGA                       |  |  |  |

| I/O ポート  |                 | 208                                 |                   | 149               |                   | 130               |                   | 196                       |  |  |  |

| コードMR    | AM              | 1 MB, 512 KB                        | 1 MB, 512 KB      |                   |                   |                   |                   |                           |  |  |  |

| CPU0 TCM | Л               | 256 KB                              |                   |                   |                   |                   |                   |                           |  |  |  |

| CPU1 TCN | И               | なし                                  | 128 KB            | なし                | 128 KB            | なし                | 128 KB            |                           |  |  |  |

| CPU0 I/D | キャッシュ           | 32 KB                               |                   |                   |                   | •                 |                   |                           |  |  |  |

| CPU1 C/S | キャッシュ           | なし                                  | 32 KB             | なし                | 32 KB             | なし                | 32 KB             |                           |  |  |  |

| SRAM     |                 | 1792 KB                             | 1664 KB           | 1792 KB           | 1664 KB           | 1792 KB           | 1664 KB           |                           |  |  |  |

| フラッシュ    | L               | なし                                  |                   | •                 |                   |                   |                   | 8 MB, 4 MB                |  |  |  |

| DMA      | DTC             | 1                                   | 2                 | 1                 | 2                 | 1                 | 2                 |                           |  |  |  |

|          | DMAC            | 8                                   | 16                | 8                 | 16                | 8                 | 16                |                           |  |  |  |

| BUS      | 外部バス            | 32 ビットバス                            | ,                 | 16 ビットバス          |                   |                   |                   |                           |  |  |  |

|          | SDRAM           | 32 ビットバス                            | •                 | 16 ビットバス          | •                 |                   |                   |                           |  |  |  |

|          | CPU0 クロッ<br>ク   | 最高 1 GHz                            |                   |                   |                   | 最高 600 MHz        |                   | 最高 1 GHz                  |  |  |  |

|          | CPU1 クロッ<br>ク   | なし                                  | 最高<br>250 MHz     | なし                | 最高<br>250 MHz     | なし                | 最高<br>200 MHz     | 最高<br>250 MHz             |  |  |  |

|          | CPU クロッ<br>クソース | MOSC, SOSC, HOCO, MOCO, LOCO, PLL1P |                   |                   |                   |                   |                   |                           |  |  |  |

|          | CAC             | あり                                  | あり                |                   |                   |                   |                   |                           |  |  |  |

|          | WDT             | 1                                   | 2                 | 1                 | 2                 | 1                 | 2                 |                           |  |  |  |

|          | IWDT            | あり                                  |                   |                   |                   |                   |                   |                           |  |  |  |

|          | バックアップ<br>レジスタ  | 128 B                               |                   |                   |                   |                   |                   |                           |  |  |  |

| 通信       | SCI             | 10                                  |                   | 9                 |                   |                   |                   | 10                        |  |  |  |

|          | IIC             | 3                                   |                   |                   |                   |                   |                   |                           |  |  |  |

|          | I3C             | あり                                  | <br>あり            |                   |                   |                   |                   |                           |  |  |  |

|          | SPI             | 2                                   | 2                 |                   |                   |                   |                   |                           |  |  |  |

|          | CANFD           | 2                                   | 2                 |                   |                   |                   |                   |                           |  |  |  |

|          | USBFS           | あり                                  |                   |                   |                   |                   |                   |                           |  |  |  |

|          | USBHS           | あり                                  |                   |                   |                   |                   |                   |                           |  |  |  |

|          | OSPI            | 2                                   |                   | 1                 | 2 <sup>(注2)</sup> |                   |                   |                           |  |  |  |

|          | SSIE            | 2                                   |                   |                   |                   |                   |                   |                           |  |  |  |

|          | SDHI/MMC        | 2                                   |                   |                   |                   |                   |                   |                           |  |  |  |

|          | ESWM            | MII, RMII, GM                       | II, RGMII         | MII, RMII, RG     | MII               | MII, RMII         |                   | MII, RMII,<br>GMII, RGMII |  |  |  |

|          | PDMIF           | あり                                  |                   |                   |                   | 1                 |                   | 1                         |  |  |  |

#### 表 1.14 機能の比較 (2/2)

| 型名     |                       | R7KA8M2Ax<br>xCAC | R7KA8M2Jx<br>xCAC | R7KA8M2Ax<br>xCAB | R7KA8M2Jx<br>xCAB | R7KA8M2Ax<br>xCHC | R7KA8M2Jx<br>xCHC | R7JA8M2Jx<br>xSAJ                     |

|--------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------|

| タイマ    | GPT32 <sup>(注1)</sup> | 14                |                   | •                 |                   |                   |                   |                                       |

|        | PDG                   | 4                 |                   |                   |                   |                   |                   |                                       |

|        | AGT <sup>(注1)</sup>   | 2                 |                   |                   |                   |                   |                   |                                       |

|        | ULPT <sup>(注1)</sup>  | 2                 |                   |                   |                   |                   |                   |                                       |

|        | RTC                   | あり                |                   |                   |                   |                   |                   |                                       |

| アナログ   | ADC16H                | ユニット 0: 15<br>15  | 5、ユニット 1:         | ユニット 0: 7、        | ユニット 1: 5         |                   |                   | ユニット 0:<br>15、ユニット<br>1: 15           |

|        | DAC12                 | 2                 |                   |                   |                   |                   |                   |                                       |

|        | ACMPHS                | 4                 |                   |                   |                   |                   |                   |                                       |

|        | TSN                   | あり                |                   |                   |                   |                   |                   |                                       |

| НМІ    | CEU                   | あり                |                   |                   |                   |                   |                   |                                       |

| データ処理  | CRC                   | あり                |                   |                   |                   |                   |                   |                                       |

|        | DOC                   | あり                |                   |                   |                   |                   |                   |                                       |

| イベント制御 | ELC                   | あり                |                   |                   |                   |                   |                   |                                       |

| セキュリティ | ·                     | RSIP-E50D、        | オンザフライ復           | [号、セキュアテ          | ·<br>バッグ、OTP、     | TrustZone、ラ       | ・<br>イフサイクル<br>1  | · · · · · · · · · · · · · · · · · · · |

注: 製品型名は、サポートしているメモリサイズによって異なります。「1.3. 型名」を参照してください。注 1. 使用できる端子はピン数によります。詳細は、「1.7. 端子一覧」を参照してください。注 2. OSPI1 は、SiP 製品のシリアルフラッシュに接続されます。

# 1.5 端子機能

# 表 1.15 端子機能 (1/7)

| 機能        | 信号                                             | 入出力 | 説明                                                                                                                                                    |

|-----------|------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 電源        | VCC_01~<br>VCC_10,<br>VCC2_11~<br>VCC2_15      | 入力  | 電源端子。システムの電源に接続してください。この端子は、0.1 µF のコンデンサを介して同じ番号の VSS_01~VSS_15 に接続してください。コンデンサは端子近くに配置してください。<br>SiP 製品では、VCC2_11~VCC2_15 をシステムの 1.8 V 電源に接続してください。 |

|           | VCC2_16~<br>VCC2_19                            | 入力  | SiP 製品用の専用電源端子。システムの 1.8 V 電源に接続してください。この端子は、 0.1 µF のコンデンサを介して同じ番号の VSS_16~VSS_19 に接続してください。コンデンサは端子近くに配置してください。                                     |

|           | VCC_DCDC                                       | 入力  | スイッチングレギュレータ電源端子                                                                                                                                      |

|           | VLO                                            | 入出力 | スイッチングレギュレータ端子                                                                                                                                        |

|           | VCL0~VCL11                                     | 入力  | この端子は、内部電源を安定化するための平滑コンデンサを介して同じ番号の VSS0~VSS11 端子に接続してください。コンデンサは端子近くに配置してください。                                                                       |

|           | VBATT                                          | 入力  | バッテリバックアップ電源端子                                                                                                                                        |

|           | VSS_01~<br>VSS_15, VSS0~<br>VSS11,<br>VSS_DCDC | 入力  | グランド端子。システムの電源 (0 V) に接続してください。                                                                                                                       |

|           | VSS_16~<br>VSS_19, VSS                         | 入力  | SiP 製品用の専用グランド端子。システムの電源 (0 V) に接続してください。                                                                                                             |

| クロック      | XTAL                                           | 出力  | 水晶振動子用の接続端子。EXTAL 端子を通じて外部クロック信号の入力が可能です。                                                                                                             |

|           | EXTAL                                          | 入力  |                                                                                                                                                       |

|           | XCIN                                           | 入力  | サブクロック発振器用の入出力端子。XCOUT と XCIN の間には、水晶振動子を接続し                                                                                                          |

|           | XCOUT                                          | 出力  | てください。                                                                                                                                                |

|           | EXCIN                                          | 入力  | 外部サブクロック入力                                                                                                                                            |

|           | CLKOUT                                         | 出力  | クロック出力端子                                                                                                                                              |

| 動作モード制御   | MD                                             | 入力  | 動作モード設定用の端子。この端子の信号レベルは、リセット解除時の動作モードの 遷移中に変更しないでください。                                                                                                |

| システム制御    | RES                                            | 入力  | リセット信号入力端子。この端子が Low になると、MCU はリセット状態となります。                                                                                                           |

|           | PUP                                            | 入力  | 抵抗を介して VCC2 に接続してください。                                                                                                                                |

| CAC       | CACREF                                         | 入力  | 測定基準クロックの入力端子                                                                                                                                         |

| オンチップエミュレ | TMS                                            | 入力  | オンチップエミュレータ用またはバウンダリスキャン用端子                                                                                                                           |

| ータ        | TDI                                            | 入力  |                                                                                                                                                       |

|           | TCK                                            | 入力  |                                                                                                                                                       |

|           | TDO                                            | 出力  |                                                                                                                                                       |

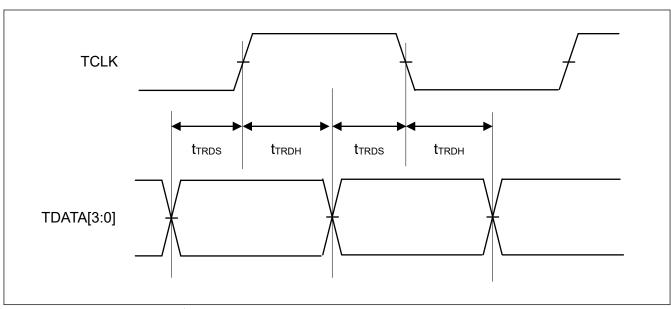

|           | TCLK                                           | 出力  | トレースデータと同期をとるためのクロックを出力します。                                                                                                                           |

|           | TDATA0~<br>TDATA3                              | 出力  | トレースデータ出力                                                                                                                                             |

|           | SWO                                            | 出力  | シリアルワイヤトレース出力端子                                                                                                                                       |

|           | SWDIO                                          | 入出力 | シリアルワイヤデバッグデータの入出力端子                                                                                                                                  |

|           | SWCLK                                          | 入力  | シリアルワイヤクロック端子                                                                                                                                         |

| 割り込み      | NMI                                            | 入力  | ノンマスカブル割り込み要求端子                                                                                                                                       |

|           | IRQn                                           | 入力  | マスカブル割り込み要求端子                                                                                                                                         |

|           | IRQn-DS                                        | 入力  | マスカブル割り込み要求端子は、ディープソフトウェアスタンバイモード時も使用できます。                                                                                                            |

# 表 1.15 端子機能 (2/7)

| 機能          | 信号                                          | 入出力 | 説明                                                                                                                 |

|-------------|---------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|

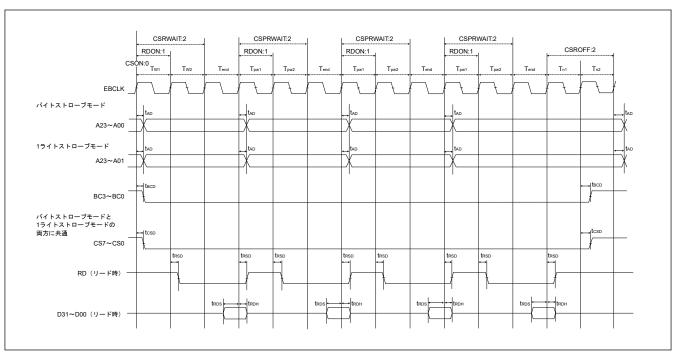

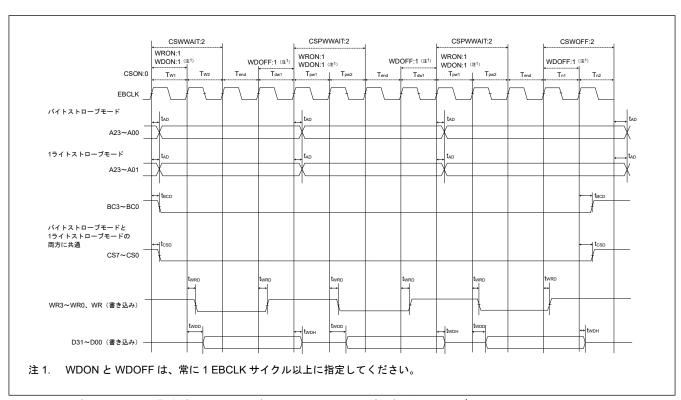

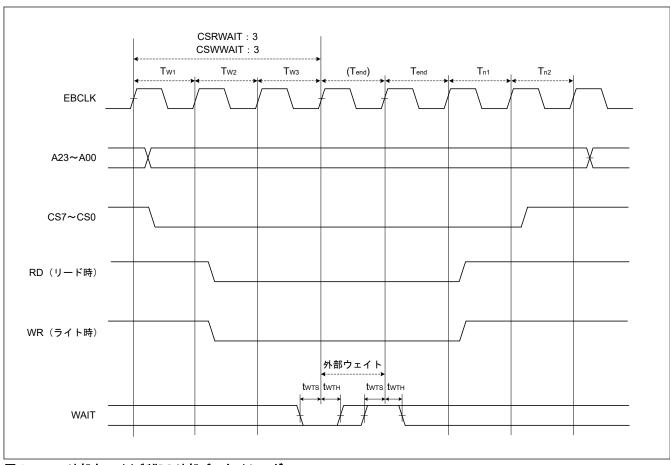

| 外部バスインタフェ   | EBCLK                                       | 出力  | 外部デバイス用の外部バスクロックを出力します。                                                                                            |

| ース          | RD                                          | 出力  | 外部バスインタフェース空間から読み出し中であることを示すストローブ信号、アクティブ Low                                                                      |

|             | WR                                          | 出力  | 1 ライトストローブモード時、外部バスインタフェース空間に書き込み中であることを<br>示すストローブ信号、アクティブ Low                                                    |

|             | WRn                                         | 出力  | バイトストローブモード時、外部バスインタフェース空間に書き込み中で、データバス端子 (D07~D00, D15~D08, D23~D16, D31~D24) のいずれかが有効であることを示すストローブ信号、アクティブ Low   |

|             | BCn                                         | 出力  | 1 ライトストローブモード時、外部バスインタフェース空間にアクセス中で、データバス端子 (D07~D00, D15~D08, D23~D16, D31~D24) のいずれかが有効であることを示すストローブ信号、アクティブ Low |

|             | ALE                                         | 出力  | アドレス/データマルチプレクスバス選択時のアドレスラッチ信号                                                                                     |

|             | WAIT                                        | 入力  | 外部空間をアクセスするときのウェイト要求信号用の入力端子、アクティブLow                                                                              |

|             | CSn                                         | 出力  | CS 領域選択信号、アクティブ Low                                                                                                |

|             | A00~A23                                     | 出力  | アドレスバス                                                                                                             |

|             | D00~D31                                     | 入出力 | データバス                                                                                                              |

|             | A00/D00~<br>A15/D15                         | 入出力 | アドレス/データマルチプレクスバス                                                                                                  |

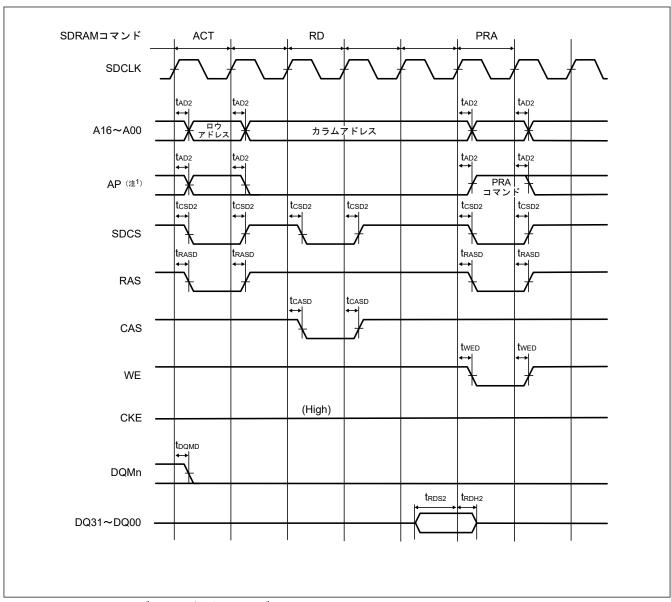

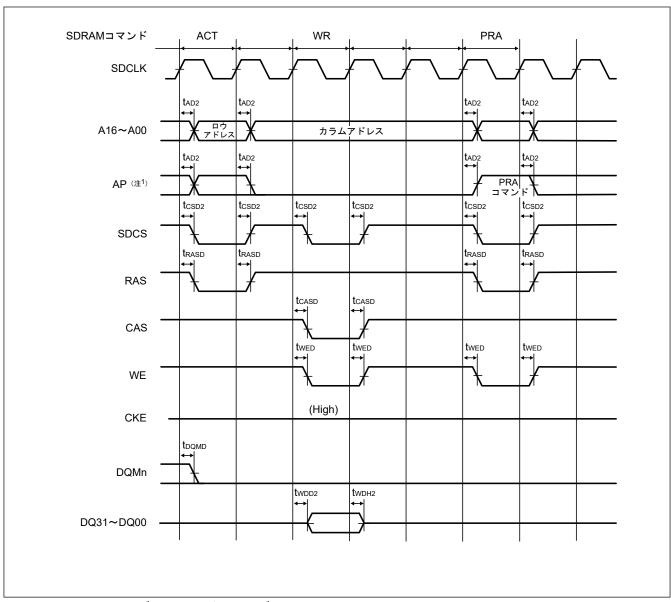

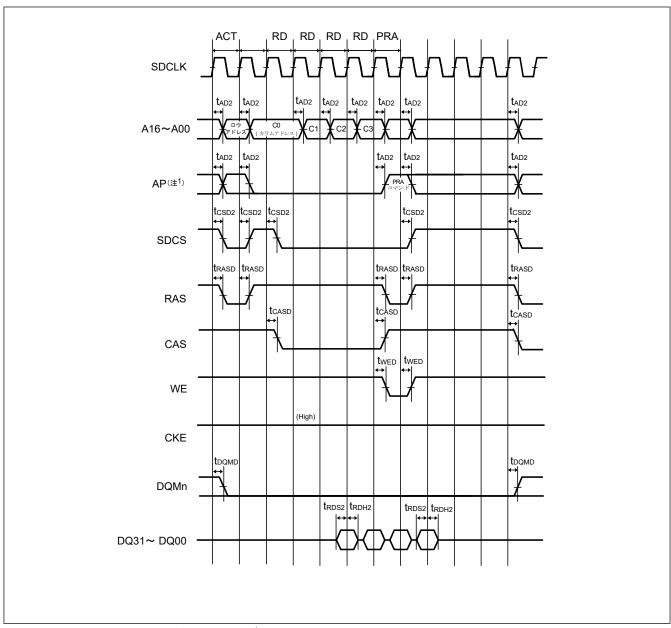

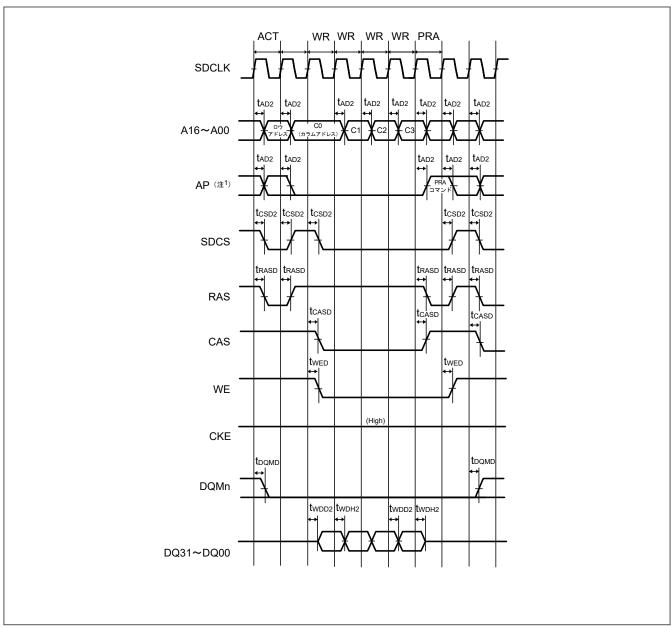

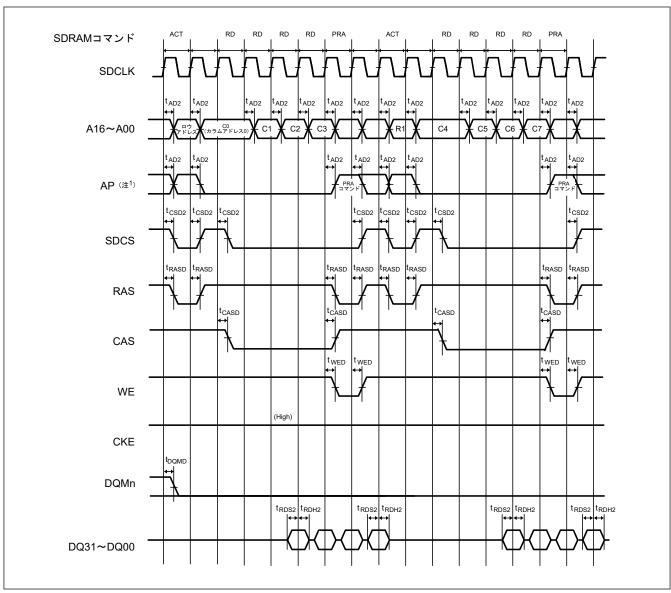

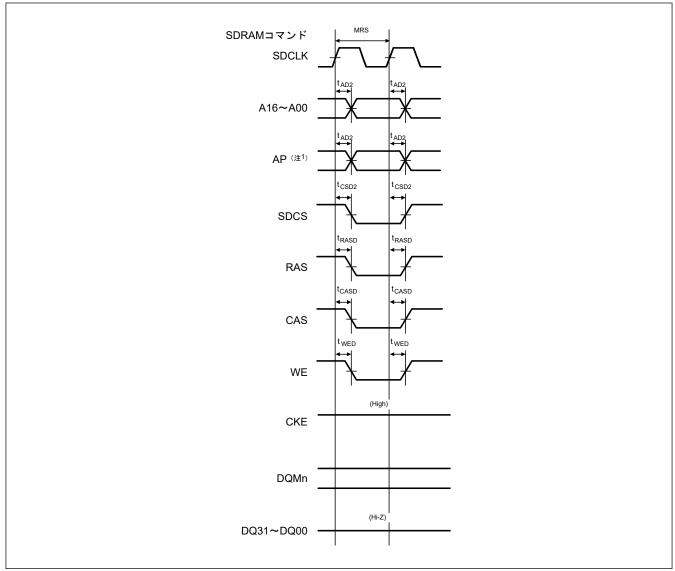

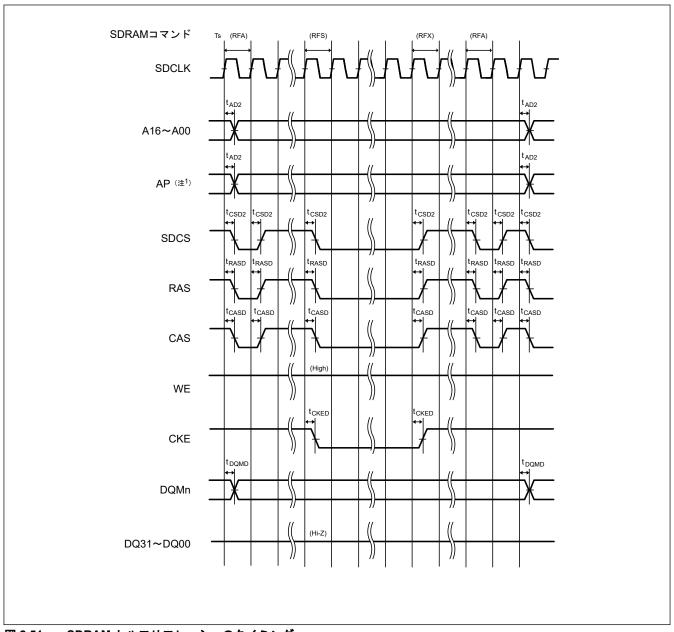

| SDRAM インタフェ | SDCLK                                       | 出力  | SDRAM 専用クロックを出力します。                                                                                                |

| ース          | CKE                                         | 出力  | SDRAM クロックイネーブル信号                                                                                                  |

|             | SDCS                                        | 出力  | SDRAM のチップ選択信号、アクティブ Low                                                                                           |

|             | RAS                                         | 出力  | SDRAM Low アドレスストローブ信号、アクティブ Low                                                                                    |

|             | CAS                                         | 出力  | SDRAM 列アドレスストローブ信号、アクティブ Low                                                                                       |

|             | WE                                          | 出力  | SDRAM 書き込みイネーブル信号、アクティブ Low                                                                                        |

|             | DQMn                                        | 出力  | SDRAM 入出力データマスクイネーブル信号 (DQ07~DQ00, DQ15~DQ08, DQ23~DQ16, DQ31~DQ24)                                                |

|             | A00~A16                                     | 出力  | アドレスバス                                                                                                             |

|             | DQ00~DQ31                                   | 入出力 | データバス                                                                                                              |

| GPT         | GTETRGA,<br>GTETRGB,<br>GTETRGC,<br>GTETRGD | 入力  | 外部トリガ入力端子                                                                                                          |

|             | GTIOCnA,<br>GTIOCnB                         | 入出力 | インプットキャプチャ、アウトプットコンペア、または PWM 出力端子                                                                                 |

|             | GTADSM0,<br>GTADSM1                         | 出力  | A/D 変換開始要求モニタリング出力端子                                                                                               |

|             | GTCPPOn                                     | 出力  | PWM 同期トグル出力                                                                                                        |

|             | GTIU                                        | 入力  | ホールセンサ入力端子 U                                                                                                       |

|             | GTIV                                        | 入力  | ホールセンサ入力端子 V                                                                                                       |

|             | GTIW                                        | 入力  | ホールセンサ入力端子 W                                                                                                       |

|             | GTOUUP                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 U 相)                                                                                    |

|             | GTOULO                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 U 相)                                                                                    |

|             | GTOVUP                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 V 相)                                                                                    |

|             | GTOVLO                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 V 相)                                                                                    |

|             | GTOWUP                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 W 相)                                                                                    |

|             | GTOWLO                                      | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 W 相)                                                                                    |

# 表 1.15 端子機能 (3/7)

| TATA BAL- | <b>地工版</b> |                             |                                                       | =0==                                                  |

|-----------|------------|-----------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 機能        |            | 信号                          | 入出力                                                   | 説明                                                    |

| AGT       |            | AGTEEn                      | 入力                                                    | 外部イベント入力イネーブル信号                                       |

|           |            | AGTIOn                      | 入出力                                                   | 外部イベント入力およびパルス出力端子                                    |

|           |            | AGTOn                       | 出力                                                    | パルス出力端子                                               |

|           |            | AGTOAn                      | 出力                                                    | アウトプットコンペアマッチ A 出力端子                                  |

|           |            | AGTOBn                      | 出力                                                    | アウトプットコンペアマッチ B 出力端子                                  |

| ULPT      | JLPT       | ULPTEEn                     | 入力                                                    | 外部カウント制御入力                                            |

|           |            | ULPTEVIn                    | 入力                                                    | 外部イベント入力                                              |

|           |            | ULPTEEn-DS                  | 入力                                                    | 外部カウント制御入力はディープソフトウェアスタンバイモード 1 時も使用できます。             |

|           |            | ULPTEVIn-DS                 | 入力                                                    | 外部イベント入力はディープソフトウェアスタンバイモード1時も使用できます。                 |

|           |            | ULPTOn                      | 出力                                                    | パルス出力                                                 |

|           |            | ULPTOAn                     | 出力                                                    | アウトプットコンペアマッチ A 出力                                    |

|           |            | ULPTOBn                     | 出力                                                    | アウトプットコンペアマッチ B 出力                                    |

|           |            | ULPTOn-DS                   | 出力                                                    | パルス出力はディープソフトウェアスタンバイモード 1 時も使用できます。                  |

|           |            | ULPTOAn-DS                  | 出力                                                    | アウトプットコンペアマッチ A 出力はディープソフトウェアスタンバイモード 1 時も<br>使用できます。 |

|           | ULPTOBn-DS | 出力                          | アウトプットコンペアマッチ B 出力はディープソフトウェアスタンバイモード 1 時も<br>使用できます。 |                                                       |

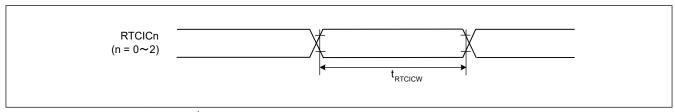

| RTC       |            | RTCOUT                      | 出力                                                    | 1 Hz または 64 Hz のクロック出力端子                              |

|           |            | RTCICn                      | 入力                                                    | 時間キャプチャイベント入力端子                                       |

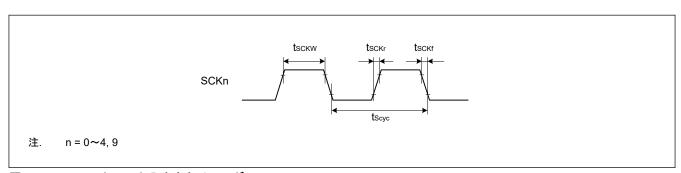

| SCI       | SCI        | SCKn                        | 入出力                                                   | クロック用の入出力端子 (クロック同期式モード)                              |

|           |            | RXDn                        | 入力                                                    | 受信データ用の入力端子(調歩同期式モード/クロック同期式モード)                      |

|           |            | TXDn                        | 出力                                                    | 送信データ用の出力端子(調歩同期式モード/クロック同期式モード)                      |

|           |            | CTSn_RTSn                   | 入出力                                                   | 送受信の開始制御用の入出力端子(調歩同期式モード/クロック同期式モード)、アクティブ Low        |

|           |            | CTSn                        | 入力                                                    | 送信の開始用の入力端子                                           |

|           |            | DEn                         | 出力                                                    | RS-485 用のドライバイネーブル信号                                  |

|           |            | SCLn                        | 入出力                                                   | IIC クロック用の入出力端子(簡易 IIC モード)                           |

|           |            | SDAn                        | 入出力                                                   | IIC データ用の入出力端子(簡易 IIC モード)                            |

|           |            | SCKn                        | 入出力                                                   | クロック用の入出力端子(簡易 SPI モード)                               |

|           |            | MISOn                       | 入出力                                                   | データのスレーブ送信用の入出力端子(簡易 SPI モード)                         |

|           |            | MOSIn                       | 入出力                                                   | データのマスタ送信用の入出力端子(簡易 SPI モード)                          |

|           |            | SSn                         | 入力                                                    | チップセレクト入力端子(簡易 SPI モード)、アクティブ Low                     |

| IIC       |            | SCLn                        | 入出力                                                   | クロック用の入出力端子                                           |

|           |            | SDAn                        | 入出力                                                   | データ用の入出力端子                                            |

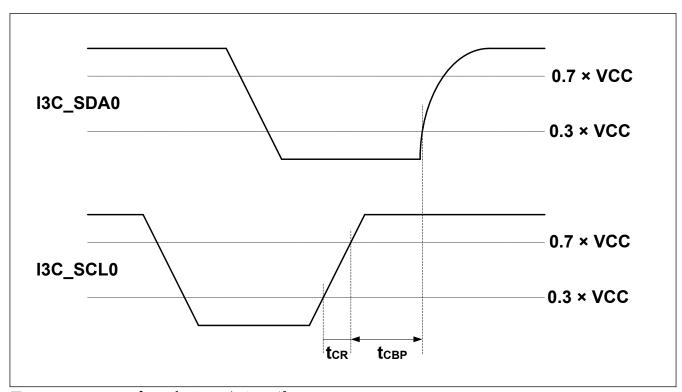

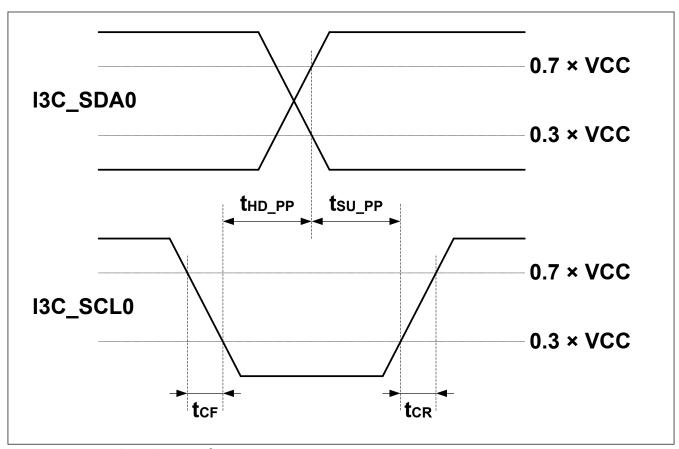

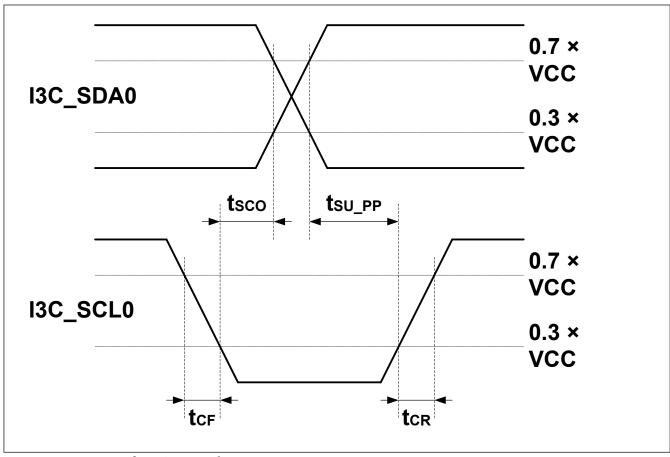

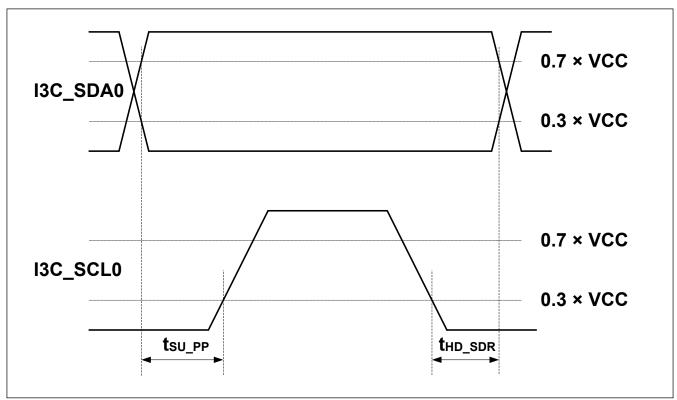

| I3C       |            | I3C_SCL0                    | 入出力                                                   | クロック用の入出力端子                                           |

|           |            | I3C_SDA0                    | 入出力                                                   | データ用の入出力端子                                            |

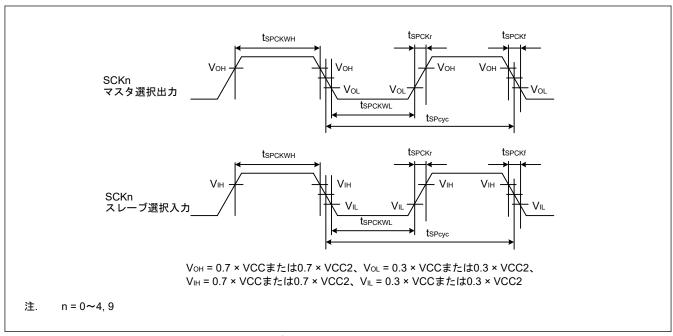

| SPI       |            | RSPCKA,<br>RSPCKB           | 入出力                                                   | クロック入出力端子                                             |

|           |            | MOSIA, MOSIB                | 入出力                                                   | マスタからの出力データ用の入出力端子                                    |

|           |            | MISOA, MISOB                | 入出力                                                   | スレーブからの出力データ用の入出力端子                                   |

|           |            | SSLA0, SSLB0                | 入出力                                                   | スレーブ選択用の入出力端子                                         |

|           |            | SSLA1~SSLA3,<br>SSLB1~SSLB3 | 出力                                                    | スレーブ選択用の出力端子                                          |

# 表 1.15 端子機能 (4/7)

| 機能    | 信号                                            | 入出力 | 説明                                                                                                                   |

|-------|-----------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| CANFD | CRXn                                          | 入力  | 受信データ                                                                                                                |

|       | CTXn                                          | 出力  | 送信データ                                                                                                                |

| USBFS | VCC_USB                                       | 入力  | 電源端子                                                                                                                 |

|       | VSS_USB                                       | 入力  | グランド端子                                                                                                               |

|       | USB_DP                                        | 入出力 | USB 内蔵トランシーバ D+端子。この端子は USB バスの D+端子に接続してください。                                                                       |

|       | USB_DM                                        | 入出力 | USB 内蔵トランシーバ D-端子。この端子は USB バスの D-端子に接続してください。                                                                       |

|       | USB_VBUS                                      | 入力  | USB ケーブル接続モニタ端子。USB バスの VBUS に接続してください。ファンクションコントローラ機能選択時の VBUS の接続/切断を検出できます。                                       |

|       | USB_EXICEN                                    | 出力  | 外部電源 (OTG) チップの低消費電力制御信号                                                                                             |

|       | USB_VBUSEN                                    | 出力  | 外部電源チップへの VBUS (5 V) 供給許可信号                                                                                          |

|       | USB_OVRCURA                                   | 入力  | これらの端子には外部過電流検出信号を接続してください。OTG 電源チップとの接続                                                                             |

|       | ,<br>USB_OVRCURB                              |     | 時には VBUS コンパレータ信号を接続してください。<br>                                                                                      |

|       | USB_OVRCURA<br>-DS,<br>USB_OVRCURB<br>-DS     | 入力  | USBFS 用オーバーカレント端子は、ディープソフトウェアスタンバイモード 1 時も使用できます。これらの端子には外部過電流検出信号を接続してください。OTG 電源チップとの接続時には VBUS コンパレータ信号を接続してください。 |

|       | USB_ID                                        | 入力  | OTG 動作時に MicroAB コネクタの ID 入力信号を接続してください。                                                                             |

| USBHS | VCC_USBHS                                     | 入力  | 電源端子                                                                                                                 |

|       | VSS1_USBHS,<br>VSS2_USBHS                     | 入力  | グランド端子                                                                                                               |

|       | AVCC_USBHS                                    | 入力  | アナログ電源                                                                                                               |

|       | USBHS_RREF                                    | 入出力 | USBHS 用の基準電流源端子。 $2.2~{ m k}\Omega~(\pm 1\%)$ の抵抗を介して AVSS_USBHS 端子に接続してください。                                        |

|       | USBHS_DP                                      | 入出力 | USB バスの D+データラインの入出力端子                                                                                               |

|       | USBHS_DM                                      | 入出力 | USB バスの D-データラインの入出力端子                                                                                               |

|       | USBHS_EXICEN                                  | 出力  | OTG 電源 IC に接続してください。                                                                                                 |

|       | USBHS_ID                                      | 入力  | OTG 電源 IC に接続してください。                                                                                                 |

|       | USBHS_VBUSE<br>N                              | 出力  | USBHS 用の VBUS 電源イネーブル端子                                                                                              |

|       | USBHS_OVRCU<br>RA,<br>USBHS_OVRCU<br>RB       | 入力  | USBHS 用オーバーカレント端子                                                                                                    |

|       | USBHS_OVRCU<br>RA-DS,<br>USBHS_OVRCU<br>RB-DS | 入力  | USBHS 用オーバーカレント端子は、ディープソフトウェアスタンバイモード 1 時も使用できます。                                                                    |

|       | USBHS_VBUS                                    | 入力  | USB ケーブル接続モニタ入力端子                                                                                                    |

# 表 1.15 端子機能 (5/7)

| 機能       | 信号                                          | 入出力 | 説明                                 |

|----------|---------------------------------------------|-----|------------------------------------|

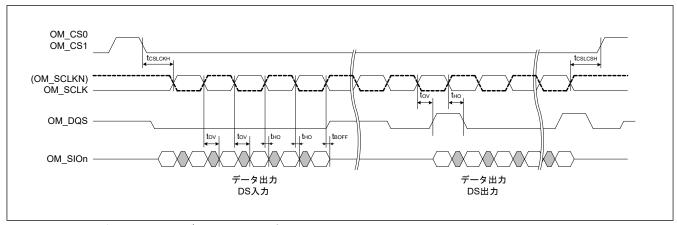

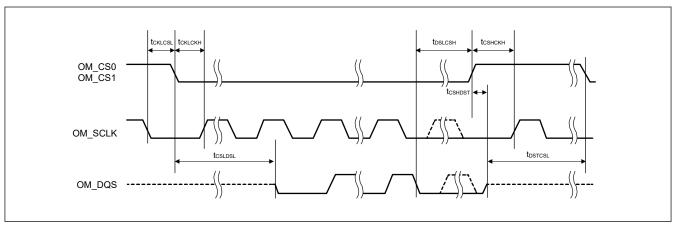

| OSPI     | OM_n_SCLK                                   | 出力  | クロック出力(OCTACLK の 2 分周)             |

|          | OM_n_SCLKN                                  | 出力  | 反転クロック出力(OCTACLK の 2 分周)           |

|          | OM_n_CSn                                    | 出力  | OctaFlash デバイス用チップセレクト信号、アクティブ Low |

|          | OM_n_DQS                                    | 入出力 | 読み出しデータストローブ/書き込みデータマスク信号          |

|          | OM_n_SIOn                                   | 入出力 | データ入出力                             |

|          | OM_n_RESET                                  | 出力  | 両スレーブデバイス用のリセット信号、アクティブ Low        |

|          | OM_n_ECSINT1                                | 入力  | スレーブ1のエラー訂正状態と割り込み                 |

|          | OM_n_RSTO1                                  | 入力  | スレーブ1のスレーブリセット状態                   |

|          | OM_n_WP1                                    | 出力  | スレーブ1の書き込み保護、アクティブLow              |

| SSIE     | SSIBCK0,<br>SSIBCK1                         | 入出力 | SSIE シリアルビットクロック端子                 |

|          | SSILRCK0/<br>SSIFS0,<br>SSILRCK1/<br>SSIFS1 | 入出力 | LR クロック/フレーム同期端子                   |

|          | SSITXD0                                     | 出力  | シリアルデータ出力端子                        |

|          | SSIRXD0                                     | 入力  | シリアルデータ入力端子                        |

|          | SSIDATA1                                    | 入出力 | シリアルデータ入出力端子                       |

|          | AUDIO_CLK                                   | 入力  | オーディオ用の外部クロック端子(入力オーバーサンプリングクロック)  |

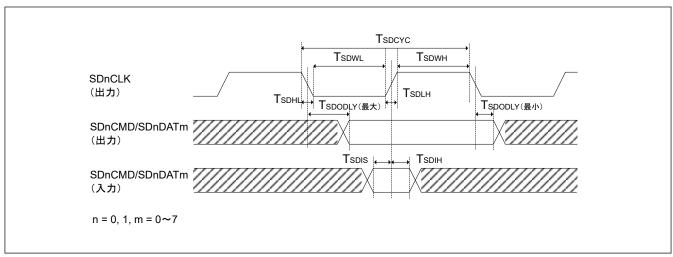

| SDHI/MMC | SDnCLK                                      | 出力  | SD クロック出力端子                        |

|          | SDnCMD                                      | 入出力 | コマンド出力端子および応答入力信号端子                |

|          | SDnDAT0~<br>SDnDAT7                         | 入出力 | SD/MMC データバス端子                     |

|          | SDnCD                                       | 入力  | SD カード検出端子                         |

|          | SDnWP                                       | 入力  | SD 書き込み保護信号                        |

# 表 1.15 端子機能 (6/7)

| 機能       | 信号                           | 入出力 | 説明                                     |

|----------|------------------------------|-----|----------------------------------------|

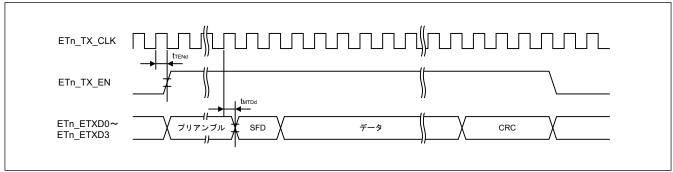

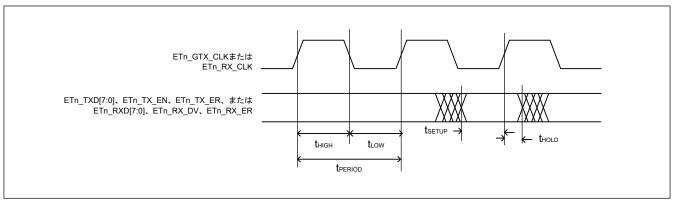

| ESWM     | ETn_GTX_CLK                  | 出力  | 1000 Mb/s の送信クロック                      |

|          | ETn_TX_CLK                   | 入力  | 100 Mb/s、10 Mb/s の送信クロック               |

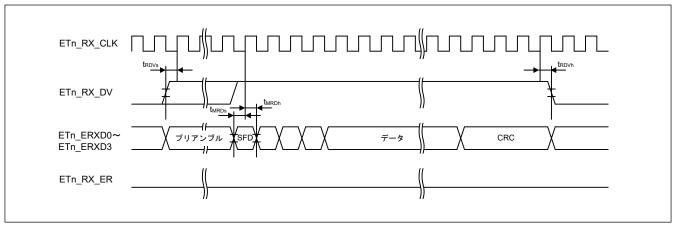

|          | ETn_RX_CLK                   | 入力  | 受信クロック                                 |

|          | ETn_TX_EN                    | 出力  | 送信許可                                   |

|          | ETn_TXD0~<br>ETn_TXD7        | 出力  | 送信データ                                  |

|          | ETn_TX_ER                    | 出力  | 送信コーディングエラー                            |

|          | ETn_RX_DV                    | 入力  | 受信データ有効                                |

|          | ETn_RXD0~<br>ETn_RXD7        | 入力  | 受信データ                                  |

|          | ETn_RX_ER                    | 入力  | 受信エラー                                  |

|          | ETn_MDC                      | 出力  | 管理データクロック                              |

|          | ETn_MDIO                     | 入出力 | 管理データ入出力                               |

|          | RGMIIn_TXC                   | 出力  | 送信クロック                                 |

|          | RGMIIn_RXC                   | 入力  | 受信クロック                                 |

|          | RGMIIn_TX_CTL                | 出力  | 送信制御                                   |

| <u> </u> | RGMIIn_TXD0~<br>RGMIIn_TXD3  | 出力  | 送信データ                                  |

|          | RGMIIn_RX_CTL                | 入力  | 受信制御                                   |

|          | RGMIIn_RXD0~<br>RGMIIn_RXD3  | 入力  | 受信データ                                  |

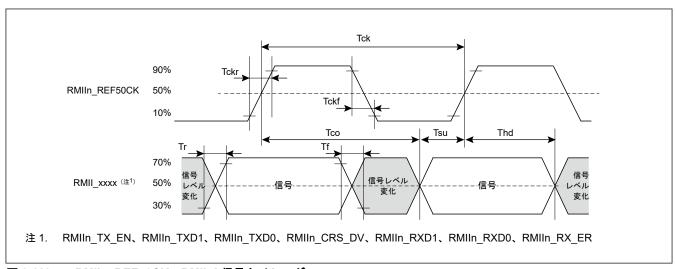

|          | RMIIn_REF50CK                | 入力  | 同期クロック参照                               |

|          | RMIIn_TX_EN                  | 出力  | 送信許可                                   |

|          | RMIIn_TXD0~<br>RMIIn_TXD1    | 出力  | 送信データ                                  |

|          | RMIIn_CRS_DV                 | 入力  | キャリア感知/受信データ有効                         |

|          | RMIIn_RXD0~<br>RMIIn_RXD1    | 入力  | 受信データ                                  |

|          | RMIIn_RX_ER                  | 入力  | 受信エラー                                  |

|          | ETn_LINKSTA                  | 入力  | PHY リンク状態                              |

|          | ETn_INT                      | 入力  | PHY 割り込み                               |

|          | ETn_WOL                      | 出力  | Wake-on-LAN。Magic Packet が受信されたことを示す信号 |

|          | GPTP_CAPTUR<br>En            | 入力  | メディアクロックキャプチャ入力                        |

|          | GPTP_MATCHn                  | 出力  | メディアクロックリカバリ出力                         |

|          | GPTP_PPSn                    | 出力  | PPS 信号                                 |

|          | GPTP_PTPOUT 0~ GPTP_PTPOUT 3 | 出力  | PTP パルスジェネレータ信号                        |

|          | ET_TAS_STA0~<br>ET_TAS_STA3  | 出力  | TAS 状態監視                               |

|          | ETHPHYCLK                    | 出力  | PHY 用クロック出力                            |

# 表 1.15 端子機能 (7/7)

| 機能      | 信号                  | 入出力 | 説明                                                                                            |

|---------|---------------------|-----|-----------------------------------------------------------------------------------------------|

| PDMIF   | PDMCLK0~<br>PDMCLK2 | 出力  | クロック出力端子                                                                                      |

|         | PDMDAT0~<br>PDMDAT2 | 入力  | データ入力端子                                                                                       |

| アナログ電源  | AVCC0               | 入力  | アナログ電圧源端子。それぞれのモジュールのアナログ電源端子として使用されます。                                                       |

|         | AVSS0               | 入力  | アナロググランド端子。それぞれのモジュールのアナロググランド端子として使用されます。この端子には VSS 端子と同じ電圧を供給してください。                        |

|         | VREFH               | 入力  | ADC16H (ユニット1) と D/A コンバータ用のアナログ基準電圧端子。ADC16H (ユニット1) および D/A コンバータを使用しない場合は AVCC0 に接続してください。 |

|         | VREFL               | 入力  | ADC16H および D/A コンバータのアナログ基準グランド端子。ADC16H (ユニット 1) および D/A コンバータを使用しない場合は AVSSO に接続してください。     |

|         | VREFH0              | 入力  | ADC16H(ユニット0) 用のアナログ基準電圧端子。ADC16H(ユニット0) を使用しない場合は AVCC0 に接続してください。                           |

|         | VREFL0              | 入力  | ADC16H 用のアナログ基準グランド端子。ADC16H (ユニット 0) を使用しない場合は<br>AVSS0 に接続してください。                           |

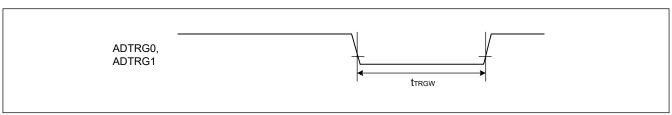

| ADC16H  | ANxxx               | 入力  | A/D コンバータで処理されるアナログ信号用の入力端子。                                                                  |

|         | ADTRGm              | 入力  | A/D 変換を開始する外部トリガ信号用の入力端子、アクティブ Low                                                            |

|         | ADSTm               | 出力  | AD 変換開始                                                                                       |

|         | ADmFLAG1            | 出力  | AD 変換終了                                                                                       |

|         | ADSYNC              | 出力  | ユニット間の同期信号                                                                                    |

| DAC12   | DAn                 | 出力  | D/A コンバータで処理されるアナログ信号用の出力端子。                                                                  |

| ACMPHS  | VCOUT               | 出力  | コンパレータ出力端子                                                                                    |

|         | IVREFn              | 入力  | コンパレータ用基準電圧入力端子                                                                               |

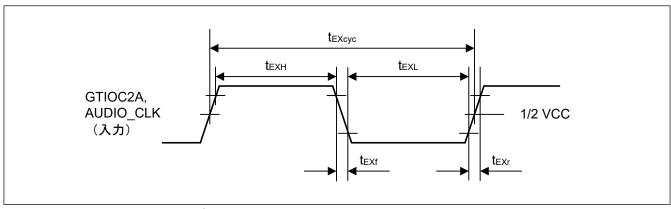

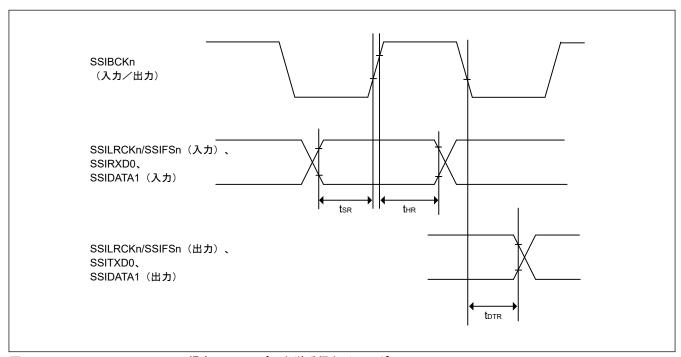

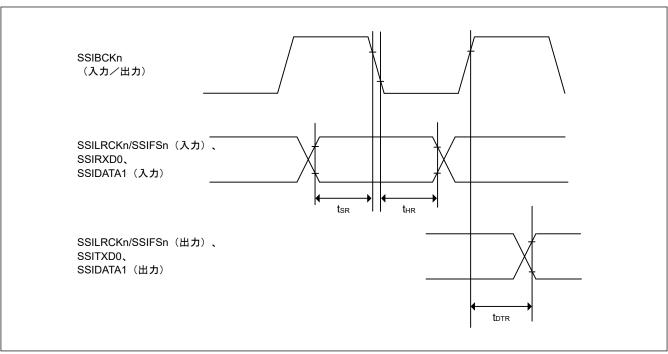

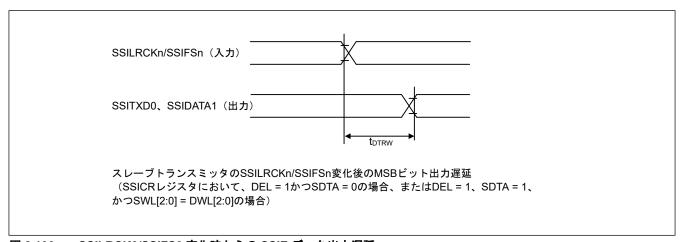

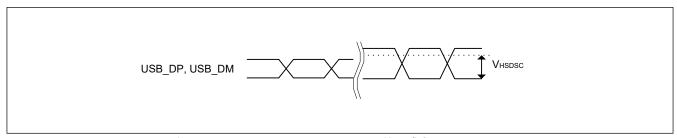

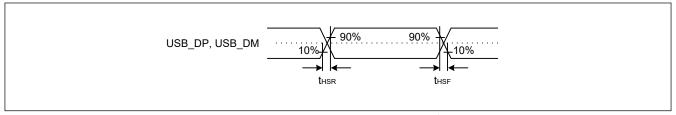

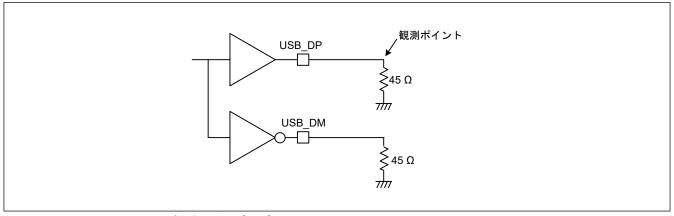

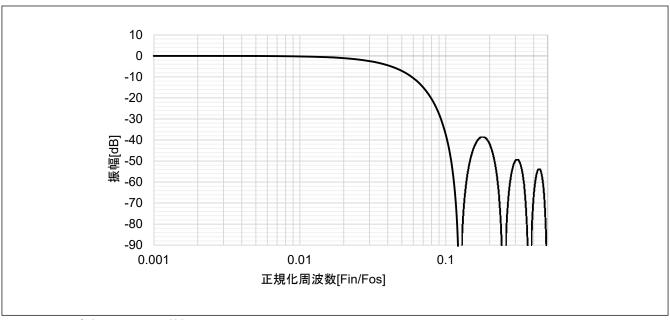

|         | IVCMPn              | 入力  | コンパレータ用アナログ電圧入力端子                                                                             |