RA4T1 グループ

ルネサスマイクロコントローラ

R01DS0415JJ0130 Rev.1.30 Oct 24, 2025

最高 100 MHz の Arm<sup>®</sup> Cortex<sup>®</sup>-M33 コア、128 KB~256 KB のコードフラッシュメモリ、4 KB のデータフラッシュメモリ、 40 KB の SRAM。CANFD、I3C、ADC を含むペリフェラル。

# 特長

- Arm® Cortex®-M33 コア

- Armv8-M アーキテクチャ(メイン拡張)

- 最高動作周波数:100 MHz

- ◆ Arm メモリプロテクションユニット (Arm MPU)

保護メモリシステムアーキテクチャ (PMSAv8)

- セキュア MPU (MPU\_S): 8 領域

- 非セキュア MPU (MPU\_NS): 8 領域 SysTick タイマ

- - 2 つの SysTick タイマを搭載: セキュアおよび非セキュアイ ンスタンス

- LOCO 駆動またはシステムクロック

- CoreSight<sup>™</sup> ETM-M33

## ■メモリ

- 最大 256 KB のコードフラッシュメモリ

- 4 KB のデータフラッシュメモリ (100,000 回のプログラム/ イレース (P/E) サイクル)

- 40 KB ∅ ŠRÁM

### ■ 接続性

- ◆ シリアルコミュニケーションインタフェース (SCI)×2- 調歩同期式インタフェース- 8 ビットクロック同期式インタフェース

- スマートカードインタフェース

- 簡易 IIC

- 簡易 SPI

- マンチェスタコーディング

- I3C バスインタフェース (I3C)

- シリアルペリフェラルインタフェース (SPI) × 2

- CAN フレキシブルデータレート (CANFD)

#### ■アナログ

- 12 ビット A/D コンバータ (ADC12)

サンプル&ホールド回路×3

プログラマブルゲインアンプ×3

高速アナログコンパレータ (ACMPHS)×3

12 ビット D/A コンバータ (DAC12)×2

フロスカース (TSN)

- 温度センサ回路 (TSN)

### ■タイマ

- 16 ビット汎用 PWM タイマ (GPT16E)×6● 低消費電力非同期汎用タイマ (AGT)×2

#### ■ セキュリティ

- Arm® TrustZone®

- Ann Trustzone コードフラッシュ用領域:最大3領域 データフラッシュ用領域:最大2領域

- SRAM 用領域:最大3領域 各ペリフェラルに対して個別のセキュアまたは非セキュア のセキュリティ属性

- 128 ビットの固有の ID

- 真性乱数生成器 (TRNG)

- 端子機能

- セキュア端子マルチプレキシング

#### ■ システムおよび電源管理

- 低消費電力モードイベントリンクコントローラ (ELC)データ転送コントローラ (DTC)

- DMA コントローラ (DMAC) × 8パワーオンリセット

- 低電圧検出 (LVD) (電圧設定)

- ・ ウォッチドッグタイマ (WDT)・ 独立ウォッチドッグタイマ (IWDT)

#### ■ データ処理アクセラレータ

- 三角関数ユニット (TFU)

- マルチクロックソース

- メインクロック発振器 (MOSC) (8~24 MHz)

- サブクロック発振器 (SOSC) (32.768 kHz)

- 高速オンチップオシレータ (HOCO) (16/18/20 MHz)

中速オンチップオシレータ (MOCO) (8 MHz)

- 中盛ネンテップオシレータ (LOCO) (32.768 kHz)● IWDT 専用オンチップオシレータ (15 kHz)

- HOCO/MOCO/LOCO に対するクロックトリム機能

- PLL

- クロックアウトのサポート

#### ■ 汎用入出力ポート

5 V トレラント、オープンドレイン、入力プルアップ、切り替え可能駆動能力

#### ■ 動作電圧

• VCC: 2.7~3.6 V

#### ■ 動作温度およびパッケージ

- $Ta = -40^{\circ}C \sim +105^{\circ}C$

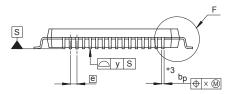

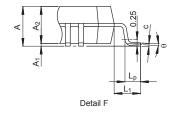

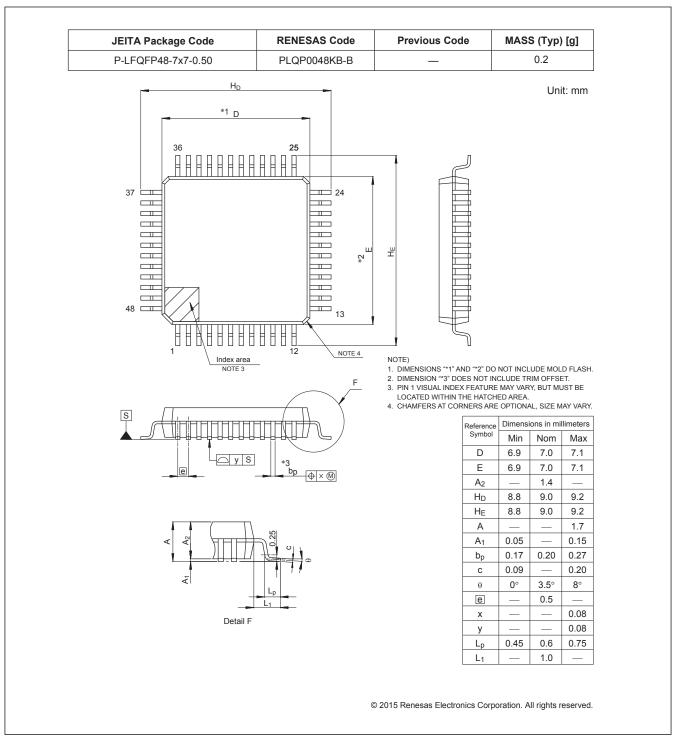

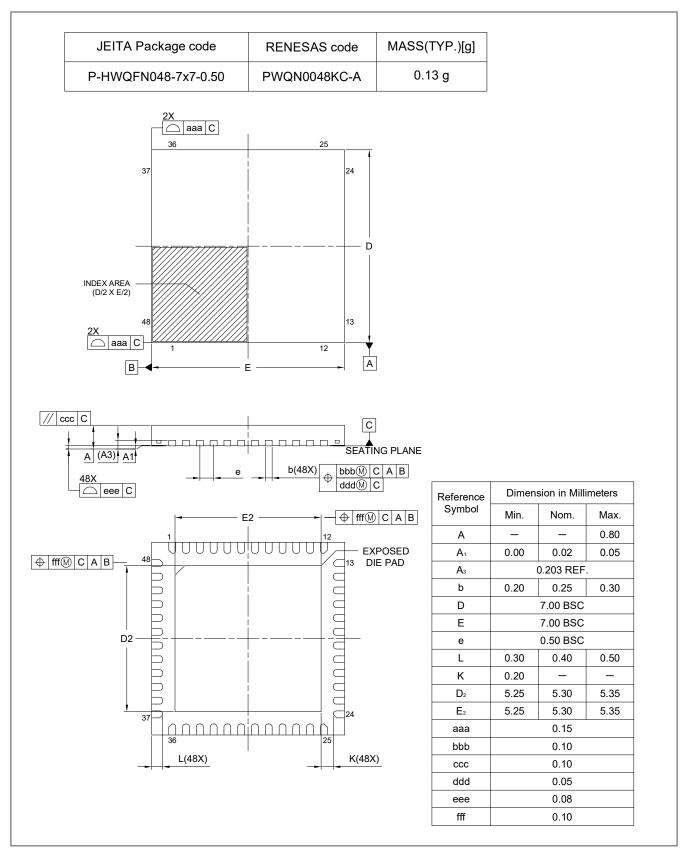

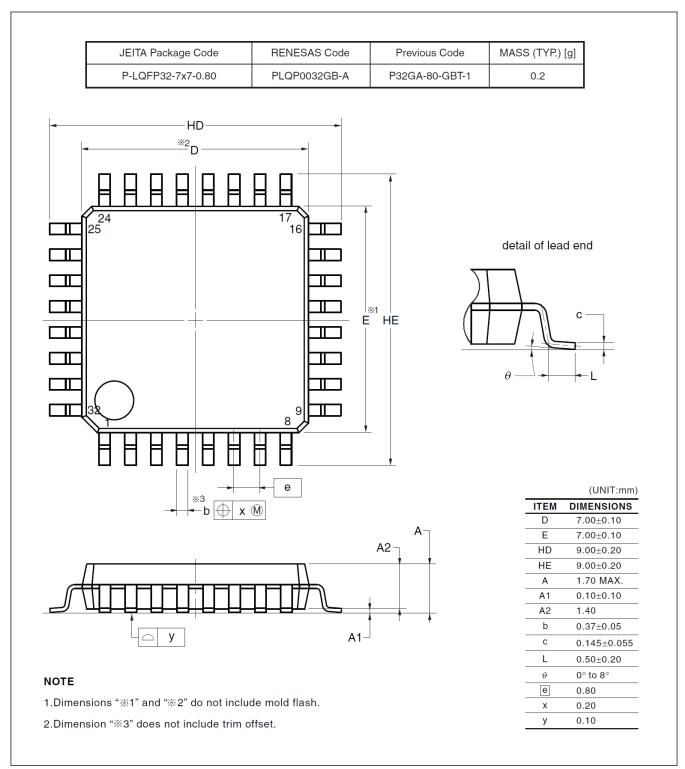

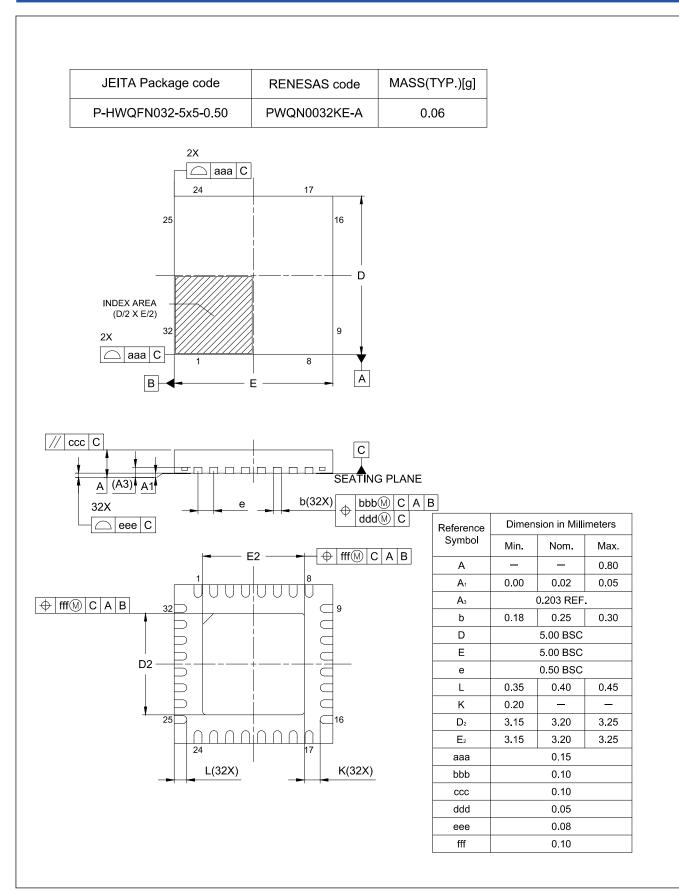

- 1a 40 と + 10.5 cmm × 10 mm、0.5 mm ピッチ) 64 ピン LQFP(10 mm×10 mm、0.5 mm ピッチ) 48 ピン LQFP(7 mm×7 mm、0.5 mm ピッチ) 48 ピン QFN(7 mm×7 mm、0.5 mm ピッチ) 32 ピン LQFP(7 mm×7 mm、0.8 mm ピッチ) 32 ピン QFN(5 mm×5 mm、0.5 mm ピッチ)

# 1. 概要

本MCUは、さまざまなシリーズのソフトウェアおよび端子と互換性のあるArm®ベースの32ビットコアで構成されています。同じ一連のルネサス周辺デバイスを共有することで、設計の拡張性やプラットフォームベースの製品開発の効率が高まります。

本シリーズの MCU は最高 100 MHz で動作する高性能な Arm Cortex®-M33 コアを内蔵しており、以下の特長があります。

- 最大 256 KB のコードフラッシュメモリ

- 40 KB SRAM

- アナログ周辺機能

- セキュリティ&セーフティ機能

# 1.1 機能の概要

## 表 1.1 CPU

| 機能                | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm Cortex-M33 コア | <ul> <li>最高動作周波数: 100 MHz</li> <li>Arm Cortex-M33 コア:         <ul> <li>Armv8-M アーキテクチャ(セキュリティ拡張機能付き)</li> <li>リビジョン: r0p4-00rel0</li> </ul> </li> <li>Arm メモリプロテクションユニット (Arm MPU)         <ul> <li>保護メモリシステムアーキテクチャ (PMSAv8)</li> <li>セキュア MPU (MPU_S): 8 領域</li> <li>非セキュア MPU (MPU_NS): 8 領域</li> </ul> </li> <li>SysTick タイマ         <ul> <li>2 個の Systick タイマ: セキュアおよび非セキュアインスタンス</li> <li>SysTick タイマクロック (SYSTICCLK) またはシステムクロック (ICLK) による駆動</li> </ul> </li> <li>CoreSight™ ETM-M33</li> </ul> |

### 表 1.2 メモリ

| 機能          | 機能の説明                                         |  |

|-------------|-----------------------------------------------|--|

| コードフラッシュメモリ | 大 256 KB のコードフラッシュメモリ。                        |  |

| データフラッシュメモリ | 4 KB のデータフラッシュメモリ。                            |  |

| オプション設定メモリ  | オプション設定メモリは、MCU のリセット後の状態を決定します。              |  |

| SRAM        | パリティビットまたは誤り訂正コード (ECC) を備えた高速 SRAM を内蔵しています。 |  |

## 表 1.3 システム (1/2)

| 機能            | 機能の説明                                                                                                                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 動作モード         | 2 種類の動作モード:  ● シングルチップモード  ● SCI/SWD ブートモード                                                                                                                                                                          |

| リセット          | 本 MCU は、14 種類のリセットをサポートしています。                                                                                                                                                                                        |

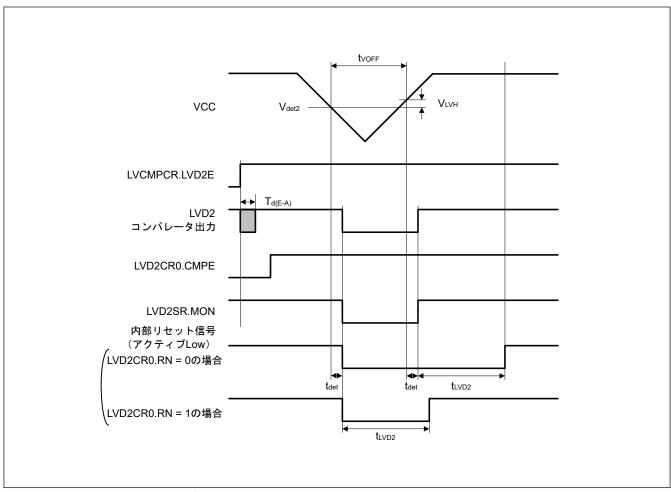

| 低電圧検出回路 (LVD) | 低電圧検出モジュール (LVD) は、VCC 端子への入力電圧レベルを監視します。検出レベルはレジスタ設定で選択できます。LVD は、3 つの独立した電圧監視回路(LVD0、LVD1、LVD2)で構成され、LVD0、LVD1、LVD2 は VCC 端子への入力電圧レベルを監視します。LVD のレジスタを設定することにより、さまざまな電圧しきい値で VCC 端子への入力電圧の変動を監視できます。               |

| クロック          | <ul> <li>メインクロック発振器 (MOSC)</li> <li>サブクロック発振器 (SOSC)</li> <li>高速オンチップオシレータ (HOCO)</li> <li>中速オンチップオシレータ (MOCO)</li> <li>低速オンチップオシレータ (LOCO)</li> <li>IWDT 専用オンチップオシレータ</li> <li>PLL</li> <li>クロックアウトのサポート</li> </ul> |

# 表 1.3 システム (2/2)

| 機能                   | 機能の説明                                                                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| クロック周波数精度測定回路 (CAC)  | クロック周波数精度測定回路 (CAC) は、測定の対象となるクロック (測定対象クロック) に対して、測定の基準となるクロック (測定基準クロック) で生成した時間内のクロックのパルスを数え、それが許容範囲内にあるか否かで精度を判定します。測定終了時、または測定基準クロックで生成した時間内のパルスの数が許容範囲内にない時、割り込み要求を発生します。 |

| 割り込みコントローラユニット (ICU) | 割り込みコントローラユニット (ICU) は、ネスト型ベクタ割り込みコントローラ (NVIC)、DMA<br>コントローラ (DMAC)、およびデータトランスファコントローラ (DTC) モジュールにリンクされ<br>るイベント信号を制御します。ICU はノンマスカブル割り込みも制御します。                              |

| 低消費電力モード             | クロック分周器の設定、モジュールストップ設定、通常動作時の電力制御モード選択、低消費電力モードへの遷移など、さまざまな方法で消費電力を低減できます。                                                                                                      |

| レジスタライトプロテクション       | レジスタライトプロテクション機能は、ソフトウェアエラーによって重要なレジスタが書き換えられないように保護します。保護するレジスタは、プロテクトレジスタ (PRCR) で設定します。                                                                                      |

| メモリプロテクションユニット (MPU) | 本 MCU は、1 つのメモリプロテクションユニットを備えています。                                                                                                                                              |

# 表 1.4 イベントリンク

| 機能  | 機能の説明                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------|

| , , | イベントリンクコントローラ (ELC) は、各周辺モジュールで発生するイベント要求をソース信号として使用し、それらのモジュールを別のモジュールと接続することによって、CPU を介さずにモジュール間の直接リンクを実現します。 |

# 表 1.5 ダイレクトメモリアクセス

| 機能                       | 機能の説明                                                                                                                        |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| データトランスファコントローラ<br>(DTC) | データトランスファコントローラ (DTC) は、割り込み要求によって起動するとデータ転送を行います。                                                                           |

| DMA コントローラ (DMAC)        | 本 MCU は、8 チャネルの DMA コントローラ (DMAC) を内蔵しており、CPU を介さずにデータ<br>転送が可能です。DMA 転送要求が発生すると、DMAC は転送元アドレスに格納されているデー<br>タを転送先アドレスへ転送します。 |

# 表 1.6 タイマ

| 機能                          | 機能の説明                                                                                                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 汎用 PWM タイマ (GPT)            | 汎用 PWM タイマ (GPT) は、GPT16E を 6 チャネルもつ 16 ビットタイマです。PWM 波形はアップカウンタ、ダウンカウンタ、またはその両方を制御することにより生成が可能です。さらに、ブラシレス DC モーターを制御するために、PWM 波形の生成が可能です。GPT は、汎用タイマとしても使用できます。    |

| GPT 用のポートアウトプットイネーブル (POEG) | ポートアウトプットイネーブル (POEG) は、以下の方法のいずれかにより、汎用 PWM タイマ (GPT) の出力端子を出力禁止状態にすることが可能です。                                                                                      |

| 低消費電力非同期汎用タイマ (AGT)         | 低消費電力非同期汎用タイマ (AGT) は、パルス出力、外部パルスの幅または周期の測定、および外部イベントのカウントに利用可能な 32 ビットのタイマです。このタイマは、リロードレジスタとダウンカウンタで構成されています。これらのリロードレジスタとダウンカウンタは、同一アドレスに配置され、AGT レジスタでアクセス可能です。 |

| ウォッチドッグタイマ (WDT)            | ウォッチドッグタイマ (WDT) は 14 ビットのダウンカウンタです。システムが暴走すると WDT をリフレッシュできなくなるため、カウンタがアンダーフローした際に MCU をリセットすることができます。さらに、ノンマスカブル割り込みやアンダーフロー割り込み、を発生させるためにも使用できます。                |

| 独立ウォッチドッグタイマ (IWDT)         | 独立ウォッチドッグタイマ (IWDT) は 14 ビットのダウンカウンタで、システム暴走時に MCU をリセットすることができます。 IWDT は、 MCU をリセットする機能や、カウンタのアンダーフロー発生時に、割り込み/ノンマスカブル割り込みを発生させることが可能です。                           |

# 表 1.7 通信インタフェース

| 機能                                                            | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| シリアルコミュニケーションインタフェース (SCI)                                    | <ul> <li>シリアルコミュニケーションインタフェース (SCI) × 2 チャネルには調歩同期式および同期式のシリアルインタフェースがあります。</li> <li>● 調歩同期式インタフェース (UART および調歩同期式通信インタフェースアダプタ (ACIA))</li> <li>● 8 ビットクロック同期式インタフェース</li> <li>● 簡易 IIC (マスタのみ)</li> <li>● 簡易 SPI</li> <li>● スマートカードインタフェース</li> <li>■ マンチェスタインタフェース</li> <li>スマートカードインタフェース</li> <li>スマートカードインタフェースは、電子信号と伝送プロトコルに関して ISO/IEC 7816-3 規格に準拠しています。SCIn (n = 0, 9) は FIFO バッファを内蔵しており、連続した全二重通信が可能です。また、内蔵のボーレートジェネレータを用いて、データ転送速度の個別設定が可能です。</li> </ul> |

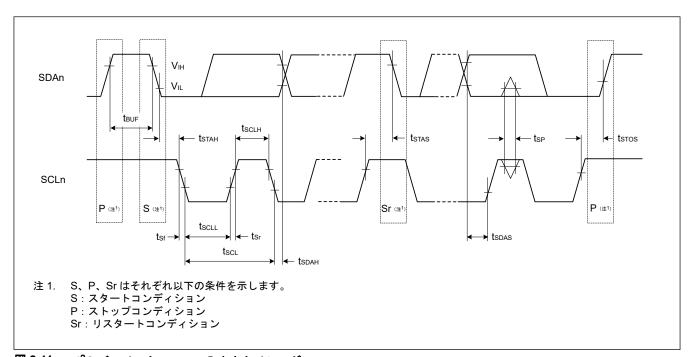

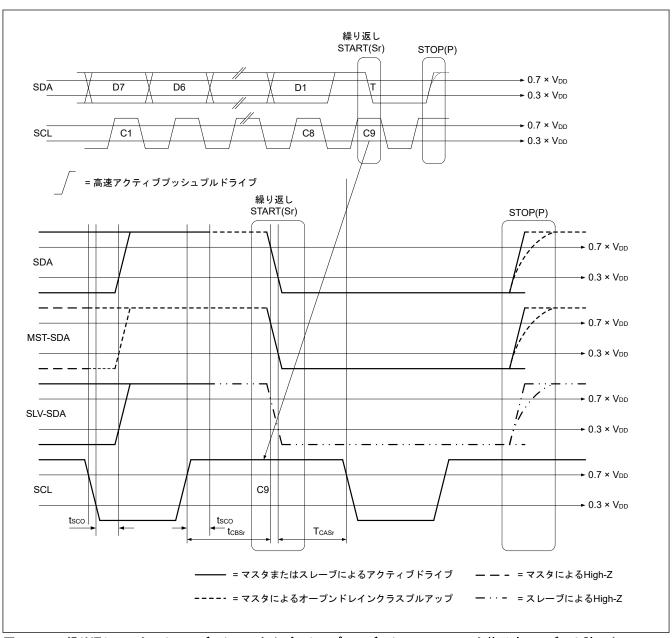

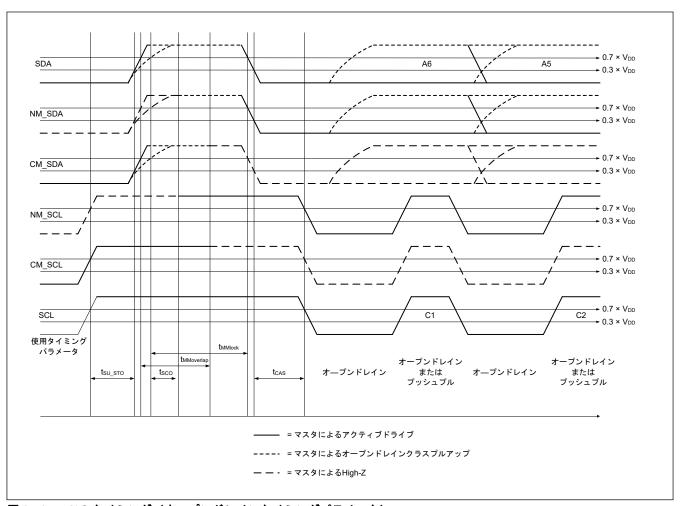

| I3C バスインタフェース (I3C)                                           | I3C バスインタフェース (I3C) には 1 チャネルあります。I3C は、NXP 社の I2C (Inter-Integrated Circuit) および MIPI 社の I3C バスインタフェース方式に準拠しており、それらのサブセット機能を備えています。                                                                                                                                                                                                                                                                                                                                    |

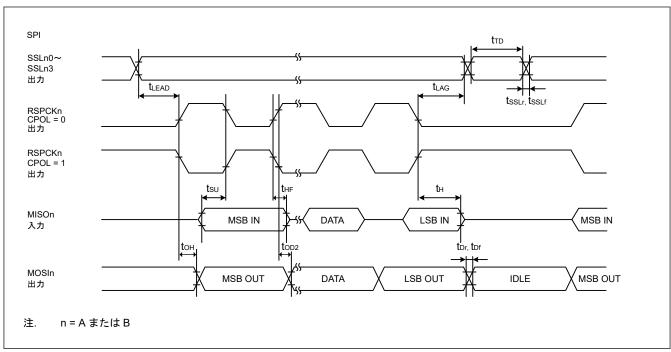

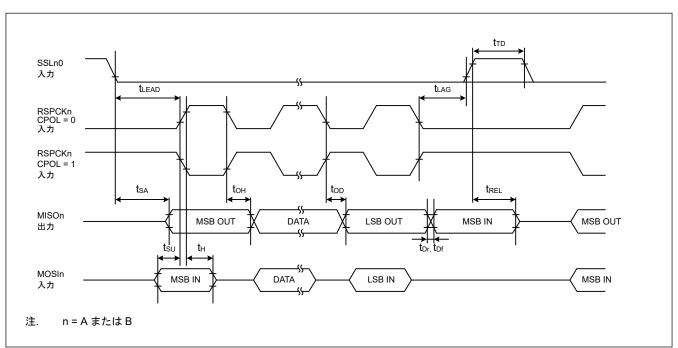

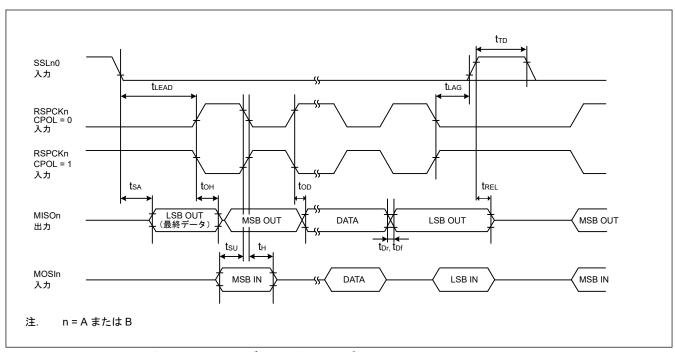

| シリアルペリフェラルインタフェース<br>(SPI)                                    | シリアルペリフェラルインタフェース (SPI) には 2 チャネルあります。SPI によって、複数のプロセッサや周辺デバイスとの高速な全二重同期式シリアル通信が可能です。                                                                                                                                                                                                                                                                                                                                                                                   |

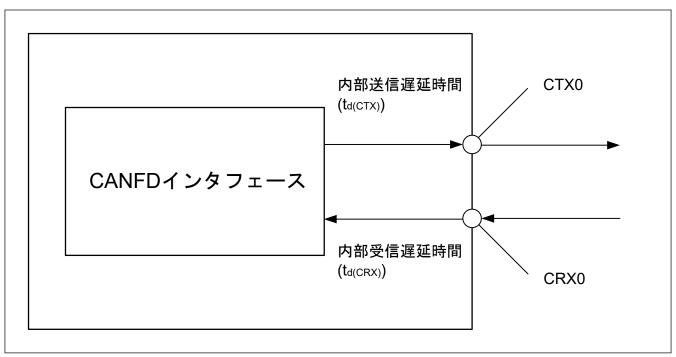

| Control Area Network with Flexible<br>Data-Rate モジュール (CANFD) | CAN with Flexible Data-Rate (CANFD) モジュールは、クラシカル CAN フレームと ISO 11898-1<br>規格に準拠する CANFD フレームの両方を取り扱うことができます。<br>このモジュールは4つの送信バッファと32の受信バッファをサポートしています。                                                                                                                                                                                                                                                                                                                  |

# 表 1.8 アナログ機能

| 機能                       | 機能の説明                                                                                                                                                                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

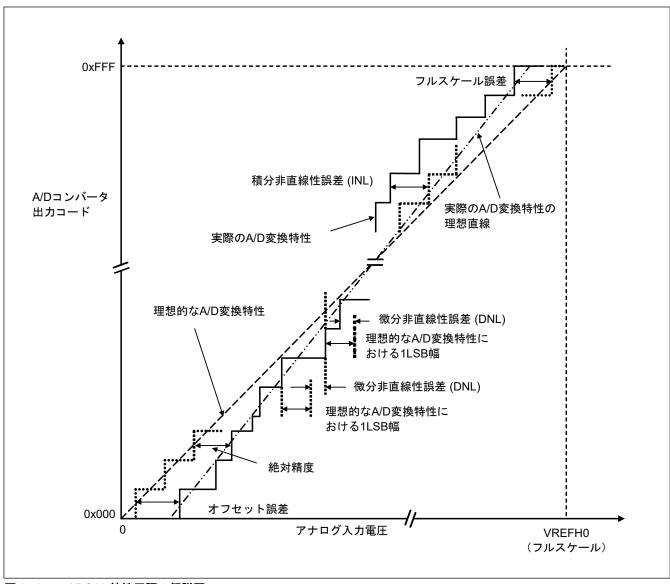

| 12 ビット A/D コンバータ (ADC12) | サンプル&ホールド回路とプログラマブルゲインアンプ (PGA) を備えた逐次比較方式の 12 ビット A/D コンバータ (ADC12) です。最大 12 チャネルのアナログ入力を選択可能です。変換には温度センサ出力および内部基準電圧を選択できます。                                                                                                                         |

| 12 ビット D/A コンバータ (DAC12) | 12 ビットの D/A コンバータ (DAC12) を内蔵しています。                                                                                                                                                                                                                   |

| 高速アナログコンパレータ (ACMPHS)    | 高速アナログコンパレータ (ACMPHS) は試験電圧と基準電圧を比較し、比較結果に基づいてデジタル出力します。試験電圧と基準電圧は、どちらも DAC12 出力や内部基準電圧などの内部ソース、および外部ソース(内部 PGA 有りまたは無し)からコンパレータに供給できます。このような柔軟性は、A/D 変換を行うことなくアナログ信号間の合否判定を実施する必要があるアプリケーションで有用です。section x, High-Speed Analog Comparator を参照してください。 |

| 温度センサ (TSN)              | デバイス動作の信頼性確保のため、内蔵されている温度センサ (TSN) でチップの温度を測定し、監視します。センサはチップの温度と正比例する電圧を出力します。チップ温度と出力電圧はほとんどリニアの関係にあります。出力された電圧は ADC12 で変換されてから、末端の応用機器で使用できます。                                                                                                      |

# 表 1.9 データ処理

| 機能               | 機能の説明                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 巡回冗長検査 (CRC) 演算器 | 巡回冗長検査 (CRC: Cyclic Redundancy Check) は、CRC コードを生成してデータエラーを検出します。LSB ファーストまたは MSB ファーストでの通信用に、CRC 演算結果のビットオーダーを切り替えることができます。さらに、さまざまな CRC 生成多項式を使用できます。 |

| データ演算回路 (DOC)    | データ演算回路 (DOC) は、16 ビットのデータを比較、加算、または減算する機能です。選択した条件に一致する場合、割り込み要求が発生します。                                                                                |

# 表 1.10 データ処理アクセラレータ

| 機能             | 機能説明                                                                            |

|----------------|---------------------------------------------------------------------------------|

| 三角関数ユニット (TFU) | 正弦、余弦、逆正接、および平方根 (x2 + y2)  ■ 正弦と余弦は同時に計算できます。  ■ 逆正接と平方根 (x2 + y2) は同時に計算できます。 |

# 表 1.11 I/O ポート

| 機能              | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| プログラマブル I/O ポート | <ul> <li>64 ピンLQFP 用の I/O ポート         <ul> <li>入出力端子:45</li> <li>入力端子:5</li> <li>プルアップ抵抗:46</li> <li>Nチャネルオープンドレイン出力:45</li> <li>5Vトレラント:11</li> </ul> </li> <li>48 ピンLQFP 用の I/O ポート             <ul> <li>入出力端子:29</li> <li>入力端子:5</li> <li>プルアネルオープンドレイン出力:29</li> <li>5Vトレラント:6</li> <li>32 ピンLQFP 用の I/O ポート                     <ul> <li>入力端子:16</li> <li>入力端子:5</li> <li>プルアップ抵抗:17</li> <li>Nチャネルント:4</li> <li>48 ピン QFN 用の I/O ポート</li> <li>入出力端子:29</li> <li>入力端子:5</li> <li>プルアップ抵抗:30</li> <li>Nチャネルナープンドレイン出力:29</li> <li>5Vトレラント:6</li> <li>32 ピン QFN 用の I/O ポート</li> <li>入出力端子:5</li> <li>プルアップ抵抗:17</li> <li>入力端子:5</li> <li>プルアップ抵抗:17</li> <li>Nチャネルオープンドレイン出力:16</li> <li>5Vトレラント:4</li> <li>Nチャネルオープンドレイン出力:16</li> <li>ラント・5</li> <li>プルアップ抵抗:17</li> <li>Nチャネルオープンドレイン出力:16</li> <li>ストナーラント:4</li> <li>ストナーシート・</li> <li>ストナー・</li> <li>ストナ</li></ul></li></ul></li></ul> |

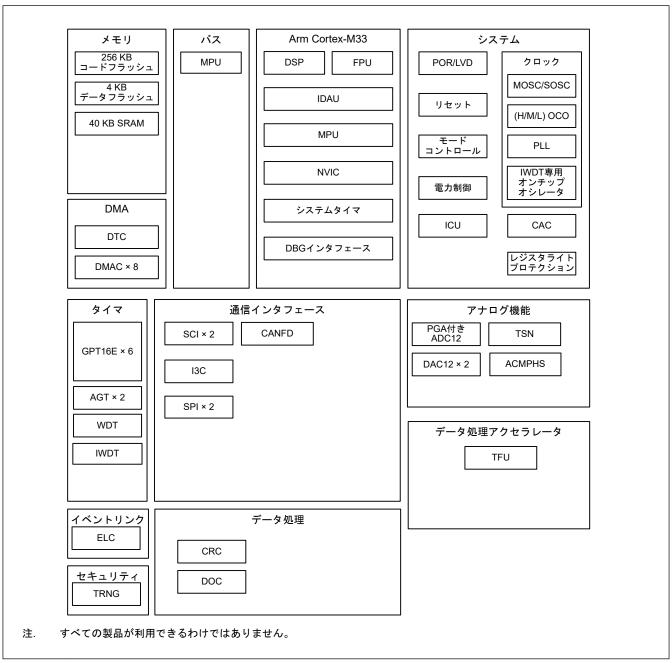

# 1.2 ブロック図

図 1.1 に、本 MCU のスーパーセットのブロック図を示します。グループ内の個々のデバイスは、その機能のサブセットを持つ場合があります。

図 1.1 ブロック図

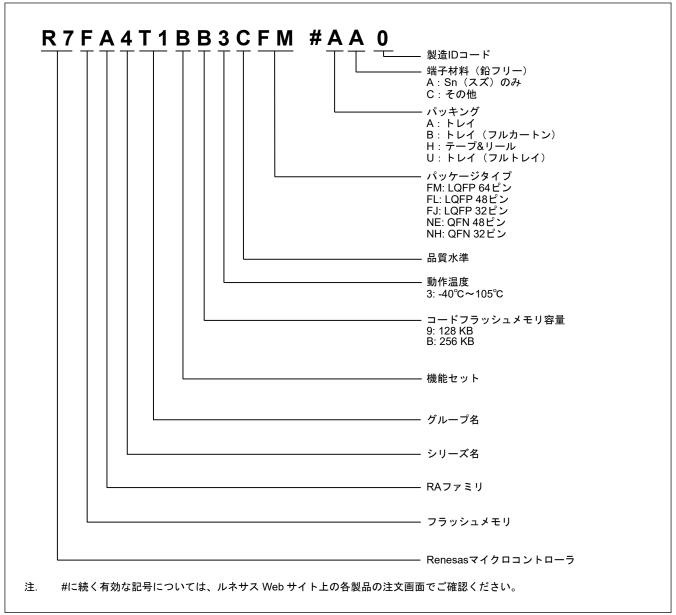

## 1.3 型名

図 1.2 に、メモリ容量およびパッケージタイプを含む製品の型名情報を示します。表 1.12 に、製品一覧表を示します。

### 図 1.2 型名の読み方

## 表 1.12 製品一覧

| 製品型名          | パッケージコード     | コードフラッ<br>シュ | データフ<br>ラッシュ | SRAM  | 動作温度       |

|---------------|--------------|--------------|--------------|-------|------------|

| R7FA4T1BB3CFM | PLQP0064KB-C | 256 KB       | 4 KB         | 40 KB | -40∼+105°C |

| R7FA4T1BB3CFL | PLQP0048KB-B |              |              |       |            |

| R7FA4T1BB3CFJ | PLQP0032GB-A |              |              |       |            |

| R7FA4T1BB3CNE | PWQN0048KC-A |              |              |       |            |

| R7FA4T1BB3CNH | PWQN0032KE-A |              |              |       |            |

| R7FA4T1B93CFM | PLQP0064KB-C | 128 KB       | 4 KB         | 40 KB | -40∼+105°C |

| R7FA4T1B93CFL | PLQP0048KB-B |              |              |       |            |

| R7FA4T1B93CFJ | PLQP0032GB-A |              |              |       |            |

| R7FA4T1B93CNE | PWQN0048KC-A |              |              |       |            |

| R7FA4T1B93CNH | PWQN0032KE-A |              |              |       |            |

# 1.4 機能の比較

# 表 1.13 機能の比較

| 型名          |                        | R7FA4T1BB3CFM/<br>R7FA4T1B93CFM | R7FA4T1BB3CFL/<br>R7FA4T1B93CFL<br>R7FA4T1BB3CNE/<br>R7FA4T1B93CNE | R7FA4T1BB3CFJ/<br>R7FA4T1B93CFJ<br>R7FA4T1BB3CNH/<br>R7FA4T1B93CNH |  |  |

|-------------|------------------------|---------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| 端子総数        |                        | 64                              | 48                                                                 | 32                                                                 |  |  |

| パッケージ       |                        | LQFP                            | LQFP/QFN                                                           | LQFP/QFN                                                           |  |  |

| コードフラッシュメモリ |                        |                                 | 256 KB、128 KB                                                      |                                                                    |  |  |

| データフラッシュメモリ |                        |                                 | 4 KB                                                               |                                                                    |  |  |

| SRAM        |                        |                                 | 40 KB                                                              |                                                                    |  |  |

|             | パリティ                   |                                 | 32 KB                                                              |                                                                    |  |  |

|             | ECC                    |                                 | 8 KB                                                               |                                                                    |  |  |

| DMA         | DTC                    |                                 | あり                                                                 |                                                                    |  |  |

|             | DMAC                   |                                 | 8                                                                  |                                                                    |  |  |

| システム        | CPU クロック               |                                 | 最高 100 MHz                                                         |                                                                    |  |  |

|             | CPU クロックソース            | MOSC, S                         | SOSC, HOCO, MOCO, L                                                | OCO、PLL                                                            |  |  |

|             | CAC                    |                                 | あり                                                                 |                                                                    |  |  |

|             | WDT/IWDT               |                                 | あり                                                                 |                                                                    |  |  |

| 通信          | SCI                    |                                 | 2                                                                  |                                                                    |  |  |

|             | I3C                    | 1                               |                                                                    |                                                                    |  |  |

|             | SPI                    | 2                               |                                                                    |                                                                    |  |  |

|             | CANFD                  | 1                               |                                                                    |                                                                    |  |  |

| タイマ         | GPT16E <sup>(注1)</sup> |                                 | 6                                                                  | 4                                                                  |  |  |

|             | AGT <sup>(注1)</sup>    | 2                               |                                                                    |                                                                    |  |  |

| アナログ        | ADC12                  | 12                              | 8                                                                  | 5                                                                  |  |  |

|             | DAC12                  |                                 | 2                                                                  | 1                                                                  |  |  |

|             | ACMPHS                 |                                 | 3                                                                  |                                                                    |  |  |

|             | PGA                    |                                 | 3                                                                  |                                                                    |  |  |

|             | TSN                    |                                 | あり                                                                 |                                                                    |  |  |

| データ処理       | CRC                    |                                 | あり                                                                 |                                                                    |  |  |

|             | DOC                    |                                 | あり                                                                 |                                                                    |  |  |

| イベントコントロール  | ELC                    |                                 | あり                                                                 |                                                                    |  |  |

| アクセラレータ     | TFU                    |                                 | あり                                                                 |                                                                    |  |  |

| セキュリティ      |                        |                                 | TrustZone                                                          |                                                                    |  |  |

| I/O ポート     | 入出力端子                  | 45                              | 29                                                                 | 16                                                                 |  |  |

|             | 入力端子                   | 5                               | 5                                                                  | 5                                                                  |  |  |

|             | プルアップ抵抗                | 46                              | 30                                                                 | 17                                                                 |  |  |

|             | N チャネルオープンドレ<br>イン出力   | 45                              | 29                                                                 | 16                                                                 |  |  |

|             | 5 V トレラント              | 11                              | 6                                                                  | 4                                                                  |  |  |

注 1. 使用できる端子はピン数によります。詳細は、「1.7. 端子一覧」を参照してください。

# 1.5 端子機能

# 表 1.14 端子機能一覧 (1/3)

| 機能          | 端子名                                   | 入出力 | 説明                                                                               |  |  |  |  |  |

|-------------|---------------------------------------|-----|----------------------------------------------------------------------------------|--|--|--|--|--|

| 電源          | vcc                                   | 入力  | 電源端子。システムの電源に接続してください。この端子は 0.1 µF のコンデンサを介して VSS に接続してください。コンデンサは端子近くに配置してください。 |  |  |  |  |  |

|             | VCL                                   | 入出力 | この端子は、内部電源を安定化するための平滑コンデンサを介して VSS 端子に接続してください。コンデンサは端子近くに配置してください。              |  |  |  |  |  |

|             | VSS                                   | 入力  | グランド端子。システムの電源 (0 V) に接続してください。                                                  |  |  |  |  |  |

| クロック        | XTAL                                  | 出力  | 水晶振動子用の接続端子。EXTAL 端子を通じて外部クロック信号の                                                |  |  |  |  |  |

|             | EXTAL                                 | 入力  | 入力が可能です。                                                                         |  |  |  |  |  |

|             | XCIN                                  | 入力  | サブクロック発振器用の入出力端子。XCOUT と XCIN の間には、水                                             |  |  |  |  |  |

|             | XCOUT                                 | 出力  | ── 晶振動子を接続してください。<br>                                                            |  |  |  |  |  |

|             | CLKOUT                                | 出力  | クロック出力端子                                                                         |  |  |  |  |  |

| 動作モードコントロール | MD                                    | 入力  | 動作モード設定用の端子。本端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                             |  |  |  |  |  |

| システム制御      | RES                                   | 入力  | リセット信号入力端子。本端子が Low になると、MCU はリセット状態となります。                                       |  |  |  |  |  |

| CAC         | CACREF                                | 入力  | 測定基準クロックの入力端子                                                                    |  |  |  |  |  |

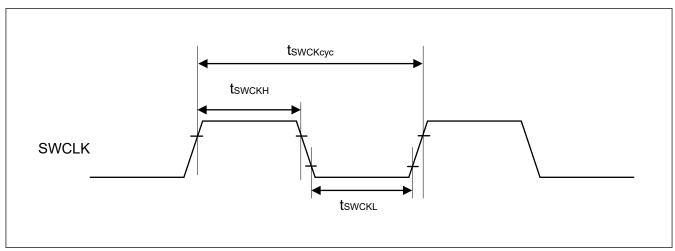

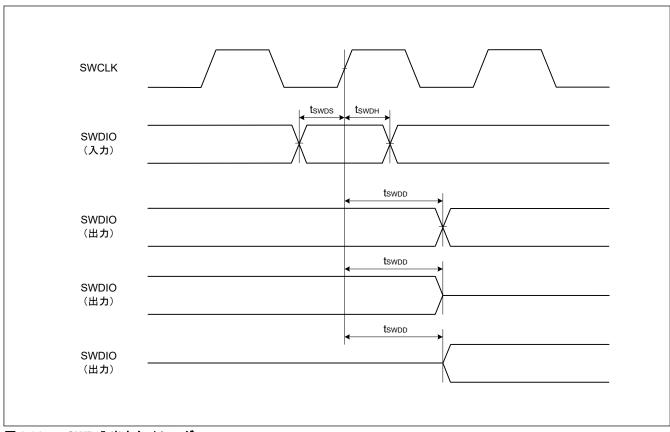

| オンチップエミュレータ | SWDIO                                 | 入出力 | シリアルワイヤデバッグデータの入出力端子                                                             |  |  |  |  |  |

|             | SWCLK                                 | 入力  | シリアルワイヤクロック端子                                                                    |  |  |  |  |  |

| 割り込み        | NMI                                   | 入力  | ノンマスカブル割り込み要求端子                                                                  |  |  |  |  |  |

|             | IRQn                                  | 入力  | マスカブル割り込み要求端子                                                                    |  |  |  |  |  |

|             | IRQn-DS                               | 入力  | マスカブル割り込み要求端子は、ディープソフトウェアスタンバイモード時も使用できます。                                       |  |  |  |  |  |

| GPT         | GTETRGA, GTETRGB,<br>GTETRGC, GTETRGD | 入力  | 外部トリガ入力端子                                                                        |  |  |  |  |  |

|             | GTIOCnA, GTIOCnB                      | 入出力 | インプットキャプチャ、アウトプットコンペア、または PWM 出力<br>端子                                           |  |  |  |  |  |

|             | GTADSM0, GTADSM1                      | 出力  | A/D 変換開始要求モニタリング出力端子                                                             |  |  |  |  |  |

|             | GTIU                                  | 入力  | ホールセンサ入力端子 U                                                                     |  |  |  |  |  |

|             | GTIV                                  | 入力  | ホールセンサ入力端子 V                                                                     |  |  |  |  |  |

|             | GTIW                                  | 入力  | ホールセンサ入力端子 W                                                                     |  |  |  |  |  |

|             | GTOUUP                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 U 相)                                                  |  |  |  |  |  |

|             | GTOULO                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 U 相)                                                  |  |  |  |  |  |

|             | GTOVUP                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 V 相)                                                  |  |  |  |  |  |

|             | GTOVLO                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 V 相)                                                  |  |  |  |  |  |

|             | GTOWUP                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(正相 W 相)                                                  |  |  |  |  |  |

|             | GTOWLO                                | 出力  | BLDC モーター制御用 3 相 PWM 出力(逆相 W 相)                                                  |  |  |  |  |  |

| AGT         | AGTEEn                                | 入力  | 外部イベント入力イネーブル信号                                                                  |  |  |  |  |  |

|             | AGTIOn                                | 入出力 | 外部イベント入力およびパルス出力端子                                                               |  |  |  |  |  |

|             | AGTOn                                 | 出力  | パルス出力端子                                                                          |  |  |  |  |  |

|             | AGTOAn                                | 出力  | 出力コンペアマッチ A 出力端子                                                                 |  |  |  |  |  |

|             | AGTOBn                                | 出力  | 出力コンペアマッチ B 出力端子                                                                 |  |  |  |  |  |

# 表 1.14 端子機能一覧 (2/3)

| 機能     | 端子名                         | 入出力 | 説明                                                                     |

|--------|-----------------------------|-----|------------------------------------------------------------------------|

| SCI    | SCKn                        | 入出力 | クロック用の入出力端子 (クロック同期式モード)                                               |

|        | RXDn                        | 入力  | 受信データ用の入力端子(調歩同期式モード/クロック同期式モード)                                       |

|        | TXDn                        | 出力  | 送信データ用の出力端子(調歩同期式モード/クロック同期式モード)                                       |

|        | CTSn_RTSn                   | 入出力 | 送受信の開始制御用の入出力端子(調歩同期式モード/クロック同期式モード)、アクティブ Low                         |

|        | CTSn                        | 入力  | 送信の開始用の入力端子                                                            |

|        | SCLn                        | 入出力 | IIC クロック用の入出力端子(簡易 IIC モード)                                            |

|        | SDAn                        | 入出力 | IIC データ用の入出力端子(簡易 IIC モード)                                             |

|        | SCKn                        | 入出力 | クロック用の入出力端子(簡易 SPI モード)                                                |

|        | MISOn                       | 入出力 | データのスレーブ送信用の入出力端子(簡易 SPI モード)                                          |

|        | MOSIn                       | 入出力 | データのマスタ送信用の入出力端子(簡易 SPI モード)                                           |

|        | SSn                         | 入力  | チップセレクト入力端子(簡易 SPI モード)、アクティブ Low                                      |

| I3C    | I3C_SCL                     | 入出力 | I3C クロック入出力端子                                                          |

|        | I3C_SDA                     | 入出力 | I3C データ用の入出力端子                                                         |

|        | SCL0                        | 入出力 | I2C クロック入出力端子                                                          |

|        | SDA0                        | 入出力 | I2C データ用の入出力端子                                                         |

| SPI    | RSPCKA, RSPCKB              | 入出力 | クロック入出力端子                                                              |

|        | MOSIA, MOSIB                | 入出力 | マスタからの出力データ用の入出力端子                                                     |

|        | MISOA, MISOB                | 入出力 | スレーブからの出力データ用の入出力端子                                                    |

|        | SSLA0, SSLB0                | 入出力 | スレーブ選択用の入出力端子                                                          |

|        | SSLA1~SSLA3、SSLB1<br>~SSLB3 | 出力  | スレーブ選択用の出力端子                                                           |

| CANFD  | CRX0                        | 入力  | 受信データ                                                                  |

|        | CTX0                        | 出力  | 送信データ                                                                  |

| アナログ電源 | AVCC0                       | 入力  | アナログ電源端子。それぞれのモジュールのアナログ電源端子として使用されます。この端子には VCC 端子と同じ電圧を供給してください。     |

|        | AVSS0                       | 入力  | アナロググランド端子。それぞれのモジュールのアナロググランド端子として使用されます。この端子には VSS 端子と同じ電圧を供給してください。 |

|        | VREFH                       | 入力  | D/A コンバータ用のアナログ基準電圧源端子                                                 |

|        | VREFL                       | 入力  | D/A コンバータ用のアナログ基準グランド端子                                                |

|        | VREFH0                      | 入力  | ADC12 用のアナログ基準電圧源端子。ADC12 を使用しない場合は<br>AVCC0 に接続してください。                |

|        | VREFL0                      | 入力  | ADC12 用のアナログ基準グランド端子。ADC12 を使用しない場合は AVSS0 に接続してください。                  |

| ADC12  | AN0n                        | 入力  | A/D コンバータで処理されるアナログ信号用の入力端子(n:ピン番号)                                    |

|        | ADTRG0                      | 入力  | A/D 変換を開始する外部トリガ信号用の入力端子、アクティブ Low                                     |

|        | PGAVSS000                   | 入力  | 疑似差動入力端子                                                               |

| DAC12  | DAn                         | 出力  | D/A コンバータで処理されるアナログ信号用の出力端子                                            |

| ACMPHS | VCOUT                       | 出力  | コンパレータ出力端子                                                             |

|        | IVREFn                      | 入力  | コンパレータ用基準電圧入力端子                                                        |

|        | IVCMPn                      | 入力  | コンパレータ用アナログ電圧入力端子                                                      |

# 表 1.14 端子機能一覧 (3/3)

| 機能      | 端子名  | 入出力 | 説明                      |

|---------|------|-----|-------------------------|

| I/O ポート | Pmn  | 入出力 | 汎用入出力端子(m:ポート番号、n:ピン番号) |

|         | P200 | 入力  | 汎用入力端子                  |

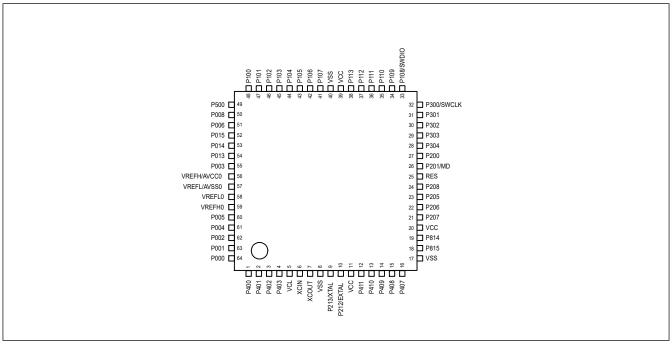

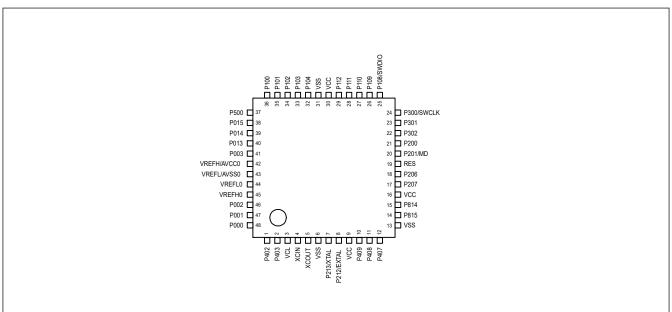

# 1.6 ピン配置図

以下にピン配置図(上面図)を示します。

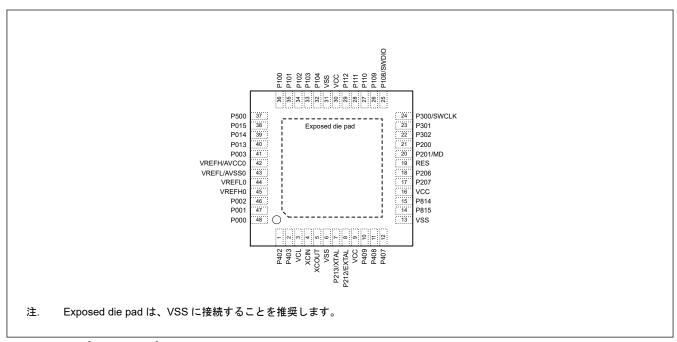

図 1.3 64 ピン LQFP のピン配置

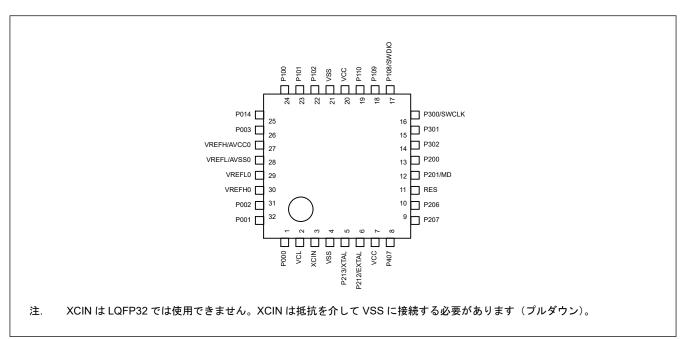

図 1.4 48 ピン LQFP のピン配置

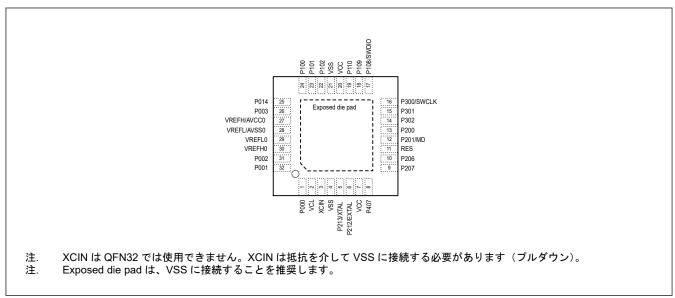

## 図 1.5 48 ピン QFN のピン配置

図 1.6 32 ピン LQFP のピン配置

図 1.7 32 ピン QFN のピン配置

# 1.7 端子一覧

# 表 1.15 端子一覧 (1/2)

| <u> </u> | -4III J         | <i>5</i> E (1/  |                               |         |          |                                  |                            |                        |

|----------|-----------------|-----------------|-------------------------------|---------|----------|----------------------------------|----------------------------|------------------------|

| LQFP64   | LQFP48<br>QFN48 | LQFP32<br>QFN32 | 電源、システム、<br>クロック、デバッグ、<br>CAC | 1/0 ポート | 外部割り込み   | SCI/I3C/SPI/CANFD                | GPT/AGT                    | ADC12/DAC12/<br>ACMPHS |

| 1        | _               |                 | _                             | P400    | IRQ0     | SCL0_A                           | AGTIO1                     | _                      |

| 2        | _               | _               | _                             | P401    | IRQ5-DS  | SDA0_A/CTX0                      | GTETRGA                    | _                      |

| 3        | 1               | _               | CACREF                        | P402    | IRQ4-DS  | CRX0                             | AGTIO0/AGTIO1/<br>GTADSM1  | _                      |

| 4        | 2               | _               | _                             | P403    | IRQ14-DS |                                  | GTIOC3A/AGTIO0/            | _                      |

| 5        | 3               | 2               | VCL                           | _       |          |                                  | AGTIO1                     | _                      |

| 6        | 4               | 3               | XCIN <sup>(注1)</sup>          | _       |          |                                  | _                          | _                      |

| 7        | 5               | _               | XCOUT                         | _       |          |                                  |                            | _                      |

| 8        | 6               | 4               | VSS                           | _       |          |                                  |                            | _                      |

| 9        | 7               | 5               | XTAL                          | P213    | IRQ2     | TXD0/MOSI0/SDA0                  | GTIOC0A/GTETRGC            | _                      |

| 10       | 8               | 6               | EXTAL                         | P212    | IRQ3     | RXD0/MISO0/SCL0                  | GTIOC0B/GTETRGD/<br>AGTEE1 | _                      |

| 11       | 9               | 7               | VCC                           |         |          |                                  | AGTEET                     |                        |

| 11       |                 | _               | VCC                           | P411    | IRQ4     | TXD0/MOSI0/SDA0                  | GTOVUP                     | _                      |

| 13       | -<br> -         |                 | _                             | P411    | IRQ4     | RXD0/MISO0/SCL0                  | GTOVLO                     | _                      |

| 14       | 10              | _               | _                             | P410    | IRQ5     | — RXDU/MISOU/SCLU                | GTIOC1A/GTOWUP/<br>AGTOA1  | _                      |

| 15       | 11              | _               | _                             | P408    | IRQ7     | SCL0_B                           | GTIOC1B/GTIW/<br>AGTOB1    | _                      |

| 16       | 12              | 8               | _                             | P407    |          | SDA0_B                           | GTIV/AGTIO0/<br>GTADSM0    | ADTRG0                 |

| 17       | 13              | _               | VSS                           | _       |          |                                  | _                          | _                      |

| 18       | 14              | _               | _                             | P815    |          |                                  | GTIOC0A/GTETRGC            | _                      |

| 19       | 15              | <u> </u>        |                               | P814    |          |                                  | GTIOC0B/GTETRGB            | _                      |

| 20       | 16              | _               | VCC                           | _       |          |                                  | _                          |                        |

| 21       | 17              | 9               | CACREF                        | P207    | _        | SCK9/MOSIA_A                     | GTIOC5A/GTIW/<br>AGTIO1    | _                      |

| 22       | 18              | 10              | _                             | P206    | IRQ0-DS  | CTS9/SDA0_C/<br>MISOA_A          | GTIOC5B/GTIU               | _                      |

| 23       | _               | _               | CLKOUT                        | P205    | IRQ1-DS  | CTS_RTS9/SS9/<br>SCL0_C/SSLA3_A  | GTIOC4A/GTIV/AGTO1         | _                      |

| 24       | _               | _               | _                             | P208    |          | _                                | GTOVLO                     | ADTRG0                 |

| 25       | 19              | 11              | RES                           | _       |          |                                  | _                          | _                      |

| 26       | 20              | 12              | MD                            | P201    |          |                                  | _                          | _                      |

| 27       | 21              | 13              | _                             | P200    | NMI      |                                  | _                          | _                      |

| 28       | _               | _               | _                             | P304    | IRQ9     |                                  | GTOWLO                     | _                      |

| 29       | _               | _               | _                             | P303    |          | CTS9                             | _                          | _                      |

| 30       | 22              | 14              | _                             | P302    | IRQ5     | CTS0/SCK9/<br>RSPCKA_A           | GTIOC4A/GTOUUP             | _                      |

| 31       | 23              | 15              | _                             | P301    | IRQ6     | CTS_RTS9/SS9/<br>SSLA0_A         | GTIOC4B/GTOULO/<br>AGTIO0  | _                      |

| 32       | 24              | 16              | SWCLK                         | P300    |          | SSLA1_B                          | GTIOC0A/GTOUUP             | _                      |

| 33       | 25              | 17              | SWDIO                         | P108    | _        | CTS_RTS9/SS9/<br>SSLA0_B         | GTIOC0B/GTOULO             | _                      |

| 34       | 26              | 18              | CLKOUT                        | P109    |          | TXD9/MOSI9/SDA9/<br>MOSIA_B/CTX0 | GTIOC1A/GTOVUP/<br>AGTOA0  | _                      |

| 35       | 27              | 19              | _                             | P110    | IRQ3     | RXD9/MISO9/SCL9/<br>MISOA_B/CRX0 | GTIOC1B/GTOVLO/<br>AGTOB0  | VCOUT                  |

| 36       | 28              | _               | _                             | P111    | IRQ4     | SCK9/RSPCKA B                    | GTIOC3A                    | _                      |

| 37       | 29              | _               | _                             | P112    | _        | SSLA0_B                          | GTIOC3B/GTETRGD/<br>AGTO1  | _                      |

| 38       | _               | _               |                               | P113    |          |                                  | GTIOC2A                    | _                      |

| 39       | 30              | 20              | VCC                           | _       |          |                                  |                            | _                      |

#### 表 1.15 端子一覧 (2/2)

| <u> </u> | 710 3           | JE (=/-         | ,                             |          |          |                                              |                            |                        |

|----------|-----------------|-----------------|-------------------------------|----------|----------|----------------------------------------------|----------------------------|------------------------|

| LQFP64   | LQFP48<br>QFN48 | LQFP32<br>QFN32 | 電源、システム、<br>クロック、デパッグ、<br>CAC | <b>₩</b> | 外部割り込み   | SCI/I3C/SPI/CANFD                            | GPT/AGT                    | ADC12/DAC12/<br>ACMPHS |

| 40       | 31              | 21              | VSS                           | _        | _        | _                                            | _                          | _                      |

| 41       | _               | _               | _                             | P107     | _        | SSLA2_B                                      | AGTOA0                     | _                      |

| 42       | _               | _               | _                             | P106     | _        | SSLB3                                        | AGTOB0                     | _                      |

| 43       | _               | _               | _                             | P105     | IRQ0     | SSLB2                                        | GTIOC1A/GTETRGA            | _                      |

| 44       | 32              | _               | _                             | P104     | IRQ1     | SSLB1                                        | GTIOC1B/GTETRGB/<br>AGTIO1 | _                      |

| 45       | 33              | _               | _                             | P103     | _        | CTS_RTS0/SS0/SSLB0/<br>CTX0                  | GTIOC2A/GTOWUP             | _                      |

| 46       | 34              | 22              | _                             | P102     | _        | SCK0/RSPCKB/CRX0/<br>QIO0/SSIBCK0_B          | GTIOC2B/GTOWLO/<br>AGTO0   | ADTRG0                 |

| 47       | 35              | 23              | _                             | P101     | IRQ1     | TXD0/MOSI0/SDA0/<br>I3C_SDA/SDA0_D/<br>MOSIB | GTIOC5A/GTETRGB/<br>AGTEE0 | _                      |

| 48       | 36              | 24              | _                             | P100     | IRQ2     | RXD0/MISO0/SCL0/<br>I3C_SCL/SCL0_D/<br>MISOB | GTIOC5B/GTETRGA/<br>AGTIO0 | _                      |

| 49       | 37              | _               | CACREF                        | P500     | _        | _                                            | GTIU/AGTOA0                | AN016/IVREF0           |

| 50       | _               | _               | _                             | P008     | IRQ12-DS | _                                            | _                          | AN008                  |

| 51       | _               | _               | _                             | P006     | IRQ11-DS | _                                            | _                          | AN006                  |

| 52       | 38              | _               | _                             | P015     | IRQ13    | _                                            | _                          | AN013/DA1/IVCMP0       |

| 53       | 39              | 25              | _                             | P014     | _        | _                                            | _                          | AN012/DA0/IVREF1       |

| 54       | 40              | _               | _                             | P013     | _        | _                                            | _                          | AN011                  |

| 55       | 41              | 26              | _                             | P003     | _        | _                                            | _                          | AN007/PGAVSS000        |

| 56       | 42              | 27              | VREFH/AVCC0                   | _        | _        | _                                            | _                          | _                      |

| 57       | 43              | 28              | VREFL/AVSS0                   | _        | _        | _                                            | _                          | _                      |

| 58       | 44              | 29              | VREFL0                        | _        | _        | _                                            | _                          | _                      |

| 59       | 45              | 30              | VREFH0                        | _        | _        | _                                            | _                          | _                      |

| 60       | _               | _               | _                             | P005     | IRQ10-DS | _                                            | _                          | AN005                  |

| 61       | _               | _               | _                             | P004     | IRQ9-DS  | _                                            | _                          | AN004                  |

| 62       | 46              | 31              | _                             | P002     | IRQ8-DS  | _                                            | _                          | AN002/IVCMP2           |

| 63       | 47              | 32              | _                             | P001     | IRQ7-DS  | _                                            | _                          | AN001/IVCMP2           |

| 64       | 48              | 1               | _                             | P000     | IRQ6-DS  | _                                            | _                          | AN000/IVCMP2           |

いくつかの端子名には、\_A、\_B、\_C、および\_Dという接尾語が付加されています。これらの接尾語は、機能の割り当て時には無視 注. できます。 注 1. XCIN は、QFN32 および LQFP32 では使用できません。XCIN は抵抗を介して VSS に接続(プルダウン)する必要があります。

# 2. 電気的特性

サポートする周辺機能と端子は、製品型名によって異なります。

特に記載のない限り、本 MCU の電気的特性は以下の条件で定義されています。

- VCC = AVCC0 =  $2.7 \sim 3.6$

- $2.7 \le VREFH0/VREFH \le AVCC0$

- VSS = AVSS0 = VREFL0/VREFL = 0 V

- $\bullet \quad T_a = T_{opr}$

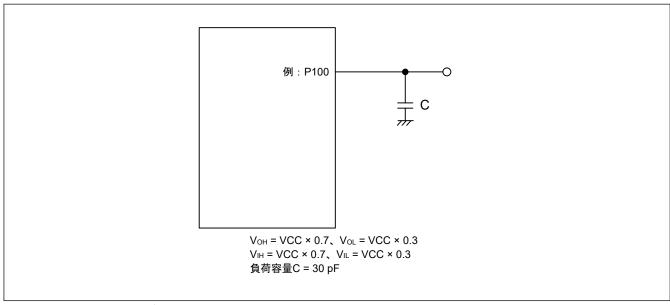

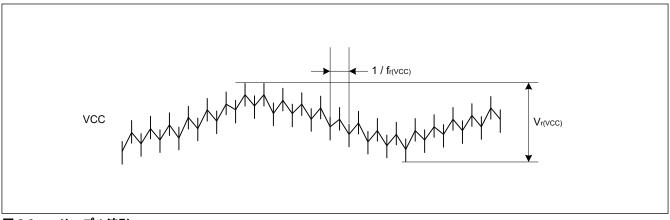

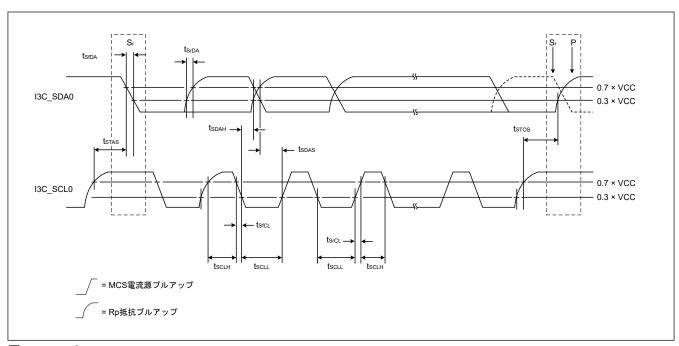

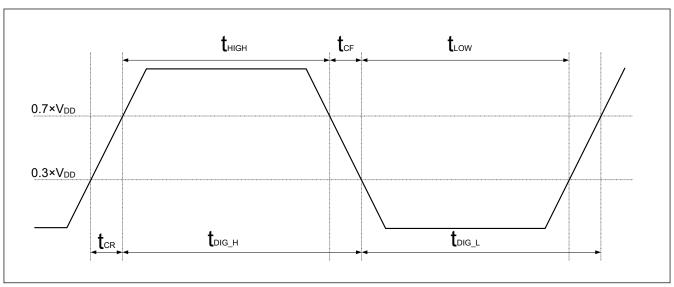

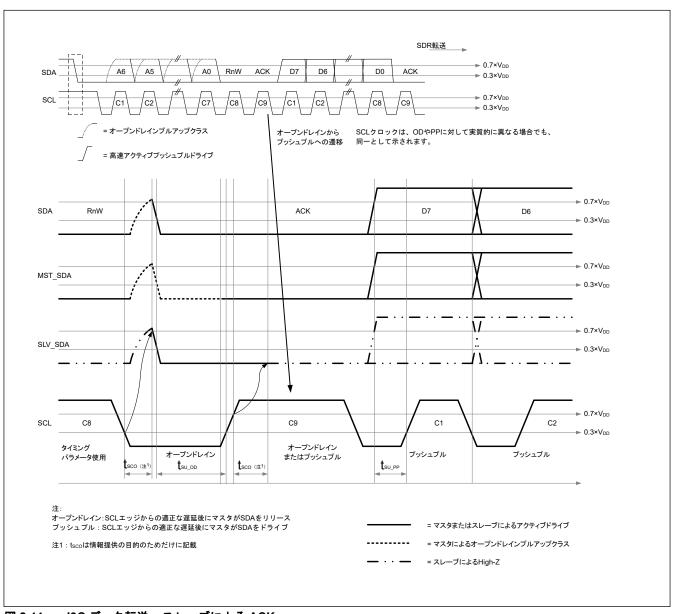

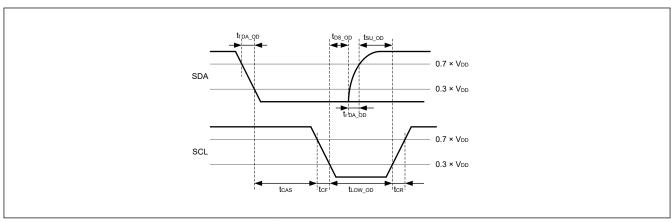

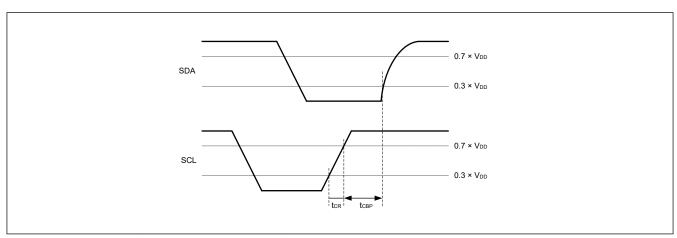

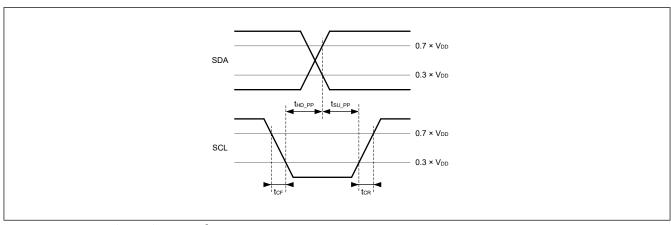

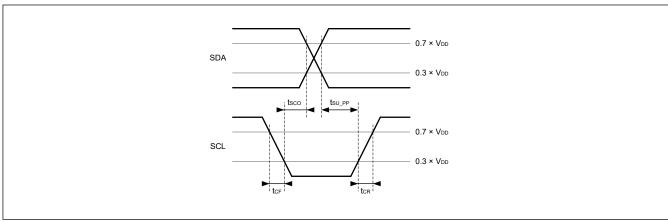

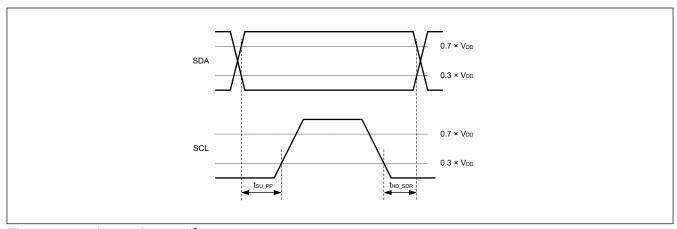

図 2.1 は、タイミング条件を示しています。

## 図 2.1 入出力タイミング計測条件

提供される各周辺モジュールのタイミング仕様の推奨計測条件は、最適な周辺動作に対するものです。ただし、 ユーザー条件に合うように、各端子の駆動能力を調整してください。

# 2.1 絶対最大定格

## 表 2.1 絶対最大定格

| 項目                                     | シンボル                  | 値                        | 単位 |

|----------------------------------------|-----------------------|--------------------------|----|

| 電源電圧                                   | VCC                   | -0.3~+4.0                | V  |

| 入力電圧(5 V トレラントポートを除く <sup>(注1)</sup> ) | V <sub>in</sub>       | -0.3~VCC + 0.3           | V  |

| 入力電圧(5 V トレラントポート <sup>(注1)</sup> )    | V <sub>in</sub>       | -0.3~+ VCC + 4.0(最大 5.8) | V  |

| リファレンス電源電圧                             | VREFH/VREFH0          | -0.3~VCC + 0.3           | V  |

| アナログ電源電圧                               | AVCC0 <sup>(注2)</sup> | -0.3~+4.0                | V  |

| アナログ入力電圧(P000~P003 を除く)                | V <sub>AN</sub>       | -0.3~AVCC0 + 0.3         | V  |

| PGA 疑似差動入力無効時のアナログ入力電圧(P000~<br>P003)  | VAN                   | -0.3~AVCC0 + 0.3         | V  |

| PGA 疑似差動入力有効時のアナログ入力電圧(P000~<br>P002)  | VAN                   | -1.3~AVCC0 + 0.3         | V  |

| PGA 疑似差動入力有効時のアナログ入力電圧 (P003)          | VAN                   | -0.8~AVCC0 + 0.3         | V  |

| 動作温度 <sup>(注3) (注4)</sup>              | T <sub>opr</sub>      | -40~+105                 | °C |

| 保存温度                                   | T <sub>stg</sub>      | -55~+125                 | °C |

- 注 1. ポート P100、P101、P205、P206、P400、P401、P407~P411 は 5 V トレラント対応ポートです。

- 注 2. AVCC0 を VCC に接続してください。

- 注 3. 「2.2.1. Tj/Ta の定義」を参照してください。

- 注 4. Ta =  $+85^{\circ}$  °C  $\sim$  +105 °C の場合のディレーティング動作については、弊社営業窓口までお問い合わせください。ディレーティングとは、信頼性向上のための系統的な負荷軽減策です。

## 【使用上の注意】絶対最大定格を超えて MCU を使用した場合、MCU の永久破壊となることがあります。

#### 表 2.2 推奨動作条件

| 項目       | シンボル                  | Min | Тур | Max | 単位 |

|----------|-----------------------|-----|-----|-----|----|

| 電源電圧     | vcc                   | 2.7 | _   | 3.6 | V  |

|          | vss                   | _   | 0   | _   | V  |

| アナログ電源電圧 | AVCC0 <sup>(注1)</sup> | _   | VCC | _   | ٧  |

|          | AVSS0                 | _   | 0   | _   | V  |

注 1. AVCC0 を VCC に接続してください。A/D コンバータ、D/A コンバータ、およびコンパレータを使用していない場合、AVCC0 端子、VREFH/VREFH0 端子、AVSS0 端子、および VREFL/VREFL0 端子を開放したままにしないでください。AVCC0 端子および VREFH/VREFH0 端子を VCC に、AVSS0 端子および VREFL/VREFL0 端子を VSS にそれぞれ接続してください。

# 2.2 DC 特性

# 2.2.1 Tj/Ta の定義

#### 表 2.3 DC 特性

| 項目          | シンボル | Тур | Max | 単位 | 測定条件                                                |

|-------------|------|-----|-----|----|-----------------------------------------------------|

| 許容ジャンクション温度 | Tj   | _   | 125 | င  | High-speed モード<br>Low-speed モード<br>Subosc-speed モード |

注.  $T_j = T_a + \theta ja \times$  総消費電力 (W) となるようにしてください。このとき、総消費電力 = (VCC -  $V_{OH}$ ) ×  $\Sigma I_{OH} + V_{OL} \times \Sigma I_{OL} + I_{CC}$ max × VCC です。

# 2.2.2 I/O V<sub>IH</sub>, V<sub>II</sub>

## 表 2.4 I/O V<sub>IH</sub>, V<sub>IL</sub> (1/2)

| 項目          | 項目                                    |                      |                 | Min       | Тур                   | Max       | 単位 |

|-------------|---------------------------------------|----------------------|-----------------|-----------|-----------------------|-----------|----|

| 入力電圧(シュ     | 周辺機能端子                                | EXTAL (外部クロック入力)、SPI | V <sub>IH</sub> | VCC × 0.8 | _                     | _         | V  |

| 入力端子を除      | , , , , , , , , , , , , , , , , , , , |                      | V <sub>IL</sub> | _         | ı                     | VCC × 0.2 |    |

| I3C (SMBus) |                                       | V <sub>IH</sub>      | 2.1             | _         | VCC + 3.6(最<br>大 5.8) |           |    |

|             |                                       |                      | V <sub>IL</sub> | _         | _                     | 0.8       |    |

# 表 2.4 I/O V<sub>IH</sub>, V<sub>IL</sub> (2/2)

| 項目               | 項目     |                                  |                 | Min        | Тур | Max                    | 単位 |

|------------------|--------|----------------------------------|-----------------|------------|-----|------------------------|----|

| シュミットト<br>リガ入力電圧 | 周辺機能端子 | I3C(SMBus を除く)                   | V <sub>IH</sub> | VCC × 0.7  |     | VCC + 3.6(最<br>大 5.8)  | V  |

|                  |        |                                  | V <sub>IL</sub> | _          | _   | VCC × 0.3              |    |

|                  |        |                                  | $\Delta V_{T}$  | VCC × 0.05 | _   | _                      |    |

|                  |        | 5 V トレラントポート <sup>(注1)(注5)</sup> | V <sub>IH</sub> | VCC × 0.8  | _   | VCC + 3.6(最<br>大 5.8)  |    |

|                  |        |                                  | V <sub>IL</sub> | _          | _   | VCC × 0.2              |    |

|                  |        |                                  | $\Delta V_{T}$  | VCC × 0.05 | _   | _                      |    |

|                  |        | その他の入力端子 <sup>(注2)</sup>         | V <sub>IH</sub> | VCC × 0.8  | _   | _                      |    |

|                  |        |                                  | V <sub>IL</sub> | _          | _   | VCC × 0.2              |    |

|                  |        |                                  | $\Delta V_{T}$  | VCC × 0.05 | _   | _                      |    |

|                  | ポート    | 5 V トレラントポート <sup>(注3)(注5)</sup> | V <sub>IH</sub> | VCC × 0.8  | _   | VCC + 3.6 (最<br>大 5.8) | V  |

|                  |        |                                  | V <sub>IL</sub> | _          | _   | VCC × 0.2              |    |

|                  |        | その他の入力端子 <sup>(注4)</sup>         | V <sub>IH</sub> | VCC × 0.8  | _   | _                      |    |

|                  |        |                                  | V <sub>IL</sub> | _          | _   | VCC × 0.2              | ]  |

- 注 1. P100、P101、P205、P206、P400、P401、P407~P411(合計 12 端子)に関連する RES および周辺機能端子

- 注 2. 表で説明した周辺機能端子を除くすべての入力端子

- 注 3. P100、P101、P205、P206、P400、P401、P407~P411(合計 11 端子)

- 注 4. 表で説明したポートを除くすべての入力端子

- 注 5. VCC が  $2.7 \lor$  未満の場合、 $5 \lor$  トレラントポートの入力電圧は、 $3.6 \lor$  未満としてください。このようにしないと、絶縁破壊が発生する可能性があります。 $5 \lor$  トレラントポートは耐圧違反を防止するように電気的に制御されるためです。

# 2.2.3 I/O I<sub>OH</sub>, I<sub>OL</sub>

# 表 2.5 I/O I<sub>OH</sub>, I<sub>OL</sub> (1/2)

| 項目               |                           |                                                                                          | シンボル            | Min | Тур  | Max  | 単位 |

|------------------|---------------------------|------------------------------------------------------------------------------------------|-----------------|-----|------|------|----|

| 許容出力電流(端子ごとの平均値) | I3C 端子                    | IIC 標準モード <sup>(注4)</sup>                                                                | I <sub>OL</sub> | _   | _    | 3.0  | mA |

|                  |                           | IIC ファストモード <sup>(注4)</sup>                                                              | I <sub>OL</sub> | _   | _    | 6.0  | mA |

|                  |                           | IIC 標準モード(注4)                                                                            | 20              | mA  |      |      |    |

|                  |                           |                                                                                          | I <sub>OL</sub> | _   | _    | 3.0  | mA |

|                  | ポート P004~P006、P008、P013~  | _                                                                                        | I <sub>OH</sub> | _   | _    | -2.0 | mA |

|                  | P015、P201                 |                                                                                          | I <sub>OL</sub> | _   | _    | 2.0  | mA |

|                  | ポート P205、P206、P407~P411(合 | 低駆動 <sup>(注1)</sup>                                                                      | I <sub>OH</sub> | _   | _    | -2.0 | mA |

|                  | 計 7 端子)                   | I <sub>OL</sub>                                                                          | _               | _   | 2.0  | mA   |    |

|                  |                           | 中駆動(注2)                                                                                  | I <sub>OH</sub> | _   | _    | -4.0 | mA |

|                  |                           | 05、P206、P407~P411(合<br>(医動 <sup>(注1)</sup><br>中駆動 <sup>(注2)</sup><br>高駆動 <sup>(注3)</sup> | I <sub>OL</sub> | _   | _    | 4.0  | mA |

|                  |                           |                                                                                          | I <sub>OH</sub> | _   | _    | -20  | mA |

|                  |                           |                                                                                          | I <sub>OL</sub> | _   | _    | 20   | mA |

|                  | その他の出力端子(注5)              | 高駆動 <sup>(注3)</sup>                                                                      | _               | _   | -2.0 | mA   |    |

|                  |                           |                                                                                          | I <sub>OL</sub> | _   | _    | 2.0  | mA |

|                  |                           | 中駆動(注2)                                                                                  | I <sub>OH</sub> | _   | _    | -4.0 | mA |

|                  |                           |                                                                                          | I <sub>OL</sub> | _   | _    | 4.0  | mA |

|                  |                           | 高駆動 <sup>(注3)</sup>                                                                      | I <sub>OH</sub> | _   | _    | -16  | mA |

|                  |                           |                                                                                          | I <sub>OL</sub> | _   | _    | 16   | mA |

## 表 2.5 I/O I<sub>OH</sub>, I<sub>OL</sub> (2/2)

| 項目                |                           |                                    | シンボル                   | Min | Тур | Max  | 単位 |

|-------------------|---------------------------|------------------------------------|------------------------|-----|-----|------|----|

| 許容出力電流(端子ごとの最大値)  | I3C 端子                    | IIC 標準モード <sup>(注4)</sup>          | I <sub>OL</sub>        | _   | _   | 3.0  | mA |

|                   |                           | IIC ファストモード <sup>(注4)</sup>        | I <sub>OL</sub>        | _   | _   | 6.0  | mA |

|                   |                           | IIC ファストモードプラ<br>ス <sup>(注4)</sup> | I <sub>OL</sub>        | _   | _   | 20   | mA |

|                   |                           | IIC High-speed モード                 | I <sub>OL</sub>        | _   | _   | 3.0  | mA |

|                   | ポート P004~P006、P008、P013~  | _                                  | I <sub>OH</sub>        | _   | _   | -4.0 | mA |

|                   | P015、P201                 |                                    | I <sub>OL</sub>        | _   | _   | 4.0  | mA |

|                   | ポート P205、P206、P407~P411(合 | 低駆動 <sup>(注1)</sup>                | I <sub>OH</sub>        | _   | _   | -4.0 | mA |

|                   | 計7端子)                     |                                    | I <sub>OL</sub>        | _   | _   | 4.0  | mA |

|                   | 中駆動 <sup>(注2)</sup>       | 中駆動(注2)                            | I <sub>OH</sub>        | _   | _   | -8.0 | mA |

|                   |                           | I <sub>OL</sub>                    | _                      | _   | 8.0 | mA   |    |

|                   |                           |                                    | I <sub>OH</sub>        | _   | _   | -40  | mA |

|                   |                           |                                    | I <sub>OL</sub>        | _   | _   | 40   | mA |

|                   | その他の出力端子(注5)              | 低駆動 <sup>(注1)</sup>                | I <sub>OH</sub>        | _   | _   | -4.0 | mA |

|                   |                           |                                    | I <sub>OL</sub>        | _   | _   | 4.0  | mA |

|                   |                           | 中駆動 <sup>(注2)</sup>                | I <sub>OH</sub>        | _   | _   | -8.0 | mA |

|                   |                           |                                    | I <sub>OL</sub>        | _   | _   | 8.0  | mA |

|                   |                           | 高駆動 <sup>(注3)</sup>                | I <sub>OH</sub>        | _   | _   | -32  | mA |

|                   |                           |                                    | I <sub>OL</sub>        | _   | _   | 32   | mA |

| 許容出力電流(全端子合計の最大値) | 全出力端子の最大値                 |                                    | ΣI <sub>OH</sub> (max) | _   | _   | -80  | mA |

|                   |                           |                                    | ΣI <sub>OL (max)</sub> | _   | _   | 80   | mA |

- 注 1. PmnPFS レジスタのポート駆動能力ビットで低駆動が選択されている場合の値です。選択された駆動能力は、ディープソフトウェアスタンバイモードで保持されます。

- 注 2. PmnPFS レジスタのポート駆動能カビットで中駆動が選択されている場合の値です。選択された駆動能力は、ディープソフトウェアスタンバイモードで保持されます。

- 注 3. PmnPFS レジスタのポート駆動能力ビットで高駆動が選択されている場合の値です。選択された駆動能力は、ディープソフトウェアスタンバイモードで保持されます。

- 注 4. SCL0\_D、SDA0\_D(合計 2 端子)。これは IIC 機能選択時の値です。

- 注 5. 入力ポートである P000~P003、P200 を除きます。

【使用上の注意】MCU の信頼性を確保するため、出力電流値はこの表の値を超えないようにしてください。平均出力電流は、 100 μs の間に計測した電流の平均値を意味します。

#### I/O V<sub>OH</sub>、V<sub>OL</sub>、その他の特性 2.2.4

#### I/O V<sub>OH</sub>、V<sub>OL</sub>、その他の特性 表 2.6

| 項目                              |                             |          | シンボル             | Min        | Тур | Max  | 単位 | 測定条件                                                       |

|---------------------------------|-----------------------------|----------|------------------|------------|-----|------|----|------------------------------------------------------------|

| 出力電圧                            | I3C <sup>(注1)</sup>         |          | V <sub>OL</sub>  | _          | _   | 0.4  | V  | I <sub>OL</sub> = 3.0 mA                                   |

|                                 |                             |          | V <sub>OL</sub>  | _          | _   | 0.6  |    | I <sub>OL</sub> = 6.0 mA                                   |

|                                 | I3C <sup>(注2)</sup>         |          | V <sub>OH</sub>  | VCC - 0.27 | _   | _    |    | I <sub>OH</sub> = 3.0 mA (PRTS.PRTMD = 0)                  |

|                                 |                             |          | V <sub>OL</sub>  | _          | _   | 0.4  |    | I <sub>OL</sub> = 15.0 mA (PRTS.PRTMD = 1, BFCTL.FMPE = 1) |

|                                 |                             |          | V <sub>OL</sub>  | _          | 0.4 | _    |    | I <sub>OL</sub> = 20.0 mA (PRTS.PRTMD = 1, BFCTL.FMPE = 1) |

|                                 |                             |          | V <sub>OL</sub>  | _          | _   | 0.4  |    | I <sub>OL</sub> = 3.0 mA (PRTS.PRTMD = 1, BFCTL.HSME = 1)  |

|                                 |                             |          | V <sub>OL</sub>  | _          | _   | 0.27 |    | I <sub>OL</sub> = 3.0 mA (PRTS.PRTMD = 0)                  |

|                                 | ポート P205、P2<br>P411(合計 7 端日 |          | V <sub>OH</sub>  | VCC - 1.0  | _   | _    |    | I <sub>OH</sub> = -20 mA<br>VCC = 3.3 V                    |

|                                 | その他の出力端子                    |          | V <sub>OL</sub>  | _          | _   | 1.0  |    | I <sub>OL</sub> = 20 mA<br>VCC = 3.3 V                     |

|                                 |                             |          | V <sub>OH</sub>  | VCC - 0.5  | _   | -    |    | I <sub>OH</sub> = -1.0 mA                                  |

|                                 |                             |          | V <sub>OL</sub>  | _          | _   | 0.5  |    | I <sub>OL</sub> = 1.0 mA                                   |

| 入カリーク電流                         | RES<br>ポート P000~P002、P200   |          | I <sub>in</sub>  | _          | _   | 5.0  | μА | $V_{in} = 0 V$<br>$V_{in} = 5.5 V$                         |

|                                 |                             |          |                  | _          | _   | 1.0  |    | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC             |

|                                 | ポート P003                    | 初期化前(注5) |                  | _          | _   | 45.0 |    | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC             |

|                                 |                             | 初期化後(注6) |                  | _          | _   | 1.0  |    | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC             |

| スリーステート<br>リーク電流(オフ<br>状態)      | 5 V トレラント対<br>ト P100、P101 を |          | I <sub>TSI</sub> | _          | _   | 5.0  | μА | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = 5.5 V           |

| (人感)                            | 5 V トレラント対<br>(P100, P101)  | 応ポート     |                  | _          | _   | 10.0 |    | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = 5.5 V           |

|                                 | その他のポート(<br>P003、P200) を    |          |                  | _          | _   | 1.0  |    | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC             |

| 入力プルアップ<br>MOS 電流               | ポート P0~P5、<br>P000~P003 を除  |          | Ip               | -300       |     | -10  | μА | VCC = 2.7~3.6 V<br>V <sub>in</sub> = 0 V                   |

| SCL 電流ソース<br>として機能する<br>プルアップ電流 | I3C <sup>(注4)</sup>         |          | I <sub>CS</sub>  | 3          | -   | 12   | mA | VCC = 3.0~3.6 V<br>Vin = 0.3 × VCC~0.7 × VCC               |

| 入力容量                            | ポート P003、P0<br>P814、P815    | 14、P015、 | C <sub>in</sub>  | _          | _   | 16   | pF | Vbias = 0 V<br>Vamp = 20 mV                                |

|                                 | その他の入力端子                    |          |                  | _          | -   | 8    |    | f = 1 MHz<br>Ta = 25°C                                     |

- 注 1. SCL0\_A、SCL0\_B、SCL0\_C、SDA0\_A、SDA0\_B、SDA0\_C(合計 6 端子) 注 2. I3C\_SCL/SCL0\_D、I3C\_SDA/SDA0\_D(合計 2 端子)

- PmnPFS レジスタのポート駆動能力ビットで高駆動が選択されている場合の値です。選択された駆動能力は、ディープソフトウェア スタンバイモードで保持されます。 中駆動または低駆動が選択されている場合は、その他の出力端子の値を参照してください。

- 注 4. I3C\_SCL/SCL0\_D (1 端子)。これは IIC High-speed モード選択時の値です。

- 注 5. P0nPFS.ASEL (n = 3) = 1

- 注 6. P0nPFS.ASEL (n = 3) = 0

#### 動作電流とスタンバイ電流 2.2.5

#### 表 2.7 動作電流とスタンバイ電流

| パラメータ                |                    |                                              |                                        |                                         | シンボル                 | Min | Тур                          | Max                         | 単位          | 測定条件                                                                                 |

|----------------------|--------------------|----------------------------------------------|----------------------------------------|-----------------------------------------|----------------------|-----|------------------------------|-----------------------------|-------------|--------------------------------------------------------------------------------------|

| 消費電流 <sup>(注1)</sup> | High-speed ₹       | 最大動作 <sup>(注2)(</sup>                        | 注13)                                   |                                         | I <sub>CC</sub> (注3) | _   | _                            | 61                          | mA          | ICLK = 100                                                                           |

|                      | - F                | CoreMark <sup>®(注</sup>                      | 5) (注6)(注12)                           |                                         | 1                    | _   | 8.2                          | _                           |             | MHz<br>PCLKA =                                                                       |

|                      |                    | 通常モード                                        | すべての周辺か<br>コードはフラッ<br><sup>(注12)</sup> | 7ロックが有効、(1)<br>ッシュから実行 <sup>(注4)</sup>  |                      | _   | 13.5                         | _                           |             | 100 MHz<br>PCLKB =<br>50 MHz<br>PCLKC =<br>50 MHz<br>PCLKD =<br>100 MHz<br>FCLK = 50 |

|                      |                    |                                              |                                        | 7ロックが無効、(1)<br>ッシュから実行 <sup>(注5)</sup>  |                      | _   | 9.1                          | _                           |             |                                                                                      |

|                      |                    | スリープモー                                       | ド(注5)                                  |                                         |                      | _   | 5.3 <sup>(注6)</sup><br>(注12) | 42 <sup>(注7)</sup><br>(注13) |             | MHz                                                                                  |

|                      |                    | BGO 動作時                                      | データフラッシ                                | ノュ P/E                                  |                      | _   | 6                            | _                           |             |                                                                                      |

|                      |                    | の増加分                                         | コードフラッシュ P/E                           |                                         |                      | _   | 8                            | _                           | -           |                                                                                      |

|                      | Low-speed モー       | - ド(注5) (注10)                                | !                                      |                                         |                      | _   | 1.8                          | _                           |             | ICLK = 1<br>MHz                                                                      |

|                      | Subosc-speed       | モード(注5)(注1                                   | 1)                                     |                                         |                      | _   | 1.6                          | _                           |             | ICLK = 32.768 kHz                                                                    |

|                      |                    | <b>、タンバイモー</b>                               | SNZCR.RXDR                             | EQEN = 1                                | 1                    | _   | _                            | 35                          |             | _                                                                                    |

|                      | ۴                  |                                              | SNZCR.RXDREQEN = 0                     |                                         |                      | _   | 1.4                          | _                           |             | _                                                                                    |

|                      | ディープソフ             | DPSBYCR.DI                                   | EEPCUT[1:0] = (                        | 00b <sup>(注14)</sup>                    | 1                    | _   | 16                           | 96                          | μА          | _                                                                                    |

|                      | トウェアスタンバイモード       | DPSBYCR.DI                                   | EEPCUT[1:0] = (                        | 01b <sup>(注14)</sup>                    |                      | _   | 11                           | 25.6                        |             | _                                                                                    |

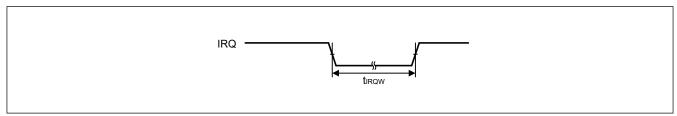

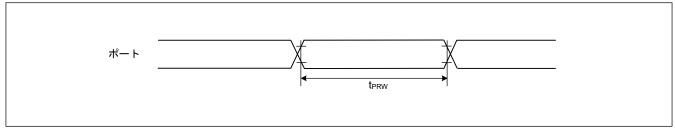

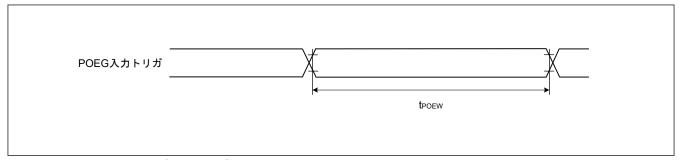

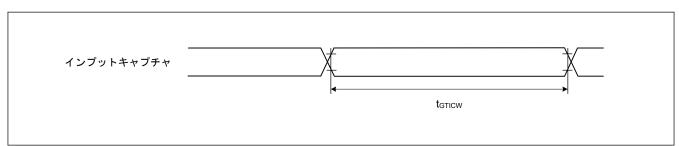

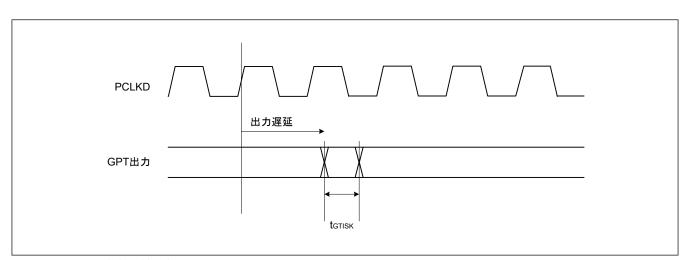

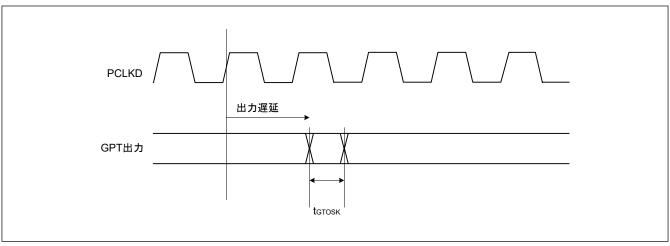

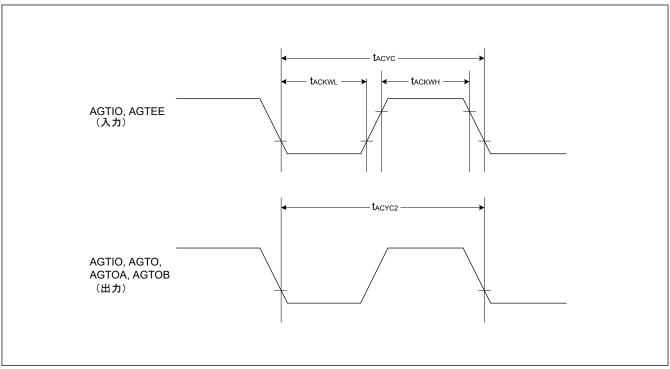

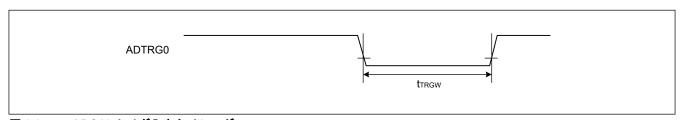

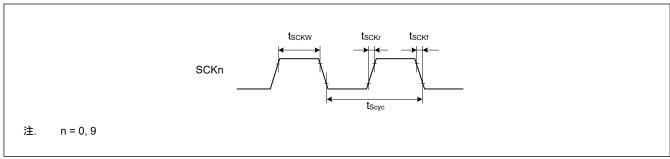

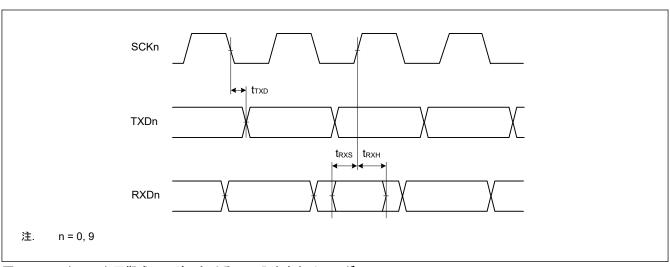

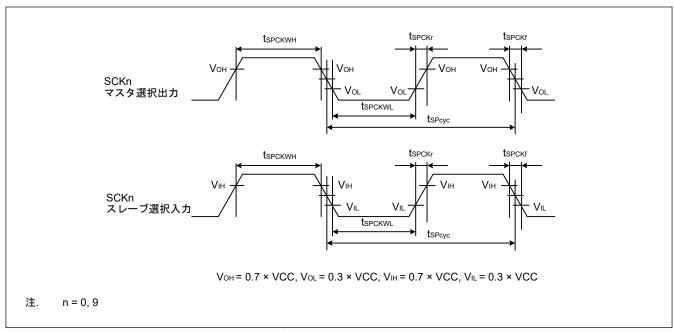

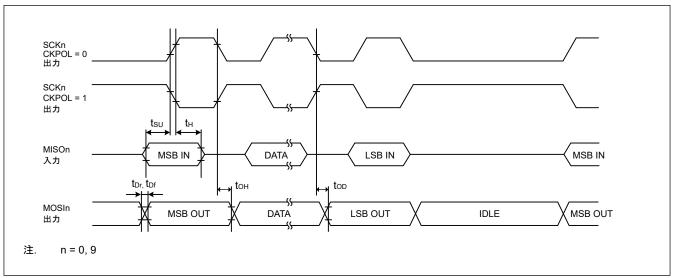

|                      |                    | DPSBYCR.DI                                   | EEPCUT[1:0] = 1                        | 11b <sup>(注14)</sup>                    | _                    | _   | 4.2                          | 20.4                        |             | _                                                                                    |