RA2E3 グループ

ルネサスマイクロコントローラ

R01DS0411JJ0130

Rev.1.30

Nov 28, 2025

超低消費電力 48 MHz Arm® Cortex®-M23 コア、最大 64 KB のコードフラッシュメモリ、16 KB の SRAM、12 ビット A/D コンバータ、セーフティ機能

## 特長

### ■ Arm Cortex-M23 コア

- Armv8-M アーキテクチャ

- 最高動作周波数 : 48 MHz

- Arm メモリプロテクションユニット (Arm MPU) (8 領域)

- デバッグ&トレース : DWT、FPB、CoreSight™ MTB-M23

- CoreSight デバッグポート : SW-DP

### ■ メモリ

- 最大 64 KB のコードフラッシュメモリ

- 2 KB のデータフラッシュメモリ (100,000 回のプログラム/イレース (P/E) サイクル)

- 16 KB の SRAM

- メモリプロテクションユニット

- 128 ビットのユニーク ID

### ■ 接続性

- シリアルコミュニケーションインターフェース (SCI) × 4

- 調歩同期式インタフェース

- 8 ビットクロック同期式インタフェース

- 簡易 IIC

- 簡易 SPI

- スマートカードインターフェース

- シリアルペリフェラルインターフェース (SPI) × 1

- I<sup>2</sup>C バスインターフェース (IIC) × 1

### ■ アナログ

- 12 ビット A/D コンバータ (ADC12)

- 温度センサ (TSN)

### ■ タイマー

- 32 ビット汎用 PWM タイマ (GPT32) × 1

- 16 ビット汎用 PWM タイマ (GPT16) × 6

- 低消費電力非同期汎用タイマ (AGT) × 2

- ウオッチドッグタイマ (WDT)

### ■ セーフティ

- SRAM のparityエラー検査

- フラッシュ領域の保護

- ADC 自己診断機能

- クロック周波数精度測定回路 (CAC)

- 巡回冗長検査 (CRC) 演算器

- データ演算回路 (DOC)

- GPT 用のポートアウトプットイネーブル (POEG)

- 独立ウォッチドッグタイマ (IWDT)

- GPIO リードバックレベル検出

- レジスタライトプロテクション

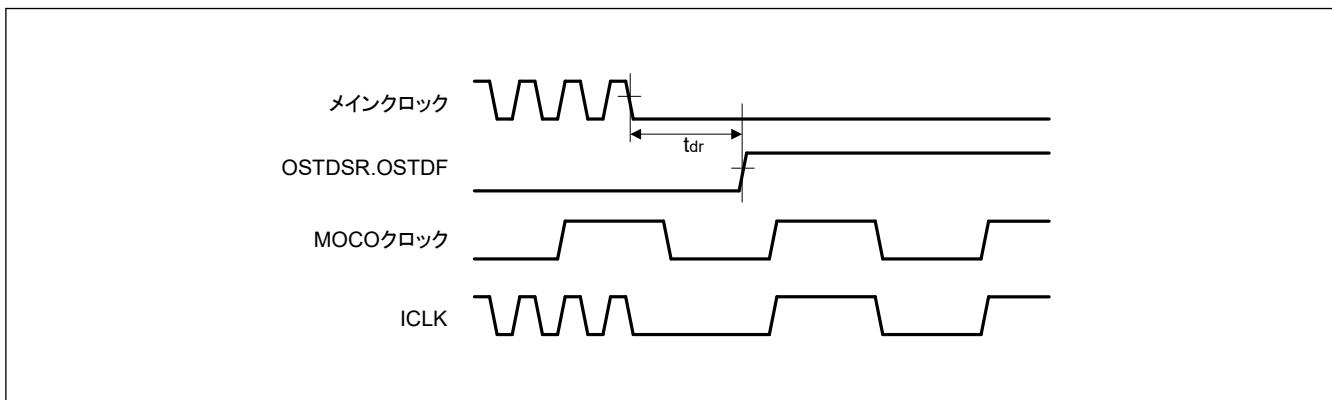

- メインクロック発振器停止検出

- 不正メモリアクセス検出

### ■ システムおよび電源管理

- 低消費電力モード

- リアルタイムクロック (RTC)

- イベントリンクコントローラ (ELC)

- データトランസファコントローラ (DTC)

- キー割り込み機能 (KINT)

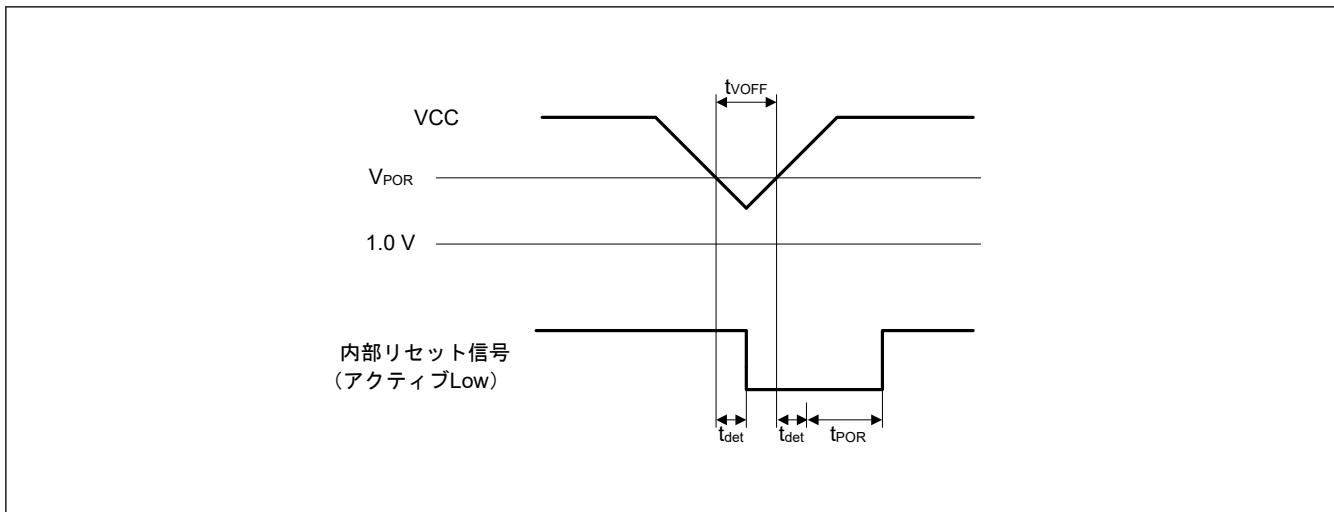

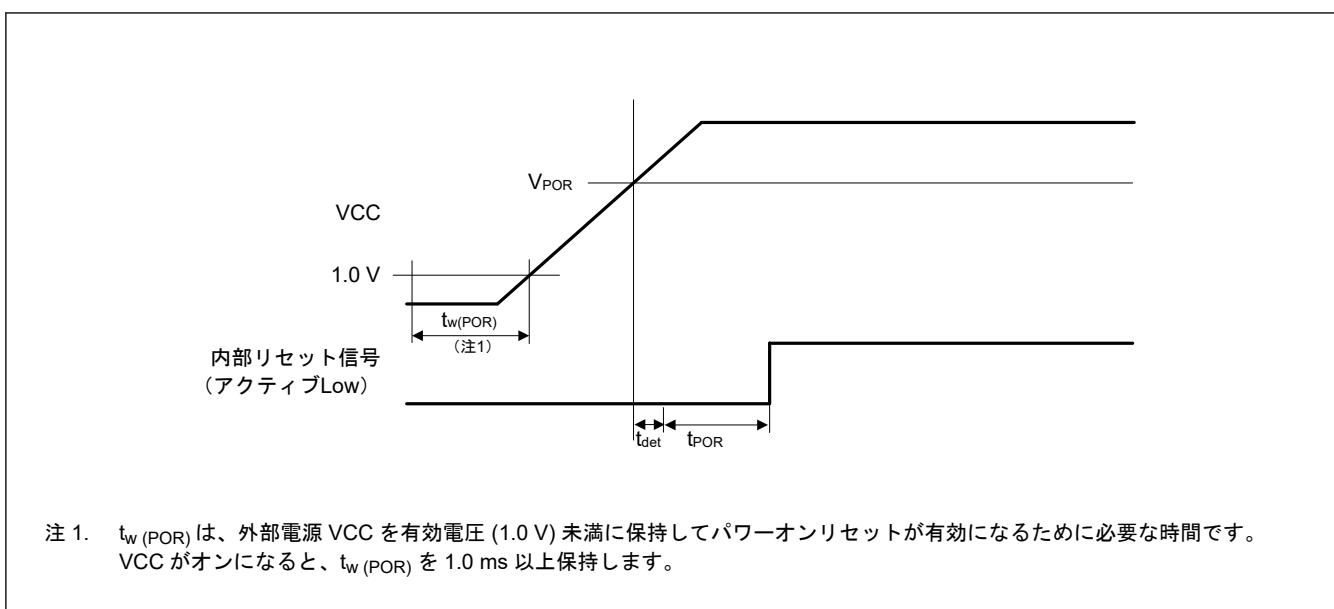

- パワーオンリセット

- 低電圧検出機能 (LVD) の設定可能

### ■ マルチクロックソース

- メインクロック発振器 (MOSC) (1~20 MHz)

- サブクロック発振器 (SOSC) (32.768 kHz)

- 高速オンチップオシレータ (HOCO) (24/32/48/64 MHz)

- 中速オンチップオシレータ (MOCO) (8 MHz)

- 低速オンチップオシレータ (LOCO) (32.768 kHz)

- HOCO/MOCO/LOCO に対するクロックトリム機能

- IWDT 専用オンチップオシレータ (15 kHz)

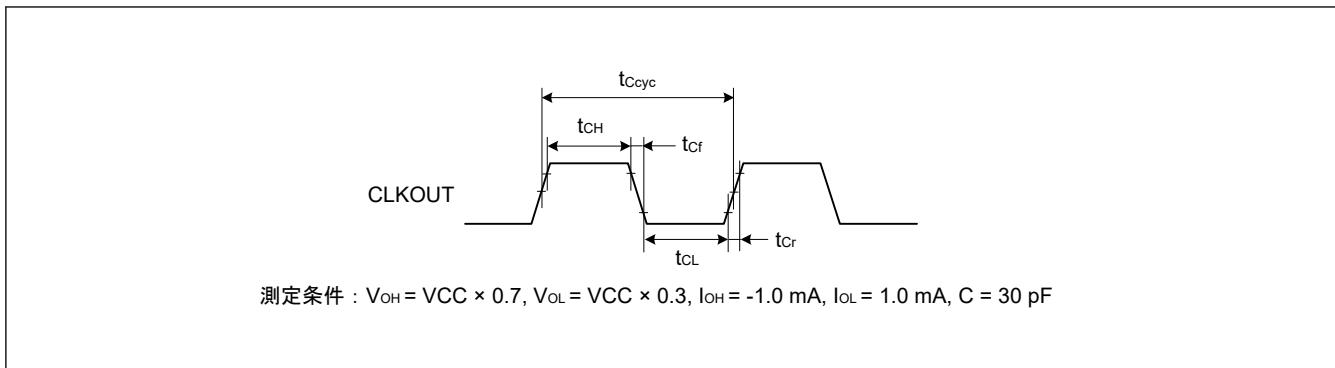

- クロックアウトのサポート

### ■ 最大 40 本の汎用入出力ポート内蔵

- 5 V トレンジス、オープンドレイン、入力プルアップ、切り替え可能駆動能力

### ■ 動作電圧

- VCC: 1.6~5.5 V

### ■ 動作温度およびパッケージ

- $T_a = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$

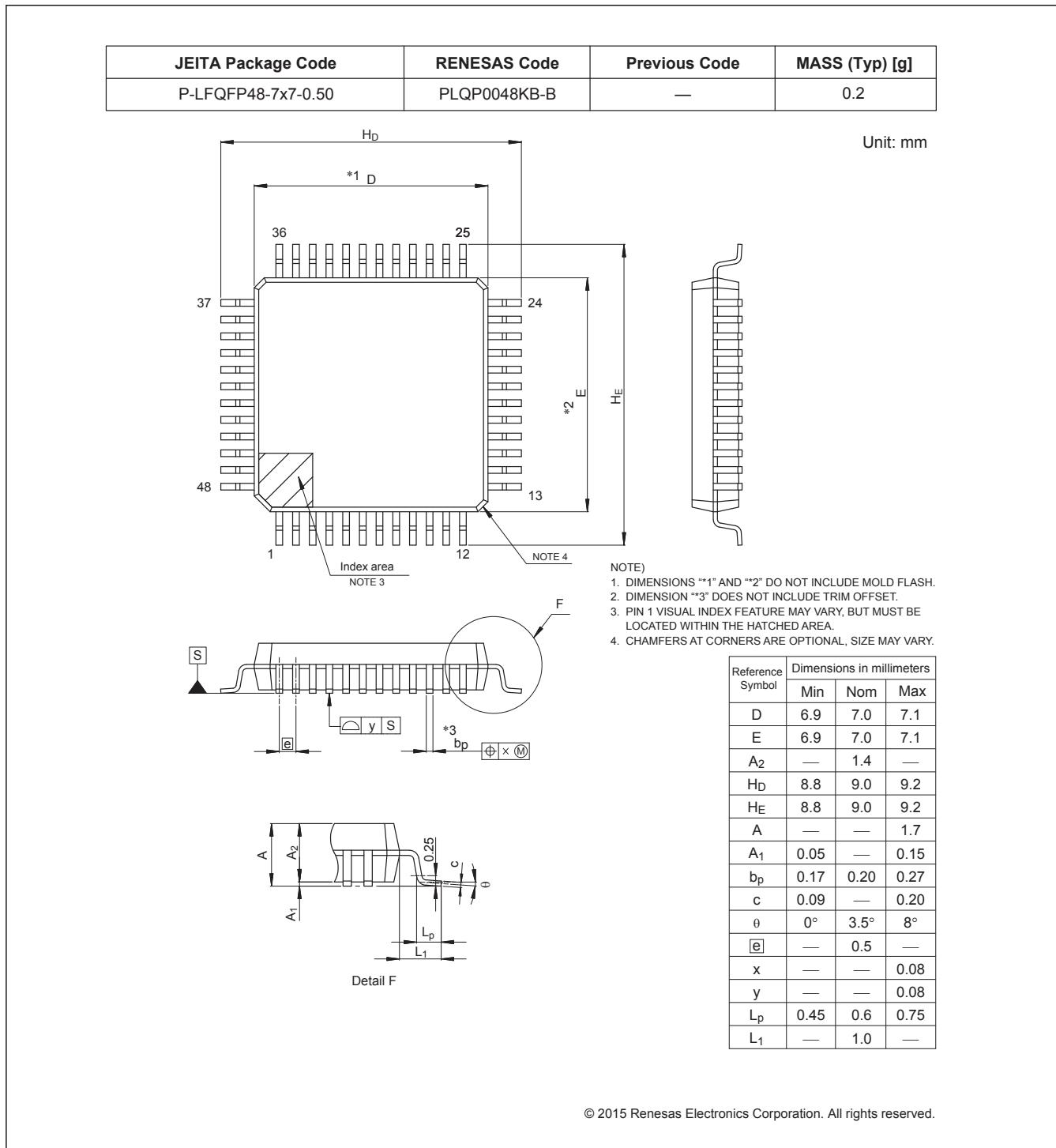

- 48 ピン LQFP (7 mm × 7 mm、0.5 mm ピッチ)

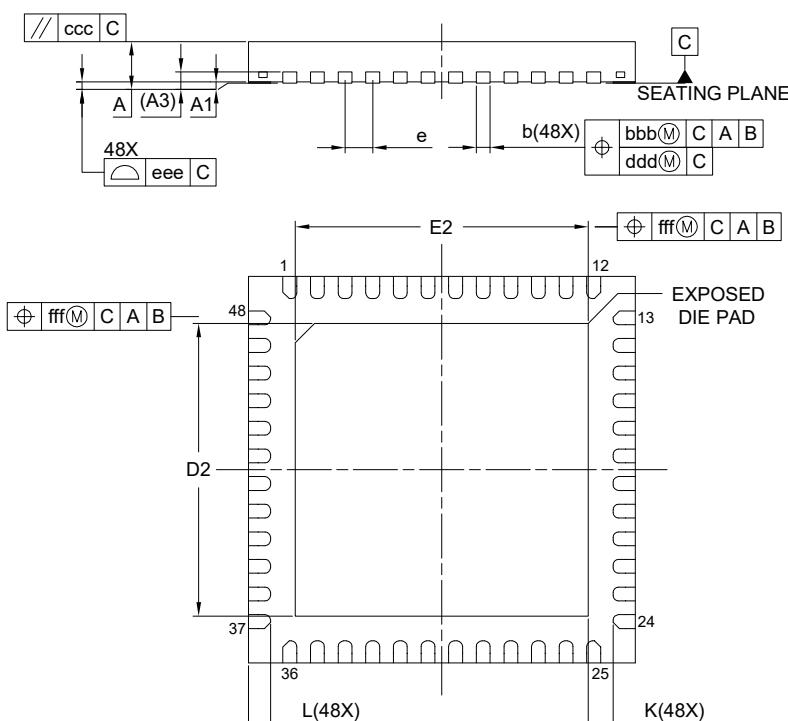

- 48 ピン HWQFN (7 mm × 7 mm、0.5 mm ピッチ)

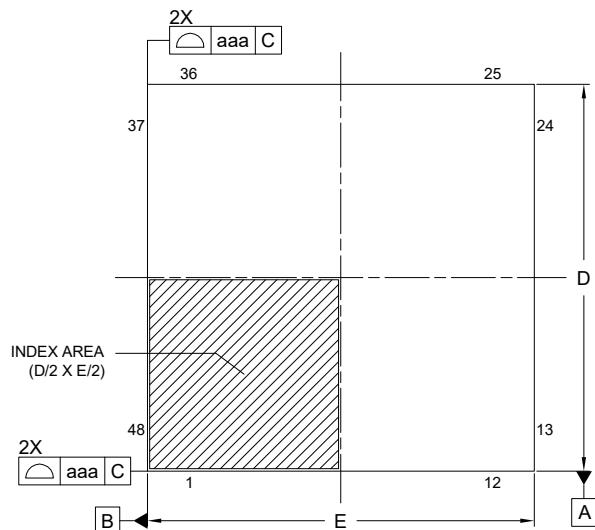

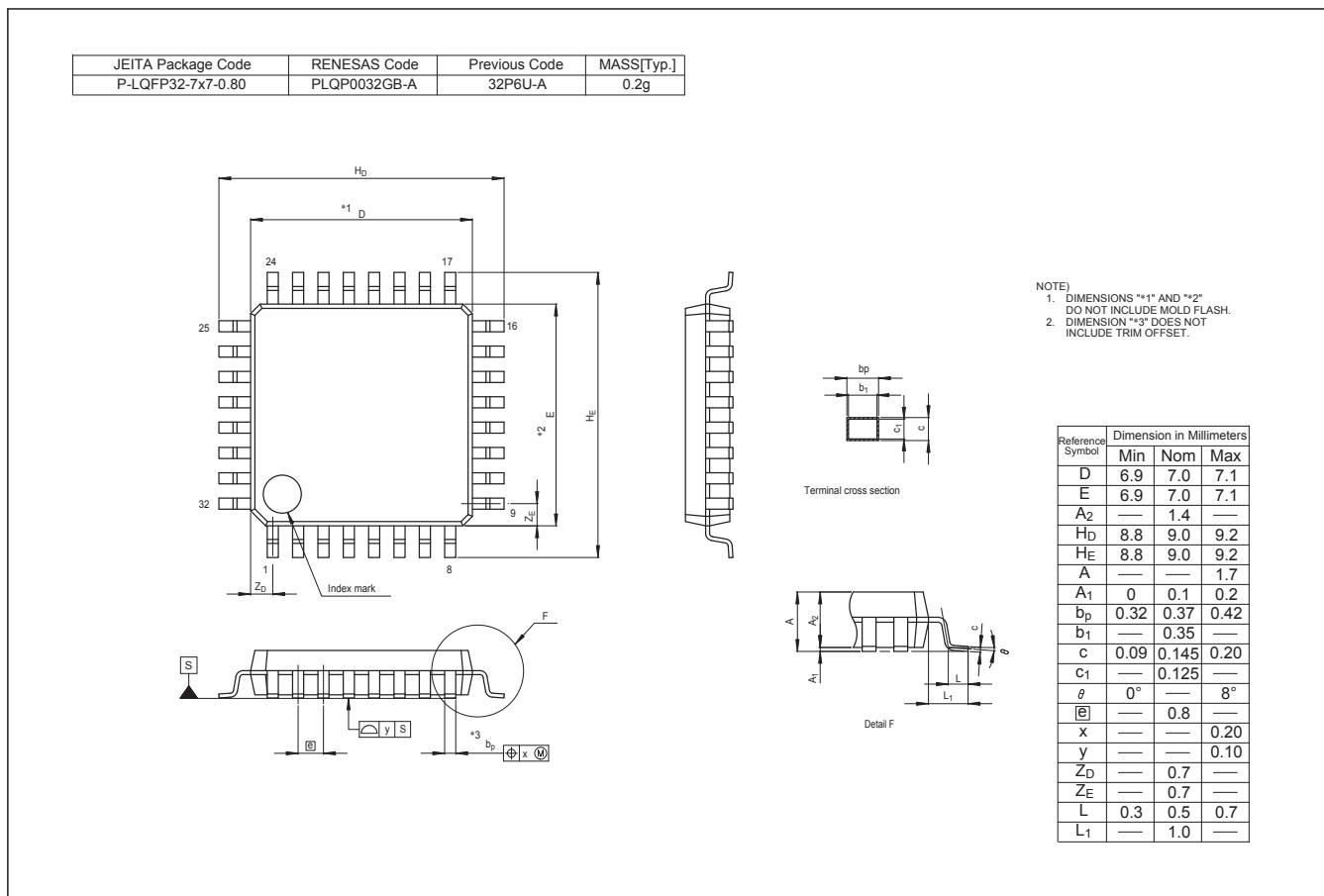

- 32 ピン LQFP (7 mm × 7 mm、0.8 mm ピッチ)

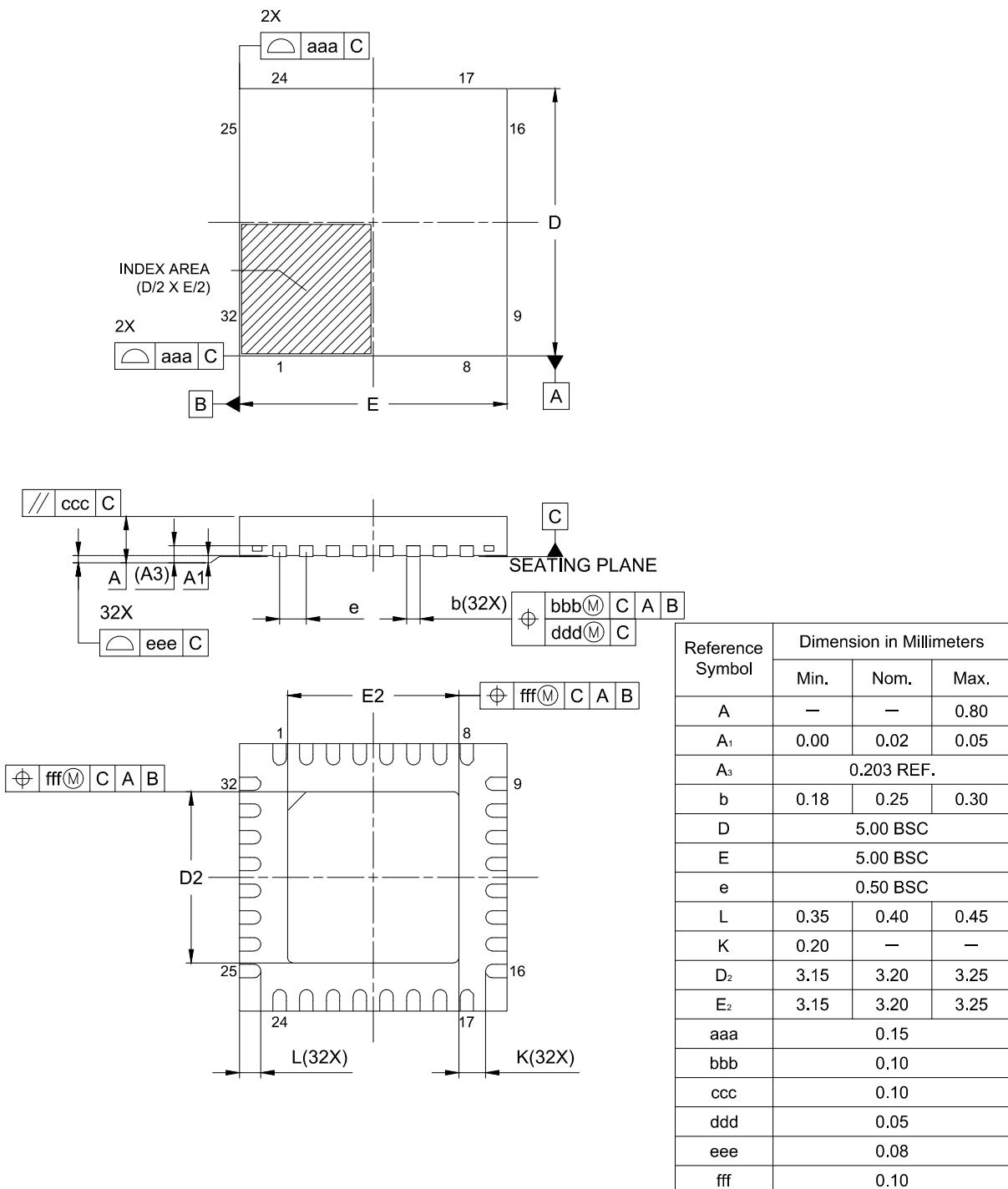

- 32 ピン HWQFN (5 mm × 5 mm、0.5 mm ピッチ)

- $T_a = -40^{\circ}\text{C} \sim +105^{\circ}\text{C}$

- 48 ピン LQFP (7 mm × 7 mm、0.5 mm ピッチ)

- 48 ピン HWQFN (7 mm × 7 mm、0.5 mm ピッチ)

- 32 ピン LQFP (7 mm × 7 mm、0.8 mm ピッチ)

- 32 ピン HWQFN (5 mm × 5 mm、0.5 mm ピッチ)

## 1. 概要

MCU は、さまざまなシリーズのソフトウェアおよび端子と互換性のある Arm®ベースの 32 ビットコアを統合しています。同じ一連のルネサス周辺デバイスを共有することで、設計の拡張性が高まります。

本 MCU は高効率な Arm Cortex®-M23 32 ビットコアを内蔵しており、特にコスト重視かつ低消費電力のアプリケーションへの適合性が高いです。本 MCU には以下の特長があります。

- 最大 64 KB のコードフラッシュメモリ

- 16 KB の SRAM

- 12 ビット A/D コンバータ (ADC12)

### 1.1 機能の概要

表 1.1 Arm コア

| 機能                | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm Cortex-M23 コア | <ul style="list-style-type: none"> <li>最高動作周波数 : 48 MHz</li> <li>Arm Cortex-M23 コア : <ul style="list-style-type: none"> <li>リビジョン : r1p0-00rel0</li> <li>Armv8-M アーキテクチャプロファイル</li> <li>シングルサイクル整数乗算器</li> <li>19 サイクル整数除算器</li> </ul> </li> <li>Arm メモリプロテクションユニット (Arm MPU) : <ul style="list-style-type: none"> <li>Armv8 保護メモリシステムアーキテクチャ</li> <li>8 つの保護領域</li> </ul> </li> <li>SysTick タイマ : <ul style="list-style-type: none"> <li>SYSTICCLK (LOCO) または ICLK による駆動</li> </ul> </li> </ul> |

表 1.2 メモリ

| 機能          | 機能の説明                            |

|-------------|----------------------------------|

| コードフラッシュメモリ | 最大 64 KB のコードフラッシュメモリ            |

| データフラッシュメモリ | 2 KB のデータフラッシュメモリ                |

| オプション設定メモリ  | オプション設定メモリは、MCU のリセット後の状態を決定します。 |

| SRAM        | パリティビットを備えた高速 SRAM を内蔵しています。     |

表 1.3 システム (1/2)

| 機能          | 機能の説明                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 動作モード       | 2 種類の動作モード : <ul style="list-style-type: none"> <li>シングルチップモード</li> <li>SCI ブートモード</li> </ul>                                                                                                                                         |

| リセット        | 本 MCU は、12 種類のリセット (RES 端子リセット、パワーオンリセット、独立ウォッチドッグタイマリセット、ウォッチドッグタイマリセット、電圧監視 0/1/2 リセット、SRAM パリティエラーリセット、バスマスター/スレーブ MPU エラーリセット、CPU スタックポイントエラーリセット、ソフトウェアリセット) をサポートしています。                                                         |

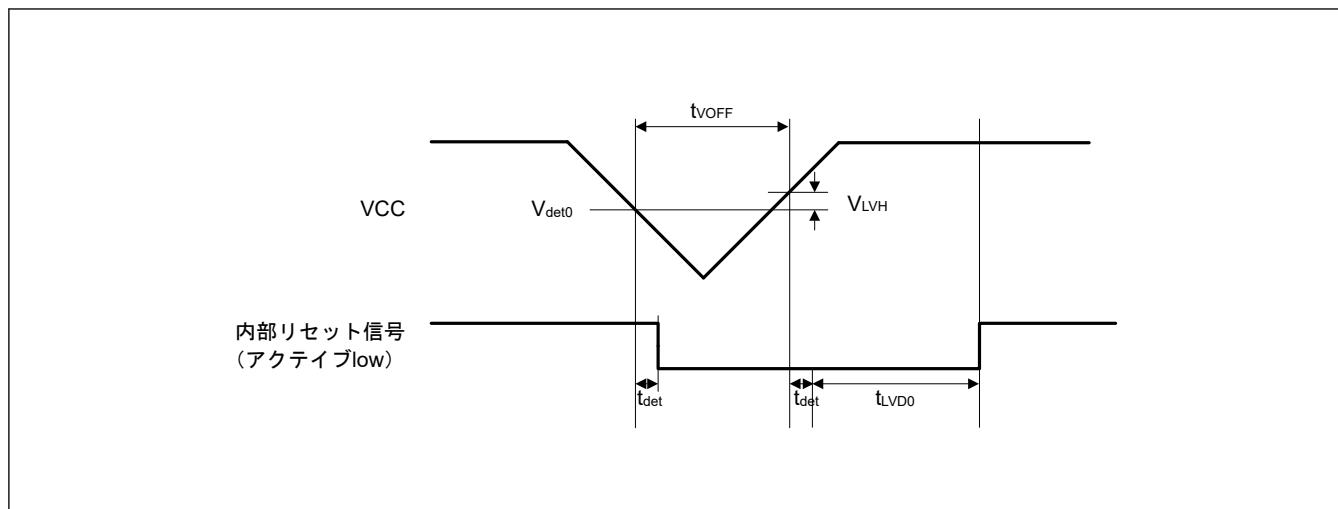

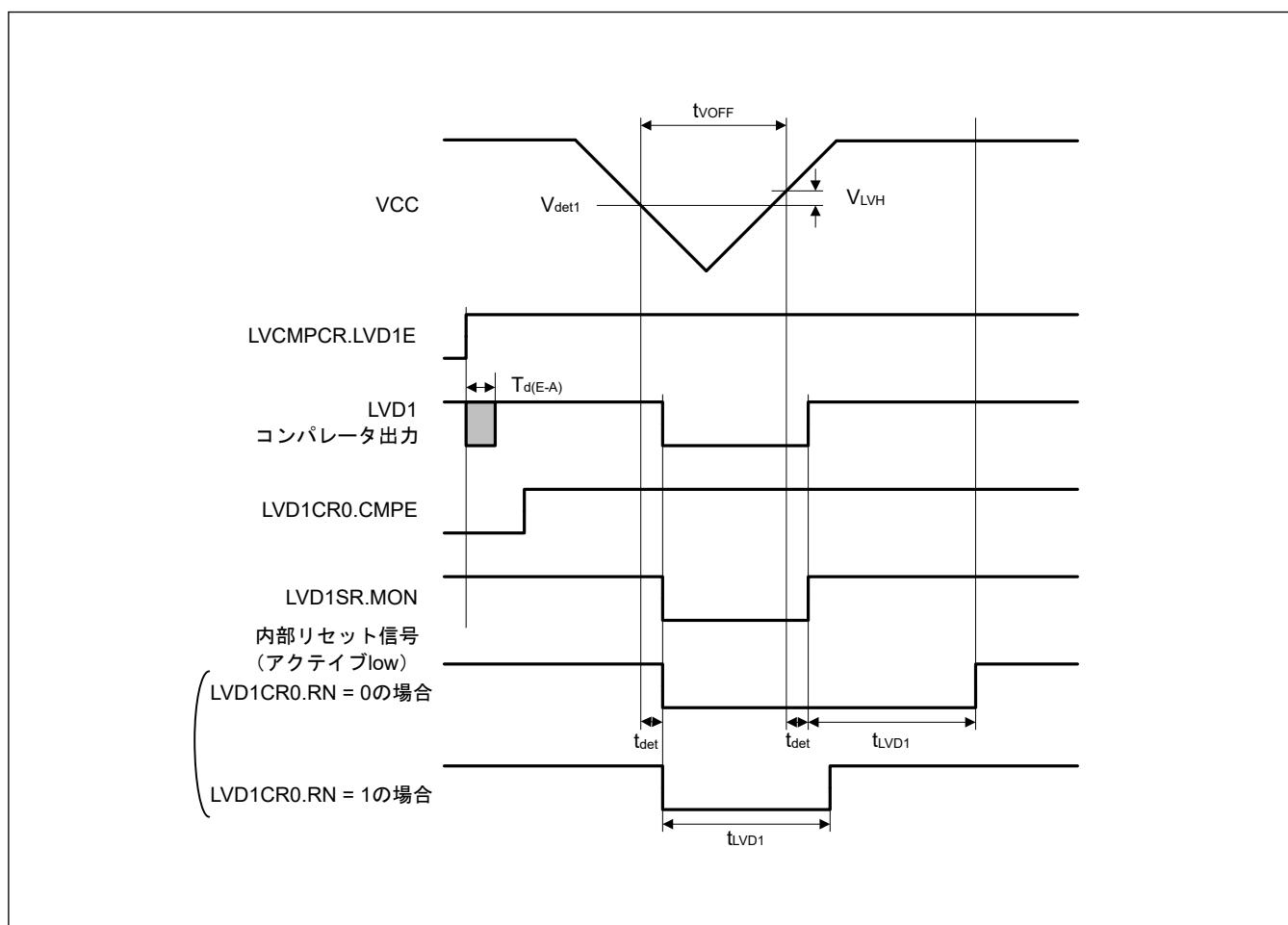

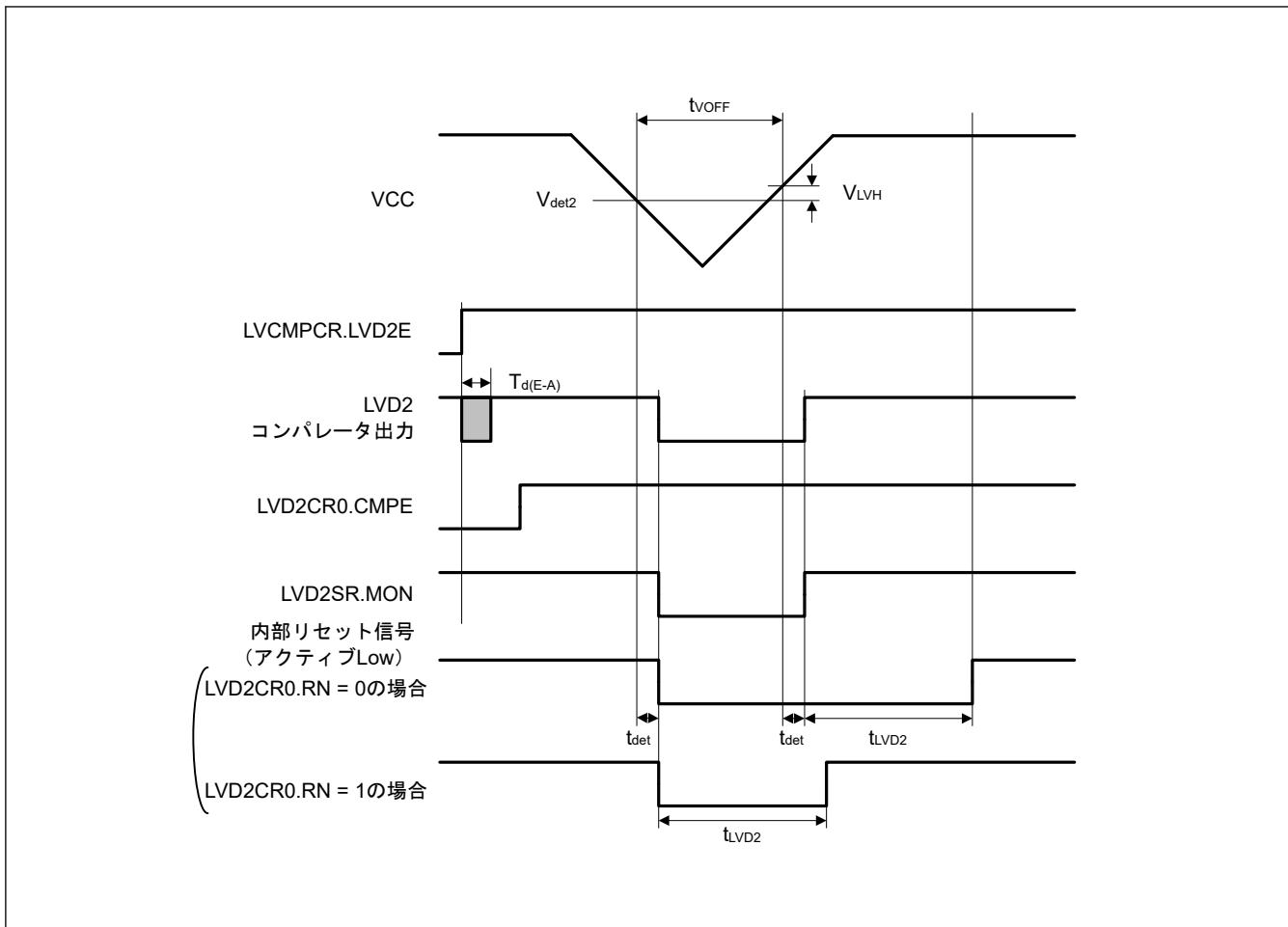

| 低電圧検出 (LVD) | 低電圧検出 (LVD) モジュールは、VCC 端子への入力電圧レベルを監視します。検出レベルはレジスタ設定で選択できます。LVD モジュールは、3 つの独立した電圧監視回路 (LVD0, LVD1, LVD2) から構成されています。LVD0, LVD1、および LVD2 は VCC 端子への入力電圧レベルを監視します。LVD のレジスタは、アプリケーションの設定により、さまざまな電圧しきい値で VCC 端子への入力電圧の変動を監視できます。       |

| クロック        | <ul style="list-style-type: none"> <li>メインクロック発振器 (MOSC)</li> <li>サブクロック発振器 (SOSC)</li> <li>高速オンチップオシレータ (HOCO)</li> <li>中速オンチップオシレータ (MOCO)</li> <li>低速オンチップオシレータ (LOCO)</li> <li>IWDT 専用オンチップオシレータ</li> <li>クロックアウトのサポート</li> </ul> |

表 1.3 システム (2/2)

| 機能                   | 機能の説明                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| クロック周波数精度測定回路 (CAC)  | クロック周波数精度測定回路 (CAC) は、測定の対象となるクロック（測定対象クロック）に対して、測定の基準となるクロック（測定基準クロック）で生成した時間内のクロックのパルスを数え、それが許容範囲内にあるか否かで精度を判定します。測定終了時、または測定基準クロックで生成した時間内のパルスの数が許容範囲内にない時、割り込み要求を発生します。                                                                                                           |

| 割り込みコントローラユニット (ICU) | 割り込みコントローラユニット (ICU) は、ネスト型ペクタ割り込みコントローラ (NVIC) およびデータトランスマルチコントローラ (DTC) モジュールにリンクされるイベント信号を制御します。ICU はノンマスカブル割り込みも制御します。                                                                                                                                                            |

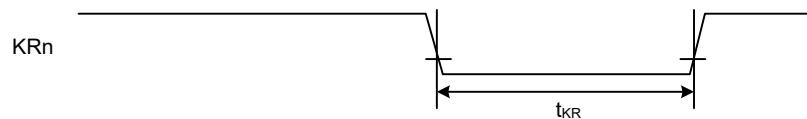

| キー割り込み機能 (KINT)      | キー割り込み機能 (KINT) は、キー割り込み入力端子の立ち上がりエッジまたは立ち下がりエッジが検出されると、キー割り込みを生成します。                                                                                                                                                                                                                 |

| 低消費電力モード             | クロック分周器の設定、モジュールストップ設定、通常動作時の電力制御モード選択、低消費電力モードへの遷移など、さまざまな方法で消費電力を低減できます。                                                                                                                                                                                                            |

| レジストライトプロテクション       | レジストライトプロテクション機能は、ソフトウェアエラーによって重要なレジスタが書き換えられないように保護します。保護するレジスタは、プロテクトレジスタ (PRCR) で設定します。                                                                                                                                                                                            |

| メモリプロテクションユニット (MPU) | 本 MCU は、4 つのメモリプロテクションユニット (MPU) と、CPU スタックポインタモニタ機能を備えています。                                                                                                                                                                                                                          |

| ウォッチドッグタイマ (WDT)     | ウォッチドッグタイマ (WDT) は 14 ビットのダウンカウンタです。システムが暴走すると WDT をリフレッシュできなくなるため、カウンタがアンダーフローした際に MCU をリセットするに使用できます。さらに、WDT はノンマスカブル割り込み、アンダーフロー割り込み、またはウォッチドッグタイマリセットを発生させるためにも使用できます。                                                                                                            |

| 独立ウォッチドッグタイマ (IWDT)  | 独立ウォッチドッグタイマ (IWDT) は 14 ビットのダウンカウンタで、カウンタのアンダーフローを防止するために定期的に点検する必要があります。IWDT には、MCU をリセットする機能やノンマスカブル割り込みまたはアンダーフロー割り込みを発生させる機能があります。このタイマは独立した専用クロックソースで動作するため、システム暴走時にフェイル-セーフメカニズムとして、MCU を既知の状態に復帰させる際に特に有用です。IWDT は、レジスタのリセット、アンダーフロー、リフレッシュエラー、またはカウント値のリフレッシュにより自動的にトリガできます。 |

表 1.4 イベントリンク

| 機能                  | 機能の説明                                                                                                           |

|---------------------|-----------------------------------------------------------------------------------------------------------------|

| イベントリンクコントローラ (ELC) | イベントリンクコントローラ (ELC) は、各周辺モジュールで発生するイベント要求をソース信号として使用し、それらのモジュールを別のモジュールと接続することによって、CPU を介さずにモジュール間の直接リンクを実現します。 |

表 1.5 ダイレクトメモリアクセス

| 機能                     | 機能の説明                                               |

|------------------------|-----------------------------------------------------|

| データトランスマルチコントローラ (DTC) | データトランスマルチコントローラ (DTC) は、割り込み要求によって起動するとデータ転送を行います。 |

表 1.6 タイマ

| 機能                          | 機能の説明                                                                                                                                                                                                                                                                                 |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 汎用 PWM タイマ (GPT)            | 汎用 PWM タイマ (GPT) は、GPT32 × 1 チャネルの 32 ビットタイマおよび GPT16 × 6 チャネルの 16 ビットタイマにより構成されます。PWM 波形はアップカウンタ、ダウンカウンタ、またはその両方を制御することにより生成が可能です。さらに、ブラシレス DC モーター制御用の PWM 波形の生成が可能です。GPT は、汎用タイマとしても使用できます。                                                                                        |

| GPT 用のポートアウトプットイネーブル (POEG) | ポートアウトプットイネーブル (POEG) は、以下の方法のいずれかにより、汎用 PWM タイマ (GPT) の出力端子を出力禁止状態にすることが可能です。                                                                                                                                                                                                        |

| 低消費電力非同期汎用タイマ (AGT)         | 低消費電力非同期汎用タイマ (AGT) は、パルス出力、外部パルスの幅または周期の測定、および外部イベントのカウントに利用可能な 16 ビットのタイマです。このタイマは、リロードレジスタとダウンカウンタで構成されています。これらのリロードレジスタとダウンカウンタは、同一アドレスに配置され、AGT レジスタでアクセス可能です。                                                                                                                   |

| リアルタイムクロック (RTC)            | RTC には、通常動作モードと低消費電力クロックモードの 2 種類の動作モードがあります。RTC には、それぞれの動作モードでカレンダーカウントモードとバイナリカウントモードの 2 種類のカウントモードがあり、レジスタの設定を切り替えることにより使用します。カレンダーカウントモードでは、RTC は 2000 年から 2099 年の 100 年間のカレンダーを保持し、うるう年の日付を自動補正します。バイナリカウントモードでは、RTC は秒をカウントし、その情報をシリアル値として保持します。バイナリカウントモードは、西暦以外のカレンダーに使用可能です。 |

表 1.7 通信インターフェース

| 機能                                | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| シリアルコミュニケーションインターフェース (SCI)       | シリアルコミュニケーションインターフェース (SCI) × 4 チャネルには、調歩同期式および同期式のシリアルインターフェースがあります。 <ul style="list-style-type: none"> <li>調歩同期式インターフェース (UART および調歩同期式通信インターフェースアダプタ (ACIA))</li> <li>8 ビットクロック同期式インターフェース</li> <li>簡易 IIC (マスターのみ)</li> <li>簡易 SPI</li> <li>スマートカードインターフェース</li> </ul> スマートカードインターフェースは、電子信号と伝送プロトコルに関して ISO/IEC 7816-3 規格に準拠しています。SCI <sub>n</sub> (n = 0) は FIFO バッファを内蔵しており、連続した全二重通信が可能です。また、内蔵のボーレートジェネレータを用いて、データ転送速度の個別設定が可能です。 |

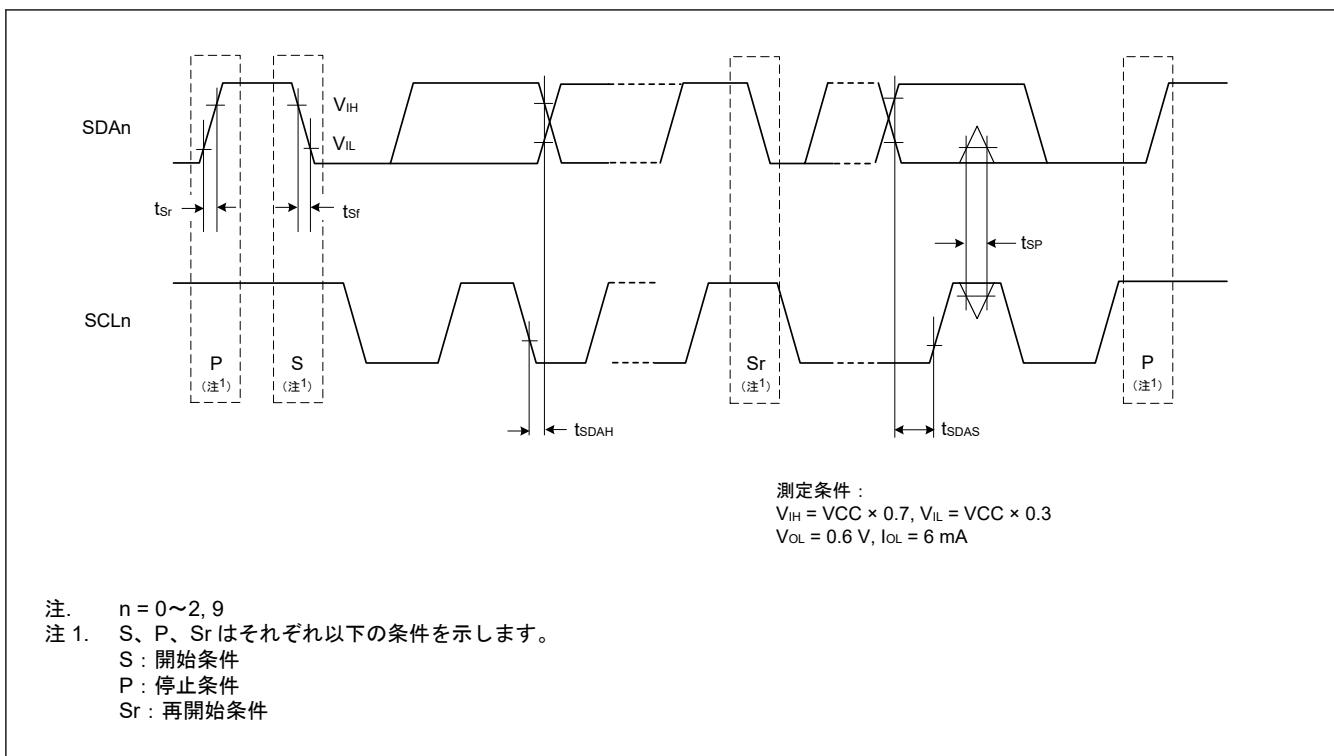

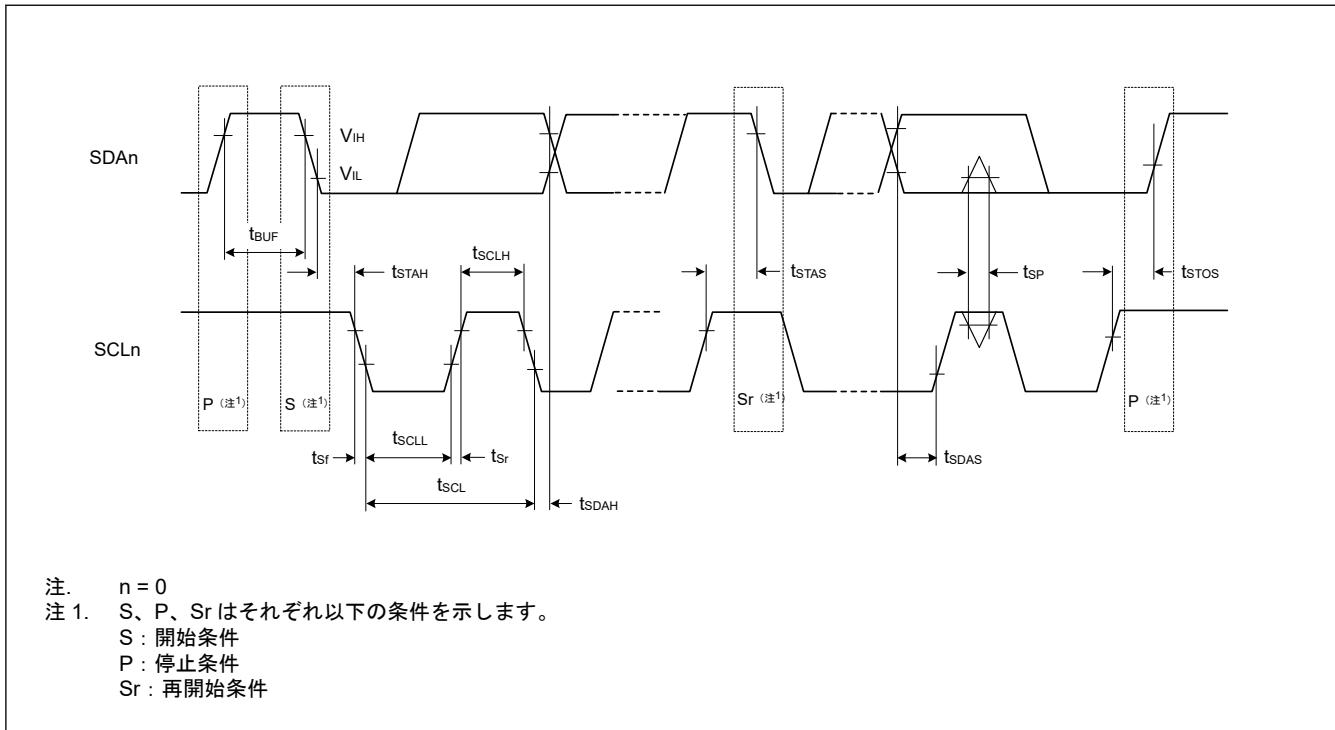

| I <sup>2</sup> C バスインターフェース (IIC) | I <sup>2</sup> C バスインターフェース (IIC) には 1 チャネルあります。IIC モジュールは、NXP 社の I <sup>2</sup> C (Integrated Circuit) バスインターフェース方式に準拠しており、そのサブセット機能を備えています。                                                                                                                                                                                                                                                                                              |

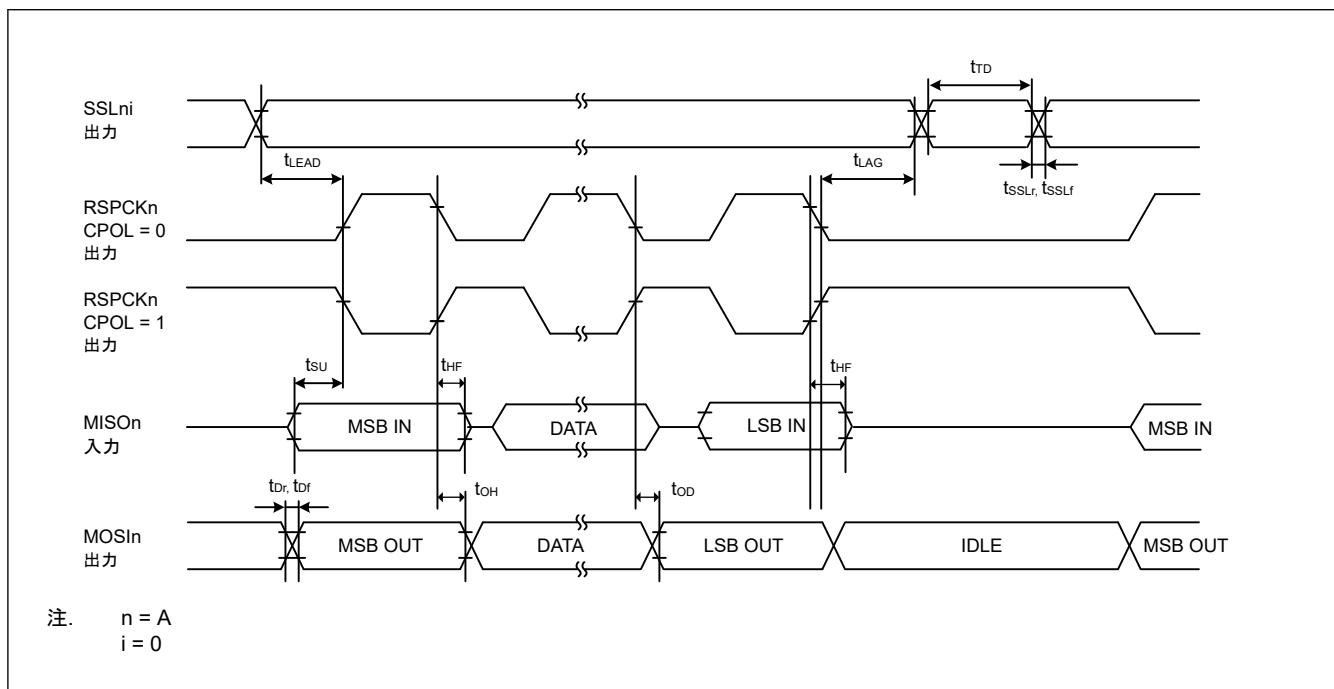

| シリアルペリフェラルインターフェース (SPI)          | シリアルペリフェラルインターフェース (SPI) には 1 つのチャネルがあります。SPI によって、複数のプロセッサおよび周辺デバイスとの高速な全二重同期式シリアル通信が可能です。                                                                                                                                                                                                                                                                                                                                                |

表 1.8 アナログ機能

| 機能                       | 機能の説明                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

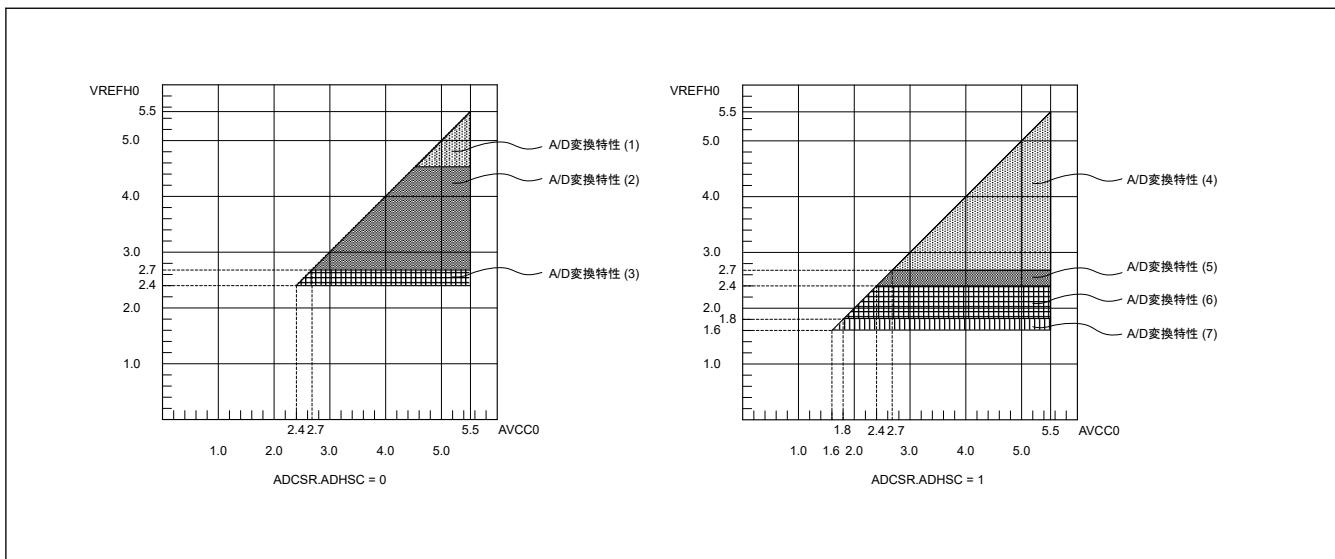

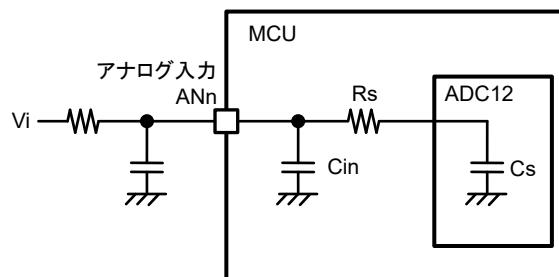

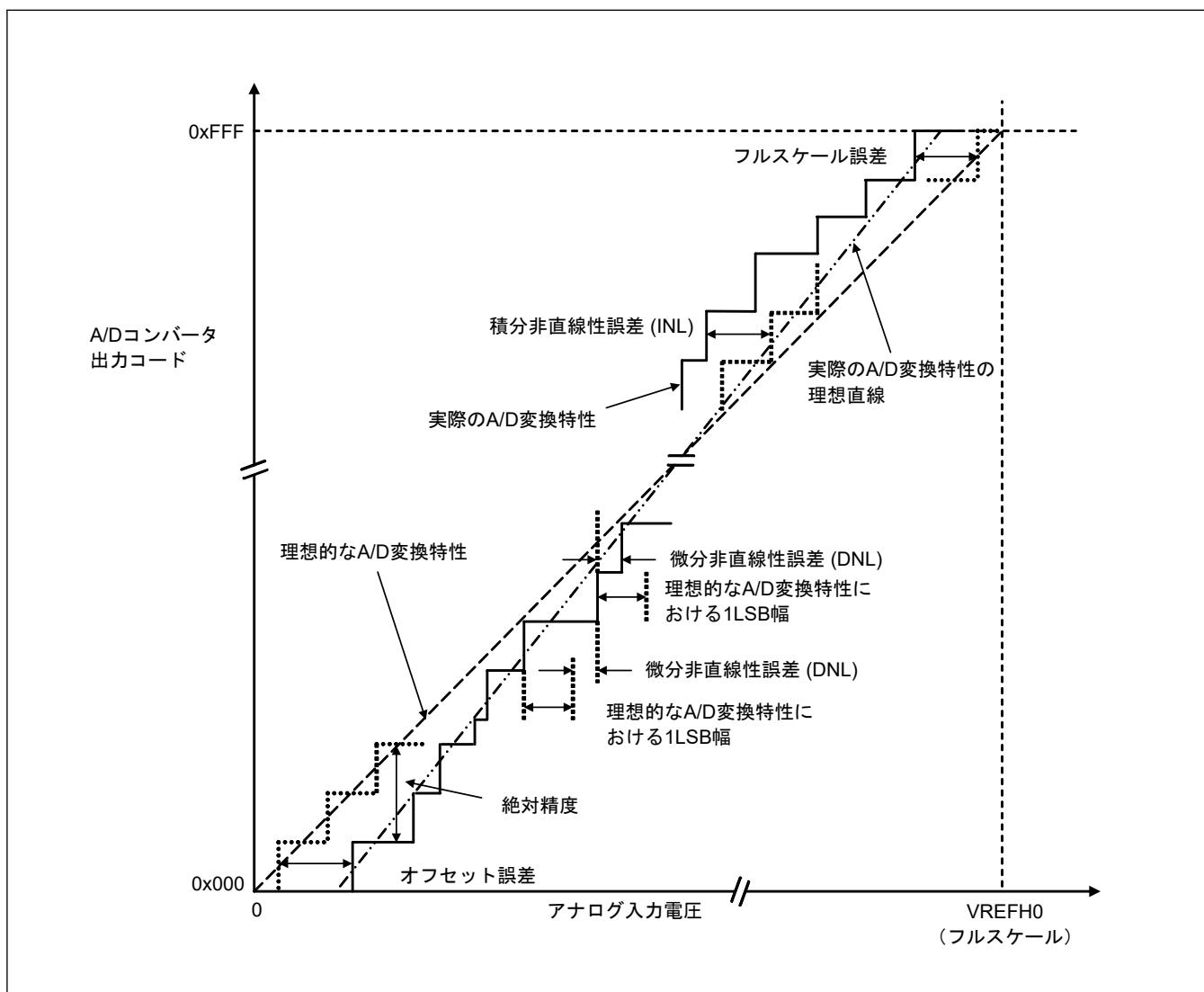

| 12 ビット A/D コンバータ (ADC12) | 逐次比較方式の 12 ビット A/D コンバータを内蔵しています。最大 13 チャネルのアナログ入力を選択可能です。変換には温度センサ出力および内部基準電圧を選択できます。                                                           |

| 温度センサ (TSN)              | デバイス動作の信頼性確保のため、内蔵されている温度センサ (TSN) でチップの温度を決定し、監視します。センサはチップの温度と正比例する電圧を出力します。チップ温度と出力電圧はほとんどリニアの関係にあります。出力された電圧は ADC12 で変換されてから、末端の応用機器で使用できます。 |

表 1.9 データ処理

| 機能               | 機能の説明                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 巡回冗長検査 (CRC) 演算器 | 巡回冗長検査 (CRC: Cyclic Redundancy Check) は、CRC コードを生成してデータエラーを検出します。LSB ファーストまたは MSB ファーストでの通信用に、CRC 演算結果のビットオーダーを切り替えることができます。さらに、さまざまな CRC 生成多項式を使用できます。スヌープ機能により、CRC コードで特定のアドレスに対するアクセスを監視できます。この機能は、シリアル送信バッファへの書き込みとシリアル受信バッファからの読み出しを監視する場合など、特定のイベントで CRC コードの自動生成が必要となるアプリケーションで役立ちます。 |

| データ演算回路 (DOC)    | データ演算回路 (DOC) は、16 ビットのデータを比較、加算、および減算する機能です。選択した条件が適用される場合、16 ビットのデータが比較され、割り込みを生成可能です。                                                                                                                                                                                                     |

表 1.10 I/O ポート

| 機能      | 機能の説明                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O ポート | <ul style="list-style-type: none"> <li>48 ピン LQFP/HWQFN 用 I/O ポート <ul style="list-style-type: none"> <li>入出力端子 : 37</li> <li>入力端子 : 3</li> <li>プルアップ抵抗 : 37</li> <li>N チャネルオープンドレイン出力 : 26</li> <li>5 V トランジスタ : 3</li> </ul> </li> <li>32 ピン LQFP/HWQFN 用 I/O ポート <ul style="list-style-type: none"> <li>入出力端子 : 23</li> <li>入力端子 : 3</li> <li>プルアップ抵抗 : 23</li> <li>N チャネルオープンドレイン出力 : 15</li> <li>5 V トランジスタ : 1</li> </ul> </li> </ul> |

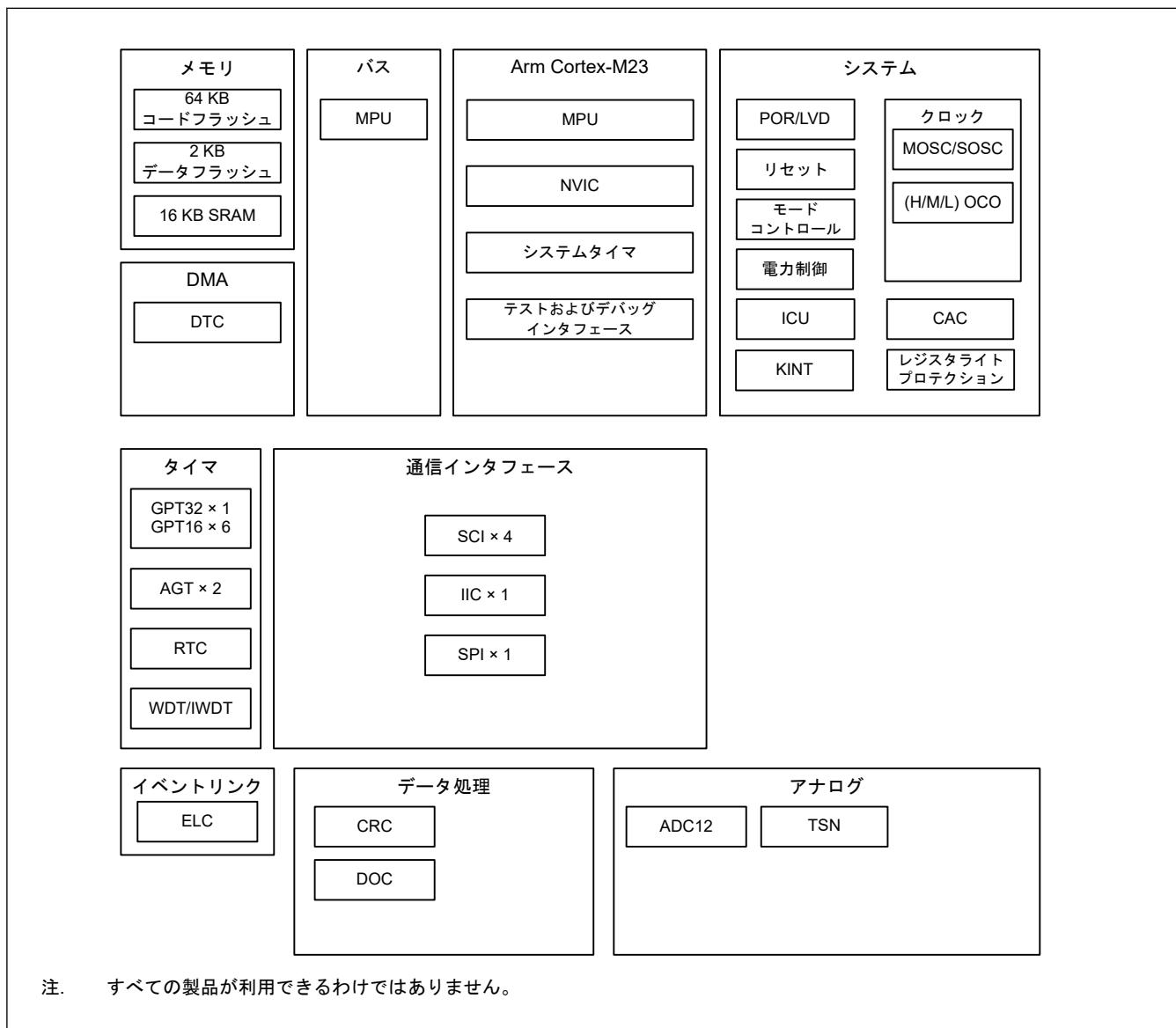

## 1.2 ブロック図

図 1.1 に、本 MCU のスーパーセットのブロック図を示します。グループ内の個々のデバイスは、その機能のサブセットを持つ場合があります。

図 1.1 ブロック図

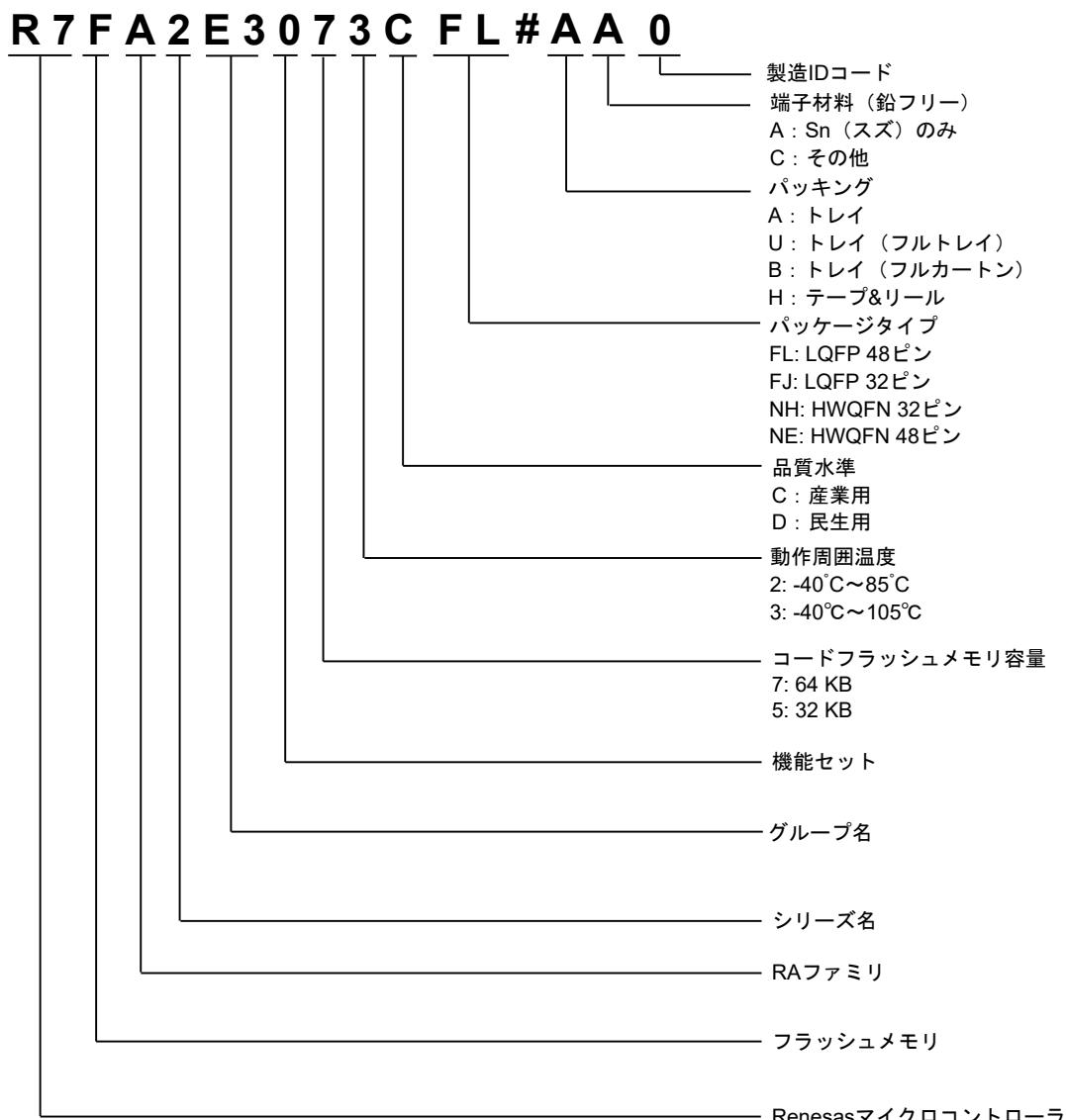

## 1.3 型名

図 1.2 に、メモリ容量およびパッケージタイプを含む製品の型名情報を示します。表 1.11 に、製品一覧表を示します。

注. #に続く有効な記号については、ルネサス Web サイト上の各製品の注文画面でご確認ください。

## 図 1.2 型名の読み方

表 1.11 製品一覧 (1/2)

| 製品型名          | パッケージコード     | コードフラッシュ | データフラッシュ | SRAM | 動作周囲温度     |

|---------------|--------------|----------|----------|------|------------|

| R7FA2E3073CFL | PLQP0048KB-B | 64       | 2        | 16   | -40~+105°C |

| R7FA2E3073CFJ | PLQP0032GB-A |          |          |      |            |

| R7FA2E3073CNH | PWQN0032KE-A |          |          |      |            |

| R7FA2E3073CNE | PWQN0048KC-A |          |          |      |            |

| R7FA2E3072DFL | PLQP0048KB-B |          |          |      | -40~+85°C  |

| R7FA2E3072DFJ | PLQP0032GB-A |          |          |      |            |

| R7FA2E3072DNH | PWQN0032KE-A |          |          |      |            |

| R7FA2E3072DNE | PWQN0048KC-A |          |          |      |            |

表 1.11 製品一覧 (2/2)

| 製品型名          | パッケージコード     | コードフラッシュ | データフラッシュ | SRAM | 動作周囲温度     |

|---------------|--------------|----------|----------|------|------------|

| R7FA2E3053CFL | PLQP0048KB-B | 32       | 2        | 16   | -40～+105°C |

| R7FA2E3053CFJ | PLQP0032GB-A |          |          |      | -40～+85°C  |

| R7FA2E3053CNH | PWQN0032KE-A |          |          |      |            |

| R7FA2E3053CNE | PWQN0048KC-A |          |          |      |            |

| R7FA2E3052DFL | PLQP0048KB-B |          |          |      |            |

| R7FA2E3052DFJ | PLQP0032GB-A |          |          |      |            |

| R7FA2E3052DNH | PWQN0032KE-A |          |          |      |            |

| R7FA2E3052DNE | PWQN0048KC-A |          |          |      |            |

## 1.4 機能の比較

表 1.12 機能の比較

| 型名          | R7FA2E307xxFL<br>R7FA2E307xxNE | R7FA2E305xxFL<br>R7FA2E305xxNE | R7FA2E307xxFJ<br>R7FA2E307xxNH | R7FA2E305xxFJ<br>R7FA2E305xxNH |

|-------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| 端子総数        | 48                             | 32                             |                                |                                |

| パッケージ       | LQFP/HWQFN                     | LQFP/HWQFN                     |                                |                                |

| コードフラッシュメモリ | 64 KB                          | 32 KB                          | 64 KB                          | 32 KB                          |

| データフラッシュメモリ | 2 KB                           |                                | 2 KB                           |                                |

| SRAM (パリティ) | 16 KB                          |                                | 16 KB                          |                                |

| システム        | CPU クロック                       | 48 MHz                         | 48 MHz                         |                                |

|             | サブクロック発振器                      | あり                             | あり                             |                                |

|             | ICU                            | あり                             | あり                             |                                |

|             | KINT                           | 5                              | 4                              |                                |

| イベントコントロール  | ELC                            | あり                             | あり                             |                                |

| DMA         | DTC                            | あり                             | あり                             |                                |

| タイマ         | GPT32                          | 1 (PWM 出力: 2)                  | 1 (PWM 出力: 2)                  |                                |

|             | GPT16                          | 6 (PWM 出力: 12)                 | 6 (PWM 出力: 7)                  |                                |

|             | AGT                            | 2                              | 2                              |                                |

|             | RTC                            | あり                             | あり                             |                                |

|             | WDT/IWDT                       | あり                             | あり                             |                                |

| 通信          | SCI                            | 4                              | 3                              |                                |

|             | IIC                            | 1                              | 1                              |                                |

|             | SPI                            | 1                              | 1                              |                                |

| アナログ        | ADC12                          | 13                             | 10                             |                                |

|             | TSN                            | あり                             | あり                             |                                |

| データ処理       | CRC                            | あり                             | あり                             |                                |

|             | DOC                            | あり                             | あり                             |                                |

| I/O ポート     | 入出力端子                          | 37                             | 23                             |                                |

|             | 入力端子                           | 3                              | 3                              |                                |

|             | プルアップ抵抗                        | 37                             | 23                             |                                |

|             | N チャネルオープンドレイン出力               | 26                             | 15                             |                                |

|             | 5 V トランジスタ                     | 3                              | 1                              |                                |

## 1.5 端子機能

表 1.13 端子機能 (1/2)

| 機能          | 端子名                                        | 入出力 | 説明                                                                                    |

|-------------|--------------------------------------------|-----|---------------------------------------------------------------------------------------|

| 電源          | VCC                                        | 入力  | 電源端子。システムの電源に接続してください。この端子は 0.1 $\mu$ F のコンデンサを介して VSS に接続してください。コンデンサは端子近くに配置してください。 |

|             | VCL                                        | 入出力 | この端子は、内部電源を安定化するための平滑コンデンサを介して VSS 端子に接続してください。コンデンサは端子近くに配置してください。                   |

|             | VSS                                        | 入力  | グランド端子。システムの電源 (0 V) に接続してください。                                                       |

| クロック        | XTAL                                       | 出力  | 水晶振動子用の接続端子。EXTAL 端子を通じて外部クロック信号の入力が可能です。                                             |

|             | EXTAL                                      | 入力  |                                                                                       |

|             | XCIN                                       | 入力  | サブクロック発振器用の入出力端子。XCOUT と XCIN の間には、水晶振動子を接続してください。                                    |

|             | XCOUT                                      | 出力  |                                                                                       |

|             | CLKOUT                                     | 出力  | クロック出力端子                                                                              |

| 動作モードコントロール | MD                                         | 入力  | 動作モード設定用の端子。本端子の信号レベルは、リセット解除時の動作モードの遷移中に変更しないでください。                                  |

| システム制御      | RES                                        | 入力  | リセット信号入力端子。本端子が Low になると、MCU はリセット状態となります。                                            |

| CAC         | CACREF                                     | 入力  | 測定基準クロックの入力端子                                                                         |

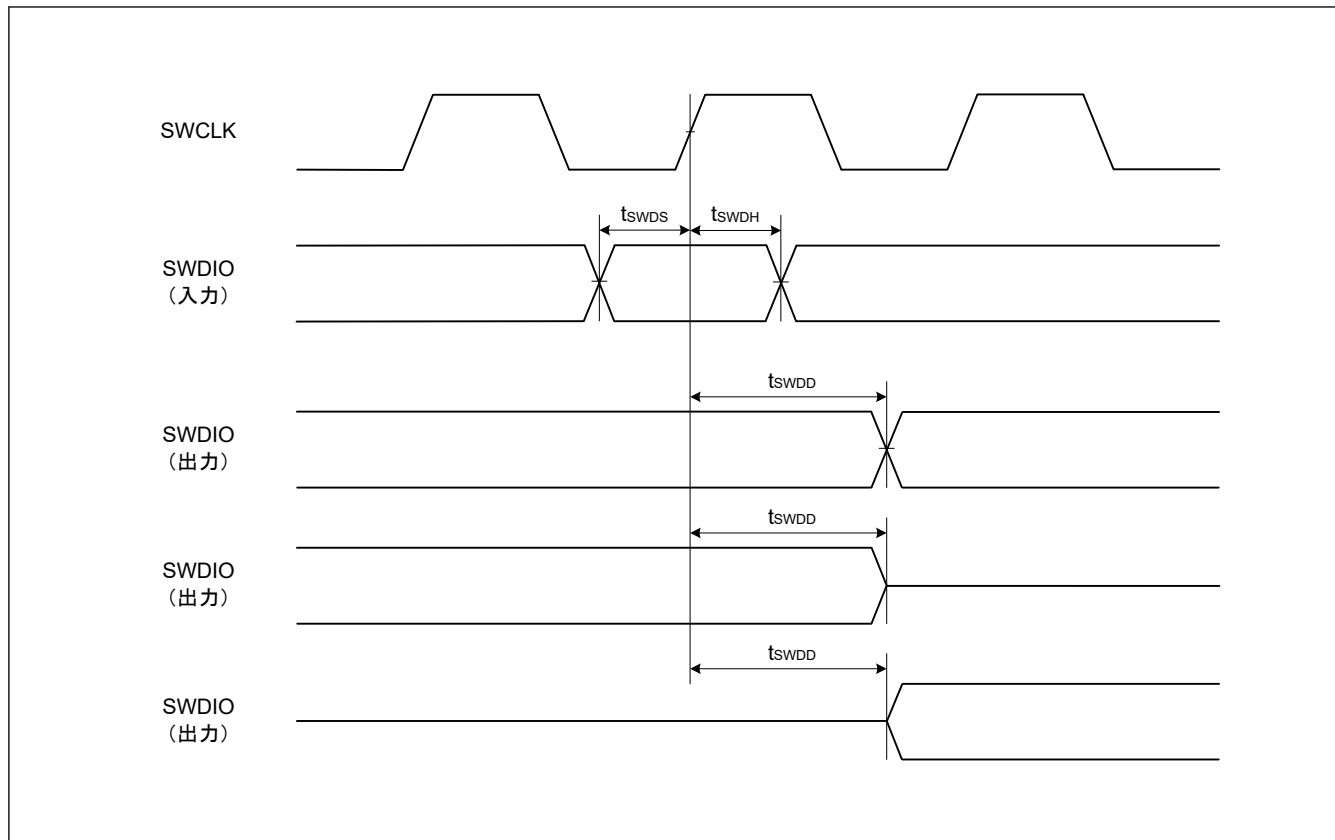

| オンチップデバッグ   | SWDIO                                      | 入出力 | シリアルワイヤデバッグデータの入出力端子                                                                  |

|             | SWCLK                                      | 入力  | シリアルワイヤクロック端子                                                                         |

| 割り込み        | NMI                                        | 入力  | ノンマスカブル割り込み要求端子                                                                       |

|             | IRQ0~IRQ7                                  | 入力  | マスカブル割り込み要求端子                                                                         |

| GPT         | GTETRGA, GTETRGB                           | 入力  | 外部トリガ入力端子                                                                             |

|             | GTIOCnA (n = 0, 4~9), GTIOCnB (n = 0, 4~9) | 入出力 | インプットキャプチャ、アウトプットコンペア、または PWM 出力端子                                                    |

|             | GTOUUP                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (正相 U 相)                                                      |

|             | GTOULO                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (逆相 U 相)                                                      |

|             | GTOVUP                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (正相 V 相)                                                      |

|             | GTOVLO                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (逆相 V 相)                                                      |

|             | GTOWUP                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (正相 W 相)                                                      |

|             | GTOWLO                                     | 出力  | BLDC モーター制御用 3 相 PWM 出力 (逆相 W 相)                                                      |

| AGT         | AGTEE0, AGTEE1                             | 入力  | 外部イベント入力イネーブル信号                                                                       |

|             | AGTIO0, AGTIO1                             | 入出力 | 外部イベント入力およびパルス出力端子                                                                    |

|             | AGTO0                                      | 出力  | パルス出力端子                                                                               |

|             | AGTOA0, AGTOA1                             | 出力  | 出力コンペアマッチ A 出力端子                                                                      |

|             | AGTOB0                                     | 出力  | 出力コンペアマッチ B 出力端子                                                                      |

| RTC         | RTCOUT                                     | 出力  | 1 Hz または 64 Hz のクロック出力端子                                                              |

表 1.13 端子機能 (2/2)

| 機能      | 端子名                                             | 入出力 | 説明                                                    |

|---------|-------------------------------------------------|-----|-------------------------------------------------------|

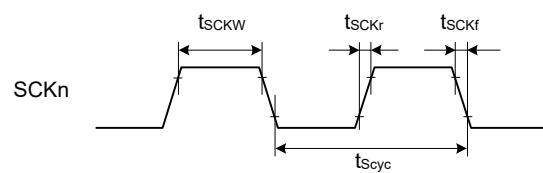

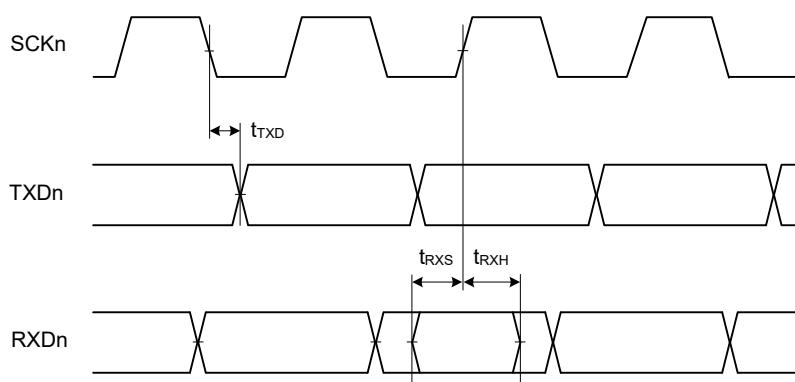

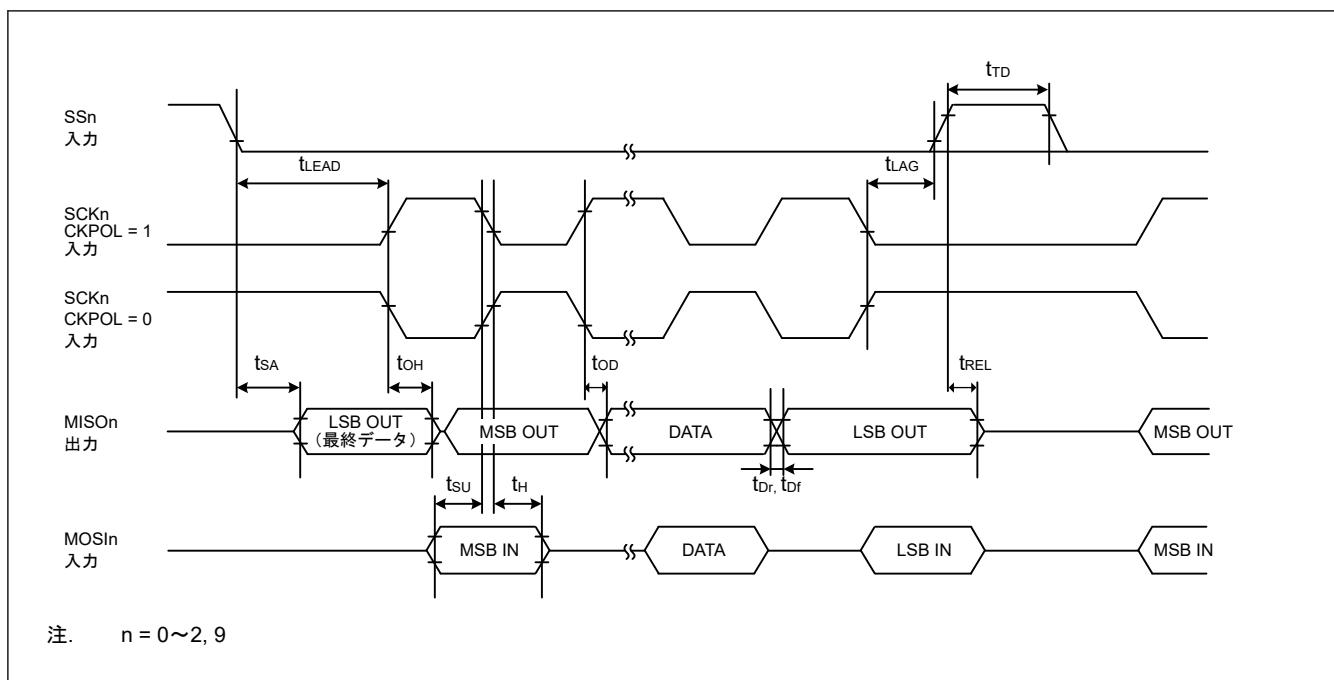

| SCI     | SCKn (n = 0~2, 9)                               | 入出力 | クロック用の入出力端子 (クロック同期式モード)                              |

|         | RXDn (n = 0~2, 9)                               | 入力  | 受信データ用の入力端子 (調歩同期式モード/クロック同期式モード)                     |

|         | TXDn (n = 0~2, 9)                               | 出力  | 送信データ用の出力端子 (調歩同期式モード/クロック同期式モード)                     |

|         | CTS <sub>n</sub> _RTS <sub>n</sub> (n = 0~2, 9) | 入出力 | 送受信の開始制御用の入出力端子 (調歩同期式モード/クロック同期式モード)、アクティブ Low       |

|         | SCLn (n = 0~2, 9)                               | 入出力 | IIC クロック用の入出力端子 (簡易 IIC モード)                          |

|         | SDAn (n = 0~2, 9)                               | 入出力 | IIC データ用の入出力端子 (簡易 IIC モード)                           |

|         | SCKn (n = 0~2, 9)                               | 入出力 | クロック用の入出力端子 (簡易 SPI モード)                              |

|         | MISOn (n = 0~2, 9)                              | 入出力 | データのスレーブ送信用の入出力端子 (簡易 SPI モード)                        |

|         | MOSIn (n = 0~2, 9)                              | 入出力 | データのマスタ送信用の入出力端子 (簡易 SPI モード)                         |

|         | SSn (n = 0~2, 9)                                | 入力  | チップセレクト入力端子 (簡易 SPI モード)、アクティブ Low                    |

| IIC     | SCLn (n = 0)                                    | 入出力 | クロック用の入出力端子                                           |

|         | SDAn (n = 0)                                    | 入出力 | データ用の入出力端子                                            |

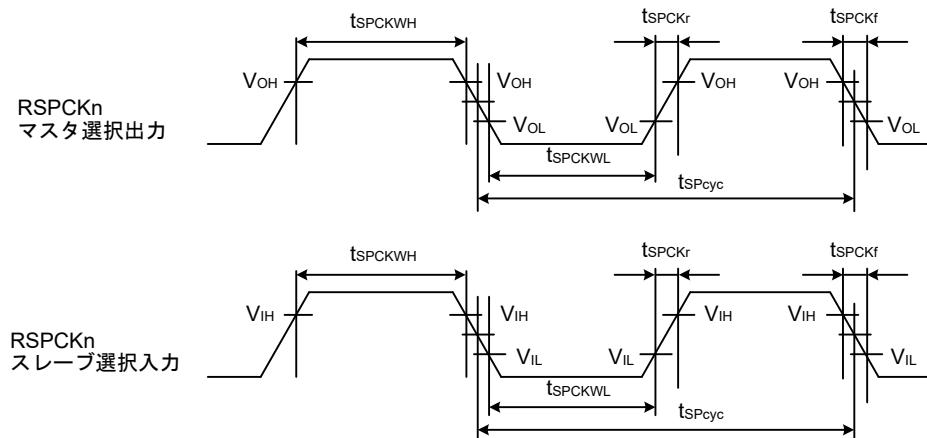

| SPI     | RSPCKA                                          | 入出力 | クロック入出力端子                                             |

|         | SSLA0                                           | 入出力 | スレーブ選択用の入出力端子                                         |

|         | SSLA1                                           | 出力  | スレーブ選択用の出力端子                                          |

|         | MOSIA                                           | 入出力 | マスタからの出力データ用の入出力端子                                    |

|         | MISOA                                           | 入出力 | スレーブからの出力データ用の入出力端子                                   |

| アナログ電源  | AVCC0                                           | 入力  | ADC12 用のアナログ電源端子                                      |

|         | AVSS0                                           | 入力  | ADC12 用のアナロググランド端子                                    |

|         | VREFH0                                          | 入力  | ADC12 用のアナログ基準電圧源端子。ADC12 を使用しない場合は AVCC0 に接続してください。  |

|         | VREFL0                                          | 入力  | ADC12 用のアナログ基準グランド端子。ADC12 を使用しない場合は AVSS0 に接続してください。 |

| ADC12   | AN000~AN002, AN005~AN010, AN019~AN022           | 入力  | A/D コンバータで処理されるアナログ信号用の入力端子                           |

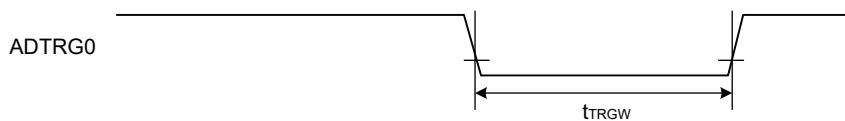

|         | ADTRG0                                          | 入力  | A/D 変換を開始する外部トリガ信号用の入力端子、アクティブ Low                    |

| KINT    | KR00~KR04                                       | 入力  | キー割り込み入力端子                                            |

| I/O ポート | P000~P002, P010~P015                            | 入出力 | 汎用入出力端子                                               |

|         | P100~P104, P108~P112                            | 入出力 | 汎用入出力端子                                               |

|         | P200                                            | 入力  | 汎用入力端子                                                |

|         | P201, P206~P208, P212, P213                     | 入出力 | 汎用入出力端子                                               |

|         | P214, P215                                      | 入力  | 汎用入力端子                                                |

|         | P300~P302                                       | 入出力 | 汎用入出力端子                                               |

|         | P400, P401, P407~P409                           | 入出力 | 汎用入出力端子                                               |

|         | P500                                            | 入出力 | 汎用入出力端子                                               |

|         | P913~P915                                       | 入出力 | 汎用入出力端子                                               |

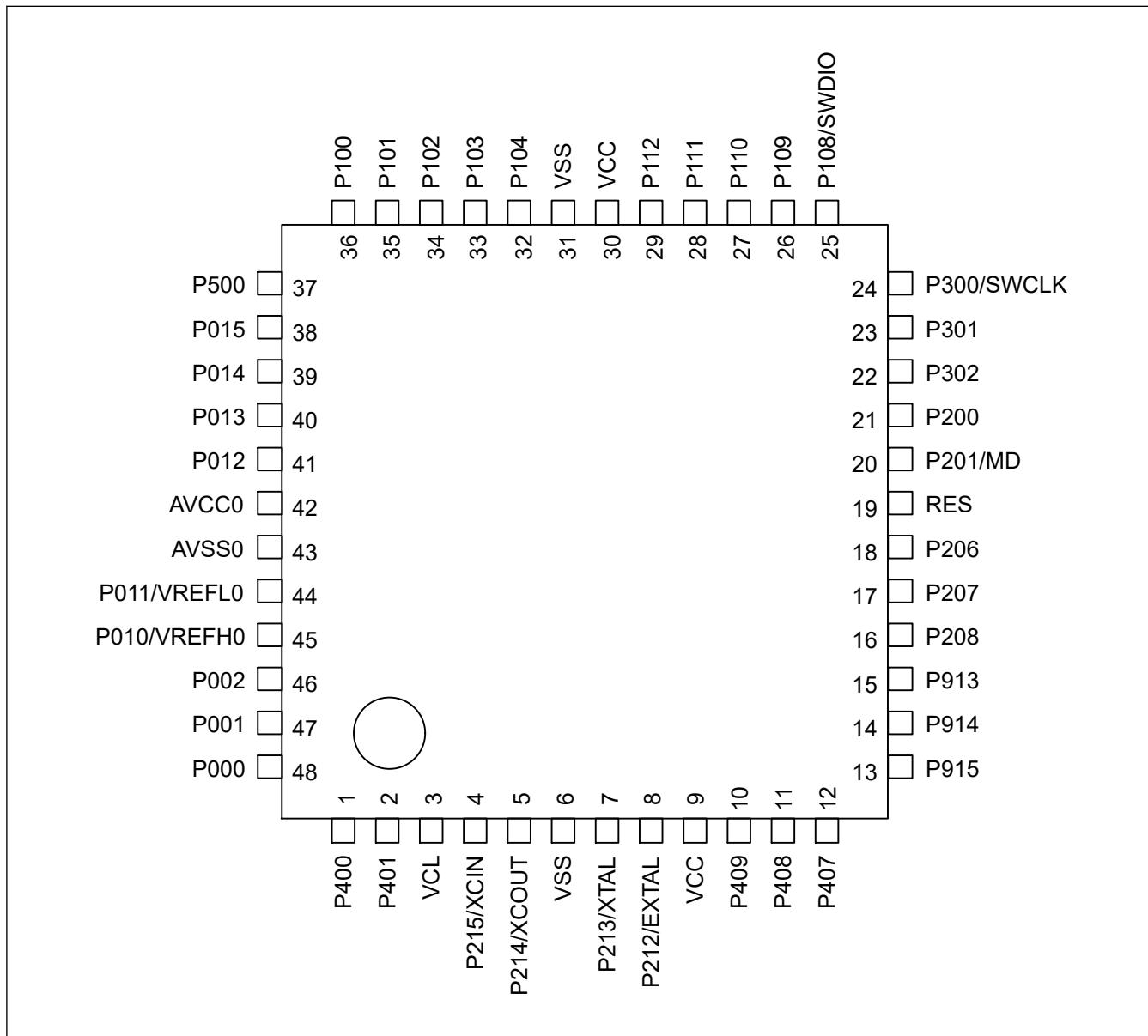

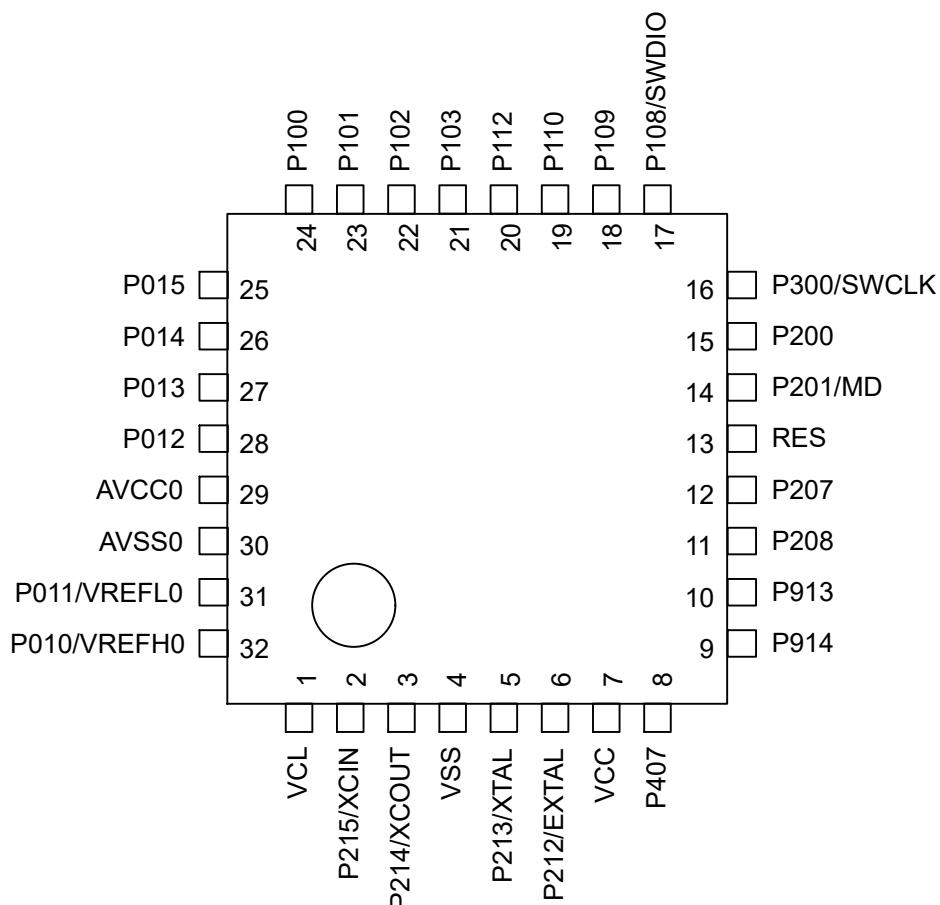

## 1.6 ピン配置図

図 1.3 と図 1.4 にピン配置図（上面図）を示します。

図 1.3 48 ピン LQFP/QFN のピン配置図（上面図）

注. QFN パッケージの製品に対しては、exposed die pad を電気的接続のない PCB のめっき領域にはんだづけしてください。

図 1.4 32 ピン LQFP/QFN のピン配置図（上面図）

注. QFN パッケージの製品に対しては、exposed die pad を電気的接続のない PCB のめっき領域にはんだづけしてください。

## 1.7 端子一覧

表 1.14 端子一覧 (1/2)

| 端子番号 | LQFP/QFN 48 ピン | LQFP/QFN 32 ピン | 電源、システム、クロック、デバッグ、CAC | IOポート    | タイマ       |                  |        |                       | 通信インターフェース                                              |                |          | アナログ | HMI    |

|------|----------------|----------------|-----------------------|----------|-----------|------------------|--------|-----------------------|---------------------------------------------------------|----------------|----------|------|--------|

|      |                |                |                       |          | AGT       | GPT_OPS、<br>POEG | GPT    | RTC                   | SCI                                                     | I <sub>C</sub> | SPI      |      |        |

| 1    | —              | CACREF_C       | P400                  | AGTIO1_C | —         | GTIOC9A_A        | —      | —                     | SCK0_B/<br>SCK1_B                                       | SCL0_A         | —        | —    | IRQ0_A |

| 2    | —              |                | P401                  | —        | GTETRGA_B | GTIOC9B_A        | —      | —                     | CTS0_RTS0_B/<br>SS0_B/TXD1_B/<br>MOSI1_B/<br>SDA1_B     | SDA0_A         | —        | —    | IRQ5   |

| 3    | 1              | VCL            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 4    | 2              | XCIN           | P215                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 5    | 3              | XCOUNT         | P214                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 6    | 4              | VSS            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 7    | 5              | XTAL           | P213                  | —        | GTETRGA_D | GTIOC0A_D        | —      | —                     | TXD1_A/<br>MOSI1_A/<br>SDA1_A                           | —              | —        | —    | IRQ2_B |

| 8    | 6              | EXTAL          | P212                  | AGTEE1   | GTETRGB_D | GTIOC0B_D        | —      | —                     | RXD1_A/<br>MISO1_A/<br>SCL1_A                           | —              | —        | —    | IRQ3_B |

| 9    | 7              | VCC            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 10   | —              |                | P409                  | —        | GTOWUP_B  | —                | —      | —                     | —                                                       | —              | —        | —    | IRQ6_B |

| 11   | —              |                | P408                  | —        | GTOWLO_B  | —                | —      | —                     | CTS1_RTS1_D/<br>SS1_D                                   | SCL0_C         | —        | —    | IRQ7_B |

| 12   | 8              |                | P407                  | AGTIO0_C | —         | —                | RTCOUT | CTS0_RTS0_D/<br>SS0_D | SDA0_B                                                  | —              | ADTRG0_B | —    | —      |

| 13   | —              |                | P915                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 14   | 9              |                | P914                  | AGTOA1_A | GTETRGB_F | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 15   | 10             |                | P913                  | AGTIO1_F | GTETRGA_F | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 16   | 11             |                | P208                  | AGTOB0_A | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 17   | 12             |                | P207                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 18   | —              |                | P206                  | —        | —         | —                | —      | —                     | RXD0_D/<br>MISO0_D/<br>SCL0_D                           | —              | —        | —    | IRQ0   |

| 19   | 13             | RES            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 20   | 14             | MD             | P201                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 21   | 15             |                | P200                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | NMI    |

| 22   | —              |                | P302                  | —        | GTOUUP_A  | GTIOC7A_A        | —      | —                     | TXD2_A/<br>MOSI2_A/<br>SDA2_A                           | —              | —        | —    | IRQ5_A |

| 23   | —              |                | P301                  | AGTIO0_D | GTOULO_A  | GTIOC7B_A        | —      | —                     | RXD2_A/<br>MISO2_A/<br>SCL2_A/<br>CTS9_RTS9_D/<br>SS9_D | —              | —        | —    | IRQ6_A |

| 24   | 16             | SWCLK          | P300                  | —        | GTOUUP_C  | GTIOC0A_A        | —      | —                     | —                                                       | —              | —        | —    | —      |

| 25   | 17             | SWDIO          | P108                  | —        | GTOULO_C  | GTIOC0B_A        | —      | —                     | CTS9_RTS9_B/<br>SS9_B                                   | —              | —        | —    | —      |

| 26   | 18             | CLKOUT_B       | P109                  | —        | GTOVUP_A  | GTIOC4A_A        | —      | —                     | SCK1_E/<br>TXD9_B/<br>MOSI9_B/<br>SDA9_B                | —              | —        | —    | —      |

| 27   | 19             |                | P110                  | —        | GTOVLO_A  | GTIOC4B_A        | —      | —                     | CTS2_RTS2_B/<br>SS2_B/TXD9_B/<br>MISO9_B/<br>SCL9_B     | —              | —        | —    | IRQ3_A |

| 28   | —              |                | P111                  | AGTOA0   | —         | GTIOC6A_A        | —      | —                     | SCK2_B/<br>SCK9_B                                       | —              | —        | —    | IRQ4_A |

| 29   | 20             |                | P112                  | AGTOB0   | —         | GTIOC6B_A        | —      | —                     | SCK1_D/<br>TXD2_B/<br>MOSI2_B/<br>SDA2_B                | —              | —        | —    | —      |

| —    | —              |                | P113                  | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 30   | —              | VCC            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

| 31   | —              | VSS            |                       | —        | —         | —                | —      | —                     | —                                                       | —              | —        | —    | —      |

表 1.14 端子一覧 (2/2)

| 端子番号 | LQFP/QFN 48 ピン | LQFP/QFN 32 ピン | 電源、システム、クロック、デバッグ、CAC | I/O ポート | タイマ      |                  |           | 通信インターフェース |                                                         |                | アナログ     | HMI                |             |

|------|----------------|----------------|-----------------------|---------|----------|------------------|-----------|------------|---------------------------------------------------------|----------------|----------|--------------------|-------------|

|      |                |                |                       |         | AGT      | GPT_OPS、<br>POEG | GPT       | RTC        | SCI                                                     | I <sub>C</sub> |          |                    |             |

| 32   | —              |                |                       | P104    | —        | GTETRGB_B        | GTIOC4B_B | —          | RXD0_C/<br>MISO0_C/<br>SCL0_C                           | —              | SSLA1_A  | —                  | KR04/IRQ1_B |

| 33   | 21             |                |                       | P103    | —        | GTOWUP_A         | GTIOC5A_A | —          | CTS0_RTS0_A/<br>SS0_A                                   | —              | SSLA0_A  | AN019              | KR03        |

| 34   | 22             |                |                       | P102    | AGTO0    | GTOWLO_A         | GTIOC5B_A | —          | SCK0_A/<br>TXD2_D/<br>MOSI2_D/<br>SDA2_D                | —              | RSPCKA_A | ADTRG0_A/<br>AN020 | KR02        |

| 35   | 23             |                |                       | P101    | AGTEE0   | GTETRGB_A        | GTIOC8A_A | —          | TXD0_A/<br>MOSI0_A/<br>SDA0_A/<br>CTS1_RTS1_A/<br>SS1_A | SDA0_C         | MOSIA_A  | AN021              | KR01/IRQ1_A |

| 36   | 24             |                |                       | P100    | AGTIO0_A | GTETRGA_A        | GTIOC8B_A | —          | RXD0_A/<br>MISO0_A/<br>SCL0_A/<br>SCK1_A                | SCL0_D         | MISOA_A  | AN022              | KR00/IRQ2_A |

| 37   | —              |                |                       | P500    | —        | —                | GTIOC5A_B | —          | —                                                       | —              | —        | —                  | —           |

| 38   | 25             |                |                       | P015    | —        | —                | —         | —          | —                                                       | —              | —        | AN010              | IRQ7_A      |

| 39   | 26             |                |                       | P014    | —        | —                | —         | —          | —                                                       | —              | —        | AN009              | —           |

| 40   | 27             |                |                       | P013    | —        | —                | —         | —          | —                                                       | —              | —        | AN008              | —           |

| 41   | 28             |                |                       | P012    | —        | —                | —         | —          | —                                                       | —              | —        | AN007              | —           |

| 42   | 29             | AVCC0          |                       | —       | —        | —                | —         | —          | —                                                       | —              | —        | —                  | —           |

| 43   | 30             | AVSS0          |                       | —       | —        | —                | —         | —          | —                                                       | —              | —        | —                  | —           |

| 44   | 31             | VREFL0         | P011                  | —       | —        | —                | —         | —          | —                                                       | —              | —        | AN006              | —           |

| 45   | 32             | VREFH0         | P010                  | —       | —        | —                | —         | —          | —                                                       | —              | —        | AN005              | —           |

| 46   | —              |                | P002                  | —       | —        | —                | —         | —          | —                                                       | —              | —        | AN002              | IRQ2        |

| 47   | —              |                | P001                  | —       | —        | —                | —         | —          | —                                                       | —              | —        | AN001              | IRQ7        |

| 48   | —              |                | P000                  | —       | —        | —                | —         | —          | —                                                       | —              | —        | AN000              | IRQ6        |

注: いくつかの端子名には、\_A、\_B、\_C、\_D、\_E、および\_Fという接尾語が付加されています。これらの接尾語は、機能の割り当て時には無視できます。

## 2. 電気的特性

特に記載のない限り、本 MCU の電気的特性は以下の条件で定義されています。

$V_{CC}^{(注1)} = AVCC0 = 1.6 \sim 5.5 \text{ V}$ ,  $VREFH0 = 1.6 \text{ V} \sim AVCC0$

$VSS = AVSS0 = VREFL0 = 0 \text{ V}$ ,  $T_a = T_{opr}$

注 1. 通常は  $VCC = 3.3 \text{ V}$  に設定されています。

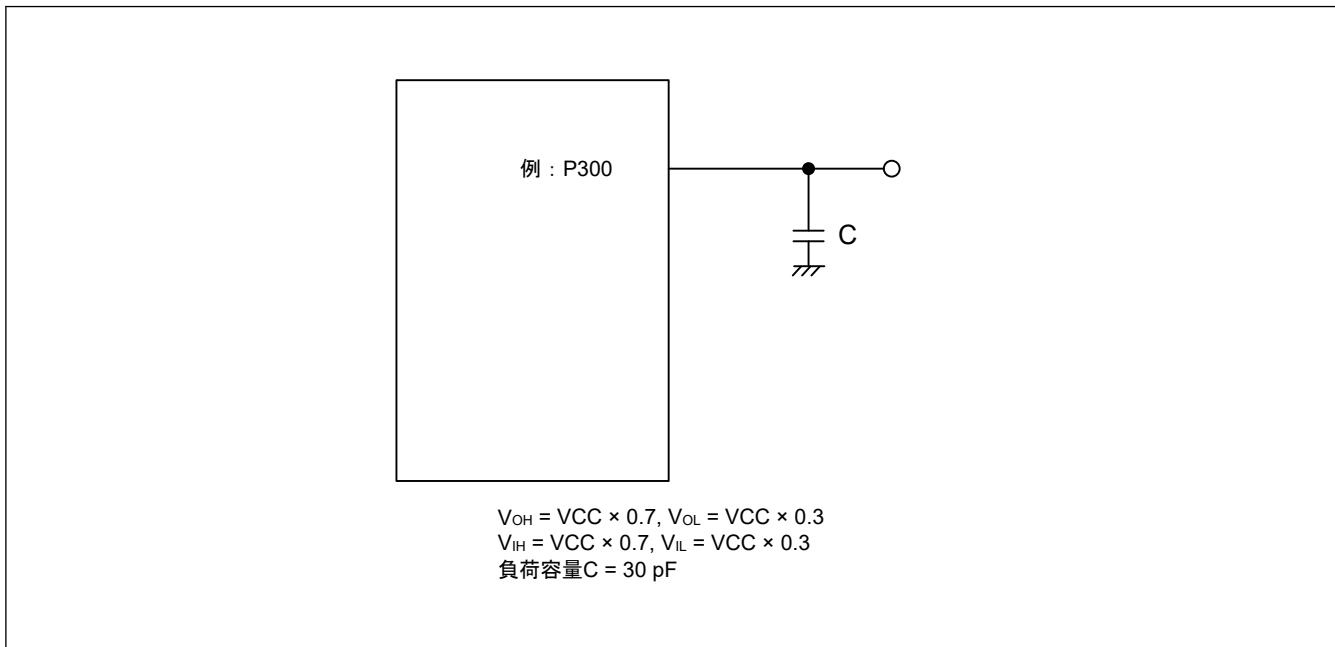

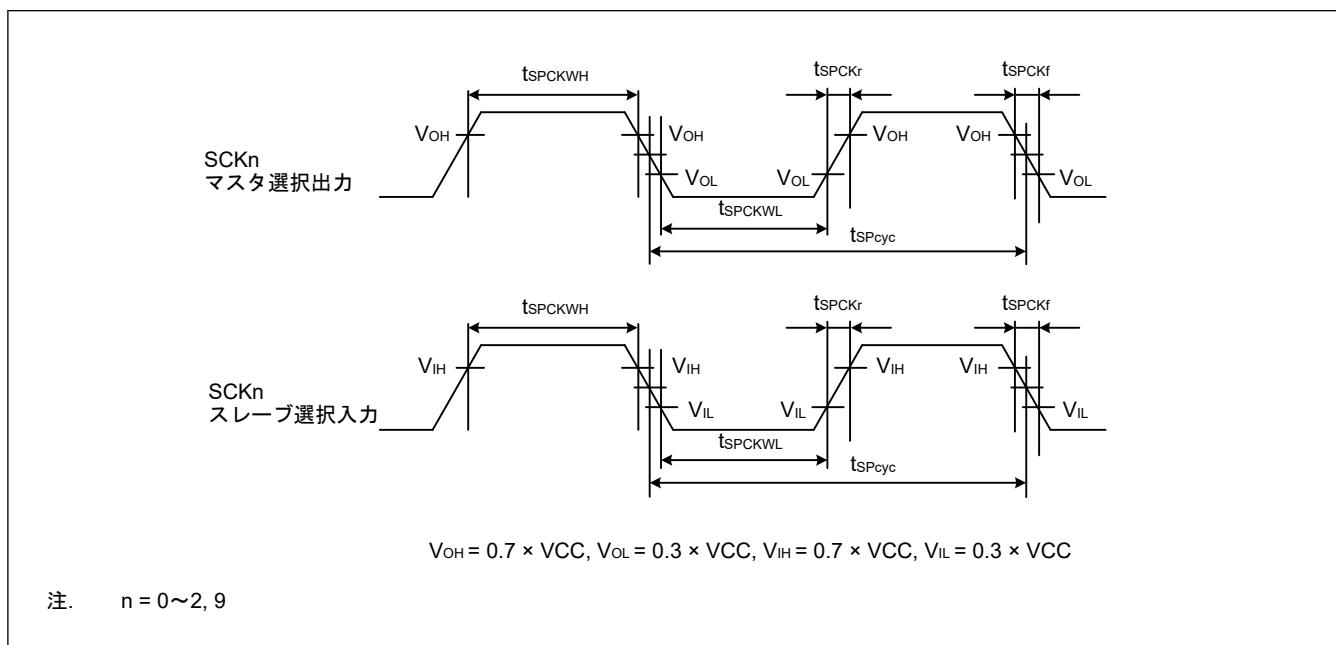

図 2.1 は、タイミング条件を示しています。

図 2.1 入出力タイミング計測条件

各周辺モジュールのタイミング仕様の計測条件は、最適な周辺動作に推奨されるものです。ただし、ユーザーシステムの条件に合うように、各端子の駆動能力を調整してください。

同じ機能に使用される各機能端子は、同じ駆動能力を選択してください。各機能端子の I/O 駆動能力が混在する場合、各機能の A/C 仕様は保証されません。

### 2.1 絶対最大定格

表 2.1 絶対最大定格

| 項目                 | シンボル      | 値                                 | 単位 |

|--------------------|-----------|-----------------------------------|----|

| 電源電圧               | $V_{CC}$  | $-0.5 \sim +6.5$                  | V  |

| 入力電圧               | $V_{in}$  | $-0.3 \sim +6.5$                  | V  |

|                    | $V_{in}$  | $-0.3 \sim AVCC0 + 0.3$           | V  |

|                    | $V_{in}$  | $-0.3 \sim VCC + 0.3$             | V  |

| リファレンス電源電圧         | $VREFH0$  | $-0.3 \sim +6.5$                  | V  |

| アナログ電源電圧           | $AVCC0$   | $-0.5 \sim +6.5$                  | V  |

| アナログ入力電圧           | $V_{AN}$  | $-0.3 \sim AVCC0 + 0.3$           | V  |

|                    |           | $-0.3 \sim VCC + 0.3$             | V  |

| 動作温度(注2) (注3) (注4) | $T_{opr}$ | $-40 \sim +85$<br>$-40 \sim +105$ | °C |

| ストレージ温度            | $T_{stg}$ | $-55 \sim +125$                   | °C |

注 1. P400、P401、P407 は 5 V トレント対応ポートです。

デバイスの電源が切れている状態で信号や I/O プルアップ電源を入力しないでください。信号または I/O プルアップの入力による電流注入は、デバイスの故障や異常電流を引き起こし、内部素子を劣化させる恐れがあります。

- 注 2. 「[2.2.1. T<sub>j</sub>/T<sub>a</sub> の定義](#)」を参照してください。

注 3. T<sub>a</sub> = +85°C ~ +105°C でのディレーティング動作については、Renesas Electronics の営業担当にお問い合わせください。

ディレーティングとは、信頼性を改善するために負荷を系統的に軽減することです。

注 4. 動作温度の上限は、85°C または 105°C です（製品によります）。

**【使用上の注意】絶対最大定格を超えて MCU を使用した場合、MCU の永久破壊となることがあります。**

VREFH0 が ADC12 の高電位基準電圧に選択されている場合にノイズ干渉による誤動作を防止するには、VCC 端子と VSS 端子の間、AVCC0 端子と AVSS0 端子の間、VREFH0 端子と VREFL0 端子の間には周波特性の良いコンデンサを挿入してください。以下に示す値のコンデンサができる限り各電源端子の近くに配置し、最短距離かつできる限り太いトレースを使用してください。

- VCC と VSS : 約 0.1 μF

- AVCC0 と AVSS0 : 約 0.1 μF

- VREFH0 と VREFL0 : 約 0.1 μF

また、コンデンサは安定容量として接続してください。

VCL 端子は、4.7 μF のコンデンサを介して VSS 端子に接続してください。各コンデンサは端子の近くに配置してください。

**表 2.2 推奨動作条件**

| 項目       | シンボル                       | Min            | Typ | Max   | 単位 |

|----------|----------------------------|----------------|-----|-------|----|

| 電源電圧     | VCC <sup>(注1)</sup> (注2)   | 1.6            | —   | 5.5   | V  |

|          | VSS                        | —              | 0   | —     | V  |

| アナログ電源電圧 | AVCC0 <sup>(注1)</sup> (注2) | 1.6            | —   | 5.5   | V  |

|          | AVSS0                      | —              | 0   | —     | V  |

|          | VREFH0                     | ADC12 基準として使用時 | —   | AVCC0 | V  |

|          | VREFL0                     |                |     | —     | V  |

注 1. 下記の条件で AVCC0 と VCC を使用してください：

AVCC0 = VCC

注 2. VCC 端子および AVCC0 端子に電源を投入する場合、両方同時に電源投入するか、最初に VCC 端子、次に AVCC0 端子の順番で電源投入してください。

VCC 端子および AVCC0 端子の電源供給を停止する場合、両方同時に電源供給を停止するか、最初に AVCC0 端子、次に VCC 端子の順番で電源供給を停止してください。

## 2.2 DC 特性

### 2.2.1 T<sub>j</sub>/T<sub>a</sub> の定義

**表 2.3 DC 特性**

条件：動作温度 (T<sub>a</sub>) が -40 ~ +105 °C の製品

| 項目          | シンボル           | Typ | Max                 | 単位 | 測定条件                                                                    |

|-------------|----------------|-----|---------------------|----|-------------------------------------------------------------------------|

| 許容ジャンクション温度 | T <sub>j</sub> | —   | 125                 | °C | High-speed モード<br>Middle-speed モード<br>Low-Speed モード<br>Subosc-Speed モード |

|             |                |     | 105 <sup>(注1)</sup> |    |                                                                         |

注. T<sub>j</sub> = T<sub>a</sub> + θ<sub>ja</sub> × 総消費電力 (W) となるようにしてください。このとき、総消費電力 = (VCC - V<sub>OH</sub>) × ΣI<sub>OH</sub> + V<sub>OL</sub> × ΣI<sub>OL</sub> + I<sub>CCmax</sub> × VCC です。

注 1. 動作温度の上限は、85 °C または 105 °C です（製品による）。型名が動作温度の上限 85 °C を示している場合、T<sub>j</sub> の最大値は 105 °C になります。それ以外の場合 125 °C になります。

2.2.2 I/O  $V_{IH}$ ,  $V_{IL}$ 表 2.4 I/O  $V_{IH}$ ,  $V_{IL}$ 条件 :  $VCC = AVCC0 = 1.6 \sim 5.5$  V

| 項目                   | ポート&機能                              |                              | シンボル | Min                | Max                | 単位 | 測定条件                   |

|----------------------|-------------------------------------|------------------------------|------|--------------------|--------------------|----|------------------------|

| 入力電圧                 | 入力ポート端子<br>P000~P002, P010~P015     | $V_{IH}$                     |      | $AVCC0 \times 0.8$ | —                  | V  | —                      |

|                      |                                     | $V_{IL}$                     |      | —                  | $AVCC0 \times 0.2$ |    |                        |

|                      | P000~P002, P010~P015 を<br>除く入力ポート端子 | $V_{IH}$                     |      | $VCC \times 0.8$   | —                  |    |                        |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.2$   |    |                        |

|                      | EXTAL                               | $V_{IH}$                     |      | $VCC \times 0.8$   | —                  |    |                        |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.2$   |    |                        |

|                      | 5 V トレラントポート <sup>(注3)</sup>        | $V_{IH}$                     |      | $VCC \times 0.8$   | 5.8                |    |                        |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.2$   |    |                        |

|                      | RES, NMI, IRQ <sup>(注4)</sup>       | $V_{IH}$                     |      | $VCC \times 0.8$   | —                  |    |                        |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.2$   |    |                        |

|                      |                                     | $\Delta V_T$ <sup>(注6)</sup> |      | $VCC \times 0.10$  | —                  |    | $VCC = 2.7 \sim 5.5$ V |

|                      |                                     |                              |      | $VCC \times 0.05$  | —                  |    | $VCC = 1.6 \sim 2.7$ V |

| 周辺機能 <sup>(注5)</sup> | IIC (SMBus を<br>除く) <sup>(注1)</sup> | $V_{IH}$                     |      | $VCC \times 0.7$   | 5.8                |    | —                      |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.3$   |    |                        |

|                      |                                     | $\Delta V_T$ <sup>(注6)</sup> |      | $VCC \times 0.10$  | —                  |    | $VCC = 2.7 \sim 5.5$ V |

|                      |                                     |                              |      | $VCC \times 0.05$  | —                  |    | $VCC = 1.6 \sim 2.7$ V |

|                      | IIC (SMBus)<br>(注2)                 | $V_{IH}$                     |      | 2.2                | —                  |    | $VCC = 3.6 \sim 5.5$ V |

|                      |                                     | $V_{IL}$                     |      | 2.0                | —                  |    | $VCC = 2.7 \sim 3.6$ V |

|                      |                                     | $V_{IL}$                     |      | —                  | 0.8                |    | $VCC = 3.6 \sim 5.5$ V |

|                      |                                     | $V_{IL}$                     |      | —                  | 0.5                |    | $VCC = 2.7 \sim 3.6$ V |

|                      | その他の周辺<br>機能                        | $V_{IH}$                     |      | $VCC \times 0.8$   | —                  |    | —                      |

|                      |                                     | $V_{IL}$                     |      | —                  | $VCC \times 0.2$   |    |                        |

|                      |                                     | $\Delta V_T$ <sup>(注6)</sup> |      | $VCC \times 0.10$  | —                  |    | $VCC = 2.7 \sim 5.5$ V |

|                      |                                     |                              |      | $VCC \times 0.05$  | —                  |    | $VCC = 1.6 \sim 2.7$ V |

注 1. SCL0\_A, SDA0\_A, SDA0\_B (合計 3 端子)

注 2. SCL0\_A, SCL0\_C, SDA0\_A, SDA0\_B, SCL0\_D, SDA0\_C (合計 6 端子)

注 3. P400, P401, P407 (合計 3 端子)

注 4. PmnPFS.ISEL = 1

注 5. PmnPFS.PMR = 1

注 6. これはシュミットトリガ回路のヒステリシス特性です。

2.2.3 I/O  $I_{OH}$ ,  $I_{OL}$ 表 2.5 I/O  $I_{OH}$ ,  $I_{OL}$  (1/3)条件 :  $VCC = AVCC0 = 1.6 \sim 5.5$  V

| 項目                    | シンボル                                                      | Min      | Typ | Max | 単位   | 測定条件 |

|-----------------------|-----------------------------------------------------------|----------|-----|-----|------|------|

| 許容出力電流 (端子ご<br>との最大値) | ポート P000~P002, P010~P015,<br>P212, P213, P400, P401, P407 | $I_{OH}$ | —   | —   | -4.0 | mA   |

|                       |                                                           | $I_{OL}$ | —   | —   | 8.0  | mA   |

|                       | その他の出力端子 <sup>(注1)</sup>                                  | $I_{OH}$ | —   | —   | -4.0 | mA   |

|                       |                                                           | $I_{OL}$ | —   | —   | 20.0 | mA   |

表 2.5 I/O  $I_{OH}$ ,  $I_{OL}$  (2/3)

条件 : VCC = AVCC0 = 1.6~5.5 V

| 項目                                                  | シンボル                  | Min | Typ | Max  | 単位 | 測定条件              |

|-----------------------------------------------------|-----------------------|-----|-----|------|----|-------------------|

| 許容出力電流 (全端子の最大値) (注2)                               | $\Sigma I_{OH}(\max)$ | —   | —   | -30  | mA | AVCC0 = 2.7~5.5 V |

|                                                     |                       | —   | —   | -8   |    | AVCC0 = 1.8~2.7 V |

|                                                     |                       | —   | —   | -4   |    | AVCC0 = 1.6~1.8 V |

|                                                     |                       | —   | —   | 50   |    | AVCC0 = 2.7~5.5 V |

|                                                     |                       | —   | —   | 4    |    | AVCC0 = 1.8~2.7 V |

|                                                     |                       | —   | —   | 2    |    | AVCC0 = 1.6~1.8 V |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | -8   | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -2   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -1   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 16.0 |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 1.2  |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 0.6  |    | VCC = 1.6~1.8 V   |

| ポート P000~P002, P010~P015 の合計                        | $\Sigma I_{OH}(\max)$ | —   | —   | -30  | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -8   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -4   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | -30  | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -8   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -4   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

| ポート P212, P213 の合計                                  | $\Sigma I_{OH}(\max)$ | —   | —   | -8   | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -2   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -1   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 16.0 |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 1.2  |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 0.6  |    | VCC = 1.6~1.8 V   |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | —    |    | —                 |

| ポート P206~P208, P400, P401, P407~P409, P913~P915 の合計 | $\Sigma I_{OH}(\max)$ | —   | —   | -30  | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -8   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -4   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | -30  | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -8   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -4   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

| ポート P100~P104, P108~P112, P201, P300~P302, P500 の合計 | $\Sigma I_{OH}(\max)$ | —   | —   | -30  | mA | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | -8   |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | -4   |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | 50   |    | VCC = 2.7~5.5 V   |

|                                                     |                       | —   | —   | 4    |    | VCC = 1.8~2.7 V   |

|                                                     |                       | —   | —   | 2    |    | VCC = 1.6~1.8 V   |

|                                                     |                       | —   | —   | —    |    | —                 |

| 全出力端子の総和                                            | $\Sigma I_{OH}(\max)$ | —   | —   | -60  | mA | —                 |

|                                                     | $\Sigma I_{OL}(\max)$ | —   | —   | 100  |    | —                 |

表 2.5 I/O  $I_{OH}$ ,  $I_{OL}$  (3/3)

条件 : VCC = AVCC0 = 1.6~5.5 V

| 項目                    | シンボル                   | Min | Typ | Max  | 単位 | 測定条件              |

|-----------------------|------------------------|-----|-----|------|----|-------------------|

| 許容出力電流 (全端子の最大値) (注2) | $\Sigma I_{OH} (\max)$ | —   | —   | -24  | mA | AVCC0 = 2.7~5.5 V |

|                       |                        | —   | —   | -6   |    | AVCC0 = 1.8~2.7 V |

|                       |                        | —   | —   | -3   |    | AVCC0 = 1.6~1.8 V |

|                       |                        | —   | —   | 48   |    | AVCC0 = 2.7~5.5 V |

|                       |                        | —   | —   | 3.6  |    | AVCC0 = 1.8~2.7 V |

|                       |                        | —   | —   | 1.8  |    | AVCC0 = 1.6~1.8 V |

|                       | $\Sigma I_{OL} (\max)$ | —   | —   | -8   | mA | VCC = 2.7~5.5 V   |

|                       |                        | —   | —   | -2   |    | VCC = 1.8~2.7 V   |

|                       |                        | —   | —   | -1   |    | VCC = 1.6~1.8 V   |

|                       |                        | —   | —   | 16.0 |    | VCC = 2.7~5.5 V   |

|                       |                        | —   | —   | 1.2  |    | VCC = 1.8~2.7 V   |

|                       |                        | —   | —   | 0.6  |    | VCC = 1.6~1.8 V   |

| 他の出力ポートの合計            | $\Sigma I_{OH} (\max)$ | —   | —   | -30  | mA | VCC = 4.0~5.5 V   |

|                       |                        | —   | —   | -20  |    | VCC = 2.7~4.0 V   |

|                       |                        | —   | —   | -12  |    | VCC = 1.8~2.7 V   |

|                       |                        | —   | —   | -6   |    | VCC = 1.6~1.8 V   |

|                       | $\Sigma I_{OL} (\max)$ | —   | —   | 50   |    | VCC = 4.0~5.5 V   |

|                       |                        | —   | —   | 20   |    | VCC = 2.7~4.0 V   |

|                       |                        | —   | —   | 8    |    | VCC = 1.8~2.7 V   |

|                       |                        | —   | —   | 4    |    | VCC = 1.6~1.8 V   |

|                       | $\Sigma I_{OH} (\max)$ | —   | —   | -54  | mA | —                 |

|                       |                        | —   | —   | 98   |    | —                 |

注 1. 入力ポートである P200、P214、P215 を除きます。

注 2. デューティー比  $\leq 70\%$  の条件下での仕様です。デューティー比  $> 70\%$  の場合、出力電流値は次式で計算できます (デューティー比を 70% から n% に変更するとき)。端子の合計出力電流 =  $(I_{OH} \times 0.7) / (n \times 0.01)$ <例> n = 80% で、 $I_{OH} = -30.0 \text{ mA}$  のとき端子の合計出力電流 =  $(-30.0 \times 0.7) / (80 \times 0.01) \approx -26.2 \text{ mA}$

ただし、1 つの端子に入力可能な電流はデューティー比によって変化しません。

【使用上の注意】MCU の信頼性を確保するため、出力電流値は表 2.5 の値を超えないようにしてください。

2.2.4 I/O  $V_{OH}$ ,  $V_{OL}$ 、その他の特性表 2.6 I/O  $V_{OH}$ ,  $V_{OL}$  (1)

条件 : VCC = AVCC0 = 4.0~5.5 V

| 項目   | シンボル                                                            | Min      | Typ         | Max | 単位 | 測定条件                       |

|------|-----------------------------------------------------------------|----------|-------------|-----|----|----------------------------|

| 出力電圧 | ポート P000~P002, P010~P015                                        | $V_{OH}$ | AVCC0 - 0.8 | —   | V  | $I_{OH} = -4.0 \text{ mA}$ |

|      | P000~P002, P010~P015 以外の出力端子 (注1)                               | $V_{OH}$ | VCC - 0.8   | —   |    | $I_{OH} = -4.0 \text{ mA}$ |

|      | ポート P000~P002, P010~P015                                        | $V_{OL}$ | —           | —   |    | $I_{OL} = 8.0 \text{ mA}$  |

|      | ポート P212, P213, P400, P401, P407                                | $V_{OL}$ | —           | —   |    | $I_{OL} = 8.0 \text{ mA}$  |

|      | P000~P002, P010~P015, P212, P213, P400, P401, P407 以外の出力端子 (注1) | $V_{OL}$ | —           | —   |    | $I_{OL} = 20.0 \text{ mA}$ |

|      |                                                                 |          |             | 1.2 |    |                            |

注 1. 入力ポートである P200、P214、P215 を除きます。

表 2.7 I/O  $V_{OH}$ 、 $V_{OL}$  (2)条件 :  $VCC = AVCC0 = 2.7 \sim 4.0 \text{ V}$

| 項目   |                                      | シンボル     | Min         | Typ | Max | 単位 | 測定条件                       |

|------|--------------------------------------|----------|-------------|-----|-----|----|----------------------------|

| 出力電圧 | ポート P000～P002, P010～P015             | $V_{OH}$ | AVCC0 - 0.8 | —   | —   | V  | $I_{OH} = -4.0 \text{ mA}$ |

|      | P000～P002, P010～P015 以外の出力端子<br>(注1) | $V_{OH}$ | VCC - 0.8   | —   | —   |    | $I_{OH} = -4.0 \text{ mA}$ |

|      | ポート P000～P002, P010～P015             | $V_{OL}$ | —           | —   | 0.8 |    | $I_{OL} = 8.0 \text{ mA}$  |

|      | P000～P002, P010～P015 以外の出力端子<br>(注1) | $V_{OL}$ | —           | —   | 0.8 |    | $I_{OL} = 8.0 \text{ mA}$  |

注 1. 入力ポートである P200、P214、P215 を除きます。

表 2.8 I/O  $V_{OH}$ 、 $V_{OL}$  (3)条件 :  $VCC = AVCC0 = 1.6 \sim 2.7 \text{ V}$

| 項目   |                                      | シンボル     | Min         | Typ | Max | 単位 | 測定条件                                                           |

|------|--------------------------------------|----------|-------------|-----|-----|----|----------------------------------------------------------------|

| 出力電圧 | ポート P000～P002, P010～P015             | $V_{OH}$ | AVCC0 - 0.5 | —   | —   | V  | $I_{OH} = -1.0 \text{ mA}$<br>$AVCC0 = 1.8 \sim 2.7 \text{ V}$ |

|      |                                      |          | AVCC0 - 0.5 | —   | —   |    | $I_{OH} = -0.5 \text{ mA}$<br>$AVCC0 = 1.6 \sim 1.8 \text{ V}$ |

|      | P000～P002, P010～P015 以外の出力端子<br>(注1) | $V_{OH}$ | VCC - 0.5   | —   | —   |    | $I_{OH} = -1.0 \text{ mA}$<br>$VCC = 1.8 \sim 2.7 \text{ V}$   |

|      |                                      |          | VCC - 0.5   | —   | —   |    | $I_{OH} = -0.5 \text{ mA}$<br>$VCC = 1.6 \sim 1.8 \text{ V}$   |

|      | ポート P000～P002, P010～P015             | $V_{OL}$ | —           | —   | 0.4 | V  | $I_{OL} = 0.6 \text{ mA}$<br>$AVCC0 = 1.8 \sim 2.7 \text{ V}$  |

|      |                                      |          | —           | —   | 0.4 |    | $I_{OL} = 0.3 \text{ mA}$<br>$AVCC0 = 1.6 \sim 1.8 \text{ V}$  |

|      | P000～P002, P010～P015 以外の出力端子<br>(注1) | $V_{OL}$ | —           | —   | 0.4 |    | $I_{OL} = 0.6 \text{ mA}$<br>$VCC = 1.8 \sim 2.7 \text{ V}$    |

|      |                                      |          | —           | —   | 0.4 |    | $I_{OL} = 0.3 \text{ mA}$<br>$VCC = 1.6 \sim 1.8 \text{ V}$    |

注 1. 入力ポートである P200、P214、P215 を除きます。

表 2.9 I/O その他の特性

条件 :  $VCC = AVCC0 = 1.6 \sim 5.5 \text{ V}$

| 項目                  |                                              | シンボル        | Min | Typ | Max | 単位               | 測定条件                                                                      |

|---------------------|----------------------------------------------|-------------|-----|-----|-----|------------------|---------------------------------------------------------------------------|

| 入力リーケ電流             | RES、ポート P200、P214、P215                       | $ I_{in} $  | —   | —   | 1.0 | $\mu\text{A}$    | $V_{in} = 0 \text{ V}$<br>$V_{in} = VCC$                                  |

| スリーステートリーケ電流 (オフ状態) | 5 V トレントポート <sup>(注1)</sup>                  | $ I_{TSI} $ | —   | —   | 1.0 | $\mu\text{A}$    | $V_{in} = 0 \text{ V}$<br>$V_{in} = 5.8 \text{ V}$                        |

|                     | その他のポート<br>(P200、P214、P215、5 V トレント対応ポートを除く) |             | —   | —   | 1.0 |                  | $V_{in} = 0 \text{ V}$<br>$V_{in} = VCC$                                  |

| 入力プルアップ抵抗           | 全ポート<br>(P200、P214、P215 を除く)                 | $R_U$       | 10  | 20  | 100 | $\text{k}\Omega$ | $V_{in} = 0 \text{ V}$                                                    |

| 入力容量                | P200                                         | $C_{in}$    | —   | —   | 30  | $\text{pF}$      | $V_{in} = 0 \text{ V}$<br>$f = 1 \text{ MHz}$<br>$T_a = 25^\circ\text{C}$ |

|                     | その他の入力端子                                     |             | —   | —   | 15  |                  |                                                                           |

注 1. P400, P401, P407 (合計 3 端子)

## 2.2.5 動作電流とスタンバイ電流

表 2.10 動作電流とスタンバイ電流 (1) (1/2)

条件 : VCC = AVCC0 = 1.6~5.5 V

| 項目           | 消費電流<br>(注1)                   | High-speed モード <sup>(注2)</sup> | ノーマル モード                                             | すべての周辺クロックが無効、CoreMark コードはフラッシュから実行 <sup>(注5)</sup> | ICLK = 48 MHz | I <sub>CC</sub> | シンボル | Typ<br>(注10) | Max | 単位   | 測定条件 |  |  |  |

|--------------|--------------------------------|--------------------------------|------------------------------------------------------|------------------------------------------------------|---------------|-----------------|------|--------------|-----|------|------|--|--|--|

| 消費電流<br>(注1) | High-speed モード <sup>(注2)</sup> | ノーマル モード                       | すべての周辺クロックが無効、CoreMark コードはフラッシュから実行 <sup>(注5)</sup> | ICLK = 32 MHz                                        | 4.80          | —               | mA   | (注7) (注11)   | —   | (注7) | (注7) |  |  |  |

|              |                                |                                |                                                      | ICLK = 16 MHz                                        | 3.45          | —               |      |              |     |      |      |  |  |  |

|              |                                |                                |                                                      | ICLK = 8 MHz                                         | 2.05          | —               |      |              |     |      |      |  |  |  |

|              |                                |                                |                                                      | —                                                    | 1.40          | —               |      |              |     |      |      |  |  |  |

|              |                                |                                | すべての周辺クロックが有効、コードはフラッシュから実行 <sup>(注5)</sup>          | ICLK = 48 MHz                                        | —             | 12.0            |      | (注9) (注11)   | —   |      | (注7) |  |  |  |

|              | スリープ モード                       | すべての周辺クロックが無効 <sup>(注5)</sup>  |                                                      | ICLK = 32 MHz                                        | 1.05          | —               |      |              |     |      |      |  |  |  |

|              |                                |                                |                                                      | ICLK = 16 MHz                                        | 0.85          | —               |      | (注7)         | —   |      |      |  |  |  |

|              |                                |                                |                                                      | ICLK = 8 MHz                                         | 0.70          | —               |      |              |     |      |      |  |  |  |

|              |                                | すべての周辺クロックが有効 <sup>(注5)</sup>  | ICLK = 48 MHz                                        | 0.60                                                 | —             | (注9)            |      | —            |     |      | (注8) |  |  |  |

|              |                                |                                | ICLK = 32 MHz                                        | 4.15                                                 | —             |                 |      |              |     |      |      |  |  |  |

|              |                                |                                | ICLK = 16 MHz                                        | 3.95                                                 | —             | (注8)            |      | —            |     |      |      |  |  |  |

|              |                                |                                | ICLK = 8 MHz                                         | 2.25                                                 | —             |                 |      |              |     |      |      |  |  |  |

|              |                                |                                | —                                                    | 1.35                                                 | —             |                 |      |              |     |      |      |  |  |  |

|              |                                | BGO 動作時の増加分 <sup>(注6)</sup>    | —                                                    | 2.1                                                  | —             |                 |      | —            |     |      |      |  |  |  |

表 2.10 動作電流とスタンバイ電流 (1) (2/2)

条件 : VCC = AVCC0 = 1.6~5.5 V

| 項目           |                      |                      |                                          |                                          | シンボル              | Typ<br>(注10)    | Max  | 単位  | 測定条件 |      |

|--------------|----------------------|----------------------|------------------------------------------|------------------------------------------|-------------------|-----------------|------|-----|------|------|